# University of Windsor Scholarship at UWindsor

**Electronic Theses and Dissertations**

1991

## High performance VLSI circuit techniques.

Sami. Bizzan University of Windsor

Follow this and additional works at: http://scholar.uwindsor.ca/etd

#### Recommended Citation

Bizzan, Sami., "High performance VLSI circuit techniques." (1991). Electronic Theses and Dissertations. Paper 2296.

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

Bibliotnèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada K1A 0N4

#### NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

#### **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microf.lmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

# HIGH PERFORMANCE VLSI CIRCUIT TECHNIQUES

by

#### Sami Bizzan

#### A Thesis

Submitted to the Faculty of Graduate Studies through the

Department of Electrical Engineering in Partial Fulfillment

of the Requirements for the Degree of

Master of Applied Science at the

University of Windsor

Windsor, Ontario, Canada December, 1991

Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada K1A 0N4

The author has granted an irrevocable nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission.

L'auteur a accordé une licence irrévocable et non exclusive permetiant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-72802-7

## Sami Bizzan 1991

© All Rights Reserved

#### **ABSTRACT**

In this thesis a novel analytical approach to sizing NFET chains is presented. The technique allows a delay-area curve to be easily obtained, allowing trade-off decisions by the circuit designer. If the NFET chain is limited by a maximum gate width, the problem of optimum sizing is transformed to a single-variable optimization procedure, thus saving a substantial amount of CPU time. A unique channel resistance approximation method for use in the transistor sizing problem is presented which yields improved results over prior published methods. This thesis also develops a simple model to enable sizing of the precharge PFET; acceptable results are obtained. Finally, some problems inherent with dynamic logic structures are discussed and some possible remedies are suggested.

#### **ACKNOWLEDGEMENTS**

#### Thank you GOD for giving me the chance to be alive

I would like to express my sincere thanks and appreciation to Dr. G. A. Jullien and Dr. W. C. Miller for their tremendous support and guidance throughout the progress of this thesis. I would also like to thank Bruce Erickson and the VLSI research group members for their valuable help when it was needed. I would like to thank my wife for her encouragement and patience during the hard times of this research. Last but not the least, I would like to express my appreciation to my father, mother, brothers, and sisters for giving me the moral support needed to complete this work.

## TABLE OF CONTENTS

| ABSTRACTi                                         | V   |

|---------------------------------------------------|-----|

| ACKNOWLEDGEMENTS                                  | ,   |

| TABLE OF CONTENTS                                 | ⁄i  |

| LIST OF FIGURES                                   | ζ.  |

| LIST OF TABLES                                    | civ |

| Chapter 1: Introduction                           | l   |

| 1.1 Introduction                                  | 1   |

| 1.2 Research Objectives                           | 3   |

| 1.3 Thesis Organization                           | 4   |

| Chapter 2: CMOS Logic Gates                       | 6   |

| 2.1 Introduction                                  | 6   |

| 2.2 Logic Gate Delay Characterization             | 6   |

| 2.2.1 FET Delay                                   | 6   |

| 2.2.2 Inverter Delay                              | 8   |

| 2.2.3 Switching Node Delay                        | 9   |

| 2.3 Static Versus Dynamic Gates                   | 10  |

| 2.3.1 CMOS Static Gate Structure                  | 10  |

| 2.3.2 CMOS Dynamic Gate Structure                 | 11  |

| 2.3.3 Comparison between Static and Dynamic Gates | 13  |

| 2.4 Worst Case Methodology                        | 15  |

| 2.5 RC Chain and Elmore's Delay Formula                        | 15   |

|----------------------------------------------------------------|------|

| 2.6 Monotonicity of the Delay with Area                        | 21   |

| 2.7 Accuracy of Elmore's Delay Formula                         | 22   |

| Chapter 3: Transistor Sizing Approaches for NFET Chains        | 25   |

| 3.1 Introduction                                               | 25   |

| 3.2 Discharge Delay of an NFET Chain                           | . 27 |

| 3.2.1 Precharge Cycle                                          | . 28 |

| 3.2.2 Evaluation Cycle                                         | . 29 |

| 3.3 RC Model                                                   | . 30 |

| 3.4 Parasitic Capacitance Approximation                        | . 33 |

| 3.5 Channel Resistance Approximation                           | . 36 |

| 3.5.1 Channel Resistance Approximation for Linear Region NFETs | . 37 |

| 3.5.2 Channel Resistance Approximation for Saturation Region   |      |

| NFET                                                           | . 38 |

| 3.6 A Survey of Optimization Approach to NFET Sizing           | . 39 |

| 3.6.1 Optimization I                                           | . 40 |

| 3.6.2 Optimization II                                          | .41  |

| 3.7 Analytical Approach to NFET Sizing                         | . 42 |

| 3.7.1 Analytical Approach                                      | . 43 |

| 3.7.2 Single Variable Optimization                             | .44  |

| 3.8 Results and Discussions                                    | . 45 |

| 3.9 Summary                                                    | . 50 |

| Chapter 4: Practical Aspects of Circuit Sizing                 | . 52 |

| 4.1 Introduction                                               | . 52 |

| 4.2 Precharge PFET Sizing                           | 53 |

|-----------------------------------------------------|----|

| 4.2.1 Precharge Delay Model                         | 53 |

| 4.2.2 Precharge Channel Resistance Approximation    | 57 |

| 4.2.3 PFET Sizing Algorithm                         | 58 |

| 4.2.4 Precharge PFET Sizing Results and Discussions | 59 |

| 4.3 Charge Sharing                                  | 63 |

| 4.3.1 Charge Sharing Problem                        | 63 |

| 4.3.2 Transistor Sizing and Charge Sharing          | 64 |

| 4.3.3 Remedies to the Charge Sharing Problem        | 67 |

| 4.4 Summary                                         | 70 |

| Chapter 5: Conclusions and Further Research         |    |

| 5.2 Conclusions                                     |    |

|                                                     |    |

| 5.3 Further Research                                | /3 |

| REFERENCES                                          | 74 |

| Appendix A: 3μ-DLM Technology SPICE Parameters and  |    |

| RC Model Computed Parameters                        |    |

| A.1 SPICE Transistor Parameters                     | 78 |

| A.2 RC Model Computed Parameters                    | 79 |

| Appendix B: NFET Chain Sizing Source Codes          | 81 |

| B.1 OPTIMIZATION I Source Code                      | 82 |

| B.2 OPTIMIZATION II Source Code                     | 92 |

| B.3 SINGLE-VARIABLE OPTIMIZATION Source Code        | 10 |

| B.4 ANALYTICAL APPROACH Source Code111                  |

|---------------------------------------------------------|

| Appendix C: Precharge PFET Sizing Source Codes          |

| C.1 Precharge Delay Approximation Source Code           |

| C.2 Precharge PFET Sizing Source Code                   |

| Appendix D: A Report on the Design, Layout, and Testing |

| of 4-bit Parallel Full Adder141                         |

| D.1 Introduction142                                     |

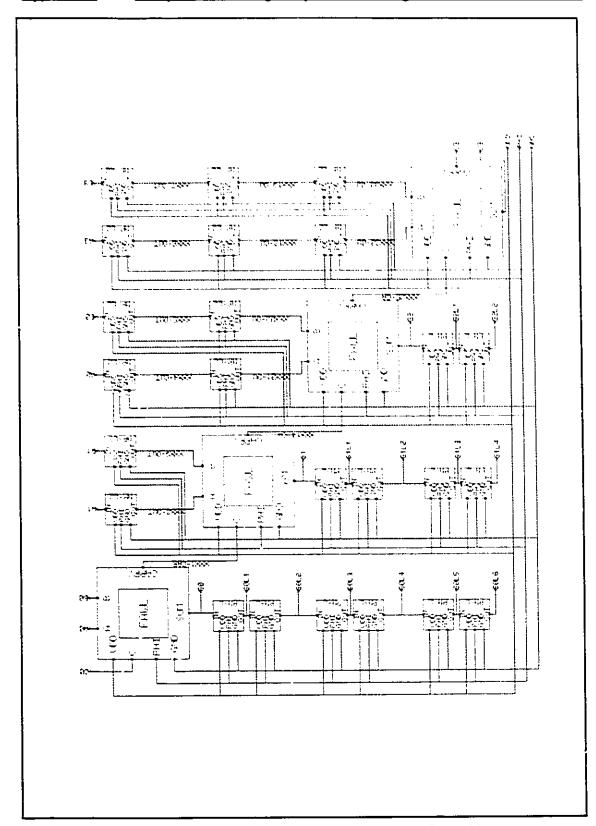

| D.2 Circuit Design142                                   |

| D.2.1 Latches                                           |

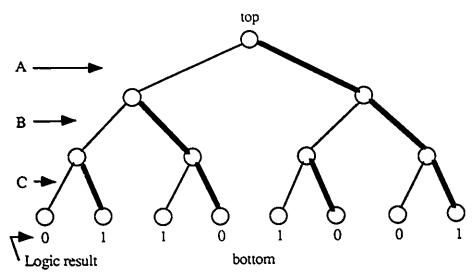

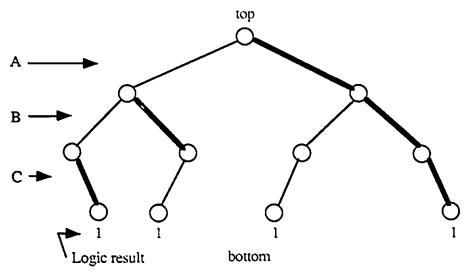

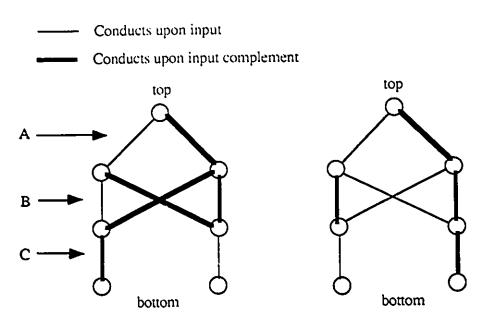

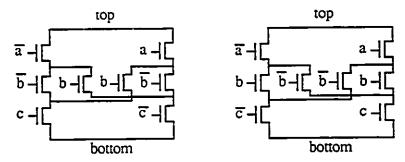

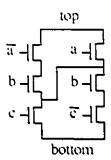

| D.2.2 Switching Graph Method143                         |

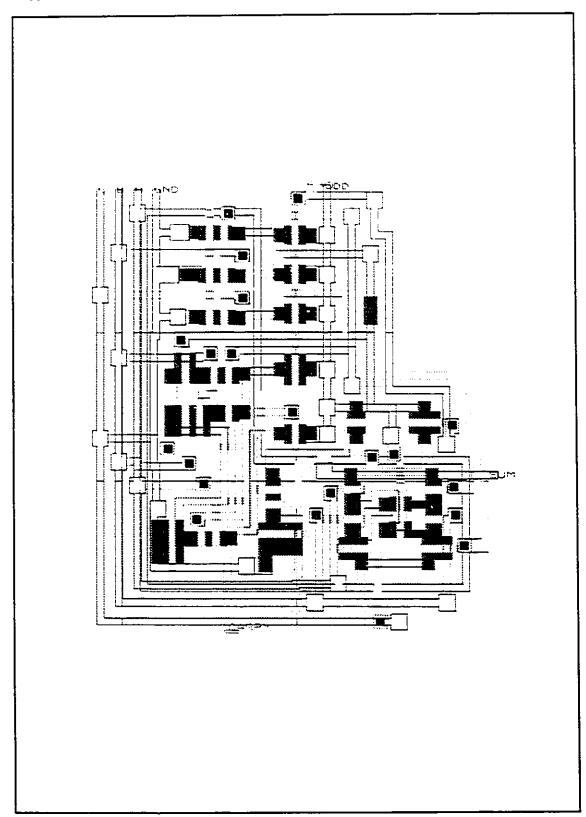

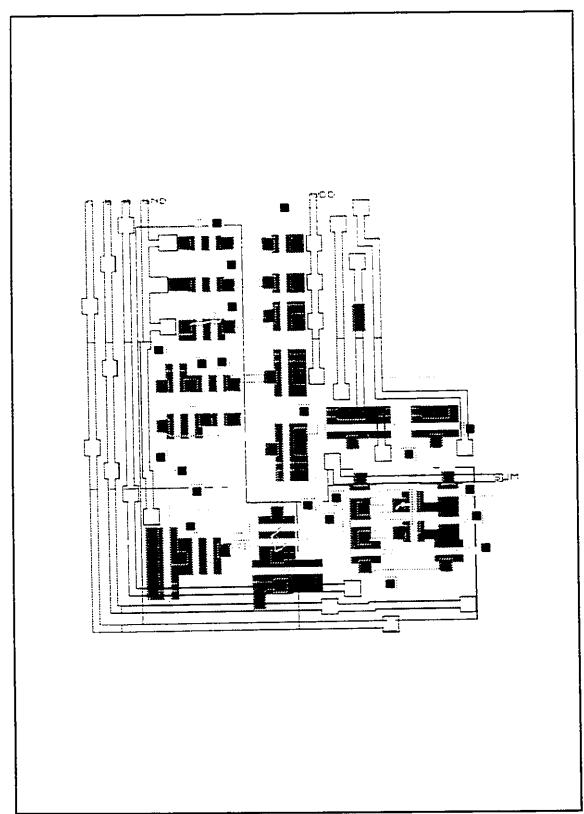

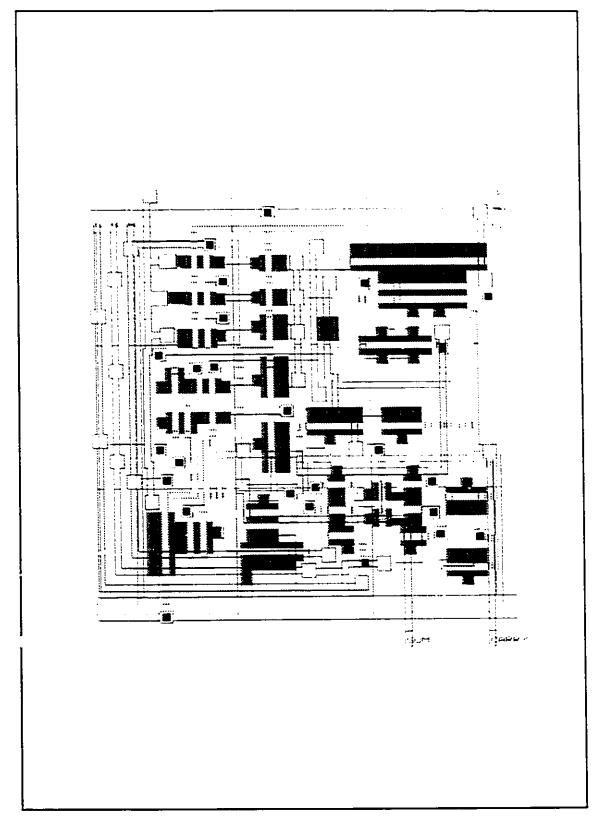

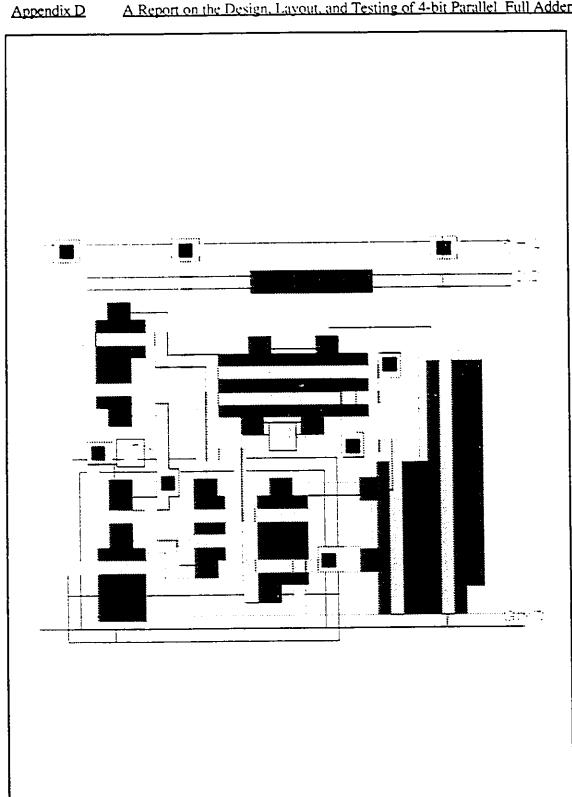

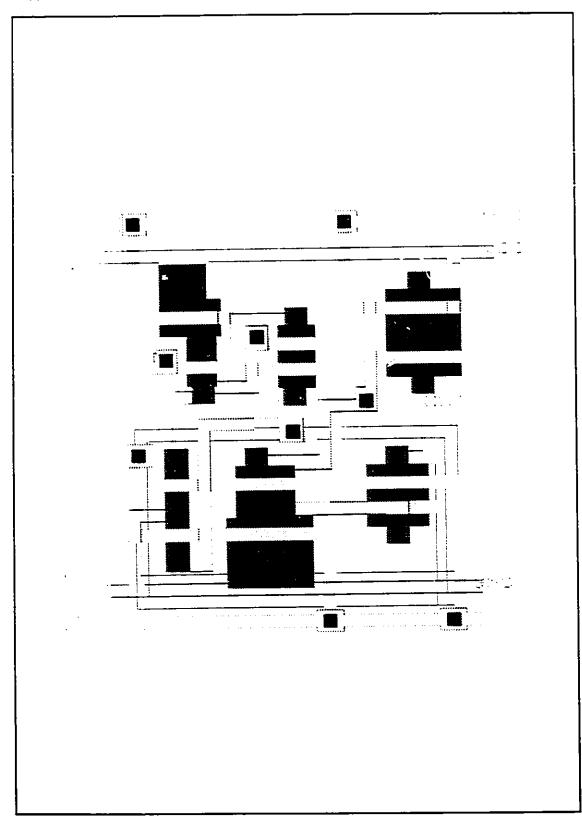

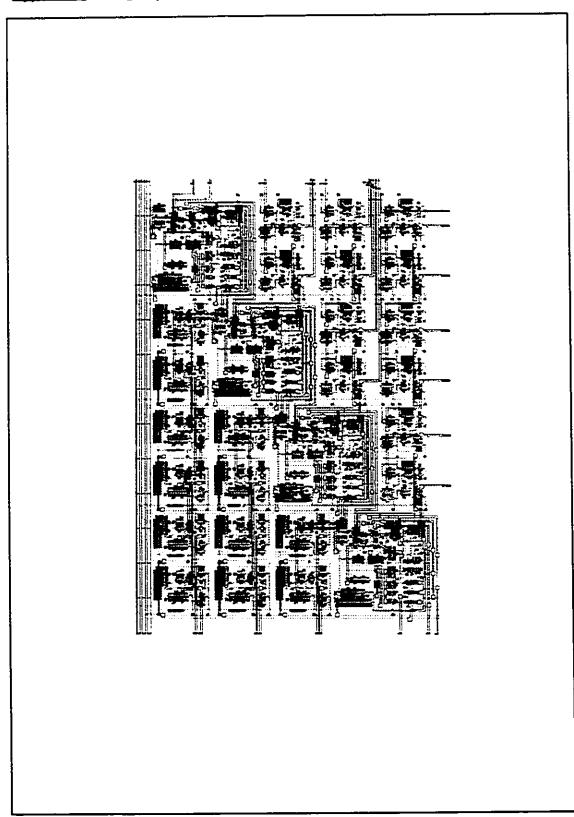

| D.3 Full Adder Layout150                                |

| D.3.1 Initial Full Adder Cell Layout                    |

| D.3.2 Full Adder Cell Manual Transistor Sizing          |

| D.3.3 Full Adder Cell with P-type Latch                 |

| D.3.4 N-P Latch and P-N Latch Layouts                   |

| D.4 4-bit Parallel Full Adder Layout                    |

| D.5 Proposed Testing Scheme                             |

| D.6 Chip Testing Results                                |

| D.7 Conclusions                                         |

| References                                              |

| VITA AUCTORIS                                           |

#### LIST OF FIGURES

| 2.1 NFET and its Model for TFET Calculation | 7    |

|---------------------------------------------|------|

| 2.2 FET Delay Versus Width                  | 8    |

| 2.3 CMOS Static Inverter                    | 8    |

| 2.4 Output waveforms of the Static Inverter | 9    |

| 2.5 Logic Block                             | 9    |

| 2.6 Output Waveforms of Switching Node      | 9    |

| 2.7 Static Gate Structure                   | 11   |

| 2.8 Dynamic Gate Structure                  | 12   |

| 2.9 RC chain circuits                       | . 17 |

| 2.10 7-RC-Link Discharge Waveforms          | . 23 |

| 2.11 Discharge Delay Versus No. of RC Links | . 24 |

| 3.1 Typical CMOS Dynamic Gate Chain         | . 27 |

| 3.2 Dynamic Gate Timing Diagram             | . 28 |

| 3.3 Long Precharge State                    | . 29 |

| 3.4 Worst Case Discharge State              | . 30 |

| 3.5 (a) Dynamic Gate Chain (b) RC Model     | .31  |

| 3.6 CMOS Transistor Capacitance Model                                | 34   |

|----------------------------------------------------------------------|------|

| 3.7 Standard Transistor Layout                                       | . 35 |

| 3.8 Test Circuit                                                     | . 38 |

| 3.9 Delay VS Width for the Test Circuit                              | . 39 |

| 3.10 Delay VS Area                                                   | . 47 |

| 3.11 Discharge Delay VS Chain Height                                 | . 48 |

| 3.12 Total Chain Area VS Chain Height                                | . 49 |

| 3.13 RC model delay VS SPICE delay (for sized NFET chains)           | . 50 |

| 4.1 Precharge Delay Model                                            | . 53 |

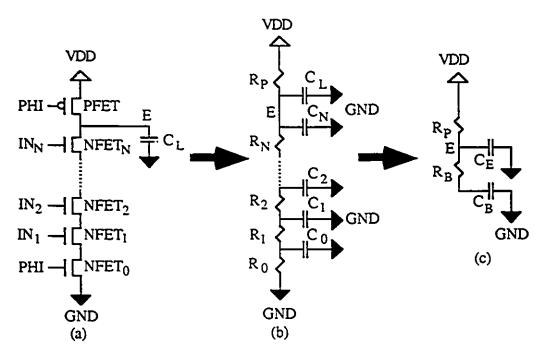

| 4.2 (a) Dynamic Gate Chain (b) RC Model (c) Precharge Delay Model    | . 56 |

| 4.3 Precharge Test Circuit                                           | . 57 |

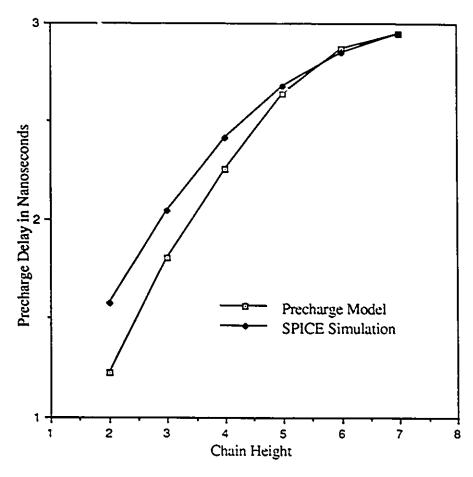

| 4.4 Precharge Delay Versus Chain Height                              | .61  |

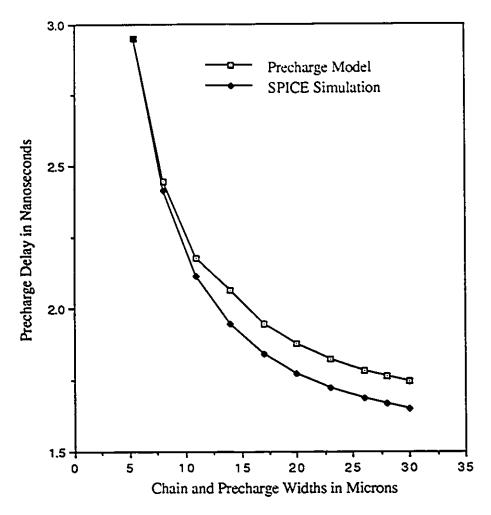

| 4.5 Precharge Delay Versus Width                                     | . 62 |

| 4.6 N-logic Block Dynamic Logic Structure                            | . 64 |

| 4.7 6 input NAND Dynamic Structure                                   | 65   |

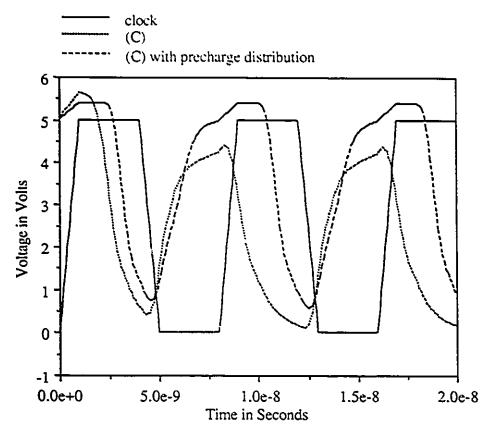

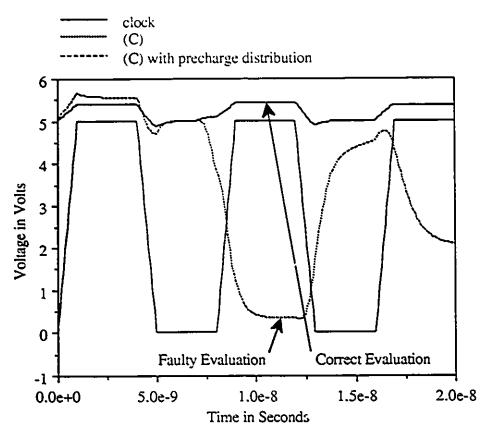

| 4.8 Worst Case Precharge and Evaluation of the Circuits in Table 4.3 | . 67 |

| 4.9 Worst Case Charge Sharing Condition of the Circuits in Table 4.3 | . 67 |

| 4.10 Worst Case Precharge and Evaluation of the Circuit (C) with and without   |       |

|--------------------------------------------------------------------------------|-------|

| Precharge Distribution                                                         | . 69  |

| 4.11 Worst Case Charge Sharing Condition of the Circuit (C) with and without   |       |

| Precharge Distribution                                                         | .70   |

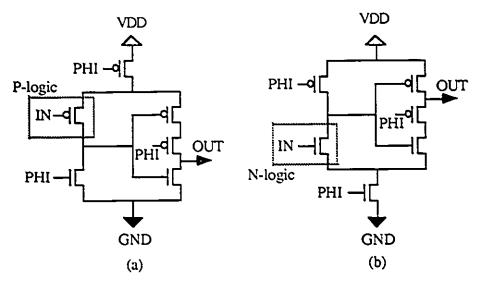

| D.1 Single Phase Dynamic Latches(a) P-logic Latch (b) N-logic Latch            | . 143 |

| D.2 Sum Binary Switching Tree                                                  | . 145 |

| D.3 Reduced Sum Binary Tree                                                    |       |

| D.4 Resulting Switching Graphs                                                 | 147   |

| D.5 Two Possible Realizations of the Sum                                       |       |

| D.6 Carry Realization                                                          |       |

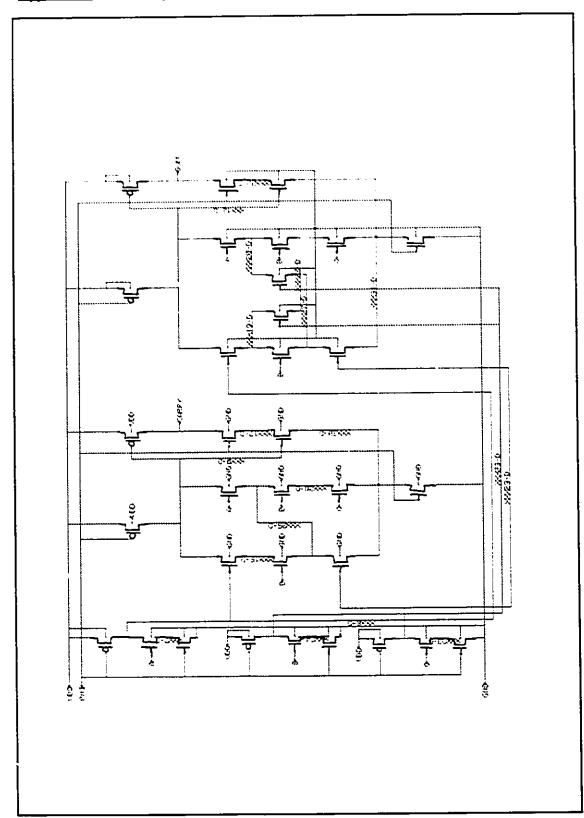

| D.7 Circuit Schematic for One Bit Full Adder                                   |       |

| D.8 One Bit Full Adder Cell Layout                                             |       |

| D.9 Final One Bit Full Adder Cell Layout                                       |       |

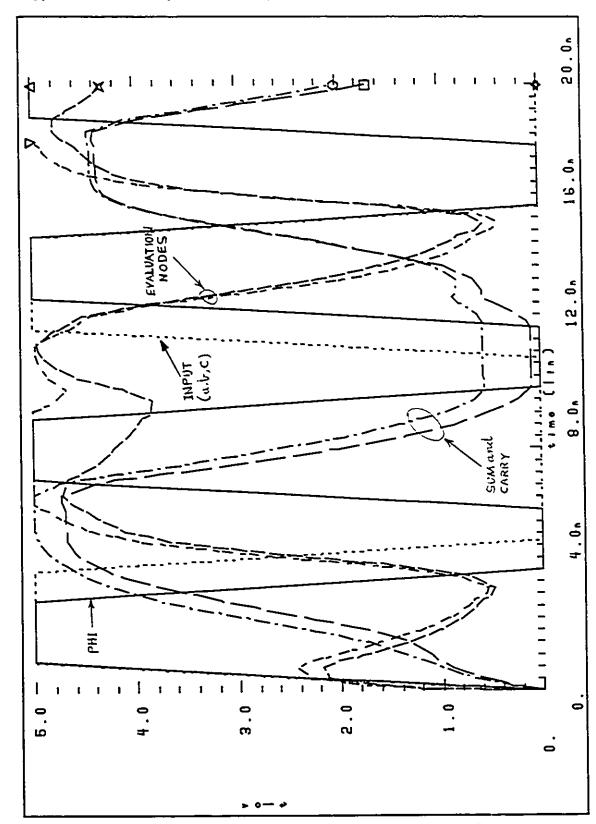

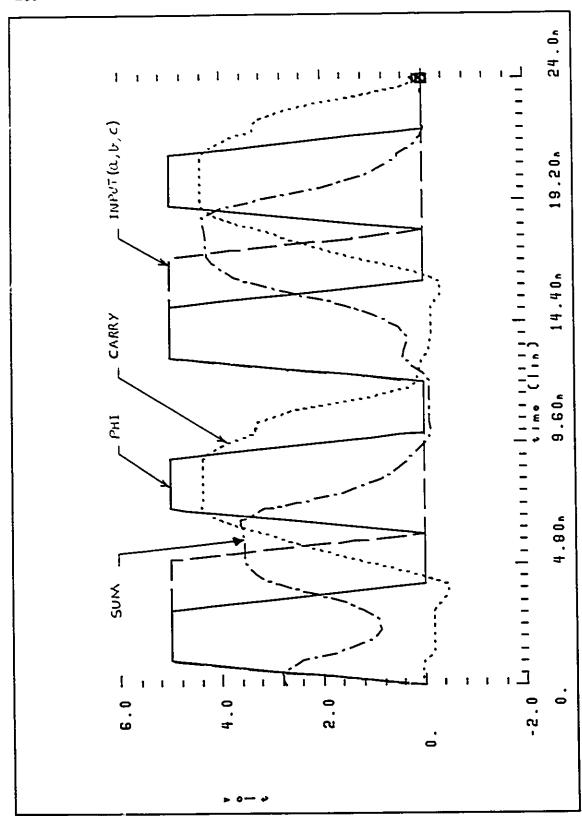

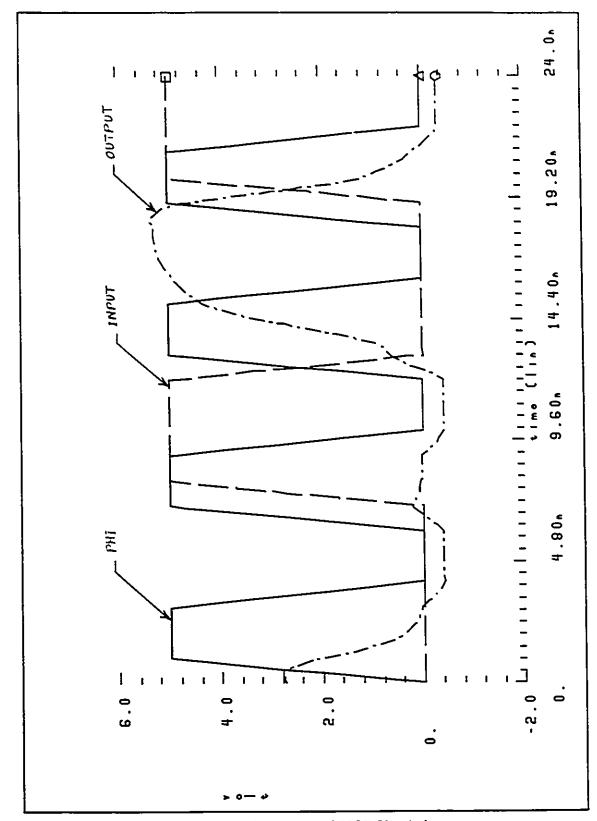

| D.10 SPICE simulation for the Final One Bit Full Adder Cell Layout             | 154   |

| D.11 One Bit Full Adder Cell Layout with P-logic Latch for the Carry           | 156   |

| D.12 SPICE simulation of the One Bit Full Adder Cell Layout with P-logic Latch | 157   |

| D.13 N-P Latch Layout                                                          | 159   |

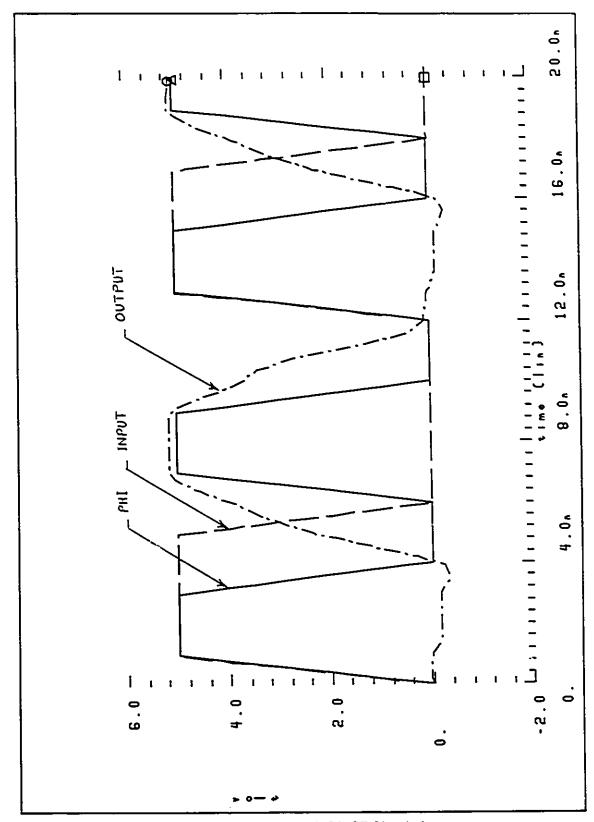

| D 14 M D Latch SDICE Simulation                                                | 160   |

| D.15 P-N Latch Layout                                | 161 |

|------------------------------------------------------|-----|

| D.16 P-N Latch SPICE Simulation                      | 162 |

| D.17 Circuit Schematic for 4-bit Parallel Full Adder | 164 |

| D.18 4-bit Parallel Full Adder Layout                | 165 |

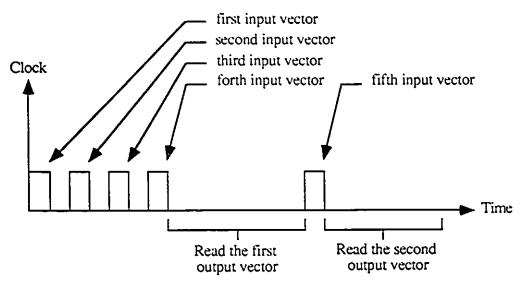

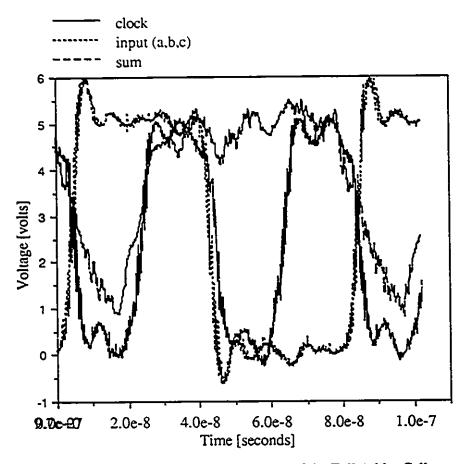

| D.19 Test Vector Timing Diagram                      | 166 |

| D.20 Input/Output Scope Plot of the Full Adder Cell  | 167 |

## LIST OF TABLES

| 2.1 Comparison between Dynamic and Static gates                            | .14   |

|----------------------------------------------------------------------------|-------|

| 3.1 Glossary Table                                                         | 45    |

| 4.1 Precharge Test Circuit Time Constants                                  | . 58  |

| 4.2 Precharge PFET sizing example results                                  | . 63  |

| 4.3 Sample Circuit Sizes and the Predicted Charge Sharing Problem Severity | . 66  |

| D.1 Sum and Carry Truth Ta' '>                                             | . 144 |

| D.2 Logical Test Results of the Full Adder Cell.                           | . 168 |

## CHAPTER 1

Introduction

#### 1.1 Introduction

Integrated circuit technology has made tremendous impact on our society in the last few years, in areas ranging from consumer products to business management to manufacturing control. The economic and strategic rewards gained by the use of very large scale integration, *VLSI*, have motivated the relentless search for high performance and perfection. Data processing speed, silicon area, power consumption, reliability, and testability of the VLSI end product, commonly referred to as a *chip*, have been the focus of many research activities in recent years. One of the most important aspects of chip performance is the rate at which data is being processed. Some research activities have targeted the fabrication technology itself to allow the designer to produce fast operating circuit structures as in the development of BiCMOS (bipolar and MOSFET technologies on the same chip) technology. Others have targeted the circuit design techniques within the fabrication technology and they have discovered numerous methods such as parallel structures, pipelined systems, dynamic logic blocks, and single phase clocking schemes.

Chapter 1 Introduction

2

At the transistor level, some scholars have been dealing with the problem of transistor size selection and transistor layout shape for increased speed and/or decreased area of the circuit under consideration. To reduce parasitic capacitances, and thus increasing circuit performance, many layout techniques are practiced, such as node merging and doughnut shaped transistor layout [8]. Transistor sizing techniques have played a major role in circuit design and layout to meet the never ending demands on circuit performance. Recently, it has been shown that 10% of the delay and 30% of the gate area can be decreased simultaneously by transistor sizing techniques [15] and also as much as 60%-90% increase in clocking speed alone has been reported [22], pushing the limits of the given fabrication technology.

A method to estimate circuit delay is essential in the transistor sizing problem and, certainly, SPICE [11] is the standard approach commonly used thus far. Indeed, AT&T bell laboratories have developed a transistor sizing program, ADVICE, which is used intensively and utilizes SPICE for the circuit delay approximation [17]. SPICE is a general purpose circuit simulation program that not only approximates the circuit delay but also solves for all node voltages and implements iterative procedures for the numerical integrations needed for the transient analysis. SPICE, therefore, is not suitable for the transistor sizing problem due to the large amount of CPU time it consumes each time a circuit delay is required to be evaluated. Time efficient methods for circuit delay approximations have been developed recently such as the RC tree [13] and macromodeling [9]. The RC tree is well suited for the transistor sizing problem since it deals with individual transistors rather than blocks of them, as is the case with macromodeling. There are some known problems associated with the RC tree method such as inaccurate handling of pass transistors, large delay error when considering short transistor chains, difficulties in modeling some of the logic structures, and difficulties in approximating its elements. CRYSTAL [12], TILOS [6], and TMODS [18] are some of the delay simulators or timing <u>Chapter 1</u> <u>Introduction</u>

3

verification programs that has been based on the RC tree method and used intensively in the VLSI design process.

Recent trends in the transistor sizing problem is the use of some type of heuristic optimization algorithms along with the RC tree method to alleviate some of the problems sighted earlier and this was done in SLOP [22] (transistor sizing program based on TMODS). This approach is proven to have a great success in circuit speed optimization for low transistor count circuits. The iterative nature with this approach and most optimization algorithms limit their use in large problems and this enhances the need of some type of analytical formulation for the transistor sizing problem.

A literature search has uncovered the fact that most, if not all, analytical approaches to transistor sizing problem are based on semiconductor device non-linear equations and parameters that make them applicable to only a few simple circuits such as inverters and buffers. In this thesis, a unique analytical formulation is introduced which is based on the RC model and the circuit topology, rather than the transistor equations; this approach alleviates the problems encountered with large transistor count circuits. The dream of obtaining global optimum transistor sizing for chips is closer than ever with this approach. Other aspects of this approach is the possibility of integrating the following;

- 1. Layout techniques such as node merging, different transistor layout shapes, floor plans .... etc.

- 2. Physical limitations on circuit behavior such as charge sharing, clock skew, and coupling capacitances.

- 3. Automated logic realization techniques such as binary switching trees being investigated by the VLSI research group at the University of Windsor.

## 1.2 Research Objectives

Chapter 1 Introduction 4

The main purpose of this work is to study and investigate available transistor sizing techniques and possibly devise and formulate more efficient methods. Ultimately, this research is targeted to integrate with other circuit design and layout techniques being developed by the VLSI research group at the University of Windsor.

### 1.3 Thesis Organization

Chapter 2 covers the pre-requisite material needed to understand and follow subsequent discussions. In particular, a concise review of the fundamental ideas relating to a circuit delay definition, logic gate types and operating mechanisms, worst case methodology, and RC chain delay approximation is presented. This chapter also provides a background for the definitions and notations used throughout the thesis.

The main theme and contributions of this research is contained in chapter 3. The RC model and its application to CMOS dynamic gates is given in this chapter and detailed explanations of MOSFET parasitic capacitances and channel resistances approximations are described. Transistor sizing techniques using optimization algorithms and the RC model are discussed for comparison purposes. In this chapter, a novel analytical approach based on the RC model is introduced and several sizing techniques for series transistors are described. This is followed by detailed discussions of the results of these various sizing techniques which give some insight into their advantages and disadvantages.

Chapter 4 presents a precharge delay model based on the RC model and develops an algorithm to size the Precharge PFET. Chapter 4 also contains discussions and suggests solutions to the inherent problem of charge sharing or node coupling of a typical dynamic structure. Chapter 5 contains thesis conclusions and introduces suggestions for further research activities around the topics investigated in this thesis.

<u>Chapter 1</u> <u>Introduction</u>

5

Appendix A contains Northern Telecom Canada 3µ-DLM fabrication technology parameters that are used in SPICE simulations and in the transistor sizing techniques and also lists some computed parameters for the RC model implementations. FORTRAN source codes, that employ various transistor sizing techniques for a single NFET dynamic chain, discussed in chapter 3, are given in Appendix B and these codes run on Sun Microsystems SPARC station 2. Precharge delay approximation and precharge PFET sizing FORTRAN source codes are given in Appendix C. Finally, Appendix D contains a report on the design, layout, and testing of a four bit parallel full adder test circuit that has been optimized manually for high clocking speeds. This report is added to this thesis because it was the motivation of this research and to show the difficulties encountered if manual transistor sizing is sought even for such a small circuit. Other aspects of the report is the implementation of single phase clocking scheme with dynamic latches and the logic function realization using binary switching trees (currently being investigated by the VLSI research group at the University of Windsor).

**CHAPTER 2**

**CMOS Logic Gates**

#### 2.1 Introduction

Various topics deemed essential in subsequent discussions are reviewed in this chapter. Some simplifying assumptions and definitions about circuit operating mechanisms are given here to facilitate further development of the transistor sizing techniques.

## 2.2 Logic Gate Delay Characterization

The basic definition of delay which is used widely in logic gate design is the time lapse between the input occurrence and the output occurrence. This definition can be interpreted in many ways according to the type of circuit under consideration and, in the following sub-sections, we detail some more specific commonly used definitions.

## 2.2.1 FET Delay

A measure of the performance of a FET as a switching device is determined by the time it takes to discharge its own parasitic capacitance [16]. In the *switched on* mode, the FET channel resistance is approximated by,

$$\frac{VDD}{I_{Dmax}(V_{G}=VDD,V_{D}=VDD)}$$

$$V_{D}=VDD \text{ at } t=0$$

$$V_{G}=VDD \text{ s}$$

$$I_{Dmax} \downarrow C_{G}+C_{D}$$

$$V_{G}=VDD \text{ s}$$

$$V_{G}=VDD \text{ s}$$

$$V_{G}=VDD \text{ s}$$

Figure 2.1 NFET and its Model for TFET Calculation

Figure 2.1 shows an NFET and its conceptual model for calculating T<sub>FET</sub>. The parasitic capacitance of the FET depends on the way the FET is used, but typically is given by:

$$C = C_G + C_D$$

112-0

where  $C_G$  is the gate capacitance and  $C_D$  is the drain diffused island capacitance. The time constant of the FET is then defined by:

$$T_{\text{FET}} = \frac{\text{VDD}}{I_{\text{Dmax}}} (C_{\text{G}} + C_{\text{D}}) \tag{2.1}$$

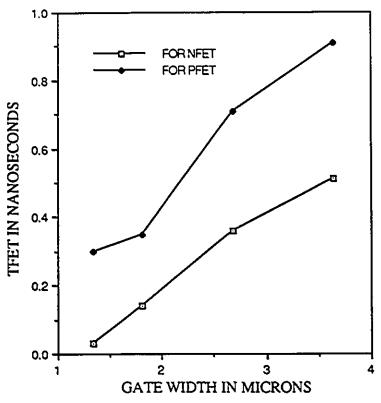

Figure 2.2 shows FET delay, T<sub>FET</sub>, versus FET width, W, with constant channel length. This delay definition is useful in developing initial ideas about the technology at hand; in other words, it usually answers the question whether transistor sizing enhances circuit performance or not. This delay definition, however, is not useful in the transistor sizing problem since, in a circuit structure, the circuit delay could be more sensitive to the FET parasitic capacitance or the channel resistance than the product of both; this will be demonstrated in chapter 3.

Figure 2.2 FET Delay Versus Width

## 2.2.2 Inverter Delay

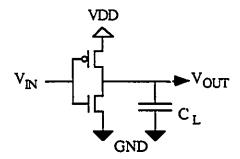

Inverters are considered to be the basic logic units in the family of functional logic blocks and their delay often used as a delay unit for other more complex logic structures. Figure 2.3 shows a typical CMOS static inverter and Figure 2.4 shows input/output waveforms.

Figure 2.3 CMOS Static Inverter

Figure 2.4 Output waveforms of the Static Inverter

The inverter pulldown delay is  $\tau$  and its pullup is  $k\tau$  where k is a multiplicative factor to account for the difference in delays. In a pipelined system, it is desirable to match the inverter delays; the size of the PFET is selected such that its pullup is equal to the inverter pulldown.  $\tau$  is specified as the time the inverter output voltage takes to cross some reference voltage such as  $\frac{\text{VDD}}{2}$  [10].

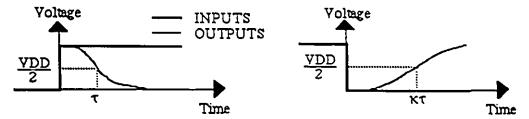

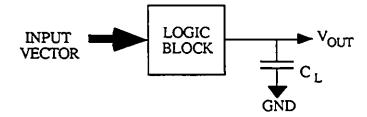

#### 2.2.3 Switching Node Delay

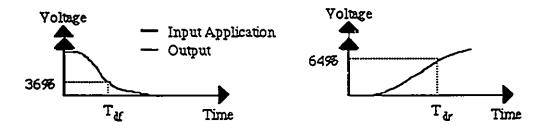

This delay is used intensively in this thesis and is defined as the time the output node voltage takes to drop to 36% of its initial value or to rise to 64% of its final value; it is measured from the application of the input vector.

Figure 2.5 Logic Block

Figure 2.6 Output Waveforms of Switching Node

10

In complex logic structures, the circuit topology is not symmetrical to all bits of the input vector and, therefore, different input vectors will result in different delays. Usually the worst case condition that produces the longest delay is considered for system timing purposes. It is worth mentioning that this delay definition originates from single time constant linear circuits and is useful when considering linear models with dominant time constants for the logic block; this will be shown in chapter 3.

## 2.3 Static Versus Dynamic Gates

The CMOS static gate logic family has been the most popular for VLSI fabrication over the last decade. One of its major advantages is the very small static power consumption (when the logic gate output is not changing state). A disadvantage is the silicon area required to implement the two complementary FET blocks, that are used in the CMOS static structure. In regularly clocked systems of gates, there is never the requirement that gates hold their input/output logic levels indefinitely. In such systems, it is possible to replace the p-channel FET block by a single transistor and form a gate that functions dynamically (the p-FET is clocked rather than used with static logic levels). The advantages are reduced area and reduced self load capacitance of the logic gate. In general CMOS dynamic gates offer good area efficiency with high speed operation and moderate power consumption.

We will compare typical structures of static and dynamic CMOS gates in the following subsections.

#### 2.3.1 CMOS Static Gate Structure

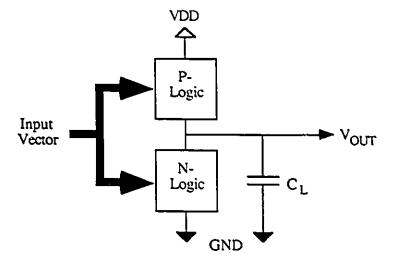

Figure 2.7 shows a typical static gate structure; it consists of two logic block types; n-logic which is made of n-channel MOSFETs and p-logic which is made of p-channel MOSFETs.

The output node lies between these two logic blocks and VDD is connected to the top of the

11

p-logic block while GND is connected to the bottom of the n-logic block. Note that the same input vector is applied to both blocks.

Figure 2.7 Static Gate Structure

It is always the case, for static gates to operate properly, that the p-logic block complements the n-logic block and the n-logic block complements the p-logic block. If an input vector results in a connection between VDD and the output node through the p-logic block then the n-logic block must isolate the output node from GND and the reverse is true. This mechanism ensures that no path exists between VDD and GND (if the output node is not changing), and thus static power is limited to leakage currents only; these are very small in normal operating environments. Dynamic power consumption is due to the migration of charges from VDD to the output node to GND and is proportional to the switching rate of the static gate and to the node capacitances between VDD and GND.

## 2.3.2 CMOS Dynamic Gate Structure

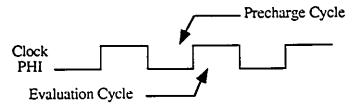

Dynamic gates differ in their structures depending on the type and technique of mapping the logic functions. Figure 2.8 shows two CMOS dynamic gate types; n-logic and p-logic. We restrict ourselves to the n-logic since the p-logic works in a similar manner.

12

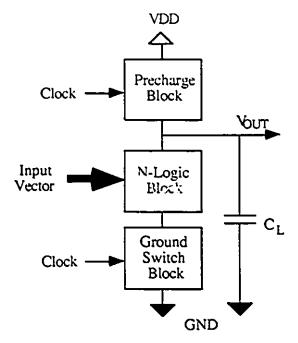

Figure 2.8 Dynamic Gate Structure

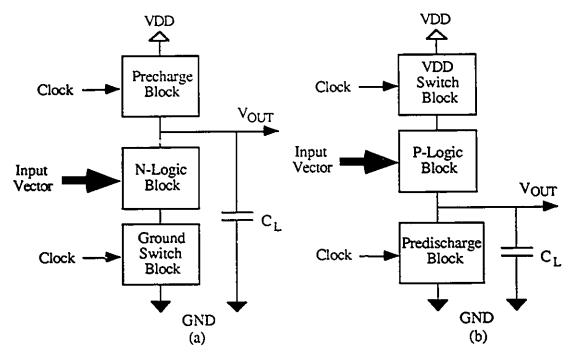

The dynamic gate uses a clocked load with a ground switch to prevent the n-logic block from producing static current drain when the load is being clocked. The dynamic gate structure is shown in Figure 2.8(a). The precharge block, which is usually made of a single PFET, connects the evaluation node to VDD when the clock is low while the ground switch, a single NFET, isolates the circuit from GND. This phase of the clock is called the precharge cycle and results in a charged high evaluation node. After the input settles, the clock makes a low to high transition and the precharge block isolates the evaluation node from VDD while the ground switch provides a path to GND for the n-logic block. This phase of the clock is called the evaluation cycle. During this part of the cycle, the n-logic block, which is made of interconnections of NFETs, either discharges or keeps high the evaluation node according to the input vector. The power consumption of a dynamic gate is roughly proportional to the clock frequency, especially when the evaluation node has to stay low or has to make transitions, and to internal node capacitances. It is very beneficial

13

to a circuit designer to have an expression that estimates or provides an upper limit of the power consumption of a dynamic gate. We can write,

$$P_{\text{dynamic gate}} = f_{\text{clock}} \cdot C_{\text{internal}} \cdot VDD^2$$

(2.2)

where f<sub>clock</sub> is the clocking frequency of the dynamic gate and C<sub>internal</sub> is the summation of all internal node capacitances involved in the precharge and evaluation cycles. Equation (2.2) gives the worst case power consumption since (1) the Cinternal does not necessarily discharge each period of the clock and (2) most of the internal node capacitances are not likely to be fully charged in the precharge cycle. Approximation of CMOS switching circuit node capacitances will be discussed in chapter 3 and more detailed explanations of specific dynamic gate families, such as domino, NORA, and zipper, can be found in [16].

#### 2.3.3 Comparison between Static and Dynamic Gates

Table 2.1 summarizes the advantages of each gate type over the other. The first column lists the VLSI circuit aspect and the second column states which gate provides best performance in this category. The third column contains comments rationalizing the choice made in the second column. It is important to note that the order in which the circuit aspects are listed do not reflect their importance in the circuit design and, in fact, the type of application in which the circuit is being used will dictate the order of priority of each circuit aspect.

| Circuit Aspect        | Gate Type | Comments                                                                                                                                                                                                                                                                    |

|-----------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Processing Speed | Dynamic   | Dynamic gates are faster than their counterpart static gates because of the following (for n-logic); (1) Pullup is done during the precharge cycle rather than the evaluation cycle. (2) Reduced output node capacitance and reduced overlap current.                       |

| Power Consumption     | Static    | In general, static gates consume less power than dynamic gates since the latter has to be precharged each cycle.                                                                                                                                                            |

| Layout Area           | Dynamic   | Dynamic gates occupy less area since they only require one logic block.                                                                                                                                                                                                     |

| Transistor Count      | Dynamic   | The same explanation as above.                                                                                                                                                                                                                                              |

| Noise Immunity        | Static    | The output node of static gates is solidly connected to either VDD or GND while in dynamic gates the output node is left floating. This makes the dynamic gate more susceptible to circuit noise such as voltage surges with coupling capacitances and/or leakage currents. |

| Input Vector Loading  | Dynamic   | The input vector is driving one logic block in dynamic gates and two logic blocks in static gates.                                                                                                                                                                          |

| Gate Clocking         | Static    | Static gates do not need internal clocking which makes them easier to design and layout. Dynamic gates need internal clocking to control the precharge/discharge and the evaluation cycles.                                                                                 |

Table 2.1 Comparison between Dynamic and Static gates

15

## 2.4 Worst Case Methodology

It is common practice in the VLSI design process to adopt a worst case methodology in order to ensure that the designed system will not fail under normal processing and operating conditions. In this methodology, system processing parameters, input vector, output loading, and operating environment are set to such worst case conditions; the design is then modified to operate under these conditions. It is important to note that some of the factors affecting the system performance might be dependent on each other and their worst case conditions should be considered collectively. Care must be taken in applying the worst case methodology so as not to be too pessimistic; this can result in an expensive or redundant design.

In this thesis, the worst case methodology is adopted and applied in approximating the discharge and precharge delays of typical dynamic logic gates. This helps in determining the clocking speed of the logic gate at which logic computation failure will not occur.

## 2.5 RC Chain and Elmore's Delay Formula

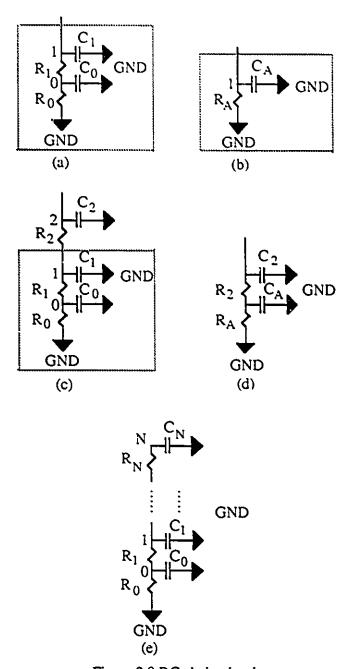

In this section, we discuss a useful method of approximating delays of an RC chain in closed form [16]. A detailed proof for the formula is obtained by considering the two-stage cascaded RC chain first and then generalized to the N-stage RC chain which was first derived in [5].

With reference to Figure 2.9(a), the problem can be stated as follows. At t=0, capacitors  $C_0$  and  $C_1$  are both charged to VDD, and the circuit begins to discharge. The objective is to find a simple closed-form formula that includes  $R_0$ ,  $R_1$ ,  $C_0$ , and  $C_1$  that gives the time

16

needed for node 1 voltage  $V_1(t)$  to drop from VDD to  $\frac{VDD}{e}$ , where e is the base of the natural logarithm. The result is given in equation. (2.3).

$$T_D = R_0(C_0 + C_1) + R_1C_1 = R_0C_0 + (R_0 + R_1)C_1$$

(2.3)

and the proof follows. The circuit equations satisfied by node 0 voltage  $V_0(t)$  and node 1 voltage  $V_1(t)$  are

$$C_0 \frac{dV_0}{dt} = \frac{V_1 - V_0}{R_1} - \frac{V_0}{R_0} \tag{2.4}$$

$$C_1 \frac{dV_1}{dt} = -\frac{V_1 - V_0}{R_1}$$

Figure 2.9 RC chain circuits

These simultaneous equations can be solved by the standard method of circuit theory: We replace the operator d/dt by s and we seek the equation satisfied by s.

We have

$$s^{2} - \frac{C_{0} + C_{1} + (R_{1}/R_{0})C_{1}}{R_{1}C_{0}C_{1}} s + \frac{1}{R_{0}R_{1}C_{0}C_{1}} = 0$$

(2.5)

If  $\alpha$  and  $\beta$  are the roots, they satisfy

$$\alpha + \beta = \frac{C_0 + C_1 + (R_1/R_0)C_1}{R_1C_0C_1} \qquad \alpha\beta = \frac{1}{R_0R_1C_0C_1}$$

(2.6)

Node voltages V<sub>0</sub>(t) and V<sub>1</sub>(t) are written as

$$V_{0}(t) = V_{00}e^{-\alpha t} + V_{01}e^{-\beta t}$$

$$V_{1}(t) = V_{10}e^{-\alpha t} + V_{11}e^{-\beta t}$$

(2.7)

and they satisfy the following four initial conditions at t=0.

$$V_0(0) = V_1(0) = VDD$$

$$\left[\frac{dV_1(t)}{dt}\right]_{t=0} = 0 \qquad \left[\frac{dV_0(t)}{dt}\right]_{t=0} = -\frac{VDD}{C_0R_0}$$

We obtain

$$V_0(t) = VDD \frac{(C_0 R_0 \beta - 1)e^{-\alpha t} - (C_0 R_0 \alpha - 1)e^{-\beta t}}{C_0 R_0(\beta - \alpha)}$$

$$V_1(t) = VDD \frac{\beta e^{-\alpha t} - \alpha e^{-\beta t}}{\beta - \alpha}$$

(2.8)

When  $R_0 \gg R_1$ , equation (2.5) has one solution that is small: The  $s^2$  term in equation (2.5) is neglected and we obtain

$$s = \frac{1}{R_0(C_0 + C_1)} \qquad (=\alpha)$$

and another solution that is large: The term in Equation (2.5) that does not contain s is neglected and we obtain

$$s = \frac{C_0 + C_1}{R_1 C_0 C_1}$$

(=\beta)

We define  $\alpha$  and  $\beta$  in this way, so that  $\beta >> \alpha$ . When t is positive, the terms in equation (2.8) that involve  $e^{-\beta t}$  may be approximated by zero. Then

$$V_1(t) = VDD \frac{\beta}{\beta - \alpha} e^{-\alpha t} = VDD e^{-\alpha t + \log \frac{\beta}{\beta - \alpha}}$$

and therefore by requiring

$$-\alpha T_D + \log \frac{\beta}{\beta - \alpha} = -1$$

we get

$$T_{D} = \frac{\alpha + \beta}{\alpha \beta} \tag{2.9}$$

when  $\beta \gg \alpha$ . Using equation (2.6), we obtain equation (2.3).

When  $R_1 >> R_0$ , equation (2.5) has the solution

$$s \approx \frac{1}{R_1 C_1} \qquad (=\alpha)$$

and another solution,

$$s = \frac{1}{R_0 C_0} \qquad (=\beta)$$

and again  $\beta >> \alpha$ . Then following the same manipulation we arrive at equation (2.3). When neither  $R_0 >> R_1$  nor  $R_1 >> R_0$  is satisfied, the simplification does not hold, but the formula is still quite accurate.

The error when R<sub>0</sub>=R<sub>1</sub>=R and C<sub>0</sub>=C<sub>1</sub>=C is estimated as follows. Since

$$\alpha = \frac{3-\sqrt{5}}{2} \left[ \frac{1}{RC} \right] = \frac{0.3819}{RC}$$

and  $\beta = \frac{3+\sqrt{5}}{2} \left[ \frac{1}{RC} \right] = \frac{2.6180}{RC}$

the delay time is determined from

$$\frac{1}{e} = \frac{1}{2\sqrt{5}} \left\{ (3+\sqrt{5}) e^{-\frac{3-\sqrt{5}}{2}} \left( \frac{t}{RC} \right) - (3-\sqrt{5}) e^{-\frac{3+\sqrt{5}}{2}} \left( \frac{t}{RC} \right) \right\}$$

as t = 3.03(RC). Equation (2.3) gives t = 3(RC). Therefore, even in this case the agreement is good.

The analysis shows that the two-stage RC chain shown in Figure 2.9(a) can be approximated by the single-stage RC chain shown in Figure 2.9(b), consisting of only RA and CA. We showed that

$$R_AC_A = T_D = (R_0 + R_1)C_1 + R_0C_0$$

The two circuits can be made quite similar in their characteristics by further requiring that the low-frequency impedance looking into the single port is the same. This requirement means that the two circuits, one of them is a simple approximation of the other, must drive the same resistive impedance at DC. This results in

$$R_A = R_0 + R_1$$

When the three-stage circuit shown in Figure 2.9(c) is considered, the first two stages can be substituted for by Figure 2.9(b). Then the circuit of Figure 2.9(b) has a delay

$$T_D = (R_A + R_2)C_2 + R_AC_A$$

$$= (R_0 + R_1 + R_2)C_2 + (R_0 + R_1)C_1 + R_0C_0$$

As a generalization, the discharge delay of the last node of the cascaded N-stage RC chain circuit is given by

$$T_D = \sum_{i=0}^{N} R_i \sum_{j=i}^{N} C_j = \sum_{i=0}^{N} C_i \sum_{j=0}^{i} R_j$$

(2.10)

<u>Chapter 2</u> <u>CMOS Logic Gates</u> 21

## 2.6 Monotonicity of the Delay with Area

In the previous section, we have shown a closed form formulation approximating the discharge delay of an RC chain. In this section, we will use this formulation along with a set of simplifying assumptions to prove that the discharge delay decreases monotonically with transistor chain area if the transistor size distribution is selected properly.

Referring to Figure 2.9(e), each RC link is assumed to be related to a transistor geometry by the following;

$$R_i = \frac{K_r}{W_i} \tag{2.11}$$

and

$$C_i = K_c W_i \tag{2.12}$$

where  $W_i$  is the gate width of the i<sup>th</sup> transistor (assuming fixed channel length) and  $K_r$  and  $K_c$  are transistor constants. More detailed discussions about modelling of transistor chains, capacitance approximation, and resistance approximation will be presented in chapter 3. Now, we re-write equation (2.10) in the form of delay terms as follows;

$$T_{D} = \sum_{i=0}^{N} T_{Di}$$

(2.13)

where

$$T_{Di} = R_i \sum_{i=i}^{N} C_j \tag{2.14}$$

Substituting equations (2.11) and (2.12) in equation (2.14), we obtain;

Chapter 2 CMOS Logic Gates 22

$$T_{Di} = K_r K_c \sum_{j=i}^{N} \frac{W_j}{W_i}$$

(2.14)

Now, let us consider the case where all the transistor widths in the chain are fixed to WFIXED except for the bottom one which corresponds to i=0, we obtain

$$T_{D0} = K_r K_c \sum_{i=1}^{N} \frac{W_{FIXED}}{W_0}$$

(2.15)

From equation (2.15), It is clear that  $T_{D0}$  decreases monotonically with  $W_0$  and hence, by equation (2.13), the discharge delay of the chain also decreases monotonically with  $W_0$ . Note that all delay terms other than  $T_{D0}$  in equation (2.13) are independent of  $W_0$ .

Here we have shown that it is possible to decrease the delay by increasing the transistor chain area and in chapter 3 we will present several techniques to minimize the discharging delay of NFET chains.

# 2.7 Accuracy of Elmore's Delay Formula

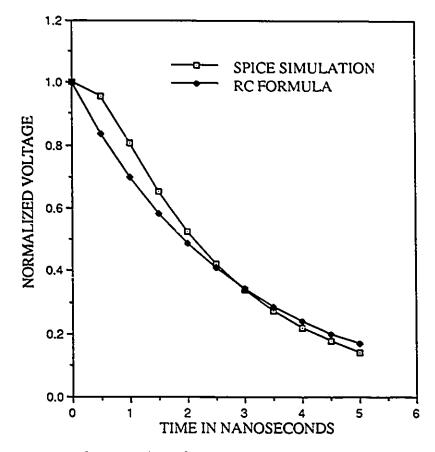

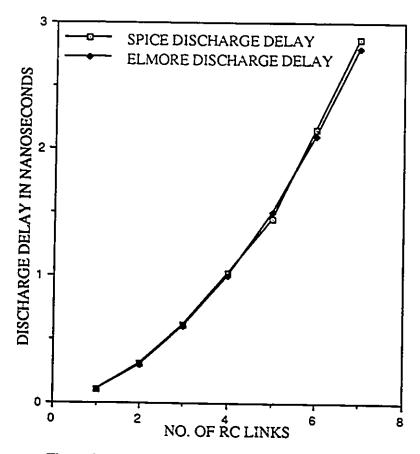

Before leaving this chapter, we will discuss the accuracy of Elmore's delay formula. Figure 2.9 shows discharging node waveforms of a seven link RC chain. The waveforms are obtained by SPICE simulation and by applying Elmore's single time constant. It is clear that the waveforms are not well matched and this is expected because Elmore's formula assumes single time constant and ignores many minor poles that modify the discharging node waveform. Figure 2.11 shows a plot of the discharge delay (when the output node drops to 36% of its original value) versus the number of links in the RC chain. With its computational simplicity, Elmore's formula predicts the discharge delay quite accurately and, hence, for those problems that do not require waveform shapes, the RC model and Elmore's formula are quite acceptable. The simple algebraic expressions produced by

23

Elmore's approximations will be indispensable in obtaining the analytic results of Chapter 3.

Figure 2.10 7-RC-Link Discharge Waveforms

Figure 2.11 Discharge Delay Versus No. of RC Links

# CHAPTER 3

Transistor Sizing Approaches for NFET Chains

## 3.1 Introduction

Switching circuits can be analyzed using standard circuit simulators such as SPICE [11] and ASTAP [20]. But such circuit simulators require a great amount of CPU time and memory storage. To reduce the complexities of the analysis and the models, a number of new techniques have been developed, for example, using tables instead of transistor equations [3], using macromodels [9], ....etc.

One of the successful techniques that has emerged in recent years is the RC tree model [13],[7] based on Elmore's delay formula [5]. The RC model is the heart of many switch level simulators such as TMODS [18] and CRYSTAL [12].

Recently, RC model based delay simulators have been used in circuit speed optimization; for example SLOP [22]. Circuit sizing techniques are powerful since it has been shown that 10% of the delay and 30% of the gate area can be decreased simultaneously [15]. From an extensive literature search it appears that all sizing techniques, so far published, rely on

some type of iterative optimization procedure rather than an analytical formulation to the sizing problem. It is clear that an analytical approach to circuit sizing will both save substantial amounts of CPU time and, more importantly, provide an algebraic foundation on which to base automated design procedures.

A rule of thumb that has been evolved in the design of VLSI circuits is to limit the number of transistors connected serially in a logic block (logic height) in order to maintain a minimum performance level; however, as the feature size becomes smaller in the submicron region, this rule can be relaxed [14] and higher logic chains are possible. This encourages more extensive use of NAND/NOR complex gates and makes the transistor sizing more important and effective. In such circumstances, the use of analytical techniques in transistor sizing will eximinate the very large computational time that will be required for iterative techniques.

In this chapter we introduce a new RC analytical model and several sizing techniques for series transistor chains. Section 3.2 explains the necessary mechanisms of a typical dynamic NFET chain structure that are needed to generate an adequate delay model. The RC model is discussed in section 3.3 and its parasitic capacitance approximation is dealt with in section 3.4. In section 3.5, a unique approach is introduced to approximate the channel resistance. SPICE level 2 model equations are used to approximate the resistance of those NFETs that mainly discharge in the linear region while a test circuit is proposed to approximate the resistance of the top NFET that mainly discharges in the saturation region. This approach not only assures that an optimum top NFET width, relative to the other NFET widths, is achieved but also reduces the discharge delay error for the scaled NFET chains to a  $\pm$  5% window. Section 3.6 discusses existing optimization techniques, for NFET sizing, that we use for comparison purposes in section 3.8. In section 3.7 we introduce a novel analytical approach to NFET sizing. Delay-area curves for optimum NFET chain sizes are obtained easily, allowing suitable trade-off decisions by the circuit

designer. A further novel technique is presented in this chapter which transforms any N-variable optimization problem for NFET chain sizing to a single-variable optimization if the constraint of limiting the transistor widths is desired. Section 3.8 presents the results and discussions and section 3.9 contains the final conclusions.

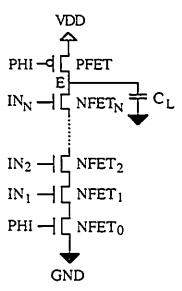

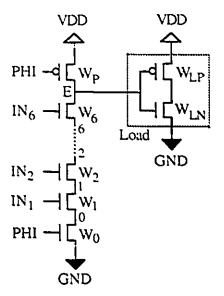

# 3.2 Discharge Delay of an NFET Chain

Consider the dynamic gate structure shown in Figure 3.1. The NFET chain consists of N+1 serially connected transistors from the evaluation node to the ground. The bottom NFET is the ground switch while the top PFET is the precharge transistor. C<sub>L</sub> models the load capacitance connected to the evaluation node. IN<sub>1</sub>, IN<sub>2</sub>,..., IN<sub>N</sub> is the input vector and PHI is the gate clock connected to both the ground switch and the precharge PFET. This dynamic structure is general to most dynamic gates with only slight modifications.

Figure 3.1 Typical CMOS Dynamic Gate Chain

The problem becomes too complex if the dependence of the discharge delay on the rate of change of the input voltage is included in the analysis. Therefore, we assume that the gate

:::...· :

input voltages switch instantly. The clock has two distinct cycles in which the gate operates; precharge cycle and evaluation cycle as shown in Figure 3.2.

Figure 3.2 Dynamic Gate Timing Diagram

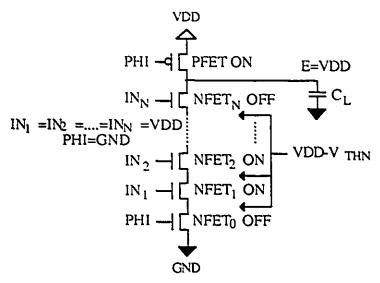

### 3.2.1 Precharge Cycle

In this cycle, the clock level is low and the ground switch NFET<sub>0</sub> is off isolating the circuit from ground. The precharge PFET is on and the evaluation node is pulled up to VDD. Now, let us consider the worst case precharge condition where all inputs to the NFET chain are high (we assume a voltage of VDD in our analysis). If the precharge cycle is kept on for a relatively long period of time, the top transistor, NFET<sub>N</sub>, in the chain will enter the cutoff region leaving  $V_S = V_D - V_{THN} = VDD - V_{THN}$ . Where  $V_{THN}$  is the threshold voltage of NFET<sub>N</sub> including the back-bias effect. Transistors NFET<sub>1</sub> to NFET<sub>N-1</sub> will continue to conduct until  $V_{DS} = 0$  and all internal nodes of the chain will be charged up to VDD-V<sub>THN</sub>. The state of the dynamic gate after this long precharge period is shown in Figure 3.3.

Figure 3.3 Long Precharge State

## 3.2.2 Evaluation Cycle

After the input vector stabilizes, the clock level switches high and the precharge PFET is turned off. The ground switch NFET<sub>0</sub> turns on and the evaluation node discharges low or remains high depending on the state of the input vector. The worst case evaluation condition is where the evaluation node has to discharge low and the input vector is high. In this case, the top transistor, NFET<sub>N</sub>, pulls out of the cutoff region to the saturation region and then to the linear region. All other transistors in the chain stay in the linear region throughout the discharge period including the ground switch. Figure 3.4 shows the state of the dynamic gate after worst case evaluation condition.

Figure 3.4 Worst Case Discharge State

It is worth mentioning that it is the discharge delay which limits the clocking speed of the gate and any improvement to the discharge delay greatly enhances the logic gate performance. There are two dominant factors, working against each other, that directly affect the discharge delay. The first is the evaluation node capacitance which consists of  $C_L$  and the PFET drain capacitance. The second factor is the size of the NFET chain. As the size of an NFET transistor in the chain increases, the current driving capability also increases which tends to decrease the delay; however, the parasitic capacitances associated with the NFET increase and this tends to increase the delay. In the next section, we deal with the problem of predicting the discharge delay for given sizes of the NFET chain [15], using these dominant factors.

## 3.3 RC Model

In order to analyze the delay characteristics of an NFET chain, the chain must be represented by a simple and manageable circuit model that contains the essential physical mechanisms. In this work we use the established RC model presented in [13] and [7] since

it predicts the discharge delay in terms of circuit parameters not device parameters [21]. This former method is useful in developing algorithms for gate-level delay simulators, but the present objective is to approximate the NFET chain pulldown delay.

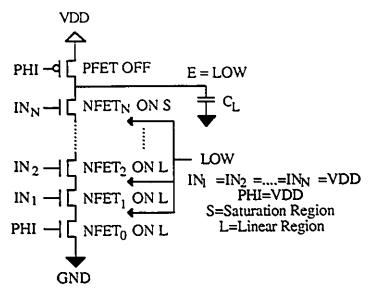

Each transistor in the NFET chain is replaced by a series resistance, R<sub>i</sub>, and a parallel parasitic capacitance, C<sub>i</sub>. The loading effect of the precharge PFET is added to C<sub>L</sub>. Figure 3.5 shows the process of constructing the RC model.

Figure 3.5 (a) Dynamic Gate Chain (b) RC Model

#### C<sub>i</sub> consists of the following contributions;

- 1. Drain-diffused island capacitance of NFET<sub>i-1</sub>.

- 2. Source-diffused island capacitance of NFET<sub>i</sub>.

- 3. 1/2 the gate-to-channel capacitance of NFET<sub>i-1</sub>.

- 4. Gate-to-drain overlap capacitance of NFET<sub>i-1</sub>.

- 5. 1/2 the channel-to-substrate capacitance of NFET<sub>i-1</sub>.

- 6. 1/2 the gate-to-channel capacitance of NFET<sub>i</sub>.

- 7. Gate-to-drain overlap capacitance of NFET<sub>i</sub>.

- 8. 1/2 the channel-to-substrate capacitance of NFET<sub>i</sub>.

Normally, the above parasitic capacitances are lumped to node  $N_i$  [16] and thus over estimate the actual delay of the circuit [12].  $R_i$  models the average channel resistance during discharge and depends on the voltage of the nodes  $N_{i+1}$ ,  $N_i$ , and  $IN_i$ . We assume that the inputs switch instantly and  $V_{INi}$ =VDD; therefore, the current,  $I_i$ , that flows through NFET<sub>i</sub>, and  $R_i$  are ideally related by equation (3.1)

$$R_{i} = \frac{1}{T_{D}} \int_{0}^{VN_{i+1} - VN_{i}} dt$$

(3.1)

Now, for a given technology, it is possible to calculate C<sub>i</sub> and R<sub>i</sub> as will be shown shortly. The discharge delay where the evaluation node drops to 0.36 of its original value (VDD) is approximately given by Elmore's delay formula [5]

$$T_{D} = \sum_{i=0}^{N} R_{i} \sum_{j=i}^{N} C_{j} = \sum_{i=0}^{N} C_{i} \sum_{j=0}^{i} R_{j}$$

(3.2)

In order to take account of the C<sub>L</sub> load, from Figure 3.5(b), we re-write equation (3.2) as:

$$T_{D} = \sum_{i=0}^{N} R_{i} \left[ \sum_{j=i}^{N} C_{j} + C_{L} \right] = \sum_{i=0}^{N} C_{i} \sum_{j=0}^{i} R_{j} + C_{L} \sum_{j=0}^{N} R_{j}$$

(3.3)

It is worth noting that equation (3.3) implicitly assume that all internal node voltages of the RC chain are initially equal to the evaluation node voltage. This assumption, however, is not true for the NFET discharge chain and we expect some extra error due to this. Another

source of error is in the approximation of  $R_i$  where the channel resistance is not linear and in some cases is difficult to linearize, as in the case of the saturation region.

With appropriate linear definitions for the non-linear channel resistances and parasitic capacitances, the approximate RC model produces satisfactory results for delay approximation [7] and, more importantly, gives excellent results in sizing NFET chains [15]. This will also be demonstrated later in this chapter.

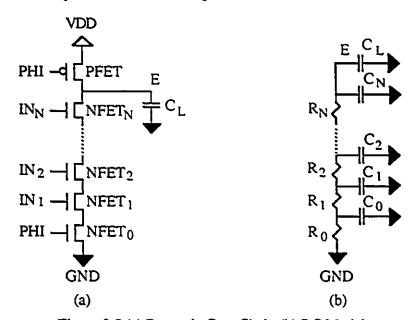

# 3.4 Parasitic Capacitance Approximation

The capacitances involved in the RC model are relatively easy to calculate. At this point it is necessary to simplify matters and ignore non-linear capacitances or suppress the non-linearity by assuming fixed voltages. The errors due to these assumptions can be taken care of by scaling the resulting delay in accordance with SPICE simulations. Figure 3.6 shows the capacitances considered in the RC model representation of an NFET (likewise for a PFET).

Figure 3.6 CMOS Transistor Capacitance Model

There are two things worth mentioning concerning Figure 3.6(b). The first is that the channel capacitance, C<sub>CHAN</sub>, which is due to the channel potential with respect to the bulk voltage, has little affect on the total delay of the model, and therefore is not considered. The second thing is that the gate-to-channel capacitance, C<sub>G</sub>, is distributed over the channel resistance and, for simplicity, we assume that it is lumped between C<sub>Di</sub> and C<sub>Si</sub>. Furthermore, in the RC model, a step input is assumed and, hence, the gate voltage is constant and equal to VDD. Therefore all capacitances connected to the gate voltage, V<sub>G</sub>, will be replaced by a ground terminal (virtual ground) without affecting the behavior of the capacitance.

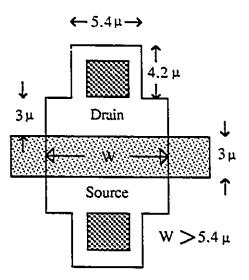

Before we explain the various capacitances in Figure 3.6(b,c), the transistor layout has to be defined. The following standard layout technique is assumed, throughout the thesis, using technology rules from our target 3µ-DLM process [4].

Figure 3.7 Standard Transistor Layout

The drain and source island area and perimeter are easily found and given by,

$$AD = AS = W \times 3 \times 10^{-6} + 22.68 \times 10^{-12}$$

$PD = PS = W + 14.4 \times 10^{-6}$

Note that other layout techniques, such as node merging, and other technology rules can be easily incorporated. Now we consider the capacitances shown in Figure 3.6(b) and their evaluations according to SPICE models [2],[19].

1. Gate-to-channel capacitance

$$C_G = COX \times gate area + CEDGE \times gate perimeter$$

2. Gate-to-drain overlap capacitance

$$C_{GDO} = CGDO \times W$$

3. Drain-to-substrate capacitance

$$C_{BD} = CJ \frac{AD}{\left[1 \cdot \frac{V_{BD}}{PE}\right]^{MJ}} + CJSW \frac{PD}{\left[1 \cdot \frac{V_{BD}}{PB}\right]^{MJSW}}$$

Assuming V<sub>BD</sub>=0 to remove the non-linearity of the capacitance, we get

$$C_{RD} = CJ \times AD + CJSW \times PD$$

4. Gate-to-source overlap capacitance

$$C_{GSO} = CGSO \times W$$

5. Source-to-substrate capacitance as in (3.3)

$$C_{BS} = CJ \times AS + CJSW \times PS$$

Capacitances 2,3, and half of 1 are lumped to C<sub>Di</sub> in Figure 3.6(c). Likewise capacitances 4,5, and half of 1 are lumped to C<sub>Si</sub>.

## 3.5 Channel Resistance Approximation

We are modeling the non-linear behavior of the MOSFET channel with a linear resistor. There are two distinct approaches, to approximate the channel resistance, sighted in the literature. The first approach is to simulate a test circuit using SPICE and then extract the average discharge resistance from the data obtained [24]. The second approach is to use SPICE model equations to calculate the average channel resistance [15]. Here we present a unique method that combines both approaches which results in a smaller area-delay product for the NFET chain.

As explained in section 3.2, the transistors in the discharge chain are either in the linear or saturation region. The top transistor in the chain mainly operates in the saturation region while the others mainly operate in the linear region.

#### 3.5.1 Channel Resistance Approximation for Linear Region NFETs

We model transistors in the linear region with a minimum channel resistance using the SPICE MOSFET level-2 model, as shown in equation (3.4);

$$I_{DS} = \beta [(V_{GS} - V_{BIN} - \frac{\eta V_{DS}}{2})VDS - \frac{2}{3}\gamma S [(2\phi_F + V_{DS} - V_{BS})^{\frac{3}{2}} - (2\phi_F - V_{BS})^{\frac{3}{2}}]]$$

(3.4)

where,

$$\beta = \frac{KP.W}{L-2X_{jl}}$$

then,

$$R_{DS}(V_{DS}) = \frac{\delta V_{DS}}{\delta I_{DS}} = \frac{1}{\beta \left[ V_{GS} - V_{BIN} - \eta V_{DS} - \gamma_{S} (2\phi_{F} + V_{DS} - V_{BS}) \frac{1}{2} \right]}$$

(3.5)

The minimum channel resistance is found for  $V_{DS}=0$ , and this value can be used for the RC model [15]. Hence:

$$R_{DS}(\text{minimum}) = \frac{1}{\beta \left[ V_{GS} - V_{BIN} - \gamma_S (2\phi_F - V_{BS})^{\frac{1}{2}} \right]}$$

(3.6)

At this point, it is convenient to express the resistance with W as the single independent variable:

$$RDS = \frac{PURL}{W}$$

(3.6)

where:

$$PURL = \frac{L-2X_{j1}}{KP[V_{GS}-V_{BIN}-\gamma_{S}(2\phi_{F}-V_{BS})^{\frac{1}{2}}]}$$

(3.7)

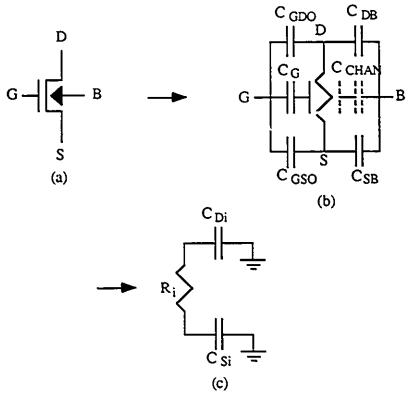

## 3.5.2 Channel Resistance Approximation for Saturation Region NFET

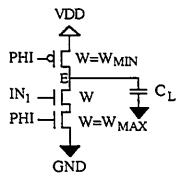

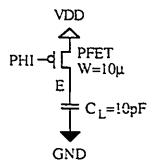

For the transistor working mainly in the saturation region (the top MOSFET connected to the evaluation node), we use SPICE simulations, along with the RC model and an optimization routine, in order to define its per unit channel resistance. Consider the test circuit shown in Figure 3.8.

Figure 3.8 Test Circuit

W<sub>MAX</sub> and W<sub>MIN</sub> are the maximum and the minimum transistor widths that most likely will be used in the transistor sizing problem. Node IN<sub>1</sub> is kept at VDD and C<sub>L</sub> is replaced by a minimum size static inverter to more appropriately simulate the output loading. The following algorithm is used to obtain the per unit resistance, PURS, of the top NFET:

- (1) Using SPICE simulations of the test circuit, we define the clock signal, PHI, as switching from low to high at the start of the simulation; the discharge delay of node E is recorded for a range of values of W.

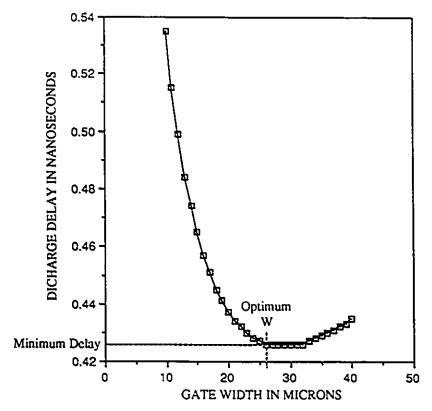

- (2) Plot the discharge delay versus W, and select an optimum width from the plot; an example is shown in Figure 3.9.

Figure 3.9 Delay VS Width for the Test Circuit

- (3) Assign an initial value to PURS (e.g. the value of PURL), and use the optimization routine of section 3.6 and the RC model to find the optimum W for the test circuit given in Figure 3.8.

- (4) Adjust PURS until the optimum W obtained in step (3.3) matches that from step (2).

For this particular example and using our target 3µ-DML technology, it is found that

$$PURS = 1.7 \times PURL \tag{3.8}$$

The fact that two different values of resistance are obtained validates our improved modeling procedure.

# 3.6 A Survey of Optimization Approach to NFET Sizing

In this section we will discuss optimization techniques normally used to size NFET discharge chains. We will use the results of this survey in a comparison study with our new approaches. These results are presented in Section 3.7.

The RC model is used to define the cost function, discharge delay, which is to be minimized. The delay is given by equation (3.3). Usually NFET sizes are only given by the width of the channel; the length of the channel is kept constant at the minimum feature size offered by the given technology. The resistance and capacitance approximations are calculated according to sections 3.4 and 3.5.

Two optimization approaches are shown here that are commonly used in the transistor sizing problem; they are classified according to the type of constraint applied.

#### 3.6.1 Optimization I

A maximum and a minimum transistor widths constraint, given by equation (3.9), is applied,

$$W_{MIN} < W_i < W_{MAX} \tag{3.9}$$

W<sub>MIN</sub> is usually set to the minimum feature size of the given technology and W<sub>MAX</sub> is chosen according to layout constraints. The width of the lowest NFET in the chain can be eliminated from the size vector and set to Wmax. This is true because the discharge delay is more sensitive to the channel resistance of the lowest NFET than its parasitic capacitance contributions, and so we choose the minimum resistance possible by setting the width to Wmax. It is also possible to further reduce the computational time by choosing an appropriate starting vector. Initial optimization results show that the minimum delay occurs when the NFET sizes gradually decrease from the grounded end to the evaluation node, and this suggests using the starting vector of equation (3.10):

$$W_{i} = W_{MAX} + \frac{W_{MIN} - W_{MAX}}{N \ i}$$

(3.10)

Equation (3.10) produces a linear width tapering from the bottom to the top transistor. The following is a brief description of the algorithm used in this approach;

- 1. Record the delay for W<sub>i</sub>, W<sub>i</sub>+STEP, W<sub>i</sub>-STEP.

- 2. Replace  $W_i$  by  $W_i \pm STEP$  if, Delay  $(W_i \pm STEP) \le Delay (W_i)$

- 3. Apply the constraint,  $W_{MIN} < W_i < W_{MAX}$

- 4. Repeat steps 1-3 for all transistor widths.

- 5. Stop when no transistor width changes.

#### 3.6.2 Optimization II

In this approach, an area constraint is used rather than a transistor width constraint. The algorithm given below is similar to several sighted in the literature e.g. SLOP [22] and TILOS [6];

- 1. Start with minimum transistor widths.

- 2. Calculate the delay sensitivity of all transistors

Sensitivity<sub>i</sub> = Delay

$$(W_i)$$

- Delay  $(W_i+STEP)$

- 3. Replace Wi by Wi+STEP only for the transistor with the largest sensitivity.

- 4. Repeat 2 to 3 until user specified area limit is achieved.

A major drawback of the above algorithm is the requirement of an initial width vector of minimum transistor sizes, and thus the algorithm tends to require many iterations, even if only moderate size logic gates are considered.

# 3.7 Analytical Approach to NFET Sizing

It has been shown, in the previous section, that optimization techniques can be used along with the RC model to size a discharging NFET chain. As the number of transistors to be sized increases, optimization techniques tend to be extremely slow and alternate analytical approaches become attractive. In this section, a novel analytical approach is introduced which not only speeds the computation time, but also provides the design flexibility afforded by an algebraic formulation.

We start by re-writing equation (3.3) as follows:

$$T_{D} = \sum_{i=0}^{N} T_{Di}$$

(3.11)

where,

$$T_{Di} = R_i \left[ \sum_{j=i}^{N} C_j + C_L \right]$$

(3.12)

From extensive simulations we find that we can make the assumption that a close to optimum transistor size distribution is achieved when all of the delay terms are identical:

$$T_{D0} = T_{D1} = T_{D2} = \dots = T_{DN}$$

(3.13)

The results in section 3.8 will demonstrate the validity of this assumption.

We will discuss two approaches to the sizing problem, based on the assumption in (3.13). The first approach produces an area-delay curve that the designer can use to select the best trade-off point; this is a purely analytical technique. The second approach allows the designer to select a maximum limit to the width of the largest (bottom) transistor in the

chain; the technique uses a single variable optimization procedure to arrive at the optimum sizing profile.

#### 3.7.1 Analytical Approach

Let the number of transistors in the chain be N+1 and the discharge delay be  $T_D$ . From equations, (3.12) and (3.13), we obtain:

$$T_{Di} = \frac{T_D}{N+1} = R_i \left[ \sum_{j=i}^{N} C_j + C_L \right]$$

(3.14)

Consider the top NFET (i=N):

$$\frac{T_{D}}{N+1} = R_{N}(C_{N} + C_{L}) \tag{3.15}$$

Now we can define a single resistor value for this NFET (in saturation) similar to the definition for resistance for NFETs in the linear region (see equation (3.6)). Let:

$$R_{N} = \frac{PURS}{W_{N}} \tag{3.16}$$

Any node capacitance in the equivalent circuit for the chain is dependent on the two transistors connected to that node. In the case of the top node, however, the capacitance is only dependent on the width of the top transistor (we assume the pre-charge transistor is a known fixed size). We can therefore solve the problem, analytically, by solving for widths, starting from the top node. We know, from section 3.4, that the top node capacitance has the form:

$$C_N = K_1 + K_2 W_N$$

(3.17)

Note that  $C_L$  is included in  $K_1$ . We can now solve for  $W_N$ :

$$\frac{T_D}{N+1} = \frac{PURS}{W_N} (K_1 + K_2 W_N)$$

(3.18)

and:

$$W_{N} = \frac{PURS K_{1}}{\frac{T_{D}}{N+1} - PURS K_{2}}$$

(3.19)

Now consider any other transistor in the chain. From equation (3.6):

$$R_i = \frac{PURL}{W_i} \tag{3.20}$$

and from section 3.4:

$$C_{i} = K_{3} + K_{4} W_{i} + K_{5} W_{i+1}$$

(3.21)

substituting (3.20) and (3.21) in equation (3.14), we get:

$$W_{i} = \frac{PURL(K_{3}+K_{5} W_{i+1}+C_{i+1}+....+C_{N})}{\frac{T_{D}}{N+1} - PURL K_{4}}$$

(3.22)

Note that i ranges from N-1 to 0 therefore, when we solve for  $W_i$ , all transistor widths above the ith node in the chain are known, and hence the right hand side of equation (3.22) is readily computed. Sections 3.4 and 3.5 discuss the methods used to generate parameters PURS, PURL,  $K_1$ ,  $K_2$ ,  $K_3$ ,  $K_4$ , and  $K_5$ .

### 3.7.2 Single Variable Optimization

In this optimization technique, we will use  $W_N$  as the single variable, along with a constraint  $W_{MAX}$  on the maximum width of any transistor in the chain. The cost function to be minimized is the delay. We know that if  $W_N$  is given then all the transistor sizes in the chain can be found by using equation (3.22). If, in this calculation,  $W_i$  for i=j exceeds the constraint, we simply replace  $W_i$  by  $W_{MAX} \ \forall \ i \leq j$  (i.e. a constant width from node j to the bottom of the chain). This method always transforms an N+1 variable optimization method to one of only one variable. Our experience is that this approach yields results very

close to those of a conventional N+1 variable optimization procedure. We will demonstrate this in the next section.

### 3.8 Results and Discussions

Our test circuit is that shown in Figure 3.1 with C<sub>L</sub> replaced by a minimum size static inverter. The resurs presented here are for our target 3µ-DML technology offered by Northern Telecom, Canada. A glossary of the terms used in the plots is defined in table 3.8.1.

| Wp                  | Precharge transistor width                                                                                             |

|---------------------|------------------------------------------------------------------------------------------------------------------------|

| W <sub>MAX</sub>    | Maximum transistor width allowed, in this case 30µ                                                                     |

| W <sub>MIN</sub>    | Minimum transistor width allowed, in this case 5.4µ                                                                    |

| FIXED WIDTHS        | All transistors widths in the chain are set to W <sub>MAX</sub>                                                        |

| OPTIMIZATION I      | Transistor widths obtained by a standard optimization algorithm with maximum width limitation constraint.              |

| OPTIMIZATION II     | Transistor widths obtained by a standard optimization algorithm with area limit constraint.                            |

| ANALYTICAL APPROACH | Analytical approach described in section 3.7.1                                                                         |

| S-V OPTIMIZATION    | Top transistor width is selected by the optimizer and the rest of the chain is scaled analytically (see section 3.7.2) |

Table 3.1 Glossary Table

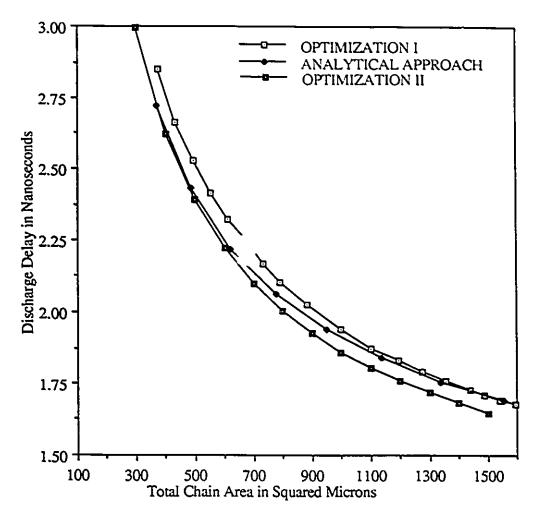

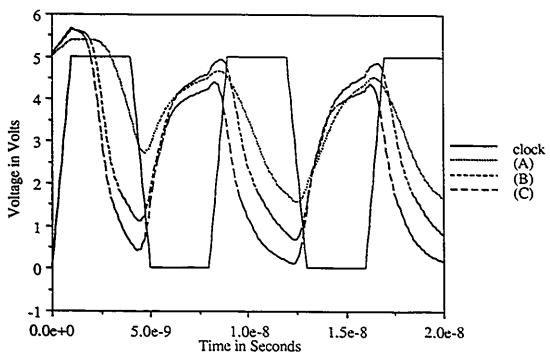

A delay-area curve for a seven level height NFET chain is given in Figure 3.10. In this example our analytical approach yields a smaller delay than the standard Optimization I algorithm, and compares well with the Optimization II angle particularly in the small area range. The Optimization approach II took as many as 2000 iterations, per point, in the large area range (STEP= $0.6\mu$ ) whereas the analytical approach produces results in one calculation per point.

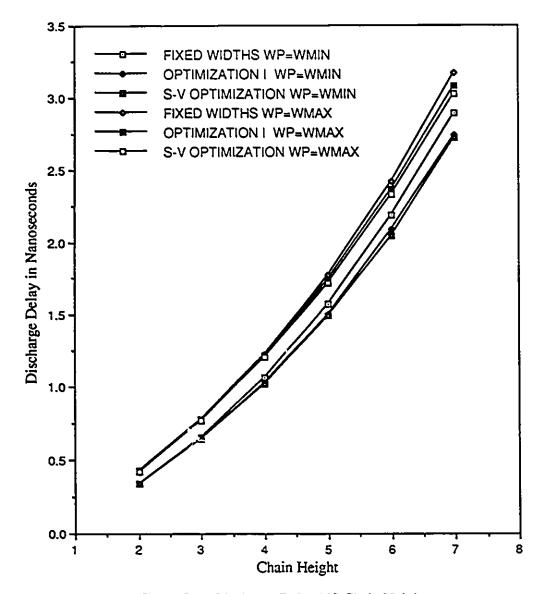

Discharge delay versus chain height for various methods is shown in Figure 3.11. There are two sizes of Wp used to simulate different loading effects on the evaluation node for each method. It is clear that that Optimization I and the S-V Optimization method result in very similar discharge delay curves for both values of Wp compared to the Fixed Widths method. It is also observed that smaller delays are obtained by chain sizing for (1) higher logic heights and (2) for low capacitive loading on the evaluation node. Note that these delays are obtained by SPICE level-2 simulations with the same transistor sizes as produced by the respective methods.

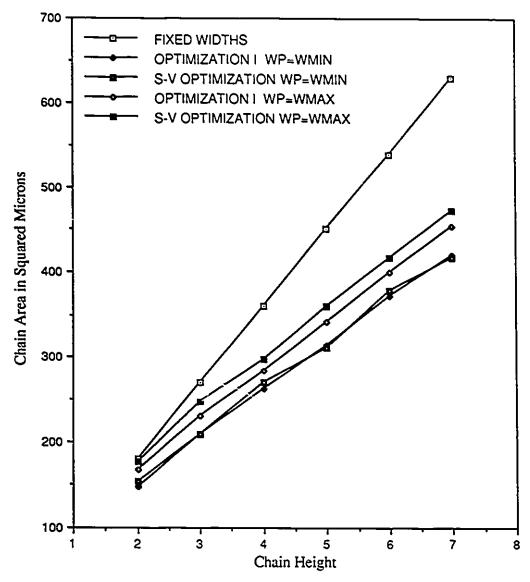

Figure 3.12 shows chain area versus chain height for the same transistor sizes used in Figure 3.11. It is apparent that a substantial chain area reduction can be obtained by circuit sizing techniques (up to 30% savings for 7 level height chain). The Optimization I and the S-V Optimization methods show very close results for Wp=W<sub>MIN</sub> a larger difference for Wp=W<sub>MAX</sub>, but still within very acceptable limits.

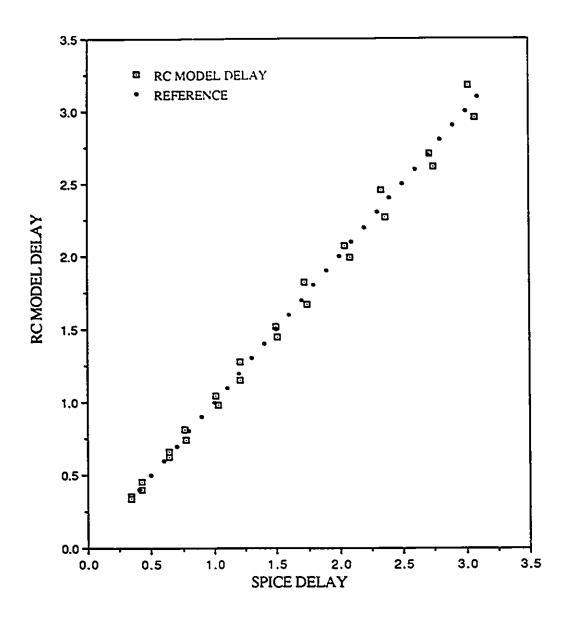

Finally, Figure 3.13 shows the accuracy of the delays, for sized chains, computed by the RC model. The deviations between plots indicate that the transistor sizing is within  $\pm$  5% of the optimum that would have been obtained by using SPICE as a delay calculator.

Figure 3.10 Delay VS Area

Figure 3.11 Discharge Delay VS Chain Height

Figure 3.12 Total Chain Area VS Chain Height

Figure 3.13 RC model delay VS SPICE delay (for sized NFET chains)

# 3.9 Summary

-;.·

This chapter has used the RC model to produce a purely analytical approach to the sizing of NFET chains. This analytical method is up to 2000 times faster in computation time than competing iterative optimization techniques. The ability to express the sizing problem

algebraically will undoubtedly have ramifications in the construction of complex NFET block design tools.

This chapter has also presented a single variable optimization approach for NFET chain sizing that implements a maximum width constraint to produce a sub-optimal delay-area curve. We have demonstrated that the results of this approach compare favorably to those obtained from existing iterative N-variable optimization strategies using the same constraint.

# **CHAPTER 4**

Practical Aspects of Circuit Sizing

### 4.1 Introduction

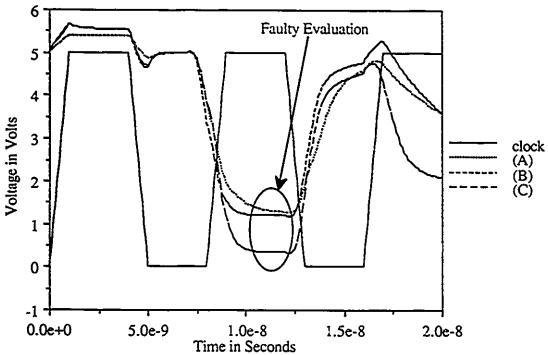

In this chapter, practical aspects of circuit sizing techniques are considered, such as precharge sizing and the charge sharing, or node coupling, problem. We start this chapter by introducing a simple RC precharge delay model that parallels the developments made earlier for the discharge delay in chapter 3. The main difference between the two models is that the precharge model has two dominant time constants; this produces a transcendental equation that can be solved by standard numerical techniques, such as the Newton-Raphson method. Also, in this chapter, a major problem associated with dynamic logic structures, due to the floating nature of the evaluation node, is discussed and some possible solutions are suggested. These solutions not only eliminate the charge sharing problem but also increase the stability of the evaluation node against leakage currents and surges and, hence, increases the frequency range at which the dynamic structure can operate.

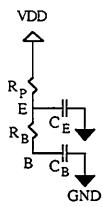

# 4.2 Precharge PFET Sizing

This section concentrates on the precharge cycle of the dynamic structure. The underlying assumption throughout this section is that all transistor sizes of the circuit are known and only the precharge PFET is to be found based on the desired precharge delay, Tp. Usually Tp is selected to be equal to the discharge delay, Tp. of the logic gate so that the clock is symmetrical. Capacitance approximation of NFETs and PFETs and channel resistance approximations of the NFETs are those discussed in detail in chapter 3 and only the modelling of the precharge PFET channel resistance will be presented here.

### 4.2.1 Precharge Delay Model