# University of Windsor Scholarship at UWindsor

**Electronic Theses and Dissertations**

1985

# A REAL TIME GENERAL PURPOSE SIGNAL PROCESSOR ARCHITECTURE.

MOHSIN MOHAMMAD. JAMALI University of Windsor

Follow this and additional works at: http://scholar.uwindsor.ca/etd

#### Recommended Citation

JAMALI, MOHSIN MOHAMMAD., "A REAL TIME GENERAL PURPOSE SIGNAL PROCESSOR ARCHITECTURE." (1985). *Electronic Theses and Dissertations.* Paper 727.

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

## CANADIAN THESES ON MICROFICHE

I.S.B.N.

### THESES CANADIENNES SUR MIGROFICHE

National Library of Canada Collections Development Branch

Canadian Theses on Microfiche Service

Ottawa, Canada K1A 0N4 Bibliothèque nationale du Canada Direction du développement des collections

Service des thèses canadiennes sur microfiche

#### NOTICE

The quality of this microfiche is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us a poor photocopy.

Previously copyrighted materials (journal articles, published tests, etc.) are not filmed.

Reproduction in full or in part of this film is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30. Please read the authorization forms which accompany this thesis.

THIS DISSERTATION

HAS BEEN MICROFILMED

EXACTLY AS RECEIVED

#### **AVIS**

La qualité de cette microfiche dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut l'aisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de mauvaise dualité.

Les documents qui font déjà l'objet d'un droit d'auteur (articles de revue, examens publiés, etc.) ne sont pas microfilmés.

La reproduction, même partielle, de ce microfilm est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30. Veuillez prendre connaissance des formules d'autorisation qui accompagnent cette thèse.

LA THÈSE A ÉTÉ MICROFILMÉE TELLE QUE NOUS L'AVONS RECUE

A REAL TIME GENERAL PURPOSE SIGNAL PROCESSOR ARCHITECTURE

bν

Mohsin Mohammad Jamali

A dissertation

presented to the University of Windsor

in partial fulfillment of the

requirements for the degree of,

Doctor of Philosophy

in

The Department of Electrical Engineering

Windsor, Ontario, 1984

(c) Mohsin Mohammad Jamali, 1984

#### ACKNOWLEDGEMENT.

The author would like to express his sincere thanks and appreciations to his supervisors Dr. G. A. Jullien and DR. S. I. Ahmad for their valuable advice, help and constant encouragement throughout the progress of this research. The author is also thankful to Dr. W. C. Miller and Dr. J. J. Soltis for their valuable advice and suggestions. Thanks are also extended to the graduate students for their help during the course of this work.

The author also wishes to thank his parents, brothers, sisters and friends for their help and unlimited support.

#### LIST OF ABBREVIATIONS

ALU Arithmetic Logic Unit

CCP Cyclic Convolution Property

CPU Central Processing Unit

DFG Data Flow Graph

DESP Data Flow Signal Processor

DFT Discrete Fourier Transform

DIF Decimation in Frequency

DSP Digital Signal Processing

FFT Fast Fourier Transform

FIR Finite Impulse Response

FNTT Fast Number Theoretic Transform

IIR Infinite Impulse Response

MQRNS Modified Quadratic Residue Number System

NTT Number Theoretic Transform

PE Processing Element

. PSP Programmable Signal Processor

QRNS Quadratic Residue Number System

RAM Random Access Memory

RNS Residue Number System

ROM Read Only Memory.

VLSI Very Large Scale Integeration

# LIST OF FIGURES

| Numbe | r Figures                                  | Page |

|-------|--------------------------------------------|------|

| 2.1   | A bit serial array multiplication .        | 17   |

| 2.2   | Programmable Signal Processor Architecture | 20   |

| 2.3   | X-Pipe evaluation of arithmetic expression | 25   |

| 2.4   | An overview of the expression processor    | 26   |

| 2.5   | sytolic arrays                             | 29   |

| 2.6   | Von-Neumann Model                          | 31   |

| 2.7   | Mago's tree structure                      | 34   |

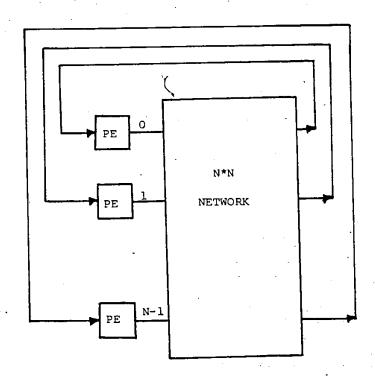

| 2.8   | N*N communication network                  | 37   |

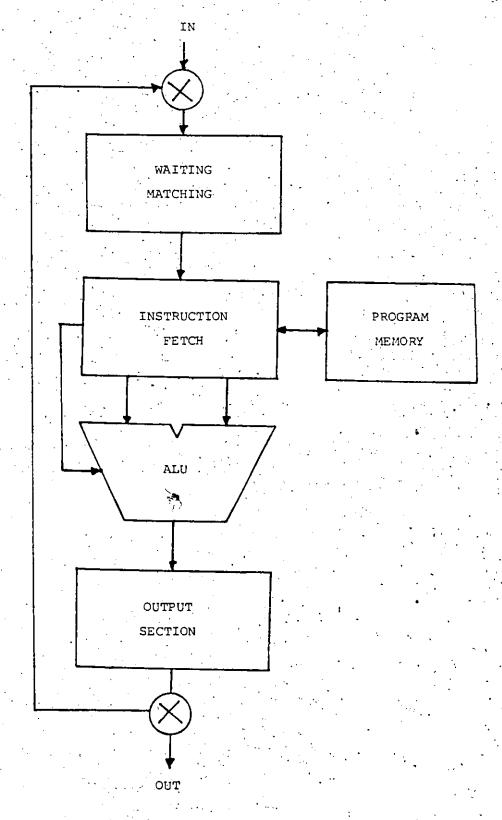

| 2.9   | Cell structure of a data flow architecture | 38.  |

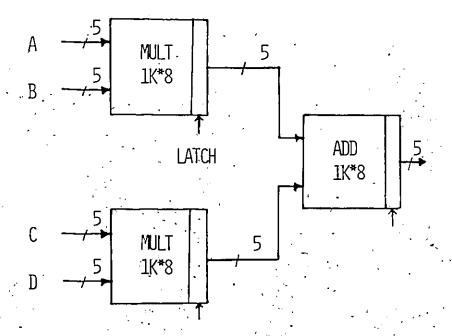

| 3.1   | Hardware implementation of the expression  | 47   |

| 3.2   | Bandpass filter structure                  | 54   |

| 3.3   | Computational element                      | 55   |

| 3.4   | Normalized frequency response              | 56   |

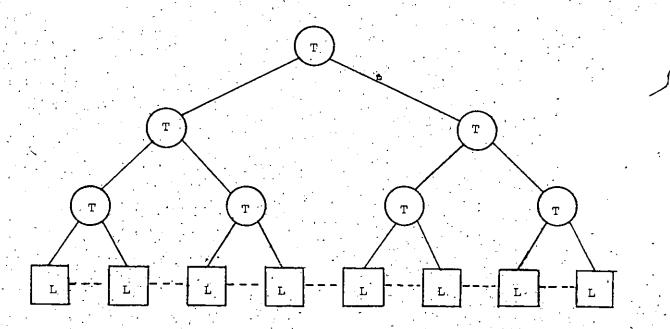

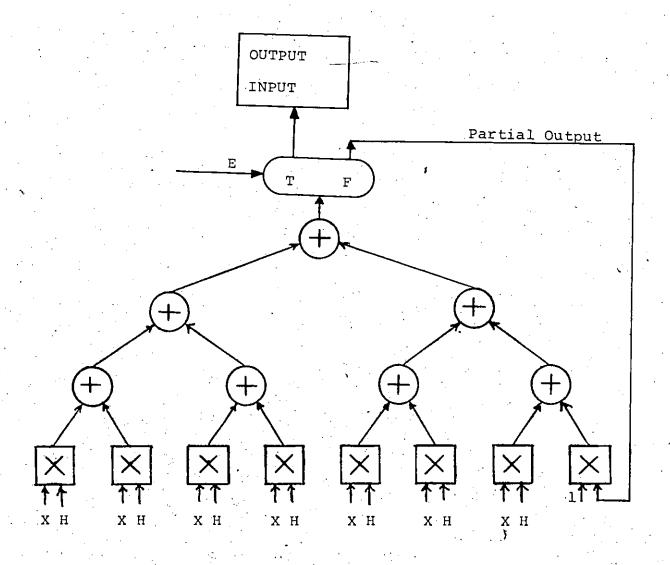

| 4.1   | Binary tree structure                      | 63   |

| 4.2   | Tree cell structure                        | 67   |

| 4.3   | Base cell C architecture                   | 68   |

| 4.4   | Base cell interconnection                  | , 69 |

| 4.5   | Control bits for addressing                | 70   |

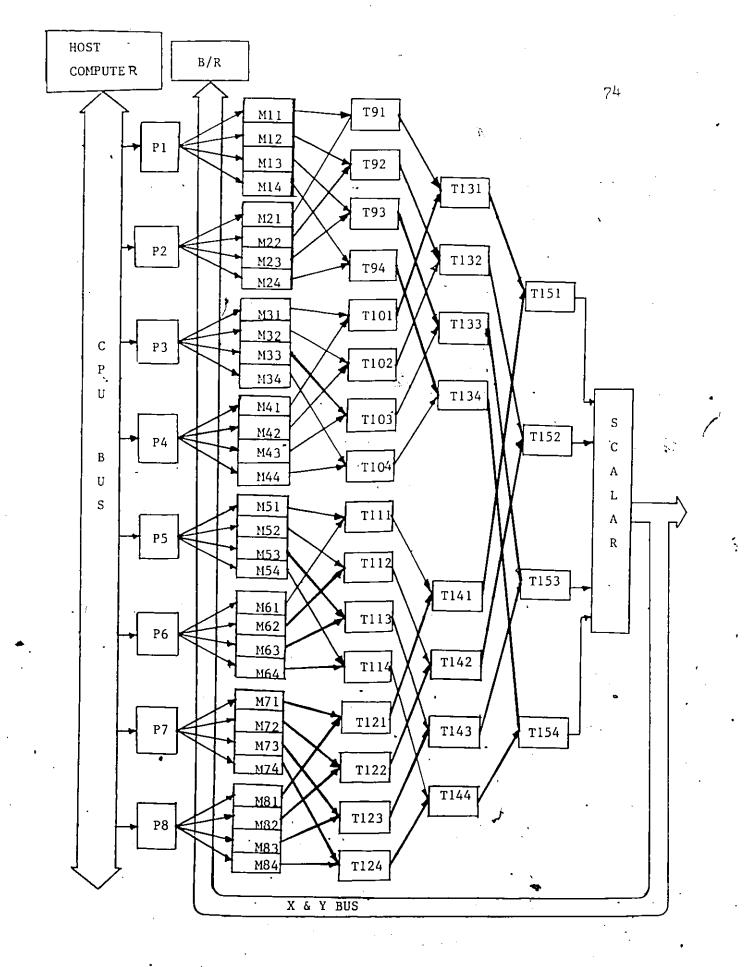

| 4.6   | Host computer Interface                    | 74   |

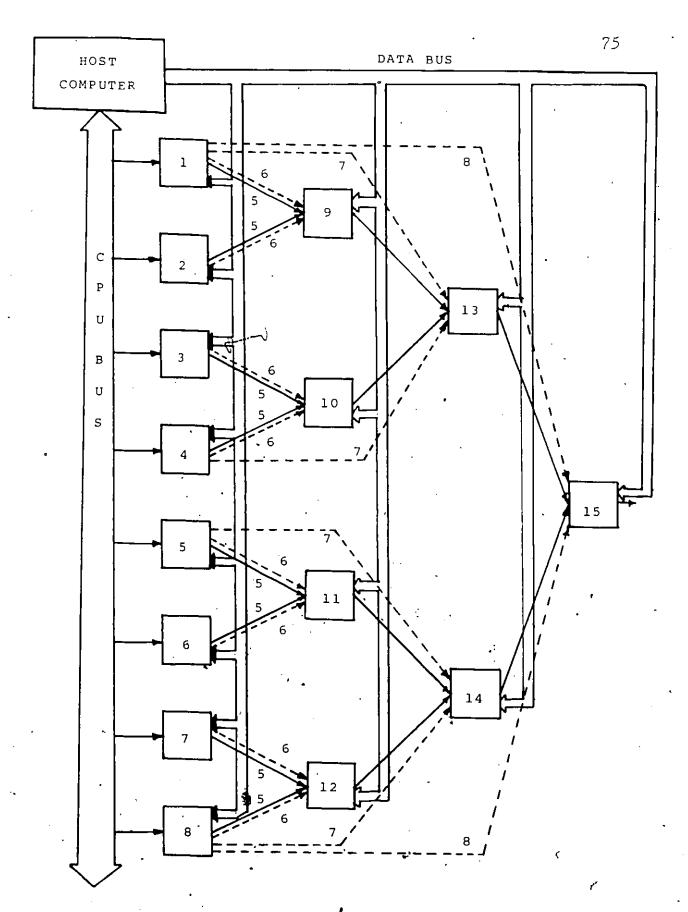

| 4.7   | Ram loading looup table interconnections   | 75   |

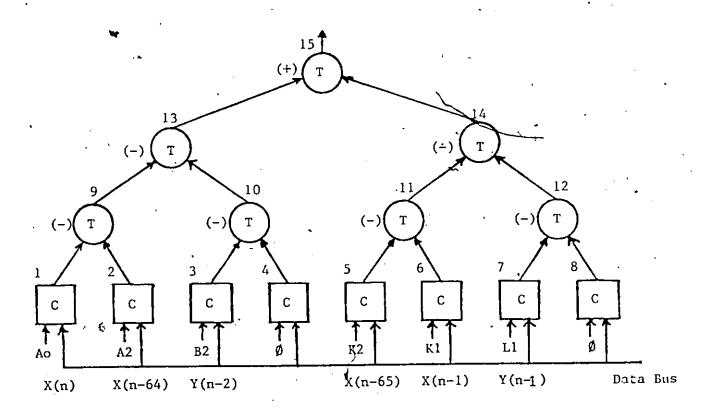

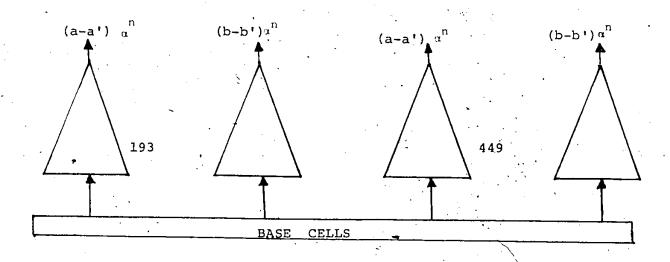

| 4.8   | Binary tree structure for filters          | 78   |

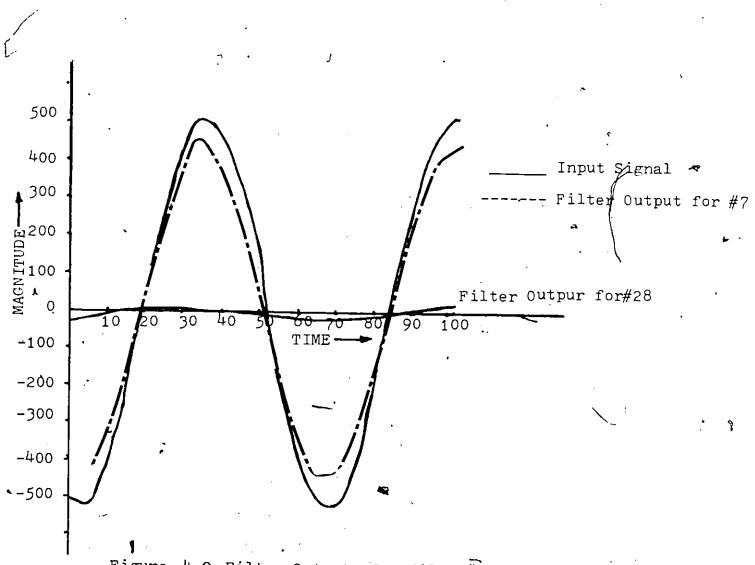

| 4.9   | Filter Outputs for #7 and #8               | 79   |

| 1 | N |

|---|---|

|   |   |

|   |   |

| 5.1   | Radix 2 DIF butterfly                          | 89     |

|-------|------------------------------------------------|--------|

| 5.2   | Butterfly for 4n+1 prime                       | 90     |

| 5.3   | Twiddle factor multiplication using large mode | ıli 91 |

| 5.4   | Implementation of NTT on the DFSP              | 92     |

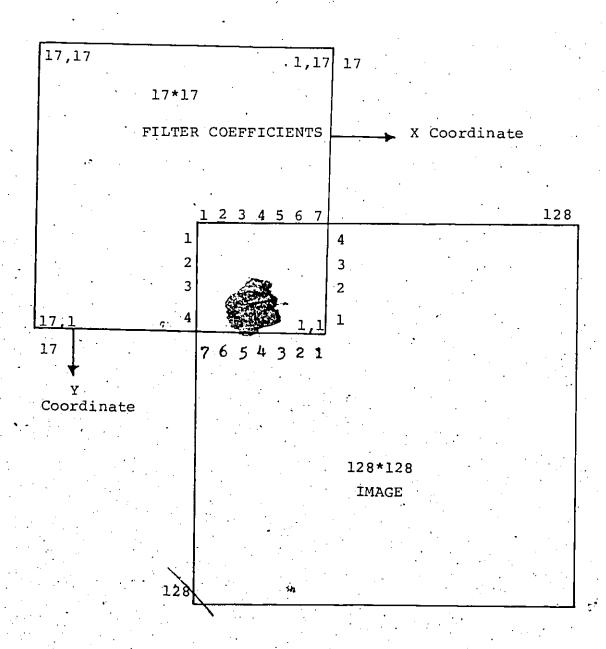

| 5.5   | 2 D direct convolution algorithm .             | , 100  |

| 5.6   | Computation time for 2 D convolution           | 101    |

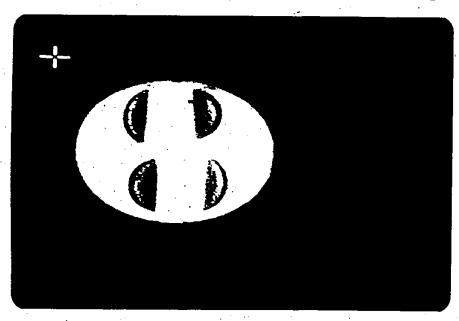

| 5.7a  | Original piston Head Image .                   | 108    |

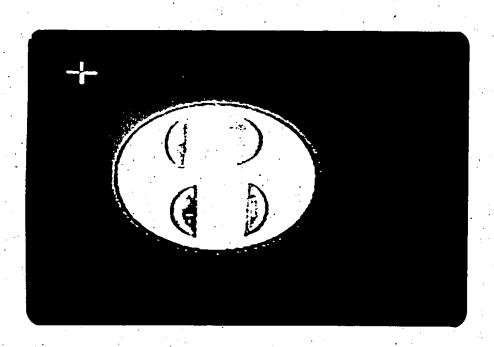

| .5.7b | Filtered image                                 | 109    |

| 6.1   | Data flow graph                                | 124    |

| 6.2   | Data flow graph for command program .          | 125    |

| A.1   | Block diagram of the filter structure          | 139    |

| A.2   | Block diagram of the complete system           | 140    |

| A.3   | binary to residue conversion unit              | 141    |

| A.4   | Modified Scaler unit                           | . 144  |

| B.1   | QRNS implementation of FIR filters             | 149    |

| B.2   | 1 D convolution using QRNS                     | 150    |

#### ABSTRACT

Digital signal processing has many applications in the areas of signal, radar, speech and image processing time implementation requires a very high throughput rate. applications need computation of repeated simple arithmetic operations and few 1/0 operations. Various processor architectures have been investigated [1-6] which reveals that a special purpose processor appropriate to the algorithms should be designed in order to achieve high throughput rates. Recently research efforts [7-14] are directed towards the exploitation of parallelism in the algorithms and parallel computation of these algorithms. been established that the Residue Number System (RNS) can be exploited for high speed signal processing applications [15-25]. The objective of this work is to propose new concepts for high speed computation of real time general purpose signal processing algorithms. As a starting point a very basic example of a set of band pass filter is used to investigate the feasibility of achieving the goal of high speed signal processing using RNS. The digital filter is first constructed and its structure is extended to a more peneral purpose signal processor architecture.

A novel architecture of a real time general purpose data flow signal processor (DFSP), based on the binary tree structure, is proposed for real time signal processing applications. The data flow signal processor exploits distributed, parallel, and pipeline processing approaches to achieve high throughput rates. The processor utilizes the residue number system (RNS) for high speed signal processing applications. The arithmetic operations in RNS can be performed via Random Access Memory (RAM) look up tables, and the execution time of any particular arithmetic operation is reduced to the access time of a RAM.

The data flow signal processor is demonstrated to be suitable for performing recursive, non-recursive digital filtering and convolution operations. Various signal processing algorithms are studied in order to investigate the adoptability of the DFSP to their special needs. Finally the thesis describes various alternatives for programming the DFSP, and data flow graphs are used to demonstrate the programming of the data flow signal processor. The data flow graphs are incoporated into an interactive program environment which is used to write application programs without knowing the internal architecture of the DFSP.

#### CONTENTS

| ACKNOWLEDGEMENT                                                                                                                                                                                                | ii                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| LIST OF ABBREVIATIONS                                                                                                                                                                                          | iii                        |

| LIST OF FIGURES                                                                                                                                                                                                | iv                         |

| ABSTRACT                                                                                                                                                                                                       | vi                         |

|                                                                                                                                                                                                                |                            |

| <u>Chapter</u>                                                                                                                                                                                                 | age                        |

| I INTRODUCTION                                                                                                                                                                                                 | 1                          |

| The Objective and Outline of the Research Thesis Outline                                                                                                                                                       | 8<br>10                    |

| II. GENERAL SIGNAL PROCESSING ARCHITECTURES                                                                                                                                                                    | 11                         |

| Microprogrammable Signal Processor  Fast Digital signal Processor Using RNS  Expression Tree Processor  Systolic Architectures  Data Flow Structures  Mago's Tree Structure  Data Flow Structures Using Packet | 21<br>22<br>27             |

| III. INITIAL STEPS FOR RNS IMPLEMENTATION OF DIGITAL FILTERS                                                                                                                                                   | 42                         |

| RNS Review Implementation of the Digital Filter Extension to General Purpose Signal Processor Architecture                                                                                                     | 42<br>44<br>49<br>57<br>58 |

| IV. DATA FLOW SIGNAL PROCESSOR                                                                                                                                                                                 | 59                         |

| Introduction .  Architecture Of The Signal Processor                                                                                                                                                           | 64                         |

|              |                                                                                                                                                                                                     |                                 | _          |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------|

|              |                                                                                                                                                                                                     |                                 | • • • •    |

|              | Host Computer Interface Operation of the Signal Processor Comments & Summary                                                                                                                        | . 71<br>. 76<br>. 80            |            |

| , <b>v</b> . | FIR FILTER IMPLEMENTATION                                                                                                                                                                           | . 82                            |            |

|              | Introduction  Number Theoretic Transform  Direct Convolution  Two Dimension Image Convolver  RNS Implementation of direct Convolution  Throughput Rate Considerations  Computer Simulation  Summary | . 94<br>. 96<br>103             | ~          |

| VI           | PROGRAMMING CONCEPTS OF THE NEW DATA FLOW                                                                                                                                                           |                                 |            |

|              | SIGNAL PROCESSOR                                                                                                                                                                                    | 112                             | ·          |

|              | introduction                                                                                                                                                                                        |                                 |            |

|              | DFSP                                                                                                                                                                                                | 116<br>118<br>119<br>120<br>126 |            |

| VI           | II. CONCLUSION                                                                                                                                                                                      | 128                             | <b>V</b> : |

| RE           | EFERENCES                                                                                                                                                                                           | 133                             |            |

| <u>A</u> r   | ppendix                                                                                                                                                                                             | page                            |            |

| Α.           | STRUCTURAL DESIGN OF A FILTER                                                                                                                                                                       | 137                             |            |

|              | Hardware Implementation                                                                                                                                                                             | 142                             |            |

| В            | COMPLEX DIGITAL SIGNAL PROCESSING                                                                                                                                                                   | 145                             |            |

|              | Hardware Implementation of QRNS                                                                                                                                                                     | 147                             | •          |

| C.           | COMPUTER PROGRAMS                                                                                                                                                                                   | 151                             |            |

| ĎΊ           | PTA AUCTORIS                                                                                                                                                                                        | 167                             |            |

|              |                                                                                                                                                                                                     |                                 |            |

|              | - ix -                                                                                                                                                                                              | •                               | •          |

|              |                                                                                                                                                                                                     |                                 |            |

#### Chapter I

#### INTRODUCTION

Digital signal processing has many applications in the area of speech, geophysics, radar, sonar, and image processing. These applications may be speech synthesis, speech recognition, signal generation, matched filtering, image enhancement, image restoration. They all have two dependent factors. The first concerns various parameters, such as frequency contents, dynamic range and signal to noise ratio. The second factor is of signal modelling which actually determines the processing requirements. The signals are mathematically modelled and manipulated to recover desired signal information. The signal manipulations consist of very few signal processing operations such as difference equation calculations for filtering operations, evaluation of coefficients for the discrete fourier transform (DFT), convolution and vector or matrix arithmetic operations. These common processing functions are the basic tools of digital signal processing and are widely described in the literature [3,25,39]. In the following we give a brief description of some basic signal processing operations and their requirements for the type of architecture employed.

The basic difference equation of an Nth order digital filter is of the form

$$Y(n) = \sum_{k=0}^{N-1} a_k \cdot X(n-k) - \sum_{k=1}^{M-1} b_k \cdot Y(n-k)$$

(1.1)

Recursive, or infinite impulse response (IIR), filters may be represented using eqn. (1.1).

X(n), Y(n) are the input and filtered output sequences, respectively. The parameters N, M,  $a_k$ ,  $b_k$  characterize the mathematical properties of the difference eqn. (1.1). The output Y(n) is the weighted sum of the N past and present inputs and M past outputs. If we remove the feedback elements by setting  $b_k = 0$  and k > 1 then:

$$Y(n) = \sum_{k=0}^{N-1} a_k . X(n-k)$$

(1.2)

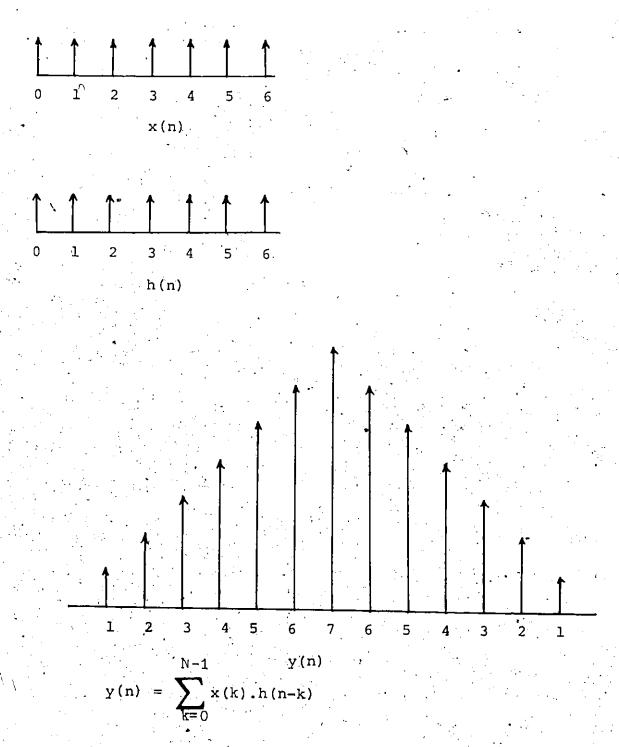

This equation represents a non-recursive or finite impulse response (FIR) filter and is commonly called the convolution sum. For FIR filters, the convolution sum can be directly evaluated to determine the output of the digital system; for IIR filters the equivalent convolution sum has, in general, an infinite number of terms.

Signal processing operations of frequency translation are commonly used by multiplying the input sequences of samples with the complex exponential which is shown as follows.

$$Y(n)=X(n).Exp(j2\pi nk)$$

(1.3)

Equation (1.3) is a part of the discrete Fourier transform which is used to translate data from time domain into frequency domain. The convolution property of the discrete fourier transform can be utilized for implementing FIR filters. The discrete Fourier transform can be defined as:

DFT:

$$X(k) = \sum_{n=0}^{N-1} x(n) \cdot Exp(-j2\pi nk/N)$$

(1.4)

DFT:

$$x(n) = \overline{N}^{1} \sum_{k=0}^{N-1} X(k) \cdot Exp(j2\pi nk/N)$$

(1.5)

where n=0,1,.....N-1

Various parameters and suitable signal processing operation for a particular digital signal processing (DSP) application specify a signal processing system. It has been shown above that signal processing operations need extensive addition, subtraction and multiplication operations. This arithmetic intensity characteristic of these operations requires a considerable amount of computation time if a processor is not designed to exploit parallelism. The implementation of these signal processing techniques for various applications varies from the use of general purpose computers, to the construction of special purpose hardware. The speed, cost and processing flexibility are factors in the choice of the implementation structure.

An efficient implementation of signal processing algorithms is very important for many applications. There are two

ways to achieve this goal: the first is to have an efficient algorithm, and the second is to implement it using fast processors. It is desirable to have an efficient approach for both algorithm and implementation for real time applications. The algorithms may be made efficient by using new techniques to reduce the number of arithmetic operations. An example may be of reducing the number of multiplications by first adding or subtracting the data which are multiplied by the same coefficient. Jeng [28] obtained an efficient convolution algorithm by dividing the input into smaller sequences and computing the convolution in parallel by using a multiprocessor system. Huang [38] described the convolution sum requiring 25 multiplication and 25 additions which was reduced to 6 multiplications and 15 additions by first adding data which are multipled by the same coefficients.

The second approach of efficient implementation is to use fast computers. The processing requirements for some of the applications are very high and can only be fulfilled by using a high speed and high performance computer. General purpose computers normally have many extra options such as complex arithmetic logic units, large memory, direct memory access and interrupt capabilities. The cost of these computers as compared to special purpose computers may be very high and some of their options may not be useful for signal processing applications. The implementation of these algor-

ithms on a general purpose computer does not match with architecture and requires arithmetic and memory intensive architectures. An architecture more appropriate for the implementation of these algorithms would require several high speed arithmetic logic unit (ALU), and separate data and coefficient memories. The execution speed of the ALU and the transfer rate of the data between the ALU and the memory should be balanced. The operands should be available for every execution cycle and there should be no excessive wait states either for the operands or for the execution of the arithmetic logic units.

In recent years there has been a growing interest in the implementation of DSP algorithms on special purpose hardware. This hardware varies from dedicated hardwired processors, for a particular algorithm, to specialized processors attached to a host computer. The computational speed is the major factor leading to the choice of a particular implementation dictated by the signal processing application. The basic building blocks of a processor are the components which determine the speed of operation. The components depend upon the current state - of- the art in the appropriate technology. The growth in VLSI technology has led to the implementation of special purpose signal processors. Further improvement in computational speed are obtained by exploiting parallelism in the algorithms by performing concurrent execution of the arithmetic operations.

Several processing elements are connected in parallel in order to perform computations concurrently. The approach of exploiting parallelism can provide high speed computations.

Peled & Liu [3] proposed a bit slice approach for the mechanization of the array multiplication which is a multiplication operation frequently used in signal processing algorithms. This operation can also be performed using a multiplication unit but their computation time will be high and will depend upon the size of the array. Peled & Liu's approach utilizes precomputed multiplication operations which are stored in a Read Only Memory (ROM). The computation time for any array multiplication will be B times the access time of a ROM (B is the word length). The Peled & Liu's structure is useful for dedicated signal processing algorithms. Hartung [2] proposed a programmable signal processor using two multiplication accumulator units and separate data memories. Multiplication accumulator units require two cycles to compute one operation. Using two units, an output would be produced in each cycle. The use of multiple memories eliminated delays associated with the waiting of the operands. Huang et al [38] proposed a fast digital processor for performing a two dimensional pulse matching convolution. Their approach adds the data which are multiplied with the same coefficients in order to reduce the number of multiplications. This approach is suitable for one particular application. Jeng [28] has manipulated the convolution algorithm in order to save arithmetic operations and proposed a sequence of operations which leads to saving in computation time. Jeng showed that the technique of breaking the convolution sum in smaller sequences provided faster computation time than the FFT approach. Using several multipliers and adders connected in the form of a tree structure increased the throughput rate.

The exploitation of parallelism in the algorithm is receiving wide attention. Massive parallelism can be achieved if the algorithms are designed to introduce a high degree of pipelining and multiprocessing. This has simulated work in the areas of data flow machines [7-12] and systolic arrays [13]. Data flow machines utilize multiple processing elements for concurrent computation of one algorithm. In a systolic array [13] data is fetched one element at a time from the memory, which can be used by all the processing elements in the array. Data flow machines and systolic arrays are very attractive architectures for high speed implementation of signal processing functions.

Recently the Residue Number System (RNS) [15-25] has been, utilized for high speed digital signal processing. Using RNS arithmetic operations are precomputed and are stored in ROM's in the form of look up tables. The computation time of the arithmetic operation is the access time of the ROM. RNS offers carry free operations and is more appropriate for parallel and pipelined computation. This work explores the

use of RNS for the design of a general purpose signal processor.

The architecture of the processor should be able to perform signal processing algorithms efficiently. The processor should be software driven and be able to adopt various applications by modifying the software. This goal can be achieved by expoiting parallel, pipelining and distributed processing approaches to increase the throughput rates. The goals for developing a novel architecture have been described in the following section.

#### 1.1 THE OBJECTIVE AND OUTLINE OF THE RESEARCH

The principal objective of this research is to explore various signal processor architectures which are described in the literature and to propose a novel architecture for a real time general purpose signal processor. The proposed processor should be programmable and suitable for wide variety of signal processing applications. The developments in the area of VLSI has led to the design of more and more signal processors which may be single chip processors [39,40] or special purpose processors optimized for a particular application.

It has been established that the RNS can be used for arithmetic operations associated with high speed signal processing applications. The RNS allows computation of arithmetic operation via look up tables where the operations of

addition, subtraction and multiplication are precalculated and are stored in the look up tables. The computation time required for these operations is the access time of the memory. The RNS offers parallel computation of arithmetic operations and is suitable for pipelining.

This work investigates various architectures which are available in the literature and explores the implementation of digital filters. As a starting point we explore the implementation of a set of band pass filters utilizing RNS approach. The structure of the filter will be extended to adopt wide variety of signal processing algorithms. We propose a binary tree data flow structure which will be capable of performing real time signal processing applications. The tree structure is capable of performing various operations and is very appropriate for distributed, parallel and pipeline processing. The binary tree structure is attached to a host computer which facilitates the programming of the processor.

We show that this proposed processor can accommodate recursive and non recursive filter operations. It is also shown that the direct convolution approach is better than the transform approach for the computation of convolution on this signal processor. Finally the software techniques for programming the processor are considered and various alternatives for programming the data flow signal processor are evaluated. Data flow graphs are shown as a software tool for programming for this processor.

#### 1.2 THESIS OUTLINE

In chapter 2, a review of the implementation of the varies ous signal processors is discussed. The architectures for general computations are also explored. Specifically data flow computers and systolic arrays are discussed and we evaluate if these architectures can be exploited for signal processing applications.

Chapter 3 covers the review of RNS and applications of RNS approach for signal processing operations. A description of the construction of a set of band pass filters is provided. The extension of this structure for more general purpose signal processing applications is discussed.

In chapter 4, the proposed no el architecture of a data flow signal processor is discussed. The binary tree structure and its host interface are shown and a scheme of loading the look up tables in the tree structure is described.

Chapter 5 describes the implementation of FIR filters using transform approach and direct convolution. A comparison is shown for a 2 D convolution example of an edge enhancement filtering operation of an image. A complex filtering approach using Quadratic Residue Number System (QRNS) is also presented.

Chapter 6 evaluates various software techniques available for programming parallel computers. A data flow graph approach is shown to program the data flow signal processor.

Chapter 7, concludes with a summary of this research.

#### Chapter II

#### GENERAL SIGNAL PROCESSING ARCHITECTURES

#### 2.1 INTRODUCTION

The growing demand for high speed computation has led to the design of faster computers utilizing the state of art components. Efforts have been directed towards exploiting the parallelism in the algorithms and performing parallel operations. The approaches of pipelinning in the instruction and utilizing more than one CPU's are also applied in order to reduce computation time. Array processors are used to provide faster computational ability. The concept of dual or multi processors is also a popular technique in the design of general purpose computers. The area of digital signal processing demands higher computation speed for real time applications. Many dedicated systems have been implemented for various signal processing algorithms. The techniques of developing efficient algorithms and using high speed hardware have been utilized and many researchers exploited the characteristics of a particular algorithm by tuning the architecture for maximum speed. This chapter reviews some of the dedicated signal processing approaches that have been adopted for dedicated signal processing hardware. Three different structures are discussed representing techniques which are used to improve throughput rate of a system. First approach discussed is of Peled & Liu [3] which mechanizes the multiplication accumulation operation frequently used in signal processing applications and represents a novel technique for high speed computation. The second structure described is the programmable signal processor [2] and illustrates an example of using multiple functional units and memories. This technique represents a parallel processing of algorithms. The last approach presented is the implementation of fast digital signal processor [38] and is an example of algorithm modelling for efficient computation of algorithms.

A review of other non-signal processing hardware is also presented which includes the expression processor, data flow computers and systolic arrays. The expression processor is based upon a binary tree structure and its processing elements are connected in the form of a binary tree which processes data concurrently. Data flow computers reject the well known Von-Neumann model and, instead, utilize multiple processors executing operations in parallel. The systolic structure provides an opportunity to utilize data for many operations and avoids repeated reading and writing of data from the memory. This property of systolic arrays reduces the computation time of a particular algorithm. The structure of systolic arrays and data flow computers are studied for their feasibility for implementing general purpose sig-

nal processing architecture. In the following sections we review various signal processing architectures that have been adopted to handle the high speed arithmetic functions. required for many real-time applications.

# 2.2 BIT SLICE APPROACH FOR ARRAY MULTIPLICATIONS

The multiplication of coefficients and data is a frequent arithmetic operation in the implementation of digital filters. This operation may be implemented using a multiplier and accumulator unit. Its sequential operation may require a longer computation time than that obtained using several multiplication units computing in parallel. Peled & Liu [3] proposed a new hardware realization for multiplication of apriori known coefficients and data using precomputed function which is stored in a ROM. The computation time will be the access time of the ROM times its word length. This approach is described using mathematical equations for calculating the function which can be precomputed and stored in the form of a lookup table. A frequent arithmetic operation which is repeatedly performed is of an array multiplications as shown by the following equation.

$$y = \sum_{j=1}^{L} a_j \cdot x_{,j}$$

(2.1)

a, is the set of predetermined coefficients and x are the input data values and y is the output. The scaled values of

input data  $|x_j| < 1$  can be represented in the 2's complement code with B bits accuracy in fixed point notation and can be rewritten as

y=

$$\sum_{j=1}^{L} a_j \cdot \sum_{k=1}^{B-1} x_j^k \cdot 2^{-1} \cdot x_j^0$$

(2.2)

If we interchange the order of summation over the indices j and k yields

$$y = \sum_{k=1}^{B-1} 2^{-k} \cdot \sum_{j=1}^{L} x_{j}^{k} \cdot a_{j} - \sum_{j=1}^{L} a_{j} \cdot x_{j}^{0}$$

(2.3)

a function F with L binary valued arguments can be defined as

$$F(X^{1}, X^{2}, ... X^{L}) = \sum_{j=1}^{L} x^{j}.a_{j}$$

(2.4)

Now equation (2.2) can be rewritten as.

$$y = \sum_{k=1}^{B-1} 2^{-k} \cdot F(X_1^k, X_{2'}^k, \dots, X_{n_k}^L) - F(X_1^k, \dots, X_{n_k}^L) - F(X_{n_k}^k, \dots, X_{n_k}^L)$$

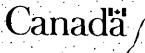

The values of the function are prestored in a ROM. There will be  $\overset{1}{2}$  possible values of F since F can take on the values 0 or 1 only and all possible combinations can be stored in a ROM of size 2. The output y is computed using the given value of the function and adding (subtracting for k=0) the partial outputs during the bit serial operations as shown in Figure 2.1. The data sequence X; is shifted serially into shift register SR1 to SRL by first shifting the least significant bit followed by all B-1 remaining bits. The address of read only memory (ROM) is constructed by tapping bits X, at the output of each shift register. The output of all shift registers becomes the address of the ROM. The value of the function F is accessed from the ROM and will be loaded into R1 and added to value in R2 and the result appears in R3. The operation is repeated B times except for the last operation where a subtraction is performed. The computed value of Y is available in R3 at the end of B cycles.

The above approach of Peled & Liu mechanizes array multiplication and is useful for small values of L. An increase in the value of L will exponentially increase the memory requirements. For example an increase in 15 from 15 to 16 would require an increase in memory from 2<sup>15</sup> =32K to 2<sup>16</sup> =64K. The design is appropriate for a particular dedicated application. Any change in the algorithm would require hardware modifications to the design. Peled & Liu have shown in [3] various trade offs of the hardware and speeds. Their design suffers with the dependence of the algorithm on the hardware.

Figure 2.1 A bit serial mechanization of an L term array multiplication

# 2.3 MICROPROGRAMMABLE SIGNAL PROCESSOR

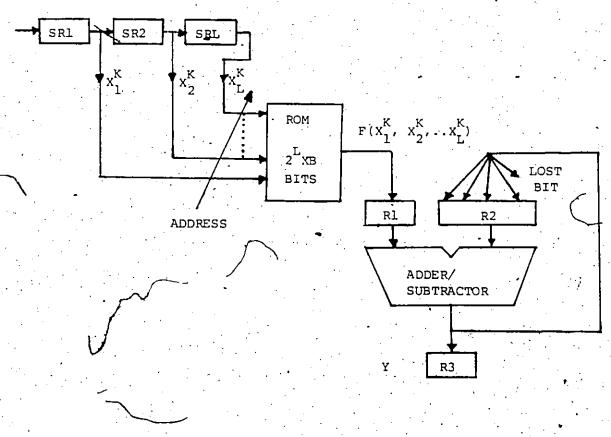

An architecture review of a microprogrammable signal processor is presented in this section. This design is proposed by Hartung [2] and the processor is attached to a DEC LSI 11 system which is capable of controlling the Progammable Signal Processor (PSP). The architecture utilizes two overlapped functional units, one arithemtic logic unit, three separate memories and separate data, memory and control buses as shown in Figure 2.2. Various functional units, memory and buses operate in parallel to improve the computational speed. The function (multiplication & accumulation) units require, two cycles to perform one operation. Using two overlapped functional units can produce results in every cycle provided if the input operands are supplied in every cycle. One functional unit is loaded with two operands while the other outputs to either the scaler unit or to the memory, this maintains one operation per cycle. The philosophy of apping the two functional units can be extended to more complex operations by providing the same number of functional units as the number of cycles required to compute one operation. If a functional unit requires N cycles to perform one operation, then utilizing N functional units will produce one result in every cycle after N cycles.

The microprogrammable signal processor proposed by Hartung [2] can implement sequential algorithms such as wave digital filters more efficiently. The proposed processor

does not optimize the functional units, control unit structure and program sequences. It is obvious from this design that by employing multiple functional units the processor speed can be improved.

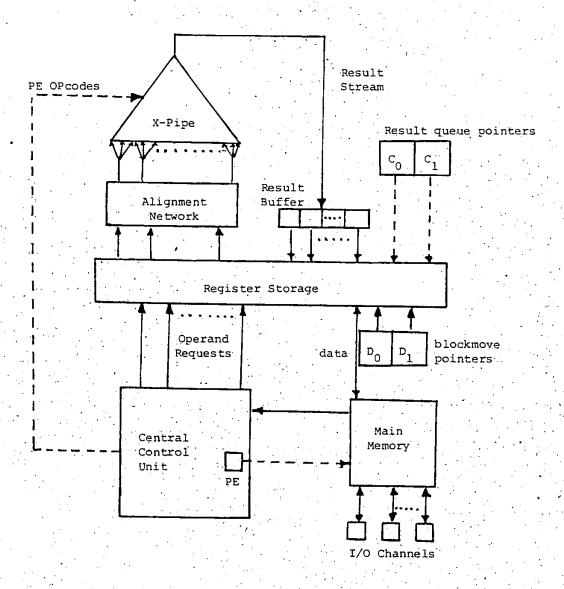

Figure 2.2 Programmable Signal Processor Architecture

#### 2.4 FAST DIGITAL SIGNAL PROCESSOR USING RNS

Huang et al [38] proposed a fast digital signal processor for performing a two dimensional pulse matching convolution. A two dimensional convolution is performed using a 5\*5 data with a 5\*5 predetermined filter kernel. The filter is symmetrical and the coefficients of row 1 & row 5 and row 2 & row 4 are identical. In order to save computation time the data of row 1 & row 5, row 2 & row 4 can be added since they are multiplied by the same coefficients. The addition of the data will reduce the required 25 multiplications and 25 additions to 6 multiplications and fifteen additions which will saye considerable computation time. The alogorithm proposed by Huang et al [38] is an example of algorithm modelling which reduces 25 multiplications and 25 additions for every outputs to 6 multiplications and fifteen additions. This approach offers an efficient algorithm which can be executed with a higher throughput rate than the original algorithm. Huang implemented this algorithm using dedicated. hardware controlled by an Intel 8086 microprocessor. Huang utilized a residue number system (RNS) for arithmetic opera-These operations are prestored in the ROM look up tions. tables and the computation time of the arithmetic operation is the access time of the ROM. . The detailed design can be found in reference [38].

Processor designs discussed above were directed towards dedicated signal processing applications and now we present

a few general non-signal processing acrchitectures in the following sections.

#### 2.5 EXPRESSION TREE PROCESSOR

An expression tree processor [14] based on a pipelined multiple processor architecture which is developed by Vanaken and Zick and is discussed in this section. The processor is a low cost machine constructed as a binary tree network. It is capable of exploiting the potential concurrency in numerical task and is intended to speed up the execution of a single large task rather than be multiplexed among a number of smaller tasks. The expression processor consists of a number of processing elements (FE's) and a large register space for high speed access of a data. It interfaces to a main memory containing data and its program code.

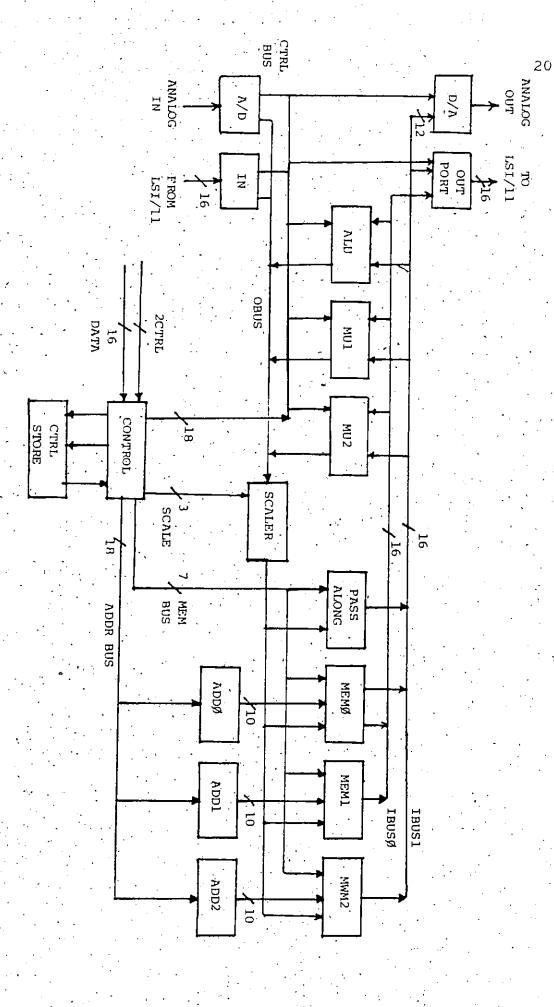

The operation of an expression tree pipeline (X-pipe) of seven PE's evaluating the expression tree for

is shown in Figure 2.3.

The processing elements are data driven and a series of expression trees can be executed in a pipeline for enhanced concurrency. The design emphasis of the processor is on limiting the complexity of the interconnection topology and distributed control functions in a modular fashion.

An expression processor containing 32 PE's and eight register modules are considered in this design. The 32 PE's are

connected in a binary tree network. Data is supplied from 8 fast RAM modules operating in parallel at a rate of eight words per cycle. The result from X-pipe emerges in serial fashion and is collected in an eight-word register buffer, which is transferred to the register modules in parallel. A block diagram of expression processor is shown in Figure 2.4.

The processing elements are not allowed to exchange data directly with the main memory. Operands are routed to input ports of eight PE's through a set of eight operand corridors. A general purpose alignment network is used to route operands from the register module to the operand corridor. A block transfer of data takes place between the memory and the register space, which is managed by DO-D1 pointers. The main memory stores both data and program codes. A set of I/O channels are used to interface the processor with the outside world. The central control unit manages the program counter, interprets instructions and updates register pointers.

The processor has modular structure, using identical PE's. It simplifies the design of the system, and control functions do not have to be implemented in random logic. It uses a central control unit to perform global coordination, initiating request for register data and issues opcodes to PE's. Most of the interconnection complexity is located in the interface between the PE's and the register modules.

The expression processor concept can be utilized for signal processing applications. A drawback of this design is that operands can not be supplied to all processing elements in the base of the tree structure in one clock cycle. The processor will require redesigning of the processing elements, register modules and memory. An additional module is required for scaling operations and control among all the moduli units.

Figure 2.3 X-pipe evaluation of arithmetic expoession

Figure 2.4 An overview of the expression processor

## 2.6 SYSTOLIC ARCHITECTURES

An appropriate method to increase the computation speed is to utilize several processing elements which can operate in parallel. The processing elements should be connected in such a way as to avoid any communication problem between the memory and its processing element (PE). The balance between the execution time of an operation and obtaining the operands from the memory should be maintained. If an operand fetched from the memory can be utilized by several PE's then an increase in the computation speed can be achieved. Kung [13] proposed the concept of systolic architectures for mapping high level computations into hardware structures. The data in a system flows from the computer memory in a rhythmic fashion, passing through many processing elements before it returns to memory much as blood circulates to and from the heart.

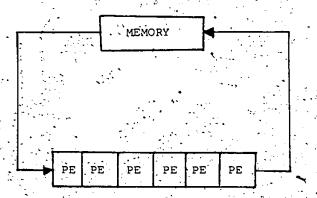

A systolic system consists of a set of interconnected cell each capable of performing some arithmetic operations as shown in Figure 2.5. Data in a systolic system flows in a pipeline fashion and communication with the outside world occurs only at the boundry cells. In a systolic array the boundry cells may be the I/O ports. The basic principle of systolic structure is to replace single processing element with an array of PE's. This type of arcitectures can achieve higher computation throughput and use simpler communication and control structures.

An example of systolic design for the convolution problem is presented here.

Given: the sequence of weights  $(w_1, w_2, \dots w_k)$  and input sequence  $(x_1, x_2, \dots x_n)$

compute the result sequence  $(y_1, y_2, \dots, y_{n+1-k})$  defined by  $y = w_1 \cdot x(i) + w_2 \cdot x(i+1) + \dots \cdot w_k \cdot x(i+k-1)$

The convolution problem can be viewed as a problem of combining two data streams wi's and xi's to obtain a result stream of yi's. There are several ways of implementation, one of the three data values are stored in the cells and the other two can be moved either in the same or opposite directions.

Systolic arrays have been utilized for 1 dimensional, 2 dimensional convolutions and matrix multiplications. The convolution problems perform more computation operations than I/O operations. This problem is well suited to systolic arrays since an input data xi can be multiplied by all the weighting coefficients. One of the advantages of the systolic arrays is that they utilize identical PE's which are more adoptable for VLSI implementation. Systolic arrays are utilized by various researchers for signal processing applications and offers a promising technique.

Figure 2.5 Systolic Array

#### 2.7 DATA FLOW STRUCTURES

A general purpose computer is based upon the John Von-Neumann model [7-12] which has a single Central Processing Unit (CPU), memory and a link connecting the CPU and the memory as shown in Figure 2.6. The huge contents of the memory must pass through the link which connect CPU and the This link blocks parallel execution of the algormemory. ithm and is known as the Von-Neumann bottleneck. The philosophy of the execution of a general purpose computer is based on storage. Instructions are executed by first accessing operands from the storage, perform arithmetic operation and store the output result back in the memory. Algorithms are executed sequentially even if the algorithm may have operations which can be performed in parallel. The sequential. execution of algorithms can be changed using direct memory access and interrupt techniques. Direct memory access and interrupt approaches are the earlier efforts to block the sequential operation of a particular algorithm.

Recently attention has been focussed on the data flow computers which rejects the Von-Neumann model. The data flow computers can employ multiple processing elements and provide patallel execution of the algorithms. Two data flow structures namely Mago's [7,9,10] tree structure and U- Interpreter [10] proposed by Dennis and Arvind are presented in the following sections.

Figure 2.6 Von-Neumann Model

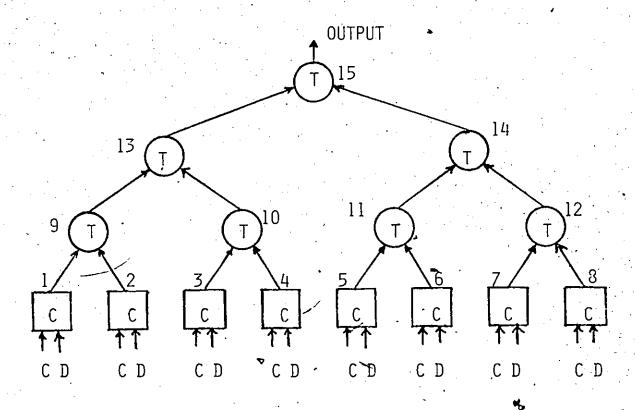

# 2.7.1 Mago's Tree Structure

Mago's data flow computer consists of an arbitrarily large number of cells connected in a binary tree [7,9] as shown in Figure 2.7. There are two types of cells namely leaf or L cells and tree or T cells. Each cell communicates with one parent cell and two child cells. The leaf cells form the base of the tree. They are connected to their two neighbouring L cells and are the child of a T cell. All the L cells and T cells are identical, so that the overall computer design is simple and well adapted to VLSI technology.

The functional programs and data are fed into L cells. The T cell partitions the expressions, breaking it down into smaller sub- expressions. They are composed of a function and the data; each function can be evaluated at the same time. The L cell has its local storage and processor, while T cells manage communication between the L with a very simple processing unit. The operation of the computer consists of a series of upward and downward sweeps of information. The process begins with the innermost parts and ends when the entire expression has been evaluated.

T cells distribute the microprogram required by each L cell and program execution is performed by all the T cells and L cells. The information will sweep up to the top of the tree working on a given expression in each cycle. The information is collected at the top T cell and is sent down for further processing by L cells. These upward and down-

ward sweeps of processing are continued until an entire expression is computed.

This architecture has a fairly simple cell containing a microprocessor and its storage. The cost of the system will not be very expensive since all the cells are identical. The approach is deterministic and can be applied to signal processing applications with several modifications in the structure which will be described later in chapter 4.

L = Leaf Cell

(CPU, Condition registers and u storage)

T = Tree Cell

(Data register and simple processing unit):

Figure 2.7 Mago's tree structure computer

# 2.7.2 Data Flow Structures Using Packet communication Network

An important alternate approach of data flow architectures [7,10-12] is led by Dennis and Arvind followed by a number of researcher including Burkowski [12] and Watson [11]. Their machine can employ multiple processing elements connected by a packet communication network as shown in Figure 2.8. The information is conveyed from one unit to another using the tokens or packets. A token contains the data, source and destination tag and sufficient control information to travel across the network. The tokens carry the information telling to what processor the token is to be sent and with which other tokens its data is to be combined. When a processor receives a token it matches with its mate, performs the appropriate operation and forms a resultant token.

The architecture of a processor is as shown in Figure 2.9. A token normally arrives at the waiting matching section, which keeps tokens waiting for their mates. When a pair of matching tokens is formed, it is sent to instruction fetch retrieving the needed instruction froms its program memory. The tokens are then forwarded to ALU for the computation of arithmetic operation. The result is sent to the output section where it is incorporated into a new token whose control information is obtained from the tags of the incoming tokens. The output token is sent back to the network.

There are a few drawbacks of this type of data flow architectures.

- 1. There is a 200% overhead in the bits of the tokens.

- 2. The tokens are transmitted byte serially using an asynchronous packet communication protocol.

- 3. The approach is non-deterministic and it will be difficult to calculate the throughput rate of the system.

These problems lead to the conclusion that this type of architecture is not suitable for real time signal processing applications, since there is an unlimited delay at the waiting matching unit. The token may have to wait for a longer period of time for its mate. Moreover, if a token is lost then the particular algorithm cannot be performed which will affect the performance of the system.

Figure 2.8: N\*N Communication Network

Figure 2.9 Cell structure of a data flow architecture

## 2.8 SUMMARY & COMMENTS

A review of various digital signal processing hardware available in the literature has been presented. This review is by no means complete and a full review will be beyond the scope of this thesis. The implmentation of a bit slice approach for array multiplication and its limitation were discussed. The main philosophy behind the programmable signal processor proposed by Hartung is the utilization of overlapped functional units which requires two cycles to complete one operation. Using two functional units, the processor can produce an output result in every cycle. Hartung's idea advocates the use of many processing elements to improve the computation speed. The programmable signal processor can be used for the implementation of wave digital filters.

Various other signal processing architectures have been reported in the literature [39-40]. Jenq [28] proposed an algorithm for computing direct convolution. He showed that performing direct convolution using multiprocessor system provides better speed than using transform approach. Baraniecka [21], Jenkins [25], Akhter [23], Modak [24], and Nagpal [22] showed the implementation of number theoretic transform (NTT) using residue number system. Their approach of implementing NTT can be utilized for fast digital signal processing applications. Nagpal et al [20] proposed an architecture for two dimensional convolver which performs 2D convolution using NTT approach within the video rate limits.

The expression tree proposed by Vanaken [14] utilizes multiprocessors connected in a tree structure. This design has a limitation of providing the operands to all the processors in one cycle and better memory management approach is required to further improve its speed of operation. Systolic arrays provide a solution to the balancing of the execution time of the processor and I/O transfer between the memory and the processor. All processors in the systolic arrays can utilize data fetched from the memory repeatedly. This saves the repeated access of the data from the memory and improves the computation speed.

Finally the approach of non-Von Neumann computer such as data flow computers was also evaluated. The data flow computer proposed by Arvind is not appropriate for real time signal processing applications. The main drawbacks of the U-Interpreter are the indefinite time delay in the waiting matching units and the 200% overhead in the communication of the tokens. The tree structure proposed by Mago [9] can be utilized for signal processing applications.

It can be concluded at this point that there is a need for a general purpose signal processor which should be appropriate for a wide variety of signal processing algorithms. The processor should be software configurable and hardware independent. The architecture should exploit all the parallel processing approaches to provide a high throughput rate. A new concept of a general purpose pro-

grammable signal processor architecture is discussed in the next two chapters.

# Chapter III

# INITIAL STEPS FOR RNS IMPLEMENTATION OF DIGITAL FILTERS

#### 3.1 INTRODUCTION

Most of the research work in the area of hardware implementation of digital signal processing algorithms utilizes binary number system (fixed or floating point): It has been established that DSP algorithms require extensive simple addition, subtraction, and multiplication operations. The multiplication is considered as the most time consuming operation and many forms of binary multiplier structure have been proposed to reduce the multiplication time. The commercially available high speed multipliers are restricted to a limited dynamic range. Any increase in the dynamic range may require. either an extra multiplier or reduction in the computational speed. The residue number system (RNS) offers carry borrow free arithmetic operations which does not introduce internal. delays due to carry-borrow digit propagation, flexibility in the dynamic range, equal computation time for all the arithmetic operations and is described in the following section.

Recent work in the area of residue number systems (RNS) [15-25] provides the opportunity of parallel computation or multiprocessing of high speed digital signal processing al-

gorithms, even though the algorithms do not possess inherent parallel Tsm. Using the RNS arithmetic operations can be prestored in ROM arrays. The time required for a particular operation is the access time of the ROM and the time to capture the data in a latch for the pipelining purposes. The memory structures are appropriately utilized by the RNS because of the parallel nature of the arithmetic. The arithmetic operations within a given dynamic range are performed using N independent parallel paths. The dynamic range can be increased by adding additional parallel paths. problems with RNS arithmetic are the computation of division, sign detection and magnitude comparison. Fortunately, the operations can be effectively dispersed with in most of the useful signal processing functions. The other problem, that of efficient scaling has been addressed in great detail in the published literature and several schemes are available to provide overflow protection.

Jenkin and Leon [25] proposed the implementation of FIR filters using RNS. A ROM oriented scaling operations and implementation of recursive filters have been described by Jullien [16]. The implementation of the number theoretic transform has been investigated by Baraniecka [21], Akhter [23], Modak [24], and Nagpal [22]. It has been established by the above mentioned works and the works of other researchers that RNS can be effectively used to implement high speed signal processing algorithms.

## RNS REVIEW

completeness.

The residue number system (RNS) has been discussed profusely in the literature. Here we present a brief review for

A number in the RNS can be represented in the form of an n tuple

$$X = (x_1, x_2, x_3, \dots, x_n)$$

(3.1)

where  $x_1, x_2, \dots, x_n$  are the residues w.r.t. the set of moduli  $m_1, m_2, m_3, \dots, m_n$  where  $GCD(m_1, m_2, m_3, \dots, m_n) = 1$

The residues are normally represented as |x| The range of numbers that can be uniquely represented is the product of the moduli.  $m_{\hat{1}}$  A binary operation (\*) between two numbers can be represented as:

$$Z=(X*Y) \tag{3.2}$$

It can be shown that the operations can be performed independently between matching residues such that

$z = (x_i * y_i) |_{m}$

Thus the result can be computed with n-parallel arithmetic functions. By restricting the size of each module, all possible arithmetic results can be precomputed and stored in the look-up tables. Using RNS arithmetic, addition, subtraction have no carry or borrow operations and multiplication is free from the generation of partial products. A

signed integer can be represented using RNS by assuming positive numbers in the range of (0, M/2-1), (0,M-1/2) for even and odd M respectively. The negative numbers can be represented in the interval (M/2,M-1), ((M+1)/2,M-1) for even and odd M respectively. Division is a complicated process in RNS, normally a scaling operation is used in which the divisor is limited to a predetermined factor and should be a product of some of the moduli.

Recent advances in the memory technology provide an opportunity to perform arithmetic operations using look up tables stored in the memory. The arithmetic operations are precalculated and are stored in a location addressed by the two input operands. A memory size of (2 \*B) bits is required to store the look up tables for a B bit modulus, For example  $m_1 \leq 32$  can be stored in a commercially available ROM package of 1k\*8. The main advantage of look up table implementation is that it requires equal time to compute addition, subtraction and multiplication. Figure 3.1 shows the implementation of

$$5*(A*B)+3*(C*D)$$

(3.3)

One of the advantages of RNS is that the multiplication by constants 5 and 3 used in Eqn. (3.3) wil not require an extra look up table. Using RNS it is easy to pipeline arithmetic operations since the output of one stage becomes the input address of the next stage. The use of RNS arithmetic requires the conversion of binary numbers into and out of the

RNS representation. A binary to residue operation is simpler than residue to binary conversion and can be implemented using ROM arrays. For example, in an L-moduli RNS the ith residue of number x is given by

$$x_{i} = \left| \sum_{j=0}^{B-1} b_{j} \cdot 2^{j} \right|_{m_{i}}$$

(3.4)

where bj is the jth bit of binary representation of X. For B<10 bits and m<32 equation 3.4 can be implemented with a ROM package of 1k\*8 bit.

Figure 3.1 Hardware Implementation of  $|5*(A*B)| + 3*(C*D)|_{31}$

There are two general techniques for residue to binary conversion based on Chinese Remainder Theorem (CRT) and mixed radix conversion (MRC) schemes.

Using CRT a number X in the range 0 to M-1 is given by

$$\left\| \mathbf{x} \right\|_{\mathbf{M}} = \left\| \sum_{\mathbf{j}=1}^{\mathbf{n}} \mathbf{m}_{\mathbf{j}} \cdot \left\| \frac{\mathbf{r}_{\mathbf{j}}}{\mathbf{m}_{\mathbf{j}}} \right\|_{\mathbf{m}_{\mathbf{j}}} \right\|_{\mathbf{m}_{\mathbf{j}}}$$

where

$$M = \prod_{i=1}^{n} m_i$$

,  $m_i = -\frac{M}{m_i}$

and

$$\left(\begin{array}{c} \frac{1}{m_{j}} \\ \end{array}\right)_{m_{j}}$$

is the multiplicative inverse of

The hardware implementation of (3.5) requires a large modulo M adder which is difficult to implement for large values of M. The chinese remainder theorem conversion scheme may not be preferable for many applicatations.

The mixed radix conversion scheme is normally used for high speed implementation of residue to binary conversion. Using MRC a number in the range O to M-I has the representation

$$X = \sum_{i=0}^{L-1} a_i \cdot P_i$$

where  $P_0 = 1$  and  $P_1 = \prod_{k=0}^{\infty} m_k$  and the a are the mixed radix digits in 0 < a < m

The [a] can be generated using look up table implementation by forming the partial outputs. The MRC approach is widely used and has been discussed in the literature [21].

RNS arithmetic is applied to a digital filtering problem in order to explore its usefulness and determine the degree of difficulty in its implementations. An example of a set of band pass filters using RNS is analysed and simulated on the digital computer to check the proper flow of data and verify the output results. The filter is then constructed as a prototype to uncover any hidden problems in the architecture.

#### 3.3 IMPLEMENTATION OF THE DIGITAL FILTER

Many hardware implementations of digital signal processing algorithms are available in the literature. There are hardware which are dedicated to one particular algorithm. Others are more flexible which may incorporate any changes in the algorithm. The process of designing hardware for a particular algorithm is performing a marriage between the algorithm and the hardware. Before this marriage can be performed there are number of questions which should be answered ie word length, quantization, speed of operations the algorithm characteristics and a simulation study should be used to investigate any flaws in the design. In terms of

hardware considerations, it has been shown earlier that signal processing algorithms require arithmetic and memory intensive architectures. Multiple computational units and memory units can be utilized to perform concurrent arithmetic operations. Multiple memories can provide operands in one clock cycle which will avoid any delay associated with the waiting of operands.

Using an appropriate model of input signal, the filter structure is simulated on the digital computer. The output of the simulated filter is compared with that obtained, using infinite precision to find the error between the outputs. If the error is not within the acceptable limits, the word length can be varied in order to achieve an acceptable error. The wordlength may be decided based on the simulation results. With the specified dynamic range and quantization level, a suitable hardware can be realized. The computation is again performed within the specified wordlength and checked for any overflow during the execution of the algorithm. If there is any overflow dynamic range may be in-After verification from the simulation of the creased. hardware, efforts can be directed towards a more detailed design of the hardware. In order to verify these steps for building general hardware for digital signal processing algorithm, we select a very basic design of a set of band pass filters which is first designed and will be constructed. We will use this example for a set of band pass filters as a

test vehicle for more general purpose structure. The process of designing hardware for a digital filter is divided into the step of structural design of the filter and its hardware implementation. The stuctural design of the filter has been described in detail in Appendix A.

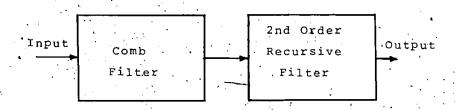

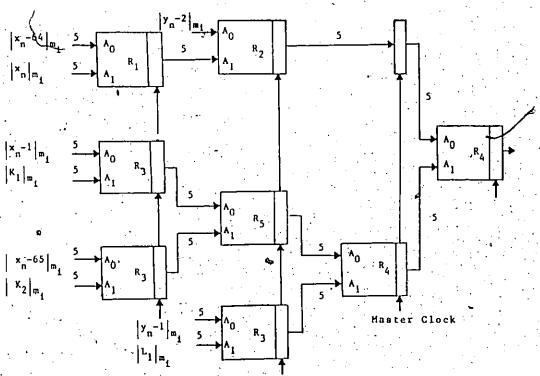

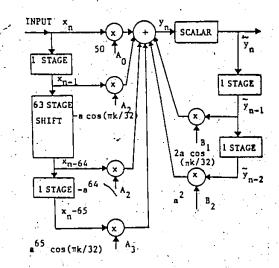

A set of band pass filters can be implemented by multiplexing a single filter section as shown in Figure 3.2. The first part of the filter is a comb filter which can be used unchanged for all the filters. The latter part of the filter, is a second order section. The result is a filter with the maximum gain at the particular cancelling frequency and reducing gain side lobes. This filter is expressed mathematically as follows.

$$Y(n)=X(n)-a.Cos(\pi k/32).X(n-1)-a^{64}.X(n-64)+a^2..Y(n-2)$$

+a<sup>65</sup>.Cos(\pi k/32).X(n-65)+2a.Cos(\pi k/32).Y(n-1)

where k=1, .... 32, and  $a=1-2^{-5}$

It can be seen from the above equation that the filter implementation requires multiplication, addition and subtraction operations. These operations can be precalculated and stored in ROM's in the form of look up tables. One of the advantage of RNS is that multiplying with a constant

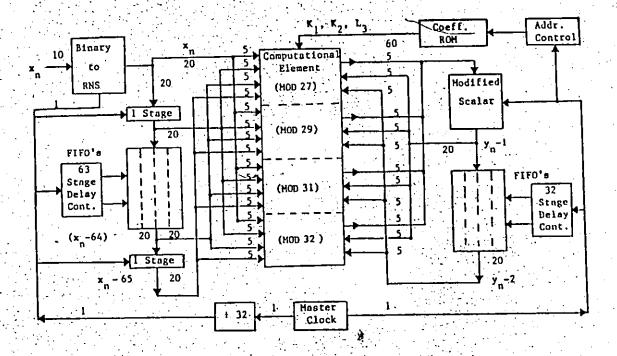

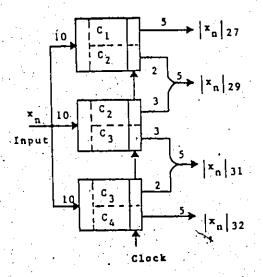

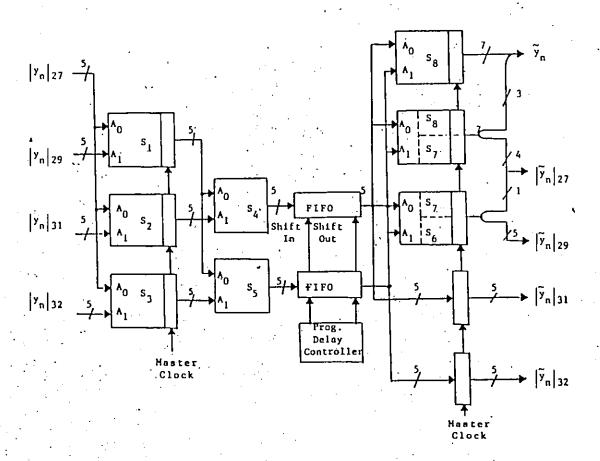

does not require an extra look up table. This property has been exploited and multiplication with fixed coefficients are incorporated in the look up tables. The block diagram of the computational element is shown in Figure 3.3. Four five bit moduli 27,29,31 and 32 are selected giving a dynamic range of 20 bits which is sufficient for this application. The detailed structure of the filter is given in Appendix A. Binary data are converted into four residues which are inputs to the computational element. A programmable delay: controller is implemented and a FIFO is used to provide an arbitrary delay. Thus, when initializing the 64 stage delay FIFO, we start the shift in pulse train, wait for 64 pulses to occur and then start the shift out pulse train. Using this scheme, there is one pitfall to watch out for. We have to make sure that the data has sufficient time to 'fall through from the input to the output. Fall through time has to be less than or equal to the delay of the FIFO. There are four computational elements representing each moduli and data is processed in four redundant paths. The computational element produces four output residues and they are scaled down using an efficient scaler which gives a direct binary output. The filter is constructed using EPROM's, shift registers and FIFO memories. . The performance of the filters, in terms of throughput rate depends on the components chosen. The basic pipeline element for the arithmetic circuit is an EPROM followed by a latch. We used the 2708 EPROM and

8212 latch. The worst propagation delay is (470+30)=500 ns. The delay time can be reduced if we select faster EPROM's. The basic pipeline element for the delay stages is a FIFO. We used the MMI 67402 5 bit FIFO which gives the worst case propagation delay of 3µs/D (D is the FIFO delay) or 100 ns whichever is the larger. For delays, D, greater than 30, the worst case delay is 100 ns. This covers all of the FIFO's except those in the scaler array. In the later case the worst case propagation delay is 115 ns. Using an average figure (500+115)/2=305 ns, the output data will be generated at a rate of 3.2 M Hz which translates into a rate of 100 K. Hz for input data. The filter bank can thus handle signals with bandwidths of up to 50 K Hz.

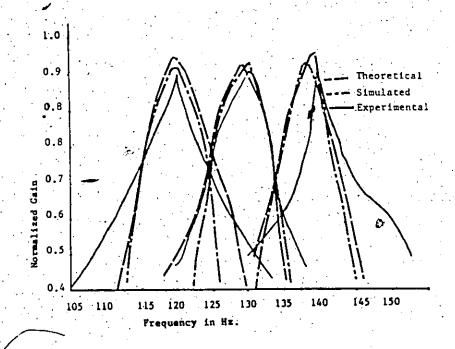

A varying frequency sinusoid of maximum allowed magnitude was applied to the input of the filters. The output of each filter was monitored on an oscilloscope. A maximum positive magnitude of the sinusoid output was measured of each increment in the input frequency. Normalized filter gain versus frequency was plotted for three consective filter outputs 13,14,15 as shown in Figure 3.4. We used for convenience an 8 bit A/D and an 8 bit D/A chip. Some errors are to be expected between simulated and experimental results because of, this excessive quantization. Even so, the results as shown in the comparison plot are in remarkably close agreement.

Figure 3.2: Bandpass Filter Structure

$R_1$ ,  $R_2$  = constant coefficient ROMs  $R_3$ ,  $R_4$ ,  $R_5$  = Multiplication, Addition, Subtraction ROMs

Figure 3.3: Comutational Element

Figure 3.4: Normalized Frequency Response

# 3.4 EXTENSION TO GENERAL PURPOSE SIGNAL PROCESSOR ARCHITECTURE

The implementation of the digital filter described above utilizes EPROM's for storing precalculated arithmetic operations and shift registers & FIFO's to provide input and output data delays. This structure of digital filter can be extended to a more general purpose signal processor by changing all the EPROM's used for storing arithmetic operation and coefficients into RAM's. The data can also be stored in RAM's and any arbitrary delay can be obtained by an appropriate address generation scheme.

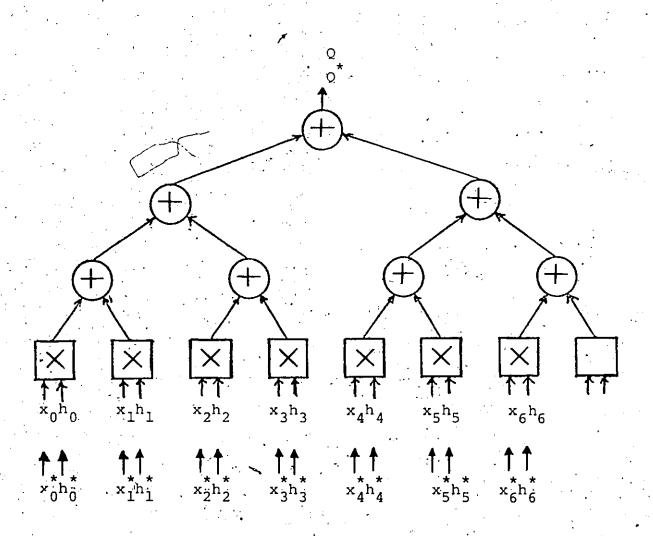

The structure of the above filter has many arithmetic operations which are independent of each other and can be performed in parallel. This structure will then resemble a binary tree having a number of cells at every level. The base of the tree structure can be used as multipliers. The outputs of the base cells are forwarded to the next level for additions and subtractions. The final output can be obtained at the last stage. If this structure is replaced with a binary tree structure then it can be used by a large number signal processing algorithms. This idea is implemented into a general purpose signal processor and the example of the set of bandpass filters will be used to verify the adaptability to the new architecture.

#### 3.5 SUMMARY

A review of the RNS was presented and it was shown that arithmetic operations can be precalculated and stored in ROM's in the form of look up tables. The RNS offers carry borrow free multiplication, addition and subtraction operations and operations with fixed numbers do not require an extra look up table. The time required for a particular arithmetic operation is the access time of the ROM and time to capture data in a latch for pipelining purposes.

This work demonstrates that practical high speed digital filtering designs can be realized using the residue number system. The resulting memory intensive structure which implement the filter example shows the viability of inherent parallel processing, and ease of pipelining. This is evident even in the implementation of recursive filter structure with inherent feedback loops. Although the structure is programmable in nature changing coefficients and moduli will require re-programming of EPROM's and some changes to the control circuitry. It was discussed that the filter structure can be extended to more general signal processing architecture.

# Chapter IV DATA FLOW SIGNAL PROCESSOR

#### 4.1 INTRODUCTION

Advances in the computer technology has led to a growing demand for real time applications of digital signal processing. Algorithms for these applications require repeated simple arithmetic operations and few I/O operations. acteristics of these algorithms can be exploited by designing arithmetic and memory intensive architectures. Many arithmetic units can be utilized to perform arithmetic operations concurrently and separate memories can provide. data and coefficients as required operands in one cycle. Accessing of two operands in one cycle will improve the throughput rate. Many researchers have exploited these characteristics and designed various processors for dedicated signal processing applications [1-6,15-26]. These hardware seem to have one common thing that they are dedicated to, one or another class of algorithms such as filtering or transform algorithms.

Hardware discussed in the literature [2-5,28,38] have exploited parallelism to a certain extent and some efforts are made to exploit parallelism in the algorithm. In order to execute a particular algorithm efficiently both algorithms

and their implementation should be exploited for maximum throughput rates. Many of the hardware in the literature tend to be dedicated to a particular algorithm. Our intention is to introduce a new concept which can be used to develop a general purpose signal processor architecture. The processor can be utilized for a wide variety of signal processing algorithms.

We utilize the results of previous example of the band pass filter for implementation of the digital filters and develop a novel general purpose signal processor. It can be shown that a binary tree may be able to adopt a wide variety of algorithms and perform computations concurrently. The concurrent computation of a particular algorithm will give a very high throughput rate which will be suitable for real time signal processing applications. Processing elements can be connected in a binary tree and may have their CPU and memory. The parallel operation of these processing elements will be independent of each other. The operands will be available simultaneously to perform a particular arithmetic operation. Outputs will be forwarded to the next level of the processing elements. This architecture rejects the Von-Neumann model and will not require any central control unit. This structure can be named as data flow tree structure since the data flows without any control unit. The structure may require a host computer to provide a user interface. We propose a general purpose data flow signal processor architecture which can be used for many signal processing applications and should be software driven.

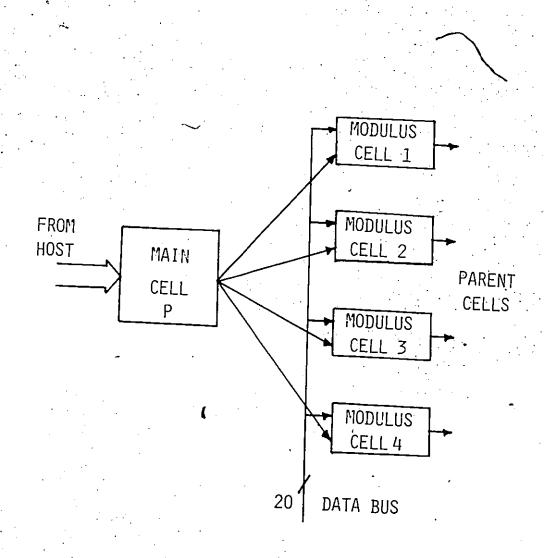

This chapter on the Data Flow Signal Processor (DFSP) describes a novel structure of a programmable general purpose signal processor for real time signal processing operations. The DFSP architecture is based on a binary tree structure [7,9,14,18] as shown in Figure 4.1.

There may be an arbitrary number of processing cells in the binary tree, depending upon the design, processing data simultaneously. A particular algorithm can be divided into smaller tasks and distributed to several processing cells. A host computer distributes the control program to the base cells of the tree structure. The base cells perform individual tasks, and facilitate the multiprocessing and pipelining of the tree structure. The data flows without requiring any central control units, unlike Von-Neumann architectures.

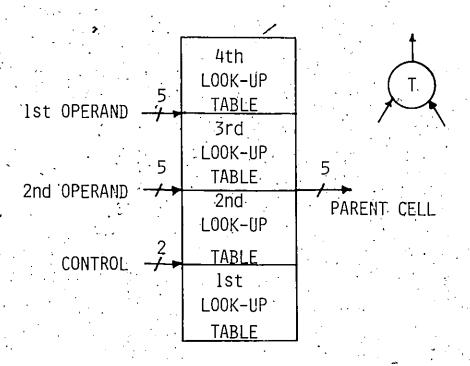

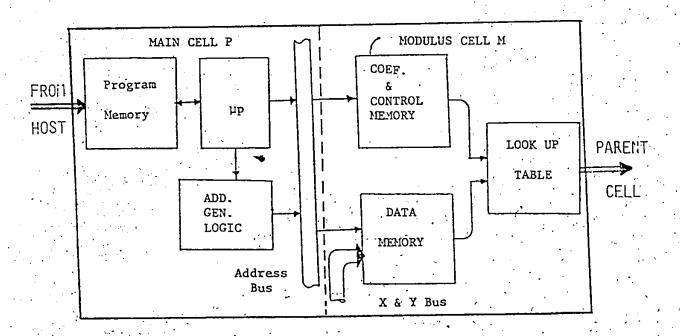

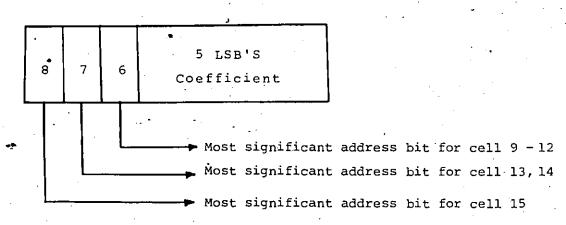

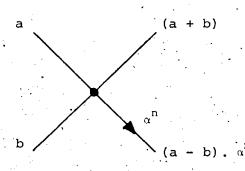

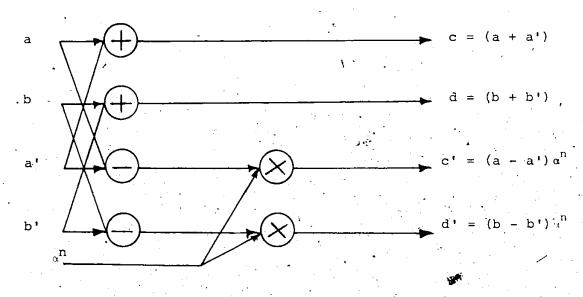

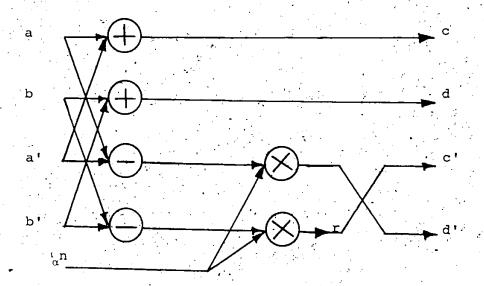

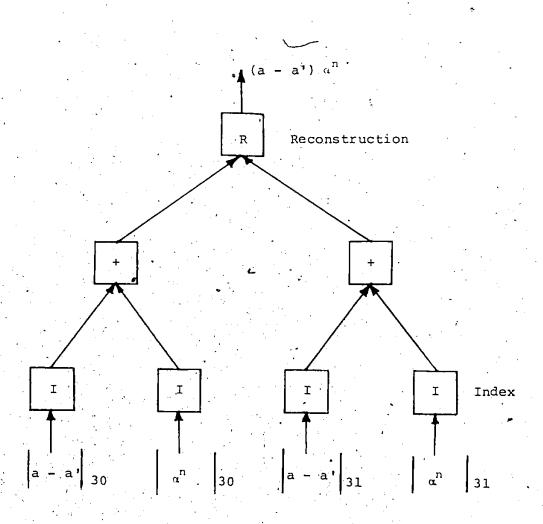

The processor utilizes RNS for the arithmetic operations which can be performed in parallel for each modulus. By restricting the size of each modulus, all possible arithmetic operations can be precomputed and stored in the look up tables. The structure of the DFSP discussed in this thesis is restricted to four five bit moduli but the number of moduli can be increased. Identical tree structure are required for each modulus as discussed in the previous chapter. The tree structure is appropriately utilized by the RNS because of the parallel nature of the arithmetic. This chapter demon-