# University of Windsor Scholarship at UWindsor

**Electronic Theses and Dissertations**

1995

# Synthesis of multilevel pass transistor logic networks.

Arunita. Jaekel *University of Windsor*

Follow this and additional works at: http://scholar.uwindsor.ca/etd

#### Recommended Citation

Jaekel, Arunita., "Synthesis of multilevel pass transistor logic networks." (1995). Electronic Theses and Dissertations. Paper 3699.

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Onlano K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontano) K1A 0N4

FOR DRIVE SOME OF STATE

Charles - Note reference

#### NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

#### **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

# Synthesis of Multilevel Pass Transistor Logic Networks

by **Arunita Jaekel**

# A Dissertation Submitted to the Faculty of Graduate Studies through the Department of Electrical Engineering in Partial Fulfilment of the Requirements for the Degree of Doctor of Philosophy at the University of Windsor

Windsor, Ontario May, 1995

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your her. Notice reference

Charles Automalaina

The author has granted an irrevocable non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence et non exclusive irrévocable la Bibliothèque permettant à nationale du Canada reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette disposition thèse des la personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-612-10938-0

Arunita Jackel 1995

© All Rights Reserved

#### **ABSTRACT**

Traditional design of logic circuits involves implementing a function in terms of standard logic gates. However, this type of design does not fully exploit the unique switching properties of MOSFETs, which can lead to more efficient realizations.

Over the past decade there has been considerable interest in Pass Transistor Logic (PTL) circuits. PTL circuits implement a logic function as a network of NMOS transistors. They show enhanced performance over conventional logic in terms of both speed and area optimization as well as reduced power dissipation, particularly for certain classes of circuits.

Existing synthesis techniques for PTL are limited to two-level synthesis, similar to that used for conventional logic. In conventional logic multilevel logic implementations have been shown to provide significant improvements over two-level representations. So it is of considerable interest to develop formal multilevel design methodologies for PTL in order to exploit potential efficiencies in that circuit family. Such formal design methodologies are also necessary to avoid incorrect implementations which can result from ad hoc design of PTL networks.

This thesis deals with the development of methodologies for the systematic design of multi-level PTL networks. In this thesis, we have investigated two approaches to multi-level logic synthesis techniques for PTL networks based on the concepts of (i) factorization and (ii) decision diagrams. Both approaches have shown significant savings over known synthesis techniques for PTL networks.

To my husband, Martin

# **ACKNOWLEDGEMENTS**

I would like to acknowledge the guidance and support provided by my supervisors Dr. S. Bandyopadhyay and Dr. G.A. Jullien. I am grateful for the time and effort they have contributed in guiding me through this work. This thesis could not have been completed without their patient and active supervision. I would also like to thank my committee members Dr. M. Ahmadi, Dr. W.C. Miller and Dr. N. Wigley for their comments and suggestions regarding the thesis. Special thanks must go to Ms. Barbara Szydłowska and Mr. Sandeep Kamat for their invaluable help in implementing the various algorithms in this thesis and to John De Ryckere and Todd Bealor for their help with Cadence and FrameMaker. I would like to express my sincere thanks to our system administrators Mr. Walid Mnaymneh and Mr. Stephen Karamatos for all their help throughout the course of this work and the members of the Graduate Lab for a friendly and enlightening working atmosphere.

I would also like to thank my parents, Tushar and Manju Sarkar, and my sister Mitun for their constant support and words of encouragement. Finally, I must thank my husband Martin, for all his help and support. Without his patience and understanding, I could not have finished this thesis.

# TABLE OF CONTENTS

| Chapter 1 Intr             | roduction                                                                                                                                                                                                                                                                         | 1                                |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 1.1                        | Introduction                                                                                                                                                                                                                                                                      | 1                                |

| 1.2                        | Motivation                                                                                                                                                                                                                                                                        | 2                                |

| 1.3                        | Solution Outline                                                                                                                                                                                                                                                                  | 2                                |

| 1.4                        | Thesis Organization.                                                                                                                                                                                                                                                              | 3                                |

| Chapter 2 Rev              | view of PTL and Multilevel Logic Design                                                                                                                                                                                                                                           | 5                                |

| 2.1                        | Introduction                                                                                                                                                                                                                                                                      | 5                                |

| 2.2                        | Pass Transistor Logic Design:                                                                                                                                                                                                                                                     | 6                                |

|                            | 2.2.1 What is a PTL Network                                                                                                                                                                                                                                                       |                                  |

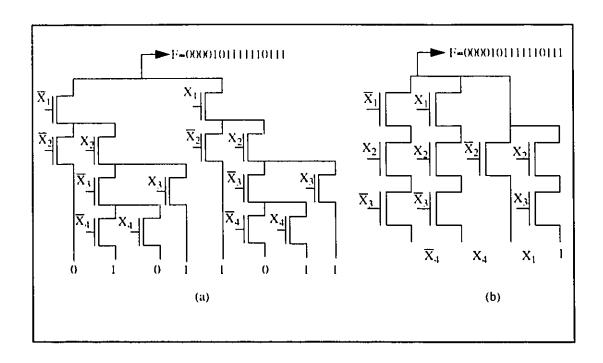

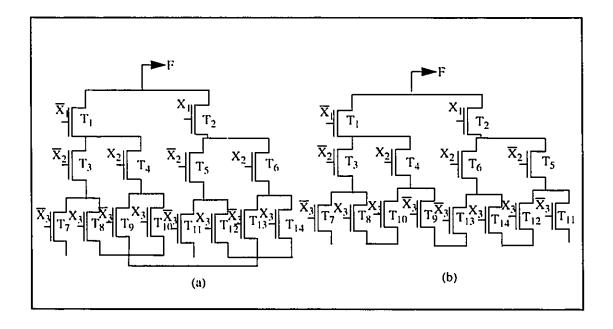

|                            | 2.2.2 PTL synthesis Techniques:                                                                                                                                                                                                                                                   | 7                                |

|                            | 2.2.3 Heuristic for Finding Minimal Cover                                                                                                                                                                                                                                         | 10                               |

| 2.3                        | Multilevel Logic Synthesis                                                                                                                                                                                                                                                        |                                  |

|                            | 2.3.1 What is Multilevel Logic Synthesis                                                                                                                                                                                                                                          |                                  |

|                            | 2.3.2 Basic Concepts of Factorization                                                                                                                                                                                                                                             |                                  |

|                            | 2.3.3 Factorization Algorithm                                                                                                                                                                                                                                                     |                                  |

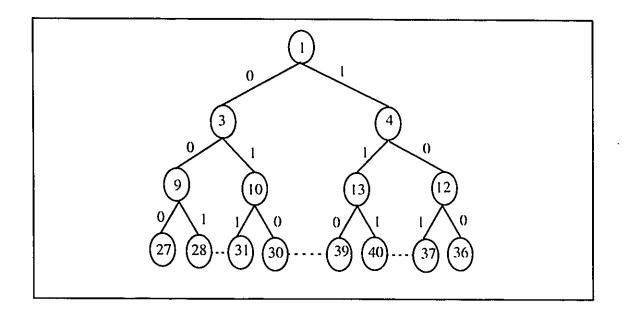

| 2.4                        | Binary Decision Diagrams                                                                                                                                                                                                                                                          |                                  |

|                            | 2.4.1 What is a BDD                                                                                                                                                                                                                                                               |                                  |

|                            | 2.4.2 Important Definitions and Properties of OBDDs                                                                                                                                                                                                                               |                                  |

| 25                         | Conclusions                                                                                                                                                                                                                                                                       |                                  |

| 2)                         | Conclusions                                                                                                                                                                                                                                                                       | 41                               |

| Chapter 3 Fac              | ctorization for Pass Transistor Logic                                                                                                                                                                                                                                             | 22                               |

| 3.1                        | Introduction                                                                                                                                                                                                                                                                      | 22                               |

| 3.2                        | Why Factorization Algorithm Must be Modified for PTL                                                                                                                                                                                                                              | 23                               |

|                            | 3.2.1 Restrictions on Ordering of Input Variables                                                                                                                                                                                                                                 |                                  |

|                            | 3.2.2 Need for a More Realistic Cost Estimator                                                                                                                                                                                                                                    | 26                               |

|                            | 3.2.3 Two-level Minimal Sum-of-Products Covers Do Not                                                                                                                                                                                                                             |                                  |

|                            | Lead to Significant Savings                                                                                                                                                                                                                                                       |                                  |

| 2.2                        |                                                                                                                                                                                                                                                                                   |                                  |

| 3.3                        | Outline of Our Algorithm                                                                                                                                                                                                                                                          |                                  |

|                            | 3.3.1 Some Definitions                                                                                                                                                                                                                                                            |                                  |

|                            |                                                                                                                                                                                                                                                                                   |                                  |

|                            |                                                                                                                                                                                                                                                                                   |                                  |

|                            | 3.3.3 Justification of the Heuristic                                                                                                                                                                                                                                              | 33                               |

| 3.4                        | 3.3.3 Justification of the Heuristic                                                                                                                                                                                                                                              | 33<br>35                         |

| 3.4                        | 3.3.3 Justification of the Heuristic                                                                                                                                                                                                                                              | 33<br>35<br>36                   |

| 3.4<br>3.5                 | 3.3.3 Justification of the Heuristic                                                                                                                                                                                                                                              | 33<br>35<br>36                   |

| 3.5                        | 3.3.3 Justification of the Heuristic                                                                                                                                                                                                                                              | 33<br>35<br>36                   |

| 3.5                        | 3.3.3 Justification of the Heuristic                                                                                                                                                                                                                                              | 33<br>35<br>36<br>38             |

| 3.5<br>Chapter 4 PT        | 3.3.3 Justification of the Heuristic                                                                                                                                                                                                                                              | 33<br>35<br>36<br>38<br>40       |

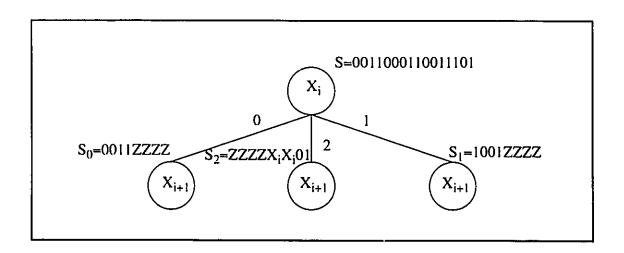

| 3.5<br>Chapter 4 PT<br>4.1 | 3.3.3 Justification of the Heuristic 3.3.4 Complexity of the Heuristic Example of Multilevel PTL Network Design Conclusions  CL Synthesis and 123-Decision Diagrams Introduction 123-Decision Diagrams: A Graph Model for PTL 4.2.1 Can We Use Decision Diagrams for PTL Networks | 33<br>35<br>36<br>38<br>40<br>40 |

| 3.5<br>Chapter 4 PT<br>4.1 | 3.3.3 Justification of the Heuristic 3.3.4 Complexity of the Heuristic Example of Multilevel PTL Network Design Conclusions  CL Synthesis and 123-Decision Diagrams Introduction 123-Decision Diagrams: A Graph Model for PTL                                                     | 33<br>35<br>36<br>40<br>40<br>40 |

| 4.3          | Useful Properties and Definitions for 123-DDs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 45  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

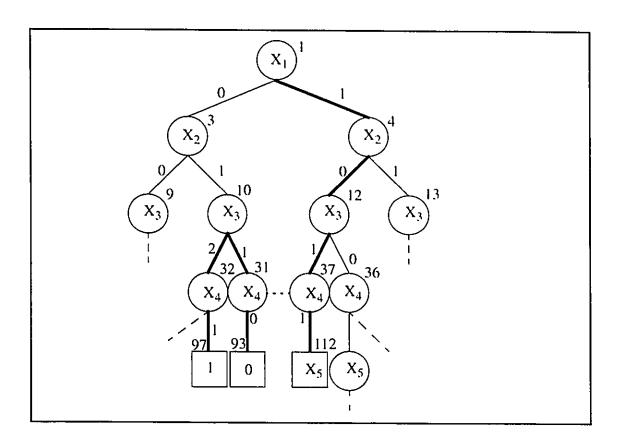

| 4,4          | The List Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 51  |

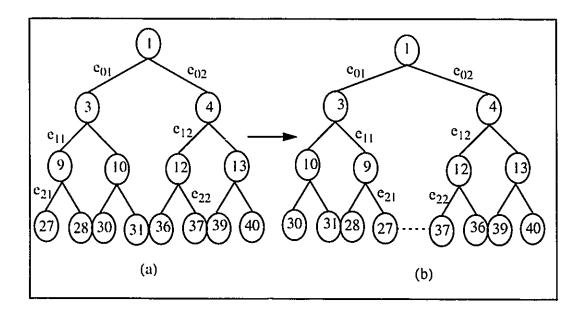

| 4.5          | The Transformation rules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

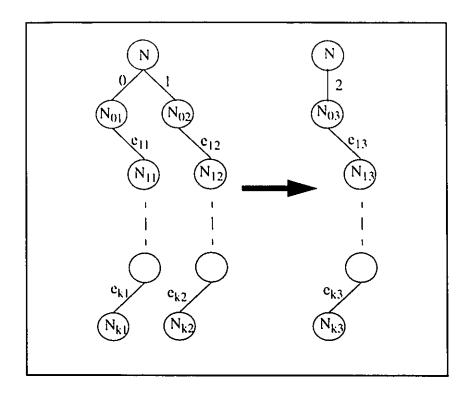

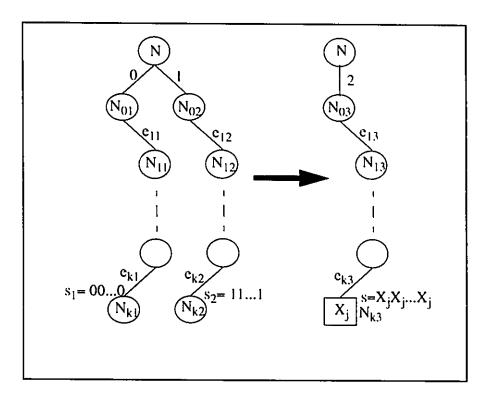

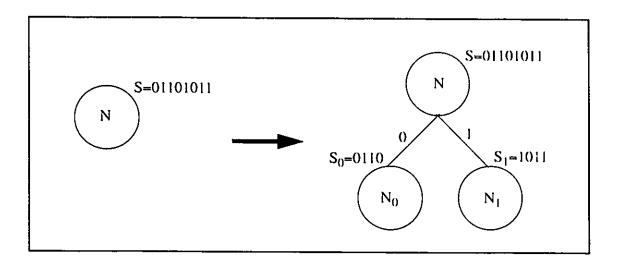

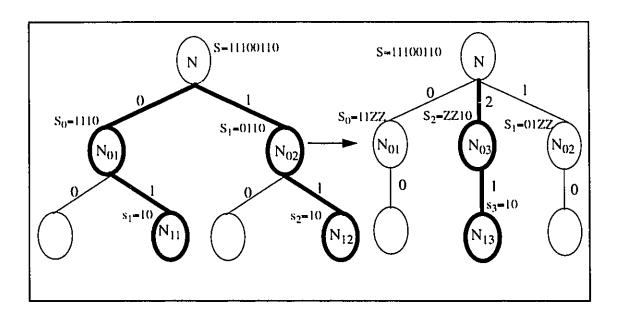

|              | 4.5.1 Generating Children of a Node                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 55  |

|              | 4.5.2 Combining Two Paths 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

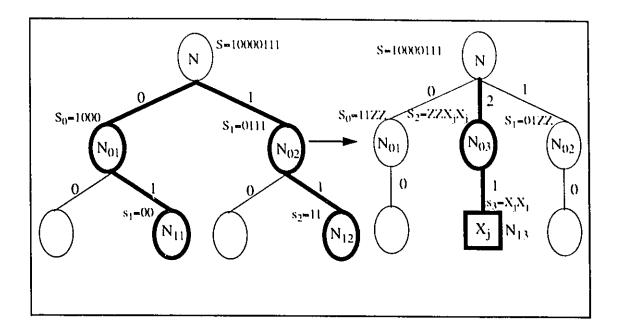

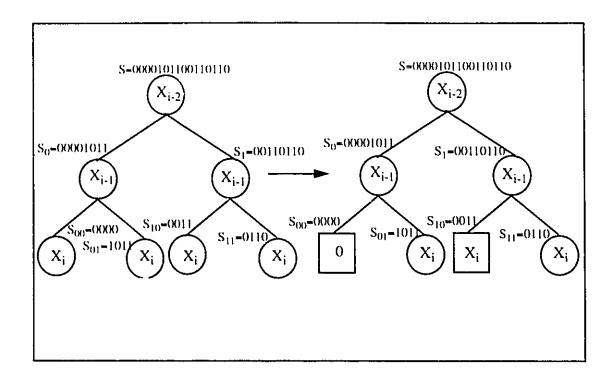

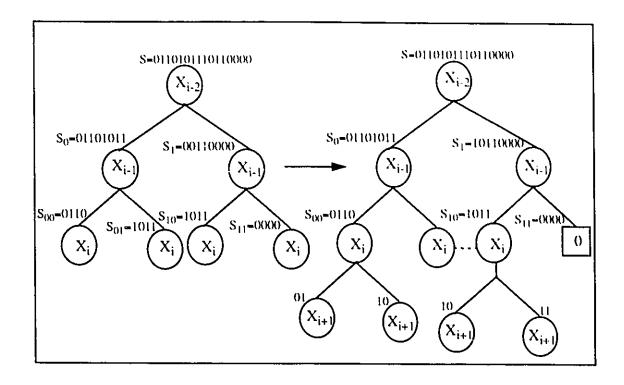

|              | 4.5.3 Combining Two Paths II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

|              | 4.5.4 Converting Nonterminal Nodes to Terminal Nodes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

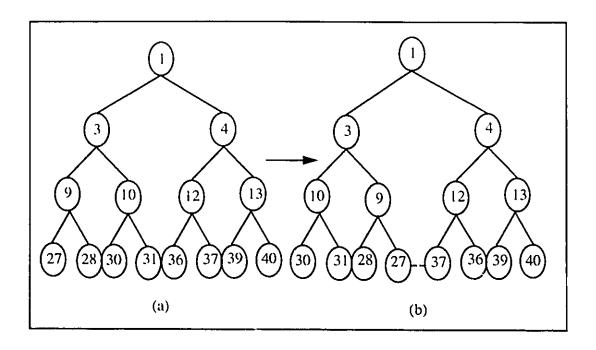

|              | 4.5.5 Merging of Subgraphs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 58  |

|              | 4.5.6 Layout Factors Affecting Transformations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|              | 4.5.6.1 Layout Considerations for Transformation 4.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 59  |

|              | 4.5.6.2 Layout Considerations for Transformations 4.2 and 4.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

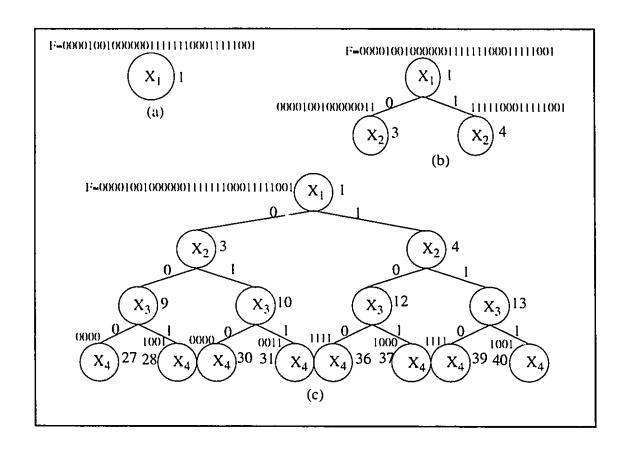

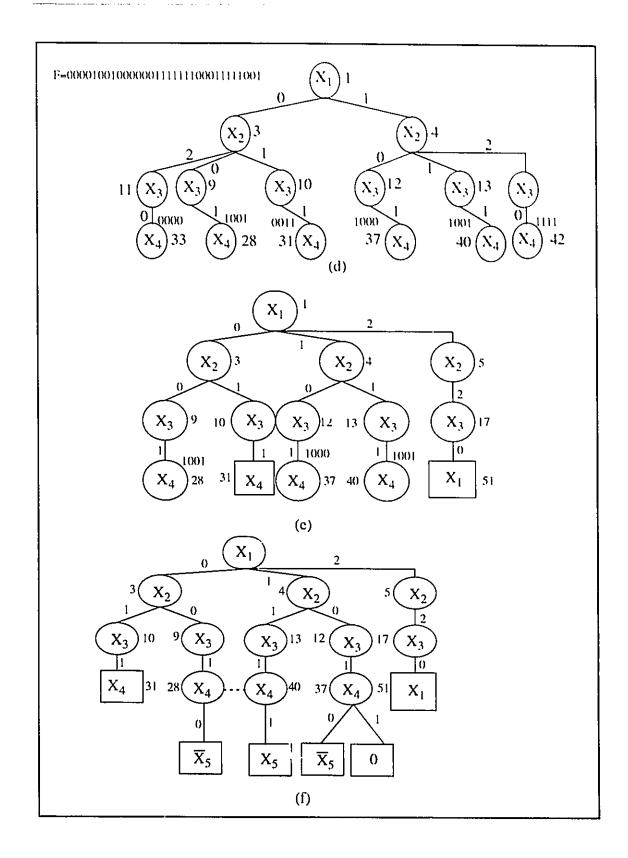

| 4,6          | Synthesis Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|              | 4.6.1 Synthesis procedure in a nutshell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|              | 4.6.2 Complexity of the Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

|              | the state of the s |     |

| 4.7          | Interesting properties of 123-DD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|              | 4.7.1 Sneak Paths in MOS Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

|              | 4.7.1.1 Sneak Paths in 123-DDs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| 4.0          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

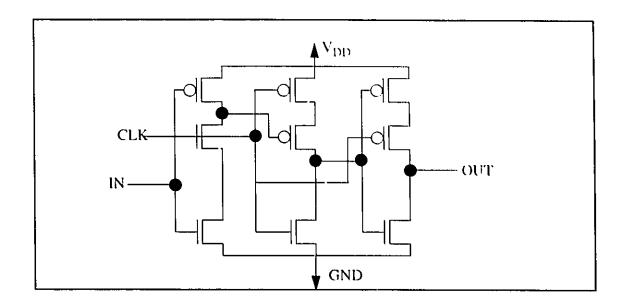

| 4.8          | Example of PTL Synthesis with 123-DD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| 4.9          | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 74  |

| Chapter 5 Ex | ranimental Decultu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 75  |

|              | sperimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| 5.1          | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

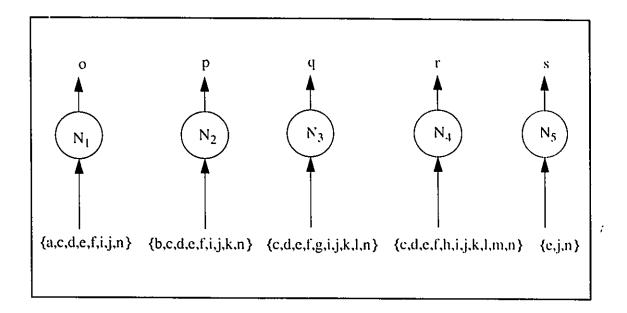

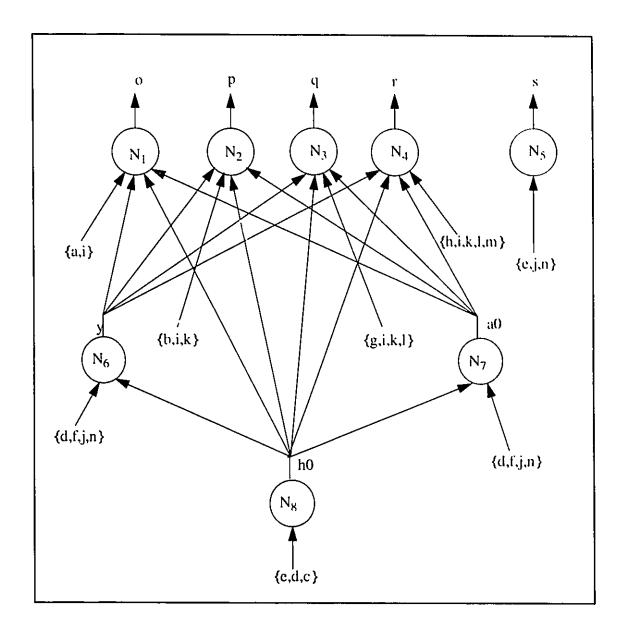

| 5.2          | Boolean Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

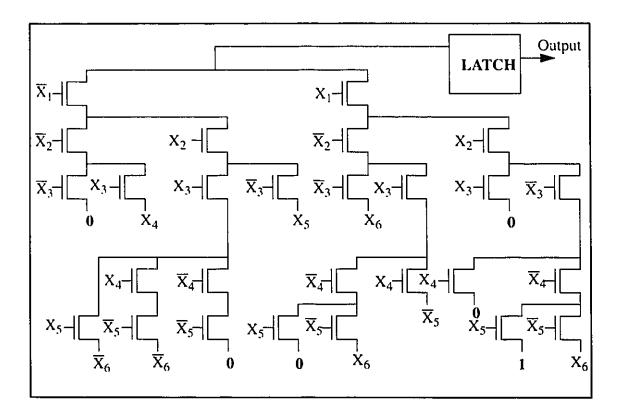

| 5.3          | Factorization Approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

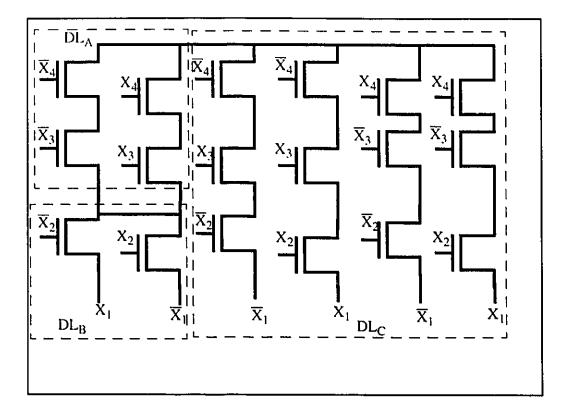

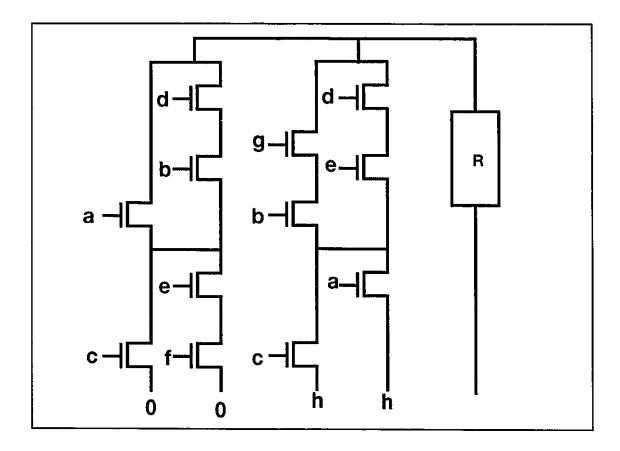

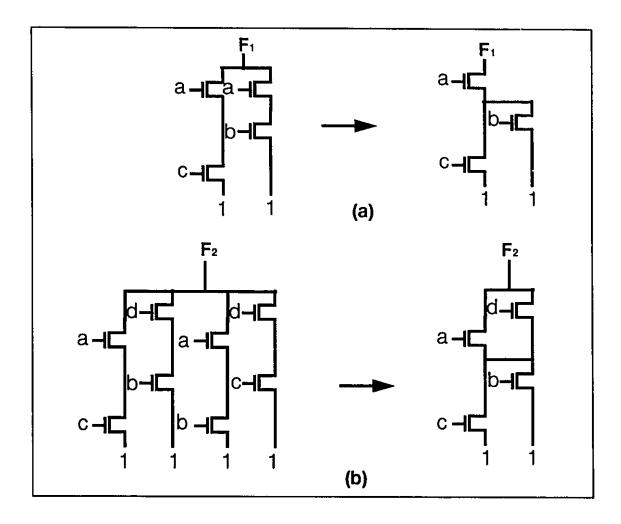

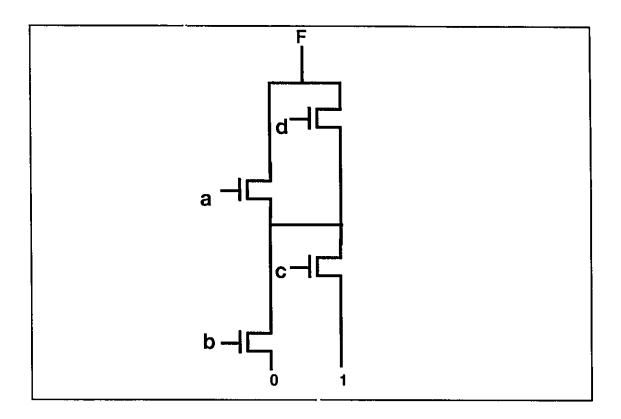

|              | 5.3.1 Area Requirements for Benchmark Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |