# University of Windsor Scholarship at UWindsor

**Electronic Theses and Dissertations**

1995

# FPGA implementation of adaptive interference canceler for periodic signal.

Tony Wai Sing. Yuen University of Windsor

Follow this and additional works at: http://scholar.uwindsor.ca/etd

#### Recommended Citation

Yuen, Tony Wai Sing., "FPGA implementation of adaptive interference canceler for periodic signal." (1995). *Electronic Theses and Dissertations*. Paper 2152.

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your file Votre référence

Our Na Notre référence

#### NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

#### **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

## FPGA Implementation of Adaptive Interference Canceler for Periodic Signal

by

Tony Wai Sing Yuen

A Thesis

Submitted to the Faculty of Graduate Studies through the

Department of Electrical Engineering in Partial Fulfillment

of the Requirement for the Degree of

Master of Applied Science

at the

University of Windsor

Windsor, Ontario

December, 1995

© 1995 Tony Wai Sing Yuen

Acquisitions and Bibliographic Services Branch

395 Weltington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your life Votre référence

Our file Notre référence

The author has granted an irrevocable non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence et non exclusive irrévocable la Bibliothèque permettant à du Canada nationale reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette disposition des thèse la personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-612-11039-7

Name TONY YEEN WAI SING YUEN

Dissertation Abstracts International and Masters Abstracts International are arranged by broad, general subject categories. Please select the one subject which most nearly describes the content of your dissertation or thesis. Enter the corresponding four-digit code in the spaces provided.

Electronics and Electrical

SUBJECT CODE

#### **Subject Categories**

#### THE HUMANITIES AND SOCIAL SCIENCES

| ***************************************           |        |

|---------------------------------------------------|--------|

| COMMUNICATIONS AND THE                            | A DTC  |

| A Literary                                        | ヘアクロ   |

| Architecture                                      | 0727   |

| Art History                                       | 03//   |

| Gnema                                             |        |

| Dance                                             | 03/6   |

| Fine Arts                                         | 035/   |

| Fine Arts                                         | 0723   |

|                                                   |        |

| Library Science                                   | 0399   |

| Library Science                                   | 0708   |

| Anisto                                            | ua i a |

| Speech Communication                              | 0459   |

| Speech Communication                              | 0465   |

|                                                   |        |

| EDUCATION                                         |        |

|                                                   | 0515   |

| Administration                                    | 0514   |

| Adult and Continuing                              | 0514   |

| Agricultural                                      | 0517   |

| AA                                                | 0273   |

| Administration                                    | 0282   |

| Business                                          | 0486   |

| Business<br>Community College                     | 0274   |

| Curriculum and Instruction                        | ^7727  |

|                                                   |        |

| Edity Childhood                                   |        |

| Elementary                                        | 032    |

| ringince                                          | UZ/    |

| Guidance and Counseling                           | 0217   |

| Elementary Finance Guidance and Counseling Health | 000    |

| Higher                                            | U/A:   |

| Himoly of """                                     | 0321   |

| Home Economics                                    | 02/6   |

| industrial                                        | 0521   |

| Language and Literature                           | 02/5   |

| History of Home Economics                         | 0280   |

| Music<br>Philosophy of                            | 0522   |

| Philosophy of                                     | 0998   |

| Physical                                          | 0523   |

| •                                                 |        |

|                                                   |        |

| Psychology                                                                           | .vozo                                                                  |

|--------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| Redgious                                                                             | .0535                                                                  |

| Religious                                                                            | .0527                                                                  |

| Sciences                                                                             | .0/14                                                                  |

| Secondary                                                                            | .0533                                                                  |

| Social Sciences                                                                      | .0534                                                                  |

| Social Sciences<br>Socialogy of                                                      | 0340                                                                   |

| Special                                                                              | .0529                                                                  |

| Special Teacher Training                                                             | .0530                                                                  |

| Technology                                                                           | .0710                                                                  |

| Technology                                                                           | 0288                                                                   |

| Vocational                                                                           | 0747                                                                   |

| AOCTIONAL ************************************                                       | . 4, 4,                                                                |

| LANGUAGE, LITERATURE AND                                                             |                                                                        |

|                                                                                      |                                                                        |

| LINGUISTICS                                                                          |                                                                        |

| Language                                                                             |                                                                        |

| General                                                                              | .0679                                                                  |

| Ancien!                                                                              | .0287                                                                  |

| Linguishes                                                                           | .0270                                                                  |

| Modern                                                                               | .0291                                                                  |

| Literature                                                                           |                                                                        |

| General                                                                              | .0401                                                                  |

|                                                                                      | 0.004                                                                  |

|                                                                                      | 0205                                                                   |

| Comparative                                                                          | , 42/-                                                                 |

| Comparative                                                                          | .0297                                                                  |

| Comparative                                                                          | 0297<br>0298                                                           |

| Modern                                                                               | UZ70                                                                   |

| African                                                                              | .0276                                                                  |

| African                                                                              | 0276                                                                   |

| African                                                                              | 0276                                                                   |

| African                                                                              | 0276                                                                   |

| Modern African American Asian Crandian (English) Conadian (French)                   | 0316<br>0591<br>0305<br>0352                                           |

| Modern African American Asian Consodian (English) Consodian (French)                 | 0316<br>0591<br>0305<br>0352<br>0355                                   |

| Modern African American Asian Cresodian (English) Canadian (French) English Germanic | 0316<br>0591<br>0305<br>0352<br>0355<br>0353                           |

| Modern African American Asian Conadian (English) Canadian (French) English Germanic  | 0316<br>0591<br>0305<br>0352<br>0355<br>0353                           |

| Modern African American Asian Conadian (English) Canadian (French) English Germanic  | 0316<br>0591<br>0305<br>0352<br>0355<br>0353                           |

| Modern African American Asian Cresodian (English) Canadian (French) English Germanic | .0276<br>.0316<br>0591<br>0352<br>0355<br>0353<br>0311<br>0312<br>0313 |

| 12:                                          |

|----------------------------------------------|

|                                              |

| 318                                          |

| 32                                           |

| )31:<br>)32:<br>)31:<br>)32:<br>)32:<br>)46: |

| 32                                           |

| 32                                           |

| 146                                          |

|                                              |

|                                              |

| 32                                           |

|                                              |

| 32                                           |

| 32                                           |

| )3 <u>2</u>                                  |

| )32<br>)32                                   |

| יונכ                                         |

| 121                                          |

| "                                            |

| 4                                            |

| 33                                           |

| )33<br>)38                                   |

|                                              |

| 350                                          |

| 350                                          |

| 050<br>050<br>050                            |

| 350                                          |

| JSU                                          |

| JOL                                          |

| 051                                          |

| <b>035</b>                                   |

| 036                                          |

| 036<br>035                                   |

|                                              |

| 057                                          |

|                                              |

|                                              |

|                                              |

| Ancient                                                               | 057   | 9  |

|-----------------------------------------------------------------------|-------|----|

| Medievol                                                              | .058  | 1  |

| Modern                                                                | 058   | 2  |

|                                                                       |       |    |

| AL:                                                                   | V33   | ĭ  |

| Arrican                                                               | 737   | ż  |

| Asia, Australia ana Oceania                                           | 033   | 5  |

| Zangalan                                                              | 222   | ?  |

| ruropean                                                              | , UJJ | ş  |

| African Asia, Australia and Oceania Canedian European Latin American  | .033  | ō  |

|                                                                       |       |    |

| United States                                                         | .033  | 7  |

| History of Science                                                    | . 058 | ے  |

| Lay                                                                   | .039  | 8  |

| Political Science                                                     |       |    |

| General                                                               | 067   | 5  |

| General<br>International Law and                                      | ,     | _  |

| Relations                                                             | 061   | 6  |

| Public Administration                                                 | 1An   | ž  |

| Describes                                                             | ÓŘÍ   | 'n |

| Recreation<br>Social Work                                             | 045   | 7  |

| SOCIAL VYORK                                                          |       | -  |

| Sociology                                                             | ^/1   | ,  |

| General                                                               | . VOZ | 9  |

| Criminology and Penology                                              | .062  | ′  |

| Demography                                                            | .093  | ğ  |

| General Criminology and Penology Demography Ethnic and Racial Stydies | .C63  | Ţ  |

|                                                                       |       |    |

| Studies                                                               | .062  | 8  |

| Industrial and Labor                                                  |       |    |

| Relations                                                             | .062  | ς  |

| Relations<br>Public and Social Wellare                                | .063  | 0  |

| Social Structure and                                                  |       | •  |

| Development                                                           | 070   | 'n |

| Development                                                           | 024   | ĭ  |

| TUMOLA dud tymuogs """"                                               | . 034 | č  |

| ransportation                                                         | .0/0  | ď  |

| nibar and kedional Lapping                                            | UYY   | ž  |

| Women's Studies                                                       | .045  | ٤  |

|                                                                       |       |    |

#### THE SCIENCES AND ENGINEERING

| BIOLOGICAL SCIENCES                            |           |

|------------------------------------------------|-----------|

| Amicultura                                     |           |

| Geren                                          | .0473     |

| Admoomy                                        | 0285      |

| Agronomy                                       | . • • • • |

| Nutrition                                      | 0475      |

| Nutrition                                      | 0.476     |

| Food Science and                               |           |

| Technology                                     | 0350      |

| Enante ZWildlife                               | 0.478     |

| Technology Forestry and Wildlife Plant Culture | 0470      |

| Plant Pathology                                | 0490      |

| Diam Disciples                                 | 0817      |

| Plant Physiology                               | 0777      |

| Range Management                               | .0///     |

| Nood lechnology                                | .0/40     |

| Biology                                        | 0004      |

| General                                        | 2000      |

| Analomy                                        | .028/     |

| Bioslatistics                                  | .0308     |

| Bolony                                         | .0309     |

|                                                | .0379     |

| Ecology                                        | .0329     |

| Enfomology                                     | . 0353    |

| Genetics                                       | 0369      |

| Limnology                                      | .0793     |

| Microbiology                                   | .0410     |

| Molecular                                      | 030/      |

| Neuroscience                                   | 0317      |

| Oceanography<br>Physiology                     | 0416      |

| Physiology                                     | 0433      |

| KOCHONOR                                       | ,, VOZ I  |

| Veterinary Science                             | 0778      |

| Zoology                                        | 0472      |

| Binohanier                                     |           |

| General                                        | 0786      |

| Medical                                        | 0760      |

| ****                                           |           |

| EARTH SCIENCES                                 |           |

| Ringenchamistry                                | 0425      |

| Geochemistry                                   | 0996      |

|                                                |           |

| Geology Geophysics Hydrology Wineralogy Paleobotany Paleobotany                               | .0372  |

|-----------------------------------------------------------------------------------------------|--------|

| Geophysics                                                                                    | .0373  |

| Hydrology                                                                                     | 0.0300 |

| Palenhatony                                                                                   | 0345   |

| Paleoscology                                                                                  | 0426   |

| Paleontology                                                                                  | .0418  |

| Paleozoology                                                                                  | 0985   |

| Paleonology Paleozoology Palyoology Physical Geography Physical Oceanography                  | . 0427 |

| Physical Geography                                                                            | 0300   |

| rhysical Casanography                                                                         |        |

| <b>HEALTH AND ENVIRONMENTA</b>                                                                | L      |

| SCIENCES                                                                                      |        |

| Environmental Sciences                                                                        | . 0768 |

| Health Sciences                                                                               |        |

| General                                                                                       | 0566   |

| Audiology                                                                                     | .0300  |

| Chemotherapy<br>Dentistry                                                                     | 0567   |

| Education                                                                                     | 0350   |

| Hospital Management                                                                           | 0769   |

| Education Hospital Management Human Development Immunology Medicine and Surgery Manial Health | 0758   |

| Immunology                                                                                    | 0982   |

| Medicine and Surgery                                                                          | 0347   |

|                                                                                               |        |

| Nutrition                                                                                     | 0570   |

| Nutrition                                                                                     | 0380   |

| Occupational Health and                                                                       |        |

| Therapy                                                                                       | 0354   |

| Ophthalmology                                                                                 | 0381   |

| Phomosolom                                                                                    | 03/ i  |

| Phomocy                                                                                       | 0572   |

| Pharmacy<br>Physical Therapy<br>Public Health                                                 | 0382   |

| Public Health                                                                                 | 0573   |

| Radiology<br>Recreation                                                                       | 0574   |

| Recreation                                                                                    | 0575   |

|                                                                                               |        |

| Home Economics                                      | 0383 |

|-----------------------------------------------------|------|

| PHYSICAL SCIENCES                                   |      |

| Pure Sciences                                       |      |

| Chemistry                                           |      |

| General<br>Agricultural                             | 0485 |

| Agricultural                                        | 0749 |

| Analytical                                          | 0486 |

| Biochemistry                                        | U46/ |

| Nuclear                                             | 0738 |

| Nuclear<br>Organic<br>Pharmocutical                 | 0490 |

| Pharmoceutical                                      | 0491 |

| rnvucal                                             |      |

| Polymer                                             | 0495 |

| Radiation                                           | 0754 |

| Mathematics                                         | 0405 |

| Physics<br>General                                  | 0404 |

| Acoustics                                           | 000  |

|                                                     |      |

| Astronomy and Astrophysics Almospheric Science      | 0606 |

| Almospheric Science                                 | 0608 |

| Alomic                                              | 0748 |

| Alomic and Electricity<br>Elementary Particles and  | 060/ |

| Link Engage                                         | 0700 |

| High Energy<br>Fluid and Plasma                     | 0759 |

| Molecular                                           | 0609 |

| Nuclear                                             | 0610 |

| Optics                                              | 0757 |

| Radiation                                           | 0756 |

| Solid Stole                                         |      |

| Statistics                                          | 046  |

| Applied Sciences                                    |      |

| Applied Mechanics                                   | 0344 |

| Applied Sciences Applied Mechanics Computer Science | 0984 |

|                                                     |      |

Speech Pathology ......0460

| Engineering General Aerospoce Agricultural Automotive Biomedical Chemical Civil Electronics and Electrical Heat and Thermodynamics Hydraulic Industrial Marine Materials Science Mechanical Metallurgy Mining Nuclear Packoging | 0539<br>0540<br>0541<br>0542<br>0543<br>0544<br>0545<br>0545<br>0547<br>0548<br>0548 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Nuclear Packaging Petroleum Sanitary and Municipal System Science Geolechnology Operations Research Plastics Technology Textile Technology                                                                                      | 0765<br>0554<br>0790<br>0428<br>0796<br>0795                                         |

| PSYCHOLOGY General Behavioral Clinical Developmental Experimental Industrial Personality Physiological Psychobiology Rsychometrics Social                                                                                       | 0623<br>0624<br>0625<br>0989<br>0349                                                 |

## **Abstract**

This thesis describes the design, implementation and testing of an adaptive digital interference canceler for periodic signals. This canceler uses the least mean-square (LMS) adaptive filtering technique to eliminate interference from an input signal. An advantage of the adaptive interference cancelling approach is that it requires no prior the interference knowledge of both the signal and characteristics. A digital design approach is used in this thesis because of its reliability and accuracy. The canceler is implemented using a Xilinx FPGA chip. A prototype design demonstrated that the canceler was able to reduce the input interference power by about 40%.

To my parents

&

my love

Agnes

# Acknowledgements

I wish to express my gratitude to my thesis supervisor and advisor, Dr. H. K. Kwan, who suggested to me the present project and introduced me to the subjects of adaptive signal processing and FPGA technology. Dr. Kwan has also provided me with invaluable technical advice, encouragement, and an enriching research environment throughout the course of this thesis.

I would like to thank the other two members of my thesis committee, Prof. P. H. Alexander for serving as my Department Reader, and Dr. M. Wang for serving as my Outside Department Reader. Their comments are gratefully acknowledged. In particular, I also like to thank Prof. Alexander for the advice in the thesis presentation.

I would like to acknowledge Mr. J. Hochreiter for his technical assistance and Mr. A. Johns for his help in providing me some equipment.

I would also like to acknowledge my fellow graduate students, in particularly, Andy Hung and Jacky Luk for research interactions and friendship.

I sincerely thank my family and particularly my parents for their encouragement and support. Special thanks are expressed to my friend, Agnes Chung, for her patience and understanding.

# **Table of Contents**

| Abstract   | :                                             | iii  |

|------------|-----------------------------------------------|------|

| Dedication |                                               |      |

| Acknowle   | edgements                                     | v    |

| List of    | Figures                                       | ix   |

| List of    | Tables                                        | xiii |

| Chapter    | 1 Introduction                                | 1    |

| 1.1        | Motivation                                    | 2    |

| 1.2        | Thesis Organization                           | 3    |

| Chapter    | 2 Background Theory                           | 5    |

| 2.1        | Concept of Adaptive Noise Cancellation        | 5    |

| 2.2        | Adaptive Nonrecursive Filter                  | 11   |

| 2.3        | Least-Mean-Squares Adaptive Algorithm         | 13   |

| 2.4        | ANC without an External Reference Input       | 16   |

| 2.5        | Summary                                       | 17   |

| Chapter    | 3 Introduction of FPGA Technology             | 18   |

| 3.1        | Evolution of Programmable Devices             | 18   |

| 3.2        | Structure of FPGA                             | 21   |

| 3.3        | Programming Technologies                      | 24   |

|            | 3.3.1 Static RAM Programming Technology       | 25   |

|            | 3.3.2 Anti-fuse Programming Technology        | 26   |

|            | 3.3.3 EPROM and EEPROM Programming Technology | 29   |

| 3.4        | Application of FPGA                           | 32   |

| 3.5        | Xilinx's FPGA                                 | 34   |

|            | 3.5.1 Xilinx XC2000                           | 34   |

|         | 3.5.2                            | Xilinx XC3000                                  | 36 |  |  |  |

|---------|----------------------------------|------------------------------------------------|----|--|--|--|

|         | 3.5.3                            | Xilinx XC4000                                  | 37 |  |  |  |

| 3.6     | FPGA Design Flow                 |                                                |    |  |  |  |

| 3.7     | Summary                          | Summary                                        |    |  |  |  |

| Chapter | 4 Adaptive Interference Canceler |                                                |    |  |  |  |

| 4.1     | Design                           | of the AIC                                     | 42 |  |  |  |

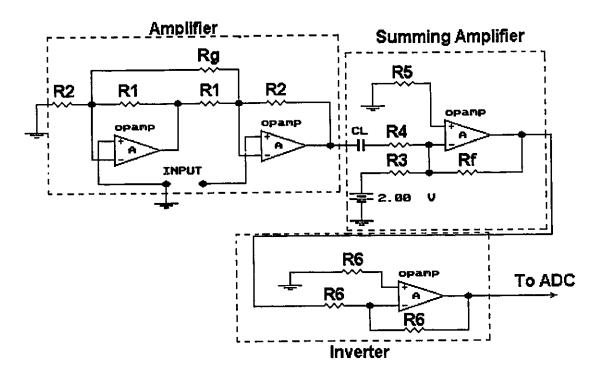

| 4.2     | Design                           | of Input & Output Circuits                     | 45 |  |  |  |

|         | 4.2.1                            | Input Amplification Circuit                    | 46 |  |  |  |

|         | 4.2.2                            | Successive-Approximation A/D Converter         | 48 |  |  |  |

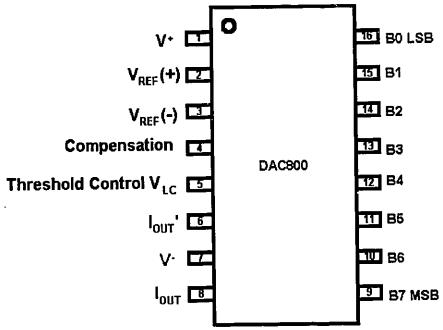

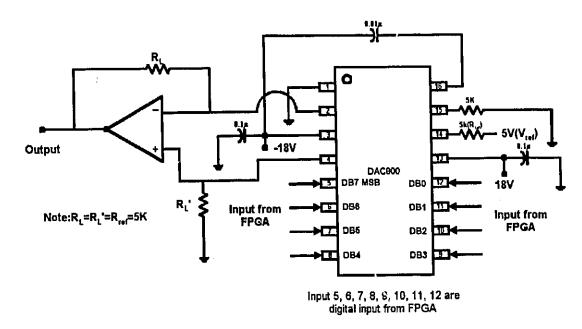

|         | 4.2.3                            | Digital-to-Analog Converter                    | 52 |  |  |  |

| 4.3     | FPGA D                           | esign of Arithmetic Units                      | 54 |  |  |  |

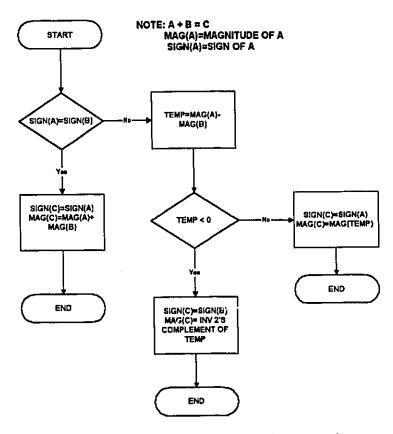

|         | 4.3.1                            | Signed binary Adder                            | 56 |  |  |  |

|         | 4.3.2                            | Binary Multiplier                              | 61 |  |  |  |

|         | 4.3.3                            | Unsigned Binary to Signed Binary<br>Converter  | 64 |  |  |  |

|         | 4.3.4                            | Signed Binary to Unsigned Binary<br>Converter  | 65 |  |  |  |

|         | 4.3.5                            | Divisor                                        | 69 |  |  |  |

|         | 4.3.6                            | 16 Bit Binary Number to 8 Bit<br>Binary Number | 70 |  |  |  |

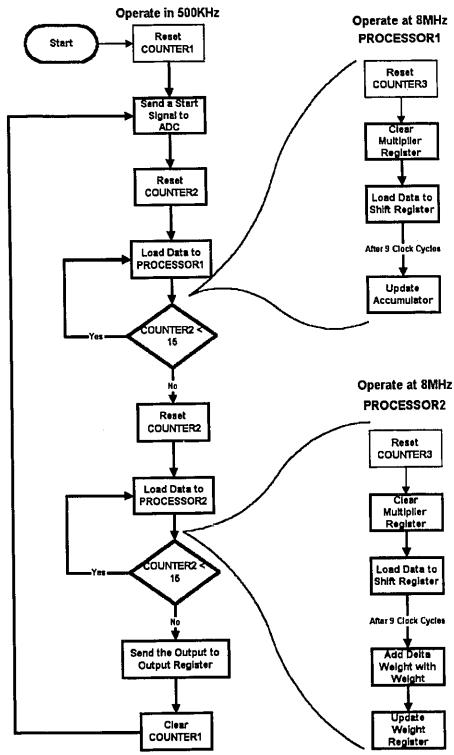

| 4.4     | Struct                           | ure of the AIC                                 | 71 |  |  |  |

|         | 4.4.1                            | Queue Structure of the AIC                     | 72 |  |  |  |

|         | 4.4.2                            | Processors                                     | 73 |  |  |  |

|         | 4.4.3                            | Control Unit                                   | 77 |  |  |  |

| 4.5     | Summar                           | У                                              | 81 |  |  |  |

| Chapter | 5 Har                            | dware Implementation & Test Results            | 82 |  |  |  |

| 5.1     | Simulations                      |                                                |    |  |  |  |

|         | 5.1.1                            | Design Verification                            | 83 |  |  |  |

|               | 5.1.2 Simulation Results         | 85  |  |  |

|---------------|----------------------------------|-----|--|--|

| 5.2           | Hardware Testing                 | 88  |  |  |

|               | 5.2.1 Test Results               | 89  |  |  |

| 5.3           | Summary                          |     |  |  |

| Chapter       | 6 Conclusion                     | 95  |  |  |

| 6.1           | Summary                          | 96  |  |  |

| 6.2           | Future Work                      | 97  |  |  |

| Referen       | ces                              | 99  |  |  |

| Appendi       | x A: Plots of Simulation Results | 102 |  |  |

| Vita Auctoris |                                  | 108 |  |  |

# **List of Figures**

| Figure | 2.1  | Model of Adaptive Noise Cancellation                                          | 6  |

|--------|------|-------------------------------------------------------------------------------|----|

| Figure | 2.2  | Multiple-input Adaptive FIR Filter with<br>Desired Response and Error Signals | 10 |

| Figure | 2.3  | Single-input Adaptive FIR Filter with<br>Desired Response and Error Signals   | 12 |

| Figure | 2.4  | A Two-dimensional Quadratic Performance<br>Surface of Adaptive Filter         | 14 |

| Figure | 2.5  | Block Diagram of ANC without External Reference Input                         | 16 |

| Figure | 3.1  | Conceptual FPGA                                                               | 21 |

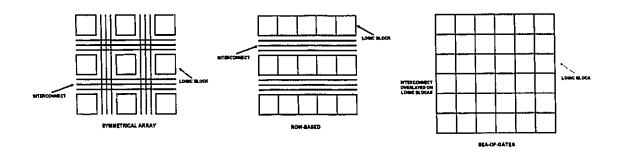

| Figure | 3.2  | Three Classes of Commercial FPGA                                              | 23 |

| Figure | 3.3  | Static RAM Programming Technology                                             | 26 |

| Figure | 3.4  | PLICE Anti-fuse Programming Technology                                        | 27 |

| Figure | 3.5  | ViaLink Anti-fuse Programming Technology                                      | 28 |

| Figure | 3.6  | EPROM Programming Technology                                                  | 30 |

| Figure | 3.7  | XC2000 CLB                                                                    | 35 |

| Figure | 3.8  | XC3000 CLB                                                                    | 36 |

| Figure | 3.9  | XC4000 CLB                                                                    | 37 |

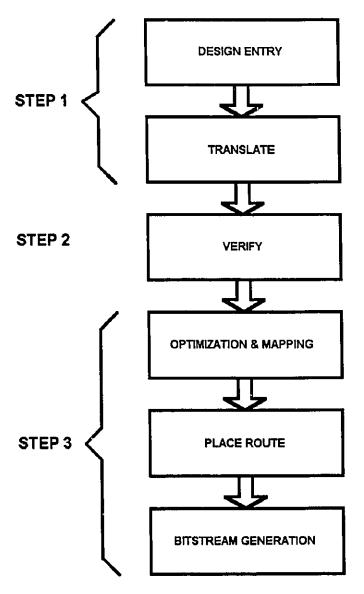

| Figure | 3.10 | Xilinx Design CAD Flow                                                        | 39 |

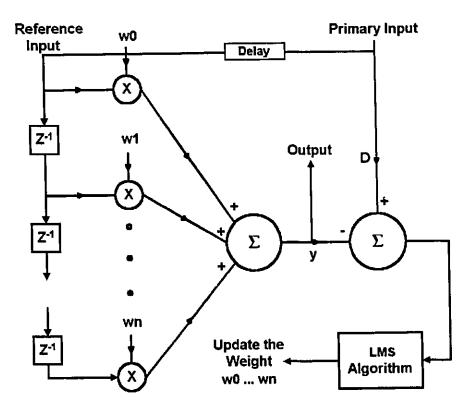

| Figure | 4.1  | Structure of Adaptive Interference<br>Canceler                                | 43 |

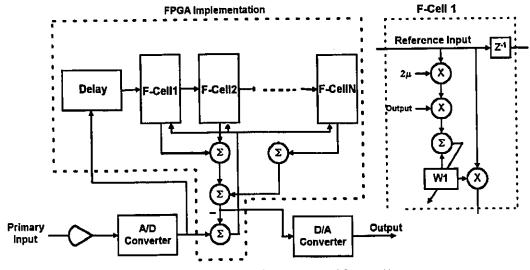

| Figure | 4.2  | Structure of the AIC                                                          | 44 |

| Figure | 4.3  | Input Circuit Layout                                                          | 46 |

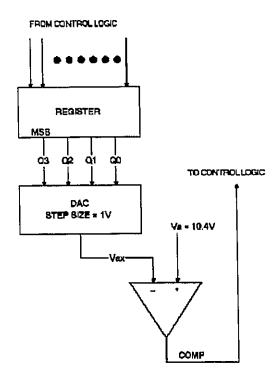

| Figure | 4.4  | Simplified Block Diagram of Successive-<br>Approximation ADC                  | 49 |

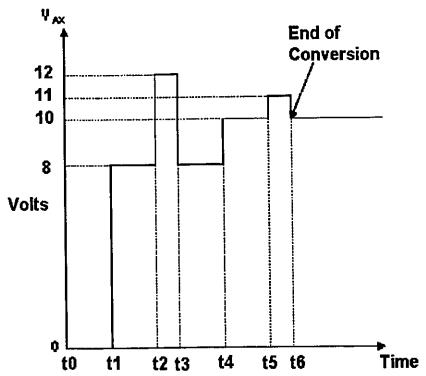

| Figure | 4.5  | Timing Graph for SAC Operation                                                | 50 |

| Figure | 16   | Pin Layout of ADC0804                                                         | 52 |

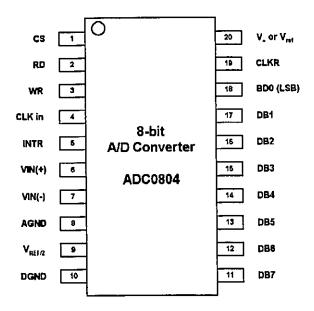

| Figure | 4.7  | Typical Connection of ADC0804                                                                                                                                    | 53 |

|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure | 4.8  | Pin Layout of ADC0804                                                                                                                                            | 54 |

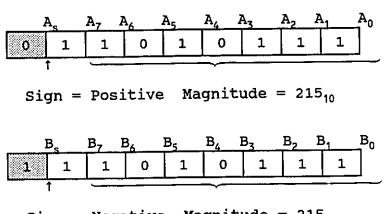

| Figure | 4.9  | Connection of Symmetrical Offset Binary Operation                                                                                                                | 55 |

| Figure | 4.10 | Representation of Signed Number in Sign-magnitude Format                                                                                                         | 56 |

| Figure | 4.11 | Flowchart of Signed Binary Adder                                                                                                                                 | 59 |

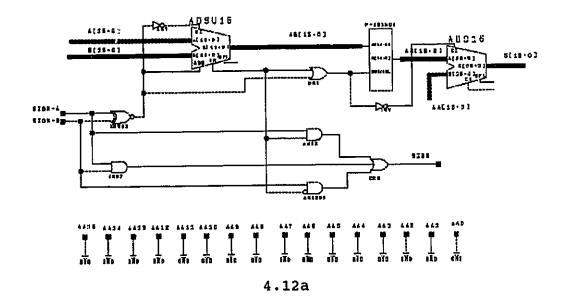

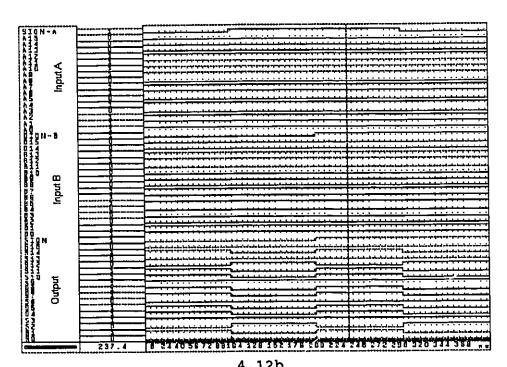

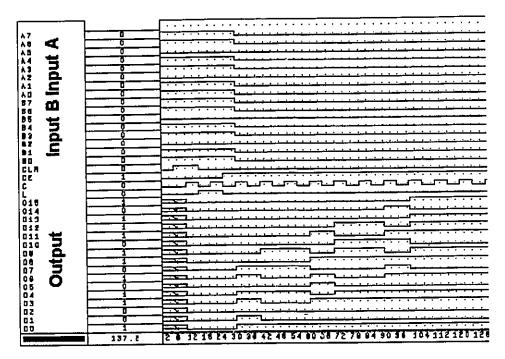

| Figure | 4.12 | <ul><li>a. Schematic of Signed Binary Adder</li><li>b. Simulation Results of Signed<br/>Binary Adder</li></ul>                                                   | 60 |

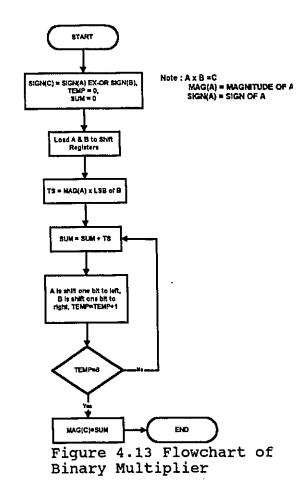

| Figure | 4.13 | Flowchart of Binary Multiplier                                                                                                                                   | 63 |

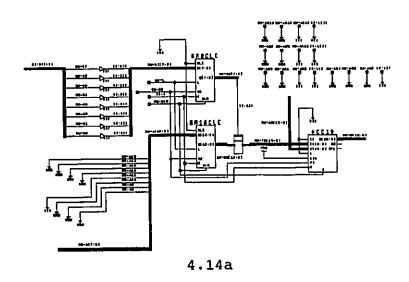

| Figure | 4.14 | <ul><li>a. Schematic of Binary Multiplier</li><li>b. Typical Signals during Multiplication</li></ul>                                                             | 63 |

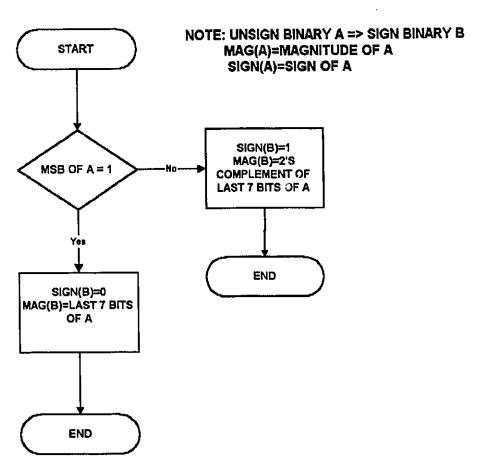

| Figure | 4.15 | Flowchart of Unsigned Binary to Signed<br>Binary Converter                                                                                                       | 66 |

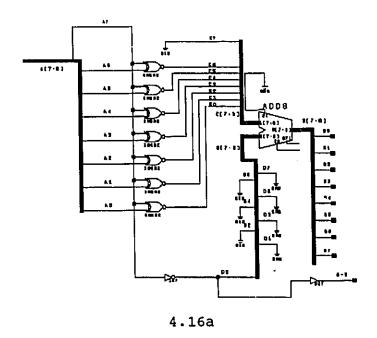

| Figure | 4.16 | <ul><li>a. Schematic of Unsigned Binary to Signed Binary Converter</li><li>b. Simulation Results of Unsigned Binary to Signed Binary Converter</li></ul>         | 67 |

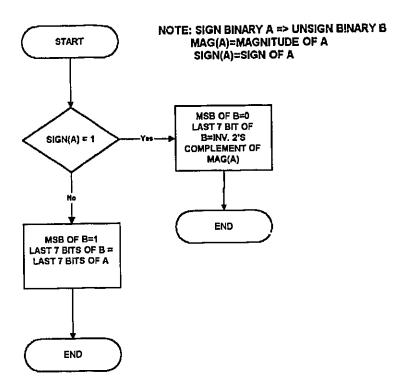

| Figure | 4.17 | Flowchart of Signed Binary to Unsigned<br>Binary Converter                                                                                                       | 68 |

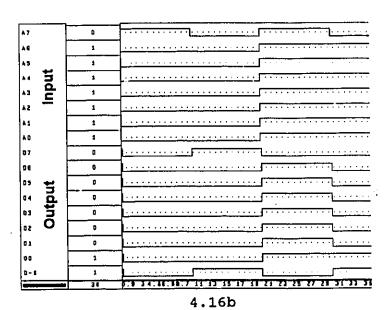

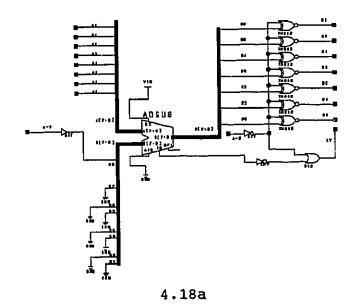

| Figure | 4.18 | <ul><li>a. Schematic of Signed Binary to Unsigned<br/>Binary Converter</li><li>b. Simulation Results of Signed Binary<br/>to Unsigned Binary Converter</li></ul> | 68 |

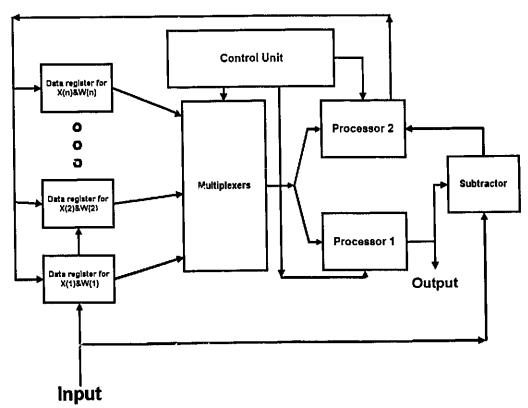

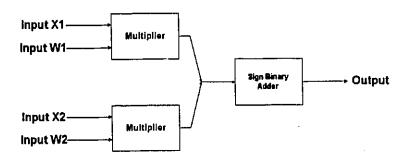

| Figure | 4.19 | Block Diagram of AIC                                                                                                                                             | 73 |

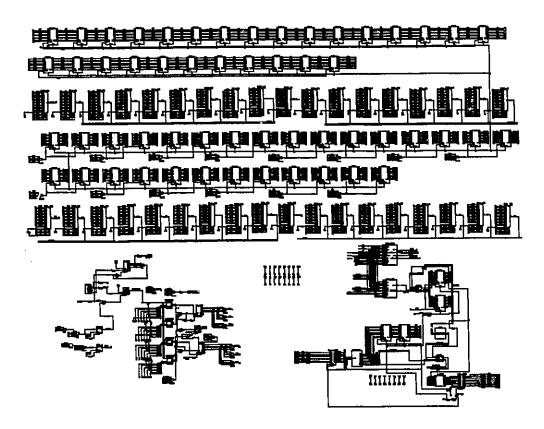

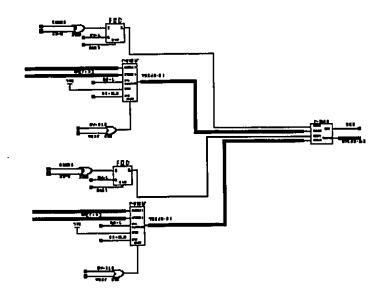

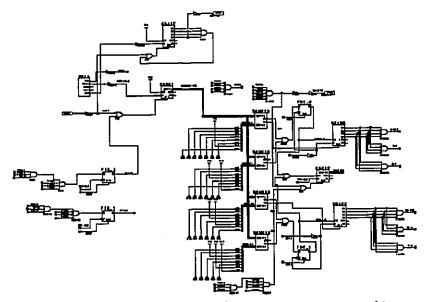

| Figure | 4.20 | Schematic of AIC                                                                                                                                                 | 75 |

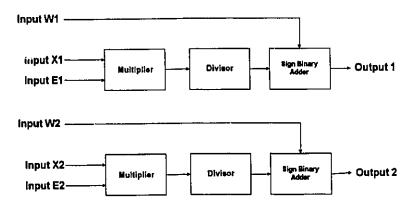

| Figure | 4.21 | Block Diagram of PROCESSOR1                                                                                                                                      | 75 |

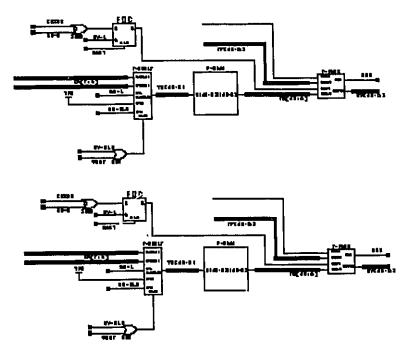

| Figure | 4.22 | Schematic of PROCESSOR1                                                                                                                                          | 76 |

| Figure | 4.23 | Block Diagram of PROCESSOR2                                                                                                                                      | 76 |

| Figure | 4.24 | Schematic of PROCESSOR2                                                                                                                                          | 77 |

| Figure | 4.25 | Flowchart of AIC                                                                                                                                                 | 79 |

| Figure | 4.26 | Schematic of Control Unit                                                                                                                                        | 80 |

| Figure | 4.27 | Control Signal During Adaptive Process                        | 80  |

|--------|------|---------------------------------------------------------------|-----|

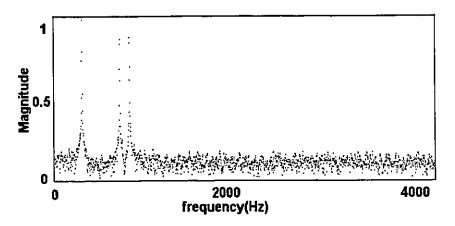

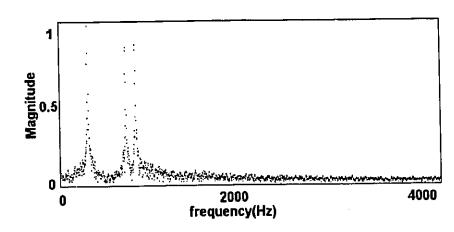

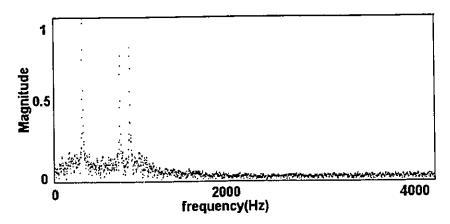

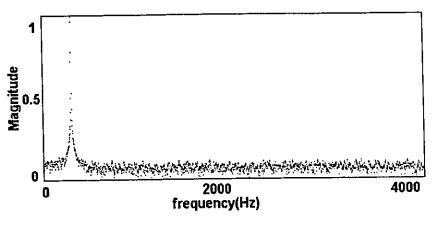

| Figure | 5.1  | Frequency Spectrum of Test Input                              | 85  |

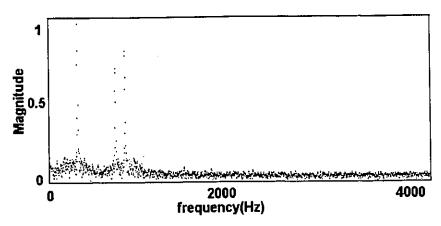

| Figure | 5.2  | Magnitude Response of Canceler in Simulation 4                | 86  |

| Figure | 5.3  | Magnitude Response of Canceler in Simulation 7                | 87  |

| Figure | 5.4  | Magnitude Response of Canceler in Simulation 12               | 87  |

| Figure | 5.5  | Magnitude Response of Canceler in Simulation 8                | 88  |

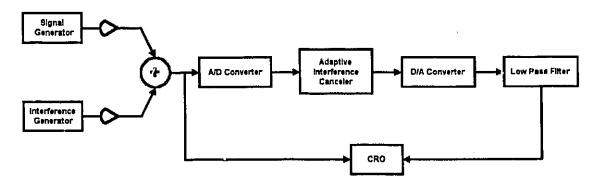

| Figure | 5.6  | Connection of Equipment                                       | 88  |

| Figure | 5.7  | AIC Demonstration Board                                       | 90  |

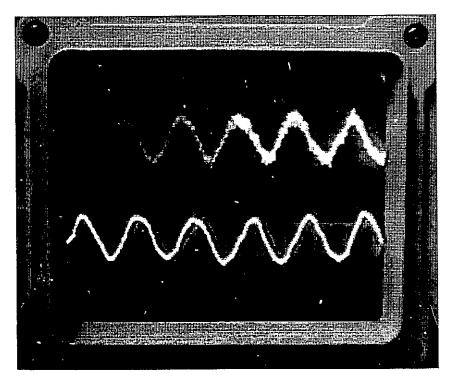

| Figure | 5.8  | Test Result of AIC                                            | 91  |

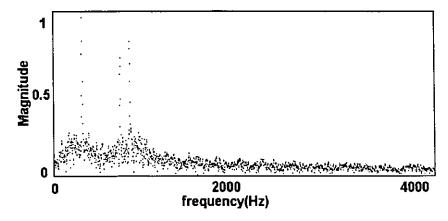

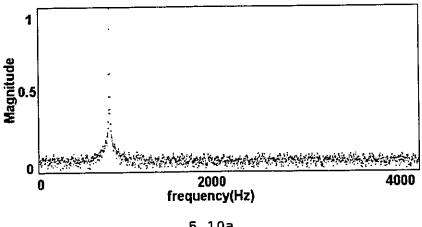

| Figure | 5.9  | Hardware Simulation 1                                         | 92  |

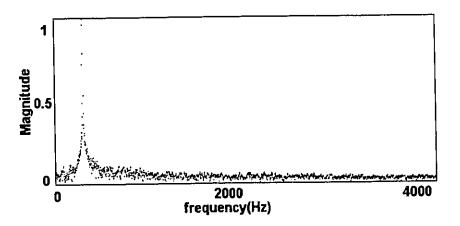

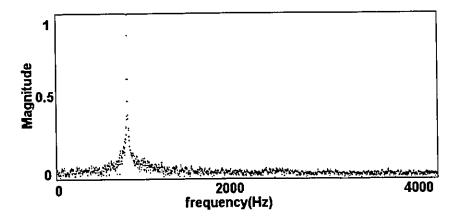

| Figure | 5.10 | Hardware Simulation 2                                         | 93  |

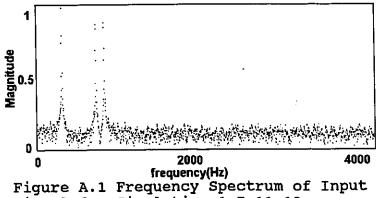

| Figure | A.1  | Frequency Spectrum of Input Signal for Simulation 1-7 & 11-12 | 102 |

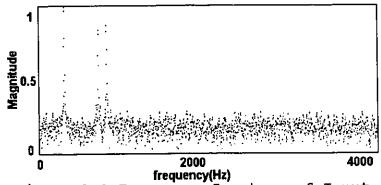

| Figure | A.2  | Frequency Spectrum of Input Signal for Simulation 8           | 102 |

| Figure | A.3  | Frequency Spectrum of Input Signal for Simulation 9           | 103 |

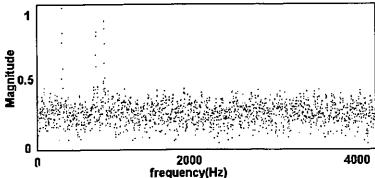

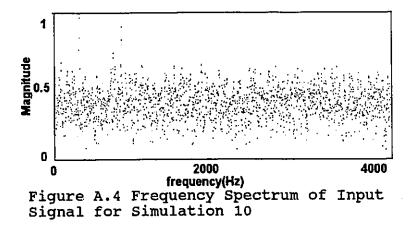

| Figure | A.4  | Frequency Spectrum of Input Signal for Simulation 10          | 103 |

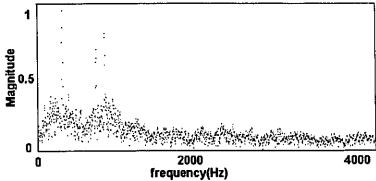

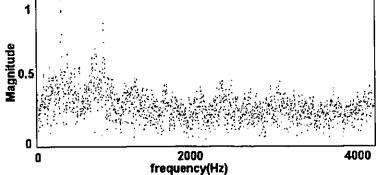

| Figure | A.5  | Frequency Spectrum of Output Signal for Simulation 1          | 103 |

| Figure | A.6  | Frequency Spectrum of Output Signal for Simulation 2          | 104 |

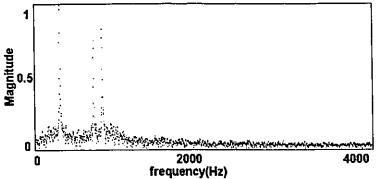

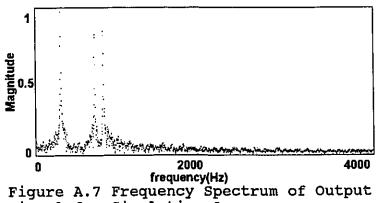

| Figure | A.7  | Frequency Spectrum of Output Signal for Simulation 3          | 104 |

| Figure | A.8  | Frequency Spectrum of Output Signal for Simulation 4          | 104 |

| Figure | A.9  | Frequency Spectrum of Output Signal for Simulation 5          | 105 |

| Figure | A.10 | Frequency Simulation    |                | of | Output | Signal | for | 105 |

|--------|------|-------------------------|----------------|----|--------|--------|-----|-----|

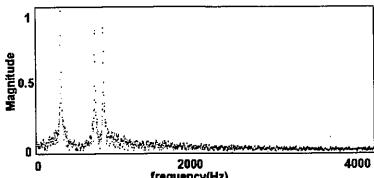

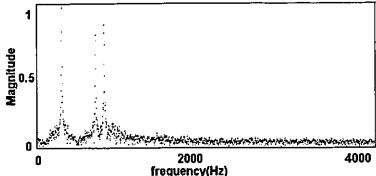

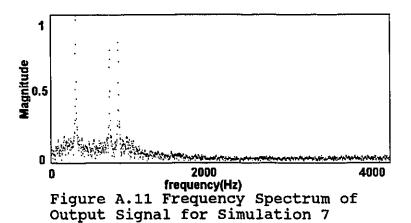

| Figure | A.11 | Frequency Simulation    |                | of | Output | Signal | for | 105 |

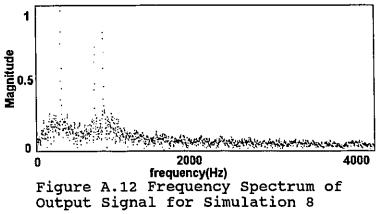

| Figure | A.12 | Frequency<br>Simulation |                | of | Output | Signal | for | 106 |

| Figure | A.13 | Frequency<br>Simulation |                | of | Output | Signal | for | 106 |

| Figure | A.14 | Frequency<br>Simulation |                | of | Output | Signal | for | 106 |

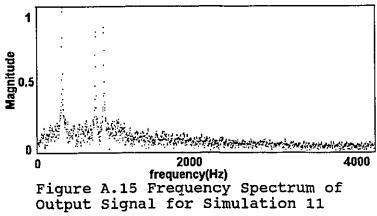

| Figure | A.15 | Frequency<br>Simulation | Spectrum<br>11 | of | Output | Signal | for | 107 |

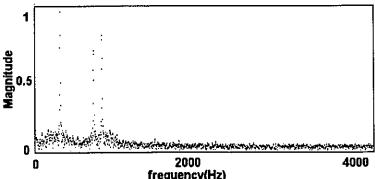

| Figure | A.16 | Frequency<br>Simulation |                | of | Output | Signal | for | 107 |

# **List of Tables**

| Table 3.1 | Characteristics of Programming<br>Technologies                            | 31 |

|-----------|---------------------------------------------------------------------------|----|

| Table 3.2 | Xilinx FPGA Logic Capacities                                              | 34 |

| Table 4.1 | Input & Output Example for Symmetrical Offset Binary Operation            | 55 |

| Table 4.2 | Truth-table of Signed Multiplication                                      | 62 |

| Table 4.3 | Relationship between Different Numerical Format                           | 65 |

| Table 4.4 | Comparison between Direct Implementation & Queue Structure Implementation | 74 |

| Table 5.1 | Result of Different Configuration Simulations                             | 84 |

# Chapter 1

## Introduction

This thesis presents the design methodology for an adaptive interference canceler (AIC) for periodic signals. The canceler can reduce interference power from a corrupted signal based on the principles of least mean-square (LMS) adaptive filtering [1]. This approach has the advantage of requiring no prior knowledge of the interference signal because the filter has the ability to adjust its own parameters automatically. Implementation details and stimulation results are given for a Field Programmable Gate Array (FPGA) prototype. This chapter provides a brief introduction and motivation of the research work conducted. In addition, the outline of the thesis is described.

#### 1.1 Motivation

Separating a desired signal from background interference is an important problem in signal processing. In many environments, such as in aircrafts, helicopters, and concert halls, the characteristics of interference changes frequently. It is known that the presence of high levels of acoustic interference in an audio signal significantly reduces the intelligibility of the signal. Although the use of gradient (noise cancelling) microphones and a physical barrier such as oxygen facemasks reduces the noise problem somewhat, the ambient interference levels encountered in environments such as high performance tactical aircrafts are often severe enough that the performance of vocoders and automatic speech recognition systems are seriously affected.

Traditionally, a fixed weight filter is used for interference cancellation. However, the design of fixed filter must be based on prior knowledge of both signal and interference. If the properties of the interference are unknown, the fixed weight filter for interference cancellation is not a suitable approach. A useful method that requires more than one input source is adaptive noise cancellation (ANC) proposed by Widrow et al.[1]. The ANC method uses a second sensor, commonly called the reference, to gain additional information about the background interference. If

the reference sensor contains only a correlated version of the interference component in the primary sensor, and an interference corrupted signal is applied in the primary, the filter minimizes the interference power while leaving the desired signal unaffected. If the interference in the reference microphone is related to the noise in the primary microphone by a linear filter, then it is possible to cancel completely the noise corrupting the desired signal.

In this thesis, an adaptive digital interference canceler is implemented to process the corrupted periodic signal directly using a third generation of programmable logic devices FPGA. The results of this thesis show that the adaptive digital interference canceler performs satisfactorily.

## 1.2 Thesis Organization

This thesis is divided into six chapters. Chapter 2 provides the background information on the adaptive noise cancellation and the LMS algorithm. Chapter 3 presents the background material to understand FPGA technology. It includes a brief description about the evolution of programmable devices, FPGA architectures and CAD flow for implementation. Design methodology of the adaptive interference canceler is in Chapter 4. The structure of

#### Chap.1 Introduction

different arithmetic units are also described. In Chapter 5, the test results of a FPGA implementation are presented and compared with computer simulation results. Finally, Chapter 6 summarizes the tasks undertaken by this thesis and shows some directions that can be taken for future work.

# Chapter 2

# **Background Theory**

This chapter provides a brief overview of the background theory relevant to this thesis. The concept of adaptive noise cancellation is presented followed by an brief introduction of adaptive filters and the adaptive LMS algorithm.

## 2.1 Concept of Adaptive Noise Cancellation

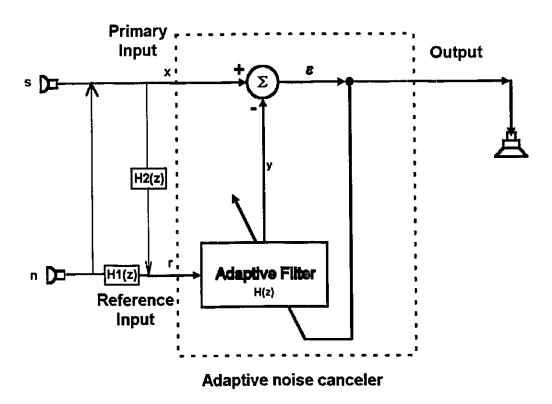

One of the most useful applications of adaptive filtering is the method of Adaptive Noise Cancellation (ANC). It was proposed by Widrow et al.[8] in 1975. Fig. 2.1 illustrates the basic model of the ANC. The signal x at the primary input is composed of a desired component s and a noise

component n, whereas the signal r

#### Adaptive Noise Cancellation Model

Figure 2.1 Model of Adaptive Noise Cancellation

at the reference input consists of a filtered version of the desired signal s' and noise signal n'. For simplicity, the discrete time index has been removed. The transfer functions  $H_1(z)$  and  $H_2(z)$  are assumed to be models of propagation channels for the noise and the signal in reference input. The r is filtered by H(z) to produce the output y that is an estimate of the additive noise n. The estimated desired

signal  $\epsilon$  is obtained by subtraction  $\epsilon = X - y$  and it is also used to control the adaptive filter. If it is assumed that  $|H_2(z)| \approx 0$  so that the signal r contains no signal s component and signal s is uncorrelated with both noise signal s and s, then the result of Widrow et al. shows that minimizing  $E[\epsilon^2]$  will give the best least-square fit to the clean signal s. From Fig 2.1, the system output is

$$\epsilon = s + n - y \tag{2.1}$$

Squaring, one obtains

$$\epsilon^2 = s^2 + (n-y)^2 + 2s(n-y)$$

(2.2)

Taking expectations of both sides of (2.2), and realizing that s is uncorrelated with n and with y, yields

$$E[\epsilon^{2}] = E[s^{2}] + E[(n-y)^{2}] + 2E[s(n-y)]$$

$$= E[s^{2}] + E[(n-y)^{2}]$$

(2.3)

The signal power  $E[s^2]$  will be unaffected as the filter is adjusted to minimize  $E[\epsilon^2]$ . Accordingly, the minimum output power is

$$E_{\min}[\epsilon^2] = E[s^2] + E_{\min}[(n-y)^2]$$

(2.4)

Since minimizing  $E[\epsilon^2]$  corresponds to minimizing  $E[(n-y)^2]$ , y is the best least-square estimate of noise n.

The success of the ANC is dependent on obtaining an

#### Chap.2 Background Theory

external reference noise input which satisfies the stated requirements. In some applications, the reference input contains signal components  $|H_2(z)| \neq 0$ . Assume the input signal and noise power spectra are  $\Phi_{ss}(z)$  and  $\Phi_{nn}(z)$  respectively. The spectrum of the reference input is related to the spectrum of the input x as,

$$\Phi_{rr}(z) = \Phi_{ss}(z) |H_2(z)|^2 + \Phi_{nn}(z) |H_1(z)|^2$$

(2.5)

The cross-spectrum between the reference input and the primary inputs is identical to the cross-spectrum between the filter's input r and desired response x, which is

$$\Phi_{rx}(z) = \Phi_{ss}(z)H_2(z^{-1}) + \Phi_{nn}(z)H_1(z^{-1})$$

(2.6)

When the adaptive process has converged, the unconstrained Wiener transfer function of the adaptive filter is

$$H(Z) = \frac{\Phi_{ss}(Z)H_2(Z^{-1}) + \Phi_{nn}(Z)H_1(Z^{-1})}{\Phi_{ss}(Z)|H_2(Z)|^2 + \Phi_{nn}(Z)|H_1(Z)|^2}$$

(2.7)

The transfer function of the propagation path from the signal input to the noise-canceler output is  $1-H_2(z)H(z)$  and that of the path from the noise input to the canceler output is  $1-H_1(z)H(z)$ . The spectrum of the signal component in the output is

$$\Phi_{ss-out}(z) = \Phi_{ss}(z) |1-H_2(z)H(z)|^2$$

Chap.2 Background Theory

$$= \Phi_{ss}(z) \left| \frac{[H_1(z) - H_2(z)] \Phi_{nn}(z) H_1(z^{-1})}{\Phi_{ss}(z) |H_2(z)|^2 + \Phi_{nn}(z) |H_1(z)|^2} \right|^2 (2.8)$$

and that of the noise component is similarly

$$\Phi_{\text{nn-out}}(z) = \Phi_{\text{nn}}(z) |1-H_1(z)H(z)|^2$$

$$= \Phi_{\text{nn}}(z) \left| \frac{[H_2(z)-H_1(z)]\Phi_{\text{ss}}(z)H_2(z^{-1})}{\Phi_{\text{cs}}(z)|H_2(z)|^2 + \Phi_{\text{nn}}(z)|H_1(z)|^2} \right|^2 (2.9)$$

The output signal-to noise density ratio is

$$\rho_{\text{out}}(z) = \frac{\Phi_{\text{ss}}(z)}{\Phi_{\text{nn}}(z)} \left| \frac{\Phi_{\text{nn}}(z) H_1(z^{-1})}{\Phi_{\text{ss}}(z) H_2(z^{-1})} \right|^2$$

$$= \frac{\Phi_{\text{nn}}(z) |H_1(z)|^2}{\Phi_{\text{cs}}(z) |H_2(z)|^2}$$

(2.10)

The output-to-signal density ratio can be expressed in terms of the signal-to-noise density ratio at the reference input,  $\rho_{\rm ref}(z)$ . The spectrum of the signal component in the reference input is

$$\Phi_{\text{ss-ref}}(z) = \Phi_{\text{ss}}(z) |H_2(z)|^2 \qquad (2.11)$$

and that of the noise component is similarly

$$\Phi_{\text{nn-ref}}(z) = \Phi_{\text{nn}}(z) |H_1(z)|^2$$

(2.12)

The signal-to-noise density ratio at the reference input is

Chap. 2 Background Theory

$$\rho_{\text{ref}}(z) = \frac{\Phi_{\text{ss}}(z) |H_2(z)|^2}{\Phi_{\text{nn}}(z) |H_1(z)|^2}$$

(2.13)

The output signal-to-noise density ratio is

$$\rho_{\text{out}}(z) = \frac{1}{\rho_{\text{ref}}(z)} \tag{2.14}$$

This equation is known as the signal-to-noise inversion principle. Assuming the adaptive solution to be unconstrained and the noise in the primary and reference inputs to be mutually correlated, the SNR of the ANC system output is the inverse of the SNR of the reference.

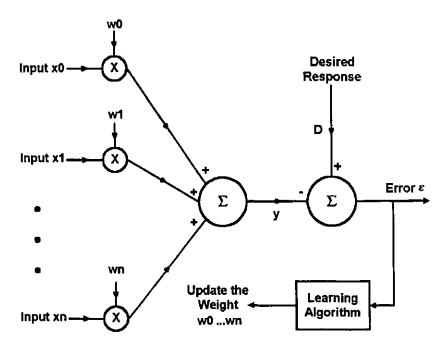

Figure 2.2 Multiple-input Adaptive FIR Filter with Desired Response and Error Signals

## 2.2 Adaptive Nonrecursive Filter

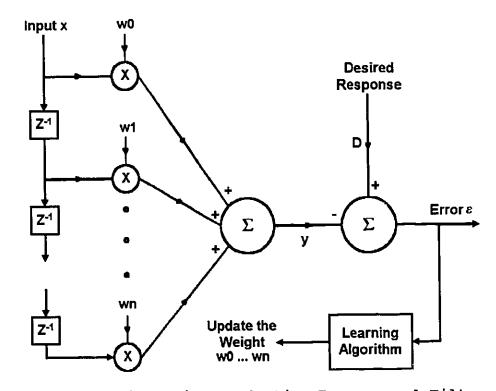

An adaptive nonrecursive or FIR filter, sometimes called an adaptive linear combiner, is fundamental to adaptive signal processing. It is the single most important element in adaptive or learning processes. Because of its nonrecursive structure, the adaptive FIR filter is relatively easy to understand. A general form of adaptive FIR filter is shown in Fig. 2.2. It consists of an input signal vector with elements  $x_0, x_1, x_2 \ldots x_n$  ( $X = x_0, x_1, x_2 \ldots x_n$ ), a corresponding set of adjustable weights  $w_0, w_1, w_2 \ldots w_n$  ( $W = w_0, w_1, w_2 \ldots w_n$ ), a summing unit, and a single output signal y. The procedure for adjusting the weights is called a "weight adjustment" or "adaptation" procedure. The weights are updated based on the  $\epsilon$  and the learning algorithm.

There are two forms of the input vector X. First they may be considered to be simultaneous inputs from n+1 different signal sources. Second, the elements in vector X may be considered to be n+1 sequential samples for the same signal source. The structure of a single input FIR filter is shown in Fig. 2.3. This thesis focuses on a single input FIR filter.

For multiple input:

$$X_{k} = [ x_{0k} x_{1k} x_{2k} \dots x_{nk} ]^{T}$$

(2.15)

Chap.2 Background Theory

$$y_{k} = \sum_{l=0}^{n} w_{lk} x_{lk}$$

(2.16)

Corresponding to (2.16), we have a weight vector

$$W_{k} = [ w_{0k} w_{1k} w_{2k} \dots w_{nk} ]$$

(2.17)

Equation (2.17) can be expressed in vector notation

$$y_{k} = X_{k}^{\mathsf{T}} W_{k} \tag{2.18}$$

Figure 2.3 Single-input Adaptive Transversal Filter with Desired Response and Error Signal

Chap. 2 Background Theory

For single input:

$$X_{k} = [ x_{k} x_{k-1} x_{k-2} \dots x_{k-n} ]^{T}$$

(2.19)

$$y_{k} = \sum_{l=0}^{n} w_{lk} x_{k-l}$$

(2.20)

Error signal is

$$\epsilon_{\mathbf{k}} = D_{\mathbf{k}} - Y_{\mathbf{k}} \tag{2.21}$$

where k is the time index.

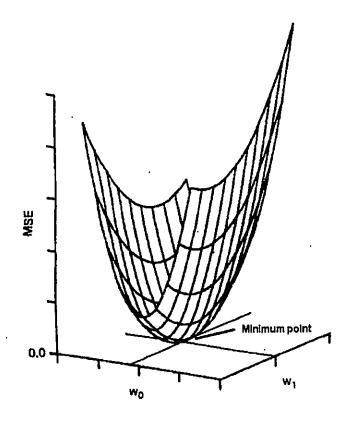

## 2.3 Least-Mean-Squares Adaptive Algorithm

The purpose of the adaptive algorithm is to adjust the weights of the adaptive filter to minimize the mean-square error  $\epsilon$ . For stationary input signals and a desired response, the mean-square error is a quadratic function of the weights with a single fixed minimum point [2],[3]. The least-mean-squares (LMS) algorithm [1],[3],[4],[5] is a widely used adaptive algorithm for finding close approximate solutions in real time. The algorithm does not require specific measurements of correlation functions and complex arithmetic operations. Accuracy is limited by statistical sample size because the weight values found are based on real-time measurements of input signals.

Figure 2.4 A Two-dimensional Quadratic Performance Surface of Adaptive Filter

The LMS is a gradient search algorithm using the steepest descent, the estimation of the gradient is based on the instantaneous value of the error. According to LMS, the "next" weight vector  $W_{k+1}$  is equal to the "present" weight vector  $W_k$  plus a change proportional to the negative gradient:

$$W_{k+1} = W_k - \mu \nabla_k \tag{2.22}$$

The parameter  $\mu$  is the factor that controls stability and rate of convergence.  $v_k$  represents the true gradient at the  $k^{th}$

#### Chap.2 Background Theory

iteration. The LMS algorithm estimates an instantaneous gradient  $v_k$ ' by assuming that  $\epsilon_k^2$  is an estimate of the meansquare error and by differentiating  $\epsilon_k^2$  with respect to W. The formulas for the true and estimated gradients are given as follows:

$$\nabla_{\mathbf{k}} \triangleq \begin{bmatrix} \frac{\partial E[\epsilon_{\mathbf{k}}^{2}]}{\partial E[\epsilon_{\mathbf{k}}^{2}]} / \frac{\partial w_{0}}{\partial w_{n}} \end{bmatrix}$$

(2.23)

$$\nabla_{\mathbf{k}'} = \begin{bmatrix} \frac{\partial \epsilon_{\mathbf{k}}^{2}}{\partial \epsilon_{\mathbf{k}}^{2}} & \frac{\partial w_{0}}{\partial w_{0}} \\ \frac{\partial \epsilon_{\mathbf{k}}}{\partial \epsilon_{\mathbf{k}}^{2}} & \frac{\partial w_{0}}{\partial w_{0}} \end{bmatrix} = 2\epsilon_{\mathbf{k}} \begin{bmatrix} \frac{\partial \epsilon_{\mathbf{k}}}{\partial \epsilon_{\mathbf{k}}} & \frac{\partial w_{0}}{\partial w_{0}} \\ \frac{\partial \epsilon_{\mathbf{k}}}{\partial \epsilon_{\mathbf{k}}} & \frac{\partial w_{0}}{\partial w_{0}} \end{bmatrix} = -2\epsilon_{\mathbf{k}} X_{\mathbf{k}}$$

(2.24)

To replace the true gradient of (2.23) with the estimated gradient in (2.24) gives the Widrow-Hoff LMS algorithm:

$$W_{k+1} = W_k + 2\mu \epsilon_k X_k \tag{2.25}$$

This algorithm is simple and easy to implement in a practical system without squaring, averaging and differentiation. It has been shown [9] that starting with an arbitrary weight vector, the algorithm will converge in the mean and will remain stable as long as the parameter  $\mu$  is greater than zero but less than the reciprocal of the largest eigenvalue of the matrix R:

$$R = E[X_n X_n^{\mathsf{T}}] \tag{2.26}$$

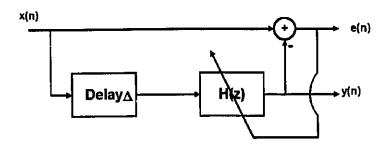

### 2.4 ANC without an External Reference Input

In some situations, no external reference input free of the signal is available. If an input signal is consisted of a multiple of sinusoidal signals and is corrupted by some broadband signals. It is possible to construct an ANC system without an external reference. A delayed version of the input signal is used as the reference in this case. The block diagram of the ANC without the external reference input is shown in Figure 2.5. The approach is to used a fixed delay  $\Delta$  to cause the broadband signal components in the reference input to become decorrelated from those in the primary input.

$$E\{ s(n) *s(n-\Delta) \} \approx 0$$

(2.27)

The chosen delay A must be sufficient to decorrelate the broadband components. Because of the periodic nature of the periodic components, they will remain correlated with each other.

Figure 2.5 Block Diagram of ANC without External Reference Input

## 2.5 Summary

In this chapter, the basic concepts of the ANC, adaptive FIR filters and the LMS algorithm have been introduced. The ANC requires a reference signal to cancel the noise from a primary signal. It greatly improves the signal-to-noise ratio of noisy signals under certain conditions. The advantage of the ANC is that it requires little or no prior knowledge of signal or noise characteristics. Due to its simple structure, it is suitable for digital implementation as demonstrated in this thesis.

# Chapter 3

# **Introduction to FPGA Technology**

This chapter provides a brief introduction to FPGA technology. It begins by describing the evolution of programmable devices, and follows with a brief discussion on programming elements, FPGA examples and the related CAD flow for the implementation of circuits.

## 3.1 Evolution of Programmable Device

Digital system design has changed a great deal in the last ten years. Programmable devices, which are general-purpose chips that can be configured for different

applications, have become a key role in the design of digital hardware. A programmable Read-Only Memory (PROM) was the first type of programmable device used widely. It is a one-time programmable device that consists of an array of read-only cells. A pre-defined truth-table in the form of a logic circuit is stored in memory cells. By using the PROM's address lines as the circuit's inputs, the circuit's outputs are based on the stored bits. With this strategy, any truth-table function can be implemented. A PROM is suitable for computer memories in microcontroller based systems.

There are two basic versions of PROMs: mask-programmable and field programmable. The first is configured by the manufacturer. It provides a high speed of operation because connections within the device can be hardwired during the manufacturing process. In contrast, the speed of field-programmable devices is always slowed down by programmable switches. However, a field programmable chip can be programmed within days using inexpensive equipment. There are two enhanced versions of field programmable devices, the Erasable Programmable Read-Only Memory and Electrically Erasable Programmable Read-Only Memory. Both of them can be erased and reprogrammed many times.

The second type of programmable device is called a Programmable Logic Device (PLD) which is specifically designed for implementing logic circuits. Programmable Array Logic

is the most basic form of PLD. It contains a (PAL) programmable AND-plane followed by a fixed OR-plane. The ANDplane can give the product of inputs as an output and the ORplane can generate the sum of product terms. Hence, PAL is ideal for implementation of sum-of-products form of logic The outputs of the OR-gates can be registered by functions. a flip-flop optionally. The Programmable Logic Array (PLA) is a variant of PAL in that both planes are programmable. types of PLDs allow high operation speed but they can only implement small logic circuits due to their simple structures. The logic capacity is about 5000 logic gates. They are also available in either mask-programmable or field-programmable versions.

Besides PLDs, Mask-Programmable Gate Arrays (MPGAs) are also widely used in industry. An MPGA consists of rows of transistors that can be interconnected to form a desired logic circuit. User specified connections are available between rows (to connect basic gates together) and within rows (to construct basic logic gates). All mask layers of the chip are pre-defined by the manufacturer, except for those that specify the final metal layers. These metal layers are customized to connect the transistors in the array during fabrication in order to form the desired circuit. The advantage of MPGAs is that they allow the implementation of much larger circuits. However, they lack of the instantaneous programmability and

have a large non-recurring engineering cost.

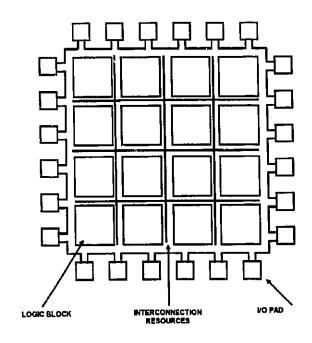

In order to take advantage of both PLDs and MPGAs, Field Programmable Gate Arrays (FPGAs) were introduced by Xilinx Company in 1985. FPGAs combine the programmability of PLDs and the scalable interconnection structure of MPGAs. Hence, present programmable devices have a much higher logic density.

Figure 3.1 Conceptual FPGA

## 3.2 Structure of FPGA

FPGAs were introduced by the Xilinx Company in 1985. They are programmable devices like PALs, in that the interconnections between the elements are user-programmable without the use of an integrated circuit fabrication facility.

Also like an MPGA, an FPGA includes an array of uncommitted elements that can be interconnected in a general way. Since then, a number of companies, such as Actel, Advanced Micro Devices (AMD), Motorola, AT&T and Crosspoint Solutions, have introduced many different FPGAs.

FPGAs are a collection of functionally complete or universal logic elements placed in an interconnection Some parts look like two dimensional cell arrays framework. with little interconnection channels running horizontally and vertically between the cells. It is shown in Figure 3.1. Other parts look more like stacked logic gates with The PLDs. arrays, similar to regular programmable interconnect contains segments of wire, where the segments may vary in lengths. By the programmable switches, logic blocks can connect different wire segments, or one wire segment to Logic circuits are implemented in a FPGA by another. partitioning the logic into individual logic blocks and then interconnecting the blocks as required via the switches.

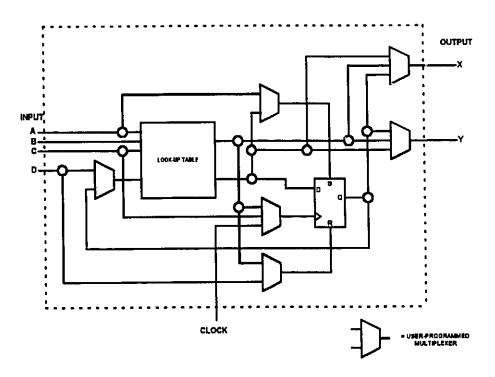

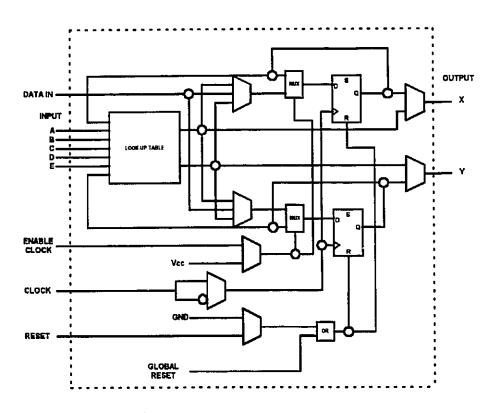

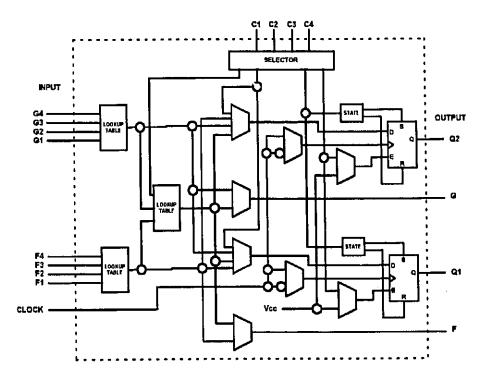

The heart of FPGAs is the programmable logic block. The structure and content of a logic block are called its architecture. The design of the logic block should be as versatile as possible. Some FPGA logic blocks can be as simple as 2-input NAND gates or have a more complex structure, such as look-up tables (Xilinx's FPGA [7]) and multiplexers (Actel's FPGA [8]). In some FPGAs, a logic block compares

#### Chap.3 Introduction to FPGA Technology

with an entire PAL-like structure. Most logic blocks also contain some type of flip-flop, to aid in the implementation of sequential circuits.

Figure 3.2 Three Classes of Commercial FPGA [6]

The structure and content of the interconnect in FPGA is called its routing architecture. The routing architecture includes programmable switches and wire segments. The programmable switches can be built using several methods including: pass-transistors controlled by static RAM cells, anti-fuses, EPROM transistors, and EEPROM transistors. As in the logic blocks, different companies provide different routing architectures. Some FPGAs offer a large number of simple connections between blocks but others provide less connections with more complex routes.

## 3.3 Programming Technologies

The instant programmability of FPGA depends on the programmable devices of a FPGA chip, including programmable logic blocks and programmable elements. It is important to understand how the programmable devices work. programmable elements refer to the entities that allow programmable connections between wire segments. Generally, a typical FPGA may contain more than 100,000 programmable elements. The design of programmable elements depends on the application in which a FPGA is used. For example, some programmable elements are non-volatile and some elements can be re-configured without being removed from the circuit board. No matter which design is used, the programming elements can be configured in one of two states: ON or OFF. Due to the huge number of programmable elements in a chip, the design of a programmable element should have the following properties:

- the chip area of programmable element should be as small as possible,

- the programmable element should have a low ON resistance and a very high OFF resistance,

- the programmable element should contribute low parasitance to the wiring resources to which it is attached,

- the programmable element should be reliably manufactured in large volume on a chip.

There are four types of programming elements that are currently used in commercial FPGAs. They are static RAM cells, anti-fuses, EPROM transistors, and EEPROM transistors. Each one of them has different properties and different fabrication procedures. The details of each of the programming elements will be described in the following.

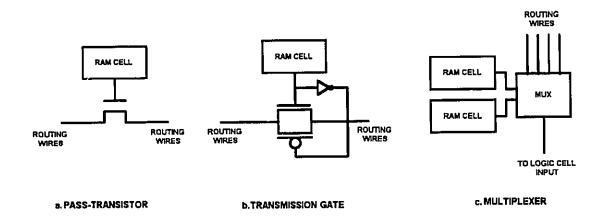

#### 3.3.1 Static RAM Programming Technology

Static RAM programming technology uses SRAM cells to control pass-transistors, transmission gates or multiplexers in programmable connections. Figure 3.3a shows the use of a static RAM cell to control a CMOS pass-transistor. Also the SRAM can control both the n-channel and p-channel transistors of a full transmission gate (Figure 3.3b). In the OFF state, the pass-gate forms a very high resistance between the two wires to which it is attached. In the ON state, it creates a low resistance connection between the two wires. Besides the above two approaches, several SRAMs can be used to control the select inputs on a multiplexer. It is shown in Figure 3.3c. This design is used to optionally connect one of several wires to a single input of a logic block.

Due to volatility of SRAM, static RAM FPGA must be reconfigured when the power is applied to the chip. Hence, permanent storage, such as a ROM or a disk, is required to store the programming information. Compared with other programming technology, this technology requires a relatively large chip area. This is because at least five transistors are needed for each RAM cell and the transistors for the passgate or multiplexers. The major advantage of this technology is that FPGAs using this technology can be reconfigured very quickly and the programmable elements can be produced using standard CMOS process technology. FPGA's produced by Algotronix, Concurrent Logic, Plessey Semiconductors, and Xilinx use static RAM programming technology.

Figure 3.3 Static RAM Programming Technology [6]

#### 3.3.2 Anti-fuse Programming Technology

Anti-fuse programming technology is used in FPGAs offered by Actel Corp., QuickLogic and Crosspoint Solutions. Although

the implementation of these elements is different from company to company, their function is the same. An anti-fuse element normally stays in a high-impedance state but can be "fused" into a low-impedance state when programmed by a high voltage.

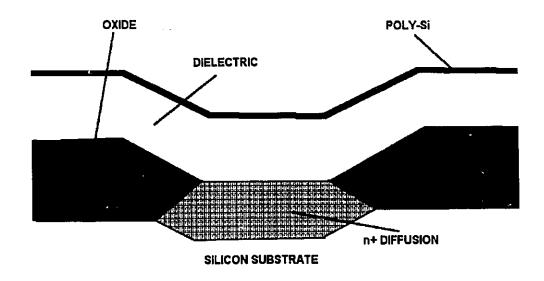

Figure 3.4 PLICE Anti-fuse Programming Technology [6]

pLICE [9] is an anti-fuse device used by Actel. It can be described as a square structure that consists of three layers: the top layer made of poly silicon, the middle layer, a dielectric (Oxygen-Nitrogen-Oxygen insulator), and the bottom layer, composed of positively-doped silicon (n+silicon). This construction is shown in Figure 3.4. When a high voltage (18 V) is applied across the anti-fuse terminals and driving a current of about 5 mA through the device, enough

heat in the dielectric is generated to form a conductive link between the Poly-Si and n+ diffusion. Metal wires are connected to both the bottom layer and top layer. When it is in ON state, there is a resistance of about 300-500 ohms between the two metal wires. The PLICE anti-fuse requires special high-voltage transistors within FPGA to accommodate the necessary large voltages and currents, and three additional specialized masks to a normal CMOS process in fabrication.

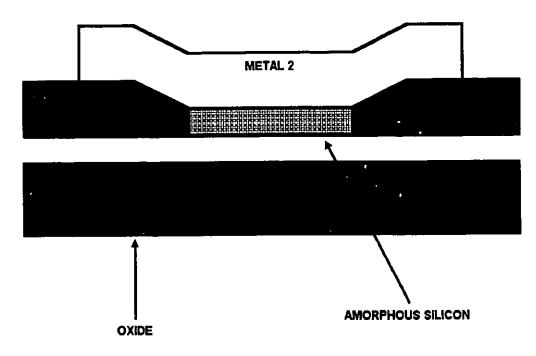

Figure 3.5 ViaLink Anti-fuse Programming Technology [6]

ViaLink [10] is an anti-fuse used by Quicklogic. It consists of a metal bottom layer, an alloy of amorphous

silicon for its middle layer, and a metal top layer. The structure of ViaLink anti-fuse is shown in Figure 3.5. When 10V is applied across its terminals, the amorphous silicon will create a conductive link between the bottom and top layers of metal. The resistance of the conductive layer is about 80 ohms between the two metal wires. This anti-fuse is manufactured using three extra masks above a normal CMOS process.

Compared to other programming technologies, anti-fuses require less chip area. However, they require large chip area for the high-voltage transistors that are needed to handle the high programming voltages and currents. Also, anti-fuse technology requires modification to the basic CMOS manufacture process.

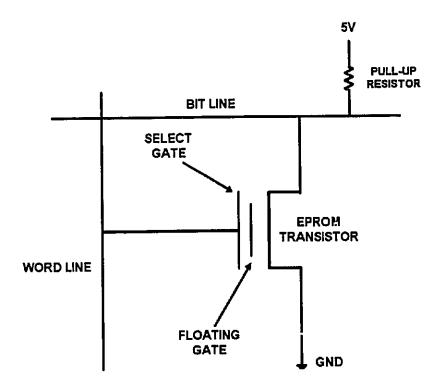

### 3.3.3 EPROM & EEPROM Programming Technology

EPROM programming technology is used by Altera Corp [6] and Plus Logic. It consists of two gates, a floating gate and a select gate. The floating gate is located between the select gate and the transistor's channel, and it is not electrically connected to any circuitry. The structure of the EPROM programming circuitry is shown in Figure 3.6.

Figure 3.6 EPROM Programming Technology [6]

In its unprogrammed state, no charge exists in the floating gate and the transistor can be turned ON in the normal fashion by using the select gate. When the transistor is programmed by causing a large current to flow between the source and drain, a charge is trapped under the floating gate. This charge turns the transistor OFF permanently. Hence, the EPROM transistor can function as a programmable element. An EPROM transistor can be re-programmed by removing the trapped charge from the floating gate. By exposing the gate to ultraviolet light, the trapped charge is excited to the point where they can pass through the gate oxide into the substrate. One

#### Chap.3 Introduction to FPGA Technology

advantage of the EPROM programming transistors is that they are reprogrammable and do not require external storage. However, the EPROM programming transistors cannot be reprogrammed in circuit.

| Programming<br>Technology | Volatile | Re-Prog        | Chip-Area                                    | R<br>(ohm)  | C<br>(ff) |

|---------------------------|----------|----------------|----------------------------------------------|-------------|-----------|

| Static RAM<br>Cells       | yes      | in<br>circuit  | large                                        | 1-2 k       | 10-20     |

| PLICE<br>Anti-fuse        | no       | no             | small anti-<br>fuse,<br>large prog.<br>tran. | 300-<br>500 | 3-5       |

| ViaLink<br>Anti-fuse      | no       | no             | small anti-<br>fuse,<br>large prog.<br>tran  | 50-80       | 1.3       |

| EPROM                     | no       | out of circuit | small                                        | 2-4 k       | 10-20     |

| EEPROM                    | no       | in<br>circuit  | 2x EPROM                                     | 2-4 k       | 10-20     |

Table 3.1 Characteristics of Programming Technologies [6]

The EEPROM approach is similar to the EPROM technology except that EEPROM transistors can be re-programmed incircuit. The disadvantage of using EEPROM transistors is that they consume about twice the chip area as EPROM transistors and they require a voltage source for re-programming.