#### University of Windsor Scholarship at UWindsor

**Electronic Theses and Dissertations**

Winter 2014

# Efficient finite field computations for elliptic curve cryptography

Wangchen Dai University of Windsor

Follow this and additional works at: http://scholar.uwindsor.ca/etd Part of the <u>Electrical and Computer Engineering Commons</u>

#### **Recommended** Citation

Dai, Wangchen, "Efficient finite field computations for elliptic curve cryptography" (2014). *Electronic Theses and Dissertations*. Paper 5017.

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

#### EFFICIENT FINITE FIELD COMPUTATIONS FOR ELLIPTIC CURVE CRYPTOGRAPHY by WANGCHEN DAI

A Thesis Submitted to the Faculty of Graduate Studies through Electrical and Computer Engineering in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science at the University of Windsor

Windsor, Ontario, Canada 2013

© 2013 Wangchen DAI

#### EFFICIENT FINITE FIELD COMPUTATIONS FOR ELLIPTIC CURVE CRYPTOGRAPHY

by WANGCHEN DAI

APPROVED BY:

Dr. D. Wu School of Computer Science

Dr. C. Chen Department of Electrical and Computer Engineering

Dr. H. Wu, Advisor Department of Electrical and Computer Engineering

December 11, 2013

### **Author's Declaration of Originality**

I hereby certify that I am the sole author of this thesis and that no part of this thesis has been published or submitted for publication.

I certify that, to the best of my knowledge, my thesis does not infringe upon anyones copyright nor violate any proprietary rights and that any ideas, techniques, quotations, or any other material from the work of other people included in my thesis, published or otherwise, are fully acknowledged in accordance with the standard referencing practices. Furthermore, to the extent that I have included copyrighted material that surpasses the bounds of fair dealing within the meaning of the Canada Copyright Act, I certify that I have obtained a written permission from the copyright owner(s) to include such material(s) in my thesis and have included copies of such copyright clearances to my appendix.

I declare that this is a true copy of my thesis, including any final revisions, as approved by my thesis committee and the Graduate Studies office, and that this thesis has not been submitted for a higher degree to any other University or Institution.

### Abstract

Finite field multiplication and inversion are two basic operations involved in Elliptic Cure Cryptosystem (ECC), high performance of field operations can be applied to provide efficient computation of ECC. In this thesis, two classes of fields are proposed for multipliers with much reduced time delay. A most-significant-digit first and a least-significant-digit first digit-serial Montgomery multiplications are also proposed, using novel fixed elements R(x) which are different from  $x^m$  and  $x^{m-1}$ . Architectures of the proposed Montgomery multipliers are studied and obtained for the fields generated by the irreducible pentanomials, which are selected based on the proposed special finite fields. Complexities of the Montgomery multipliers in term of critical path delay and gate count of the architectures are investigated; the critical path delay of the proposed multipliers are found to be as good as or better than the existing works for the same class of fields. Then, implementation of the proposed multipliers (m = 233) using Field Programmable Gate Array (FPGA) is provided. In addition, an FPGA implementation of an efficient normal basis inversion algorithm is also presented (m = 163). The normal basis multiplication unit is implemented using a digit-level structure, and a C-code is written to generate the first coordinate of the product of two normal basis elements for all field size *m*.

**Key Words:** Montgomery multiplication, digit-serial, Elliptic Curve Cryptography, normal basis inverse, FPGA.

### Dedication

I dedicate this thesis to my parents for supporting me to accomplish my master's degree at University of Windsor in Canada.

### Acknowledgments

I would like to express my sincere gratitude and appreciation to everyone who helped make this thesis possible. I am deeply indebted to my supervisor Prof. Huapeng Wu, Professor of Electrical and Computer Engineering at University of Windsor, for guiding me throughout the writing of this thesis. As one of best teachers I have ever had, Professor Wu impressed upon me that a good teacher instructs students in matters far beyond those in textbooks. His broad knowledge and logical way of thinking have been of great value; without his detailed and constructive comments on my research, none of this thesis would be possible.

I would also grateful to my colleagues and friends, Yiruo He, Ya Tan, Ran Xiao and Shoaleh Hashemi Namin for their time and support.

Finally, I with to extend my gratitude to everyone at UWindsor's Faculty of ECE for their efforts during my study in the M.A.Sc. Program. I also gratefully acknowledge the financial support form University of Windsor and Professor Huapeng Wu.

### Contents

| Αι | ithor <sup>9</sup> | 's Decla | ration of Originality                     |  |  | iii |

|----|--------------------|----------|-------------------------------------------|--|--|-----|

| Ał | ostrac             | et       |                                           |  |  | iv  |

| De | edicat             | ion      |                                           |  |  | v   |

| Ac | cknow              | ledgme   | ents                                      |  |  | vi  |

| Li | st of l            | Figures  |                                           |  |  | X   |

| Li | st of [            | Fables   |                                           |  |  | xii |

| Li | st of A            | Append   | ices                                      |  |  | xiv |

| Li | st of A            | Abbrevi  | ations/Symbols                            |  |  | XV  |

| 1  | Intr               | oductio  | n                                         |  |  | 1   |

| 2  | Mat                | hemati   | cal Preliminaries                         |  |  | 4   |

|    | 2.1                | Finite   | Field and Representations                 |  |  | 4   |

|    | 2.2                |          | comery Multiplication over $GF(2^m)$      |  |  |     |

|    | 2.3                |          | c Curve Cryptosystem                      |  |  |     |

|    |                    | 2.3.1    | Elliptic Curves                           |  |  | 7   |

|    |                    | 2.3.2    | Finite Field Inversion Using Normal Basis |  |  | 9   |

|    |                    | 2.3.3    | Elliptic Curve Cryptosystem               |  |  |     |

| 3  | A R                | eview o  | f Existing Work                           |  |  | 13  |

#### CONTENTS

| <b>Pro</b> ]    | posed D                                                                                         | Digit-serial Montgomery Multipliers                                                                                                                                                                                                                                                     | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|-----------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 4.1             | Propos                                                                                          | sed Digit-Serial MSD First Montgomery Multiplier                                                                                                                                                                                                                                        | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|                 | 4.1.1                                                                                           | Algorithm                                                                                                                                                                                                                                                                               | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|                 | 4.1.2                                                                                           | General Architecture                                                                                                                                                                                                                                                                    | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|                 | 4.1.3                                                                                           | Advanced Architecture                                                                                                                                                                                                                                                                   | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 4.2             | Propos                                                                                          | sed Digit-Serial LSD First Montgomery Multiplier                                                                                                                                                                                                                                        | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|                 | 4.2.1                                                                                           | Algorithm                                                                                                                                                                                                                                                                               | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|                 | 4.2.2                                                                                           | General Architecture                                                                                                                                                                                                                                                                    | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|                 | 4.2.3                                                                                           | LFSR-Based Architecture                                                                                                                                                                                                                                                                 | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 4.3             | Comp                                                                                            | lexity Analysis                                                                                                                                                                                                                                                                         | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 4.4             | FPGA                                                                                            | Implementation of the Proposed Multipliers                                                                                                                                                                                                                                              | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|                 | 4.4.1                                                                                           | Summary of the MSD-First Multiplier Implementation                                                                                                                                                                                                                                      | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|                 | 4.4.2                                                                                           | Summary of the LSD-First Multiplier Implementation                                                                                                                                                                                                                                      | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| FPC             | A Imp                                                                                           | lementation of Inverse Generator                                                                                                                                                                                                                                                        | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 5.1             | The D                                                                                           | esign of Inverse Generator                                                                                                                                                                                                                                                              | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

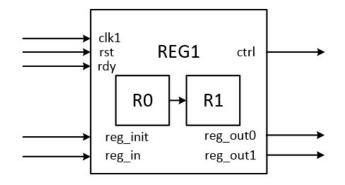

|                 | 5.1.1                                                                                           | REG1 Module                                                                                                                                                                                                                                                                             | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

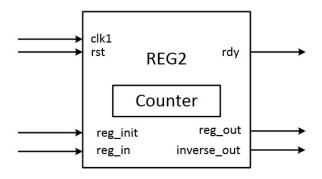

|                 | 5.1.2                                                                                           | REG2 Module                                                                                                                                                                                                                                                                             | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

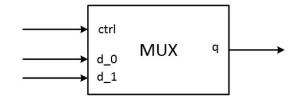

|                 | 5.1.3                                                                                           | MUX Module                                                                                                                                                                                                                                                                              | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

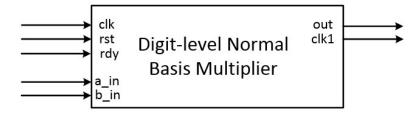

|                 | 5.1.4                                                                                           | Digit-level Normal Basis Multiplier Module and Multiplication Al-                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                 |                                                                                                 | gorithm                                                                                                                                                                                                                                                                                 | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|                 | 5.1.5                                                                                           | Top-Level                                                                                                                                                                                                                                                                               | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 5.2             | Simula                                                                                          | ation and Compilation                                                                                                                                                                                                                                                                   | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|                 | 5.2.1                                                                                           | Simulation Results                                                                                                                                                                                                                                                                      | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|                 | 5.2.2                                                                                           | Compilation Results                                                                                                                                                                                                                                                                     | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Con             | clusion                                                                                         | S                                                                                                                                                                                                                                                                                       | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| C-co            | ode of F                                                                                        | $F(s)$ and the First Coordinate $c_0$ Generation                                                                                                                                                                                                                                        | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Gen             | erated                                                                                          | VerilogHDL-code of the First Coordinate $c_0$                                                                                                                                                                                                                                           | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Bibliography 72 |                                                                                                 |                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                 | 4.1<br>4.2<br>4.3<br>4.4<br><b>FPG</b><br>5.1<br>5.2<br><b>Con</b><br><b>C-co</b><br><b>Gen</b> | 4.1 Propose<br>4.1 4.1.2<br>4.1.1<br>4.1.2<br>4.1.3<br>4.2 Propose<br>4.2.1<br>4.2.2<br>4.2.3<br>4.3 Comp<br>4.4 FPGA<br>4.4.1<br>4.4.2<br>FPGA Imp<br>5.1 The D<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.2 Simula<br>5.2.1<br>5.2.2<br>Conclusion<br>C-code of F<br>Generated | 4.1.1       Algorithm         4.1.2       General Architecture         4.1.3       Advanced Architecture         4.1.4       Proposed Digit-Serial LSD First Montgomery Multiplier         4.2       Proposed Digit-Serial LSD First Montgomery Multiplier         4.2.1       Algorithm         4.2.2       General Architecture         4.2.3       LFSR-Based Architecture         4.3       Complexity Analysis         4.4       FPGA Implementation of the Proposed Multipliers         4.4.1       Summary of the MSD-First Multiplier Implementation         4.4.2       Summary of the LSD-First Multiplier Implementation         5.1       The Design of Inverse Generator         5.1.1       REG1 Module         5.1.2       REG2 Module         5.1.3       MUX Module         5.1.4       Digit-level Normal Basis Multiplier Module and Multiplication Al- gorithm         5.1.5       Top-Level         5.2       Simulation Results         5.2.1       Simulation Results         5.2.2       Compilation Results |  |  |

CONTENTS

Vita Auctoris

76

# **List of Figures**

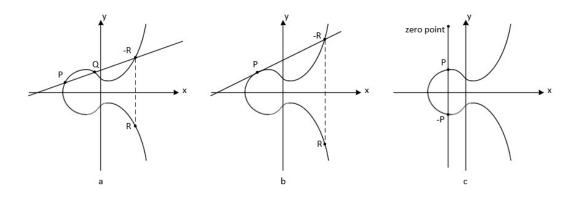

| 2.1  | Operations in an elliptic curve                                                       | 7  |

|------|---------------------------------------------------------------------------------------|----|

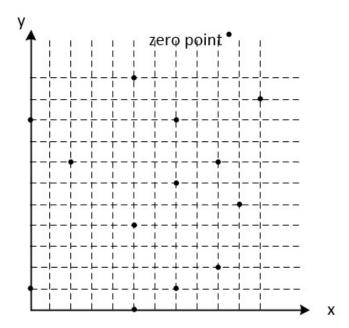

| 2.2  | Elliptic curve over binary field $GF(2^m)$                                            | 9  |

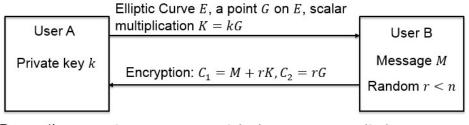

| 2.3  | Encryption/decryption of elliptic curve cryptosystem                                  | 10 |

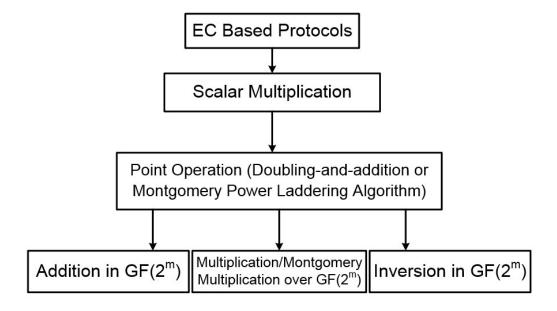

| 2.4  | Computation structure of ECC over $GF(2^m)$                                           | 11 |

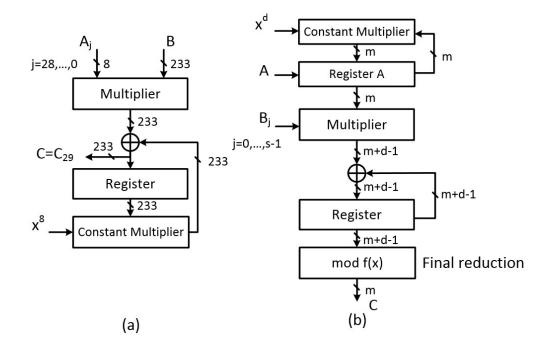

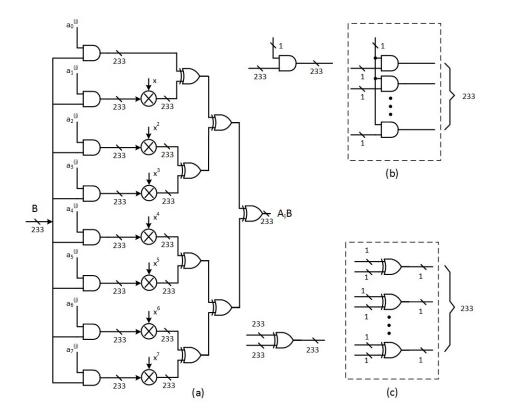

| 3.1  | (a)Tang's architecture of $GF(2^{233})$ multiplier [17] (b)Kumar's architecture       |    |

|      | of $GF(2^m)$ multiplier [19]                                                          | 15 |

| 3.2  | Tang's architecture of partial product multiplier, generates the product of           |    |

|      | $A_j \times B$ [17]                                                                   | 16 |

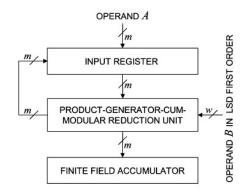

| 3.3  | Meher's block diagram of proposed field multiplier over $GF(2^m)$ [24]                | 17 |

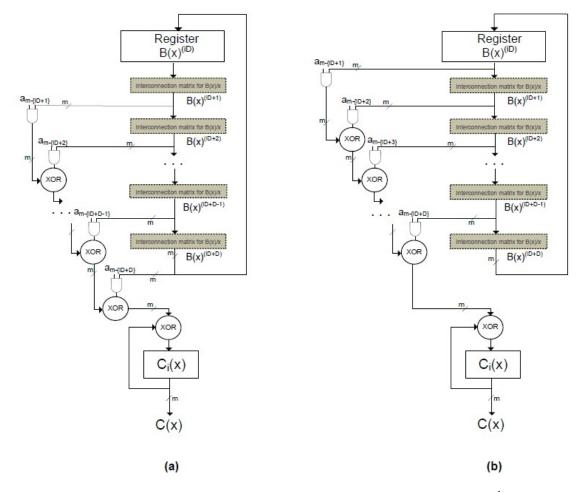

| 3.4  | Work reported in [28], (a) $R(x) = x^m$ , (b) $R(x) = x^{m-1}$                        | 18 |

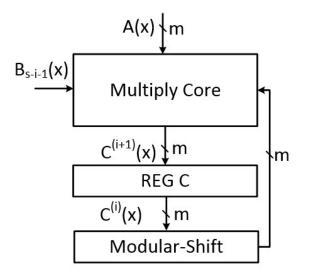

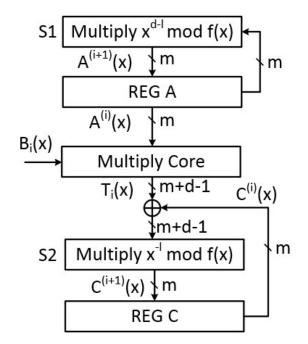

| 4.1  | Block diagram of proposed digit-serial MSD-first Montgomery multiplier                |    |

|      | when $R(x) = x^l$                                                                     | 22 |

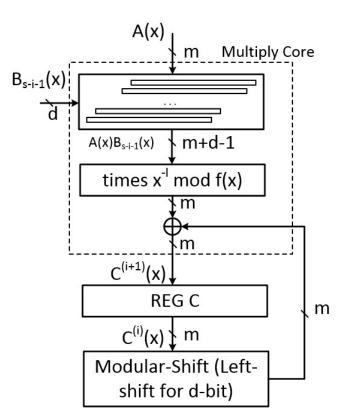

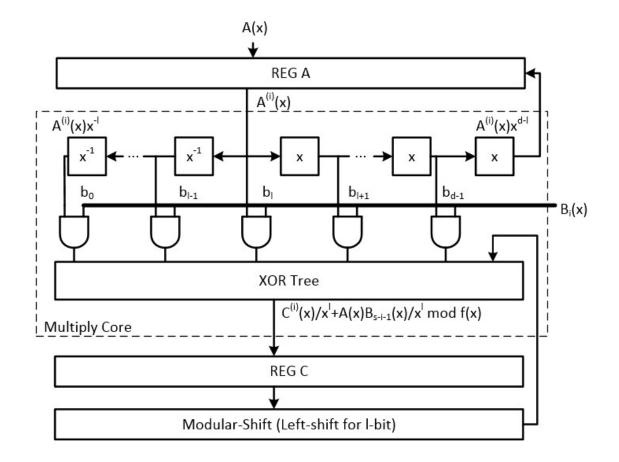

| 4.2  | General architecture of the proposed multiplier when $R(x) = x^{u} \dots \dots \dots$ | 23 |

| 4.3  | Implementation of equation $(4.11)$                                                   | 25 |

| 4.4  | Model 1: multiply by $x$ structure                                                    | 27 |

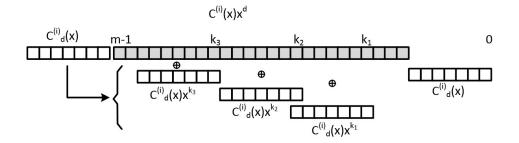

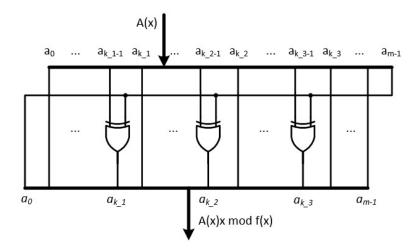

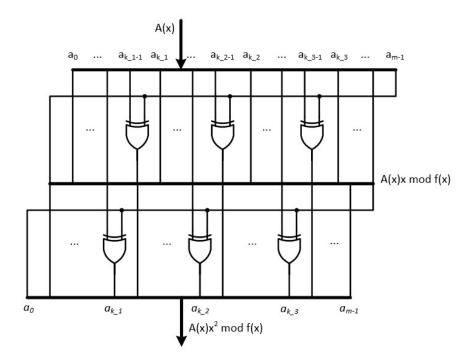

| 4.5  | Implementation of computation $A(x)x^2 \mod f(x) \ldots \ldots \ldots \ldots$         | 28 |

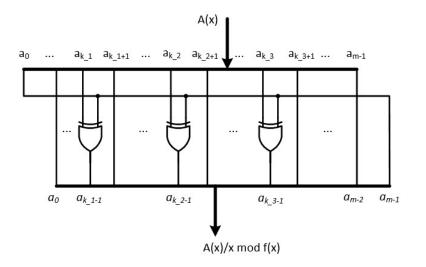

| 4.6  | Model 2: multiply by $x^{-1}$ structure                                               | 29 |

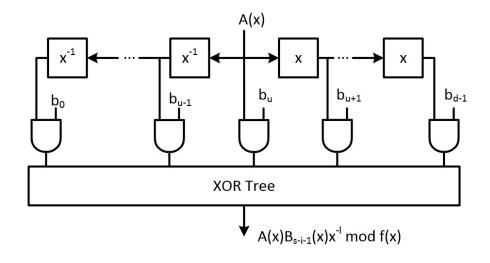

| 4.7  | Implementation of $A(x)B_{s-i-1}(x)x^{-l} \mod f(x) \ldots \ldots \ldots \ldots$      | 30 |

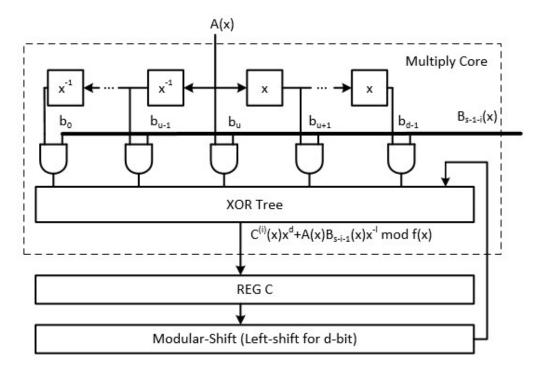

| 4.8  | Advanced architecture of proposed multiplier                                          | 30 |

| 4.9  | General architecture of the proposed digit-serial LSD first multiplier                | 33 |

| 4.10 | LFSR-based architecture of the proposed LSD Montgomery multiplier                     | 37 |

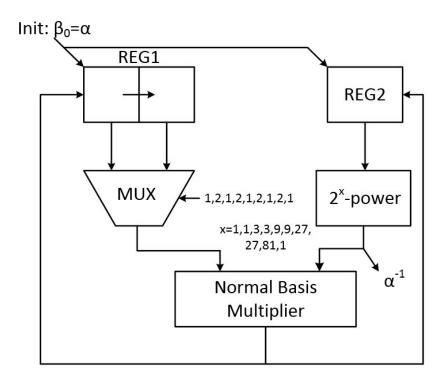

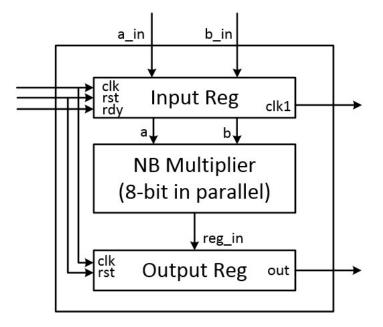

| 5.1  | Architecture of the designed inverse generator                                        | 46 |

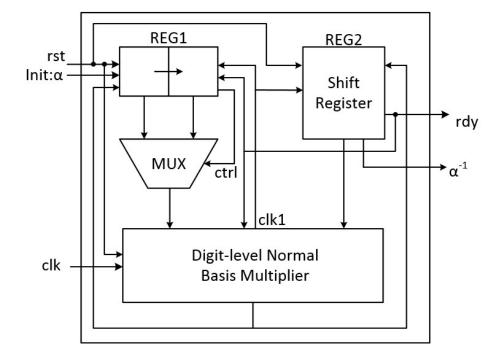

| 5.2  | Block diagram of the inverse generator for FPGA implementation                        | 47 |

| 5.3  | REG1 module                                                                           | 48 |

| 5.4  | REG2 module                                   |

|------|-----------------------------------------------|

| 5.5  | MUX module                                    |

| 5.6  | Digit-level normal basis multiplier module    |

| 5.7  | Digit-level Normal Basis multiplier structure |

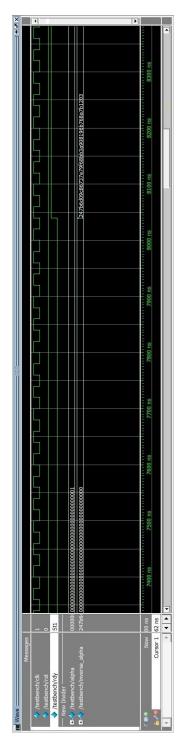

| 5.8  | Simulation result of the Inverse Generator    |

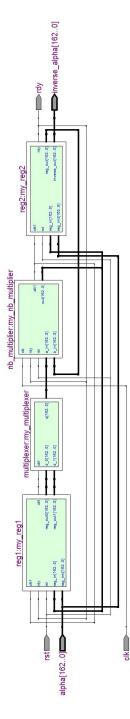

| 5.9  | RTL of the design                             |

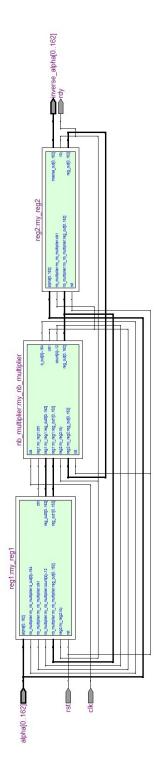

| 5.10 | Technology map viewer of the design           |

### **List of Tables**

| 1.1        | Key size comparison between RSA and ECC with same secure level                                                                                                  | 2        |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.1        | Algorithm of Binary Field Bit-Parallel Montgomery Multiplication                                                                                                | 6        |

| 3.1<br>3.2 | Algorithm of Bit-Serial Montgomery Multiplication                                                                                                               | 14<br>14 |

| 4.1        | Digit-serial MSD-first Montgomery Multiplier $(R(x) = x^l)$ , where $0 \le l \le d-1$                                                                           | 21       |

| 4.2        | Complexity of each block of the proposed MSD-first Montgomery multiplier                                                                                        |          |

| 4.3        | Complexity of proposed digit-serial MSD-first Montgomery multiplication<br>(Algorithm I, general architecture, when $k_{i+1} - k_i \ge d - 1, k_0 = 0, k_4 = m$ |          |

|            | and $0 \leq l \leq d-1$ ).                                                                                                                                      | 26       |

| 4.4        | Complexity of proposed digit-serial MSD-first Montgomery multiplica-<br>tion (Algorithm I, advanced architecture, when $k_{i+1} - k_i \ge max\{l, d - l - 1\}$  | 21       |

| 15         | 1}, $i = 0, 1, 2, 3, k_0 = 0, k_4 = m$ and $0 \le l \le d - 1$                                                                                                  | 31       |

| 4.5<br>4.6 | Digit-serial LSD-first Montgomery Multiplier ( $R(x) = x^{sl}$ ), where $l \ge 0$                                                                               | 32<br>33 |

| 4.0        | Complexity of digit-serial LSD Montgomery multiplication (Algorithm II,                                                                                         | 55       |

| т./        | when $1 \leq l \leq d-1$ and $k_{i+1}-k_i \geq d-1$ , $k_0 = 0$ , $k_4 = m$ )                                                                                   | 34       |

| 4.8        | Complexity of digit-level Montgomery multiplication (Algorithm II, when                                                                                         |          |

|            | $l = d$ , and $k_{i+1} - k_i \ge d - 1$ , $k_0 = 0$ , $k_4 = m$ )                                                                                               | 34       |

| 4.9        | Degree range of each term of equation (4.22)                                                                                                                    | 35       |

| 4.10       | Value of $l$ in terms of XOR gate usage of block S1                                                                                                             | 35       |

| 4.11       | Complexity of digit-level Montgomery multiplication (Algorithm II, when                                         |    |

|------------|-----------------------------------------------------------------------------------------------------------------|----|

|            | $l > d$ , and $k_{i+1} - k_i \ge l$ , $k_0 = 0$ , $k_4 = m$ )                                                   | 36 |

| 4.12       | LFSR-Based Digit-serial LSD-first Montgomery Multiplier $(R(x) = x^{sl})$ ,                                     |    |

|            | where $0 \leq l \leq d-1$                                                                                       | 36 |

| 4.13       | Complexity of digit-level Montgomery multiplication (Algorithm III, when                                        |    |

|            | $0 \leq l \leq d-1$ , and $k_{i+1} - k_i \geq max\{l, d-l-1\}, k_0 = 0, k_4 = m\}$                              | 38 |

| 4.14       | Intrinsic delay of XOR2 and AND2 gate, we assume each gate could drive a                                        |    |

|            | maximum of two gates (25°C, 1.8V, CMOSP18 Tech., $Y = A \cdot B$ , or $Y = A \oplus B$ )                        | 38 |

| 4.15       | Digit-serial Montgomery multipliers comparison $(f(x) = x^m + x^{k_3} + x^{k_2} +$                              |    |

|            | $x^{k_1}+1, s=m/d$                                                                                              | 39 |

| 4.16       | Proposed multipliers compared with Polynomial Basis finite field multipli-                                      |    |

|            | ers (MSD cases, $f(x) = x^m + x^{k_3} + x^{k_2} + x^{k_1} + 1$ , $s = \lceil m/d \rceil$ , $T_{DFF}$ represents |    |

|            | the time delay of a D-flipflop)                                                                                 | 39 |

| 4.17       | Proposed multipliers compared with Polynomial Basis finite field multipli-                                      |    |

|            | ers (LSD cases, $T_M$ represents the time delay of a 2 × 1 Multiplexer, $T_{TFF}$                               |    |

|            | represents the time delay of a T-flipflop)                                                                      | 40 |

| 4.18       | Efficiency of the proposed multipliers and existing Montgomery multipli-                                        |    |

|            | ers $(m = 233, d = 8, \text{ if } l < d, \text{ then } l = 4)$                                                  | 41 |

| 4.19       | Efficiency of the proposed multipliers and existing PB multipliers ( $m =$                                      |    |

|            | 233, $d = 8$ , if $l < d$ , then $l = 4$ )                                                                      | 41 |

| 4.20       | Cells usage of compilation ( $m = 233, d = 8, u = 4$ )                                                          | 42 |

| 4.21       | Gate count of each module $(m = 233, d = 8, u = 4)$                                                             | 42 |

| 4.22       | Time complexity of the design $(m = 233, d = 8, u = 4)$                                                         | 43 |

| 4.23       | Cells usage of compilation $(m = 233, d = 8, l = 4)$                                                            | 43 |

| 4.24       | Gate count of each module $(m = 233, d = 8, l = 4)$                                                             | 43 |

| 4.25       | Time complexity of the design $(m = 233, d = 8, l = 4)$                                                         | 44 |

| 5.1        | Description of Each Clock cycle                                                                                 | 52 |

| 5.2        | Cells usage of compilation                                                                                      | 55 |

| 5.2        | Area cost of each module                                                                                        | 55 |

| 5.5<br>5.4 | Operation delay of the design Inverse Generator over $GF(2^{163})$                                              | 55 |

| 5.4        | operation delay of the design inverse deficitation over $OI(2)$                                                 | 55 |

# **List of Appendices**

| C-code of $F(s)$ and the First Coordinate $c_0$ Generation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 61 |

|----------------------------------------------------------------------------------------------------------------------|----|

| Generated VerilogHDL-code of the First Coordinate $c_0$                                                              | 66 |

## List of Abbreviations/Symbols

| GF   | Finite Field or Galois Field         |

|------|--------------------------------------|

| PB   | Polynomial Basis                     |

| NB   | Normal Basis                         |

| EC   | Elliptic Curve                       |

| ECC  | Elliptic Curve Cryptosystems         |

| RSA  | Rivest, Shamir, Adleman              |

| FPGA | Field Programmable Gate Array        |

| ALUT | Adaptive Look Up Tables              |

| MSD  | Most Significant Digit               |

| LSD  | Least Significant Digit              |

| LE   | Logic Element                        |

| MUX  | Multiplexer                          |

| XOR  | Exclusive OR                         |

| TFF  | T-Flipflop                           |

| DFF  | D-Flipflop                           |

| LFSR | Linear Feedback Shift Register       |

| VLSI | Very Large Scale Integrated Circuits |

### Chapter 1

### Introduction

The development of cryptography can be divided into the following two stages [1]: classical cryptography, and modern cryptography. Classical cryptography was the study of the confidentiality of a message through encryption and decryption. An encryption operation can be described as the conversion of a message or a piece of information from comprehensible text into some incomprehensible form. Transposition cipher [3] and substitution cipher [2] are two representative classical ciphers.

Due to the rapid development of computer and network technologies, and the worldwide application of on-line trading services, mobile phones, and credit cards, the increasing threat to personal privacy and information security is becoming a significant challenge to security engineers. Under this context, cryptography is no longer just a concern for governments, but for civilians as well. Therefore, this field has been expanded far beyond communication confidentiality to include identity authentication, digital signatures, message integrity verification, etc. This extension has led to modern cryptography. Cipher algorithms in modern cryptography are achieved by using a key to encrypt and decrypt information. The Data Encryption Standard (DES) and the Advanced Encryption Standard (AES) are two symmetrical cipher algorithms created in modern cryptography. The encryption and decryption of these algorithms share the same key. The problem is that over time, more users know the key, and the risk of security breaches increases: once the key is revealed by one of the uses, the entire cryptosystem will be on longer secure.

During the 1970s, the public-key cryptosystem, known as the most notable advance in the field of cryptography after World War II, was invented [1]. A public-key system is an

asymmetrical key system that uses a public key to encrypt but decrypts with a private key. The concept of public-key cryptography was first raised in 1976 by Diffie and Hellman [6]; they demonstrated the possibility of network communication when the public key could be widely distributed, while its paired private key remains secret. After that, RSA, which was first published in 1978 by three talented scientists [7], is considered to be the most widely used public-key cryptosystem. To break RSA, a large-number factorization problem must be solved first. Later, elliptic curve cryptosystem (ECC), another public-key system was proposed by Koblitz [8] and Miller [9] during 1985 to 1987. The breaking of an ECC is equivalent to solving discrete logarithm problems. A RSA algorithm with 768-bit key size was broken in 2010 [4], while the hardest ECC scheme broken at present had only a 112-bit key size [5], ECC seems to be superior to RSA. The following table lists the key size in terms of security level with regard to these two public-key cryptosystems.

| RSA(bit) | ECC(bit) | Key Size Comparison |

|----------|----------|---------------------|

| 1024     | 160      | 6:1                 |

| 2048     | 224      | 9:1                 |

| 3072     | 256      | 12:1                |

| 7680     | 384      | 20:1                |

Table 1.1: Key size comparison between RSA and ECC with same secure level

ECC uses a binary field  $GF(2^m)$  or a prime field GF(p). The encryption and decryption speed is an important indicator for evaluating an ECC algorithm. Efficiency of finite field arithmetic operation has great impact on the performance of an ECC, since an ECC computation consists a set of point operations and field multiplication and field inversion are the basic operations involved in the point operation. Due to the fact that field inversion also requires field multiplication during the computation, as a consequence, a large number of studies are mainly aimed at high-speed and efficient implementations of field multiplication.

The binary field  $GF(2^m)$  is widely used in field operations because it is very suitable for VLSI implementation. However, the multiplication is more complicated and timeconsuming. Efficient computation of field multiplication is one of the critical issue of public-key based cipher algorithms. In 1985, Montgomery introduced a new method for integer modular multiplication [10], and proved that the time-consuming trial division operation can be avoided. Later, Koc [12] extended the method to binary field and showed that binary field multiplication can be implemented dramatically faster than standard multiplication. A number of Montgomery multipliers has been designed, and in general, the existing Montgomery multipliers can be divided into two styles: general styles including bit-serial, bit-parallel, and digit-level sub-types; and systolic styles. Bit-serial multipliers have the least gate count but require the longest time to process one operation. In contrast, bit-parallel multipliers have the smallest time delay but require largest implementation area. Digit-level multipliers are available to combine the advantages of both of them and balance the relationship between gate count and critical path delay by processing constant bits each clock cycle.

The works reported in this thesis mainly focus on the efficient computation and hardware implementation of digit-serial Montgomery multiplication. A most-significant-digit first and a least-significant-digit first digit-serial Montgomery multiplier are proposed; two novel fixed elements R(x), which are different from the general ones  $(x^{m-1} \text{ and } x^m)$ , are applied. Two classes of fields for the multipliers with much reduced critical path delay are also proposed. Architectures of the proposed Montgomery multipliers are studied and obtained for the fields generated by the irreducible pentanomials. The complexities of the proposed multipliers in terms of gate count and critical path delay of the architecture are investigated, and demonstrated that the critical path delay of the proposed multipliers can be further reduced by applying the special finite fields. The contributions of this research work also consist of an FPGA implementation of the proposed Montgomery multipliers in the case where m = 233. Furthermore, an FPGA implementation of a normal basis inversion algorithm in  $GF(2^m)$  is also presented in this thesis.

The outline of this thesis is as follows. Chapter 2 presents the mathematical background of the finite field, digit-level Montgomery multiplication, elliptic curve cryptosystem, and some other related equations and concepts. After that, a review of the existing literatures will be presented in Chapter 3. Chapter 4 presents the details of the proposed digit-serial Montgomery multipliers, the comparison results of the proposed Montgomery multipliers in terms of cell usage and critical path delay, the FPGA simulation, and a compilation report of the proposed works. Chapter 5 describes the FPGA implementation of the normal basis inversion generator and provides the results. Finally, in the last chapter, there will be a profound discussion regarding the conclusions and further work.

### Chapter 2

### **Mathematical Preliminaries**

This chapter introduces the relevant mathematical background. The definition of finite field as well as its two general representation methods, the definition of Montgomery multiplication, and the algorithm of elliptic curve cryptosystem (ECC) will be introduced in turn.

#### 2.1 Finite Field and Representations

A finite field (or Galois field) is a group of finitely many elements in which both the addition and the multiplication are defined, also the usual algebraic laws, commutative, associative, and distributive can be applied [14]. The number of elements contained in a finite field is called the order of the field. A finite field can be denoted as GF(q), where q is an positive integer number greater than one. The order of a nonzero element  $A \in GF(q)$  is defined as the smallest positive integer k to make  $A^k = 1$ , and k always divides q - 1. In cryptography, there are two kinds of finite fields that are commonly used: prime field GF(p), where p is prime, and binary extension field  $GF(2^m)$  where m is a positive integer great then or equal to two. The representation of field GF(p) is simply a set of integers modulo p, however, unlike prime field, the binary field has many frequently-used representations. Polynomial basis represent a binary field element.

In a polynomial basis representation, every element in  $GF(2^m)$  is represented by a unique polynomial of degree less than m. For example, element A of  $GF(2^m)$  can be represented as  $A(x) = a_{m-1}x^{m-1} + a_{m-2}x^{m-2} + \cdots + a_1x + a_0 = (a_{m-1}a_{m-2} \dots a_1a_0)$ , and

the coefficient  $a_i$  of each term equals either 0 or 1. The polynomial basis is the set:

$$PB = \{x^{m-1}, x^{m-2}, \dots, x^2, x, 1\}$$

(2.1)

Using polynomial basis to represent elements in binary field  $GF(2^m)$  has been proved to be well suited. By applying such a representation, an addition operation in binary field can be very efficiently implemented by a single XOR gate, and a multiplication operation are defined simply as the product of the corresponding polynomials reduced by modulo f(x). f(x) is an irreducible polynomial which generates the binary field  $GF(2^m)$ , see equation (2.2). If we let only three  $f_i$  equals to one, where 1 < i < m, we could have an irreducible pentanomial  $f(x) = x^m + x^{k_3} + x^{k_2} + x^{k_1} + 1$ , where  $1 < k_1 < k_2 < k_3 < m$ . The works reported in this thesis are focusing on the binary field due to its efficient implementation in both hardware and software.

$$f(x) = x^m + f_{m-1}x^{m-1} + \dots + f_1x + 1 = 0, \text{ where } f_i = 0 \text{ or } 1$$

(2.2)

In normal basis representation, we use the basis set

$$NB = \{\theta^{2^{m-1}}, \theta^{2^{m-2}}, \dots, \theta^2, \theta\}$$

(2.3)

to represent elements in the binary field, and elements  $\theta^{2^i}$ , where  $i \in [0, m - 1]$ , in the basis set must be linearly independent. Using normal basis, a binary field element  $A = (a_{m-1}a_{m-2}...a_1a_0)$  can be represented by equation (2.4):

$$A = a_{m-1}\theta^{2^{m-1}} + a_{m-2}\theta^{2^{m-2}} + \dots + a_1\theta^2 + a_0\theta$$

(2.4)

Normal basis representation has the computational advantage that  $2^x$ -power operations can be implemented very efficiently by a left-shift operation, see equation (2.5). But the multiplication operations are very complicated and time consuming (see [14] Section A.3.8 and Section A.6.4). In that case, a special class of normal bases called Gaussian normal bases are studied in order to minimize the complexity of multiplication.

$$A^{2^{2}} = (A^{2})^{2} = (a_{m-1}\theta^{2^{(m-mod\,m)}} + a_{m-2}\theta^{2^{m-1}} + \dots + a_{1}\theta^{2^{2}} + a_{0}\theta^{2^{1}})^{2}$$

=  $a_{m-3}\theta^{2^{m-1}} + a_{m-4}\theta^{2^{m-2}} + \dots + a_{0}\theta^{2^{2}} + a_{m-1}\theta^{2} + a_{m-2}\theta$  (2.5)

#### **2.2** Montgomery Multiplication over $GF(2^m)$

Montgomery multiplication was first proposed by Montgomery in 1985 [10] and was extended to binary field by Koc in 1998 [12]. Compared with the standard multiplication, the Montgomery multiplication can avoid trail division operations whereas standard modular multiplication cannot.

Montgomery multiplication in  $GF(2^m)$  is defined by equation (2.6).

$$C(x) = A(x) \times B(x) \times R(x)^{-1} \mod f(x)$$

(2.6)

| Table 2.1: Algorithm of Binary Field Bit-Parallel Montgomery Multiplicatio | Table 2.1: Algorithm of | <b>Binary Field Bit</b> | -Parallel Montgom | erv Multiplication |

|----------------------------------------------------------------------------|-------------------------|-------------------------|-------------------|--------------------|

|----------------------------------------------------------------------------|-------------------------|-------------------------|-------------------|--------------------|

Algorithm Binary Field Bit-Parallel Montgomery Multiplication

| •        | •                                       | •               | - |  |

|----------|-----------------------------------------|-----------------|---|--|

| Inputs:  | $A(x), B(x) \in GF(2^m), f(x)$          | ), f'(x)        |   |  |

| Outputs: | $C(x) = A(x) \times B(x) \times R^{-1}$ | (x) $\mod f(x)$ | ) |  |

| Step 1:  | T(x) = A(x)B(x)                         |                 |   |  |