#### 2008 Solar Annual Review Meeting

**Session: Process Development and Integration Lab (PDIL)**

Organization: National Renewable Energy Laboratory

**Funding Opportunity: PDIL Capital Equipment**

## Wafer Replacement Cluster Tool

Howard M. Branz National Renewable Energy Laboratory Golden, CO 80401 howard\_branz@nrel.gov

NREL/PR-520-43195

Presented at the Solar Energy Technologies Program (SETP) Annual Program Review Meeting held April 22-24, 2008 in Austin, Texas

## Wafer Replacement Cluster Tool

- Platform for advanced R&D toward SAI 2015 Cost Goal

- Crystal silicon PV at area costs closer to amorphous Si PV

- 15% efficiency

- Inexpensive substrate

- Moderate temperature processing (<800°C)</li>

- Why silicon?

- Industrial and knowledge base

- Abundant and environmentally benign

- Market acceptance

- Good efficiency

- Why replace wafers?

- Expensive

- High embedded energy content

- Use 50-100 times more silicon than needed

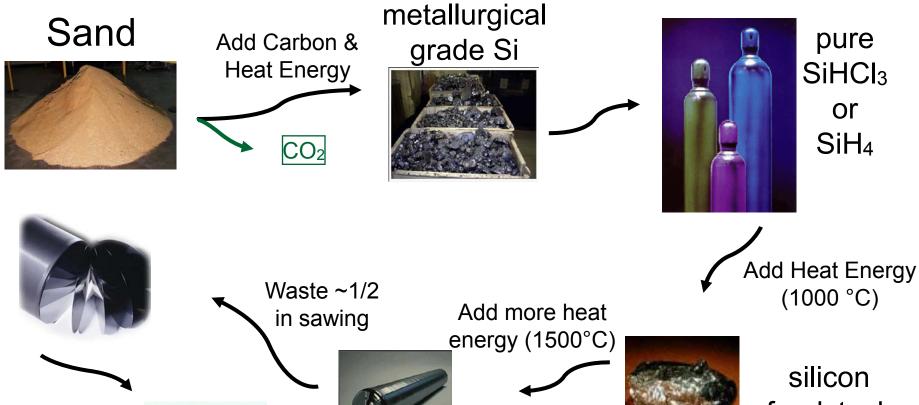

## **Energy and Si-intensive wafers**

## **Current process:**

- 2 yr energy payback

- \$0.60/W \$1.00/W for feedstock alone

Use 10X more than needed

feedstock

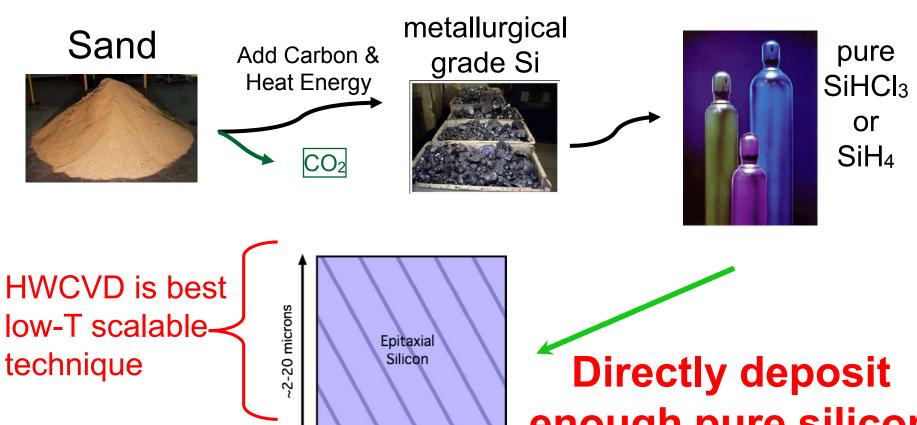

## Vision for wafer replacement Si

## Film Si growth:

Seed Layer

**Glass Substrate**

Directly deposit enough pure silicon for light absorption

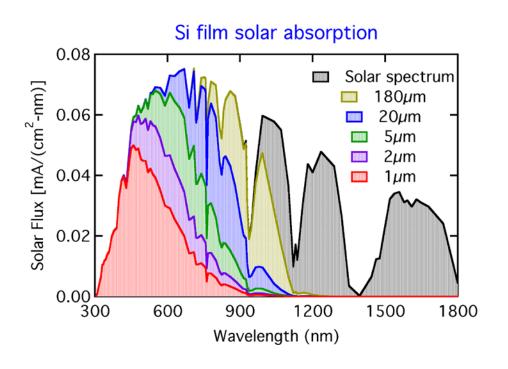

## Thick wafers not needed for c-Si PV

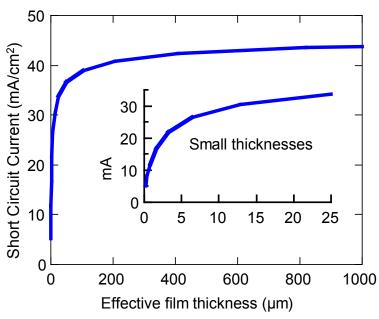

#### Potential Current vs effective thickness

- Most current available at 20 μm effective thickness

- Over 30 mA attainable for 5-μm silicon with 5X light trapping

- absorbs like 25 μm silicon layer

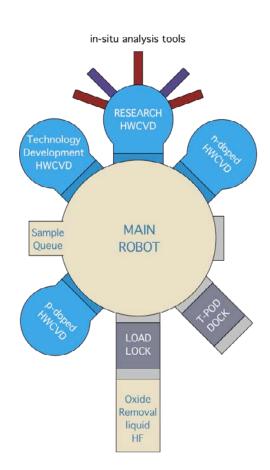

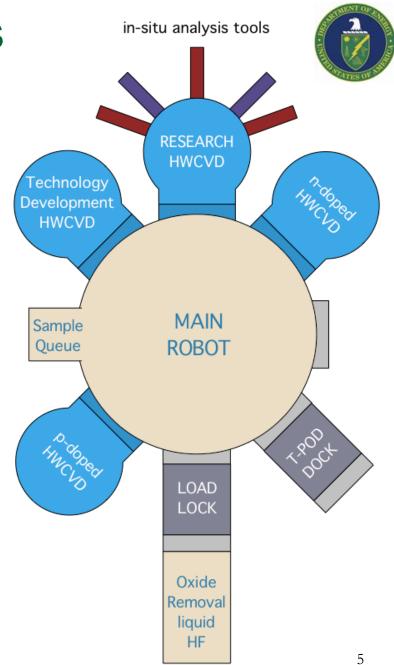

# Tool and its capabilities

- Substrate to 800°C

- 156-mm samples queue in vacuum

- Automated liquid-based oxide removal

- key last-minute step

- Doping control in separate chambers

- n-type

- p-type

- Research HWCVD

- 10⁻¹ Torr vacuum, low impurity

- RTSE, RHEED, pyrometer, RGA

- Technology development HWCVD

- Develop new filament and heater designs

- Load Lock

- Vacuum Transfer Pod to other PDIL Tools

- Spare port for alternatives and collaborations

#### Tool Alignment with Film c-Si Technology Roadmap

#### Roadmap

#### Wafer Replacement Tool

| Need                                                                                                                                                  | Significance                                                                    |                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Develop inexpensive large-grain<br>or single-crystal, high-quality<br>c-Si film growth processes and<br>materials for use with low-cost<br>substrates | Higher efficiency than<br>amorphous, but lower cost<br>than wafer-based silicon | Scalable hot-wire (HWCVD) epitaxy  – 300 nm/min, 10 µm, with low dislocations  – Epitaxy on all orientations |

| Develop seeding techniques for<br>high-quality epitaxial c-Si film<br>formation on low-cost substrates                                                | Increased efficiency                                                            | Will enable us to evaluate seed layers                                                                       |

| Develop light-management<br>strategies for weakly absorbing<br>c-Si films                                                                             | Increased efficiency                                                            | Will enable us to develop light-trapping at 6-inch scale                                                     |

| Develop inexpensive, high-<br>temperature (>600°C) substrates<br>for c-Si films                                                                       | Reduced cost                                                                    | Will enable us to evaluate new substrates                                                                    |

| Develop inexpensive, reduced-<br>temperature processing for c-Si<br>films                                                                             | Reduced cost                                                                    | Glass-compatible temperatures 600 - 700°C                                                                    |

| Develop low-temperature<br>passivation techniques for film-<br>Si surfaces, interfaces, and grain<br>boundaries                                       | Increased efficiency                                                            | Hot-wire hydrogenation possible, if needed                                                                   |

| Develop, automate, and scale up<br>deposition equipment for c-Si<br>film fabrication                                                                  | Reduced cost and increased yield                                                | Technology development chamber and in-situ diagnostics                                                       |

## Status and schedule

- Conceptual design (chambers) complete

- based on new test epitaxy chamber (1")

- Detailed design work continuing

- Statement of work for RFQ in preparation

- Bids and vendor selection in FY08

- Delivery of robot and key chambers in FY09

## Partnerships anticipated

- Seed layer candidates

- semiconductor equipment companies

- display companies

- glass companies

- start-ups

- NREL R&D

- university and national labs

- PV ventures testing low-T epitaxy step

- Equipment vendors

- chamber to test HWCVD innovations

#### **NREL Contacts**

Chaz Teplin

charles\_teplin@nrel.gov 303-384-6440

**Paul Stradins**

pauls\_stradins@nrel.gov 303-384-6774

**Howard Branz**

howard\_branz@nrel.gov 303-384-6694

## **CIGS Platform**

## Miguel Contreras

|             | PV Technology Road Maps |         |     |      |                    |     |      |  |

|-------------|-------------------------|---------|-----|------|--------------------|-----|------|--|

|             | Wafer Si                | Film Si | CPV | CdTe | CIGS               | OPV | DSPV |  |

| Platform    | Š                       | 団       | 5   | Ö    | $\overline{\circ}$ | Ö   | Dê   |  |

| Thin Si     |                         |         |     |      | i                  |     |      |  |

| Wafer Rep.  |                         |         |     |      |                    |     |      |  |

| CIGS        |                         |         |     |      |                    |     |      |  |

| CdTe        |                         |         |     |      |                    |     |      |  |

| Atm. Proc.  |                         |         |     |      |                    |     |      |  |

| M&C Ind.    |                         |         |     |      |                    |     |      |  |

| M&C Cluster |                         |         |     |      |                    |     |      |  |