U.S. Department of Energy FreedomCAR and Vehicle Technologies, EE-2G 1000 Independence Avenue, S.W. Washington, D.C. 20585-0121

FY 2008

# INVESTIGATIONS INTO HIGH TEMPERATURE COMPONENTS AND PACKAGING

Prepared by:

Oak Ridge National Laboratory

Mitch Olszewski, Program Manager

### Submitted to:

Energy Efficiency and Renewable Energy FreedomCAR and Vehicle Technologies Vehicle Systems Team

Susan A. Rogers, Technology Development Manager

December 2007

FOR THE DEPARTMENT OF ENERGY

## **Engineering Science and Technology Division**

# Investigations into High Temperature Components and Packaging

L. D. Marlino

L. E. Seiber

M. B. Scudiere

M. S. Chinthavali

Oak Ridge National Laboratory

F. Patrick McCluskey University of Maryland

Publication Date: December 2007

Prepared by the

OAK RIDGE NATIONAL LABORATORY

Oak Ridge, Tennessee 37831

managed by

UT-BATTELLE, LLC

for the

U.S. DEPARTMENT OF ENERGY

Under contract DE-AC05-00OR22725

#### **DOCUMENT AVAILABILITY**

Reports produced after January 1, 1996, are generally available free via the U.S. Department of Energy (DOE) Information Bridge:

Web site: http://www.osti.gov/bridge

Reports produced before January 1, 1996, may be purchased by members of the public from the following source:

National Technical Information Service

5285 Port Royal Road Springfield, VA 22161

Telephone: 703-605-6000 (1-800-553-6847)

**TDD**: 703-487-4639 **Fax**: 703-605-6900

E-mail: info@ntis.fedworld.gov

Web site: http://www.ntis.gov/support/ordernowabout.htm

Reports are available to DOE employees, DOE contractors, Energy Technology Data Exchange (ETDE) representatives, and International Nuclear Information System (INIS) representatives from the following source:

Office of Scientific and Technical Information

P.O. Box 62

Oak Ridge, TN 37831 *Telephone:* 865-576-8401 *Fax:* 865-576-5728 *E-mail:* reports@osti.gov

Web site: http://www.osti.gov/contact.html

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

## **CONTENTS**

|    |                                                             | Page                  |

|----|-------------------------------------------------------------|-----------------------|

| LI | ST OF FIGURES                                               | iv                    |

| LI | ST OF TABLES                                                | vi                    |

| Α( | CRONYMS                                                     | vii                   |

| 1. | INTRODUCTION                                                | . 1                   |

| 2. | CAPACITOR TESTING                                           | . 2                   |

|    | 2.1 MURATA 25 μF CAPACITOR TESTS                            |                       |

|    | 2.1.1 Static Murata Tests                                   |                       |

|    | 2.1.2 Dynamic Murata Tests                                  |                       |

|    | 2.2 SBE 580 µF CAPACITOR TESTS                              |                       |

|    | 2.2.1 Static SBE Tests                                      |                       |

|    | 2.2.2 Dynamic SBE Tests                                     | . 15                  |

| _  | DUED JE ON THE ENGLIS ASSOCIATION THE MEDIA TO THE LOCATION | 10                    |

| 3. |                                                             |                       |

|    | 3.1 EXPERIMENTAL SETUP                                      |                       |

|    | 3.2 TEST PROCEDURE                                          |                       |

|    | 3.3 RESULTS                                                 |                       |

|    | 3.4 CONTINUOUS DC CURRENT TEST                              |                       |

|    | 5.5 CONCLUSION                                              | <i>2</i> <del>4</del> |

| 4  | OPAL-RT TEST SETUP                                          | . 25                  |

| •• | 4.1 DEVELOPMENT PROCESS                                     |                       |

|    | 4.2 TEST PROCEDURE                                          |                       |

|    | 4.3 CALIBRATION OF EQUIPMENT                                |                       |

|    | · · · · · · · · · · · · · · · · · · ·                       |                       |

| 5. | SiC DEVICE TESTING                                          | . 28                  |

| 6. | RELIABILITY OF POWER ELECTRONICS PACKAGING TECHNIQUES       | . 29                  |

| 7  | CONCLUSIONS                                                 | 30                    |

|    |                                                             |                       |

| Αŀ | PPENDIX A: WIDE-BANDGAP MATERIALS                           |                       |

|    | A.1 TASKS                                                   | . 31                  |

|    | A.2 APPROACH                                                |                       |

|    | A.3 MAJOR ACCOMPLISHMENTS                                   |                       |

|    | A.3.1 Technical Discussions                                 |                       |

|    | A.3.1.1 Device testing                                      |                       |

|    | A.3.1.1.1 SiC Schottky diode                                |                       |

|    | A.3.1.1.2 <i>SiC MOSFET</i>                                 |                       |

|    | A.3.1.1.3 <i>SiC JFET</i>                                   |                       |

|    | A.3.1.1.4 High temperature Si IGBT                          |                       |

|    | A.3.1.2 Fault current limiting tests of SiC JFETs           |                       |

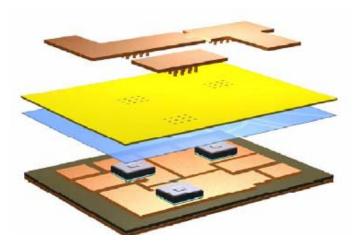

|    | A.3.1.3 Hybrid packaging                                    | 41                    |

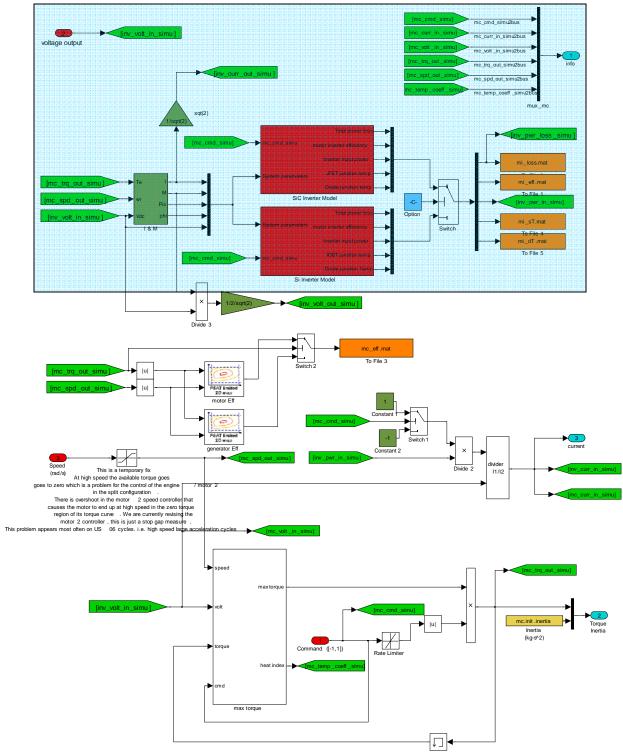

|    | A.3.1.4 PSAT traction drive model for a PHEV                | 43                    |

## **CONTENTS** (cont'd)

|                                                                               | Page |

|-------------------------------------------------------------------------------|------|

| A.4 CONCLUSION                                                                | 44   |

| A.5 FUTURE DIRECTION                                                          | 45   |

| A.6 PUBLICATIONS                                                              | 45   |

| A.7 REFERENCES                                                                | 45   |

| APPENDIX B                                                                    |      |

| ORNL/TM-2007/046, Power Module Investigation for High Temperature (175–200°C) |      |

| Automotive Application                                                        | 46   |

### LIST OF FIGURES

| 2.1 ESPEC environment chamber  2.2 Current amplifier rack  2.3 Instrumentation for the capacitor tests  2.4 Murata 25 μF, 630 Vdc ceramic capacitor  2.5 Murata 25 μF ceramic capacitor ESR frequency response  2.6 Murata 25μF capacitor—ESR vs. temperature from 0–180°C  2.7 Murata 25 μF ceramic capacitor frequency response  2.8 (a) Murata 25μF capacitor—capacitance vs. temperature, and  (b) Murata 25μF capacitor—capacitance vs. temperature  2.9 Murata 25 μF ceramic capacitor DF vs. frequency  2.10 Murata 25μF capacitor—DF vs. temperature  2.11 Murata 25 μF ripple current at multiple frequencies  | Page |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| <ul> <li>Instrumentation for the capacitor tests</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3    |

| <ul> <li>Instrumentation for the capacitor tests</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

| <ul> <li>Murata 25 μF, 630 Vdc ceramic capacitor</li> <li>Murata 25 μF ceramic capacitor ESR frequency response</li> <li>Murata 25 μF capacitor—ESR vs. temperature from 0–180°C</li> <li>Murata 25 μF ceramic capacitor frequency response</li> <li>(a) Murata 25 μF capacitor—capacitance vs. temperature, and</li> <li>(b) Murata 25 μF capacitor—capacitance vs. temperature</li> <li>Murata 25 μF ceramic capacitor DF vs. frequency</li> <li>Murata 25 μF capacitor—DF vs. temperature</li> <li>Murata 25 μF capacitor—DF vs. temperature</li> <li>Murata 25 μF ripple current at multiple frequencies</li> </ul> |      |

| <ul> <li>2.5 Murata 25 μF ceramic capacitor ESR frequency response</li> <li>2.6 Murata 25μF capacitor—ESR vs. temperature from 0–180°C</li> <li>2.7 Murata 25 μF ceramic capacitor frequency response</li> <li>2.8 (a) Murata 25μF capacitor—capacitance vs. temperature, and</li> <li>(b) Murata 25μF capacitor—capacitance vs. temperature</li> <li>2.9 Murata 25 μF ceramic capacitor DF vs. frequency</li> <li>2.10 Murata 25μF capacitor—DF vs. temperature</li> <li>2.11 Murata 25 μF ripple current at multiple frequencies</li> </ul>                                                                           |      |

| <ul> <li>Murata 25 μF capacitor—ESR vs. temperature from 0–180°C</li> <li>Murata 25 μF ceramic capacitor frequency response</li> <li>(a) Murata 25 μF capacitor—capacitance vs. temperature, and</li> <li>(b) Murata 25 μF capacitor—capacitance vs. temperature</li> <li>Murata 25 μF ceramic capacitor DF vs. frequency</li> <li>Murata 25 μF capacitor—DF vs. temperature</li> <li>Murata 25 μF ripple current at multiple frequencies</li> </ul>                                                                                                                                                                    |      |

| <ul> <li>2.7 Murata 25 μF ceramic capacitor frequency response</li> <li>2.8 (a) Murata 25μF capacitor—capacitance vs. temperature, and</li> <li>(b) Murata 25μF capacitor—capacitance vs. temperature</li> <li>2.9 Murata 25 μF ceramic capacitor DF vs. frequency</li> <li>2.10 Murata 25μF capacitor—DF vs. temperature</li> <li>2.11 Murata 25 μF ripple current at multiple frequencies</li> </ul>                                                                                                                                                                                                                  |      |

| <ul> <li>(a) Murata 25μF capacitor—capacitance vs. temperature, and</li> <li>(b) Murata 25μF capacitor—capacitance vs. temperature</li> <li>2.9 Murata 25 μF ceramic capacitor DF vs. frequency</li> <li>2.10 Murata 25μF capacitor—DF vs. temperature</li> <li>2.11 Murata 25 μF ripple current at multiple frequencies</li> </ul>                                                                                                                                                                                                                                                                                     |      |

| <ul> <li>2.9 Murata 25 μF ceramic capacitor DF vs. frequency.</li> <li>2.10 Murata 25 μF capacitor—DF vs. temperature.</li> <li>2.11 Murata 25 μF ripple current at multiple frequencies.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| <ul> <li>2.9 Murata 25 μF ceramic capacitor DF vs. frequency.</li> <li>2.10 Murata 25 μF capacitor—DF vs. temperature.</li> <li>2.11 Murata 25 μF ripple current at multiple frequencies.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                    | 7    |

| 2.11 Murata 25 μF ripple current at multiple frequencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 1 11 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9    |

| 2.12 SBE 580 μF 100 Vdc film capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10   |

| 2.13 SBE 580 $\mu$ F 100 Vdc film capacitor with test fixture and thermocouples attached.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 11   |

| 2.14 SBE 580 μF film capacitor ESR frequency response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11   |

| 2.15 SBE 580 μF film capacitor ESR temperature response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

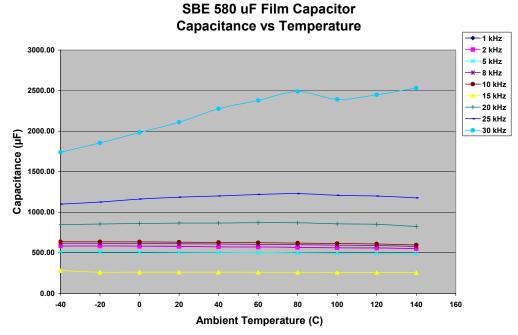

| 2.16 SBE 580 μF film capacitor frequency response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13   |

| 2.17 SBE 580 μF film capacitor temperature response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 13   |

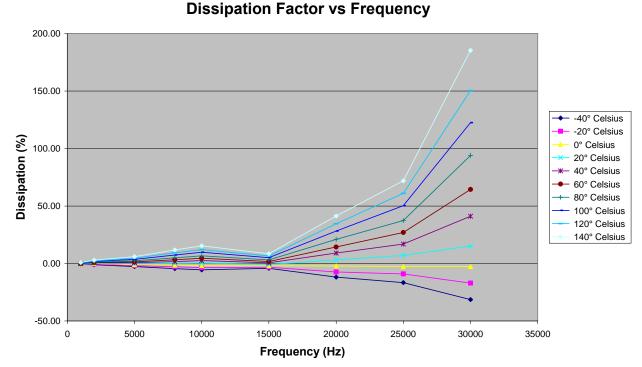

| 2.18 SBE 580 μF capacitor DF frequency response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 14   |

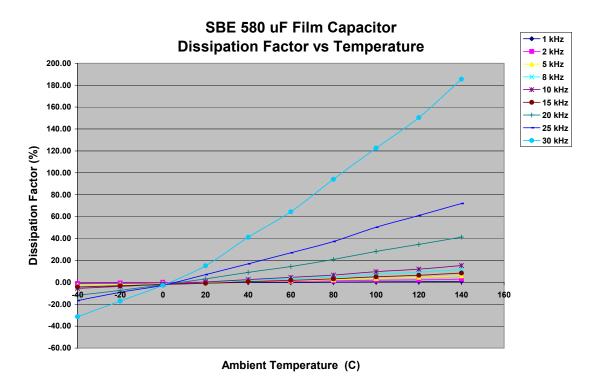

| 2.19 SBE 580 μF film capacitor DF temperature response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15   |

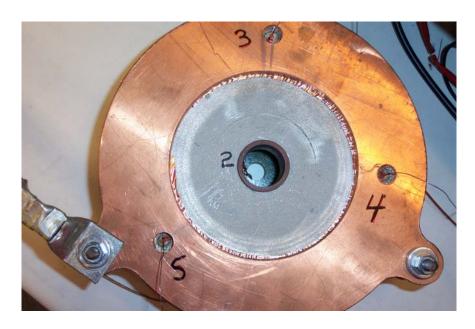

| 2.20 SBE 580 µF capacitor thermocouple layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 16   |

| 2.21 SBE 580 μF film capacitor test fixture inside environmental chamber                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16   |

| SBE 580 μF film capacitor ripple current vs. temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 3.1 Layout of the Infineon IGBT module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

| 3.2 Schematic of the circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 18   |

| 3.3 (a) Test setup, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 19   |

| (b) Test setup (closer view)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| 3.4 (a) Current for 250V, 16A operation; and (b) Voltage for 250V, 16A operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| 3.5 (a) Current for 250V, 23A operation; and (b) Voltage for 250V, 16A operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22   |

| 3.6 (a) Current for 250V, 200°C junction temperature operation; and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

| (b) Voltage for 250V, 200°C junction temperature operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

| 3.7 Device failure at 250V, 16A, 200°C junction temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

| A.1 Forward characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

| A.2 Reverse characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

| A.3 Leakage current of a SiC Schottky diode at different temperatures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| A.4 Reverse recovery test circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 34   |

| A.5 Reverse recovery current waveforms of the SiC Schottky diode at different temperatures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 34   |

| A.6 Switching energy losses of a SiC diode at different temperatures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

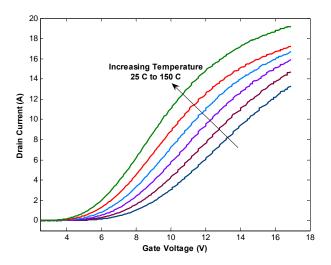

| A.7 I-V curves of SiC MOSFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| A.8 On-resistance of SiC MOSFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

| A.9 Transfer characteristics of SiC MOSFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

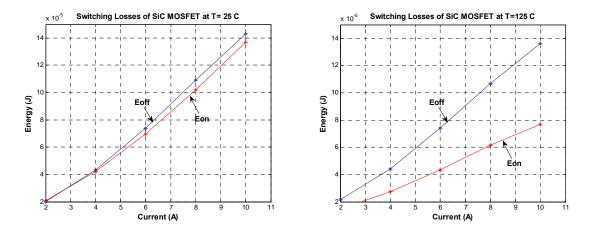

| A.10 Switching energy losses of SiC MOSFET for different currents and temperatures.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

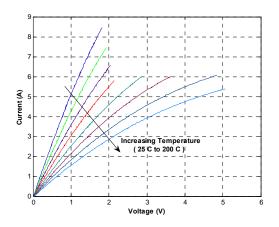

| A.11 I-V curves of a SiC JFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

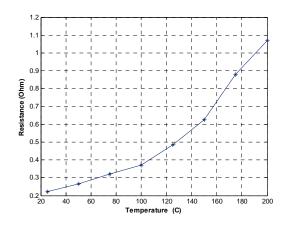

| A.12 On-resistance of a SiC JFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

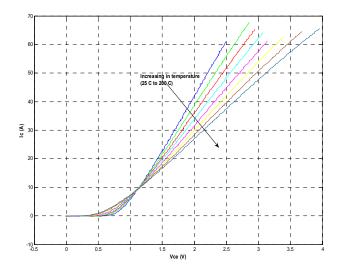

| A.13 I-V characteristics of IGBT at different temperatures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

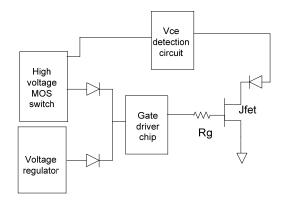

| A.14 Schematic of the circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

### LIST OF FIGURES

| Figure |                                                                              | Page |

|--------|------------------------------------------------------------------------------|------|

| A.15   | Test setup                                                                   | 38   |

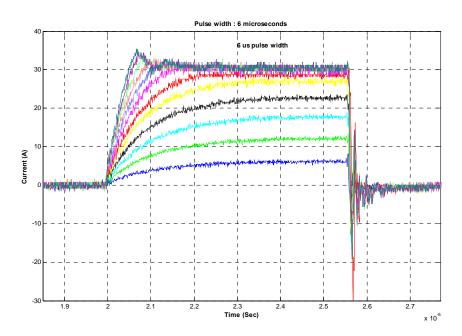

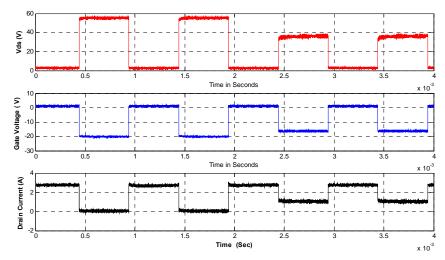

| A.16   | Short circuit pulse test waveforms of a SiC JFET                             | 39   |

| A.17   | Temperature response profile of a SiC JFET                                   | 40   |

| A.18   | Schematic of the protection circuit for fault protection                     | 40   |

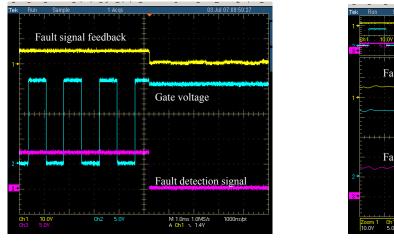

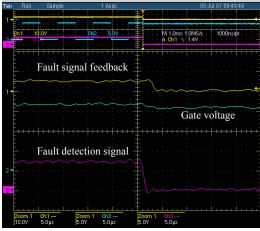

| A.19   | Test results of the protection circuit: (a) Normal view, and (b) Zoomed view | 41   |

| A.20   | Gate voltage, drain voltage, and drain current waveforms of a SiC JFET       | 41   |

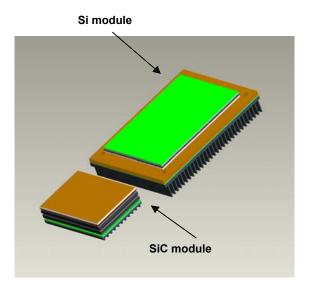

| A.21   | Comparison of sizes between Hybrid package and Si IPM                        | 42   |

| A.22   | New motor controller model                                                   |      |

### LIST OF TABLES

| Table       |                                                                          | Page |

|-------------|--------------------------------------------------------------------------|------|

| 4.1         | Equipment list that was calibrated to support ORNL high temperature test |      |

|             | efforts in FY07                                                          | 27   |

| <b>A</b> .1 | Power diodes                                                             | 32   |

| A.2         | Power switches                                                           | 32   |

### **ACRONYMS**

Α ampere **CALCE** Center for Advanced Life Cycle Engineering data acquisition system DAQ dc direct current dissipation factor DF **DUT** device under test **ESR** effective series resistance FC fuel cell hybrid-electric vehicle **HEV** IC internal combustion insulated gate bipolar transistor **IGBT** intelligent power module **IPM JFET** junction field-effect transistor LCR inductance, capacitance, and resistance metal oxide semiconductor field-effect transistor **MOSFET NETL** National Energy Technology Laboratory **ORNL** Oak Ridge National Laboratory **PEEMRC** Power Electronics and Electric Machinery Research Center **PHEV** plug-in hybrid-electric vehicle rpm revolutions per minute real-time operating system **RTOS** Si silicon SiC silicon carbide SOI silicon on insulator **UDDS Urban Driving Scheme** wide-bandgap **WBG**

This report documents activity in support of high temperature power electronics.

### 1.0 INTRODUCTION

The purpose of this report is to document the work that was performed at the Oak Ridge National Laboratory (ORNL) in support of the development of high temperature power electronics and components with monies remaining from the Semikron High Temperature Inverter Project managed by the National Energy Technology Laboratory (NETL).

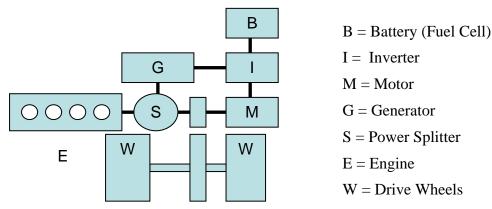

High temperature electronic components are needed to allow inverters to operate in more extreme operating conditions as required in advanced traction drive applications. The trend to try to eliminate secondary cooling loops and utilize the internal combustion (IC) cooling system, which operates with approximately 105°C water/ethylene glycol coolant at the output of the radiator, is necessary to further reduce vehicle costs and weight. The activity documented in this report includes development and testing of high temperature components, activities in support of high temperature testing, an assessment of several component packaging methods, and how elevated operating temperatures would impact their reliability.

This report is organized with testing of new high temperature capacitors in Section 2 and testing of new 150°C junction temperature trench insulated gate bipolar transistor (IGBTs) in Section 3. Section 4 addresses some operational OPAL-GT information, which was necessary for developing module level tests. Section 5 summarizes calibration of equipment needed for the high temperature testing. Section 6 details some additional work that was funded on silicon carbide (SiC) device testing for high temperature use, and Section 7 is the complete text of a report funded from this effort summarizing packaging methods and their reliability issues for use in high temperature power electronics.

Components were tested to evaluate the performance characteristics of the component at different operating temperatures. The temperature of the component is determined by the ambient temperature (i.e., temperature surrounding the device) plus the temperature increase inside the device due the internal heat that is generated due to conduction and switching losses. Capacitors and high current switches that are reliable and meet performance specifications over an increased temperature range are necessary to realize electronics needed for hybrid-electric vehicles (HEVs), fuel cell (FC) and plug-in HEVs (PHEVs). In addition to individual component level testing, it is necessary to evaluate and perform long term module level testing to ascertain the effects of high temperature operation on power electronics.

#### 2.0 CAPACITOR TESTING

A test sequence has been developed to test the performance capability of advanced capacitors for potential use in transportation related applications. An ESPEC environmental chamber is utilized to produce a controlled ambient temperature so that capacitor performance can be determined at various ambient temperatures. For these tests, the temperature in the environmental chamber was cycled over its temperature range in steps of 20°C. The environmental chamber has the capability to control the ambient temperature from -70–180°C.

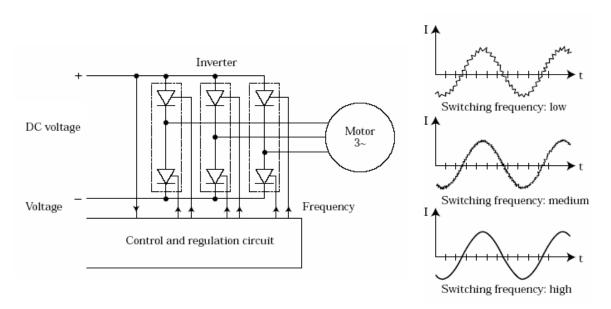

Capacitors are tested in two modes: static and dynamic. Static mode tests are performed without power being applied to the device under test (DUT) so the temperature of the device is determined solely by the ambient conditions. Effective series resistance (ESR), dissipation factor (DF), and capacitance are measured during static mode tests. The dynamic mode test requires a direct current (dc) bias voltage and ripple current to be applied to the DUT. The maximum ripple current at different ambient temperatures is determined during the dynamic mode test. DC bus capacitors used in inverters require high ripple current capability to protect the battery and insure its reliability and longevity.

Capacitor testing in the static mode requires a thermal cycling process that must continue uninterrupted for extended periods of time. To accomplish this long term testing, an automated data acquisition system (DAQ) using a LABView interface was developed to control an environmental chamber and log data from an Agilent 4284 inductance, capacitance, and resistance (LCR) meter. This system allows the operator to specify upper and lower temperature limits as well as temperature steps to be used during the evaluation. The program commands a target temperature to the environmental chamber and when that temperature has been reached, it monitors a capacitor parameter until stable. The program then logs the capacitor data from the LCR meter at predefined test frequencies before another temperature step is commanded.

Capacitor testing in the dynamic mode is accomplished in these tests by manually commanding a temperature to the environmental chamber and allowing the capacitor temperature to stabilize at that temperature before applying a ripple current. Thermocouples are attached to the capacitor during the dynamic test allowing the temperature of the capacitor to be monitored. After the temperature has stabilized, a ripple current is applied and the capacitor temperature is recorded. The ripple current is increased and the process is repeated. Ripple current values are determined by the size and type of capacitor being tested.

Testing was performed on new Murata ceramic capacitors and SBE "Power Ring" film capacitors using the ESPEC environmental test chamber in both the static and dynamic test modes. The SBE film capacitors are configured in a new geometry that shortens the resistive path from the terminals resulting in lower ESR. The reduction in the ESR leads to reduced heating within the capacitor and enables them to be operated at higher temperatures.

Figure 2.1 shows the ESPEC test chamber that was used during the tests. There is an access port on the left side of the chamber for instrumentation and power cables. The amplifier rack utilized is shown in Fig. 2.2. Additional instrumentation used during the capacitors tests is shown in Fig. 2.3.

Fig. 2.1. ESPEC environment chamber.

Fig. 2.2. Current amplifier rack.

Fig. 2.3. Instrumentation for the capacitor tests.

### 2.1 MURATA 25 $\mu$ F CAPACITOR TESTS

### 2.1.1 Static Murata Tests

Static testing was performed on a Murata 25  $\mu$ F 630 Vdc ceramic capacitor, shown in Fig. 2.4. The pins were removed and leads attached to allow attachment to the current source. A thermocouple was also adhered to the surface of the capacitor.

Fig. 2.4. Murata 25 μF 630 Vdc ceramic capacitor.

The Murata ceramic capacitor was tested in the static mode from 0–180°C over a frequency range of 1–40 kHz.

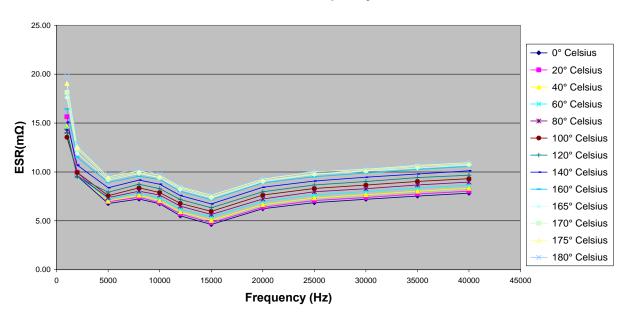

The graph in Fig. 2.5 shows ESR versus frequency for each temperature step.

### Murata 25 μF 630 V Capacitor ESR vs Frequency

Fig. 2.5. Murata 25 µF ceramic capacitor ESR frequency response.

ESR is the sum of the in-phase ac resistances. For a given frequency, ESR increases with increasing temperatures. ESR acts like a resistor in series with a capacitor. The higher the ESR, the higher the losses in the capacitor and the more power is dissipated. If the power dissipation is too high, the capacitor heats up to a point that values change (causing drift in operation) or the capacitor fails.

During these tests, the ESR decreased 53% from 1–5 kHz at 0°C. At 180°C, the ESR decreased 51% from 1–5 kHz. The ESR increased 15% from 5–40 kHz at 0°C. At 180°C, the ESR increased 14% from 5–40 kHz.

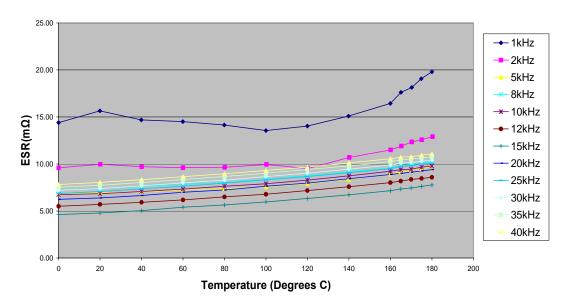

Figure 2.6 shows the same information graphed with ESR versus temperature, illustrating fairly stable performance over temperature at a given frequency.

# Murata 25 μF 630 V Capacitor ESR vs Temperature

Fig. 2.6. Murata 25μF capacitor—ESR vs. temperature from 0–180°C.

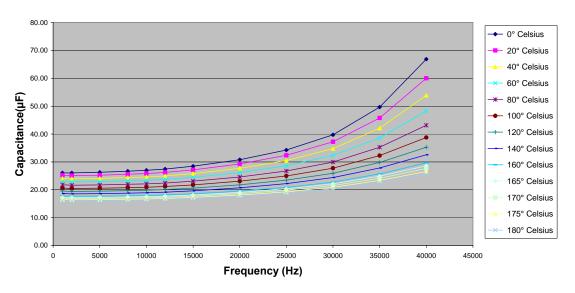

Figure 2.7 shows the capacitance variation over the frequency range of 1–40 kHz at each temperature step.

### Murata 25 μF 630 V Capacitor Capacitance vs Frequency

Fig. 2.7. Murata 25 μF ceramic capacitor frequency response

The capacitance increased 157% from 1–40 kHz at 0°C. Above 15 kHz the increase was 147%. Between 1–15 kHz, the capacitance value increased only 10% at 0°C. At 180°C, the capacitance increased 60% from 1–40 kHz. Above 15 kHz, the increase in capacitance was 51% at 180°C. Between 1–15 kHz, the capacitance increased by 9% at 180°C.

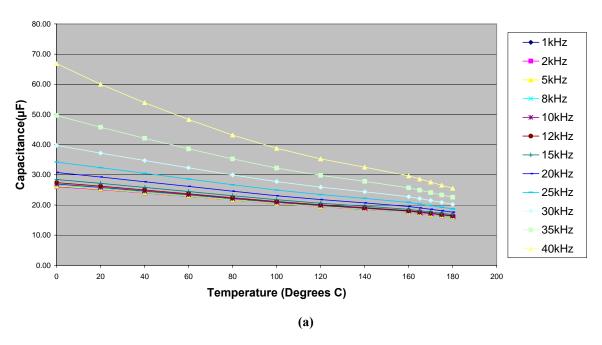

Figure 2.8 graphs the capacitance variation over temperature at different frequencies.

# Murata 25 μF 630 V Capacitor Capacitance vs Temperature

# Murata Capacitor Capacitance vs Temperature

Fig. 2.8. (a) Murata 25 μF capacitor—capacitance vs. temperature, and (b) Murata 25 μF capacitor—capacitance vs. temperature.

Changing the y-axis scaling and selecting a few frequencies of interest, it can be seen from Fig. 2.8(b) that a significant decrease in capacitance occurs over temperature from 0–180°C.

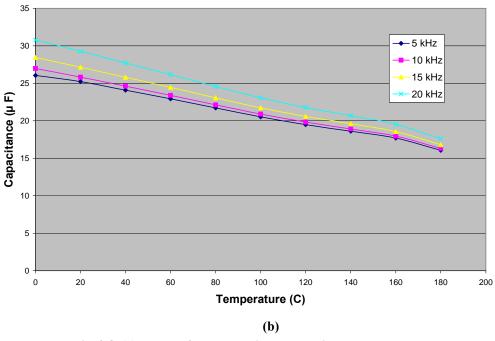

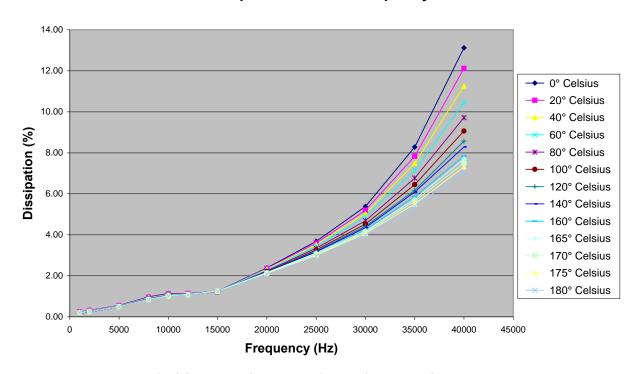

Figure 2.9 shows the DF over the frequency range of 1–40 kHz at each temperature step.

# Murata 25 μF 630 V Capacitor Dissipation Factor vs Frequency

Fig. 2.9. Murata 25 μF ceramic capacitor DF vs. frequency.

The DF is the ratio of power loss in the capacitor to the total power transmitted through the capacitor. The DF is a ratio of a capacitor's resistance (ESR) to its capacitive reactance (Xc). DF is usually expressed as a percentage (i.e., ESR/Xc \* 100%). A capacitive reactance (Xc) is calculated by the expression  $Xc = 1/(2\pi fC)$ . The DF increases with increasing frequency. At a given frequency, the DF shows some decrease with increasing temperature.

The Murata 25  $\mu$ F ceramic capacitor has a .2% DF at 1 kHz and 180°C. This changed to 1.23% DF at 15 kHz and 180°C, which is a 515% increase. At 0°C and 1 kHz, the DF is .23% and increases to 1.24% at 15 kHz and 0°C, which is a 439% increase.

Between 15 kHz and 40 kHz at 180°C, the DF increases 469% and between 15 kHz and 40 kHz at 0°C, the DF increases 948%.

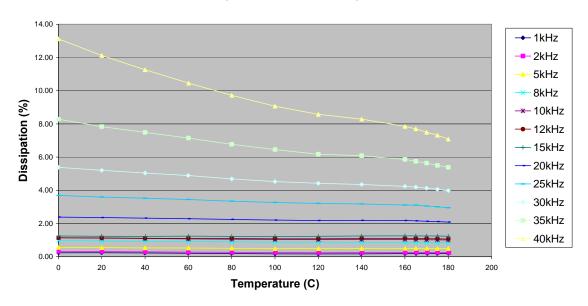

Figure 2.10 graphs the DF versus temperature showing fairly stable values for the lower frequencies tested.

# Murata 25 uF 630 V Capacitor Dissipation Factor vs Temperature

Fig. 2.10. Murata 25  $\mu F$  capacitor—DF vs. temperature.

### 2.1.2 Dynamic Murata Tests

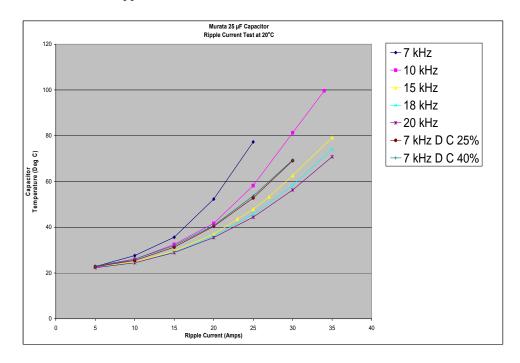

The Murata 25  $\mu$ F 630 Vdc ceramic capacitor was tested in the dynamic mode. Figure 2.11 shows the temperature rise relative to ripple current values.

Fig. 2.11. Murata 25  $\mu$ F ripple current at multiple frequencies.

The ripple current tests were not intended to be a test to failure, only to get an indication of how the capacitor responded to ripple current at various frequencies. Ripple current at higher frequencies generated a lower temperature rise than ripple current at lower frequencies.

At 20 kHz with an ambient temperature of 20°C, 25 A of ripple current generated a temperature of 44.4°C on the surface of the capacitor. At 7 kHz with an ambient temperature of 20°C, 25 A of ripple current resulted in a temperature of 77.3°C on the surface of the capacitor.

### 2.2 SBE 580 µF CAPACITOR TESTS

### 2.2.1 Static SBE Tests

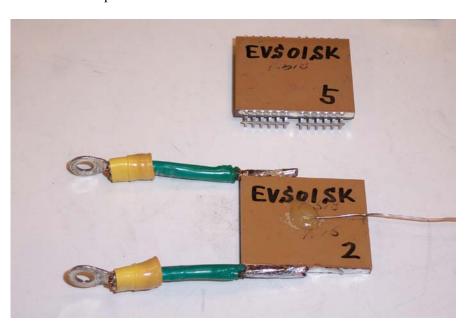

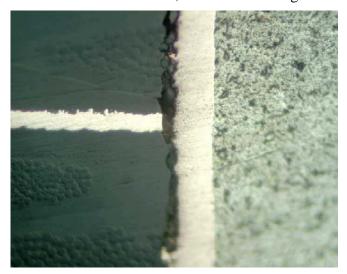

Static testing was performed on a SBE 580  $\mu$ F 100 Vdc power ring film capacitor, shown in Figs. 2.12 and 2.13. This capacitor's geometry is structured to enable significantly more heat transfer by shortening the distance of the current flow between the terminals. This novel approach lends itself to higher temperature operation in innovative inverter designs.

Fig. 2.12. SBE 580  $\mu F$  100 Vdc film capacitor.

Fig. 2.13. SBE 580  $\mu F$  100 Vdc film capacitor with test fixture and thermocouples attached.

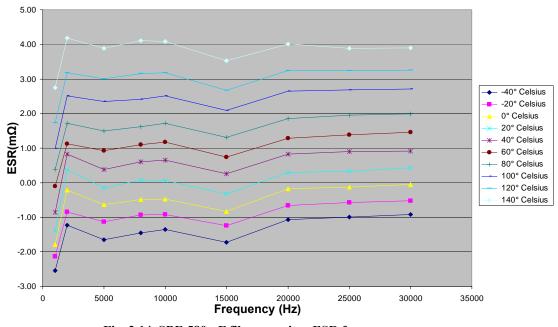

The SBE 580  $\mu$ F 100 Vdc film capacitor was tested in the static mode from -40–140°C over a frequency range of 1–30 kHz. Figure 2.14 shows the variation of ESR versus frequency response at each temperature step.

# SBE 580 µF 100 VDC Film Capacitor ESR vs Frequency

Fig. 2.14. SBE 580  $\mu F$  film capacitor ESR frequency response.

An Agilent 4284 LCR meter was used to measure ESR, capacitance value, and DF for the static tests. The negative values shown here for ESR can be attributed to the LCR meter's method of measurement. An explanation from the manufacturer indicated that a capacitor with very low losses could fall in the + or – tolerance range and could display as negative. The geometry of the SBE film cap, as shown in Fig. 2.12, provides very little distance between the top and bottom; therefore, the ESR is very low at certain temperatures and frequencies.

At -40°C, the ESR increased 51% between 1–2 kHz. Between 2–30 kHz the ESR increased 25%. At 140°C, the ESR increased 52% from 1–2 kHz and decreased 6.7% from 2–30 kHz. Overall, the ESR response over frequency appears fairly flat if averaged over the entire range of frequencies tested.

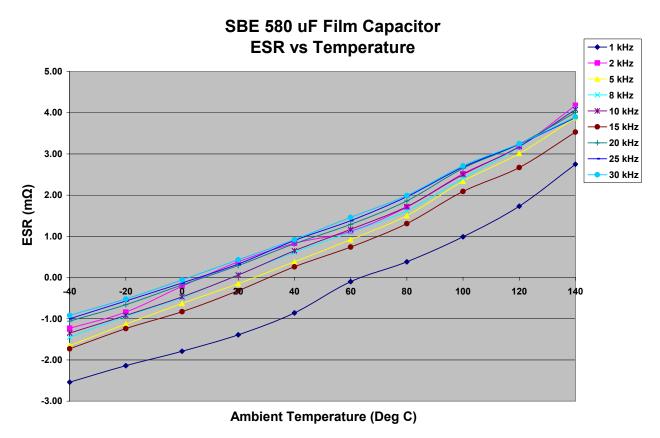

Figure 2.15 plots the same ESR data versus temperature.

Fig. 2.15. SBE 580 μF film capacitor ESR temperature response.

From the data, a significant rise in ESR can be seen across the temperature range tested.

The ESR increased 5.29 m $\Omega$  at 1 kHz over the temperature range of -40–140°C. At 30 kHz, the ESR increased 4.82 m $\Omega$  over the temperature range of -40–140°C.

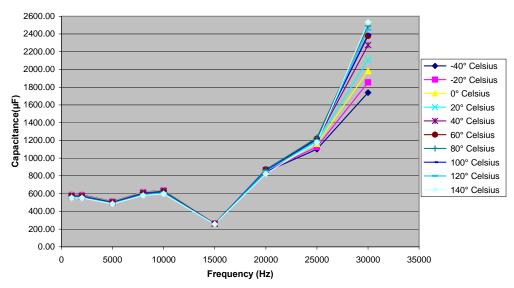

Figure 2.16 shows the capacitance response over the frequency range of 1–30 kHz at each temperature step.

### SBE 580 µF 100 VDC Film Capacitor

Capacitance vs Frequency

Fig. 2.16. SBE 580 μF film capacitor frequency response.

The rise in capacitance appears fairly significant at frequencies over 15 kHz. The capacitance decreased 55% from 1–15 kHz at -40°C, but increased 569% from 15–30 kHz at -40°C. The capacitance decreased 54% from 1–15 kHz at 140°C, but increased 892% from 15–30 kHz at 140°C.

Figure 2.17 graphs this data showing how the capacitance changes over temperature, while keeping the frequency constant.

Fig. 2.17. SBE 580 μF film capacitor temperature response.

At 1 kHz, the capacitance changed from 584  $\mu F$  to 552  $\mu F$ , a decrease of 32  $\mu F$ , over the temperature range of -40–140°C. At 30 kHz and -40°C, the capacitance value was 1739  $\mu F$ . At 30 kHz and 140°C, the capacitance value had changed to 2531  $\mu F$ , an increase of 792  $\mu F$  over the temperature range of -40–140°C.

The capacitance value did not change in regard to temperature at or below 20 kHz. Above 20 kHz, the ambient temperature made a difference in the capacitance value. Lower temperatures produced less change in capacitance at higher frequency.

Figure 2.18 shows how the DF responded over the frequency range of 1–30 kHz at each temperature step between -40–140°C.

# SBE 580 µF 100 VDC Film Capacitor

Fig. 2.18. SBE 580 μF capacitor DF frequency response.

These data indicates a negative DF at several temperatures, which is explained in the ESR data plot in Fig. 2.14. In discussions with the LCR manufacturer, if a capacitor has a very low loss, the ESR and DF could fall within the + and – tolerance range and be displayed as a negative number. The SBE film capacitor has a geometry that provides very low losses at certain temperatures and frequencies. Negative ESR and DF are not possible, so the absolute values of these data will be discussed relative to percent change in regard to temperature and frequency.

At -40°C, the DF decreased 367% from 1–15 kHz. From 15–30 kHz, the DF decreased 645%. At  $140^{\circ}$ C, the DF increased from .93–8.5 (810%) from 1–15 kHz. From 15–30 kHz, the DF increased from 8.5–185.5 (2082%) at  $140^{\circ}$ C.

Figure 2.19 graphs the DF over temperature from -40-40°C.

Fig. 2.19. SBE 580 μF film capacitor DF temperature response.

The DF for the SBE 580  $\mu$ F film capacitor increased 1.84 units at 1 kHz over the temperature range of -40–140°C. The DF increased 216.79 units at 30 kHz over the same temperature range of -40–140°C.

The slope of the graph shows a considerable increase at the higher frequencies.

From these data it shows that higher temperatures at higher frequencies result in much higher DF. At temperatures below 20°C, the DF will decrease as the frequency increases. At temperatures of 20°C and higher, the DF will increase as frequency increases.

### 2.2.2 Dynamic SBE Tests

Ripple current tests were conducted on the SBE 580  $\mu$ F 100 Vdc film capacitor at 20°C ambient. Figure 2.20 shows the test fixture and the thermocouples locations. Figure 2.21 shows the capacitor test fixture inside the environmental chamber.

Thermocouple number 2 is attached to the inside of the phenolic ring. Holes were drilled in three separate locations as recommended by SBE with depths half the thickness of the capacitor. Thermocouples 3, 4, and 5 are placed inside the holes at these locations. There is also a copper crush ring between the capacitor and each of the test fixture plates to ensure equal conduction between the plates and the capacitor to avoid hot spots.

Fig. 2.20. SBE 580  $\mu F$  capacitor thermocouple layout.

Fig. 2.21. SBE 580  $\mu F$  film capacitor test fixture inside environmental chamber.

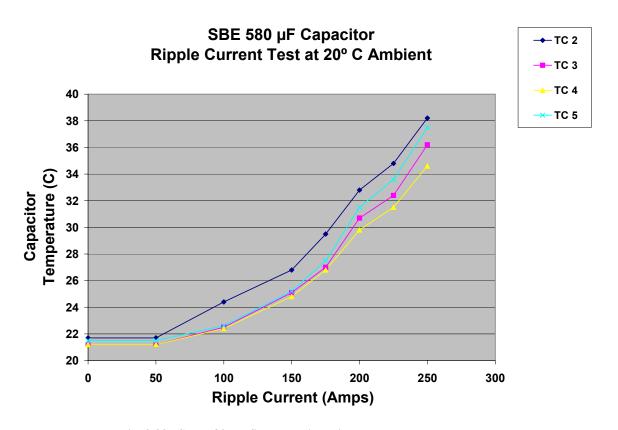

Figure 2.22 shows the ripple current versus temperature results for four different thermocouples at  $20^{\circ}$ C ambient temperature.

Fig. 2.22. SBE 580  $\mu F$  film capacitor ripple current vs. temperature.

The ripple current tests were done at 4 kHz with a maximum current of 250 A. Thermocouple number 2 increased 76% with a maximum temperature of 38.2°C at 250 A. The average increase of thermocouples 3, 4, and 5 was 69% with an average maximum temperature of 36.1°C at 250 A.

### 3. INFINEON TRENCH 150°C JUNCTION TEMPERATURE IGBT TESTS

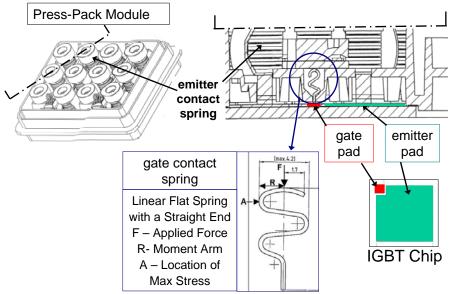

**Task:** Test the performance of the Infineon FS30R06W1E3 trench technology IGBTs across a wide temperature range (25–200°C).

### 3.1. EXPERIMENTAL SETUP

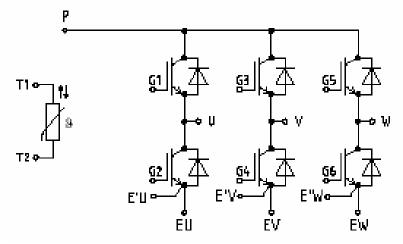

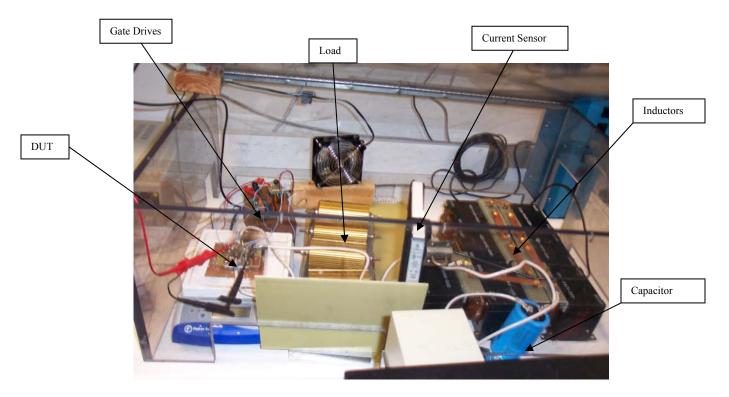

Figure 3.1 Shows details of an Infineon IGBT pack FS30R06W1E3 layout.

Fig. 3.1. Layout of the Infineon IGBT module.

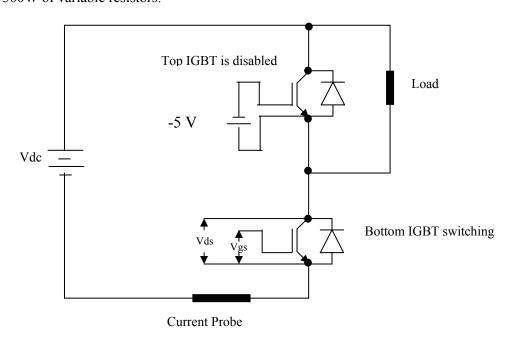

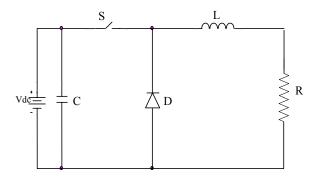

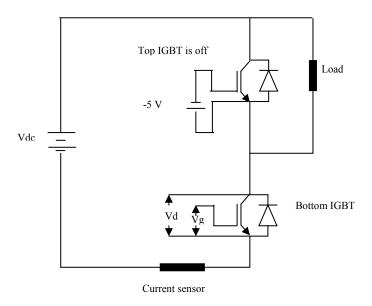

Figure 3.2 shows the test schematic. Only one leg of the IGBT module was utilized for the test. The other two legs were left 'floating.' A 300V, 200A dc power supply was used for Vdc. The power supply was connected across the P and EU terminals, shown in Fig. 3.1. The load was connected across the first IGBT between the P and U terminals. The load was comprised of 28mH's  $(4\text{mH} \times 7)$  of inductance rated for 40A and 300W of variable resistors.

Fig. 3.2. Schematic of the circuit.

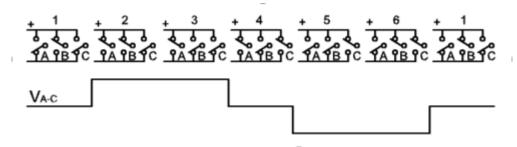

The upper IGBT was turned OFF by supplying -5V between the gate and the source (i.e. between the G1 and U terminals) referencing Fig. 3.1. A Fuji EXB840 chip was used as the gate driver. The lower IGBT was hard switched, no snubber was utilized. An Agilent 33250A waveform generator was used to generate the 5 kHz switching frequency with a duty cycle of 20%. The voltage was measured across the drain and the source (between the U terminal and E'U terminals of Fig 3.1) of the lower IGBT. A Tektronix TCP404XL current probe was used along with a TCPA400 current amplifier to measure the lower IGBT source current. A Tektronix TDS 5104B oscilloscope was used to monitor and record the various current and voltage waveforms. The setup is shown in Fig. 3.3(a).

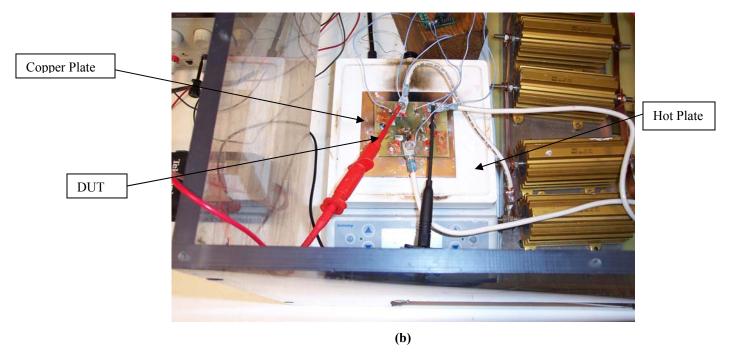

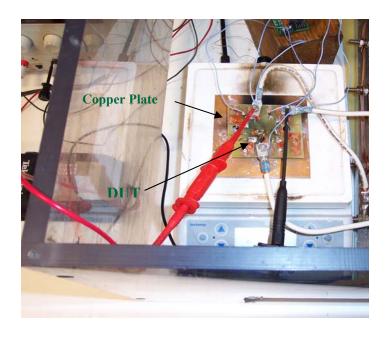

As shown in Fig. 3.3(b), a Fisher Scientific Isotemp hot plate was used to vary the junction temperature of the IGBT. The IGBT module was mounted on a copper plate, which was glued to the hot plate using thermal grease. The temperature of the hot plate was measured and fed back using a thermocouple to control the desired temperature.

Fig. 3.3(a). Test setup.

Fig. 3.3(b). Test setup (closer view).

### 3.2 TEST PROCEDURE

- Connect the desired value of resistance  $(10\Omega, 5\Omega, 3.33\Omega, 2.5\Omega, 2.20\Omega, \text{ and/or } 1.8\Omega)$  by connecting  $20\Omega, 300$  W resistances in parallel.

- Slowly increase Vdc to 250V.

- Record the current and voltage waveform at different temperatures in steps of 25–200°C.

- Increase the current in steps of 5; from 5A 10A, 15A, 20A, 25A to 30 A to supply continuous dc current.

### 3.3 RESULTS

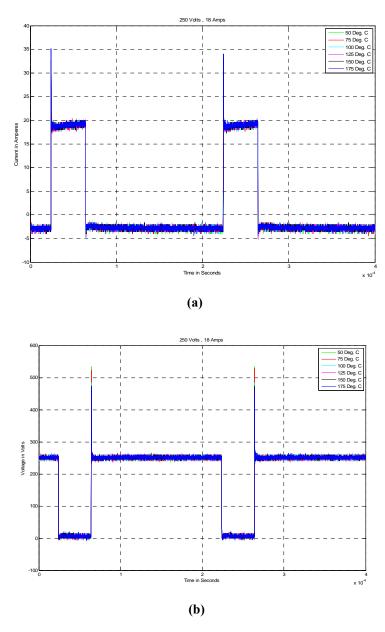

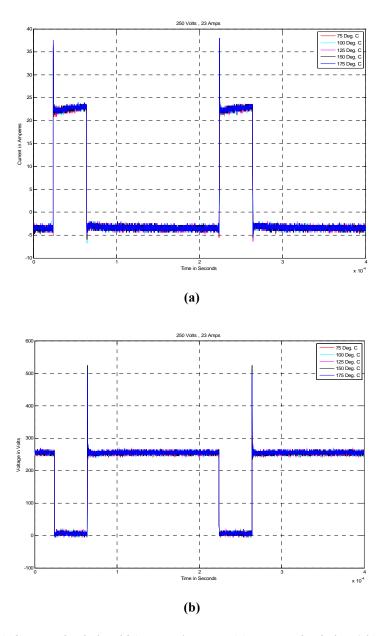

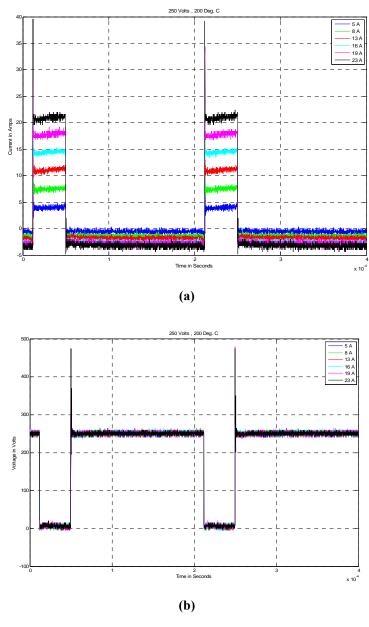

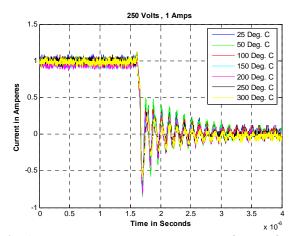

Some of the graphs obtained from the data recorded are shown in Figs. 3.4–3.6.

Fig. 3.4. (a) Current for 250V, 16A operation; and (b) Voltage for 250V, 16A operation.

Fig. 3.5. (a) Current for 250V, 23A operation; and (b) Voltage for 250V, 16A operation.

Fig. 3.6. (a) Current for 250V, 200°C case temperature operation; and (b) Voltage for 250V, 200°C case temperature operation.

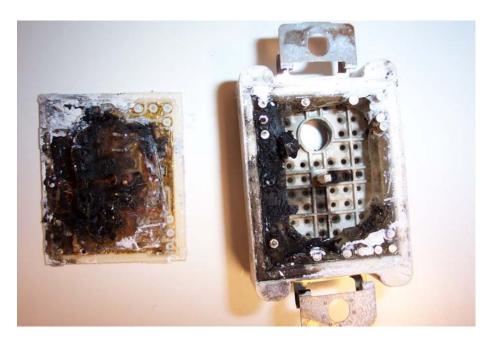

It should be noted that the devices were operated without any snubbers in the circuit. The voltage spikes seen in the waveforms are due to the hard switching of the devices without any snubbers. The IGBT failed while operating at 250V and 16A with a case temperature of 200°C after approximately 10 minutes, as shown in Fig. 3.7. Similar steps were carried out on different legs of the module to confirm the failure. A second IGBT failed at 250 V, 23 A while operating with a case temperature of 200°C.

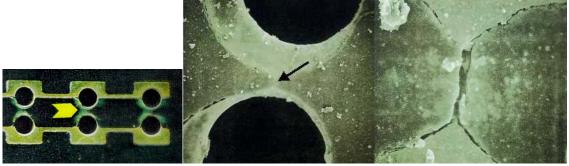

Fig. 3.7. Device failure at 250V, 16A, 200°C case temperature.

### 3.4 CONTINUOUS DC CURRENT TEST

In this test, (10)  $20\Omega$ , 300W resistors were connected in parallel to obtain a total of 1.8  $\Omega$  resistance. Voltage was increased in order to obtain current steps of 5, 10, 15 20, 25, and 30 A. Tests were carried out at 50, 100, 150, 175, and 200°C case temperatures. One device failed at 30A while operating at 200°C case temperature after approximately 5 minutes. Similar tests were carried out on a different IGBT leg to confirm the failure point. This leg also failed at 30A, with a case temperature of 200°C.

### 3.5 CONCLUSION

The devices performed without failures up to 175°C junction temperature under different load conditions. The test devices were switched at 5kHz, 20% duty cycle, 250V, and 23A (38 A peak transients) without any problems (refer to Fig. 3.5). The devices were operational with different load conditions for at least 15 minutes at each data point. After increasing the case temperature to 200°C, one device failed after 10 minutes of operation with 16A of load current (refer Fig. 3.7). A second test device failed at 23A load current while operating at a case temperature of 200°C.

The devices were subjected to continuous dc current tests to study the performance of the devices close to the rated current. The devices operated without failures at the rated current of 30A and 175°C case temperature. These test conditions were maintained for 15 minutes of operation. However, when the case temperature was raised to 200°C the device operated satisfactorily at 25A and then failed at 30A of load current. The tests were repeated to confirm the failure point and the second device failed again at 30A load current.

It can be concluded that the device is capable of operating at 175°C without derating of the continuous current rating. However, at operation with a case temperature of 200°C the devices failed during both switching tests and dc tests below the rated current.

#### 4.0 OPAL-RT TEST SETUP

The control system necessary for module level testing consists of two computers connected by an ethernet cable. One is a Windows based system (Command Station) and is the control computer that the user interfaces with. The other (Target Node) is QNX OS supplied with Opal, which is a real-time operating system (RTOS) dedicated computer with I/O cards that actually performs the control. This Target Node computer contains all the digital and analog I/O hardware to the DUT.

The Opal-RT system consists of a suite of programs that interface and build upon one another. Therefore all programs (with their respective licenses) need to be on the Command Station computer for development efforts. For execution only, just RT-LAB needs to be on the Command Station. The control code is entered in MATLAB/Simulink and the resultant compiled code is processed by RT-LAB to be loaded on the Target Node(s). In systems with more than one Target Node, the executable code needs to be split up among the various Target Nodes by the user. However, in the ORNL configuration only one Target Node is utilized so all executable code is loaded on the same Target.

### 4.1 DEVELOPMENT PROCESS

Users who wish to develop or alter code need to be familiar with MATLAB/Simulink in order to develop or change the control code. MATLAB is a technical computing software package that integrates programming, calculation, and visualization. Simulink is a software package that enables modeling, simulation, and analysis of dynamic systems. The models are described graphically following a precise format based on a library of blocks. RT-LAB uses Simulink to define models that will be executed by the real-time multiprocessing system and defines its own simulation parameters through Simulink.

Full development of a new model or even the modification of a current model requires good working knowledge of the entire suite of Opal-RT and Matlab. The operation of the RT-LAB for controlling power electronics assumes the system has been fully implemented both in hardware and software and only the operation of the control for running tests is described here.

In addition to knowledge about Matlab/Simulink, the user should consult the Opal-RT manual for specific requirements of RT-LAB such as subsystem requirement of master, slave, and console. To edit an existing controller model, follow steps 1 and 2 in the test procedure below. Then click "Edit" to load Matlab/Simulink and wait about one minute for the model to be opened. Make any necessary changes. After the file is saved, click "Compile" to compile the convert the real-time model and be on alert for any compilation warnings or errors. Follow steps 3–5 below to load and execute the controller program.

#### 4.2 TEST PROCEDURE

In the following test procedures, bold indicates control buttons on Main Control Panel:

- 1. Call RT-Lab Main Control panel up with icon in far right Window's task bar.

- 2. **Open** module to load on Target in C:\TAB\Simulink\(prog dir)\\*.mdl.

- 3. **Load**. Insure message panel has no errors. If so fix.

- 4. Turn on Inverter with manual switch or 15V power supply. This needs to be done before turning on the controller.

- 5. **Execute** code on Target. It will take two–three seconds for response.

- 6. To change **Parameters**:

- a. Revolutions per minute (**rpm**) is target speed in rpm.

- b. **rpmrate** is acceleration in radians/sec to get to rpm. For deceleration, unit will just coast to target rpm.

- 7. Shutdown Inverter enable first before reset of control program via manual switch or 15V power supply.

- 8. **Reset** only after motor under test coasts to zero.

- 9. To restart go to step 3 above.

#### Notes:

Be sure to turn on inverter enable before executing Target control code and turn it off before Reset of control program.

CPU fan on Target node has a tendency to fail causing Target computer to quit in middle of testing. Insure backup to CPU cooling.

### **4.3 CALIBRATION OF EQUIPMENT**

It was necessary to perform calibration of laboratory equipment in order to accurately test components and potential high temperature power electronic modules. During the year various pieces of equipment were sent for calibration to support ORNL's extensive test efforts, as well as high temperature component benchmarking.

Table 4.1 lists the complete equipment list that was calibrated to support ORNL high temperature test efforts in FY07.

Table 4.1. Equipment list that was calibrated to support ORNL high temperature test efforts in FY07

| DESCRIPTION                                                  | SERIAL      |

|--------------------------------------------------------------|-------------|

|                                                              | NUMBER      |

| Yokogawa 2531 series power meter with harmonics              | 24AW2056    |

| measurement, model#2531-30-C2-3-D/HRM                        |             |

| Yokogawa PZ4000 power meter actual model# 253710-D/B5/C7/M3  | 27CC16078M  |

| Agilent 3458A high accuracy Digital Voltmeter                | US28031302  |

| Agilent 35670A Dynamic Signal Analyzer                       | MY42506754  |

| options 1C21D01D11D21D31D4AY6                                |             |

| Tektronix TDS5104B 4 channel Digital Phosphor oscilloscope   | B010713     |

| Tektronix TDS5104B 4 channel Digital Phosphor oscilloscope   | B021145     |

| Yokogawa DL7480 8 channel analog 16 ch. Digital oscilloscope | 27D232620B  |

| acutal model# 701480-D-J2/B5/E4/N4/C7/C10/G2/P4              |             |

| Yokogawa DL7480 8 channel analog 16 ch. Digital oscilloscope | 12C813404 H |

| acutal model# 701480-D-J2/B5/E4/N4/C7/C10/G2/P4              |             |

| F.W. Bell/Sypris model 7010 Gauss/Teslameter05% accuracy     | 335020      |

| F.W. Bell/Sypris T-71-116 transverse probe                   | 03A0102     |

| F.W. Bell/Sypris STM71-0204-15-T transverse probe            | 460011      |

| FWBell/Sypris VT-500 reference magnet 500 gauss-transverse   | 329445      |

| FWBell/Sypris VT-10K reference magnet 10K gauss-transverse   | 329447      |

| FWBell/Sypris VA-2K reference magnet 2Kgauss-axial           | 329448      |

| Yokogawa DL750 scope/recorder                                | 27D510633D  |

| model# 701210-D-J2/HE/M3/C8/C10/G2/G3                        |             |

| Yokogawa 701251 - 16 bit 1MS/Sec. isolation module for DL750 | 27D405647D  |

| Yokogawa 701251 - 16 bit 1MS/Sec. isolation module for DL750 | 27D405657D  |

| Yokogawa 701271 dual strain gauge module for DL750           | 27D520396E  |

| Yokogawa 701271 dual strain gauge module for DL750           | 27D520395E  |

| Yokogawa 701260 module-16bit 100KSa/Sec. isolated            | 27D231318   |

| Yokogawa 701260 module-16bit 100KSa/Sec. isolated            | 27D341527   |

| Yokogawa 701260 module-16bit 100KSa/Sec. isolated            | 27D341526   |

| Yokogawa 701250 module- 12 bit isolation, 10 Msa/Sec.        | 27D422251   |

| Yokogawa 701250 module - 12 bit isolation, 10 Msa/Sec.       | 27D341344   |

| Yokogawa 701250 module - 12 bit isolation, 10 Msa/Sec.       | 27D341345   |

| Yokogawa 701265 module                                       | 27D222124B  |

| Yokogawa 701265 module                                       | 27D222125B  |

| Yokogawa 701265 module                                       | 27D222130B  |

| Yokogawa 701265 module                                       | 27D222131B  |

# 5. SiC DEVICE TESTING

A portion of the funding provided for this effort was allocated to support wide-bandgap (WBG) device characterizations. The complete report on this effort is documented in the ORNL annual report in the "Wide-Bandgap Materials" section. It is included in Appendix A.

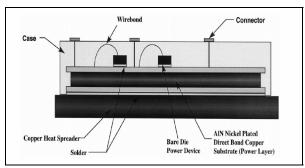

# 6. RELIABILITY OF POWER ELECTRONICS PACKAGING TECHNIQUES

As part of this effort a subcontract with Pat McCluskey of Center for Advanced Life Cycle Engineering (CALCE) at the University of Maryland was initiated to investigate power module packaging reliability issues with operation at high temperatures. The entirety of the report is attached in Appendix B.

### 7. CONCLUSIONS

As a result of funding remaining from an effort by Semikron on the development of a high temperature inverter designed to operate with 105°C coolant, several tasks were performed by ORNL to examine the viability of high temperature components for use in such a module. Findings from Semikron during their work revealed that one of the main challenges of this work was obtaining capacitors with sufficient capabilities at the elevated temperatures. As a result of this several capacitor technologies were examined and tested for possible use in high temperature power electronics. SiC components and new high temperature silicon (Si) IGBTs were also evaluated to assess their reliability and characteristics at elevated temperatures and under fault conditions.

In order to perform accurate performance evaluations of components and modules calibrations of select laboratory equipment and software modifications to the existing test beds in the Power Electronics and Electric Machinery Research Center (PEEMRC) laboratory were made.

Finally, a detailed study on existing power module packaging techniques was performed to identify limitations on current methods and provide insight into their use in high temperature applications for future advanced vehicles.

### APPENDIX A: WIDE-BANDGAP MATERIALS

### A.1. TASKS

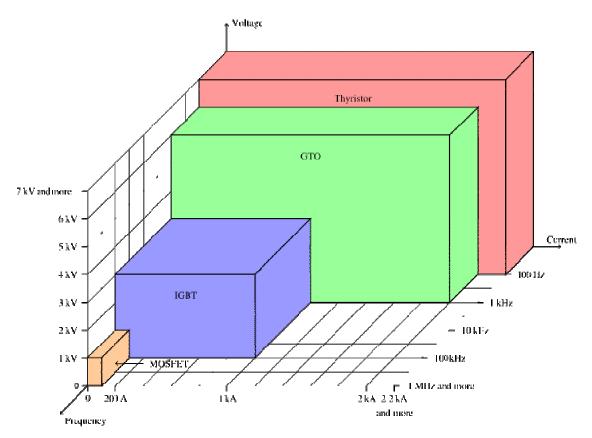

- Assess the impact of replacing Si power devices in transportation applications with devices based on WBG semiconductors, especially SiC.

- To study the impact of SiC devices on PHEVs.

- To study the possibility of using a thermal boundary in SiC intelligent power modules (IPMs) where Si gate drivers can be used.

- To study the fault current limiting capability of SiC devices for safety and protection.

### A.2 APPROACH

- Develop models of WBG semiconductor devices, junction field-effect transistors (JFETs), and metal oxide semiconductor field-effect transistors (MOSFETs).

- Integrate Si-based and SiC-based inverter loss models into a drive train using PSAT software to compare the impact of replacing Si devices with SiC devices.

- Develop a hybrid device package and simulate the model to study the feasibility of using a thermal boundary in SiC-based IPMs.

- Develop circuits to study the fault current limiting capability of SiC devices.

### A.3 MAJOR ACCOMPLISHMENTS

- Acquired several SiC Schottky diodes, JFETs, and SiC MOSFETs.

- Tested, characterized, and modeled SiC Schottky diodes, JFETs, and MOSFETs.

- Developed and modeled a hybrid device package.

- An inverter loss model was successfully integrated into the drive train model in PSAT.

### A.3.1 Technical Discussion

### A.3.1.1 Device testing

Several new WBG devices were acquired this year and these devices were tested, characterized, and modeled. The devices included SiC JFETs, SiC MOSFETs, and SiC Schottky diodes. All the devices obtained were experimental samples. A high temperature Si IGBT was also tested this year to verify the claims of high temperature. Tables A.1 and A.2 below show results of some of the WBG devices tested from 2004–2007.

Table A.1. Power diodes

| Device Type           | Ratings          | On-Resistance (Ω)                      | Forward Voltage<br>Drop (Volts)        | Manufacturer | Year<br>Tested |

|-----------------------|------------------|----------------------------------------|----------------------------------------|--------------|----------------|

| SiC Schottky Diode    | 1200 V, 7.5<br>A | 0.15 Ω at -50°C to<br>0.32 Ω at 175°C  | 1.42 V at -50°C to<br>1.21 V at 175°C  | Vendor A     | 2004           |

| SiC Schottky Diode    | 300 V, 10 A      | 0.15 Ω at -50°C to<br>0.16 Ω at 175°C  | 1.11 V at -50°C to<br>0.83 V at 175°C  | Vendor B     | 2004           |

| SiC Schottky Diode    | 600 V, 4 A       | 0.19 Ω at -50°C to<br>0.39 Ω at 175°C  | 1.09 V at -50°C to<br>0.87 V at 175°C  | Vendor C     | 2004           |

| SiC Schottky Diode    | 600 V, 10 A      | 0.14 Ω at -50°C to<br>0.25 Ω at 175°C  | 1.09 V at -50°C to<br>0.82 V at 175°C  | Vendor C     | 2004           |

| SiC Schottky Diode    | 600 V, 75 A      | 0.01 Ω at -50°C to<br>0.03 Ω at 175°C  | 0.91 V at -50°C to<br>0.61 V at 175°C  | Vendor C     | 2005           |

| GaN Schottky<br>Diode | 600 V, 4 A       | 0.23 Ω at 25°C to 0.47 Ω at 175°C      | 0.83 V at 25°C to<br>0.67 V at 175°C   | Vendor D     | 2006           |

| SiC Schottky Diode    | 600 V, 6 A       | 0.138 Ω at 50°C to<br>0.359 Ω at 300°C | 0.745 V at 50°C to<br>0.365 V at 300°C | Vendor E     | 2007           |

Table A.2. Power switches

| Device Type | Ratings      | On-Resistance (Ω)                                                                | Voltage Drop at Rated Current @ Room Temperature (Volts) | Manufacturer | Year<br>Tested |

|-------------|--------------|----------------------------------------------------------------------------------|----------------------------------------------------------|--------------|----------------|

| SiC JFET    | 1200 V, 2 A  | 0.36 Ω at -50°C to<br>1.4 Ω at 175°C                                             | 1.3 V @ Vgs = 0 V                                        | Vendor F     | 2004           |

| SiC JFET    | 1200 V, 10 A | 0.25 Ω at -50°C to<br>0.58 Ω at 175°C                                            | 2.71  V @  Vgs = 0  V                                    | Vendor F     | 2006           |

| SiC JFET    | 1200 V, 15 A | 0.15 Ω at -50°C to<br>2.2 Ω at 175°C                                             | $3.2 \text{ V} @ \text{V}_{gs} = 3 \text{ V}$            | Vendor A     | 2006           |

| SiC JFET    | 600 V, 5 A   | 0.26 Ω at -50°C to<br>1.87 Ω at 175°C                                            | $2.25 \text{ V} @ \text{V}_{gs} = 3 \text{ V}$           | Vendor G     | 2006           |

| SiC MOSFET  | 1200 V, 5 A  | (0.48 Ω at -50°C to<br>0.23 Ω at 50°C)<br>(0.24 Ω at 75°C to<br>0.29 Ω at 175°C) | 1.5 V@ V <sub>gs</sub> = 20 V                            | Vendor C     | 2005           |

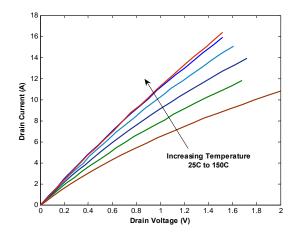

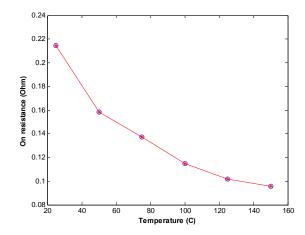

| SiC MOSFET  | 800 V, 10 A  | 0.25 Ω at 25°C to<br>0.09 Ω at 150°C                                             | 1.8 V@ V <sub>gs</sub> = 15 V                            | Vendor C     | 2007           |

| SiC JFET    | 600 V, 2 A   | 0.25 Ω at 25°C to<br>1.07 Ω at 200°C                                             | 1.3 V@ V <sub>gs</sub> = 0 V                             | Vendor G     | 2007           |

### A.3.1.1.1 SiC Schottky diode

### **Static Characteristics**

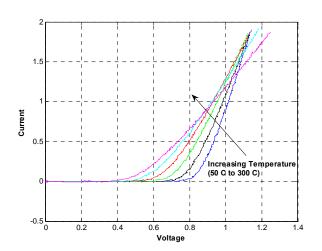

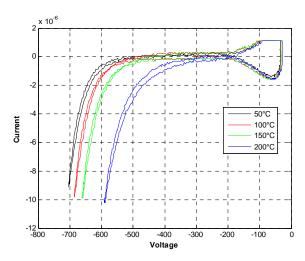

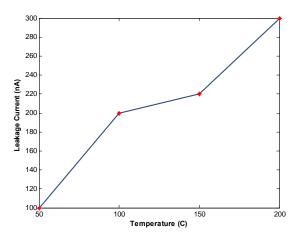

A 600V/6 A SiC Schottky diode packaged in a high temperature package was obtained from Sienna Technologies. The main objective was to determine the performance of the diode at higher temperatures which would not be possible with a standard package. I-V characteristics of the diode were obtained at different temperatures in the 50–300°C temperature range (Fig. A.1). Figure A.2 shows the reverse characteristics of the diode over a wide temperature range. The blocking voltage decreases with increasing temperature. The leakage current increases with increasing temperature (Fig. A.3).

Fig. A.1. Forward characteristics.

Fig. A.2. Reverse characteristics.

Fig. A.3. Leakage current of a SiC Schottky diode at different temperatures at 600 V.

### **Dynamic Characteristics**

The SiC Schottky diode was also tested in a chopper circuit, shown in Fig. A.4, to observe its dynamic characteristics. The IGBT was switched at 1 kHz with a duty cycle of 50% and an R-L load. The reverse recovery tests were performed at different voltages and currents.

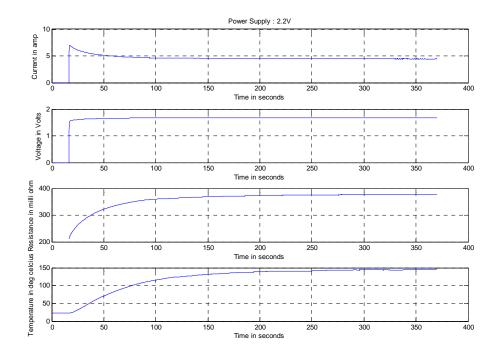

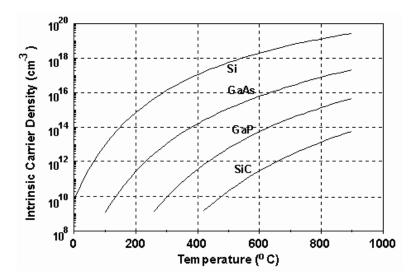

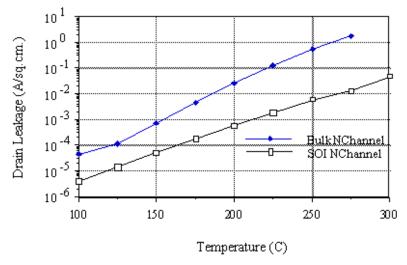

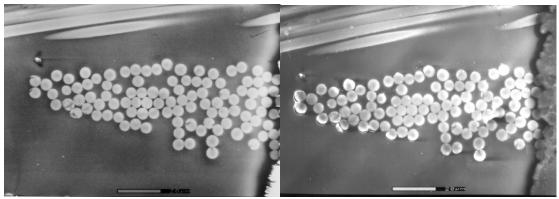

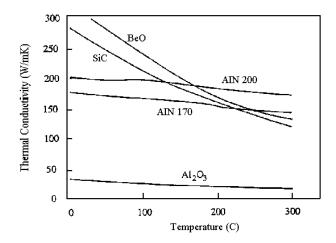

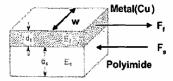

Fig. A.4. Reverse recovery test circuit.