# **SANDIA REPORT**

SAND2008-6015 Unlimited Release Printed September 2008

# Soft-Core Processor Study for Node-Based Architectures

Daniel E. Gallegos, Benjamin J. Welch, Jason J. Jarosz, Jonathan R. Van Houten, and Mark W. Learn

Prepared by Sandia National Laboratories Albuquerque, New Mexico 87185 and Livermore, California 94550

Sandia is a multiprogram laboratory operated by Sandia Corporation, a Lockheed Martin Company, for the United States Department of Energy's National Nuclear Security Administration under Contract DE-AC04-94AL85000.

Approved for public release; further dissemination unlimited.

Issued by Sandia National Laboratories, operated for the United States Department of Energy by Sandia Corporation.

**NOTICE:** This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government, nor any agency thereof, nor any of their employees, nor any of their contractors, subcontractors, or their employees, make any warranty, express or implied, or assume any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represent that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government, any agency thereof, or any of their contractors or subcontractors. The views and opinions expressed herein do not necessarily state or reflect those of the United States Government, any agency thereof, or any of their contractors.

Printed in the United States of America. This report has been reproduced directly from the best available copy.

Available to DOE and DOE contractors from

U.S. Department of Energy Office of Scientific and Technical Information P.O. Box 62 Oak Ridge, TN 37831

Telephone: (865) 576-8401 Facsimile: (865) 576-5728

E-Mail: reports@adonis.osti.gov

Online ordering: http://www.osti.gov/bridge

#### Available to the public from

U.S. Department of Commerce National Technical Information Service 5285 Port Royal Rd. Springfield, VA 22161

Telephone: (800) 553-6847 Facsimile: (703) 605-6900

E-Mail: <u>orders@ntis.fedworld.gov</u>

Online order: <a href="http://www.ntis.gov/help/ordermethods.asp?loc=7-4-0#online">http://www.ntis.gov/help/ordermethods.asp?loc=7-4-0#online</a>

# SAND2008-6015 Unlimited Release Printed September 2008

# **Soft-Core Processor Study for Node-Based Architectures**

Daniel E. Gallegos, Jason J. Jarosz, Jonathan R. Van Houten, and Mark W. Learn Embedded Sensor Systems, 2623

> Benjamin J. Welch System Engineering, 5933

Sandia National Laboratories P.O. Box 5800 Albuquerque, New Mexico 87185-0530

## **ABSTRACT**

Node-based architecture (NBA) designs for future satellite projects hold the promise of decreasing system development time and costs, size, weight, and power and positioning the laboratory to address other emerging mission opportunities quickly. Reconfigurable Field Programmable Gate Array (FPGA) based modules will comprise the core of several of the NBA nodes. Microprocessing capabilities will be necessary with varying degrees of mission-specific performance requirements on these nodes. To enable the flexibility of these reconfigurable nodes, it is advantageous to incorporate the microprocessor into the FPGA itself, either as a hardcore processor built into the FPGA or as a soft-core processor built out of FPGA elements. This document describes the evaluation of three reconfigurable FPGA based processors for use in future NBA systems – two soft cores (MicroBlaze and non-fault-tolerant LEON) and one hard core (PowerPC 405). Two standard performance benchmark applications were developed for each processor. The first, Dhrystone, is a fixed-point operation metric. The second, Whetstone, is a floating-point operation metric. Several trials were run at varying code locations, loop counts, processor speeds, and cache configurations. FPGA resource utilization was recorded for each configuration. Cache configurations impacted the results greatly; for optimal processor efficiency it is necessary to enable caches on the processors. Processor caches carry a penalty; cache error mitigation is necessary when operating in a radiation environment.

# **TABLE OF CONTENTS**

| EX | ECUT | IVE SU | JMMARY                      | 11   |

|----|------|--------|-----------------------------|------|

| 1. | INTI | RODUC  | CTION                       | 13   |

| 2. | FPG. | A-BAS  | ED PROCESSOR DOWN-SELECTION | 15   |

| 3. | PER  | FORM   | ANCE METRICS                | 17   |

|    | 3.1  | Virtex | -4 Dhrystone                | . 18 |

|    |      | 3.1.1  | Virtex-4 PPC405             |      |

|    |      | 3.1.2  | MicroBlaze                  | . 21 |

|    |      | 3.1.3  | LEON3                       | . 23 |

|    | 3.2  | Virtex | -4 Whetstone                | . 24 |

|    |      | 3.2.1  | Virtex-4 PPC405             |      |

|    |      | 3.2.2  | MicroBlaze                  | . 28 |

|    |      | 3.2.3  | LEON3                       | . 31 |

|    | 3.3  | Virtex | -4 Resources                | 32   |

|    |      | 3.3.1  | Virtex-4 PPC405             | 35   |

|    |      | 3.3.2  | MicroBlaze                  | 35   |

|    |      | 3.3.3  | LEON3                       | . 37 |

|    | 3.4  | Virtex | -5 FX130T Resources         | 38   |

| 4. | RΔΓ  | IATIO  | N EFFECTS MITIGATION        | 39   |

| ١. | 4.1  |        | -4 PPC405                   |      |

|    | 4.2  |        | -4 MicroBlaze               |      |

|    | 4.3  |        | -4 LEON3                    |      |

|    | 4.4  |        | -5 (SIRF) PPC440            |      |

|    | 4.5  |        | -5 (SIRF) MicroBlaze        |      |

|    | 4.6  |        | -5 (SIRF) LEON3             |      |

| 5. | SIZE |        | GHT, AND POWER              |      |

| 6. |      |        | MENT TOOLS                  |      |

| 0. | 6.1  |        | ricing                      |      |

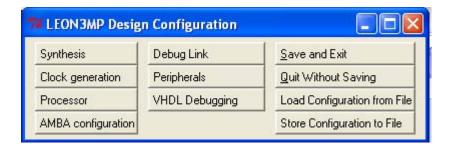

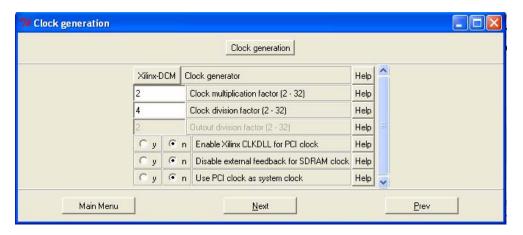

|    | 6.2  |        | sor/System Definition       |      |

|    | 0.2  |        | PPC405 and MicroBlaze       |      |

|    |      |        | LEON3                       |      |

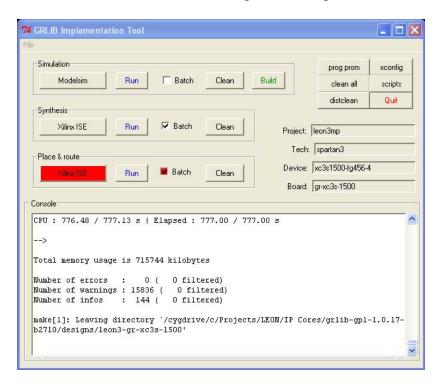

|    | 6.3  |        | esis                        |      |

|    | 0.5  | 6.3.1  | PPC405 and MicroBlaze       |      |

|    |      | 6.3.2  | LEON3                       |      |

|    | 6.4  |        | are Development             |      |

|    | 0.1  | 6.4.1  | PPC405 and MicroBlaze       |      |

|    |      |        | LEON3                       |      |

|    | 6.5  |        | ging Tools                  |      |

|    | 6.6  | $\sim$ | ing Systems                 |      |

|    | 0.0  | 6.6.1  | PPC405                      |      |

|    |      | 6.6.2  | MicroBlaze                  |      |

|    |      | 6.6.3  | LEON3                       |      |

|    |      |        |                             |      |

| 7. CON | CLUSIONS AND RECOMMENDATIONS | 57 |

|--------|------------------------------|----|

| REFERE | NCES                         | 59 |

| APPEND | X A                          | 61 |

# **LIST OF FIGURES**

| Figure 1. Processor speed normalized Dhrystone benchmark results: all processors    | 19 |

|-------------------------------------------------------------------------------------|----|

| Figure 2. Non-normalized Dhrystone benchmark results: all processors.               | 19 |

| Figure 3. Normalized Dhrystone benchmark details: Virtex-4 PPC405                   | 21 |

| Figure 4. Virtex-4 MicroBlaze normalized Dhrystone benchmark details                | 22 |

| Figure 5. Virtex-4 LEON3 normalized Dhrystone benchmark details                     | 23 |

| Figure 6. Processor speed normalized Whetstone benchmark results: all processors    | 24 |

| Figure 7. Non-normalized Whetstone benchmark results: all processors                | 25 |

| Figure 8. Virtex-4 PPC405 normalized Whetstone benchmark details, FPU disabled      | 27 |

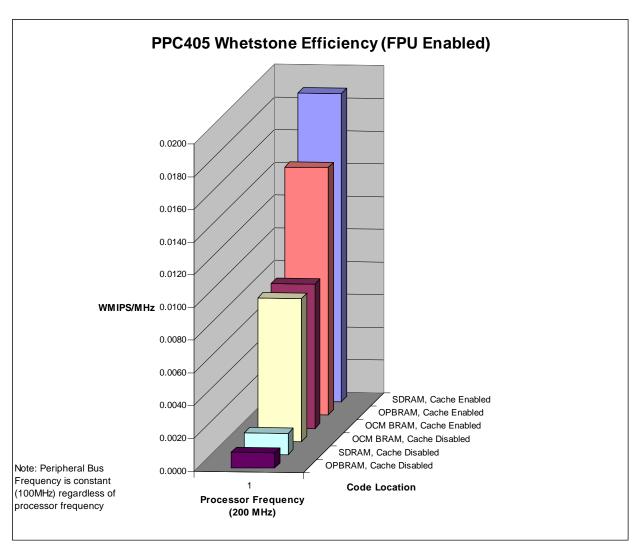

| Figure 9. Virtex-4 PPC405 normalized Whetstone benchmark details, FPU enabled       | 28 |

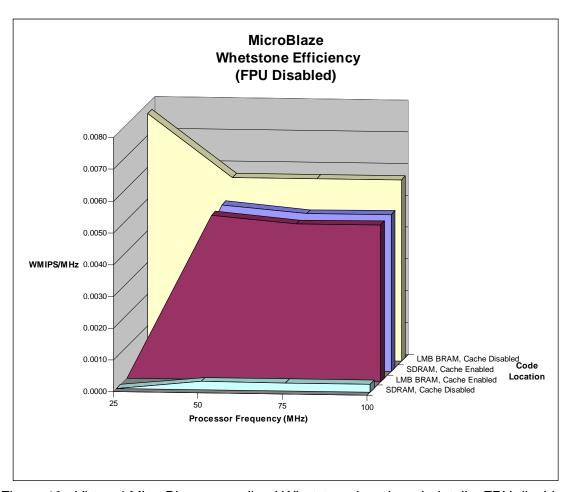

| Figure 10. Virtex-4 MicroBlaze normalized Whetstone benchmark details, FPU disabled | 30 |

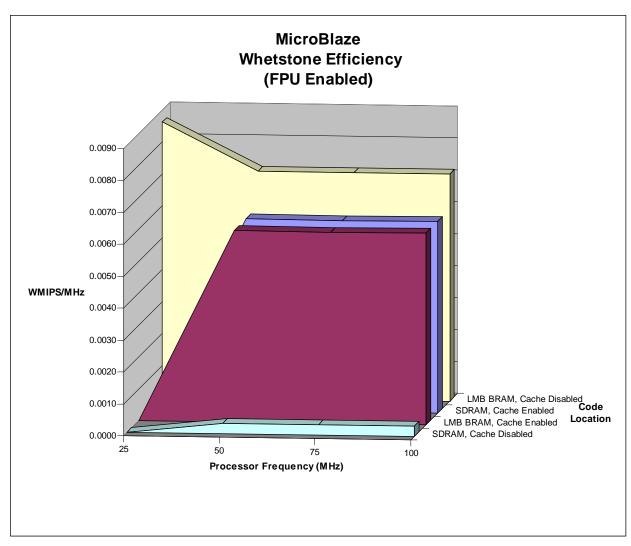

| Figure 11. Virtex-4 MicroBlaze normalized Whetstone benchmark details, FPU enabled  | 31 |

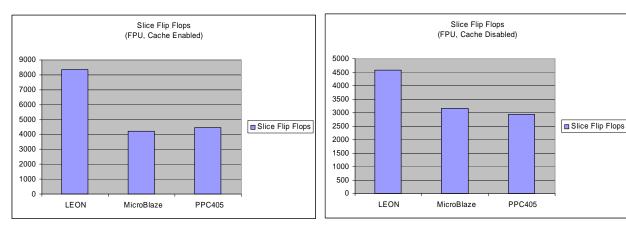

| Figure 12. Virtex-4 FPGA Resources: Slice Flip-Flops.                               | 32 |

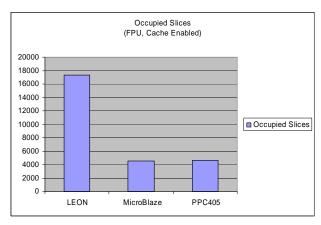

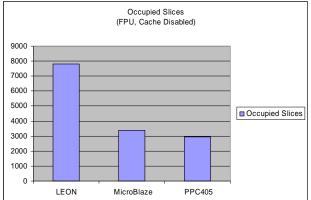

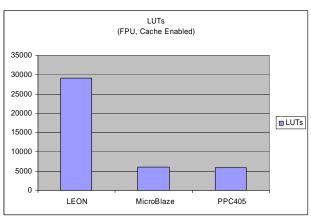

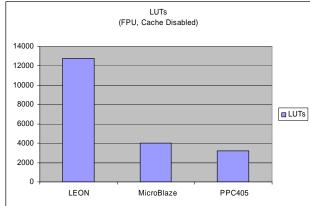

| Figure 13. Virtex-4 FPGA Resources: Occupied Slices.                                | 33 |

| Figure 14. Virtex-4 FPGA Resources: Lookup Tables                                   | 33 |

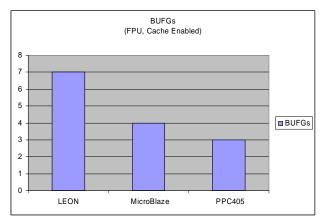

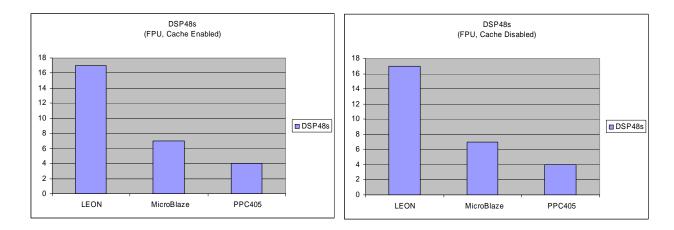

| Figure 15. Virtex-4 FPGA Resources: Clock Buffers.                                  | 33 |

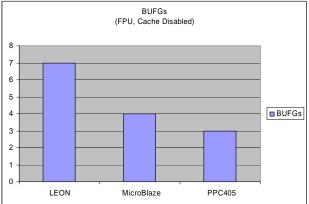

| Figure 16. Virtex-4 FPGA Resources: Digital Clock Managers.                         | 34 |

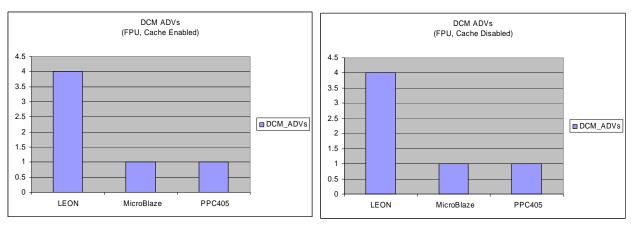

| Figure 17. Virtex-4 FPGA Resources: DSP Blocks.                                     | 34 |

| Figure 18. Virtex-4 FPGA Resources: BRAMs.                                          | 34 |

# **LIST OF TABLES**

| Table 2. Virtex-4 MicroBlaze Dhrystone Application Configuration and Memory Utilization            | Table 1. | Virtex-4 PPC405 Dhrystone Application Configuration and Memory Utilization | . 20 |

|----------------------------------------------------------------------------------------------------|----------|----------------------------------------------------------------------------|------|

| Table 3. Virtex-4 LEON3 Dhrystone Application Configuration and Memory Utilization                 | Table 2. | Virtex-4 MicroBlaze Dhrystone Application Configuration and Memory         |      |

| Table 4. Virtex-4 PPC405 Whetstone Application Configuration and Memory Utilization                | Util     | ization                                                                    | . 22 |

| Table 5. Virtex-4 MicroBlaze Whetstone Application Configuration and Memory Utilization            | Table 3. | Virtex-4 LEON3 Dhrystone Application Configuration and Memory Utilization  | . 23 |

| Utilization                                                                                        | Table 4. | Virtex-4 PPC405 Whetstone Application Configuration and Memory Utilization | . 26 |

| Table 6. Virtex-4 LEON3 Whetstone Application Configuration and Memory Utilization                 | Table 5. | Virtex-4 MicroBlaze Whetstone Application Configuration and Memory         |      |

| Table 6. Virtex-4 LEON3 Whetstone Application Configuration and Memory Utilization                 | Util     | ization                                                                    | . 29 |

| Table 8. Virtex-4 MicroBlaze System FPGA Resource Utilization                                      |          |                                                                            | . 32 |

| Table 9. Virtex-4 LEON3 System FPGA Resource Utilization                                           | Table 7. | Virtex-4 PPC405 System FPGA Resource Utilization                           | . 36 |

| Table 10. Device Utilization Estimates for LEON3 System on Virtex-5 FX130T,  Cache and FPU Enabled | Table 8. | Virtex-4 MicroBlaze System FPGA Resource Utilization.                      | . 36 |

| Cache and FPU Enabled                                                                              | Table 9. | Virtex-4 LEON3 System FPGA Resource Utilization.                           | . 37 |

| Table 11. Device Utilization Estimates for MicroBlaze System on Virtex-5 FX130T,                   | Table 10 | . Device Utilization Estimates for LEON3 System on Virtex-5 FX130T,        |      |

| · · · · · · · · · · · · · · · · · · ·                                                              | Cac      | he and FPU Enabled                                                         | . 38 |

| Cache and FPU Enabled                                                                              | Table 11 | . Device Utilization Estimates for MicroBlaze System on Virtex-5 FX130T,   |      |

|                                                                                                    | Cac      | he and FPU Enabled                                                         | . 38 |

## **ACRONYMS**

ASIC application-specific integrated circuit

BRAM Block RAM

COTS commercial off-the-shelf CPU central processing unit

DCM Digital Clock Manager DSP digital signal processing

EDAC error detection and correction EDK Embedded Development Kit

FPGA Field Programmable Gate Array

FPU floating-point unit

GUI graphical user interface

HDL hardware description language

IP intellectual property

JTAG Joint Test Action Group

LMB Local Memory Bus

LUT lookup table

MHS Microprocessor Hardware Specification

MMU memory management unit

MSS Microprocessor Software Specification

OCM on-chip memory controller OPB on-chip peripheral bus

NBA node-based architecture

PPC PowerPC

RAM random access memory ROM read-only memory

SDRAM synchronous dynamic random access memory

SEE single-event effect

SEFI single-event functional interrupt

SEU single-event upset

SIRF SEU Immune Reconfigurable FPGA

SNL Sandia National Laboratories SRAM Static Random Access Memory

TMR triple mode redundancy

UART Universal Asynchronous Receiver/Transmitter

XPS Xilinx Platform Studio

XRTC Xilinx Radiation Test Consortium

## **EXECUTIVE SUMMARY**

Node-based architecture (NBA) designs for future satellite projects hold the promise of decreasing system development time and costs, size, weight, and power, and, through its reconfigurable nature, being able to position the laboratory to address other emerging mission opportunities quickly.

Reconfigurable Field Programmable Gate Array (FPGA) based modules will comprise the core of several of the NBA nodes identified in the "Future NDS Architecture Description" document. Microprocessing capabilities will be necessary with varying degrees of mission-specific performance requirements on these nodes. To enable the flexibility of these reconfigurable nodes, it is advantageous to incorporate the microprocessor into the FPGA itself, either as a hard-core processor built into the FPGA or as a soft-core processor built out of FPGA elements.

The reconfigurable FPGA targeted for the NBA is the Xilinx SEU Immune Reconfigurable FPGA (SIRF) device, a radiation-hardened by design Static Random Access Memory (SRAM) device based on the commercial off-the-shelf (COTS) Xilinx Virtex-5 FX130T. The SIRF device is still currently under development but is expected to be available in the first quarter of 2010. NBA developers can begin designing now with the COTS equivalent and then incorporate the SIRF device into their designs when it becomes available.

Currently the SIRF development effort is targeted to eliminate the device configuration errors that upset Xilinx SRAM-based FPGAs when operated in radiation environments. The characterization of SIRF device internal building blocks such as Memory Resources (Block RAMs), Logic Resources (Slices, Logic Cells, CLB Flip-Flops), Clock Resources (DCM, PLL), and Embedded Hard Intellectual Property Resources (DSP48E slices, PowerPC (PPC) 440 processor, RocketIO Transceivers) in radiation environments will provide designers with the information needed to develop a mitigation strategy at the device level based on the target mission (orbit).

Three different FPGA-based processors (two soft core and one hard core) were evaluated on the Xilinx Virtex-4FX FPGA because Virtex-5 FXT devices were not available at the onset of the study. Two processors "native" to the Xilinx FPGAs were evaluated, the soft-core MicroBlaze processor and the hard-core PPC405. Processors native to the Xilinx FPGAs are attractive for NBA because of the amount of testing and mitigation that Xilinx and the Xilinx Radiation Test Consortium develop for these processors. In addition, the soft-core LEON3 (non-fault-tolerant) processor was included because of the popularity of the LEON cores in the space processing community and the potential for code and tool reuse if the rad-hard application-specific integrated circuits (ASICs) such as the Atmel AT697E (LEON2 Fault-Tolerant) or the AeroFlex UT699 (LEON3 Fault-Tolerant) devices are used in other NBA modules.

Two standard performance benchmark applications were developed for each processor. The first, Dhrystone, is a fixed-point operation metric. The second, Whetstone, is a floating-point operation metric. Several trials were run at varying code location, loop counts, processor speeds, and cache configurations. FPGA resource utilization was recorded for each configuration.

The MicroBlaze and PPC processors have wider operating ranges than the LEON processor. Surprisingly, more FPGA resources were consumed by the LEON processor than by either of the other two processors. Cache configurations impacted the results greatly – for optimal processor efficiency it is necessary to enable caches on the processors. Processor caches carry a penalty – cache error mitigation is necessary when operating in a radiation environment. The Virtex-4 PPC instruction cache contains an error that does not allow for the graceful mitigation of this resource.

Similar characterizations (with possible optimizations) should be conducted on the COTS Xilinx Virtex-5 FX130T device when it becomes available.

# 1. INTRODUCTION

This document describes the evaluation of three reconfigurable Field Programmable Gate Array (FPGA) based processors for use in future node-based architecture (NBA) systems – two soft cores (MicroBlaze and non-fault-tolerant LEON) and one hard core (PowerPC [PPC] 405).

The Xilinx SIRF (Virtex-5 FX130T) reconfigurable FPGA device that is targeted for NBA is not yet available; Xilinx Virtex-4 FPGAs were used exclusively in this study. MicroBlaze and PPC405 evaluations were conducted on an ML-405 board that contains a Virtex-4 FX20 device. LEON evaluations required the use of a different development board, the ML-410 with a larger Virtex-4 FX60 device because resources consumed by the LEON core. Lessons learned in this study will be directly applicable to developing Virtex-5 processor based systems.

In general: LEON would be good for low-intensity applications; PowerPC and MicroBlaze have wider operating ranges and are better suited for more computationally intensive applications.

LEON processors can be found in radiation-hardened application-specific integrated circuits (ASICs) such as the Atmel AT697E (LEON2 Fault-Tolerant) or the AeroFlex UT699 (LEON3 Fault-Tolerant). It is not yet known whether a fault-tolerant LEON soft core would be fault tolerant in a Xilinx SEU Immune Reconfigurable FPGA (SIRF) device.

Operating systems and how they interact with mitigation schemes were not evaluated as part of this study – they should be included in follow on efforts along with:

- Optimizing the processor hardware designs to minimize FPGA resource utilization. One particular point to investigate is why the LEON processor required so much more FPGA resources than the other two processors; in particular, why did the LEON soft-core processor consume significantly more resources than the soft-core MicroBlaze?

- Exploring low-power modes of the processors.

- Evaluating the PPC440 hard core resident in the Virtex-5 FX devices. (The PPC440 is expected to have higher performance numbers than the PPC405 tested.)

- Measuring the power consumed by the FPGA when configured with an internal hard/ soft core processor.

Xilinx and the Xilinx Radiation Testing Consortium (XRTC) are performing a great deal of mitigation and testing on the Virtex-4QV space-grade device and will continue to do so for the SIRF device. The processors that Xilinx supports are the MicroBlaze (Virtex-4 and SIRF), the PPC405 (Virtex-4) and the PPC440 (SIRF). Sandia National Laboratories (SNL) is currently positioned to help develop mitigation strategies for the SIRF device through its involvement in the XRTC. It is highly recommended that SNL continue to place a high priority on its involvement in XRTC activities.

# 2. FPGA-BASED PROCESSOR DOWN-SELECTION

The long list of processor intellectual property (IP) suitable for NBAs and its wide variety of applications was whittled down using the following criteria:

- Only 32-bit processors were considered. It was desirable to eliminate memory space addressing and paging problems associated with 8- and 16-bit devices.

- Only processors that could be outfitted with a floating-point unit (FPU) were considered.

- The search was limited to popular architectures to take advantage of economies of scale.

- Support for radiation effects testing and mitigation was desired.

Processor cores "native" to the Xilinx Virtex-5 (MicroBlaze and PPC) are attractive for use in NBAs for several reasons:

- They are inexpensive. Dual PPC440 cores are built into the FX130T device and are essentially "free" with the purchase of the FPGA itself Xilinx has paid for the PPC440 IP and built that into the sale price of the FPGA. The MicroBlaze processor is IP that is available with the purchase of the Xilinx Embedded Development Kit (EDK) software at a very affordable price of \$500. Software development tools for both processors are available as part of the EDK.

- Mitigation strategies are developed and tested by Xilinx and the XRTC. SNL is a

member and contributor to the XRTC. Xilinx and the XRTC are going to great effort to

characterize their FPGAs and to develop mitigation strategies for all of the FPGA

building blocks, including these processors. This type of development effort would be

left to the individual with non-native processors targeted to the Xilinx platform.

Xilinx native processors and the Xilinx processor design flow are not without their drawbacks, including:

- Soft-core processor and support IP can change from one release of Xilinx tools to the next, impacting the number of resources used for both system definition and mitigation. One could be "stuck" with using older Xilinx toolsets just to support a known processor and processor IP version.

- Newer versions of Xilinx tools tend to drop off support for older FPGA devices. This could be a concern several years down the NBA development path.

The risk mitigation scheme for these issues would be to include a tool archival process into the project.

A couple of popular processor IP cores that are traditionally used in System on Chip (SoC) designs and can also be targeted to FPGA platforms were initially considered but then eliminated because of IP licensing issues.

**ARC International** provides several configurable central processing unit (CPU) and digital signal processing (DSP) IP cores. However, the licensing fees for these cores were outside of the budget of this study.

ARM Ltd is the provider of the most widely used microprocessor cores. The newest cores in the ARM product line come from the ARM Cortex family. ARM has licensing fees on par with ARC. An attempt was made to obtain an evaluation license and non-disclosure agreement for characterizing ARM Cortex performance after Xilinx TMRTool mitigation. However, an agreement could not be negotiated and this effort was abandoned. Currently Actel has a license agreement with ARM to provide Cortex processors in FLASH-based FPGA devices. Unfortunately, the license agreement does not extend to anti-fuse FPGA devices. It is not expected that Actel will support anti-fuse devices with the Cortex processor in the near future.

# 3. PERFORMANCE METRICS

Dhrystone v2.1 processing metric applications (fixed-point performance) were developed for three processor types (PPC405, MicroBlaze Version 6.00.b, and LEON3) and executed on the Xilinx ML-405 and Xilinx ML-410 development boards. The main objective of this Dhrystone benchmark experiment was not only to compare the processors to each other with respect to their suitability for use in any NBA scenario, but to also see how each processor behaves when operational design parameters of the processor system are modified and how these processor designs impact FPGA resource utilization. The benchmark results shown may not match those published by manufacturers – the benchmarks included in this report are for *unoptimized* hardware and software designs.

For the PPC405 processor, configurations that were tested for multiple trials included:

- Processor speed (100 MHz to 300 MHz)

- Application location in memory (internal BlockRAM [BRAM] or external synchronous dynamic random access memory [SDRAM])

- Cache configuration (enabled or disabled)

Configurations in the MicroBlaze trials included:

- Processor speed (50 MHz to 100 MHz)

- Application location in memory (internal BRAM or external SDRAM)

- Cache configuration (enabled or disabled)

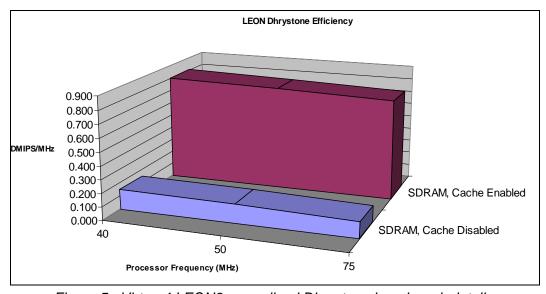

Variables in the LEON trials included:

- Processor speed (40 MHz to 75 MHz)

- Application location in external SDRAM

- Cache configuration (enabled or disabled)

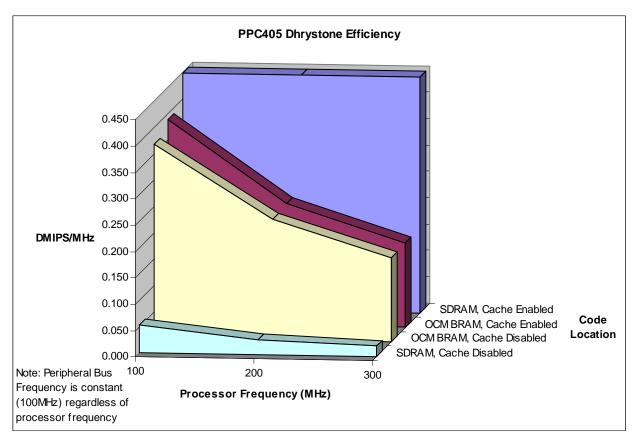

For all processors, performance increased by enabling the caches. For the PPC405, the location of the application in memory was a surprising factor – the processor was most efficient when running out of external SDRAM as opposed to the internal BRAMs of the Virtex-4. The processing efficiency of the PPC also decreased with increasing clock rates. This points to some non-optimal design of the PPC system – the peripheral bus frequency being held at a constant 100 MHz is the likely cause.

Normalized plots of the processor benchmarks show that the LEON3 is more efficient than either the MicroBlaze or PPC405 in DMIPS/MHz, but because it cannot operate at the higher frequencies that the others can it is not suitable for computationally intensive algorithms.

Whetstone v1.2 processing performance metric applications (floating-point performance) were also created for the three processors. Tests were conducted with both floating-point emulation

and with floating-point units. All three processors utilized soft-core floating-point unit (FPU) to enhance the floating-point performance of the standard core.

For the PPC405 processor, configurations that were tested with floating-point emulation were:

- Processor speed (100 MHz to 300 MHz)

- Application location in memory (internal BRAM or external SDRAM)

- Cache configuration (enabled or disabled)

IP restrictions for the PPC405 FPU used (evaluation version) limited the processor speed to a single frequency (200 MHz) when the FPU was enabled. Otherwise, the following parameters were varied:

- Application location in memory (internal BRAM or external SDRAM)

- Cache configuration (enabled or disabled)

MicroBlaze Whetstone tests included varying:

- Processor speed (50 MHz to 100 MHz)

- Application location in memory (internal BRAM or external SDRAM)

- Cache configuration (enabled or disabled)

- FPU configuration (enabled or disabled)

LEON processor Whetstone test results with the FPU enabled were a bit inconclusive and unresolved after several iterations. With the LEON processor FPU enabled and running at 20 MHz, the performance of the LEON was 8x greater than the PPC running at 200 MHz. These results are unbelievable, even though the LEON core passed all of the core validation metrics.

Independent Whetstone performance numbers for each of the three processor types were unavailable to corroborate the results that were obtained.

# 3.1 Virtex-4 Dhrystone

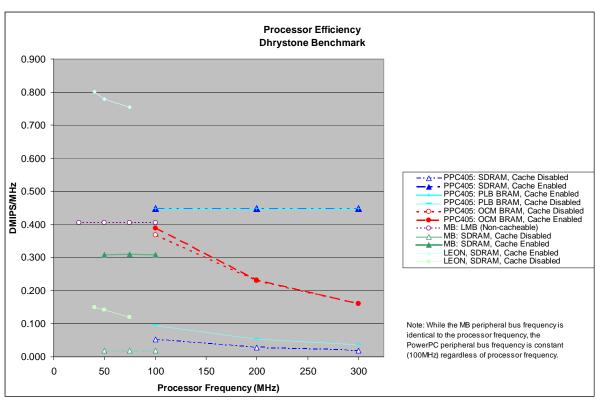

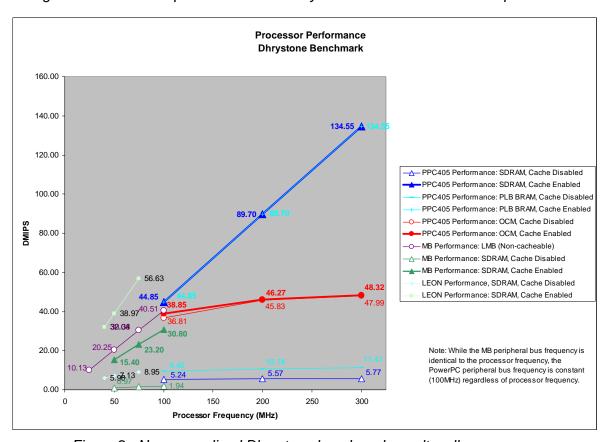

The normalized Dhrystone plot in Figure 1 shows that the LEON3 soft-core processor is more efficient than the MicroBlaze and PPC processors – especially when the cache is enabled. Computationally intensive applications are not well suited for the LEON3, however, because the maximum operational frequency of the soft core is only around 75 MHz due to FPGA timing limitations. The upper frequency tested on the soft-core MicroBlaze was 100 MHz (again, FPGA timing restrictions) and the upper frequency tested for the PowerPC405 was 300 MHz.

The on-chip memory controller (OCM) for the PPC405 shows a decline in efficiency for increasing processor frequencies.

Figure 2 shows that the PPC405 processor hard core has better raw performance than both the LEON3 and the MicroBlaze soft cores, and therefore is considered a better target for computationally intensive applications.

Figure 1. Processor speed normalized Dhrystone benchmark results: all processors.

Figure 2. Non-normalized Dhrystone benchmark results: all processors.

### 3.1.1 Virtex-4 PPC405

This section contains a summary of the PPC405 configuration used in the Dhrystone benchmark.

Processor core frequency is listed in the second column of Table 1. The on-chip peripheral bus (OPB) frequency is 100 MHz for PPC405. It is possible to modify the OPB frequency, but it was held constant during these tests for the sake of reducing configurations.

The Virtex-4 PPC405 has a *fixed* cache size: 16 Kbytes for data and 16 Kbytes for instruction. Unlike the soft core MicroBlaze and LEON3 processors, the cache size for the V4 PPC405 cannot be changed.

Local memory (BRAM) used in these tests was 32 KBytes for data and 32 Kbytes for instructions.

The size of the executable listed in Table 1 is the size of an executable created for loading via the Joint Test Action Group (JTAG) cable and not the Flash read-only memory (ROM) binary size.

Note: The Virtex-4 speed grade –10 does not allow for 400 MHz PPC405 operation (DS302, p13, CPMC405CLOCK AC switching limitations). 300 MHz was the highest PPC405 frequency tested on the ML-405 board.

The V4 PPC405 FPU can only be used up to 233 MHz in a –10 speed grade Virtex-4, an IP limitation. The highest frequency tested was 200 MHz.

Figure 3 shows the Virtex-4 PPC405 Dhrystone efficiency vs. frequency for the different configurations.

Table 1. Virtex-4 PPC405 Dhrystone Application Configuration and Memory Utilization.

|           | Pro       | cessor Se | etup     |          |           |          | Dhrystone Sc     | ores       |        |        |       | Appli | cation S | ize           |

|-----------|-----------|-----------|----------|----------|-----------|----------|------------------|------------|--------|--------|-------|-------|----------|---------------|

| Processor | Processor | FPU       | Cache    | Code     | # of Runs | Duration | Microseconds for | Dhrystones | DMIPS  | DMIPS/ | .text | .data | .bss     | Total Size of |

|           | Frequency |           |          | Location |           | (sec)    | one run through  | per Second |        | MHz    |       |       |          | Executable    |

|           | (MHz)     |           |          |          |           |          | Dhrystone        |            |        |        |       |       |          |               |

| PPC405    | 100       | Disabled  | Disabled | PLB      | 100000    | 6.02     | 60.2             | 16611.3    | 9.45   | 0.095  | 24058 | 1360  | 12936    | 38354         |

| PPC405    | 200       | Disabled  | Disabled | PLB      | 100000    | 5.30     | 53.0             | 18875.0    | 10.74  | 0.054  | 24058 | 1360  | 12936    | 38354         |

| PPC405    | 300       | Disabled  | Disabled | PLB      | 100000    | 4.99     | 49.9             | 20040.1    | 11.41  | 0.038  | 24058 | 1360  | 12936    | 38354         |

| PPC405    | 100       | Disabled  | Enabled  | PLB      | 100000    | 1.27     | 12.7             | 78801.7    | 44.85  | 0.449  | 24058 | 1364  | 12932    | 38354         |

| PPC405    | 200       | Disabled  | Enabled  | PLB      | 100000    | 0.63     | 6.3              | 157602.3   | 89.70  | 0.448  | 24058 | 1364  | 12932    | 38354         |

| PPC405    | 300       | Disabled  | Enabled  | PLB      | 100000    | 0.42     | 4.2              | 236401.8   | 134.55 | 0.448  | 24058 | 1364  | 12932    | 38354         |

| PPC405    | 100       | Disabled  | Disabled | ОСМ      | 100000    | 1.55     | 15.5             | 64683.1    | 36.81  | 0.368  | 24058 | 1360  | 18828    | 44246         |

| PPC405    | 200       | Disabled  | Disabled | OCM      | 100000    | 1.24     | 12.4             | 80515.3    | 45.83  | 0.229  | 24058 | 1360  | 12940    | 38358         |

| PPC405    | 300       | Disabled  | Disabled | OCM      | 100000    | 1.19     | 11.9             | 84317.0    | 47.99  | 0.160  | 24058 | 1360  | 12940    | 38358         |

| PPC405    | 100       | Disabled  | Enabled  | OCM      | 100000    | 1.47     | 14.7             | 68259.4    | 38.85  | 0.388  | 24058 | 1364  | 18824    | 44246         |

| PPC405    | 200       | Disabled  | Enabled  | OCM      | 100000    | 1.23     | 12.3             | 81300.8    | 46.27  | 0.231  | 24058 | 1364  | 12936    | 38358         |

| PPC405    | 300       | Disabled  | Enabled  | ОСМ      | 100000    | 1.18     | 11.8             | 84889.6    | 48.32  | 0.161  | 24058 | 1364  | 12936    | 38358         |

| PPC405    | 200       | Disabled  | Disabled | OPBRAM   | 100000    | 10.69    | 106.9            | 9351.9     | 5.32   | 0.027  | 24058 | 1360  | 12948    | 38366         |

| PPC405    | 200       | Disabled  | Enabled  | OPBRAM   | 100000    | 0.63     | 6.3              | 157599.8   | 89.70  | 0.448  | 24058 | 1364  | 12940    | 38362         |

| PPC405    | 100       | Disabled  | Disabled | SDRAM    | 100000    | 10.86    | 108.6            | 9205.9     | 5.24   | 0.052  | 24058 | 1360  | 18824    | 44242         |

| PPC405    | 200       | Disabled  | Disabled | SDRAM    | 100000    | 10.22    | 102.2            | 9784.7     | 5.57   | 0.028  | 24058 | 1360  | 12936    | 38354         |

| PPC405    | 300       | Disabled  | Disabled | SDRAM    | 100000    | 9.87     | 98.7             | 10133.5    | 5.77   | 0.019  | 24058 | 1360  | 12936    | 38354         |

| PPC405    | 100       | Disabled  | Enabled  | SDRAM    | 100000    | 1.27     | 12.7             | 78801.2    | 44.85  | 0.448  | 24058 | 1364  | 18820    | 44242         |

| PPC405    | 200       | Disabled  | Enabled  | SDRAM    | 100000    | 0.63     | 6.3              | 157600.2   | 89.70  | 0.448  | 24058 | 1364  | 12932    | 38354         |

| PPC405    | 300       | Disabled  | Enabled  | SDRAM    | 100000    | 0.42     | 4.2              | 236397.2   | 134.55 | 0.448  | 24058 | 1364  | 12932    | 38354         |

Figure 3. Normalized Dhrystone benchmark details: Virtex-4 PPC405.

### 3.1.2 MicroBlaze

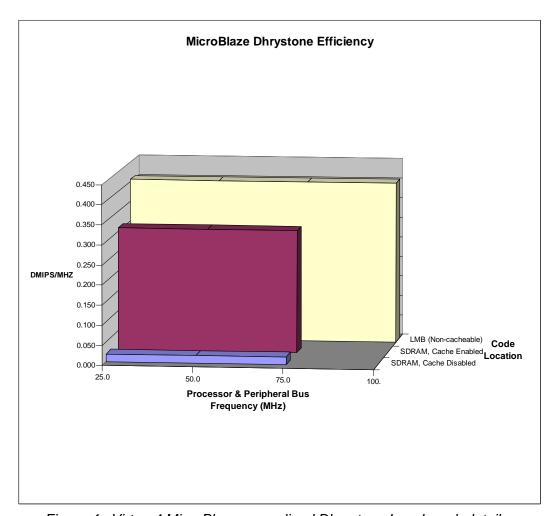

This section contains a summary of the MicroBlaze configuration used in the Dhrystone benchmark.

Processor core frequency is listed in the second column of Table 2. The OPB frequency was equal to the processor frequency for the MicroBlaze.

The MicroBlaze has a *programmable* cache size. For this test 16 Kbytes for data and 16 Kbytes for instruction cache were defined. The cache is comprised of BRAM blocks.

The size of the executable listed in Table 1 is the size of an executable created for loading via the JTAG cable and is not the Flash ROM binary size.

The MicroBlaze is capable of utilizing internal Virtex-4 BRAM as program/data space with the Local Memory Bus (LMB) IP.

Figure 4 shows the MicroBlaze Dhrystone efficiency vs. frequency for the different configurations.

Table 2. Virtex-4 MicroBlaze Dhrystone Application Configuration and Memory Utilization.

|           | Pro                             | cessor Se | tup      |                  |           |                   | Dhrystone Sco                                    | ores                  |        |               |       | Appli | cation S | ze                          |

|-----------|---------------------------------|-----------|----------|------------------|-----------|-------------------|--------------------------------------------------|-----------------------|--------|---------------|-------|-------|----------|-----------------------------|

| Processor | Processor<br>Frequency<br>(MHz) | FPU       | Cache    | Code<br>Location | # of Runs | Duration<br>(sec) | Microseconds for<br>one run through<br>Dhrystone | Dhrystones per Second | DMIPS  | DMIPS/<br>MHz | .text | .data | .bss     | Total Size of<br>Executable |

| MB        | 25                              | Disabled  | Disabled | LMB              | 100000    | 5.62              | 56.2                                             | 17793.6               | 10.13  | 0.405         | 13052 | 3146  | 12896    | 29094                       |

| MB        | 50                              | Disabled  | Disabled | LMB              | 100000    | 2.81              | 28.1                                             | 35587.2               | 20.25  | 0.405         | 13052 | 3146  | 12896    | 29094                       |

| MB        | 75                              | Disabled  | Disabled | LMB              | 100000    | 1.87              | 18.7                                             | 53380.8               | 30.38  | 0.405         | 13040 | 3146  | 12900    | 29086                       |

| MB        | 100                             | Disabled  | Disabled | LMB              | 100000    | 1.41              | 14.1                                             | 71174.4               | 40.51  | 0.405         | 13048 | 3146  | 12900    | 29094                       |

| MB        | 25                              | Disabled  | Disabled | SDRAM            | 100000    | would not run     | #VALUE!                                          | #VALUE!               | ###### | ######        | 14108 | 3146  | 12896    | 30150                       |

| MB        | 50                              | Disabled  | Disabled | SDRAM            | 100000    | 58.82             | 588.2                                            | 1700.2                | 0.97   | 0.019         | 14108 | 3146  | 12896    | 30150                       |

| MB        | 75                              | Disabled  | Disabled | SDRAM            | 100000    | 39.34             | 393.4                                            | 2541.9                | 1.45   | 0.019         | 14096 | 3146  | 12900    | 30142                       |

| MB        | 100                             | Disabled  | Disabled | SDRAM            | 100000    | 29.41             | 294.1                                            | 3400.5                | 1.94   | 0.019         | 14104 | 3146  | 12900    | 30150                       |

| MB        | 25                              | Disabled  | Enabled  | SDRAM            | 100000    | would not run     | #VALUE!                                          | #VALUE!               | ###### | ######        | 14108 | 3150  | 12892    | 30150                       |

| MB        | 50                              | Disabled  | Enabled  | SDRAM            | 100000    | 3.70              | 37.0                                             | 27057.1               | 15.40  | 0.308         | 14108 | 3150  | 12892    | 30150                       |

| MB        | 75                              | Disabled  | Enabled  | SDRAM            | 100000    | 2.45              | 24.5                                             | 40766.7               | 23.20  | 0.309         | 14096 | 3150  | 12888    | 30134                       |

| MB        | 100                             | Disabled  | Enabled  | SDRAM            | 100000    | 1.85              | 18.5                                             | 54114.3               | 30.80  | 0.308         | 14104 | 3150  | 12888    | 30142                       |

Figure 4. Virtex-4 MicroBlaze normalized Dhrystone benchmark details.

#### 3.1.3 LEON3

This section contains a summary of the LEON3 configuration used in the Dhrystone benchmark.

The processor frequency is equal to the core frequency listed in Table 3.

Table 3. Virtex-4 LEON3 Dhrystone Application Configuration and Memory Utilization.

|           |                                 | Processo                 | r Setup  |          |                  |           |                   | Dhrysto | ne Scores             |             |               |       | Applicat | ion Size |                                  |       |

|-----------|---------------------------------|--------------------------|----------|----------|------------------|-----------|-------------------|---------|-----------------------|-------------|---------------|-------|----------|----------|----------------------------------|-------|

| Processor | Processor<br>Frequency<br>(MHz) | mv8<br>Compile<br>Switch | FPU      | Cache    | Code<br>Location | # of Runs | Duration<br>(sec) |         | Dhrystones per Second |             | DMIPS/M<br>Hz | .text | .data    | .bss     | Total Size<br>of Execu-<br>table | Notes |

| LEON      | 25                              | Disabled                 | Disabled | Disabled | SDRAM            | 200000    |                   |         | Would                 | not synthe  |               |       |          |          |                                  |       |

| LEON      | 40                              | Disabled                 | Disabled | Disabled | SDRAM            | 200000    | 20.958            | 104.79  | 9542.9                |             |               | 50432 | 2464     | 10772    | 52896                            |       |

| LEON      | 50                              | Disabled                 | Disabled | Disabled | SDRAM            | 200000    | 17.657            | 88.29   | 11327.0               | 6.45        | 0.129         | 50432 | 2464     | 10772    | 52896                            |       |

| LEON      | 75                              | Disabled                 | Disabled | Disabled | SDRAM            | 200000    | 14.022            | 70.11   |                       |             |               | 50432 | 2464     | 10772    | 52896                            |       |

| LEON      | 25                              | Disabled                 | Disabled | Enabled  | SDRAM            | 200000    |                   |         |                       | d not synth |               |       |          |          |                                  |       |

| LEON      | 40                              | Disabled                 | Disabled | Enabled  | SDRAM            | 200000    | 3.828             |         |                       |             |               | 50432 |          | 10772    | 52896                            |       |

| LEON      | 50                              | Disabled                 | Disabled | Enabled  | SDRAM            | 200000    | 3.138             | 15.69   |                       |             |               | 50432 |          | 10772    |                                  |       |

| LEON      | 75                              | Disabled                 | Disabled | Enabled  |                  | 200000    | 2.157             | 10.79   | 92721.4               | 52.77       | 0.704         | 50432 | 2464     | 10772    | 52896                            |       |

| LEON      | 25                              | Enabled                  | Disabled | Disabled | SDRAM            | 200000    |                   |         | Woul                  | d not synth | esize         |       |          |          |                                  |       |

| LEON      | 40                              | Enabled                  | Disabled | Disabled | SDRAM            | 200000    | 19.042            |         |                       |             |               | 50416 |          | 10772    |                                  |       |

| LEON      | 50                              | Enabled                  |          | Disabled | SDRAM            | 200000    | 15.969            |         |                       |             |               | 50416 |          | 10772    |                                  |       |

| LEON      | 75                              | Enabled                  | Disabled | Disabled | SDRAM            | 200000    | 12.713            | 63.57   |                       |             |               | 50416 | 2464     | 10772    | 52880                            |       |

| LEON      | 25                              | Enabled                  | Disabled | Enabled  | SDRAM            | 200000    |                   |         |                       | d not synth |               |       |          |          |                                  |       |

| LEON      | 40                              | Enabled                  | Disabled | Enabled  | SDRAM            | 200000    | 3.553             |         |                       |             |               | 50416 |          | 10772    |                                  |       |

| LEON      | 50                              | Enabled                  | Disabled | Enabled  |                  | 200000    | 2.921             | 14.61   |                       |             |               | 50416 |          | 10772    |                                  |       |

| LEON      | 75                              | Enabled                  | Disabled | Enabled  | SDRAM            | 200000    | 2.010             | 10.05   | 99502.5               | 56.63       | 0.755         | 50416 | 2464     | 10772    | 52880                            |       |

The LEON3 has an *extremely programmable* cache size. For this test 16 Kbytes for data and 16 Kbytes for instruction cache were defined.

There are fewer memory configuration options for LEON3 than for MicroBlaze and Virtex-4 PPC405 processors for the ML-405 and ML-410 platforms; all LEON code was located in SDRAM for these tests. The LEON3 configuration utility is FPGA platform independent and does not know how to construct a processor memory block from the internal Virtex-4 BRAMs.

Figure 5 shows the MicroBlaze Dhrystone efficiency vs. frequency for the different configurations.

Figure 5. Virtex-4 LEON3 normalized Dhrystone benchmark details.

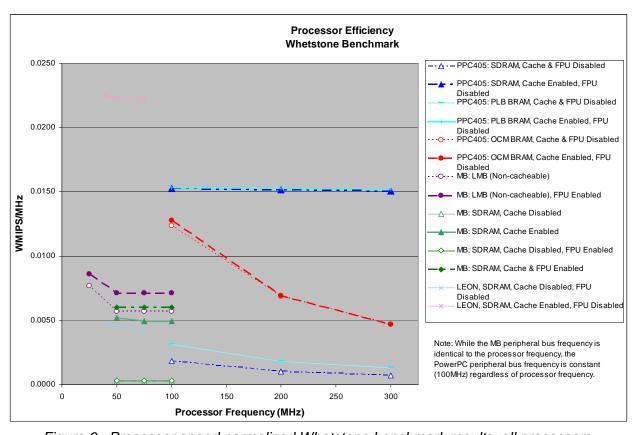

## 3.2 Virtex-4 Whetstone

The normalized Whetstone plot in Figure 6 shows that the LEON3 soft-core processor is more efficient than the MicroBlaze and PPC processors – especially when the cache is enabled. Computationally intensive applications are not well suited for the LEON3, however, because its raw performance is limited by the maximum synthesizable core frequency (75 MHz on the Virtex-4 –10 speed-grade). The PPC FPU was compiled into the hardware design for the Whetstone tests discussed in this section.

The OCM for the PPC405 again shows a decline in efficiency for increasing processor frequencies.

Figure 6. Processor speed normalized Whetstone benchmark results: all processors.

Figure 7 shows that the PPC405 processor hard core outperforms both the LEON3 and the MicroBlaze soft cores, and therefore is considered a better target for computationally intensive applications.

Figure 7. Non-normalized Whetstone benchmark results: all processors.

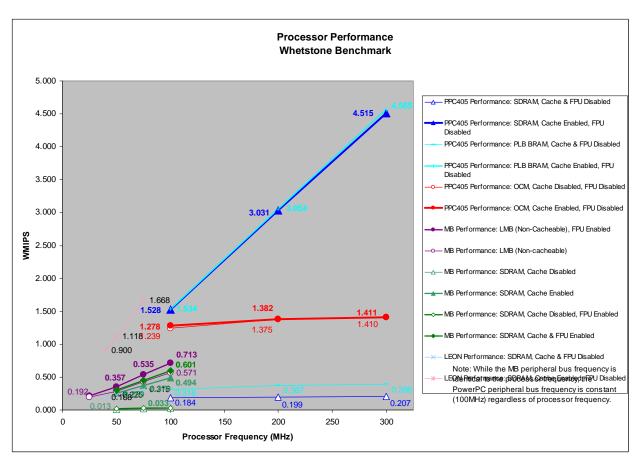

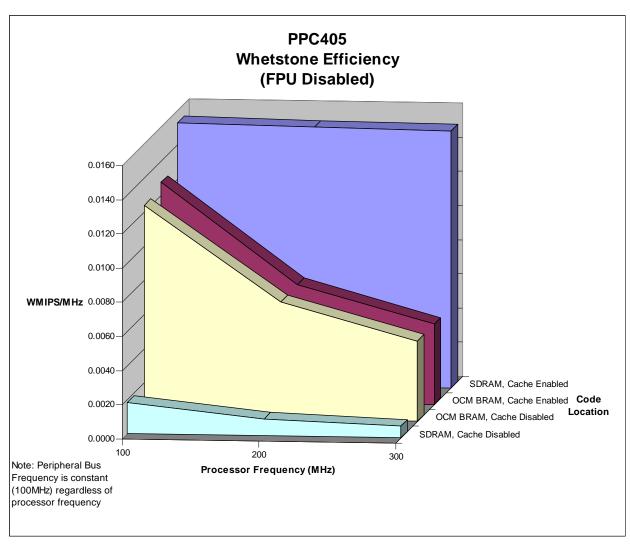

#### 3.2.1 Virtex-4 PPC405

This section contains a summary of the PPC405 configuration used in the Whetstone benchmark.

Processor core frequency is listed in the second column of Table 4. The OPB frequency is 100 MHz for PPC405. It is possible to modify the OPB frequency, but it was held constant during these tests for the sake of reducing configurations.

Note: The PPC405 FPU can only be used when the peripheral frequency is exactly 1/2 the processor frequency.

The Virtex-4 PPC405 has a *fixed* cache size: 16 Kbytes for data and 16 Kbytes for instruction. Unlike the soft core MicroBlaze and LEON3 processors, the cache size for the Virtex-4 PPC405 cannot be changed.

Table 4. Virtex-4 PPC405 Whetstone Application Configuration and Memory Utilization.

|           | Pro                             | cessor se | tup      |                  |            | Single Preci       | ision FP W        | hetstone Sco         | res       |       | Application Size |      |                             |                            |  |

|-----------|---------------------------------|-----------|----------|------------------|------------|--------------------|-------------------|----------------------|-----------|-------|------------------|------|-----------------------------|----------------------------|--|

| Processor | Processor<br>Frequency<br>(MHz) | FPU       | Cache    | Code<br>Location | # of loops | # of<br>Iterations | Duration<br>(sec) | Whetstones<br>(MIPS) | WMIPS/MHz | .text | .data            | .bss | Total Size of<br>Executable | Speed-<br>Up Due<br>to FPU |  |

| PPC405    | 100                             | Disabled  | Disabled | PLB              | 30         | 1                  | 9.442             | 0.318                | 0.0032    | 42613 | 324              | 2676 | 45613                       |                            |  |

| PPC405    | 200                             | Disabled  | Disabled | PLB              | 30         | 1                  | 8.168             | 0.367                | 0.0018    | 42613 | 324              | 2676 | 45613                       |                            |  |

| PPC405    | 300                             | Disabled  | Disabled | PLB              | 30         | 1                  | 7.571             | 0.396                | 0.0013    | 42613 | 324              | 2676 | 45613                       |                            |  |

| PPC405    | 200                             | Enabled   | Disabled | PLB              | 30         | 1                  | 6.279             | 0.478                | 0.0024    | 40257 | 324              | 2684 | 43265                       | 23%                        |  |

| PPC405    | 100                             | Disabled  | Enabled  | PLB              | 30         | 1                  | 1.956             | 1.534                | 0.0153    | 42613 | 328              | 2672 | 45613                       |                            |  |

| PPC405    | 200                             | Disabled  | Enabled  | PLB              | 30         | 1                  | 0.982             | 3.054                | 0.0153    | 42613 | 328              | 2672 | 45613                       |                            |  |

| PPC405    | 300                             | Disabled  | Enabled  | PLB              | 30         | 1                  | 0.657             | 4.565                | 0.0152    | 42613 | 328              | 2672 | 45613                       |                            |  |

| PPC405    | 200                             | Enabled   | Enabled  | PLB              | 30         | 1                  | 0.789             | 3.803                | 0.0190    | 40257 | 328              | 2680 | 43265                       | 20%                        |  |

| PPC405    | 100                             | Disabled  | Disabled | OCM              | 30         | 1                  | 2.421             | 1.239                | 0.0124    | 42613 | 324              | 2676 | 45613                       |                            |  |

| PPC405    | 200                             | Disabled  | Disabled | OCM              | 30         | 1                  | 2.182             | 1.375                | 0.0069    | 42613 | 324              | 2676 | 45613                       |                            |  |

| PPC405    | 300                             | Disabled  | Disabled | OCM              | 30         | 1                  | 2.128             | 1.410                | 0.0047    | 42613 | 324              | 2676 | 45613                       |                            |  |

| PPC405    | 200                             | Enabled   | Disabled | OCM              | 30         | 1                  | 1.714             | 1.750                | 0.0088    | 40257 | 324              | 2676 | 43257                       | 21%                        |  |

| PPC405    | 100                             | Disabled  | Enabled  | OCM              | 30         | 1                  | 2.347             | 1.278                | 0.0128    | 42613 | 328              | 2672 | 45613                       |                            |  |

| PPC405    | 200                             | Disabled  | Enabled  | OCM              | 30         | 1                  | 2.171             | 1.382                | 0.0069    | 42613 | 328              | 2672 | 45613                       |                            |  |

| PPC405    | 300                             | Disabled  | Enabled  | OCM              | 30         | 1                  | 2.126             | 1.411                | 0.0047    | 42613 | 328              | 2672 | 45613                       |                            |  |

| PPC405    | 200                             | Enabled   | Enabled  | OCM              | 30         | 1                  | 1.700             | 1.765                | 0.0088    | 40257 | 328              | 2672 | 43257                       | 22%                        |  |

| PPC405    | 100                             | Disabled  | Disabled | SDRAM            | 30         | 1                  | 16.346            | 0.184                | 0.0018    | 42613 | 324              | 2676 | 45613                       |                            |  |

| PPC405    | 200                             | Disabled  | Disabled | SDRAM            | 30         | 1                  | 15.047            | 0.199                | 0.0010    | 42613 | 324              | 2676 | 45613                       |                            |  |

| PPC405    | 300                             | Disabled  | Disabled | SDRAM            | 30         | 1                  | 14.461            | 0.207                | 0.0007    | 42613 | 324              | 2676 | 45613                       |                            |  |

| PPC405    | 200                             | Enabled   | Disabled | SDRAM            | 30         | 1                  | 11.489            | 0.261                | 0.0013    | 40257 | 324              | 2684 | 43265                       | 24%                        |  |

| PPC405    | 100                             | Disabled  | Enabled  | SDRAM            | 30         | 1                  | 1.963             | 1.528                | 0.0153    | 42613 | 328              | 2672 | 45613                       |                            |  |

| PPC405    | 200                             | Disabled  | Enabled  | SDRAM            | 30         | 1                  | 0.990             | 3.031                | 0.0152    | 42613 | 328              | 2672 | 45613                       |                            |  |

| PPC405    | 300                             | Disabled  | Enabled  | SDRAM            | 30         | 1                  | 0.664             | 4.515                | 0.0150    | 42613 | 328              | 2672 | 45613                       |                            |  |

| PPC405    | 200                             | Enabled   | Enabled  | SDRAM            | 30         | 1                  | 0.796             | 3.770                | 0.0189    | 40257 | 328              | 2680 | 43265                       | 20%                        |  |

| PPC405    | 200                             | Disabled  | Disabled | OPBRAM           | 30         | 1                  | 16.040            | 0.187                | 0.0009    | 42613 | 324              | 2676 | 45613                       |                            |  |

| PPC405    | 200                             | Disabled  | Enabled  | OPBRAM           | 30         | 1                  | 0.992             | 3.025                | 0.0151    | 42613 | 328              | 2672 | 45613                       |                            |  |

Figures 8 and 9 show graphically the Whetstone performance of the PPC405 processor for different memory configurations.

Figure 8. Virtex-4 PPC405 normalized Whetstone benchmark details, FPU disabled.

Figure 9. Virtex-4 PPC405 normalized Whetstone benchmark details, FPU enabled.

### 3.2.2 MicroBlaze

This section contains a summary of the MicroBlaze configuration used in the Whetstone benchmark.

Processor core frequency is listed in the second column of Table 5. The OPB frequency was equal to the processor frequency for the MicroBlaze.

The MicroBlaze has a *programmable* cache size. For this test 16 Kbytes for data and 16 Kbytes for instruction cache were defined. The cache is comprised of BRAM blocks.

The size of the executable listed in Table 5 is the size of an executable created for loading via the JTAG cable and is not the Flash ROM binary size.

Table 5. Virtex-4 MicroBlaze Whetstone Application Configuration and Memory Utilization.

|           | Pro       | cessor set | tup      |          |            | Single Preci | sion FP W     | hetstone Sco | res       |       | Appl  | lication | ı Size        |        |

|-----------|-----------|------------|----------|----------|------------|--------------|---------------|--------------|-----------|-------|-------|----------|---------------|--------|

| Processor | Processor | FPU        | Cache    | Code     | # of loops | # of         | Duration      | Whetstones   | WMIPS/MHz | .text | .data | .bss     | Total Size of | Speed- |

|           | Frequency |            |          | Location |            | Iterations   | (sec)         | (MIPS)       |           |       |       |          | Executable    | Up Due |

|           | (MHz)     |            |          |          |            |              |               |              |           |       |       |          |               | to FPU |

| MB        | 25        | Disabled   | Disabled | LMB      | 10         | 1            | 5.203         | 0.192        | 0.0077    | 42328 | 2626  | 2632     | 47586         |        |

| MB        | 50        | Disabled   | Disabled | LMB      | 10         | 1            | 3.504         | 0.285        | 0.0057    | 42328 | 2626  | 2632     | 47586         |        |

| MB        | 75        | Disabled   | Disabled | LMB      | 10         | 1            | 2.336         | 0.428        | 0.0057    | 42328 | 2626  | 2632     | 47586         |        |

| MB        | 100       | Disabled   | Disabled | LMB      | 10         | 1            | 1.752         | 0.571        | 0.0057    | 42324 | 2626  | 2636     | 47586         |        |

| MB        | 25        | Enabled    | Disabled | LMB      | 10         | 1            | 4.644         | 0.215        | 0.0086    | 39236 | 2610  | 2636     | 44482         | 11%    |

| MB        | 50        | Enabled    | Disabled | LMB      | 10         | 1            | 2.805         | 0.357        | 0.0071    | 39232 | 2610  | 2636     | 44478         | 20%    |

| MB        | 75        | Enabled    | Disabled | LMB      | 10         | 1            | 1.870         | 0.535        | 0.0071    | 39232 | 2610  | 2636     | 44478         | 20%    |

| MB        | 100       | Enabled    | Disabled | LMB      | 10         | 1            | 1.402         | 0.713        | 0.0071    | 39232 | 2610  | 2636     | 44478         | 20%    |

| MB        | 25        | Disabled   | Disabled | SDRAM    | 10         | 1            | would not run | #VALUE!      | #VALUE!   | 42360 |       | 2632     | 47618         |        |

| MB        | 50        | Disabled   | Disabled | SDRAM    | 10         | 1            | 75.907        | 0.013        | 0.0003    | 42360 | 2626  | 2632     | 47618         |        |

| MB        | 75        | Disabled   | Disabled | SDRAM    | 10         | 1            | 51.027        | 0.020        | 0.0003    | 42360 | 2626  | 2632     | 47618         |        |

| MB        | 100       | Disabled   | Disabled | SDRAM    | 10         | 1            | 37.998        | 0.026        | 0.0003    | 42356 | 2626  | 2636     | 47618         |        |

| MB        | 25        | Enabled    | Disabled | SDRAM    | 10         | 1            | would not run | #VALUE!      | #VALUE!   | 39268 | 2610  | 2628     | 44506         |        |

| MB        | 50        | Enabled    | Disabled | SDRAM    | 10         | 1            | 60.756        | 0.016        | 0.0003    | 39264 |       | 2624     | 44502         | 20%    |

| MB        | 75        | Enabled    | Disabled | SDRAM    | 10         | 1            | 40.880        | 0.024        | 0.0003    | 39256 | 2610  | 2636     | 44502         | 20%    |

| MB        | 100       | Enabled    | Disabled | SDRAM    | 10         | 1            | 30.430        | 0.033        | 0.0003    | 39256 |       | 2636     | 44502         | 20%    |

| MB        | 25        | Disabled   | Enabled  | SDRAM    | 10         | 1            | would not run | #VALUE!      | #VALUE!   | 42356 | 2630  | 2624     | 47610         |        |

| MB        | 50        | Disabled   | Enabled  | SDRAM    | 10         | 1            | 3.867         | 0.259        | 0.0052    | 42356 |       | 2624     | 47610         |        |

| MB        | 75        | Disabled   | Enabled  | SDRAM    | 10         | 1            | 2.703         | 0.370        | 0.0049    | 42356 | 2630  | 2624     | 47610         |        |

| MB        | 100       | Disabled   | Enabled  | SDRAM    | 10         | 1            | 2.026         | 0.494        | 0.0049    | 42356 | 2630  | 2624     | 47610         |        |

| MB        | 25        | Enabled    | Enabled  | SDRAM    | 10         | 1            | would not run | #VALUE!      | #VALUE!   | 39268 | 2614  | 2628     | 44510         |        |

| MB        | 50        | Enabled    | Enabled  | SDRAM    | 10         | 1            | 3.333         | 0.300        | 0.0060    | 39264 | 2614  | 2624     | 44502         | 14%    |

| MB        | 75        | Enabled    | Enabled  | SDRAM    | 10         | 1            | 2.225         | 0.449        | 0.0060    | 39256 | 2614  | 2624     | 44494         | 18%    |

| MB        | 100       | Enabled    | Enabled  | SDRAM    | 10         | 1            | 1.665         | 0.601        | 0.0060    | 39256 | 2614  | 2624     | 44494         | 18%    |

Figures 10 and 11 show graphically the Whetstone efficiency of the MicroBlaze processor for different memory, code, and FPU configurations. There is approximately a 20% increase in Whetstone efficiency when using a hardware-based FPU over an emulated FPU.

Figure 10. Virtex-4 MicroBlaze normalized Whetstone benchmark details, FPU disabled.

Figure 11. Virtex-4 MicroBlaze normalized Whetstone benchmark details, FPU enabled.

### 3.2.3 LEON3

The Whetstone efficiency of the Leon processor was much higher than that of the MicroBlaze and the PPC. This anomaly was not fully investigated due to time constraints but should be investigated further. Some possible explanations: (1) the MicroBlaze C compiler may not have been generating machine code to take advantage of the hardware FPU, and (2) the timer on the LEON3 may not have been calibrated correctly, skewing the overall run times.

This section contains a summary of the LEON3 configuration used in the Whetstone benchmark.

The processor frequency is equal to the core frequency listed in Table 6.

The LEON3 has an *extremely programmable* cache size. For this test 16 Kbytes for data and 16 Kbytes for instruction cache were defined.

There are fewer memory configuration options for LEON3 than for MicroBlaze and Virtex-4 PPC405 processors for the ML-405 and ML-410 platforms; all LEON code was located in SDRAM for these tests. The LEON3 configuration utility is FPGA platform independent and does not know how to construct a processor memory block from the internal Virtex-4 BRAMs.

The "mv8" compiler switch allows the issuing of hardware multiply and divide instructions – this compiler switch was required for proper LEON FPU operation.

|           |           | Processo | r setup  |          |          | Sin        | gle Precisi | on FP Whe | tstone Sco | ores    |       | Applicat | ion Size |            |          |                             |

|-----------|-----------|----------|----------|----------|----------|------------|-------------|-----------|------------|---------|-------|----------|----------|------------|----------|-----------------------------|

| Processor | Processor | mv8      | FPU      | Cache    | Code     | # of loops | # of        |           |            | WMIPS/M | .text | .data    | .bss     | Total Size |          |                             |

|           | Frequency | Compile  |          |          | Location |            | Iterations  | (sec)     | es (MIPS)  | Hz      |       |          |          | of         | Speed-Up |                             |

|           | (MHz)     | Switch   |          |          |          |            |             |           |            |         |       |          |          | Executabl  | Due to   |                             |

|           |           |          |          |          |          |            |             |           |            |         |       |          |          | е          | FPU      | Notes                       |

| LEON      | 25        |          |          | Disabled | SDRAM    | 100        | 1           |           |            |         |       |          |          |            |          | Would not synthesize        |

| LEON      | 40        |          |          | Disabled | SDRAM    | 100        | 1           | 61.157    | 0.164      | 0.0041  | 55104 | 2480     | 596      | 57584      |          |                             |

| LEON      | 50        |          | Disabled | Disabled | SDRAM    | 100        | 1           | 51.038    | 0.196      | 0.0039  | 55104 | 2480     | 596      | 57584      |          |                             |

| LEON      | 75        |          |          | Disabled | SDRAM    | 100        | 1           | 39.999    | 0.250      | 0.0033  | 55104 | 2480     | 596      | 57584      |          |                             |

| LEON      | 25        | Disabled | Disabled | Enabled  | SDRAM    | 100        | 1           |           |            |         |       |          |          |            |          | Would not synthesize        |

| LEON      | 40        |          | Disabled | Enabled  | SDRAM    | 100        | 1           | 14.232    | 0.703      | 0.0176  | 55104 | 2480     | 596      | 57584      |          |                             |

| LEON      | 50        | Disabled | Disabled | Enabled  | SDRAM    | 100        | 1           | 11.433    | 0.875      | 0.0175  | 55104 | 2480     | 596      | 57584      |          |                             |

| LEON      | 75        | Disabled | Disabled | Enabled  | SDRAM    | 100        | 1           | 7.658     | 1.306      | 0.0174  | 55104 | 2480     | 596      | 57584      |          |                             |

| LEON      | 25        | Disabled | Enabled  | Enabled  | SDRAM    | 500        | 1           |           |            |         |       |          |          |            |          | Would not synthesize        |

| LEON      | 40        | Disabled | Enabled  | Enabled  | SDRAM    | 500        | 1           | 2.452     | 20.392     | 0.5098  | 45648 | 2480     | 596      | 48128      |          | # of loops increased to 500 |

| LEON      | 50        | Disabled | Enabled  | Enabled  | SDRAM    | 500        | 1           | 3.923     | 12.745     | 0.2549  | 45648 | 2480     | 596      | 48128      |          | # of loops increased to 500 |

| LEON      | 75        | Disabled | Enabled  | Enabled  | SDRAM    | 500        | 1           |           |            |         |       |          |          |            |          | Would not meet timing       |

| LEON      | 25        | Enabled  | Disabled | Disabled | SDRAM    | 100        | 1           |           |            |         |       |          |          |            |          | Would not synthesize        |

| LEON      | 40        | Enabled  | Disabled | Disabled | SDRAM    | 100        | 1           | 53.085    | 0.188      | 0.0047  | 55056 | 2480     | 596      | 57536      |          |                             |

| LEON      | 50        | Enabled  | Disabled | Disabled | SDRAM    | 100        | 11          | 44.368    | 0.225      | 0.0045  | 55056 | 2480     | 596      | 57536      |          |                             |

| LEON      | 75        | Enabled  | Disabled | Disabled | SDRAM    | 100        | 1           | 31.719    | 0.315      | 0.0042  | 55056 | 2480     | 596      | 57536      |          |                             |

| LEON      | 25        | Enabled  | Disabled | Enabled  | SDRAM    | 100        | 1           |           |            |         |       |          |          |            |          | Would not synthesize        |

| LEON      | 40        | Enabled  | Disabled | Enabled  | SDRAM    | 100        | 1           | 11.117    | 0.900      | 0.0225  | 55056 | 2480     | 596      | 57536      |          |                             |

| LEON      | 50        | Enabled  | Disabled | Enabled  | SDRAM    | 100        | 1           | 8.942     | 1.118      | 0.0224  | 55056 | 2480     | 596      | 57536      |          |                             |

| LEON      | 75        | Enabled  | Disabled | Enabled  | SDRAM    | 100        | 1           | 5.997     | 1.668      | 0.0222  | 55056 | 2480     | 596      | 57536      |          |                             |

| LEON      | 25        | Enabled  | Enabled  | Enabled  | SDRAM    | 500        | 1           |           |            |         |       |          |          |            |          | Would not synthesize        |

| LEON      | 40        | Enabled  | Enabled  | Enabled  | SDRAM    | 500        | 1           | 2.066     | 24.201     | 0.6050  | 45536 | 2480     | 596      | 48016      |          | # of loops increased to 500 |

| LEON      | 50        | Enabled  | Enabled  | Enabled  | SDRAM    | 500        | 1           | 3.306     | 15.124     | 0.3025  | 45536 | 2480     | 596      | 48016      |          | # of loops increased to 500 |

| LEON      | 75        | Enabled  | Enabled  | Enabled  | SDRAM    | 500        | 1           |           |            |         |       |          |          |            |          | Would not meet timing       |

Table 6. Virtex-4 LEON3 Whetstone Application Configuration and Memory Utilization.

## 3.3 Virtex-4 Resources

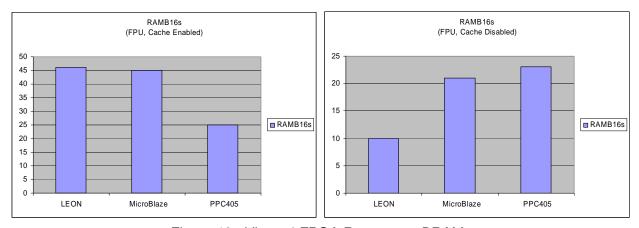

Figures 12 through 18 summarize the Virtex-4 FPGA resources consumed by the three different processors tested for the hardware configuration extremes (Cache and FPU enabled/disabled). These numbers are dependent on the processor configuration (peripherals) – the processors tested consisted of "default" configurations and may not be representative of a fully optimized hardware design.

Figure 12. Virtex-4 FPGA Resources: Slice Flip-Flops.

Figure 13. Virtex-4 FPGA Resources: Occupied Slices.

Figure 14. Virtex-4 FPGA Resources: Lookup Tables.

Figure 15. Virtex-4 FPGA Resources: Clock Buffers.

Figure 16. Virtex-4 FPGA Resources: Digital Clock Managers.

Figure 17. Virtex-4 FPGA Resources: DSP Blocks.

Figure 18. Virtex-4 FPGA Resources: BRAMs.

### 3.3.1 Virtex-4 PPC405

This section and Table 7 contains a summary of the Virtex-4 FPGA resources consumed by the PPC405 configuration used in the Dhrystone and Whetstone benchmarks. Since the processor itself is a hard-core processor, FPGA resources are only needed to realize external "glue-logic" building blocks such as memory controllers and for peripherals such as Universal Asynchronous Receiver/Transmitters (UARTs). The FPU for the PPC405 was realized using FPGA resources – it is not part of the hard core itself.

The instruction and data caches for the PPC405 are internal to the hard core itself – no BRAM blocks are used in the cache structure. The PPC405 requires the use of internal BRAM to boot initially but is quite flexible in the number of internal and external memory configurations that are possible.

Several PPC405 design requirements drive how the processor memory map can be optimally defined and ultimately how to best use internal BRAM:

- The processor must boot from address 0xFFFFFFC.

- The interrupt vector table must be aligned on a 64 Kbyte address boundary.

- The interrupt vector table length is 0x20C4 bytes long (8K + 196 bytes) and does not fit well within the address spaces definable through EDK Platform Studio (multiples of 4K, 8K, and 16K bytes).

One possible PPC405 memory architecture defines in BRAM the last 64 Kbyte memory space that includes the boot vector (0xFFFF0000 to 0xFFFFFFF). This block could contain the interrupt vector table, the boot vector, and has some space left over for code or data. This configuration is problematic when considering the recommended BRAM single-event upset (SEU) mitigation scheme (see XAPP962), as this scheme requires a three-fold increase in BRAM resources for triple-mode redundancy. For an optimally configured PPC405 (interrupt vectors located in BRAM), the TMR requirements for the BRAMs will consume a large number of FPGA resources.

#### 3.3.2 MicroBlaze

This section and Table 8 contains a summary of the Virtex-4 FPGA resources consumed by the MicroBlaze configuration used in the Dhrystone and Whetstone benchmarks. Since the processor itself is a soft-core processor, FPGA resources are needed to realize the entire processor, caches, memory controllers, FPU, and peripherals.

Table 7. Virtex-4 PPC405 System FPGA Resource Utilization.

|           | Proc                            | cessor setu | ıp       |                  |                     |                    |      |       |          |        |          |

|-----------|---------------------------------|-------------|----------|------------------|---------------------|--------------------|------|-------|----------|--------|----------|

| Processor | Processor<br>Frequency<br>(MHz) | FPU         | Cache    | Code<br>Location | Slice Flip<br>Flops | Occupied<br>Slices | LUTs | BUFGs | DCM_ADVs | DSP48s | RAMB16s  |

| PPC405    | 100                             | Disabled    | Disabled | PLB              |                     |                    |      |       |          |        |          |

| PPC405    | 200                             | Disabled    | Disabled | PLB              | 710                 | 786                | 728  | 2     | 1        | 0      | 32       |

| PPC405    | 300                             | Disabled    | Disabled | PLB              |                     |                    |      |       |          |        |          |

| PPC405    | 200                             | Enabled     | Disabled | PLB              | 2236                | 2592               | 3464 | 2     | 1        | 4      | 34       |

| PPC405    | 100                             | Disabled    | Enabled  | PLB              |                     |                    |      |       |          |        |          |

| PPC405    | 200                             | Disabled    | Enabled  | PLB              | 710                 | 786                | 717  | 2     | 1        | 0      | 32       |

| PPC405    | 300                             | Disabled    | Enabled  | PLB              |                     |                    |      |       |          |        |          |

| PPC405    | 200                             | Enabled     | Enabled  | PLB              | 2236                | 2592               | 3464 | 2     | 1        | 4      |          |

| PPC405    | 100                             | Disabled    | Disabled | OCM              | 710                 | 726                | 741  | 1     | 1        | 0      | 36       |

| PPC405    | 200                             | Disabled    | Disabled | OCM              |                     |                    |      |       |          |        |          |

| PPC405    | 300                             | Disabled    | Disabled | OCM              |                     |                    |      |       |          |        |          |

| PPC405    | 200                             | Enabled     | Disabled | OCM              | 2234                | 2467               | 3488 | 2     | 1        | 4      | 38       |

| PPC405    | 100                             | Disabled    | Enabled  | OCM              | 708                 | 726                | 741  | 3     | 1        | 0      | 36       |

| PPC405    | 200                             | Disabled    | Enabled  | OCM              |                     |                    |      |       |          |        |          |

| PPC405    | 300                             | Disabled    | Enabled  | OCM              |                     |                    |      |       |          |        |          |

| PPC405    | 200                             | Enabled     | Enabled  | OCM              | 2234                | 2467               | 3488 | 2     | 1        | 4      | 38       |

| PPC405    | 100                             | Disabled    | Disabled | SDRAM            | 2925                | 2945               | 3188 | 3     | 1        | 0      | 23       |

| PPC405    | 200                             | Disabled    | Disabled | SDRAM            | 2925                | 2945               | 3188 | 3     | 1        | 0      | 23       |

| PPC405    | 300                             | Disabled    | Disabled | SDRAM            |                     |                    |      |       |          |        |          |

| PPC405    | 200                             | Enabled     | Disabled | SDRAM            | 4451                | 4637               | 5935 | 3     | 1        | 4      | 25       |