### **D0 Silicon Strip Detector Upgrade Project**

# SVX SEQUENCER CRATE CUSTOM J2/J3 BACKPLANE

**D0** Engineering Note Number 3823.110-EN-479

10/23/97

M. Utes

| 1 | GEN | GENERAL INFORMATION1                 |   |  |  |

|---|-----|--------------------------------------|---|--|--|

|   | 1.1 | Custom Bus System Used               | 1 |  |  |

|   | 1.2 | Application                          | 1 |  |  |

|   | 1.3 | Configuration1-                      | 2 |  |  |

| 2 | INT | ERFACE SPECIFICATIONS                | 3 |  |  |

| _ | 2.1 | Connector Pin Configuration          | 3 |  |  |

|   | 2.1 | AMP Connector Grounds                | 1 |  |  |

|   | 2.2 | 3M Connector Grounds                 | 1 |  |  |

|   | 4.5 | SWI Connector Grounds                | + |  |  |

| 3 |     | ECTRICAL & MECHANICAL SPECIFICATIONS |   |  |  |

|   | 3.1 | Packaging & Physical Size            | 4 |  |  |

|   | 3.2 | PC Board Construction                | 4 |  |  |

|   |     | Power Capacity                       |   |  |  |

|   |     |                                      |   |  |  |

| 4 | ELE | ECTRICAL SAFETY                      | 4 |  |  |

|   |     |                                      |   |  |  |

| A | PPE | NDIX                                 |   |  |  |

|   |     | Design Drawing                       | 5 |  |  |

#### 1 GENERAL INFORMATION

#### 1.1 Custom Bus System Used

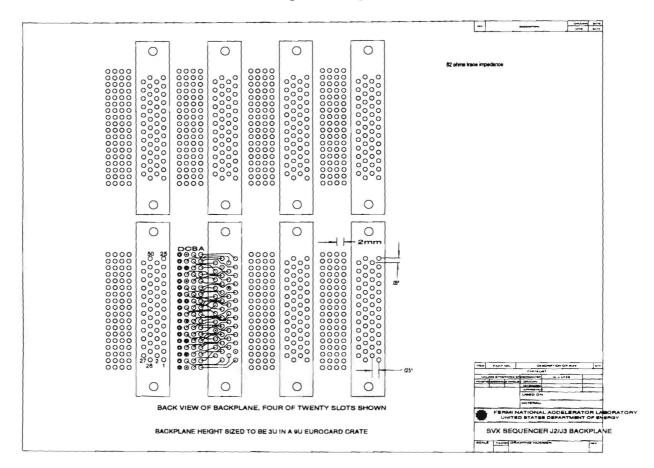

The Custom J2/J3 Backplane is a full length (21 slot) user specified custom 3U backplane to be used in both the J2 and J3 positions. Slot spacing is identical to that used for VME (0.8"), and each backplane shall fit into a standard Eurocard VME style crate.

#### 1.2 Application

The purpose of the Custom J2/J3 Backplane is to send and receive control and clock signals from the SVX chips via 3M pleated foil cables (Slots 2-21), and in slot 1, accept a cable connector and route its signal through to a signal distribution board.

#### 1.3 Configuration

#### 1.3.1 Slot definition

The leftmost slot corresponding to Slot 1 will be unique; the other twenty slots will be identical. Slots will be numbered from 1 to 21.

#### 1.3.2 Connectors

Slot one will have provisions for accepting a cable connector and feeding its signals through to the LSL Fanout Board plugged into slot one. The connector will be a 48-pin DIN female mounted exactly in the same position as the top half of a standard VME connector. In the rear of the backplane, Row C will be cut, leaving the tails of rows A and B to protrude and mate with the female connector on a cable. These 32 pins will have a common shroud, and penetration into the cable connector should be between 0.3" and 0.4". The tails should be .025" square.

Each of slots two through twenty will have two 72-pin AMP (or equivalent) metric connectors with P/N 1-536504-2 on the front side of the backplane to accept cards. The horizontal card positioning shall be the same as that for a standard VME crate. On the rear of the backplane, each slot will have two 50-pin 3M Mini D ribbon bulkheads P/N 10250-6212VC, to accept the connectors on the pleated-foil cable. When viewed from the front of the backplane, the 3M Mini D connector will be to the left of its corresponding AMP connector, but will protrude out the rear.

#### 1.3.3 Traces

There are 46 signals on the pleated-foil cable, and there are four grounds. Each of these signals is received by the 3M connector and routed approximately ½" to its corresponding pin on the AMP connector. This leaves 26 ground pins on the AMP connector that are used for ground.

Each signal trace is to have 82 ohms characteristic impedance. Each pair of 3M/AMP connectors is to be routed identically. There is no common bussing on this backplane.

There are no traces emanating from the connector in slot 1 in the J2/J3 backplane.

#### 1.3.4 Planes

There will be two ground planes and two signal planes. Spacing will be governed by the 82 ohm impedance requirement. The thickness of the backplane should be at least .125" to provide rigidity.

#### 2 INTERFACE SPECIFICATIONS

#### 2.1 Connector Pin Configurations

TABLE 1

J2/J3 Backplane Pin Assignments

| Not Name                           | 2M Din Number             | AMD Din Number               |

|------------------------------------|---------------------------|------------------------------|

| <u>Net Name</u><br>53 <b>M</b> HzA | <u>3M Pin Number</u><br>I | <u>AMP Pin Number</u><br>A18 |

| ISBMHZA                            | 26                        | C17                          |

| GND                                | 20                        | GND                          |

| CLK A                              | 27                        | B17                          |

| CLK_A                              | 3                         |                              |

| _                                  | 3<br>28                   | B18                          |

| CROSSINGA                          |                           | A17                          |

| RESETA                             | 4                         | A16                          |

| PRIORITY IN A                      | 29                        | B16                          |

| CHANGE_MODE_A                      |                           | A15                          |

| MODEI_A                            | 30                        | C15                          |

| MODEO_A                            | 6                         | B15                          |

| D7_A                               | 31                        | B14                          |

| D6_A                               | 7                         | A14                          |

| D5_A                               | 32                        | C13                          |

| D4_A                               | 8                         | A13                          |

| D3_A                               | 33                        | B13                          |

| D2_A                               | 9                         | A12                          |

| GND                                | 34                        | GND                          |

| $DI_A$                             | 10                        | B12                          |

| D0_A                               | 35                        | C12                          |

| HDI_ENABLE_A                       | 11                        | All                          |

| $DVALID_A$                         | 36                        | BII                          |

| PRIORITY_OUT_A                     | 12                        | B10                          |

| DIR_A                              | 37                        | C10                          |

| VCAL_A                             | 13                        | A10                          |

| VCAL_B                             | 38                        | B9                           |

| $DIR \ \bar{B}$                    | 14                        | A9                           |

| PRIORITY OUT B                     | <i>39</i>                 | C9                           |

| DVALID B                           | 15                        | A8                           |

| HDI ENABLE B                       | 40                        | B8                           |

| $DO \bar{B}$                       | 16                        | <i>B7</i>                    |

| $D1^{-}B$                          | 41                        | C7                           |

| $\overline{GND}$                   | 17                        | GND                          |

| D2 B                               | 42                        | В6                           |

| $D3^{-}B$                          | 18                        | A7                           |

| D4B                                | 43                        | C6                           |

| $D5^{-}B$                          | 19                        | A6                           |

| D6 B                               | 44                        | A5                           |

| D7 B                               | 20                        | B4                           |

| MODEO_B                            | 45                        | B5                           |

| MODE1 B                            | 21                        | A4                           |

| CHANGE MODE B                      |                           | C4                           |

| PRIORITY IN B                      | 22                        | A3                           |

| RESETB                             | 47                        | B3                           |

| CROSSINGB                          | 23                        | A2                           |

| /CLK_B                             | 48                        | B2                           |

| CLK B                              | 24                        | BI                           |

| GND                                | 49                        | GND                          |

| /53MHzB                            | 25                        | AI                           |

| 53MHzB                             | 50                        | C2                           |

| No. 11 1 C                         |                           | C.I. AMB                     |

Note: We have defined the four columns of the AMP connector as A, B, C, and D. When viewed from the front of the backplane, rowA is on the left.

#### 2.2 AMP Connector Grounds

All AMP Connector pins not mentioned in Table 1 are connected to the backplane ground. This includes all of Row D.

#### 2.3 3M Connector Grounds

In addition to the four pins defined as ground, the connector housing serves as a ground connection between the pleated foil shield and the backplane ground. The region underneath the 3M connectors' mounting holes shall be free of solder mask and tinned to effect good ground connections.

#### 3 ELECTRICAL AND MECHANICAL SPECIFICATIONS

#### 3.1 Packaging & Physical Size

This backplane is the width of a standard 21-slot VME backplane, and must be able to be used as either the J2 or the J3 backplane.

#### 3.2 PC Board Construction

The printed circuit board is a 4 layer board. The high speed signal traces (defined in section 2.1) are implemented as microstrip above ground plane, with geometry chosen to produce a characteristic impedance of 82 ohms.

#### 3.3 Power Capacity

No power supply currents are carried through the signal traces.

#### 4 ELECTRICAL SAFETY

Materials required for an Electrical Safety Review, such as artwork, data sheets, and Engineering Notes, are available from the author.

## APPENDIX Design Drawing