LABORATORY

# Hybrid MPI: Efficient Message Passing for Shared and Distributed Memory

A. Friedley, G. Bronevetsky, T. Hoefler, A. Lumsdaine

February 14, 2013

International Conference on Supercomputing Eugene, OR, United States June 10, 2013 through June 14, 2013

# Disclaimer

This document was prepared as an account of work sponsored by an agency of the United States government. Neither the United States government nor Lawrence Livermore National Security, LLC, nor any of their employees makes any warranty, expressed or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States government or Lawrence Livermore National Security, LLC. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States government or Lawrence Livermore National Security, LLC, and shall not be used for advertising or product endorsement purposes.

# Hybrid MPI: Efficient Message Passing for Shared and Distributed Memory

Andrew Friedley Indiana University

Torsten Hoefler ETH Zurich

#### ABSTRACT

Many-core shared memory architectures are ubiquitous in the design of both High-Performance Computing (HPC) and commodity systems because they provide an excellent tradeoff between performance, power efficiency and programmability. The MPI programming model is very popular in scientific applications and provides a strong development platform for future power-constrained systems. MPI's abstraction of explicit communication across distributed memory helps developers minimize data motion. Unfortunately, MPI's distributed memory abstraction makes it difficult for MPI implementations to fully leverage the capabilities of shared memory hardware. OS-level separations between processes force MPI to perform unnecessary copying to transfer data within shared memory nodes.

This paper presents a new approach to the design of MPI libraries that shares the addresses spaces of MPI ranks executing on the same node, allowing them to communicate directly like native threaded applications. While prior approaches to the design of such libraries are based on threading, we demonstrate that this approach is both brittle and performs poorly in practice. We instead propose a novel approach based on OS processes that enables both highperformance shared memory communication and full, highperformance integration with existing MPI libraries for internode communication.

#### 1. INTRODUCTION

With the end of processor frequency scaling performance and efficiency improvements in processor designs are achieved primarily by increasing the number of cores on a processing chip. The most common type of architecture for these designs is based on fully-featured compute cores connected via coherent shared memory, which provides significantly higher application developer productivity than alternative, more constrained designs. MPI is the de facto programming model for large-scale computing, used to implement the vast Greg Bronevetsky Lawrence Livermore National Laboratory

> Andrew Lumsdaine Indiana University

majority of scalable scientific applications. However, it was originally designed for systems where single-core compute nodes were connected by an inter-node network. Even as the MPI standard and individual MPI implementations have worked to adapt to new types of systems, the poor support MPI implementations provide for many-core shared memory architectures has forced developers to use alternative programming models such as OpenMP [11] or OpenCL [1] to parallelize computations on such hardware, using MPI only for inter-node communication.

Despite the limitations of today's MPI implementations, its programming model is actually highly compatible with the needs of future applications. In particular, since communication is expected to make up the bulk of application power use in the future, algorithms are expected to limit their communication and memory use. MPI simplifies this by defaulting memory to be private to each computation thread and requiring the developer to explicitly indicate any communication. The challenge of MPI implementations is to provide developers this efficient abstraction across a wide range of architectures, including those where memory is actually shared or where only restricted communication primitives are available.

This paper focuses on the design of MPI libraries for many-core processors connected via shared memory hardware. Given the wide variety of applications that use MPI and systems on which they wish to run, our goal is to ensure that peak shared memory communication performance is available to these applications without sacrificing (i) portability, (ii) inter- and intra-node communication performance, and (iii) with no need for root access to the system. We present and evaluate the design of a new MPI library called Hierarchical MPI (HMPI) that is optimized for intra-node shared memory communication. HMPI composes with traditional MPI libraries optimized for inter-node communication by using only operations in the MPI standard to interoperate with them. The resulting composition of HMPI for intra-node communication with a traditional MPI for inter-node communication produces a comprehensive communication system for clusters of shared-memory nodes. We demonstrate this experimentally by composing HMPI with MVAPICH2 [7] and BlueGene/Q MPI [8].

The intuition of our design is that efficient use of shared memory hardware requires the memories of MPI ranks running on the same shared memory to be shared with each other (in MPI terminology a "rank" is a thread of execution that may be an OS process, thread or some other entity). As discussed in Section 2 this makes it possible for

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee.

Copyright 20XX ACM X-XXXXX-XX-X/XX/XX ...\$15.00.

MPI to transfer data directly from a sender's buffer to a receiver's buffer with no additional copies to overcome OS separations between their address spaces. Further, it enables novel shared-memory optimizations such as ownership passing [2] where the sender passes a pointer to its data buffer to the receiver, allowing the receiver to copy the data directly into its internal data structures without the need to first copy it into a receive buffer. Fundamentally, sharing memory among MPI ranks allows MPI applications to utilize shared memory hardware as efficiently as threaded applications, making it possible for developers to achieve high performance on modern architectures without significantly changing their applications.

These observations have also been made by the MPI Forum, which introduced shared memory windows in MPI-3.0 [4]. Those windows allow to create shared memory regions for direct sharing of data. However, using this mechanism may require complex code changes. In the following, we will demonstrate how most of the benefits of shared memory communication can be utilized without changing applications.

Other prior work on sharing memory across MPI ranks has focused on implementing ranks as threads within the same OS process. While multiple threads appear to be the natural solution to sharing memory, this approach suffers from several challenges that reduce both its generality and performance.

In our approach, we transparently share memory among OS processes. This transition from threads to processes enables our MPI library to work seamlessly with existing MPI applications and without the performance issues of the thread-oriented approach. Our approach works on both POSIX and Blue Gene platforms with no kernel extensions or administrator access. Further, we demonstrate that because our architecture-focused MPI library interacts with other MPI libraries exclusively via MPI operations it is fully generic and can work with any other MPI implementation that is focused on other types of resources.

Finally, Section 6 experimentally evaluates the performance of our approach, showing that it outperforms native MPI libraries on multiple benchmarks. Further, we analyze HMPI's performance in detail to demonstrate that it improves performance primarily by utilizing caches more efficiently and therefore interfering less with the application's own use of the cache.

The key contributions of our work are the following:

- 1. Analysis of thread-based MPI design and identification of its limitations.

- 2. A shared memory allocator technique for enabling shared memory between local MPI ranks without modifying application code.

- 3. A new design for message passing utilizing single data copies in a shared address space.

- 4. Analysis of single-copy shared-memory message passing performance on a system using our shared memory allocator technique, and BlueGene/Q, a system providing a shared address space feature.

#### 2. MPI ON SHARED MEMORY SYSTEMS

In this paper, we discuss three different approaches to memory layout and intra-node communication in MPI. Section 2.1 discusses the traditional (process-based) approach used in practice by most implementations. Previous work has investigated the idea of a thread-based MPI design in which each rank is a thread sharing memory with all ranks on the same node. For reasons we will discuss in Section 2.2, this approach is not prevalent in practice. We contribute a third approach, discussed in Sections 3 and 4 that assigns each rank to its own process, but shares heap memory among all ranks in a node. Our approach combines the benefits of process-based and thread-based MPI design.

#### 2.1 Process-based MPI

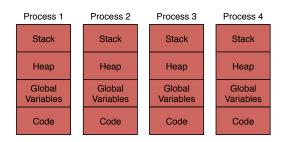

Although the MPI standard does not prescribe how MPI ranks are implemented, the traditional assumption has been that each rank is an OS process with its own private memory. Figure 1 illustrates this layout. The advantage of the process-based design is that it makes it easier to coordinate inter-node communication by multiple cores. Since each core is used by a separate process, their MPI libraries maintain separate state and thus require no synchronization. Since network interfaces are typically designed to provide each process a separate context in which to coordinate its outgoing and incoming communication, no MPI-level synchronization is required to access the network.

Figure 1: Memory layout in the traditional process-based MPI design. No application-visible memory is shared when MPI ranks are processes.

The limitation of this design is in communicating among different ranks that are executing within the same shared memory node. MPI libraries often use a FIFO connection (one for each pair of local ranks) for small messages, and one or more shared memory regions mapped by multiple ranks for larger messages. Either case inherently requires two copy operations per message. The sender copies from its privatememory send buffer into the FIFO queue or shared memory region, and the receiver copies back out into its separate private-memory receive buffer. FIFOs are a pair-wise connection, and shared memory regions may also be created on a pair-wise basis to simplify communication. Thus, the number of resources grows as the square of the number of MPI ranks per node, which is often the number of cores per node. Such an approach will consume too many resources as the amount of memory available per core continues to decrease on HPC systems.

#### 2.2 Thread-based MPI

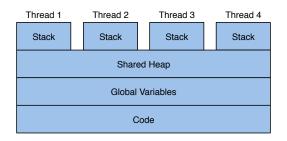

The limitations of process-oriented MPI implementations has motivated research on implementations where MPI ranks are implemented as OS threads, all of which execute within the same process [5, 14, 15]. Figure 2 illustrates this layout. Threads are an excellent choice since they share all their memory by default. However, many MPI applications are written with the assumption that global variables are private to each MPI rank. While threading gives each rank its own stack and heap within he shared address space, one set of global variables is shared among all MPI ranks in a node. Application state becomes corrupted as different MPI ranks write to the common global variables, which may exist within the application and in any libraries they link with.

Figure 2: Memory layout in the thread-based MPI design. All application visible memory is shared when MPI ranks are threads.

Developers of thread-oriented MPI implementations have attempted to resolve this problem in two ways. First, they have developed techniques to privatize global variables so that each thread is provided its own copy. At the source code level, privatization can be done using thread-local storage, using the **\_\_thread** keyword available in many C compilers, or using compiler transformation tools [10, 14]. There has been work on tools that modify object files to privatize global variables when the source code is not available [10].

Given the complexity of privatization, especially in library code, an alternative approach is to adjust the use of libraries to ensure that no globals are used. This involves replacing regular library calls with their thread-safe variants, for example using strtok\_r instead of strtok. Where thread-safe alternatives are not available (e.g., the getopt function uses static variables internally) locks are required to protect access to the function. While it is possible to build compiler tools to perform this replacement, they would require knowledge about each library and its thread safety guarantees.

#### 2.2.1 Network Performance

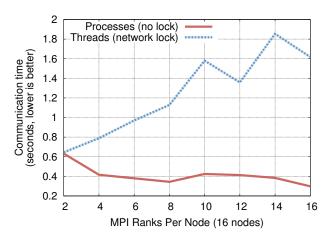

Where high performance is desired, MPI implementations must use a network interface directly. Depending on the network, issues can arise due to the use of multiple threads. For example, not all network interfaces provide thread safe APIs. Any MPI using multiple threads must protect all inter-node communication using a lock. Process-based MPI implementations face no such requirement. Unfortunately, an MPI-level network lock results in high contention for network resources and reduced performance. Figure 3 shows the effect of this contention on the MiniMD<sup>1</sup> application. We measured the time taken by the communication portions of MiniMD, using varying numbers of ranks on 16 nodes of the Cab system. Cab has an InfiniBand-based Performance Scaled Messaging (PSM) network that is not thread-safe. Network resource contention will be a problem when using any network that does not support multiple threads as efficiently as multiple processes.

Driver thread-safety also creates issues when using multiple threads with a process-based MPI implementation. If MPI is running in MPI\_THREAD\_SINGLE mode, application threads must use locking to control access to MPI, which creates contention. However, if MPI provides MPI\_THREAD\_MULTIPLE mode, then the calls library's calls to the network drivers from the various threads must also be locked inside MPI because the drivers are not threadsafe. This is one of the reasons why multi-threaded MPI applications are not common and perform sub-optimally [16].

Figure 3: Affect of overhead due to lock contention for network resources in the MiniMD application with constant problem size. Due to strong scaling, the communication volume decreases with the number of processes. However, when using threads, the communication overhead increases due to lock contention.

All in all, the above observations suggest that threadbased MPI implementations are not a practical approach for the future of multi- and many-core HPC systems. We note that no thread-based MPI has been widely adopted in practice.

#### 3. SHARED MEMORY IN PROCESSES

The goal of our work is to develop an implementation of MPI that is (i) optimized for shared memory hardware, (ii) works on existing operating systems with no root access, (iii) is compatible with any inter-node MPI implementation and (iv) provides peak performance for both intra- and inter-node communication. Given the challenges faced by MPI implementations that use threads to implement MPI ranks, we have chosen to implement them using OS processes. The challenge of this approach is to share memory across processes by developing some mechanism to circumvent the memory protections typically enforced by the OS.

A number of solutions for sharing memory between processes already exist on HPC systems. XPMEM [12, 18] is a Linux kernel extension that allows processes to map memory from another process, and is commonly found on SGI and Cray systems. Blue Gene/Q systems have a feature that shares heap memory among all MPI ranks in a node, and is enabled by setting an environment variable (BG\_MAPCOMMONHEAP) [8].

<sup>&</sup>lt;sup>1</sup>See Section 6.1 for details on MiniMD.

For Linux-based commodity clusters without such functionality built in, we have developed a replacement for the default memory allocator that shares heap memory among all processes in a similar manner. Our shared memory heap allocator enables the same shared-memory techniques on all Linux systems without requiring installation of kernel extensions or anything else that requires administrative permissions. Furthermore, our shared heap allocator is stand-alone and not MPI specific; we imagine it is useful for other forms of shared memory communication.

#### 3.1 Shared Memory Heap Allocator

We override the system's default memory allocator with our own design that always provides shared memory. Our allocator is based on Doug Lea's malloc library (dlmalloc), which is also basis for the default Linux memory allocator. Normally, the memory allocator incrementally requests memory from the operating system using the sbrk call or using mmap with the MAP\_PRIVATE option. We implement our own version of sbrk that requests memory from a shared memory region mapped on all MPI processes.

We start by initializing one shared memory memory region to the largest possible size allowed by the system. At the beginning of our shared region we place a small data structure that contains a counter to track the 'break' address for the region and a pointer to the end of the shared region. Our sbrk implementation obtains memory by atomically incrementing the shared break counter by the amount of memory requested. If the counter is incremented past the shared memory region, we signal that we are out of memory. This counter is the only point of contention between processes allocating memory from the shared region. Each process maintains its own instance of the dlmalloc allocator that manages the memory returned to it by our sbrk, requiring no inter-process locking for memory management.

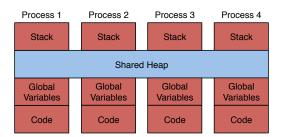

Figure 4: Memory layout of processes with our shared heap allocator. Dark red segments are private to each process, while the light blue heap segment is shared among all processes in a node.

Figure 4 illustrates how our shared memory allocator connects multiple processes together. Stack, global variables, and code are private to each process, but the heap is shared. Our memory allocator provides the same shared-heap benefits as thread-based MPI and systems with kernel extensions. However, we incur none of the global variable privatization challenges encountered by thread-based MPIs and do not rely on specific operating systems, resulting in maximum portability. Our approach works on any POSIX-compliant operating system<sup>2</sup> and platform that provides an MPI and allows memory allocation calls to be overridden.

In addition to the heap, MPI allows communication buffers located in global variables and the stack segment. Section 2.2 discussed why sharing global variables is problematic and undesirable. Sharing stack memory would not cause problems, but there is no good mechanism for doing so. If the application's main routine only operates on local variables before calling a routine we control (i.e., malloc or MPI\_Init, it is possible to use the swapcontext et al. routines to switch to a stack located in shared memory. More generally, a compiler tool could transform the application's source code or object files to enable sharing of stack memory. Since the benchmarks and applications we have considered so far primarily communicate using heap memory, we have not implemented any form of shared-memory stack. Instead, our library uses traditional MPI communication (also through shared memory as described in Section 2.1) if memory is not in the shared heap.

#### 4. HYBRID MPI

We have implemented a 'Hybrid' MPI (HMPI) library to investigate single-copy message passing techniques. Rather than building an entire MPI implementation from the ground up, we have taken the unique approach of layering HMPI on top of any existing MPI library. There are three advantages to our approach: portability, transparency, and simplicity.

*Portability*: HMPI works on top of any existing MPI library simply by linking it into the application. We are able to extend both open- and closed-source MPI implementations on multiple platforms.

*Transparency*: No code transformations or object file modifications are needed. Neither the application nor the underlying MPI library need to be changed or made aware of HMPI's presence.

Simplicity: Much of MPI's functionality can be provided by passing calls through to the underlying MPI. We implement portions we are interested in for research purposes (in this paper, shared memory point-to-point communication), and defer for all other functionality (e.g., inter-node communication and collectives).

The combination of these advantages allows us to experiment with new message passing techniques on multiple platforms (including those with closed-source, proprietary MPI implementations) with minimal effort.

To implement shared-memory message passing, HMPI assumes that memory used for communication is mapped to the same virtual address in every process on a node. In this paper, we show experimental results using our shared memory heap allocator on a commodity x86 cluster ('Cab'), and using the BG\_MAPCOMMONHEAP feature on Blue Gene/Q ('Sequoia'). Section 6 describes these systems in detail.

#### 4.1 Message Matching

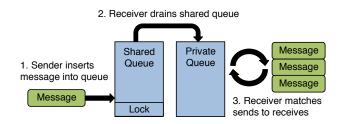

We implement two incoming message queues per receiver using linked lists. Figure 5 illustrates our design. One queue is globally accessible by all ranks. Senders add messages to the global queue owned by the rank for which the message is destined. Each global queue is protected by an MCS lock [9]. An important benefit of the MCS lock is guaranteed FIFO ordering of lock acquisitions. When using a lock without this property (e.g., a simple compare and swap lock), some ranks could be blocked for long, unpredictable periods waiting to

<sup>&</sup>lt;sup>2</sup>or an OS that allows shared memory

add a message to a receiver's queue. FIFO ordering ensures fairness.

The second queue is private. Whenever a receiver attempts to match incoming sends to local receives, it drains its global queue and adds incoming sends to its private queue. Since the queues are linked lists, the draining operation only involves updating two pointers. The receiver then attempts to match sends on its private queue to local receives. Since the private queue is not shared, the receiver can loop over it many times without need for synchronization. Thus, our dual queue technique minimizes contention between processes.

Figure 5: HMPI's matching design. Each receiver has two queues, one shared and one private. Senders insert messages into the shared queue protected by a lock. The receiver drains the shared queue into its private queue and enters a loop to match incoming sends to local receives.

### 4.2 Communication Protocols

Although single-copy message transfer was our goal with HMPI, we have discovered that simply using memcpy to transfer the data is often not the fastest method possible. We use an 'immediate' protocol for small messages less than the *immediate threshold* (currently 256 bytes, Section 4.2.1), and a 'synergistic' protocol for messages larger than the *synergistic threshold* (currently 8 kB, Section 4.2.2). We support buffers from global variables or the stack by checking the location of each buffer given to HMPI by the application. If the buffer address lies outside of our shared memory heap, we fall back to a two-copy transfer mechanism.

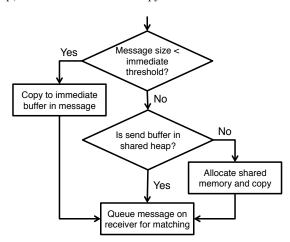

Figure 6: Sender protocol flow. The sender ensures its buffer is in the shared heap and uses the immediate transfer protocol for small messages.

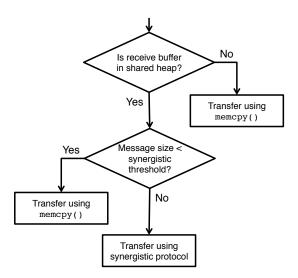

Figure 7: Receiver protocol flow. A single memcpy is used if the receive buffer is not in the shared heap or if the message is too small for the synergistic protocol.

Before queuing a message, the sender goes through a series of checks as shown in Figure 6. If the message is small, we go into the immediate protocol, inlining the message data with the message's matching information. If the application's send buffer is not located in the shared heap, we allocate a shared buffer and copy the data over. Finally, the message is queued on the receiver's shared queue.

Once a message is matched, the receiver decides how to transfer data from the send buffer to the receive buffer. Figure 7 shows the decision process. If the receive buffer is not on the shared heap or if the message is not large enough to use the synergistic protocol, we use one **memcpy** call to transfer the data. For larger messages we enter the synergistic protocol.

#### 4.2.1 Immediate Transfer Protocol

Message Size (bytes)

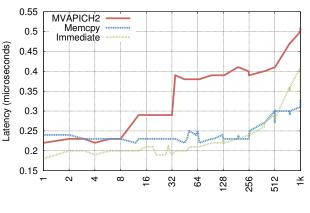

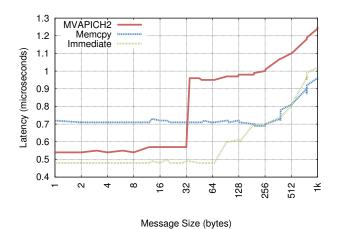

Figure 8: Intra-socket small message latency on Cab. [htor: I can barely see the "immediate" line on my printout]

For small messages, the best latency is achieved by utilizing a two-copy method with the message data located immediately after the matching information. The perfor-

Figure 9: Inter-socket small message latency on Cab.

Message Size (bytes)

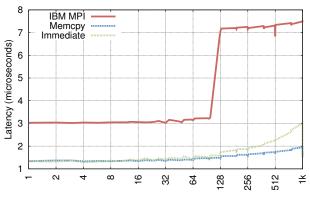

Figure 10: Small message latency on Sequoia.

mance advantage stems from the following simple observation: When a message is matched, the receiver accesses the source message information (source rank, tag, communicator), incurring a cache miss. With a single-copy data transfer approach, copying the message data will incur another cache miss, since that data has not been seen by the receiver. Inlining the message after the sender's matching information causes the hardware to bring the data into cache at the same time as the matching information, avoiding the second cache miss when copying the data.

As seen in Figure 6, the sender will perform the additional copy before queuing the message at the receiver. From the receiver's point of view, the immediate protocol is the same as single-copy transfer—just copy the data from the location provided by the sender. For small messages, the time saved by avoiding the cache miss more than makes up for the cost of doing two copies.

Figures 8 and 9 show intra- and inter-socket small message latency on the  $Cab^3$  system. All latency results were obtained using the NetPIPE [17] benchmark. Based on these results, we chose a threshold of 256 bytes, below which we use the immediate protocol. After that, we revert to a single memcpy or the synergistic protocol. Figure 10 shows small message latency on the Sequoia<sup>3</sup> system. Since we observe no benefit to using the immediate protocol on this system, we conditionally disable it if compiling for a Blue Gene/Q machine and fall back to memcpy.

#### 4.2.2 Synergistic transfer protocol

For large messages, bandwidth is most important. We can achieve higher data transfer rates than possible with a single **memcpy** by having both the sender and receiver participate in copying data from the send buffer to the receive buffer. To do this, we break the data into blocks and utilize a shared counter that is atomically updated by the sender and receiver. When the receiver matches a message, it initializes the counter (used as a byte offset) and begins copying data one block at a time. Before copying each block, the counter is incremented. If the sender enters the MPI library and sees that the receiver is copying in block mode, it also begins incrementing the counter and copying blocks of data until the entire message has been copied.

In the worst case, the sender does not participate (it is either executing application code or helping with other transfers), and we see the same bandwidth as a memcpy, which is the peak bandwidth achievable by one core. The sender can enter and assist the transfer at any point. Bandwidth improvement then depends on when the sender begins assisting and on the peak bandwidth achievable by two cores.

The advantage of this protocol is that communicationcomputation overlap is greater than that of existing protocols when the sender has other work to do. Unlike the two-copy protocols used in current MPI implementations, the receiver can perform the entire data transfer without the sender, and does so when beneficial. Communication performance is dynamically accelerated when the sender is able to assist the receiver in copying data.

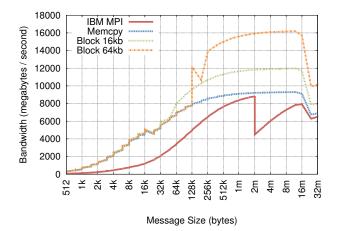

Message Size (bytes)

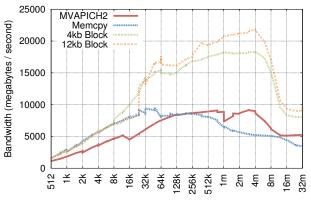

Figure 11: Intra-socket large message bandwidth on Cab.[htor: also nearly impossible to read]

Figures 11 and 12 show intra- and inter-socket large message bandwidth on the Cab system. Based on experimentation, we chose two different block sizes: 4kb and 12kb. For messages smaller than twice the block size, we use a single memcpy, since the synergistic protocol needs multiple blocks to provide a benefit. Starting at 8kb, we use the synergistic protocol with a 4kb block. For messages greater than 24kb,

$<sup>^{3}\</sup>mathrm{Details}$  on the Cab and Sequoia systems can be found in Section 6.

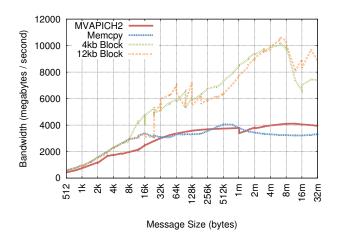

Figure 12: Inter-socket large message bandwidth on Cab.

Figure 13: Large message bandwidth on Sequoia.

we switch to a 12kb block. In some cases peak bandwidth is more than double that of MPI or memcpy.

Figure 13 shows large message bandwidth on Sequoia, which only has one socket per node. Based on experimental results for this system, we chose block sizes of 16kb and 64kb.

NetPIPE, as used in the figures, represents the ideal case for the synergistic protocol—both the sender and receiver are always ready and available to assist in data transfer. In practice, the bandwidth seen by applications will vary somewhere between that of memcpy and the peak synergistic bandwidth depending on communication-computation overlap.

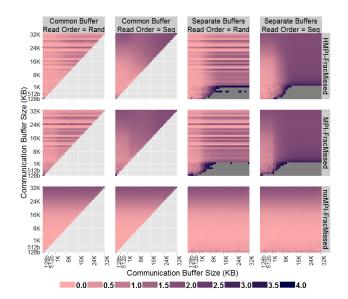

#### 5. COMMUNICATION ANALYSIS

While raw communication performance is important, another way that MPI libraries affect application performance is in their effects on the cache and the application data structures within it [13]. We thus studied the effect that HMPI's and MPI's communication protocols have on the cache via the microbenchmark in Figure 14, which models the typical interaction between the application and the MPI library. It reads the elements of a data buffer to bring it into the cache, then performs a ping-pong communication and finally reads the data buffer again. We conducted experiments on Cab with buffers of size between 128 bytes and 32KB (the size of Cab's L1 Data cache) where the read loop either accesses buffer entries in sequential or random orders and each cache line is accessed exactly once. Further, we studied configurations where separate buffers were used for both data and communication or a common buffer for both (in this case message size was  $\leq$  buffer size). To understand how the different types of communication protocols affect the application's use of the cache we measure the number of cache misses the benchmark incurs during the read loop.

```

unsigned char *data_buf, *comm_buf;

// Read the buffer, bringing it into the cache.

for(int i = 0; i < x; i++) data_buf[i] = 1;

sum += data_buf[index(i)];

// Perform ping-pong communication on either

// the data buffer (Common configuration) or a

// communication buffer (Separate)

if(Common) Do_PingPong(data_buf);

else if(Separate) Do_PingPong(comm_buf);

// Read the buffer in sequential or random order,

// while measuring cache misses.

Start_Counters();

int sum;

for(int i = 0; i < x; i++)

sum += data_buf[index(i)];

Measure_Elapsed_Counters();

```

Figure 14: Benchmark that models the impact of MPI communication on application cache use.

Figure 15: Fraction of accesses to the data buffer on which an L1 cache miss occurs

Figure 15 shows the misses in the L1 data cache on the Cab system (32KB in size), showing the average of 10 runs. Specifically, we report the fraction of the data buffer reads that miss: (number of L1 data misses) \* (cache line size) / (data buffer size). From top to bottom the graph shows misses for cases where HMPI is used for communication, then MPI and finally the case where no communication was performed between the write and read loops. From left to right we show data for the sequential and random loop orders and configurations where the buffers were the common or separate. For each configuration we show a heatmap where the x-axis is communication buffer size and y-axis is the data buffer size with the range [128b, 256b, ...896b, 1KB, 2KB, ...32KB]. The shade of each tile denotes the above fraction miss metric where it falls in the range [1-4] and is shown uniformly in grey for larger values to ensure high visual resolution for the primary value range.

The data shows that the miss rate is low when no communication is performed. It grows with the size of the data buffer upto the 32KB size of the L1 data cache. This phenomenon is observed for both read orders but is more significant for sequential. gb: Need updated no-mpi data Since the sequential access pattern can be readily detected by the cache hardware, this indicates that the cache replacement algorithm is being used for this access pattern on this processor is making sub-optimal replacement decisions.

Looking at the HMPI and MPI data, we observe both libraries increase the number of cache misses in the read loop. This is caused both by evictions of data from the cache as well as due to poor decisions by the cache replacement algorithm. The impact of line evictions can be seen in the increased miss fractions for the separate buffer configuration relative to common buffer, since in the former case the processor touches more individual addresses. The impact of the replacement algorithm is observed by looking at the difference between the results for random and sequential access orders. It can be seen that the difference between separate and common is generally small for all the buffer size configurations the two share. In contrast, the sequential access order causes many more misses than the random, indicating that the increase is due to interference with the replacement policy. The likely cause is that the cache access pattern of the communication code trains the replacement algorithm to expect the same access pattern in subsequent code and when control returns to the application it makes poor decisions that result in unnecessary misses. Indeed, in many cases there are more misses than the number of lines in the data buffer, especially for small data buffers and large communication buffers. This indicates that the useless lines from the communication buffer are being prefetched when in fact the application is attempting to access the data buffer.

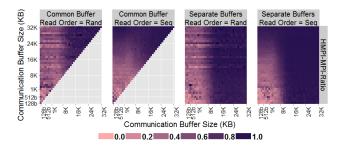

Figure 16: The fraction of accesses to the data buffer on which an L1 cache miss occurs with HMPI, divided by the same with MPI.

Finally, Figure 16 shows the miss fraction metric of HMPI

divided by the same metric of HMPI. Values closer to 0 (HMPI has fewer misses) are shown in light shades while values close to 1.0 (HMPI and MPi are the same) are shown as dark. The data shows that for random reads HMPI induces fewer application misses across all data buffer sizes when communication buffers are smaller than 8KB (quarter of the L1 cache). The same is true for sequential reads where data buffers are smaller than 16KB (half the L1 cache) The conclusion is that for applications that operate on and communicate with buffers of a few KB (expected to be the norm as the same amount of data is divided among more computing cores), HMPI has a significantly smaller impact on the application's use of the cache.

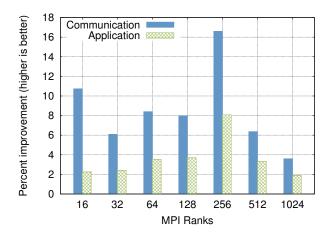

#### 6. APPLICATION ANALYSIS

The various microbenchmark results shown in Sections 4 and 5 give a picture of HMPI's shared memory communication performance in isolated scenarios. In this section, we compare the performance of HMPI to MPI for two applications: MiniMD and LULESH. We show results for one node (where our shared memory protocols are used exclusively in HMPI) as well as up to 64 nodes.

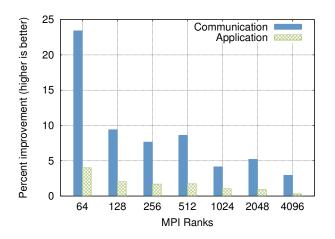

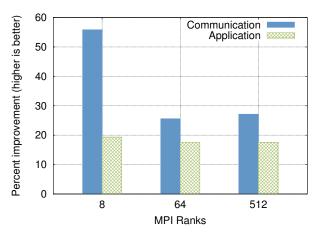

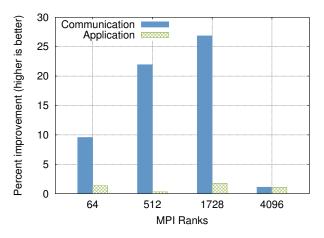

All figures in this section show 'percent improvement' on the y-axis to show the reduction in wall clock time of HMPI compared to MPI. For each application, we report the improvement in total application time as well as time taken specifically by the communication routines. The ratio of speedup between application and communication time varies based on the ratio of communication to computation in the application, which in turn depends on problem size. All of our results show weak scaling with a fixed problem size per rank.

We show results for two different systems. Cab has two Xeon ES-2670 (eight core, 2.6 GHz) processors (16 cores total), 32 GiB of RAM per node, and a PSM InfiniBand network. MVAPICH2 v1.8.1 was used as our comparison MPI on Cab. Sequoia is a Blue Gene/Q system with one PowerPC A2 (sixteen core, four threads per core, 1.6 GHz) processor (64 tasks total) and 16 GiB of RAM per node. IBM's MPICH-based MPI library was used as our comparison MPI on Sequoia.

#### 6.1 MiniMD

MiniMD is part of the Mantevo [3] mini-application suite, which consists of several mini-applications representing larger application classes. Such mini-applications are increasingly used in exascale research for their combination of simplicity and relevance. MiniMD is a molecular dynamics simulation that computes atom movement over a 3D space decomposed into a processor grid. The primary communication pattern is a 3D, 6-point nearest neighbor exchange performed twice per work iteration.

Figures 17 and 18 show performance comparisons for MiniMD. We ran 2500 iterations and scaled the problem size so that each rank had approximately 1,000 atoms. On Cab, we observe communication speedups ranging from 3.6-16.6%, resulting in total application time improvements of 1.9-8.1%. Sequoia shows improvements of 2.9-23.5% communication time and 0.2-4.0% application time.

#### 6.2 LULESH

LULESH, also known as Livermore Unstructured Lagrangian Explicit Shock Hydrodynamics [6], is the mini-

Figure 17: HMPI performance gains relative to MPI for MiniMD on the Cab system (16 ranks per node).

Figure 18: HMPI performance gains relative to MPI for MiniMD on the Sequoia system (64 ranks per node).

application version of a full-size hydrodynamics code in use at Lawrence Livermore National Laboratory. In particular, LULESH simulates the Sedov blast wave problem on a uniform 3D mesh. The mesh is decomposed spatially among MPI ranks. In each time step, multiple exchanges with up to 27 neighbors are performed. Each data exchange is implemented using non-blocking sends and receives.

Figures 19 and 20 show performance comparisons for LULESH. LULESH requires that the number of ranks be a perfect cube (i.e.,  $NP = x^3$ ). A fixed problem size of  $15^3$  per rank was used. The relatively small application time speedups are due to the fact that LULESH spends far more time performing computation compared to communication. Inspecting the code, we note that communication is often overlapped with computation using non-blocking MPI calls. On Cab, we see communication time speedups of 25.6-55.8% and application time speedups of 17.6-25.6%. Communication time speedups of 4.0-26.8% and application time speedups of 0.3-0.7%.

#### 7. CONCLUSION

In this work we developed a novel scheme for exploiting

Figure 19: HMPI performance gains relative to MPI for Lulesh on the Cab system (16 ranks per node).

Figure 20: HMPI performance gains relative to MPI for Lulesh on the Sequoia system (64 ranks per node).

shared memory hardware in MPI programs that are written for distributed memory systems. This mechanism shares *selected subsets* of memory among MPI ranks to implement communication between them more efficiently. We demonstrated how to accelerate on-node MPI communications significantly. However, the mechanism is not limited to MPI, it further enables optimizations such as ownership passing [2] or send/recv loop fusion, both departures from the one-copy semantics of MPI, or other application-specific optimization, such as communication with accelerators.

In addition, we utilize a *layered* model for our optimization. HMPI resides on top of the MPI interface, however, it also integrates *vertically* in that it hooks into MPI's communications and transparently optimizes them. We showed that this model is highly portable and enables new ways to design libraries on top of MPI. Similar mechanisms could be used to optimize heterogeneous systems, e.g., interfacing GPUs with accelerator-specialized but MPI-portable extensions.

We used these two mechanisms to develop HMPI, a fast layered MPI library that optimizes hybrid shared memory communication. Our optimizations show significantly less on-node communication overheads compared with traditional MPI approaches and unlike prior work with thread-based MPI implementations, it integrates transparently into legacy applications. We demonstrate the applicability with [htor: XXX application codes which gain a speedup of up to XXX%].

[htor: put some big sentence at the end how a we some all this is!]

# 8. ACKNOWLEDGMENTS

This work was supported in part by the Department of Energy X-Stack program and the Early Career award program. It was partially performed under the auspices of the U.S. Department of Energy by Lawrence Livermore National Laboratory under Contract DE-AC52-07NA27344.

#### 9. **REFERENCES**

- $[1]~{\rm The~OpenCL}$  specification version 1.0, 2009.

- [2] A. Friedley, T. Hoefler, G. Bronevetsky, C.-C. Ma, and A. Lumsdaine. Ownership passing: Efficient distributed memory programming on multi-core systems. February 2013. PPoPP 2013.

- [3] M. A. Heroux, D. W. Dorfler, P. S. Crozier, J. M. Willenbring, H. C. Edwards, A. Williams, M. Rajan, E. R. Keiter, H. K. Thornquist, and R. W. Numrich. Improving performance via mini-applications. 2009.

- [4] T. Hoefler et al. Leveraging MPI's One-Sided Communication Interface for Shared-Memory Programming. In Recent Advances in the Message Passing Interface - 19th European MPI Users' Group Meeting, EuroMPI 2012, Vienna, Austria, September 23-26, 2012. Proceedings, volume 7490. Springer, Sep. 2012.

- [5] C. Huang, O. Lawlor, and L. V. Kalé. Adaptive MPI. In Proceedings of the 16th International Workshop on Languages and Compilers for Parallel Computing (LCPC 2003), LNCS 2958, pages 306–322, College Station, Texas, October 2003.

- [6] Lawrence Livermore National Laboratory. Hydrodynamics challenge problem, 2012.

- [7] J. Liu, J. Wu, and D. K. Panda. High performance rdma-based mpi implementation over infiniband. In In 17th Annual ACM International Conference on Supercomputing (ICS'03, 2003.

- [8] Megan Gilge. IBM system Blue Gene solution: Blue Gene/Q application development, December 20 2012.

- [9] J. M. Mellor-crummey and M. L. Scott. Algorithms for scalable synchronization on shared-memory multiprocessors. ACM Transactions on Computer Systems, 9:21–65, 1991.

- [10] S. Negara, G. Zheng, K.-C. Pan, N. Negara, R. E. Johnson, L. V. Kale, and P. M. Ricker. Automatic MPI to AMPI Program Transformation using Photran. In 3rd Workshop on Productivity and Performance (PROPER 2010), number 10-14, Ischia/Naples/Italy, August 2010.

- [11] OpenMP Architecture Review Board. OpenMP application program interface version 3.0, May 2008.

- [12] K. Pedretti and B. Barrett. XPMEM: Cross-Process Memory Mapping.

- [13] S. Pellegrini, T. Hoefler, and T. Fahringer. On the Effects of CPU Caches on MPI Point-to-Point Communications. In *Cluster Computing (CLUSTER)*, 2012 IEEE International Conference on, pages 495 -503, sept. 2012.

- [14] M. Pérache, P. Carribault, and H. Jourdren. MPC-MPI: An MPI implementation reducing the overall memory consumption. In *Proceedings of the* 16th European PVM/MPI Users' Group Meeting on Recent Advances in Parallel Virtual Machine and Message Passing Interface, pages 94–103, Berlin, Heidelberg, 2009. Springer-Verlag.

- [15] H. Tang and T. Yang. Optimizing threaded MPI execution on SMP clusters. In ACM International Conference on Supercomputing (ICS), pages 381 – 392, 2001.

- [16] R. Thakur and W. Gropp. Test suite for evaluating performance of multithreaded mpi communication. *Parallel Comput.*, 35(12):608–617, Dec. 2009.

- [17] D. Turner and X. Chen. Protocol-dependent message-passing performance on linux clusters. In Proceedings of the IEEE International Conference on Cluster Computing, CLUSTER '02, pages 187-, Washington, DC, USA, 2002. IEEE Computer Society.

- [18] M. Woodacre, D. Robb, D. Roe, and K. Feind. The SGI Altix 3000 global shared-memory architecture. 2005.