# Affordable Multi-Layer Ceramic (MLC) Manufacturing for Power Systems (AMPS)

Final Report - Phases I and II

Reporting Period Start Date: 1 October 1999 Reporting Period End Date: 31 March 2002

Author: E. A. Barringer, Ph.D.

Issue Date: November 27, 2002

DOE Award Number: DE-AC26-99FT40691 - Phases I & II

McDermott Technology, Inc. Contract Research Division 2016 Mt. Athos Road Lynchburg, VA

McDermott Technology, Inc.

Research and Development Division

2016 Mt. Athos Road

Lynchburg, VA 24504-5447

and

1562 Beeson Street

Alliance, OH 44601-2196

Ceramatec, Inc. 2425 South 900 West Salt Lake City, UT 84119

M/A-COM Ceram, Inc. (formerly Advanced Refractory Technologies, Inc.) 699 Hertel Avenue Buffalo, NY 14207

# **DISCLAIMER**

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor McDermott Technology, Inc. nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

### **ABSTRACT**

McDermott Technology, Inc. (MTI) is attempting to develop high-performance, cost-competitive solid oxide fuel cell (SOFC) power systems. Recognizing the challenges and limitations facing the development of SOFC stacks comprised of electrode-supported cells and metallic interconnects, McDermott Technology, Inc. (MTI) has chosen to pursue an alternate path to commercialization. MTI is developing a multi-layer, co-fired, planar SOFC stack that will provide superior performance and reliability at reduced costs relative to competing designs.

The MTI approach combines state-of-the-art SOFC materials with the manufacturing technology and infrastructure established for multi-layer ceramic (MLC) packages for the microelectronics industry. The rationale for using MLC packaging technology is that high quality, low-cost manufacturing has been demonstrated at high volumes. With the proper selection of SOFC materials, implementation of MLC fabrication methods offers unique designs for stacks (cells and interconnects) that are not possible through traditional fabrication methods. The MTI approach eliminates use of metal interconnects and ceramic-metal seals, which are primary sources of stack performance degradation. Co-fired cells are less susceptible to thermal cycling stresses by using material compositions that have closely matched coefficients of thermal expansion between the cell and the interconnect.

The development of this SOFC stack technology was initiated in October 1999 under the DOE cosponsored program entitled "Affordable Multi-layer Ceramic Manufacturing for Power Systems (AMPS)". The AMPS Program was conducted as a two-phase program: Phase I – Feasibility Assessment (10/99 - 9/00); and Phase II – Process Development for Co-fired Stacks (10/00-3/02). This report provides a summary of the results from Phase I and a more detailed review of the results for Phase II.

Phase I demonstrated the feasibility for fabricating multi-layer, co-fired cells and interconnects and resulted in selection of the most promising configuration for high-performance, low-cost SOFC stacks. During Phase II, the MTI Team successfully refined the fabrication processes and achieved low-rate production of cells and interconnects (about 100 per month). Short stacks (3-10 cells) using co-fired cells and interconnects were assembled and tested to validate the MTI multi-layer SOFC design. The team successfully demonstrated co-fired repeat units, comprised of a cell and the interconnect layers. Development of co-fired cells and multi-layer interconnects based on the new stack design was completed; all component fabrication and stack testing efforts were redirected to the new design toward the end of Phase II. Finally, low-cost alternate materials for the interconnect body and conductors within the interconnect were identified. At the end of Phase II, the MTI Team successfully transitioned the multi-layer SOFC stack development effort to the Solid State Energy Conversion Alliance (SECA) program.

# **TABLE OF CONTENTS**

| <u>SECTION</u>                                                          | <b>PAGE</b> |

|-------------------------------------------------------------------------|-------------|

| EXECUTIVE SUMMARY                                                       | 1           |

| MULTI-LAYER, CO-FIRED SOFC STACK CONCEPT                                | 3           |

| PHASE I – FEASIBILITY ASSESSMENT                                        | 5           |

| Phase I Summary                                                         |             |

| Phase I Task Structure and Organization                                 |             |

| Task 1 – NEPA Reporting & Development of Co-fired Cells                 | 6           |

| Task 2 – Development of Filled-via Interconnects                        | 8           |

| Task 3 – Cell and Stack Modeling and Design                             | 9           |

| Task 4 – Manufacturing Cost Evaluation                                  |             |

| Task 5 – Multi-layer, Co-fired Oxide Configuration and Manufacturing    |             |

| Process Selection                                                       | 12          |

| Task 6 – Project Management and Reporting                               | 12          |

| PHASE II – PROCESS DEVELOPMENT FOR CO-FIRED STACKS                      | 13          |

| Phase II Objectives                                                     | 13          |

| Phase II Task Structure                                                 | 13          |

| Task 7 – Information Required for the National Environmental Policy Act | 15          |

| Task 8 – Preliminary Design of Short Stack (Active Area Component)      | 16          |

| Fabrication Process Modeling                                            |             |

| Stack Performance and Structural Modeling                               | 22          |

| Short Stack Assembly and Testing                                        |             |

| Task 9 – Co-fired Short Stack Development and Characterization          | 33          |

| Subtask 9.1 Co-fired Cell Refinement                                    |             |

| Subtask 9.2 Multi-layer Interconnect Refinement                         | 42          |

| Subtask 9.3 Development of Co-fired Short Stacks                        |             |

| Optional Subtask 9A – Design and Fabrication Development for            |             |

| Improved SOFC Stack                                                     | 50          |

| Optional Subtask 9B – Alternate SOFC Materials                          |             |

| Task 10 – Test Methodology and Plan                                     |             |

| Task 11 – Short Stack Fabrication and Cost Verification                 |             |

| Task 12 – Project Management and Reporting                              |             |

# **FIGURES**

| <b>NUMBER</b> |                                                                                                                                                                                                                                            | <b>PAGE</b> |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 1             | Schematic of multi-layer, co-fired repeat unit                                                                                                                                                                                             | 3           |

| 2             | Phase I project organization.                                                                                                                                                                                                              | 6           |

| 3             | Electrochemical performance for an initial 2.5 cm "button" cell                                                                                                                                                                            | 7           |

| 4             | Long-term test results for initial 2.5 cm "button" cells.                                                                                                                                                                                  | 8           |

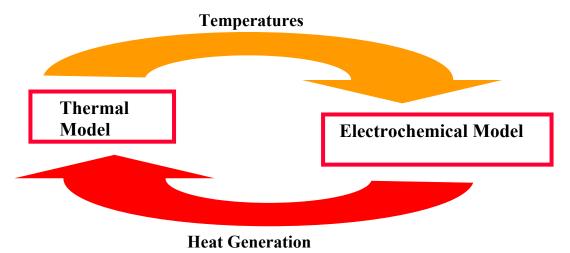

| 5             | The combined thermal/electrochemical model for stack performance requires an iterative process to reach solutions.                                                                                                                         | 9           |

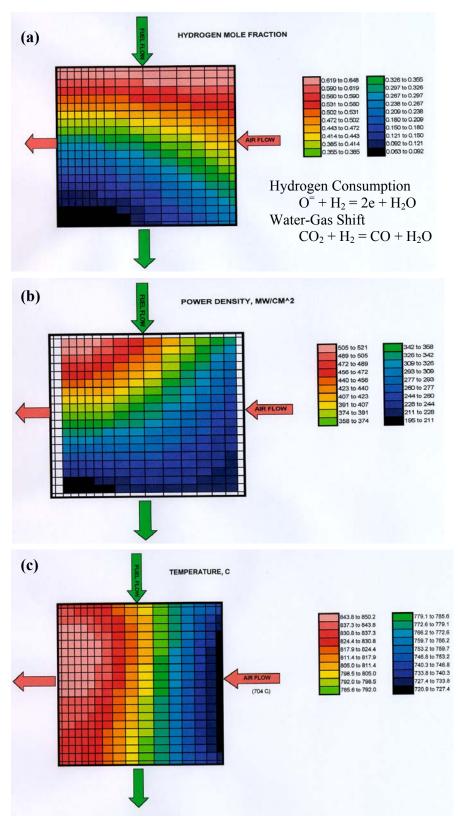

| 6             | Thermal/electrochemical model results for a cross-flow stack: a) hydrogen concentration; b) power density; and c) temperatures.                                                                                                            |             |

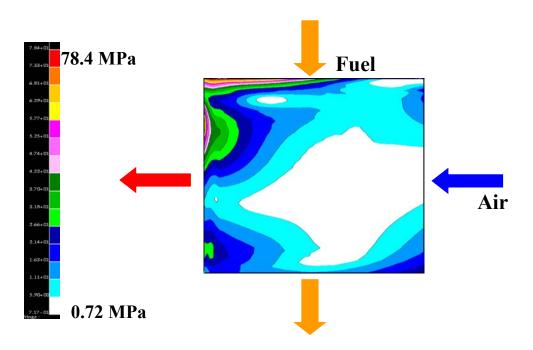

| 7             | Stress distribution for a typical temperature profile exhibited by a cross-flow stack (stress values in MPa).                                                                                                                              | 11          |

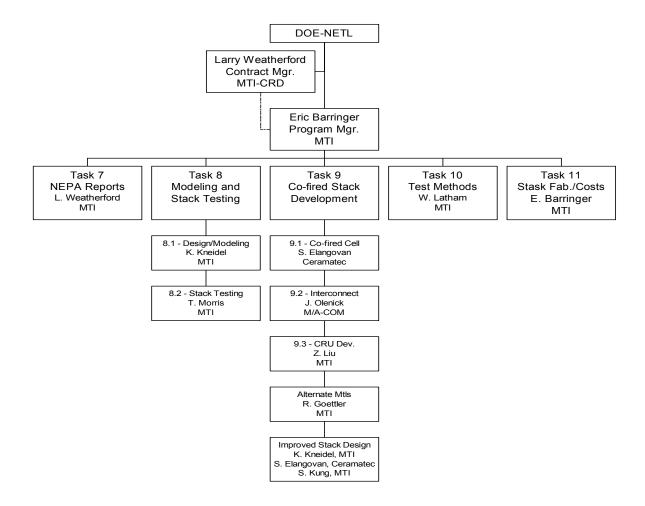

| 8             | Phase II project organization.                                                                                                                                                                                                             | 15          |

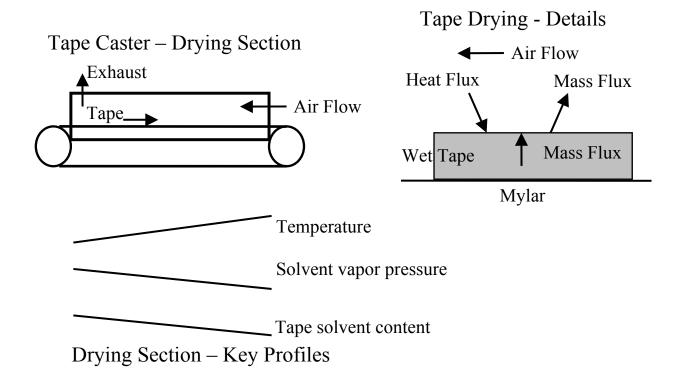

| 9             | Illustration showing key processes addressed in modeling the slip drying step with the tape caster                                                                                                                                         | 17          |

| 10            | Finite element model prediction showing the expected level of cell deformation within a mock co-fired repeat unit (prior to firing) and the observed deformation of a cell within a mock repeat unit due to excessive lamination pressure. | 18          |

| 11            | Simplified cylindrical conductor surrounded by a ceramic matrix was used for finite element models to assess stresses due to CTE mismatch between alternate conductor materials and the ceramic matrix.                                    |             |

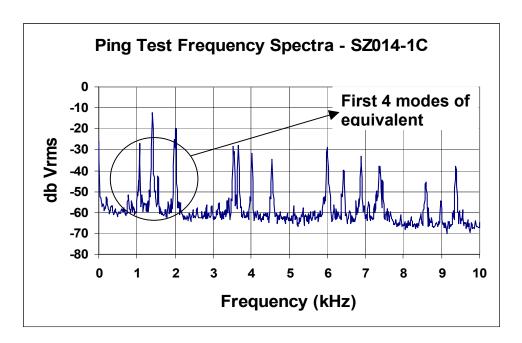

| 12            | The measured frequency spectrum for a 10cm x 10cm multi-layer interconnect.                                                                                                                                                                | 24          |

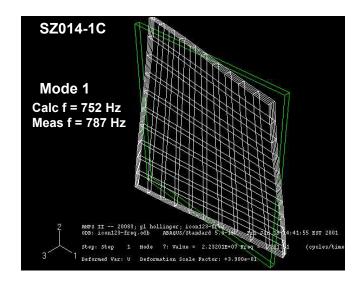

| 13            | The first two calculated vibration modes for a multi-layer interconnect                                                                                                                                                                    | 25          |

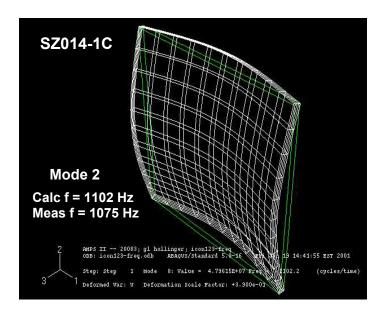

| 14            | Ping test data for three interconnects showing the sound attenuation for good, fair and bad interconnects.                                                                                                                                 | 26          |

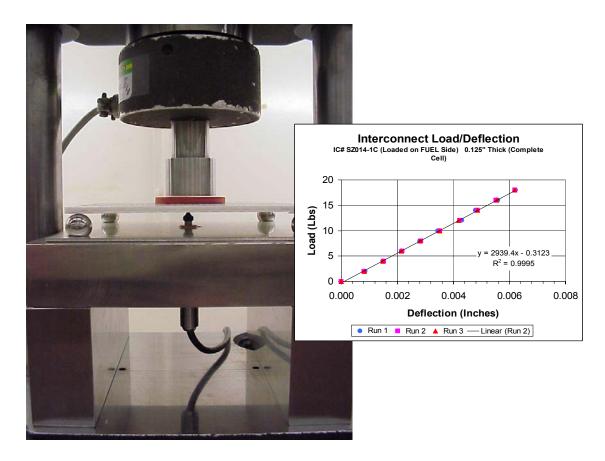

| 15            | Mechanical testing arrangement for the multi-layer interconnects                                                                                                                                                                           | 27          |

# **FIGURES - Continued**

| <u>NUMBER</u> |                                                                                                                                                                                | <b>PAGE</b> |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 16            | Load-to-failure data for a multi-layer interconnect.                                                                                                                           | 28          |

| 17            | Schematic showing general arrangement for stacks assembled using co-fire cells and multi-layer interconnects.                                                                  |             |

| 18            | Initial steps for stack assembly when using co-fired cells and multi-<br>layer interconnects.                                                                                  | 30          |

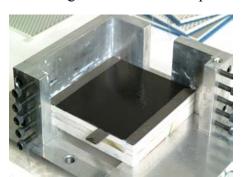

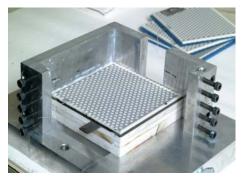

| 19            | A completed 5-cell stack assembled with co-fired cells and multi-layer interconnects.                                                                                          | 31          |

| 20            | Electrochemical performance data for a stack constructed with co-fired cell and multi-layer ceramic interconnects.                                                             |             |

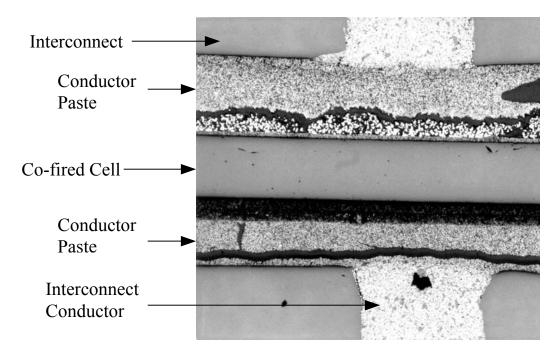

| 21            | Cross-section of a co-fired cell in a stack showing separations between the conductor paste and the cell.                                                                      | 32          |

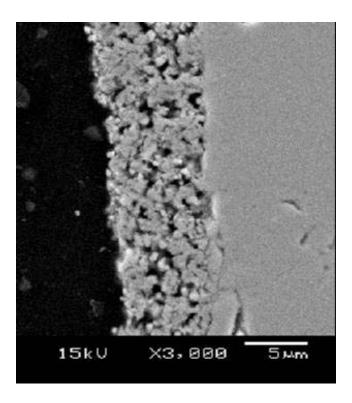

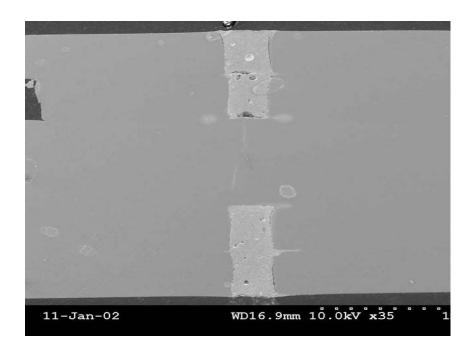

| 22            | SEM micrograph showing the structure of the improved co-fired anode                                                                                                            | 35          |

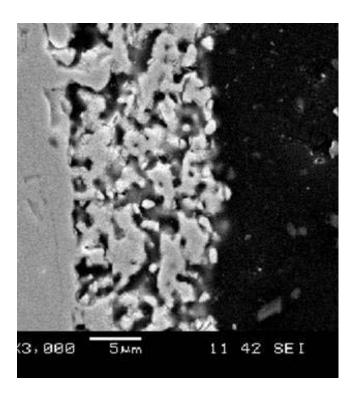

| 23            | SEM micrograph showing a cathode with an over-fired appearance                                                                                                                 | 36          |

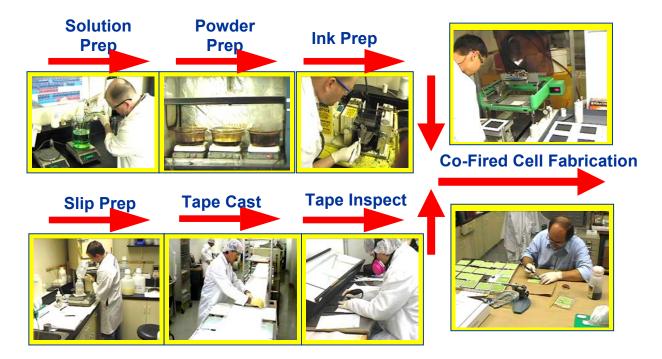

| 24            | Process flow for fabrication of co-fired cells.                                                                                                                                | 37          |

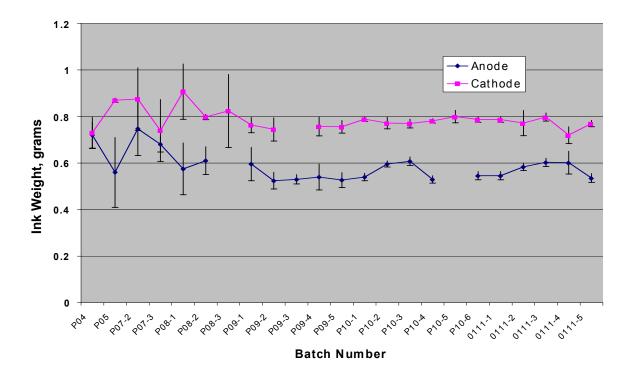

| 25            | Average weight of anode and cathode inks screen printed onto blanks for cell lots processed over a 9-month period.                                                             | 39          |

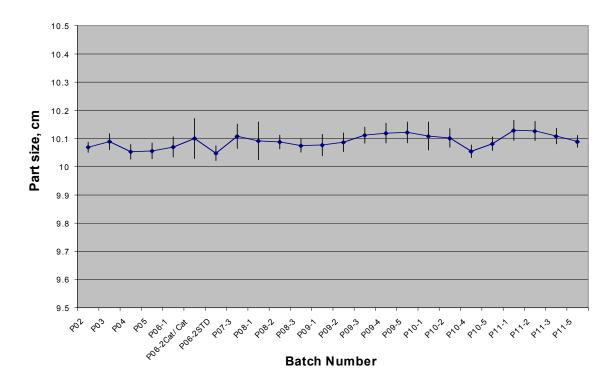

| 26            | Average dimension (in centimeters) of cells from lots processed over a 9-month period.                                                                                         | 40          |

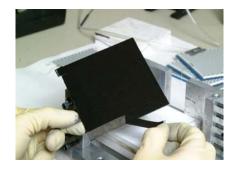

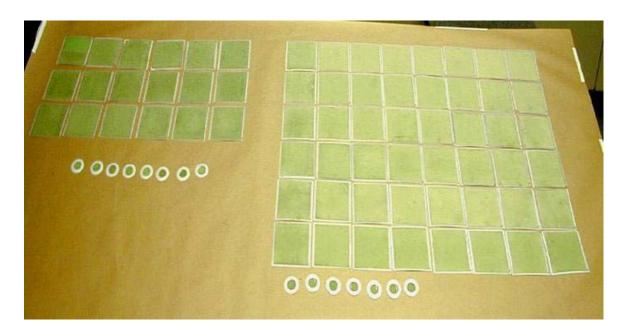

| 27            | Typical 10 cm x 10 cm cells produced in small (left) and large (right) production runs, along with the rider button cells that are used to assess electrochemical performance. | 41          |

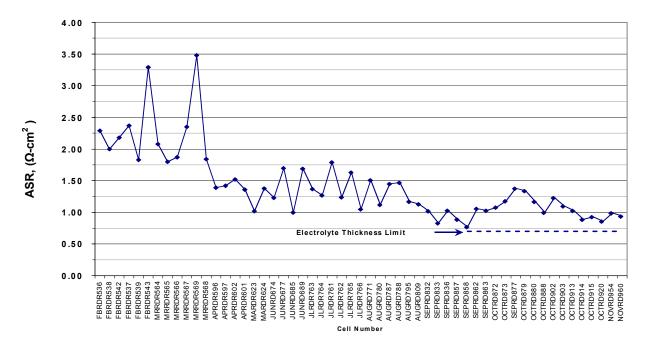

| 28            | Run chart showing the ASR values obtained for individual rider button cell over the period of February through November 2001.                                                  |             |

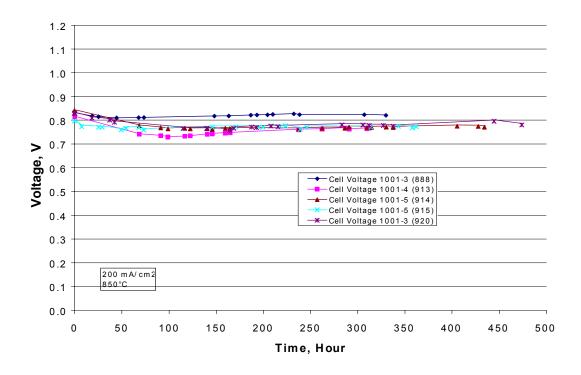

| 29            | Performance of rider button cells produced in October 2001.                                                                                                                    | 42          |

| 30            | Twenty-five meter long continuous tape caster at M/A-COM (Buffalo, NY) used to fabricate the interconnect tape.                                                                |             |

# **FIGURES - Continued**

| <b>NUMBER</b> |                                                                                                                                      | <b>PAGE</b> |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------|

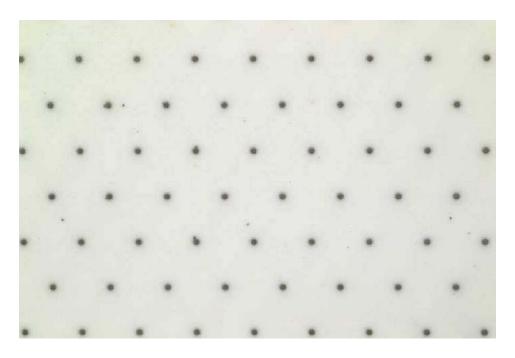

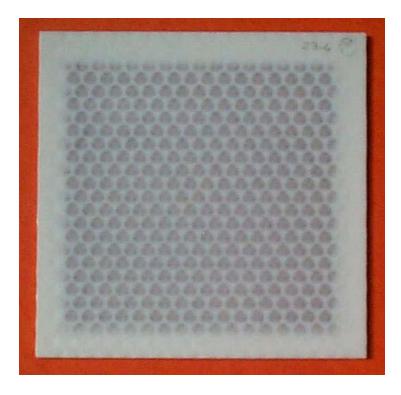

| 31            | Arrangement of conductive vias in the separator layer of an interconnect                                                             | 44          |

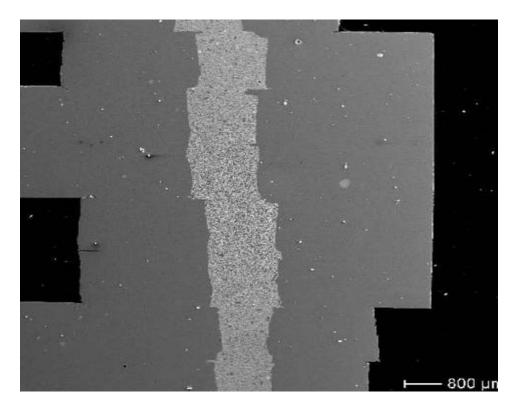

| 32            | Cross-section of an interconnect showing dense vias within the individual layers comprising the interconnect.                        | 44          |

| 33            | Arrangement of kiln furniture and setters in the periodic furnace used for interconnect co-firing.                                   | 45          |

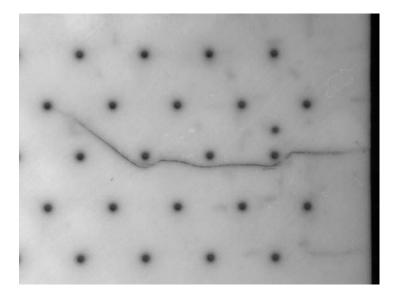

| 34            | Crack in a co-fired separator caused by improper binder burnout.                                                                     | 46          |

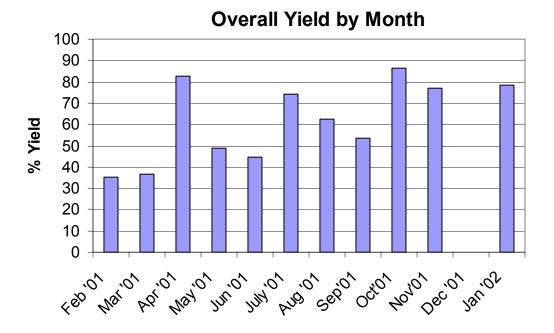

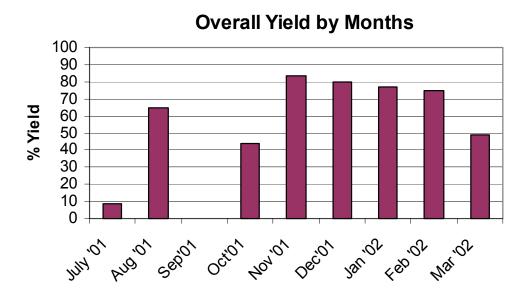

| 35            | Monthly production yields for the multi-layer interconnect.                                                                          | 47          |

| 36            | Illustration showing the fabrication of a co-fired repeat unit from a green c and the individual interconnect layers.                |             |

| 37            | Top view of a "good" 10cm x 10cm co-fired repeat unit (CRU)                                                                          | 49          |

| 38            | Fabrication yields for 10cm x n interconnects.                                                                                       | 52          |

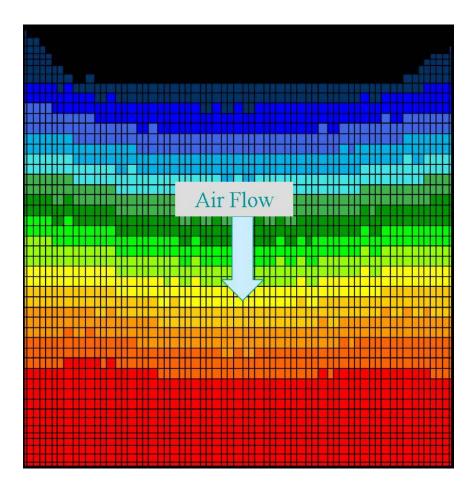

| 39            | Typical temperature distribution for the 10cm x n stack design                                                                       | 53          |

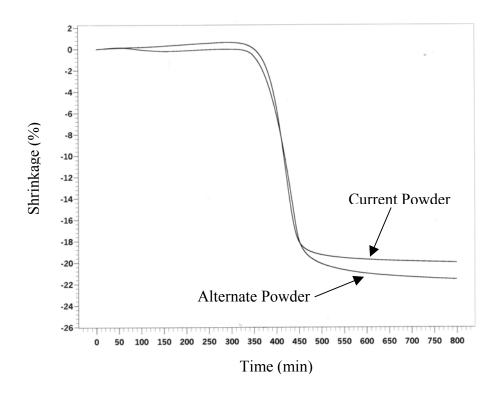

| 40            | Dilatometry curves (shrinkage as a function of time and temperature) for the current interconnect powder and a candidate replacement | 55          |

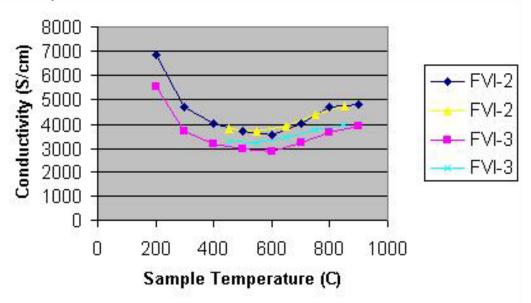

| 41            | Conductivity as a function of temperature for two candidate conductor materials for the fuel-flow layers within an interconnect.     | 56          |

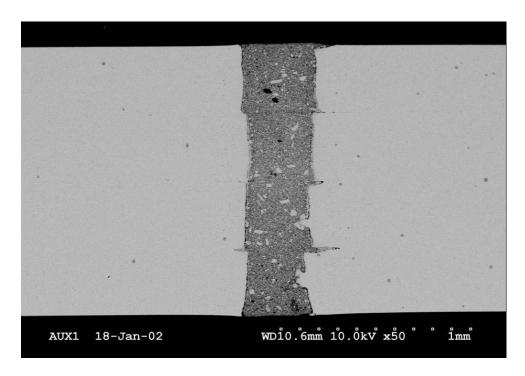

| 42            | Fuel-side conductor (in the form of vias) within a mock interconnect                                                                 | 57          |

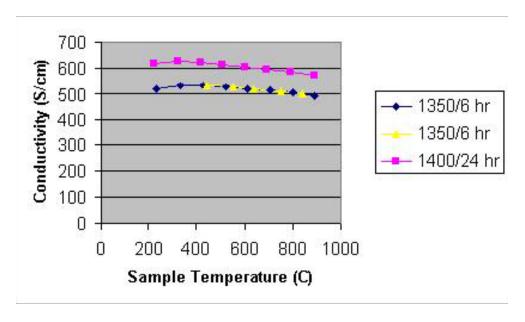

| 43            | Conductivity as a function of temperature for the candidate perovskites oxi material sintered under different conditions             |             |

| 44            | Co-fired perovskite conductor (in the form of vias) within a mock interconnect.                                                      | 59          |

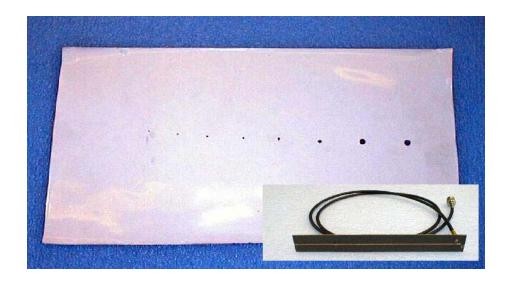

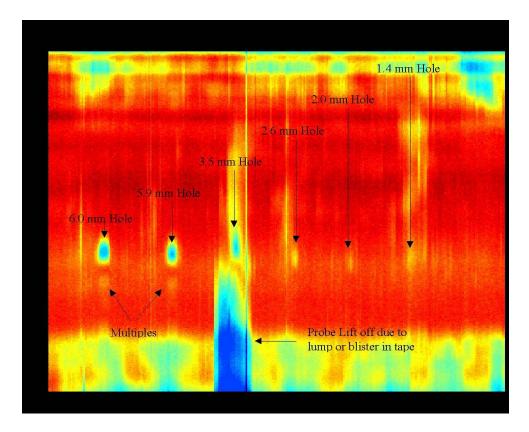

| 45            | Green electrolyte tape containing punched holes of the following diameter 1.4 mm, 2.0 mm, 2.6 mm, 3.5 mm, 5.9 mm and 6.0 mm.         |             |

| 46            | Time domain reflectometry results for green tape containing holes                                                                    | 61          |

# FIGURES – Continued

| NUMBE   | <u>CR</u>                                                                                                                                   | <b>PAGE</b> |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------|

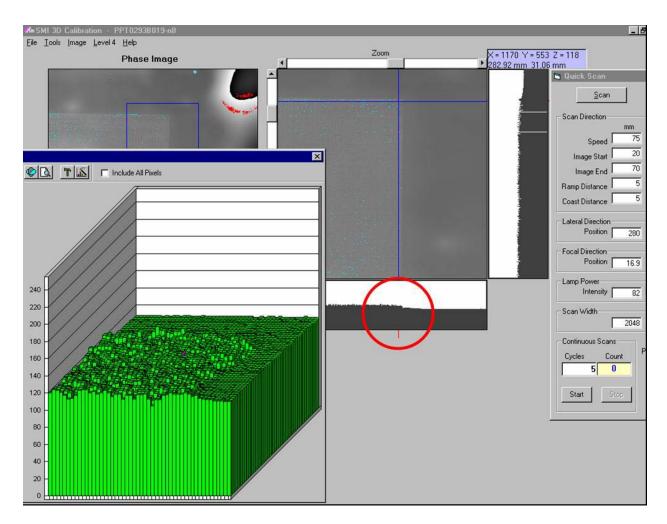

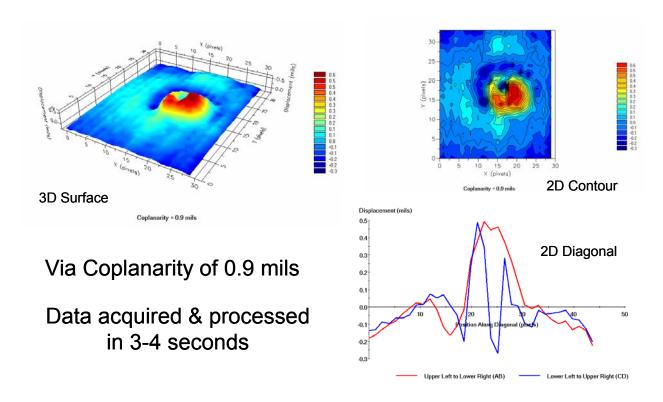

| 47      | Graphical output from a Shadow Moiré imaging system.                                                                                        | 62          |

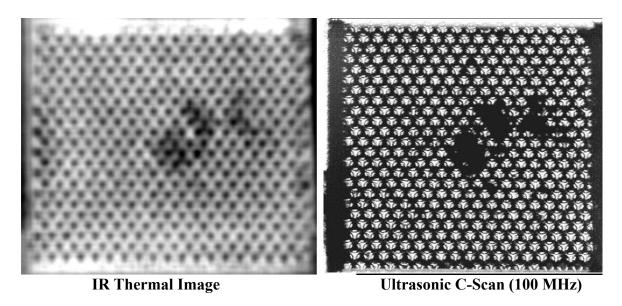

| 48      | Inspections of a mock interconnect to locate possible delaminations using using IR thermal imaging (left) and ultrasonic C-scanning (right) | 63          |

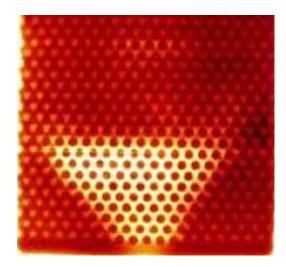

| 49      | IR thermal image showing large delaminations (bright area in image) in green mock interconnect                                              | 63          |

| 50      | Surface inspection of a green via on an interconnect using Shadow Moiré imaging                                                             | 64          |

|         | TABLES                                                                                                                                      |             |

| NUMBE   | <u>CR</u>                                                                                                                                   | <b>PAGE</b> |

| 1       | Phase II Schedule and Key Milestones                                                                                                        | 14          |

| LIST OI | F ACRONYMS AND ABBREVIATIONS                                                                                                                | 66          |

## **EXECUTIVE SUMMARY**

McDermott Technology, Inc. (MTI) is attempting to develop high-performance, cost-competitive solid oxide fuel cell (SOFC) power systems. Recognizing the challenges and limitations facing the development of SOFC stacks comprised of electrode-supported cells and metallic interconnects, MTI has chosen to pursue an alternate path to commercialization. MTI is developing a multi-layer, co-fired, planar SOFC stack that will provide superior performance and reliability at reduced costs relative to competing designs. The development of this SOFC stack technology was initiated in October 1999 under the DOE co-sponsored program entitled "Affordable Multi-layer Ceramic Manufacturing for Power Systems (AMPS)". The AMPS Program was proposed as a three-phase program: Phase I – Feasibility Assessment (10/99 – 9/00); Phase II – Process Development for Co-fired Stacks (10/00-3/02); and Phase III – SOFC Testing and Preparation of Business Plan (4/02-12/02). This report provides a summary of the results from Phase I and a more detailed review of the results for Phase II. Phase III of the research program was not authorized.

The SOFCo approach combines state of the art SOFC materials with the manufacturing technology and infrastructure established for multi-layer ceramic (MLC) packages for the microelectronics industry. The rationale for using MLC packaging technology is that high quality, low-cost manufacturing has been demonstrated at high volumes. With the proper selection of SOFC materials, implementation of MLC fabrication methods offers unique designs for stacks (cells and interconnects) that are not possible through traditional fabrication methods.

The overall objective for Phase I was to demonstrate the feasibility for fabrication of co-fired cells and multi-layer interconnects, and then to select the most promising configuration for high-performance, low-cost SOFC stacks. The MTI Team achieved almost all of the Phase I milestones. The preliminary design and materials characterization activities for the multi-layer cells and interconnects were completed. The team also made significant progress in the development of fabrication processes. The design/modeling team completed development of 2-D and 3-D electrochemical/thermal models and performed analyses for a number of alternative stack designs. Structural analyses were performed for many of the design options. This work led to the discovery of a new stack design that should provide for superior performance and reliability. Concurrently, a preliminary manufacturing cost model for the multi-layer SOFC stack was completed. Initial results suggested that the current cost target can be achieved, but only if low-cost raw materials for the interconnect are used.

The goal for Phase II was to complete implementation of MLC manufacturing processes for cell and interconnect fabrication and to demonstrate co-firing of cells and interconnect layers to form integral repeat units and short stacks. During Phase II, the MTI Team successfully refined the materials compositions and processes to achieve repeatable fabrication of cells and interconnects at a low production rate of 100 per month. In support of the manufacturing process development efforts, numerical models were developed for tape casting, lamination of interconnects and co-fired repeat units, binder removal, and stresses generated during co-firing. Intermediate cell performance targets (e.g., area specific resistance less than 0.8 ohm-cm²) were achieved for 2.5cm button cells. However, the desired level of performance was not obtained for full-size 10cm cells. Materials and process refinements to improve performance for full-size cells will be

continued on the Solid-State Energy Conversion Alliance (SECA) program. One key outcome from this effort was the definition of a path forward for development of co-fired cells that will achieve commercial performance targets.

Short stacks (3-10 cells) using co-fired cells and interconnects were assembled and tested to validate the MTI multi-layer SOFC design and to provide feedback to the cell and interconnect fabrication efforts. In support of stack assembly and testing, 3-D finite element models were developed to define stresses associated with stack assembly processes and stack operation. A 3-D finite element current distribution model was also developed to better understand the relationship between interconnect design and stack resistance.

A key accomplishment during Phase II was the successful demonstration of co-fired repeat units comprising a cell, the air-flow interconnects layers (laminated to the cathode side of the cell) and the fuel-flow interconnect layers (laminated to the anode side of the cell). While more work is required to achieve the desired level of performance, no major hurdles were identified. The MTI Team elected to not pursue the development of co-fired short stacks during Phase II due to the perceived challenges and the lack of clear benefits.

Another major accomplishment for the MTI Team was the successful development of co-fired cells and multi-layer interconnects using a new stack design. This design should offer improved performance and reliability relative to the initial stack design. Toward the end of Phase II, all component fabrication and stack assembly/testing activities were redirected to the new stack design. This design will be used for future development activities within the SECA program.

Significant progress was made in the development of alternate materials for the interconnect. Low-cost commercial powders for the multi-layer interconnect body were identified. In addition, promising candidate conductor materials for the interconnect were developed. These materials will be further refined and then implemented into interconnect production development efforts in the SECA program.

Finally, the MTI Team evaluated many non-destructive examination methods to assess their suitability for in-process quality control and final cell/interconnect inspection. A number of commercial-ready inspection methods, including microfocus X-ray radiography, C-scan ultrasonics, IR thermal imaging, and Shadow Moiré imaging, were shown to provide valuable quality information.

# **MULTI-LAYER, CO-FIRED SOFC STACK CONCEPT**

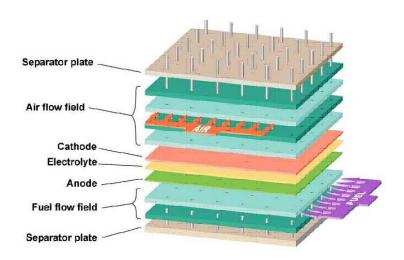

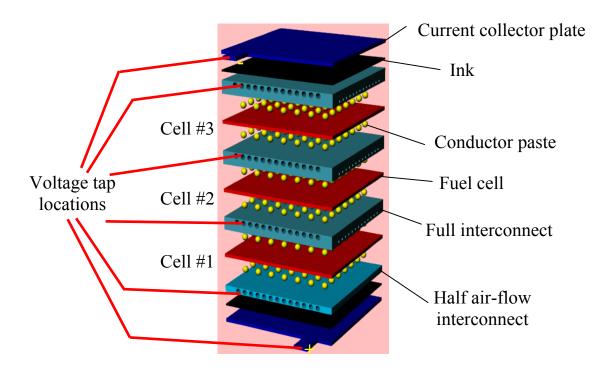

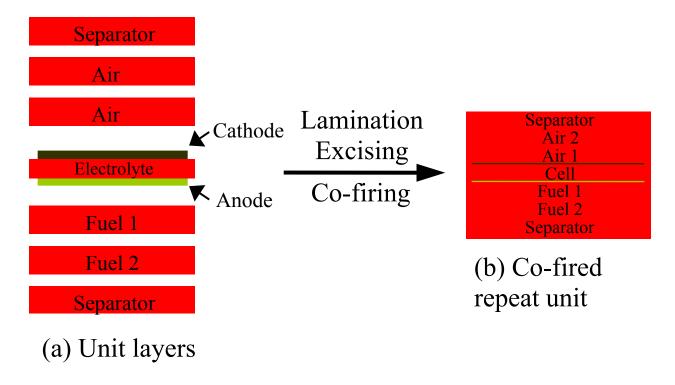

The basic design for the MTI multi-layer, co-fired SOFC stack repeat unit is illustrated in *Figure 1*. For the cell, a thin electrolyte layer (50-75 µm green thickness) is fabricated by tape casting. Anode ink is screen-printed onto one side of the electrolyte tape and cathode ink is printed onto the other side. The printed cell can be excised and then co-fired to form a self-supported cell or combined with the interconnect layers and then co-fired to form a single repeat unit (as illustrated in the figure).

Figure 1. Schematic of multi-layer, co-fired repeat unit. A single cell is surrounded by the fuel and air-flow layers of the interconnect.

The interconnect consists of multiple dense ceramic layers which provide for the essential functions of gas separation, reactant gas flow and electrical conduction. Air and gas separation is accomplished using one or more dense layers. Current flow through the interconnect is accomplished by imbedding conducting materials within each layer. *Figure 1* illustrates one such approach being explored by MTI, in which conductive vias permit current flow through the ceramic layers. The use of conductive vias is well established in the microelectronics industry. The conductor material must have sufficient conductivity so that the electric current can flow from one cell to the next with minimal resistive losses. Reactant gas flow is facilitated by punching holes or other structures in the gas flow layers within the interconnect (not illustrated in the figure). The size of the holes (or other features) and the thickness of the layers are driven by SOFC operating considerations, such as fuel distribution and utilization, air-side pressure drop, and temperature gradients. The interconnect is fabricated using standard multi-layer ceramic production operations: tape casting, punching, screen-printing, lamination, excising and co-firing.

In developing the multi-layer, co-fired SOFC stack components, a critical issue is the selection and engineering of materials for the cell and interconnect that have compatible processing characteristics. For the cell, defining a co-firing temperature that yields a dense electrolyte while avoiding deleterious reactions between the cathode and the electrolyte is a significant challenge. In addition, the materials have to be engineered so that shrinkage matching is achieved between the electrolyte and the electrodes, while maintaining the desired porosity in the electrodes. For the interconnect, selection of the composition of the ceramic body is driven by a number of factors. A key objective is to match the thermal expansion behavior of the cell. A second objective is to avoid materials that will adversely contaminate the cells, either during manufacturing or during SOFC stack operation. The conductor materials used in the interconnect have to provide sufficient conductivity to carry the current, but also require close matching of the coefficient of thermal expansion (CTE) and sintering shrinkage with the interconnect body.

The MTI multi-layer, co-fired SOFC approach offers a number of key advantages over competing approaches:

- Eliminates the use of metal interconnects and ceramic-metal seals, which are major sources for stack performance degradation.

- Less susceptible to thermal cycling problems (through close matching of the coefficient of thermal expansion (CTE) between the cell and interconnect).

- Reduced contact resistance between the electrodes and interconnect (for co-fired repeat units).

- Requires fewer sintering steps.

- Low-cost, high-volume manufacturing, which has been established in the microelectronics industry.

## PHASE I – FEASIBILITY ASSESSMENT

## **Phase I Summary**

Phase I of the AMPS Program began in October 1999 and was completed in September 2000 (12 month duration). The objectives for the Phase I effort were:

- Develop the materials and fabrication processes for multi-layer, co-fired cells and interconnects;

- Establish analytical performance and structural models for planar SOFC stacks; and

- Develop a manufacturing cost model for multi-layer SOFC stacks and demonstrate the viability of achieving low-cost manufacturing.

In accomplishing these objectives, the key outputs from Phase I were demonstrating the feasibility for the fabrication of multi-layer, co-fired cells and interconnects, and selecting the most promising configurations for high-performance, low-cost SOFC stacks.

The MTI Team substantially achieved the Phase I objectives. The preliminary design and materials characterization activities for the multi-layer cells and interconnects were completed. The team also made significant progress in the development of fabrication processes. The design/ modeling team completed development of 2-D and 3-D electrochemical/thermal models and performed analyses for a number of alternative stack designs. Structural analyses were performed for many of the design options. Concurrently, a preliminary manufacturing cost model for the multi-layer SOFC stack was completed. Initial results suggest that the current cost target can be achieved, but only if low-cost raw materials are used for the interconnect.

#### **Phase I Task Structure and Organization**

Phase I of the AMPS Program was subdivided into six (6) tasks:

- Task 1 NEPA Reporting and Development of Co-fired Cells (10/99-9/00)

- Task 2 Development of Filled-Via Interconnects (10/99-9/00)

- Task 3 Cell and Stack Modeling and Design (12/99-9/00)

- Task 4 Manufacturing Cost Evaluation (3/00-9/00)

- Task 5 Multi-layer, Co-fired Oxide Configuration and Manufacturing Process Selection (7/00-9/00)

- Task 6 Project Management and Reporting (10/99-9/00)

The Phase I effort was led by McDermott Technology, Inc (MTI), and was supported by two key subcontractors: Ceramatec, Inc. and Advanced Refractory Technology (now M/A-COM). The primary responsibilities for each entity follow:

- McDermott Technology, Inc (MTI) Prime Contractor

- Materials development and characterization

- Multi-layer SOFC design and modeling

- Inspection/test methods development (e.g., NDE methods)

- Ceramatec, Inc. Subcontractor

- SOFC materials technology

- Co-fired cell development

- Cell testing

- Advanced Refractory Technologies (now M/A-COM) Subcontractor

- Multi-layer interconnect development

- MLC manufacturing process development

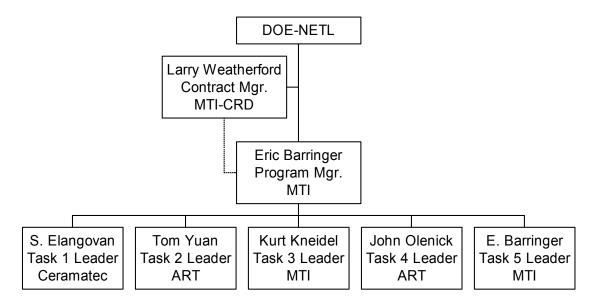

The Phase I project organization is shown in *Figure 2*. The responsibility for planning and executing the work within each task was assigned to key individuals within the MTI Team. These Task Leaders worked with the MTI Program Manager, Dr. Eric Barringer, to insure that the project objectives were achieved on time and within budget.

Figure 2. Phase I project organization.

Additional information regarding the Phase I activities and key accomplishments is provided in the following sections.

# Task 1 – NEPA Reporting & Development of Co-fired Cells

MTI completed a report providing environmental information described in "Required Information for the National Environmental Policy Act (NEPA)". The report was reviewed by DOE; the MTI Team was granted a Categorical Exclusion status for the Phase I activities. In addition, Hazardous Waste Substance Plans were prepared for each participant of the MTI Team. At the conclusion of Phase I, Hazardous Waste Reports were prepared and submitted to DOE.

MTI No. 1409 Final Report – Phases I & II Nov. 27, 2002 DOE No. DE-AC26-99FT40691 Page 6 of 66

A preliminary design of the co-fired cell was established. The design utilized current SOFC materials and is consistent with MLC fabrication methods. This cell is expected to have good electrochemical performance; area specific resistance (ASR) should be  $\leq 0.5$  ohm-cm<sup>2</sup> at 850°C.

The team determined that the present anode, cathode and electrolyte materials are compatible with co-firing in air at 1300-1400°C. Matching of sintering behavior (shrinkage) and achieving the desired level of residual porosity in the electrodes were achieved by adjusting the physical properties (particle size and surface area) of the starting powders and adding fugitive material to the electrode compositions.

Substantial progress was made in the development of the cell fabrication processes. Development of the YSZ tape formulation was completed. Tape casting, punching and lamination operations were demonstrated. Furthermore, tape-casting operations were successfully transitioned to a new 30-foot Carsten caster at Ceramatec. Substantial progress was also achieved in the formulation and screen-printing of electrode inks. However, achieving shrinkage matching between the electrolyte tape and the electrodes during co-firing, while at the same time obtaining the required electrode adhesion and desired level of porosity, was a significant challenge. The MTI Team defined a number of potential approaches toward achieving the desired electrode properties with the goal that acceptable electrodes would be developed during Phase II of the program.

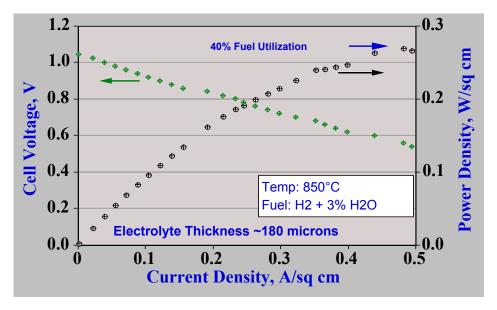

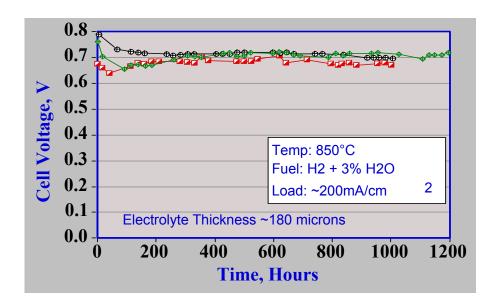

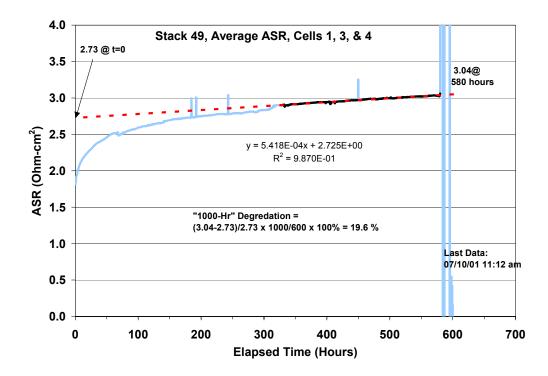

Initial co-fired button cells ( $\sim$ 2.5 cm diameter) achieved open circuit voltages > 1 Volt and area specific resistance (ASR) values in the range of 0.9-1.2 ohm-cm<sup>2</sup> at 850°C; the electrolyte thickness for these cells was approximately 180 microns. The performance of a button cell is shown in *Figure 3* (ASR  $\sim$  1.0 ohm-cm<sup>2</sup> at 850°C). Although testing of cells was limited during Phase I, preliminary endurance test data, shown in *Figure 4*, indicate that cell performance is relatively stable after an initial "burn-in" period (first 100 hours).

Figure 3. Electrochemical performance for an initial 2.5 cm "button" cell. The ASR for this cell is approximately 1.0 ohm-cm<sup>2</sup> at 850°C.

Figure 4. Long-term test results for initial 2.5 cm "button" cells.

Performance is relatively stable after an initial "burn-in" period.

Based on these results, performance of full-size ( $10 \text{cm} \times 10 \text{cm}$ ) co-fired cells using our proprietary electrolyte design (effective thickness of ~100 microns) should meet the Phase I target of  $\leq 0.8 \text{ ohm-cm}^2$  at  $850^{\circ}\text{C}$ . Further reduction of the ASR to  $< 0.5 \text{ ohm-cm}^2$  at  $850^{\circ}\text{C}$  will require improved electrolyte and anode materials (planned for Phase II). The team demonstrated fabrication of  $10 \text{cm} \times 10 \text{cm}$  co-fired cells in August 1999 (using 250 micron thick electrolyte tape). Initial efforts to fabricate cells using thin electrolyte tape yielded mixed results. It is believed that the improvements in ink formulation discussed above will be necessary to successfully fabricate large co-fired cells (MTI proprietary design). Based on the results to date, though, the MTI Team believes that the Phase I objective of demonstrating the feasibility for fabrication of co-fired, multi-layer cells has been met.

# Task 2 – Development of Filled-Via Interconnects

A preliminary design for the co-fired filled-via interconnect was established. The design utilized materials having thermal coefficients of expansion that were well matched to those for the electrolyte. Materials usage, pressure drop in the air and fuel gas flow passageways, and through-thickness resistance were key factors considered in the design. The MTI Team was successful in developing a design that appears to be consistent with the design guidelines and manufacturing practices (tape casting, punching, screen printing, lamination and excising) for MLC packages. This fact was demonstrated through the successful fabrication of "mock" filled-via interconnects by an outside vendor using two different tape/ink systems (low temperature co-fired ceramic/gold and alumina/platinum).

A set of materials for co-firing filled-via interconnects in air at 1300-1400°C was defined. The interconnect material was selected based on compatibility with the materials comprising the cell in terms of chemical interactions, physical properties (e.g., thermal coefficient of expansion), and sintering behavior. Materials to be used for conductive pathways through the interconnect were

selected based on compatibility with the interconnect material and electrical conductivity. Although the selected materials are suitable for demonstrating the feasibility of fabricating cofired, multi-layer SOFCs, their cost may be too high to achieve commercial cost targets for SOFC stacks. As a result, the MTI Team will need to explore lower cost materials for the interconnect body and the electrical conductors during Phase II.

Development of the fabrication processes for the filled-via interconnect represented the most difficult challenge for the MTI Team. Significant progress was made during Phase I. First, construction of an 8000 square foot clean room facility at M/A-COM (formerly ART) was completed and all equipment required for MLC component fabrication was installed. Second, preliminary interconnect tape and conductor ink formulations were defined. Third, all of the basic MLC operations (tape casting, blanking, punching, screen printing, lamination and firing) were demonstrated in the MLC facility at M/A-COM. During September 1999, fabrication of the first co-fired, filled-via interconnect was performed. While much work remains to enable the fabrication of functional interconnects, the MTI Team believes that feasibility for the multi-layer, co-fired interconnect design was successfully demonstrated.

# Task 3 – Cell and Stack Modeling and Design

The objective of this task was to develop analytical models that can be used to guide the design of a high-performance, reliable multi-layer SOFC stack. Significant accomplishments toward this objective were made during Phase I. A combined thermal/electrochemical model for planar SOFC stacks was developed. The basic concept behind this iterative model is illustrated in *Figure 5*.

Figure 5. The combined thermal/electrochemical model for stack performance requires an iterative process to reach solutions.

The model was used to predict 2-D distributions of temperature, resistance, current density and fuel gas composition (electrochemical potential) for a number of stack designs. *Figure 6* provides an example of the model results for a cross-flow stack at a specific set of operating conditions. *Figure 6a* shows the hydrogen concentration over the surface of a cell, while *Figures 6b and 6c* show the resulting power density and temperatures, respectively.

Figure 6. Thermal/electrochemical model results for a cross-flow stack: a) hydrogen concentration; b) power density; and c) temperatures.

Initial structural mechanics models were generated to calculate stress distributions resulting from temperature gradients across cells. As an example, the stress distribution predicted for a typical temperature profile exhibited by a cross-flow stack is shown in *Figure 7*. Since limited mechanical property data were available for the cell and interconnect materials, the modeling was only performed at the macro-scale level. Detailed models incorporating properties for each layer and specific geometric features are being prepared as material properties become available. A number of design options were analyzed, such as optimization of air and fuel gas flow. Although many options showed little difference in apparent electrochemical performance, substantial differences in temperature distribution and peak stresses were observed.

Figure 7. Stress distribution for a typical temperature profile exhibited by a cross-flow stack (stress values in MPa).

To address issues regarding the flow of air and fuel gas through the multi-layer stack additional modeling was performed. Computational Fluid Dynamics (CFD) codes were used to evaluate pressure drop through the air and fuel gas flow channels within the filled-via interconnect. In addition, micro-analyses were conducted to assess mass transfer through the porous electrodes. Micro-analyses of current flow through the stack were performed to insure that the selected materials and design features would provide for low stack resistance during operation at 800-900°C.

The most promising outcome of the modeling effort was the development of a novel modular stack design. Performing analyses for this design, however, required that the 2-D thermal/electrochemical model be extended to 3-D. The MTI design includes unique approaches for air and fuel gas manifolds, current collection and integration with air preheating and fuel

reformation. Significant improvements in electrochemical performance and stack reliability (temperature uniformity) appear possible. Equally important, the design represents a standardized stack configuration that appears to be amenable to high-volume production. The MTI Team pursued this new stack design during Phase II.

# **Task 4 – Manufacturing Cost Evaluation**

A critical factor in selecting SOFC stack designs and fabrication methods will be manufacturing costs. As such, the MTI Team is developing cost models for MLC production operations, with specific focus on the multi-layer, co-fired SOFC. Initial production models providing high-level cost estimates have been established and include raw material inputs and all factors (labor, equipment through-put and capacity, yields, etc.) associated with each manufacturing operation. Estimates of capital cost for a 110-120 MW/year production facility were included. Although more work is required to refine the production model, results to date indicate that raw material costs and process yields will have a major impact on stack cost. In particular, raw material costs may represent 30-50% of the total manufacturing costs for planar SOFC stacks, thus emphasizing the critical need to develop low-cost sources of raw materials.

# Task 5 – Multi-layer, Co-fired Oxide Configuration and Manufacturing Process Selection

The purpose of this task was to select the most promising stack design and approach to stack manufacturing. This task was initiated during August 2000 (month 11 of Phase I). Based on the work performed to date, the MTI Team developed a unique multi-layer SOFC stack design that can be readily configured into a standardized module that includes manifolds and current collectors. This design provides for superior electrochemical performance and reliability and appears to be compatible with MLC manufacturing methods. Preliminary cost analyses indicate that this stack can be manufactured at a cost of less than \$300/kW. During Phase II, the MTI Team further refined the fabrication processes established during Phase I and developed the new stack design. Cost modeling efforts were expanded to include process simulations in preparation for design of a pilot-scale manufacturing facility.

# Task 6 – Project Management and Reporting

All project management activities necessary to organize task activities, ensure adherence to project schedules and control costs were performed on a routine basis. A key accomplishment during Phase I was the creation of a unified team comprised of three different organizations in four geographic locations (MTI-Alliance, MTI-Lynchburg, Ceramatec-Salt Lake City, and M/A-COM-Buffalo). Open, direct communication between team members and technical assistance/collaboration between team members was accomplished. We also initiated activities involving external resources, such as Sandia National Laboratory, the Idaho National Engineering and Environmental Laboratory, Oak Ridge National Laboratory and Virginia Tech.

Nov. 27, 2002

# PHASE II – PROCESS DEVELOPMENT FOR CO-FIRED STACKS

# **Phase II Objectives**

Phase II of the AMPS Program begin in October 2000 and was completed in March 2002 (18 month duration). As proposed, the goal for Phase II was to complete implementation of MLC manufacturing processes for cell and interconnect fabrication and to demonstrate co-firing of active cell components to form integral short stacks (with 3-10 cells). This goal was subsequently modified to include demonstration of 3-10 cell stacks using separately co-fired cells and interconnects.

To achieve the Phase II goal, the following specific objectives were defined:

- Refine the materials and processes for fabrication of co-fired cells and multi-layer interconnects. Demonstrate the ability to achieve repeatable fabrication of cells and interconnects.

- Develop models to support manufacturing process development for cells and interconnects and to support stack assembly and performance testing.

- Establish the materials and methods for assembly of short stacks (3-10 cells) using co-fired cells and interconnects.

- Demonstrate cell ASR < 0.8 ohm-cm<sup>2</sup> and stack ASR < 1.0 ohm-cm<sup>2</sup> at 850°C (for electrolyte supported cells). Define a pathway to reduce cell and stack ASR to commercial targets.

- Demonstrate the fabrication of co-fired repeat units and assess the feasibility for the fabrication of co-fired short stacks.

- Develop an improved SOFC stack design that overcomes the limitations created by the initial stack design and takes advantage of the strengths associated with multi-layer ceramic manufacturing methods.

- Assess the feasibility for replacing the high-cost raw materials used for multi-layer interconnects with low-cost alternatives.

- Develop destructive, non-destructive and electrochemical characterization methods that can be used for in-process quality control and final component inspection.

- Update the preliminary manufacturing cost model and reaffirm the potential for low-cost, high-volume production of co-fired, multi-layer SOFC stacks.

#### Phase II Task Structure

The Phase II effort was subdivided into six (6) primary tasks and additional subtasks, as follows:

- Task 7 Information Required for the National Environmental Policy Act

- Task 8 Preliminary Design of Short Stack (Active Area Component)

- Subtask 8.1 Design and Modeling

- Subtask 8.2 Stack Assembly and Testing

- Task 9 Co-fired Short Stack Development and Characterization

- Subtask 9.1 Refinement of Co-fired Cell Fabrication

- Subtask 9.2 Refinement of Multi-layer Interconnect Fabrication

- Subtask 9.3 Development of Co-fired Short Stacks

- Optional Subtask 9A Design and Fabrication Development for Improved SOFC Stack

- Optional Subtask 9B Alternate SOFC Materials

- Task 10 Test Methodology and Plan

- Task 11 Short Stack Fabrication and Cost Verification

- Task 12 Project Management and Reporting

The schedule for the Phase II activities is shown in Table 1.

Table 1. Phase II Schedule and Key Milestones

| TASK             | Y  | EAI | R 1 |    | YEAR 2 |    |    |    | YEAR 3 |    |          |    | YE | AR 4 | MILESTONE/DECISION POINT<br>DESCRIPTION                   |

|------------------|----|-----|-----|----|--------|----|----|----|--------|----|----------|----|----|------|-----------------------------------------------------------|

|                  | Q1 | Q2  | Q3  | Q4 | Q1     | Q2 | Q3 | Q4 | Q1     | Q2 | Q3       | Q4 | Q1 | Q2   |                                                           |

| PHASE I          |    |     |     |    |        |    |    |    |        |    |          |    |    |      |                                                           |

| PHASE II         |    |     |     |    |        |    |    |    |        |    |          |    |    |      |                                                           |

| TASK 7           |    |     |     |    | Y      |    |    |    |        |    |          |    |    |      | NEPA reporting requirements completed                     |

| TASK 8           |    |     |     |    |        |    |    |    | V      |    |          |    |    |      | Models validated and pSOFC short stack design established |

| TASK 9.1         |    |     |     |    |        |    |    | \  |        | j  |          |    |    |      | Fabrication of high quality co-fired cells (100/mo)       |

| TASK 9.2         |    |     |     |    |        |    |    | 1  | 7      |    |          |    |    |      | Fabrication of high quality interconnects (100/mo)        |

| <b>TASK 9.3</b>  |    |     |     |    |        |    |    |    |        | Y  |          |    |    |      | Co-fired pSOFC short stack demonstrated                   |

| TASK 10          |    |     |     |    |        |    |    |    |        |    |          |    |    |      | Inspection methods defined & test plan completed          |

| TASK 11          |    |     |     |    |        |    |    |    |        | V  |          |    |    |      | Decision on short stack design/assembly                   |

|                  |    |     |     |    |        |    |    |    |        | •  | <b>•</b> |    |    |      | Short stacks successfully fabricated                      |

| TASK 12          |    |     |     |    |        |    |    |    |        |    |          |    |    |      |                                                           |

| Optional<br>Work |    |     |     |    |        |    |    |    |        |    |          |    |    |      |                                                           |

| TASK 9A          |    |     |     |    |        |    |    |    |        |    |          |    |    |      | Design and development of improved stack (10cmxn)         |

|                  |    |     |     |    |        |    |    |    | ▼      |    |          |    |    |      | Demonstration of 10cmxn cells and interconnects           |

|                  |    |     |     |    |        |    |    |    | 7      |    |          |    |    |      | 10 cm x n pSOFC stack demonstrated                        |

|                  |    |     |     |    |        |    |    |    |        |    |          |    |    |      | Preliminary validation of models & 10 cm x n design       |

| TASK 9B          |    |     |     |    |        |    |    |    |        |    |          |    |    |      | Improved cell and interconnect materials identified       |

▼ Milestone ◆ Decision Point

The Phase II project organization is shown in *Figure 8*. The responsibility for planning and executing the work within each task was assigned to key individuals within the MTI Team. These Task Leaders worked with the MTI Program Manager, Dr. Eric Barringer, to insure that the project objectives were achieved on time and within budget.

Figure 8. Phase II project organization

Additional information regarding the Phase II activities and key accomplishments is provided in the following sections.

# Task 7 – Information Required for the National Environmental Policy Act

MTI provided to DOE all of the information required for the National Environmental Policy Act (NEPA). In particular, Environmental Questionnaires and Hazardous Waste Substance Plans were prepared for each entity participating in the Phase II effort. At the conclusion of Phase II, Hazardous Waste Reports were prepared for each entity and submitted to DOE.

# Task 8 – Preliminary Design of Short Stack (Active Area Component)

The Task 8 effort, as originally proposed, consisted of updating the planar SOFC performance and structural models developing during Phase I, and then establishing a preliminary design for a 3-10 cell co-fired short stack. Prior to initiating Phase II, the work plan was modified to incorporate the following additional activities:

- Fabrication Process Modeling Fabrication of co-fired cells, multi-layer interconnects and co-fired short stacks involve a number of sequential steps. Fabrication of high-quality components that achieve expected performance requires substantial knowledge of the key processing steps and the ability to control the processes. As such, the MTI Team recognized that numerical modeling of specific processes might be required to support the manufacturing process development work being performed under Task 9.

- Stack Performance and Structural Modeling In addition to performing design/modeling activities for co-fired short stacks, the MTI Team defined the need to perform parallel design/modeling efforts for post-fired assembled stacks comprised of co-fired cells and multi-layer interconnects. The models were to be used to evaluate alternate designs, assess the impact of new materials, and to evaluate the structural reliability of individual components and assembled stacks.

- Short Stack Testing Testing of short stacks (3-10 cells) comprised of co-fired cells and interconnects was determined to be a critical activity for validating the MTI multi-layer SOFC stack design and also for providing feedback to the cell and interconnect fabrication development tasks. Thus, the Team proposed to fabricate and test a limited number of short stacks. Performance data from these tests were to be used to validate the thermal/electrochemical and structural models and to update them, as appropriate. It was estimated that post-fired short stacks would be available for testing in the first quarter of 2001, while co-fired short stacks would not be available until early 2002. The results from this work produced improvements in the cells and interconnect design about one year earlier than originally scheduled.

The Task 8 activities and key results are summarized in the following sections.

#### **Fabrication Process Modeling**

Numerical modeling was performed to support the manufacturing process development efforts for co-fired cells, multi-layer interconnects and co-fired repeat units. Modeling activities are summarized below for the following areas: tape casting, lamination of interconnects and co-fired repeat units, binder removal, and stresses generated during co-firing.

• Tape Casting – Two modeling activities were conducted to support tape casting of electrolyte and interconnect tape. First, modeling of the slip drying process during tape casting was performed to improve the quality of tape used for cell and interconnect fabrication. Casting of the electrolyte and interconnect tape proved to be quite difficult

due to the use of fine-grained ceramic powders that are necessary for the co-fired repeat unit approach (to minimize the co-firing temperature). Tape fabricated with these powders often showed excessive defects (cracks, curling) and poor thickness uniformity. After considerable study, it became evident that controlled removal of solvent from the slip in the drying section of the tape caster was the key to improving tape quality. To optimize the slip drying process, illustrated in *Figure 9*, a gas-phase mass transfer model was developed. The model was used to calculate the required air flow rate and temperature profile within the drying section of the caster to insure that almost all of the solvent was removed, but that the drying rate would not exceed the internal diffusion rate of solvent from the slip (to prevent "skinning"). Calculations were performed for both electrolyte and interconnect tapes; recommended drying profiles were successfully implemented on the tape casting machines at Ceramatec and M/A-COM. Significant improvements in tape quality resulted at both locations.

Figure 9. Illustration showing key processes addressed in modeling the slip drying step with the tape caster.

Second, modeling of slip flow in the doctor blade assembly was performed to support the design of an improved doctor blade that would achieve more uniform flow distribution for the slip and allow for casting of wider tape. Based on the modeling results, a new doctor blade assembly was fabricated and successfully demonstrated. After a few minor modifications, the new doctor blade assembly was implemented in the manufacturing development operations at Ceramatec and M/A-COM.

• Lamination of Interconnects and Co-fired Repeat Units – In the fabrication of the multi-layer interconnects and co-fired repeat units, laminating individual tape layers together to form a coherent body is required. Lamination is achieved by applying pressure to the tape layers at an appropriate elevated temperature to cause the "green" (unfired) tape layers to bond together. Insufficient pressure or too low in temperatures leads to non-bonded areas (delaminations) within the laminated part. Excessive pressure generally leads to deformation of the tape and/or the formation of cracks. Because of the fine ceramic powder used in fabricating the multi-layer interconnects, lamination of the interconnect tape proved to be very difficult.

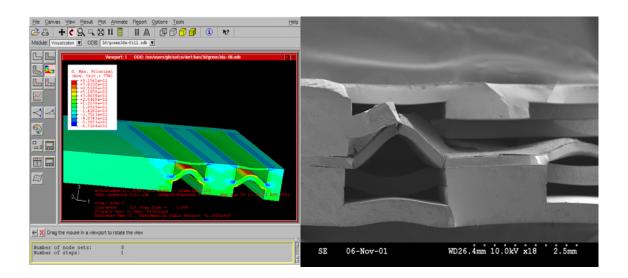

To identify appropriate temperature and pressure conditions for achieving acceptable lamination, numerical modeling of the lamination process was performed. Finite element models were developed for simplified versions of the multi-layer interconnect and the cofired repeat units; these "mock" structures retained the key features of the components, but eliminate details that would overly complicate the models. In order to run the models, mechanical properties for the interconnect tape were required. A substantial number of tape specimens were tested under tension and compression to obtain the necessary data. An example of the finite element model output for a mock co-fired repeat unit is shown in *Figure 10*. For the case shown, the lamination conditions were such that the model predicted that substantial deformation of the cell would occur. Upon examination of mock repeat units fabricated using such conditions, the predicted level of deformation was observed (see *Figure 10*).

Figure 10. Finite element model prediction showing the expected level of cell deformation within a mock co-fired repeat unit (prior to firing) and the observed deformation of a cell within a mock repeat unit due to excessive lamination pressure.

After validation using mock components, the finite element models were used to evaluate design modifications for the interconnect and co-fired repeat units and changes to the lamination process in order to achieve more uniform stress distributions during lamination, and thereby substantially reduce the occurrence of deformation and cracks.

• Binder Removal – Removal of organic tape constituents from laminated multi-layer ceramic bodies is a critical step within the co-firing process. Improper removal of the binder phase (organics) during co-firing can result in defects, such as minor delaminations between layers or slight warpage of the component. In the extreme case, excessive binder removal rates can cause severe deformation and cracking of the part.

During the development of the fabrication processes for multi-layer interconnects and cofired repeat units, the MTI Team experienced significant difficulties in the co-firing operations. Significant delamination and cracking was observed; improper binder burnout was identified as a primary cause. Initial investigations showed that binder removal from the interconnect tape was made more difficult as a result of two factors: a) the fine ceramic powder used for the interconnect requires a high binder content in the tape to enable lamination; and b) the fine ceramic powder creates very small pathways for the diffusion of gasses out of the components during the burnout process. Rather than rely on empirical approaches to finding a solution to the binder removal problem, the MTI Team used numerical modeling to define an optimal binder burnout process.

Modeling of the binder removal process involved a multi-step approach. First, thermogravimetric analysis (TGA) runs were performed in flowing air for the interconnect tape using a range of heating rates. The TGA data were then used to generate rate equations for the various kinetic processes (volatilization of solvent and low molecular weight species, oxidation of binder constituents, diffusion of gasses out of the part). Calculated values of weight loss versus time/temperature for the interconnect tape agreed well with the measured values (from TGA runs). Second, the rate expressions were used to define an "ideal" binder burnout heating schedule. The "ideal" heating schedule was then converted into a practical heating schedule that might be implemented in a commercially available co-firing furnace. Third, a numerical thermal transient model was developed for the current sintering furnace. The furnace was instrumented with numerous thermocouples and then run to obtain data for model validation. Fourth, final calculations were performed and a refined binder burnout heating schedule was defined. In addition, recommendations were made regarding the furnace capabilities and settering method that would achieve the desired binder removal process.

As a result of the modeling effort, a binder burnout step was added to the co-firing process for both interconnects and co-fired repeat units. This process change dramatically improved the quality of the co-fired parts, eliminating many of the delaminations and cracks, and improving flatness.

Nov. 27, 2002

• Stresses Generated During Co-firing – A key area of concern for the MTI Team was the stresses generated during co-firing of cells and interconnects. It was recognized that high stresses would lead to warpage of components and the formation of cracks. Excessive stresses could lead to component failure. Preliminary analysis indicated that the primary sources for stresses were: a) shrinkage mismatch during co-firing between the materials comprising the cells and interconnects, and b) coefficient of thermal expansion (CTE) mismatch between the materials.

Shrinkage mismatch during co-firing was examined for both the cells and interconnects. For the cells, the primary concern was shrinkage behavior of the electrodes that were in contact with the electrolyte layer. Finite element modeling, primarily performed by Sandia National Laboratory, and experimental work revealed that shrinkage mismatch between cell constituents would strongly affect the flatness of the co-fired cells. Cell failure due to cracks or other defects was not an issue unless the shrinkage mismatch was excessive. For interconnects, shrinkage mismatch between the ceramic body and the electrical conductors was investigated through modeling and experimentation. Cracking of the ceramic body surrounding the conductors was the key concern. Through careful engineering of the starting raw materials, good shrinkage match was readily achieved for the interconnect; no cracks or other defects have been observed.

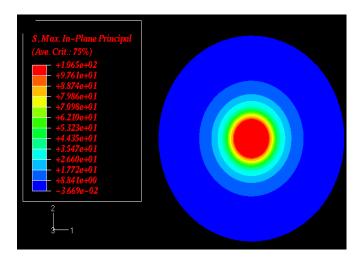

Mismatch of coefficients of thermal expansion (CTE) between the cell and interconnect constituent materials is a major source for stresses, particularly during cool down of components from the sintering temperature and subsequently during thermal cycling. For the interconnects, the CTE mismatch between the ceramic body and the conductor material used during Phase II was very small. As a result, high stresses and crack formation were not an issue. However, the conductor material utilized a noble metal, making it prohibitively expensive for practical use. To support development of new, low-cost conductor materials for the interconnect; finite element modeling was performed using a simplified conductor geometry, as illustrated in *Figure 11*. The modeling results were used to define the allowable range of CTE mismatch to minimize stresses and achieve an acceptable probability of failure.

Figure 11. Simplified cylindrical conductor surrounded by a ceramic matrix was used for finite element models to assess stresses due to CTE mismatch between alternate conductor materials and the ceramic matrix.

For cells, the CTE mismatch between the anode and the electrolyte became an important issue. Finite element models for various cell designs showed that significant stresses are generated at the anode-electrolyte interface when the cells are cooled down from the sintering temperature to room temperature. In some cases, tensile stresses in the anode greater than 300 MPa were predicted. Cell fabrication experiments were performed in concert with the modeling effort. Cells fabricated under conditions for which high stresses were predicted were observed to have substantial microcracking of the anode; this confirmed that the tensile stresses in the anode exceeded the projected anode strength (~ 100 MPa). As a result of the modeling and experimental work, substantial effort was directed toward re-engineering the anode, with the

intent of reducing the CTE mismatch with the electrolyte while maintaining the electrochemical activity.

# Stack Performance and Structural Modeling

Numerical modeling was performed in two areas to support the development of the multi-layer, co-fired stacks: a) stack performance modeling, and b) structural modeling of cells, interconnects and stack assemblies. The modeling work performed in these two areas is summarized below.

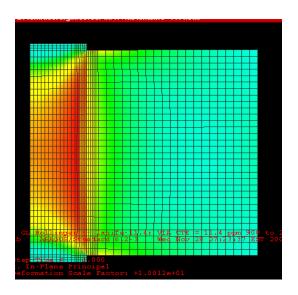

- Stack Performance Modeling During Phase I, the MTI Team developed a 2-D coupled thermal/electrochemical model for the initial stack design. During Phase II, the model was modified for the new 10cm x n stack design and included the appropriate material properties and the primary geometric factors. After benchmarking the new model against the older 2-D models, calculations were performed to assess stack performance and temperature distributions for a number of stack operating conditions. A 3-D finite element structural model was also developed for the new stack design. Calculated temperature distributions for selected operating conditions were used in the finite element model to assess stress levels. The stress modeling did not reveal any area of concern within the stack, but did confirm that high stresses may exist at the electrolyte-anode interface due to the mismatch in CTE.

- Stack Performance Micro-modeling While the thermal/electrochemical model provided useful insight into the expected operation of stacks, the MTI multi-layer SOFC stack design incorporates some unique design features that may significantly impact performance. Two specific areas were further investigated using "micro-models": a) current flow through the stack, with particular emphasis on the conductors within the interconnect, and b) diffusion of reactants from the gas flow channels within the interconnect to the active electrode surfaces.

During operation of the multi-layer SOFC stack, current flows through the conductors within an interconnect to the cathode on the adjacent cell, through the cell, and then flows into the conductors in the interconnects that are adjacent to the anode. Experience has shown that the overall stack resistance is determined by the combination of individual resistances: cell resistance, interconnect resistance, contact resistance between cells and interconnects (on both the anode and cathode sides), and the current collector resistance. Furthermore, the resistance of the multi-layer interconnects depends on the resistivity of the conductor material and the conductor cross-sectional area (size and number of conductors). In addition, the interfacial resistance between the cells and the interconnect depends on the resistivity of the electrodes and the distribution of conductors within the interconnect that make contact with the cells. In order to better understand the relationship between the interconnect design, including the choice of conductor material and stack resistance, numerical modeling was performed. A 3-D finite element current distribution model was developed. The model incorporated all of the relevant design features and material properties. Calculations were first performed for specific test configurations; actual components incorporating the test configuration features were

fabricated and then tested to validate the models. Subsequently the model was used to estimate the interconnect and interface resistances for a range of interconnect designs and material conductivities. Improvements in the stack design and guidance for materials selection were key outcomes of this work. Toward the end of Phase II, the model was modified to facilitate analyses for various current collector designs and methods for attaching the current collectors to the multi-layer interconnects.

In addition to evaluating current flow, the MTI Team performed modeling to examine diffusion of fuel gas (hydrogen) and oxygen from the gas flow channels within the interconnects into the active portions of the anode and cathode, respectively. The gas diffusion models provided valuable insight regarding specific interconnect design features and the required thickness and porosity for the anodes and cathodes.

• Structural Modeling for Stack Assembly – Several modeling activities were performed in support of the stack assembly efforts involving co-fired cells and multi-layer interconnects. One approach to stack assembly explored by the MTI Team involved sequentially stacking together interconnects and cells, followed by application of a compressive load to insure good electrical contact and sealing between the cells and interconnects. When stacks are constructed with non-flat cells and interconnects, stresses are generated when the compressive load is applied and the components are deformed. To assess the level of stresses generated during stack assembly, physical characterization (including flatness) was performed for a number of cells and interconnects. Stiffness was also measured for these components using a specially designed fixture and a mechanical testing system. The data was then used in a finite element model for the stack and the stresses were estimated for both cells and interconnect. A key outcome from this modeling effort was guidelines regarding the desired flatness for cells and interconnects being produced under the cell and interconnect refinement task.

In support of the stack assembly development effort, structural modeling was performed to examine several different approaches for attaching metal current collectors the multi-layer interconnects. Effective current collector attachment required good electrical contact with the conductors incorporated into the interconnect and, at the same time, low stresses. Finite element modeling was performed to estimate the expected stresses for a number of candidate current collector materials and several bonding materials (including conductive ceramic bond agents and various braze alloys). Through this work, the most promising combinations of current collector materials and bonding methods were identified.

• Cell and Interconnect Structural Modeling – Substantial structural modeling was performed during Phase II to support the design and fabrication development for co-fired cells and multi-layer interconnects. In addition to the previously mentioned finite element modeling to assess CTE and co-firing shrinkage mismatch issues for both cells and interconnects, modeling was performed to estimate the mechanical properties of the multi-layer interconnects (both the 10cm x 10cm and 10cm x n designs).

Nov. 27, 2002

Initially, physical characterization of 10cm x 10 cm interconnects was performed, with particular emphasis on thickness profile and flatness. These data were used to generate solids models for selected interconnects and used in finite element models to estimate their stiffness and potential stresses that might be generated when these interconnects are incorporated into stacks. Measurements of actual stiffness for these interconnects were made using a mechanical load frame with appropriate fixtures. Correlation of the calculated stiffness and the measured stiffness for the interconnects showed good agreement (within 10%).

As a secondary check of the FEA model, the expected natural frequencies of an interconnect were predicted and they correlated very closely with the first four modal frequencies that were obtained from a "ping" test. In the ping test, an interconnect is struck with a "hammer" and the sound is recorded. An example of a typical ping test frequency spectrum is shown in *Figure 12*. The first two calculated vibration modes for the interconnect are shown in *Figure 13*.

Figure 12. The measured frequency spectrum for a 10cm x 10cm multi-layer interconnect.

Figure 13. The first two calculated vibration modes for a multi-layer interconnect. Good agreement between the calculated and measured model frequencies was obtained.

One key outcome from this work was that the "ping test" was shown to be a good indicator of interconnect quality. A good interconnect gives a clear ring, along with well-defined modal frequencies. Conversely, an interconnect having cracks or delaminations tends to give a dull thud (substantial attenuation of the sound). Examples of typical ping test spectra for good and bad interconnects are given in *Figure 14*. The agreement between the models and the ping test results provides additional confidence in the models and the current set of mechanical properties being used in the calculations.

Figure 14. Ping test data for three interconnects showing the sound attenuation for good, fair and bad interconnects.

To support the structural modeling effort, the MTI Team had to perform a variety of tests on cell and interconnect materials to acquire the necessary mechanical property data. First, MTI obtained structural property data for the electrolyte and interconnect body materials using a 4-point test fixture. Virginia Tech also performed mechanical characterization for the electrolyte and interconnect body materials, using a ball-on-ring technique. Failed specimens were sent to the Idaho National Engineering and Environmental Laboratory for fractographic analysis in order to identify the strength limiting flaws that caused failure of the specimens. Penn State obtained mechanical property data at elevated temperatures for a range of cell and interconnect materials using dynamic modulus testing. Finally, as previously mentioned, MTI performed mechanical testing on complete interconnects (both the 10cm x 10cm and 10cm x n designs). The test set-up is shown in *Figure 15*. The measured stiffness for the interconnects compared well with predicted stiffness when the above-mentioned material property data was used in the finite element models.

Figure 15. Mechanical testing arrangement for the multi-layer interconnects. This test was used to determine interconnect stiffness and to assess the strength of interconnects.

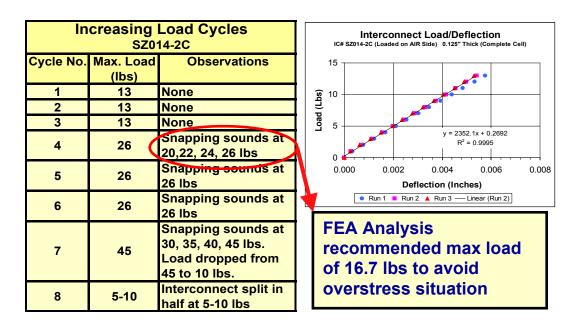

Interconnects were also loaded to failure, using a cycling load method. During loading, crack initiation/propagation was assessed by using acoustic sensors "listening" for snapping sounds. An example of the data obtained in testing one interconnect is shown in *Figure 16*. In general, there was good agreement between the observed occurrences of interconnect cracking and the maximum recommended load to avoid overstress conditions based on finite element analyses.

Figure 16. Load-to-failure data for a multi-layer interconnect. Cracking of the interconnect was observed when the applied load exceeded the maximum recommended load from finite element analyses.

# **Short Stack Assembly and Testing**