# **CONTRACTOR REPORT**

SAND99-0235 Unlimited Release

# Fundamental Understanding and Development of Low-Cost, High-Efficiency Silicon Solar Cells

Annual Progress Report: Sept. 1997 – Aug. 1998

RECEIVED FEB 1 8 1999 OSTI

A. Rohatgi, S. Narasimha, J. Moscher, A. Ebong, S. Kamra, T. Krygowski, P. Doshi, A. Ristow, and V. Yelundur University Center of Excellence for Photovoltaics Research and Education School of Electrical and Computer Engineering Georgia Institute of Technology Atlanta, GA 30332-0250

Prepared by Sandia National Laboratories Albuquerque, New Mexico 87185 and Livermore, California 94550

Sandia is a multiprogram laboratory operated bySandia Corporation, a Lockheed Martin Company, for the United States Department of Energy under Contract DE-AC04-94AL85000.

Approved for public release; distribution is unlimited.

Printed February 1999

Issued by Sandia National Laboratories, operated for the United States Department of Energy by Sandia Corporation.

**NOTICE:** This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government, nor any agency thereof, nor any of their employees, nor any of their contractors, subcontractors, or their employees, make any warranty, express or implied, or assume any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represent that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government, any agency thereof, or any of their contractors or subcontractors. The views and opinions expressed herein do not necessarily state or reflect those of the United States Government, any agency thereof, or any of their contractors.

Printed in the United States of America. This report has been reproduced directly from the best available copy.

Available to DOE and DOE contractors from Office of Scientific and Technical Information P.O. Box 62 Oak Ridge, TN 37831

Prices available from (615) 576-8401, FTS 626-8401

Available to the public from National Technical Information Service U.S. Department of Commerce 5285 Port Royal Rd Springfield, VA 22161

NTIS price codes Printed copy: A07 Microfiche copy: A01

SAND99-0235 Unlimited Release Printed February 1999

## Fundamental Understanding and Development of Low-Cost, High-Efficiency Silicon Solar Cells

#### Annual Progress Report: Sept. 1997-Aug. 1998

A. Rohatgi, S. Narasimha, J. Moscher, A. Ebong, S. Kamra, T. Krygowski, P. Doshi, A. Ristow, and V. Yelundur

University Center of Excellence for Photovoltaics Research and Education School of Electrical and Computer Engineering Georgia Institute of Technology Atlanta, Georgia 30332-0250

Sandia Contract: AO-6162

#### ABSTRACT

The overall objective of this program is 1) to develop rapid and low-cost processes for manufacturing that can improve yield, throughput, and performance of silicon photovoltaic devices, 2) to design and fabricate high-efficiency solar cells on promising low-cost materials, and 3) to improve the fundamental understanding of advanced photovoltaic devices. Several rapid and potentially low-cost technologies are described in this report that were developed and applied toward the fabrication of high-efficiency silicon solar cells.

•

# TABLE OF CONTENTS

| SUMMARY   | i                                                                                                                        |

|-----------|--------------------------------------------------------------------------------------------------------------------------|

| CHAPTER 1 | FUNDAMENTAL UNDERSTANDING AND DEVELOPMENT OF<br>SCREEN-PRINTING METALLIZATION FOR MONOCRYSTALLINE                        |

|           | SI SOLAR CELLS 1-1                                                                                                       |

| 1.1       | Fill Factor Loss Mechanisms 1-1                                                                                          |

| 1.2       | Effect of SP Firing Treatment on Conductor Paste Resistivity 1-2                                                         |

| 1.3       | Effect of Junction Depth on the FF of Monocrystalline Si Solar Cells 1-3                                                 |

| 1.4       | Reducing Leakage and Shunting with Deeper n <sup>+</sup> Emitters 1-4                                                    |

| 1.5       | Effect of Firing Conditions and Post-Firing Forming Gas Anneal on the                                                    |

|           | Contact Resistance and Fill Factor 1-5                                                                                   |

| 1.6       | Effect of Peak Firing Temperature on Solar Cell Shunting Behavior and                                                    |

|           | Fill Factor 1-7                                                                                                          |

| 1.7       | SP mc-Si Solar Cells 1-8                                                                                                 |

| 1.8       | Conclusions 1-8                                                                                                          |

| 1.9       | References 1-9                                                                                                           |

| CHAPTER 2 | COMPARISON OF FRONT AND BACK SURFACE PASSIVATION<br>SCHEMES FOR SILICON SOLAR CELLS                                      |

| 2.1       | Introduction                                                                                                             |

| 2.2       | Experimental                                                                                                             |

| 2.3       | Results and Discussion                                                                                                   |

| 2.4       | Impact of Surface Passivation on Photovoltaic Device Performance                                                         |

| 2.5       | Conclusions                                                                                                              |

| 2.6       | References 2-9                                                                                                           |

| CHAPTER 3 | EFFECTIVE PASSIVATION OF THE LOW RESISTIVITY SILICON<br>SURFACE BY A RAPID THERMAL OXIDE/PLASMA SILICON NITRIDE<br>STACK |

| 3.1       | Introduction                                                                                                             |

| 3.2       | Experimental                                                                                                             |

| 3.3       |                                                                                                                          |

|           | Results and Discussion                                                                                                   |

| 3.4       | Results and Discussion                                                                                                   |

####

| 4-4       |

|-----------|

| on Al-BSF |

| 4-5       |

| ation 4-6 |

| olar Cell |

| 4-7       |

| 4-7       |

|           |

| 4-9       |

| 4-11      |

| (         |

####

| 5.1   | High efficiency 100 µm thin string ribbon solar cell fabricated by |     |

|-------|--------------------------------------------------------------------|-----|

|       | conventional furnace processing                                    | 5-2 |

| 5.1.2 | Experimental Approach                                              |     |

| 5.1.3 | Results and Discussion                                             |     |

| 5.1.4 | Future Directions                                                  | 5-7 |

|       |                                                                    |     |

### 5.2 High Efficiency 100μm Thin String Ribbon Solar Cells Fabricated by Rapid Thermal Beltline Processing and Screen-Printing

| 5.3   | Gettering and Passivation of Bulk Defects in String Ribbon Silicon with |     |

|-------|-------------------------------------------------------------------------|-----|

| 5.2.4 | Discussion 5                                                            | -35 |

| 5.2.3 | Results 5                                                               |     |

| 5.2.2 | Solar Cell Processing of Screen Printed Gridded Back Contact Cells 5    |     |

| 5.2.1 | Introduction 5                                                          |     |

## Beltline Rapid Thermal Processing, Screen-Printing, and PECVD SiN

| 5.3.1 | Introduction | 37 |

|-------|--------------|----|

| 5.3.2 | Experimental | 38 |

| 5.3.3 | Results 5-   | 39 |

| 5.3.4 | Conclusions  | 40 |

| 5.4        | High Efficiency 250 µm Thin String Ribbon Solar Cells by Rapid Therr<br>Beltline Processing and Screen-Printing |             |

|------------|-----------------------------------------------------------------------------------------------------------------|-------------|

| 5.4.1      | Introduction                                                                                                    |             |

| 5.4.2      | Experimental Procedure                                                                                          | 5-42        |

| 5.4.3      | Results and Discussion                                                                                          |             |

| 5.4.4      | Conclusions                                                                                                     | 5-49        |

| 5.5        | Final Conclusions                                                                                               | 5-51        |

| CHAPTER 6  | A NOVEL PROCESSING TECHNOLOGY FOR HIGH                                                                          | -EFFICIENCY |

|            | SILICON SOLAR CELLS                                                                                             | 6-1         |

| 6.1        | SILICON SOLAR CELLS                                                                                             |             |

| 6.1<br>6.2 |                                                                                                                 | 6-1         |

|            | Introduction                                                                                                    | 6-1<br>6-4  |

| 6.2        | Introduction<br>Experimental                                                                                    |             |

| CHAPTER 7 | INTEGRATION OF RAPID PROCESS TECHNOLOGIES FOR HIGH |   |

|-----------|----------------------------------------------------|---|

|           | EFFICIENCY SILICON SOLAR CELLS                     | 1 |

# **FIGURES**

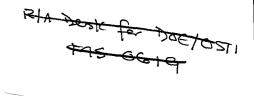

| Figure 1.1  | Fill factor loss mechanisms associated with screen printing 1-10                                                                                                      |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

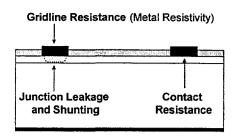

| Figure 1.2  | Solar cell equivalent circuit. Fill factor is influenced by $J_{02}$ , $R_{shunt}$ and $R_{series}$                                                                   |

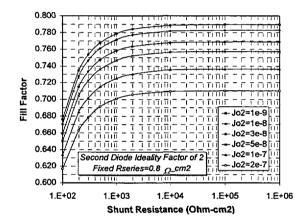

| Figure 1.3  | Effect of $R_{shunt}$ and $J_{02}$ on fill factor response ( $R_{series}$ fixed at 0.8 $\Omega$ -cm <sup>2</sup> ) 1-10                                               |

| Figure 1.4  | Effect of $R_{series}$ and $R_{shunt}$ on fill factor response ( $J_{02}$ fixed at 10 <sup>-8</sup> A/cm <sup>2</sup> .)                                              |

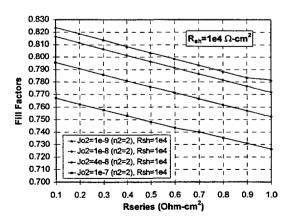

| Figure 1.5  | Effect of $R_{series}$ and $J_{02}$ on fill factor response ( $R_{shunt}$ fixed at 10 <sup>4</sup> $\Omega$ -cm <sup>2</sup> .) 1-10                                  |

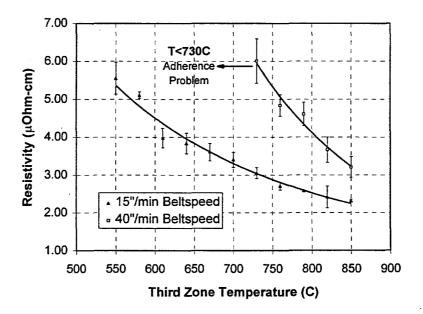

| Figure 1.6  | Effect of beltline firing temperature and beltspeed on metal conductivity. The corresponding hotzone dwell times are 30 sec (15"/min) and 11 sec (40"/min) 1-11       |

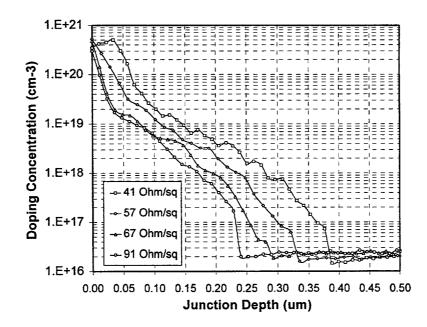

| Figure 1.7  | Solid source diffusion profiles measured by the spreading resistance technique. The diffusion time was fixed at 30 min, and the highest temperature used was 50°C1-12 |

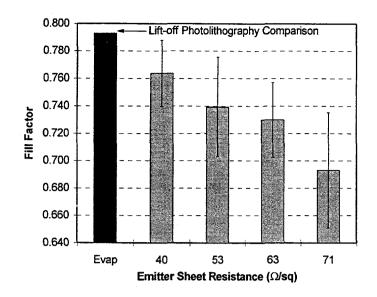

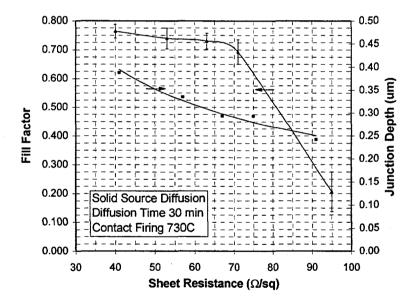

| Figure 1.8  | Fill factor versus emiter sheet resistance1-13                                                                                                                        |

| Figure 1.9  | Relationship between screen-printed fill factor and junction depth1-13                                                                                                |

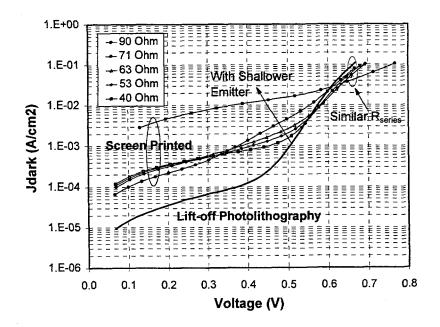

| Figure 1.10 | Shunt and junction leakage effects on solar cell dark IV response1-14                                                                                                 |

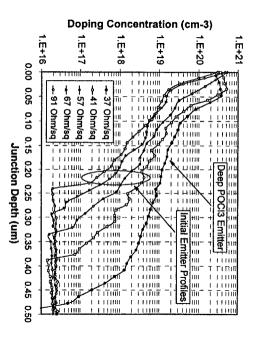

| Figure 1.11 | Deeper POCl <sub>3</sub> emitter as compared to original solid source diffusion1-15                                                                                   |

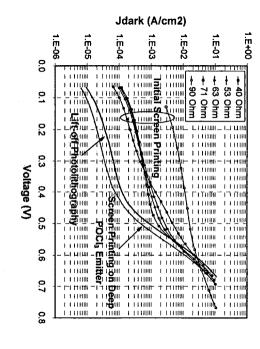

| Figure 1.12 | Dark IV response when printing is done on deeper emitter1-15                                                                                                          |

| Figure 1.13 | Fill factor response as a function of hotzone temperature and dwell time 1-16                                                                                         |

| Figure 1.14 | The effect of a 400°C FGA on the series resistance of fired SP contacts 1-17                                                                                          |

| Figure 1.15 | The effect of the FGA on the $\rho_c$ of SP contacts to $n^+$ emitter regions                                                                                         |

| Figure 1.16 | Effect of post-firing contact anneal in non-reduing $(N_2)$ and reducing (FG) ambients.<br>The anneal temperature was 400°C 1-18                                      |

| Figure 1.17 | Effect of hotzone firing temperature on the ensuing dark IV response of solar cells 1-19                                                                              |

| Figure 1.18 | Effect of hotzone firing temperature on R <sub>sh</sub> value                                                                                                         |

| Figure 1.19 | The effect of junction depth on fill factors for SP mc-Si solar cells                                                                                                 |

| Figure 2.1 | Emitter saturation current densities for different passivation schemes on 40 $\Omega$ /sq. RTP emitters                                                                                                                                                         |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.2 | Emitter saturation current densities for 90 $\Omega$ /sq. RTP emitters                                                                                                                                                                                          |

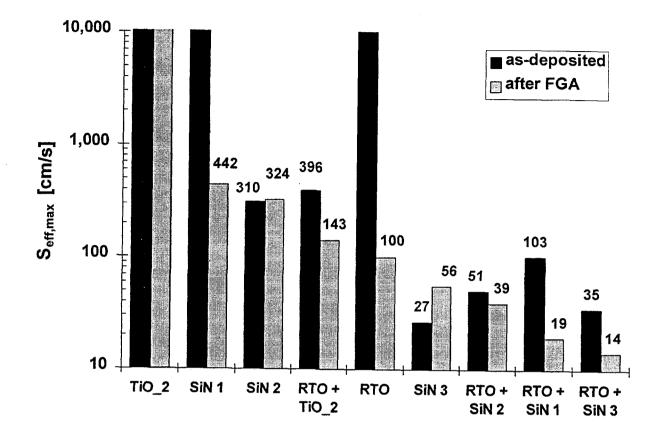

| Figure 2.3 | Surface recombination velocities for different passivation schemes on planar surfaces. S values above 10 <sup>4</sup> cm/s cannot be resolved by the measurement technique used and are not shown                                                               |

| Figure 2.4 | Surface recombination velocities for textured surfaces                                                                                                                                                                                                          |

| Figure 2.5 | Surface recombination velocities for planar samples after contact firing                                                                                                                                                                                        |

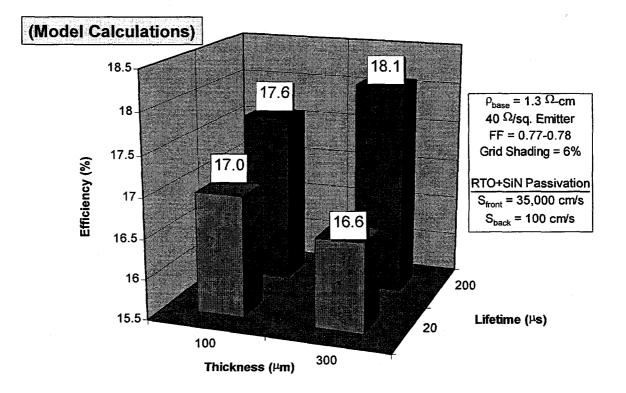

| Figure 2.6 | Impact of front and/or back surface passivation on photovoltaic device performance<br>All calculations were performed with a 40 $\Omega$ /sq. Emitter, 6% grid shading factor, and<br>fill factor of 0.77-0.78 to be consistent with screen-printed solar cells |

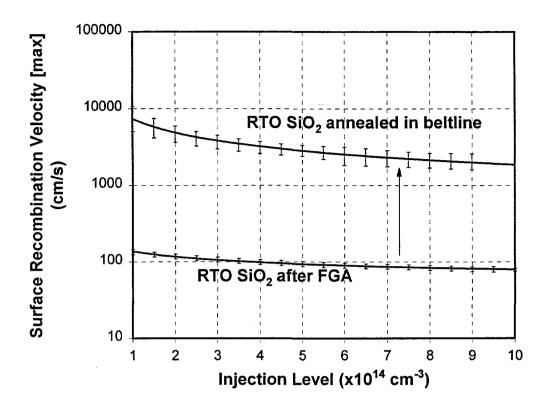

| Figure 3.1 | Passivation of the 1.25 $\Omega$ -cm p-type (100) Si surface by RTO SiO <sub>2</sub> alone. The RTO was done at 900 °C in 5 minutes ( $\approx$ 79Å), and the ensuing forming gas anneal (FGA) was done at 400 °C in 15 minutes                                 |

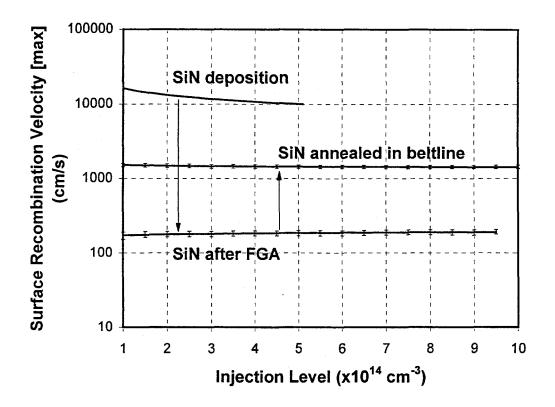

| Figure 3.2 | Passivation of the 1.25 $\Omega$ -cm p-type (100) Si surface by SiN alone. The FGA was done at 400 °C in 30 minutes                                                                                                                                             |

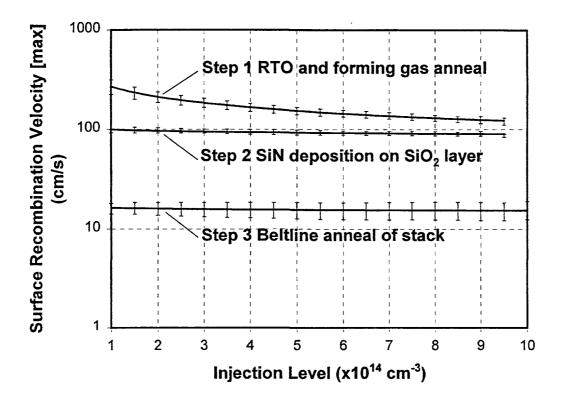

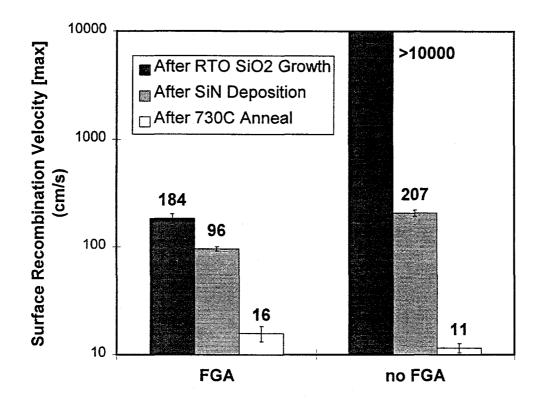

| Figure 3.3 | Progression of S values for passivation by the RTO $SiO_2/PECVD$ SiN stack.<br>SiO <sub>2</sub> films ( $\approx 57$ Å) were grown at 900°C in 2 minutes, and the ensuing FGA was done at 400°C in 15 minutes                                                   |

| Figure 3.4 | Effect of intermediate FGA (immediately after RTO growth) on the stack passivation. RTO films were grown at 900°C in 2 minutes, and the FGA was done at 400°C in 15 minutes                                                                                     |

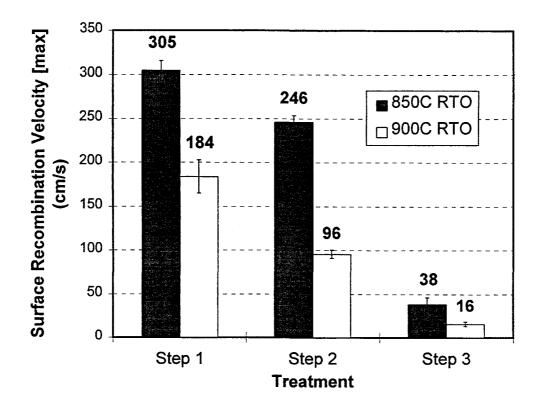

| Figure 3.5 | Effect of RTO temperature on the stack passivation. <u>Step 1</u> : 2 minute RTO growth (≈43Å at 850°C, ≈57Å at 900°C) followed by FGA at 400°C in 15 minutes, <u>Step 2</u> : SiN deposition on RTO layer, <u>Step 3</u> : 730°C anneal of stack               |

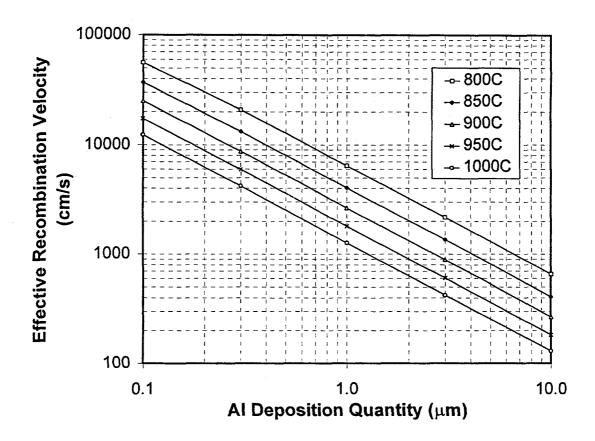

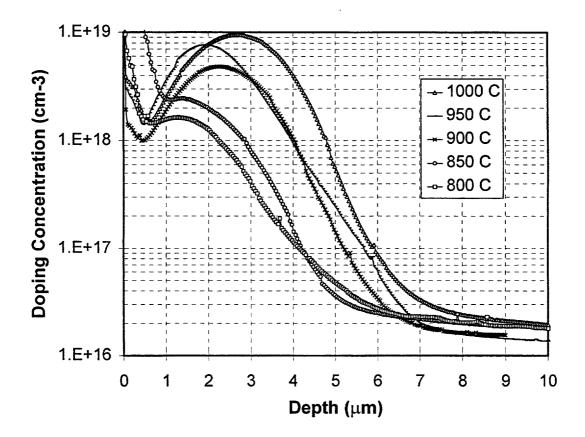

| Figure 4.1 | Simulations relating the $S_{eff}$ achieved by the Al-BSF on 2.3 $\Omega$ -cm Si to the Al deposition quantity and alloying temperature                                                                                                                         |

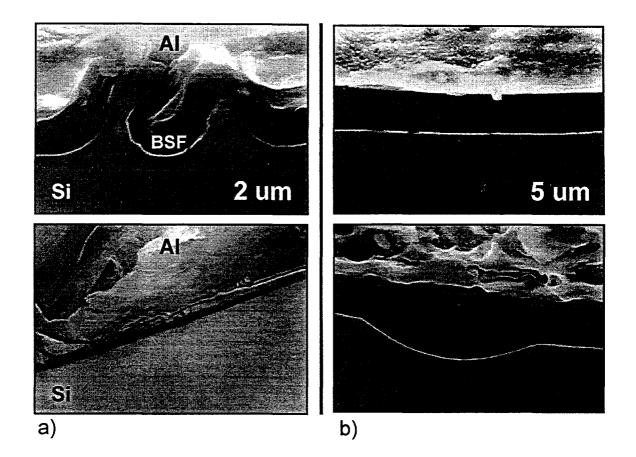

| Figure 4.2 | BSF regions formed un (a) slow ramp conditions (top shows severe junction non-<br>uniformity, bottom shows non-formation) and (b) fast ramp conditions (both top<br>and bottom show clean formation and improved uniformity)                                    |

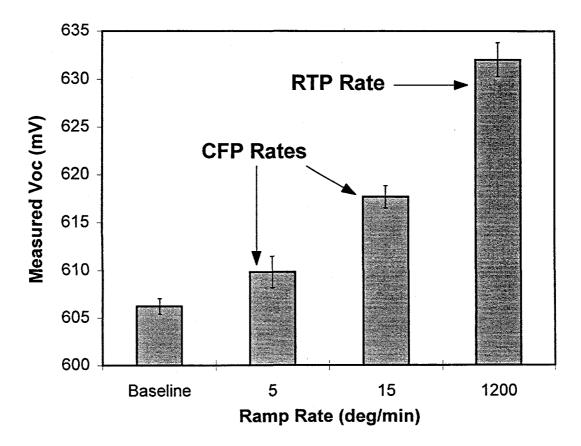

| Figure 4.3  | The effect of ramp rate used during Al-BSF alloying on solar cell Voc (2.3 Ω-cm FZ Si substrate). The peak alloying temperature was 850°C. CFP indicates conventional furnace processing                                                                                                                                                                     |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

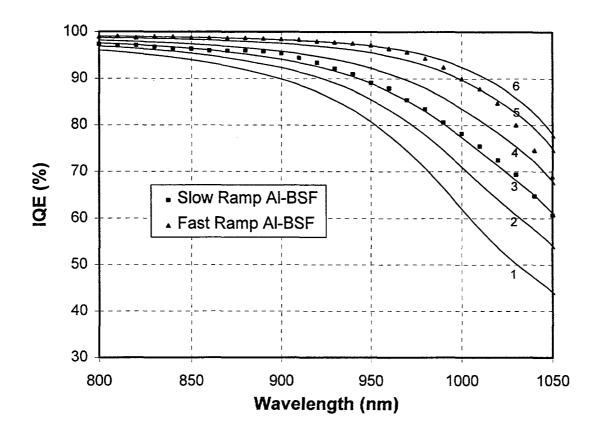

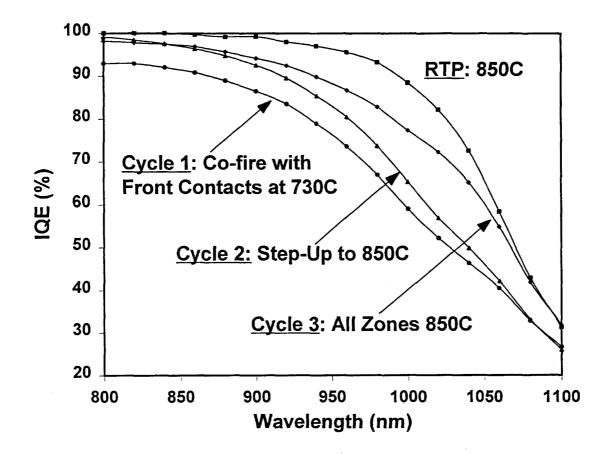

| Figure 4.4  | Effect of ramp rate used during alloying on long wavelength IQE response (fast ramp: 1200°C/min, slow ramp: 5°C/min). The solid lines represent simulated IQE curves For an analogous cell with different S <sub>b</sub> . Lines 1-6 represent S <sub>b</sub> values of 10000 cm/s, 2000 cm/s, 1000 cm/s, 500 cm/s, 200 cm/s, and 100 cm/s, respectively4-20 |

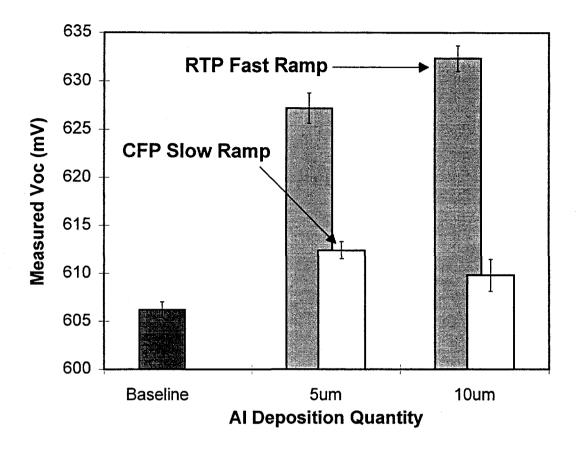

| Figure 4.5  | The effect of Al deposition thickness and ramp-rate on solar cell $V_{oc}$ (2.3 $\Omega$ -cm FZ Si). The CFP and RTP ramp rates were 5°/min and 1200°/min, respectively, and the peak alloy temperature was 850°C. Each data bar represents the average of none 4cm <sup>2</sup> cells taken from a wafer                                                    |

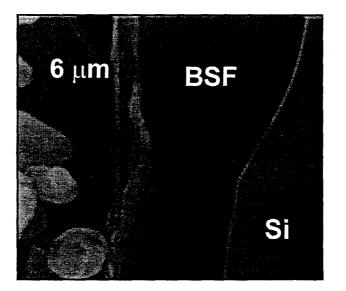

| Figure 4.7  | SEM image of a p <sup>+</sup> region formed by screen-printing Al paste and alloying at 850°C in an RTP unit4-23                                                                                                                                                                                                                                             |

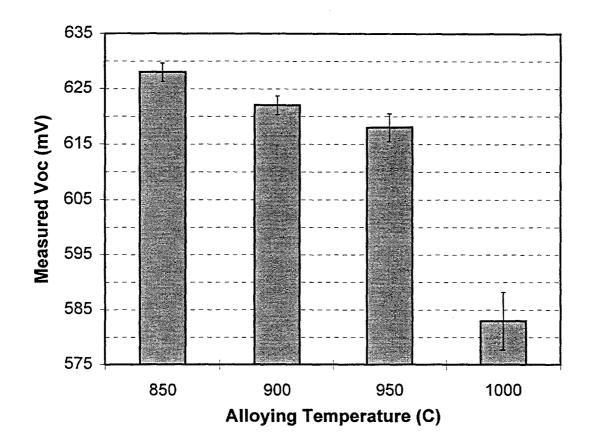

| Figure 4.8  | Effect of alloying temperature on contamination in SP-Al BSF solar cells. The $V_{oc}$ values were measured without AR coatings (2.3 $\Omega$ -cm FZ Si). Each data bar represents the average of nine 4 cm <sup>2</sup> cells taken from a wafer                                                                                                            |

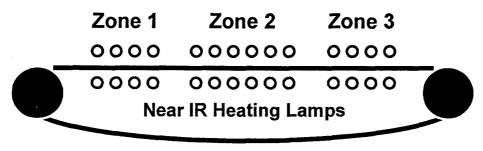

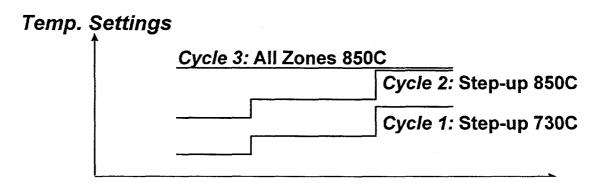

| Figure 4.9  | Schematic of the beltline furnace used in this study, and the temperature settings used to investigate Al-BSF formation                                                                                                                                                                                                                                      |

| Figure 4.10 | Long wavelength IQE difference for solar cells with Al-BSFs alloyed in a beltline furnace and an RTP unit (2.3 $\Omega$ -cm FZ Si)4-26                                                                                                                                                                                                                       |

| Figure 5.1  | Histogram of improvement in cell efficiency5-9                                                                                                                                                                                                                                                                                                               |

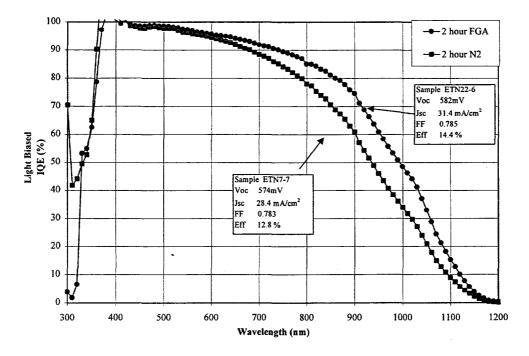

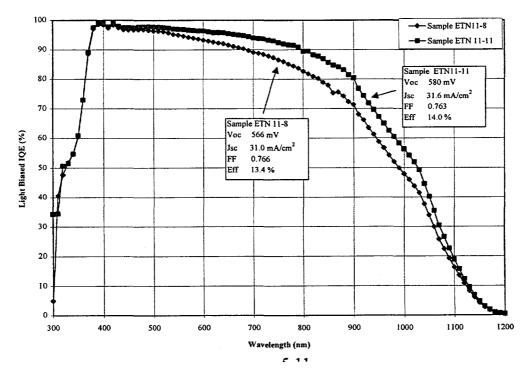

| Figure 5.2  | Effect of 2-hour forming gas anneal on string ribbon solar cells                                                                                                                                                                                                                                                                                             |

| Figure 5.3a | Effect of 2-hour FGA on long wavelength IQE5-11                                                                                                                                                                                                                                                                                                              |

| Figure 5.3b | Evidence of variation in bulk lifetime of samples5-11                                                                                                                                                                                                                                                                                                        |

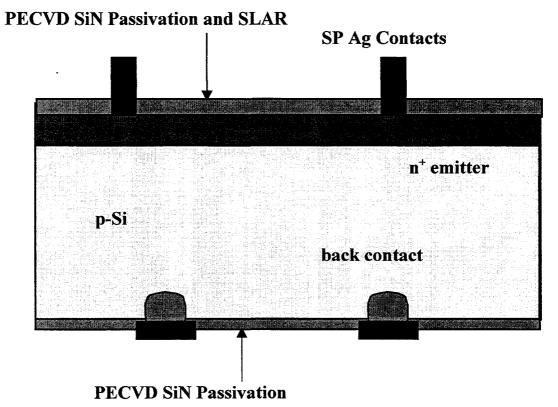

| Figure 5.4  | Schematic of gridded back contact string ribbon cell5-34                                                                                                                                                                                                                                                                                                     |

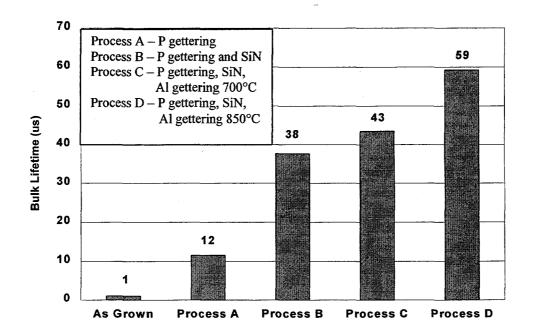

| Figure 5.6  | Bulk lifetime of string ribbon silicon after gettering treatments                                                                                                                                                                                                                                                                                            |

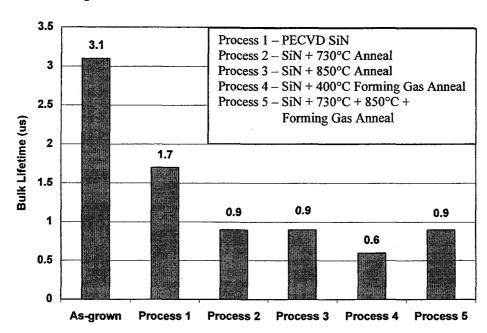

| Figure 5.7  | Effect of Hydrogenation alone on bulk lifetime of string ribbon 5-39                                                                                                                                                                                                                                                                                         |

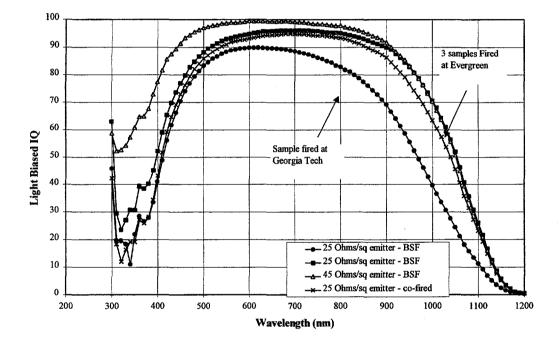

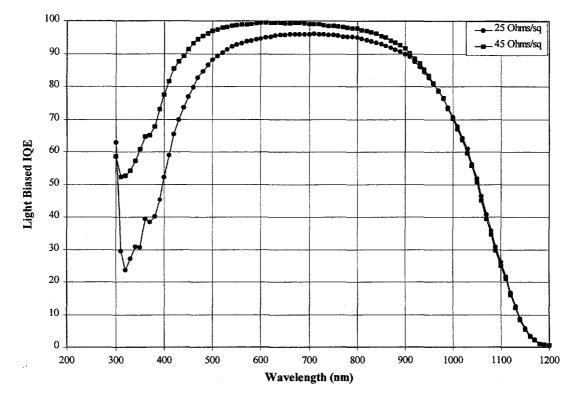

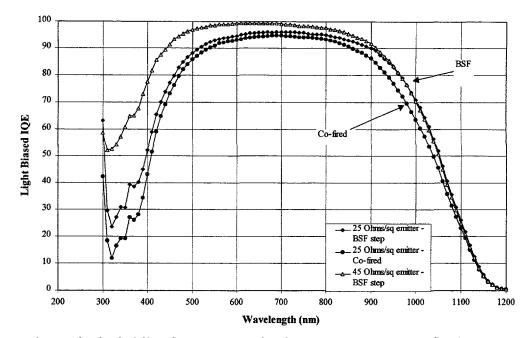

| Figure 5.8  | Light Biased IQE of Cells fired at Georgia Tech and Evergreen Solar5-45                                                                                                                                                                                                                                                                                      |

| Figure 5.9  | Effect of Emitter Doping on short wavelength response                                                                                                                                                                                                                                                                                                        |

· ·

| Figure 5.10 | Effect of BSF alloying on long wavelength IQE 5-48                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

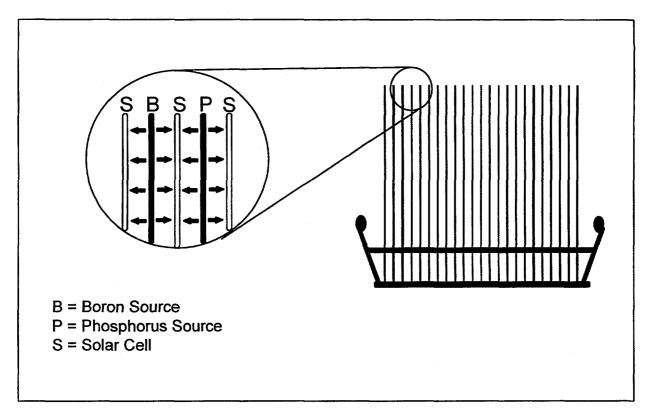

| Figure 6.1  | Furnace stacking arrangement, with the solar cell wafers (S) interleaved with the Boron (B) and Phosphorus (P) solid sources developed in this work                                                                                                                                                                                                                                                                                                 |

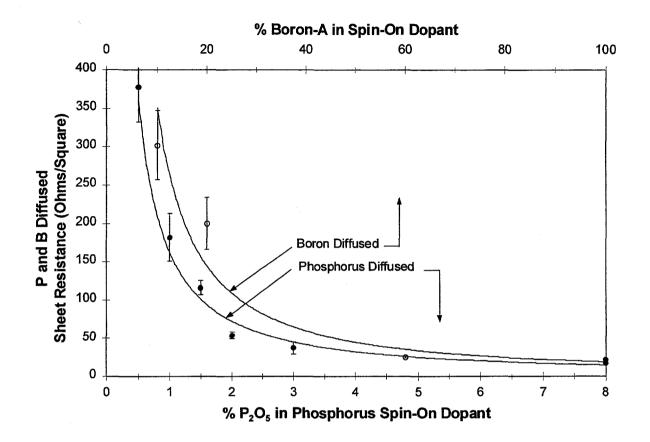

| Figure 6.2  | Dependence of phosphorus and boron-diffused sheet resistance on source fabrication conditions for a 1000 °C/60 min process. The phosphorus sources were tailored by adjusting the concentration of $P_2O_5$ in the SOD film, while the boron sources were tailored by diluting the 100% boron-A SOD film with toluene                                                                                                                               |

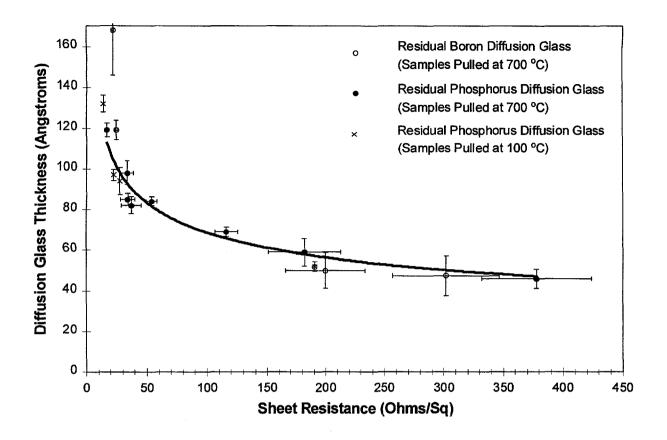

| Figure 6.3  | Residual diffusion glass thickness vs. Sheet resistance for a $1000^{\circ}$ C/60 minprocess in N <sub>2</sub> for phosphorus and boron diffusions, with no <i>in-situ</i> oxidation                                                                                                                                                                                                                                                                |

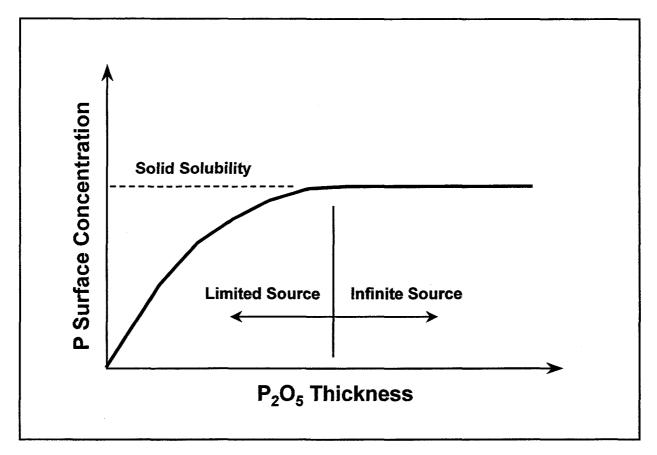

| Figure 6.4  | Proposed reaction pathway for phosphorus diffusions using solid sources<br>fabricated from a spin-on dopant film                                                                                                                                                                                                                                                                                                                                    |

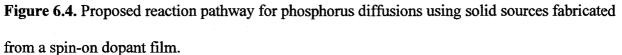

| Figure 6.5  | Dependence of sheet resistance on $\[mmodel]{P_2O_5}$ in phosphorus SOD film for a 925°C/60 min process, for planer and pyramid-textured surfaces                                                                                                                                                                                                                                                                                                   |

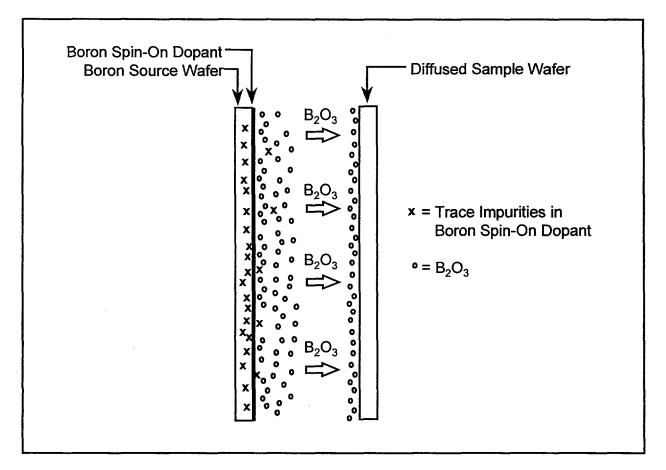

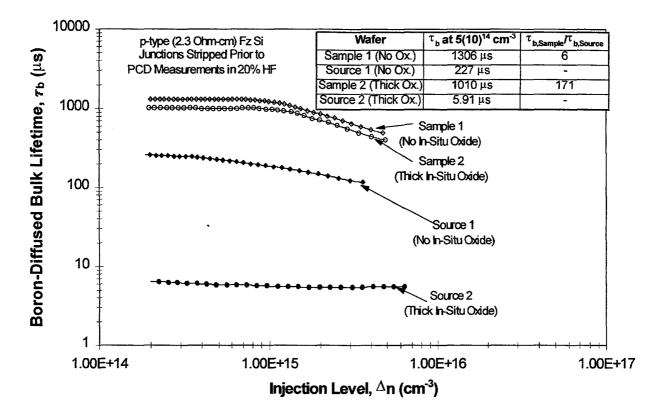

| Figure 6.6  | Demonstration of high minority carrier lifetimes due to impurity filtering from boron<br>SOD-coated solid sources. Source 1 wafer on which the boron SOD was applied was<br>facing sample 1 in a 1000°C/60 min process with no <i>in-situ</i> oxidation, while the Source<br>2 wafer was facing sample 2 in a 1000°C/60 min process with an additional 66 min<br><i>in-situ</i> oxidation at 1000°C                                                 |

| Figure 6.7  | Schematic of impurity filtering action commensurate with boron SOD-coated source wafers: The impurities (X) in the SOD film are diffused into the source wafers while the volatile dopant species, $B_2O_3$ (O) is transported to the sample wafer, resulting in a high-purity boron diffusion                                                                                                                                                      |

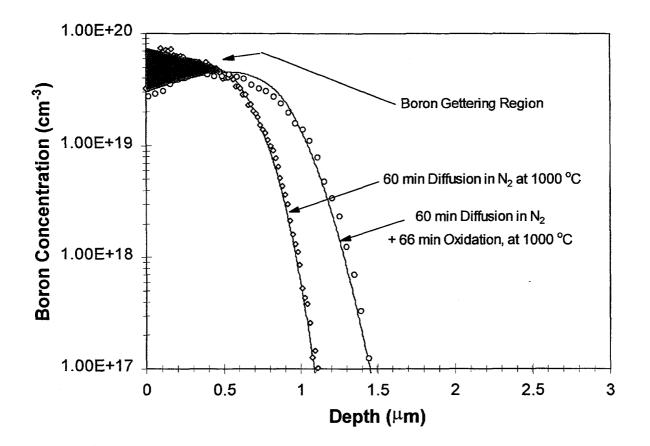

| Figure 6.8  | Spreading resistance measurments for boron diffusions formed in a 1000°C/60 min process, with and without <i>in-situ</i> oxidations. The reduction in boron surface concentration for the oxidized case is believed to reduce the gettering effectiveness of the diffused region relative to the non-oxidized case                                                                                                                                  |

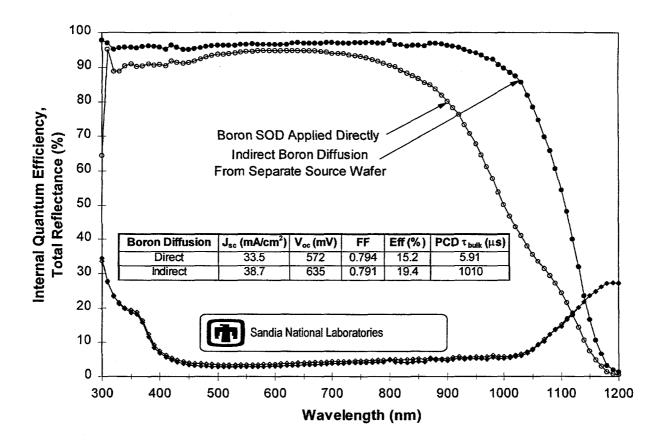

| Figure 6.9  | Internal Quantum Efficiency and reflectance vs. Wavelength measurements for a solar cell wafer on which the boron SOD was directly applied (source wafer) and the adjacent solar cell (sample wafer) that was facing this source in the diffusion furnace. The 4.2% increase in absolute efficiency for the sample wafer is attributed to impurity filtering, resulting from the se parate source/sample arrangement in the diffusion furnace. 6-28 |

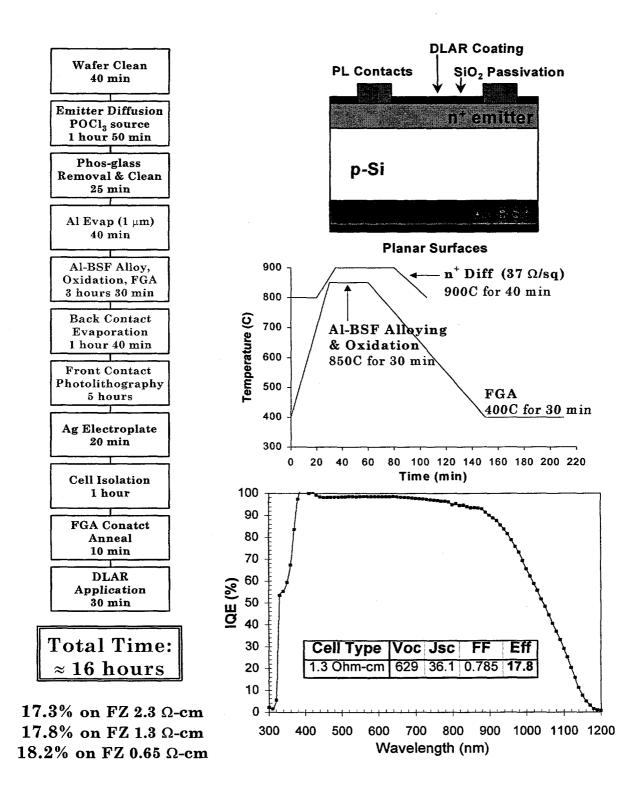

| Figure 7.1  | Baseline cell process sequence by conventional furnace processing and photolithography                                                                                                                                                                                                                                                                                                                                                              |

l)

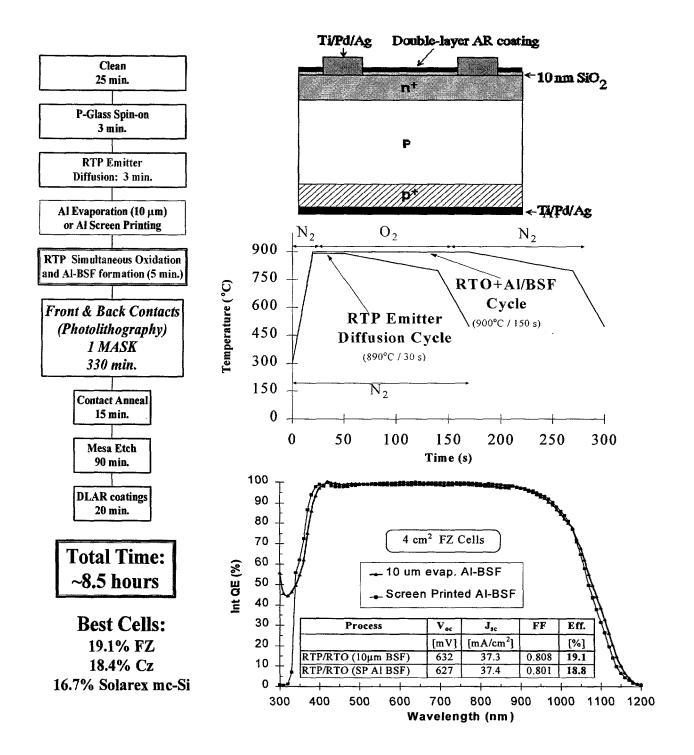

| Figure 7.2 | Rapid Thermal Processing (RTP) of cells with photolithography contacts                                         | 7-4          |

|------------|----------------------------------------------------------------------------------------------------------------|--------------|

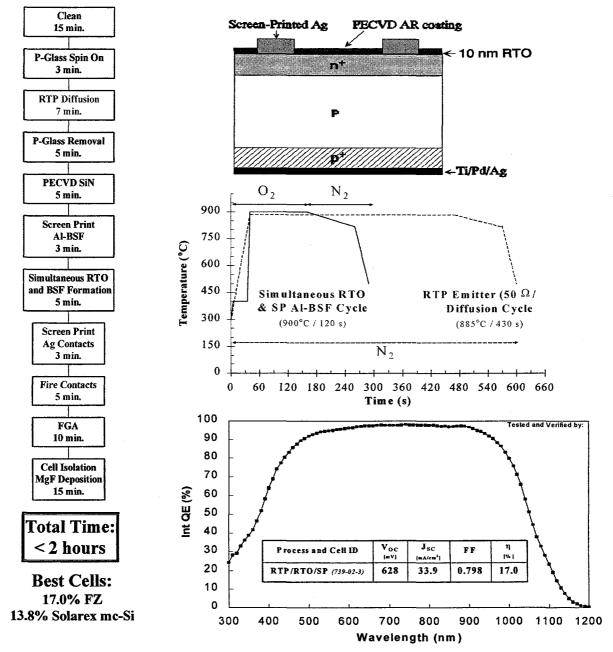

| Figure 7.3 | Rapid Thermal Processing of Cells with screen-printed contacts                                                 | 7-5          |

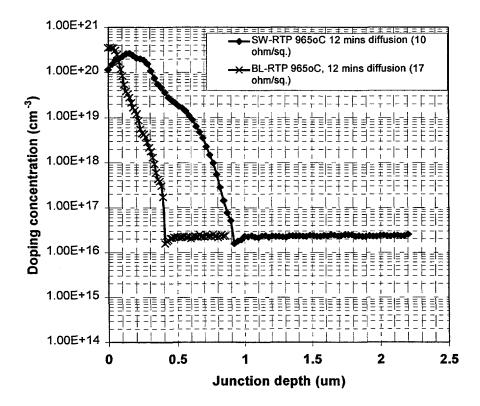

| Figure 7.4 | Comparison of the effective diffusivity of phosphorous in single wafer and BLP emitter at 965°C for 12 minutes | 7-6          |

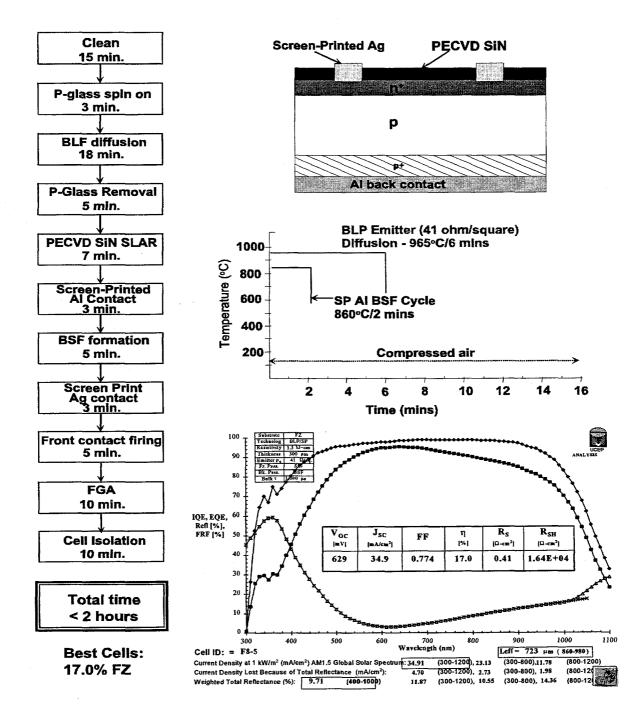

| Figure 7.5 | Beltline processing of cells with screen-printed contacts                                                      | 7-7          |

| Figure 7.6 | Dielectric passivation with gridded back contacts vs. Full screen-printed Al BSF                               | 7-8          |

| Figure 7.7 | Modeling of screen-printed solar cells as a function of thickness and lifetime with $S_{back}$ of 100 cm/s     | 7 <b>-</b> 9 |

\$

# TABLES

| Table 1.1 | Junction depth requirement for screen printed contact formation to monocrystalline<br>Si solar cells1-5                                                                                                                                                                      |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 1.2 | Reproducibility of the SP process developed in this study. Each entry represents an average value over multiple (≈ 9) cells. All devices are planar, 4 cm <sup>2</sup> in area, with single Layer AR coatings                                                                |

| Table 4.1 | Effect of alloying temperature on Al-BSF solar cell $V_{oc}$ . All samples (except the baseline case) were formed by 10 $\mu$ m Al evaporation followed by RTP fast ramp alloying. Each data value represents the average of nine 4 cm <sup>2</sup> cells taken from a wafer |

| Table 4.2 | Process sequence comparison: high-efficiency laboratory process and high-throughput industry-type process. <i>SP</i> represents screen-printing4-14                                                                                                                          |

| Table 4.3 | Al-BSF solar cells formed using a high-efficiency, laboratory fabrication sequence. All results have been officially verified at Sandia National Labs. (Cell area: 4 cm <sup>2</sup> )4-15                                                                                   |

| Table 4.4 | Average performance of Al-BSF solar cells formed using a high throughput, industry-<br>type fabrication sequence. (Cell area: 4 cm <sup>2</sup> )4-16                                                                                                                        |

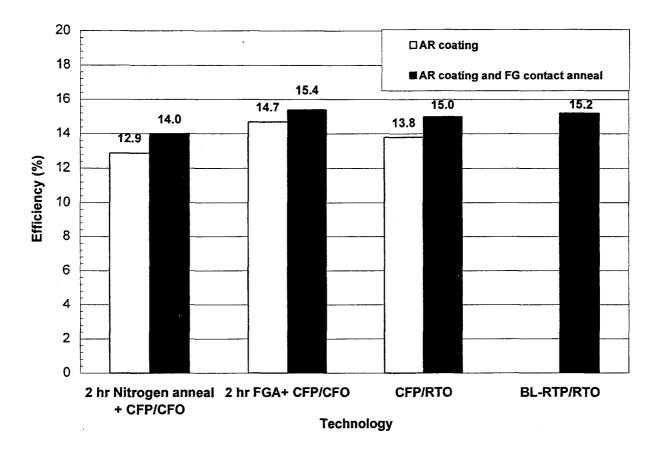

| Table 5.1 | Best cell performance after ARC & 15 minutes FGA contact anneal on evergreen material with various technologies                                                                                                                                                              |

| Table 5.2 | Effect of FGA at various stages of processing on the performance of evergreen string ribbon solar cells fabricated by different technologies                                                                                                                                 |

| Table 5.3 | The effect of ZnS/MgF2 ARC & FGA contact anneal for photolithography solar cells on evergreen ribbon material                                                                                                                                                                |

| Table 5.4 | Above 14% efficient PL solar cells fabricated on ribbon thin evergreen material5-28                                                                                                                                                                                          |

| Table 5.6 | Highest evergreen cell efficiency achieved by photolithography5-35                                                                                                                                                                                                           |

| Table 5.7 | Experiment matrix 5-42                                                                                                                                                                                                                                                       |

| Table 5.8 | Pre-FGA average light IV data                                                                                                                                                                                                                                                |

| Table 5.9 | Post FGA average light IV data5-44                                                                                                                                                                                                                                           |

.

•

| Table 5.10 | Dark IV five parameter fit results                                                                                                                                                                             | . 5-46 |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Table 5.11 | Light IV data of cells measured by Sandia National Labs                                                                                                                                                        | 5-49   |

| Table 6.1  | Comparison of conventional $SiP_2O_7$ -based solid sources, POCl <sub>3</sub> and the limited solid sources developed in this work, to form light phosphorus diffusions on planer and textured silicon wafers. | 6-17   |

| Table 6.2  | Saturation current density (Jo) measurements for in-situ oxide passivated and Unpassivated 80-90 $\Omega/\Box$ boron and phosphorus diffusions                                                                 | 6-20   |

# **SUMMARY**

Overall objective of this program is threefold. First, to develop rapid and lowcost manufacturable processes that can improve yield, throughput and performance of silicon photovoltaic devices; second, to design and fabricate high efficiency solar cells on promising low-cost photovoltaic materials and third, to improve the fundamental understanding of advanced photovoltaics devices. In this report several rapid and potentially low-cost technologies are developed and applied toward the fabrication of high efficiency silicon solar cells.

One of the most difficult aspects of large scale solar cell production is forming low-cost, high-quality front contacts. Screen-printing (SP) offers a simple, cost-effective contact method that is consistent with the requirements for high-volume manufacturing. The current problem with SP, however, is that the throughput gains are attained at the expense of device performance. Literature shows considerable scatter in the fill factor values of SP solar cells. In addition there are no clear guidelines for achieving high fill factors. Therefore, a methodology for optimizing SP metallization is developed, recognizing the fact that fill factor can be degraded by gridline resistance, contact resistance, and contact formation induced junction leakage and shunting. Systematic optimization of the firing cycle and junction depth, coupled with a post contact forming gas anneal, resulted in fill factors in excess of 0.78 on monocrystalline silicon. Preliminary results on multicrystalline silicon cells indicate that firing cycle and junction depth may need to be optimized for each multicrystalline silicon material due to the possible role of defects in causing junction shunting underneath the gridlines.

A comprehensive and systematic investigation of low-cost surface passivation technologies is presented for achieving high-performance silicon devices such as solar Most commercial solar cells today lack adequate surface passivation, while cells. laboratory cells use conventional furnace oxides (CFO) for high-quality surface passivation involving an expensive and lengthy high-temperature step. This investigation tries to bridge the gap between commercial and laboratory cells by providing fast, lowcost methods for effective surface passivation. This report demonstrates for the first time, the efficacy of TiO<sub>2</sub>, thin (<10 nm) RTO, and PECVD SiN individually and in combination for (phosphorus diffused) emitter and (undiffused) back surface passivation. The effects of emitter sheet resistance, surface texture, and three different SiN depositions (two direct PECVD systems and one remote plasma system) were investigated. The impact of post-growth/deposition treatments such as forming gas anneal (FGA) and firing of screen-printed contacts was also examined. This study reveals that the optimum passivation scheme consisting of a thin RTO with a SiN cap and 730°C screen-printed contact firing anneal can (a) reduce the emitter saturation current density,  $J_{Oe}$ , by a factor >15 for a 90  $\Omega$ /sq. emitter, (b) reduce  $J_{Oe}$  by a factor of >3 for a 40  $\Omega$ /sq. emitter, and (c) reduce S<sub>back</sub> below 20 cm/s on 1.3  $\Omega$ cm p-Si. Furthermore, this double-layer RTO+SiN passivation is relatively independent of the deposition conditions (direct or remote) of the SiN film and is more stable under heat treatment than SiN or RTO alone. Critical to achieving low S by the RTO/PECVD SiN stack is the use of a short, moderate temperature anneal (in this study 730°C for 30 seconds) after the stack formation. This thermal treatment is believed to enhance the release and delivery of atomic hydrogen from the SiN film to the Si-SiO<sub>2</sub> interface, thereby reducing the density of interface traps at the silicon surface. Compatibility with this post-deposition anneal makes the stack passivation scheme attractive for cost-effective solar cell production where a similar anneal is required to form screen-printed contacts. Model calculations are also performed to show that the RTO+SiN surface passivation scheme may lead to greater than 17%-efficient thin screen-printed cells even with a low bulk lifetime of 20  $\mu$ s.

Screen-printing and rapid thermal annealing have been combined to achieve an aluminum- alloyed back surface field (Al-BSF) that lowers the effective back surface recombination velocity ( $S_{eff}$ ) to approximately 200 cm/s for solar cells formed on 2.3  $\Omega$ -cm Si. Analysis and characterization of the BSF structures show that this formation process satisfies the two main requirements for achieving low  $S_{eff}$ : 1) deep  $p^+$  regions and 2) uniform junctions. Screen-printing is ideally suited for fast deposition of thick Al films which, upon alloying, result in deep BSF regions. Use of a rapid alloying treatment is shown to significantly improve the BSF junction uniformity and reduce  $S_{eff}$ . The Al-BSFs formed by screen-printing and rapid alloying have been integrated into both laboratory and industrial-type fabrication sequences to achieve solar cell efficiencies in excess of 19.0% and 17.0%, respectively, on planar 2.3  $\Omega$ -cm float zone Si. For both process sequences, these cell efficiencies are 1-2% (absolute) higher than analogous cells made with un-optimized Al-BSFs or highly recombinative rear surfaces.

Research was also conducted to achieve high efficiency cells on multicrystalline silicon materials. In this report, the effect of impurity gettering and defect passivation by hydrogenation was examined on 100 µm thick string ribbon silicon material from

xvii

Evergreen solar. Solar cells were fabricated with photolithography contacts as well as screen-printed contacts. Solar cells fabricated with phosphorus and aluminum gettering and FGA hydrogenation showed an increase in efficiency of 1.2% (absolute) over cells with the same gettering treatments but without FGA hydrogenation. Without the gettering treatments, FGA had little effect on the bulk lifetime. Cells processed with conventional furnace processing and photolithography contacts had an average efficiency of 14.6% with a maximum of 15.4%. A lifetime study of the optimization and application of beltline gettering and passivation techniques indicates that lifetimes over 50  $\mu$ s are achievable even though the as-grown lifetime values are only about 1  $\mu$ s. The first 100 µm thick fully screen-printed cell with a beltline diffused emitter (BLP) of 45  $\Omega$ / produced efficiencies as high as 10.9%. The main loss components of the screenprinted devices are in the blue response and low shunt resistance. The shunt resistance of screen-printed devices was increased from 200  $\Omega$ -cm<sup>2</sup> to over 5000  $\Omega$ -cm<sup>2</sup> by implementing a spike in the contact firing profile. An increase in the red response resulted in cells that were spike fired and may be due enhanced bulk hydrogenation from the SiN film. Cell efficiencies as high as 14.9% were achieved on 250 µm substrates using beltline processing and screen-printing.

A novel simultaneous boron and phosphorus diffusion technique is presented to produce simple, high efficiency  $n^+$  pp<sup>+</sup> silicon solar cells in one thermal cycle. This technique uses boron and phosphorus spin-on dopant films to fabricate limited solid doping sources out of dummy silicon wafers. This approach results in the delivery of a fixed dose of P<sub>2</sub>O<sub>5</sub> or B<sub>2</sub> O<sub>3</sub> to the diffused sample. The resulting diffusion glass is extremely thin (~60 Å) which allows for the *in-situ* growth of a passivating thermal oxide without increasing the solar cell reflectance.  $J_0$  measurements show that the *in-situ* oxide passivation for a light boron and phosphorus diffusion provides excellent passivation properties, resulting in  $J_0$  values in the 100 fA/cm<sup>2</sup> range. Measurements of the bulk minority carrier lifetime show that by fabricating separate boron solid sources, trace impurities in the spin-on dopant film are not transported to the diffused sample. This filtering action is shown to result in bulk lifetimes in excess of 1 ms for silicon doped indirectly from the source wafers, but gives much lower lifetimes (~6 µs) for the wafers on which the boron spin-on film was directly applied. This process was validated by fabricating, *in-situ* oxide passivated, n<sup>+</sup> pp<sup>+</sup> solar cells in one high temperature cycle incorporating several high efficiency features including surface texturing and a Back Side Reflector (BSR), resulting in confirmed efficiencies in the 19-20% range.

Finally, the individual rapid and potentially low-cost processes are integrated to form high efficiency devices. RTP solar cell efficiencies of 17% and >19% are achieved on monocrystalline silicon with screen printed and photolithography contact, respectively. Rapidly formed screen printed cells in a commercial beltline machine also resulted in 17% efficient cells on monocrystalline silicon and 14.9% efficient cells on multicrystalline string ribbon material.

# **1.** Fundamental Understanding and Development of Screen-Printed Metallization for Monocrystalline Si Solar Cells

One of the most difficult aspects of large scale solar cell production is forming high-quality front contacts. The metallization techniques used in laboratory settings (which involve vacuum evaporation, lift-off photolithography, and plating) are too time consuming and impractical for large scale application. On the contrary, screen-printing (SP) offers a simple, cost-effective contact method that is consistent with the requirements for high-volume manufacturing. The problem with SP, however, is that the throughput gains are attained at the expense of device performance. The losses associated with SP metallization fall into three categories: 1) increased minority carrier recombination in the required heavily doped n<sup>+</sup> regions, 2) increased shading due to wide grid fingers (> 100µm), and 3) fill factor degradation due to poor contact quality. The purpose of this section is to provide a detailed study of the third issue: *contact quality*. This is important because contact quality determines the device fill factor, and therefore, affects the overall cell efficiency ( $\eta = V_{oc} J_{sc} FF$ ). Though high fill factor performance has been demonstrated in the past with SP [1], most commercial solar cell processes which implement this technology result in relatively low fill factors ( $\approx 0.750$ ) [2]. No comprehensive study has been conducted to isolate the causes for low fill factor in SP cells and relate them to specific process conditions.

In this study, the SP process is closely analyzed and developed so that high fill factors ( $\approx$  0.785-0.790) can be reproducibly achieved on monocrystalline Si solar cells. The requirements on emitter junction depth and contact firing schedules are established in a systematic manner. For the first time, the beneficial effect of a *post-fire* forming gas anneal on contact resistance is demonstrated. By achieving high fill-factor response, device efficiencies of 17.0% (4 cm<sup>2</sup>) are demonstrated for fully screen-printed, planar, single layer AR coated solar cells fabricated on FZ Si substrates.

#### **1.1 Fill Factor Loss Mechanisms**

The *primary* fill factor loss mechanisms associated with SP metallization are shown in Fig. 1.1. The losses arise from excess: 1) gridline resistivity, 2) contact resistance, and 3) junction leakage and shunting. The *gridline resistivity* and the *contact resistance* both depend on the

contact firing cycle and the material qualities of the conductor paste. If the overall resistance becomes excessive, then the solar cell fill factor will be lowered. The *junction leakage* and *shunting behavior* depend primarily on the junction design and the contact firing cycle. If the junction is compromised during the firing cycle, the lowered shunt resistance and increased junction leakage will cause severe fill factor degradation.

The impact of series resistance ( $R_{series}$ ), shunt resistance ( $R_{shunt}$ ), and junction leakage ( $J_{02}$  and  $n_2$ ) on device fill factor can be simulated numerically using the solar cell equivalent circuit model shown in Fig. 1.2. (The  $J_{o2}$  diode and its corresponding ideality factor model the effect of junction leakage via depletion region recombination.) This equivalent circuit was employed together with a device simulator (*PC1D-4*) to model the fill factor change as a function of  $R_{series}$ ,  $R_{shunt}$ , and  $J_{o2}$ . The results (Fig. 1.3-Fig. 1.5) can be used to formulate the following guidelines for attaining high fill factor:  $R_{shunt}$ >1000  $\Omega$ -cm<sup>2</sup>,  $R_{series}$ <0.50  $\Omega$ -cm<sup>2</sup>, and  $J_{o2}$ <10<sup>-8</sup> A/cm<sup>2</sup>. In the following sections, the experimental behavior of screen printed metallization in the context of these parameters is presented. Different characterization techniques, such as diode (dark) IV, solar cell lighted IV, contact resistance, and conductivity analysis, are used to extract the parameters which govern fill factor response.

### 1.2 Effect of SP Firing Treatment on Conductor Paste Resistivity

The conductor paste used in this work was made by Ferro Corporation (*3349 Ag Conductor*). After printing, the following procedure was used to form the contacts. First, the solvents were removed by baking on a hotplate at 150°C for 2 minutes. This was followed by firing in a 3-zone IR-belt furnace in which the lengths of zones 1,2, and 3 were 7.5", 15", and 7.5", respectively. The first two zones were set to 425°C and 580°C and used to burn off organic materials in the printed paste. The *hotzone* (zone 3) temperature was varied to suit the particular investigation. The overall firing time was determined by the beltspeed through the furnace. Beltspeeds of 15"/min and 40"/min were implemented in this study, which correspond to hotzone dwell times of 30 seconds and 11 seconds, respectively.

First, the Ag resistivity was determined so that basic model calculations could be performed. (It is instructive to note that the resistivity of pure Ag is 1.6  $\mu\Omega$ -cm.) As shown in Fig. 1.6, this parameter is a function of hotzone firing temperature. In fact, the resistivity changes by more than a factor of 2 (from 5.3 to 2.2  $\mu\Omega$ -cm) for a hotzone temperature swing of 300°C and a dwell time of 30 seconds. The data also shows the effect of varying the beltspeed through the furnace. Two points are important to note when considering the effects of beltspeed on a process. The first issue is obvious: a higher beltspeed reduces the overall process time. Additionally, for a fixed temperature setting, a higher beltspeed will result in the sample moving deeper into the furnace before it is brought to temperature. To compensate for these effects, the temperature setpoints must be increased when a faster beltspeed is implemented. This behavior is evident in Fig. 1.6.

The data in Fig. 1.6 was used to model and compare the power loss expected for solar cells with pure Ag contacts (1.6  $\mu\Omega$ -cm) and SP Ag contacts (3.5  $\mu\Omega$ -cm, 700°C hotzone, 30 sec dwell time). The following device parameters were used for simulation purposes: solar cell active area of 2 cm by 2 cm, 8 grid fingers, a single tapered bus bar, and a 40  $\Omega$ /sq emitter sheet resistance. The width and height of each finger were fixed at 130  $\mu$ m and 8  $\mu$ m, respectively (typical values for screen-printed solar cells). The simulations show that the increased metal resistivity of SP Ag compared to pure Ag leads to an R<sub>series</sub> increase of 0.12  $\Omega$ -cm<sup>2</sup> and an *additional* power loss of 0.14 mW/cm<sup>2</sup>. In other words, SP fill factors are inherently lower than those of a pure Ag metallization by approximately 0.010 due to higher  $\rho_{metal}$  and R<sub>series</sub>.

### 1.3 Effect of Junction Depth on the FF of Monocrystalline Si Solar Cells

As discussed in Section 2, most conductor pastes contain a small amount of glass frit. The frit serves to improve adhesion to the substrate by conforming to the surface topology. Additionally, for Si substrates, the frit *etches* a small distance into the Si material. If the firing process is too aggressive, the glass frit along with the metal particles will begin to encroach on the n<sup>+</sup>p junction. This encroachment manifests itself as decreased  $R_{sh}$  and increased  $J_{o2}$ . As indicated by the modeling results in Fig. 1.2, low  $R_{sh}$  and high  $J_{o2}$  can destroy the device fill factor.

In this section, the importance of junction depth on the quality of SP contacts is explored. A set of phosphorus diffusions was carried out using cerium pentaphosphate solid sources. The diffusion time was fixed at 30 minutes, and in each case the peak temperature was varied. The resulting sheet resistances were in the 40-90  $\Omega$ /sq range, and the junction depths are shown in Fig. 1.7.

Screen-printed solar cells were formed on each emitter. (Throughout this study, all devices were  $4 \text{ cm}^2$  in area, and the front contact coverage was roughly 7%). To fire the contacts, an

intermediate beltline firing cycle (hotzone temperature of 730°C and beltspeed of 15"/min) was selected based on Fig. 1.6. After firing, the contacts were annealed in forming gas at 400°C. (This FGA plays an important role in reducing contact resistance, and will be discussed in detail in a following section.) A histogram of fill factor versus emitter sheet resistance is shown in Fig. 1.8. For comparison, the high fill factor of a device formed with photolithography (PL) contacts is also shown. The same data is presented as a function of junction depth in Fig. 1.9.

As shown in Fig. 1.9, the highest fill factor was measured for the deepest junction (40  $\Omega/sq$ ,  $x_i$  of 0.38µm). Yet even for this case, there is a noticeable fill factor spread (0.740-0.780) which is unacceptable for reliable, high-efficiency devices. As the emitter junction depth decreases, the fill factor drops off sharply. This behavior suggests two possibilities: 1) with reduced junction depth the cells suffer from lowered R<sub>sh</sub> and high J<sub>o2</sub>, or 2) with increased emitter sheet resistance the devices experience higher R<sub>series</sub> from contact resistance effects. In order to precisely determine the cause for the fill factor drop, the non-illuminated I-V responses for the cells were measured and analyzed. Plots of these IV curves are shown in Fig. 1.10. For comparison, the IV response for a cell with contacts formed by lift-off PL is also shown. It is immediately evident that the lift-off PL cell has a large R<sub>sh</sub> and low leakage current. Fitting this IV curve to the equivalent circuit model in Fig. 1.2 reveals in an  $R_{sh}=6x10^3 \Omega$ -cm<sup>2</sup>,  $J_{o2}=1x10^{-8} A/cm^2$  (with  $n_2=2$ ), and  $R_{series}=0.35 \ \Omega$ -cm<sup>2</sup>. These parameters are consistent with the high fill factor (0.792) exhibited by the cell. On the contrary, the R<sub>sh</sub> behavior for all the screen-printed devices is significantly worse. Analysis of these devices reveals  $R_{sh}$  values less than 1000  $\Omega\text{-}cm^2$  in all cases and  $J_{o2}$ values greater than 0.5  $\mu$ A/cm<sup>2</sup> (n<sub>2</sub>=2.2). Moreover, the junction leakage worsens with increasing emitter sheet resistance and decreasing junction depth. These effects are responsible for the fill factor degradation and scatter shown in Fig. 1.8 and Fig. 1.9.

It is interesting to note that for all the n<sup>+</sup> emitters shown in Fig. 1.10, which exhibit surface concentrations between  $2x10^{20}$ - $5x10^{20}$  cm<sup>-3</sup>, the R<sub>series</sub> for all SP contacts is essentially the same. This observation is important because R<sub>series</sub> is often presumed to be the cause of fill factor degradation when in fact the problem stems from the compromised junction.

### 1.4 Reducing Leakage and Shunting with Deeper n<sup>+</sup> Emitters

Deeper emitters were attained by diffusion from a POCl<sub>3</sub> liquid source at a diffusion temperature of 900°C. An appropriate gas flow condition and diffusion time were established so that a 35-40  $\Omega$ /sq emitter with 0.5 µm junction depth was achieved. The n<sup>+</sup> region profile is

shown in Fig. 1.11 along with the first set of emitters formed by solid source diffusion. Initial SP solar cells were fabricated on this new emitter using the same process detailed above (hotzone of 730°C and beltspeed of 15"/min). Average fill factors of 0.785 were consistently achieved. It is evident from Fig. 1.12 that the problems of excess shunting and leakage are eliminated.

| Junction Depth | R <sub>shunt</sub> Value              | Junction/FF Quality            |  |

|----------------|---------------------------------------|--------------------------------|--|

| < 0.25 µm      | low                                   | Completely shunted/Low FF      |  |

| 0.30-0.40 μm   | $< 1000 \Omega\text{-cm}^2$           | Onset of leakage/Moderate FF   |  |

| > 0.50 μm      | $\approx 10,000 \ \Omega\text{-cm}^2$ | No shunting or leakage/High FF |  |

Table 1.1. Junction depth requirement for screen printed contact formation to monocrystalline Si solar cells.

By consolidating the data in Fig. 1.8 through Fig. 1.12, the following guidelines for emitter junction depth are established for SP contact formation.

# **1.5 Effect of Firing Conditions and Post-Firing Forming Gas Anneal on the Contact Resistance and Fill Factor**

In addition to  $R_{sh}$  and  $J_{o2}$ , the quality of SP contacts depends critically on the overall  $R_{series}$ . This was shown in the modeling results of Fig. 1.4 and Fig. 1.5.  $R_{series}$  is comprised of different resistance components (metal resistivity and contact resistance, among others). The metal resistivity issue was discussed in Section 4.2.2. In this section, the contact resistance ( $\rho_c$ ) associated with SP metallization is investigated. In a novel application, a low-temperature FGA is shown to be effective in lowering  $\rho_c$  after the SP contacts have been fired in the IR-belt furnace.

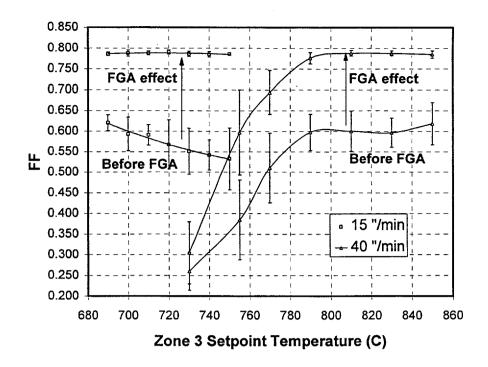

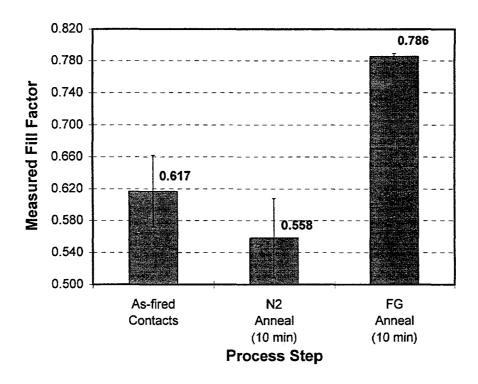

The investigation of peak firing condition on fill factor was extended for large temperature variations. The response is shown in Fig. 1.13 for beltspeeds of 15"/min and 40"/min. Immediately after the firing treatment, the fill factors are prohibitively low ( $\approx 0.500-0.600$ ). However, the fill factors drastically improve after the samples are annealed in forming gas at 400°C. For the hotzone dwell time of 30 sec (beltspeed of 15"/min), there exists at least a 60°C range in acceptable peak firing temperature (690°C to 750°C) in which final fill factors of 0.785 are attained. For the 40"/min beltspeed, a similar range exists, though higher process temperatures are required to offset the reduced dwell time and increased ramp-up distance. These

results indicate that, in contrast to conventional thinking on the topic, the range of acceptable firing temperatures is relatively broad.

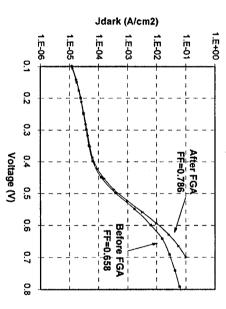

In order to verify that the FGA specifically acts to improve  $\rho_c$ , non-illuminated IV measurements were conducted for a typical device before and after the FGA treatment. The result in Fig. 1.15 shows that after annealing, the curve changes in the high-current regime where the response is most sensitive to  $R_{series}$ . It was determined separately that the FGA has no effect on the gridline resistivity of the fired metal. This clearly shows that the only parameter altered by the FGA is  $\rho_c$ . Additionally, *transmission line model* (TLM) based contact resistance measurements were performed for the SP metallization (Fig. 1.14). These results also provide clear support of  $\rho_c$  reduction as a result of the FGA treatment.

It is believed that the FGA initiates an oxidation-reduction (redox) reaction at the interface between the printed metal and the Si surface. The question is why should such a reaction be important for SP contacts? The Ag paste used in this study contains a lead borosilicate glass frit. At the time of printing, the Ag and frit particles are packed together within the organic vehicle. When firing is initiated, the organic vehicle is burned away leaving behind the metal-frit combination. As the temperature is raised further, the metal particles begin to sinter which serves to expel or "squeeze out" the frit from the interior of the printed feature. (This process is also referred to as glass "bleedout" [3].) The glass frit is forced to migrate to the metal surface and the Si-metal interface. Since the firing is done in air, some of the lead content in the frit becomes oxidized. This creates an insulating layer and a large  $\rho_c$  at the metal-Si interface. The hydrogen in the ensuing FGA is believed to reduce this species back to Pb, bringing about the measured improvement in the  $\rho_c$ .

In order to provide a degree of verification for this model, a similar contact anneal at 400°C was conducted in N<sub>2</sub> instead of forming gas. The results in Fig. 1.16 show that the N<sub>2</sub> anneal in *no way* improves the contact quality. However, subjecting the same samples to a subsequent FGA treatment improves the fill factor to a high level. This provides clear evidence that hydrogen is the active species in this process, and it supports the theory that a reduction reaction is occurring at the Si surface to lower  $\rho_c$ .

1-6

# **1.6 Effect of Peak Firing Temperature on Solar Cell Shunting Behavior and Fill Factor**

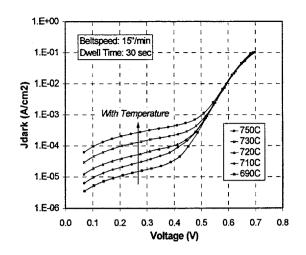

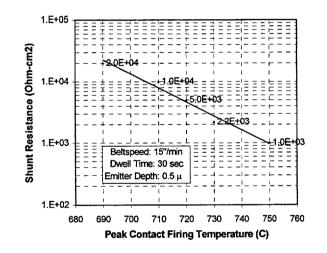

It is instructive to analyze the results of Fig. 1.13 in greater detail to ascertain the effect of peak firing temperature on contact quality. As indicated in this figure, there is a relatively large firing window (>60°C) which can be implemented to form high quality contacts. The question arises as to precisely what effect (if any) the process temperature within this range has on the contact quality. The average dark IV responses for certain devices are shown in Fig. 1.17. The corresponding  $R_{sh}$  values, extracted from numerical analysis of the IV curves, are shown in Fig. 1.18. The analysis reveals that increasing the hotzone temperature by as little as 10°C results in a measurably reduced  $R_{sh}$ . A 60°C increase in hotzone temperature reduces  $R_{sh}$  by over one order of magnitude, from 2x10<sup>4</sup>  $\Omega$ -cm<sup>2</sup> at 690°C to 10<sup>3</sup>  $\Omega$ -cm<sup>2</sup> at 750°C. However, as shown in Fig. 1.3, an  $R_{sh}$  value of 10<sup>3</sup>  $\Omega$ -cm<sup>2</sup> essentially marks the cutoff between high and low fill factor response for solar cells. Since all cases in Fig. 1.17 have  $R_{sh}$  values are higher than 10<sup>3</sup>  $\Omega$ -cm<sup>2</sup>, all devices exhibit high fill factors (≈0.785).

Fig. 1.6 and Fig. 1.17 illustrate the fundamental competition in the SP process. Higher temperatures are needed to achieve low gridline resistivity, whereas lower temperatures are desirable to avoid shunting. The highest fill factors are achieved only when both  $R_{series}$  and  $R_{shunt}$  values fall within acceptable ranges.

Table 1.2. Reproducibility of the SP process developed in this study. Each entry represents an average value over multiple ( $\approx 9$ ) cells. All devices are planar, 4 cm<sup>2</sup> in area, with single layer AR coatings.

| Run ID | Cell Type                           | Voc<br>(mV) | Jsc<br>(mA/cm²) | Fill<br>Factor | Eff.<br>(%) |

|--------|-------------------------------------|-------------|-----------------|----------------|-------------|

| 1      | 1.3Ω-cm Si (850°C beltline Al-BSF)  | 624         | 34.5            | 0.791          | 17.0        |

| 2      | 1.3Ω-cm Si (850°C beltline Al-BSF)  | 623         | 33.8            | 0.789          | 16.6        |

| 3      | 1.3Ω-cm Si (850°C RTP Al-BSF)       | 626         | 34.4            | 0.783          | 17.0        |

| 4      | 0.65Ω-cm Si (no BSF)                | 621         | 32.8            | 0.785          | 16.0        |

| 5      | 0.65Ω-cm Si (900°C beltline Al-BSF) | 635         | 33.7            | 0.796          | 17.0        |

In order to determine the reproducibility of this contact formation method, many solar cells were fabricated with the above developed process. By implementing the 0.5  $\mu$ m deep POCl<sub>3</sub> emitter, a hotzone temperature of 700°C-730°C with a dwell time of 30 seconds, and a 10 min FGA after firing, fill factors between 0.785-0.795 were achieved in a consistent manner on monocrystalline Si. Some of these results are listed in Table 1.2.

1-7

#### 1.7 SP mc-Si Solar Cells

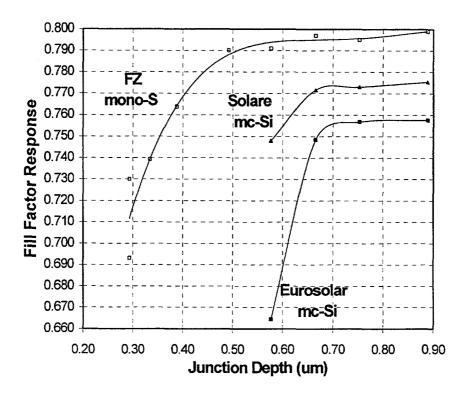

The SP process has been applied to various mc-Si substrates including Solarex, HEM, and Eurosolare. The fill factors as a function of junction depth are shown in Fig. 1.19. The results show that for highest FF response, deeper junctions are required for mc-Si substrates than for (100) single crystal Si. The increase in junction depth required, and the relative fill factors achieved, are material specific. It has been observed [4] that the etch reaction between the frit and Si is more aggressive for certain crystalline orientations (preference for <111> over <100>). Since mc-Si grains exhibit random orientations across a wafer, the reaction of the frit with various grains will be different. Some regions will have a greater tendency to react, and therefore, decrease the  $R_{shunt}$ .

#### **1.8 Conclusions**

An effective SP methodology has been developed which yields high-quality contacts and fill factors in the 0.785-0.795 range on single crystal Si solar cells. These values approach those achieved by intricate lift-off photolithography procedures. In achieving these results, multiple device related effects have been established. It has been shown that a critical junction depth (0.5  $\mu$ m in the present case) is required to avoid fill factor degradation due to device shunting and excessive leakage. For this optimal emitter design, a relationship between peak firing temperature and the resulting R<sub>shunt</sub> has been determined. Additionally, a novel post-firing FGA process has been shown to dramatically improve fill factor by lowering the contact resistance. It is believed that the hydrogen exposure during this treatment induces a redox reaction at the interface between Si and the SP contacts. This contact formation methodology has been used to achieve 17% efficient fully screen-printed, planar, single layer AR coated devices (4 cm<sup>2</sup> area) on FZ substrates. Other important aspects of these high-efficiency devices are discussed in the upcoming sections.

#### **1.9 References**

<sup>[1]</sup> J. Nijs, E. Demesmaeker, J. Szlufcik, J. Poortmans, L. Frisson, K. De Clercq, M. Ghannam, R. Mertens, R. Van Overstraeten, "Latest Efficiency Results with the Screenprinting Technology and Comparison with the Buried Contact Structure," in *Proc. 24<sup>th</sup> IEEE Photovoltaics Specialists Conf.*, 1994, pp. 1242-1249.

[2] R.R. King, K.W. Mitchell, and J.M. Gee, "Back Surface Cell Structures for Reducing Recombination in CZ Silicon Solar Cells," in *Proc.* 24<sup>th</sup> IEEE Photovoltaics Specialists Conf., 1994, pp. 1291-1294.

[3] B.E. Taylor and W.A. Craig, "Thick Film Palladium Silver Conductors: A Processing and Performance Survey," *Proceedings of the 1986 International Symposium on Microelectronics*, pp. 124-131.

Fig. 1.1. Fill factor loss mechanisms associated with screen printing.

Fig. 1.2. Solar cell equivalent circuit. Fill factor is influenced by Jo2, Rshunt, and Rseries.

0.820

0.810

0.800

0.790

0.780

0.760

0.750

0.740

0.730

0.720

0.710

0.700

0.1 0.2 0.3 0.4 0.5 0.6 0.7 8.0 0.9 1.0

Fill Factors 0.770

Fig. 1.3. Effect of R<sub>shunt</sub> and J<sub>02</sub> on fill factor response. (R<sub>series</sub> fixed at  $0.8 \Omega$ -cm<sup>2</sup>).

Rseries (Ohm-cm<sup>2</sup>) Fig. 1.4. Effect of Rseries and Rshunt on fill factor response. (J<sub>02</sub> fixed at 10<sup>-8</sup> A/cm<sup>2</sup>.)

-Rsh=1e6, Jo2=1e-8 (n2=2)

- Rsh=1e3, Jo2=1e-8 (n2=2)

-Rsh=5e2, Jo2=1e-8 (n2=2)

<sub>o2</sub>=1e-8 A/cm<sup>2</sup> (n<sub>2</sub>=2)

Fig. 1.5. Effect of Rseries and Jo2 on fill factor response. (R<sub>shunt</sub> fixed at  $10^4 \Omega$ -cm<sup>2</sup>.)

Fig. 1.6. Effect of beltline firing temperature and beltspeed on metal conductivity. The corresponding hotzone dwell times are 30 sec  $(15^{"}/min)$  and 11 sec  $(40^{"}/min)$ .

Fig. 1.7. Solid source diffusion profiles measured by the spreading resistance technique. The diffusion time was fixed at 30 min, and the highest temperature used was 850°C.

Fig. 1.8. Fill factor versus emitter sheet resistance.

Fig. 1.9. Relationship between screen-printed fill factor and junction depth.

Fig. 1.10. Shunt and junction leakage effects on solar cell dark IV response.

.

.

Fig. 1.11. Deeper POCl<sub>3</sub> emitter as compared to original solid source diffusion.

Fig. 1.12. Dark IV response when printing is done on deeper emitter.

Fig. 1.13. Fill factor response as a function of hotzone temperature and dwell time.

.

Fig. 1.14. The effect of a 400°C FGA on the series resistance of fired SP contacts.

|                         |     |             | Conta                                                            | ict Resi                                          | stance                                                    | (mΩ-cn                                                                              | n2)                                                              |

|-------------------------|-----|-------------|------------------------------------------------------------------|---------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------|

|                         |     | 1.E-03      | 1.E-02                                                           | 1.E-0                                             | 1.E+00                                                    | 1.E+01                                                                              | 1.E+02                                                           |

|                         | 30  | Ť           | TTIN                                                             | <del>, , , , , , , , , , , , , , , , , , , </del> |                                                           | Trind                                                                               |                                                                  |

|                         | 40  |             | 4 841000<br>4 841000<br>4 84100<br>4 84100<br>4 84400<br>4 84400 |                                                   |                                                           |                                                                                     |                                                                  |

| Sh                      | ន   | + i         |                                                                  | <u>                                      </u>     |                                                           | -                                                                                   |                                                                  |

| Sheet Resistance (Ω/sq) | 60  | <br>   <br> | 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 +                          | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1             |                                                           | 1                                                                                   |                                                                  |

| tance (                 | 70  |             | 111100                                                           |                                                   | 1 11110<br>211100<br>111100<br>111100<br>111100<br>111100 | 1 1 1 1 1 1 1<br>A 121721 L<br>1 1 1 1 1 1<br>1 1 1 1 1 1<br>1 1 1 1 1 1<br>1 1 1 1 |                                                                  |

| ∩/sq)                   | 80  |             | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                            | + + + + + + + + + + + + + + + + + + +             | 1 1 1100<br>+ +-0+100<br>-+ +-0+100<br>                   | + + + + + + + + + + + + + + + + + + +                                               | -1 + 1 + 1 + 1 + 1<br>-1 + 1 + 1 + 1 + +<br>1 + 1 + 1 + 1 + − =  |

|                         | 90  | - +         | I FITH                                                           | 4 1 + 1300<br>+ 5+64100+<br>1 4 630000            | 1 1 1010<br>1010<br>1010<br>1011<br>1011<br>1011<br>1011  | 1 + 1 + 14<br># 1 + 1 + 1 + 1<br>1 + 1 + 1 + 1 + 1<br>1 + 1 +                       | L 6 1 1 1 1 1<br>-1 + 1+1111<br>0 1 1 1 1 1 1 1<br>1 1 1 1 1 1 1 |

|                         | 100 | Ľ           | 111000                                                           | 1 4 1 1 1 1 1 1 1                                 | 1                                                         | 1 1 1 1 1 1 1 1 1                                                                   | 11111                                                            |

Fig. 1.15. The effect of the FGA on the  $\rho_c$  of SP contacts to  $n^+$  emitter regions.

-

Fig. 1.16. Effect of post-firing contact anneal in non-reducing  $(N_2)$  and reducing (FG) ambients. The anneal temperature was 400°C.

Fig. 1.17. Effect of hotzone firing temperature on the ensuing dark IV response of solar cells.

Fig. 1.18. Effect of hotzone firing temperature on  $R_{\rm sh}$  value.

Fig. 1.19. The effect of junction depth on fill factors for SP mc-Si solar cells.

# 2. Comprehensive Study of Rapid, Low-Cost Silicon Surface Passivation Technologies

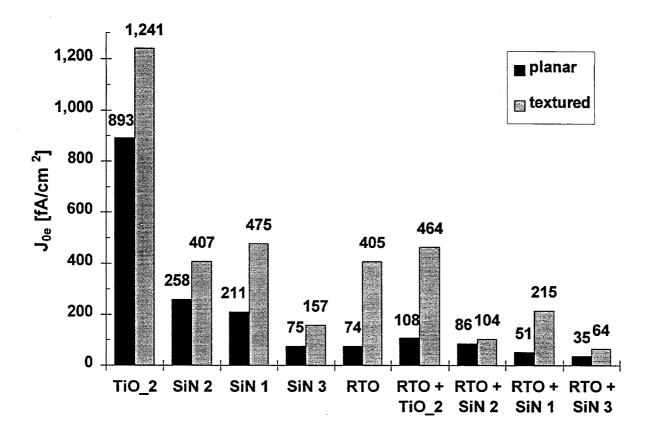

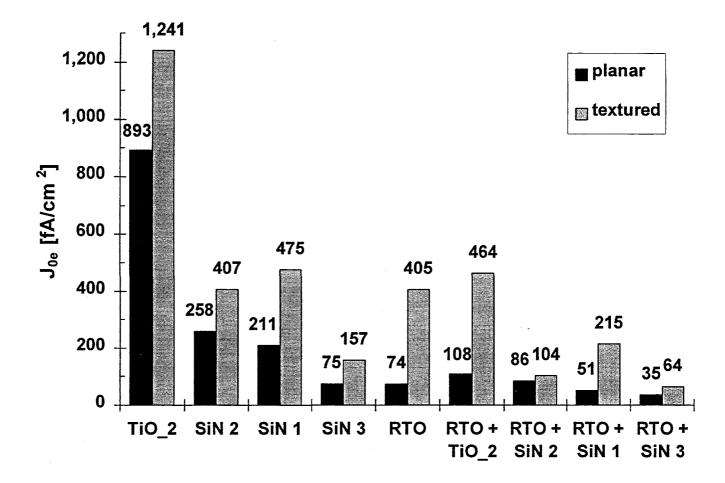

A comprehensive and systematic investigation of low-cost surface passivation technologies is presented for achieving high-performance silicon devices, in this case for photovoltaic devices. Most commercial solar cells today lack adequate surface passivation. In contrast, laboratory cells use conventional furnace oxides (CFO) for high-quality front and/or back surface passivation but at the expense of a lengthy, high-temperature step. This investigation tries to bridge the gap between commercial and laboratory cells by providing fast, low-cost methods for effective surface passivation. As an alternative to CFO, rapid thermal oxides (RTO) can give comparable passivation in a much shorter time. Additionally, plasma deposition of silicon nitride (SiN) has recently emerged as a low-temperature passivation technique, which simultaneously provides a good antireflection coating for silicon solar cells. In this work, we demonstrate, for the first time, the efficacy of TiO<sub>2</sub>, thin (<10 nm) RTO, and PECVD SiN passivation individually and in combination for (diffused) emitter and (non-diffused) back surface passivation. The effects of emitter sheet resistance, surface texture, and three different SiN depositions (two using a direct PECVD system and one using a remote system) were investigated. The impact of post-growth/deposition treatments such as forming gas anneal (FGA) and firing of screen-printed contacts was also examined. This study reveals that the optimum passivation scheme consisting of a thin RTO, SiN, and 730°C screen-printed contact firing anneal can (a) reduce the emitter saturation current density,  $J_{0e}$ , by a factor of >15 for a 90  $\Omega$ /sq. emitter, (b) reduce J<sub>0e</sub> by a factor of > 3 for a 40  $\Omega$ /sq. emitter, and (c) reduce Sback below 20 cm/s on 1.3 Ocm p-Si. Furthermore, this double-layer RTO+SiN passivation is independent of the deposition conditions (direct or remote) of the SiN film and is more stable

under heat treatment than SiN or RTO alone. Model calculations are also performed to show that the RTO+SiN surface passivation scheme may lead to 17%-efficient thin screen-printed cells even with a low bulk lifetime of 20  $\mu$ s.

## 2.1 INTRODUCTION

Minimizing recombination of minority-carriers at the surfaces of silicon is crucial for the performance of many Si devices including solar cells, BJTs, CCDs, power devices. The objective of this paper is to provide a comprehensive and systematic study of different surface passivation technologies available for diffused and non-diffused silicon, planar (flat) and chemically textured surfaces. The information is immediately applicable for junction devices such as solar cells, which typically have a n<sup>+</sup>p structure. For such devices, surface passivation is the key to higher performance especially because the trend is towards thinner substrates, which bring the surface closer to the collecting junction.