# **High-Performance RF Coil Inductors on Silicon**

V. Malba D. Young J.J. Ou A.F. Bernhardt B.E. Boser

This paper was prepared for submittal to the 48th Electronic Components and Technology Conference Seattle, WA

May 25-28, 1998

## **March 1998**

# DISCLAIMER

This document was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor the University of California nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or the University of California. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or the University of California, and shall not be used for advertising or product endorsement purposes.

# High-Performance RF Coil Inductors on Silicon

V. Malba, D. Young\*, J. J. Ou\*, A. F. Bernhardt, and B. E. Boser\*

Lawrence Livermore National Laboratory Livermore, California 94550

\*Department of Electrical Engineering and Computer Sciences University of California, Berkeley, California 94720

#### **Abstract**

Strong demand for wireless communication devices has motivated research directed toward monolithic integration of transceivers. The fundamental electronic component least compatible with silicon integrated circuits is the inductor, although a number of inductors are required to implement oscillators, filters and matching networks in cellular devices. Spiral inductors have been integrated into the silicon IC metallization sequence but have not performed adequately due to coupling to the silicon which results in parasitic capacitance and loss. We have, for the first time, fabricated three dimensional coil inductors on silicon which have significantly lower capacitive coupling and loss and which now exceed the requirements of potential applications. Quality factors of 30 at 1 GHz have been measured in single turn devices and Q > 16 in 2 and 4 turn devices. The reduced Q for multiturn devices appears to be related to eddy currents in outer turns generated by magnetic fields from current in neighboring turns. Higher Q values significantly in excess of 30 are anticipated using modified coil designs.

#### Introduction

Increasing demands for wireless communications motivate a growing interest in low-cost, monolithic personal communication transceivers. High-performance RF inductors are the key components for implementing critical building blocks such as low-noise RF voltagecontrolled oscillators (VCOs), low-loss impedance matching networks, passive filters, and inductive loads for power amplifiers. Critical parameters include inductance value, quality factor, and self-resonant frequency. Many cellular communication systems such as AMPS and GSM operate around 1 GHz and require inductance values on the order of 5 nH, Q of at least 10, and a self-resonant frequency well in excess of the operating frequency. However, such high performance inductors are not available in current silicon IC technology. Therefore, the integration of these devices has become the key task for realizing monolithic wireless transceivers.

Conventional aluminum spiral inductors fabricated on standard silicon substrates achieve Q-factors around 3 at 1 GHz [1, 2]. Two issues contribute to the limited quality factor: eddy currents in the substrate and metal resistive losses. The first problem can be addressed in part by removing the silicon substrate underneath the inductor, leading to a Q value around 5 reported in [3]. Reference [4] reports a Q close to 10 at 1 GHz through using copper traces on a sapphire substrate. While improving the Q-value, sapphire substrates are incompatible with standard IC processes.

In this paper, a new solution based on a three-dimensional (3-D) coil inductor is proposed. The 3-D microstructure minimizes the device capacitive coupling to the substrate and eddy current loss. Thick copper traces reduce the series resistance thus ensuring a high Q. Because of the low processing temperature, the inductor can be fabricated on top of wafers with completed electronics without affecting the characteristics of active devices. This is particularly crucial in RF applications where the availability of the most recent IC technology is a critical competitive advantage.

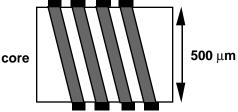

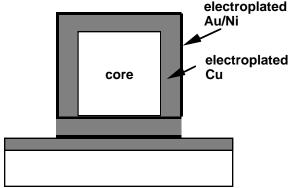

#### Monolithic Three-Dimensional Coil Inductor

Figure I shows the schematic top and cross-sectional views of a 3-D four-turn coil inductor. The device consists of 5 um thick copper traces electroplated around an insulating core with a 650 um by 500 um cross-section. Electroplated copper traces are 50  $\mu m$  wide separated by 50  $\mu m$  spaces. The silicon dioxide covering the silicon substrate is also 5  $\mu m$  thick.. Compared to spiral inductors, this geometry minimizes the coil area which is in close proximity to the substrate and hence minimizes the eddy current loss, resulting in a maximized Q-factor and self-resonant frequency of the device.

Figure 1a: Inductor top view

Figure 1b: Inductor cross-section

Copper is selected as the interconnect metal because of its low sheet resistance, critical for achieving a high Q-factor. The skin depth at 1 GHz determines the

optimal metal thickness of 5 um. The 50 um metal width represents a compromise between the interconnect resistance and capacitance to the substrate. A 50 um line spacing is used in this conservative design to avoid processing difficulties.

Alumina is used as the core material because of its negligible loss tangent at high frequencies [5], a key parameter to ensure a high Q-factor. The core width of 500 um is found experimentally to be the minimum that avoids tilting during attachment to the bottom copper traces. Its height is limited by the thickness of a commercially available alumina sheet.

A typical RF transceiver employs inductances on the order of 5 nH. For the current fabrication, devices with one, two, and four turns are designed to achieve 5 nH, 8.5 nH, and 13.5 nH, respectively.

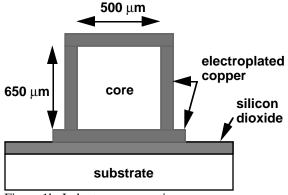

#### **Fabrication Process**

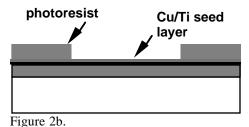

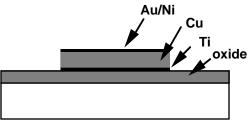

Figure 2 illustrates the process flow. First, the passivated with 5 um or 10 um lowtemperature oxide (Fig. 2a). Then the bottom traces of the inductors are fabricated. For this purpose, a 500 Å titanium and 3000 Å copper seed layer are sputtered and then covered by an 8 um thick electroplated resist. The electroplating method is chosen because it can conformally deposit a thick resist on a complex surface such as an inductor core. The patterns of the bottom metal traces are transferred photolithographically (Fig. 2b). This step is followed by selective electroplating of the 5 um copper traces. To prevent oxidation, the copper is passivated with two 1000 Å layers of electrolytic nickel and gold (Fig. 2c). Finally the photoresist and copper/titanium seed layer are removed with a wet etch, leaving the bottom metal traces of the inductor on the substrate (Fig. 2d).

Au/Ni passivation electroplated Cu

Figure 2c.

Figure 2d.

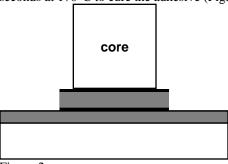

The core of the inductor is formed from an alumina sheet. The sheet is first covered with a 75 um thick electrically insulating thermoplastic adhesive film and then diced into 500 um wide strips. A 2% width accuracy has been achieved by using a thin diamond grit blade on a commercial dicing saw. The strips are then centered on the bottom copper traces and baked for 30 seconds at 170°C to cure the adhesive (Fig. 2e).

Figure 2e.

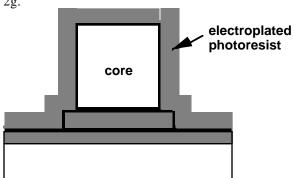

To fabricate the copper traces on the side and the top of the alumina core, the same process as was used to fabricate the bottom traces is used (Fig. 2f). However, the resist is exposed with a three-dimensional maskless direct-write laser lithography tool [6]. After developing the laser exposed resist, 5 um thick copper traces are electroplated at the sides and on the top of the alumina core. The completed inductor coil is illustrated in Fig. 2g.

Figure 2f.

Figure 2g.

## **Experimental Results**

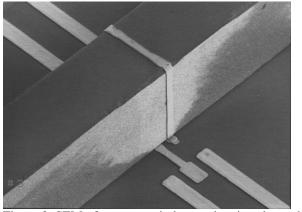

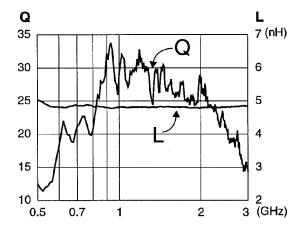

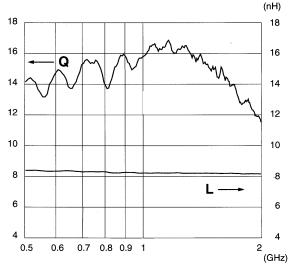

Figure 3 shows an SEM of a one turn inductor on a 10  $\Omega$ -cm silicon substrate with a 5  $\mu$ m deposited oxide. The two-port S-parameters of devices are obtained with an HP8719 network analyzer. Q and the inductance values as a function of frequency are generated after deembedding the parasitics from the probe pads. An inductance of 4.8 nH is measured with a Q of 30 at 1 GHz as shown in Figure 4. The device has Q over 15 out to 3 GHz.

Figure 3: SEM of a one-turn inductor showing the probe pad structure.

Figure 4: Inductance and Q vs. frequency for a one-turn inductor.

The self-resonant frequency observed in the S-parameter measurement is 10 GHz, including the parasitic capacitance of the probe pads. The self-resonant frequency of the inductor itself is significantly higher but

numerical de-embedding was not extended to high frequencies.

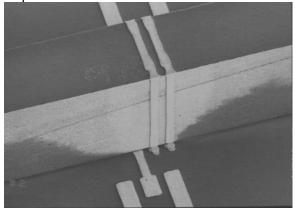

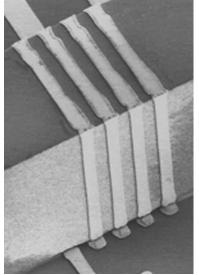

Figure 5: SEM of a two-turn inductor.

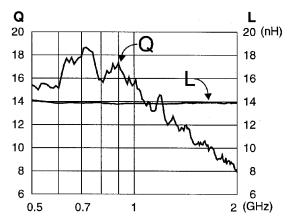

Figure 5 shows an SEM of a two-turn inductor on a similar substrate. The coil area above the substrate is approximately 250 um by 500 um, comparable to that of a typical spiral inductor of the same inductance value. The two-turn inductor achieves 8 nH inductance with a peak Q of 16 at 900 MHz as seen in Figure 6.. These results closely match the simulated values. The self-resonant frequency observed in the raw S-parameter data for the two-tun inductor was 8 GHz.

Figure 6: Inductance and Q vs. frequency for a two-turn inductor.

Figure 7 presents an SEM of an inductor with four turns. Measurement results for this device are shown in Figure 8 with a peak Q over 18 at about 750 MHz. The observed self-resonant frequency was 4 GHz.

### Discussion

The 3-D inductors fabricated in this work have the advantage that most of the metallization is removed from the vicinity of the silicon. Traces on the sides and top of the core have relatively small capacitance to the substrate and this raises the self resonant frequency of the inductors to well above the important 1 to 3 GHz operating range.

In 3-D inductors most magnetic field loops do not penetrate the silicon substrate. In an approximate sense, only field loops generated by current flowing in the traces between the core and the substrate can penetrate

the silicon, while fields from current flowing in traces on the top and sides of the core do not. Thus, much smaller eddy currents are generated in the silicon.

Figure 7: SEM of a four-turn inductor.

Figure 8: Inductance and Q vs. frequency for a four-turn inductor.

Finally, the effect of eddy currents in the traces themselves must be considered. We believe that the significant reduction in O value observed in the two- and four-turn inductors compared to the one-turn inductor can be explained by eddy currents generated in one trace by current flowing in a neighboring trace. In an infinite solenoid, the magnetic field at a given trace from a neighboring trace is canceled by the field generated by the neighbor on the opposite side. At the ends of a finite solenoid, however, this cancellation cannot occur and the non-zero magnetic field at the outer traces generates eddy currents. The trace of a single turn inductor has no neighboring traces (except under the core - see Figure 3). Therefore, although additional turns increase inductance they also increase loss more than would be predicted simply from the increase trace length and the corresponding Ohmic loss. This line of reasoning leads to two conclusions which will be verified in future work: a 3/4 turn inductor (no traces under the core) should have O significantly above 30 and devices with much higher turn counts will have diminished end effects and should have Q higher than 16.

#### Conclusions

Compared to conventional aluminum spiral inductors, 3-D copper coil inductors achieve a substantially superior performance with Q-values up to 30 at 1 GHz. This performance is attributed to lower Ohmic loss associated with 5  $\mu$ m thick copper traces, lower eddy current loss in the silicon and lower capacitive coupling to the substrate. At the same time still higher Q values may be possible with more sophisticated designs which take into account details of the field and current distributions.

Inductors integrated onto active silicon substrates are critical for reducing the off-chip component count, lowering power dissipation, and improving the performance of personal RF communication devices such as cellular phones. While initial devices have been fabricated on bare silicon wafers, all fabrication steps are compatible with standard IC technology, thus allowing monolithic integration of active devices with high-Q inductors.

## Acknowledgment

The authors wish to thank Christopher Harvey, Leland Evans, and Robert T. Graff for helpful suggestions and processing assistance. this work was performed in part under the auspices of the U.S. Department of Energy by Lawrence Livermore National Laboratory under contract number W-7405-ENG-48. Certain fabrication steps were carried out in the Berkeley Microfabrication Laboratory.

#### References

- [1] N.M Nguyen and R.G. Meyer, "Si IC-compatible inductors and LC passive filters," IEEE Journal of Solid-State Circuits, vol 25, no. 4, pp. 1028-1031, August 1990.

- [2] J.N. Burghartz, et al., "Microwave inductors and capacitors in standard multilevel interconnect silicon technology," IEEE Transactions on Microwave Theory and Techniques, vol. 44, no. 1, pp. 100-104, January 1996

- [3] J.Y-C. Chang, A.A. Abidi, and M. Gaitan, "Large suspended inductors on silicon and their use in a 2-um CMOS RF amplifier," IEEE Transactions on Electron Device Letters, vol 14, no. 5, pp. 246-248, May 1993.

- [4] J.N. Burghartz, et al., "Monolithic spiral inductors fabricated using a VLSI Cu-damascene interconnect technology and low-loss substrate," in IEDM Tech. Dig., pp. 96-99, 1996

- [5] A. Nakayama and K. Shimizu, "An improves reflection wave method for measurement of complex permittivity at 100 MHz 1 GHz", IECE Transactions Electron, vol. E77-C, no. 4, pp. 633-638, April 1994

- [6] V. Malba, V. Liberman, A.F. Bernhardt, "Fabrication of a DRAM cube using a novel laser patterned 3-D interconnect process," in Proceedings of the

International Conference on Multichip Modules, pp. 160-165, April 1997.

| Technical Information Department • Lawrence Livermore National Laboratory<br>University of California • Livermore, California 94551 |

|-------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                     |

|                                                                                                                                     |

|                                                                                                                                     |

|                                                                                                                                     |