# THE RISC PROCESSOR MODULE FOR FASTBUS COMPUTATION APPLICATIONS

## The Results of a Phase II SBIR Grant

## Scientific Systems International, Ltd.\*

#### DISCLAIMER

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

Work performed under the auspices of the U.S. Department of Energy SBIR Contract DE-AC02-88ER-80599 \*3491 B Trinity Drive Los Alamos, New Mexico (505) 662-6712

DISTRIBUTION OF THIS DOCUMENT IS UNLIMITED

#### DISCLAIMER

Portions of this document may be illegible in electronic image products. Images are produced from the best available original document.

# TABLE OF CONTENTS

| and the second |     |  |

|------------------------------------------------------------------------------------------------------------------|-----|--|

| 1. Overview                                                                                                      | 1   |  |

| 2. Chronology of the Contract                                                                                    | 2   |  |

| 2.1 Discussion of Objectives                                                                                     | 3   |  |

| 2.2 Actions by ASIC Manufacturers                                                                                | 5   |  |

| 2.3 Organization of the Report                                                                                   | 6   |  |

| Appendix A - FRPM Specifications & Operations Manual                                                             | 8   |  |

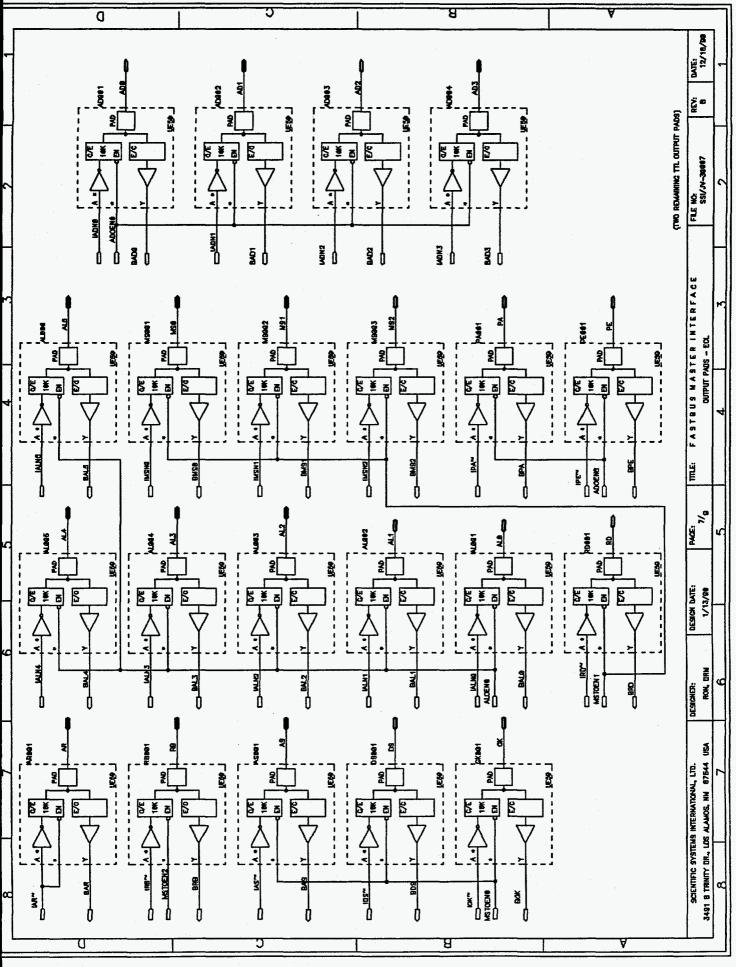

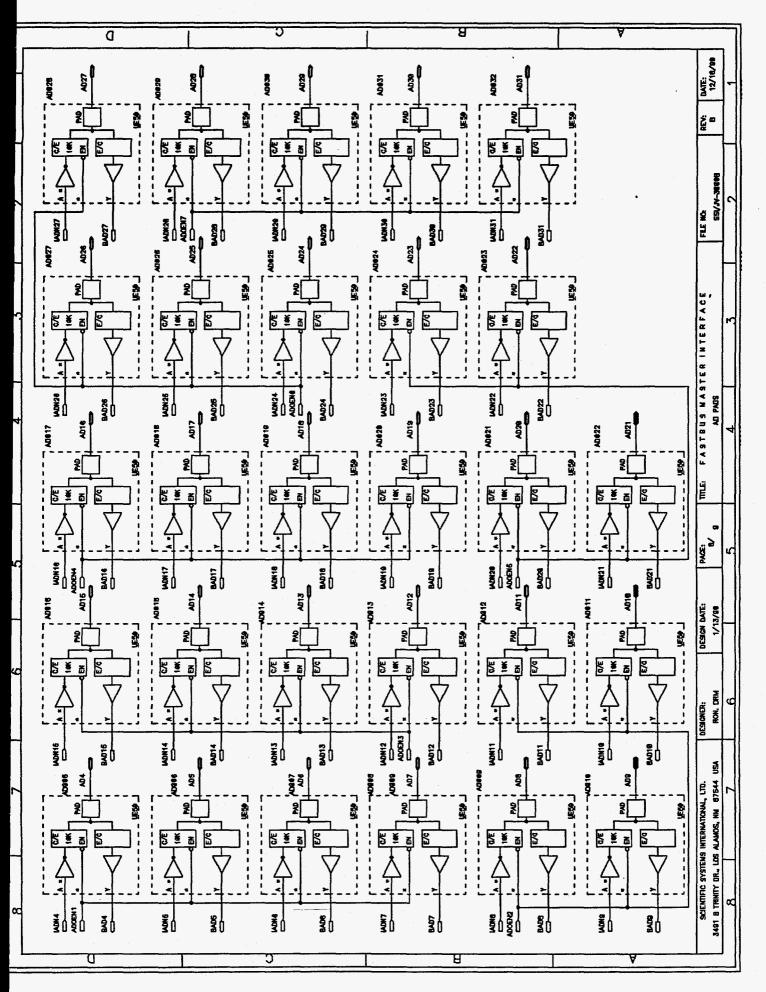

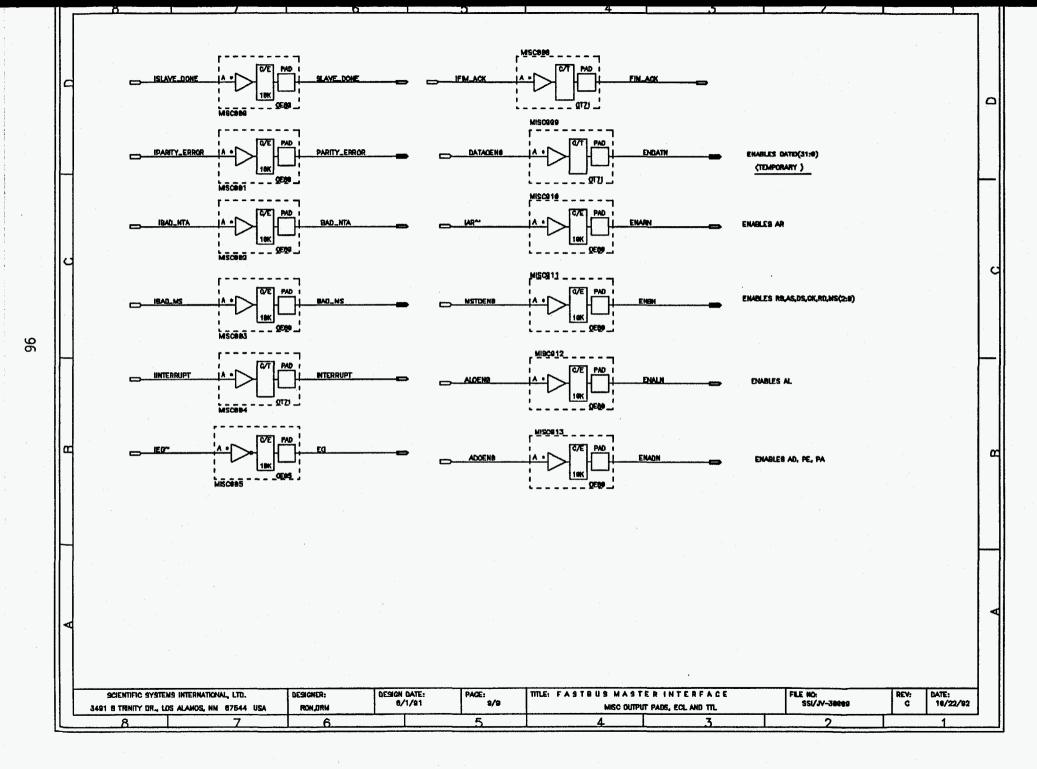

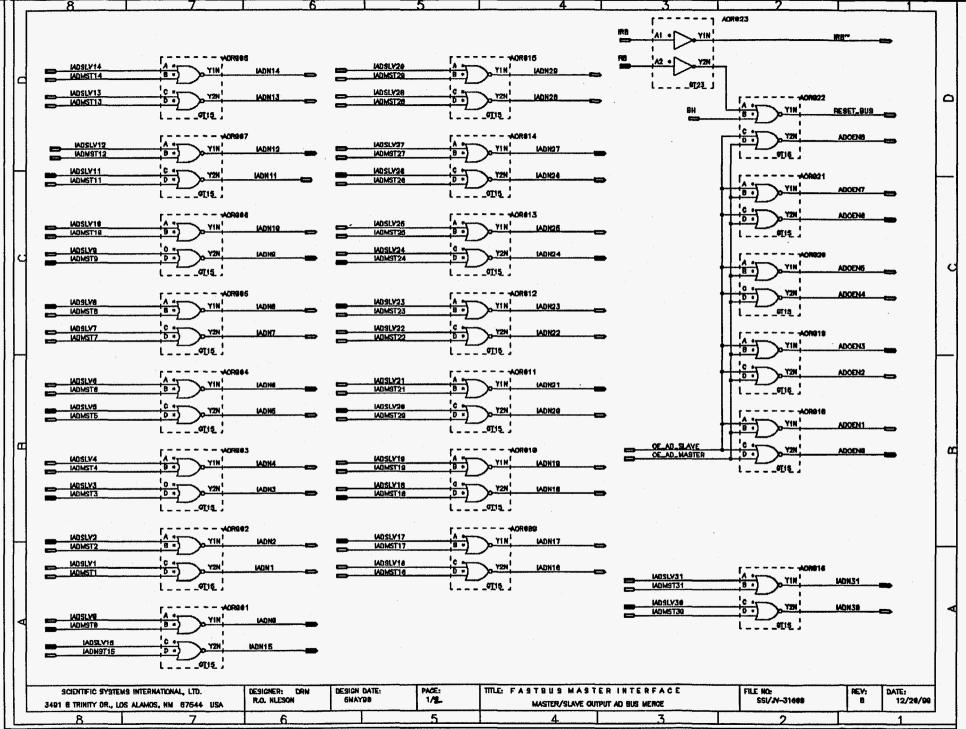

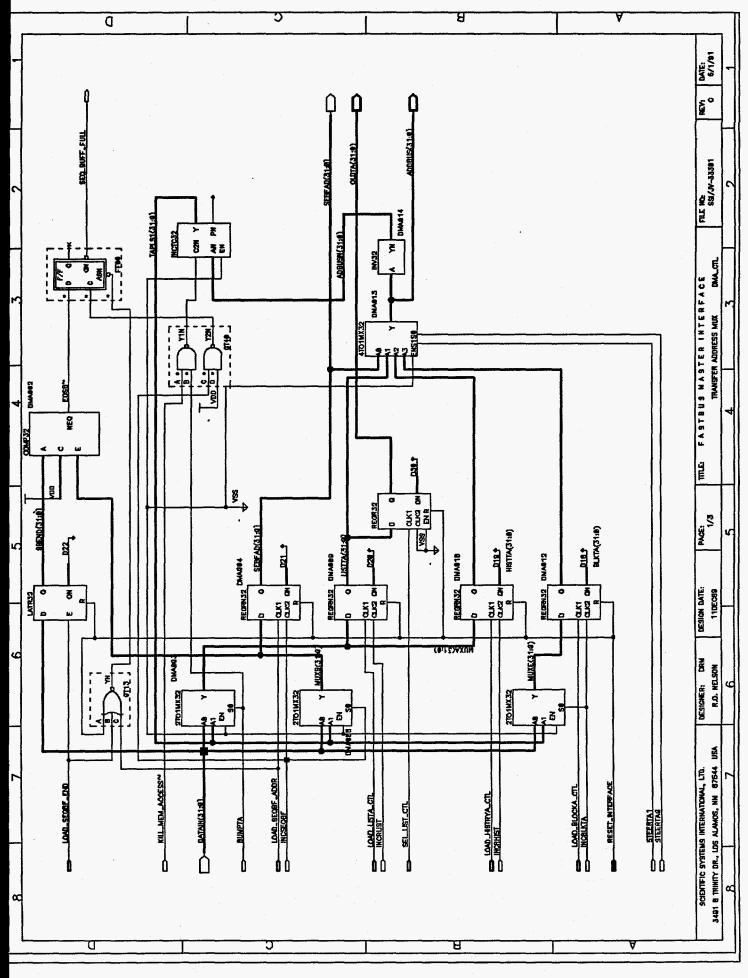

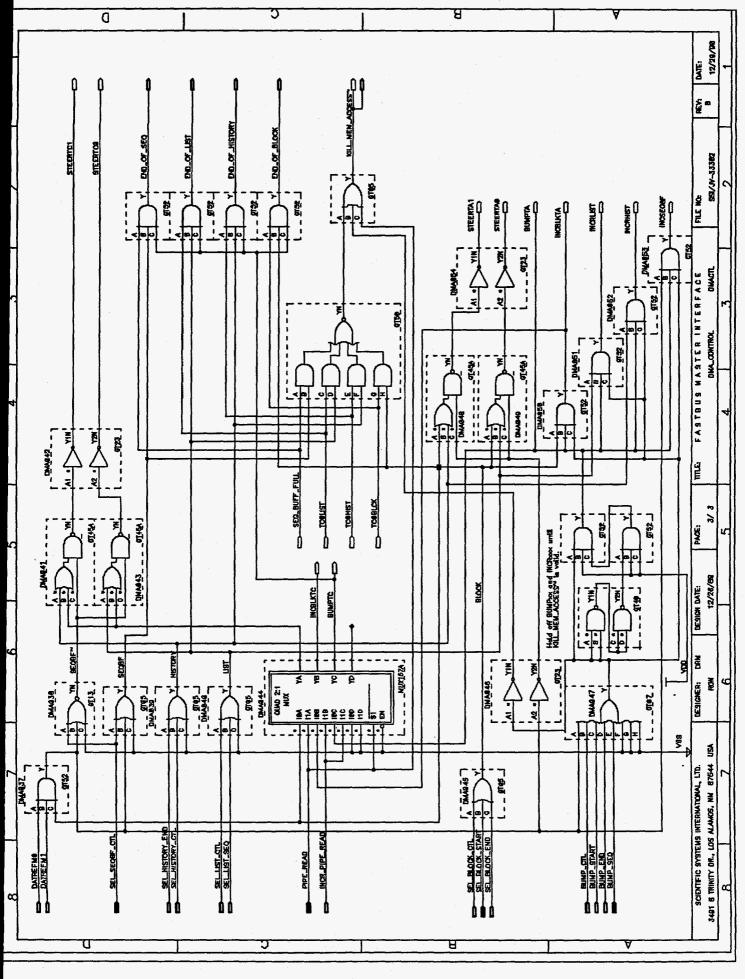

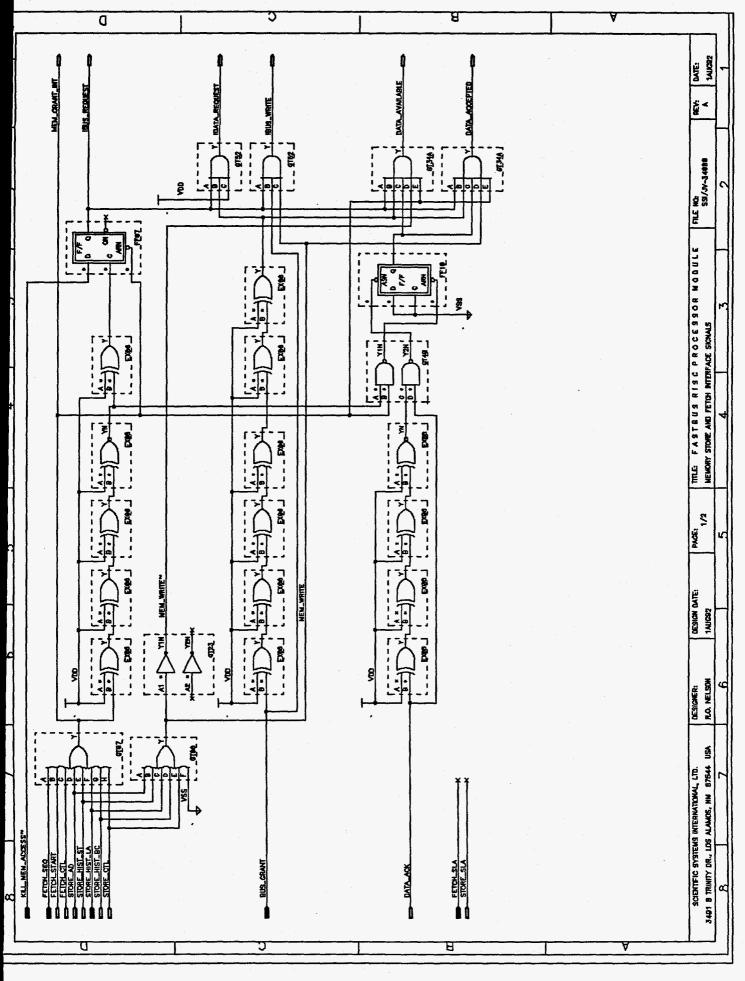

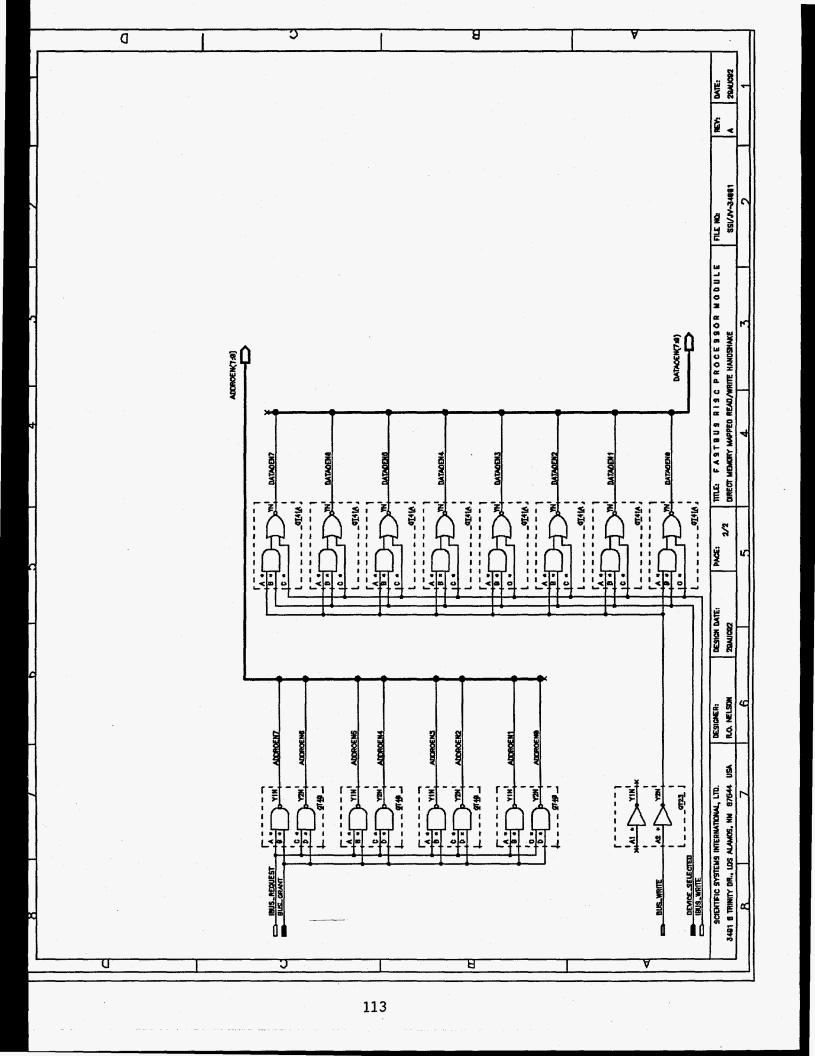

| Appendix B - FRPM Schematics-TTL Logic Interface                                                                 | 22  |  |

| Appendix C - FASTBUS Master Interface Specifications                                                             |     |  |

| Appendix D - Simulation Techniques                                                                               |     |  |

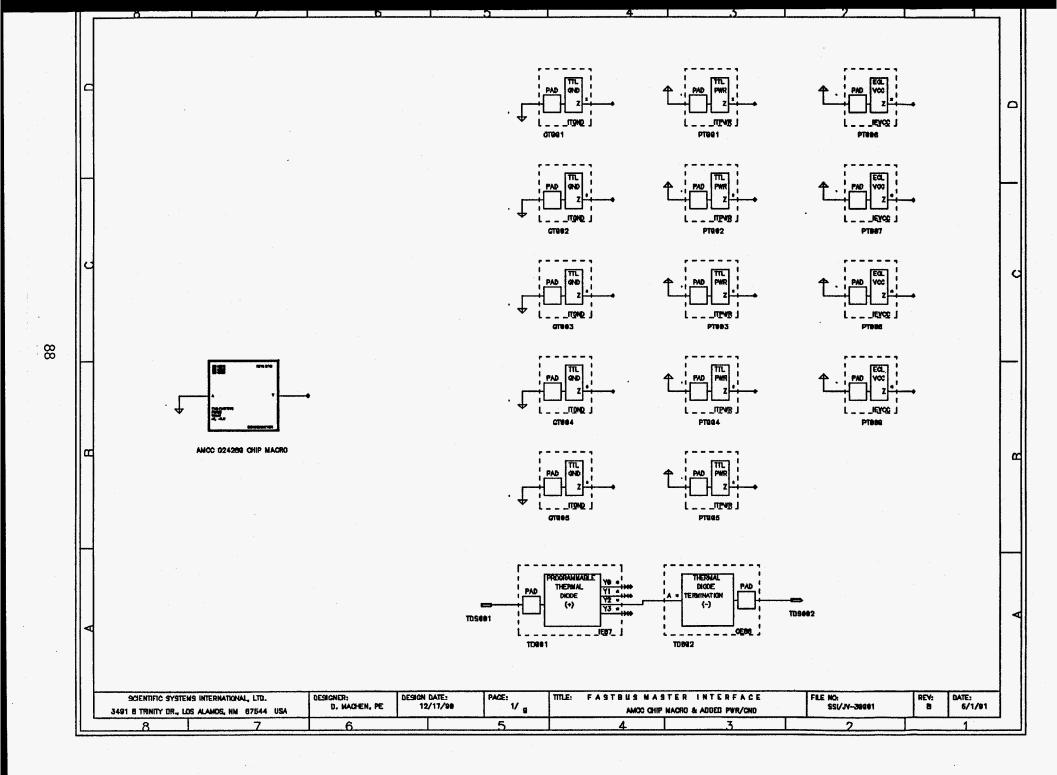

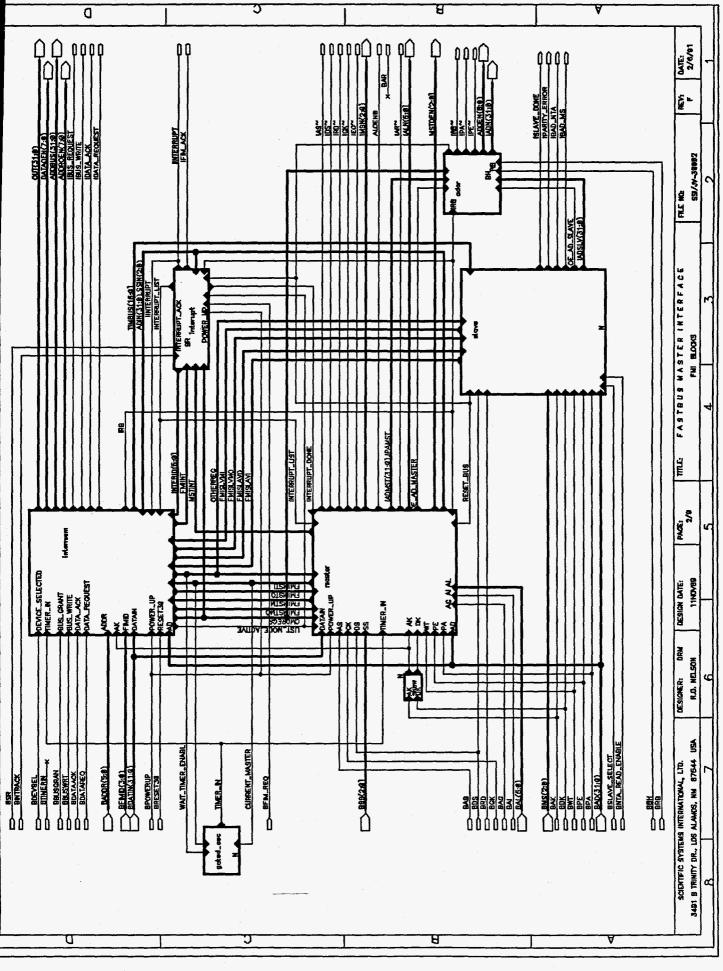

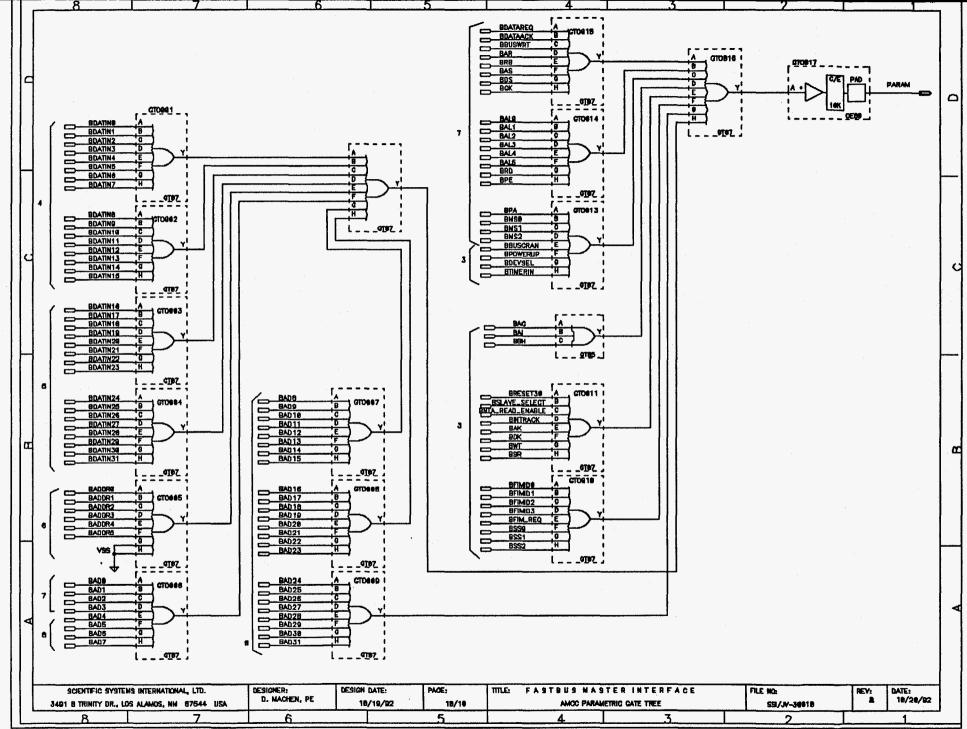

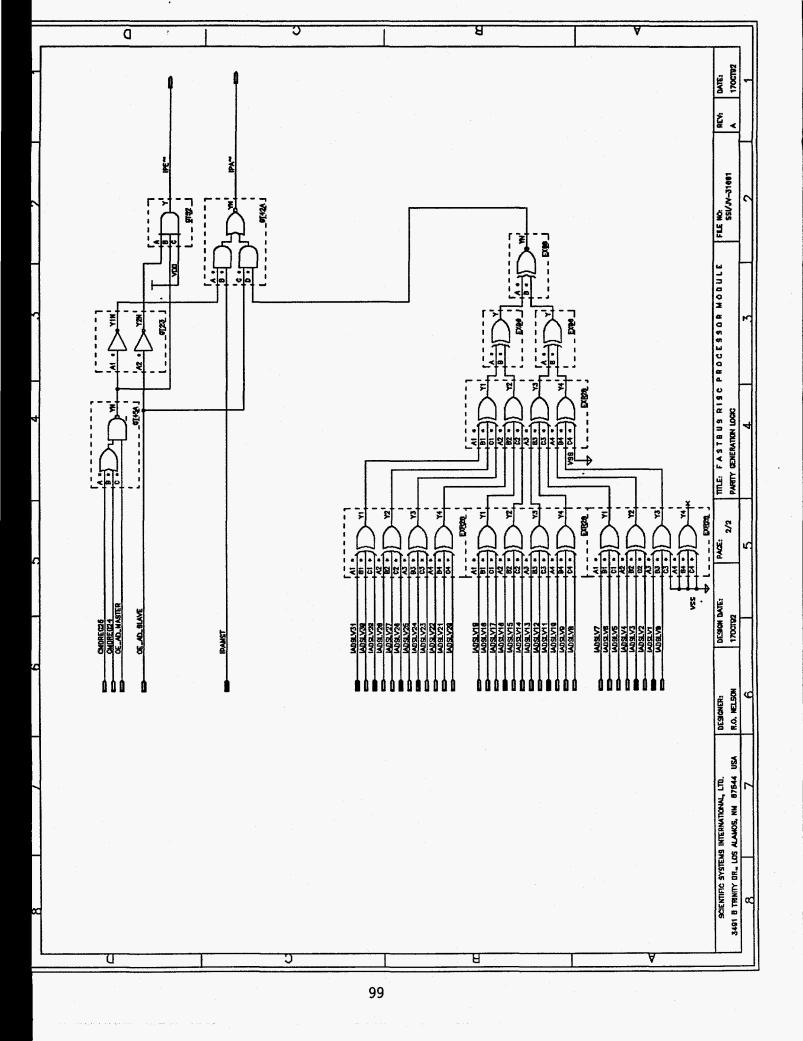

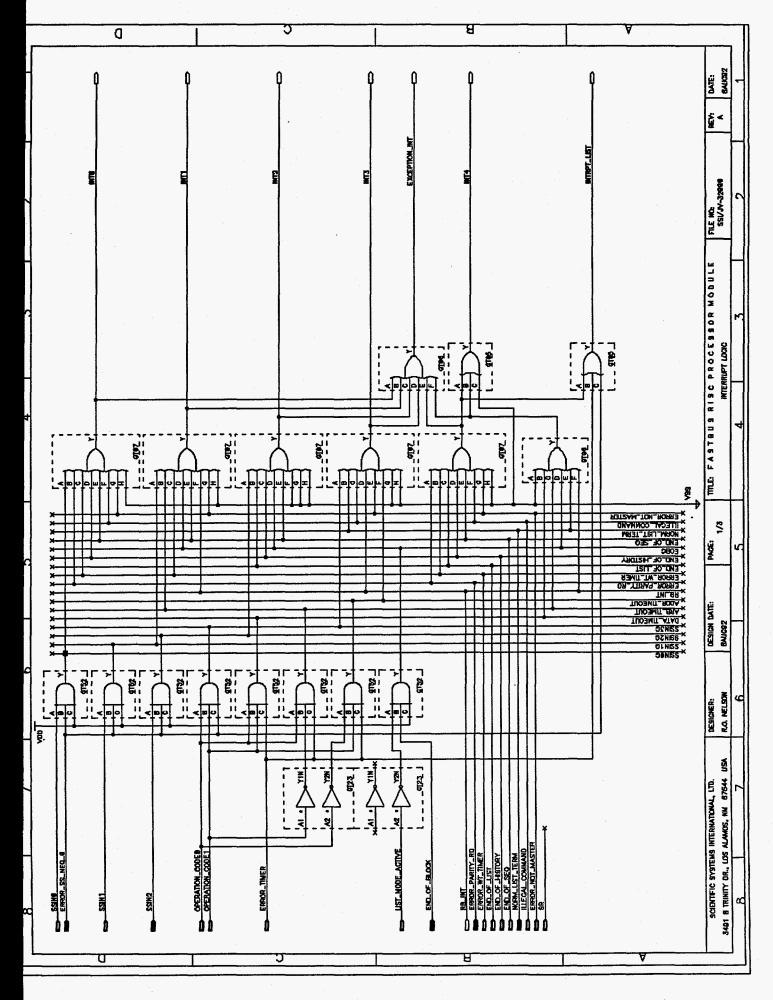

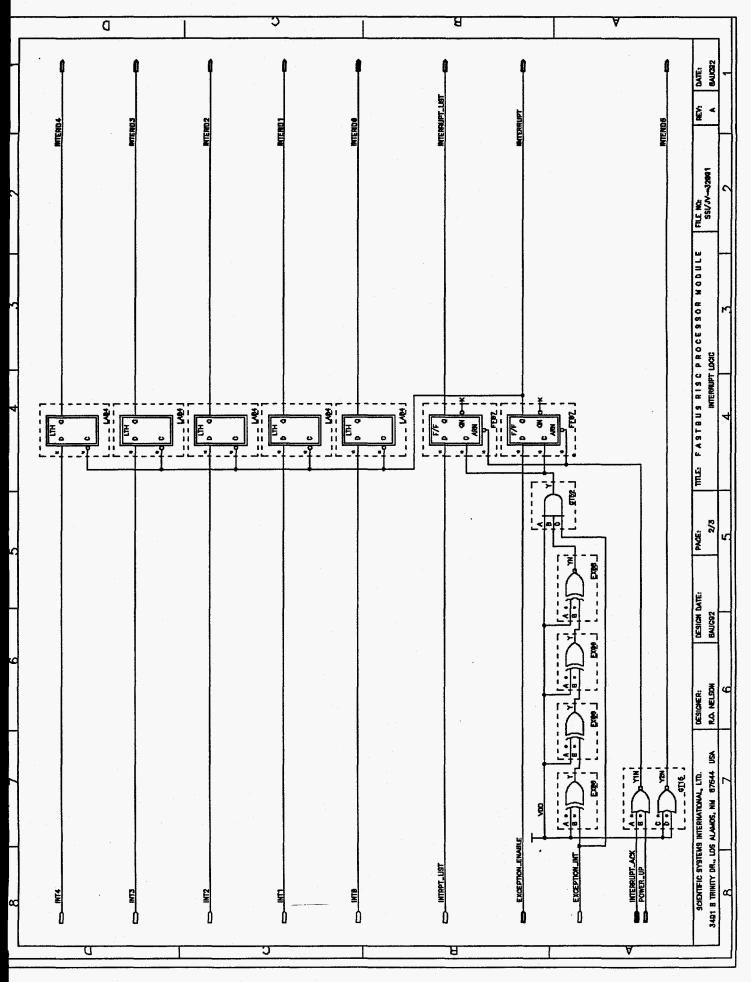

| Appendix E - FMI Schematics, AMCC BiCMOS Array                                                                   | 86  |  |

| Appendix F - FRPM Advertising Flyer                                                                              | 174 |  |

-i-

SBIR DATA

## THE RISC PROCESSOR MODULE FOR FASTBUS COMPUTATION APPLICATIONS FINAL TECHNICAL REPORT

#### 1.0 <u>Overview</u>

The FASTBUS system specification for high-energy physics and other datasystem applications anticipates the use of multiple, high-performance processor modules for data control and event reduction associated with experiments in the physical sciences. Existing processor designs will be unable to cope with the projected data-reduction and event-handling requirements of the complex experiments planned for the next generation of particle accelerators. Data-handling strategies for experimental physics are evolving from systems based upon a single central computer to those with arrays of high-speed, sophisticated, front-end processing elements. The advent of accelerators such as LEP and LHC, and beyond, is forcing the architecture of these processors toward the simpler RISC designs to enhance both speed and the software-development issue.

This report describes the prototype development of a <u>FASTBUS RISC</u> <u>Processor Module (FRPM)</u> for use as a standard processing element in FASTBUS data-acquisition systems under a Phase II SBIR grant through the U. S. Department of Energy, Division of Energy Research. The FRPM hosts a reduced instruction set computer--the SPARCengine-2 by Sun Microcomputer Systems, Inc.--capable of executing 4.2 million floating point instructions per second with a clock of up to 40 MHz.. The prototype FRPM supports a port to the FASTBUS crate segment by way of a standardlogic interface. The FRPM processor operates under a commercially available real-time operating system, and application software can be developed on workstation and mainframe computer systems.

We further cover the chronology of the Phase II work, a discussion of the objectives, and our experiences with an ASIC manufacturer in attempting to complete the fabrication of a chip implementing the FASTBUS Master Interface (FMI).

The appendices of this report contain the functional description and design details of the FRPM and of the FMI chip design.

- 1 -

SBIR DATA

#### 2.0 Chronology of the Contract

The SBIR Phase II portion of the Department of Energy contract DE-AC02-88ER8059—The RISC Processor Module for FASTBUS Computation Applications—FRPM was approved to begin on May 19, 1989; a letter to our technical contract administrator requested that effort on Phase II begin on September 1, 1989. Design effort began at that time on both the FASTBUS Master Interface (FMI) and the processor support logic. Our reevaluation of processors for the FRPM was completed in late May 1990 and development work continues with the Sun Microsystems the "SPARCengine" processor in place of the BIT chipset. Development of the FMI gate array design was delayed during our search for an alternate ASIC manufacturer, which concluded in late December 1990. We selected Applied Microcircuits Corporation (AMCC) to be the fabrication house for the FMI gate array, allowing development work to continue and an extension to the contract through December 31, 1991 was granted due to time slips associated with both the ASIC and the RISC processor. A further request for extension to December 31, 1992 was granted in order to complete the FMI gate array portion of the contract, which must be in place before the remainder of the contract work can be completed. AMCC, the ASIC prototype manufacturer, canceled the contract with SSI in late October 1993, which prompted a request for modification of the original contract and extension through December 31, 1993 to complete a new Scope of Work. Following the submission of the design package for a gatearray design in another Phase II effort (87ER80454), AMCC terminated our prototype fabrication contracts for the that array and for the FASTBUS Master Interface (FMI) design. In actual fact, AMCC unilaterally canceled our contract and refunded most of the NRE paid (\$25,400.00) without giving us an opportunity to respond. The scope of work of the contract was modified to reflect the changes forces upon us by the ASIC manufacturer's failure to carry our their part of our agreement. The modified FRPM design supports a standard-logic interface (completed in July 1993) from the SparcEngine to the FASTBUS. Control of the FRPM is The prototype FRPM was assembled accomplished by software control. and hardware/software tested during the final 3-month period of the contract. As of 12/31/93, all items in the agreed-upon modification to the contract Scope of Work were completed.

- 2 -

#### 2.1 Discussion of Objectives

Because of the unilateral action by the ASIC manufacturer (discussed in 2.0 and 2.2), we were forced to propose a modified set of objectives for the Phase II effort in December 1992. We discuss these objectives below in relation of the completed prototype FASTBUS module.

6.2.1 Develop an FRPM prototype design based on the conceptual design from the Phase I study and the effort through 12/92 in Phase II. Select the processor structure and design interface support logic to the FASTBUS system using standard logic elements for prototype module.

This modified objective was completed on 6/30/93. It reflected the fact that the processing element originally selected never made it to market and was dropped by Sun Microsystems as a potential processor for their SPARCengines. Following this, we selected the current SPARCengine as the FRPM computing element. The standard-logic interface was dictated by the cancellation of our FMI ASIC development effort by Advanced Micro Circuits Corporation in late October 1992. The modified specification and the original specification for the FRPM are contained in Appendix A.

6.2.2 Expand the behavioral model developed in Phase I for use as a operational standard in the simulation of the prototype FMI design. Develop a comprehensive set of test vectors for the FMI model.

We eliminated this objective in the modified scope of work, however the behavioral model and test vector set were actually completed by the end of the FMI design. The specification for the FMI is contained in Appendix C; the FMI design contained in Appendix E was derived from the specification and a comprehensive behavioral model, and was in the process of being tested against test vectors that had been developed with the model when the agreement was canceled.

6.2.3 Prepare the preliminary operations and testing manual for the FRPM.

The operations and testing manual was competed with the final testing of the prototype FRPM on 12/30/93 and is contained in Appendix A along with the FRPM specifications.

6.2.4 Select and evaluate potential sources of a real-time operating system software package.

The modification of the scope of work following the ASIC manufacturer cancellation of our FMI development agreement had no detrimental effect on this objective other that delaying the completion somewhat. Several suppliers of real-time operating system software were investigated during

- 3 -

SBIR DATA

the work on this objective. We were looking for a potential manufacturer who was familiar to the experimental physics community while having a product that would address the various important aspects of real-time systems. These were multitasking capability, effective scheduling of tasks to be run, context switching with fast response, software settable priority levels, semaphore signaling between tasks, and interrupt handling that was fast and deterministic. Other attributes, such as compatibility with the new POSIX standard, UNIX structure, and networking support. We found that the VxWorks product by Wind River Systems, Inc. meet these requirements and was selected for evaluation. This objective was completed with the final testing of the FRPM on 12/30/93.

6.2.5 Evaluate potential sources of application-software tools.

This objective was eliminated when we dropped the original BIT processor in favor of the SUN SPARCengine (see 2.0). The SUN development tools available would quite well fulfill this the requirements of this objective with no further investigating—we adopted the SUN tools and other commercially available tools from 3rd. party manufacturers for this part of the development.

6.2.6 Select the ASIC vendor and negotiate a design agreement to allow CAE workstation design, capture, simulation, vendor place/route, test-vector simulation, and prototype-part fabrication. Convert the expanded FMI model to an ASIC and PAL design using CAE libraries. Compare the prototype design to the behavioral model using the test vectors generated in 6.2.2.

This objective was eliminated when the ASIC manufacturer canceled our FMI development agreement, however, we had selected and negotiated the required design agreement that would allow the specified tasks; we had converted the behavioral model into an ASIC and PAL design and were in the process of testing this design when the agreement was canceled. Appendix D discusses the simulation techniques used during this part of the FRPM development.

6.2.7 Prepare printed-circuit negatives for construction of a FASTBUS RISC Processor Module in multilayer technology. Prepare two multilayer printed-wiring boards for further evaluation.

The standard-interface FRPM design was converted to multilayer printedwiring boards by 9/30.93 by a local layout company and a printed-circuit fabrication facility in Phoenix, AZ. Fabrication problems determined during check-out of the boards required a second pass through fabrication to complete this objective.

## 6.2.8 Assemble, test, and evaluate the printed-circuit prototype modules of the FRPM. Prepare the final operations and testing manual.

The multilayer printed-wiring boards were assembled and tested during the final 3 months of the Phase II effort. We were able to interface the SUN SPARCengine SBus I/O to the FRPM by was of a Motorola SBus interface chip on an SBus I/O board. The Motorola chip allows a variety of timing and I/O signal characteristics to be controlled directly by software. The FRPM, containing the SPARCengine, SBus I/O board, and the standardlogic interface was powered in a FASTBUS crate in our FASTBUS test stand. In addition, the SUN Open Boot Prom, resident in the SPARCengine, contains a full FORTH interpreter for I/O testing. With the help of FORTH code, we were able to fully test the FRPM interface and characterize the design for evaluation, while the real-time software package (VxWorks by Wind River Systems) was tested with the aid of a SUN server/workstation connected to the FRPM by an Ethernet link. Our design proved to be quite robust and required only a few changes to have a fully functioning system. Final development of the commercial version of FRPM will continue in Phase III of the contract to be funded by Scientific Systems International, Ltd.

#### 2.2 Actions by ASIC Manufacturers

Early in the Phase II effort, we had selected Raytheon Company, Semiconductor Division as the ASIC manufacturer based upon another Phase II (87ER80454) selection. Raytheon was unable to complete our 80454 agreement in December 1991 and we evaluated, and selected Applied MicroCircuits Corporation (AMCC) as the ASIC manufacturer for both Phase II ASIC developments (80454 and 80599). In late October 1992, AMCC elected to shutdown their BiCMOS product that we were using and unilaterally canceled our FMI development agreement, thus making it impossible to complete the FMI ASIC development and prompting the modification of the Phase II work in an attempt to complete a version of the FRPM.

While the semiconductor companies were initially very anxious to accept our designs, we found that internal problems with the technologies and the business outlook for ASICs in general made small business, and especially small business serving the scientific community, expendable. Our recommendation, based upon these devastating experiences, is that the physics community and small technology-businesses serving this community should be very wary of attempting to use any of the faster, more complicated integrated-circuit technologies.

SBIR DATA

- 5 -

Within the physics community, there have been some successes with CMOS custom and semicustom designs, and one example of a successful <u>small</u> ECL ASIC, but large (>20,000 gate) ECL or BiCMOS designs are rare to nonexistent. Unless the potential market is very large (e.g., 100,000 units per year fabricated), even the government does not have a good chance of being able to complete a design. We further found, in the case of Raytheon Company, that the tools available to the company were out of date and quite antiquated. Their eventual exit from the ASIC business could be a reason why their design tools were poor. In the case of AMCC, the design tools were adequate, but the company seemed to be unable to meet specifications with the BiCMOS technology and were actually moving to a bipolar ECL technology when they canceled our design agreement. In both cases, the small size of the potential FASTBUS market was a deciding factor to drop our agreements.

#### 2.3 Organization of the Report

The prototype FRPM is fully tested, evaluated, and operational and the designs for this device are contained in Appendix A (specifications and Operations Manual), Appendix B (Standard-logic TTL interface schematics), and Appendix F (advertising flyer for the FRPM distributed at the 1993 IEEE Nuclear Science Symposium). For reference, the FMI design is also contained in Appendix C (specifications), Appendix D (simulation techniques), and Appendix E (schematics for the AMCC BiCMOS array design).

## APPENDIX A

## FRPM SPECIFICATIONS

## &

## **OPERATIONS MANUAL**

-7-

SBIR DATA

#### INTERFACE DETAILS AND OPERATIONS MANUAL

#### SBus to FASTBUS MASTER INTERFACE for FRPM GENERAL

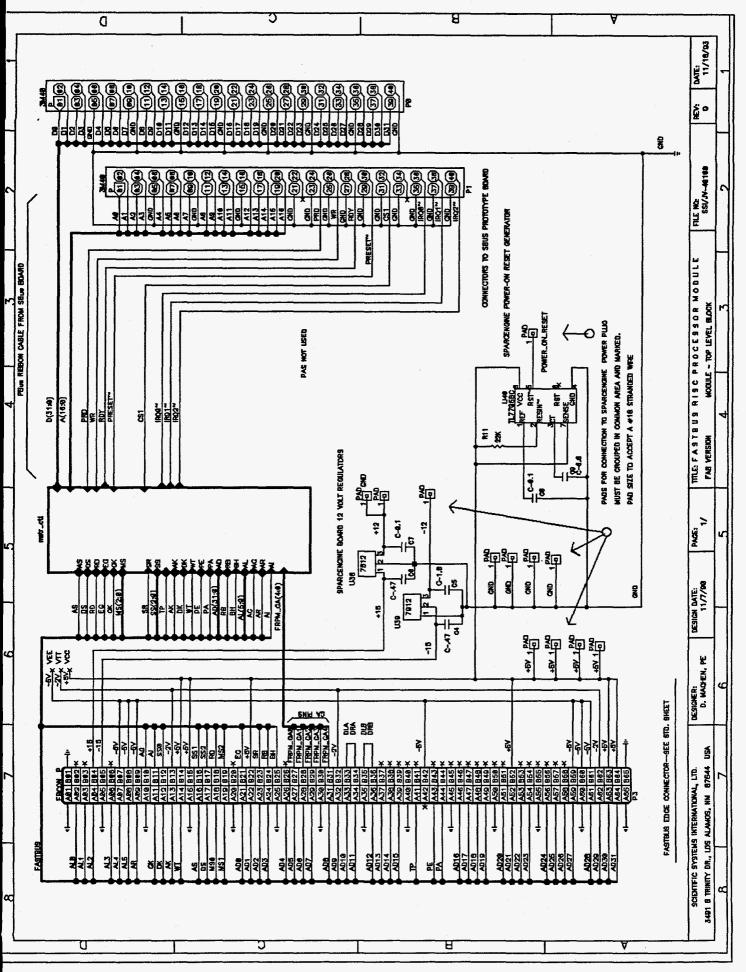

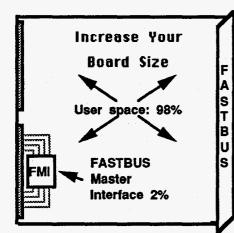

Physically, the FRPM consists of a SUN Microsystems Inc. "SPARCengine" processor mounted in the front section of a 3-wide FASTBUS module, leaving the remaining rear 1/3 of the FASTBUS board-space available for FASTBUS master interface logic. Additional hardware space may be gained by taking advantage of the 3-wide module board-space behind the SPARCengine.

Through SPARCengine connectors, the user may add temporary SCSI devices and hard or floppy disc controllers for test, diagnostic or configuration purposes. Communication with the FRPM is via the on-board SPARCengine Ethernet port to other system processors. Alternatively, limited communications with the FRPM can be accomplished via the FASTBUS port. The VxWorks Real Time Operating System (RTOS) from Wind River Systems has been ported to the FRPM to allow easier software development and operation within an experimental environment.

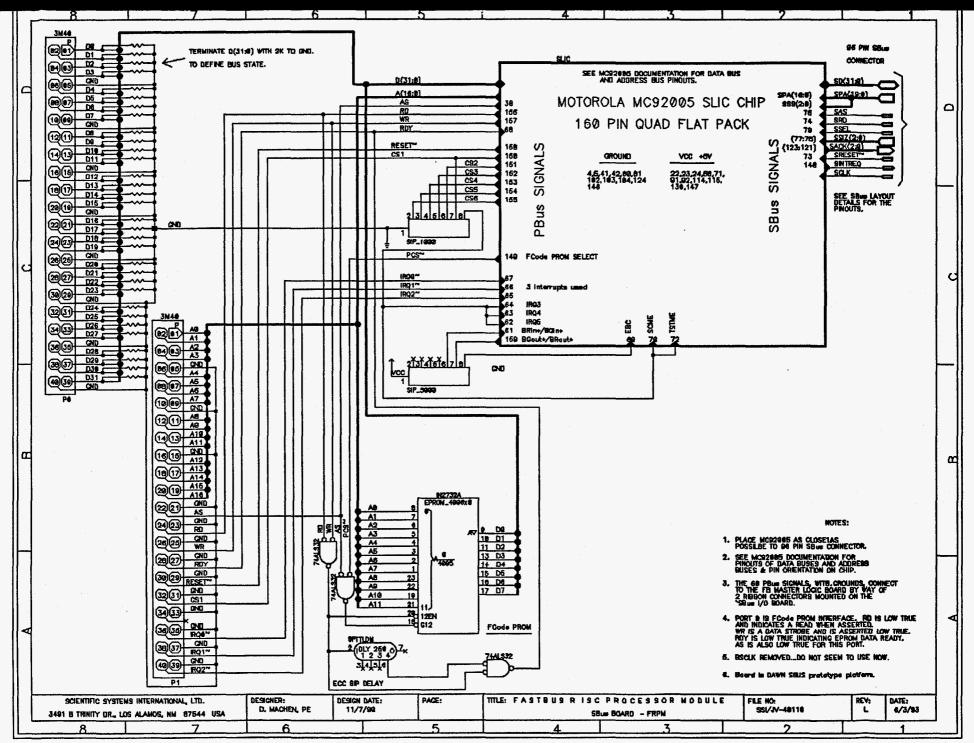

The interface from a SUN SPARCengine to the FASTBUS data system master interface hardware is accomplished by a Motorola MC92005 SBus Slave Interface Controller (SLIC) chip. The chip, which interfaces SBus to a multi-ported private bus, or PBus, is a 160 pin quad flat pack CMOS ASIC produced by Motorola Inc. and meets the Rev. B.0 specification for the SBus interface standard (IEEE P1496). The interface is presently contained on a DAWN VME Products SLIC Evaluation Board with ribbon cable connection to the FRPM board.

#### **INTERFACE PHILOSOPHY**

Interface to FASTBUS is accomplished by **primitive operations** rather that channel control operations. Arbitration, Address and Data Cycle functions are handled by separate I/O operations. All time-out functions are cpu implemented, as are the basic block transfer and pipe-line transfer operations. The interface is not autonomous; there are no buffer or list memories available other than two 16 word, 32-bit registers in the SLIC interface for program use if desired. Interrupts are used with SS  $\neq$  0, SR, AK = 1, and DK(t), if enabled. Other information is available in the interface status register. The philosophy of the interface is "simple", with all data and control available to the programmer, in contrast to a more autonomous device with little to no data/control available.

#### **INTERFACE DETAILS**

The SLIC chip provides 6 interface ports with separate selects and one FCODE prom port (required by SBus spec). Internal chip control registers are handled by the last available port; each port has a 128kbytes of address space available if needed.

A single-wide SBus interface board--containing the SLIC chip, the FCODE prom and ribbon cable connectors--will mount in a SPARCengine SBus slot. Ribbon cable from the SBus board connects 60 port 1 PBus interface signals, with commons, to the master interface logic board. The PBus connection path is kept short to minimize reflections and delay electrical problems; the SBus connection path is kept very short and is localized to the SLIC chip only. The FRPM master interface logic is controlled by port 1 only, register addresses 0-5 as described below:

| Port 1.Register 0State | us Register:                         | <u>R/W</u> | <u>R/O</u> |

|------------------------|--------------------------------------|------------|------------|

| Bits 0-3               | CSR #0, bits 0, 1, 2, 14             | *          |            |

| Bits 4-7               | CSR #9, bits 4, 5, 6, 7              | *          |            |

| Bit 8                  | I/O Reset-clears GK & Data cycle s   | tuff       | *          |

| Bit 9                  | RB-holds GK as long as RB=1          | *          |            |

| Bit 10                 | RB from FB                           |            | *          |

| Bit 11                 | BH from FB                           |            | *          |

| Bit 13                 | SS $\neq$ 0 interrupt enable/disable | * IRQ0     | )          |

| Bit 14                 | SR interrupt enable/disable          | * IRQ1     | -          |

| Bit 15                 | AK = 1/DK(t) interrupt enable/disa   | ble        | *          |

| IRQ2                   |                                      |            |            |

| Bit 16                 | SBus interrupt enable/disable        | *          |            |

| Bits 17                | Clear IRQ0 (0 clears IRQ)            |            | w/o        |

| Bit 18                 | Clear IRQ1 (1 sets IRQ for tes       | st)        | w/o        |

| Bit 19                 | Clear IRQ2 (no readback)             |            | w/o        |

| Bit 20                 | Set $PE = 1$ on data cycles          | *          |            |

| Bits 21-23             | SS(0:2)-current cycle                |            | *          |

| Bit 24                 | WT-current cycle                     |            | *          |

| Bit 25                 | AK-current cycle                     |            | *          |

| Bit 26                 | DK-current cycle                     |            | *          |

| Bit 27                 | SR-from FASTBUS                      |            | *          |

| Bit 28                 | Parity Error gated with PE on curr   | ent read   | cycle      |

|                        |                                      |            | <b>4</b> 4 |

| Bit 29                 | Slave port active                    |            | *          |

| Bit 30                 | Data cycle in progress               |            | *          |

| Bit 31                 | Master interface is FASTBUS curre    | ent maste  | r *        |

SBIR DATA

#### Port 1, Register 1--Arbitration Control:

Bits 0-7 CSR #8--Bits 0-5 = AL(0:5), Bit 6 = PRIA, Bit 7 = IAI Bit 8-13 0 Bit 15 1 = arbitrate, 0 = drop GK and current master

FASTBUS rules for arbitration hold. The FRPM must have arbitrated before executing a FB primitive operation control. GK is held until mastership is dropped. The holding register does not clear with SBUS or I/O Reset commands and must be written to clear. PRIA is priority access and IAI is assured access, as described in the FASTBUS Standard specification.

#### Port 1, Register 2--Address Cycle Control

Bits 0-2MS(0:2)Bit 3EG--1=> Port 1, Reg 3 = GA, otherwise =logicaladdressBit 4Parity odd = 1, even = 0 (testing purposes)Bit 5Bit 6AK-from FASTBUS (R/O)Bit 7Address cycle = 1, Drop AS & terminate = 0

Time-outs done by cpu as are status checks. Poll Status Register for AK, or use AK = 1 interrupt to determine if the address cycle was responded to by the FASTBUS slave addressed. The FRPM must be current master before register will accept write command.

#### Port 1. Register 3--Address Register

Bits 0 - 31 FASTBUS address 0 - 31

This register is R/W by PBus. Driver software must load Register 3 prior to executing Address Cycle Control, as last address written is held. Interpretation of Register 3 contents is based on the EG bit in Register 2. If EG is set to 1, the contents of Register 3 is a geographical address. If EG is set to 0, the contents of Register 3 is a logical address.

#### Port 1, Register 4--Data Cycle Control

| MS(0:2)                                            |

|----------------------------------------------------|

| RD                                                 |

| Parity odd = 1, Parity even = 0 (testing purposes) |

|                                                    |

| DK-from FASTBUS (R/O)                              |

| Data Cycle =1. Terminate = $0$                     |

|                                                    |

The written value of MS determines the action of bit 7. For MS=0 or 2, the data cycle will terminate when bit 7 -> 0. For MS=1 or 3, DS will be toggled when bit 7 -> 0 or 1. To complete a BT sequence MS must be set to 0 when bit 7 -> 0. DK polled in Status Register, register 4, or use DK(t) interrupt. Data time-outs are fielded by the cpu. BT and PL control by cpu. FRPM must be current master before register will accept write command.

#### Port 1, Register 5--Data Register

#### Bits 0-31 AD(0:31)

R/W by PBus, R/W by FBus. Register 5 must be loaded before a FB write operation, and must be read before the next read operation. An SBus write of REG 5 followed by an SBus read of REG 5 will read the holding register. Following a FASTBUS read cycle, an SBus REG 5 read will read the latched FASTBUS AD lines, and will do so until the next SBus write of REG 5 in preparation for a FASTBUS write operation. Thus, REGISTER 5 is made up of 2 physical registers, one to hold write data and one to accept read data. Which register to read by an SBus operation is dictated by the FASTBUS operation just completed.

#### Slave Port

The FRPM contains a minimal slave port that may be addressed only geographically to CSR space only by another FASTBUS master, or by the FRPM for <u>testing purposes</u>, for example. The slave port will accept NTA = 0, 1, 8, and 9. A bad NTA will generate SS=7, as will a parity error. MS=1 for address operations is the only code accepted, and MS=0 or 2; other MS codes will result in SS=6 returned to the controlling master.

The information returned by a CSR0 read are bits 0, 1, 2, and 14. Bits 0, 1, 2, 14, 16, 17, 18 and 30 can be written, as described in the FASTBUS Standard specification. The FRPM module ID is 10D6 (hex) contained in the upper 16 bits of the 32 bit word returned by a CSR0 read. The contents of REGISTER 1 are read with a CSR8 read is executed and CSR9-4 to 7 is read with a CSR9 read.

-12-

SBIR DATA

#### FASTBUS RISC PROCESSOR MODULE SPECIFICATIONS AND FUNCTIONAL REQUIRMENTS

#### ORIGINAL DOCUMENTATION PRIOR TO MODIFICATION OF SCOPE-OF-WORK

#### 1. Introduction

The FASTBUS RISC Processor Module (FRPM) shall be a single or double width FASTBUS module supporting a RISC processor architecture. The Module shall also support conventional input-output (I/O) devices including ethernet for local area networks (LAN), RS-232 ports for data terminals, small computer system interface (SCSI) ports for disk storage, and several front-panel signals for general input and output control purposes.

The FRPM shall also be both a FASTBUS master and slave device, and control two FASTBUS I/O ports. One shall connect to the crate segment and the other to the auxiliary connector port.

#### 1.1. Scope

This document identifies the functional capabilities and interface features of the FRPM. These requirements, resulting from studies performed during the Phase I research for the FASTBUS RISC Processor Module, represent compromises made between the set of all desirable features for FASTBUS processor modules, and the set of feasible implementations. While these requirements are not inflexible, they are established only after thorough research to direct and limit subsequent design and implementation.

#### 1.2. Functional Summary

#### 1.2.1. Processor

The RISC processor shall be a 32-bit ECL device. It shall provide full arithmetic operations for integer and floating point operations using an internal capability or an external floating point coprocessor. It shall be compatible with a memory mapped architecture for I/O and I/O control. The processor shall provide external interrupts, and shall expedite rapid context switching through use of many switchable internal register files. Performance shall exceed 40 MIPS on a scale where a VAX 11/780<sup>1</sup> is rated as a 1 MIP machine.

-13-

<sup>&</sup>lt;sup>1</sup> Digital Equipment Corporation

#### 1.2.2. FASTBUS Master Interface

The FASTBUS Master Interface (FMI) shall implement a bus and a processor interface. The bus interface shall allow direct connection to the FASTBUS crate segment, and shall support all the protocol defined by IEEE 960 for master devices. The processor interface shall provide a single 64-bit path to the FMI that may be used in two modes. Seven other ancillary signals shall be provided to select the interface operation and provide timing controls. For the first mode of control, the interface path shall enable the processor to control each operation executed by the FMI. In this slaved mode, the FMI is totally dependent on the processor for control. The processor shall optionally supply data embedded in the control stream. For the second mode for control of the FMI, the interface path allows the FMI to fetch equivalent control and data information from a dedicated memory through a direct memory access (DMA) controller built into the FMI. The latter mode of operation permits the FMI to operate autonomously once triggered, and provides a high performance FASTBUS sequencer controlled by predefined lists of primitive FASTBUS operations stored in shared processor memory. Both modes shall use the list sequencer to deposit input data in processor memory.

#### 1.3. Assumptions and Constraints

The address space for FASTBUS is potentially so large that the FRPM shall not attempt to map FASTBUS address space into the processor address space. An arbitrary FASTBUS module may contain  $2^{32}$  addresses for each of data space and control space.

The memory and memory interface architecture shall not prevent the FRPM from executing at the maximum speed permitted by the FASTBUS specification, IEEE 960. Therefore, a built-in list sequencer shall be provided within the FMI to achieve satisfactory performance. Furthermore, the associated memory architecture should be optimized to minimize contention between the processor and the DMA.

All addresses generated by the FRPM shall be absolute addresses referencing physical memory. No address translation shall be provided.

#### 2. Applicable Documents

- 2.1. FASTBUS Documents

- 2.1.1. Hardware

IEEE Standard FASTBUS Modular High-Speed Data Acquisition and Control System, ANSI/IEEE Std 960-1986.

- 2.1.2. Software FASTBUS Standard Routines, U. S. NIM Committee, May 1988.

- 2.2. FMI Requirements Specification

"FASTBUS Master Interface Specification and Functional Requirements," Appendix B of this document.

- 3. Functional Requirements

- 3.1. Processor Requirements

3.1.1. RISC Engine

- 3.1.1.1. Architecture

- 3.1.1.1.1. Harvard

To relieve congestion at the memory interface, processors supporting the Harvard architecture (separate data and instruction memories) shall be preferred.

3.1.1.1.2. Instruction/Data Cache

To reduce the number of memory fetches and optimize processor performance, processors supporting on-chip caching shall be preferred.

The FRPM shall implement memory with high-speed static RAM, and shall not implement any on-board cache.

#### 3.1.1.2. Integer Operations

Integer operations shall be an integral part of the RISC processor or shall be available as a standard option within the family of microprocessor support chips. Addition, subtraction, multiplication, and division shall be supported. Multiplication shall produce a 64-bit product. Division shall use a 32-bit divisor and a 64-bit dividend to produce a 32-bit quotient.

#### 3.1.1.3. Floating Point Operations

Floating point operations shall be an integral part of the RISC processor or shall be available as a standard option within the family of microprocessor support chips. Both 32-bit and 64-bit floating point operands shall be supported for addition, subtraction, multiplication, and division operations.

#### 3.1.1.4. Optional Coprocessors

The processor shall support an optional application specific coprocessor. This coprocessor may effectively extend the instruction set of the processor to include functions that are optimized for the application.

#### 3.1.1.5. Register Sets

The processor shall have a minimum of 32 general purpose registers. Processors with larger numbers of registers and with register management algorithms optimized for rapid context switching and subroutining are preferred.

#### 3.1.1.6. Interrupts

The processor or floating point coprocessor shall generate internal interrupts for errors including integer overflow, divide by zero, exponent overflow, and exponent underflow.

Two external interrupts shall be connected from the front panel to the processor, and three interrupts shall be connected from the FMI to the processor.

#### 3.1.1.7. Performance

#### 3.1.1.7.1. Absolute

Performance shall exceed 40 MIPS on a scale where a VAX 11/780 is rated as a 1 MIPS machine.

#### 3.1.1.7.2. Interrupt Response Time

The processor shall response to an interrupt in  $\leq 10 \ \mu s$  if the processor is not currently active at the same or higher interrupt level.

#### 3.1.1.7.3. Growth Path The processor shall be selected from a family of processors that has planned growth plan which includes a 100 MIPS ECL processor.

#### 3.1.2. Memory

#### 3.1.2.1. Architecture

3.1.2.1.1. Memory Size

The FRPM program memory shall contain two megabytes of static random access semiconductor storage (SRAM). All memory shall be directly addressable from the controlling processor.

#### 3.1.2.1.2. Expansion

The program memory shall be expandable to at least four megabytes, with no limitations on the direct addressability of the memory.

3.1.2.1.3. Word Size

The program memory word size shall be 32 bits, or greater. Additional data-path width shall be in increments of 8 bits.

3.1.2.1.4. Configuration

The program memory configuration is dictated by the semiconductor industry, however, no limitation shall be placed on the number of memory cells contained within a single memory integrated circuit. Basic configurations of 256 K x 1, 1 M x 1, etc., are equally acceptable.

#### 3.1.2.2. Technology

The process technology used for the SRAM devices shall match that of the controlling processor in speed and signaling levels.

#### 3.1.2.3. Access Time

The access time of the program memory shall match the cycle time of the controlling processor, within the limits of available SRAM devices.

#### 3.1.2.4. Management

Memory management shall be limited to address-bounds checking for application programs. The controlling processor shall be signaled on detection of an out-of-bounds condition during memory accesses.

#### 3.1.2.5. FMI List-Sequencer Memory

The FMI list-sequencer memory shall be a subset of the FRPM program memory containing at least 1/2 Mbyte storage capacity. The memory section shall be accessed by both the controlling processor and the FASTBUS interface.

There shall be a list-sequencer memory associated with each FMI.

#### 3.1.2.6. Table Memory

The table, or calibration data-base memory, shall consist of dynamic random access semiconductor memory devices (DRAM) configured as 1 M x 1 or 4 M x 1 integrated circuits. The memory size shall be 1 megabyte, or greater, and the word size shall be identical to that of the program memory.

#### 3.1.2.7. Multiple Access

The program memory, and list-sequencer memories associated with each FMI, shall be multiply accessed. The processor address space shall contain all memory in a contiguous block; the processor shall be allowed read/write access to the list-sequencer memory for FMI control code loading and data transfer while the FMI data channel controller shall be allowed read/write access of the list-sequencer memory. Control of the multiple port access to the contiguous block of memory shall be under control of a separate data-channel interface.

#### 3.2. Interface Requirements

#### 3.2.1. SCSI

The FRPM shall provide a Small Computer System interface (SCSI) to service optional disk drives and other peripheral devices. This interface shall provide direct memory access between the external SCSI devices and the FRPM memory.

#### 3.2.2. Ethernet

The FRPM shall provide an ethernet interface to service interprocessor communication. This interface shall provide direct memory access between the external ethernet nodes and the FRPM memory.

#### 3.2.3. RS-232

The FRPM shall provide two RS-232 interfaces to service data terminals and/or inter-processor communication. This interface shall provide memory-mapped control and data transfer between the processor and the RS-232 controller integrated circuit.

#### 3.2.4. Timers

For support of real-time operations, the FRPM shall provide four 32bit timers with time increments 1 ms and 100ns.

#### 3.2.5. Memory Data Channel Interface

A separate memory data channel controller shall provide contention resolution during accesses to the program/list-sequencer memory to allow both the controlling processor and FMI controller access to memory. The data channel controller shall be independent of the controlling processor and the FMI controllers.

#### 3.2.6. FMI for Crate and Cable Segments

The FRPM shall control two FASTBUS I/O ports. One shall connect to the crate segment and the other to the auxiliary connector. With an auxiliary adapter card, the latter port may be connected to a cable segment or a custom bus through a protocol converter. Program control for each FASTBUS port shall be possible through category B and category I FASTBUS standard routines.

The FASTBUS Master Interface (FMI) shall drive each FASTBUS port. The FMI enables the processor to initiate arbitration, address, and data cycles, as well as other control functions. In addition the processor may initiate a series of FASTBUS operations and control functions, directed by a user-specified list contained in the listsequencer memory.

#### 3.2.7. General Purpose Input and Output Signals

A set of eight differential general purpose input signals and eight differential general purpose output signals shall be available outside the FRPM module. The voltage level shall be compatible with 10K ECL technology. The output signals shall be able to drive a 25 ohm load continuously.

#### 3.3. Special Requirements

#### 3.3.1. Form Factor

The FRPM module shall be a single or a double width FASTBUS module, as specified in IEEE-960.

#### 3.3.2. Front Panel Indicators

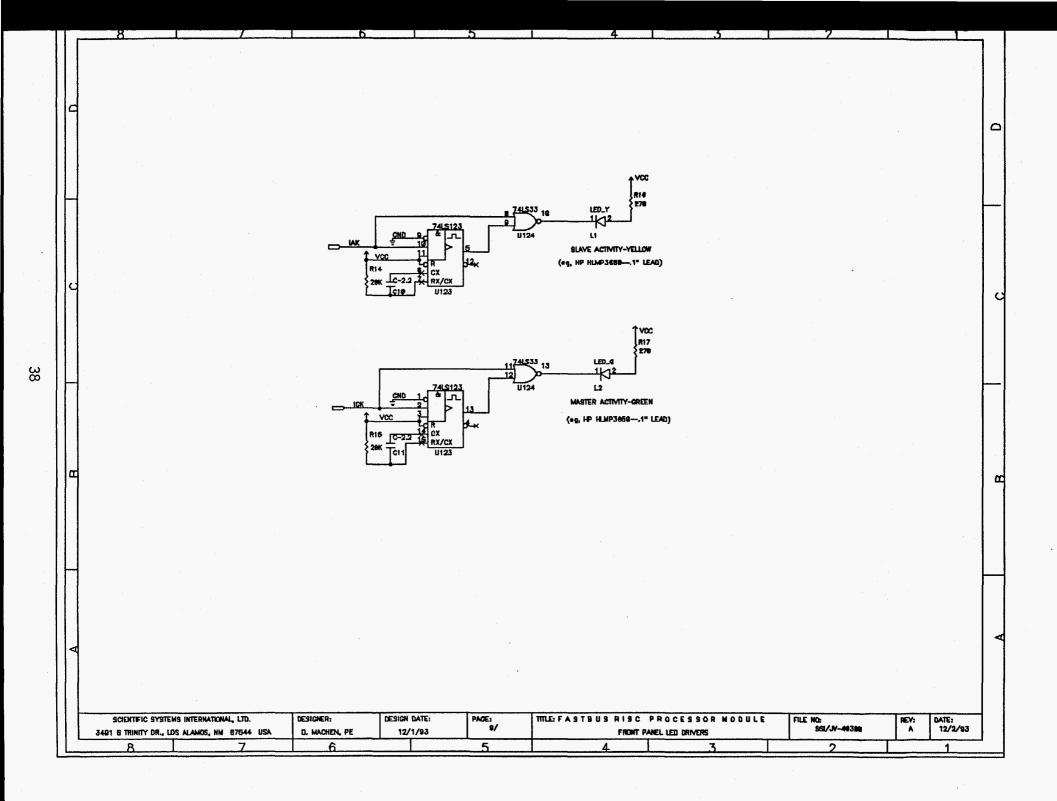

The FRPM shall meet the specifications of IEEE-960 for each master/slave front panel indicators. In addition, there shall be a red LED indicating the operating status of the controlling processor.

#### 3.3.3. Front Panel Connectors

The FRPM front panel shall contain a multi-pin connector for the general purpose input and output signals specified in Section 3.2.7.

#### 3.3.4. Operating Systems

#### 3.3.4.1. Real-time

The operating system shall support real-time functions.

Interrupts servicer shall allow interrupts from the FMIs or from the front panel to trigger tasks executing on the processor. The time during which interrupts are inhibited during the interrupt routine shall be 100 us.

The operating system shall support external timers for task scheduling.

#### 3.3.4.2. Multi-tasking

The operating system shall support the creation, termination, and sequential execution of multiple tasks. A task shall be able to suspend its execution or the execution of another task until an I/O event occurs, a timer event occurs, or until resumed by another task. A task shall be able to terminate itself or another task. A task shall be able to create a new task.

#### 3.3.4.3. Input/Output

The operating system shall support standard I/O devices including ethernet with TCP/IP, SCSI for disks, and RS-232 for terminals.

#### 3.3.4.4. Commercial Availability

The operating system for the FRPM shall be sold and supported by a commercial vendor in business for two or more years.

#### 3.3.5. Development Tools

#### 3.3.5.1. Compilers

Compilers for assembly language, Fortran, and C shall be available to generate code for the target processor. These software packages may either run on a support computer based upon a different processor family (cross compiler) or upon the same processor family (native compiler). Each compiler shall translate source files to object files.

#### 3.3.5.2. Libraries

Software libraries shall be available to interface with operating systems functions and mathematical operations.

#### 3.3.5.3. Linkers

Linkers shall be available to combine object files and libraries into executable images. The executable images shall be downlineloadable into the target processor.

#### 3.3.5.4. Debuggers

Symbolic source code debuggers shall be available. The debuggers shall allow interactive placement of breakpoints and interactive variable examination and modification. The debugger may run on the support computer or on the target processor itself.

#### 3.3.5.5. Workstations

A processor that is used as the computer engine for a commercial workstation shall be preferred if the workstation can be used for some code development and documentation generation.

#### 3.3.5.6. Commercial Availability

The development tools for the FRPM shall be sold and supported by a commercial vendor in business for two or more years.

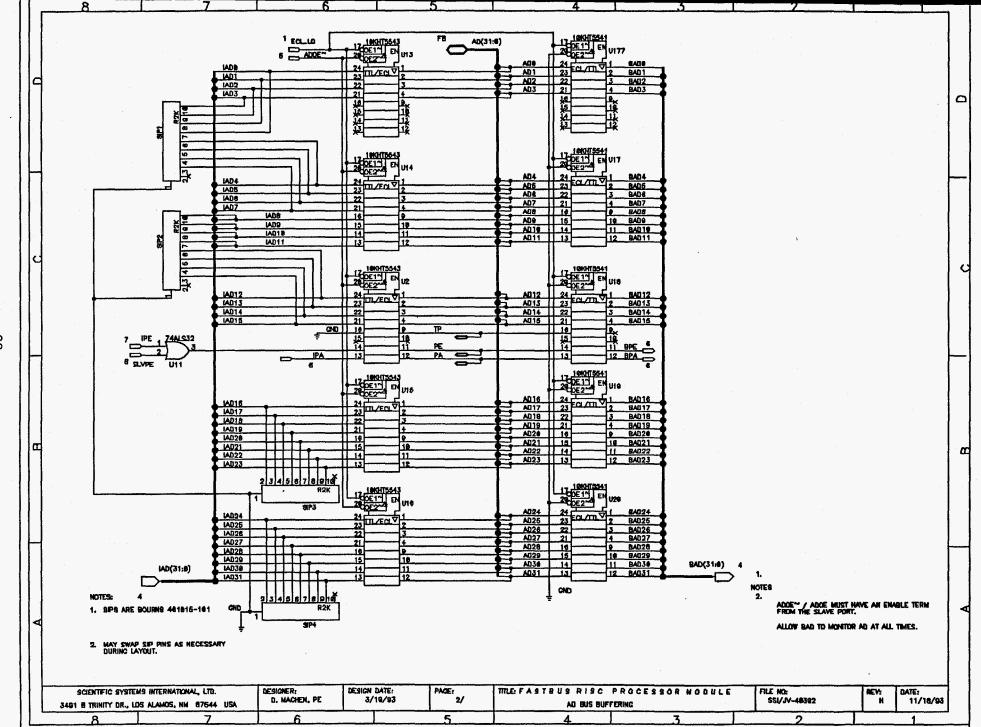

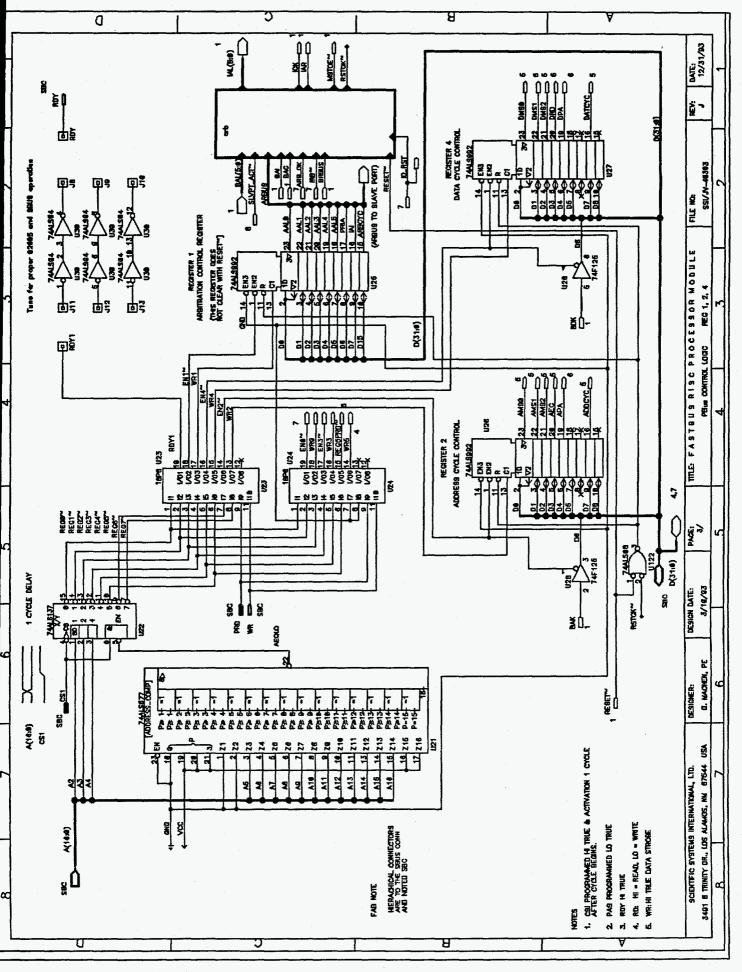

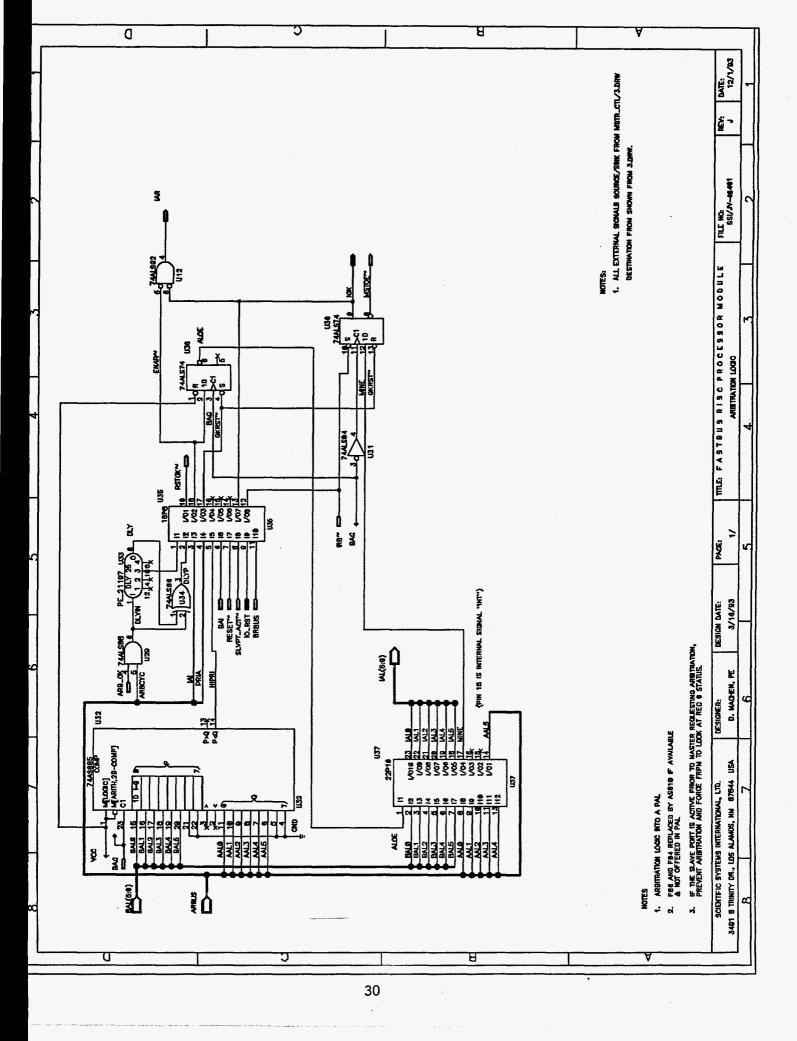

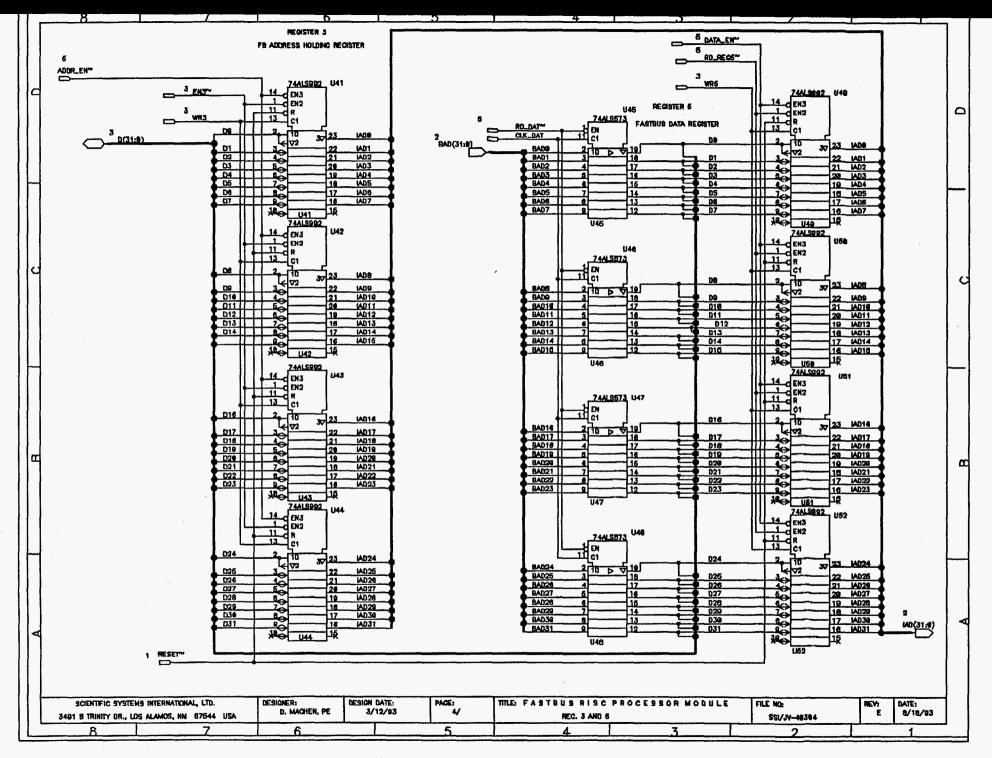

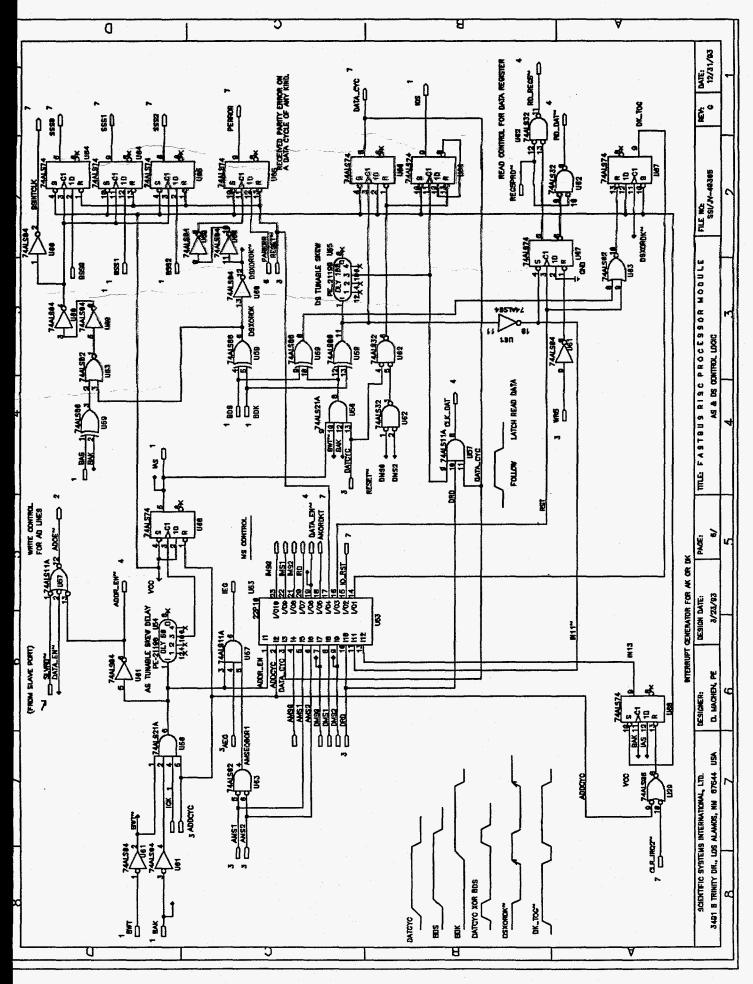

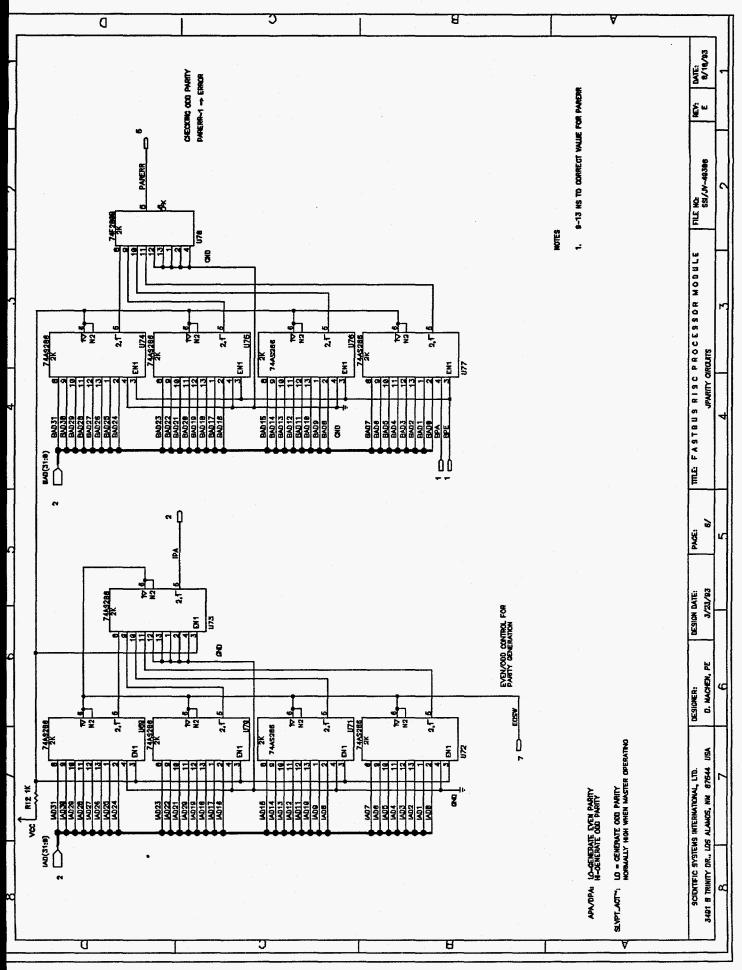

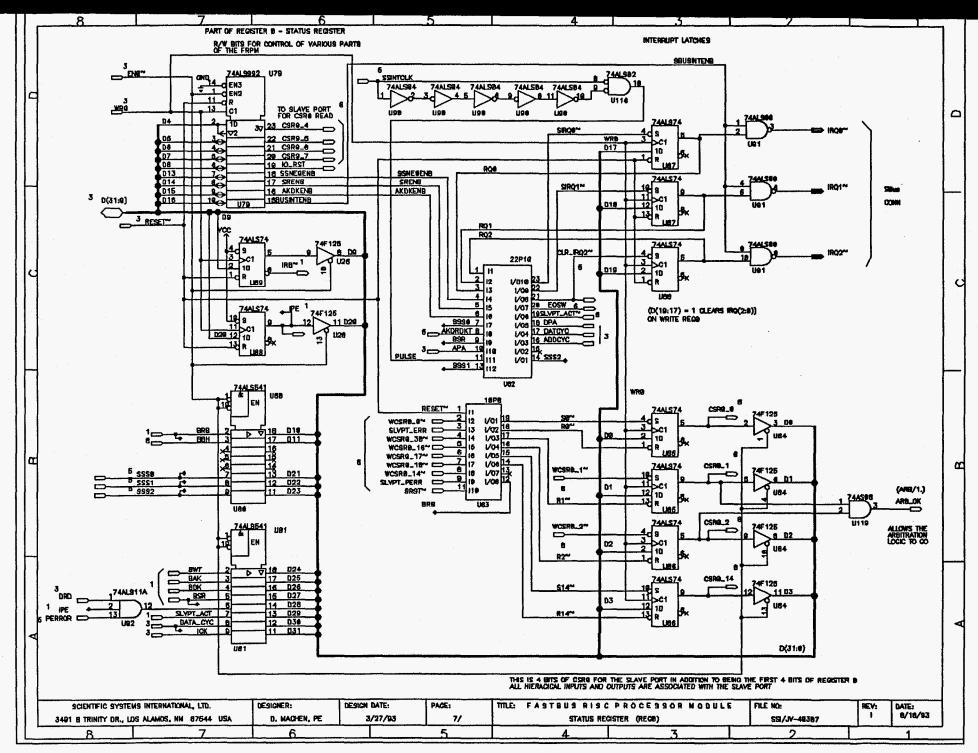

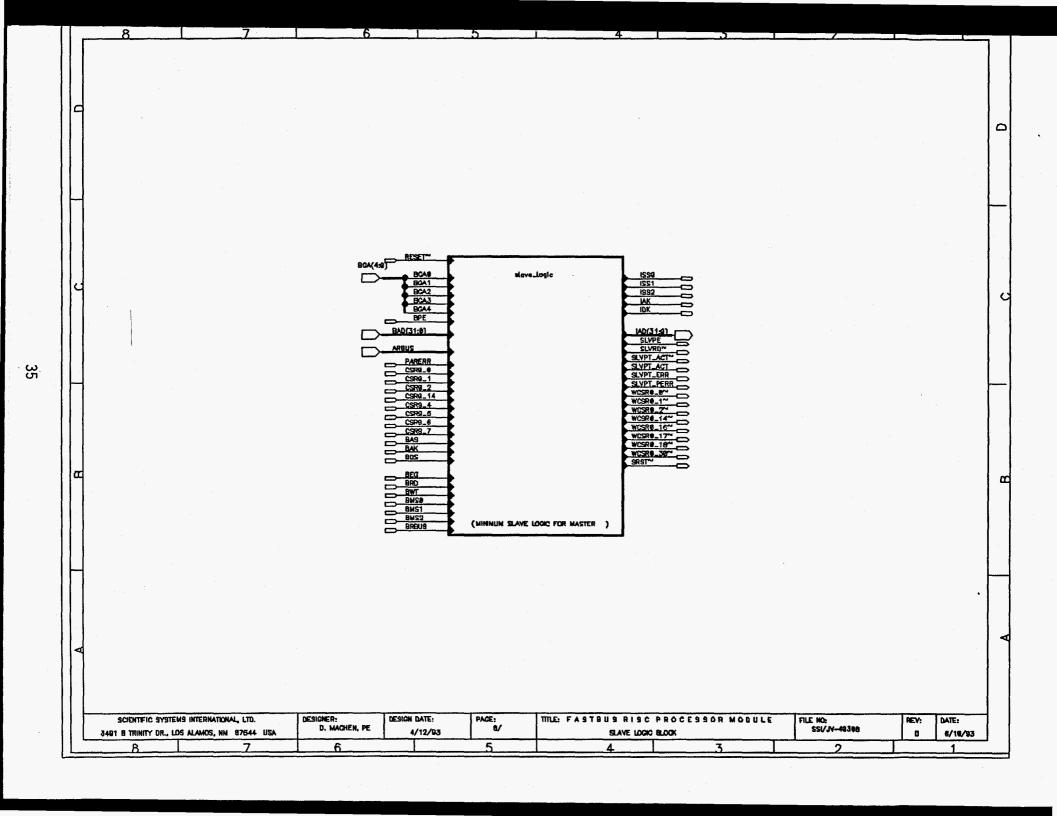

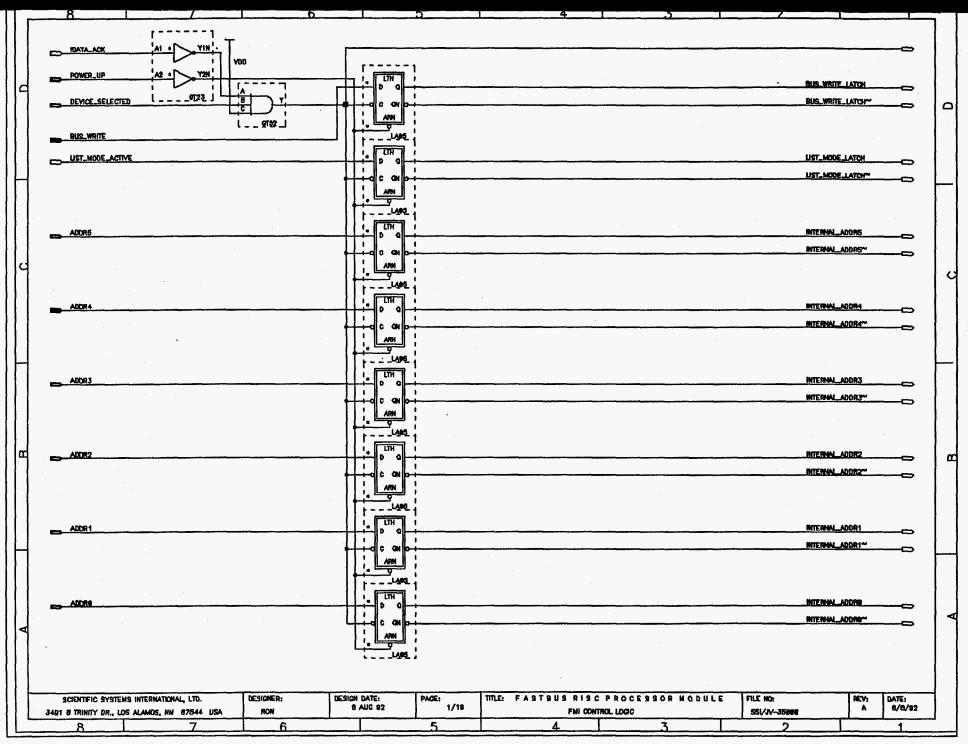

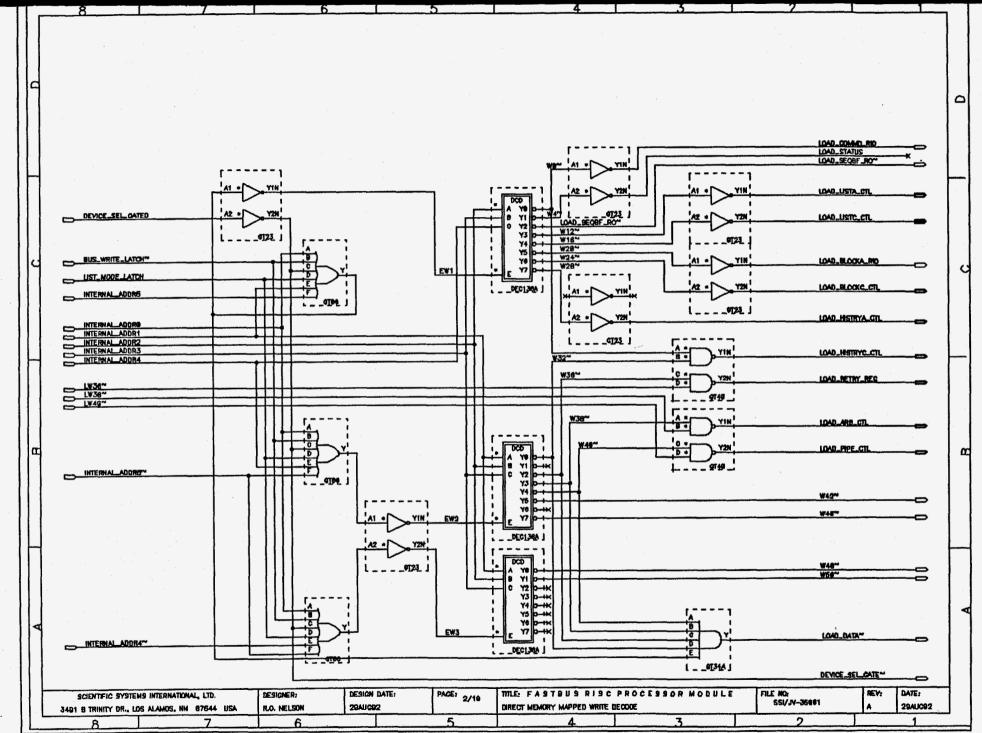

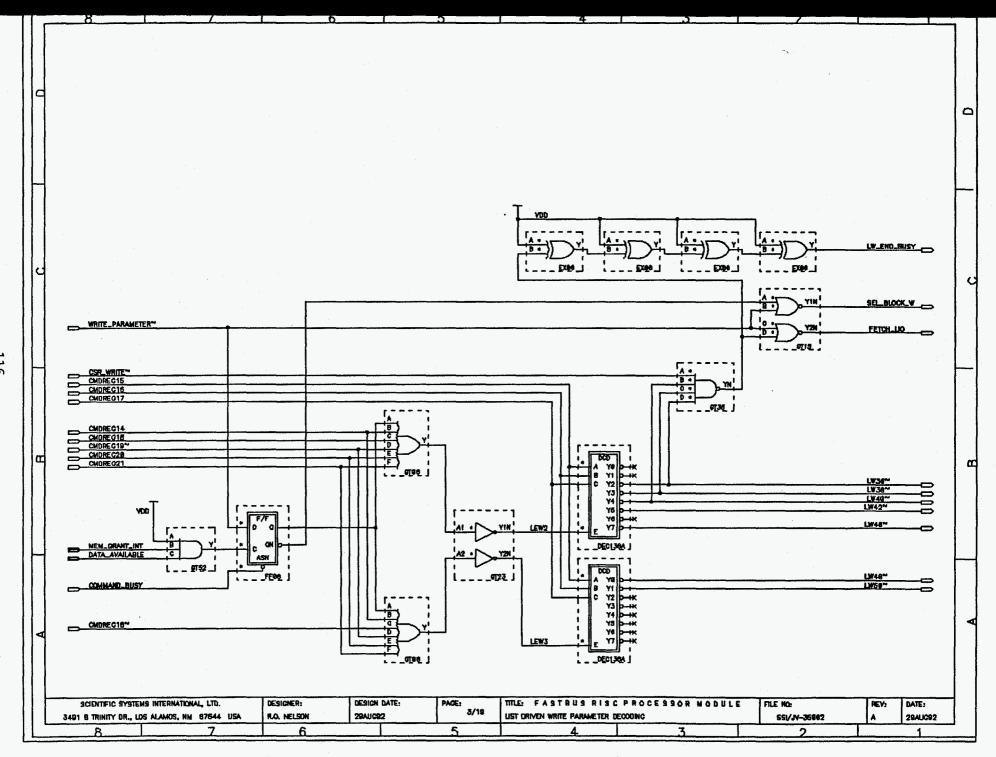

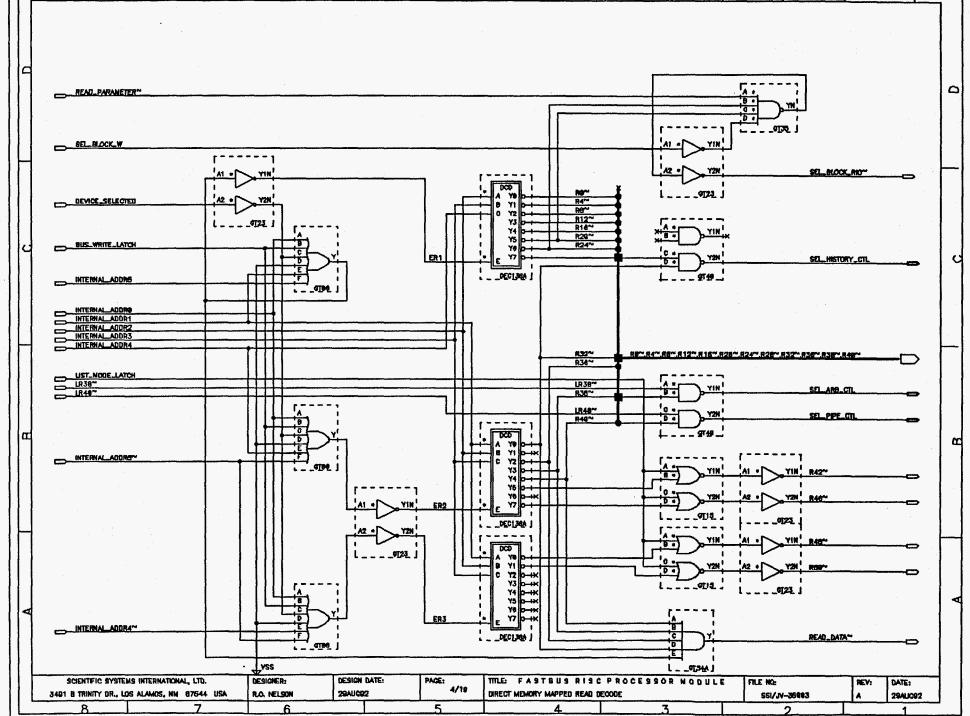

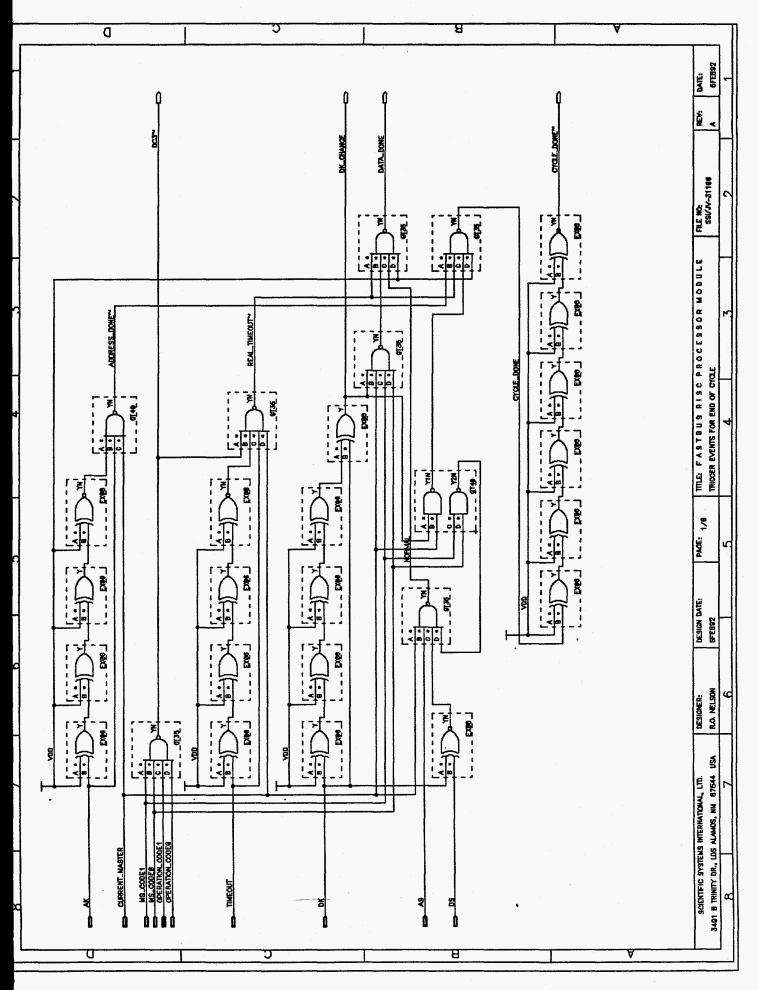

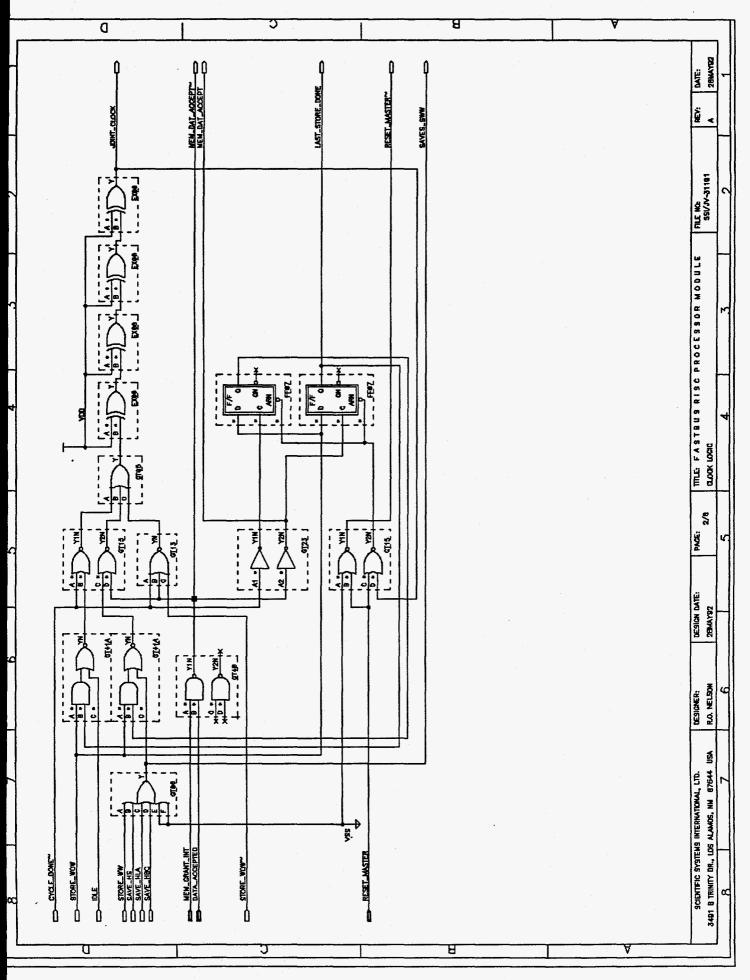

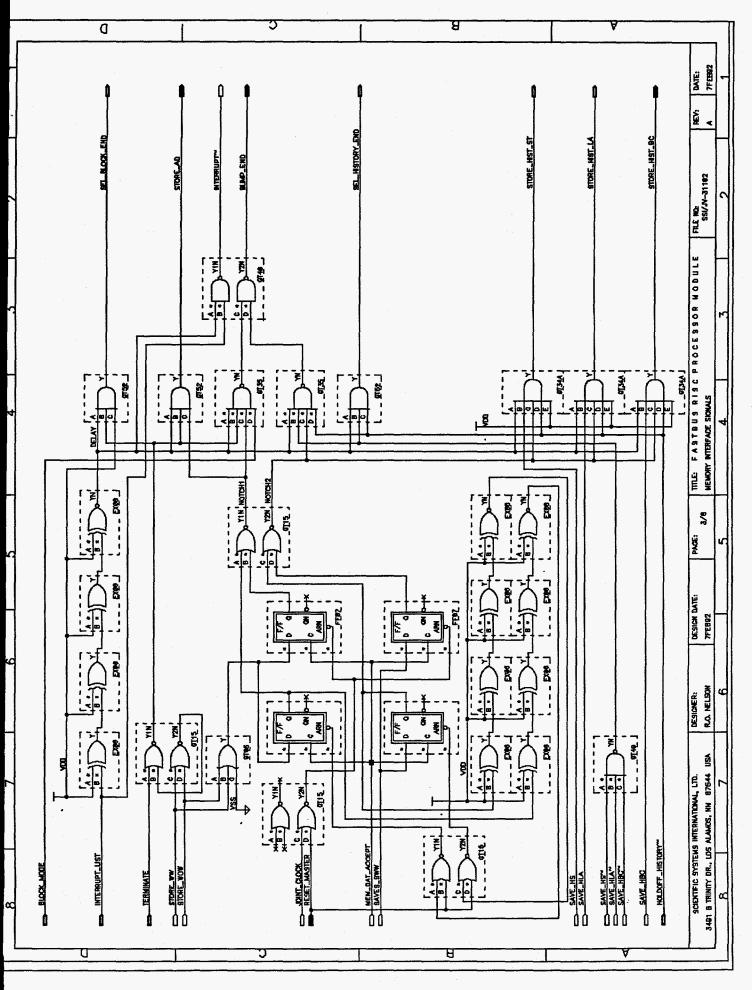

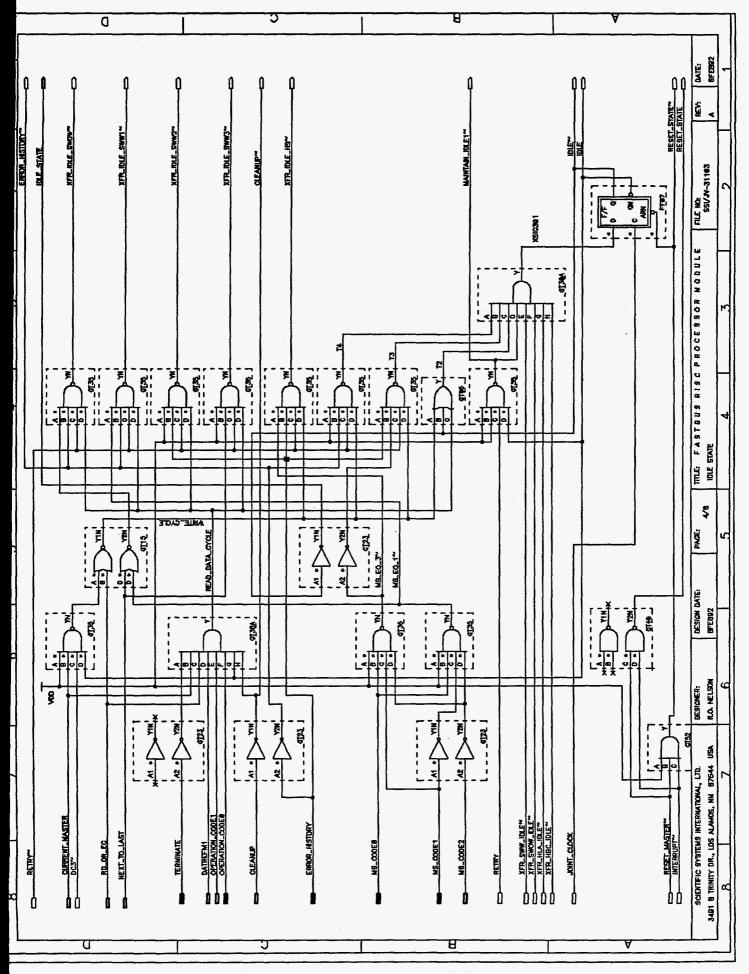

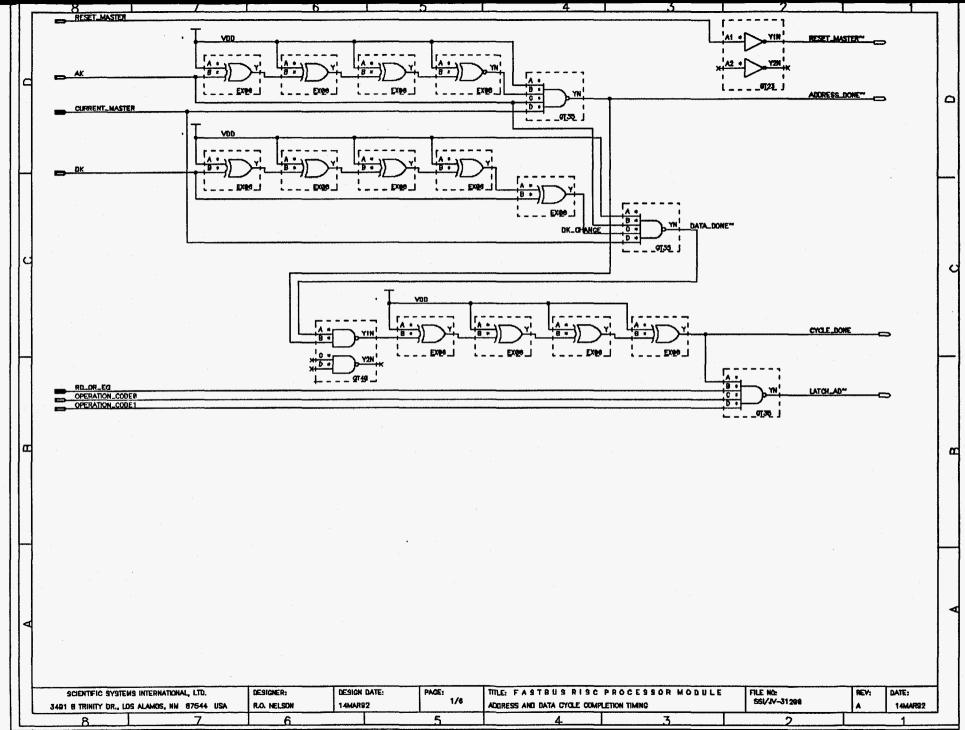

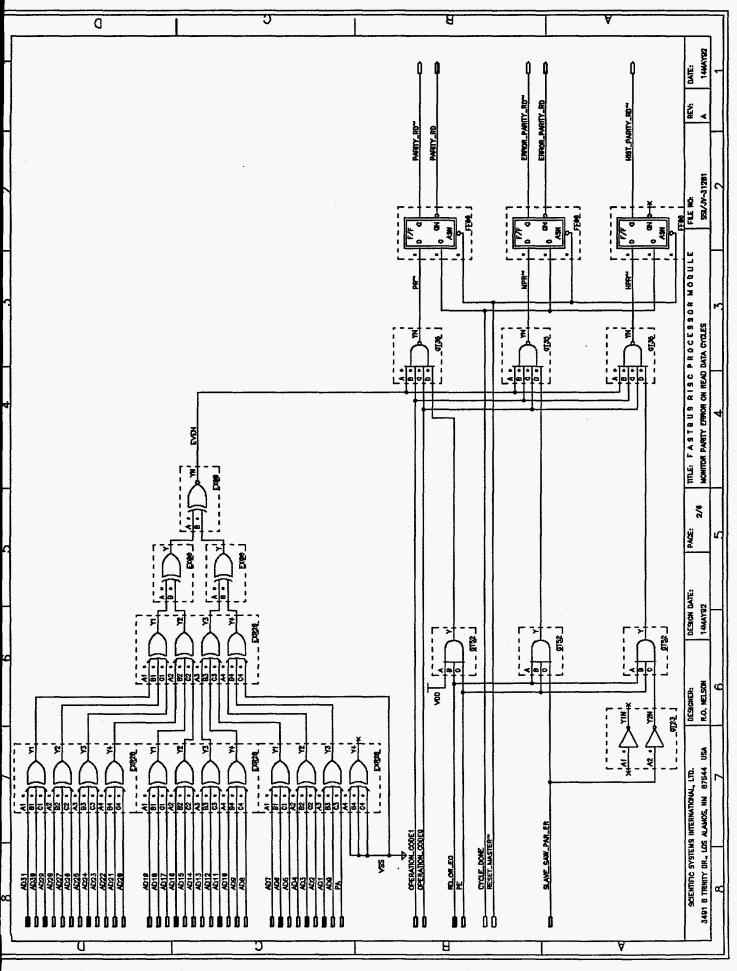

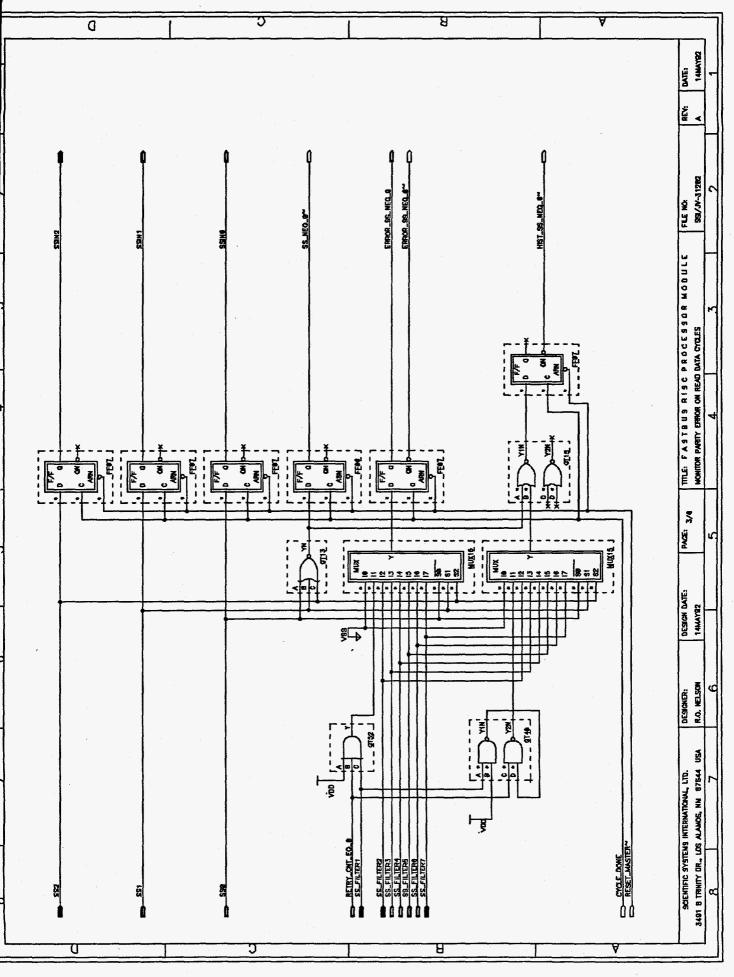

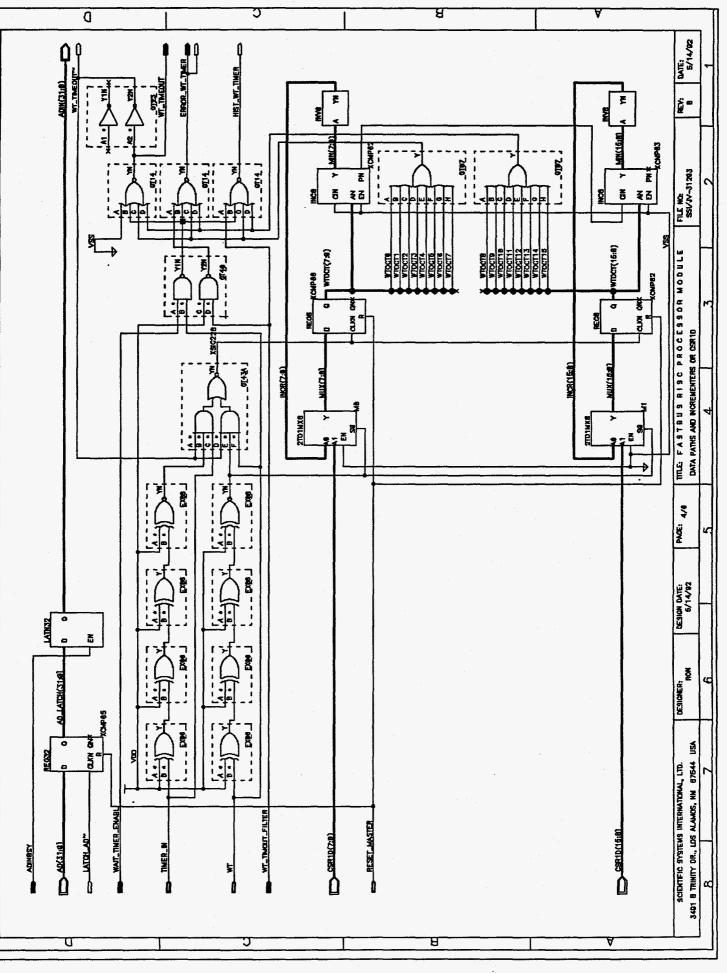

# APPENDIX B FRPM SCHEMATICS TTL LOGIC INTERFACE

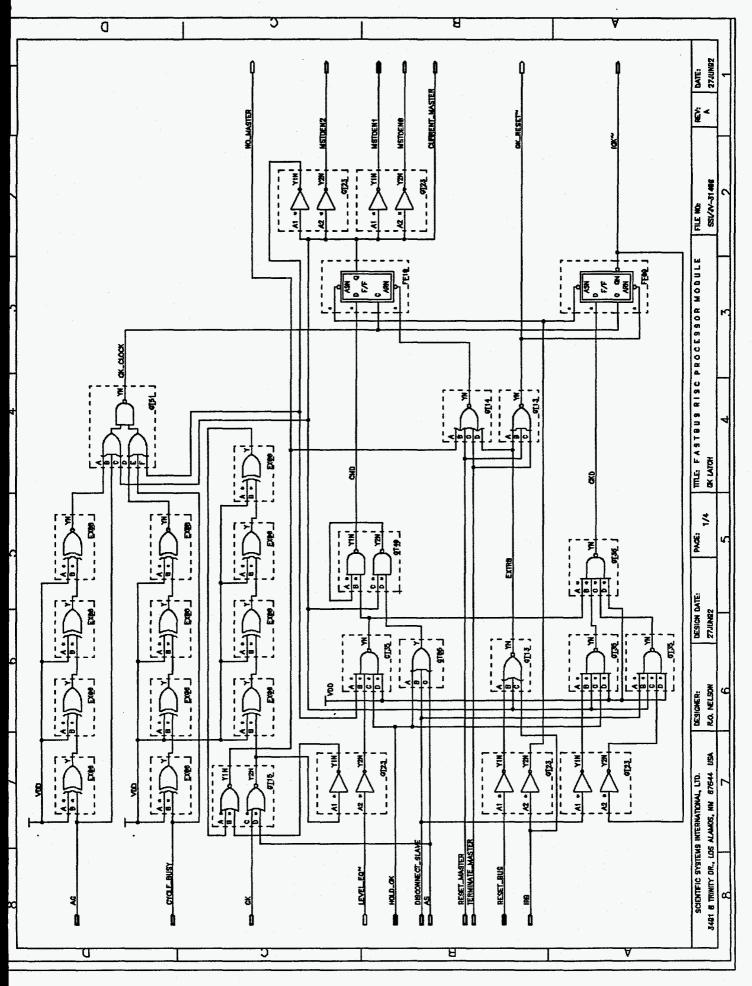

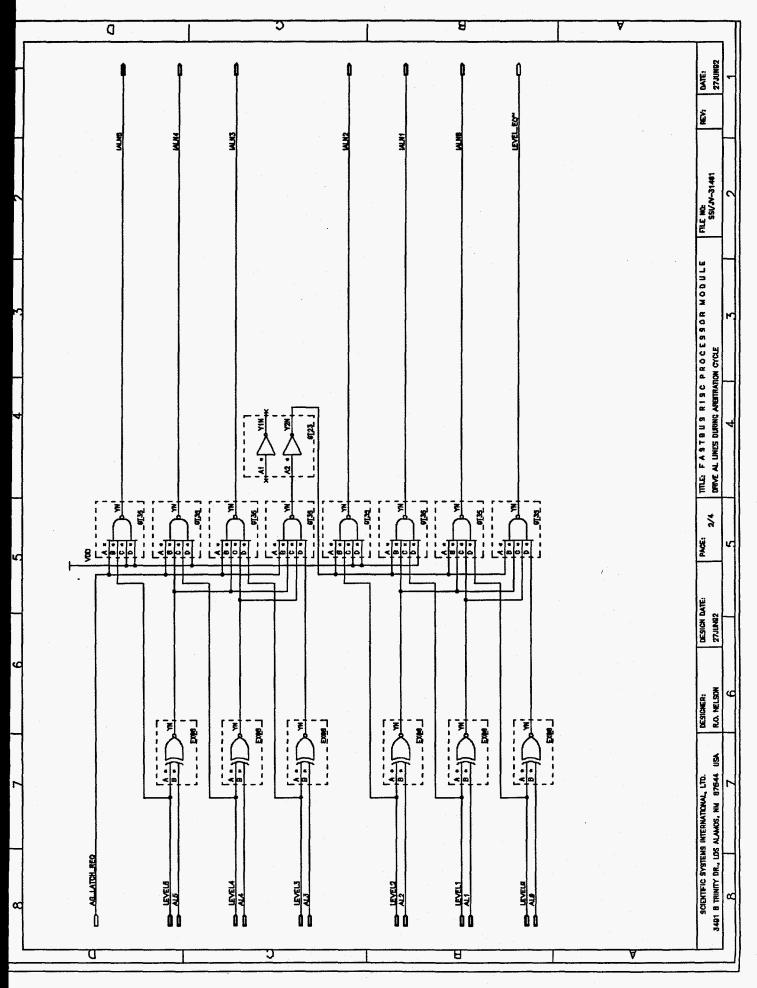

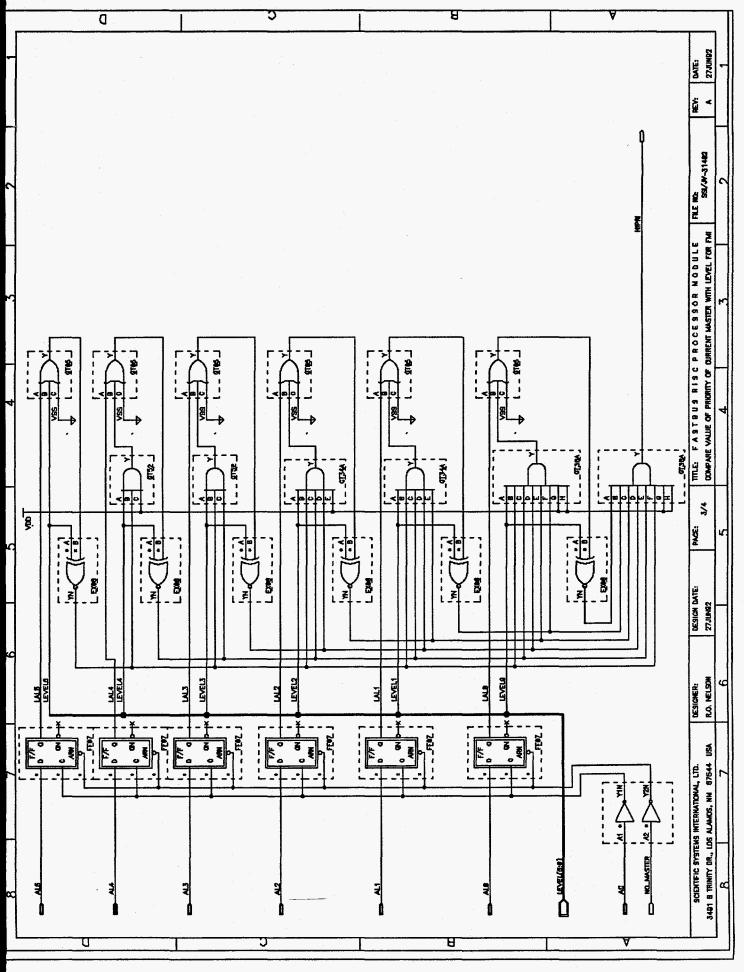

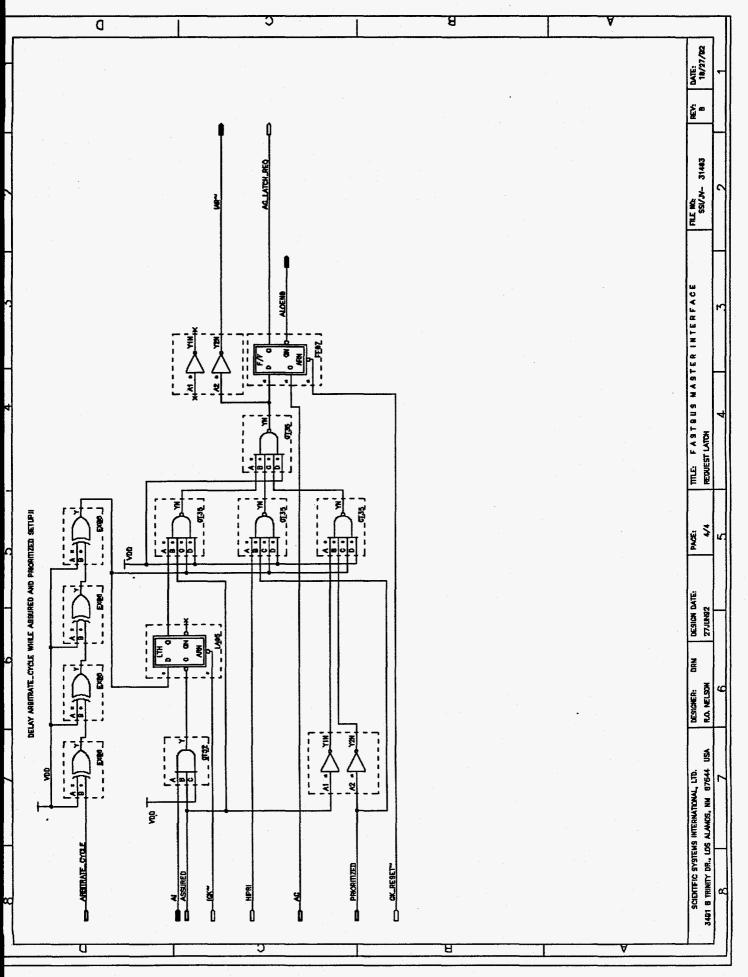

#### FRPM STANDARD-LOGIC (TTL) INTERFACE

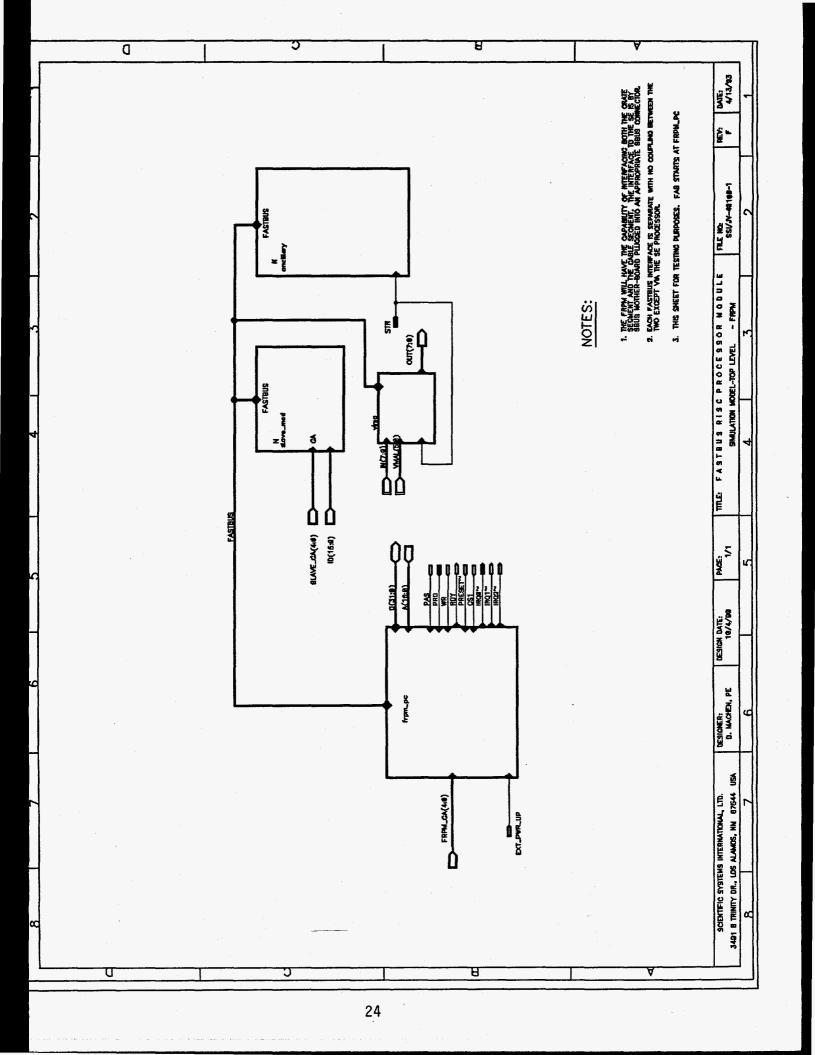

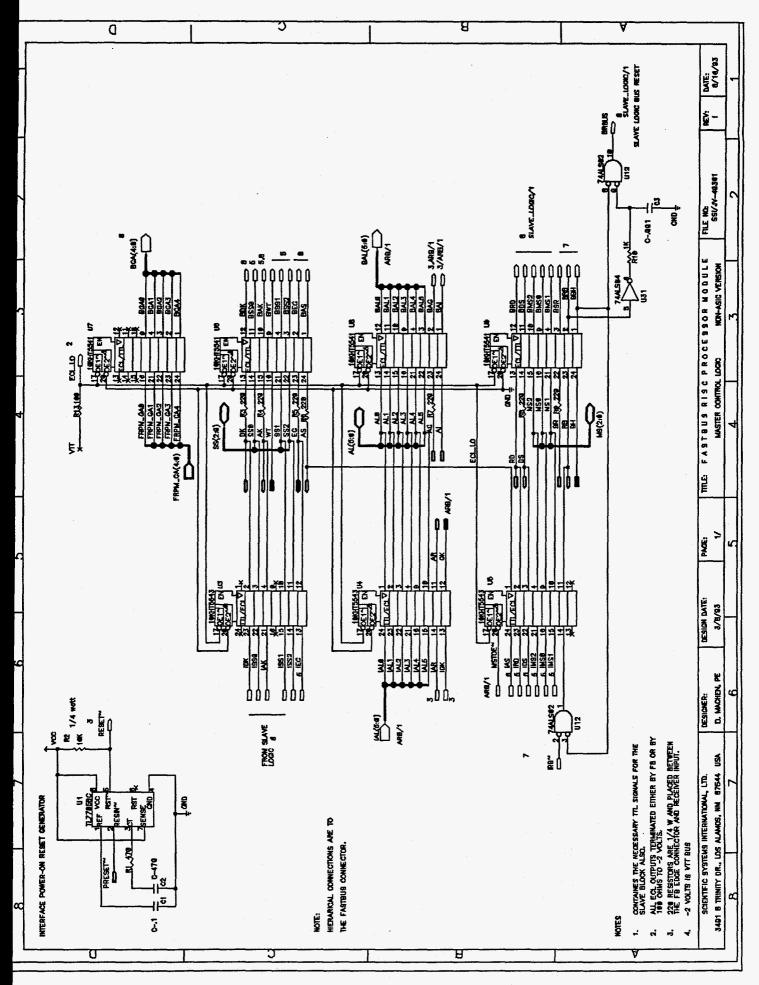

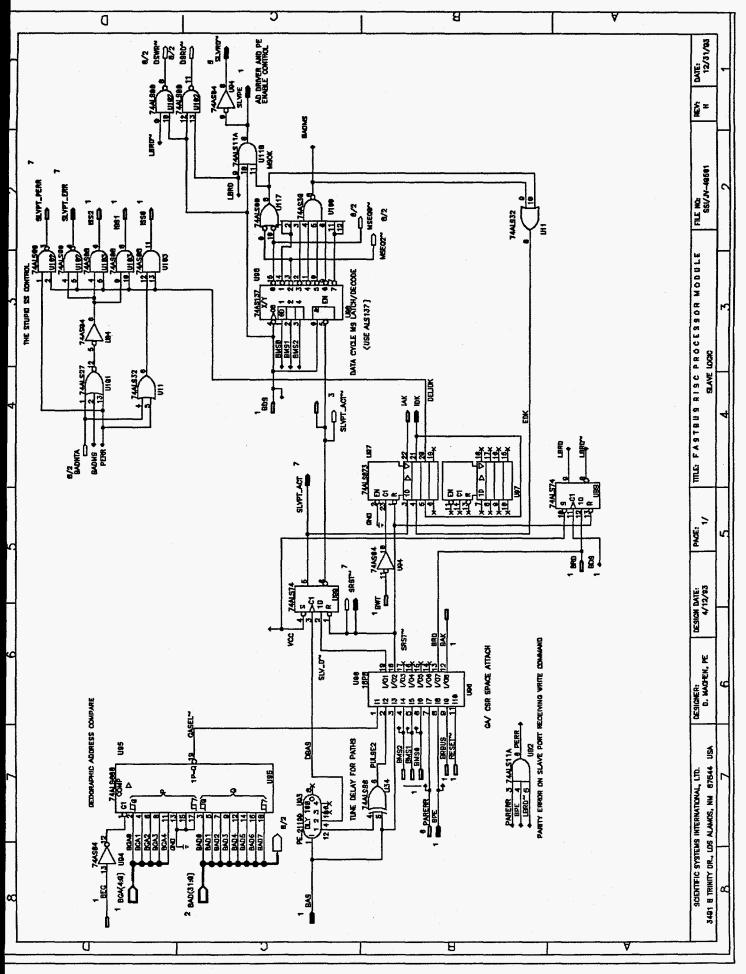

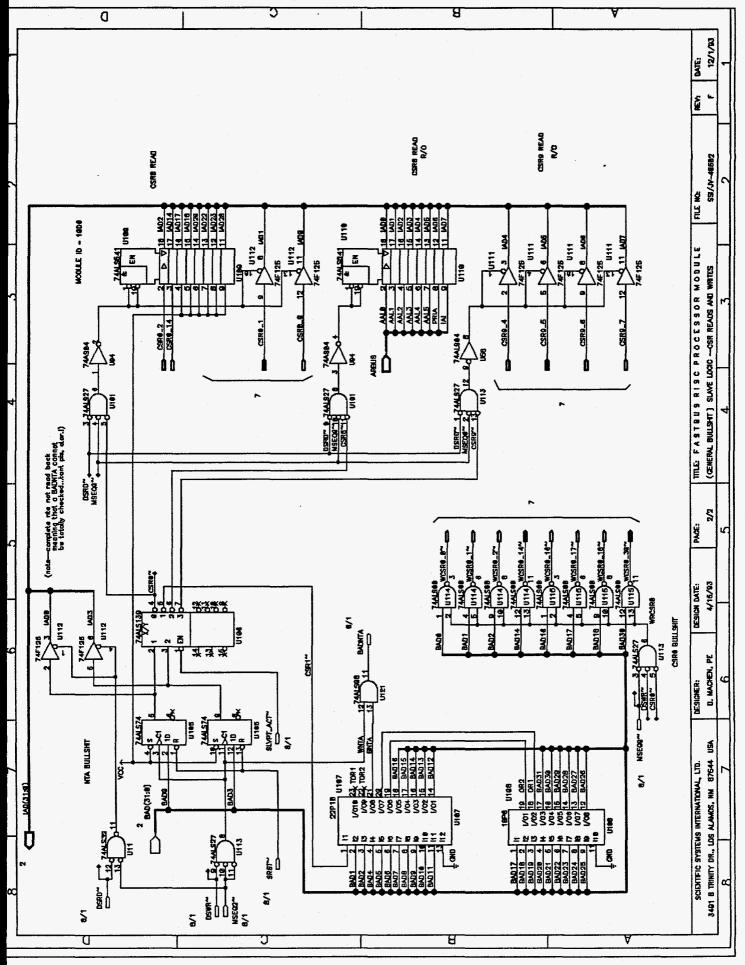

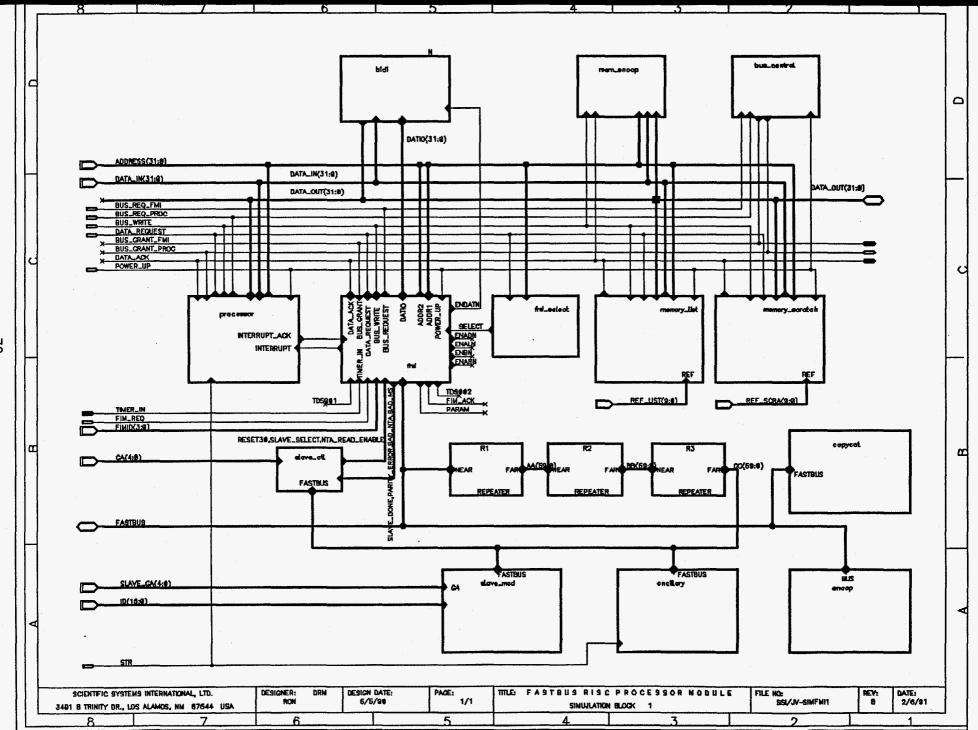

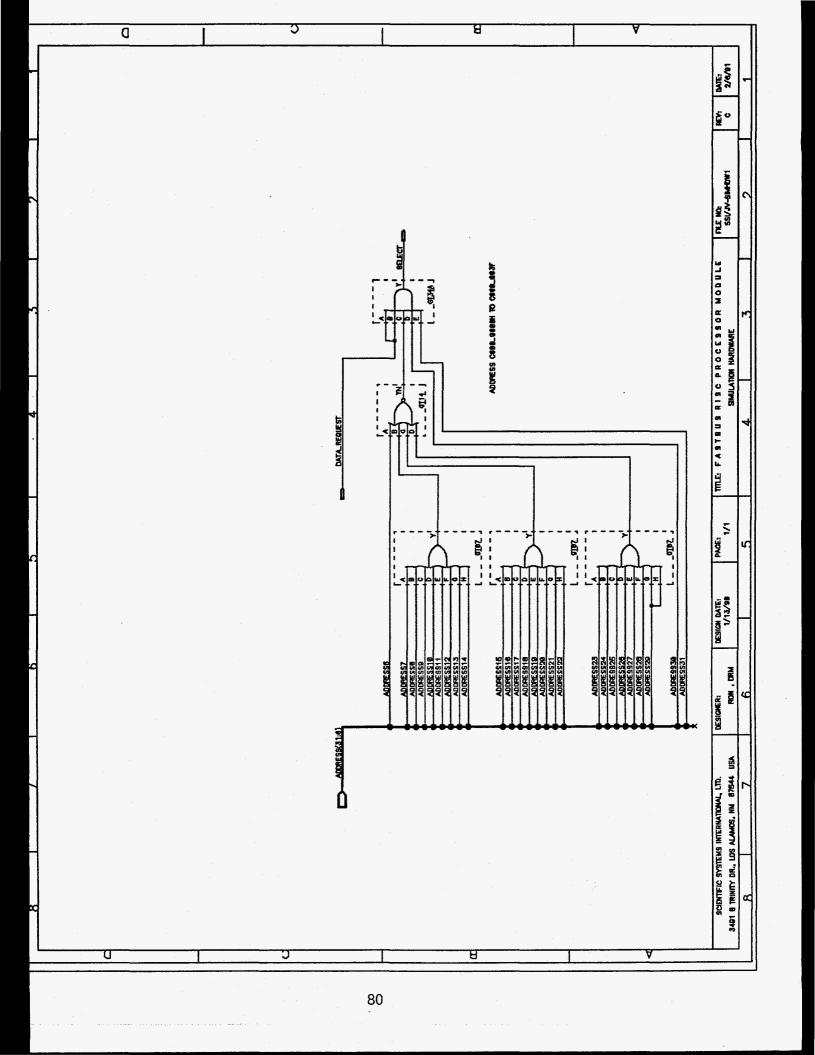

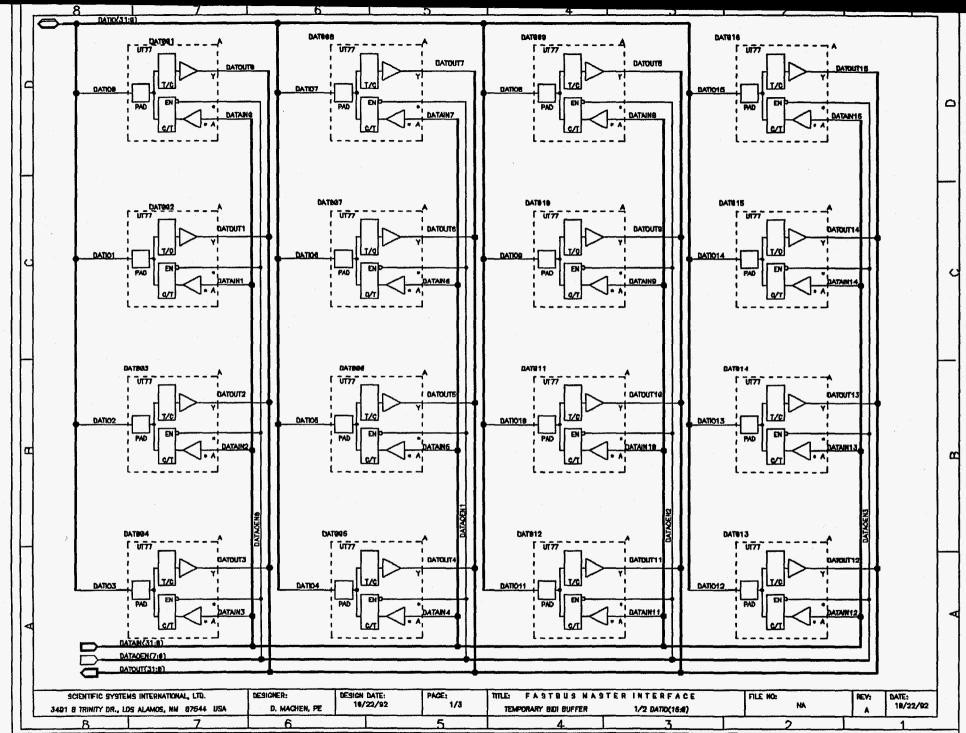

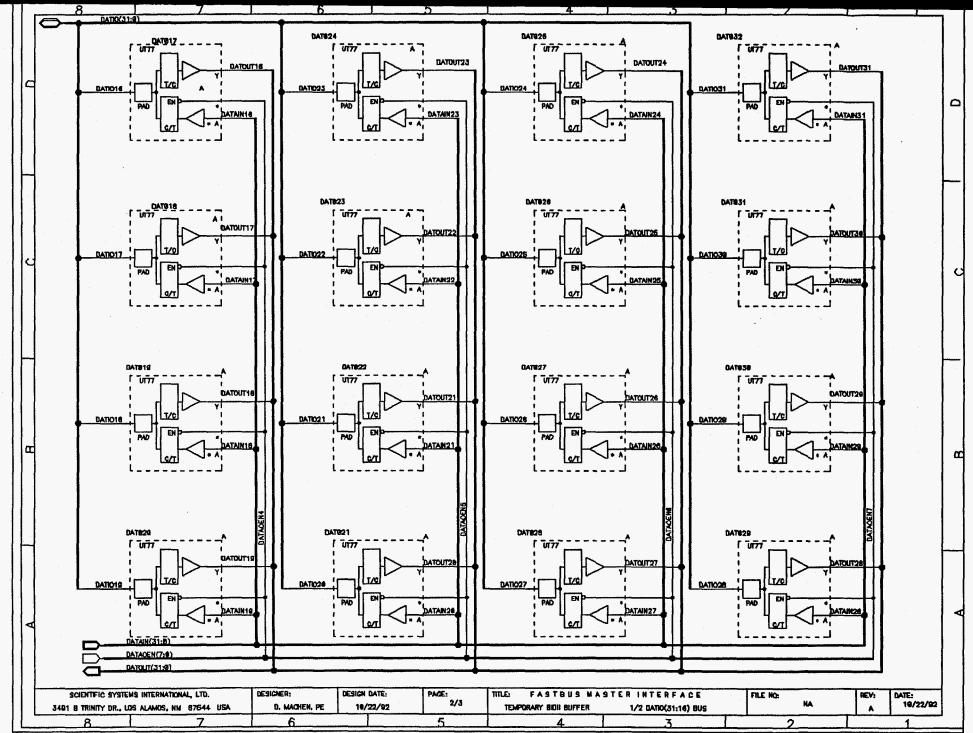

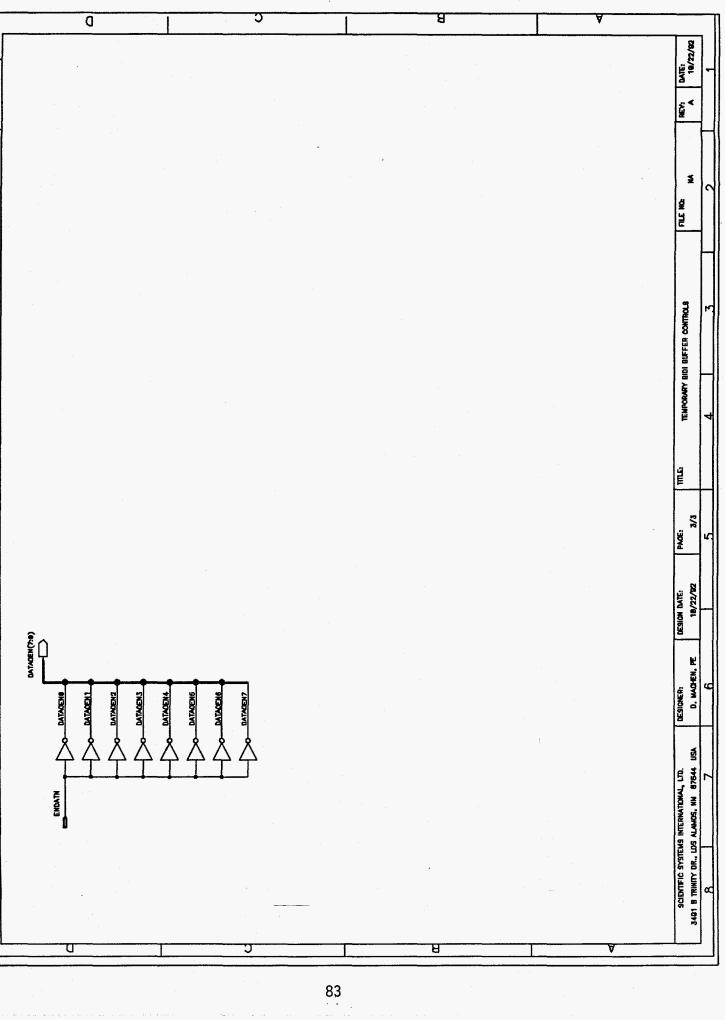

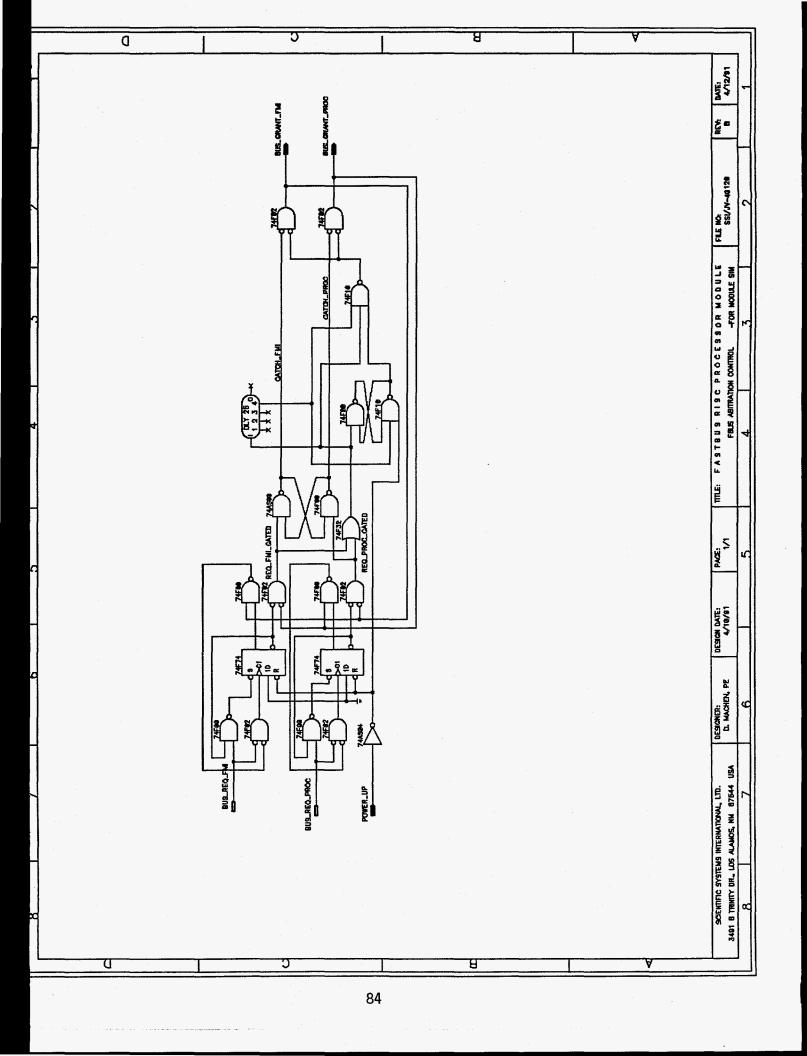

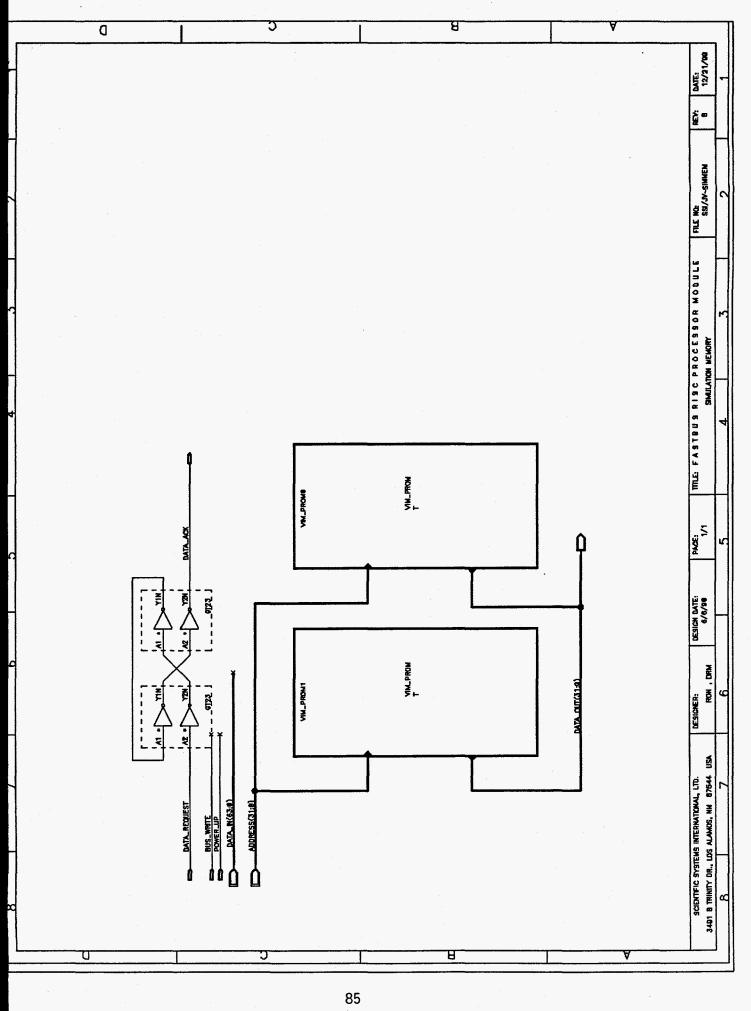

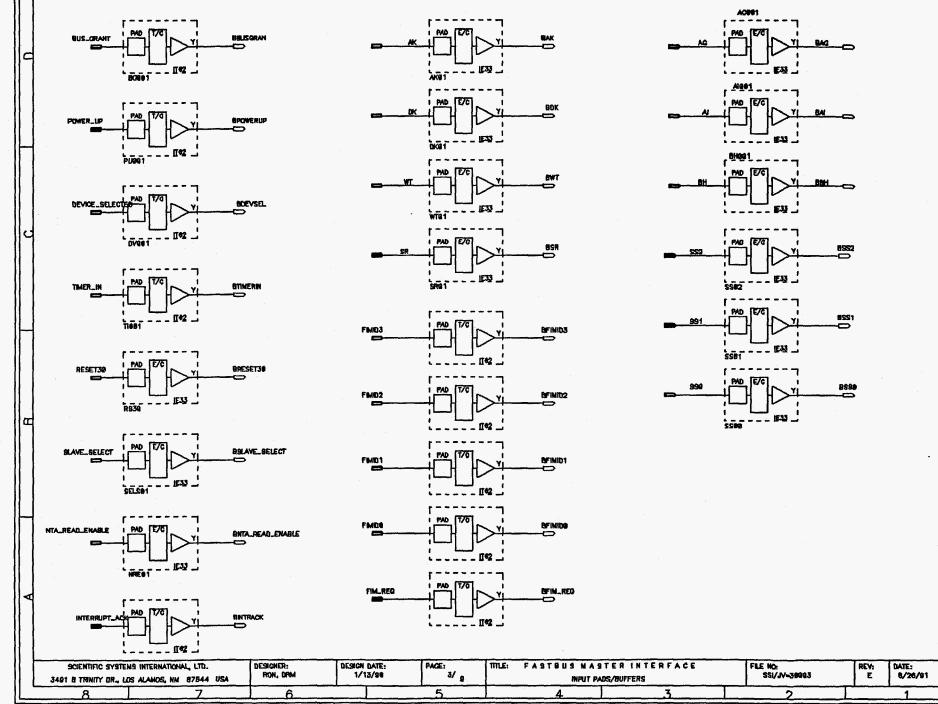

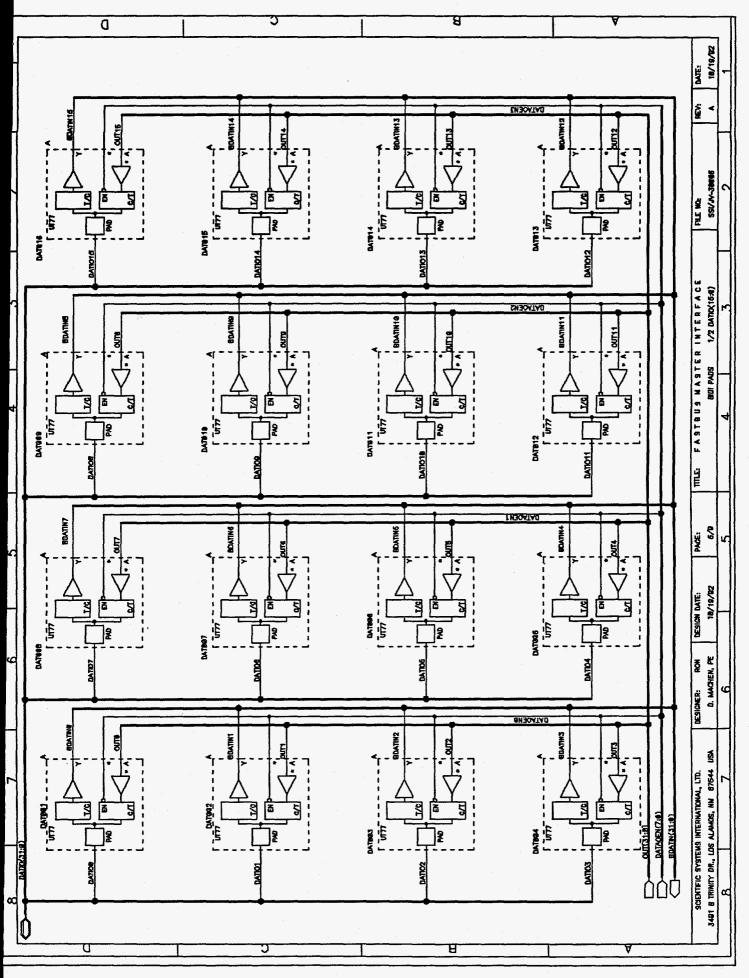

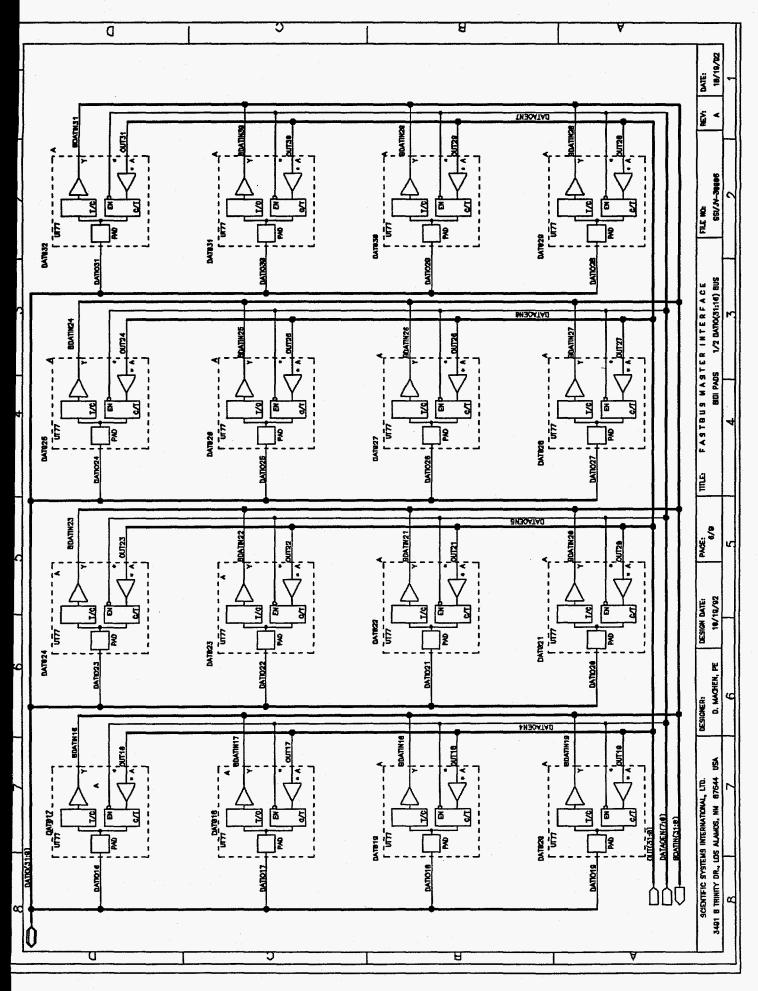

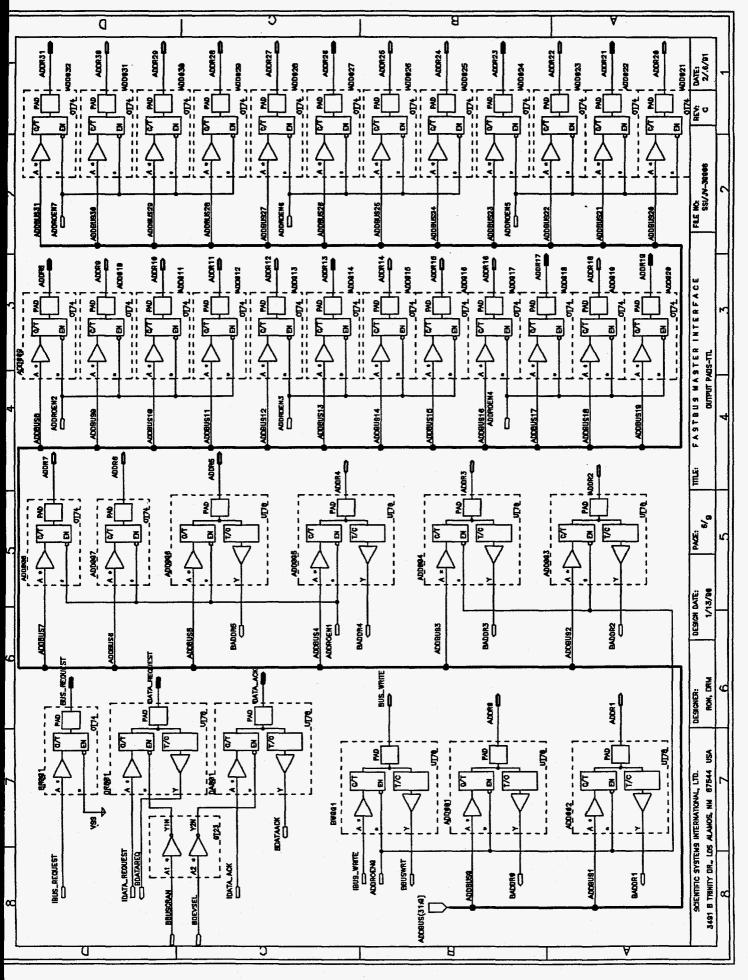

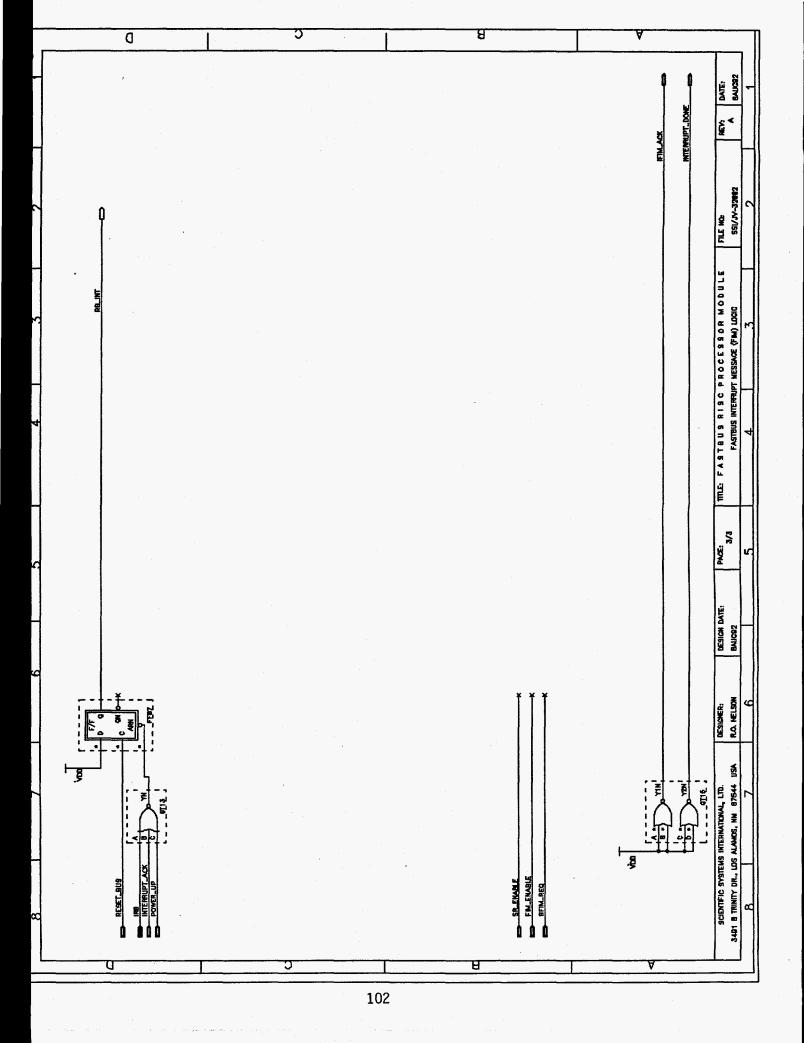

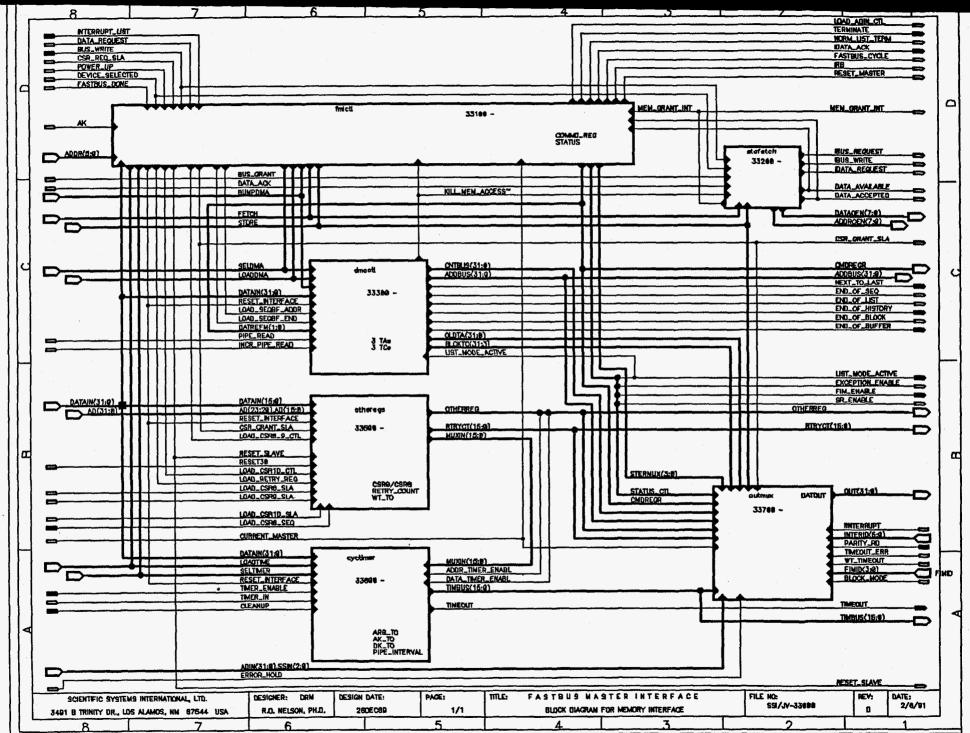

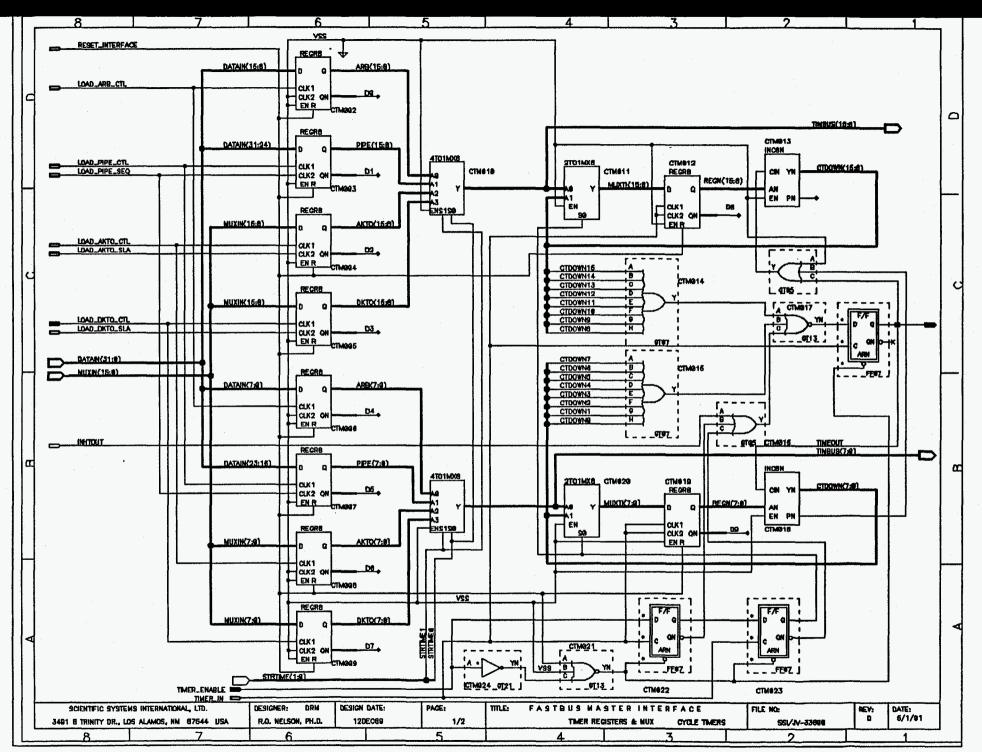

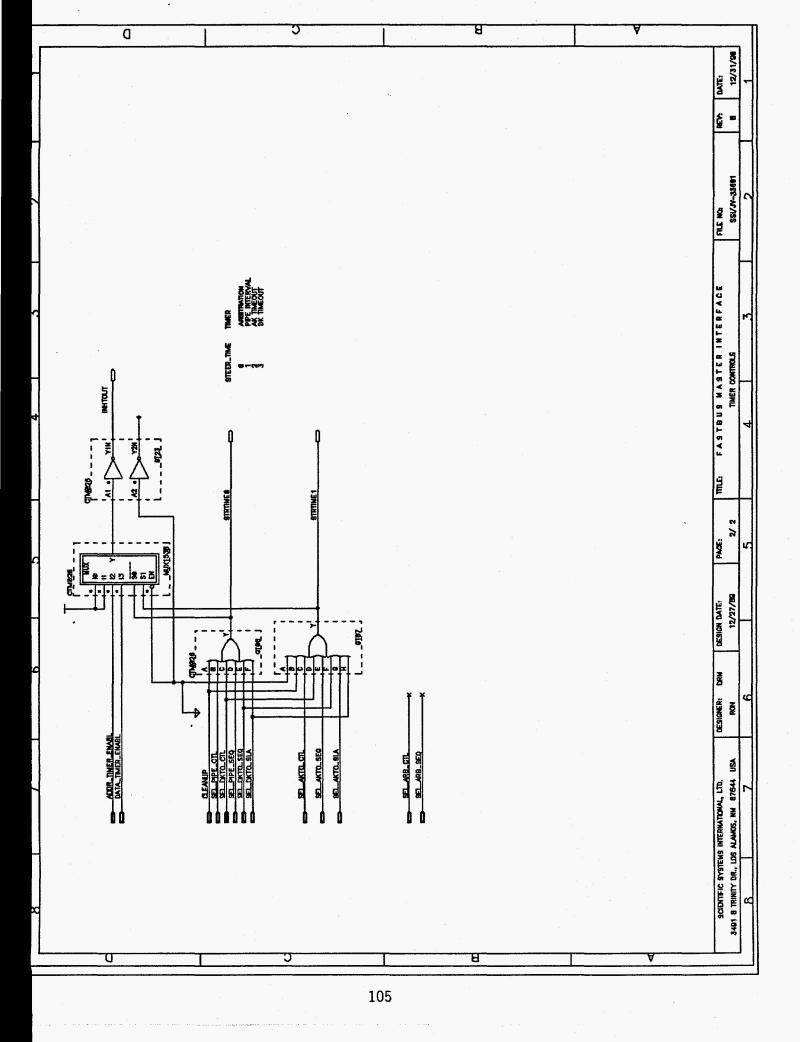

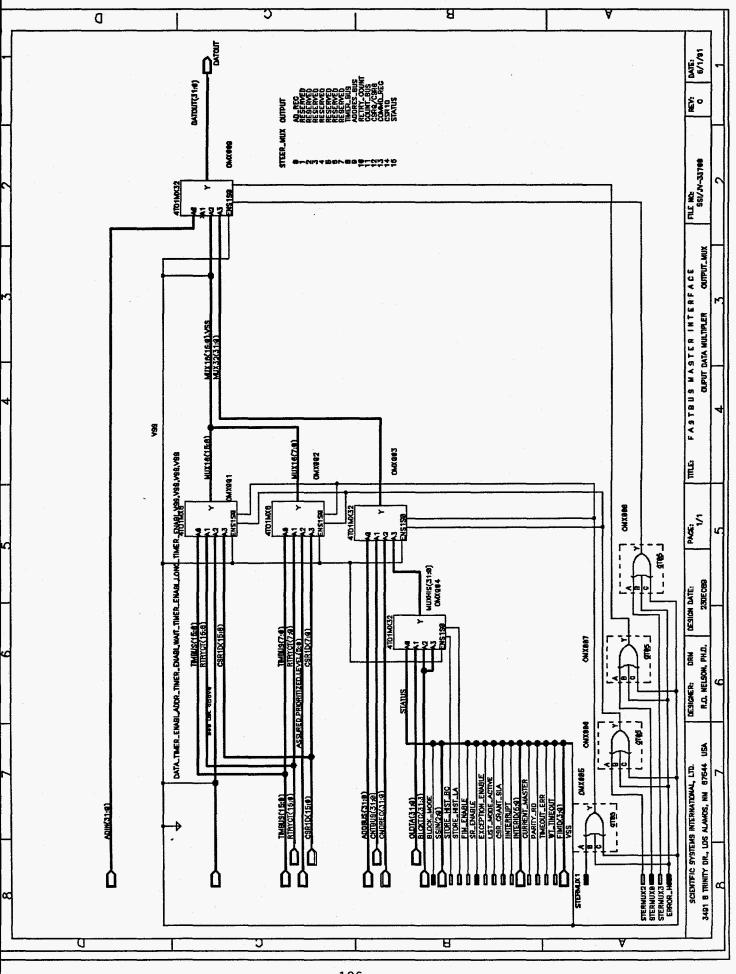

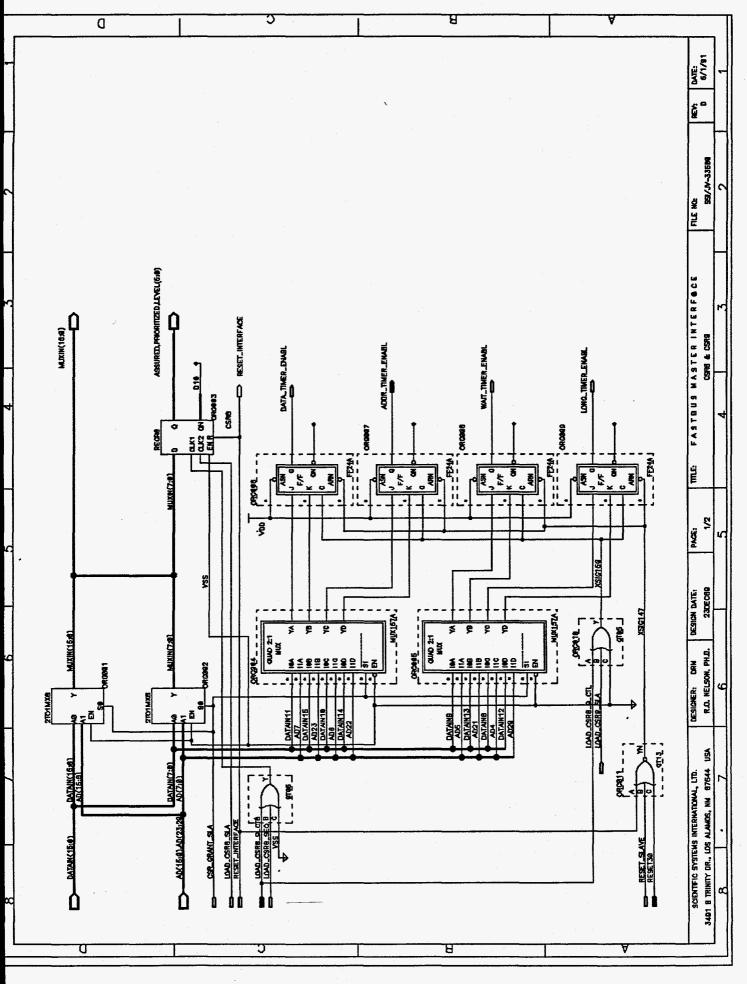

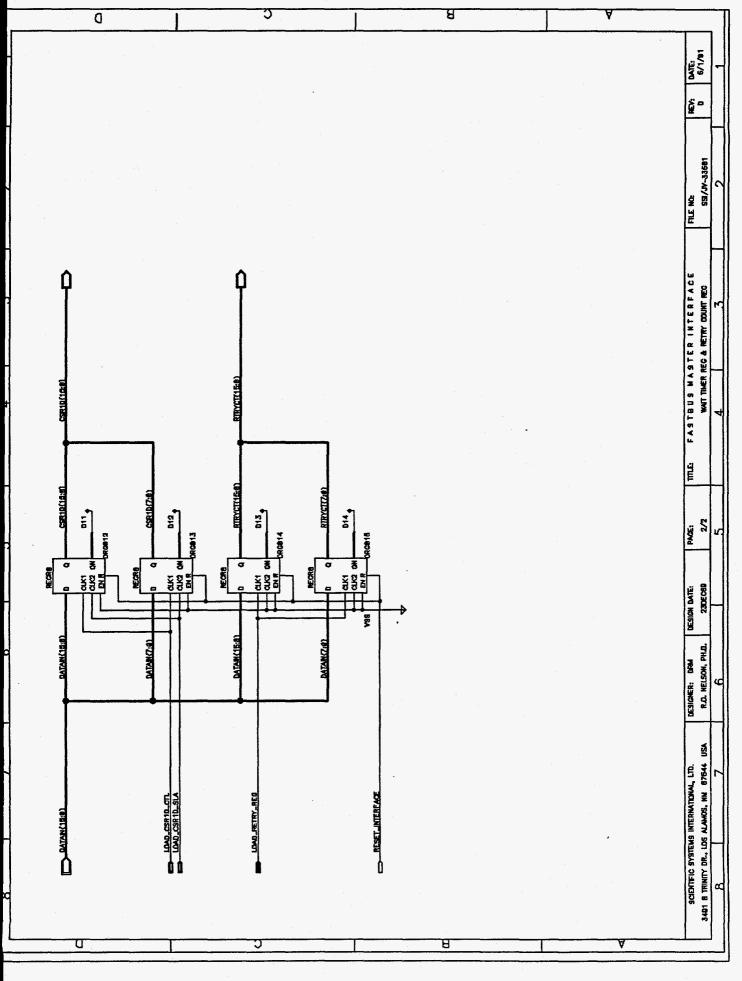

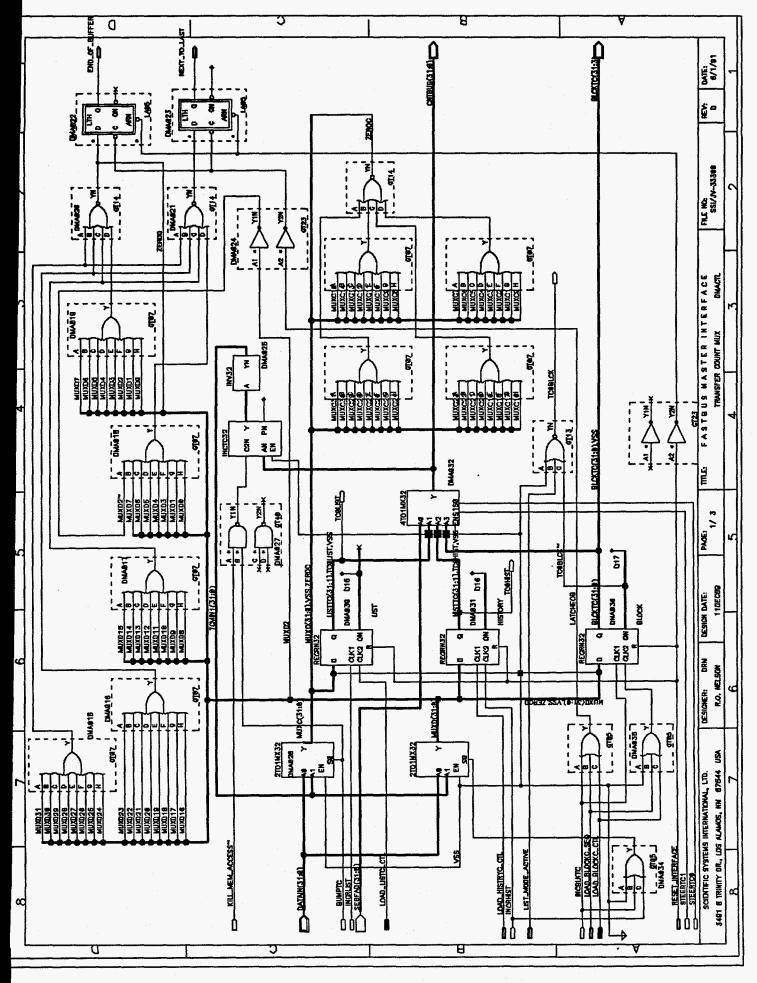

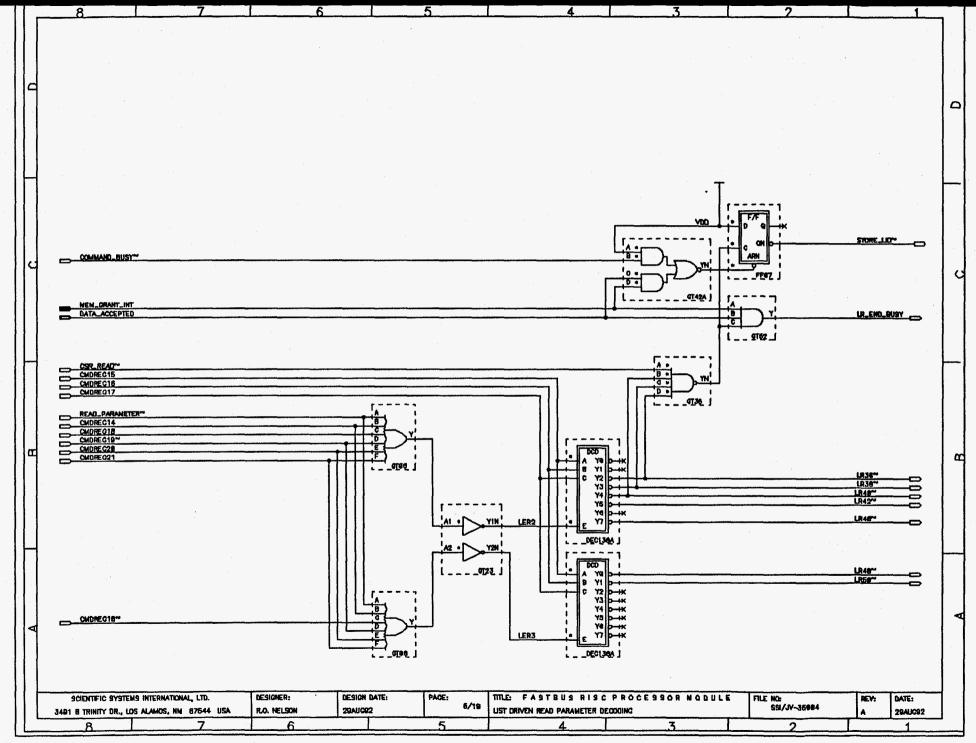

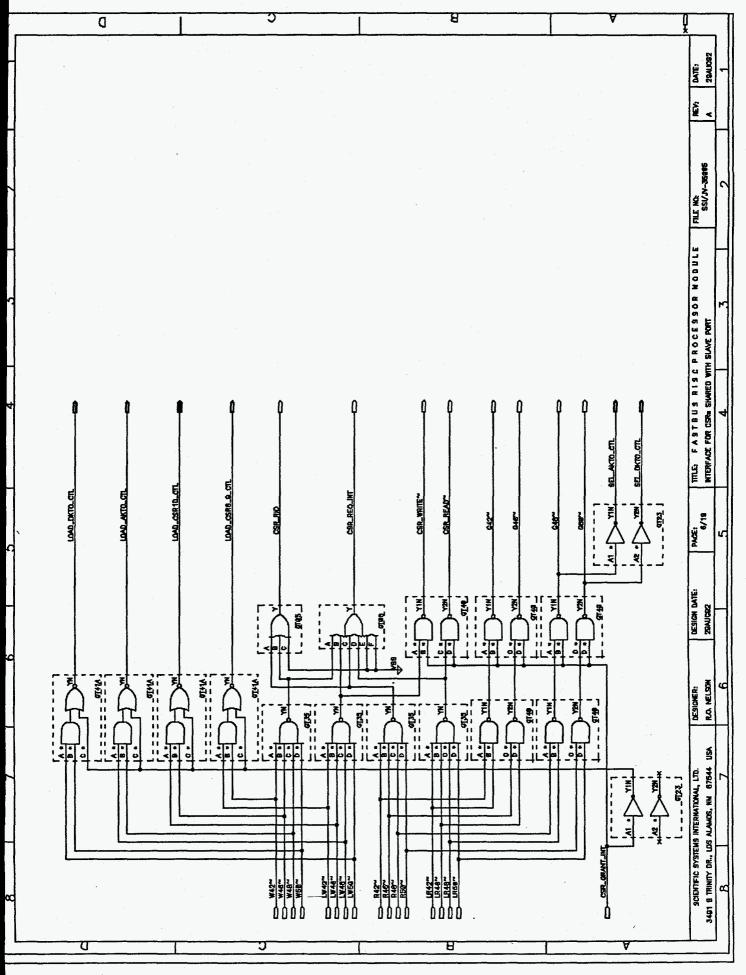

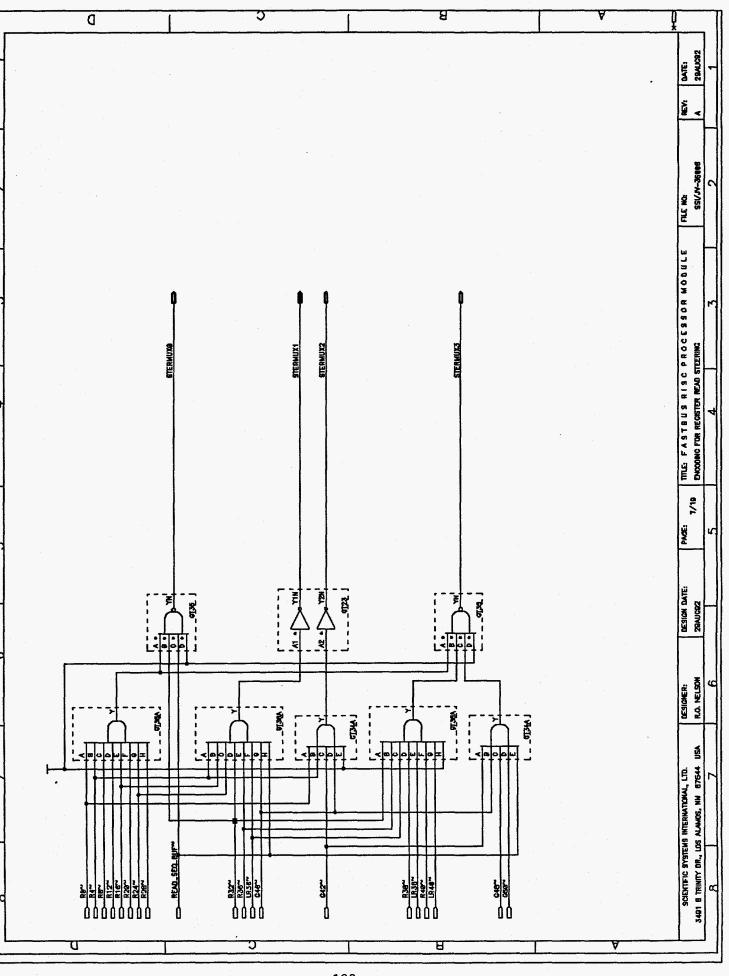

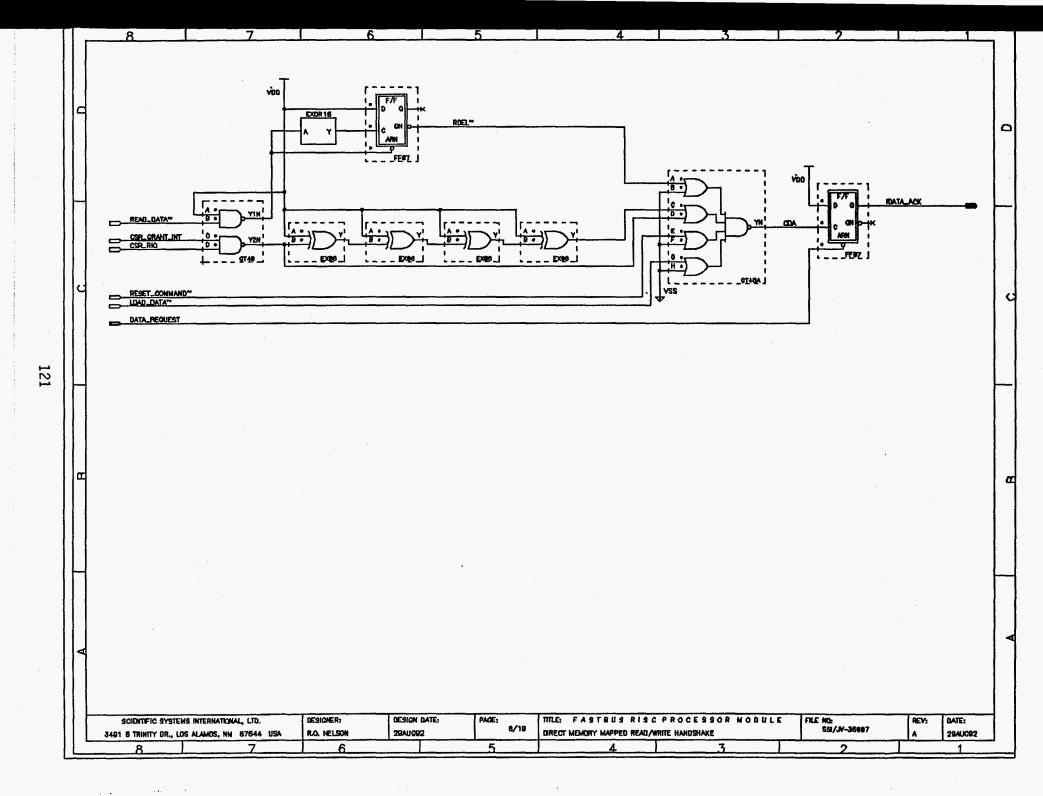

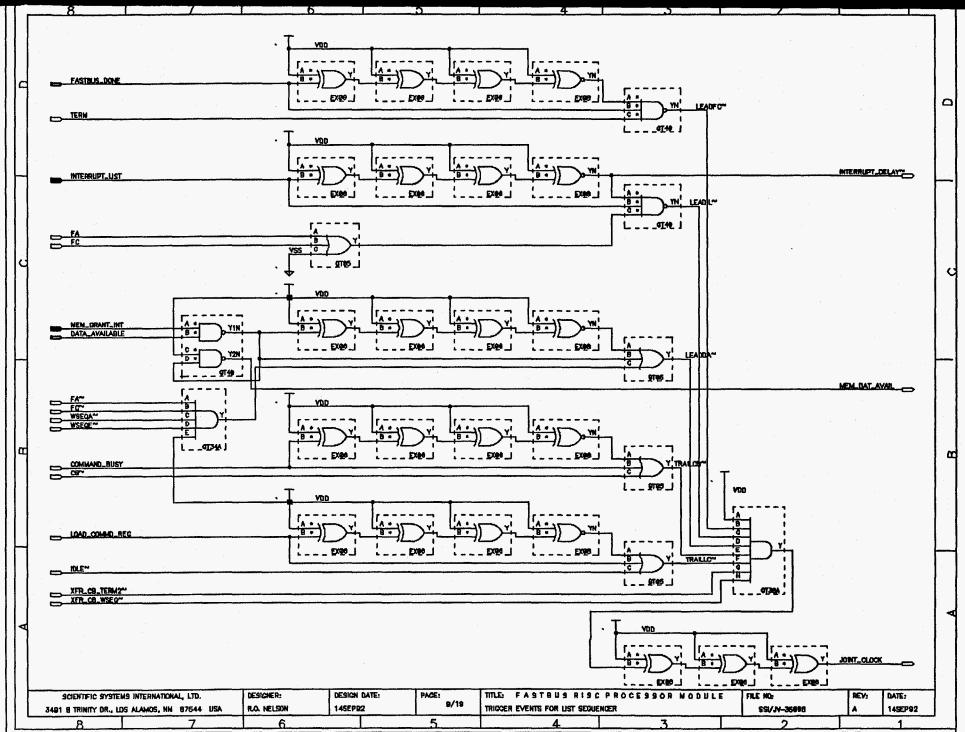

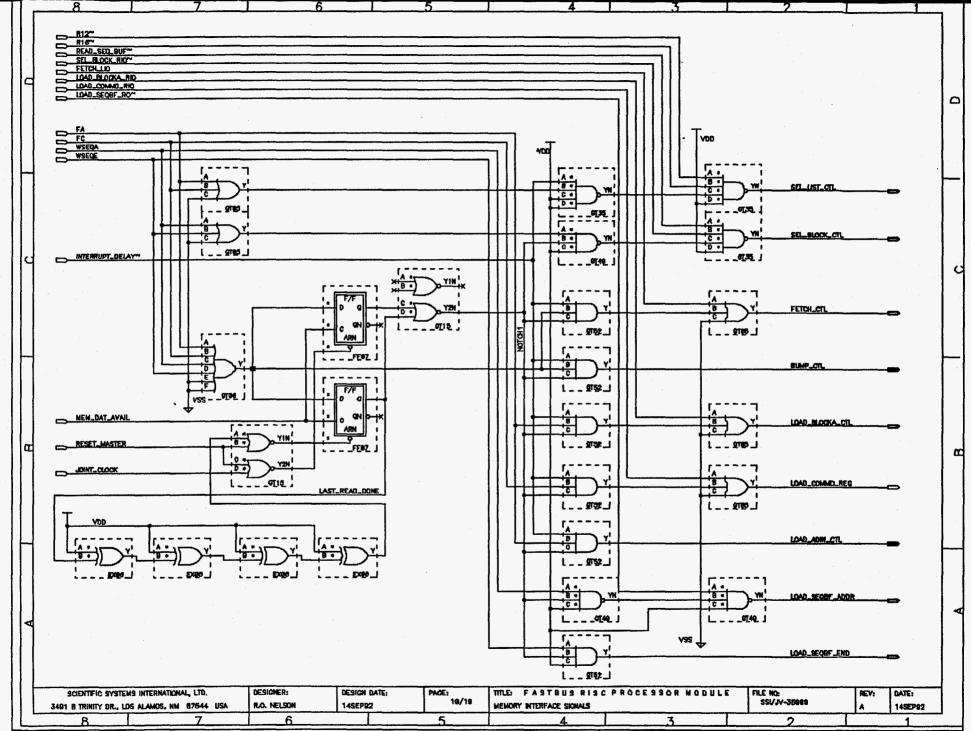

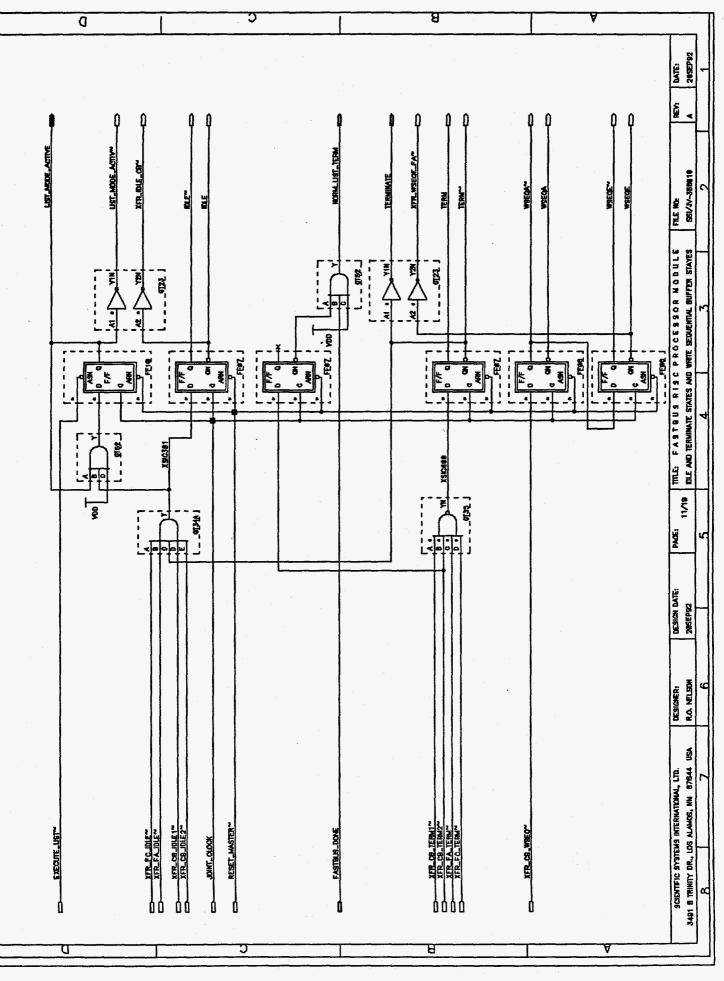

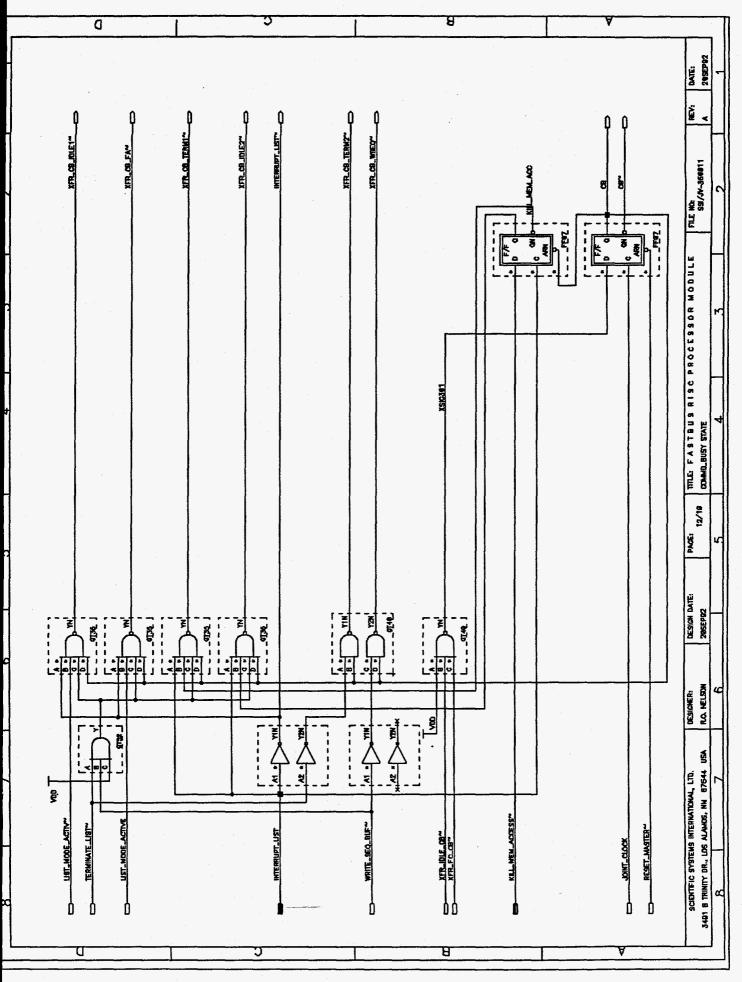

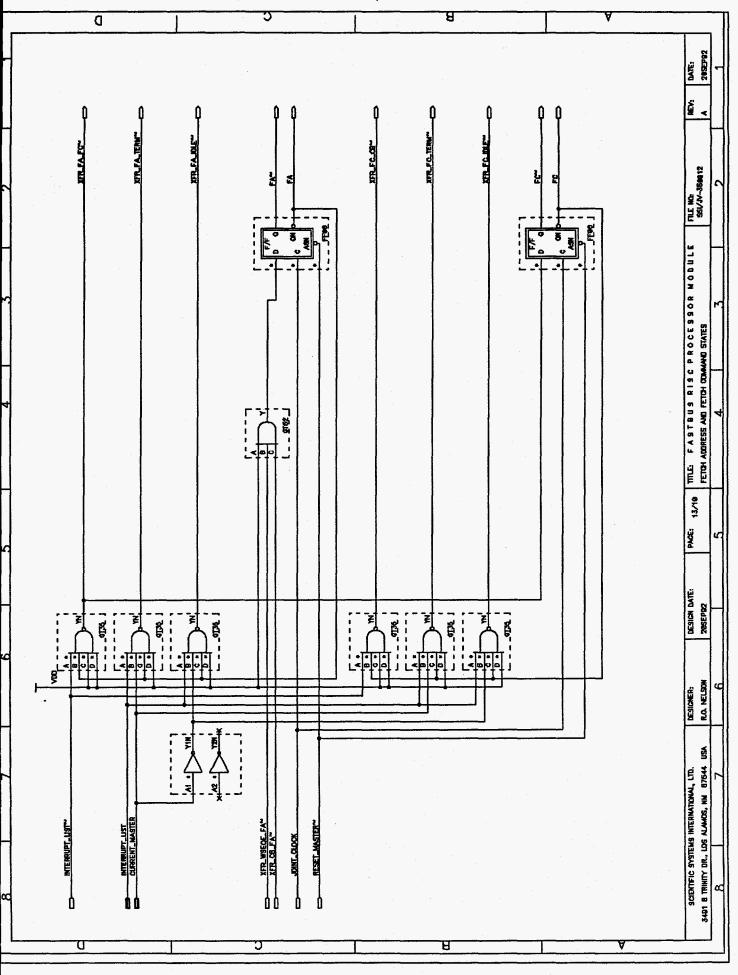

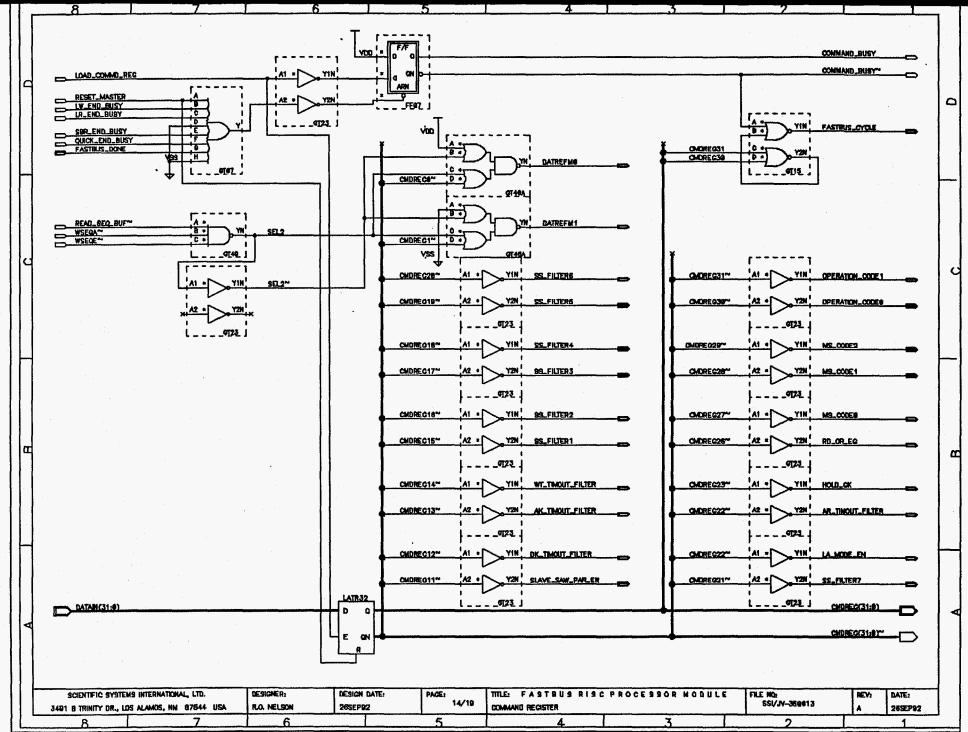

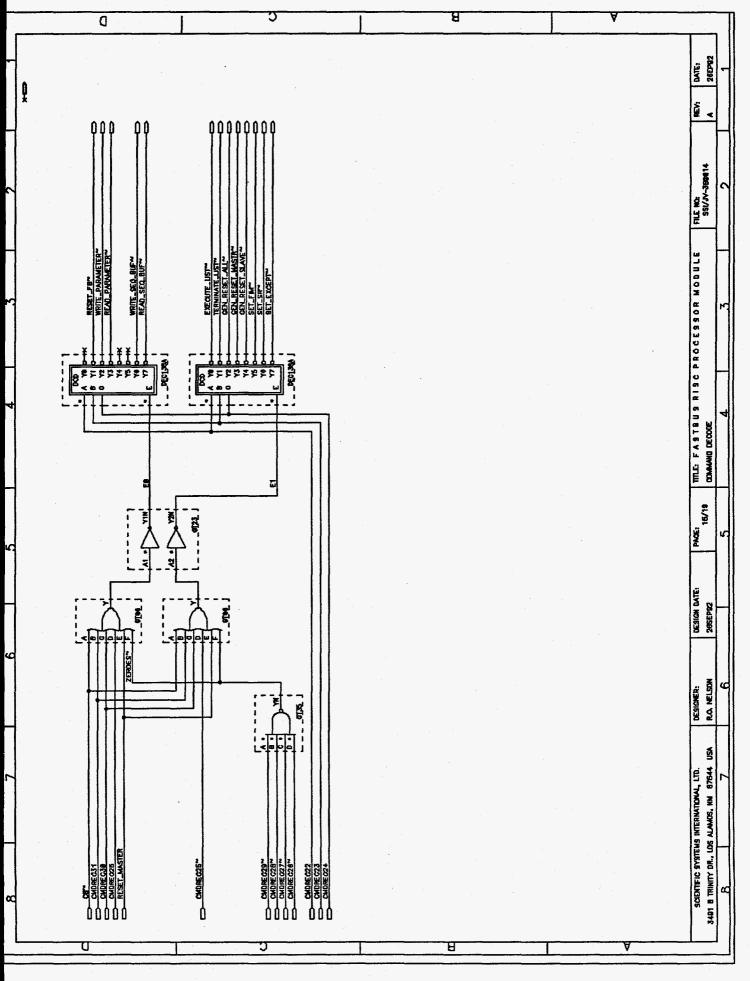

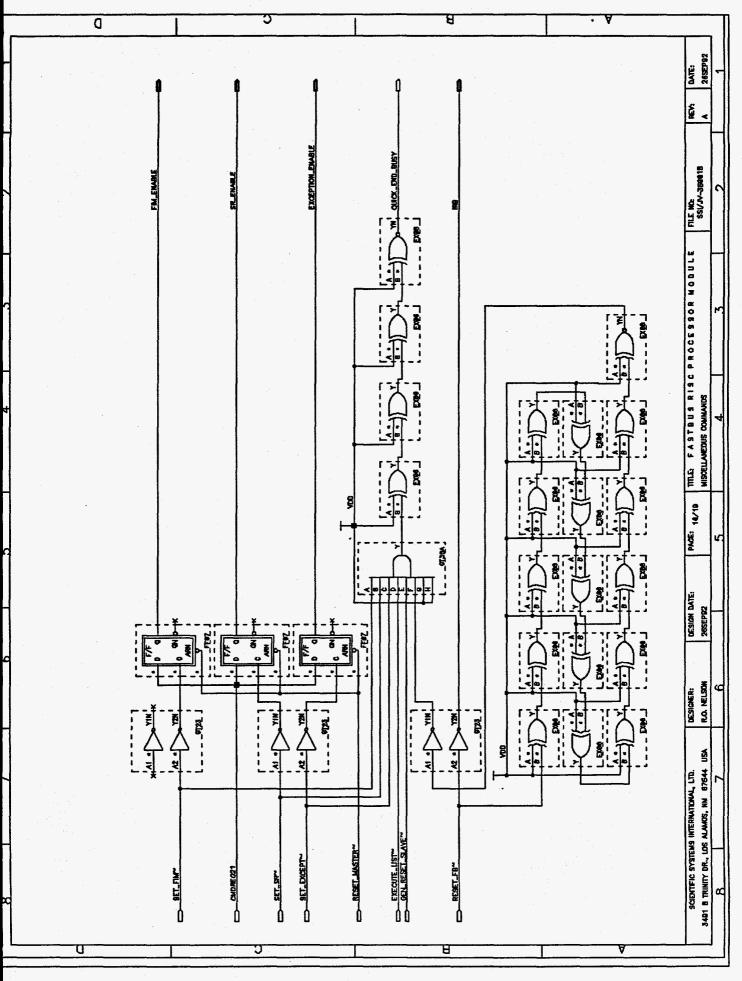

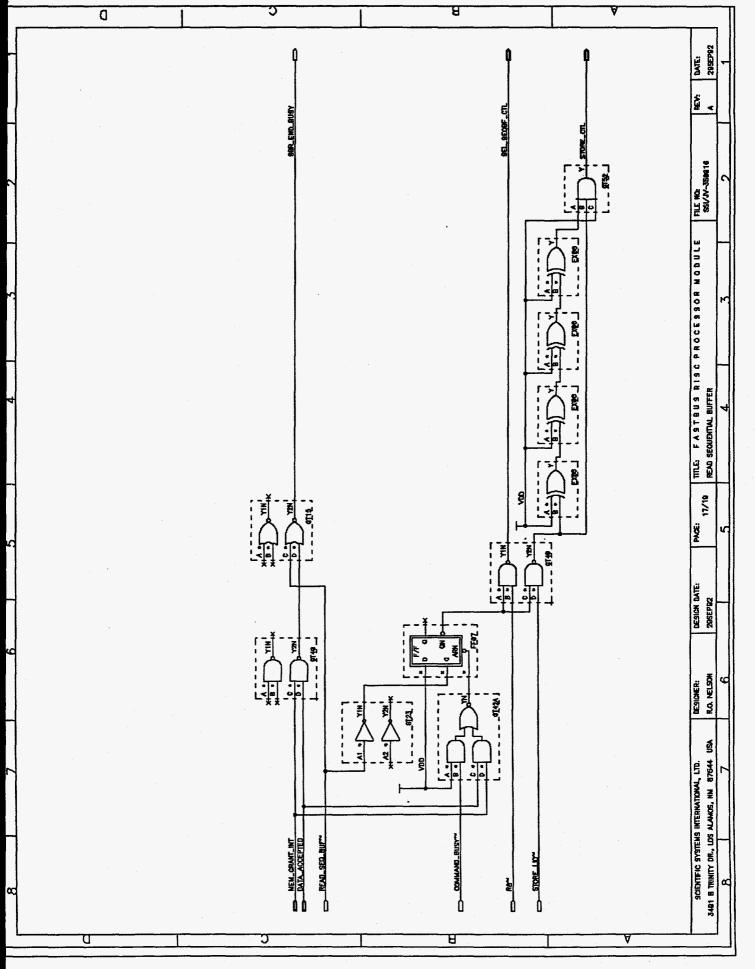

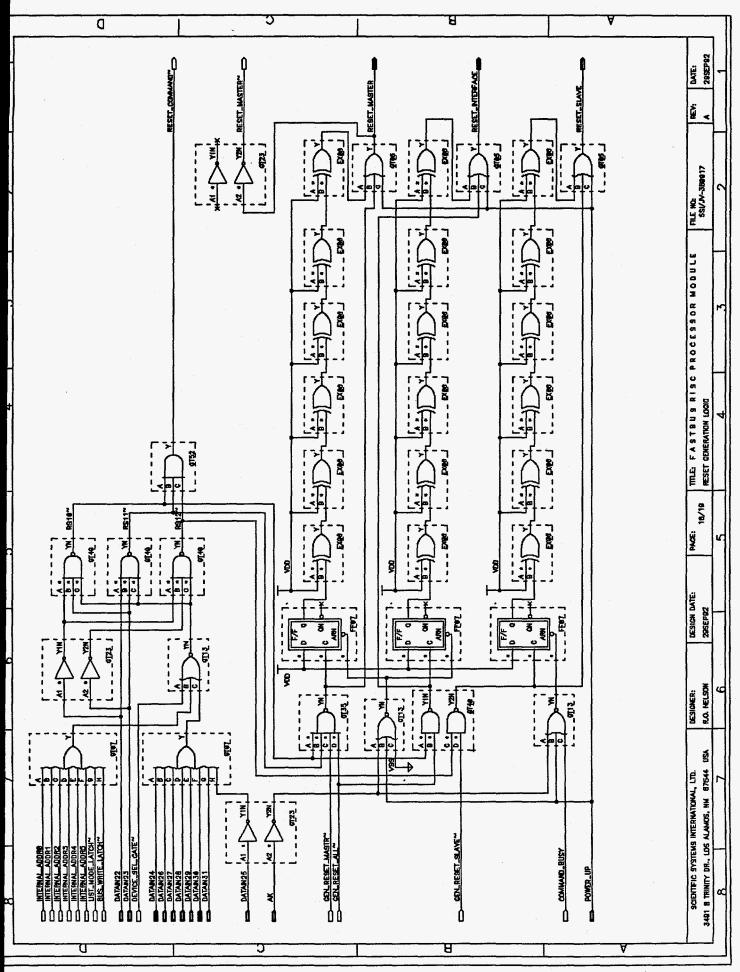

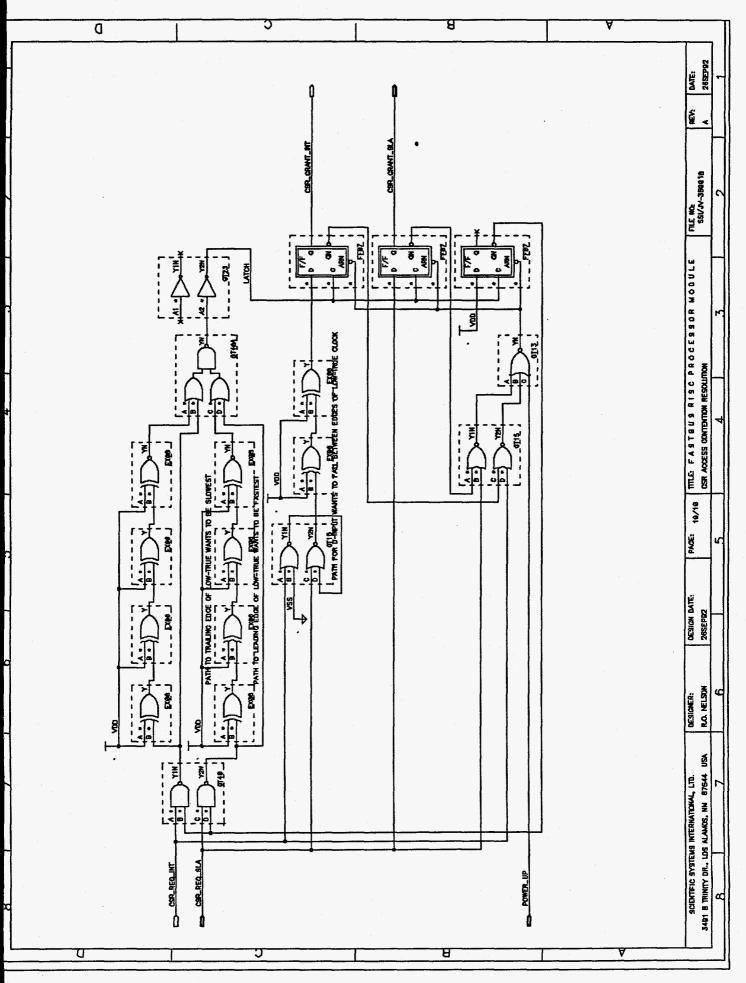

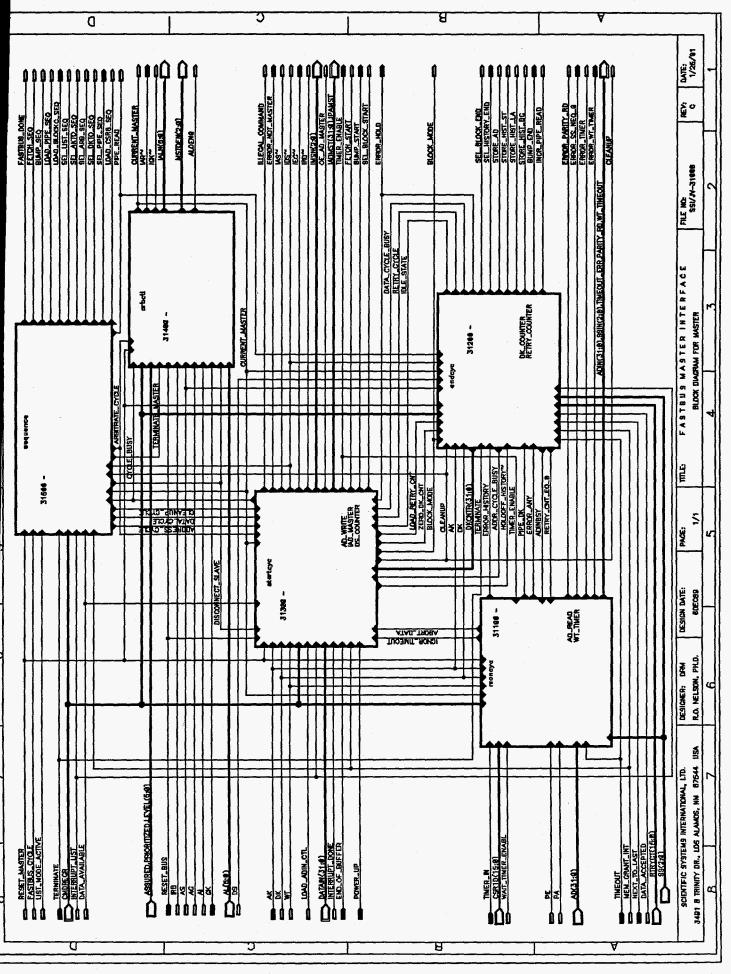

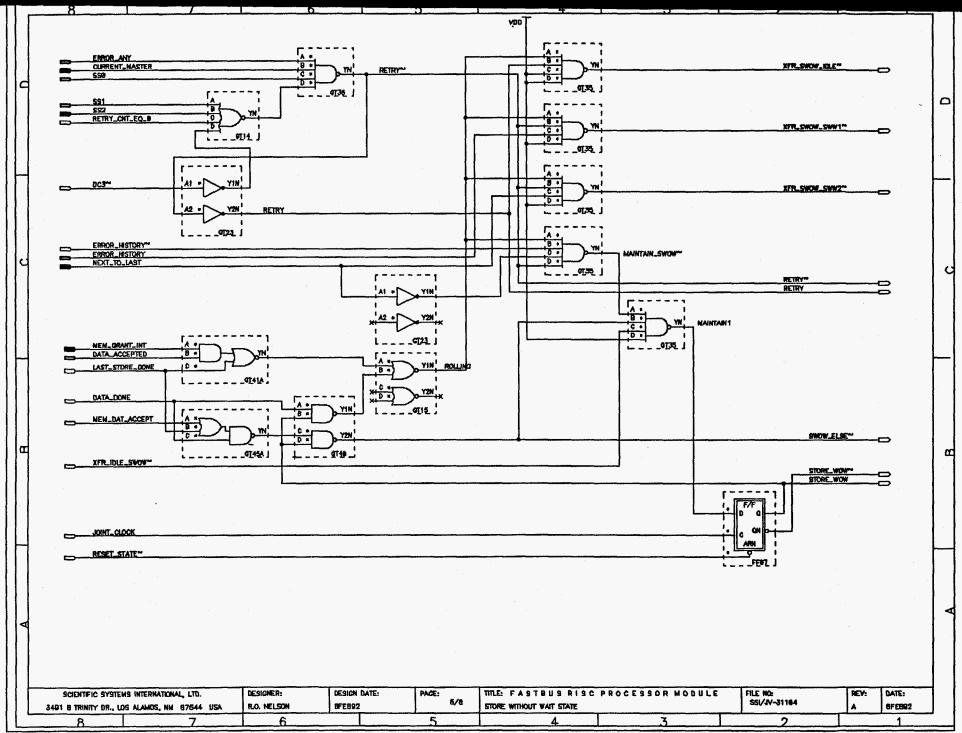

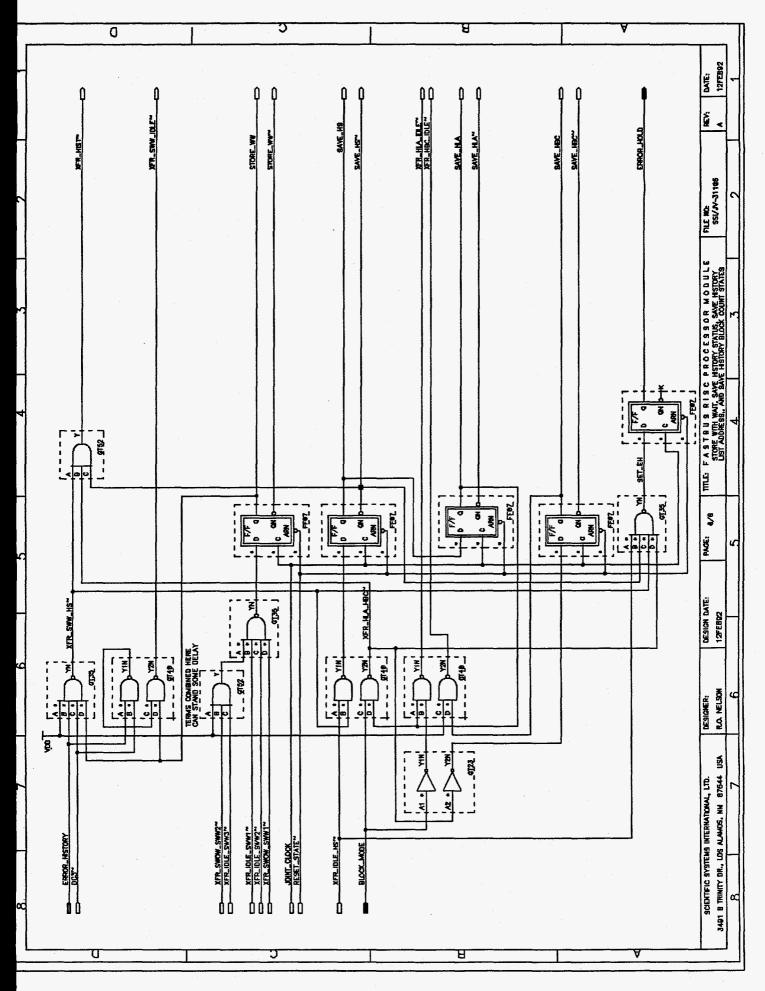

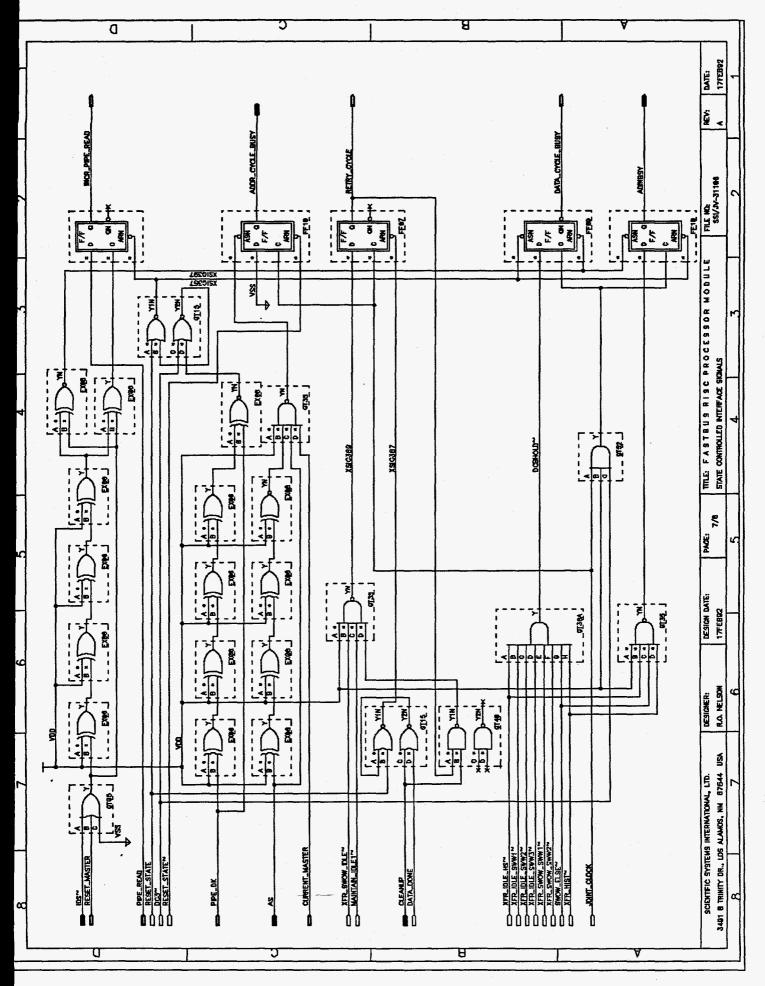

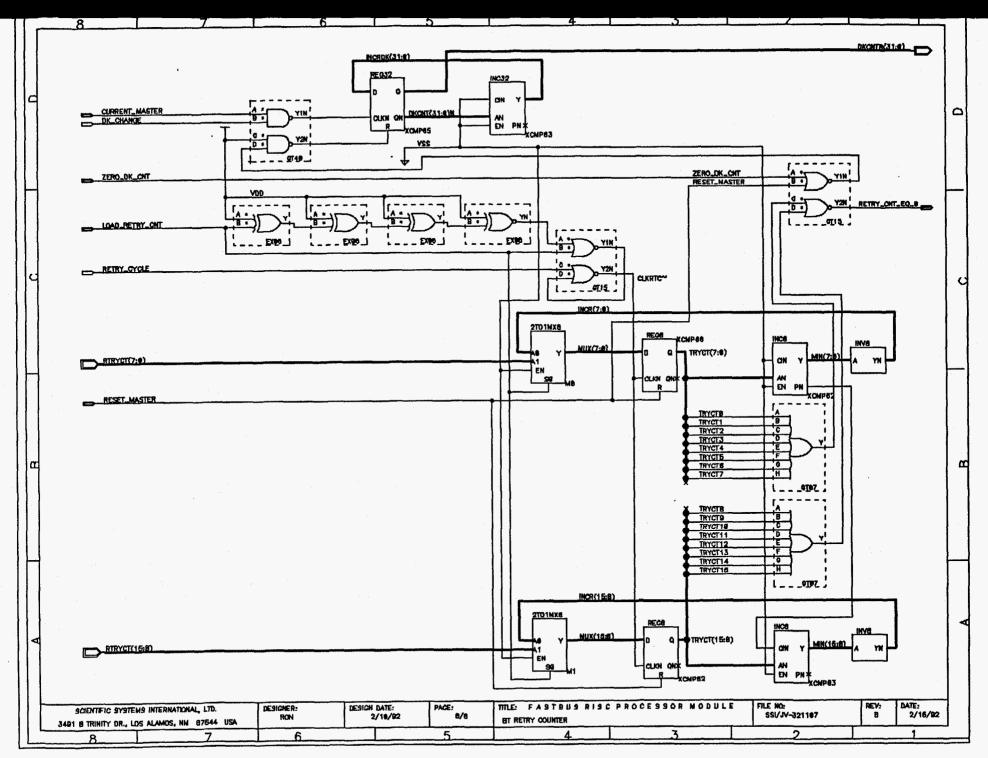

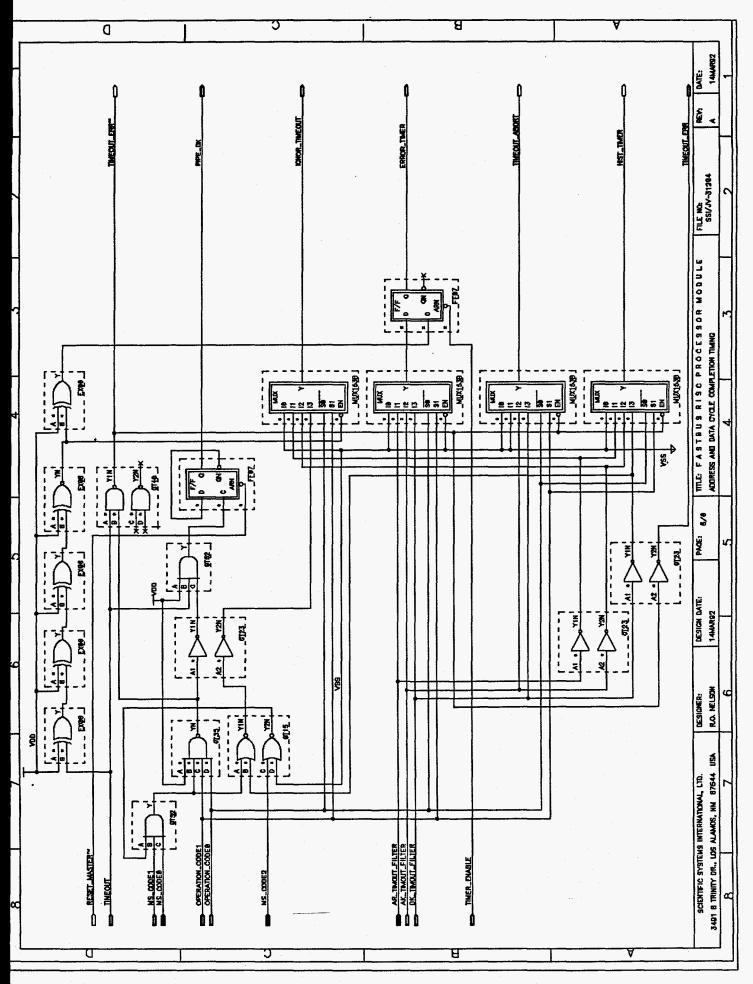

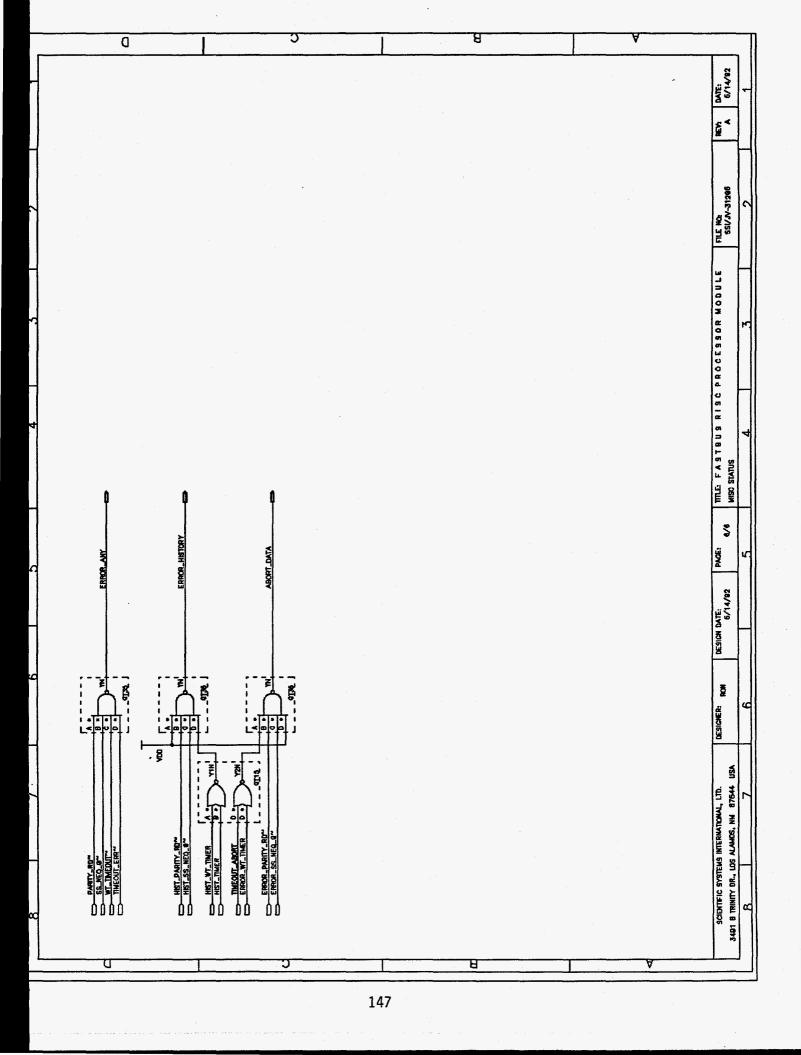

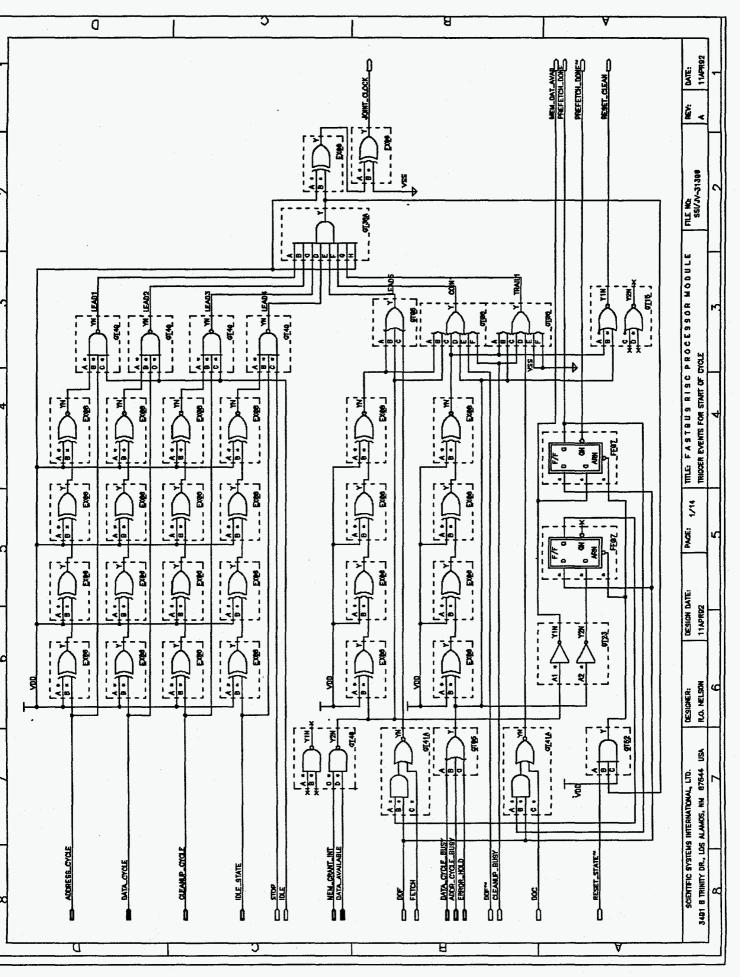

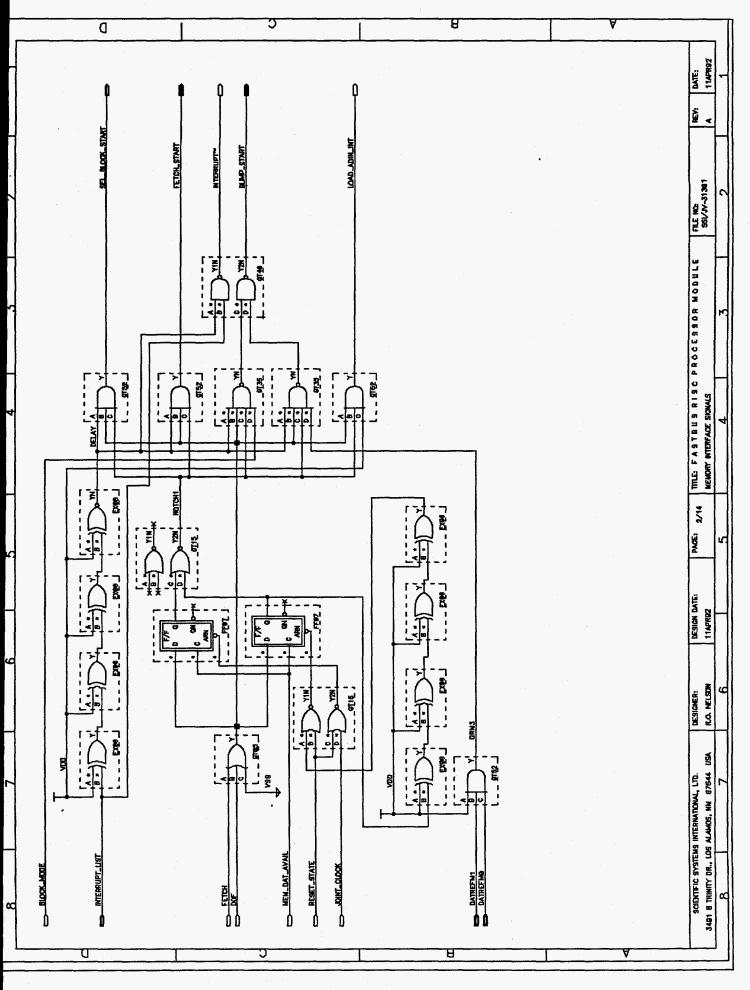

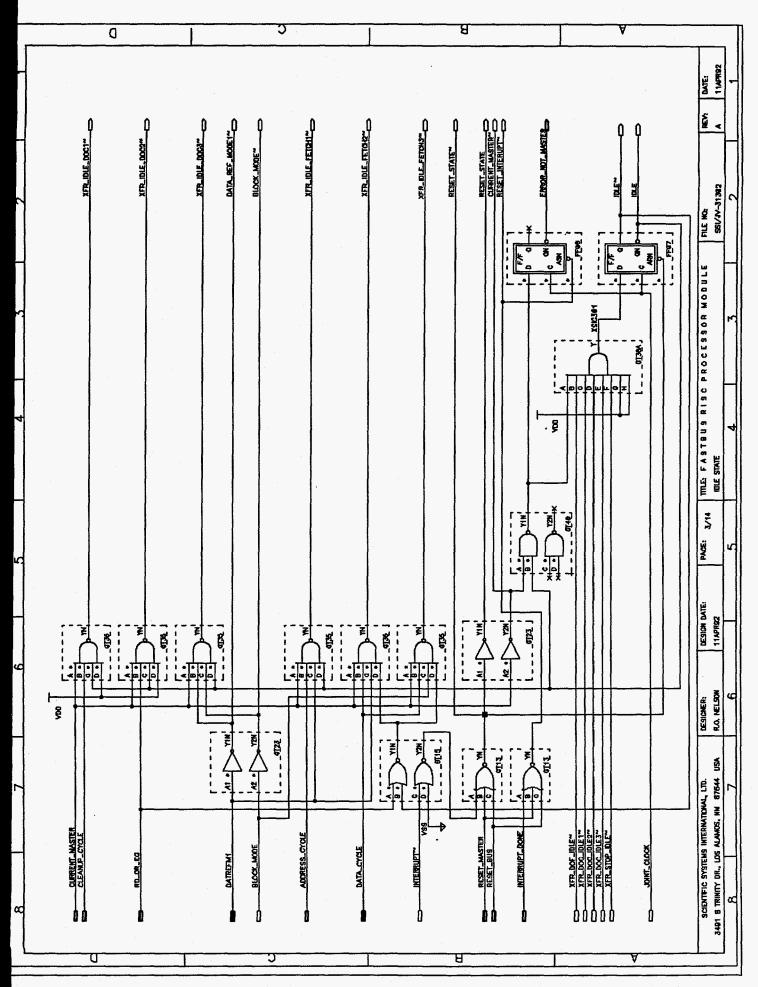

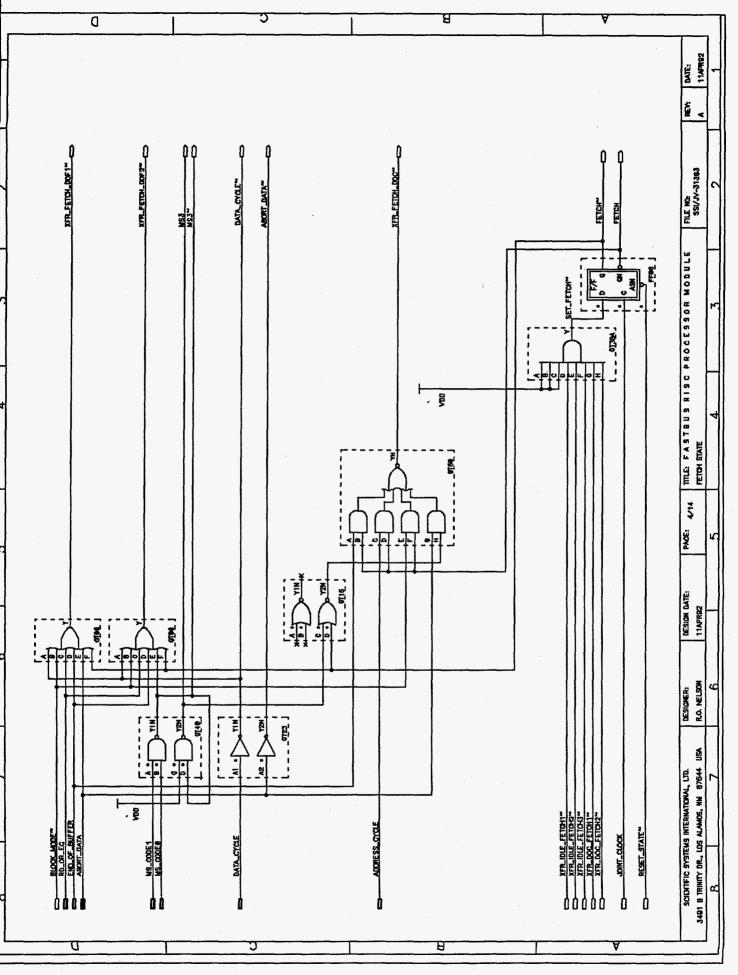

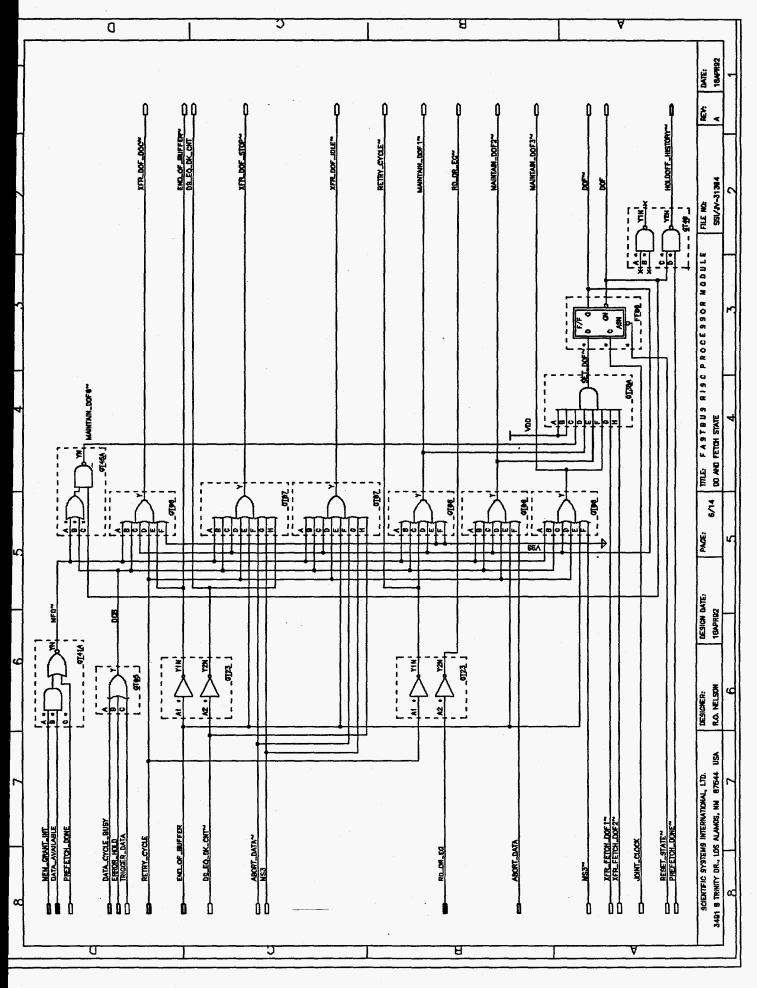

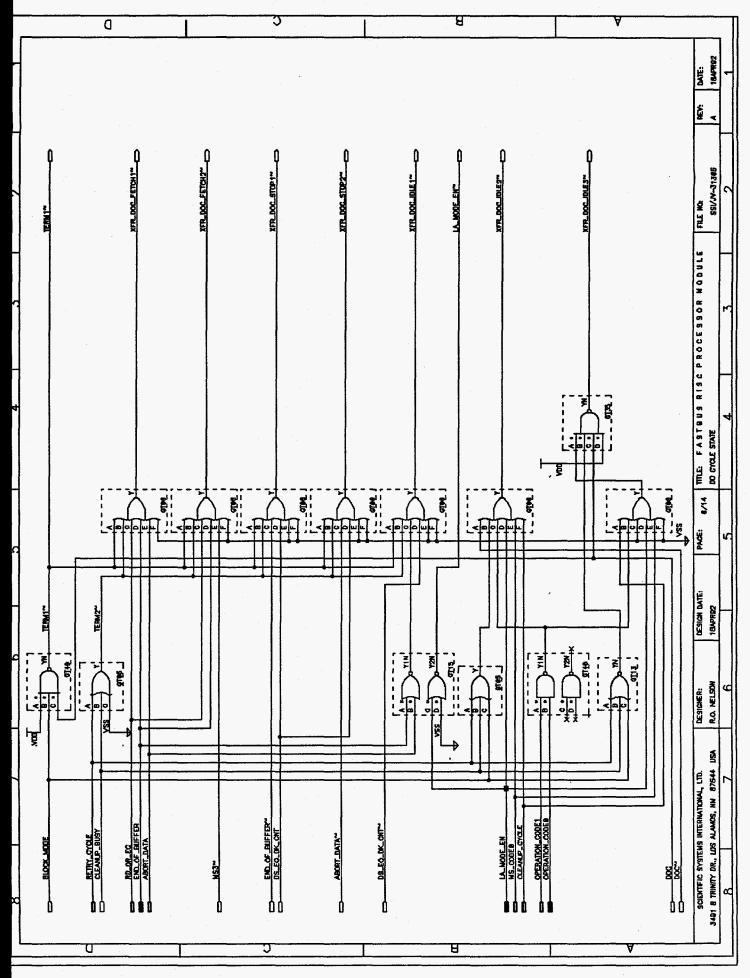

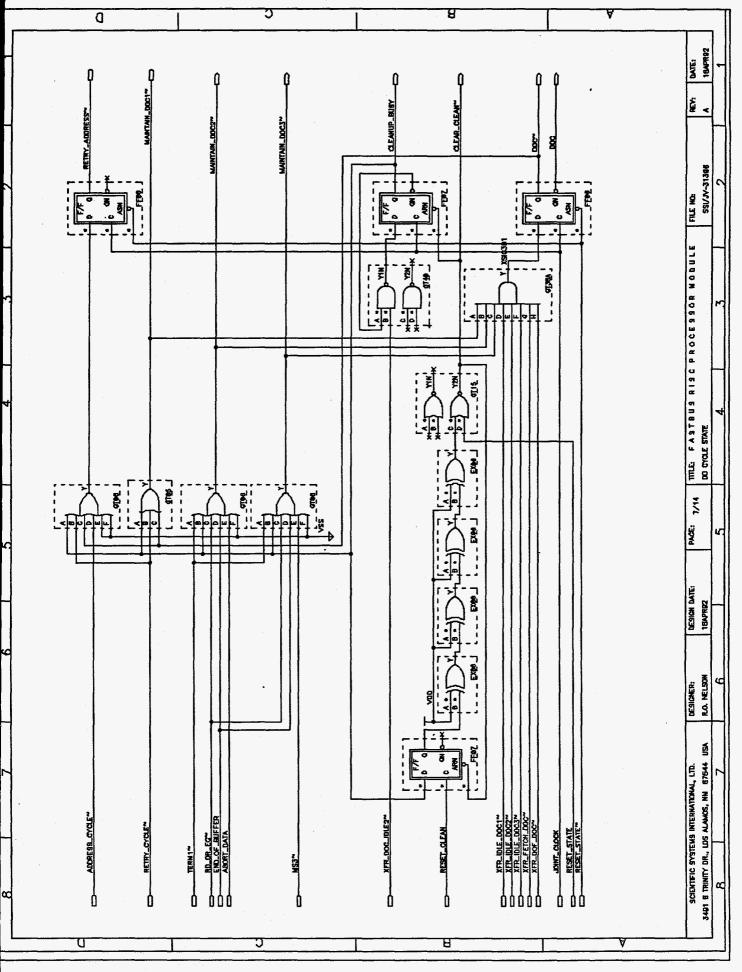

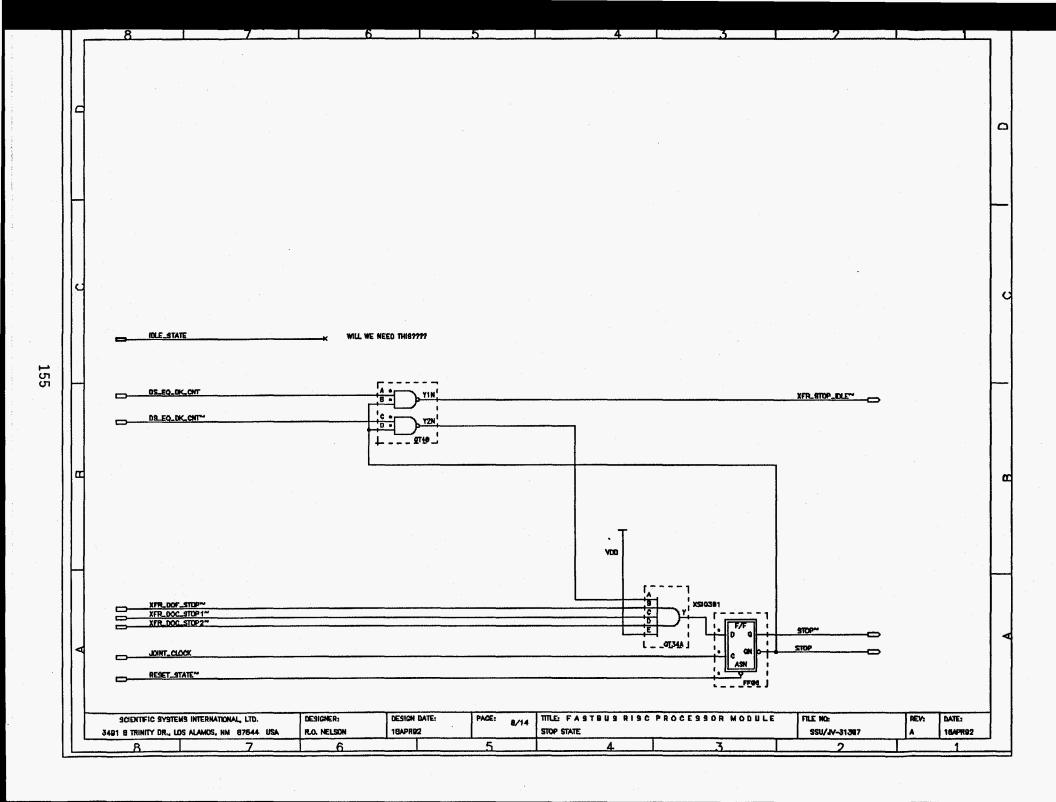

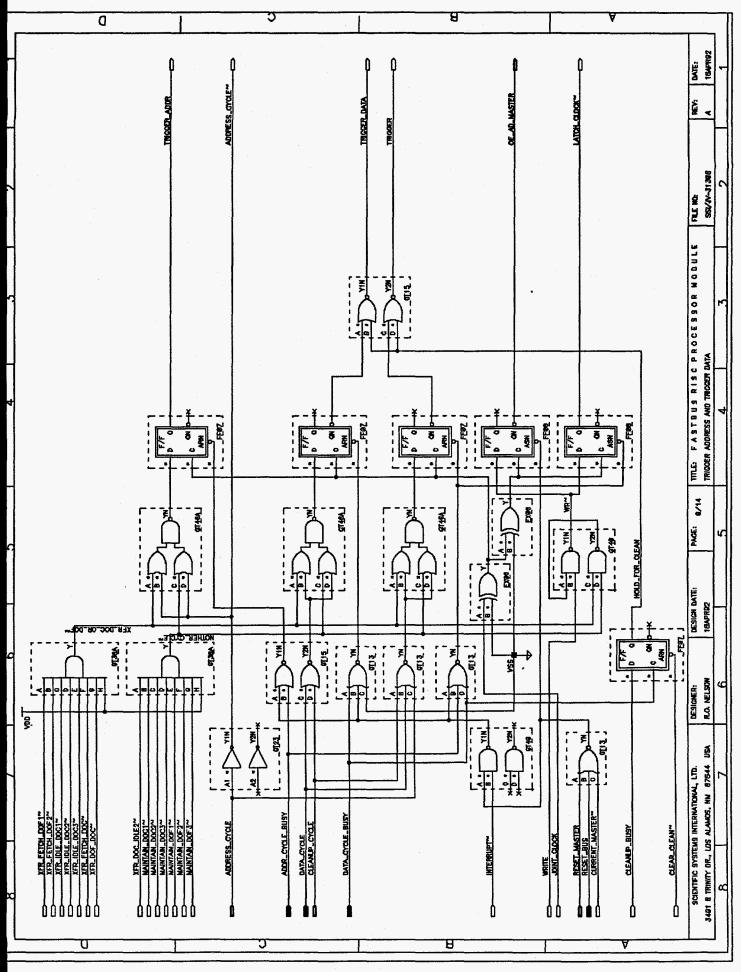

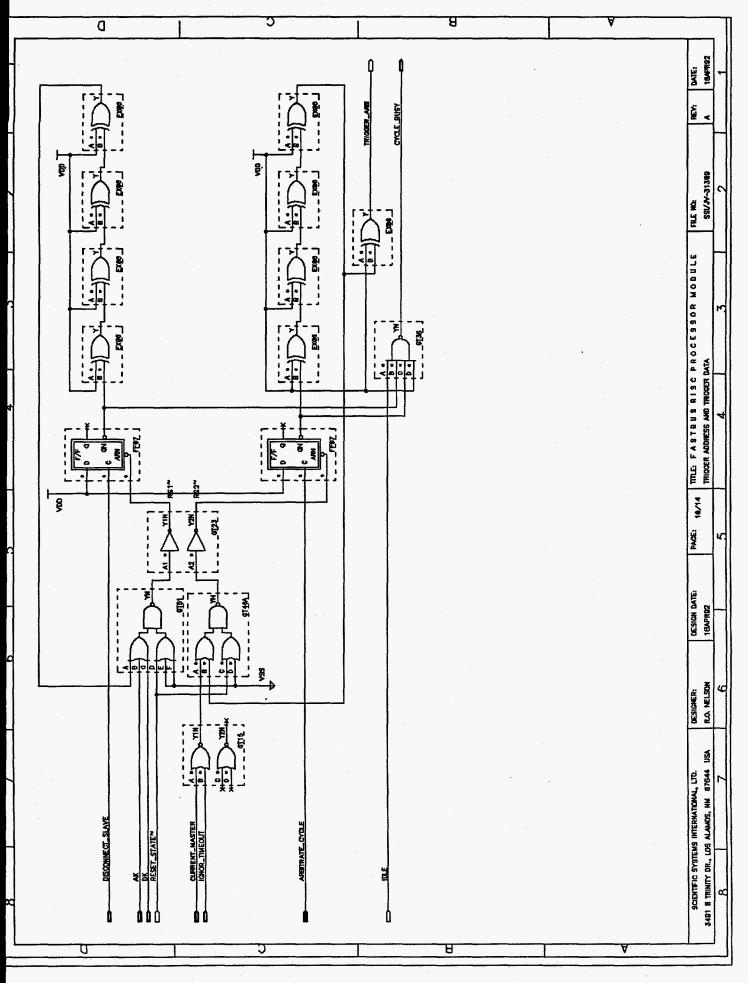

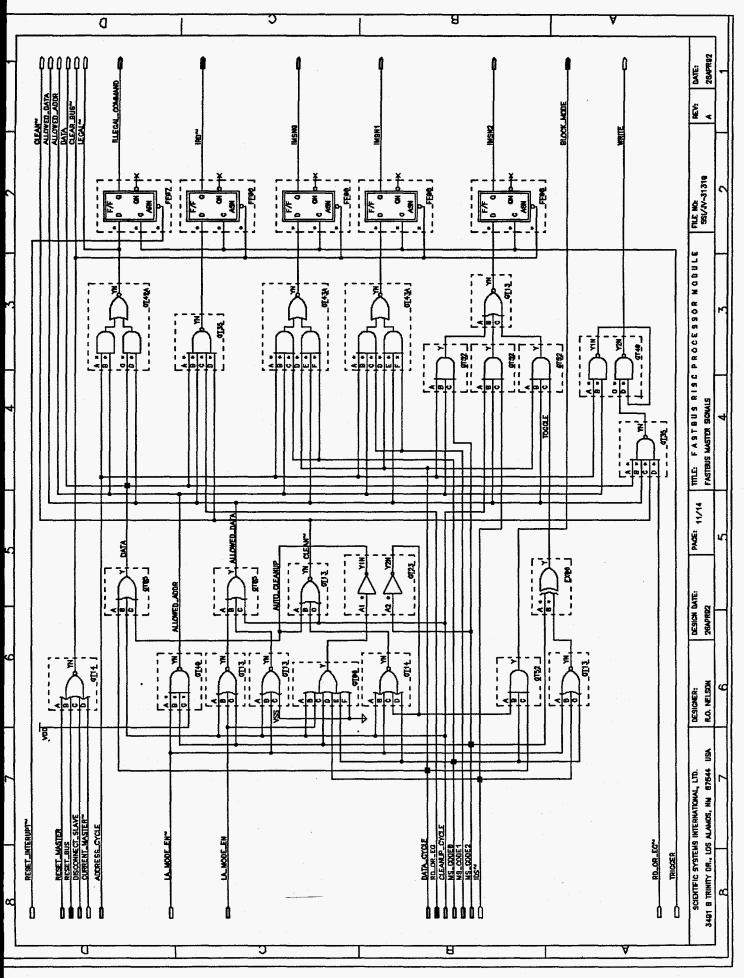

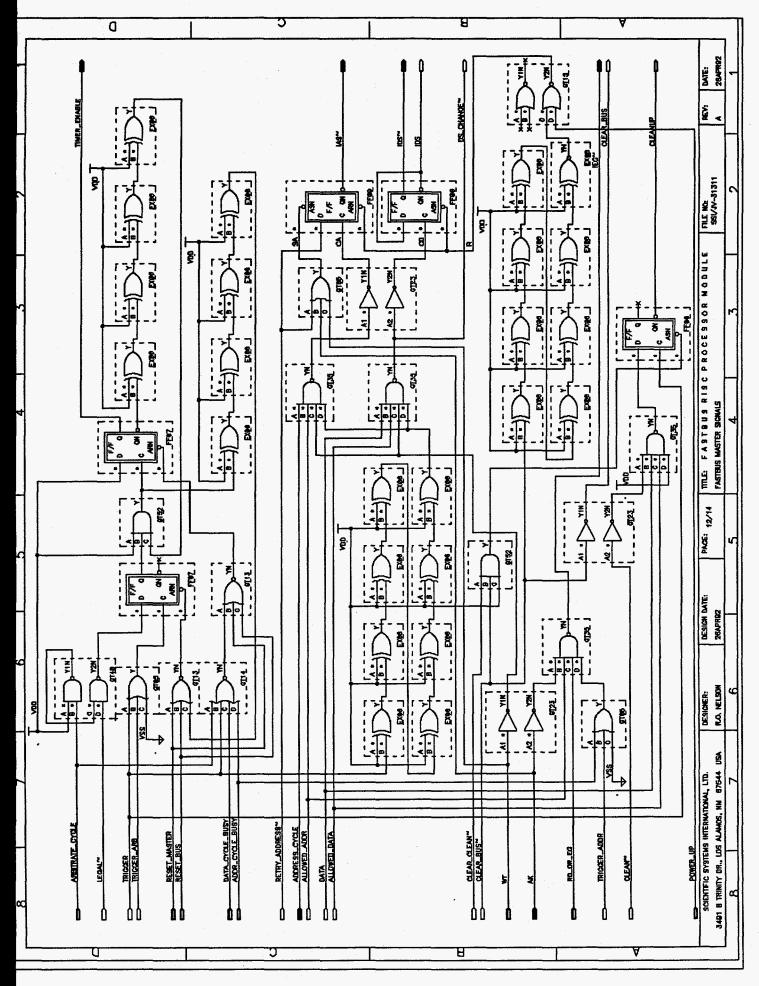

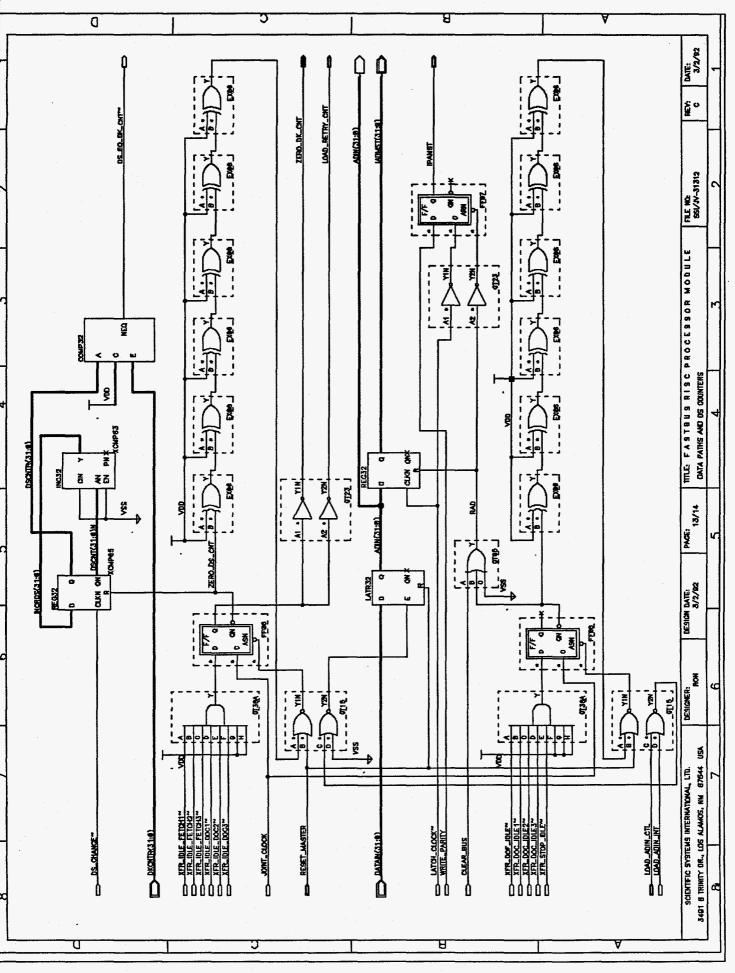

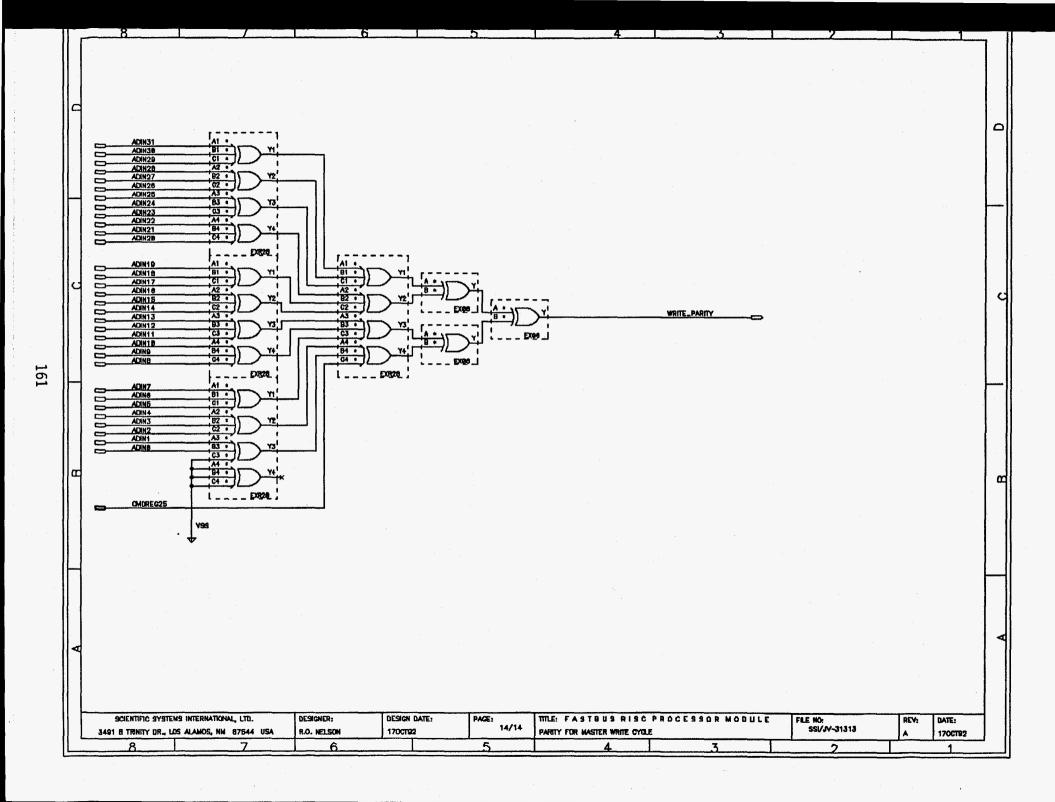

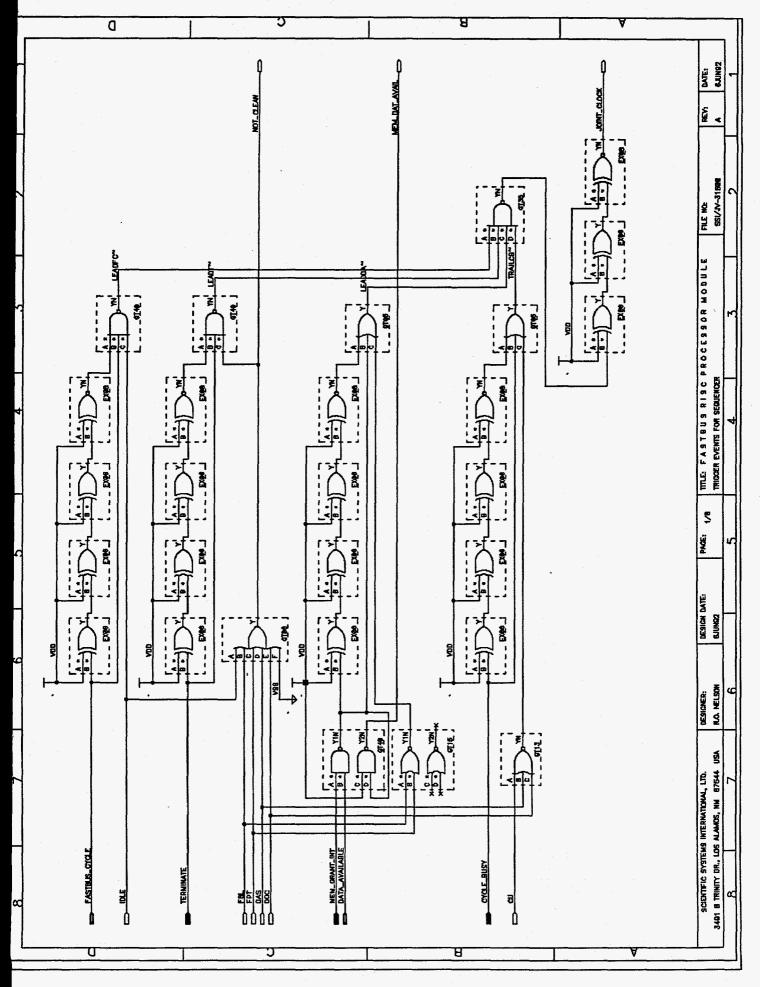

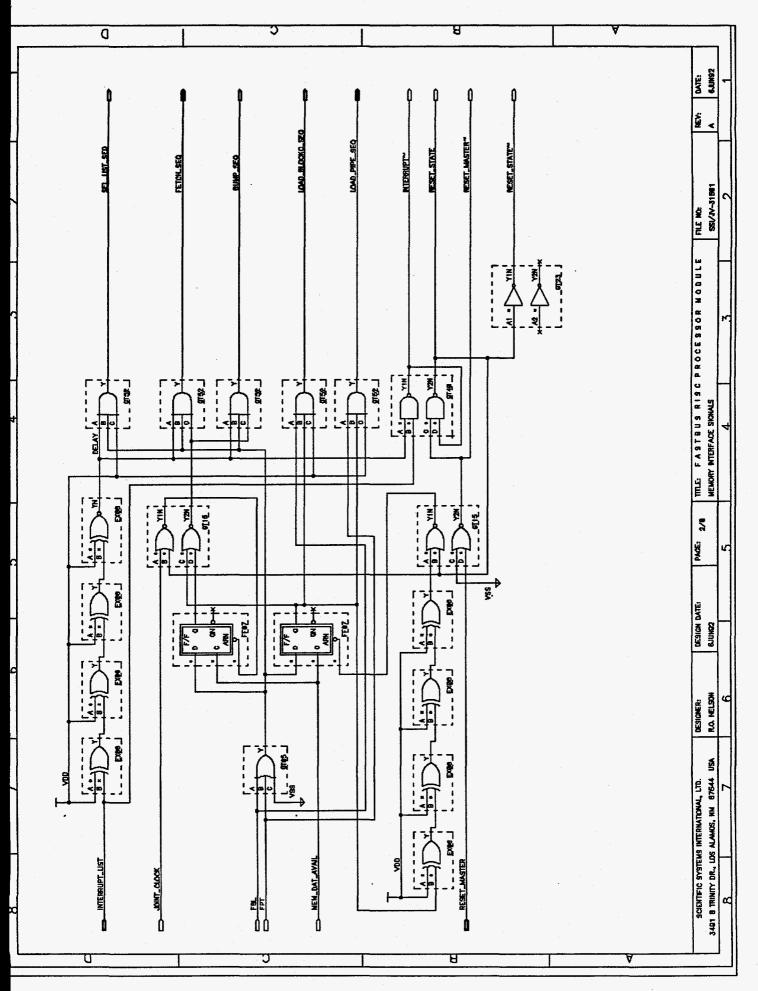

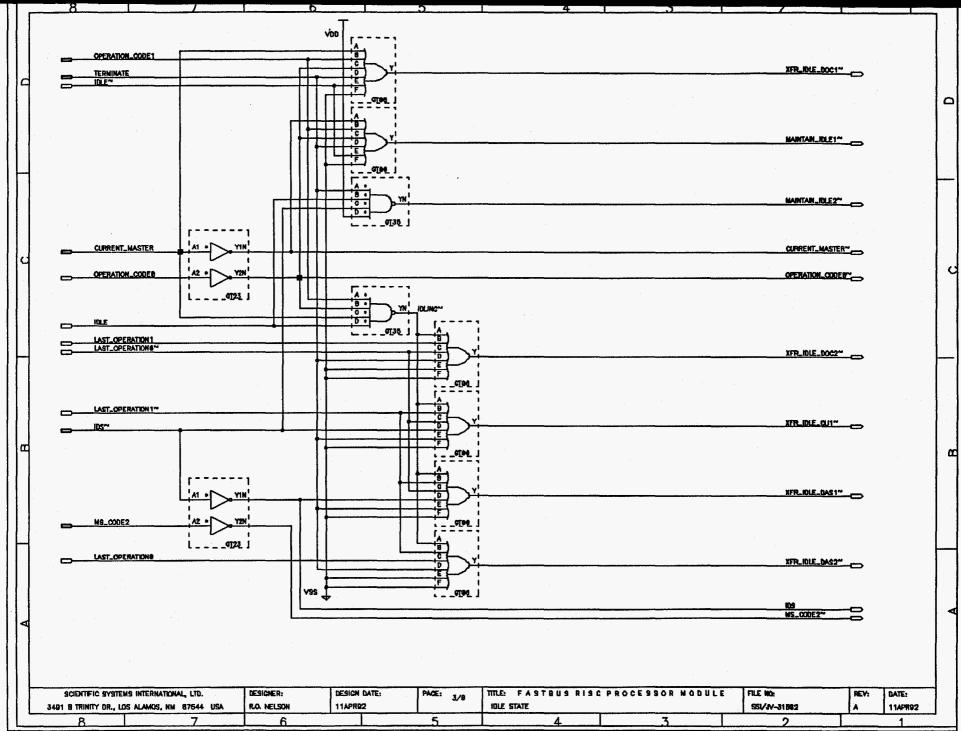

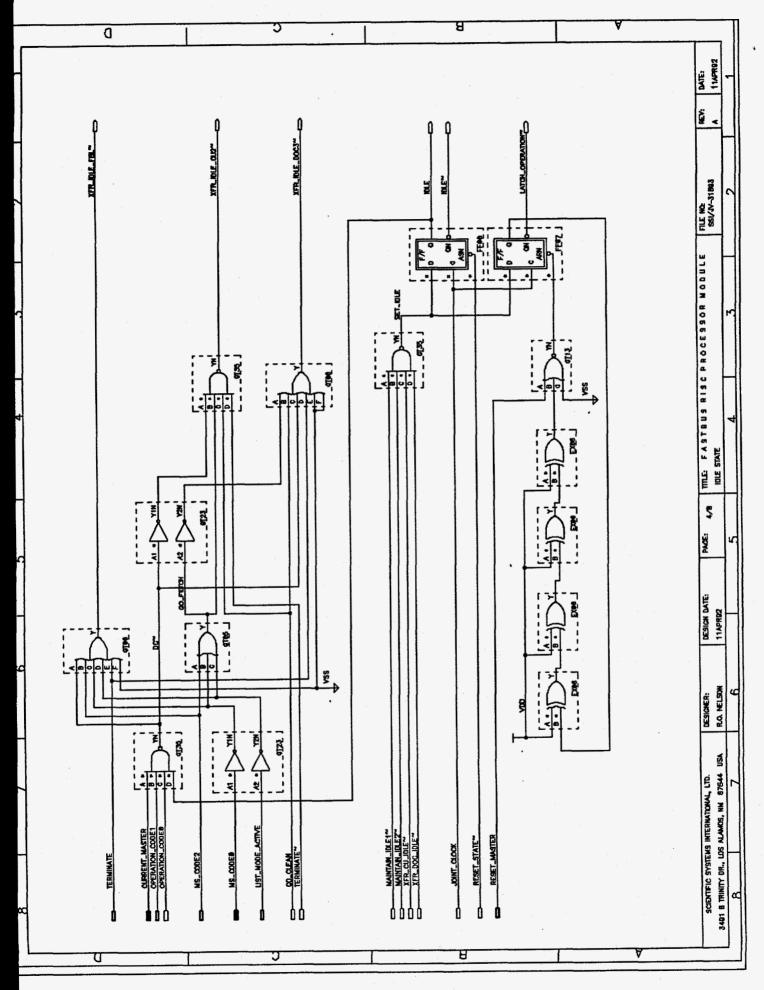

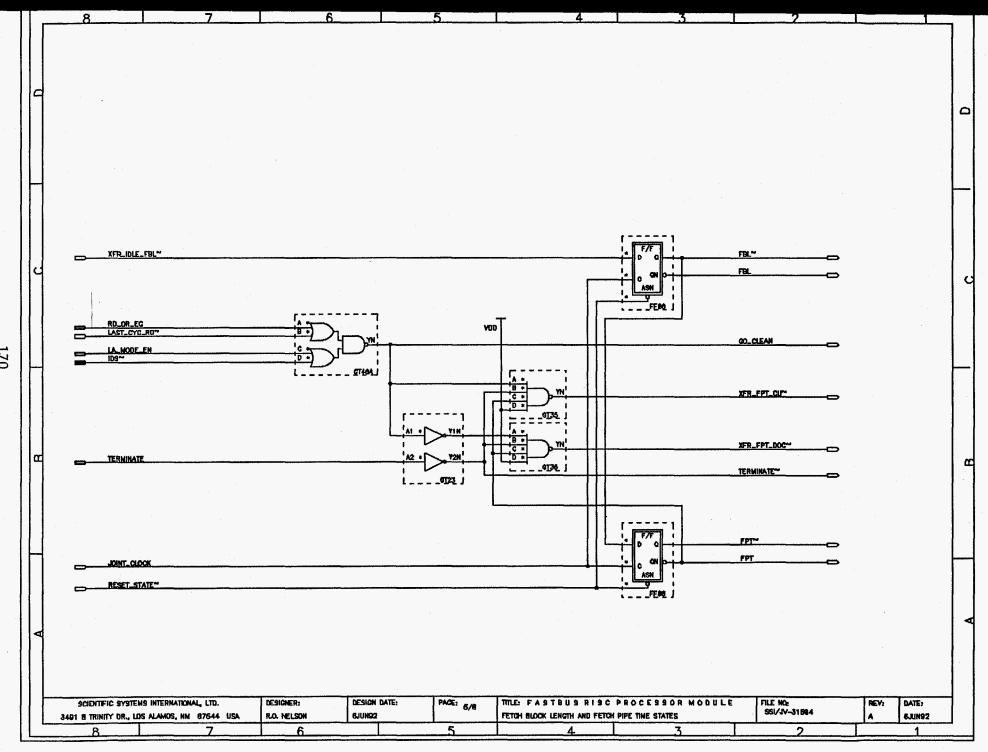

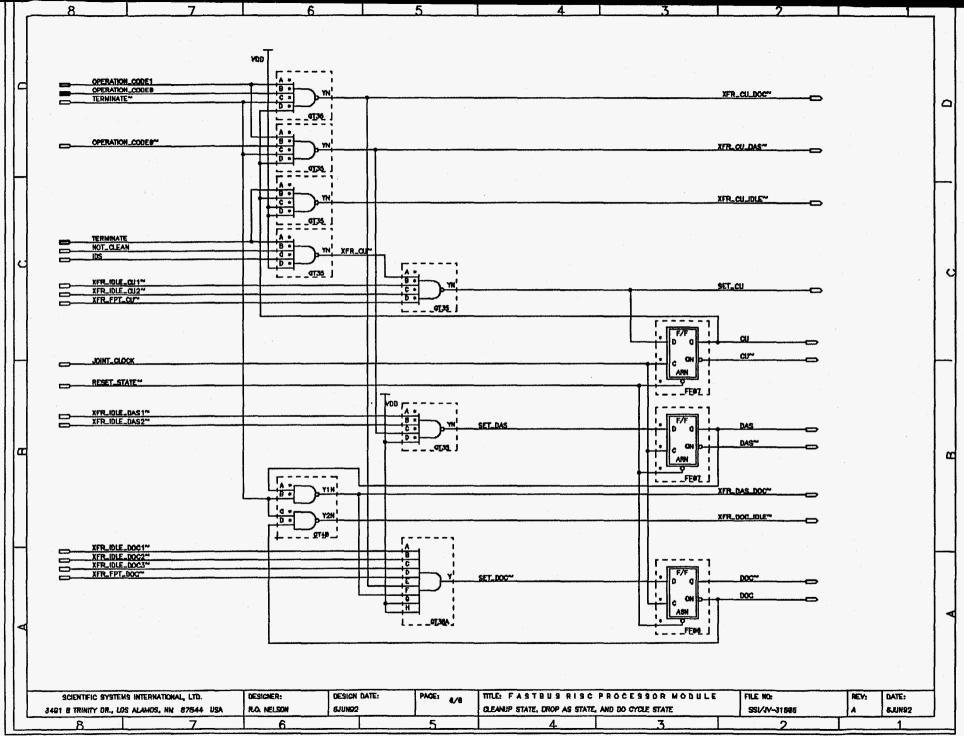

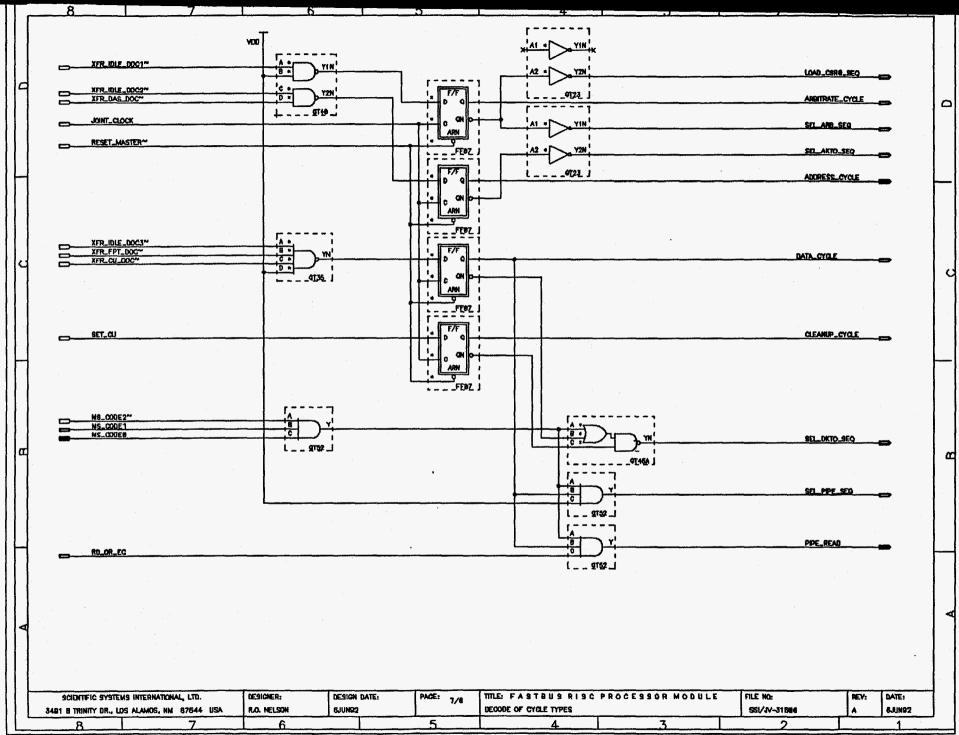

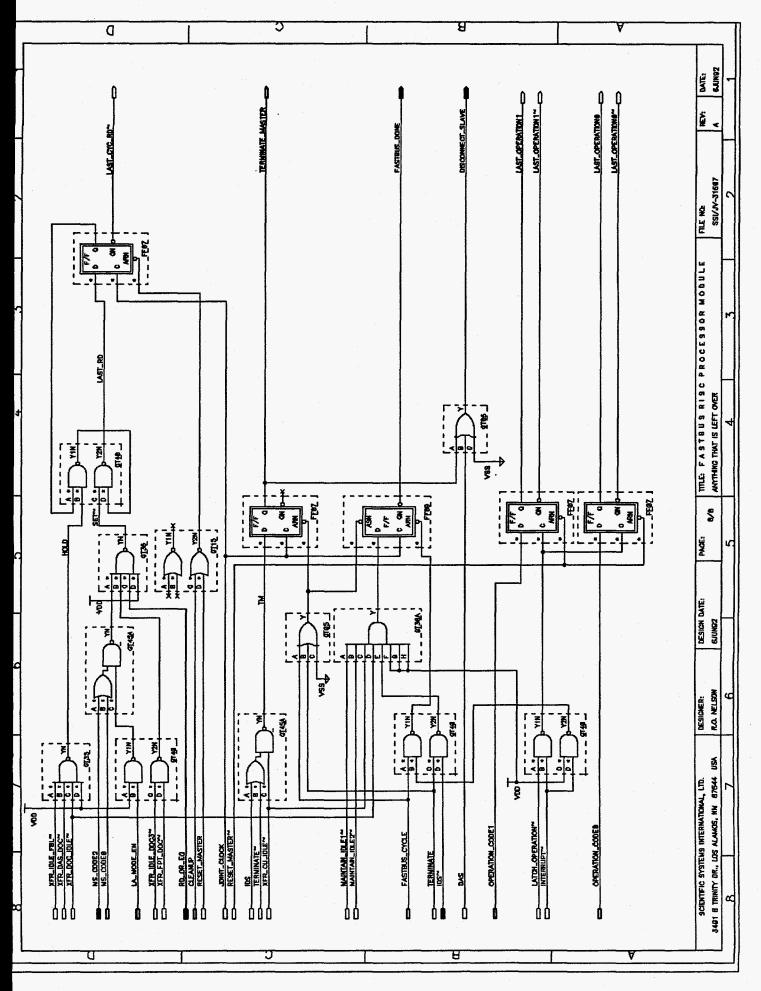

The schematic contained on page 24 is the simulation block diagram for the FRPM, while the schematic on page 25 is the SBus interface logic used to couple the SPARCengine interface bus to the FRPM master logic. Pages 26 through 38 contain the actual master logic interface that was completed and operationally tested during the Phase II effort. Prior to commiting the design to printed-circuit wiring layout, the entire design was simulated to test the operation of the interface.

NE

Ű

:7

,

.

# APPENDIX C FASTBS MASTER INTERFACE (FMI) GATE-ARRAY SPECIFICATIONS

# FASTBUS MASTER INTERFACE SPECIFICATION AND FUNCTIONAL REOUIREMENTS

#### ORIGINAL DOCUMENTATION PRIOR TO MODIFICATION OF THE SCOPE-OF-WORK

# 1. Introduction

The FASTBUS Master Interface (FMI) shall be a single-chip ASIC implementation of protocols defined by IEEE 960 for FASTBUS master devices. In addition the FMI shall include complete slave logic to perform all slave functions. Thus, modules acting primarily as master devices and necessarily as slave devices, will require only a single FASTBUS interface chip.

The FMI shall be controlled through a processor port. The port enables the processor to initiate arbitration, address, and data cycles, as well as other control functions described below. In addition the processor may initiate a series of FASTBUS operations and control functions, directed by a user-specified list contained in a memory and shared between the processor and FMI.

#### <u>1.1. Scope</u>

This document identifies the functional capabilities and interface features of the FMI. These requirements, resulting from studies performed during the Phase I research for the FASTBUS RISC Processor Module, represent compromises made between the set of all desirable features for FASTBUS masters, and the set of feasible implementations. While these requirements are not inflexible, they are established only after thorough research to direct and limit subsequent design and implementation.

#### 1.2. Interface Summary

The FMI shall implement a bus and a processor interface. The bus interface shall allow direct connection to the FASTBUS crate segment, and shall support all the protocol defined by IEEE 960 for master devices. The processor interface shall provide a single 64-bit path to the FMI that may be used in two modes. Seven other ancillary signals shall be provided to select the interface operation and provide timing controls. For the first mode of control, the interface path shall enable the processor to control each operation executed by the FMI. In this slaved mode, the FMI is totally dependent on the processor for control. The processor shall optionally supply data embedded in the control stream. For the second mode for control of the FMI, the interface path allows the FMI to fetch equivalent control and data information through a direct memory access (DMA) controller built into the FMI. The latter mode of operation permits the FMI to operate autonomously once triggered, and provides a high performance FASTBUS sequencer controlled by predefined lists of primitive FASTBUS operations stored in shared processor memory. Both modes shall use the list sequencer to deposit input data in memory.

## **1.3.** Functional Summary

The FMI shall provide direct FASTBUS I/O for a controlling processor, list driven FASTBUS sequences with data driven to/from memory via a list sequencer, flexible buffer management options, interrupts for exception handling, and primitive FASTBUS slave operations. Direct FASTBUS I/O shall allow the processor to execute simple FASTBUS operations such as arbitration cycles, address cycles, data cycles, and embedded control functions. The control functions allow the processor to alter the prevailing FASTBUS operating environment by changing the parameters set that characterizes the state and mode of the interface. Full FASTBUS transactions may be constructed with combinations of arbitration, address, and data cycles.

FASTBUS errors shall be reported as exceptions. When sequencing through a predefined list in memory, execution shall move data to/from user memory until the list terminates or an unexpected SS code is encountered. With each FASTBUS cycle, the user shall specify a filter that defines which SS codes or timeouts shall generate exceptions. The FMI response to an exception is handled in one of two ways: the list execution promptly terminates, or faults are saved in an exception list that is passed to the user upon completion of the FASTBUS operation list.

When processing FASTBUS operation lists, data references shall have three alternate mechanisms. First, the reference shall be immediate, i.e. the data itself is passed to the FMI from the memory. This immediate data shall be allowed for write operations only. Second, the reference shall provide an address for the data. Data shall be read/written at this address. Third, the reference shall provide the address of a data structure that manages a stack which shall provide/accept data. The mode of access shall be specified by the FASTBUS operation list.

The FMI shall support interrupts of two different forms: interrupt messages and service requests. The FMI shall support up to 16 interrupt receiver blocks, the maximum defined by IEEE 960.

# 1.4. Assumptions and Constraints

The memory and memory interface architecture shall not prevent the FMI from executing at the maximum speed permitted by the FASTBUS specification, IEEE 960. Therefore, a built-in list sequencer shall be provided within the FMI to achieve satisfactory

performance. Furthermore, the associated memory architecture should be optimized to minimize contention between the processor and the DMA.

The FMI shall be a memory-mapped I/O device. As such, the 64-bit data bus and 32-bit address bus shall be common to both processor access and list sequencer access to memory.

All addresses presented to the FMI from either the processor or the list sequencer shall be absolute addresses referencing physical memory. No address translation shall be provided.

## 2. Applicable Documents

#### 2.1. FASTBUS Documents

# 2.1.1. Hardware

IEEE Standard FASTBUS Modular High-Speed Data Acquisition and Control System, ANSI/IEEE Std 960-1986.

# 2.1.2. Software

FASTBUS Standard Routines, U. S. NIM Committee, May 1988.

#### <u>3. Requirements</u>

#### 3.1. Interface Requirements

#### 3.1.1. FASTBUS

Electrical characteristics of the FMI FASTBUS protocol pins shall conform with limits defined by the bus standard IEEE 960, such that the FMI may be directly connected to the FASTBUS crate segment. To drive the FASTBUS cable segment, these same signals shall be buffered with appropriate current-mode drivers.

Protocol for the FASTBUS signals shall also conform to the requirements of IEEE 960. All address and data cycle modes shall be supported including those known as advanced modes (first proposed in Los Alamos in August, 1987). The advanced modes allow data transfers to take place on each and every DS(t) except those specifically identified as bus cleanup cycles.

#### 3.1.2. Processor-directed I/O

If not processing a FASTBUS operation list, the FMI shall accept a processor-directed I/O sequence to alter the state or mode of the FMI and/or execute one or more FASTBUS primitive operations. Each command shall consist of one 64-bit word received by the FMI from the processor. Upon receipt of the command, the FMI shall initiate an asynchronous FASTBUS operation, or a synchronous non-FASTBUS operation. In either case, the processor shall await completion of the command before proceeding to the next command.

Processor-directed I/O shall be used to initiate list-directed I/O. Once initiated, the list-directed I/O shall have priority over processor-directed I/O. By checking a 32-bit FMI status register, the processor shall be able to determine that list-directed I/O is in progress and that attempts to initiate any other I/O shall be denied. Details of the internal formats for commands, data, and status for the FMI are included in Section 3.3.1.

# 3.1.3. List-directed I/O

List-directed I/O shall be initiated by processor-directed I/O. After initialization, the built-in list sequencer shall provide 64-bit word memory access for both control and data transfer. The behavior of the FMI shall be virtually identical for identical sequences of FMI commands independent of whether the sequence is received directly from the processor, or indirectly from the list sequencer fetching/storing 64-bit data words and commands.

Once initiated, list-directed I/O runs to completion, i.e. until the list terminates successfully, or the list prematurely terminates with an exception. The FMI shall notify the processor of list completion by issuing an interrupt.

Details of the internal formats for commands and data are included in Section 3.3.1.

#### 3.1.4. Configurability

The FMI chip shall be configurable with option enable pins permitting selection of various features. Separate pins shall be provided to enable use of internal registers CSR0, CSR3, CSR7, CSR8, CSR9, CSR1D, CSR1E, and CSR1F. With a set a five pins, a user shall be able to specify the width of the internal address field for logical addressing. Another option shall allow a user to select either SS = 1 or WT = 1 slave responses for internal busy conditions.

#### 3.1.5. Interface Signals

<u>3.1.5.1.</u> Processor Interface Signals All processor interface signals shall be used by the FASTBUS interface for access to data memory.

## Signal Description

ADDRESS(31:0) Address for internal memory mapped control registers accepted by FMI during processor-directed I/O operation. Address for command or data access asserted by FMI during list-directed I/O operation. Contents of NTA register during FASTBUS access to user application memory.

BUS\_GRANT Set by user application to indicate FMI has control of processor bus

BUS\_REQUEST Set by FMI to obtain control of processor bus.

BUS\_WRITE Set to indicate write operation on processor bus. Reset for read operation.

DATA\_ACK DATA\_ACK(t) asserted by memory when data accepted/asserted.

DATA\_IN(63:0) 64-bit wide input data/command bus. FASTBUS interface uses bits 31 to 0 only.

DATA\_OUT(31:0) 32-bit wide output data bus.

DATA\_REQUEST DATA\_REQUEST(t) asserted by FMI for memory to accept/assert data.

DATA\_TYPE(1:0) Selects data type on processor bus. For null operation, set = 0. For 32-bit transfer, set = 1. For 64-bit transfer, set = 2.

INTERRUPT\_EXCEPT Issued to the processor when an exception has been issued.

INTERRUPT\_FIM Issued to the processor when a FASTBUS interrupt message has been received in one of 16 message receiver blocks. INTERRUPT\_SR Issued to the processor when a service request has been received.

# 3.1.5.2. FASTBUS Interface Signals

All 60 FASTBUS signals shall be connected to the FMI. These are listed in IEEE 960, and are not repeated here.

Signal Description

ADDRESS\_CYCLE Asserted by FMI when module is initially addressed but reset once data cycles AK

ATTACH Command/status for slave attachment. Asserted by FMI to indicate module is attached. Asserted by user to force attachment at address time.

BLOCK\_MODE Asserted by FMI for either block or pipeline mode active.

BUSY Asserted by user signal indicate that a request has been received while the module is busy.

CLEAR\_DATA Asserted by FMI during CSR0 load if bit 31 is asserted.

CLEAR\_ERROR Asserted by FMI during CSRO load if bit 16 is asserted.

CSR0\_EN User signal indicating that CSR0 bits 0 to 5, bit 14, and bit 15 are supported on-board the FMI chip.

CSR0\_LOAD Asserted by FMI for load command of CSR0.

CSR0\_READ Asserted by FMI to indicate read command for CSR0.

CSR3\_EN User signal indicating that CSR3 internal to the FMI chip is used and that logical addressing is possible.

CSR7\_EN User signal indicating that CSR7 internal to the FMI chip is used and that case 2 (class N) broadcast addressing is possible.

CSR\_SPACE Asserted by FMI if CSR space is attached. EOB Asserted by user when end of block for block transfer or pipeline operation. LA\_MODE\_EN User signal indicating that advanced features of the FASTBUS protocol defined in the Los Alamos understanding are enabled.

LOGICAL\_ADDR\_EN Asserted by FMI when logical addressing is enabled with CSR0<1>.

LOGICAL\_WIDTH(4:0) User signals defining the width of the internal address.

NOT\_VALID Asserted by user to indicate the NTA address is not valid.

NTA\_CARRY\_IN Asserted by user to indicate whether the NTA will advance when incremented.

NULL\_CYCLE Asserted by FMI following address connectdisconnect without a data cycle.

PARITY\_ERROR Asserted by FMI when the FASTBUS data bus has wrong parity during data write cycles. User may use this signal to define SET\_ERROR\_FLAG and REJECT. Latched until CLEAR\_ERROR is sensed.

POWER\_UP Asserted by user when power has been applied to the user module.

RESET\_BUS Deglitched reset bus, RB.

READ Asserted by FMI to indicate read data cycle.

REJECT Asserted by user to indicate that bad data or bad addresses will result in rejected data.

RESET Asserted by FMI during CSR0 load if bit 30 is set or during periods when the user asserts POWER\_UP.

RESPONSE\_CTL\_IN Signal from user indicating that FMI may safely generate either AK or DK.

RESPONSE\_CTL\_OUT Signal to user indicating that module needs to generate either AK or DK. User logic may simply delay this signal and return the delayed version as RESPONSE\_CTL\_IN, or may implement more complex logic.

RUNNING Asserted when module is enabled to run with CSRO<2> = 1.

SET\_ERROR\_FLAG Asserted by user when error to be reported through CSRO<0>.

SET\_HALT Asserted by user when run mode latched by CSR0<2> is to be cleared.

SET\_SR Asserted by user when SR is desired.

SET\_SS3 Asserted by user when SS = 3 is to be generated.

SKEW\_IN Asserted by user when skew time has elapsed. Generally this is SKEW\_OUT passed through a fixed delay.

SKEW\_OUTAsserted when skew time interval required.

SR\_FLAG Asserted by FMI following receipt of SET\_SR from user. Reset when CSR0 loaded and bit 21 is set. Independent of the state of CSR0<4>.

TIMER\_IN Asserted by user to provide time intervals counted by master timers.

TRANSFER\_DONEDK-like handshake from user. Generated for all data cycles, even those internal to the FMI chip. Prerequisite for RESPONSE\_CTL\_OUT.

TRANSFER\_ENABLE Asserted by FMI to indicate that the user must either accept or assert data.

TRANSFER\_REQUEST DS-like handshake to user. Request may be read, write, or cleanup cycle in either CSR or data space. User logic may simply delay this signal and return the delayed version as TRANSFER\_DONE, or may implement more complex logic. WT\_EN User signal which if set high will generate WT when BUSY asserted until TRANSFER\_DONE indicates completion of transfer.

#### 3.2. Functional requirements

The FMI functions are divided into four categories: segment driver, service request receiver, segment salve, and interrupt receiver. Of these, the segment driver functions are far more complex and diverse. These functions and the comparatively simple function of the service request receiver are identified under master functions Section 3.2.1. The segment slave and interrupt receiver functions are identified as slave functions in Section 3.2.2.

# 3.2.1. Master Functions

The FMI shall support all mandatory IEEE 960 master specifications. The FMI shall generate bus arbitration cycles and geographical, logical, and broadcast address cycles. Supported data cycles shall include single word, secondary address, block, and pipeline cycles.

# 3.2.1.1. FASTBUS Cycles

The FMI shall provide building blocks from which arbitrary FASTBUS transactions may be constructed. These primitive operations shall consist of arbitration, address, and data cycles. Each 64-bit word from the processor or list sequencer may specify one such cycle. An operation code shall determine which cycle shall be executed, and the remaining bits shall supply other required parameters. The state of AS and GK following each cycle shall be considered an attribute of the primitive operation (see Sections 3.2.1.1.3.8 and 3.2.1.1.3.9).

# 3.2.1.1.1. Arbitration Cycle

An arbitration cycle shall be executed when the FMI receives the arbitrate cycle command from the processor or list sequencer and GK = 0. The format for the arbitrate command shall be as follows: Arbitration cycle command

| Bits  | Value | Description of field         |             |

|-------|-------|------------------------------|-------------|

| 63:62 | 2     | 1 Operation code             |             |

| 61:56 | 5     | 0                            |             |

| 55    | 0,1   | Hold GK after arbitration cy | <b>vcle</b> |

| 54    | 0,1   | Arbitration timeout filter   |             |

| 53:8  | Х     | Unused                       |             |

| 7     | 0,1   | Assured access enable        |             |

| 6     | 0,1   | Prioritized access enable    |             |

|       |       |                              |             |

5:0 1..63 Arbitration level

Bits 7 to 0 shall be loaded into the corresponding bits of CSR8. At the discretion of the user, it shall be possible to perform arbitration cycles without executing any address or data cycles. Failure to successfully arbitrate for the bus shall result in continued reties until arbitration timeout occurs as specified in Section 3.3.1.3.1. The arbitration timeout filter defined by bit 54 shall determine whether an exception is generated or not.

# 3.2.1.1.2. Address Cycle

An address cycle shall be executed when the FMI receives the address cycle command from the processor or list sequencer, GK = 1, and the FMI is the bus master. The format for the address command shall be as follows:

Address cycle command

| Bits  | Value | 9      | Description                         |

|-------|-------|--------|-------------------------------------|

| 63:62 | 2     | 2      | Operation code                      |

| 61:59 | )     | 07     | MS code for address cycle           |

| 58    | 0,1   | Gene   | rate EG                             |

| 57    | 0,1   | Gene   | rate parity                         |

| 56    | 0,1   | Hold   | AS after address cycle              |

| 55    | 0,1   | Hold   | GK after address cycle              |

| 54    | 0,1   | Enab   | le advanced MS codes                |

| 53:47 | 7     | Х      | SS response exception filter        |

| 46:44 | ł .   | Х      | Timeout exception filter            |

| 43    | 0,1   | Parity | y error from slave exception filter |

| 42:34 | 1     | Χ      | Unused                              |

| 33:32 | 2     | 02     | Data reference mechanism            |

| 31:0  | X     | Data   | reference                           |

The MS code and EG for the resulting address cycle shall be specified by bits 61:59 and bit 58, respectively.

At the discretion of the user, it shall be possible to perform address cycles without executing any data cycles.

# 3.2.1.1.3. Data Cycle

A data cycle shall be executed when the FMI receives the data cycle command from the processor or list sequencer, AK = 1, and the FMI is the bus master. The format for the data command shall be as follows:

Data cycle command

| Bits  | Value | Description    |

|-------|-------|----------------|

| 63:62 | 2 3   | Operation code |

- 61:59 0..7 MS code for data cycle

- 58 0,1 RD selector

- 57 0,1 Generate parity

- 56 0,1 Hold AS after data cycle

- 55 0,1 Hold GK after data cycle

- 54 0,1 Enable advanced MS codes

- 53:47 X SS response exception filter

- 46:44 X Timeout exception filter

- 43 0,1 Parity error from slave exception filter

- 42:34 X Unused

- 33:32 0..2 Data reference mechanism

- 31:0 X Data reference

The MS code and RD for the resulting address cycle shall be specified by bits 61:59 and bit 58, respectively.

Data cycles shall be initiated at DS(t) and terminated at DK(t). For read cycles (RD = 1), the FMI shall latch the slave supplied data at data cycle termination. For write cycles (RD = 0), the FMI shall assert data on the AD bus before cycle initiation as required by IEEE 960.

Data cycles function shall be sensitive to the phase of DS at DS(t) and to the MS mode at DS(t). The following table defines the function for each possibility:

Data cycle type

- MS DS(u) DS(d)

- 0 Single word Bus cleanup

- 1 Block Block

- 2 Load NTA(PA) for RD = 0 Bus cleanup Read NTA for RD = 1

- 3 Pipeline Pipeline

- 4 Bus cleanup Single word

- 5 Protective buffer Protective buffer

- 6 Bus cleanup Load NTA(PA) for RD = 0Read NTA for RD = 1

- 7 Load NTA(PA~) for RD = 0 Load NTA(PA~) for RD = 0Read CSR0 for RD = 1 Read CSR0 for RD = 1

References to NTA(PA) denote a space switch to that space selected at primary address time, coupled with load of the NTA register. Reference to NTA(PA~) is similar except that space selected is opposite to that selected at primary address time. If the advanced MS codes are disabled, then MS codes 4-7 are reserved and the FMI shall not use them.

#### 3.2.1.1.3.1. Single Word Cycle

The single word cycle shall always be selected by the data cycle command with MS field set to 0. If the advanced MS codes are enabled, then the FMI shall optimize FASTBUS performance by issuing either MS = 0 or MS = 4.

#### 3.2.1.1.3.2. Secondary Address Cycle for NTA(PA)

The secondary address cycle for the space selected at address time shall always be selected by the data cycle command with MS field set to 2. If the advanced MS codes are enabled, then the FMI shall optimize FASTBUS performance by issuing either MS = 2 or MS = 6. Read secondary address commands shall not be sensitive to the space selected at address time and shall not change the selected space.

# 3.2.1.1.3.3. Secondary Address Cycle for NTA(PA~)

The secondary address cycle for the space opposite to that selected at address time shall be selected by the data cycle command with MS field set to 7 and with RD = 0. If the advanced MS codes are not enabled, then the FMI shall issue an exception indicating an illegal command.

The read secondary address command shall not be sensitive to the space selected at address time. MS = 2 shall be used to read the secondary address register. MS = 7 with RD = 1 shall have a separate function (see Section 3.2.1.1.3.4).

#### <u>3.2.1.1.3.4. CSR0 Read Cycle</u>

The CSRO read cycle shall be selected by the data cycle command with MS field set to 7 and with RD = 1. If the advanced MS codes are not enabled, then the FMI shall issue an exception indicating an illegal command.

The read CSR0 command shall not be sensitive to the space selected at address time and shall not change the selected space.

The implementation of this advanced mode CSR0 read cycle shall in no way interfere with standard technique for reading CSR0 using a primary address cycle to CSR space, a secondary address write cycle with value zero, and finishing with a single word cycle to read.

#### <u>3.2.1.1.3.5. Block or Pipeline Cycle</u>

Block transfers or pipeline transfers shall include one additional 64bit word to define the block length for the transfer. The format for the block length shall be as follows:

#### Block length

| Bits  | Value | e Desci     | ription                                  |

|-------|-------|-------------|------------------------------------------|

| 63    | 0,1   | Enable NTA  | A post increment                         |

| 62    | 0,1   | Enable use  | of blocklets                             |

| 61:48 | 3     | 016K        | Pipelined transfer data cycle clock time |

| 47:32 | 2     | 064K        | Blocklet size                            |

| 31:0  |       | Block lengt | h in 32-bit words                        |

|       |       | . –         |                                          |

The block/pipeline command shall not be executed until the block length is received.

Block transfer cycles shall be selected by the data cycle command with MS field set to 1.

Pipeline transfer cycles shall be selected by the data cycle command with MS field set to 3. The pipelined transfer data cycle clock time shall be the count of TIMER\_IN(u) transitions allowed during each data cycle.

The block or pipeline command shall resolve the reference address according to the specified reference mechanism and then copy the address and block length into internal DMA registers.

### <u>3.2.1.1.3.6. Protective Buffer Cycle</u>

The protective buffer cycle shall be selected by the data cycle command with MS field set to 5. If the advanced MS codes are not enabled, then the FMI shall issue an exception indicating an illegal command.

# 3.2.1.1.3.7. Bus cleanup Cycle

A bus cleanup cycle shall be generated when a read cycle is followed by a write data cycle.

#### 3.2.1.1.3.7.1. Explicit

The bus cleanup cycle shall be selected by the data cycle command with MS field set to 4. If the advanced MS codes are enabled, then the FMI shall optimize FASTBUS performance by selecting either MS = 4 or MS = 0. If the advanced MS codes are not enabled, then the FMI shall issue an exception indicating an illegal command.

# 3.2.1.1.3.7.2. Implicit

A bus cleanup cycle shall be inserted at DS(d) after a data cycle command that begins on DS(u) and enables the advanced MS codes if it is followed by a data cycle command that disables the advanced MS codes.

If the data cycle command does not enable the advanced MS codes, a bus cleanup cycle shall be generated following each single word or secondary address cycle.

#### 3.2.1.1.3.8. AS Release

During all cycle commands following an primary address cycle, AS = 1 shall be maintained if bit 56 of the cycle command is set. AS = 0 shall be maintained after a cycle where bit 56 of the cycle command is reset.

Once AS(d) occurs, the FMI shall maintain AS = 0 until another primary address cycle successfully completes independent of the state of bit 56 of the cycle command.

# 3.2.1.1.3.9. Bus Release

During all cycle commands following arbitration, GK = 1 shall be maintained if bit 55 of the cycle command is set. GK = 0 shall be maintained after a cycle where bit 55 of the cycle command is reset. If GK = 0 is currently maintained, GK may be switched to GK = 1 at any cycle command assuming that the FMI remains the current bus master and that bit 55 of the cycle command is set.

## 3.2.1.1.3.10. Generate Parity

For address cycles and data write cycles, bit 57 shall enable parity generation. If set, parity, PA, shall be generated, and PE = 1. If reset, then PE = 0 and PA = 0.

#### 3.2.1.1.3.11. Enable Advanced MS Codes

For address and data cycles, bit 54 shall enable use of the advanced MS codes. If bit 54 is set, then the advanced MS codes shall be enabled. This document does not yet specify the use of advanced modes for address cycles. See section 3.2.1.1.3 for the use of advanced modes during data cycles.

# 3.2.1.2. Control Operations

A control operation shall be executed when the FMI receives a command from the processor or list sequencer, and the format for the command is as follows:

Control command

Bits Value Description

63:62 0 Operation code

61:54 0..255 Control function code

53:0 X Control parameters

The control function code field shall provide the means to decode additional commands other than FASTBUS cycle commands.

# 3.2.1.2.1. Reset Bus Command

The reset bus command shall be executed when the FMI receives a command from the processor or list sequencer, and the format for the command is as follows: Reset bus command

Bits Value Description 63:54 1 Function control code 53:0 X Unused

The reset bus command shall set RB = 1, and after an interval defined in IEEE 960, shall reset RB = 0. The FMI shall not be required to be bus master for the reset bus operation.

# 3.2.1.2.2. Write Parameter Command

The write parameter command shall be executed when the FMI receives a command from the processor or list sequencer, and the format for the command is as follows:

#### Reset bus command

Description Bits Value

| 63:54 | 2 Fur | iction control code          |

|-------|-------|------------------------------|

| 53:46 | 0255  | Base register offset address |

- 46:34 Х Unused

- 33:32 0..2 Data reference mechanism

- 31:0 X Data reference

The write parameter command shall write the parameter from the location specified from the location specified through the data reference mechanism to the FMI internal register specified by the base register offset address. See Section 3.3.1 for a list of the displacements.

# 3.2.1.2.3. Read Parameter Command

The read parameter command shall be executed when the FMI receives a command from the processor or list sequencer, and the format for the command is as follows:

Reset bus command

| Bits Value | e Description                     |

|------------|-----------------------------------|

| 63:54      | 3 Function control code           |

| 53:46      | 0255 Base register offset address |

| 46:34      | X Unused                          |

| 33:32      | 02 Data reference mechanism       |

| 31:0 X     | Data reference                    |

The read parameter command shall copy the parameter specified by the base register offset address to the location specified through the data reference mechanism. See Section 3.3.1 for a list of the displacements. An immediate reference shall be illegal for the read parameter command. If attempted, an exception shall indicate an illegal command.

# 3.2.1.2.4. Write FASTBUS Lines Command

The FMI could have an extremely primitive capability to write the 60 FASTBUS protocol lines enabling operation in a mode often useful for debugging hardware. It remains to determine whether this level of operation is desirable for the FMI.

#### 3.2.1.2.5. Read FASTBUS Lines Command

The FMI could have an extremely primitive capability to read the 60 FASTBUS protocol lines enabling operation in a mode often useful for debugging hardware. It remains to determine whether this level of operation is desirable for the FMI.

# 3.2.1.2.6. Execute List Command

The execute list command shall be executed when the FMI receives a command from the processor and the format for the command is as follows:

Execute list command

| Bits Value | e      | Description                 |

|------------|--------|-----------------------------|

| 63:54      | 8      | Function control code       |

| 53:32      | Х      | List length in 32-bit words |

| 31:0 X     | List a | ddress                      |

The execute list command shall include one additional 64-bit word to define the storage for the status history. The format for the status history storage shall be as follows:

Status history storage

| Bits Value | e Description                |

|------------|------------------------------|

| 63:32      | Block length in 32-bit words |

| 31:0       | Storage address              |

The execute list command shall not be executed until the status history storage is received.

The execute list command shall copy the list address, list length, status history storage address, and status history storage length into internal DMA registers, and initiate the list sequencer for listdirected operation. The processor interface shall be disabled for commands until the list execution either terminates or aborts with an exception.

If the execute list command is encountered during list-directed execution, the command shall be treated as a null operation.

## <u>3.2.1.2.7. Terminate List Command</u>

The terminate list command shall be executed when the FMI receives a command from the list sequencer, and the format for the command is as follows:

Terminate list command

| Bits Value | 3    | Description           |

|------------|------|-----------------------|

| 63:54      | 9    | Function control code |

| 53:0 X     | Unus | ed                    |

The terminate list command shall terminate list sequencer activity, and enable the processor interface for commands. If received from the processor, this command shall be treated as a null operation.

#### 3.2.1.2.8. Reset Segment Driver Command

The reset segment driver command shall be executed when the FMI receives a command from the processor or list sequencer, and the format for the command is as follows:

Reset segment driver commandBitsValueDescription63:5410Function control code53:0XUnused

The reset segment driver command shall act as a programmable reset command. The segment driver shall reset its internal state to that obtained after power-up initialization. Any list sequencer activity shall terminate and the processor interface shall be enabled to receive commands.

#### 3.2.1.2.9. Reset Interrupt Receiver Command

The reset interrupt receiver command shall be executed when the FMI receives a command from the processor or list sequencer, and the format for the command is as follows:

Reset segment receiver command

Bits Value Description

63:54 11 Function control code

53:0 X Unused

The reset interrupt receiver command shall act as a programmable reset command. The interrupt receiver shall reset its internal state to that obtained after power-up initialization.

3.2.1.2.10. Enable/Disable Interrupt Receiver Command The enable/disable interrupt receiver command shall be executed when the FMI receives a command from the processor or list sequencer, and the format for the command is as follows: Enable/disable interrupt receiver command

BitsValueDescription63:5412Function control code530,1Set to enable, reset to disable52:0XUnused

The enable/disable interrupt receiver command shall either enable or disable interrupt receiver messages depending on whether bit 53 is set or reset, respectively.

## 3.2.1.2.11. Reset Service Request Receiver

The reset service request receiver command shall be executed when the FMI receives a command from the processor or list sequencer, and the format for the command is as follows: Reset service request receiver command

| Bits Value | 3    | Description           |

|------------|------|-----------------------|

| 63:54      | 13   | Function control code |

| 53:0 X     | Unus | ed                    |

The reset service request receiver command shall act as a programmable reset command. The service request receiver shall reset its internal state to that obtained after power-up initialization.

3.2.1.2.12. Enable/Disable Service Request Receiver Command The enable/disable service request receiver command shall be executed when the FMI receives a command from the processor or list sequencer, and the format for the command is as follows: Enable/disable service request receiver command

| Bits  | Valu | е      | Description              |

|-------|------|--------|--------------------------|

| 63:54 | 1    | 14     | Function control code    |

| 53    | 0,1  | Set to | enable, reset to disable |

| 52:0  | X    | Unuse  | ed                       |

The enable/disable service request receiver command shall either enable or disable service requests depending on whether bit 53 is set or reset, respectively.

# <u>3.2.1.3. List Processing</u>

## 3.2.1.3.1. Flow Control