# EXPLORING MEMRISTOR BASED ANALOG DESIGN IN SIMSCAPE

Mahesh Gautam

Thesis Prepared for the Degree of

# MASTER OF SCIENCE

## UNIVERSITY OF NORTH TEXAS

May 2013

# APPROVED:

Saraju P. Mohanty, Major Professor Elias Kougianos, Co-Major Professor Mahadevan Gomathisankaran, Committee Member Barrett Bryant, Chair of the Department of Computer Science and Engineering Costas Tsatsoulis, Dean of the College of Engineering Mark Wardell, Dean of the Toulouse Graduate School Gautam, Mahesh. *Exploring Memristor Based Analog Design in Simscape*. Master of Science (Computer Engineering), May 2013, 47 pp., 4 tables, 41 figures, bibliography, 46 titles.

With conventional CMOS technologies approaching their scaling limits, researchers are actively investigating alternative technologies for ever increasing computing and mobile demand. A number of different technologies are currently being studied by different research groups. In the last decade, one-dimensional (1D) carbon nanotubes (CNT), graphene, which is a two-dimensional (2D) natural occurring carbon rolled in tubular form, and zero-dimensional (0D) fullerenes have been the subject of intensive research. In 2008, HP Labs announced a ground-breaking fabrication of memristors, the fourth fundamental element postulated by Chua at the University of California, Berkeley in 1971. In the last few years, the memristor has gained a lot of attention from the research community. In-depth studies of the memristor and its analog behavior have convinced the community that it has the potential in future nano-architectures for optimization of high-density memory and neuromorphic computing architectures. The objective of this thesis is to explore memristors for analog and mixed-signal system design using Simscape. This thesis presents a memristor model in the Simscape language. Simscape has been used as it has the potential for modeling large systems. A memristor based programmable oscillator is also presented with simulation results and characterization. In addition, simulation results of different memristor models are presented which are crucial for the detailed understanding of the memristor along with its properties.

Copyright 2013

by

Mahesh Gautam

#### ACKNOWLEDGMENTS

I would like to sincerely thank my major professor, Dr. Saraju P. Mohanty, for the encouragement and guidance he has given me throughout my studies at the University of North Texas. His constant support and technical feedback have made this research possible. I would also like to thank my co-major professor, Dr. Elias Kougianos, who also encouraged and motivated me through the completion of this work. I am grateful for his guidance on EDA tools. I would also like to thank Dr. Mahadevan Gomathisankaran, my committee member, for agreeing to examine this research. I would also like to thank my parents, brothers, and my fiancée whose constant moral and financial support and encouragement have helped me finish this research. I would also like to acknowledge the NanoSystem Design Laboratory (NSDL) members: G. Zheng, O. Okobiah, and O. Garitselov who have helped me with my research work. I also wish to thank the staff of the Department of Computer Science and Engineering and Mr. Bobby Grimes from Engineering Technology for being very helpful and caring in times of need.

# TABLE OF CONTENTS

| ACKNOWLEDGMENTSiii                                    |

|-------------------------------------------------------|

| LIST OF TABLES vi                                     |

| LIST OF FIGURES vii                                   |

| CHAPTER 1. INTRODUCTION                               |

| 1.1. The New Fundamental Circuit Element – Memristor1 |

| 1.2. Memristor: A Promising Future                    |

| 1.3. Contributions of this Thesis                     |

| 1.4. Organization of the Thesis                       |

| CHAPTER 2. RELATED RESEARCH                           |

| 2.1. History of the Memristor 7                       |

| 2.2. Different Types of Memristors                    |

| 2.2.1. Thin-Film Memristors                           |

| 2.2.1.1. Titanium Dioxide Memristor                   |

| 2.2.1.2. Other Thin-Film Memristors                   |

| 2.2.2. Spintronic Memristors 11                       |

| 2.3. Memristor Mathematical Modeling 12               |

| 2.4. Operation of a Memristor                         |

| CHAPTER 3. DEVICE LEVEL MODELING OF THE MEMRISTOR 15  |

| 3.1. MATLAB based Behavioral Model 15                 |

| 3.2. Verilog-A based Behavioral Model 17              |

| 3.3. Verilog-AMS based Behavioral Model 22            |

| 3.4. SPICE based Behavioral Model                  |

|----------------------------------------------------|

| 3.5. Simscape based Behavioral Model               |

| CHAPTER 4. MEMRISTOR BASED WIEN OSCILLATOR         |

| 4.1. Wien Oscillator: The Case Study Circuit       |

| 4.2. One Resistor Replaced with Memristor          |

| 4.3. Two Resistors Replaced with Memristors        |

| 4.4. All Resistors Replaced with Memristors        |

| 4.5. Frequency and Power Analysis of the Memristor |

| CHAPTER 5. CONCLUSION AND FUTURE RESEARCH 41       |

| 5.1. Conclusion                                    |

| 5.2. Future Directions of Research                 |

| BIBLIOGRAPHY                                       |

# LIST OF TABLES

# Page

| 4.1 Variations of Wien oscillators              | 32 |

|-------------------------------------------------|----|

| 4.2 Equations for Wien oscillators              | 33 |

| 4.3 Frequency distribution for Wien oscillators | 39 |

| 4.4 Power profile for Wien oscillators          | 40 |

# LIST OF FIGURES

| Page                                                                                           |

|------------------------------------------------------------------------------------------------|

| 1.1 Relationship between basic circuit elements1                                               |

| 1.2 Basic circuit elements                                                                     |

| 1.3 TiO2 memristor structure                                                                   |

| 1.4 HP memristor model                                                                         |

| 2.1 Different types of memristors                                                              |

| 2.2 Other thin-film memristors                                                                 |

| 2.3 Spintronic memristor                                                                       |

| 2.4 Operation of a memristor                                                                   |

| 3.1 Different memristor-models15                                                               |

| 3.2 Current and voltage vs. time (MATLAB model)16                                              |

| 3.3 Resistance vs. time (MATLAB model)16                                                       |

| 3.4 I - V curve (MATLAB model)                                                                 |

| 3.5 Resistance-voltage curve (MATLAB model)                                                    |

| 3.6 I - V curve (Verilog-A model)                                                              |

| 3.7 $I - V$ curve at variable $R_{off}$ and $R_{in}$ (Verilog-A model)                         |

| 3.8 I - V curve at variable operating voltage (Verilog-A model)                                |

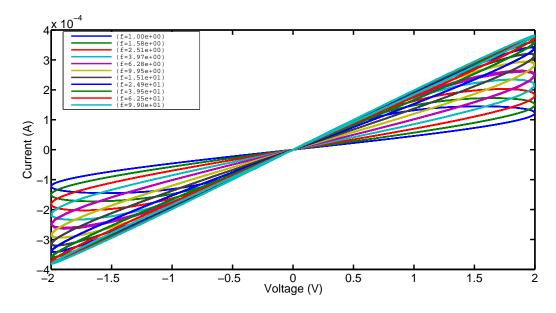

| 3.9 I - V curve at variable operating frequency (Verilog-A model)                              |

| 3.10 Resistance vs. voltage curve (Verilog-A model)                                            |

| 3.11 Resistance voltage curve at variable operating voltage (Verilog-A model)21                |

| 3.12 Resistance voltage curve at variable operating frequency (Verilog-A model)21              |

| 3.13 Resistance curve for sinusoidal input voltage with variable frequency (Verilog-AMS model) |

|                                                                                                |

| 3.14 Resistance vs. voltage (Verilog-AMS model)                                        | 23     |

|----------------------------------------------------------------------------------------|--------|

| 3.15 Current curve for sinusoidal input voltage with variable frequency (Verilog-AMS n | nodel) |

|                                                                                        | 24     |

| 3.16 Surface $I - V$ curve for sinusoidal input voltage (Verilog-AMS model)            | 24     |

| 3.17 Current and voltage vs. time (Spice model)                                        | 25     |

| 3.18 Resistance and voltage vs. time (Spice model)                                     | 25     |

| 3.19 Resistance and current vs. voltage (Spice model)                                  | 26     |

| 3.20 The configuration of Simulink/Simscape memristor simulation                       | 27     |

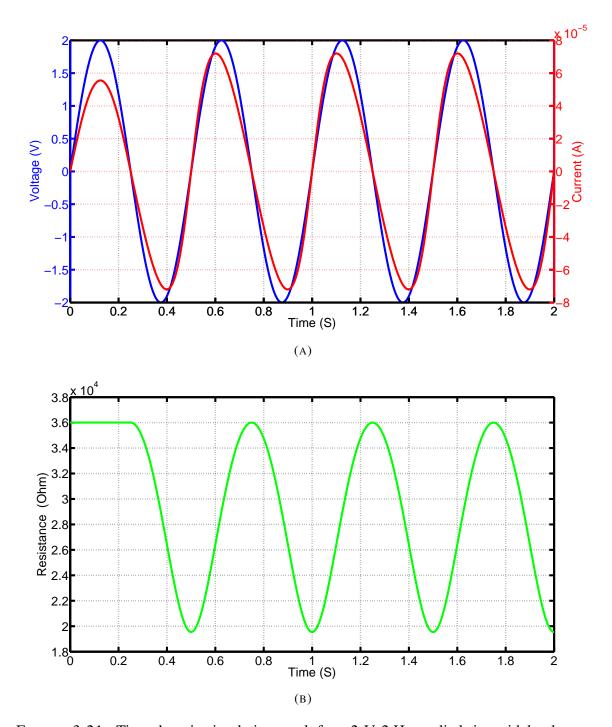

| 3.21 Time-domain simulation result for a 2-V, 2 Hz applied sinusoidal voltage          | 29     |

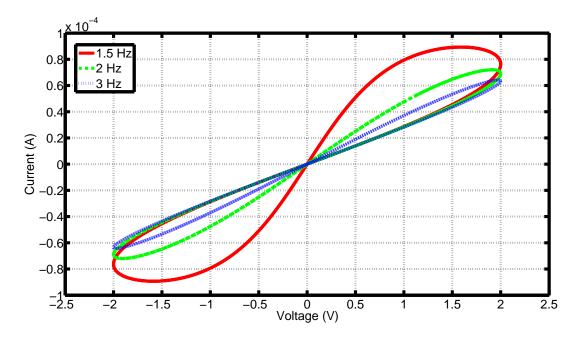

| 3.22 Memristor $I - V$ characteristics for various input frequencies                   | 30     |

| 4.1 Schematic of a Wien oscillator                                                     | 32     |

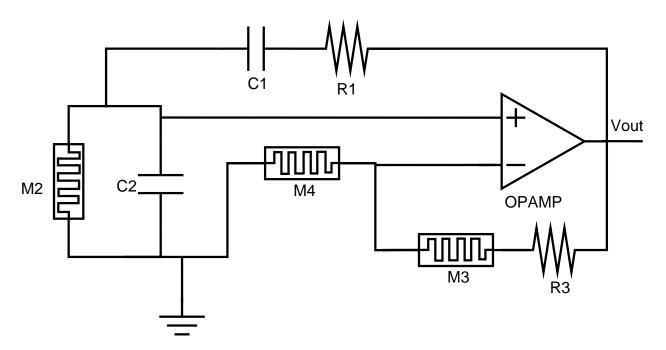

| 4.2 Resistor $R_1$ replaced with memristor (Configuration 1)                           | 34     |

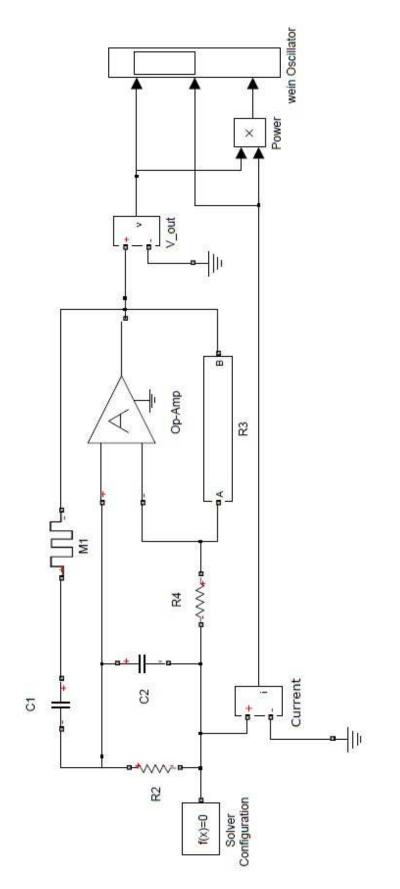

| 4.3 Experimental setup in Simulink/Simscape                                            | 35     |

| 4.4 Output signal when $R_1$ is replaced with a memristor                              | 36     |

| 4.5 Resistor $R_2$ replaced with memristor (Configuration 2)                           | 36     |

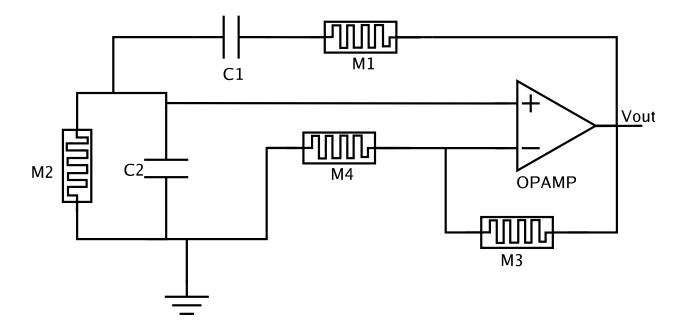

| 4.6 Two resistors replaced with memristors (Configuration 3)                           | 37     |

| 4.7 Two resistors replaced with memristors (Configuration 4)                           | 37     |

| 4.8 The schematic of the Wien oscillator with five memristors (Configuration 5)        |        |

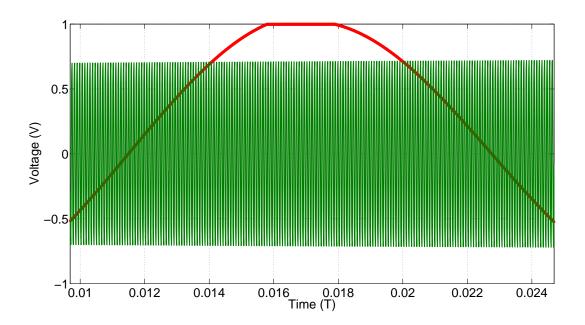

| 4.9 Oscillator output when all resistors are replaced with memristors                  |        |

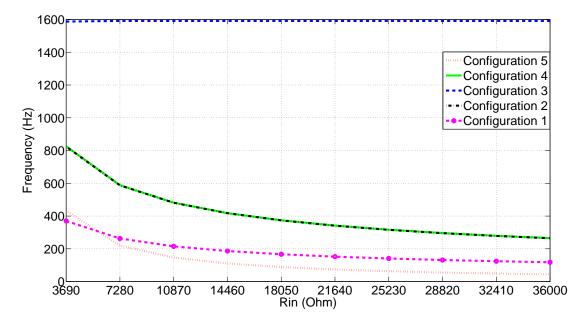

| 4.10 Frequency distribution for Wien oscillators                                       | 39     |

| 4.11 Average power dissipation for Wien oscillators                                    | 40     |

#### CHAPTER 1

#### INTRODUCTION

## 1.1. The New Fundamental Circuit Element – Memristor

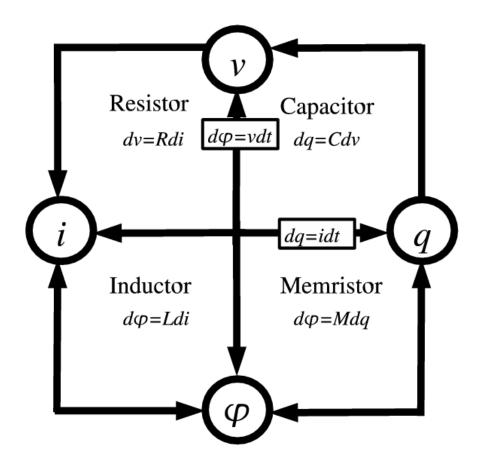

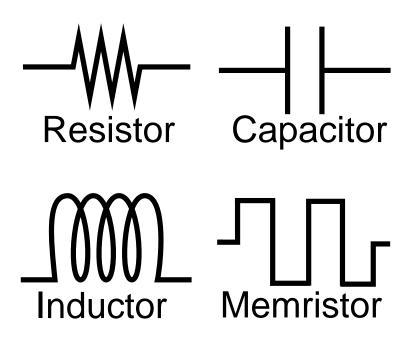

From the very first days of electronics, resistor, capacitor and inductor have been accepted as three fundamental circuit elements and are fully characterized. These three elements define five out of six possible combinations of fundamental circuit variables: current (*i*), voltage (*v*), charge (*q*) and flux ( $\varphi$ ) (Fig 1.1). In 1971, Chua [7] published a paper and theoretically presented the fourth element, memristor (Fig. 1.2) that defines the last possible combination. The name, memristor was derived from the combination of *mem*ory and *resistor*. Since memristic properties are prominent only in nanoscale it evoked little research interest and remained dormant for three decades.

FIGURE 1.1. Relationship between basic circuit elements.

FIGURE 1.2. Basic circuit elements.

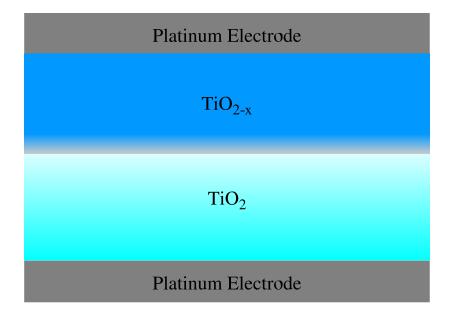

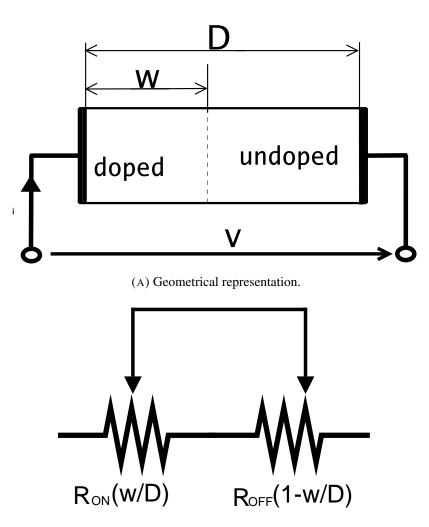

A new wave of research was introduced in the field of circuit design in 2008 involving the memristor. Hewlett-Packard (HP) Labs in 2008 [44, 37] successfully fabricated a memristor. A simple analytical model, experimental verification, and production of a titanium dioxide (TiO<sub>2</sub>) thin-film memristor (Fig. 1.3) has helped in advancing the research since then. Memristor related research started growing rapidly since the introduction of HP's coupled variable-resistor memristor model (Fig. 1.4) [37]. Researchers are optimistic about the future of the memristor and its applications in future circuits including resistive memory, artificial intelligence, and sensors.

In order to aid the design and simulation of memristor integrated circuits and systems, memristor models in various simulation environments are needed. Many memristor models have been proposed for simulation and characterization of memristor and memristor-based systems. Many different platforms and languages such as SPICE, Verilog-A, MATLAB, and Simulink have been used for these purposes. For example, in [4, 3, 46, 22, 1, 34, 19], SPICE models have been presented to capture simple behaviors of the memristor. MATLAB and Simulink models are presented in [45, 41, 36, 19] for behavioral simulation of memristor. Verilog-A simulations have been presented in [19, 36, 9]. A statistical model for capturing process variation in memristors has been

FIGURE 1.3. TiO<sub>2</sub> memristor structure.

discussed in [15]. In addition, a few memristor emulator designs were presented in [31, 26, 18] for advancement of research and education in nanoelectronics using memristors.

Simscape, an integral part of MATLAB-Simulink is fully functional but still continuous development is being made. Researchers have not yet fully explored the capability of Simscape because it is relatively unknown. This motivates the research presented in this thesis to conduct research on nanoelectronics modeling using Simscape. There is a lack of any literature presenting memristor models written in the MATLAB-Simscape physical modeling language. Simscape is designed for modeling physical systems in multiple domains such as mechanical, electrical, and hydraulic systems. Simulink employs a signal-flow modeling approach that is suitable for high-level system modeling. It is cumbersome to use Simulink, however, to model low-level physical components. For example, a complete description of an electrical node in Simulink requires two separate ports (one for voltage and one for current). Simscape overcomes this inconvenience through the introduction of the capability of modeling conservative systems similar to that of the Verilog-A language. Simscape is backed by a set of libraries of pre-defined physical components, which enables rapid model construction and design exploration in early developmental stages. This gives Simscape an edge over SPICE models which are restricted to purely electrical system simulation.

(B) Coupled variable resistor model.

FIGURE 1.4. HP memristor model.

#### 1.2. Memristor: A Promising Future

The conventional nanoscale CMOS (nano-CMOS) technologies are approaching their physical limits. For example, the oxide thickness is merely 5 layers of atoms. Researchers are actively investigating alternative technologies to meet ever increasing computing and mobile demands. Researches have shown that the memristor is crucial for the future of nanotechnology.

In nano-CMOS technology, parasitics, power dissipation, and process variation effects are some of the major concerns for design engineers [14, 23, 25]. Looking for less power hungry and more computing capable alternatives, researches have shown that neuromorphic computing tops the list. Neuromorphic computing architectures mimic the human brain and improve computing and processes information that may not be fully defined [11]. In addition, power consumption by neuromorphic architectures is much less than the traditional (nanoscale) CMOS technology based architectures [35].

The concept of neuromorphic architectures came from biological synapses that are analog in behavior and consume minimal power. The memristor has these properties and is considered by the researchers as the best choice for neuromorphic computing. The traditional CMOS technology, which is more suitable for digital circuits, requires a number of transistors to mimic one memristor. Hyun et al. [17] have presented the resemblance of memristors to synapses in the their research. Pershin et al. [29] have experimentally verified that memristors work as synapses using a memristor emulator in their work.

Apart from neuromorphic computing, the memristor can be applied in number of applications. For example, non-volatile memory, resistive memory, tunable antennas, control systems, radio frequency (RF) circuits, and low-power sensors, to name a few. One of the major benefits that end user may see is an instant boot computer which is a time consuming process even with the best available at present. Since the memristor remembers the last state when power was turned off, it would start working when power is turned on without any lengthy boot. Also, voice recognition can be greatly improved if memristor could be used to build neuromorphic architecture.

#### 1.3. Contributions of this Thesis

The overall objective of this thesis is to perform memristor modeling and memristor-based mixed-signal system design using Simscape as the platform. In the first phase of this research, different memristor models were simulated and evaluated during the research leading to this thesis. In the second phase of research, a memristor model was created using the Simscape language. A memristor based Wien oscillator was designed in Simscape and fully characterized.

The novel contributions of this thesis are the following:

• The first Simscape based modeling of a memristor device. No other existing literature presents such model. With the use of memristor model in Simscape, system level modeling will be possible.

- A programmable oscillator using memristors, which judiciously replaces resistors, is defined.

- The MATLAB Simulink/Simscape memristor based programmable oscillator model construction and simulation setup are presented.

- A study of a Wien oscillator under five memristor configurations was performed. They were examined in terms of power consumption and frequency.

- 1.4. Organization of the Thesis

The chapters of this thesis are organized in the following manner:

Chapter 2 gives a brief overview of the history of the memristor. Different memristor devices proposed after the first memristor fabrication are summarized in this chapter. Finally, mathematical modeling of a  $TiO_2$  based model proposed by HP Labs [37] is explored and detailed description of how the  $TiO_2$  memristor works is provided.

Chapter 3 discusses some of the available memristor models. Simulation results verifying the models are presented. Finally, the Simscape model developed during this thesis is presented with detailed description and experimental results.

Chapter 4 presents the Wien oscillator under different memristor configurations. This chapter is presented as an application example of memristor usage. Also, this chapters shows some of the capabilities of Simscape as power and frequency distribution of different configurations are analyzed.

Finally, Chapter 5 presents conclusion and directions for future research.

#### CHAPTER 2

#### **RELATED RESEARCH**

#### 2.1. History of the Memristor

The memristor was theoretically presented by Chua [7] citing the symmetry of equations of basic circuit elements (Fig. 1.1). Current is defined as the rate of change of charge (i = dq/dt). Magnetic flux is defined in Faraday's law of magnetism  $(v = d\varphi/dt)$ . A resistor gives a relation between voltage and current (R = dv/di). A capacitor relates charge to voltage in the following manner: (C = dq/dv). An inductor connects magnetic flux and current  $(L = d\varphi/di)$ . Chua argued that there should be a direct relation between magnetic flux and charge. He mathematically presented the fourth basic circuit element, memristor with memristance (M) that would relate magnetic flux and charge  $(M = d\varphi/dq)$ . Simply speaking, the memristance should act as a nonlinear resistance that would vary according to the amount and direction of charge passed through it.

Even before Chua presented the hypothetical memristor, there had been few instances where researchers observed memristic behaviors in their research. However, since they were not predominant in micrometer scale, they were considered as anomalies due to some unknown electrochemical reaction or electrical breakdown. The hypothetical paper remained relatively unknown to the research community. In 1976 Chua et al. [8] published yet another paper providing more details of memristive devices and systems.

From the early 1990's, research has been undertaken for studying memristic properties such as variable resistance [40]. The I - V characteristic of a variable resistance is similar to the memristor [5, 2]. Some devices with memristic properties were described but none of the researchers were able to realize the relation between their work and that of Chua [7, 8].

Since memristance follows an inverse square law, it becomes more prominent in the nanometer scale. Finally, researchers at HP Labs were able to fabricate a memristor [44, 37] in 2008. The first ever memristor was fabricated with  $TiO_2$  and  $TiO_{2-x}$  sandwiched between two platinum (Pt) electrodes. Erokhin and Fontana [12] claim to have developed the first ever polymeric memristor even before the memristor developed by HP Labs [44, 37].

With the first memristor fabricated, the research community embraced the concept and a substantial amount of research has been underway. The research community has been working to understand the properties of memristors. Without any physical memristor to work on, many memristor models have been proposed for SPICE [4, 3, 46, 22, 1, 34, 19], MATLAB/Simulink [45, 41, 36, 19], and Verilog-A [19, 36, 9] simulations. In addition, a few memristor emulator designs [31, 26, 18] and a statistical model based on process variation [15] are presented. The research community has also presented different device structures with different materials. Research is underway to determine the best possible structure for commercial use.

#### 2.2. Different Types of Memristors

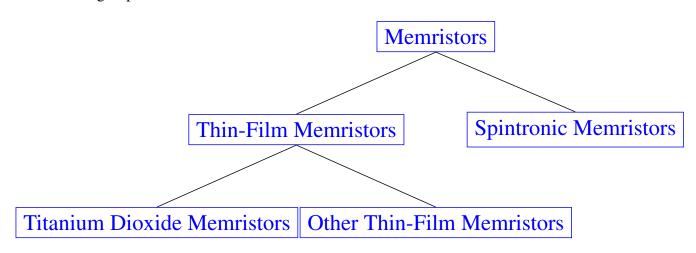

With the first physical memristor fabrication done by HP Labs, research in this field is on the rise. With the existence of the memristor verified, the research community is working diligently to find the best memristor configuration that can be adopted by industry. Memristors are broadly categorized into two groups: thin-film and spintronic [24]. In addition there are several types in each of these groups.

FIGURE 2.1. Different types of memristors.

## 2.2.1. Thin-Film Memristors

The first memristor presented by HP Labs was a thin-film memristor as it is one the simplest to build. There are many variations of thin-film memristors available from various researchers and each one has its own advantages and disadvantages.

#### 2.2.1.1. Titanium Dioxide Memristor

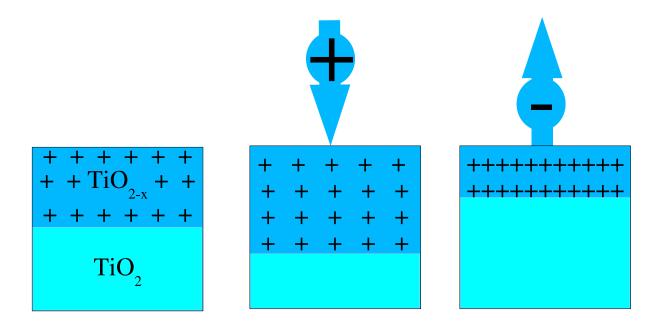

The first memristor fabricated by HP Labs was based on a titanium dioxide (TiO<sub>2</sub>) process. As shown in Fig. 1.3, it has TiO<sub>2</sub> and TiO<sub>2-x</sub> sandwiched in between platinum electrodes. TiO<sub>2</sub> is resistive and TiO<sub>2-x</sub> conductive and the ratio of these two layer varies with the application of current. This device configuration was not something researchers started with. They had designed a cross-bar structure with a layer of platinum dioxide, a layer of switching molecules and a thin film of titanium sandwiched between two platinum electrodes. Closer look revealed that the structure had changed [44]. With further analysis of the structure they realized they were working with memristor and finally Chua's theory [7] made much more sense. More details on how this system works is presented in Section 2.4.

#### 2.2.1.2. Other Thin-Film Memristors

Different variations of memristor devices have been presented in the existing literature. In these cases, different device structure and materials have been used for design and fabrication of memristors [24, 16, 17, 27, 13, 33, 21].

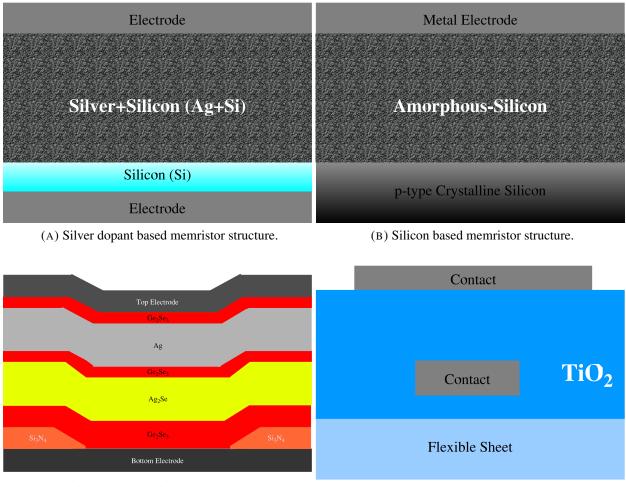

Fig. 2.2a is a schematic representation of the cross section of a memristor based on the motion of silver dopants [16]. This device is made up of amorphous silver and silicon layer and amorphous silicon layer sandwiched between two metal electrode. When positive voltage is applied on the top electrode, silver ions are pulled into the silicon layer and device resistance is lowered. When polarity is reversed the silver ions move back to silver+silicon layer raising the resistance.

Fig. 2.2b is the schematic representation of the cross section of a silicon based memristor [17]. This device has top metal electrode followed by active amorphous-silicon layer co-sputtered with silver. The ratio of silver is gradually varied from one side to the other. Heavily doped p-type crystalline is used as bottom electrode. When positive voltage is applied on top metal electrode, a conduction channel is formed through amorphous silicon and there is reduction in resistance. Applying negative voltage has the reverse effect and resistance is increased.

Fig. 2.2c shows the cross section of a silver chalcogenide based memristor [27, 32]. This device has  $Ge_2Se_3$ ,  $Ag_2Se$  and Ag layer between tungsten electrodes. Layers of  $Ge_2Se_3$  are placed between  $Ag_2Se$  and Ag layers to facilitate deposition of Ag; and between Ag and top electrode to

help tungsten to adhere to Ag. In this system when positive voltage is applied  $Ag^+$  ions migrate to chalcogenide (Ge<sub>2</sub>Se<sub>3</sub>) layer and resistance decreases. Applying negative voltage reverses the phenomenon and high resistance is gained by the system.

Fig. 2.2d shows the cross section of a unique flexible memristor [13]. The memristor was designed on a laser jet transparency. Amorphous  $TiO_2$  layer was placed between two Al electrodes. Despite this structure being in micrometer scale, it showed memristic properties showing that these properties go beyond the nanometer scale.

(D) Flexible solution-processed memristor.

FIGURE 2.2. Other thin-film memristors.

Some of the other memristors reported are  $TiO_{2+x}$  [33], Au/Ti<sub>2</sub>O<sub>5</sub>/Au [21] and Pt/TiO<sub>2</sub>/Al [21]. The  $TiO_{2+x}$  based memristor is structurally identical to the one presented by HP Labs (which is schematically presented in Fig. 1.3), but in this design  $TiO_{2-x}$  is replaced with  $TiO_{2+x}$ . When

negative voltage is applied across top/bottom electrode excess oxygen flows from  $TiO_{2+x}$  towards  $TiO_2$  and resistance is decreased; application of positive voltage reverses the phenomenon hence increases the resistance.

Structurally, Au/Ti<sub>2</sub>O<sub>5</sub>/Au would be similar to Fig. 1.3 with Au electrodes and just a layer of  $Ti_2O_5$  sandwiched in-between. Similarly, the Pt/TiO<sub>2</sub>/Al memristor would have platinum top electrode and aluminum bottom electrode with a layer of TiO<sub>2</sub> in-between.

#### 2.2.2. Spintronic Memristors

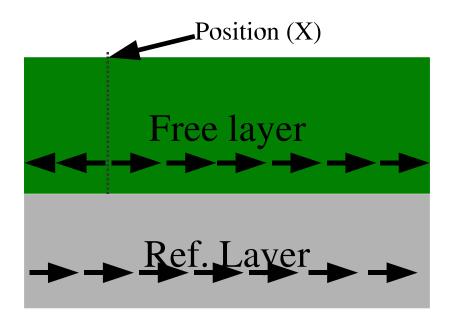

Spintronic memristors have entirely different structure [42, 43, 6, 28]. In a spintronic memristor, the direction of rotation of electrons effects the magnetic state and hence the resistance of the memristor.

Fig. 2.3 is a graphical representation of a spintronic memristor [6, 42]. This structure has a reference layer with fixed magnetic direction and a free layer. The free layer is divided into two sections with opposite polarity. Movement of the domain-wall dividing the two sections is induced by application of current and change in resistance is achieved.

FIGURE 2.3. Spintronic memristor.

#### 2.3. Memristor Mathematical Modeling

The resistance offered by the memristor is called memristance (M). In the memristor, the current depends on the amount of charge that recently passed through it. Memristance varies depending on the direction of the current flow through the memristor. When the current is zero, the memristor retains the last memristance; in other words it remembers its resistance. The memristance will increase or decrease as long as it is within the physical limits once the current flow resumes. Fig. 1.4 is a representation of the HP memristor model. It has two platinum electrodes and layers of TiO<sub>2</sub> and TiO<sub>2-x</sub> between them. Pure TiO<sub>2</sub> is insulator and is marked as undoped and TiO<sub>2-x</sub> contains vacant oxygen atoms, acts as a semiconductor and is labeled as doped in Fig. 1.4a. The doped region width w varies depending on the current flow through the memristor, which results in its variable resistance or memristance.

The current, voltage, and memristance relation of the memristor is described as follows:

(1)

$$v(t) = R_{MEM}(w)i(t),$$

where  $R_{MEM}$  is the memristance and is a function of w. Comparing Fig. 1.4a with Fig. 1.4b, Eqn. (1) can be rewritten in the following expression:

(2)

$$v(t) = \left(R_{on}\frac{w(t)}{D} + R_{off}\left(1 - \frac{w(t)}{D}\right)\right)i(t)$$

where D is the total length of the memristor.  $R_{on}$  is the resistance of the doped region and  $R_{off}$  is the resistance of the undoped region of the memristor.

The memristor dynamic, the relation between the memristor current and the change of w, is expressed as follows:

(3)

$$\frac{dw(t)}{dt} = \mu_v \frac{R_{on}}{D} i(t),$$

where  $\mu_v$  is dopant mobility and for the HP thin film memristor  $\mu_v \approx 10^{-14} m^2 s^{-1} V^{-1}$ . From the equations above, it can be derived that the memristance of the memristor has the following relationship:

(4)

$$R_{MEM} = R_{off} \left( 1 - \frac{\mu_v(R_{on})}{D^2} q(t) \right)$$

#### 2.4. Operation of a Memristor

Fig. 2.4 is a schematic representation working principle of a thin-film based memristor. As depicted in the figure, the oxygen deficient upper layer  $(\text{TiO}_{2-x})$  is a semiconductor with small resistance and stoichiometric TiO<sub>2</sub> is an insulator with very high resistance. When positive voltage is applied across the top electrode, positively charged oxygen deficiencies are pushed into the TiO<sub>2</sub> layer. This causes the boundary between the two layers to shift increasing the ratio of conductor to insulator, hence reduction in total resistance. Application of more positive voltage decreases the resistance of the memristor further until it reaches minimum ( $R_{on}$ ).

FIGURE 2.4. Operation of a memristor.

Let us consider the situation when the polarity of the voltage applied across the memristor is reversed. In this case the negative voltage attracts the positive oxygen deficiencies out of the  $TiO_2$  layer and increase resistivity. Continuous application of negative voltage, keeps increasing the resistance until it reaches its maximum value  $(R_{off})$ . This was experimentally verified using different memristor models. Results are presented in Chapter 3.

If voltage is turned off at any point of time the system freezes at its instant condition. Oxygen deficiencies remain stationary. Turning on the supply voltage, increase or decrease in resistance of the system is achieved depending on the polarity of voltage. This can be referred as writing mechanism for the memristor.

To read information from memristor very minimum voltage could be applied across memristor. Small voltage would not be enough to change the state of the memristor but would be able to give us information about its current state.

#### CHAPTER 3

#### DEVICE LEVEL MODELING OF THE MEMRISTOR

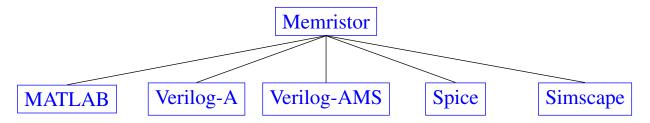

Five years into the discovery of the memristor, research is still in its primitive stage. Few memristors were fabricated at different research institutions solely for the purpose of their own research. To this date we do not have any off-the-shelf memristors available for research. Researchers rely on memristor models they created themselves or the ones published in the literature. In this research, some memristor models were adopted as representative of different languages and environments and simulated for verification and better understanding of the properties. During the course of this research, MATLAB based language, Simscape was for the first time used to create a memristor model. Known physical and electrical properties were used to create the model. An overview of different languages and a framework for memristor modeling are presented in Fig. 3.1.

FIGURE 3.1. Different memristor-models.

#### 3.1. MATLAB based Behavioral Model

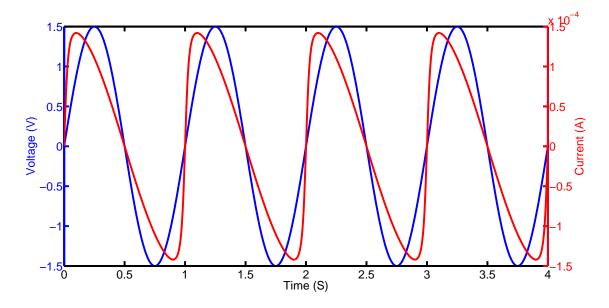

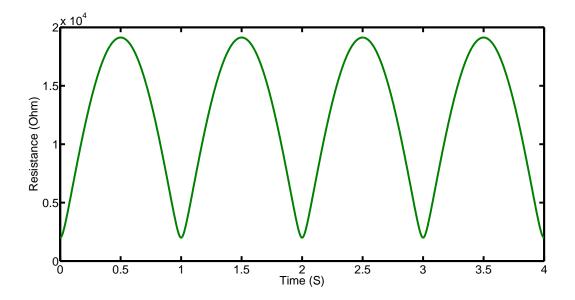

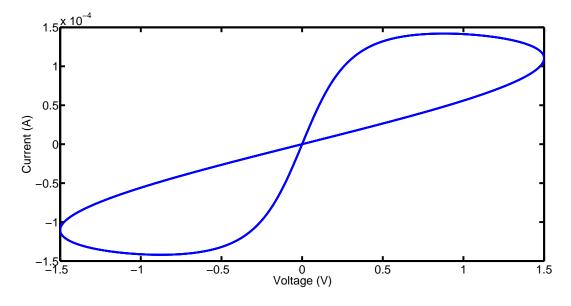

We performed exhaustive analysis of the HP memristor device. A MATLAB model for memristor was obtained from the Mathworks [41] file exchange site and simulated in MATLAB. For simulation, width of TiO<sub>2</sub> (D) = 10nm,  $R_{on} = 100\Omega$ ,  $R_{off} = 38K\Omega$ ,  $R_{in} = 2K\Omega$  and  $\mu = 10^{-14}m^2s^{-1}V^{-1}$  were used with input signal of frequency 1 Hz. Selected characteristics are presented in the following graphs.

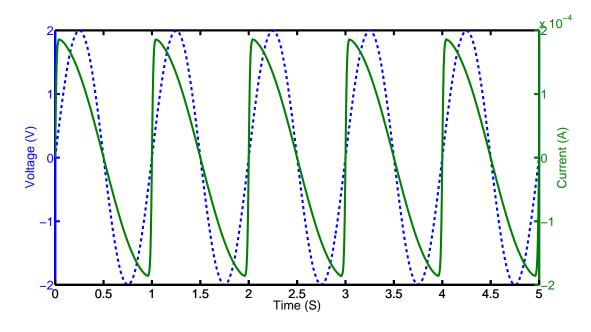

Fig. 3.2 shows the voltage and current of the memristor over time which was obtained from transient analysis. Fig. 3.3 shows the resistance characteristic of the memristor when oscillating with time. Initially the memristor has 0 voltage and current and initial resistance of  $R_{in}$ . When positive voltage is applied, current and the resistance both increase. Current will follow voltage

closely while resistance will keep increasing as long as positive voltage is applied. When voltage falls back to 0 V, resistance would be at its maximum. With application of negative voltage the resistance starts dropping, and it continues until the voltage is back to 0 V.

FIGURE 3.2. Current and voltage vs. time (MATLAB model).

FIGURE 3.3. Resistance vs. time (MATLAB model).

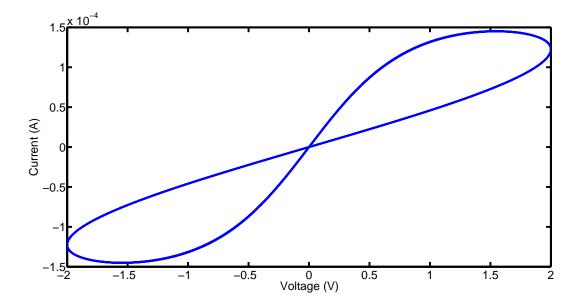

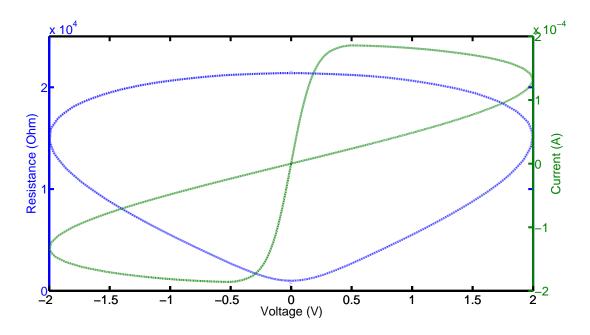

The I - V characteristics of the memristor are presented in Fig. 3.4. It is observed that the current has two values for same voltage depending on whether it is rising or falling. Current

is falling back in time when positive voltage is applied and it is leading when negative voltage is applied. This phenomenon gives such a unique I - V curve. This shows that memristor remembers the current passed through it.

FIGURE 3.4. I - V curve (MATLAB model).

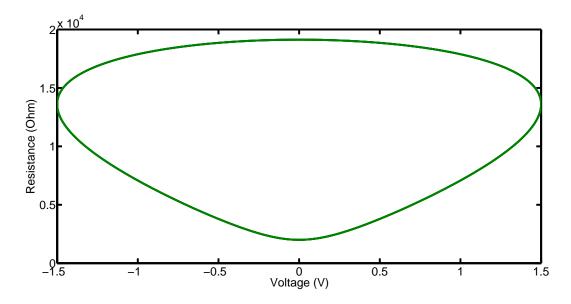

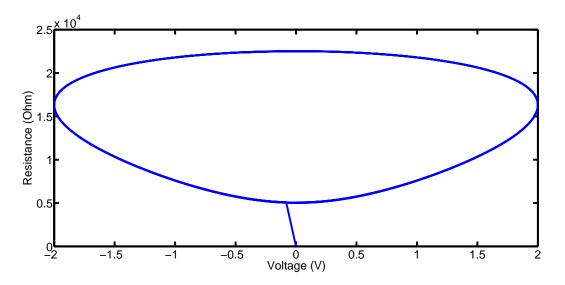

Fig. 3.5 shows the resistance voltage characteristics. It is in essence the same properties as shown in Fig. 3.3. The resistance will increase from its initial  $R_{in}$  toward  $R_{off}$  as long as positive voltage is being applied. When negative voltage is applied, the resistance decreases and reaches its minimum when the voltage is back to zero. Depending on how long the voltage is applied, it may not reach maximum possible ( $R_{off}$ ).

Unlike other elements, the memristor is dynamic in nature in terms of resistance and has the capability to remember what was the last charge applied.

#### 3.2. Verilog-A based Behavioral Model

A Verilog-A [36] model for memristors was simulated in Cadence Virtuoso. The results obtained here were consistent with the properties of memristor. They closely followed the results received in MATLAB simulations. The following values were used for simulation : D = 10nm,  $R_{on} = 100\Omega$ ,  $R_{off} = 38K\Omega$ ,  $R_{in} = 5K\Omega$  and  $\mu = 10^{-14}m^2s^{-1}V^{-1}$  and input signal of frequency 1 Hz.

FIGURE 3.5. Resistance-voltage curve (MATLAB model).

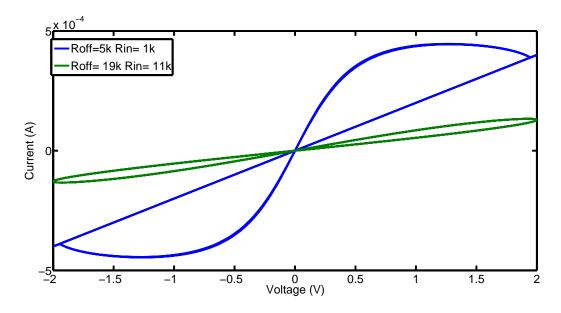

The I - V characteristics in Fig. 3.6 showed its unique hysteresis loop. The curve had some variations as shown in Fig. 3.7, when  $R_{off}$  and  $R_{in}$  were varied.  $R_{off}$  is peak resistance and  $R_{in}$  is initial resistance of the memristor. With higher value of  $R_{off}$  and  $R_{in}$  the current was lower. At lower  $R_{off}$ , half of the hysteresis loop is linear with voltage given that there is no increase in resistance. This was observed in accordance with one of the properties :  $v(t) = R_{MEM}(w)i(t)$ . The relationship is like a resistance. But the resistance is variable and hence the nature is nonlinear.

FIGURE 3.6. I - V curve (Verilog-A model).

FIGURE 3.7. I - V curve at variable  $R_{off}$  and  $R_{in}$  (Verilog-A model).

When the amplitude of the input voltage was changed, the I - V characteristic resulted is shown in Fig. 3.8. It is observed that peak to peak current is lower at lower amplitude and the loop shrinks during those conditions.

FIGURE 3.8. I - V curve at variable operating voltage (Verilog-A model).

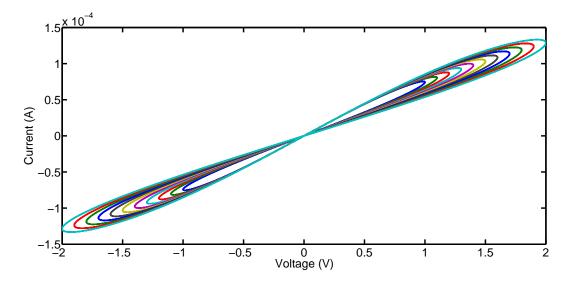

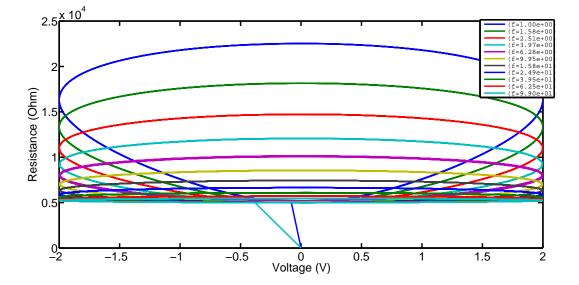

When the frequency of the input voltage was changed, the I - V curve was achieved as shown in Fig. 3.9. With increase in frequency, peak to peak current increases, but the loop continues to shrink. At very high frequency, memristor will act at resistor.

FIGURE 3.9. I - V curve at variable operating frequency (Verilog-A model).

The resistance-voltage (R - V) curve was as observed in MATLAB simulation. Resistance increased gradually from its initial value  $(R_{in})$  for positive voltage and then decreased when negative voltage was applied as shown in Fig. 3.10.

FIGURE 3.10. Resistance vs. voltage curve (Verilog-A model).

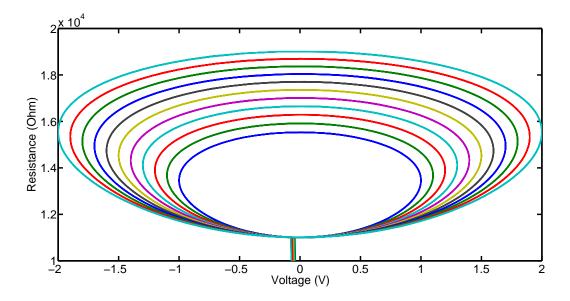

The resistance was probed at variable input voltage amplitude and frequency. The result for variable amplitude is shown in Fig. 3.11 and for variable frequency is shown in Fig. 3.12. Following  $v(t) = R_{MEM}(w)i(t)$ , the total change in resistance is lower as the input voltage amplitude

decreases. With higher frequency, application time of positive/negative voltage reduces that results in reduction of peak to peak resistance (Fig. 3.12).

FIGURE 3.11. Resistance voltage curve at variable operating voltage (Verilog-A model).

FIGURE 3.12. Resistance voltage curve at variable operating frequency (Verilog-A model).

Since the amount of resistance depends on the direction of current flow, the resistance cannot achieve its maximum value  $R_{off}$  at lower amplitude and higher frequency.

#### 3.3. Verilog-AMS based Behavioral Model

A Verilog-AMS model was developed using known properties of the memristor. The model was simulated in Cadence Virtuoso. In this simulation the following parameters were used: D = 5nm,  $R_{on} = 100\Omega$ ,  $R_{off} = 36K\Omega$ ,  $X_0 = 0.5$  and  $\mu = 10^{-14}m^2s^{-1}V^{-1}$  and input signal of frequency 6 Hz. A new parameter  $X_0 = (w0/D)$  was used in this model, where w0 is initial width of doped region (Fig. 1.4a).  $X_0$  gave initial resistance ( $R_{in} = (R_{on}X_0 + R_{off}(1 - X_0))$ ) of the memristor. The simulation results were following the properties given in various papers.

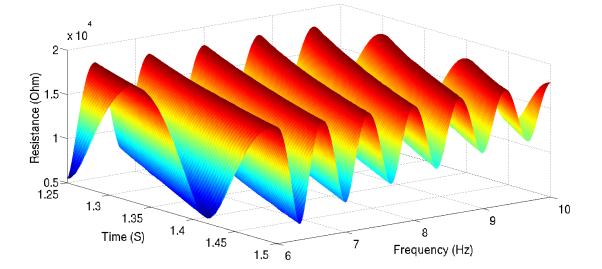

Fig. 3.13 shows the effect of input signal frequency on the resistance of the memristor. The 3dimensional plot provides a very good perspective. For this simulation the input voltage frequency was gradually increased from 6 Hz to 10 Hz. The higher the frequency the less the change in resistance of a system. Since memristor's resistance (memristance) depends on the history of current that passed the system, with higher frequency, polarity of input signal changes faster leading to less change in resistance.

FIGURE 3.13. Resistance curve for sinusoidal input voltage with variable frequency (Verilog-AMS model).

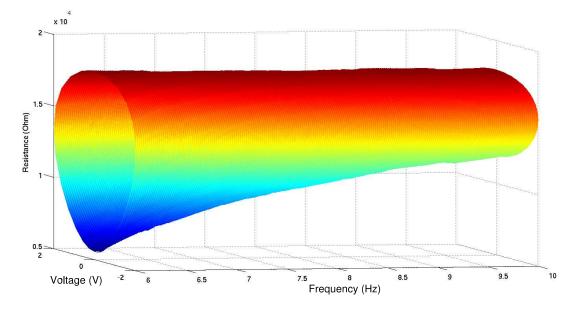

Fig. 3.14 shows the effect of frequency and voltage on the memristance. Here the resistance is plotted against input voltage and 3-dimensional view is provided for a visual perspective. As the frequency increases, the change in resistance decreases. With higher frequency, the change in ratio

of doped/undoped layer reduces (as discussed in Section 2.4) and results in less change in value of resistance of the memristor.

FIGURE 3.14. Resistance vs. voltage (Verilog-AMS model).

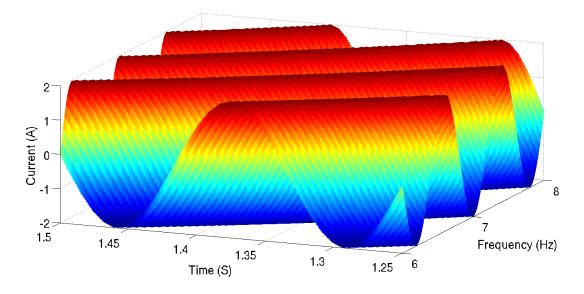

Fig. 3.15 shows the current curve for variable frequency. As observed in Fig. 3.9 with increase in frequency, peak to peak current increases, but the difference between two current values for single voltage reduces. This can be clearly observed in Fig. 3.16.

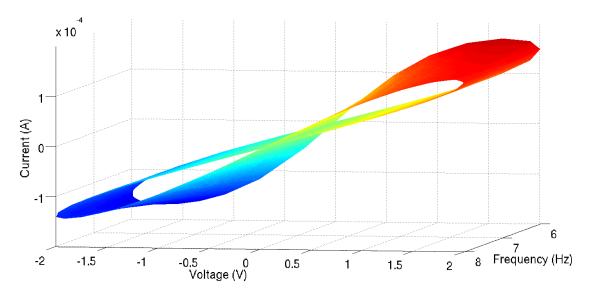

Fig. 3.16 shows the hysteresis I - V curve of memristor for various frequencies. As seen on other models as well, the loop shrinks with increase in frequency. This could be explained by Eqn. 1. With high enough frequency, the loop will be linear and memristor acts as regular resistor.

As discussed above, the results obtained in Verilog-AMS were consistent with other simulations. The results were able to verify the properties of memristor.

#### 3.4. SPICE based Behavioral Model

A spice model [4] was simulated in LTspice. For the simulation purposes D = 10nm,  $R_{on} = 100\Omega$ ,  $R_{off} = 36K\Omega$ ,  $R_{in} = 1K\Omega$  and  $\mu = 10^{-14}m^2s^{-1}V^{-1}$  and input signal of frequency 1 Hz were used. Simulation results were in accordance with known properties of memristor.

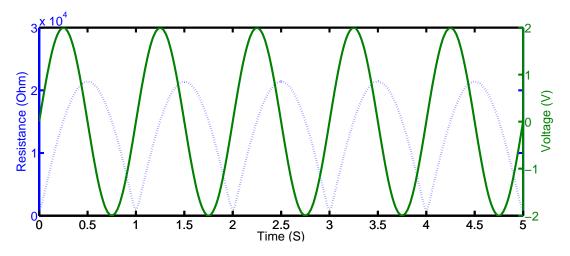

Fig. 3.17 and 3.18 show how current and resistance vary with time. As it can seen from resistance curve, the resistance continues to increase with application positive voltage and it decreases with application of negative voltage.

FIGURE 3.15. Current curve for sinusoidal input voltage with variable frequency (Verilog-AMS model).

FIGURE 3.16. Surface I - V curve for sinusoidal input voltage (Verilog-AMS model).

Fig. 3.19 shows both current and resistance values plotted against applied voltage. Hysteresis curve is observed for current, owing to the fact that memristor remembers the amount of current passed through it. The resistance curve is identical to results observed in other simulations. It verifies the properties that were first proposed by Chua [7] and which was later experimentally verified at HP Labs [37, 44].

FIGURE 3.17. Current and voltage vs. time (Spice model).

FIGURE 3.18. Resistance and voltage vs. time (Spice model).

# 3.5. Simscape based Behavioral Model

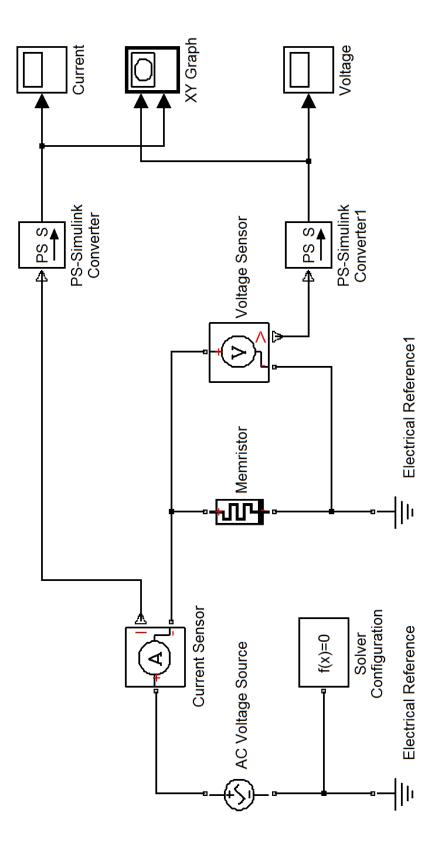

A block-based Simulink/Simscape memristor model was presented in [45] in which the variable resistor physical model was employed and the window function proposed in [4] was included. The differential equation in HP model that described the memristor dynamics was realized in integral form. The physical signal (current) through the memristor was first converted to a Simulink signal, followed by integration and windowing operation, then the signal was converted back to the physical domain. This hybrid approach limits the model efficiency. In this thesis, a memristor

FIGURE 3.19. Resistance and current vs. voltage (Spice model).

model is presented which is completely in Simscape language only. To our best knowledge, this is the first ever Simscape memristor model. The memristor dynamic is realized in differential form as the original mathematical equation, which came as salient feature of Simscape.

The environment has a variety of Simscape physical component libraries. Custom Simscape models for novel devices such as memristor can be created graphically using other fundamental Simulink/Simscape blocks or textually with Simscape physical modeling language. For this research, the latter was opted since it offers better portability and it is easier to maintain. The proposed Simscape memristor model is presented in Algorithm 1. It models the memristor current-voltage (I - V) relation and the dynamic described in Eqn. (2) and Eqn. (3).

In Algorithm 1, the parameter section (Lines 4-9) assigns the device parameters such as dopant mobility, minimum and maximum memristance values. In practice, the doped region cannot exceed the physical boundaries of the device, i.e.,  $0 \le w \le D$ . At the boundaries, dw/dt should be 0 if the externally applied voltage/current intends to push w beyond the limits. Defining the memristor state variable  $X = w/D \in (0, 1)$ ,  $X_0$  denotes the initial condition for X. Lines 21-29 realize the memristor dynamic and implement a boundary-checking mechanism to avoid boundary issues. Lines 30 and 31 implement Eqn. (2).

FIGURE 3.20. The configuration of Simulink/Simscape memristor simulation.

Algorithm 1 Simscape memristor model.

```

1

component memristor<foundation.electrical.branch

2

3

parameters

u = \{ 1e-14, 'm^2/s/V' \};

4

% Mobility

x0 = { 0,'1' }; % Initial (w/D)

5

6

d = { 5e-9, 'm' }; % Memristor Width

7

ron = {100, 'Ohm' }; % Minimum Resistance

8

roff = {36e3, 'Ohm'}; % Maximum Resistance

9

end

10

11

variables

12

x = \{1, '1'\};

Rmem ={1e3,'Ohm'};

13

14

end

15

16

function setup

17

x = x0;

18

end

19

20

equations

21

let

az = u * ron / d^2;

22

23

in

if(x \le 0 \& v \le 0) | | (x \ge 1 \& v \ge 0)

24

25

x.der == 0;

26

else

27

x.der == az * i;

28

end % if

29

end

Rmem == ron * x + roff * (1 - x);

30

31

v == i * Rmem;

32

end % equations

33

end % component

```

The memristor model was tested in Simulink/Simscape simulation environment. The memristor simulation setup in Simscape is shown in Fig. 3.20. The voltage, current, and resistance characteristics with respect to time are shown in Fig. 3.21. The memristor was simulated with the device parameter values given in Algorithm 1 and an external sinusoidal voltage source with a 2-V peak amplitude. Fig. 3.21a shows the memristor current and voltage against time. Fig. 3.21b shows resistance values against time. It is observed that the memristance increases with positive applied voltage and decreases with negative applied voltage, which was one of the memristor properties [44]. It is also observed that initially there is no change in resistance because  $X_0 = 0$  gives  $R_{in} = R_{off}$  and resistance cannot be increased above physical maximum. Fig. 3.22 shows the

FIGURE 3.21. Time-domain simulation result for a 2-V, 2 Hz applied sinusoidal voltage. I - V characteristics of the memristor with three different input frequencies [20]. The Simscape model is thus fully validated and can be used for system design exploration.

FIGURE 3.22. Memristor I - V characteristics for various input frequencies.

## CHAPTER 4

# MEMRISTOR BASED WIEN OSCILLATOR

Using Simscape, memristor modeling is performed in textual form. The textual form provides better portability and is easy to maintain. As a specific case study a memristor based programmable oscillator is presented here. As suggested in [31], programmability can be introduced in analog circuits by appropriately employing memristors. Specifically, the resistors that determine the circuit characteristics are replaced by memristors in which variable resistance provides tuning. In order for memristor integrated circuits to be practical, one should carefully verify that the undesirable behavior, if any, introduced by the memristor is within the acceptable range. For some cases, it is also necessary to explore various configurations of a memristor based circuit. As a case study, study of a Wien oscillator with the memristor added programmability using the proposed Simscape memristor model is presented in this thesis. The oscillation frequency and power consumption of various memristor configurations are presented.

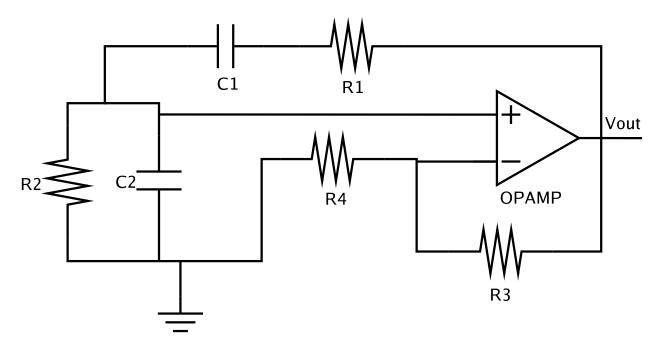

# 4.1. Wien Oscillator: The Case Study Circuit

A Wien oscillator is used as specific case study circuit. The schematic representation is shown in Fig. 4.1. The Wien oscillator comprises of four resistors and two capacitors. This oscillator works without any external oscillation source. The combination of negative and positive feedback with an operational amplifier (OP-AMP) drives it into an unstable state and hence sustained oscillation is achieved. Typically, it is used to generate signals with frequency from 20 Hz to 20 kHz and is widely used for audio signal generation.

In a traditional Wien oscillator, the resistors and capacitors have constant values. This ensures that the amplitude and the frequency of the oscillation remain constant. The condition for sustained oscillation is given by the following expression:

(5)

$$\frac{C_2}{C_1} + \frac{R_1}{R_2} = \frac{R_3}{R_4}.$$

The frequency of any Wien oscillator is calculated by the following expression:

(6)

$$f = \frac{1}{2\pi\sqrt{R_1R_2C_1C_2}}$$

FIGURE 4.1. Schematic of a Wien oscillator.

When the resistors are replaced with memristors, the oscillation frequency can be varied by controlling the memristance according to Eqn.(6). Assuming the memristance is not intentionally changed during normal oscillation, the initial condition of memristor determines the frequency of the oscillator. Five different configurations of the Wien oscillator were studied. Their functionality and characteristics are verified using Simulink/Simscape simulations. The conditions governing the sustained oscillation and formulas to calculate the frequency are included. Five different configurations of memristor that have been studied are summarized in Table 4.1.

TABLE 4.1. Variations of Wien oscillators.

| Configuration   | Independent Modifications                  | Dependent Modifications                                           |

|-----------------|--------------------------------------------|-------------------------------------------------------------------|

| Configuration 1 | $R_1 \Rightarrow M_1$                      | $R_3 \Rightarrow R_4(1 + R_{1,mem}/R_2)$                          |

| Configuration 2 | $R_2 \Rightarrow M_2$                      | $R_3 \Rightarrow R_4(1 + R_1/R_{2,mem})$                          |

| Configuration 3 | $R_3 \Rightarrow M_3, R_4 \Rightarrow M_4$ | $R_3 \Rightarrow 2R_{4,mem}$ , Given that $R_1 = R_2$             |

| Configuration 4 | $R_2 \Rightarrow M_2, R_4 \Rightarrow M_4$ | $R_3 \Rightarrow R_{2,mem} + R_1$                                 |

| Configuration 5 | $Resistors \Rightarrow Memristors$         | $R_3 \Rightarrow 2R_{4,mem}$ , Given that $R_{1,mem} = R_{2,mem}$ |

In configuration 1,  $R_1$  is replaced with memristor  $M_1$  whose resistance is labeled as  $R_{1,mem}$ . In configuration 2,  $R_2$  is replaced with memristor  $M_2$  whose resistance is labeled as  $R_{2,mem}$ . In configuration 3,  $R_3$  and  $R_4$  were replaced with  $M_3$  and  $M_4$  respectively, whose resistance is labeled

as  $R_{3,mem}$  and  $R_{4,mem}$ . Similarly in configuration 4,  $R_2$  and  $R_4$  were replaced with  $M_2$  and  $M_4$  whose resistance is labeled as  $R_{2,mem}$  and  $R_{4,mem}$  respectively. Finally in configuration 5, all resistors were replaced with memristors. The conditions for sustained oscillation and the oscillation frequencies for the five configurations are listed in Table 4.2.

| Configuration   | Condition for Oscillation                                       | Frequency                                    |

|-----------------|-----------------------------------------------------------------|----------------------------------------------|

| Traditional     | $\frac{C_2}{C_1} + \frac{R_1}{R_2} = \frac{R_3}{R_4}$           | $\frac{1}{2\pi\sqrt{R_1R_2C_1C_2}}$          |

| Configuration 1 | $1 + \frac{R_{1,mem}}{R_2} = \frac{R_3}{R_4}$                   | $\frac{1}{2\pi C\sqrt{R_{1,mem}R_2}}$        |

| Configuration 2 | $1 + \frac{R_1}{R_{2,mem}} = \frac{R_3}{R_4}$                   | $\frac{1}{2\pi C\sqrt{R_1R_{2,mem}}}$        |

| Configuration 3 | $1 + \frac{R_1}{R_2} = \frac{R_{3,mem}}{R_{4,mem}}$             | $\frac{1}{2\pi C\sqrt{R_1R_2}}$              |

| Configuration 4 | $1 + \frac{R_1}{R_{2,mem}} = \frac{R_3}{R_{4,mem}}$             | $\frac{1}{2\pi C\sqrt{R_1R_{2,mem}}}$        |

| Configuration 5 | $1 + \frac{R_{1,mem}}{R_{2,mem}} = \frac{R_{3,mem}}{R_{4,mem}}$ | $\frac{1}{2\pi C \sqrt{R_{1,mem}R_{2,mem}}}$ |

TABLE 4.2. Equations for Wien oscillators.

### 4.2. One Resistor Replaced with Memristor

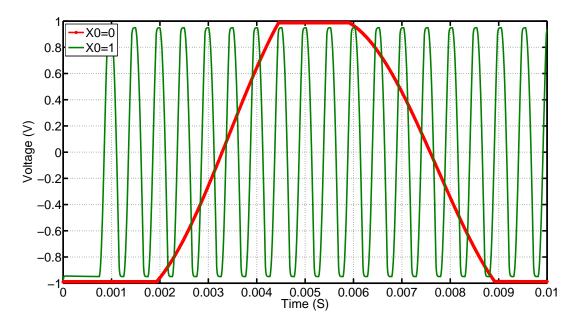

In configuration 1 (Fig. 4.2),  $R_1$  was replaced with a memristor. The memristance can vary from simulation to simulation. However, in each of the simulations, the memristance is not intentionally changed. Therefore, the oscillation frequency mainly depends upon the initial condition of memristor. According to (5) and Table 4.2, as the memristance varies, other resistance values have to be changed to satisfy the condition for sustained oscillation [38]. Here  $R_3$  is changed to achieve oscillation depending on the  $R_{in}$  (initial memristance) value.  $R_3$  is designed to be  $R_4(1 + \frac{R_{1,mem}}{R_2})$ . Fig. 4.4 plots the oscillator outputs when  $X_0 = 0$  and  $X_0 = 1$ . Similarly, for configuration 2 (Fig. 4.5),  $R_2$  was replaced a with memristor to achieve oscillation.  $R_3$  is designed to be  $R_4(1 + \frac{R_1}{R_2,mem})$ .

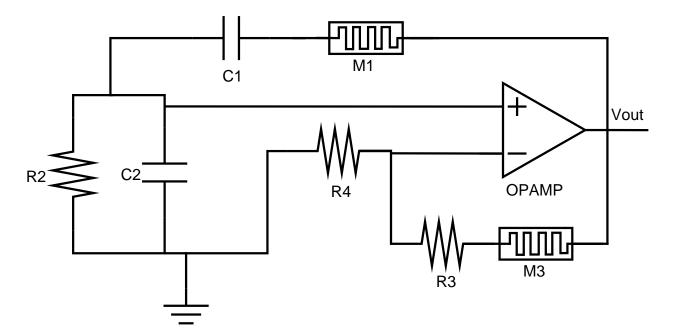

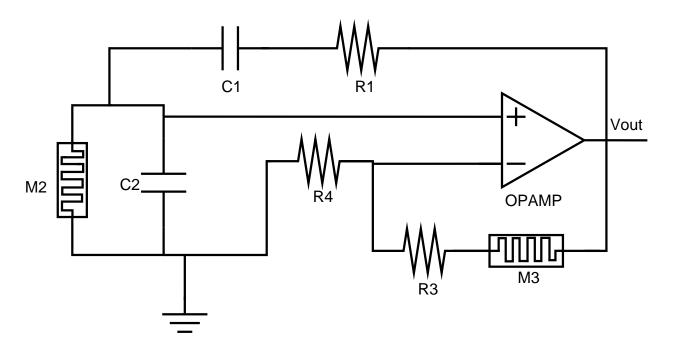

### 4.3. Two Resistors Replaced with Memristors

In this section, configurations where two resistors were replaced with memristors are discussed. Two different configurations were studied. In configuration 3 (Fig. 4.6),  $R_3$  and  $R_4$  were replaced with memristors. Again, to fulfill the condition of oscillation, different rating memristors were used. Given that  $R_4 = R_{4,mem}$  and  $R_1 = R_2$ ,  $R_3$  is calculated to be  $2R_{4,mem}$ . In configuration

FIGURE 4.2. Resistor  $R_1$  replaced with memristor (Configuration 1).

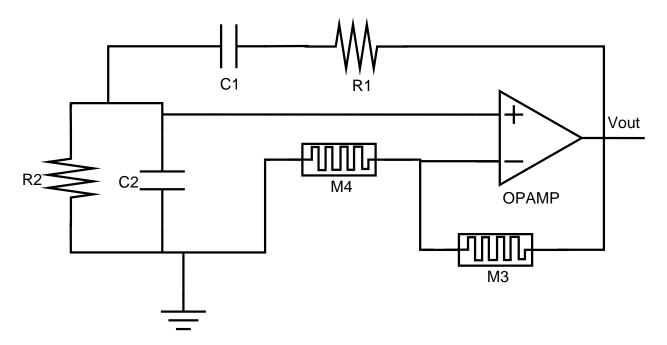

4 (Fig. 4.7),  $R_2$  and  $R_4$  were replaced with memristors. Given that  $R_{2,mem} = R_{4,mem}$ ,  $R_3$  was replaced with memristor-resistor combination expressed as  $R_{2,mem} + R_1$ .

#### 4.4. All Resistors Replaced with Memristors

Finally, all four resistors were replaced with memristors in configuration 5 as shown in (Fig. 4.8). All memristors were replaced with same rating but  $R_3$  was replaced with  $2R_{mem}$  to achieve condition of oscillation. The simulated oscillator outputs are shown in Fig. 4.9.

At frequency higher than 15 Hz the current direction changes very fast thus the variation in memristance is very low, so a memristor acts almost like a normal resistor [39].  $R_{avg}$  (average resistance) was used in all calculations where  $R_{mem}$  was required.

4.5. Frequency and Power Analysis of the Memristor

Five different configurations and the traditional Wien oscillator were simulated for various initial conditions. The oscillation frequency and the power consumption were chosen as the figure of merits (FOMs). Table 4.3 shows the simulation result obtained from Simscape and calculation obtained using Table 4.2. The simulated and calculated frequencies show high degree of agreement. The table shows the results for two extreme conditions for the memristors,  $X_0 = 0$  ( $R_{in} = R_{off}$ ) and  $X_0 = 1$  ( $R_{in} = R_{on}$ ). Fig. 4.10 shows how the frequency of different configuration changes

FIGURE 4.3. Experimental setup in Simulink/Simscape.

FIGURE 4.4. Output signal when  $R_1$  is replaced with a memristor.

FIGURE 4.5. Resistor  $R_2$  replaced with memristor (Configuration 2).

with  $R_{in}$ . It was observed that the frequency decreases with increasing  $R_{in}$  except in the configuration 3 where the frequency was constant. The frequency curve followed the relationships presented in Table 4.2.

FIGURE 4.6. Two resistors replaced with memristors (Configuration 3).

FIGURE 4.7. Two resistors replaced with memristors (Configuration 4).

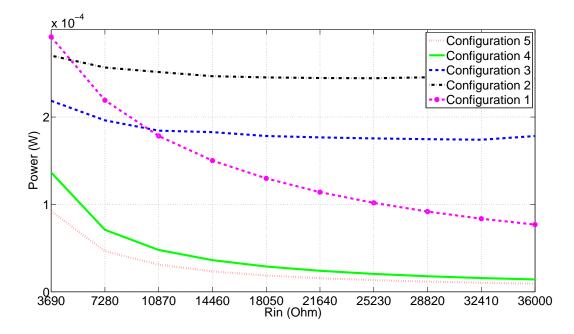

For power profile, current and voltage for different configurations were observed and power consumption was calculated. Table 4.4 shows the minimum and maximum instantaneous power and the average power for all the configurations at two extreme settings. Fig. 4.11 shows the

FIGURE 4.8. The schematic of the Wien oscillator with five memristors (Configuration 5).

FIGURE 4.9. Oscillator output when all resistors are replaced with memristors.

average power profile for different configurations observed for different  $R_{in}$  values. It was observed that the power also decreases with increasing  $R_{in}$ . From the frequency and power profiles, following observations were made:

| Frequency (Hz)  |           |           |            |         |  |

|-----------------|-----------|-----------|------------|---------|--|

| Configuration   |           | Simulated | Calculated | Error % |  |

| Traditional     |           | 1591.3    | 1591.54    | 0.0154  |  |

| Configuration 1 | $X_0 = 0$ | 118.65    | 118.65     | 0.0082  |  |

| Configuration 1 | $X_0 = 1$ | 2030.3    | 2077.3     | 2.2627  |  |

| Conformation 2  | $X_0 = 0$ | 264.67    | 265.26     | 0.2228  |  |

| Configuration 2 | $X_0 = 1$ | 4309      | 4317.27    | 0.1916  |  |

| Configuration 2 | $X_0 = 0$ | 1591      | 1591.54    | 0.0343  |  |

| Configuration 3 | $X_0 = 1$ | 1591      | 1591.54    | 0.0343  |  |

| Configuration 1 | $X_0 = 0$ | 265       | 265.41     | 0.1526  |  |

| Configuration 4 | $X_0 = 1$ | 4765.3    | 4768.44    | 0.0722  |  |

| Configuration 5 | $X_0 = 0$ | 44        | 44.23      | 0.5156  |  |

| Configuration 5 | $X_0 = 1$ | 12388     | 12791      | 3.1524  |  |

TABLE 4.3. Frequency distribution for Wien oscillators.

FIGURE 4.10. Frequency distribution for Wien oscillators.

- Oscillation frequency range were same for configurations 2 and 4 but configuration 4 consumes much lower power.

- Configuration 3 had constant frequency as a traditional Wien oscillator but its power consumption was lower.

- Configuration 5 had the lowest average power and a reasonable frequency range.

| Power (W)       |           |              |             |             |  |  |

|-----------------|-----------|--------------|-------------|-------------|--|--|

| Configuration   |           | Minimum      | Maximum     | Average     |  |  |

| Traditional     |           | -4.07300E-05 | 6.98300E-04 | 2.93600E-04 |  |  |

| Configuration 1 | $X_0 = 0$ | -1.73300E-07 | 1.30400E-04 | 6.74100E-05 |  |  |

|                 | $X_0 = 1$ | -1.36300E-04 | 7.17100E-04 | 2.69900E-04 |  |  |

| Configuration 2 | $X_0 = 0$ | -3.1450E-06  | 4.79400E-04 | 2.42500E-04 |  |  |

|                 | $X_0 = 1$ | -1.9630E-05  | 9.21600E-04 | 3.95000E-04 |  |  |

| Configuration 3 | $X_0 = 0$ | -7.43000E-05 | 4.50500E-04 | 1.78500E-04 |  |  |

|                 | $X_0 = 1$ | -4.81100E-05 | 2.03000E-03 | 4.87200E-04 |  |  |

| Configuration 4 | $X_0 = 0$ | -1.06500E-05 | 3.86800E-05 | 1.35300E-05 |  |  |

|                 | $X_0 = 1$ | -8.95300E-07 | 4.35800E-04 | 1.78500E-04 |  |  |

| Configuration 5 | $X_0 = 0$ | -1.25600E-06 | 2.20300E+06 | 9.29200E-06 |  |  |

|                 | $X_0 = 1$ | 4.43200E-04  | 2.49600E-03 | 1.41300E-03 |  |  |

TABLE 4.4. Power profile for Wien oscillators.

• In Configuration 1, the power consumption range was wide.

FIGURE 4.11. Average power dissipation for Wien oscillators.

On the basis of these observations, each of the configurations has its own advantages and disadvantages. One should select the configuration based on the specific need of the application.

## CHAPTER 5

## CONCLUSION AND FUTURE RESEARCH

# 5.1. Conclusion

With nano-CMOS approaching its physical limit, researchers are actively working on alternative technologies like carbon nanotube, graphene, fullerenes, single-electron transistor, and memristor. The recently fabricated memristor is being extensively researched because of its analog property and capability to mimic biological synapses.

This thesis has outlined brief introduction of memristor and its history. Brief overview of different types of memristor was done before getting into detail about HP memristor. Different model of HP memristors were simulated for understanding and verification. Effect of change in frequency and amplitude of input signal was studied. It was observed that with lower amplitude and higher frequency peak to peak resistance is lowered. With high frequency, peak to peak current increases but the difference between two current values for same voltage decreases.

A simple behavioral memristor model was designed in Simscape in accordance with known properties. The memristor model was verified in MATLAB Simulink/Simscape simulation environment. A memristor integrated programmable Wien oscillator was presented. The simulated oscillation frequencies were verified with the calculated values from mathematical formulas. Initial condition of the memristor was deterministic factor for the frequency. At frequency above 15 Hz, polarity of current changes rapidly thus the variation in memristance is very low, so a memristor acts almost like a normal resistor [39]. Power and frequency analysis and observations have been made. It was observed that using memristor, programmability was achieved in traditional memristor. Power was relatively less when memristors were used. Also, greater flexibility and programmability was achieved in oscillator. Programmability would allow user to use same oscillator for generating different frequency.

## 5.2. Future Directions of Research

As next step of this research, more detailed memristor model can be designed. Memristor based analog circuits that mimics synapses will be studied which may support to the foundation

of neuromorphic architecture. Recently reported memcapacitor and meminductor [30, 10] will be studied to understand memristive system. Simscape is a promising tool for physical system modeling and simulation. To further exploit the capability of rapid physical modeling provided by Simscape, designs will be implemented in Simscape. Future studies thus can take advantage of Simscape modeling language.

#### BIBLIOGRAPHY

- H. Abdalla and M.D. Pickett, *Spice modeling of memristors*, Circuits and Systems (ISCAS), 2011 IEEE International Symposium on, May 2011, pp. 1832 –1835. 2, 8

- [2] A. Beck, J. G. Bednorz, Ch. Gerber, C. Rossel, and D. Widmer, *Reproducible switching effect* in thin oxide films for memory applications, Applied Physics Letters 77 (2000), no. 1, 139 –141. 7

- [3] D. Biolek, Z. Biolek, and V. Biolkova, *Spice modeling of memristive, memcapacitative and meminductive systems*, Circuit Theory and Design, 2009. ECCTD 2009. European Conference on, Aug. 2009, pp. 249 –252. 2, 8

- [4] Z. Biolek, D. Biolek, and V. Biolkova, SPICE Model of Memristor with Nonlinear Dopant Drift, Radioengineering 18 (2009), 210–214. 2, 8, 23, 25

- [5] F. A. Buot and A. K. Rajagopal, *Binary information storage at zero bias in quantum-well diodes*, Journal of Applied Physics 76 (1994), no. 9, 5552 –5560. 7

- [6] Yiran Chen and Xiaobin Wang, Compact modeling and corner analysis of spintronic memristor, Nanoscale Architectures, 2009. NANOARCH '09. IEEE/ACM International Symposium on, Jul. 2009, pp. 7–12. 11

- [7] L. Chua, *Memristor-the missing circuit element*, Circuit Theory, IEEE Transactions on 18 (1971), no. 5, 507 519. 1, 7, 9, 24

- [8] L.O. Chua and Sung Mo Kang, *Memristive devices and systems*, Proceedings of the IEEE 64 (1976), no. 2, 209 223. 7

- [9] H.J.B. da Costa, F. de Assis Brito Filho, and P.I. de Araujo do Nascimento, *Memristor be-havioural modeling and simulations using verilog-ams*, Circuits and Systems (LASCAS), 2012 IEEE Third Latin American Symposium on, 29 2012-March 2 2012, pp. 1 –4. 2, 8

- [10] M. Di Ventra, Y.V. Pershin, and L.O. Chua, *Putting memory into circuit elements: Memris-tors, memcapacitors, and meminductors [point of view]*, Proceedings of the IEEE 97 (Aug.), no. 8, 1371–1372. 42

- [11] Rodney Douglas, Misha Mahowald, and Carver Mead, *Neuromorphic analogue vlsi*, Annual review of neuroscience 18 (1995), 255–281. 5

- [12] Victor Erokhin and Marco P. Fontana, *Electrochemically Controlled Polymeric Device: a Memristor (and more) found two years ago*, (2008). 7

- [13] N. Gergel-Hackett, B. Hamadani, B. Dunlap, J. Suehle, C. Richter, C. Hacker, and D. Gundlach, *A flexible solution-processed memristor*, Electron Device Letters, IEEE 30 (2009), no. 7, 706–708. 9, 10

- [14] D. Ghai, S.P. Mohanty, and E. Kougianos, *Design of parasitic and process-variation aware nano-cmos rf circuits: A vco case study*, Very Large Scale Integration (VLSI) Systems, IEEE Transactions on 17 (Sept.), no. 9, 1339–1342. 4

- [15] Miao Hu, Hai Li, and R.E. Pino, *Fast statistical model of tio<sub>2</sub> thin-film memristor and design implication*, Computer-Aided Design (ICCAD), 2011 IEEE/ACM International Conference on, Nov. 2011, pp. 345 –352. 3, 8

- [16] Sung Hyun Jo, Ting Chang, Idongesit Ebong, Bhavitavya B. Bhadviya, Pinaki Mazumder, and Wei Lu, *Nanoscale memristor device as synapse in neuromorphic systems*, Nano Letters 10 (2010), no. 4, 1297–1301, PMID: 20192230. 9

- [17] Sung Hyun Jo and Wei Lu, Cmos compatible nanoscale nonvolatile resistance switching memory, Nano Letters 8 (2008), no. 2, 392–397, PMID: 18217785. 5, 9

- [18] Hyongsuk Kim, M.P. Sah, Changju Yang, Seongik Cho, and L.O. Chua, *Memristor emulator for memristor circuit applications*, Circuits and Systems I: Regular Papers, IEEE Transactions on 59 (2012), no. 10, 2422 –2431. 3, 8

- [19] S. Kvatinsky, Memristors and Memristive Systems. 2, 8

- [20] Qingjiang Li, Hui Xu, Haijun Liu, and Xiaobo Tian, *Study of the noninverting amplifier based on memristor with linear dopant drift*, Intelligent System Design and Engineering Application (ISDEA), 2012 Second International Conference on, Jan. 2012, pp. 1136 –1139.

29

- [21] Gang Liu, Liang Fang, Nan Li, Bing Cai Sui, and Zhi Kui Duan, New behavioral modeling method for crossbar-based memristor, Microelectronics and Electronics (PrimeAsia), 2010

Asia Pacific Conference on Postgraduate Research in, sept. 2010, pp. 356 – 359. 9, 10

- [22] M. Mahvash and A.C. Parker, A memristor spice model for designing memristor circuits, Circuits and Systems (MWSCAS), 2010 53rd IEEE International Midwest Symposium on, Aug. 2010, pp. 989 –992. 2, 8

- [23] S.P. Mohanty, A special issue on power, parasitics, and process-variation (p3) awareness in mixed-signal design, Journal of Low Power Electronics 8 (2012), no. 3, 259–260. 4

- [24] \_\_\_\_\_, Memristor: From basics to deploymen, IEEE Potentials 32 (2013), no. 3, in press.

8, 9

- [25] S.P. Mohanty and E. Kougianos, Design of experiments and integer linear programmingassisted conjugate-gradient optimisation of high-κ/metal-gate nano-complementary metaloxide semiconductor static random access memory, Computers Digital Techniques, IET 6 (July), no. 4, 240–248. 4

- [26] R. Mutlu and E. Karakulak, *Emulator circuit of ti0<sub>2</sub> memristor with linear dopant drift made using analog multiplier*, Electrical, Electronics and Computer Engineering (ELECO), 2010

National Conference on, Dec. 2010, pp. 380 384. 3, 8

- [27] A.S. Oblea, A. Timilsina, D. Moore, and K.A. Campbell, *Silver chalcogenide based memristor devices*, Neural Networks (IJCNN), The 2010 International Joint Conference on, Jul. 2010, pp. 1–3.9

- [28] Yu. V. Pershin and M. Di Ventra, Spin memristive systems: Spin memory effects in semiconductor spintronics, Phys. Rev. B 78 (2008), 113309. 11

- [29] Yuriy V Pershin and Massimiliano Di Ventra, *Experimental demonstration of associative memory with memristive neural networks*, arXiv preprint arXiv:0905.2935 (2009). 5

- [30] Y.V. Pershin and M. Di Ventra, *Memristive circuits simulate memcapacitors and meminduc*tors, Electronics Letters 46 (1), no. 7, 517–518. 42

- [31] \_\_\_\_\_, *Practical approach to programmable analog circuits with memristors*, Circuits and Systems I: Regular Papers, IEEE Transactions on 57 (2010), no. 8, 1857 –1864. 3, 8, 31

- [32] R.E. Pino, J.W. Bohl, N. McDonald, B. Wysocki, P. Rozwood, K.A. Campbell, A. Oblea, and A. Timilsina, *Compact method for modeling and simulation of memristor devices: Ion*

*conductor chalcogenide-based memristor devices*, Nanoscale Architectures (NANOARCH), 2010 IEEE/ACM International Symposium on, june 2010, pp. 1–4. 9

- [33] T. Prodromakis, K. Michelakis, and C. Toumazou, *Fabrication and electrical characteristics* of memristors with  $tio_2/tio_{2-x}$  active layers, Circuits and Systems (ISCAS), Proceedings of 2010 IEEE International Symposium on, 30 2010-June 2 2010, pp. 1520–1522. 9, 10

- [34] A. Rak and G. Cserey, *Macromodeling of the memristor in spice*, Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions on 29 (2010), no. 4, 632 –636. 2, 8

- [35] U. Russo, D. Ielmini, C. Cagli, and A.L. Lacaita, *Filament conduction and reset mechanism in nio-based resistive-switching memory (rram) devices*, Electron Devices, IEEE Transactions on 56 (2009), no. 2, 186–192. 5

- [36] Khaled N. Salama, Memristor Model. 2, 8, 17

- [37] Dmitri B. Strukov, Gregory S. Snider, Duncan R. Stewart, and R. Stanley Williams, *The Missing Memristor Found*, Nature 453 (2008), 80–83. 2, 6, 7, 24

- [38] A. Talukdar, A.G. Radwan, and K.N. Salama, *Time domain oscillating poles: Stability redefined in memristor based wien-oscillators*, Microelectronics (ICM), 2010 International Conference on, Dec. 2010, pp. 288–291. 33

- [39] \_\_\_\_\_, State space modeling of memristor-based wien oscillator, Microelectronics (ICM),

2011 International Conference on, Dec. 2011, pp. 1 –4. 34, 41

- [40] S. Thakoor, A. Moopenn, T. Daud, and A. P. Thakoor, Solid-state thin-film memistor for electronic neural networks, Journal of Applied Physics 67 (1990), no. 6, 3132 –3135. 7

- [41] Hoang M. Thang, Memristor Model-MATLAB Central. 2, 8, 15

- [42] Xiaobin Wang and Yiran Chen, Spintronic memristor devices and application, Design, Automation Test in Europe Conference Exhibition (DATE), 2010, Mar. 2010, pp. 667 –672.

11

- [43] Xiaobin Wang, Yiran Chen, Haiwen Xi, Hai Li, and D. Dimitrov, Spintronic memristor through spin-torque-induced magnetization motion, Electron Device Letters, IEEE 30 (2009), no. 3, 294 –297. 11

- [44] R. Williams, *How we found the missing memristor*, Spectrum, IEEE 45 (2008), no. 12, 28 –35. 2, 7, 9, 24, 28

- [45] Karel Zaplatilek, *Memristor modeling in matlab & simulink*, Proceedings of the 5th European conference on European computing conference, ECC'11, 2011, pp. 62–67. 2, 8, 25

- [46] Yu Zhang, Xuliang Zhang, and Juebang Yu, *Approximated spice model for memristor*, Communications, Circuits and Systems, 2009. ICCCAS 2009. International Conference on, July 2009, pp. 928–931. 2, 8