# Vniver§itat ið València

Departamento de Física Atómica, Molecular y Nuclear IFIC (Universitat de València - CSIC)

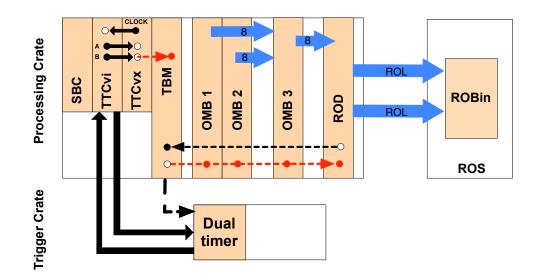

## The Back-End Electronics for the ATLAS Hadronic Tile Calorimeter at the Large Hadron Collider

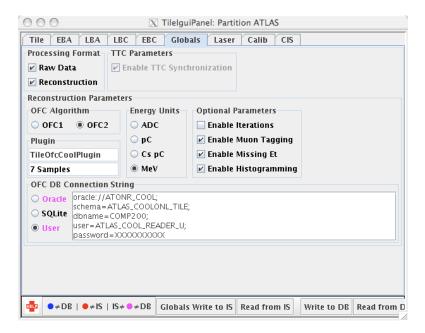

TESIS DOCTORAL

Jose Alberto Valero Biot

DIRECTORES Juan A. Valls Ferrer Vicente González Millán

Valencia, 2014

# Declaration

This dissertation is the result of my own work, except where explicit reference to the work of others is made. It has not been submitted for another qualification in this or any other university.

Jose Alberto Valero Biot

## Acknowledgements

Quiero dedicar esta tesis a mis padres. Sin la educación que me dieron y los valores de trabajo y constancia que me trasladaron no habría sido posible realizar un trabajo como este. Gracias papas.

De igual forma no habría podido terminar esta tesis sin el apoyo incondicional de Mireia, que siempre estuvo a mi lado durante este más que largo periodo animando y ayudando en todo momento. Gracias Mireieta.

First of all I would like to express my very great appreciation to professors Enrique Sanchis and Vicente González who offered me the possibility to start working in the IFIC TileCal group. I would like also thank the professors Victoria Castillo, Antonio Ferrer, Emilio Higón and Juan Valls for all the support and help during all these years. Thanks to all them for the opportunity they gave to me to participate in the LHC adventure.

In March 2005, I started working in the IFIC TileCal group and since then, I had the opportunity to work and collaborate with great colleagues and friends: Jose Castelo, Esteban, Toni Munar, Belen, Ximo, Arantxa, Jose Torres, Cristobal, Jalal, Ali, Pablo, Luca, Bruce, Fernando, Cesar, Gang, Yesenia, Damian; Luís y Leonor. It has been really a pleasure working with you all.

A special mention goes to Carlos Solans. We have lived this exciting adventure together, starting with the production of the RODs in Valencia and following the installation, commissioning, the first LHC collisions and the data taking in Run 1. We had great time but there were also hard moments and long days in the pit and in the control room trying to debug and fix unexpected problems during the commissioning and operation of ATLAS. From my period at CERN as Run Coordinator, I want to thank all the people who made easier being away from home: Irakli, Stan, Ali, Julio and Robert which were always ready for having a beer or organizing a barbecues. Obviously I cannot forget my deputy Run Coordinator Louise Heelan and our endless coffee times profiting the limited sunny moments in the R1 patio.

My special acknowledgments to Giulio Usai for his valuable help and all the constructive discussions that we had in the infinite signal reconstruction task force. Finally I want to thank to Irene Vichou for her patience and continuous good mood despite the shouts and the loud spanish conversations in the office.

To all of them, thanks. It is easy to complete a work like this when one is surrounded by fantastic colleagues and friends like you all.

Jose Alberto Valero Biot Valencia, March 2014

# Preface

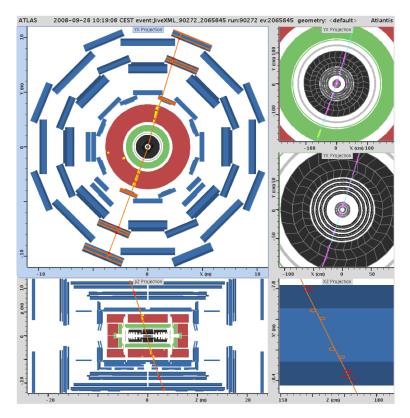

The work reported in this thesis was carried out during the first three years of operation (2010-2012) of the Large Hadron Collider accelerator at CERN (Geneva). It describes the back-end system of the Tile Hadronic Calorimeter of the ATLAS experiment.

Chapter 1 gives an overview of the history and main achievements of the CERN laboratory; it also describes the LHC accelerator and experiments, and with more detail the ATLAS detector. Finally it includes a description of the basic design concepts of the sub-detectors and the Trigger and Data Acquisition system of ATLAS.

The Tile Hadronic Calorimeter (TileCal) sub-detector and in particular the front-end instrumentation and read-out electronics are described in Chapter 2. It also introduces the TileCal calibration systems and the results obtained with them during the first years of operation.

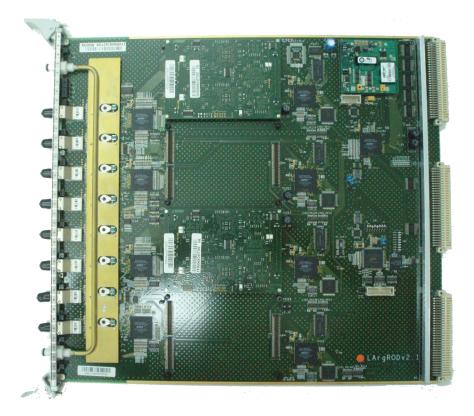

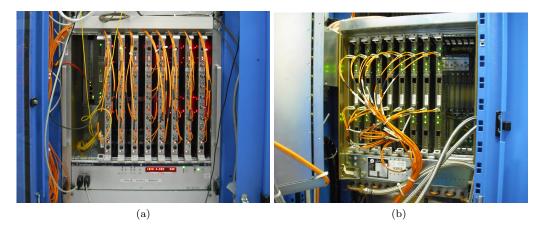

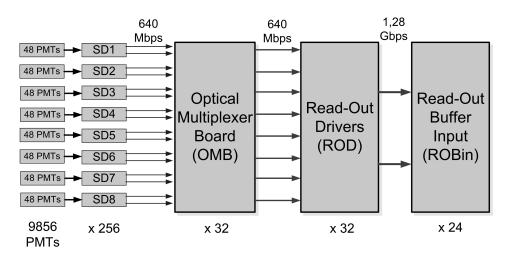

Chapters 3 and 4 describe the Read-Out Drivers (ROD) and the Optical Multiplexer Module (OMB) boards, respectively, which represent the core of the TileCal back-end system. The main components, operating modes and a complete description of the data format processed in the ROD boards are included. Then a description of the OMB module design and the main aspects of its firmware and functionalities is given. The installation, commissioning and the performance of the back-end system during the first three years of ATLAS operation are presented in Chapter 5.

Chapter 6 describes the work done in the implementation of the signal reconstruction algorithms in the Digital Signal Processors (DSP) of the ROD boards. In particular, it explains the formulation of the Optimal Filtering algorithm with a justification of its selection as the default reconstruction method in TileCal. It includes a description of the implementation of the Optimal Filtering method and the limited precision due to the usage of a fixed point arithmetic in the DSPs.

Chapter 7 is devoted to the study of the performance of the Optimal Filtering implemented in the DSPs. It includes the results of the reconstruction using pseudo-data generated in the laboratory used to corroborate the correct implementation of the method in the DSPs. Then, the performance of the DSP Optimal Filtering implementation is studied using the TileCal Charge Injection System. The last part of the Chapter shows the performance of the reconstruction for physics data, explaining the evolution of the reconstruction strategy as a function of the LHC beam parameters during the first three years of operation. Finally, results about the impact of using the TileCal DSP fixed point arithmetic in the reconstruction of jets in ATLAS are presented.

> Jose Alberto Valero Biot Valencia, June 2014

# Contents

| 1        | The | ATLA                    | AS Experiment at the CERN Large Hadron Collider | 7  |

|----------|-----|-------------------------|-------------------------------------------------|----|

|          | 1.1 | CERN                    | ·                                               | 7  |

|          | 1.2 | The La                  | arge Hadron Collider                            | 9  |

|          | 1.3 | The A                   | TLAS Experiment                                 | 12 |

|          |     | 1.3.1                   | The Inner Detector                              | 14 |

|          |     | 1.3.2                   | Calorimeters                                    | 16 |

|          |     | 1.3.3                   | The Muon Spectrometer                           | 20 |

|          |     | 1.3.4                   | Magnetic Field                                  | 21 |

|          | 1.4 | The A                   | TLAS Trigger and Data Acquisition System        | 22 |

|          |     | 1.4.1                   | The First Level of Trigger                      | 23 |

|          |     | 1.4.2                   | Data Acquisition System and High-Level Trigger  | 28 |

| <b>2</b> | The | ATLA                    | AS Tile Hadronic Calorimeter                    | 35 |

|          | 2.1 | Detector Overview       |                                                 |    |

|          | 2.2 | 2 Mechanical Structure  |                                                 | 36 |

|          |     | 2.2.1                   | Optical Components                              | 37 |

|          | 2.3 | 3 Front-end Electronics |                                                 | 39 |

|          |     | 2.3.1                   | Photomultiplier Block                           | 39 |

|          |     | 2.3.2                   | Digitizer System                                | 42 |

|          |     | 2.3.3                   | Interface Board                                 | 43 |

|          |     | 2.3.4                   | Trigger Board                                   | 43 |

#### Contents

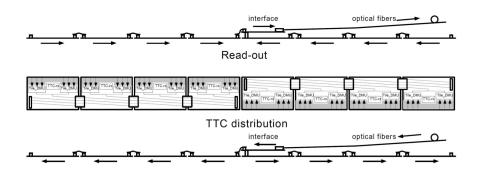

|   | 2.4  | Back-end Electronics Architecture                         |          |  |  |

|---|------|-----------------------------------------------------------|----------|--|--|

|   |      | 2.4.1 Trigger Timing and Control Modules                  | 5        |  |  |

|   |      | 2.4.2 ReadOut Modules                                     | 3        |  |  |

|   | 2.5  | TileCal ReadOut Principle    50                           | )        |  |  |

|   | 2.6  | Calibration Systems                                       | 1        |  |  |

| 3 | Tile | eCal ReadOut Driver System 57                             | 7        |  |  |

|   | 3.1  | Introduction                                              | 7        |  |  |

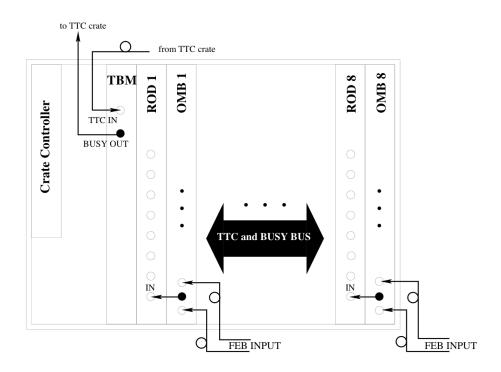

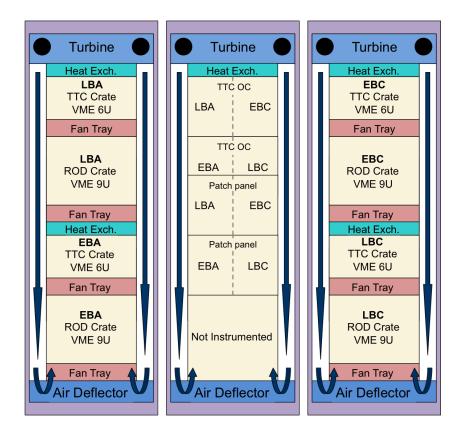

|   | 3.2  | Structure of the Back-end System. The Regions of Interest | 7        |  |  |

|   |      | 3.2.1 The TTC Crate                                       | )        |  |  |

|   |      | 3.2.2 The ROD Crate                                       | )        |  |  |

|   | 3.3  | Trigger and Busy Module                                   | 1        |  |  |

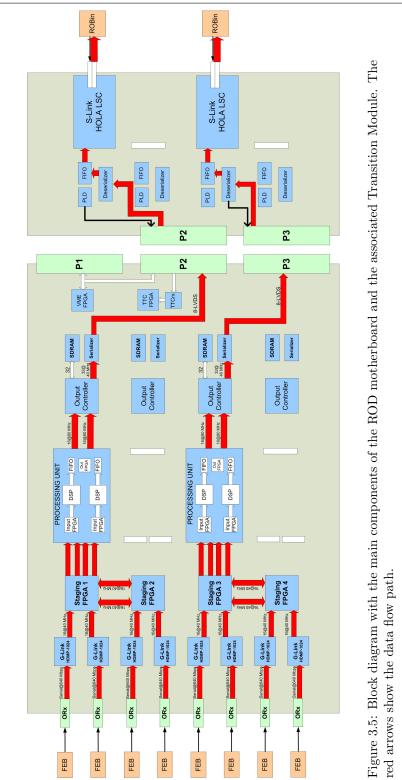

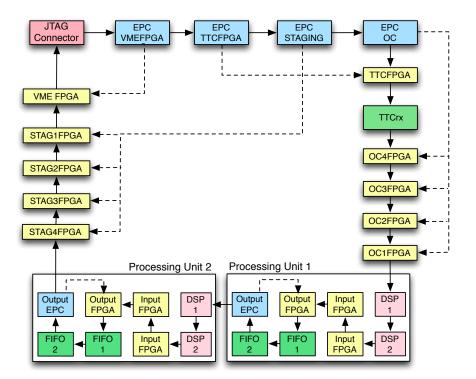

|   | 3.4  | ROD Module                                                | 2        |  |  |

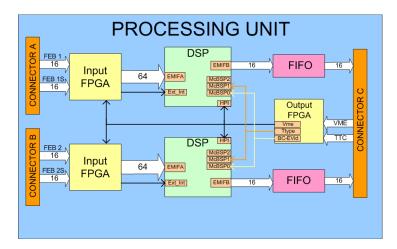

|   |      | 3.4.1 Processing Unit                                     | 7        |  |  |

|   | 3.5  | DSP Code Structure                                        | 3        |  |  |

|   | 3.6  | DSP Monitoring and Histogramming                          | 9        |  |  |

|   | 3.7  | Trigger and Data Acquisition Software                     | )        |  |  |

|   |      | 3.7.1 ROD Crate DAQ                                       | 1        |  |  |

|   |      | 3.7.2 The ROD Module                                      | 3        |  |  |

|   | 3.8  | ROD Data Format                                           | 1        |  |  |

|   |      | 3.8.1 ROD Input Data Format                               | 5        |  |  |

|   |      | 3.8.2 The DSP Input Data Format                           | 3        |  |  |

|   |      | 3.8.3 ROD Output Data Format                              | 1        |  |  |

|   |      | 3.8.4 Data Elements Description                           | 3        |  |  |

|   |      | 3.8.5 Calibration Fragments Data Format                   | 2        |  |  |

|   | 3.9  | ROD Operation Modes and Bandwidth Limitations             | 3        |  |  |

| 4 | Opt  | tical Multiplexer Board 9U 109                            | <b>)</b> |  |  |

|   | 4.1  | Introduction                                              | )        |  |  |

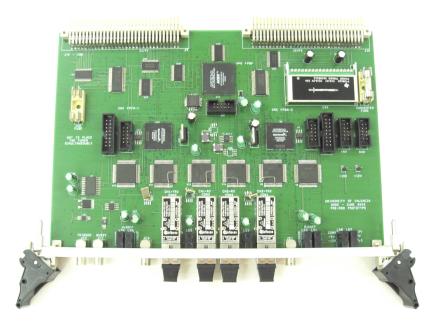

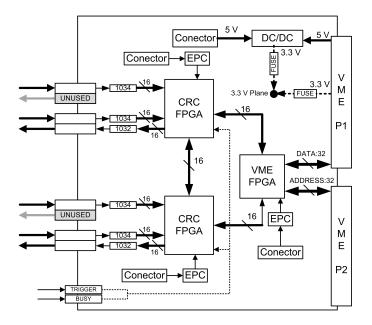

|   | 4.2  | OMB Motherboard                                           | 1        |  |  |

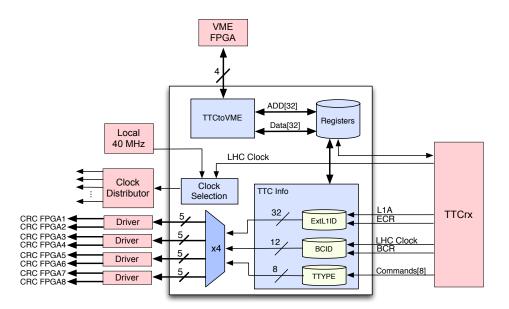

|   |      | 4.2.1 The CRC FPGA Firmware                               | 7        |  |  |

|   |     | 4.2.2                         | The VME FPGA Firmware                                                                                                                             |  |

|---|-----|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|

|   |     | 4.2.3                         | The TTC FPGA Firmware                                                                                                                             |  |

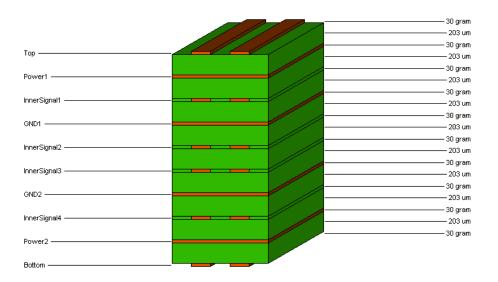

|   |     | 4.2.4                         | Printed Circuit Board and Power Distribution                                                                                                      |  |

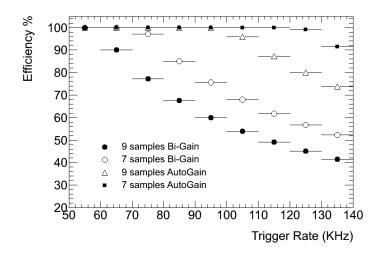

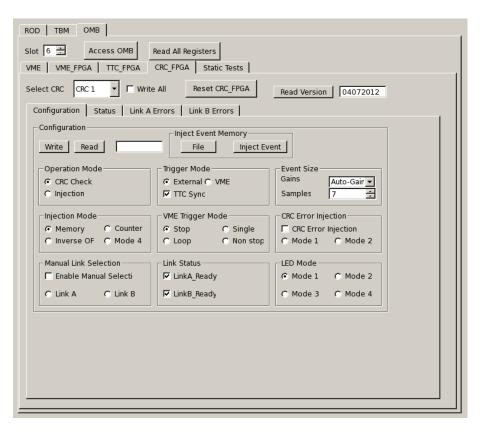

|   | 4.3 | Opera                         | ting Modes $\ldots \ldots \ldots$ |  |

|   |     | 4.3.1                         | The LHC Mode                                                                                                                                      |  |

|   |     | 4.3.2                         | Injection Modes                                                                                                                                   |  |

|   | 4.4 | VME                           | Library and Software for OMB                                                                                                                      |  |

| 5 | Pro | ductio                        | n, Commissioning and Operation of the Back-End System 131                                                                                         |  |

|   | 5.1 | Introd                        | uction $\ldots \ldots \ldots$     |  |

|   | 5.2 | Produ                         | ction and Qualification Tests                                                                                                                     |  |

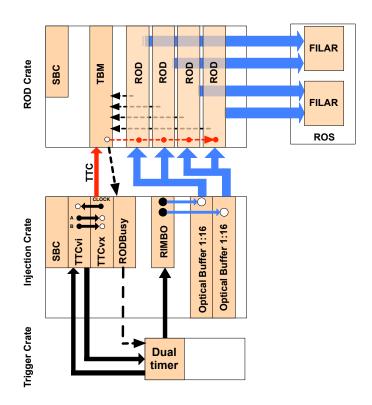

|   |     | 5.2.1                         | The ROD Production Test-Bench                                                                                                                     |  |

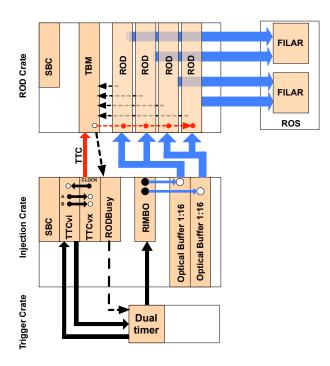

|   |     | 5.2.2                         | The Trigger Crate                                                                                                                                 |  |

|   |     | 5.2.3                         | The Injection Crate                                                                                                                               |  |

|   |     | 5.2.4                         | The ROD Crate                                                                                                                                     |  |

|   |     | 5.2.5                         | The Readout System Emulator                                                                                                                       |  |

|   |     | 5.2.6                         | ROD Qualification Protocol                                                                                                                        |  |

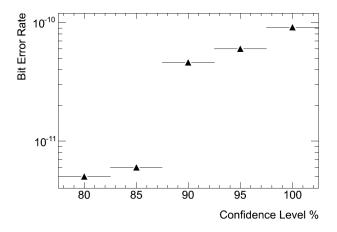

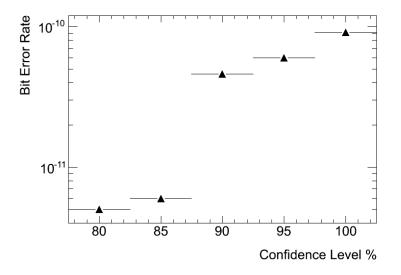

|   |     | 5.2.7                         | OMB Production and Qualification                                                                                                                  |  |

|   | 5.3 | Install                       | ation and Commissioning of the ROD System                                                                                                         |  |

|   |     | 5.3.1                         | TileCal Commissioning                                                                                                                             |  |

|   |     | 5.3.2                         | Integration of the ROD System to the Combined Cosmic Ray Muons                                                                                    |  |

|   |     |                               | Data Taking                                                                                                                                       |  |

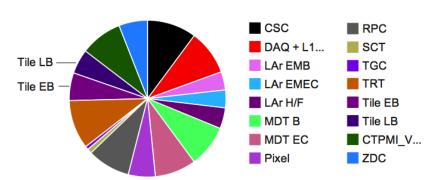

|   | 5.4 | Perfor                        | mance in ATLAS Operation                                                                                                                          |  |

|   |     | 5.4.1                         | Readiness of ROD System for Collisions in 2008                                                                                                    |  |

|   |     | 5.4.2                         | Operation During Early LHC Collisions (2009-2010)                                                                                                 |  |

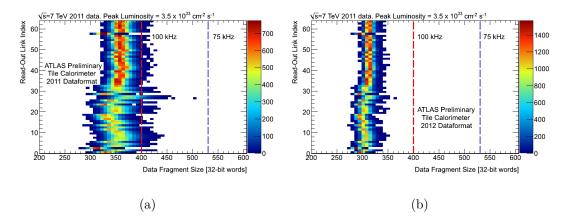

|   |     | 5.4.3                         | Operation and Performance at Design Specifications (2011-2012) 151                                                                                |  |

| 6 | The | e ROD                         | Reconstruction Algorithms 159                                                                                                                     |  |

|   | 6.1 | Introd                        | $uction \ldots 159$        |  |

|   | 6.2 | 2 Optimal Filtering Algorithm |                                                                                                                                                   |  |

|   |     | 6.2.1                         | Optimal Filtering Weights                                                                                                                         |  |

|   |                                                             | 6.2.2                                              | Iterations Method for Cosmic Ray Muons                                                             |  |  |  |

|---|-------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------|--|--|--|

|   |                                                             | 6.2.3                                              | Energy Calibration                                                                                 |  |  |  |

|   | 6.3                                                         | The D                                              | SP Reconstruction Algorithms                                                                       |  |  |  |

|   |                                                             | 6.3.1                                              | Optimal Filtering Implementation for LHC Operation                                                 |  |  |  |

|   |                                                             | 6.3.2                                              | Parabolic Deviation and Offline Correction                                                         |  |  |  |

|   |                                                             | 6.3.3                                              | Total Energy Sum Algorithm for the Level 2 $E_T^{miss}$ Trigger 186                                |  |  |  |

| 7 | Validation and Performance of the DSP Optimal Filtering 189 |                                                    |                                                                                                    |  |  |  |

|   | 7.1                                                         | Introd                                             | uction                                                                                             |  |  |  |

|   | 7.2                                                         | Valida                                             | tion of the DSP Optimal Filtering Implementation                                                   |  |  |  |

|   | 7.3                                                         | Qualif                                             | ication of DSP Reconstruction Under Controlled Conditions $\ldots \ldots \ldots 192$               |  |  |  |

|   |                                                             | 7.3.1                                              | DSP Reconstruction with Pseudo-Data                                                                |  |  |  |

|   |                                                             | 7.3.2                                              | Qualification with Calibration Data                                                                |  |  |  |

|   | 7.4                                                         | Optim                                              | al Filtering Performance with LHC Collisions Data                                                  |  |  |  |

|   |                                                             | 7.4.1                                              | Timing Adjustments for Collisions                                                                  |  |  |  |

|   |                                                             | 7.4.2                                              | Performance of the DSP Reconstruction with Low Pileup                                              |  |  |  |

|   |                                                             |                                                    | Collisions Data                                                                                    |  |  |  |

|   | 7.5                                                         | Optim                                              | nal Filtering Reconstruction with 50 ns Bunch Spacing Collisions $\ . \ . \ . \ . \ 209$           |  |  |  |

|   | 7.6                                                         | 6 Performance of the Quality Factor Reconstruction |                                                                                                    |  |  |  |

|   | 7.7                                                         | Study                                              | of the DSP Reconstruction Using Jets $\hfill \ldots \ldots \ldots \ldots \ldots \ldots \ldots 215$ |  |  |  |

|   |                                                             | 7.7.1                                              | ATLAS Jet Reconstruction Algorithms                                                                |  |  |  |

|   |                                                             | 7.7.2                                              | Impact of the DSP Energy Reconstruction in Jets                                                    |  |  |  |

| 8 | Cor                                                         | nclusio                                            | ns 225                                                                                             |  |  |  |

| 9 | Resumen 229                                                 |                                                    |                                                                                                    |  |  |  |

|   | 9.1                                                         | El Exj                                             | perimento ATLAS en el Gran Colisionador de Hadrones en el CERN 229                                 |  |  |  |

|   | 9.2                                                         | El Sist                                            | tema de electrónica de $Back\mathchar`-End$ del Calorímetro TileCal de ATLAS 231                   |  |  |  |

|   |                                                             | 9.2.1                                              | Producción y Tests de Validación de los Módulos ROD y OMB $\ .\ .\ .\ .\ 235$                      |  |  |  |

|   |                                                             | 9.2.2                                              | Instalación y Puesta a Punto                                                                       |  |  |  |

| 9.2.3 Funcionamiento Durante los Tres Primeros Años de Toma de Dato |        |                                                                                        |     |

|---------------------------------------------------------------------|--------|----------------------------------------------------------------------------------------|-----|

|                                                                     |        | ATLAS                                                                                  | 238 |

| 9.3                                                                 | Algori | tmos de Reconstrucción de Señal en los Módulos ROD de TileCal $\ .\ .\ .$              | 241 |

|                                                                     | 9.3.1  | El Método Optimal Filtering                                                            | 241 |

|                                                                     | 9.3.2  | Implementación de OF en los Procesadores Digitales de Señal (DSP) de                   |     |

|                                                                     |        | los Módulos ROD                                                                        | 243 |

| 9.4                                                                 | Valida | ción y Funcionamiento de los Métodos de Reconstrucción de Señal                        | 246 |

|                                                                     | 9.4.1  | Evaluación de la Reconstrucción de Señal con Datos de Calibración $\ $ .               | 247 |

|                                                                     | 9.4.2  | Evaluación con Datos de Física Producidos en Colisiones $\ \ \ldots \ \ldots \ \ldots$ | 250 |

| List of Acronyms                                                    |        |                                                                                        | 260 |

| Bibliography                                                        |        |                                                                                        | 265 |

| List of Figures                                                     |        |                                                                                        | 269 |

| List of Tables                                                      |        |                                                                                        | 283 |

Contents

## Chapter 1

# The ATLAS Experiment at the CERN Large Hadron Collider

## 1.1 CERN

CERN is the European Organization for Nuclear Research. The name CERN derives from the French acronym Conseil European pour la Recherche Nucleaire (European Council for Nuclear Research), which was a provisional council to set-up the laboratory in 1952 with the mandate of establishing a fundamental physics research organization in Europe. The organization became official in 1954 with the title of European Organization for Nuclear Research, although the name CERN was retained. The Globe of Science and Innovation was built on Galileo Galilei's square to celebrate the CERN's 50th anniversary of foundation (Figure 1.1). The Globe is used for general public presentations of science, technology and industry.

The knowledge of the matter in those days was limited to the atomic nucleus, hence the name nuclear. Today, our understanding of matter goes much deeper than the nucleus, and CERN's main area of research is particle physics, the study of the fundamental constituents of matter and the forces acting between them. Because of this, the laboratory operated by CERN is commonly referred to as the European Laboratory for Particle Physics.

Chapter 1. The ATLAS Experiment at the CERN Large Hadron Collider

Figure 1.1: View of the CERN Globe of Science and Innovation and the ATLAS surface buildings.

CERN is run by 20 European Member States, but many non-European countries are also involved in different ways. Scientists come from around the world to use CERNs facilities.

The discovery of neutral currents in the Gargamel bubble chamber, the first creation of anti hydrogen in the PS20 experiment, the discovery of direct CP violation in the NA48 experiment and the isolation of 38 atoms of antihydrogen are just few examples among a long list of important physics achievements made at CERN. In 1984 Carlo Rubbia and Simon Van der Meer received the Nobel Prize in physics for their contribution in the discovery of the W and Z bosons. This result conformed the unification of the electromagnetic and weak forces, the electroweak theory of the Standard Model. More recently, in 2012 the ATLAS and CMS experiments announced the discovery of a new boson with mass around 125 GeV consistent with long-sought Higgs boson, which led to the nobel prize in physics in 2013 to François Englert and Peter W. Higgs.

The discoveries of the W, Z and the Highs bosons are without a doubt the most important achievements made at CERN since its foundation. Moreover, CERN offers the excellent environment for development of new technologies in other fields like electronics or computing. One example is the World Wide Web (WWW), invented at CERN in 1989, which was conceived to facilitate the exchange of information between scientists working in different institutes and collaborating through CERN.

## 1.2 The Large Hadron Collider

In the early times particle accelerators collided high energetic particles with a stationary target where the most valuable energy of the particles was taken up by the target recoil and only a small fraction of it fed the real collision.

Since its foundation people at CERN worked in a new scheme where two particle beams were accelerated and collided with each other. Thus, no recoil energy would be wasted, making for much more efficient collisions. A new Proton Synchrotron (PS) was used to feed two Intersecting Storage Rings (ISR) where two proton beams could be built and finally collide.

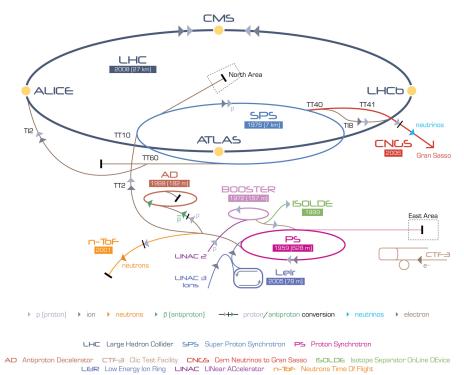

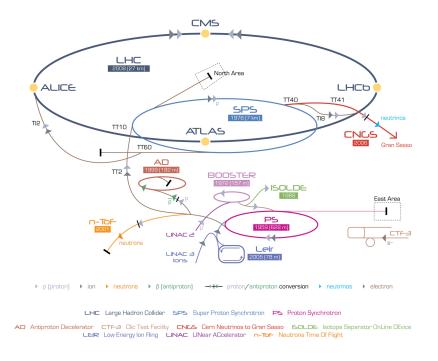

Figure 1.2: The CERN's accelerators complex.

The ISR was commissioned in 1971 and represented the world's first proton-proton collisions. The collider, regarded as a masterpiece, gained CERN the knowledge and expertise for its subsequent colliding beam projects.

In 1979 CERN profited of its ISR investment by deciding to convert its new Super Proton Synchrotron (SPS) into the world's first proton-antiproton collider. The first protonantiproton collisions were achieved just two years after the project was approved, and in 1983 the W and Z bosons were discovered.

After that the Large Electron-Positron Collider (LEP) was planned, and the ISR was switched off to release resources for its construction. LEP was a circular collider with a circumference of 27 km built in a tunnel straddling the border of Switzerland and France. It was used from 1989 until the end of 2000, when it was shut down and then dismantled in order to make room in the tunnel for the Large Hadron Collider (LHC) [1].

Protons are accelerated and formed in beams in four increasingly large machines before being injected with an energy of 450 GeV into the LHC's 27 km ring (Figure 1.2). The beams are then accelerated in the ring until their energy has increased by a factor of 15, up to 7 TeV. When that energy is reached, the proton beams collide in the center of the experiments. The details of the LHC can be seen in Table 1.1.

| Injection energy                | $450 { m GeV}$                           |

|---------------------------------|------------------------------------------|

| Collision energy                | $7000 { m ~GeV}$                         |

| Number of particles per bunch   | $1.15 \times 10^{11}$                    |

| Number of bunches per fill      | 2808                                     |

| Nominal luminosity              | $10^{34} \text{ cm}^{-2} \text{ s}^{-1}$ |

| Inelastic cross section         | 60  mb                                   |

| Total cross section             | 100  mb                                  |

| Revolution frequency            | $11.245 \mathrm{~kHz}$                   |

| Bunch frequency                 | $40.08 \mathrm{~MHz}$                    |

| Circumference length            | $26.66~\mathrm{km}$                      |

| Radius                          | $4.24 \mathrm{km}$                       |

| Number of dipole magnets        | 1232                                     |

| Number of quadrupole magnets    | 392                                      |

| Nominal magnetic field strength | 8.33 Tesla                               |

|                                 |                                          |

Table 1.1: LHC beam parameters.

Figure 1.3: Standard model of particle physics.

Four large experiments are installed around the ring of the LHC as shown in Figure 1.2. Two general-purpose experiments, ATLAS (A Toroidal LHC ApparatuS) [2] and CMS (Compact Muon Solenoid) [3], are optimized to study new physics at the TeV scale. The other two experiments are designed to study specific phenomena, LHCb (Large Hadron Collider Beauty) [4] and ALICE (A Large Ion Collider Experiment) [5]. LHCb investigates the CP violation in the bottom quark sector whereas ALICE studies quark-gluon plasma through Pb-Pb and Pb-p collisions.

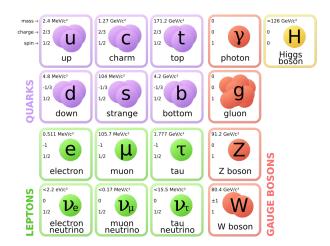

The most widely used fundamental particle physics theory, the Standard Model, leaves many unsolved questions (Figure 1.3). Among them, the reason why elementary particles have mass, and why are their masses different is one of the most important. The answer may lie within the Brout-Englert-Higgs (BEH) mechanism, which states that particles acquire mass by the interaction with a Higgs field.

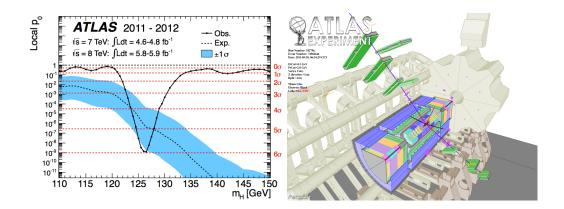

Particles which interact strongly with the Higgs field are heavy, whilst those which interact weakly are light. The Higgs field has at least one new particle associated with it, the Higgs boson. After three years of operation, in 2012 both ATLAS and CMS announced the discovery of a new particle with mass around 125 GeV consistent with the Higgs boson (Figure 1.4) [6]. The upcoming years of LHC operation will provide enough statistics to determine the new particle's properties.

Figure 1.4: Left: The observed (solid) local  $p_0$  as a function of Higgs mass in the low mass range. The dashed curve shows the expected local  $p_0$  under the hypothesis of a SM Higgs boson signal at that mass with its  $\pm 1 \sigma$  band. The horizontal dashed lines indicate the *p*values corresponding to significances of 1 to  $6 \sigma$ . Right: Event display of a  $2e2\mu$  candidate event with  $m_{4l}=124.3$  GeV. The masses of the lepton pairs are 76.8 GeV and 45.7 GeV.

### **1.3** The ATLAS Experiment

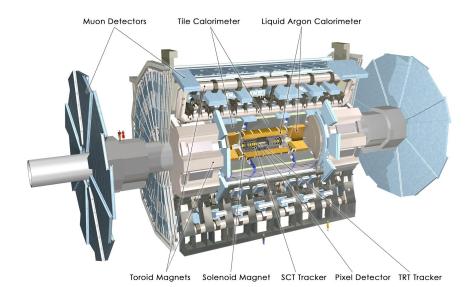

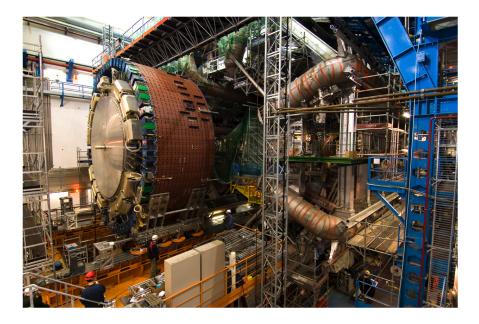

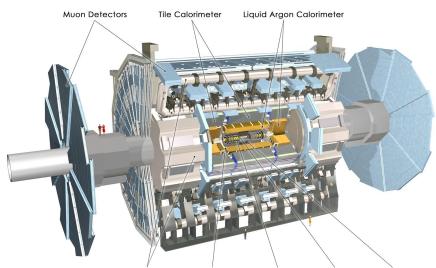

ATLAS is a general-purpose p-p detector designed to exploit the full discovery potential of the LHC [2]. ATLAS is about 45 meters long, more than 25 meters high and has an overall weight of approximately 7000 tones (Figure 1.5). The inner detector is located in the innermost part of ATLAS. It is built around the beam pipe and is designed especially for tracking and vertexing. It is formed by the Pixel detector, Semiconductor Tracker (SCT) and Transition Radiation Tracker (TRT). It measures the trajectories of the charged particles created in the collisions. The inner detector is embedded in a solenoidal magnet which generates a magnetic field of 2 Tesla. The curvature of the trajectories which results from the the magnetic field bending power, is used to calculate the momentum of the particles. Additionally, the TRT provides electron identification by measurement of the transition radiation photons generated in the radiator material. Electromagnetic and hadronic calorimeters surround the solenoid magnet and are designed to measure the absorbed energy and the direction of the different kinds of particles that cross them. The last layer of the detector is formed by the muon spectrometer and a toroidal magnet. The muon tracking system measures the trajectories of charged particles leaving the calorimeters. The trajectories are bent by the magnetic deflection

Figure 1.5: The ATLAS detector.

provided by three superconducting air-core toroid magnets, which generate an average field of 0.5 Tesla.

The detector is optimized for a long range of known and hypothetical processes. The observable cross-section for most of the interesting processes is small over a large fraction of the energy range, hence it is an important design requirement to operate at high luminosity and to maximize the detectable rates above the backgrounds by high resolution measurements. The basic design criteria of the detector include the following:

- Very good electromagnetic calorimetry for electron and photon separation and measurement, complemented by a full-coverage hadronic calorimetry for accurate jet and missing transverse energy  $(E_T^{miss})$  measurements.

- High-precision muon measurements, with the capability of guaranteing accurate measurements at the highest luminosity using the external muon spectrometer alone.

- Efficient tracking at high luminosity for high- $p_T$  lepton-momentum measurements, electron and photon identification,  $\tau$ -lepton and heavy-flavour identification, and full event reconstruction capability at low luminosity.

• Large acceptance in pseudo-rapidity  $(\eta)$  with almost full azimutal angle  $(\phi)$  coverage everywhere. The azimuthal angle is measured around the beam axis. The pseudorapidity is measured with respect to the plane perpendicular to the beam and derived from the polar angle  $(\theta)$ :

$$\eta = -ln(\tan\frac{\theta}{2}) \tag{1.1}$$

• Triggering and measurement of particles at low- $p_T$ , providing high efficiencies for most physics processes of interest at LHC.

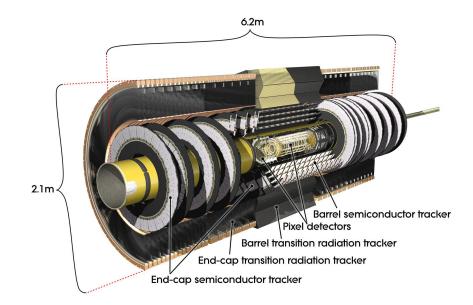

#### 1.3.1 The Inner Detector

The Inner Detector is designed to reconstruct tracks and decay vertices in any event with high efficiency [7]. Using additional information from the calorimeter and muon systems, the inner detector also contributes to electron, photon, and muon identification, and supplies extra signatures for short-lived particle decay vertices. Important physics considerations for the design of the inner detector are:

- Excellent momentum and impact parameter resolution for tracks with  $p_T > 0.5$  GeV up to very high momentum,

- tracking coverage over the range  $|\eta| < 2.5$ ,

- high efficiency with equally high noise rejection,

- identification of the charge of high- $p_T$  tracks,

- tagging of jets originating from b-quarks (b-jets),

- reconstruction of soft electrons and secondary vertices from b and  $\tau$  decays,

- identification of the primary vertex,

- electron identification capability,

- identification of a high- $p_T$  track to reduce the Level 1 electromagnetic cluster trigger rate from jet events.

Figure 1.6: The Inner detector.

The magnetic field configuration of the Inner Detector is based on an inner thin superconducting solenoid surrounding the inner detector cavity with a radius of 1.2 m and a length of 5.3 m. It provides an axial magnetic field of 2 Tesla in the centre of the tracking volume. The momentum and vertex resolution requirements from physics call for high-precision measurements to be made with fine granularity detectors, given the very large track density expected at the LHC. The layout of the Inner Detector is shown in Figure 1.6. The outer radius of the Inner Detector cavity is 115 cm. It consists of three units: a barrel section extending over 80 cm, and two identical end-caps covering the rest of the cylindrical part. In the barrel region, high-precision detector layers are arranged on concentric cylinders around the beam axis, while the end-cap detectors are mounted on disks perpendicular to the beam axis. The highest granularity around the vertex region is provided by semi-conductor pixel and strip detectors, the latter employed in the Semiconductor Tracker (SCT). The basic principle of the semiconductor detectors is that the passage of ionizing radiation creates electron-hole pairs in the semiconductor which are collected by an electrical field. The difference between strips and pixels is mainly geometry, pixels being closely spaced pads capable of good two dimensional reconstruction while strips give a better spacial resolution in one coordinate than the other. The pixel layers are segmented in  $R\phi$  and z, while SCT detector uses small angle (40 mrad) stereo strips to measure both coordinates, with one set of strips in each layer measuring  $\phi$ . The pixel detector is much more radiation tolerant than the silicon strip tracker. The number of layers of the semiconductor detectors must be limited due to the material they introduce and their high cost. A larger number of tracking points is provided by the straw tube tracker also called Transition Radiation Tracker (TRT), which provides continuous tracking with much less material per point and a lower cost. The barrel TRT tubes are parallel to the beam direction. The continuous tracking consists of radial straws arranged into wheels.

#### 1.3.2 Calorimeters

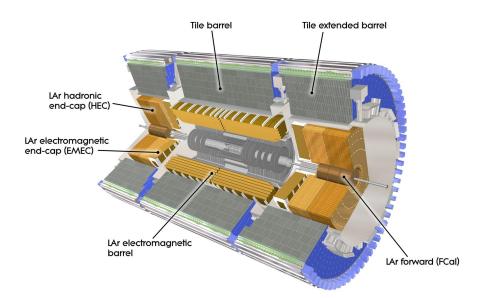

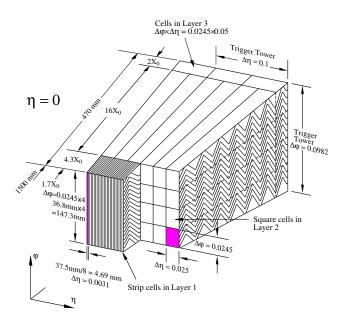

At the LHC about twenty soft collisions per bunch crossing will be produced when operating at design luminosity. Therefore fast detector response and fine granularity are required to minimize the impact of the pileup on the physics performance. The calorimetry part of the ATLAS detector consists of an electromagnetic (EM) calorimeter covering the pseudorapidity region  $|\eta| < 3.2$ , a barrel hadronic calorimeter covering  $|\eta| < 1.7$ , hadronic endcap calorimeters covering  $1.4 < |\eta| < 3.2$ , and forward calorimeters covering  $3.2 < |\eta| < 4.8$ . The EM calorimeter is a lead/Liquid-Argon (LAr) detector with accordion geometry. The hadronic barrel calorimeter is based on a sampling technique with plastic scintillator plates (tiles) embedded in an steel absorber therefore the name TileCal. At larger rapidities, where higher radiation resistance is needed, the radiation-hard LAr technology is used for all the calorimeters: the Hadronic Endcap Calorimeter (HEC) and the Forward Calorimeter (FCal). A scheme with all the calorimeters for ATLAS can be seen in Figure 1.7.

#### **Electromagnetic Calorimetry**

In the barrel, the electromagnetic calorimeter consists of two identical half-barrels covering the rapidity range  $|\eta| < 1.4$ . For each half-barrel (divided into 16 modules) the calorimeter is made of 1024 accordion-shaped absorbers alternating with 1024 readout electrodes, arranged with a complete  $\phi$  symmetry around the beam axis. Between each pair of absorbers, there are two liquid argon gaps, separated by a readout electrode.

Figure 1.7: ATLAS calorimeters system.

Figure 1.8: Diagram of a LAr EM calorimeter barrel module. It is shown the longitudinal segmentation, the cell size and the accordion structure.

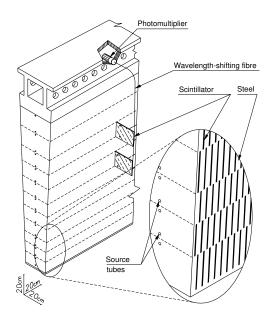

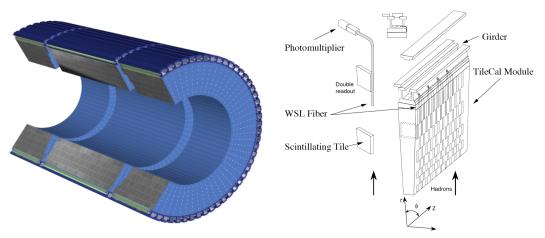

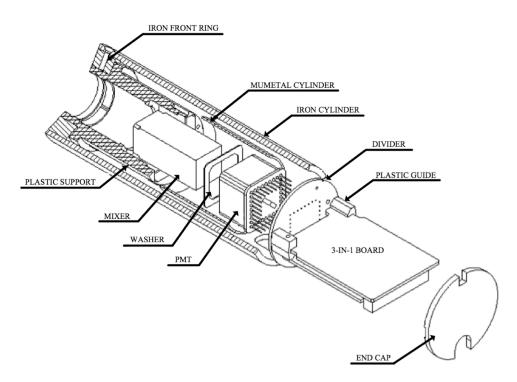

Figure 1.9: TileCal module components and structure.

The ElectroMagnetic EndCap (EMEC), the HEC and the FCal calorimeters are placed inside the endcap cryostat. The EMEC, which covers the range  $1.375 < |\eta| < 3.2$ , uses the same technique as in the barrel part. The HEC covers the range  $1.5 < |\eta| < 3.2$  and uses copper plates as absorbers, with parallel geometry in this case. The FCAL placed in the  $3.2 < |\eta| < 4.9$  region, provides EM coverage as well as hadronic showers by using copper and tungsten as absorbers, respectively. The EM calorimeter is segmented in three longitudinal samplings in the  $|\eta| < 2.5$ region and in two samples in the  $|\eta| > 2.5$  region, as Figure 1.8 shows. The total thickness of the EM calorimeter is above 24 radiation lengths for the barrel and above 26 for the endcaps.

#### Hadronic Calorimetry

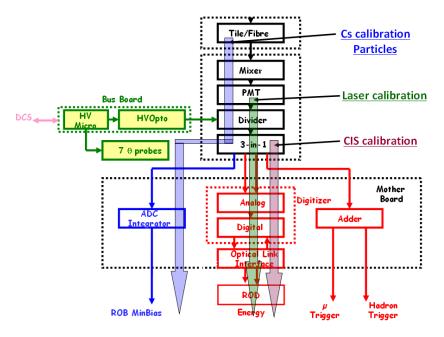

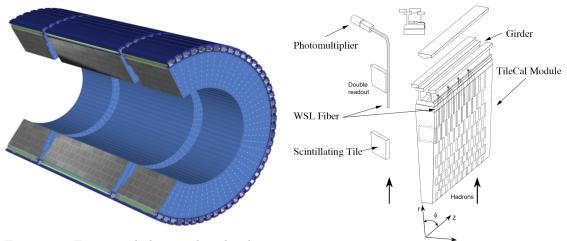

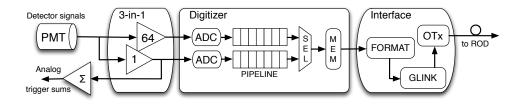

Hadronic calorimetry at the LHC is mainly designed to identify the energy and direction of jets and to measure the  $E_T^{miss}$  [8]. Fragmentation, gluon radiation and the presence of magnetic fields are intrinsic effects that limit the resolution of these measurements. However, at the LHC designed luminosity, the pile-up energy from minimum-bias events also becomes important. In order to be sensitive to interesting physics, an energy resolution of  $50\%/\sqrt{E} \oplus 3\%$  and segmentation of  $\Delta \eta \ge \Delta \phi = 0.1 \ge 0.1$  is required for the central region. For the forward region, a resolution of  $100\%/\sqrt{E} \oplus 10\%$  and segmentation of  $\Delta \eta \ge \Delta \phi = 0.2 \ge 0.2$  is sufficient. The ATLAS hadronic calorimetry covers a pseudo-rapidity range  $|\eta| < 5$ . Different techniques are used depending on  $\eta$ . The Tile calorimeter covers  $|\eta| < 1.7$ . It is composed by a barrel and two extended barrels made out of plastic scintillating tiles as active medium. For  $1.5 < |\eta| < 4.9$  liquid-argon techniques are used for the two end-caps  $(1.5 < |\eta| < 3.2)$  and the two high density forward calorimeters  $(3.2 < |\eta| < 4.9)$ . Both the HEC and FCal are embedded into the same cryostat as the electromagnetic end-cap calorimeters. In the TileCal the light produced in the scintillating tiles is collected through wavelength shifting fibers and guided to a photomultiplier (see Figure 1.9). Readout cells are defined by grouping together several fibers to the same photomultiplier, achieving three longitudinal samplings with a segmentation of  $\Delta \eta \propto \Delta \phi = 0.1 \propto 0.1$  for the two inner layers and  $(0.2 \propto 0.1)$  for the outer layer. The analogue electrical signal of the photomultiplier is digitized in samples of 10 bits taken each 25 ns. These data are sent to the ReadOut Driver (ROD) system where online reconstruction algorithms are applied. The TileCal and the ROD system are described in detail in Chapter 2.

The hadronic end-caps are made up of two equal diameter wheels. The first wheel is built out of 25 mm copper plates as absorber and the second wheel uses 50 mm copper plates. Compared to lead, copper has a shorter interaction length that allows to increase the size of liquid-argon gaps between plates, thereby reducing the electronic noise, the integration time and pile-up noise. In both wheels the absorber plates are separated by 8.5 mm gaps filled with liquid-argon and a structure of three electrodes that divide the gap into four drift spaces of  $\sim 1.8$  mm.

The forward calorimetry should be efficient at forward jet tagging and  $E_T^{miss}$  reconstruction. The forward calorimeters are high density detectors in order to accommodate at least 9 interaction lengths of active material in rather short longitudinal space. Each forward calorimeter is divided into three longitudinal sections. In the first section the absorber is copper while in the second and third sections is tungsten. The calorimeter consists of a metal matrix (the absorber) filled with rods (electrodes). Liquid-argon is the active medium and fills the gaps between the matrix and the rods.

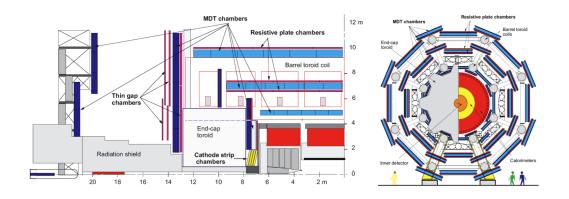

Figure 1.10: The ATLAS muon spectrometer in the rz (left) and xy view (right).

#### 1.3.3 The Muon Spectrometer

The ATLAS muon spectrometer has been designed to make efficient use of the magnet bending power with a coverage of  $|\eta| < 3$ . It provides projective towers in  $\eta$  and  $\phi$  and is made out of practical chamber dimensions for production, transport and installation [9]. Figure 1.10 shows the position of the muon chambers. The spectrometer is divided into three regions, barrel region ( $|\eta| < 1.05$ ), transition region ( $1.05 < |\eta| < 1.4$ ) and endcap region ( $|\eta| > 1.4$ ). Four different technologies have been used depending on spatial and timing resolution, resistance to radiation and engineering considerations: Monitored Drift Tube chambers (MDT), Cathode Strip Chambers (CSC), Resistive Plate Chambers (RPC) and Thin Gap Chambers (TGC).

The MDT chambers are composed of multilayers of high-pressure drift tubes. Each multilayer is mounted on each side of the support structure. The drift tubes are made of aluminum, 30 mm of diameter, with a central wire of W-Re. They work at 3 bar absolute pressure with a non-flammable mixture of Ar-CO2.

The CSCs are multiwire proportional chambers operated with a mixture of  $Ar - CO_2 - CF_4$ . The distance between anode wires (2.5 mm) equals the distance to the cathode. The cathode readout is segmented into strips (5.08 mm) orthogonal to the anode wires. The precision coordinate is obtained by measuring the induced avalanche in the segmented cathode, achieving space resolutions better than 60  $\mu$ m. The RPC is a gaseous parallel-plate detector with a typical space-time resolution of 1 cm x 1 ns with digital readout. It is composed by two

parallel resistive plates made out of bakelite. The plates are separated by spacers that define the size of the gas gaps. The gas is a mixture of  $C_2H_2F_4$ . A uniform electric field of a few kV/mm produces the avalanche multiplication of ionization electrons. The signal is read out via capacitative coupling to metal strips placed at both sides of the detector and grounded.

The TGC is built with 50  $\mu$ m wires separated by 2 mm. The wires are placed between two graphite cathodes at a distance of 1.6 mm. Behind the graphite cathodes, strips or pads are located to perform a capacitive readout in any desired geometry. Some advantages of these chambers are a fast signal, typical rise time 10 ns and low sensitivity to mechanical deformations.

In the barrel region the chambers are situated in three concentric cylinders (so called stations) around the beam axis at a radial distance of 4.5 m, 7 m and 10 m. MDT chambers are used for high precision measurements and RPC for triggering. The low- $p_T$  muon trigger uses two double-layer RPCs located on each side of the middle station, while the high- $p_T$  trigger uses one triple layer chamber located at the outer barrel muon station. In the transition and end-cap region most of the chambers are installed perpendicular to the beam axis (see Figure 1.10). In the transition region  $(1.05 < |\eta| < 1.4)$  the muon track is measured with three vertical stations, placed inside or near the barrel magnet. In the end-cap region  $(|\eta| > 1.4)$ , the stations are located before and after the end-cap toroid magnets and a third one near the cavern wall. The trigger is provided by the TGC chambers while precision measurements are provided by the MDT chambers at small  $\eta$  and the CSC chambers at large rapidity.

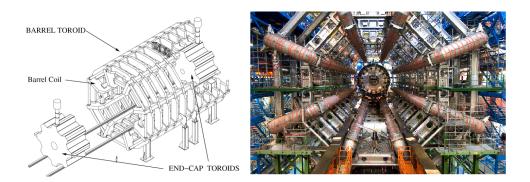

#### 1.3.4 Magnetic Field

The ATLAS magnetic field is optimized to increase the identification power of the subdetectors in a light and open structure which minimizes scattering effects [10]. It consists of a central solenoid servicing the inner detector with an axial magnetic field, surrounded by eight large scale air-core coils generating a toroidal magnetic field for the muon spectrometer (Figure 1.11). The Nb-Ti superconductor in a copper matrix technology is used in this case. The magnet system weights 1300 tons and is cooled by liquid He at 4.5 K.

Figure 1.11: Sketch of the ATLAS superconducting air-core toroid magnet system (left) and picture of the barrel toroid (right).

## 1.4 The ATLAS Trigger and Data Acquisition System

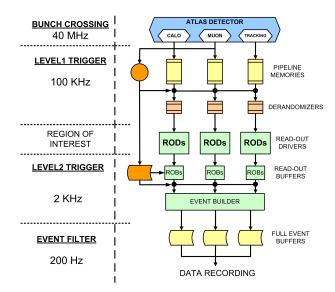

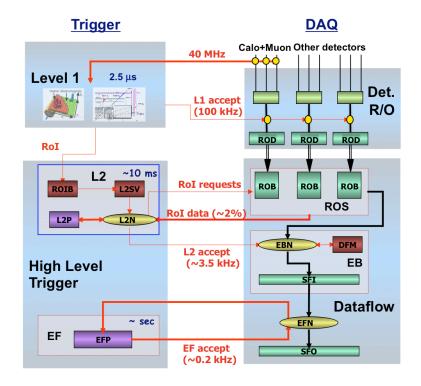

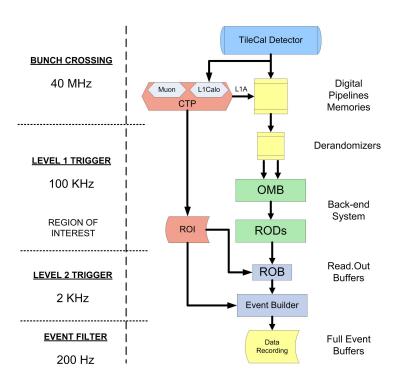

The ATLAS trigger system consists of three levels of event selection: Level 1, Level 2, and Event Filter (EF) [11]. The Level 1 trigger is implemented using custom-made electronics, while the Level 2 and EF is almost entirely based on commercially available computers and networking hardware. The Level 2 and EF together form the High-Level Trigger (HLT). A block diagram of the trigger and data acquisition systems is shown in Figure 1.12. The Level 1 trigger searches for signatures from high- $p_T$  muons, electrons/photons, jets, and  $\tau$ -leptons decaying into hadrons. It also selects events with large  $E_T^{miss}$  and large total transverse energy. The Level 1 trigger uses reduced-granularity information from the RPCs and TGCs for high $p_T$  muons, and the calorimeter for the rest of signatures. The maximum Level 1 acceptance rate that the detector readout systems can handle is 75 kHz (upgradeable to 100 kHz), and the Level 1 decision must reach the front-end electronics within 2.5  $\mu$ s after the bunch crossing with which it is associated. The Level 2 trigger is seeded by Regions-of-Interest (RoIs). These are regions of the detector where the Level 1 trigger has identified possible trigger objects within the event. The Level 2 trigger uses the RoIs information on coordinates, energy, and type of signature to limit the amount of data which must be transferred out from the detector readout. The Level 2 trigger reduces the event rate to below 3.5 kHz, with an average event processing time of approximately 40 ms. The EF uses offline analysis procedures on fully-built events to further reduce the event selection to a rate of up to 800 Hz,

with an average event processing time of the order of four seconds. HLT algorithms use full granularity and precision of the calorimeter and muon chamber data, as well as the data from the inner detector, to refine the trigger selections. Better energy resolution improves the threshold cuts, while track reconstruction in the Inner Detector significantly enhances the particle identification (for example distinguishing between electrons and photons). The event selection at both Level 1 and Level 2 primarily uses inclusive criteria, for example high- $E_T$ objects above defined thresholds. One exception is the Level 2 selection of events containing the decay of a B-hadron, which requires the reconstruction of exclusive decays into particles with low momentum.

The Data AcQuisition system (DAQ) receives and buffers the event data from the detector specific readout electronics at the Level 1 trigger rate through point-to-point ReadOut Links (ROLs). It transmits to the Level 2 farm any data requested by the trigger and, for those events fulfilling the Level 2 selection criteria, event-building is performed. The assembled events are input to the EF, and the events selected there are moved to permanent event storage. In addition to controlling movement of data down the trigger selection chain, the DAQ system also provides infrastructure for the configuration, control and monitoring of the ATLAS detector during data-taking. Supervision of the detector hardware (gas systems, power-supply voltages, etc.) is provided by the Detector Control System (DCS) [12].

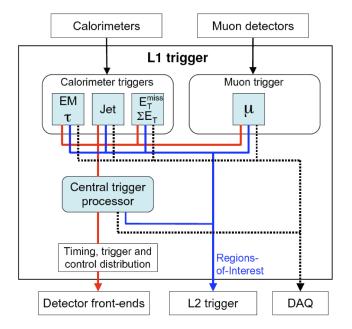

### 1.4.1 The First Level of Trigger

The first level of trigger (Level 1) performs the initial event selection based on information from the calorimeters and muon detectors as shown in Figure 1.13. The calorimeter selection is based on reduced granularity and precision information from all the calorimeters gathered by the Level 1 Calorimeter (L1Calo). The triggers select objects with high  $p_T$  and large  $E_T^{miss}$ and scalar  $\sum E_T$ . The trigger signatures can require isolation where the energetic particle must have a minimum angular separation from any significant energy deposit in the same trigger. The information for each bunch crossing used in the Level 1 trigger decision is the multiplicity of hits for 4 to 16 programmable  $E_T$  thresholds per object type.

The Level 1 muon trigger is based on signals in the muon trigger chambers: RPCs in the barrel and TGCs in the end-caps. The trigger searches for patterns of hits consistent with

Figure 1.12: ATLAS data acquisition system and trigger levels.

high- $p_T$  muons originating from the interaction region. The logic provides six independentlyprogrammable  $p_T$  thresholds. The information for each bunch crossing used in the Level 1 trigger decision is the multiplicity of muons for each of the  $p_T$  thresholds. Muons are not double-counted across the different thresholds.

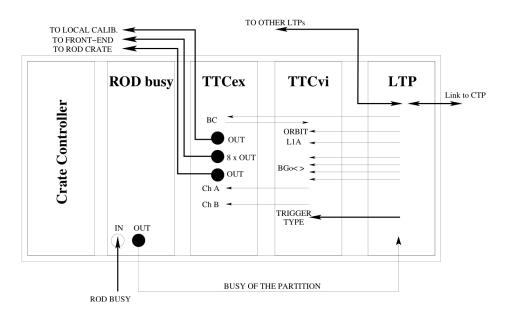

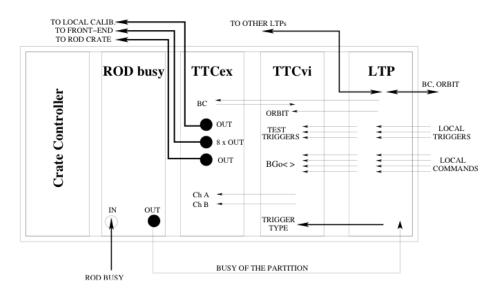

The overall Level 1 accept decision is made by the Central Trigger Processor (CTP), which combines the information for different object types. Trigger menus can be programmed with up to 256 distinct items, each item being a combination of requirements on the input data. The trigger decision, together with the LHC clock and other signals, are distributed to the detector front-end and readout systems via the Timing, Trigger and Control (TTC) system, using an optical-broadcast network [13].

While the Level 1 trigger decision is based only on the multiplicity of trigger objects or flags indicating which thresholds were passed, for global quantities, information about the geometric location of trigger objects is retained in the muon and calorimeter trigger processors. Upon the event being accepted by the Level 1 trigger, this information is sent as RoIs to the Level 2 trigger, where it is used as a seed for the selection performed by the HLT. An essential function of the Level 1 trigger is unambiguous identification of the bunch crossing of interest.

Figure 1.13: Block diagram of the Level 1 trigger.

The very short (25 ns) bunch crossing interval makes this a challenging task. In the case of the muon trigger, the physical size of the muon spectrometer implies times-of-flight exceeding the bunch crossing interval. For the calorimeter trigger, a serious complication is that the width of the calorimeter signals extends over many bunch crossings. While the trigger decision is being taken, the data from all detector channels has to be retained in pipeline memories. These memories are contained in custom electronics placed on or near the detector, where often radiation levels are high and access is difficult. In the interest of cost and reliability, it is desirable to keep the pipeline length as short as possible. The Level 1 latency, which is the time from the proton-proton collision until the Level 1 trigger decision, must therefore be kept as short as possible. The design of the trigger and front-end systems requires the Level 1 latency to be less than 2.5  $\mu$ s, with a target latency of 2.0  $\mu$ s, leaving 0.5  $\mu$ s contingency. About 1  $\mu$ s of this time is accounted for by cable-propagation delays alone. To achieve this aim, the Level 1 trigger is implemented as a system of purpose-built hardware processors.

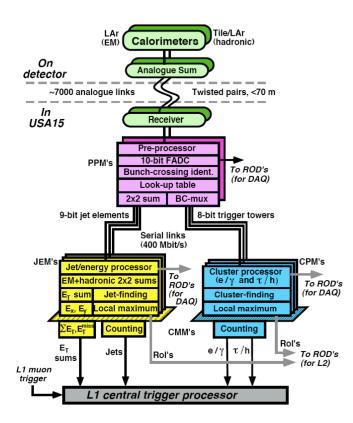

Figure 1.14: Architecture of the Level 1 calorimeter trigger. Analogue data from the calorimeters are digitized and associated with the correct bunch crossing in the pre-processor and then sent to two algorithmic processors, the Jet/Energy-Sum (JEM) processor and the Cluster Processor (CPM). The resulting hit counts and energy sums are sent to the Central Trigger Processor.

#### Calorimeter Trigger

The L1Calo is a pipelined digital system designed to work with about 7000 analogue trigger towers of reduced granularity (0.1 x 0.1 in  $\Delta \eta \propto \Delta \phi$  in most parts, but larger at higher  $|\eta|$ ) from the electromagnetic and hadronic calorimeters. It sends the results for each LHC bunch crossing to the CTP approximately 1.5  $\mu$ s after the event occurs, resulting in a total latency for the L1Calo chain of about 2.1  $\mu$ s, well within the allowed envelope. The complete diagram of the L1Calo is presented in Figure 1.14.

The L1Calo system is located off-detector in the service cavern USA15. Its architecture,

shown in Figure 1.14, consists of three main sub-systems. A pre-processor digitizes the analogue input signals, then uses a digital filter to associate them with a specific Bunch Crossings that uses a Look-Up Table to produce the transverse-energy values used for the trigger algorithms. Finally the Cluster Processor (CP) and Jet/Energy-sum Processor (JEP) subsystems receive the data in parallel. The CP sub-system identifies electron/photon and  $\tau$ -lepton candidates with  $E_T$  above the corresponding programmable threshold and satisfying, if required, certain isolation criteria. The JEP receives jet trigger elements, which are  $0.2 \ge 0.2$  sums in  $\Delta\eta \ge \Delta\phi$ , and uses these to identify jets and to produce global sums of scalar and missing transverse energy. Both processors count the multiplicities of the different types of trigger objects. The CP and JEP send these multiplicities, as well as the transverse-energy threshold information, to the CTP for every bunch crossing. When there is a Level 1 accept (L1A) decision from the CTP, the stored data from the L1Calo are read out by the DAQ: this includes input data, intermediate calculations and trigger results in order to allow full monitoring and verification of the Level 1 trigger functionality. These data can also provide useful diagnostics for the LHC machine and the ATLAS sub-detectors. The types and positions of jet,  $\tau$ -lepton and electromagnetic cluster candidates are also collected and sent to the RoI builder for use by the Level 2 trigger. The L1Calo architecture is relatively compact, with a minimal number of crates and cable links. This helps in reducing the latency. Some of the hardware modules were designed to fulfill several different roles in the system, in order to reduce hardware costs and design efforts, as well as to reduce the number of spares required.

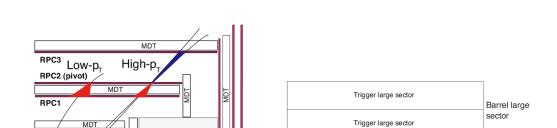

#### Muon Trigger

The Level 1 muon trigger is based on finely segmented detectors (the RPCs in the barrel and the TGCs in the end-caps) with a sufficient timing accuracy to provide unambiguous identification of the bunch crossing containing the muon candidate. The trigger in both the barrel and the end-cap regions is based on three trigger stations each (Figure 1.15). The basic principle of the algorithm is to require a coincidence of hits in the different trigger stations within the path of a muon from the interaction point through the detector. The width of the path is related to the  $p_T$  threshold to be applied. A system of programmable coincidence logic boards allow concurrent operation with a total of six thresholds, three associated with

Δη=0.2

Pad

$\Delta \eta = 0.1$

Rol

$\eta = 0$

Trigger small sector

Trigger small secto

Δη=0.

Δη=0.1

φ-cm

∆ø=0.2

η-СМ Δφ=0.1

Barrel small sector

Figure 1.15: Right: Schema of the Level 1 muon barrel trigger. Left: Segmentation of the Level 1 muon barrel trigger. The RPCs are arranged in three stations: RPC1, RPC2, and RPC3. The low- $p_T$  and high- $p_T$  roads are also shown.

15 m

the low- $p_T$  trigger (threshold range approximately 6-10 GeV) and three associated with the high- $p_T$  trigger (threshold range approximately 8-35 GeV).

#### 1.4.2 Data Acquisition System and High-Level Trigger

5

10

The main components of the Data AcQuisition system and High-Level Trigger (DAQ/HLT) are: readout, Level 2 trigger, Event-Building, Event Filter, configuration, control and monitoring (Figure 1.16) [14]. The movement of events from the detector to mass storage commences with the selection of events by the Level 1 trigger. During the latency of the Level 1 trigger selection, up to 2.5  $\mu$ s, the event data are buffered in memories located within the detector-specific front-end electronics. On selection by the Level 1 trigger the event data is transferred to the DAQ/HLT system over dedicated ReadOut Links (ROLs), having first transited through the detector-specific RODs. The event fragments are received into their respective ReadOut Buffers (ROBs) contained in the ROS units where they are temporarily stored and provided, on request, to the subsequent stages of the DAQ/HLT system. For every selected event, the Level 1 trigger sub-systems (calorimeter, muon, and CTP) also provide the RoI information on eight ROLs, a dedicated data path to the RoI builder where it is assembled into a single data structure and forwarded to one of the Level 2 trigger. It receives the RoIs

Figure 1.16: Schema of the ATLAS Trigger and Data Acquisition system. The Level 1 trigger system receives the data directly from the front-end electronics of the muon and calorimeter sub-systems. The data reconstructed by the RODs is transferred to the HLT trigger system for all the sub-systems.

and assigns each event to one of the Level 2 Trigger Processing Units (L2PUs) for analysis.

The L2PU, based on the RoI information, requests for event data are made to the appropriate ROS. The sequence of data requests is determined by the type of RoI identified by the Level 1 trigger and the configuration of the Level 2 trigger processing. The result, accept or reject, of the analysis is returned to the L2SV which subsequently forwards it to the Data-Flow Manager (DFM). In addition it also sends a summary of the analysis performed to a Level 2 trigger specific ROS.

The DFM marshals the events during the event-building. For those events which were found not to fulfill any of the Level 2 selection criteria, the DFM informs all the ROSs to expunge the associated event data from their respective ROBs. Each event which has been

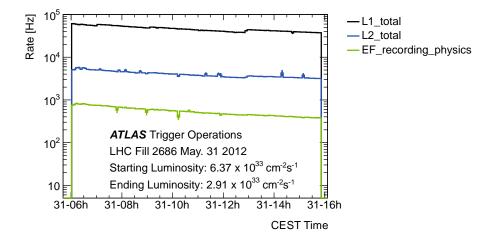

selected by the Level 2 trigger is assigned by the DFM to a Sub-Farm Input (SFI) in an eventbuilding node. The SFI collects the event data from the ROSs and builds a single event-data structure, the event. An SFI can build more than one event at a time and the requests to the ROSs for their data are dispatched according to an algorithm which ensures the quantity of data being received by the SFI does not exceed its available input bandwidth. The full event structure is sent to the Event Filter for further analysis. On completing the building of an event an SFI notifies the DFM, which subsequently informs all the ROSs to expunge the associated event data from their respective ROBes. The event filter, in addition to the selection, classifies the selected events according to a predetermined set of event streams and the result of this classification is added to the event structure. Selected events are subsequently sent to a Sub-Farm Output (SFO) in the output nodes of the DAQ/HLT system. Conversely, those events not fulfilling any of the event filter selection criteria are expunded from the system. The events received by an SFO are stored in its local file system according to the classification performed by the event filter. The event files are subsequently transferred to CERN's central data-recording facility. Figure 1.17 show the trigger rates as a function of time for a typical 2012 run for Level 1, Level 2 and Event Filter selections. The rates follow the evolution of the peak luminosity of the LHC fill.

#### **ReadOut System**

The ROS receives event data from the detector RODs via 1574 ROLs. All the ROLs have the same design and implementation, based on the S-link interface that allows the transmission of 32-bit data at 40.08 MHz. Thus, corresponds to 160 Mbyte/s with flow control and error detection. ROBs are located at the receiving end of the ROLs, there being one ROL associated to one ROB. Three ROBs are physically implemented on a ROB Input card (ROBin). The ROS, which is implemented on a server-class PC can hold up to 6 ROBin cards. The ROS provides multiplexing of up to 18 ROLs to the subsequent components of the DAQ/HLT. A request by an L2PU for data involves, on average, one or two ROBs per ROS, whereas the requests for data from the event building nodes concern the event data from all the ROBs of a ROS. In either case, the ROS replies to the requester with a single data structure. At the Level 1 trigger rate of 75 kHz, and an average of 1 kbyte received per ROL, the ROS is able

Figure 1.17: Data trigger output rate and recording rates (Hz) as a function of time for the LHC fill 2686 in 2012.

to concurrently service up to approximately 20 kHz of data requests from the Level 2 trigger, up to 3.5 kHz of requests from event building nodes, and expunge events on request from the DFM. The rate of data requests received by a specific ROS depends on the  $\Delta \eta - \Delta \phi$  region of the data it receives over the ROLs and from which detector it receives data. For example, a ROS which receives data from the EM Barrel region is solicited for data more frequently than a ROS associated with the barrel MDTs.

#### Level 2 Trigger

The Level 2 trigger is achieved by the combined functionality of the RoI builder, L2SV, L2PU and Level 2 trigger-specific ROS. The RoI builder receives the RoI information from the different sources at the Level 1 trigger rate on eight input ROLs and merges them into a single data structure. The single data structure containing the RoI data is transmitted by the RoI builder over one of the output ROLs to the L2SVs. L2SVs marshal the events through the Level 2 trigger. The principal component of the Level 2 trigger is the Level 2 processing farm, where the event selection is executed. The system is designed to provide an event rejection factor of about 30, with an average throughput per farm node of about 200 Hz, using the data

located in the RoIs, i.e. 12% of the full data of an event. The number of L2PU applications performing the physics selection per node is configurable. On the hardware currently deployed there are eight L2PUs per node, and one L2PU per processing core of the node. At the end of its event analysis, the L2PU sends to the trigger specific ROS information which summarizes the results of its analysis. Subsequently, this ROS participates in event building like any other ROS within the system, its event data being the Level 2 triggers summary analysis. In this way, the results of the Level 2 triggers analysis are built into the final event and subsequently used by the event filter to seed its selection. The failure of one or more L2PUs during run time does not incur system down time. The system continues to operate at a reduced rate while the failed application, the L2PU, can be restarted under the supervision of the run control.

#### **Event-Building**

The event-building functionality is provided by the DFM, ROSs and SFIs. The SFI is the application which collects the event data from the ROSs and assembles the event as a single formatted data structure. An SFI is configured with a randomized list of the ROSs within the system, which is used to define the order in which data requests are sent to the ROSs. This results in the randomization of the traffic pattern in the underlying network and hence improved network performance. To meet the rate requirements a number of SFIs work in parallel, each instance building a number of events concurrently. Each SFI informs the DFM of its readiness to receive events, and the DFM allocates events to the SFIs so as to ensure that the load is balanced across all available SFIs.

#### **Event Filter**

The Event Filter is a processing farm; on each processing node a configurable number of independent processing tasks receive and process events. Unlike the Level 2 trigger, these tasks are based on standard ATLAS event reconstruction and analysis applications. The steering of the event selection is the same as Level 2. For those events passing the selection criteria, a subset of the data generated during the event analysis is appended to the event data structure, enabling subsequent offline analysis to be seeded by the results from the event filter. An integral part of the selection process is the classification of the events according

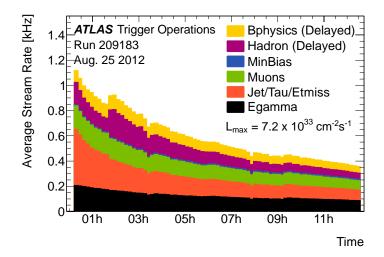

Figure 1.18: Event Filter stream recording rates (kHz) from ATLAS run 209183 (2012) with a peak luminosity of  $7.2 \times 10^{33}$  cm<sup>-2</sup>s<sup>-1</sup>. Filtered for LHC stable beams and ATLAS ready. The x-axis has an arbitrary offset.

to the ATLAS physics streams. Figure 1.18 shows the recording rates as a function of time for each stream for a typical 2012 run. The rates diminish with the decreasing instantaneous luminosity.

#### **Event Output**

The main functionality of the event-filter SFOs is to receive events which have passed the event filter selection criteria, interface the DAQ/HLT to CERN's central data-recording facility, and de-couple the data-taking process from possible variations in the central data-recording service. The SFO maintains, locally, a set of files into which it records events at a peak event rate of up to 400 Hz and stores them up to 24 hours. Under normal operating conditions, this storage capacity is only partially used. The set of files maps to the ATLAS-defined data streams: electrons, muons, jets, photons,  $E_T^{miss}$  and  $\tau$ -leptons, and B-physics. Each event is recorded in one or more files according to the stream classification made by the Event Filter processing task.

In addition to the data streams mentioned above, a subset of the events is also written to

calibration streams and to the express stream. The express stream is a subset of the events selected by the event filter that represent approximately the 10% of the data randomized that is useful for fast monitoring purposes. The calibration streams provide the minimum amount of information needed for detector calibration seeded by dedicated Level 1 triggers.

## Chapter 2

# The ATLAS Tile Hadronic Calorimeter

## 2.1 Detector Overview

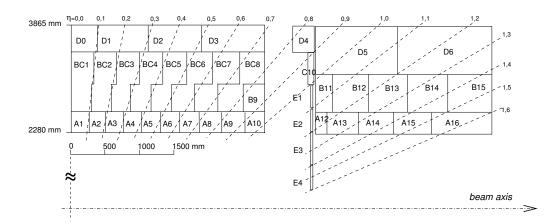

The TileCal detector is a sampling calorimeter using steel as the absorber and scintillator tiles as the active medium. It covers the region,  $|\eta| < 1.7$ , behind the liquid argon electromagnetic calorimeter and is subdivided into a central long barrel, 5.8 m in length, and two extended barrels, 2.6 m in length each with an inner radius of 2.28 m and an outer radius of 4.25 m, as shown in Figure 2.1. The radial depth of the Tile calorimeter is approximately 7.4  $\lambda$ (interaction lengths). Each barrel is azimutally divided into 64 modules or wedges of size  $\Delta \phi \sim 0.1$  with a weight of 3000 tonnes [15]. The assembled module forms an almost-periodic steel-scintillator structure with a ratio by volume of approximately 4.7:1. The geometry is sketched in Figure 2.2. The orientation of the scintillator tiles are radially disposed and normal to the beam line. This, in combination with wavelength-shifting (WLS) fibers readout coupled to the tile edges, allows almost seamless azimuthal calorimeter coverage. The grouping of the readout fibers into bundles define the calorimetric cells which are read out by PhotoMultiplier Tubes (PMTs) and also provides an approximate projective geometry in pseudo-rapidity. The gap region between the barrel and the extended barrel is instrumented with special cells, made

Figure 2.1: Three barrels of TileCal.

Figure 2.2: Schematic of a TileCal module and main components.

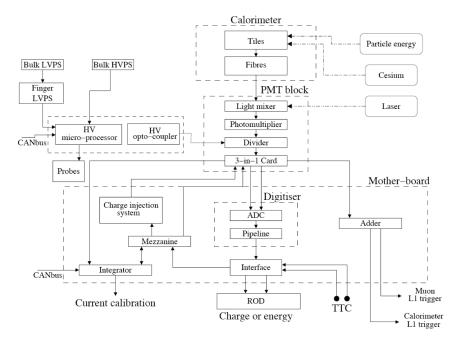

of steel-scintillator sandwiches with the same sampling fraction as the rest of the calorimeter and with thin scintillator counters in the sectors where the available space in the gaps is even more limited. The electronics and readout of the tile calorimeter are highly integrated with the mechanical structure. The photomultiplier tubes and all the front-end electronics are mounted on aluminium units, called superdrawers, which are inserted inside the supporting girder at the rear of each module. The front-end electronics also provide analogue sums from subsets of channels, forming trigger towers, for the Level 1 trigger. The low-voltage power supplies which power the front-end electronics are mounted in an external steel box, which has the cross-section of the girder and which also contains the external connections for power and other services. Finally, the calorimeter is equipped with three calibration systems: charge injection, laser and a  $^{137}Cs$  radioactive source that are used to calibrate the signals to the electromagnetic scale with very good precision.

## 2.2 Mechanical Structure

The mechanical structure of TileCal is designed as a self-supporting, segmented structure comprising 64 modules, each subtending 5.625 degrees in azimuth, for each of the three barrels.

The module sub-assembly is shown in Figure 2.2. Each module contains a precision-machined strong-back steel girder, the edges of which are used to establish a module-to-module gap of 1.5 mm at the inner radius. To maximize the use of radial space, the girder provides both the volume in which the readout electronics are contained and the flux return for the solenoid field. The readout fibers, suitably bundled, penetrate the edges of the girders through machined holes, into which plastic rings have been precisely mounted. These rings are matched to the position of photomultipliers. The fundamental element of the absorber structure consists of a 5 mm thick master plate, onto which 4 mm thick spacer plates are glued in a staggered fashion to form the pockets in which the scintillating tiles are located. The master plate was fabricated by high-precision die stamping to obtain the dimensional tolerances required to meet the specification for the module-to-module gap. At the module edges, the spacer plates are aligned into recessed slots, in which the readout fibers run. Holes in the master and spacer plates allow the insertion of stainless-steel tubes for the radioactive source calibration system. Each module is constructed by gluing the structures described above into sub-modules on a custom stacking fixture. These are then bolted onto the girder to form modules, with care being taken to ensure that the azimuthal alignment meets the specifications. The calorimeter is assembled by mounting and bolting modules to each other in sequence. Shims are inserted at the inner and outer radius load-bearing surfaces to control the overall geometry and yield a nominal module-to-module azimuthal gap of 1.5 mm and a radial envelope which is generally within 5 mm of the nominal one. The TileCal Valencia-IFIC group built 50% of the TileCal modules for one of the extended barrels of the detector.

#### 2.2.1 Optical Components

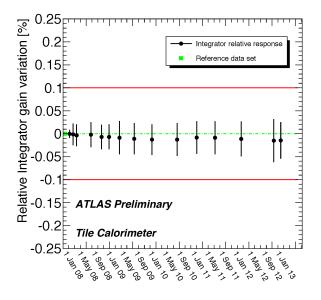

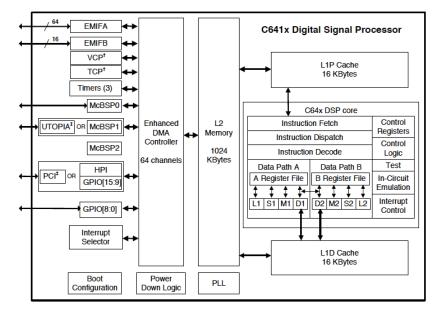

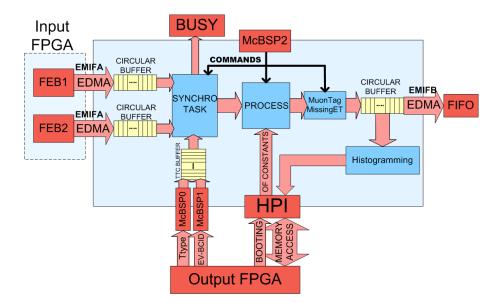

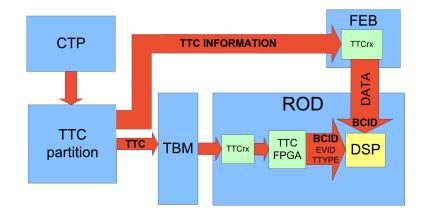

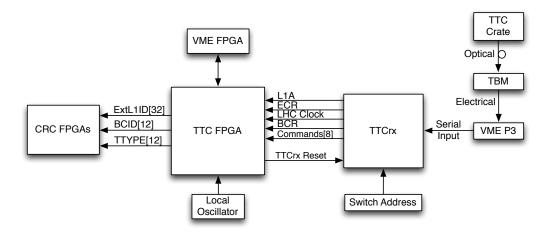

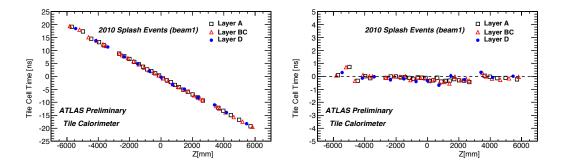

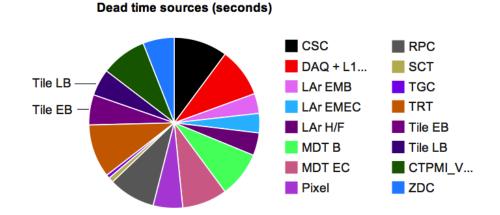

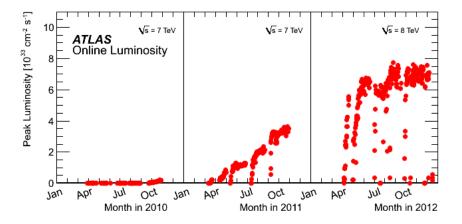

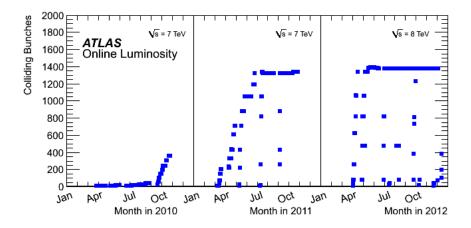

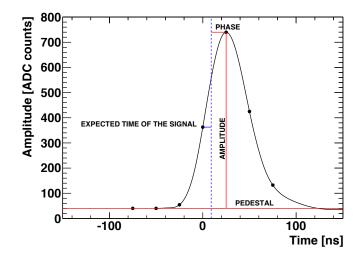

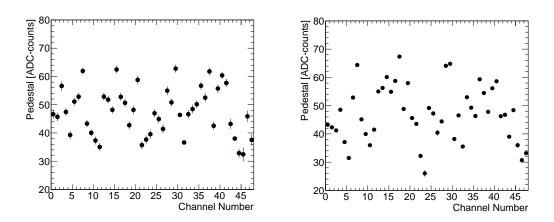

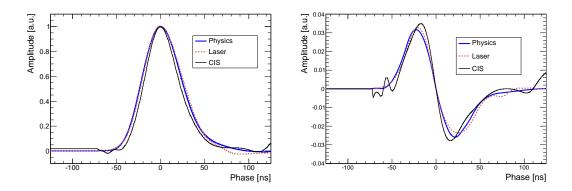

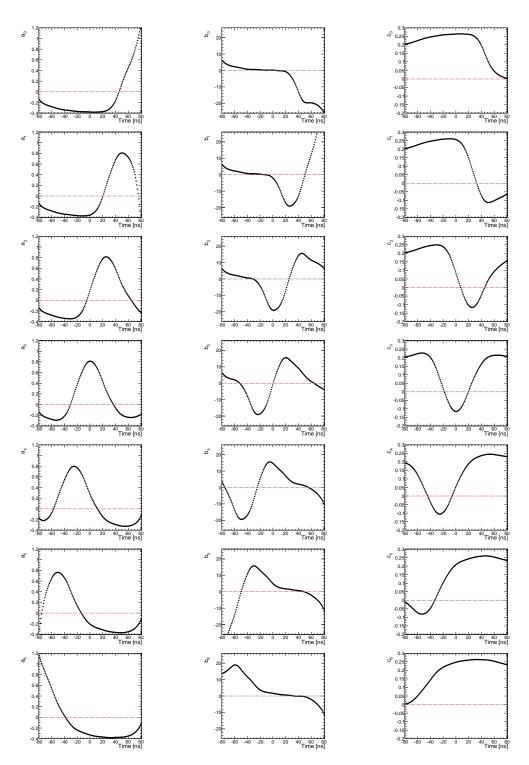

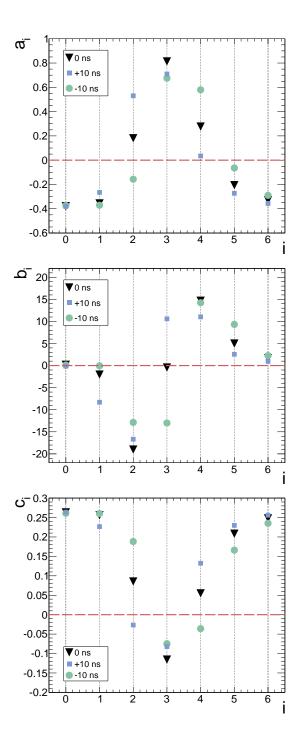

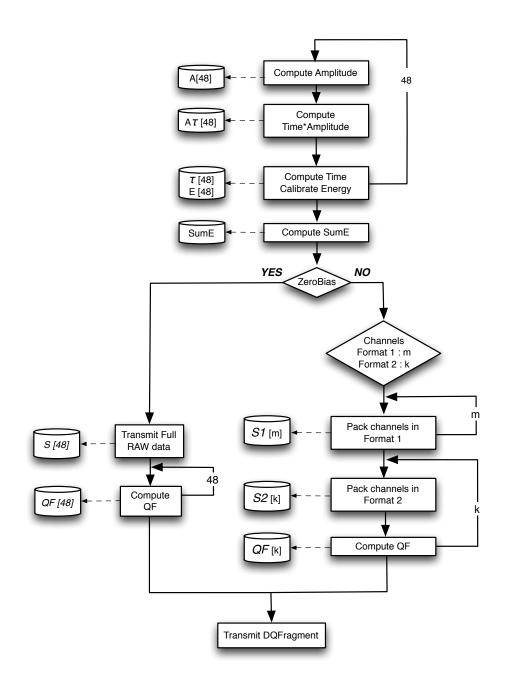

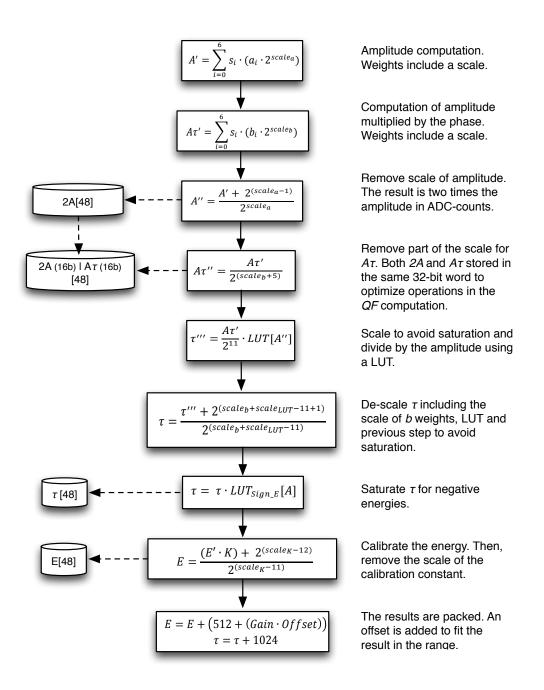

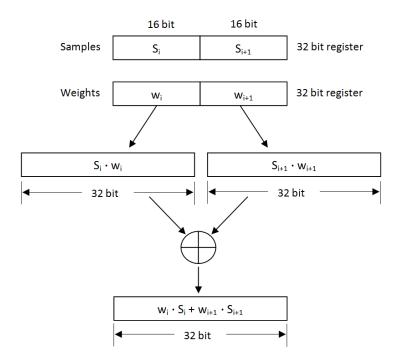

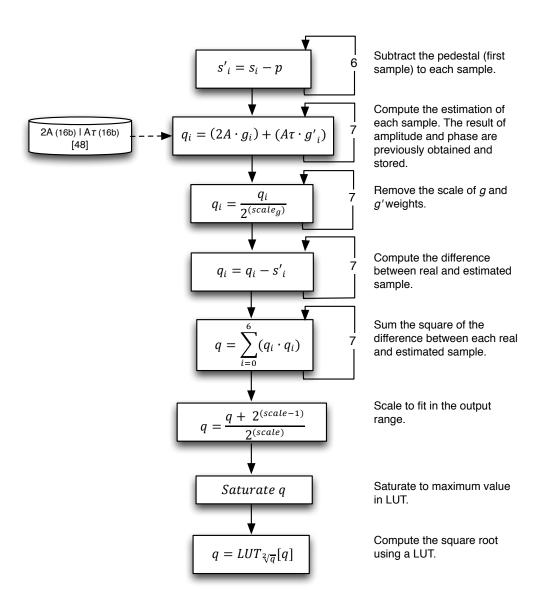

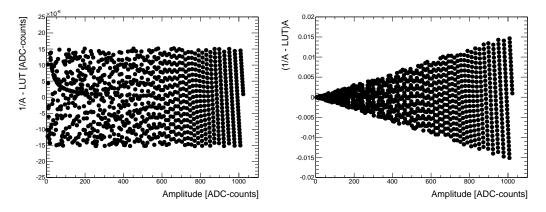

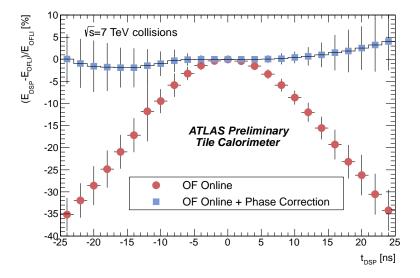

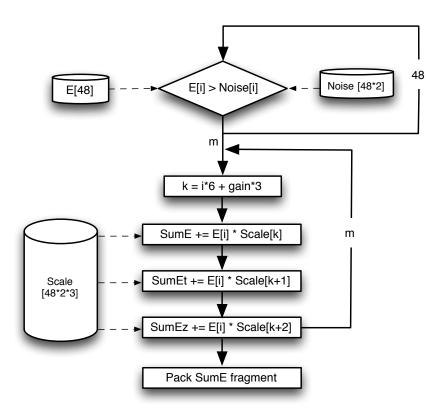

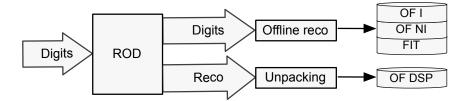

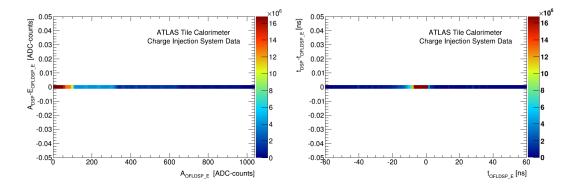

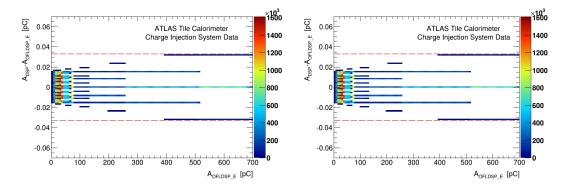

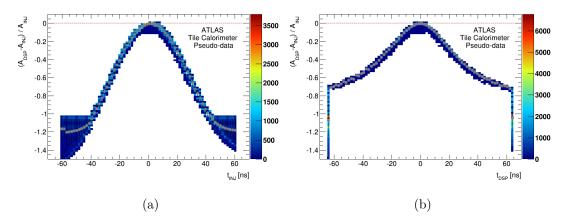

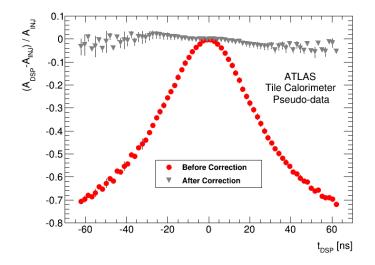

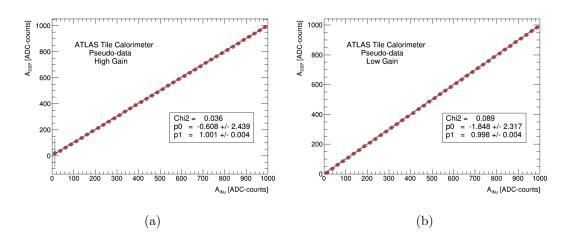

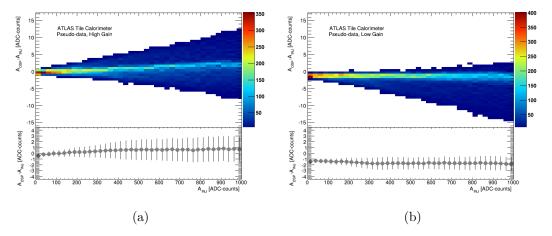

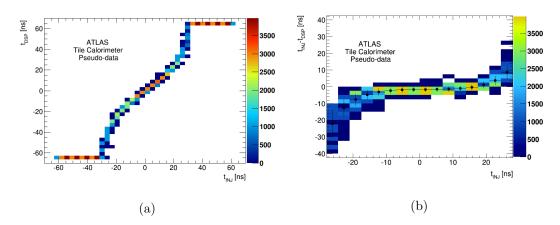

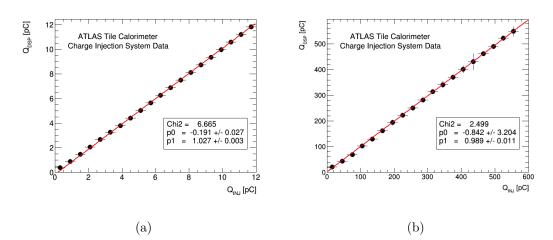

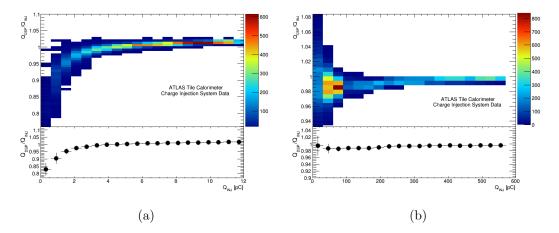

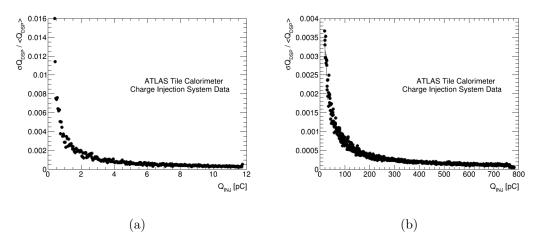

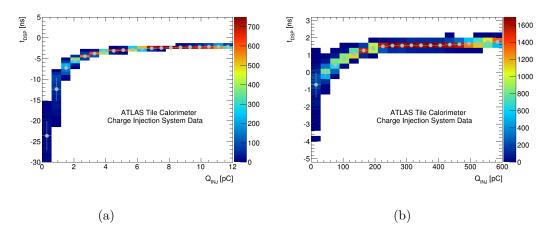

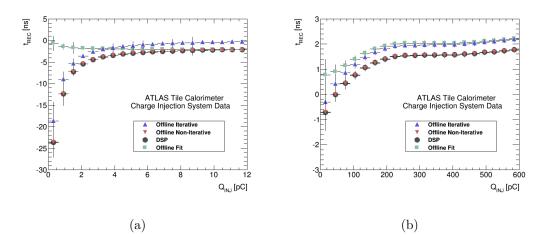

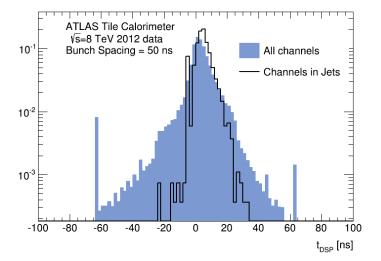

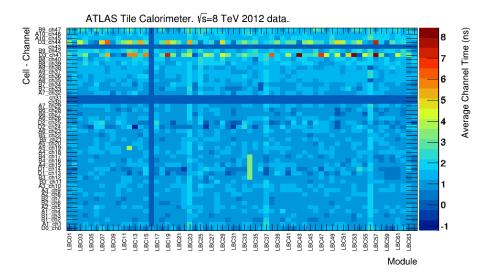

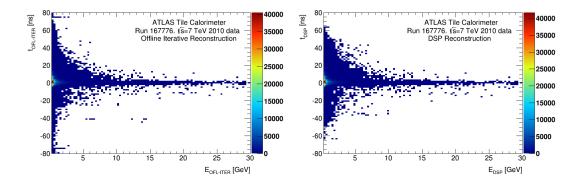

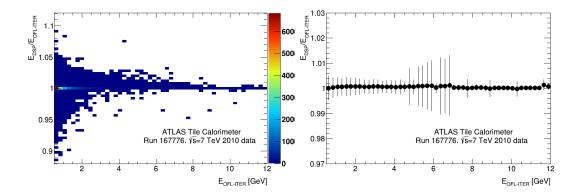

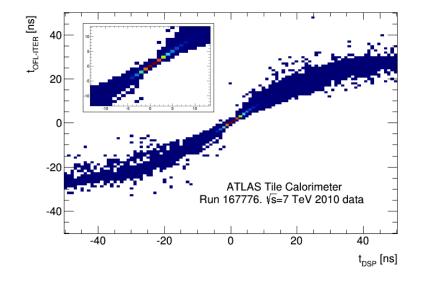

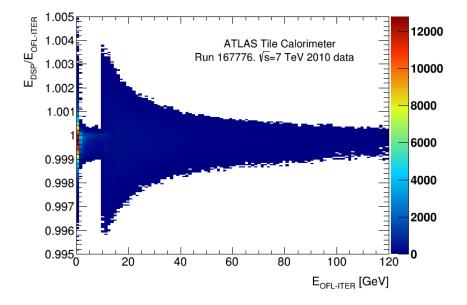

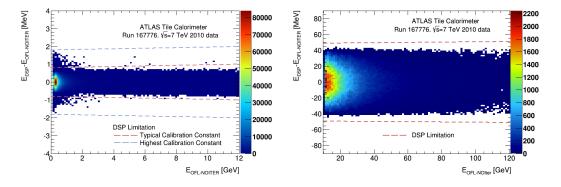

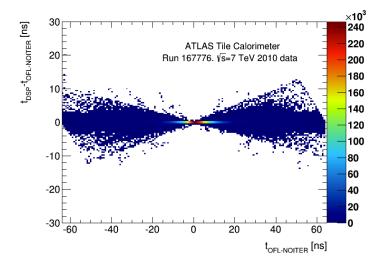

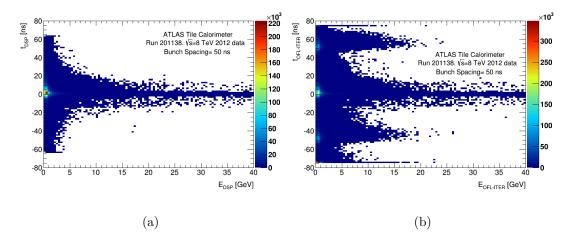

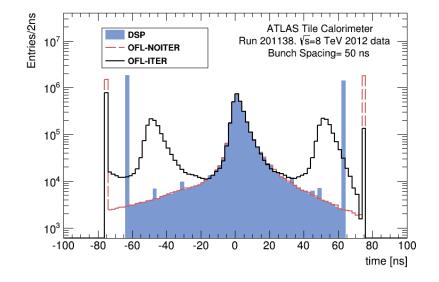

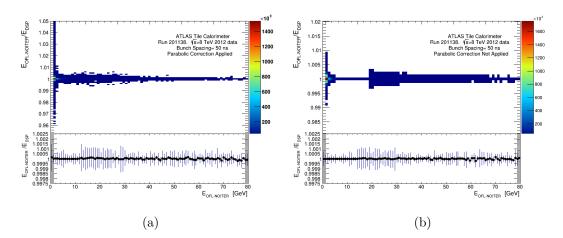

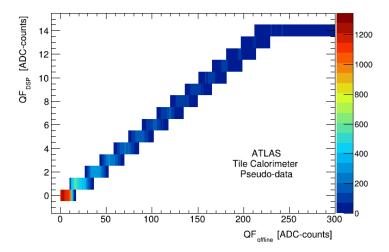

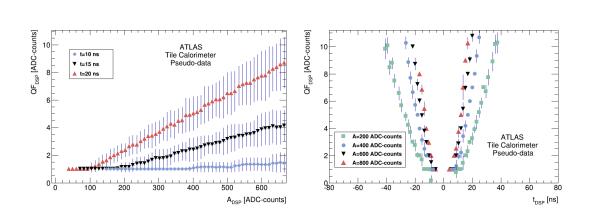

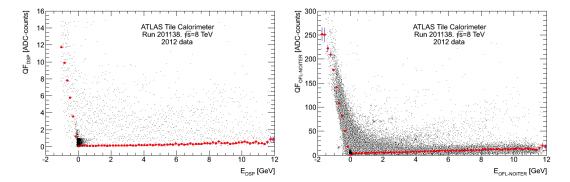

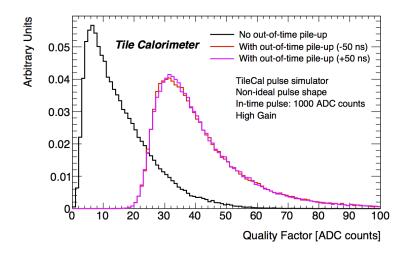

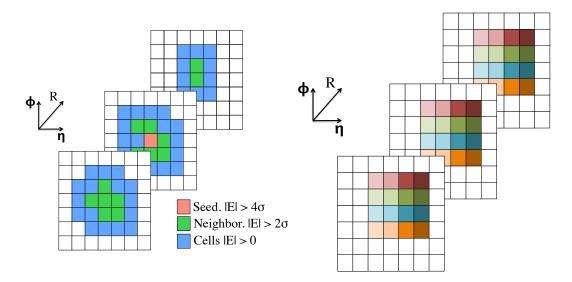

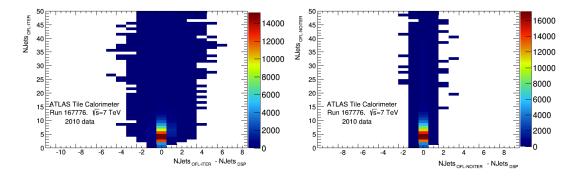

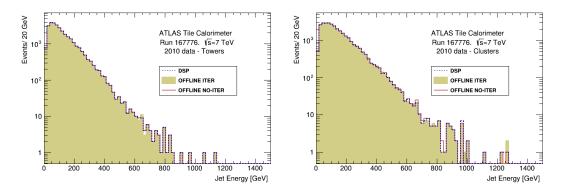

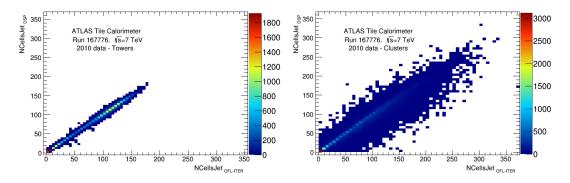

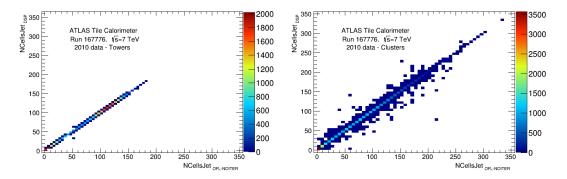

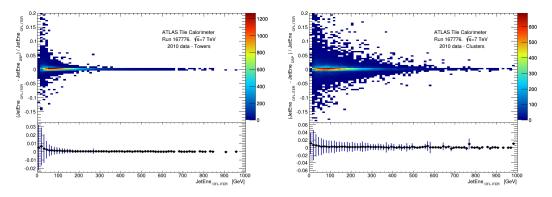

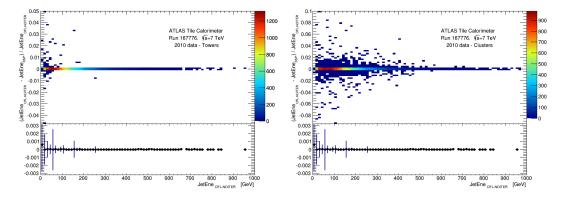

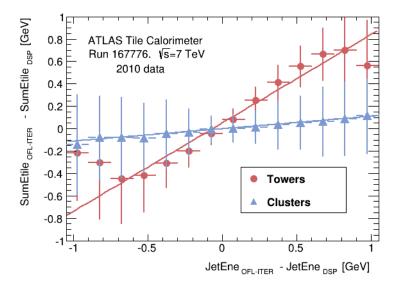

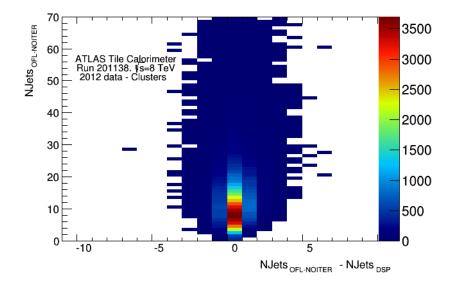

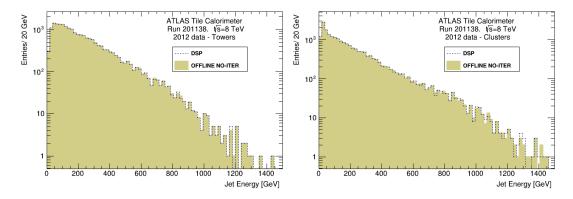

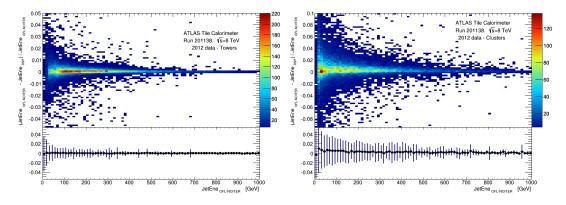

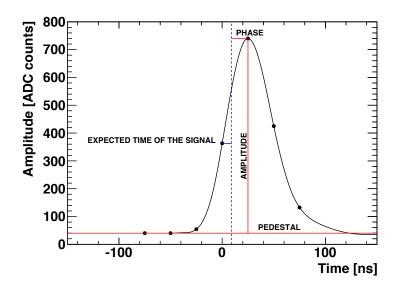

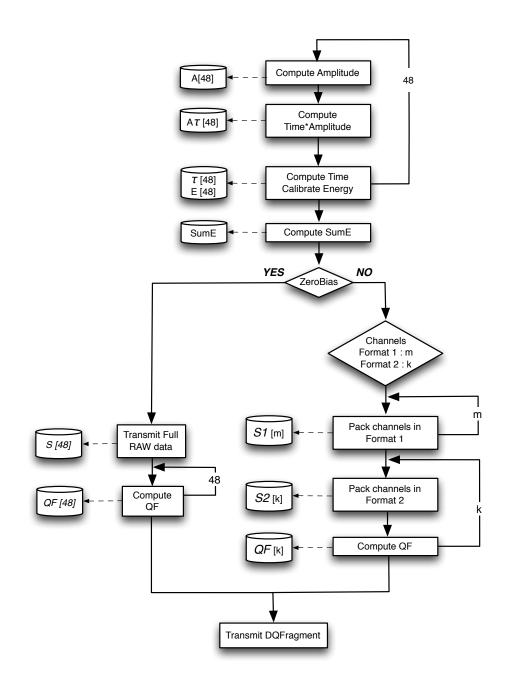

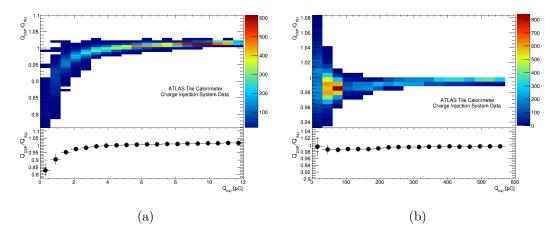

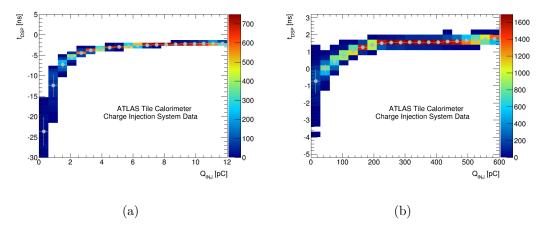

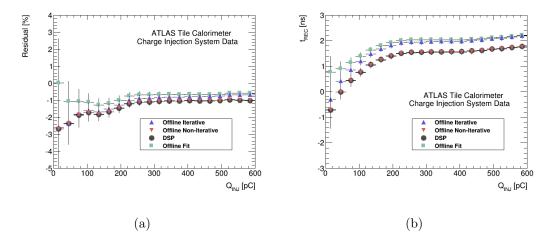

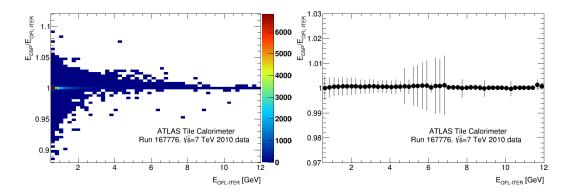

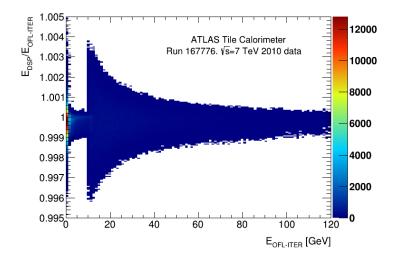

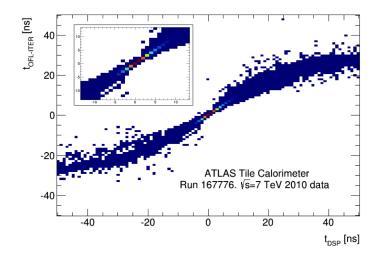

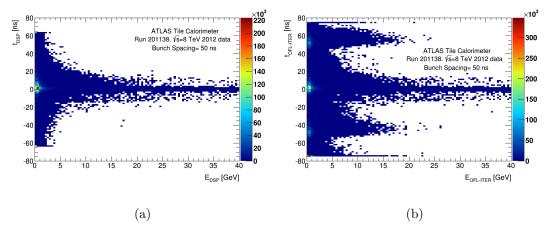

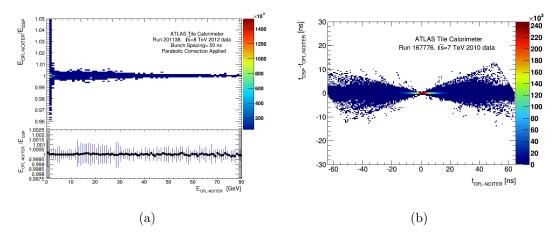

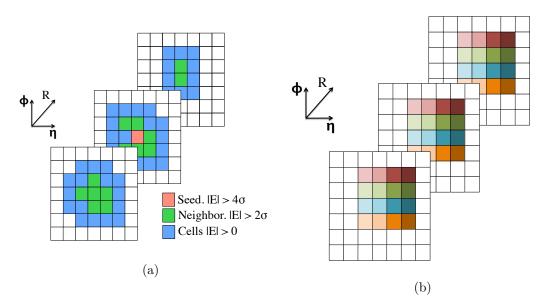

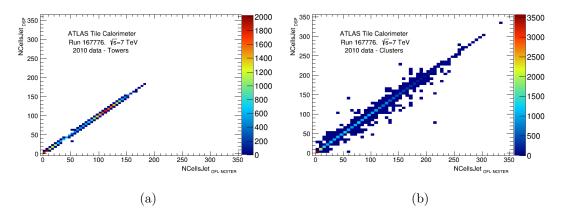

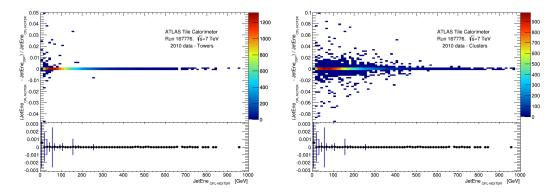

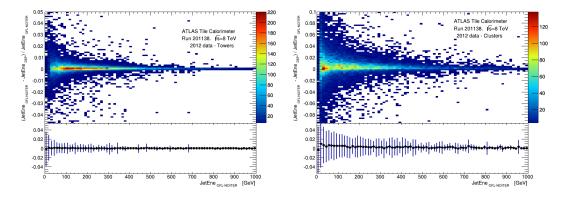

Eleven sizes of scintillating tiles (one for each depth in radius) of 3 mm thickness and with radial lengths ranging from 97 mm to 187 mm and azimuthal lengths ranging from 200 mm to 400 mm form the active medium of TileCal [16]. Ionizing particles crossing the tiles induce the production of ultraviolet scintillation light in the base material (polystyrene) and this light is subsequently converted to visible light by wavelength-shifting fluors (the polystyrene is doped with 1.5% PTP as the primary fluor and with 0.044% POPOP as the secondary fluor). Over 460,000 scintillating tiles were produced for the Tile Calorimeter by injection molding of individual tiles. The tolerance for all dimensions was held to 0.10 mm. Approximately 5% of the tile production was tested with a  $^{90}$ Sr radioactive source and the results were used to characterize the light output of each small group of approximately twenty tiles in terms of maximum intensity and attenuation length. Two sources of raw polystyrene were used for tile fabrication; during assembly, the groups of tiles were sorted so that tiles with similar response were inserted in contiguous areas of the detector. Irradiation tests of tile/fiber assemblies indicated that in the first longitudinal sampling, for an integrated dose corresponding to ten years of operation at the LHC design luminosity, a light loss of less than 10% is expected. Smaller losses will occur in the other samplings, where the radiation dose is smaller.