# Vniver§itatÿ́®València

Development and Implementation of a Selective Change-Driven Vision Sensor for High Speed Movement Analysis

Submitted in partial fulfillment of the requirements for the degree of doctor of philosophy.

Doctoral program:

Tecnologías de la Información, Comunicaciones y Matemática Computacional

Presented by: Pedro Diego Zuccarello

Directed by: Dr. Fernando Pardo Carpio and Dr. José Antonio Boluda Grau

Valencia, February 2013

## Resumen

### Motivación y objetivos

Los sensores de imágenes tradicionales trabajan bajo unos principios muy simples y conocidos: el nivel de iluminación del entorno es muestreado y transmitido a intervalos de tiempo regulares; y todos los píxeles de la matriz, sin excepción, son transmitidos secuencialmente y en orden. Esto es así aunque no se hayan producido cambios en la escena bajo observación. Esto implica que una gran parte de la información que se genera y transmite puede ser considerada como redundante. En muchos casos esta estrategia es la más adecuada. Algunos ejemplos de ello son los escáneres, los sistemas de captura de imágenes para diagnóstico médico o los sistemas de video para entretenimiento. Todas estas aplicaciones necesitan la mayor cantidad de información posible sobre el entorno, aunque este no cambie o muestre variaciones muy pequeñas en intervalos de tiempo largos. Para otro tipo de aplicaciones, como los sistemas de visión artificial o las redes de sensores inalámbricas, la gran cantidad de información redundante que genera y transmite un sensor tradicional de imágenes puede convertirse en una limitación para la implementación de sistemas en muchos entornos reales.

Muchos sistemas de visión biológicos trabajan de manera completamente distinta a los sensores de captura de imágenes tradicionales. Una de sus principales características es que las celdas sensibles (el equivalente de los píxeles en tecnología de silicio) reaccionan de manera independiente y asíncrona a los cambios de iluminación.

Tomando como punto de partida los trabajos de C. Mead y M. Mahowald [1, 2] realizados a finales de los años 80, las últimas dos décadas han presenciado avances muy significativos en el diseño de sensores de visión, todos estos fundamentalmente orientados a transmitir y procesar solo la información considerada importante o relevante dentro de la escena bajo análisis. La mayor parte de estos diseños han tomado, en mayor o menor medida, el funcionamiento del sistema biológico de visión como base de sus desarrollos. El objetivo de muchos de los trabajos realizados en este área es imitar de la mejor manera posible, y mediante las más avanzadas tecnologías de silicio, el comportamiento de los sistemas biológicos en sus facetas visual, auditiva y cognitiva (ver [2, 4, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 20] entre muchos otros). Otros trabajos han seguido otra filosofía, tomando la biología como fuente de inspiración, pero no como un objetivo en sí mismo (ver [5, 21, 22, 23, 24, 25, 26] entre muchos otros).

La estrategia de visión selectiva guiada por cambios (SCD por sus siglas en inglés) publicada en [27, 28, 29, 30], pertenece a este último grupo. Orientada a la detección y análisis de objetos moviéndose a alta velocidad, la estrategia SCD asume que solo un parte de la imagen muestra cambios entre dos *frames* consecutivos, mientras que la mayor parte de los píxeles permanecen igual. Esta hipótesis cobra especial sentido cuando se capturan frames a alta velocidad. Teniendo en cuenta que muchos de los píxeles de una determinada imagen no han cambiado respecto de sus valores en las imágenes anteriores de la secuencia, los algoritmos de procesado pueden utilizar la información ya almacenada para realizar sus cálculos. Es decir, que esta información redundante podría no transmitirse. Se podría incluso considerar que los píxeles de la matriz que muestran cambios pequeños. tendrán poco impacto en los resultados de los algoritmos. En la estrategia SCD estas hipótesis son trabajadas de forma tal que se consigue reducir sustancialmente la cantidad de información transmitida por el sensor, y por lo tanto la cantidad de información procesada fuera del mismo.

En la estrategia SCD ya no se trabaja con imágenes de forma estática, sino que la información es transportada y transmitida en la forma de un flujo de píxeles. Estos píxeles son seleccionados de forma tal que contengan solo la información con cambios temporales relevantes dentro de la escena bajo análisis. Bajo estas nuevas condiciones, sería necesario el rediseño de muchos de los algoritmos de visión tradicionales, ya que estos trabajan en base a una secuencia de imágenes estáticas transmitidas a intrevalos de tiempo regulares. El paradigma de procesado por flujo de datos (*data-flow processing*) [31] parace ajustarse de manera más adecuada a esta nueva forma de trabajo.

El principal objetivo de esta tesis es el diseño, la implementación y el testeo del primer sensor VLSI basado en la estrategia SCD de captura de información visual. En los trabajos previos a esta tesis, las ventajas de la Visión SCD fueron demostradas mediante simulaciones [27, 28, 29, 30, 32, 33]. La implementación en silicio propuesta como trabajo de esta tesis es el paso necesario para comprobar y cuantificar en entornos reales los beneficios que la estrategia SCD supondría para la implementación en hardware de muchos sistemas de visión artificial. Mas específicamente, los principales objetivos de esta tesis son:

- Diseñar el primer chip VLSI de visión artificial siguiendo la estrategia SCD de captura y transmisión de información visual.

- Implementar un sistema completo de visión artificial basado en este nuevo sensor SCD. Para cumplir con este objetivo será necesario el diseño de una PCB, un firmware y un software de PC para la adquisición de datos.

- Habiéndose cumplido los objetivos anteriores, el último objetivo es mostrar, mediante la experimentación adecuada, como un sistema SCD es una alternativa válida a los sistemas de visión artificial tradicionales basados en secuencias de imágenes estáticas. De esta manera, se pretende cuantificar y analizar, las ventajas de este nuevo tipo de sistemas propuesto.

#### Metodología

Desde el punto de vista metodológico, esta tesis ha seguido la metodología *top-down full-custom* de diseño microelectrónico. Todo diseño microelectrónico se construye a partir de una serie de especificaciones. Tomando como base dichas especificaciones, se pueden identificar las principales limitaciones de los circuitos involucrados en el diseño. Esto permite proponer un diagrama en bloques de la implementación. Para el diseño de cada bloque en particular, se pueden buscar alternativas en la bibliografía pertinente. En algunos casos, las respuestas a los problemas de diseño pueden surgir como propuestas originales dentro de la investigación en curso.

En el caso particular de esta tesis, el énfasis se ha puesto en la captura de *frames* a alta velocidad (en el orden de 1-2 kfps). Otro de los puntos importantes a tener en cuenta es el diseño del bloque en el cual se seleccionan los píxeles que más han cambiado desde la última vez que fueron transmitidos. Los circuitos que más se adaptan a esta estrategia de comparación son analógicos [34, 35, 36, 37, 38, 39, 40]. Es este el motivo por el cual se ha escogido para el diseño del sensor una tecnología CMOS con comprobadas prestaciones de señal mixta analógico/digitales.

Una vez fabricado el chip, se procedió a seguir un plan de testeo con su correspondiente protocolo de validación. Debido a que el chip es un prototipo que no sigue ningún estándar particular, la placa de pruebas, el protocolo de comunicación y el código del firmware y del software fueron diseñados enteramente a medida.

#### Conclusiones

De acuerdo a lo expuesto en el primer capítulo de esta tesis, los objetivos principales de la misma era: diseñar y fabricar el primer sensor siguiendo la estrategia SCD de captura y transmisión de información visual, y mostrar, mediante experimentación adecuada con el sensor fabricado, como un sistema de visión artificial puede mejorar sus prestaciones cuando los principios SCD son utilizados en el diseño de su hardware y de sus algoritmos de procesado. Todos estos objetivos fueron alcanzados. Se diseñó y fabricó el primer sensor de visión SCD. Una vez fabricado, el mismo se empotró dentro de un sistema portátil basado en un microcontrolador de 32 bits. Este sistema sirvió para implementar algoritmos de seguimiento de objetos moviéndose a alta velocidad. También sirvió para medir las principales características del sensor.

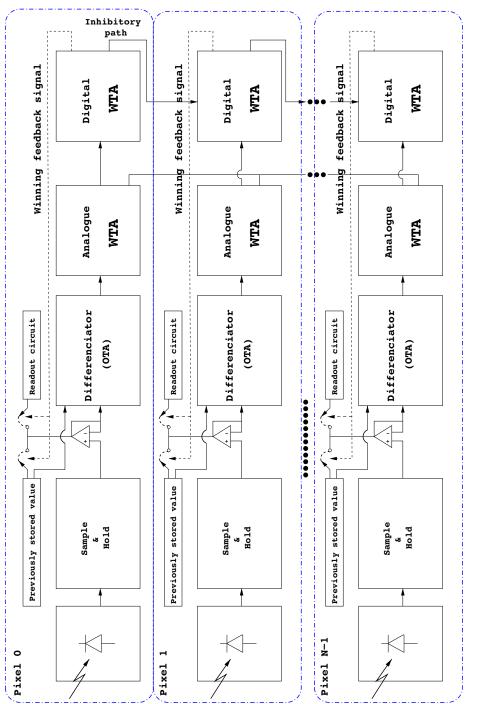

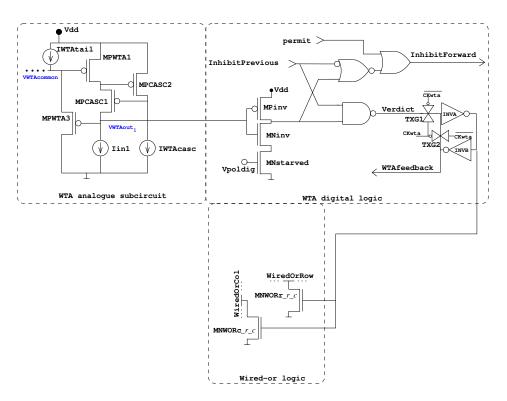

Dentro del esquema del circuito, el bloque más importante, y el que implicó un mayor desafío, es el bloque encargado de seleccionar los píxeles que más han cambiado dentro de la matriz. Este tipo de comparaciones globales de valores analógicos no son simples de realizar. En el caso de esta tesis, para esta tarea se utlizó un circuito *winner-takes-all* (WTA). En una primer etapa analógica el WTA selecciona un conjunto de valores que muestran cambios de iluminación relevantes. Una señal de inhibición digital se propaga a lo largo de toda la matriz para que solo uno de estos valores sea transmitido, de esta manera evitando colisiones en la transmisión de los píxeles. El circuito digital de inhibición ha sido publicado como una de las contribuciones originales de esta tesis [77].

En esta primera implementación del sensor la resolución es todavía baja. Esto es debido a que se trata de un primer prototipo. Se deja como trabajo futuro la implementación y fabricación de una matriz de píxeles de mayores dimensiones.

El proceso de caracterización del sensor muestra algunos problemas relativos al ruido y al rango dinámico del mismo. El ruido es bastante mayor de lo esperado. El rango dinámico es bajo, por lo que el sistema desarrollado puede utilizarse solo bajo determinadas condiciones de iluminación favorables. El consumo de potencia por pixel es más elevado de lo que se reporta en la bibliografía para otros sensores similares de reciente desarrollo. El transitorio de la señal del nivel de gris es largo y debería reducirse en futuras versiones del sensor. Todas estas cuestiones deben ser tenidas en cuenta como mejoras y trabajo futuro para futuras versiones del sensor SCD.

Los diseños VLSI en tecnología CMOS como el llevado a cabo en esta tesis son, habitualmente, difíciles de desarrollar. Los chips que llegan a obtener resultados lo suficientemente buenos como para llegar al mercado son el resultado de varias iteraciones de diseño y de la fabricación de varios prototipos. Esta tesis puede considerarse como la primer iteración de este proceso, y es evidente que todavía hay trabajo por hacer para llegar a los estándares de mercado. Aún así, bajo condiciones de iluminación adecuadas, se han realizado experimentos de seguimiento de objetos moviéndose a alta velocidad transmitiendo muy pocos píxeles del sensor hacia el sistema de procesado. Estos resultados, detallados en la sección 4.3 muestran como el hardware (sensor junto con el sistema de procesado) desarrollado en esta tesis es capaz de seguir objetos a muy alta velocidad utilizando tan solo el ancho de banda que utilizaría un sensor tradicional de baja velocidad de 25 fps, pero con la resolución temporal y las prestaciones de un hardware de captura de imágenes de alta velocidad trabajando a una tasa de 2000 fps. Esto demuestra y cuantifica como el ancho de banda y las prestaciones de un sistema de visión artificial pueden obtener una mejora sustancial al incorporar los principios SCD de diseño de hardware v procesado de la información. Esta experimentación constituye uno de los principales logros de esta tesis.

## Contribuciones

- En los trabajos previos a la realización de esta tesis, las ventajas de la estrategia de visión SCD fueron presentadas solo en entornos simulados. Una de las mayores contribuciones de esta tesis es el diseño e implementación del primer sensor VLSI siguiendo los principios de sensado SCD. Este logro abre la puerta para el desarrollo e implementación de sistemas de visión artificial en los cuales es posible obtener altas velocidades de captura y procesado, pero utilizando hardware estándar de bajo coste.

- De todos los bloques circuitales diseñados e implementados, el que implicó el mayor desafío es el encargado de seleccionar el pixel que más

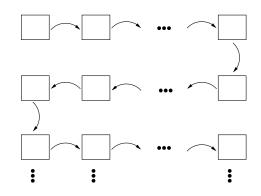

ha cambiado dentro de la matriz. La bibliografía muestra que los circuitos WTA pueden ser una solución cuando se desea averiguar el mayor de los valores entre un grupo de tensiones o corrientes analógicas. Cuando el número de celdas involucradas en la competición es muy grande, existe la posibilidad de que se seleccione más de un ganador como resultado de la misma. Una de las contribuciones originales de esta tesis es la propuesta de un subcircuito digital para lidiar con la situación de que se haya seleccionado más de un ganador en este tipo de etapas analógicas. El circuito finalmente implementado y fabricado consiste en una primer etapa analógica, en la que se podrían observar muchos ganadores, seguida de una etapa digital en la cual una señal de inhibición se propaga a través de la matriz para que solo uno de los píxeles seleccionados como ganadores en la etapa analógica pueda acceder al circuito de lectura exterior del pixel.

- Otro logro, que vale la pena mencionar, relacionado con la etapa WTA es que, al momento de escribir esta memoria, no hemos encontrado ningún reporte de la fabricación y testeo de este tipo particular de celda WTA analógica. A pesar de que el diseño de este amplificador WTA en particular fue propuesto den 1998 por Sekerkiran *et al.*, esta es la primera vez que se fabrica. En el experimento de seguimiento de objetos descrito en la sección 4.3 se muestra como el bloque de decisión basado en esta celda es capaz de encontrar el grupo de píxeles que más han cambiado dentro de la matriz.

- La implementación de un sistema de visión artificial SCD compacto, basado en el sensor VLSI diseñado durante esta tesis, y la experimentación llevada a cabo con él, pueden también considerarse uno de los mayores logros alcanzados durante esta tesis. A pesar de algunos problemas relacionados con el ruido y el rango dinámico del sensor (ver las secciones 4.2.5, 4.2.2 y 4.2.9 para una discusión detallada sobre estos temas) la experimentación descrita en la sección 4.3 muestra como, un sistema SCD sencillo basado en el sensor desarrollado en esta tesis es capaz de realizar el seguimiento de objetos moviéndose a alta velocidad con muy bajos requisitos de ancho de banda, pero con altas prestaciones en cuanto a resolución temporal y latencia en el procesado de la información.

## Abstract

An artificial vision system is basically composed of a sensor, usually in VLSI CMOS or CCD technology, and a processing stage. Nowadays, in the vast majority of real-world implementations, the sensing part of the system is a traditional frame-based imager. These types of image sensors work under some very well known principles: the illumination level of the surrounding environment is sampled and transmitted at regular time intervals, even if no new relevant information is produced in the scene under analysis. A traditional frame-based image sensor is usually not able to evaluate if the information coming from a certain pixel is relevant or irrelevant. Since they do not perform any kind of analysis of the information being captured, the illumination level of all the pixels in the sensing matrix must be transmitted to be analyzed and processed at the processing stage. Many times, a huge amount of redundant non-relevant information is transmitted. The consequences of this are that valuable resources such as bandwidth and processing power are wasted. Furthermore, depending on the particular context and hardware configuration, the processing hardware may not even be able to cope with all the generated data.

Many of these problems can be overcome with the design of new sensing and readout strategies focused on the selection of relevant changing information. Over the last decade many relevant improvements have been achieved in this direction. Taking the biological vision system as a general guide and inspiration, an increasing number of very-large scale of integration (VLSI) vision sensors have been, and are being designed where the sparcity, asynchrony and event-driven generation of the information coming from the visual field is taken into account.

It is within this framework that Selective Change-Driven Vision (SCD) emerges as an innovative and original proposal. SCD Vision relies on the idea that a pixel showing a large change in intensity is an indicator of fast movements, and object edges around it. An SCD sensor is frame-based in the sense that successive frames are captured at a very high rate, but pixel readout is performed in an entirely different manner. The pixels are read out in order of relevance. The larger the change in illumination, the more relevant the pixel is considered to be. Not all the pixels in the sensing matrix need to be transmitted. As the pixels showing relevant changing information are transmitted first, a small subset of pixels might be read out, these being the ones conveying the most important information of the scene under analysis.

In this thesis, the first VLSI CMOS vision sensor following SCD principles is presented. A 32x32 pixel matrix was implemented and fabricated in 0.35  $\mu$ m 4-metal 2-poly silicon technology.

The most challenging part of this microelectronic design was the decision block, where the pixels undergoing the largest changes in the sensing matrix are selected. This problem was solved by means of a winner-takes-all (WTA) circuit. A large WTA network together with a proposal for single winner selection was designed, implemented and its behaviour characterized.

The designed sensor was embedded into a small, but powerful artificial vision system based on a 32-bit microcontroller. This system was used to implement tracking algorithms as well as to characterize the main basic features of the sensor. The experimentation carried out in this thesis shows how a simple SCD system based on our SCD sensor is able to track fast moving objects with just the bandwidth requirements of a low speed 25 fps standard camera, but with the time resolution and performance of a high-speed camera working at 2000 fps. This clearly demonstrates that bandwidth and processing requirements are substantially reduced when SCD hardware is used.

En primer lugar, agradezco a Fernando Pardo y a José Antonio Boluda, no sólo por haber confiado en mí para realizar el trabajo que ahora presento y haberme permitido descubrir el fascinante mundo del diseño microelectrónico, sino por su activa participación en el testeo del sensor que aquí se describe y presenta. Sin su ayuda, esta tesis seguramente no hubiese llegado hasta donde llegó. Mis más sinceros agradecimientos a Paco Vegara por haberme ayudado una y otra vez con todo el cacharraje necesario para los experimentos. Su colaboración ha sido también fundamental en este trabajo.

A Tobi Delbrück, Shih-Chi Liu, Raphael Berner y Alex de la Plaza, gracias por su ayuda y sobre todo por su paciencia. Mi ignorancia en estos temas al principio de esta tesis era tan evidente como completa. Muchas gracias a Paco Serra-Graells y a Lluís Terès, no sólo por confiar en mí para las muchas responsabilidades que implica llevar adelante un proyecto en el IMB-CNM, sino por haberme permitido ceder tiempo de mi nuevo trabajo para terminar esta tesis. A Wladimiro Díaz, gracias por su paciencia y ayuda en todo lo referido al sistema operativo Linux.

Quiero también agradecer a mis compañeros de trabajo, Guillermo, Katerine, Adrián y Alicia, que han hecho de nuestro lugar de trabajo un sitio ameno y lleno de compañerismo.

Si tengo que resumir los últimos cinco años y medio de mi vida con una sola palabra, la que, sin dudas, más cabalmente se ajusta, es la palabra 'aprendizaje'. Si de una enumeración se trata, esta incompleta lista puede servir de orientación: he aprendido la difícil, artesanal e interesante tarea de diseñar chips analógicos; he aprendido a diseñar circuitos impresos; he aprendido a programar el microcontrolador PIC; he aprendido las bases, y varios de los vericuetos, del exageradamente amado por unos y exageradamente odiado por otros, sistema operativo linux; he aprendido, y todavía sigo, día a día, aprendiendo, a ser padre; he aprendido, y todavía sigo, día a día, aprendiendo, a ser padre de una hija mujer; he aprendido, a través de enfrentar fantasmas ajenos, a enfrentar muchos de los fantasmas propios con los cuales todos convivimos. Estuve en el Instituto de Neuroinformática de Zürich, lugar que me fascinó desde el primer día por la capacidad y la experiencia de la personas, punteras casi todas en sus repectivas disciplinas, que allí trabajan. Pero la fascinación más grande provino, tal vez, del hecho de la honestidad y completa humildad con la que algunas de las personas más brillantes que he conocido, y seguramente conoceré, reconocían su más completa ignorancia. Esto ha, definitivamente, dejado en mí una marca. Mi forma de trabajar y analizar la realidad que me rodea es ahora distinta. Aprendí lo que es el Acontecimiento, y me aferré a él con pasión; aprendí que la luna podría, si quisiera, tomar un helado; que la letra H es amiga de las vocales; y descubrí, que en la esquina de mi propia casa, hay un bosque, muy oscuro, y lleno de lobos. Aprendí sobre la alegría del llegar y sobre la dignidad, la entereza, la tristeza, y la aceptación del irse.

Agradezco a Max y a Sandra la confianza y una amistad que lleva ya varios años, y espero lleve muchos más. A Matu, a quien sigo considerando una de las personas con más espíritu científico de todas las que conozco, y a quien sigo queriendo como a un hermano; y a Laura, Valentín y David, su maravillosa familia, con quienes tan buenos momentos hemos compartido a lo largo de estos años. No puedo dejar de mencionar en estas páginas a Chema, quien es ya más porteño que yo mismo; a Majo, a quien conozco desde hace más años de los que puedo recordar, y a Malena y Aitana. Agradezco a Aníbal, por su amistad, por sus sabias y célebres frases, y por confiar en mi persona mucho más de lo que yo lo haré nunca. No puedo dejar de agradecer a Carlos; una parte de este trabajo, sin lugar a dudas, le pertenece. Quiero también agradecer a Esther, Miguel Ángel, Reme, Pablo y María, personas por las cuales siento muchísimo respeto y cariño, por haberme tratado desde el primer día como uno más de su familia.

Dedico un muy especial agradecimiento a Juan Antonio, Isabel, Gemma, Belén, Alberto, Nuria, Guillem y Alemnesh, por haberme ayudado a distraerme de la tesis en los momentos en los cuales nada salía bien y por haberme acompañado en los momentos en los cuales todo empezaba a cerrar, pero sobre todo, por tratar a mi familia como a la suya propia. Sus permanentes demostraciones de afecto forman parte de las cosas que nunca olvidaré.

Dedico esta tesis a mis padres, a quienes profeso el más profundo cariño, y a los cuales, a través de mi propia paternidad, comprendo cada día más. También dedico este trabajo a mi hermano, Santiago, cuyo sentido común ha sido siempre muy superior al mío; y a su familia, Malala, Renata y Genaro, por quienes siento un afecto infinito, y a quienes lamento no poder tener más cerca.

Finalmente, dedico no sólo este trabajo, sino el día a día de mi vida

entera a Esther, y a su sonrisa que todo lo ilumina, a Leo, mi pequeño sabio, y a Violeta, cuya contagiosa alegría hace que muchas de las cosas que me rodean cobren sentido. No puedo más que agradecerles por su apoyo, sus permanentes demostraciones de afecto y sobre todo, por su paciencia. Una gran parte del tiempo dedicado a esta tesis era, definitivamente, suyo. Espero poder compensarlos de ahora en adelante.

Agradecimientos y dedicatorias

## Contents

| Resumen |            | iii                                                           |                 |

|---------|------------|---------------------------------------------------------------|-----------------|

| A       | bstra      | ct                                                            | ix              |

| A       | grad       | cimientos y dedicatorias                                      | xi              |

| A       | brev       | ations and achronyms                                          | xxi             |

| 1       | Inti       | oduction                                                      | 1               |

|         | 1.1        | Motivation and objectives                                     | 3               |

|         | 1.2        | Methodology                                                   | 5               |

|         | 1.3        | Organization of the thesis                                    | 6               |

| 2       | Sta        | e of the art                                                  | 9               |

|         | 2.1        | General Overview                                              | 11              |

|         |            | 2.1.1 Biomimetic event-driven vision sensors designs $\ldots$ | 12              |

|         |            | 2.1.2 Other event-driven vision sensing strategies $\ldots$ . | 16              |

|         | 2.2        | Selective Change-Driven Vision                                | 18              |

|         | 2.3        | Conclusions                                                   | 21              |

| 3       | SCI        | ) sensor VLSI implementation                                  | <b>23</b>       |

|         | 3.1        | Working principles                                            | 26              |

|         | 3.2        | Circuit description                                           | 29              |

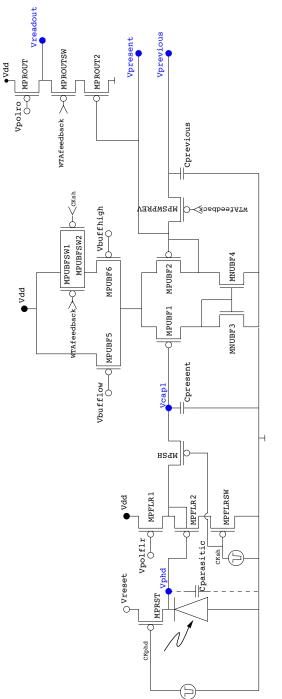

|         |            | 3.2.1 Light sensing and readout subcircuit                    | 29              |

|         |            | 3.2.2 The wide-input-range operational transconductance       | 0.4             |

|         |            | amplifier                                                     | 34              |

|         |            | 3.2.3 Winner-takes-all stage                                  | 42              |

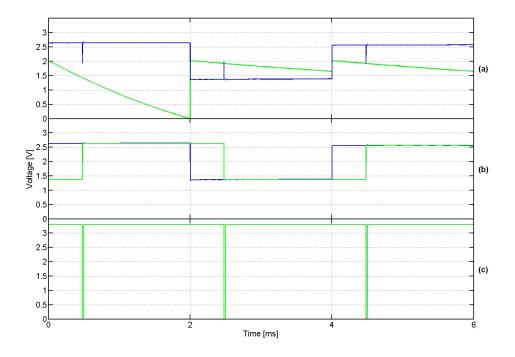

|         |            | 3.2.3.1 Analogue WTA                                          | 42              |

|         |            | 3.2.3.2 WTA digital logic                                     | 44              |

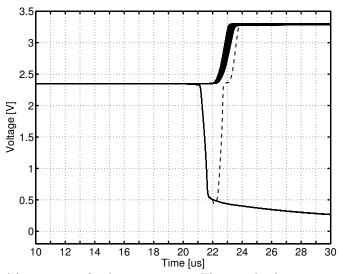

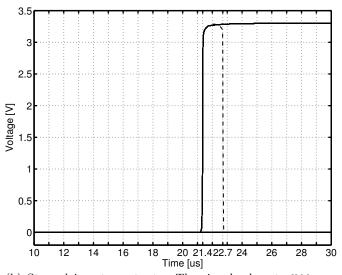

|         |            | 3.2.3.3 WTA simulations                                       | 45<br>50        |

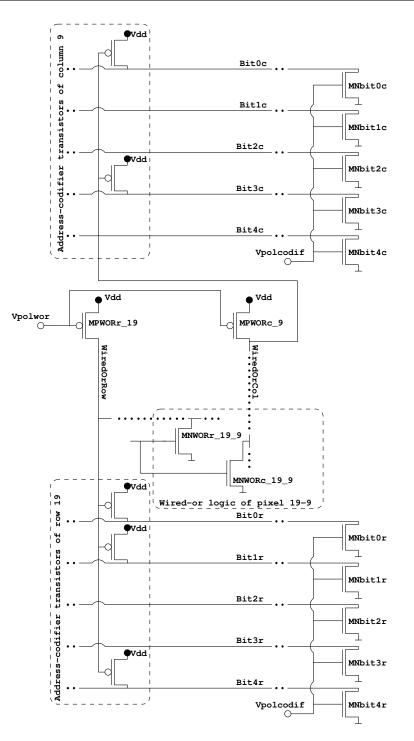

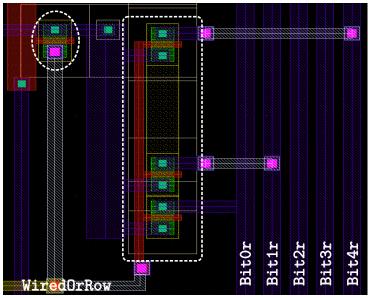

|         |            | 3.2.4 Wired-or logic and address codifiers                    | 50<br>50        |

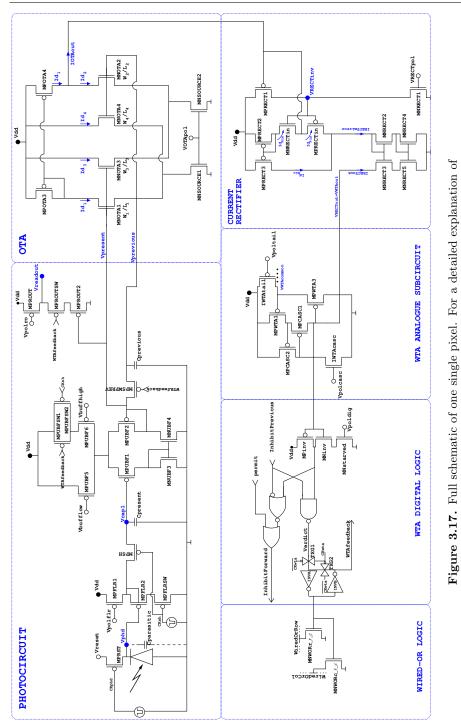

|         |            | 3.2.5 Complete schematic of the pixel                         | $50\\54$        |

|         | <b>9</b> 9 | 3.2.6 Pixel layout                                            | $\frac{54}{63}$ |

|         | 3.3        | Conclusions                                                   | 03              |

| 4 | Measurements and results    |         |                                                       | <b>65</b> |  |

|---|-----------------------------|---------|-------------------------------------------------------|-----------|--|

|   | 4.1                         | Experi  | mental set-up and sensor operation                    | 67        |  |

|   | 4.2                         | Sensor  | characterization                                      | 72        |  |

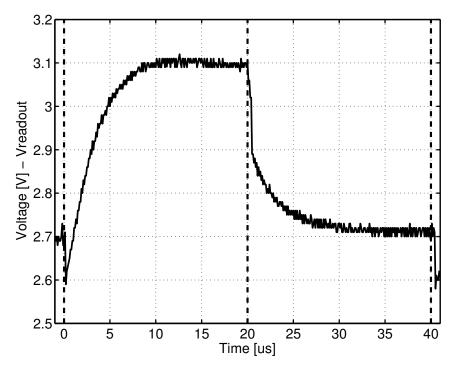

|   |                             | 4.2.1   | Grey level signal time response                       | 72        |  |

|   |                             | 4.2.2   | Dynamic range                                         | 73        |  |

|   |                             | 4.2.3   | WTA-matrix selection-logic experiments                | 76        |  |

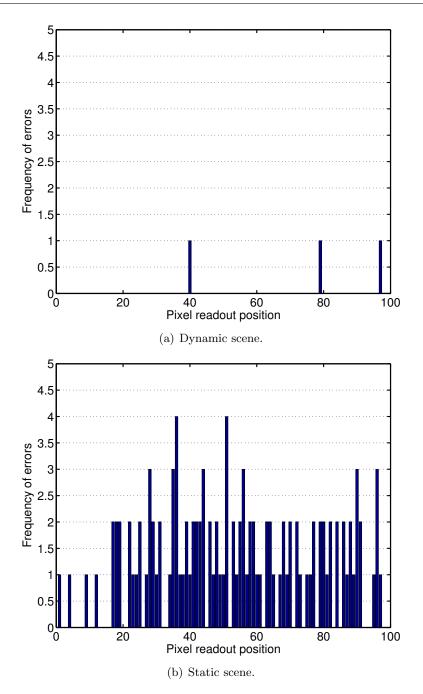

|   |                             | 4.2.4   | WTA-stage errors                                      | 77        |  |

|   |                             |         | 4.2.4.1 WTA-stage not being able to choose a winner   | 77        |  |

|   |                             |         | 4.2.4.2 WTA sequentially selecting the same winner    | 80        |  |

|   |                             | 4.2.5   | Noise                                                 | 80        |  |

|   |                             |         | 4.2.5.1 Fixed-pattern noise measurements              | 81        |  |

|   |                             |         | 4.2.5.2 Random temporal noise measurements            | 84        |  |

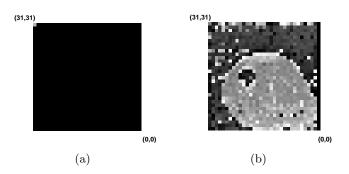

|   |                             | 4.2.6   | Images                                                | 85        |  |

|   |                             | 4.2.7   | Power consumption                                     | 86        |  |

|   |                             | 4.2.8   | Summary of characteristics                            | 87        |  |

|   |                             | 4.2.9   | Discussion and proposals                              | 87        |  |

|   | ng experiment               | 89      |                                                       |           |  |

|   |                             | 4.3.1   | Object detection and centre of mass calculation algo- |           |  |

|   |                             |         | rithm                                                 | 89        |  |

|   |                             | 4.3.2   | Results                                               | 92        |  |

|   |                             | 4.3.3   | Discussion                                            | 94        |  |

|   | 4.4                         | Conclu  | sions and improvement proposals                       | 96        |  |

| 5 | Conclusions and future work |         |                                                       |           |  |

|   | 5.1                         | Contri  | butions                                               | 103       |  |

|   | 5.2                         |         |                                                       | 105       |  |

|   | 5.3                         | List of | publications and research projects                    | 107       |  |

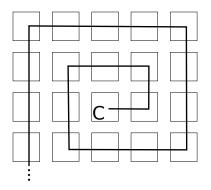

| 3.1  | Block diagram of the pixel circuit.                               | 28       |

|------|-------------------------------------------------------------------|----------|

| 3.2  | Schematic of the photocircuit.                                    | 31       |

| 3.3  | Simulations of the photocircuit operation.                        | 33       |

| 3.4  | operational transconductance amplifier (OTA)'s input voltage.     | 35       |

| 3.5  | Narrow input range OTA                                            | 36       |

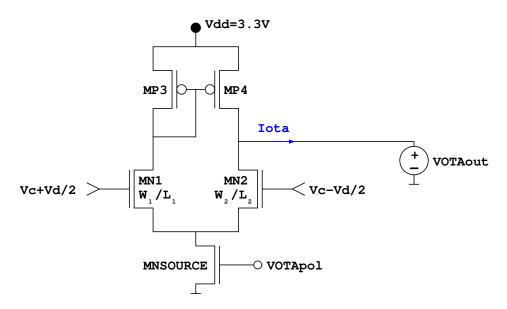

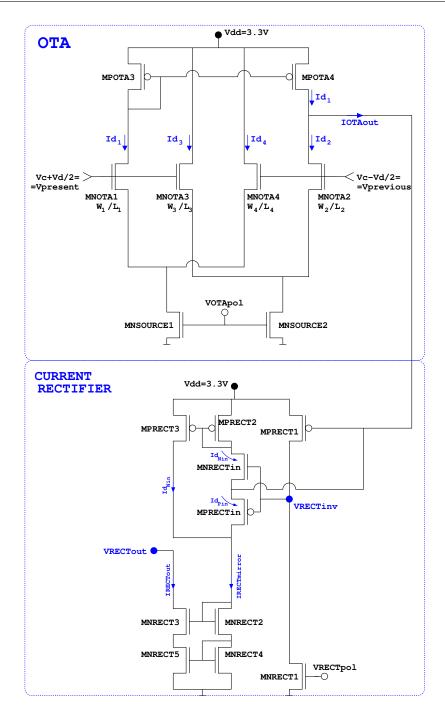

| 3.6  | Wide input range OTA and rectifier subcircuits.                   | 37       |

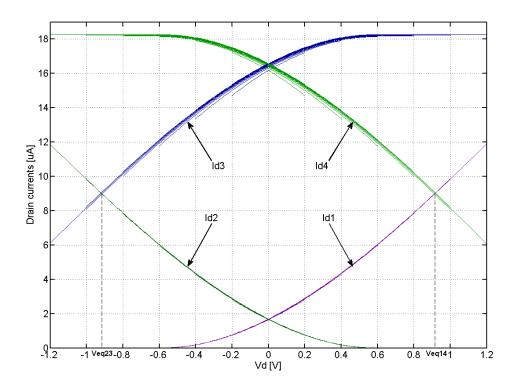

| 3.7  | Drain current for transistors MNOTA1-4.                           | 38       |

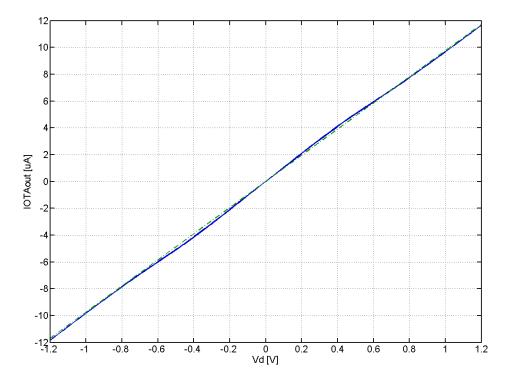

| 3.8  | OTA's output current IOTAout                                      | 39       |

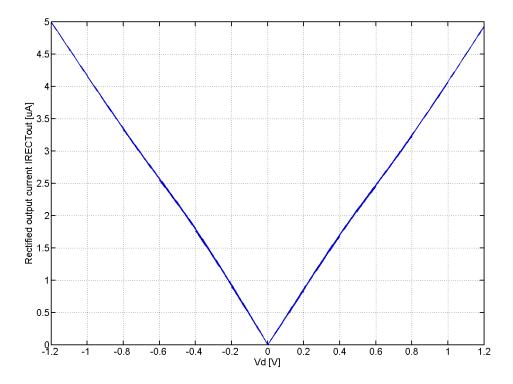

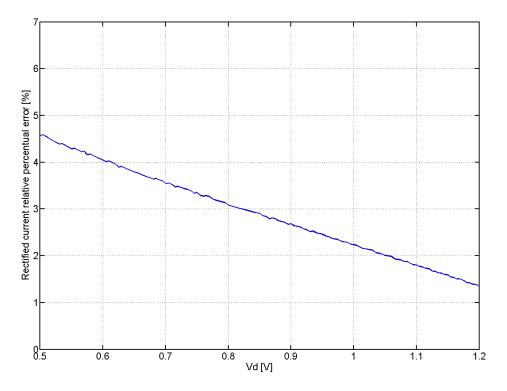

| 3.9  | Current rectifier's output current                                | 40       |

| 3.10 | IRECTout current rectifier's output relative percentual error.    | 41       |

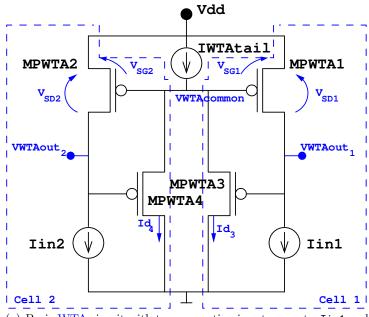

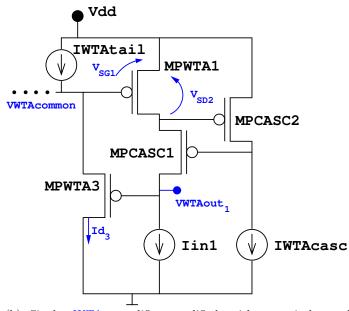

| 3.11 | WTA amplifiers.                                                   | 43       |

| 3.12 | WTA analogue/digital circuit for single winner selection          | 46       |

| 3.13 | Propagation path for WTA digital inhibition signals               | 47       |

| 3.14 | Simulation of the decision stage of the pixel matrix              | 49       |

| 3.15 | Wired-or and address-codifier transistors of the pixel in row     |          |

|      | 19 and column 9                                                   | 51       |

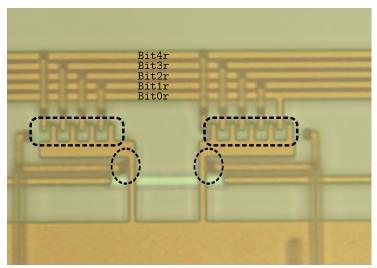

| 3.16 | Examples of the layout of the address-codifiers                   | 52       |

| 3.17 | Full schematic of one single pixel                                | 53       |

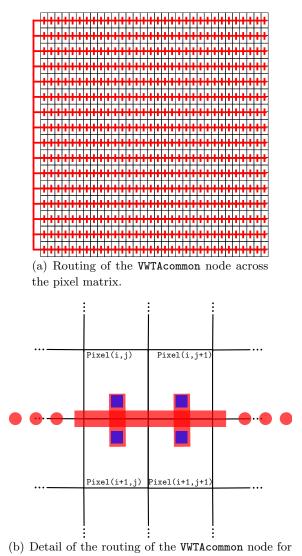

| 3.18 | Basic 4-pixel reproducible layout unit                            | 55       |

| 3.19 | Simplified representation of the routing of the VWTAcommon        |          |

|      | node                                                              | 56       |

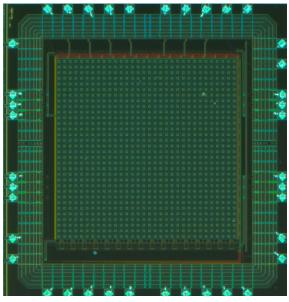

| 3.20 | Layout of the pixel matrix.                                       | 59       |

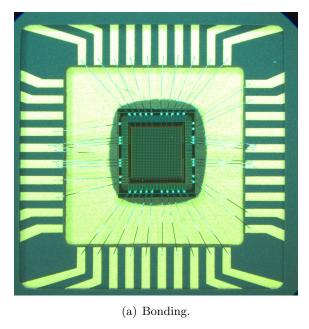

| 3.21 | Bonding diagram                                                   | 60       |

| 3.22 | Microphotographs of the chip                                      | 61       |

| 3.23 | Microphotographs of the chip                                      | 62       |

| 3.24 | Proposal for a different topology for the inhibiting signal path. | 64       |

| 4 1  | Colorting Change Driver (CCD) commendation and an                 | 60       |

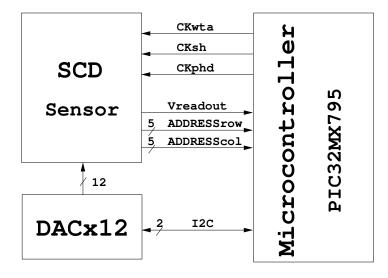

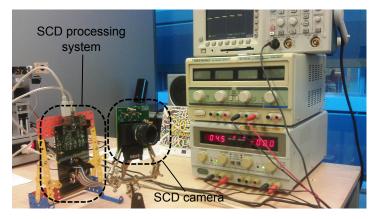

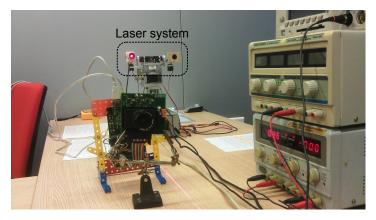

| 4.1  | Selective Change-Driven (SCD) camera and processing system.       | 69<br>70 |

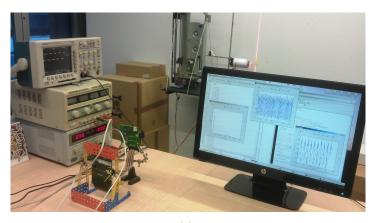

| 4.2  | Experimental set-up.                                              | 70       |

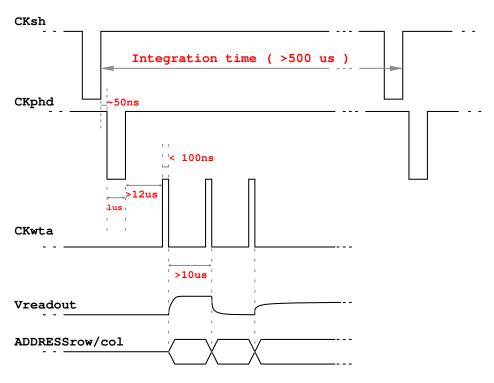

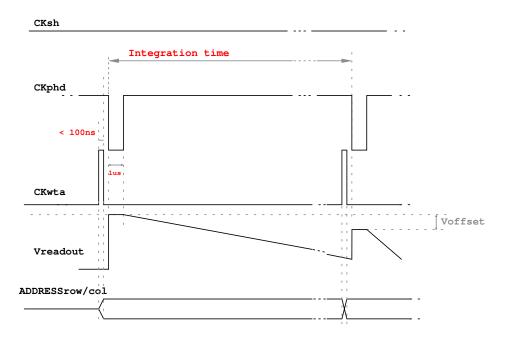

| 4.3  | SCD sensor synchronization.                                       | 71       |

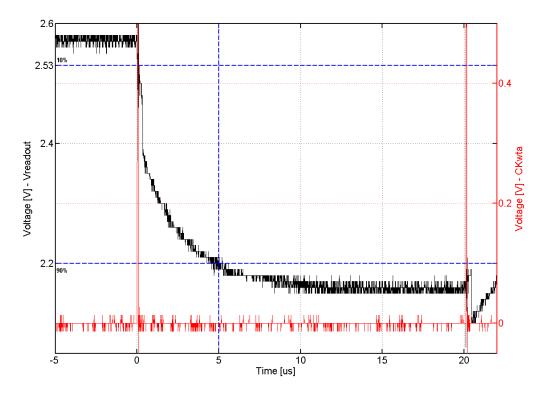

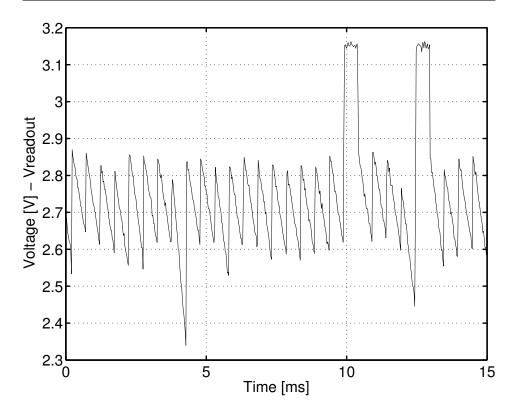

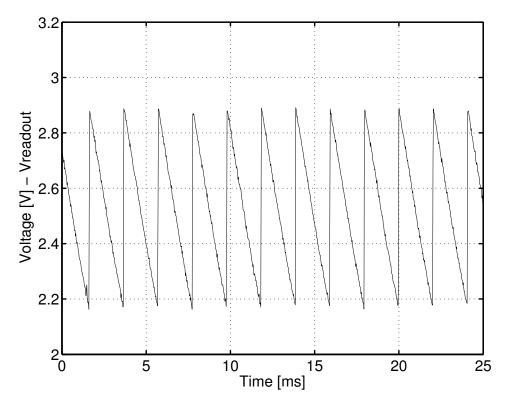

| 4.4  | Gray level output signal.                                         | 72       |

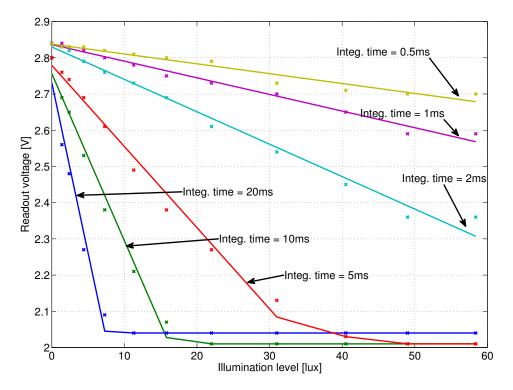

| 4.5  | Sensor output voltage against light intensity for different in-   | 75       |

|      | tegration times.                                                  | 75       |

| 4.6  | Inhibiting logic experiments                                    | 77 |

|------|-----------------------------------------------------------------|----|

| 4.7  | Oscilloscope trace of a WTA error (WTA stage not being          |    |

|      | able to choose a winner)                                        | 78 |

| 4.8  | Histogram of WTA failures (WTA stage not being able to          |    |

|      | choose a winner).                                               | 79 |

| 4.9  |                                                                 | 82 |

| 4.10 | Oscilloscope capture of the Vreadout noise during fixed-        |    |

|      | pattern noise (FPN) measurements.                               | 83 |

| 4.11 | Oscilloscope capture of the Vreadout noise during temporal      |    |

|      | noise measurements                                              | 84 |

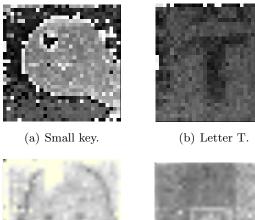

| 4.12 | Images reconstructed with the pixel-flow delivered by the       |    |

|      | SCD sensor                                                      | 85 |

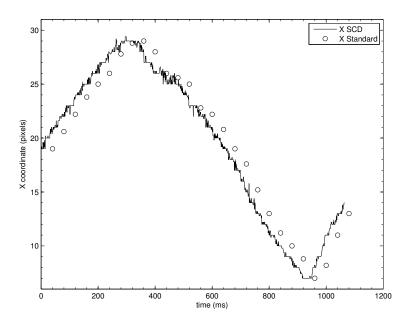

| 4.13 | x coordinate of the laser bar oscillating at 0.8 Hz             | 92 |

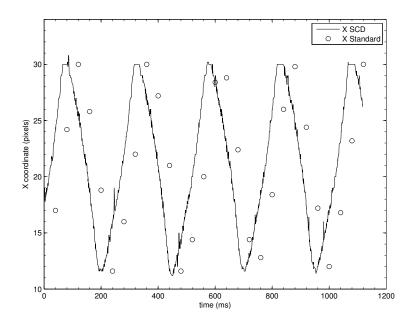

| 4.14 | x coordinate of the laser bar oscillating at 4 Hz               | 94 |

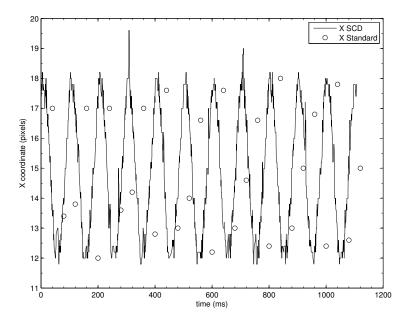

| 4.15 | $x$ coordinate of the laser bar oscillating at 10 Hz $\ldots$ . | 95 |

# List of Tables

| 3.1 | Transistor sizes for the photocircuit and readout subcircuits.  | 32 |

|-----|-----------------------------------------------------------------|----|

| 3.2 | Transistor sizes for the OTA and current rectifier subcircuits. | 38 |

| 3.3 | Transistor sizes for the analogue/digital WTA circuit.          | 45 |

| 3.4 | Pinout of the SCD sensor.                                       | 57 |

| 4.1 | Polarization values used in the testing and measurement pro-    |    |

|     | Cess                                                            | 69 |

| 4.2 | Readout voltages obtained for different integration times and   |    |

|     | light intensities.                                              | 74 |

| 4.3 | Goodness of fit of the measured dynamic range values            | 76 |

| 4.4 | Fixed-pattern noise measurements.                               | 82 |

| 4.5 | Power consumption for several integration times and number      |    |

|     | of transmitted pixels.                                          | 86 |

| 4.6 | Summary of characteristics.                                     | 87 |

| 4.7 | Comparison of three vision systems for simple object tracking.  | 96 |

## Abreviations and achronyms

- **AER** address event representation

- **ADC** analog-to-digital converter

$\mathbf{B}$  blue

**BDJ** burried double junction

**CCD** charge-coupled devices

**CDS** Correlated double sampling

CMOS complementary metal-oxide-semiconductor

**CTIA** capacitive transimpedance amplifier

${\bf DR}\,$  dynamic range

**DVS** Dynamic Vision Sensor

${\bf FBK}\,$  Bruno Kessler Foundation

**FPGA** field-programmable gate array

**FPN** fixed-pattern noise

**GB** green-blue

**I2C** Inter-Integrated Circuit

**INI** Institute of Neuroinformatics

I/O input/output

$\mathbf{MIM}$  metal-insulator-metal

**OTA** operational transconductance amplifier

$\mathbf{PC}$  personal computer

**PCB** printed circuit board

| PIP | polySi-insulator-polySi |  |

|-----|-------------------------|--|

|-----|-------------------------|--|

${\bf PWM}\,$  pulse width modulation

$\mathbf{RG}$  red-green

**RGB** red, green and blue

${\bf SCD}$  Selective Change-Driven

${\bf sDVS}\,$  sensitive Dynamic Vision Sensor

$\mathbf{TCDS}\xspace$  true correlated-double-sampling

${\bf USB}\,$  Universal Serial Bus

${\bf UWB}~{\rm Ultra-Wide-Band}$

$\mathbf{VLSI}\xspace$  very large scale of integration

WSN Wireless Sensor Network

${\bf WSNs}$  Wireless Sensor Networks

$\mathbf{WTA}$  Winner-takes-all

1

Introduction

## Introduction

## 1.1 Motivation and objectives

Traditional frame-based image sensors, frequently called imagers, work under some very well known principles: the illumination level of the surrounding environment is sampled and transmitted at regular time intervals, even if no new information is produced. While this is perfectly suited for many real-world applications such as scanning systems, medical imaging or home video systems, that need accurate, precise and complete information concerning the lighting conditions of the surrounding environment, for other applications, such as artificial vision systems or Wireless Sensor Networks (WSNs), the huge amount of redundant information to be processed and transmitted becomes a crucial limiting factor. Perfected over millions of years of evolution, biological vision systems work on a completely different basis. One of the key features of these systems, is that each sensor cell (pixel) reacts independently and asynchronously to illumination changes. Starting in the late 1980's with Mead and Mahowald's work [1, 2], the last two decades have witnessed significant efforts towards overcoming the limitations of frame-based vision sensors and algorithms - namely by incorporating biological neuromorphic principles into very large scale of integration (VLSI) hardware design. Work such as [2] and [3] pioneered in this field, and together with, [4], [5] and [6] show successful implementations of neuromorphic vision systems. Results in this field clearly show that bandwidth and processing power needs are substantially reduced when neuromorphic principles are applied.

The goal of many of the recent developments in this research field is to mimic, as closely as possible, the behaviour of the biological visual, auditory and cognitive systems by means of advanced silicon technologies (see [2, 4, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 20] amongst many others). Others, have followed a different approach by taking biology as an inspiration but not as an objective (see [5, 21, 22, 23, 24, 25, 26] amongst others).

SCD Vision presented and applied in [27, 28, 29, 30], belongs to this latter group, where biology principles serve as a general guide for VLSI implementation and algorithm design. Its working principle is oriented to fast movement detection and analysis under resource limited conditions. SCD Vision assumes that only part of the image changes between two consecutive snapshots and that the rest of the image remains unchanged. This assumption seems to be especially reasonable for very fast image rates. It, therefore, follows that any video processing algorithm does not need those parts of the image that have not changed at all, because a new result, for a new image, can be obtained just using the past results along with the changes introduced in the new image. Moreover, in all probability, those pixels that have changed little have almost no impact on the result of the processing, so it is possible that they are not needed, at least to some extent, depending on the application. SCD Vision implements these arguments in order to reduce the amount of data to be acquired, transmitted, and therefore processed, thus reducing the hardware required to process video and/or increasing the system's performance (usually both) [27].

As the only transmitted pixels are the ones that show new information catalogued as relevant by a certain criteria, the concept of image, conceived as a complete and static representation of the environment, doesn't seem to be valid any more. Instead, the information is conveyed by a continuous flow of pixels pinpointing relevant parts of the scene. This new, and seemingly much more interesting and useful approach, would require the redesign of many of the traditional computer vision algorithms. Under this new scenario, the data-flow processing paradigm ([31]) would be much more adequate than traditional image-based analysis of sequences.

The main objective of this thesis is to design, implement and test the first VLSI chip following SCD Vision principles. Before the beginning of this research work, the advantages of SCD Vision had only been presented in simulated environments ([27, 28, 29, 30, 32, 33]). A silicon implementation is the necessary and logical step to prove and quantify how much SCD Vision can improve the performance of an artificial vision system in real situations where resources such as bandwidth and processing power are a substantial and important limiting factor. More specifically, the objectives of this research work are:

- To design the first vision chip following SCD principles.

- To implement a complete SCD hardware based on the designed chip. The development of a customized printed circuit board (PCB), firmware, and personal computer (PC) software for data acquisition are needed to fulfil this objective.

- Having fulfilled all the requirements of the previous items, to show, by proper experimentation under real-world scenarios, how an SCD Vision system based on the developed SCD hardware and sensor, is a valid alternative to traditional image-based artificial vision systems. The benefits of this newly implemented system will be properly quantified and analysed.

These objectives pave the way for future developments of SCD dataflow based algorithms and more specific hardware for applications such as WSNs or very fast 3D scanning systems.

#### 1.2 Methodology

From the methodological point of view, the work carried out during this thesis followed a top-down full-custom microelectronic design approach. Any VLSI design must be constructed from a series of specifications. Based on these specifications, the bottlenecks of the real circuit can be identified, and a block diagram of the circuit can be proposed. Proposals for the design of every block can be found in the literature, or, in some cases, can emerge as original contributions during the development of the thesis in the context of the research work.

In the particular case of this thesis, the emphasis is on achieving high frame rates, in the order of 1-2 kfps, and low power consumption. Another important problem to be solved is the comparison block, where the decision whether a pixel should be delivered or not is taken. The circuits that best suit the decision block requirements are analogue [34, 35, 36, 37, 38, 39, 40]. This is the reason why a complementary metal-oxide-semiconductor (CMOS) silicon technology with mixed-signal analogue/digital design options was chosen.

Once the chip was fabricated, a testing plan and validation protocol were followed. Due to the highly customized nature of the chip, a native original testing board, code and protocol were the chosen option.

### 1.3 Organization of the thesis

In order to successfully achieve the goals proposed in Section 1.1, the first step is to carry out an extensive review of the current state-of-the-art in vision circuit design. The outcome of this bibliographical research is reflected in Chapter 2. The large number of vision sensors developed in the last decade shows that this is a very active research field. Although the variety of vision sensing strategies is very wide, they all have the common purpose of reducing the large amount of redundant data to be transmitted and processed.

A complete section of Chapter 2 is dedicated to a detailed explanation of the SCD principles applied to artificial vision systems. The main differences compared to other vision sensing strategies are analysed, and its main advantages in fundamental aspects such as bandwidth occupancy and processing power requirements are discussed.

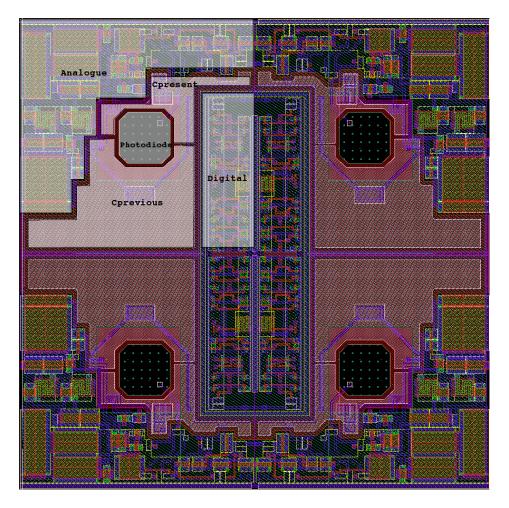

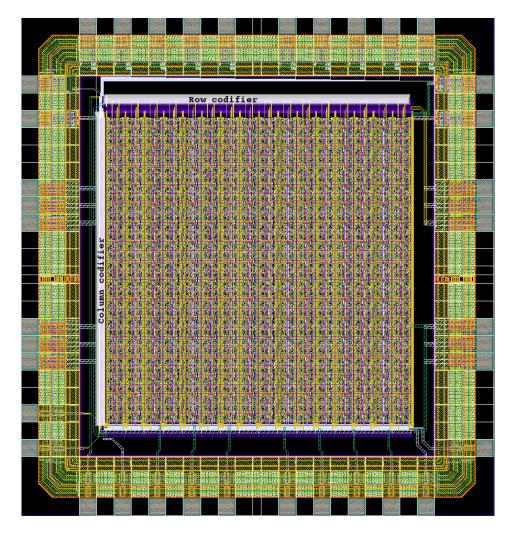

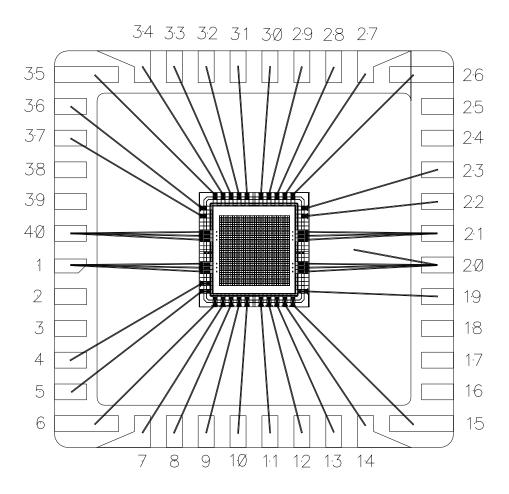

In Chapter 3 an in depth description of the proposed microelectronic VLSI circuit is given. The transistor-level description and the simulated performance of all the building blocks of this novel pixel design are described. The main characteristics of the pixel layout together with a set of microphotographs of the fabricated silicon die are also shown in this chapter.

A description of the experimental set up together with a detailed explanation of the experiments carried out and the results obtained are presented in Chapter 4. In this chapter, the sensor is characterized by its main basic features showing the advantages and drawbacks of this first VLSI SCD silicon implementation. The results of tracking experiments are also presented. These, are clearly oriented to show the advantages of SCD Vision over traditional frame-based artificial vision systems.

Finally, in Chapter 5 the conclusions and future work lines are discussed. New ideas are presented for improving the performance of the SCD pixel. The contributions of this thesis to this research field are also detailed in this chapter.

2

State of the art

## State of the art

Es polivalente en sus aplicaciones; sirve para enmendar a los presos, pero también para curar a los enfermos, para instruir a los escolares, para guardar a los locos, vigilar a los obreros, hacer trabajar a los mendigos y a los ociosos. Es un tipo de implantación de los cuerpos en el espacio, de distribución de los individuos unos en relación con los otros, de organización jerárquica, de disposición de los centros y de los canales de poder...

M. Foucault

## 2.1 General Overview

From an architectural point of view, an artificial vision system is basically composed of a sensor, usually in VLSI CMOS or charge-coupled devices (CCD) technology, and a processing stage. Nowadays, in the vast majority of real-world implementations the sensing part of the system is a framebased imager. As explained in Chapter 1, in the context of artificial vision these types of sensors seem to be very inefficient and very unlike natural visual systems. Even though a new paradigm for vision sensor design was proposed back in 1992 with Mahowald's Ph.D. work [1, 2], in which sparsity, asynchrony and event-driven generation of data were taken into account, most of the efforts in this direction have been concentrated over the last ten years. This is because it was not until the mid or late 1990's, when CMOS technology was mature enough compared to the CCD devices, that CMOS pixel design began to show reasonable and acceptable results [41].

The vision sensors developed in this field in the last decade can be classified in many ways by considering technical aspects, i.e., its synchronous or asynchronous characteristics, the type of implemented photocircuit, whether they deliver grey level values or just spiking events, if they sense and compute temporal contrast, temporal difference, spatial contrast or spatial difference, or many other technical features. Another interesting possibility is to take into account whether the sensors were conceived trying to mimic the biological system (biomimetic design), or they just consider biology as a general inspiration but not as an objective. Biomimetic research aims to open a completely new and cutting-edge way of, not only sensing, but also processing visual information. As asynchrony is one of the most relevant aspects of this trend, completely new processing hardware and algorithmic design is needed under this paradigm. On the other hand, many other research works intend to improve the performance of traditional artificial vision systems in bandwidth and processing power requirements with new sensing strategies developing new VLSI sensors that fit into traditional available processing hardware. As this particular aspect of the vision chips developed in the last decade conditions many of its technical features, this is the classification chosen in this chapter to review some of the most relevant developments in this field.

#### 2.1.1 Biomimetic event-driven vision sensors designs

One of the first relevant works in this field published at the beginning of the 2000's is [16], presented by Culurciello *et al.* in 2003. In this biomorphic arbitrated image sensor the photocurrents are integrated up to a fixed voltage threshold. A spike is generated whenever the integration signal crosses the threshold value; therefore, the magnitude of the photocurrent is inversely

proportional to the interspike interval. Events (spikes) are asynchronously transmitted out of the chip by an arbitration circuit. The original current-feedback event generator used in the photocircuit combines very little power consumption with high slew-rate response. With this strategy, a high dynamic range of 120 dB is achieved when no lower bound condition is placed for the output frequency per pixel. This value changes to 48.9 dB if the pixel update frequency is bounded to 30 Hz. Experimental results showed that the sensor was, at that time, similar to state-of-the-art frame-based CMOS imagers, in terms of speed and power consumption, although further work was needed to obtain similar results in image quality aspects.

In 2004 [12, 13], Zaghloul and Boahen reported an interesting VLSI model of the biological system by incorporating transient and sustained responses, these being characteristics of human vision. This retina performs spatial and temporal filtering adapting to illumination level. However, the performance of this design is severely limited by the FPN problem and its very low dynamic range.

In 2007 [42], a 32x32 pixel-matrix was designed where spatial contrast information was delivered as an address event representation (AER) datastream. The spatial contrast is computed taking into account not only the pixel's photocurrent, but also information coming from neighbouring pixels as well. The most important contribution of this paper is that the local average of the photocurrents from the neighbouring pixels is obtained with very low mismatch via a diffuser network and an original calibration circuit presented by this same group in [43]. The reported 6.6% mismatch value is a remarkable achievement considering the very low level of the photocurrents usually present in this kind of sensors. As the spatial contrast is computed as the ratio of the pixel's illumination value and the average illumination of the neighbouring pixels, the DC value of this magnitude is not zero, so pixels continuously output spikes, even in the absence of new relevant information. This is the main drawback of this design. An alternative design proposed in 2010 [44] overcomes this problem by computing not the ratio, but the difference between the pixel's illumination and the average of its neighbours. This difference is normalized with respect to the ambient illumination level, so the result is ambient-light independent. This chip can also be operated in time-to-first-spike mode.

Amongst the variety of vision chips published in the last decade, what seems to be a milestone in this field is the Dynamic Vision Sensor (DVS) [4] developed at the Institute of Neuroinformatics (INI)<sup>1</sup>. Zürich. The clear intention of this work, presented in 2008, is to mimic, as closely as possible, the sensing stage of the visual biological system. Presented as one of the most relevant outcomes of the CAVIAR project [45], this temporalcontrast vision sensor completely abandons the notion of frames. Each pixel works in a completely independent and asynchronous manner quantizing local relative intensity changes. Every time a pixel detects a certain fixed contrast change, a spike (event) is generated. In order to avoid collisions, a special subcircuit [18, 19, 20] is used to arbitrate the events coming from different pixels. The output of the sensor is an asynchronous stream of pixel addresses configuring an AER of the visual field. This sensor exhibits a 2.1% mismatch in relative intensity event threshold, a dynamic range of 120 dB, a minimum event latency of 15  $\mu$ s and 23 mW of chip power consumption. Although the vast majority of the systems for artificial vision processing are still frame-based, the DVS is being successfully used in many applications nowadays (see [46, 47, 48, 49]).

In 2010, a new version of the DVS pixel, called sensitive Dynamic Vision Sensor (sDVS), was presented in [50]. In this case, events are produced with only a 0.3% contrast in illumination, which represents a marked improvement (about 50 times better) compared to the original DVS design. The main difference compared to the DVS, is that another amplifying stage is introduced at the photodiode node taking advantage of the Miller effect of a PMOS transistor. However, this new design has many problems, such as mismatching, or the gain-bandwidth trade-off of the first amplifying stage, that must be resolved before a pixel matrix can be fully integrated.

In 2011, Leñero-Bardallo *et al.* published a sensor with the same working principles as the DVS but reporting latency as low as 3.6  $\mu$ s [51]. Experiments show that objects and particles rotating at speeds as fast as 10 k revolutions-per-second can be successfully detected and tracked. This improvement is achieved at the expense of increased power consumption, a slightly increased FPN and a reduced intrascene dynamic range of 54 dB (although the overall dynamic range is close to 100 dB).

Recently, in 2011 [52], Posch *et al.* presented a 304x240-pixel AER vision sensor with a remarkable pixel design that outputs not only asynchronous events related to temporal contrast, but also the grey level value of the pixels associated with these asynchronous events. In other words, the

<sup>&</sup>lt;sup>1</sup>http://www.ini.ch

grey level value is asynchronously delivered only for the pixels that changed. The event generation subcircuit is very similar to [4], while the grey level is encoded as a pulse width modulation (PWM) signal. A novel time-domain true correlated-double-sampling (TCDS) technique for obtaining the grey level value [53] yields array FPN smaller than 0.25%.

Other clear examples of biomimetic vision chips can be found in [6, 7, 54, 55].

Efforts are also being made to incorporate the event-based principles to transduce not only intensity, but also colour information. Following the same research and circuit design line of [4], in 2011 [56], Berner et al. achieve dichromatic colour sensitivity in standard 180 nm CMOS technology by means of a properly biased burried double junction (BDJ) to discriminate between incident photons with blue and red spectral characteristics. As the absorption length of incident photons in silicon increases monotonically with wavelength, the shallow junction of the BDJ is more sensitive to bluer light, while the deeper junction shows higher sensitivity in the red band of the spectrum. This same pixel also responds to log monochrome intensity changes. Two different signal pathways are implemented to amplify and integrate colour and intensity information, and different binary events are output responding to changes in wavelength or intensity of incident light. Despite several shortcomings, minutely detailed by the authors in the characterization of the pixel, the presented results show that the pixel responds to light wavelength changes as small as 15 nm, and to relative intensity changes as small as 10%. This promising design seems to point the way for future real-world performance implementations of colour event-based sensors. Also in 2011, another interesting work in this field was presented in [57] by Leñero-Bardallo et al. In this case, three buried junctions are fabricated in a standard 90 nm CMOS process to obtain three stacked photodiodes for separating colour information in three different channels: red-green (RG), green-blue (GB) and blue (B). In each channel, an integrate and fire neuron outputs spiking events; the frequency of these events is proportional to the inverse photocurrent of the corresponding p-n buried junction. A simple algorithm is used to convert pseudo-colour information provided by the sensor into red, green and blue (RGB) representation to be shown on a standard computer screen. Experimentation with the fabricated 22x22 pixel array shows satisfactory preliminary results, although much more work, also in this case, needs to be done to enable real-world

applications.

#### 2.1.2 Other event-driven vision sensing strategies

In the late 1990's, Aizawa et al. presented a CMOS vision sensor with compression capabilities on the image plane [58]. The sensor is based on the so called conditional replenishment algorithm. The sensor has a memory where the last replenished value of every pixel is stored. Current pixel values are compared to those of the last replenished frame. The pixelmatrix is sequentially scanned, and only the values and addresses of the pixels for which the magnitude of this difference is greater than a certain threshold are transmitted. Once a pixel is transmitted, its corresponding value in the frame memory is replenished with the current pixel value. In this work a first 32x32 pixel-matrix prototype is presented. Each pixel includes a memory for the last replenished value and a comparator for the thresholding operation. A second 32x32 pixel-matrix prototype is presented in [59] where the thresholding and comparison functionalities are shared column-wise, in this way the pixel size can be reduced. Despite this new architecture, fill factor is only 1.9%. In both papers, the results show that images are very noisy and any of the silicon prototypes could be used to properly evaluate the advantages of the proposed algorithm.

In 2003, a very interesting chip with image contrast and orientation extraction was reported [5]. Each pixel integrates its photocurrent until a fixed global threshold-voltage is reached. At this moment, a comparison process between neighbouring pixels is fired to compute the contrast magnitude and direction (gradient). As data is transmitted out of the chip in decreasing order according to the contrast magnitude value, the chip first delivers relevant information and can be considered an event-based sensor, although this latter comparison and readout process requires a global chiplevel synchronization similar to frame-based imagers. This sensor exhibits a remarkable dynamic range of 120 dB, detecting contrasts as low as 2% with an error on the orientation value of  $\pm 3^{\circ}$ . This sensor is being successfully used in the automotive industry [60].

The Smart Optical Sensors and Interfaces group  $^2$  at the Bruno Kessler Foundation (FBK)  $^3$  developed several vision sensors clearly oriented to

<sup>&</sup>lt;sup>2</sup>http://soi.fbk.eu/en/home

<sup>&</sup>lt;sup>3</sup>http://www.fbk.eu

WSNs applications. Prior research of this group shows interesting advances in frame-based smart vision sensors by incorporating on-chip image processing tasks (see [61] published in 2005 or [62] published in 2007). In 2009 [22]a novel pixel design for spatial-contrast extraction and binarization with event-based characteristics was presented. This 128x64-pixel-matrix sensor has a frame memory buffer so that the current spatial contrast can be compared against an arbitrary pattern stored in memory. This feature is fundamental for the built-in image processing capabilities of the chip. The sensor can be operated in two different modes: active or idle. In active mode, the matrix is scanned for pixels showing positive or negative differences with respect to the memorized spatial-contrast value. Only when a difference, positive or negative, is found the address of the pixel is latched and transmitted out of the chip. It takes about 150  $\mu$ s to complete the scanning and readout process along the whole matrix. In idle mode, the matrix is scanned and the pixels showing positive or negative differences are counted without delivering any address out of the chip. At the end of the process, the final count is transmitted and used by any external processing as an estimation of the level of activity in the scene under analysis. Depending on the content of the frame buffer, different image processing tasks can be performed: contrast extraction, motion estimation or background subtraction. The measured power consumption is in the order of 100  $\mu$ W when operated with and integration time of 10 ms and 25% of activity in the pixel matrix. Under proper lighting conditions, the integration time can be set down to 100  $\mu$ s, which added to the readout time of 150  $\mu$ s means that the sensor can be operated at a very high frame rate of 4 kfps. In 2011 [63], this sensor was thoroughly studied and characterized as a Wireless Sensor Network (WSN) node, showing that its very low power consumption and adaptability to scene activity make it a highly suitable alternative for this type of applications. This work was complemented, also in 2011, with [64], where a new version of the sensor optimized for a hierarchical energy management strategy is presented and tested.

Another interesting sensor suitable for WSNs applications is described in [25] (2010). The chip operates in three different modes: intensity, temporal difference and spatial contrast. In the first mode, the sensor acts as a traditional imager with Correlated double sampling (CDS) readout, while in temporal difference mode the intensity of the current frame is compared to the one immediately previous to it. An event is produced if the result of this comparison is greater than a certain threshold. In the third mode, using a Winner-takes-all (WTA) circuit, every pixel compares its own intensity value against the intensity value of four of its neighbours, and this information is used to find contours and edges in the scene. As claimed by the authors, the main contribution of this work seems to be the compact implementation of all these three functionalities in a pixel with just 11 transistors. The application of WTA circuits for the inter-pixel intensity comparison task seems to be the key point of this contribution.

In [24] (2012), Chen *et al.* implement a very simple strategy for movement detection. When a new frame is buffered, the pixel matrix is scanned sequentially, and only the pixels that have changed above a certain threshold from one frame to the next one are transmitted, while the information in the remaining pixels is lost. The main advantage of this chip is that incorporates an Ultra-Wide-Band (UWB) transmitter. The experiments presented in [24] indicate a power consumption of 2.4 mW (0.9 mW for the pixel matrix and 1.5 mW for the transmitter) when the pixel matrix runs at 160 fps and the UWB transmitter works at 1.3 Mbps.

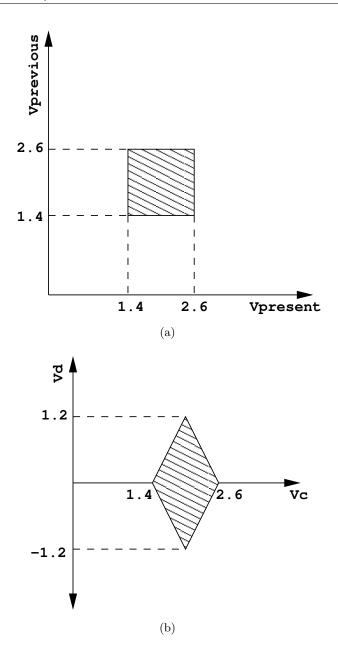

## 2.2 Selective Change-Driven Vision

Like all the sensors and artificial vision strategies described in the previous section, the aim of SCD vision is to reduce the amount of visual data to be transmitted and processed while keeping an accurate representation of the relevant information of the visual field. In SCD vision, events are collected as they are produced and selectively chosen in order of relevance according to the particular addressed problem. Although the SCD concept can be extended to many vision problems, in previous research [27, 28, 29, 32, 33, 65] the focus is on movement detection and analysis. In most movement algorithms, the most important event is the change in illumination level, since it may indicate a change in the scene being processed [66]. It seems that pixels that have undergone larger changes in illumination will offer richer information than others [27, 28] so this is the selective function used in previous SCD work and also applied in this thesis.

The SCD sensor developed in this thesis implements the principles mentioned above in the following way: frames are sequentially and synchronously captured at a very fast rate (1-2 kfps), but pixel readout is performed in a completely new manner. Pixels are now transmitted out of the chip in descending order based on their illumination level difference with respect to the last transmitted value. When a pixel's address and illumination information are transmitted, the illumination value is stored in a memory within the chip so the next forthcoming value can be compared against it. As the ordering criteria takes into account the temporal difference with respect to the last read-out value, and not with respect to the value captured in the preceding frame, if a change in a pixel is not immediately processed because it is less relevant at that moment, there is no problem since it will be processed later when there are less important changes to process. Other state-of-the-art sensors, such as [24, 25], memorize events only from one frame to the next one; this means that if an event is not instantly processed that information is lost and its impact on the result is not calculated. The SCD update mechanism of the memorized grey level value is similar to the conditional replenishment algorithm proposed by Aizawa et al. in 1997 [58, 59]. The main differences are the thresholding operation and the readout sequence criteria: in [58, 59] the pixel matrix is sequentially scanned, while in SCD strategy pixels are ordered by relevance before being read out. According to [67], this SCD VLSI implementation can be classified as a frame-based time-difference sensor.

Although frame-based, this new sensing stage can be thought of as a source of information transmitting a continuous pixel flow, delivering the pixel's position and grey level. The pixel rate can be dynamically adapted to the available processing hardware capabilities and bandwidth resources. If the pixel rate is high, most of the pixels of the sensor are read-out even if they have changed little, but this sensor becomes really interesting when the pixel rate is reduced, even by several orders of magnitude, as it is still possible to obtain good results [68, 69]. It is also possible to keep the same pixel rate as a frame-based camera with traditional sequential readout scheme, but in this case the SCD offers another advantage and this is the possibility of processing information as though it were coming from a high speed camera. In fact, the SCD sensor is internally working at equivalent rates of 1-2 kfps, while the bandwidth requirement can be easily tailored to the available hardware capabilities, whatever they may be. In any case, the sensor is always delivering the pixels that will be of the most help in order to obtain the most accurate results for that bandwidth.

Another important advantage of SCD vision processing is that results of an algorithm are calculated immediately after every pixel. This means that the result latency (time from scene event to algorithm response) can be very short (microseconds) compared to the latency of image processing which usually takes one frame acquisition time (milliseconds). This latency is very important in closed-loop control vision systems. Another advantage is that results are updated for every pixel, yielding a result flow with a much higher temporal resolution than that provided by a standard image processing system [27, 29, 69]. These aspects are very important in ultrahigh speed movement tracking, or closed-loop vision systems.

At a first glance, it seems that keeping the results updated for every pixel can increase the workload, but this is not so for most cases since the same calculations, in a different order and fashion, are performed for every pixel. The only difference is that in the traditional case, we perform the calculation for every pixel in the image after the image has been taken (in a pair of nested loops), and in the other, the calculation is performed on the pixel as it is read-out, no matter in which order (see [28, 70] for an explanation about speeding-up strategies in the processing stages of an SCD systems). This holds for most first-stage algorithms, such as filtering, convolutions, basic object detection, and others. In higher level stages, it is possible to have some extra workload, which must be taken into account, but this can be reduced by smart algorithm tailoring [65].

From the hardware processing point of view, the change in the algorithm implementation does not imply a change in the processing architecture. Nevertheless, SCD vision works on events more than on a static flow of information. It is change-driven based, meaning that a change in illumination may drive the processing to perform. Data flow architectures can take advantage of this data-driven processing. In data flow architectures, it is the incoming data which fires the instruction execution, so there is no program counter but rather a graph of interdependent instructions that are executed when their required data arrive. These architectures are inherently parallel and can be implemented in reconfigurable hardware such as a field-programmable gate array (FPGA) [33].

The main difference between SCD Vision and the biomimetic approach is that in the former it is possible to obtain a constant synchronous pixel flow that can be easily adjusted to standard processing hardware capabilities. In biomimetic artificial vision systems, there is a non-continuous flow of spikes indicating events. In this way, there are time slots with no information to be processed, and other time slots where the pixel flow is so high that the load could collapse any standard processing hardware. Asynchronous biomimetic vision chips require the design of custom specific asynchronous VLSI processing hardware [10, 11, 14, 45, 71, 72]. It seems that approaches like SCD Vision are, at present, much more flexible and much easier to translate into industrial applications.

Complete SCD vision systems, considering the sensing strategy described above followed by a processing stage, have been successfully simulated for optical flow computation, motion detection and tracking algorithms [27, 28, 29, 32, 65]. Real implementations with measured results have been recently published using the VLSI SCD sensor and processing hardware described in the following chapters of this document [68, 69, 70]. These results can be considered as direct and successful outcomes of this thesis.

# 2.3 Conclusions

All the sensors described in the preceding sections of this chapter have the common intention of reducing the huge amount of redundant non-relevant visual information produced by traditional frame-based imagers. Biological vision systems, perfected over millions of years of evolution, efficiently overcome this problem with cellular mechanisms that signal only relevant changing information in the visual field. Therefore, the biological system seems to be the perfect source of inspiration for the design of artificial vision systems. Most of the research and development efforts in this field have been concentrated over the last decade achieving relevant and important results. In many of the leading advances in this area, the focus is on mimicking as closely as possible the main features of the biological system (see Subsection 2.1.1). Other relevant works do not take biology as an objective, but as general guide for their developments by incorporating some of its principles to improve traditional sensing and processing strategies (see Subsection 2.1.2). Amongst this last group, SCD Vision is an interesting and original proposal where a frame-based temporal-contrast smart sensing strategy is used to signal relevant changes in the scene under analysis. This novel vision strategy represents a trade-off between biomimetic frameless designs and traditional frame-based sequential image-based systems. SCD Vision takes advantage of some of the data-reduction and smart-sensing principles of the former ones while presenting a synchronous pixel-flow that can be easily handled by any standard processing hardware. In this chapter, the principles of SCD vision have been explained, showing how an artificial vision system working under this basis, can reduce its bandwidth and processing power requirements while still maintaining accurate results.

# SCD sensor VLSI implementation

3

SCD sensor VLSI implementation

Cuando todo falla, lo único que queda, es pensar.

A. Aguirre

The basics of SCD Vision have been explained, described and analysed in Chapter 1 and Section 2.2. This chapter is dedicated to an in-depth description of the hardware implementation of the principles followed in this thesis.

There are two approaches to producing a camera according to SCD Vision principles. One is to make a custom-integrated circuit sensor, and the other is to construct one from a high-speed camera (>1000 fps), adding the necessary processing hardware to deliver a customizable number of pixels from frame to frame, starting with the pixel that has undergone the largest change since the last time it was read out in descending order. One of the main objectives of SCD Vision is to work on resource-limited systems (especially limited in size, power, or processing capabilities) and also embedded systems, so this second approach hardly fits in with this objective, because of the power, space, and performance requirement just for the camera itself. The custom sensor seems more appropriate for this

objective, but it is more complex, initially expensive, and it is very difficult to produce a high-end product at the first attempt, especially in such an unexplored area. Nevertheless, a 32x32 SCD CMOS vision sensor has been designed and tested. In this chapter an in-depth description of this first silicon implementation of SCD principles is given. The sensor has been designed and fabricated using 4-metal 2-poly 0.35  $\mu$ m austriamicrosystems' fabrication process.

# 3.1 Working principles

The SCD vision sensor developed in this thesis follows a temporal contrast strategy: successive snapshots of the environment are taken at a fast pace and pixels are selectively transmitted out of the chip in descending order per their illumination level difference with respect to their last transmitted value. When a pixel's address and illumination information are transmitted, the illumination value is stored in an internal pixel memory so that the next forthcoming value can be compared against it. Following this strategy, pixel readout frequency can be adapted to bandwidth availability. In the worst case scenario, one single pixel per captured frame is transmitted, this being the one with the largest illumination change in the entire scene.

For the silicon implementation of such a strategy, every pixel would require two memory elements: one for storing the last read out illumination level, and another memory element for the present one. The difference between the present and the previous illumination levels is physically represented as the output current of a wide-input-range OTA [73]. Another subcircuit is needed to select the maximum amongst all these currents. WTA circuits are a widely used solution in situations where a single winner has to be selected from a group of current or voltage competing values (see [74, 75, 76, 14] amongst many others). If we picture a WTA circuit as a black box, we can see that a set of currents is taken as input, and a set of voltages is produced as output. Every output voltage is associated with a single input current. Ideally, the output voltage associated to the highest input current should be well differentiated from the rest. According to the current polarities in our light sensing circuit, the winning pixel should output a voltage close to 0 V while the losers' output should be close to Vdd.

Given the always-limited discrimination ability of the WTA circuit, a large number of pixels increases the probability of having a certain number of cells competing with equal credentials. Therefore, multiple winners can be observed at the output nodes of the WTA amplifiers. To cope with this scenario, as one of the contributions of this thesis, a digital logic based on the propagation of vertical and horizontal inhibition signals has been proposed in [77]. Following a predefined path across the pixel matrix, inhibition signals are propagated so when the first winning output is found, the following outputs in the propagation path are forced to be close to Vdd. In favour of saving silicon area at the pixel level, only horizontal inhibition signals are used in this particular work; but the general idea of the inhibiting mechanism remains the same.

As soon as a single winner is selected, the output of the WTA digital logic activates the row and column address codifiers. In this way, the address of the pixel together with the captured grey level can be read out.

A block diagram of the circuit can be seen in Fig. 3.1. The rest of this chapter is dedicated to a detailed description of the different circuit blocks.

# 3.2 Circuit description

## 3.2.1 Light sensing and readout subcircuit