# HIGH PERFORMANCE ARCHITECTURE USING SPECULATIVE THREADS AND DYNAMIC MEMORY MANAGEMENT HARDWARE

Wentong Li

Dissertation Prepared for the Degree of DOCTOR OF PHILOSOPHY

UNIVERSITY OF NORTH TEXAS

December 2007

#### APPROVED:

Krishna Kavi, Major Professor and Chair of the Department of Computer Science and Engineering Phil Sweany, Minor Professor

Robert Brazile, Committee Member

Saraju P. Mohanty, Committee Member

Armin R. Mikler, Departmental Graduate Coordinator

Oscar Garcia, Dean of College of Engineering

Sandra L. Terrell, Dean of the Robert B.

Toulouse School of Graduate Studies

Li, Wentong, <u>High Performance Architecture using Speculative Threads and Dynamic</u>

<u>Memory Management Hardware</u>. Doctor of Philosophy (Computer Science), December 2007, 114 pp., 28 tables, 27 illustrations, bibliography, 82 titles.

With the advances in very large scale integration (VLSI) technology, hundreds of billions of transistors can be packed into a single chip. With the increased hardware budget, how to take advantage of available hardware resources becomes an important research area. Some researchers have shifted from control flow Von-Neumann architecture back to dataflow architecture again in order to explore scalable architectures leading to multi-core systems with several hundreds of processing elements.

In this dissertation, I address how the performance of modern processing systems can be improved, while attempting to reduce hardware complexity and energy consumptions. My research described here tackles both central processing unit (CPU) performance and memory subsystem performance. More specifically I will describe my research related to the design of an innovative decoupled multithreaded architecture that can be used in multi-core processor implementations. I also address how memory management functions can be off-loaded from processing pipelines to further improve system performance and eliminate cache pollution caused by runtime management functions.

Copyright 2007

by

Wentong Li

#### ACKNOWLEDGMENTS

I would like to express my gratitude to my advisor, Dr. Krishna Kavi, for his support, patience, and encouragement throughout my graduate studies. It is not often that one finds an advisor who always finds the time for listening to the little problems and roadblocks that unavoidably crop up in the course of performing research. I am deeply grateful to him for the long discussions that helped me sort out the technical details of my work. I am also thankful to him for encouraging the use of correct grammar and consistent notation in my writings and for carefully reading and commenting on countless revisions of this manuscript. His technical and editorial advice was essential to the completion of this dissertation.

My thanks also go to Dr. Saraju Mohanty and Dr. Phil Sweany, whose insightful comments and constructive criticisms at different stages of my research were thought-provoking and helped me focus my ideas.

I would like to thank Dr. Naghi Prasad and Mr. Satish Katiyar for their supports, kindly reminding and encouragements during the writing of this dissertation.

Finally, and most importantly, I would like to thank my wife Liqiong, my son Colin and my daughter Sydney. They form the backbone and origin of my happiness. Their love and encouragement was in the end what made this dissertation possible. I thank my parents, Yong and Li, my father-in-law Duanxiang for their faith in me and unconditional support.

# CONTENTS

| ACKNOWLEDGMENTS                                       | iii |

|-------------------------------------------------------|-----|

| LIST OF TABLES                                        | vii |

| LIST OF FIGURES                                       | Х   |

| CHAPTER 1. INTRODUCTION                               | 1   |

| 1.1. Dataflow Architecture                            | 2   |

| 1.2. Scheduled Dataflow Architecture                  | 2   |

| 1.3. Thread-Level Speculation                         | 3   |

| 1.4. Decoupled Memory Management Architecture         | 4   |

| 1.5. My Contributions                                 | 4   |

| 1.6. Outline of the Dissertation                      | 5   |

| CHAPTER 2. SURVEY OF RELATED WORKS                    | 6   |

| 2.1. SDF-Related Dataflow Architectures               | 6   |

| 2.1.1. Traditional Dataflow Architectures             | 6   |

| 2.1.1.1. Static Dataflow Architecture                 | 7   |

| 2.1.1.2. Dynamic (Tagged-Token) Dataflow Architecture | 7   |

| 2.1.1.3. Explicit Token Store Dataflow Architecture   | Ö   |

| 2.1.2. Hybrid Dataflow/Von Neumann Architecture       | 11  |

| 2.1.3. Recent Advances in Dataflow Architecture       | 11  |

| 2.1.3.1. WaveScalar Architecture                      | 12  |

| 2.1.3.2. SDF Architecture                             | 13  |

| 2.1.4. Multithreaded Architecture                     | 13  |

| 2.1.4.1. Multiple Threads Using the Same Pipeline     | 13  |

| 2142 Multiple Pipelines                               | 1.5 |

| 2.1.4.3. Multi-Core Processors                               | 17 |

|--------------------------------------------------------------|----|

| 2.1.5. Decoupled Architecture                                | 17 |

| 2.1.6. Non-Blocking Thread Model                             | 18 |

| 2.2. Thread-Level Speculation                                | 18 |

| 2.2.1. Single Chip TLS Support                               | 19 |

| 2.2.2. TLS Support for the Distributed Shared Memory System  | 22 |

| 2.2.3. Scalable TLS Schemas                                  | 23 |

| CHAPTER 3. SDF ARCHITECTURE OVERVIEW                         | 25 |

| 3.1. SDF Instruction Format                                  | 25 |

| 3.2. SDF Thread Execution Stages                             | 25 |

| 3.3. Thread Representation in SDF                            | 27 |

| 3.4. The Basic Processing Units in SDF                       | 28 |

| 3.5. Storage in SDF Architecture                             | 31 |

| 3.6. The Experiment Results of SDF Architecture              | 31 |

| CHAPTER 4. THREAD-LEVEL SPECULATION (TLS) SCHEMA FOR SDF     |    |

| ARCHITECTURE                                                 | 35 |

| 4.1. Cache Coherency Protocol                                | 35 |

| 4.2. The Architecture Supported by the TLS Schema            | 36 |

| 4.3. Cache Line States in Our Design                         | 38 |

| 4.4. Continuation in Speculative SDF Architecture            | 39 |

| 4.5. Thread Schedule Unit in Speculative Architecture        | 40 |

| 4.6. ABI Design                                              | 41 |

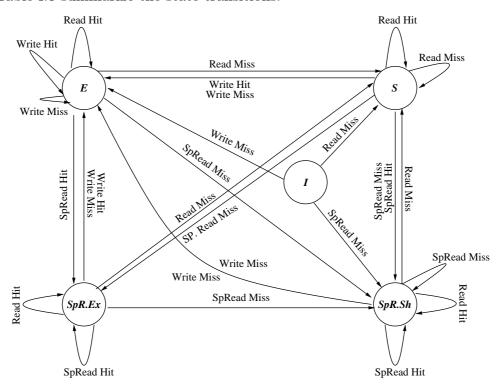

| 4.7. State Transitions                                       | 42 |

| 4.7.1. Cache Controller Action                               | 43 |

| 4.7.2. State Transitions According to the Processor Requests | 43 |

| 4.7.2.1. Invalid State                                       | 43 |

| 4.7.2.2. Exclusive State                                     | 44 |

| 4.7.2.3. Shared State                                        | 44 |

| 4.7.2.4. Sp.Exclusive State                                  | 44 |

|                                                              |    |

| 4.7.2.5. Sp.Shared State                                  | 45 |

|-----------------------------------------------------------|----|

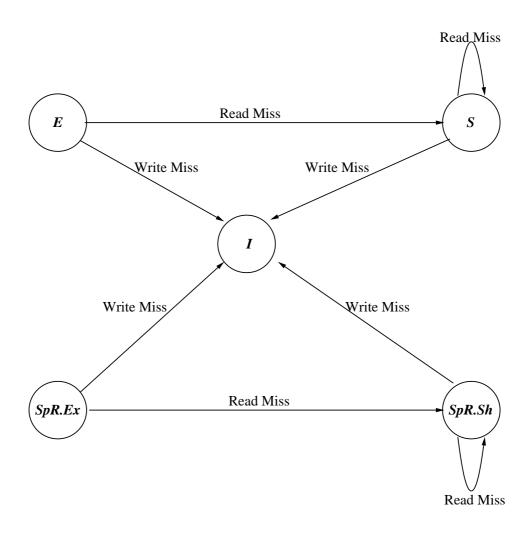

| 4.7.3. State Transitions According to the Bus Requests    | 46 |

| 4.7.3.1. Shared State                                     | 47 |

| 4.7.3.2. Sp.Shared State                                  | 48 |

| 4.7.3.3. Exclusive State                                  | 48 |

| 4.7.3.4. Sp.Exclusive State                               | 48 |

| 4.8. ISA Support for SDF architecture                     | 49 |

| 4.9. Compiler Support for SDF Architecture                | 50 |

| CHAPTER 5. SDF WITH TLS EXPERIMENTS and RESULTS           | 51 |

| 5.1. Synthetic Benchmark Results                          | 51 |

| 5.2. Real Benchmarks                                      | 55 |

| CHAPTER 6. PERFORMANCE OF HARDWARE MEMORY MANAGEMENT      | 58 |

| 6.1. Review of Dynamic Memory Management                  | 58 |

| 6.2. Experiments                                          | 59 |

| 6.2.1. Simulation Methodology                             | 59 |

| 6.2.2. Benchmarks                                         | 60 |

| 6.3. Experiment Results and Analysis                      | 62 |

| 6.3.1. Execution Performance Issues                       | 62 |

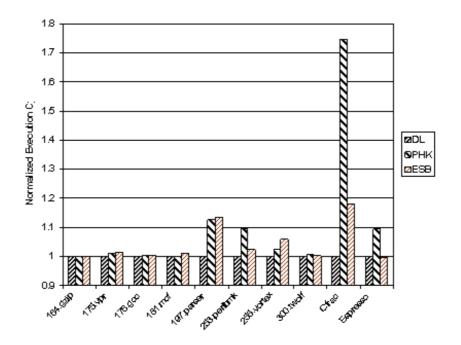

| 6.3.1.1. 100-Cycle Decoupled System Performance           | 62 |

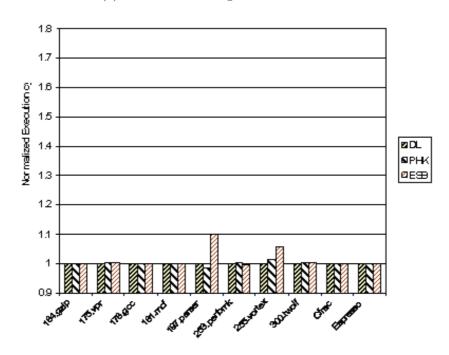

| 6.3.1.2. 1-Cycle Decoupled System Performance             | 64 |

| 6.3.1.3. Lea-Cycle Decoupled System Performance           | 65 |

| 6.3.1.4. Cache Performance Issues                         | 66 |

| CHAPTER 7. ALGORITHM IMPACT OF HARDWARE MEMORY MANAGEMENT | 69 |

| 7.1. Performance of Different Algorithms                  | 71 |

| CHAPTER 8. A HARDWARE/SOFTWARE CO-DESIGN OF A MEMORY      |    |

| ALLOCATOR                                                 | 77 |

| 8.1. The Proposed Hybrid Allocator                        | 79 |

| 8.2 Complexity and Performance Comparison                 | ۷1 |

| 8.2.1. Complexity Comparison                         | 81 |

|------------------------------------------------------|----|

| 8.2.2. Performance Analysis                          | 82 |

| 8.3. Conclusion                                      | 85 |

| CHAPTER 9. CONCLUSIONS AND FUTURE WORK               | 86 |

| 9.1. Conclusions and Contributions                   | 86 |

| 9.1.1. Contributions of TLS in dataflow architecture | 86 |

| 9.1.2. Contributions of hardware memory management   | 87 |

| 9.2. Future Work                                     | 87 |

| BIBLIOGRAPHY                                         | 89 |

# LIST OF TABLES

| 3.1 | SDF versus VLIW and Superscalar                                                   | 33 |

|-----|-----------------------------------------------------------------------------------|----|

| 3.2 | SDF versus SMT                                                                    | 34 |

| 4.1 | Cache Line States of TLS Schema                                                   | 38 |

| 4.2 | Encoding of Cache Line States                                                     | 39 |

| 4.3 | Encoding of Cache Line States                                                     | 43 |

| 4.4 | State Transitions Table for Action Initiated By SP (Part A)                       | 46 |

| 4.5 | State Transitions Table for Action Initiated By SP (Part B)                       | 47 |

| 4.6 | State Transitions Table for Action Initiated By Memory                            | 48 |

| 5.1 | Selected Benchmarks                                                               | 55 |

| 6.1 | Simulation Parameters                                                             | 61 |

| 6.2 | Description of Benchmarks                                                         | 62 |

| 6.3 | Percentage of Time Spent on Memory Management Functions                           | 63 |

| 6.4 | Execution Performance of Separate Hardware for Memory Management                  | 63 |

| 6.5 | Limits on Performance Gain                                                        | 65 |

| 6.6 | Average Number of Malloc Cycles Needed by Lea Allocator                           | 66 |

| 6.7 | L-1 Instruction Cache Behavior                                                    | 67 |

| 6.8 | L-1 Data Cache Behavior                                                           | 67 |

| 7.1 | Selection of the Benchmarks, Inputs, and Number of Dynamic Objects                | 71 |

| 7.2 | Number of Instructions(Million) Executed by Different Allocation Algorithms       | 72 |

| 7.3 | Number of L1-Instruction Cache Misses(Million) of Different Allocation Algorithms | 73 |

| 7.4 | Number of L1-Data Cache Misses(Million) of Different Allocation Algorithms        | 73 |

| 7.5 Execution Cycles of Three Allocators          | 74 |

|---------------------------------------------------|----|

| 8.1 Comparison of Chang's Allocator and my Design | 81 |

| 8.2 Selected Benchmarks and Ave. Object Sizes     | 83 |

| 8.3 Performance Comparison with PHK Allocator     | 83 |

# LIST OF FIGURES

| 2.1 Block Diagram of Dynamic Dataflow Architecture                                    | 8  |

|---------------------------------------------------------------------------------------|----|

| 2.2 ETS Representation of a Dataflow Program Execution                                | 10 |

| 2.3 Block Diagram of Rhamma Processor                                                 | 18 |

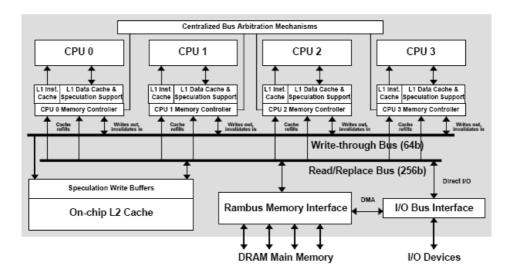

| 2.4 Architecture for SVC                                                              | 20 |

| 2.5 Block Diagram of Stanford-Hydra Architecture                                      | 21 |

| 2.6 Example of MDT                                                                    | 22 |

| 2.7 Block Diagram of Architecture Supported by Steffan's TLS Schema                   | 23 |

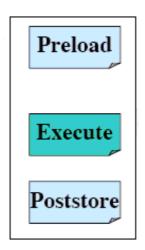

| 3.1 Code Partition in SDF Architecture                                                | 26 |

| 3.2 An SDF Code Example                                                               | 27 |

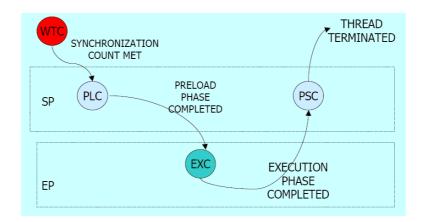

| 3.3 State Transition of the Thread Continuation                                       | 28 |

| 3.4 SP Pipeline                                                                       | 29 |

| 3.5 General Organization of the Execution Pipeline (EP)                               | 29 |

| 3.6 Overall Organization of the Scheduling Unit                                       | 30 |

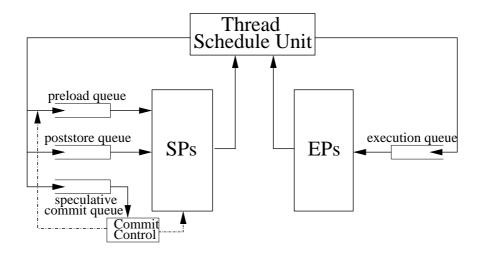

| 4.1 Architecture Supported by the TLS schema                                          | 37 |

| 4.2 Overall TLS SDF Design                                                            | 41 |

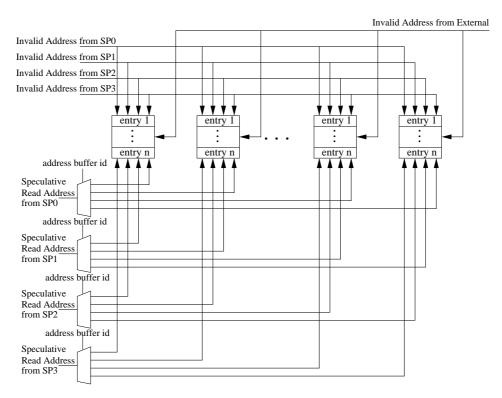

| 4.3 Address Buffer Block Diagram                                                      | 42 |

| 4.4 State Transitions for Action Initiated by SP                                      | 45 |

| 4.5 State Transitions Initiated by Memory                                             | 49 |

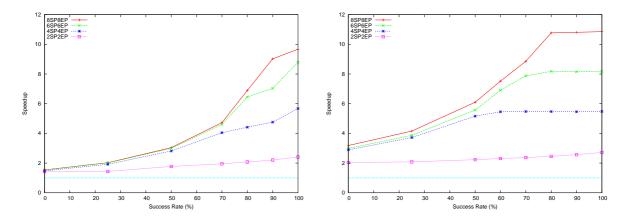

| 5.1 The Performance and Scalability of Different Load and Success Rates of TLS Schema | 52 |

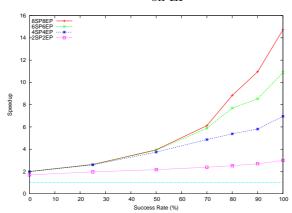

| 5.2 Ratio of Instruction Executed EP/SP                                               | 53 |

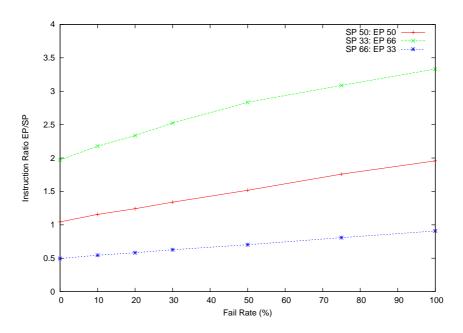

| 5 3 Normalized Instruction Ratio to 0% Fail Rate                                      | 53 |

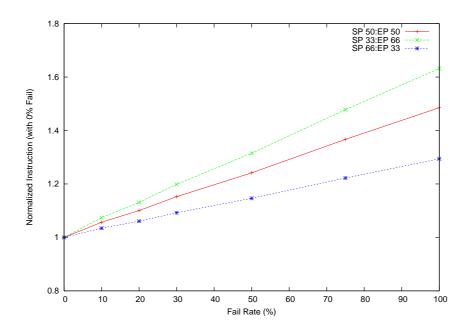

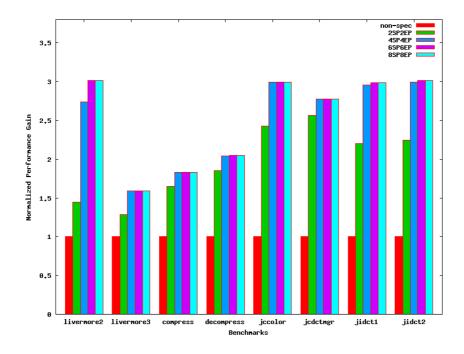

| 5.4 | Performance Gains Normalized to Non-Speculative Implementation                 | 56 |

|-----|--------------------------------------------------------------------------------|----|

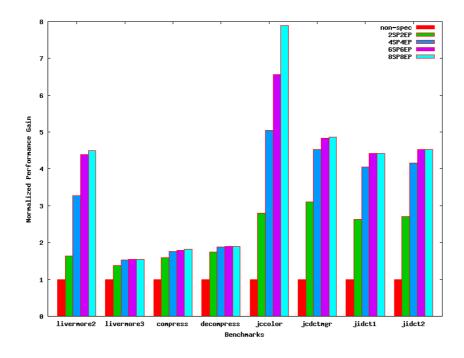

| 5.5 | Performance Gains Normalized to Non-Speculative Implementation                 | 57 |

| 7.1 | Performances of Hardware and Software Allocators                               | 75 |

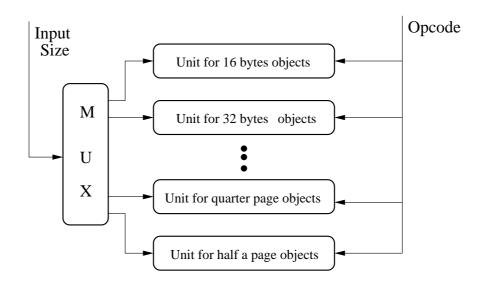

| 8.1 | Block Diagram of Overall Hardware Design                                       | 80 |

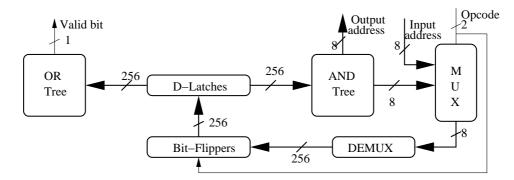

| 8.2 | Block Diagram of the Proposed Hardware Component (Page Size 4096 bytes, Object |    |

|     | Size 16 bytes)                                                                 | 80 |

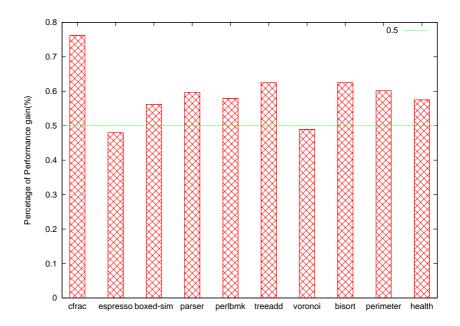

| 8.3 | Normalized Memory Management Performance Improvement                           | 84 |

#### CHAPTER 1

#### INTRODUCTION

Conventional superscalar architecture - based on the Von-Neumann execution model - has been on the main stage of commercial processors (Intel, AMD processors) for the past twenty years. The Von-Neumann architecture uses a program counter (PC) to control the execution of a program based on the control flow graph.

The superscalar architecture exploits the data independence at the instruction level and allows more than one instruction to be issued out-of-order in every clock cycle. The superscalar architecture dedicates a large amount of hardware to branch prediction, aggressive out-order-issue instructions, speculative instruction execution, etc., to get more instructions executed per cycle (IPC). It also utilizes a very deep pipeline to achieve a high clock rate. It has been shown that performance improvement diminishes by simply increasing the clock rate, or increasing the instruction scheduling window size with additional hardware resources in the superscalar architecture paradigm.

With the advances in VLSI technology, hundreds of billions of transistors can be packed into a single chip. With the increased hardware budget, how to take advantage of available hardware resources becomes an important research area. Some researchers have shifted from control flow Von-Neumann architecture back to dataflow architecture again in order to explore scalable architectures leading to multi-core systems with several hundreds of processing elements.

In this dissertation, I address how the performance of modern processing systems can be improved, while attempting to reduce hardware complexity and energy consumptions. My research described here tackles both central processing unit (CPU) performance and memory subsystem performance. More specifically I will describe my research related to the design of an innovative decoupled multithreaded architecture that can be used in multicore processor implementations. I also address how memory management functions can be off-loaded from

processing pipelines to further improve system performance and eliminate cache pollution caused by runtime management functions.

#### 1.1. Dataflow Architecture

Dataflow architecture is a drastically different architecture from the current Von-Neumann architecture. An application can be translated into a data flow graph, which is a directed graph. The nodes in the data flow graph represent the instructions and the arcs in the data flow graph represent the data dependences between the instructions.

The execution of the dataflow architecture is only driven by the availability of the input operands. Once an instruction has all its inputs, it can be fired. The firing of an instruction will consume the input data (operands) and will generate the output operands. Since the conditions of an instruction that can be executed in the dataflow architecture are only dependent on data availability, dataflow architecture can easily exploit parallelism at the instructional level. Due to this fine-grained parallelism that can easily be exploited in dataflow architectures, the parallelism is much larger than that of the Von-Neumann model.

Dataflow architecture is a very powerful alternative to the current architecture. However, pure dataflow architecture, which requires a large amount of hardware such as the number of the functional units, communication bandwidth, and the operand matching hardware, is too complex to be implemented cost effectively.

To reduce the hardware requirement of pure dataflow architecture, some researchers proposed hybrid dataflow/Von-Neumann architecture. In such architectures, a dataflow graph is statically partitioned into subgraphs. These subgraphs are executed in a data flow order, but the instructions within subgraphs are executed sequentially. By doing this, the enormous scheduling and communication overheads are saved.

# 1.2. Scheduled Dataflow Architecture

Scheduled dataflow architecture (SDF) is a further enhancement of the hybrid dataflow and Von-Neumann architecture. The subgraphs of a data flow graph are transformed into threads. An application is partitioned into multiple threads with multiple contexts. A thread can be fired when all its inputs are available. Therefore, SDF exploits the thread level parallelism (TLP) inherent in the dataflow graph.

In modern processors, the CPU clock rate is much higher than the memory speed. The access times and I/O bandwidth did not improve with the processor clock rate. The gap between the processor speed and the memory speed has widened. One way to tolerate the long latency memory operation in modern computer systems is to perform a context switch. The hardware or the operating system swaps out the task that waits for the memory operation and schedules another ready task to run. Another approach to alleviate the memory gap is to use decoupled architecture. The main feature of decoupled architecture is separation of the memory access from the execution. In this type of architecture, there are two sets of different processing elements, one for the memory access and one for the execution. SDF architecture also incorporates this feature into its architecture design. SDF architecture also uses a non-blocking thread execution model to achieve a clean separation of memory access from execution.

This architecture differs from other multi-threaded architectures in two ways: 1) the programming paradigm is based on the dataflow, which eliminates the need for runtime scheduling, reducing the hardware complexity significantly and 2) complete decoupling of the memory access from the execution pipeline.

## 1.3. Thread-Level Speculation

With the advances in compiler technology in recent years, compiler-driven code parallelization has advanced significantly. Thread-level parallelism is the key to achieving high performance for today's multi-core architectures. Unfortunately, there are still a large set of applications that cannot be parallelized due to the inability to determine data dependences or control dependences at compiling time. These types of programs are very common in many application domains, like sparse matrix computations, molecular biology, image processing, etc. Furthermore, the loops in these applications are repeated for a large number of iterations with only a few data dependences across the loop iterations.

Thread-level speculation (TLS) is a technique which enables compilers to aggressively parallelize applications despite data or control dependences. In architectures with TLS support, the hardware takes the responsibility to check the dependence violations, and recover from the violations to guarantee the correct execution result. Due to the dataflow languages

are not commonly used, one has to compile the programs written in imperative languages like C/C++. These programming languages generally have no consideration of parallel dataflow programming paradigms. TLS support in SDF architecture will improve the compiler's ability to generate parallel threads, even with undetermined dependencies, to achieve a better execution performance.

# 1.4. Decoupled Memory Management Architecture

The second part of this dissertation research investigates efficient memory management needed in modern computing systems. Dynamic memory management is traditionally implemented as library functions within system's runtime library. The memory management functions execute in different logical slices of the applications. They rarely interfere with the applications except receiving parameters and returning values. But they compete for the cache and CPU resources, with the application. By off-loading the memory management functions from the CPU, the cache contentions can be reduced and the memory management performance will be improved.

#### 1.5. My Contributions

In this dissertation, I propose a scalable thread-level speculation schema along with an architecture design for the scheduled dataflow architecture. This is the first work to propose a TLS schema in a hybrid dataflow architecture. Compared with the existing TLS schema, my design has the advantage of low hardware cost, and does not need any OS level support. I also model the performance of SDF architecture with TLS support using synthetic benchmarks. I compare the performance of TLS schema with the results reported by other researchers using selected benchmarks to show that thread-level speculation is more effective in SDF architecture. In my view, the beauty of the proposed TLS model and its hardware realization lies in its simplicity and clarity. I evaluated the performance impacts of hardware memory management in conventional architecture. I also proposed a hybrid hardware/software memory management implementation which can improve the performance of memory intensive applications by 23% with a small amount of hardware.

## 1.6. Outline of the Dissertation

The dissertation can be divided into two parts: the thread-level speculation (TLS) of SDF described in chapter 2 through chapter 5, and the hardware memory management described in chapter 6 through chapter 8. The dissertation is organized as follows: Chapter 2 will review SDF related dataflow architectures and architectures supporting thread level speculation; Chapter 3 will introduce SDF architecture in more detail; Chapter 4 will present my TLS schema; Chapter 5 will provide experimental results, analyses and comparisons with the results from other researchers; Chapter 6 will demonstrate the performance impacts of hardware memory management; Chapter 7 will compare the performance of different memory management algorithms; Chapter 8 will show a hybrid memory management unit design; and Chapter 9 will summarize contributions and some of the future improvements that can be applied to enhance the performance of my TLS schema.

#### CHAPTER 2

# SURVEY OF RELATED WORKS

This survey includes two parts: the first refers to SDF-related dataflow architectures, and the second refers to thread-level speculation-related architecture (TLS).

#### 2.1. SDF-Related Dataflow Architectures

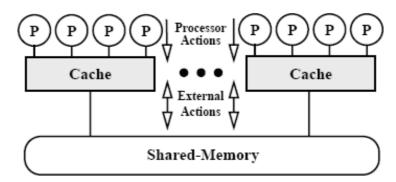

SDF architecture has the following characteristics: it is a, multi-threaded hybrid dataflow/Von-Neumann architecture, which decouples memory accesses and execution, and uses a non-block thread model. In this section, I will review works in traditional dataflow architecture, multi-threaded architecture, hybrid dataflow architecture, recent advances in dataflow architecture, decoupled architecture, and the non-blocking thread model.

#### 2.1.1. Traditional Dataflow Architectures

The dataflow computing model was developed by Dennis and Misuanas[22] in the early 1970s. Instruction execution in dataflow architecture is based on the availability of input data. An instruction can be fired when all its inputs are available. Multiple instructions can be fired at the same time if sufficient resources are available. Dataflow architecture can easily achieve maximum instruction-level parallelism possible. The synchronization for parallel execution in the dataflow architecture is implicit (data availability). Single assignment languages and notions, such as SISAL[11], VAL[1] and Id[38], were developed during the same period. In conjunction with the dataflow architecture, anti-dependences (write after read) and output dependences (write after write) are handled elegantly. It seems very promising that this new architecture will deliver high parallelism machine. However, the architecture's performance as implemented is not as expected. This is partly due to the fact that VLSI technology was not mature at the time these architectures were implemented (in the 1970s and 1980s). Other limitations of the model include: 1) excessively fine-grained thread parallelism, 2) the fact that it's very hard to integrate high speed storage (like registers and caches) into this architecture, and 3) asynchronous triggering of instructions [47][48][70][72][66].

There are three main architectures based purely on the dataflow principle: Static (Single-Token-Per-Arc) Dataflow architecture, Dynamic (Tagged-Token) Dataflow architecture, and Explicit Token Store (ETS) architecture. The following sections describe some of these architectures.

#### 2.1.1.1. Static Dataflow Architecture

In the static dataflow model, programs are represented as a collection of templates. A template contains the operation code, operand slots, and destination address fields. Destination address fields refer to the operand slots in subsequent templates that receive the results. Once the destination template receives a token, it needs to give an acknowledgment, which doubles the traffic. The instructions are fired when all the operands are available. Since only one set of operands can be held with each instruction template, the loop iterations can not be parallelized in this architecture. Architectures based on this model are: the MIT Static Dataflow Machine[22], the LAU in France, the DDMI at the University of Utah (1978), and the Texas Instrument DDP (1979).

# 2.1.1.2. Dynamic (Tagged-Token) Dataflow Architecture

Dynamic (Tagged-Token) dataflow architecture allows subprograms and loop iterations to proceed in parallel. A token consists of a tag and associated data. Each tag is composed of a PE number (to determine which processing element it refers to), context field t (uniquely identifying the context), initiation number i (identifying the loop iteration), and instruction address n. It also has a port number since the destination instruction may need more than one input. For example, a token can be defined as  $\langle t.i.ni, data \rangle p$ . Port p represents left or right. If it is a simple token without identifying loop iteration, t is the tag itself. If the tags are attached to the tokens, they allow multiple tokens to reside on the arc and the architectures supporting such tokens are called dynamic (Tagged-Token) dataflow architectures. When identical tags are present on all input arcs (indicating a complete set of operands for a specific context and loop iteration), the node can be enabled or fired. There are two units, known as the matching unit and the execution unit, which are connected by an asynchronous pipeline with queues to balance the load variations. The execution tags.

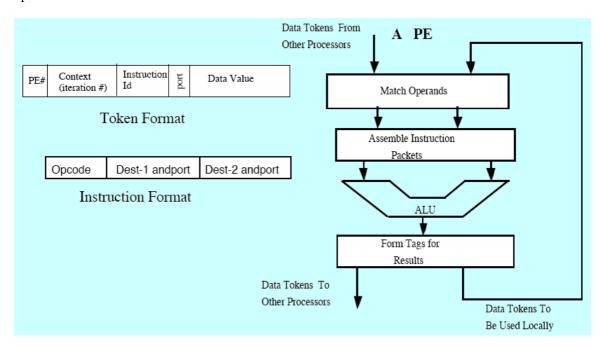

Data dependencies are translated into tag matching and transformation. The tag contains information about the destination context and how to transform the tag to achieve results. In order to support token matching, some form of associative memory, such as real memory with associative access, a simulated memory based on hashing, or a direct-matched memory, is required. The figure 2.1 below shows a block diagram, tag format, and token format of this particular architecture.

FIGURE 2.1. Block Diagram of Dynamic Dataflow Architecture

Dynamic dataflow unfolds much more parallelism than the static dataflow model. However, the large number of tokens waiting to be matched increases the size and complexity of the associative memory. Arvind et al. first proposed I-structure [8] [7], but it was simultaneously discovered by Watson and Gurd at the University of Manchester [77]. I-structure in dataflow can be viewed as a place to store structures, arrays, or indexed data using single-assignment rules. Each element of an I-structure can be read many times, but can only be written once. Each element is associated with status bits and a queue of deferred reads. The status can be defined as PRESENT (data ready), ABSENT (data not ready), and WAITING (data not ready, but with at least one deferred read). Three operations can be performed on the I-structures: I-allocate (allocation space for I-structure), I-fetch (to retrieve the contents; if the data is not ready, the read is deferred), and I-store (to write the contents). The I-fetch

instruction is executed in split phases, which means that the read request issued is independent in time from the response. It does not cause the issuing PE to wait for a response. The main drawback of this dynamic dataflow architecture is that the amount of memory needed to store tokens waiting for a match tends to be very large. To overcome this, the technique of hashing is used, which is not as fast as associative memory. Several dynamic dataflow machines have been constructed, including: 1) the MIT Tagged-Token Dataflow architecture [7], 2) the Manchester Dataflow Machine [36], 3) the Distributed Data-Driven Processor (DDDP) from OKI Electric Ind. (Japan) [49], 4) the Stateless Dataflow Architecture (SDFA) designed at the University of Manchester [23], and 5) the Data-Driven VLSI Array (DDA) designed by Technion (Haifa, Israel) [51].

# 2.1.1.3. Explicit Token Store Dataflow Architecture

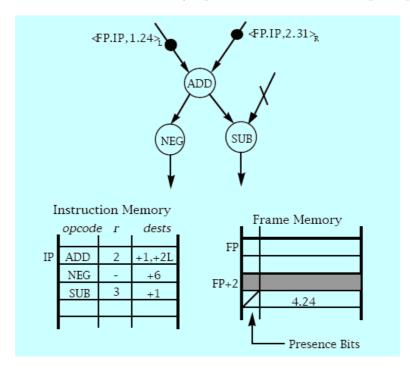

The explicit token store (ETS) concept was proposed in order to overcome the draw-backs associated with token matching using associative memory or hashing. ETS uses direct matching of operands (or tokens) belonging to an instruction. In a direct matching schema, storage (called a frame) is dynamically allocated for all the tokens needed by the instructions in a code block. A code block can be viewed as a sequence of instructions comprising a loop body or a function. The actual disposition of locations within a frame is determined at compile time; however, the actual allocation of frames is determined at run time. In a direct matching schema, any computation is completely described by a pointer to an instruction (IP) and a pointer to a frame (FP). The pair of pointers, <FP, IP>, called a continuation, corresponds to the tag part of a token. A typical instruction that an IP points to specifies an opcode, an offset in the frame where the match of input operands for that instruction will take place, one or more displacements (destinations) that define the destination instructions to receive the result token(s), and the input port (left/right) indicator that specifies the appropriate input arc for a destination instruction.

When a token arrives at a node (e.g. ADD in Figure 2.2), the IP part of the tag points to the instruction that contains an offset r as well as displacement(s) for the destination instruction(s). The actual matching process is achieved by checking the slot availability in the frame memory at FP+r. If the slot is empty, the data value from the token is written

to the slot and its presence bit is set to indicate that the slot is full. If the slot is already full (indicating a match of input operands), the value is extracted, leaving the slot empty, and the corresponding instruction is executed. The resulting token(s) generated from the operation is communicated to the destination instruction(s) by updating the IP according to the displacement(s) encoded in the instruction (e.g., execution of the ADD operation produces two result tokens <FP.OP+1,3.55>. Instruction execution in ETS is asynchronous since an instruction is enabled immediately upon the arrival of the input operands.

FIGURE 2.2. ETS Representation of a Dataflow Program Execution

MIT and Motorola jointly built the Monsoon explicit token store machine in 1990 [20][60]. The Monsoon PE used an 8-stage pipeline. The first stage is the instruction fetch. The second stage is the effective address generation, which consists of three pipeline stages. The execution stage consists of three pipeline stages, while the final stage comprises the token-form stage. The ETS model is also applied in other machines such as the EM-4 and Epsiln-2[34].

# 2.1.2. Hybrid Dataflow/Von Neumann Architecture

Even though dataflow architecture provided the natural elegance of eliminating outputdependencies and anti-dependencies, it performed poorly with sequential code. In an eightstage pipeline machine such as the Monsoon, an instruction of the same thread can only be issued to the dataflow pipeline after the completion of its predecessor instruction. In addition, the token matching and waiting matching store introduced more pipeline bubbles or stalls into the execution stage(s) of the dataflow machines. In order to overcome these drawbacks, some researchers proposed a hybrid of dataflow/control-flow models along with a multithreaded execution. In such models [59][41], several tokens within a dataflow graph are grouped together as a thread to be executed sequentially under its own private program counter control, while activation and synchronization of threads are data-driven. Such hybrid architectures deviate from the original dataflow model, where the instructions fetch data from memory or registers, instead of having instructions deposit operands (tokens) in "operand receivers" of successor instructions. In such hybrid models two key features that support these types of architectures are: sequential scheduling and the use of registers for buffering the results between instructions. Examples of such hybrid models are: the threaded abstract machine (TAM) [19], P-RISC [59] and Star-T [4].

# 2.1.3. Recent Advances in Dataflow Architecture

Due to the drawbacks listed in the section 2.1.1, dataflow architectures did not reach commercial success. With advances in VLSI technology, the gap between the wire-delay relative to the switching speed and the exponential cost of the circuit complexity make a simple scaling up of existing processor designs futile [2]. Effectively translating the hardware budget into performance becomes a new challenge. Multithreaded model is becoming a preferred possible solution to this problem. Since dataflow model presents a clean model for multithreading, many researchers are shifting their interests back to dataflow architecture again.

There are two new architectures based on the dataflow concept: WaveScalar [69] architecture from the University of Washington and SDF[32] architecture.

## 2.1.3.1. WaveScalar Architecture

WaveScalar architecture integrates the idea of computation in memory (cache) and dataflow computing. The goal of WaveScalar is to minimize the communication cost between processors and memory. The key difference between WaveScalar and the previous dataflow architectures is that it supports traditional memory semantics.

WaveScalar instructions are cached and executed by an intelligent, distributed instruction cache - the WaveCache. The WaveCache loads instructions from the memory and assigns them to a processing element for execution. These instructions will reside in the WaveCache for multiple invocations. A WaveScalar binary is the data flow graph in executable format. It resides in the memory as a collection of intelligent instruction words.

The core of WaveScalar architecture is the WaveCache. A WaveCache is a grid of 2K (2048) processing elements (PEs) arranged into clusters of 16 PEs. Each PE contains the logic of the instruction placement and execution, input and output queues for instruction placement and execution, communication logic, and function units (integer and floating). Each PE can hold eight different instructions; a total of 16,000 instructions can be kept in cache. The instruction placement is dynamic based on the resource availability. And when an instruction is loaded, the destination field of an instruction is modified accordingly.

The WaveScalar compiler breaks the control flow graph of an application into waves. A wave has the following properties: 1) each instruction in a wave only executes once in a round, 2) the instructions are partially ordered, and 3) there is no control-flow within a wave. In WaveScalar,  $\phi$  functions [18] are used to address the control dependences between waves. In this architecture, every data value carries a tag. The wave numbers are used to differentiate the data between dynamic waves. A special instruction, "WAVE\_ADVANCE", is used to manage wave numbers. This architecture assumes the wave number computation is very simple and can be combined with other instructions, for example, the ADD-WITH-WAVEADVANCE. The key feature of WaveScalar is that wave number management can be entirely distributed and under software control, whereas tag generation in traditional dataflow architecture is only partially distributed.

Unlike traditional dataflow architecture, WaveScalar does not use I-structure memory. The memory ordering problem is solved by the compiler's insertion of the annotation < pred, this, suc> tuples into the load and store instructions. Pred is the sequence number of the predecessors, this is the sequence number of this node, and suc is the sequence number of the successor. In case of ambiguous dependences, the compiler will insert a '?' as a wildcard in the annotation.

The weakness of this architecture is that it moves the complex communication between instructions in traditional superscalar from the reservation stations to the PEs, and does not reduce the number of actual communications needed, as it claims: the architecture makes communications explicit between them. The other drawback is that the utilization of PEs (not functional units) is very low. The utilization of PEs is only 0.01% from the data provided [69]. One must conclude that today's technology cannot meet the requirements of WaveScalar.

#### 2.1.3.2. SDF Architecture

SDF is one type of hybrid architecture that tries to use relatively simple hardware to achieve high performance, and to utilize the hardware more efficiently. The features of SDF architecture include decoupling and non-blocking multithreading. And SDF architecture is very flexible; one can choose the number of PEs according to different types of applications.

A detailed introduction to SDF architecture can be found in chapter three.

#### 2.1.4. Multithreaded Architecture

There are several types of multithreaded architecture, which can be divided into three categories: multiple threads that share the same pipeline, multiple pipelines that share the same register files or L1 cache, and multi-core, chip-microprocessors (CMP).

#### 2.1.4.1. Multiple Threads Using the Same Pipeline

This type of architecture has only one pipeline, but the hardware can explicitly support more than one thread (the hardware keeps multiple contexts). This kind of architecture falls into one of two categories depending on whether the instructions are issued from only a single thread or from multiple threads in a given cycle. In simultaneous multithreading (SMT) and other interleaving architectures [74][3] instructions are issued from multiple threads to the pipeline during the same cycle.

Simultaneous multithreading (SMT) is an extension of mainstream superscalar architecture, which allows multiple independent threads to issue multiple instructions during each clock cycle to a superscalar pipeline. The Intel Hyper-Threading processor is an implementation of the SMT architecture. SMT simultaneously uses the thread-level parallelism and instruction-level parallelism by running multiple tasks on a superscalar processor at the same time. The entire active contexts in the SMT architecture will compete for resources at each clock cycle. The primary changes in SMT architecture from the conventional superscalar processor are the differences in the instruction fetch and register renaming mechanism. The fetch stage needs to fetch instructions from multiple instruction streams, which will incur extra overheads, so the fetch stage of SMT architecture has to be further divided into multiple stages. After the instructions are fetched from different contexts, the renaming register mechanism maps the architectural registers into the machine's physical registers. SMT architecture requires more physical registers than what a superscalar architecture does. Due to the large renaming register file size, the renaming of the register will take extra cycles. After register renaming, the instructions are combined into a single instruction stream in an instruction queue waiting for schedule. Because the different instruction streams do not have dependencies among them, it is possible to issue more instructions (higher ILP) in a single cycle. SMT improves the throughputs of the threads and utilizes hardware resources (functional units) more efficiently than superscalar. But SMT also increases the contention for resources including the branch predictor, and caches. Some studies show that this architecture is not very scalable in terms of the number of threads due to the contentions of these resources [39][40].

Tera utilizes a single pipeline by interleaving the execution of the instructions from different threads to hide the memory latency and the pipeline stalls due to data dependencies. The Tera computer does not include a cache. Each memory access takes 70 cycles but using the 128 hardware threads that can be supported, Tera aims to hide the memory latency since instructions from other threads are interleaved with the memory access instructions of a thread.

# 2.1.4.2. Multiple Pipelines

Multiple pipelines architecture has multiple pipelines layout on a single chip. Multiscalar [67], Superthreaded [73] architecture, and TRIPS [64] are examples of this architecture.

Multiscalar Architecture

A Multiscalar processor resembles multiple pipelines, but with a single logical register file that is implemented with physical copies in parallel processing units. In the Multiscalar architecture, the static program is partitioned into sequential "tasks". A task may be a basic block, a number of connected basic blocks, a number of loop iterations, a function call, or any combination thereof. The compiler is responsible for marking task boundaries, but it need not have full knowledge of inter-task or intra-task dependences. Dependences are implied by normal sequential execution semantics, as in conventional architectures. Load balance, i.e. choosing tasks of roughly equivalent size, is one of the important design considerations.

The control unit of the Multiscalar processor executes the program binary by processing each task as a single unit. Upon encountering each task, it predicts the subsequent task (by keeping a record of past history in a manner similar to dynamic branch prediction). Then the task is assigned to one of the parallel processing units. Consequently, the control unit scans the program (speculatively) by taking large steps, one task at a time, not pausing to look at any of the individual instructions within a task (including branches that may be contained within a task). The multiple processing units fetch and execute instructions from each of the assigned tasks in parallel. The result is that many instructions are executed per clock cycle.

Each task consumes and produces values that are bound to architectural registers and memory locations. Because of the natural sequential ordering of tasks, a value that a task consumes must be a value from an (earlier) task that produces it. Although copies are physically distributed, the register file has the appearance of a single, conventional file. When a register value is produced by one task and consumed by another, later task, the value must be conveyed to the physical register file in the later task (and all tasks in between). This is accomplished by the compiler and hardware. In a MultiScalar processor, tasks complete by committing their state changes (to registers and memory) in the same order in which they

were assigned to processors. This can only happen when the task has completed execution and when any predicted branch prior to the beginning of the task has been resolved.

Superthreaded Architecture

Superthreaded architecture has multiple processing elements (PEs) connected to each other in a unidirectional ring. Each processing element has a private instruction-level cache and a private memory buffer to cache speculative stores and to support run time data dependency checking. The PEs share the L-1 data cache and unified L-2 cache, as well as a register file and lock register.

This architectural model adopts a thread pipelining execution model that allows threads with data dependences and control dependences to be executed in pipelined fashion. The basic idea of thread pipelining is to compute and forward recurrence data and possible dependent store addresses to the next thread as soon as possible, so the next thread can start execution and perform run time data dependence checking. Thread pipelining also forces contiguous threads to perform their memory write-backs in order, which enables the compiler to fork threads with control speculation. With run time support for data dependence checking and control speculation, the Superthreaded architectural model can exploit loop-level parallelism from a broad range of applications.

#### TRIPS

TRIPS is a tile-based architecture. Each TRIPS core contains four processors. These processors share instruction caches and data caches, which are connected to processors through intelligent communication tiles.

Each processor contains 16 PEs (tiles). The PEs are connected in a grid fashion by an intelligent communication channel and share common register files. All the PEs contain an integer ALU and a floating point ALU, but each PE has it own reservation stations.

The compiler will partition the programs into blocks of the same size. A block is spawned as a thread for execution. Once a thread is scheduled, the instructions within the block will be placed over all the 16 PEs in a processor and the execution will be based on the dataflow model of that block.

TRIPs can be configured to support up to eight threads from the same task. The synchronization of the eight threads is through the register files and reservation stations, but these

threads must commit their results in the order of their spawning. TRIPS also can be configured to support four tasks with two threads from each task. By using dataflow execution within a thread, TRIP can utilize the fine-grained instruction-level parallelism (D-morph). And a processor can support multiple threads so that it also capitalizes on thread-level parallelism (T-morph). By the grid connection of the PEs with an intelligent communication channel, the data exchanges between neighboring PEs are greatly improved (S-morph). Because of these three properties, TRIPS is called a processor design with polymorphism for different applications.

#### 2.1.4.3. Multi-Core Processors

When CMOS technology scales down in size, more and more transistors can be packed onto a single chip. Multiple independent cores, each representing a complete CPU, can be placed on a single chip with inter-core communication channels. Multi-core processors offer an immediate and cost-effective way to solve today's processor design challenge. There are several multi-core processors, like the Intel DUO and AMD Dual Core, which are already commercially available.

#### 2.1.5. Decoupled Architecture

J.E. Smith [65] proposed a decoupled memory access and execution architecture that requires a compiler to explicitly slice the program into a memory access slice and a computational slice. The two slices would run on a different processing elements and a synchronization mechanism would be needed to guarantee the correct execution.

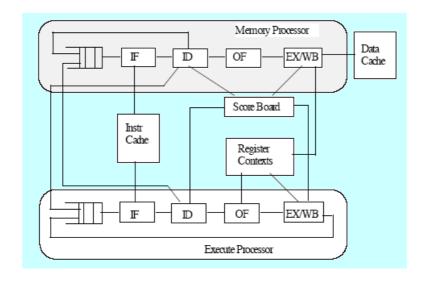

Rhamma [35] is a decoupled multi-threaded architecture that implements decoupled memory access and execution. Rhamma uses two separate pipelines: a memory access pipeline and an execution pipeline. A program interleaves on both pipelines during execution according to the instruction type. While a program running on the execution pipeline encounters a memory access instruction, a context switch will be generated and the program moved from the execution pipeline to the memory access pipeline. And when the memory access pipeline decodes a non-memory access instruction, a context switch will cause the thread to move back to an execution pipeline. The following figure 2.3 shows a block diagram of the Rhamma machine.

FIGURE 2.3. Block Diagram of Rhamma Processor

# 2.1.6. Non-Blocking Thread Model

A non-blocking thread proceeds to evaluation as soon as all input operands are available. It completes execution without blocking the processor due to the synchronization of threads. Thread context switching is controlled by the compiler with the means of generating new threads rather than blocking a thread for synchronization. It will reduce the synchronization overhead. The disadvantage of this model is that it tends to generate more fine-grained threads, which will in turn may increase the overhead.

The Cilk run-time environment [10] is a typical example of a non-blocking multi-threaded system.

#### 2.2. Thread-Level Speculation

With the advances in compiler technology in recent years, compiler-driven code parallelization has advanced significantly. Thread-level parallelism is the key to achieving high performance for today's multi-threaded architectures. Unfortunately, there are still a large set of applications that cannot be parallelized due to the ambiguous data or control dependences. Those dependences are too complicated for the modern compiler to analyze. And those dependences are very common in many application domains, like sparse matrix computations, molecular biology, image processing, etc. Furthermore, the loops in these applications are repeated for a large number of iterations with only a few data dependences across the loop iterations in actual execution.

Thread-level speculation (TLS) is a technique which enables compilers to aggressively parallelize applications despite data or control dependences between the resulting thread. In architectures with TLS support the hardware assumes responsibility of checking dependence violations and recovering from the violations to guarantee the correct execution result.

TLS support can be partitioned into three categories according to the architecture: TLS support on a single chip, TLS support on a distributed system, and TLS support on both a single chip and distributed system.

## 2.2.1. Single Chip TLS Support

Marcuello et. al. [57] proposed a multi-threaded micro-architecture that supports speculative thread execution within a single processor. The micro-architecture of a speculative multi-threaded processor (SM) consists of several thread units (TU) that execute the different threads of a program in parallel. TUs are connected using ring topology.

Each thread unit has its own physical registers, register map table, instruction queue, functional units, local memory, and reorder buffer. The loops are captured by the hardware to automatically generate parallel threads. Control speculation is used in two levels, one for the parallel loop generation, and the other for the branches. Initially, there are no speculative threads. When the non-speculative threads start a new iteration of a loop, a number of speculative threads are created and allocated to execute the subsequent iterations. When a speculative thread reaches the end of its iteration, it is suspended and waits to commit or be squashed. After the non-speculative thread is committed, the speculative thread of the next iteration either becomes non-speculative or squashed.

Data dependences across iterations can be categorized as either register dependences or memory dependences. The register dependences are solved by a loop iteration table, which records the detailed value changes of a register in that iteration. The memory dependences are solved by a multi-value cache. For each address, the multi-value cache holds the iteration number, data value, and a flag indicating whether the data value has been produced. The data is loaded or stored by that iteration. If the earlier iteration updates an address in the multi-value cache that is labeled and read by a later iteration, the multi-value cache will generate a dependency violation and the later iteration will be squashed and re-executed.

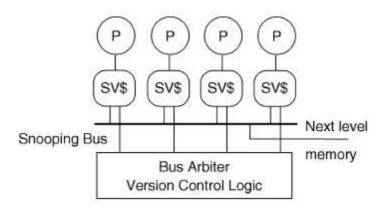

Multiscalar uses a centralized ARB (Address Resolution Buffer) [31], which is similar to a multi-value cache to support thread-level speculation. Each load will update the ARB states and each store will check the buffer to guarantee that there are no memory dependency violations while a thread commits. Because the multi-value cache and ARB are centralized, they may become the bottleneck of the system. Speculative versioning cache [33] is an attempt to distribute the centralized ARB to each processing unit in order to avoid the delay caused by serializing the operations on the ARB. The speculative versioning cache provides a private cache for each processing unit. The system is similarly organized to a snooping bus-based cache coherent symmetric multiprocessor (SMP). The architectural organization is as Figure 2.4:

FIGURE 2.4. Architecture for SVC

There are two additional fields added to each speculative versioning cache line. One is the L bit; the other is the pointer field. The L bit is set when a task loads from a line before storing it to the line. If the L bit is set it means that there is a potential memory dependency violation. The pointer field is used to store the L1 cache that contains the next copy, which forms a distributed versioning ordering list (VOL). The requested hit on the private cache will not generate an additional request to the version control logic. The cache misses will issue a bus request, which is snooped by all the caches, and the version control logic will use the information from the VOL to form the appropriate response. When a task commits, all dirty lines in its private cache will write back to the memory and other lines are invalidated. When a task is squashed, all the lines in the cache are invalidated. The cache coherence schema used in speculative versioning cache is an extension of an invalidate-based

write-back cache coherence protocol. Instead of running this protocol on an SMP system, it runs between tightly coupled PEs.

Stanford Hydra [37] is a CMP system which supports the TLS execution. The CMP contains four MIPS processors. Figure 2.5 shows the design of Hydra.

FIGURE 2.5. Block Diagram of Stanford-Hydra Architecture

Each of these four CPUs has a speculative coprocessor. The coprocessor will set up the speculative context and copy the register file to a Register Passing Buffer. This architecture also utilizes a variation of the invalidate-based write-back cache coherence protocol to detect data cache access violations. There are two sets of bits with each L1 data cache line to support the TLS execution.

The first set of bits includes a modified bit and a pre-invalid bit for invalidating a cache line. The modified bit is used to buffer the speculative memory state. By using the write-back protocol, the modified data will also be put on the bus with its sequence number. Only the CPUs that are running speculative threads will update its local cache. Once the pre-invalid bit is set, it means a speculative thread has modified this line. This bit is used to delay invalidating this cache line until a speculative thread has been assigned to the CPU. The second set of bits includes a read bit and a write bit used to detect the data dependency violation of the speculative threads. These two bits are designed to allow gang-clearing(invalid all the cache line accessed by this speculative thread in once) when a thread is either squashed or restarted. A read bit set means the thread has read this data. Once a

write from a less speculative thread is seen on the bus, the cache will generate a dependency violation and it will cause the speculative thread to be squashed. This bit set means that the thread has generated a local version of the address referenced.

Krishnan et al. [52] proposed a schema that supports the TLS execution using an memory disambiguation table (MDT) to solve the ambiguous memory dependences. The MDT is similar to a directory in a conventional shared-memory multiprocessor system. Figure 2.6 shows an example of MDT. The assumption is that each processor has a private L1 cache and a shared L2 cache. The MDT is integrated with the shared L2 cache. MDT keeps entries on a per memory-line basis and maintains information per word basis. For each word, the MDT keeps a load bit and a store bit for each processor. When a thread is initialized on a processor, all its LOAD bits and STORE bits are cleared. As the thread executes, the MDT works like a directory that keeps tracking which processor shared which words. By doing this, MDT can find the violation of the memory accesses.

| Valid | Address Tag | Load Bits (Word 0) | Store Bits (Word 0) |

|-------|-------------|--------------------|---------------------|

|       |             | $L_0L_1L_2L_3$     | $S_0S_1S_2S_3$      |

| 1     | 0x1234      | 0 0 1 0            | 0 1 0 0             |

| 0     | 0x0000      |                    |                     |

|       |             |                    |                     |

| 1     | 0x4321      | 0 0 1 1            | 0 1 0 0             |

FIGURE 2.6. Example of MDT

#### 2.2.2. TLS Support for the Distributed Shared Memory System

Zhang et al. [81] proposed a schema that supports speculative thread execution in large-scale distributed shared memory (DSM) systems by extending the directory-based cache coherence protocol. This schema partition the loop iterations into read-first iteration or writing iteration based on the non-privatization, blocked privatization, advanced privatization, and blocked advanced privatization algorithm in compile time. The directory controller will create a undo log of the memory accessed by these threads. Once the directory-controller detects a memory access violation, it will invalid the speculative threads and recover the correct memory state according to the undo log. These schema requires the speculative thread to commit in order of their iteration number.

#### 2.2.3. Scalable TLS Schemas

Cintra et al. [16] proposed a TLS schema that supports CMP and a large-scale DSM system. This schema extends the MDT schema for the CMP, described in section 2.2.1. For each node of CMP, there is a local MDT (LMDT) table, the same as the MDT in [52]. For the whole DSM system, there is a global memory disambiguation table (GMDT). The GMDT is distributed to all the nodes in the system as the directory. GMDT keeps the memory information on a per cache-line basis instead of a per word basis, such as in the MDT. In this architecture the threads assigned to each node must be in batch mode (or a chunk), so the GMDT can view the chunk of threads on a node as one speculative job, thus the design of GMDT can be greatly simplified. The GMDT uses a ring structure to perform the chunk-to-node mapping. As the driving force of the execution, at least one chunk is non-speculative in the system.

Instead of squashing one thread as in the Zhang et al.[81], the GMDT squashes a chunk of threads at one time. All the GMDTs synchronize in a barrier to ensure the integrity of the system.

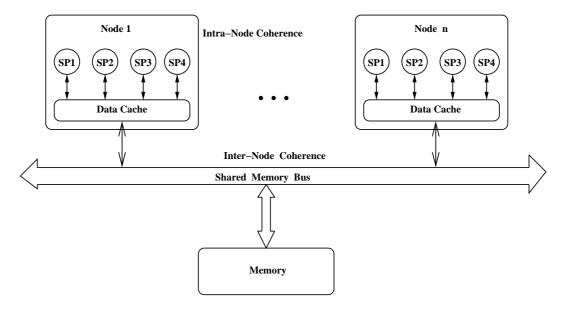

Steffan et al. [68] proposed a TLS architecture that is built upon a write-back invalidation-based cache coherence protocol. This design uses the single-chip multiprocessor or simultaneous multi-threaded processors as the building block. The base architecture is as Figure 2.7:

FIGURE 2.7. Block Diagram of Architecture Supported by Steffan's TLS Schema

This schema depends on the speculative threads committing based on their logical or program order. An epoch number is used to define the logical order of the threads. It adds the

speculative-exclusive (SpE) state to define the speculative-modified data, and speculative-shared state to define the speculatively read data. To define a speculative thread context, the following resources are needed: epoch number, cancel handler address, violation handler address, violation flag, logic late mask, replication of the SL and SM bits from cache, and an ownership buffer (ORB), which is used to record the address of the data that was speculatively modified by this line. The paper does not mention how the thread context is maintained. It can be maintained by hardware, but how to implement this hardware with very low overhead will be another challenge. Or if it is maintained by an operating system, this will result in very slow memory access for speculative threads.

This work is most closely related to ours. The difference between my work and Steffan's is that his work is based on conventional architecture, while my work is based on dataflow/Van Neumann hybrid architecture. If provide a set of fully implementable hardware design that supports thread-level speculation in SDF architecture. This design has a very low hardware complexity. All the speculative stores will be buffered in the registers instead of in the ORB, as they do in their architecture. This hardware does not need any help from operating systems.

#### CHAPTER 3

#### SDF ARCHITECTURE OVERVIEW

SDF architecture applies the dataflow model on a thread-level granularity, instead of on the fine-grained instruction-level like conventional dataflow architectures. SDF architecture is a decoupled architecture that separates memory access from the main execution pipeline to further tolerate the latency of memory access by overlapping the memory access with the execution. SDF architecture also utilizes the non-blocking thread model to reduce the context switching cost.

#### 3.1. SDF Instruction Format

Unlike conventional dataflow architecture, SDF instructions within a thread are executed in a control-flow manner with a private program counter that is associated with each thread. The instruction format of SDF architecture is very similar to the MIPS instruction format. Most instructions in SDF have two source operands and one destination operand like MIPS instructions. Due to the fact that SDF architecture maintains I-structure semantics for thread synchronization, and conventional memory semantics like MIPS, SDF has two sets of memory access instructions for memory accesses – IFetch and IStore for I-structure memory, and Read and Write for conventional memory.

SDF also has some special instructions for spawnning threads (FALLOC), thread switching between the memory access and execution pipelines (FORKSP, FORKEP), and reading and writing from the frame memory (Load and Store).

#### 3.2. SDF Thread Execution Stages

For SDF architecture, the compiler partitions the applications written in high-level languages into threads based on the data flow graph. A thread in SDF architecture can be viewed as a subgraph of a data flow graph. The size of an SDF thread is limited by the hardware resources, such as number of registers per context, number of entries in a frame memory for a thread, etc. Because SDF decouples memory access and execution, a thread

will further partition into three portions: pre-load codes, execute codes, and post-store codes. The pre-load and post-store codes will execute on the memory access pipeline, and the execution code will execute on the execution pipeline. The execution sequence of a thread is shown in the following figure 3.1.

FIGURE 3.1. Code Partition in SDF Architecture

To understand the decoupled, scheduled dataflow concept, consider one iteration of the innermost loop of matrix multiplication: c[i,j] = c[i,j] + a[i,k] \* b[k,j]. The SDF code is shown in figure 3.2. In this example, I assume that all necessary base addresses and indexes for the arrays are stored in the thread's frame. The thread is enabled after it receives all inputs in its frame and a register context is allocated. In the preload portion of the example, the base address and offsets of arrays are loaded from the frame memory and then the data element referenced in this iteration is fetched from the I-structure memory. By executing the FORKEP instruction, the thread gives up the memory access unit and the continuation of the thread is put into a queue to wait for the execution unit. When the thread is scheduled on the execution pipeline, the multiplication is performed. Then by executing the FORKSP instruction, the continuation of this thread is put into the post-store queue to wait for the execution. Finally, the thread gets the memory access unit again and the result is post-stored. Because the thread model is non-blocking, the FFREE instruction frees the frame held by the thread and the continuation is destroyed.

| Preload:    | LOAD LOAD LOAD LOAD LOAD LOAD IFETCH IFETCH FORKEP STOP | RFP 2, R2<br>RFP 3, R3<br>RFP 4, R4<br>RFP 5, R5<br>RFP 6, R6<br>RFP 7, R7<br>R2, R3, R8<br>R4, R5, R9<br>R6, R7, R10<br>Body | # base address of a into R2 #index a[i,k] into R3 # base address of b into R4 #index b[k,j] into R5 # base address of c into R6 #index c[i,j] into R7 # fetch a[i,k] to R8 # fetch b[k,j] to R9 # fetch c[i,j] to R10 # transfer to EP |

|-------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Body:       | MULTD<br>ADDD<br>FORKSP<br>STOP                         | R8, R9, R11<br>R10, R11, R10<br>Poststore                                                                                     | #a[i,k]*b[k,j] in R11<br>#c[i,j] + a[i,k]*b[k,j] in R10<br>#transfer to SP                                                                                                                                                             |

| Po ststore: | ISTORE<br>FFREE<br>STOP                                 | R6, R7, R10                                                                                                                   | #save c[i,j]<br>#free the frame                                                                                                                                                                                                        |

FIGURE 3.2. An SDF Code Example

### 3.3. Thread Representation in SDF

A thread in SDF architecture can be uniquely identified by a continuation of four tuples - <FP, IP, RS, SC>. FP is the Frame Pointer (where thread input values are stored), IP is the Instruction Pointer (which points to the thread instructions), RS is a register set (a dynamically allocated register context), and SC is the synchronization count (the number of inputs needed to enable the thread). The synchronization count is decreased when a thread receives its inputs, and the thread is scheduled on SP when the count reaches zero. Each thread has an associated continuation. At any given time a thread continuation can be in one of the following states:

- Waiting continuation (WTC) or  $\langle FP, IP, --, SC \rangle$

- Pre-Load Continuation (PLC) or <FP, IP, RS, -->

- Enabled Continuation (EXC) or <--, IP, RS, -->

- $\bullet$  Post-store Continuation (PSC) or <---, IP, RS, --->

The "--" means that the value is undefined in that state.

Figure 3.3 shows a state transition diagram of thread continuation. A thread continuation is created in the WTC state. A thread moves from the WTC state to the PLC state once a register set is assigned to the continuation and scheduled to an SP (memory access unit)

FIGURE 3.3. State Transition of the Thread Continuation

for preload. And then the thread is moved to EXC state, when it finishes using SP and transfers to EP (execution unit). After using EP, the continuation is moved to SP again and the thread continuation enters PSC state. The scheduling unit is responsible for moving continuations between SP and EP.

### 3.4. The Basic Processing Units in SDF

A processing element in scheduled dataflow architecture (SDF) is composed of three components: the Synchronization Processor (SP), the Execution Processor (EP), and the thread schedule unit.

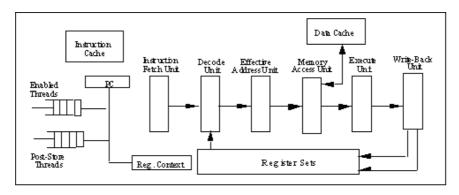

The SP is responsible for pre-loading a thread context (i.e. registers) with data from the thread's memory and post-storing results from a completed thread into frames of destination threads. The synchronization pipeline consists of six stages: instruction fetch, instruction decode, effective address computation, memory access, execution, and write-back. Figure 3.4 shows a block diagram of SP. The instruction fetch stage fetches an instruction belonging to the current thread using the PC (Program Counter). The decode stage decodes the instruction and fetches the operands from the registers. The effective address stage computes the effective address for memory access instructions like LOAD, STORE, READ, WRITE, IFETCH, and ISTORE. The memory access stage completes the memory access for memory access instructions. The write-back stage completes the LOAD, READ, and IFETCH instructions by storing the result into the register. Unlike traditional dataflow architecture, the instruction is not scheduled immediately when the operands are available. The instructions

are "scheduled" like control flow architectures using program counters. The instructiondriven approach eliminates the need for complex communications to exchange tokens among processing elements.

FIGURE 3.4. SP Pipeline

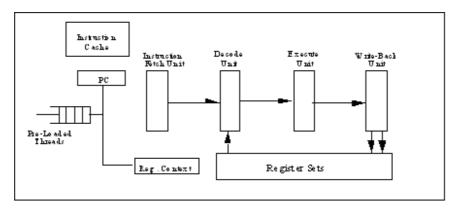

The EP performs thread computations, including integer and floating point arithmetic operations, and spawns new threads. The execution pipeline consists of four pipeline stages: instruction fetch, decode, execute, and write-back. The instruction fetch stage behaves like a traditional fetch unit, which fetches instructions pointed by the program counter (PC). The instruction decode stage decodes the instruction and fetches the operands from the registers. The execution stage executes the instruction, and the write-back units write the value to the register file.

FIGURE 3.5. General Organization of the Execution Pipeline (EP)

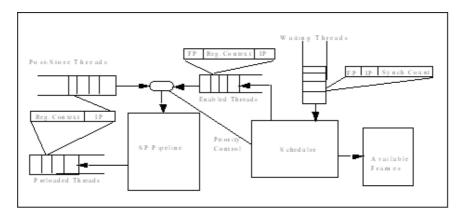

A more general implementation can include multiple EP and SPs to execute threads from a single task or independent tasks. Multiple SP and EPs can be configured into multiple clusters. Inter-cluster communications will be achieved through shared memory. The scheduling of threads to an SP and EP is handled by a scheduling unit (SU). Figure 3.6 shows the SP with scheduling queues.

FIGURE 3.6. Overall Organization of the Scheduling Unit

In SDF architecture, a thread is created by using the FALLOC instruction. The FALLOC instruction creates a frame (pointed to by an FP) related to a certain thread (pointed to by an EP) with a given Synchronization Count (SC), which indicates the number of inputs needed to enable the thread. The thread continuation (<FP, IP, --, SC>) is then handled by the SU. The SU takes care of checking when the synchronization count reaches zero. Then it allocates a register set (RS) to it, and the continuation is scheduled for execution on the SP. Now the thread is in the PLC state. The PLC thread is ready to execute on the SP for preload. At the end of the preload phase, the thread is handed off to the EP by executing the FORKEP instruction. The thread is in state EXC (<--, IP, RS, -->) and is ready to be executed on the EP. The SU is also responsible for moving the thread between the SP and the EP. The FORKSP instruction is used to move the thread from the EP to the SP (from the PLC state to the PSC state). After completing the post store, the register set (RS) is freed and the thread execution is complete.

In order to speed up the frame allocation, a fixed-size frame for the thread is pre-allocated and a stack of indexes pointing to the available frames is maintained. The SU makes a frame index available to the EP by popping the stack when executing the FALLOC instruction. The SU is also responsible for allocating the register sets. The register sets are viewed as circular buffers which are allocated to enabled threads. The SU pushes indexes of deallocated frames to the stack FFREE instruction subsequent to the post-store of completed

threads. These policies permit fast context switching and low overhead creation of threads. FALLOC and FFREE take two cycles in SDF architecture. Because the thread transition in between SP and EP are very simple, I assume these transitions can be completed in two cycles based on Rhamma architecture [35]. Note that scheduling is at the thread-level rather than instruction-level, unlike superscalar or other conventional architectures, and thus it requires much simpler hardware.

## 3.5. Storage in SDF Architecture

There are three classes of storage in SDF architecture: I-structure, conventional memory, and frame memory. I-structure follows the semantics of I-structure proposed by Arvind [8][7]. To access this memory IFETCH and ISTORE instructions are used. The IALLOC instruction is used to allocate the I-structure and the IFREE instruction is used to de-allocate the I-structure. The I-structure can be used to model the producer and consumer problem and will synchronize the thread execution.

The frame memory is used to store the inputs from one thread to the continuation of another thread. In addition, the frame memory is allocated by using the FALLOC instruction and de-allocated by using the FFREE instruction. Allocation and deallocation of frames are the EP's responsibility.

The conventional memory is accessed by using the READ and WRITE instruction. It is just like the memory in any Von Neumann architecture.

# 3.6. The Experiment Results of SDF Architecture

The SDF architecture exploits two levels of parallelism. Multiple threads can be active simultaneously, permitting thread-level parallelism. In addition, the three phases of a thread (pre-load, execute, and post-store) can be overlapped with those of other threads. I reported the results of preliminary performance comparisons of SDF with other architectures [32][46]. More recently, If also have collected data to compare SDF with SMT. The results thus far show that SDF scales better than superscalar, and VLIW systems with added functional units and register sets. Even for control-dominated applications, multi-threading computations from independent workloads can lead to better utilization of the functional units within SDF (similar to SMT). Here I show a selected subset of my results.