## San Jose State University SJSU ScholarWorks

Master's Theses

Master's Theses and Graduate Research

Spring 2015

# 30 GHz Adaptive Receiver Equalization Design Using 28 nm CMOS Technology

Gustavo Tostado Villanueva San Jose State University

Follow this and additional works at: https://scholarworks.sjsu.edu/etd theses

### Recommended Citation

Villanueva, Gustavo Tostado, "30 GHz Adaptive Receiver Equalization Design Using 28 nm CMOS Technology" (2015). *Master's Theses.* 4564.

DOI: https://doi.org/10.31979/etd.e73r-refs https://scholarworks.sjsu.edu/etd\_theses/4564

This Thesis is brought to you for free and open access by the Master's Theses and Graduate Research at SJSU ScholarWorks. It has been accepted for inclusion in Master's Theses by an authorized administrator of SJSU ScholarWorks. For more information, please contact scholarworks@sjsu.edu.

## 30 GHZ ADAPTIVE RECEIVER EQUALIZATION DESIGN USING 28 NM CMOS TECHNOLOGY

## A Thesis

## Presented to

The Faculty of the Department of Electrical Engineering

San José State University

In Partial Fulfillment

of the Requirements for the Degree of

Master of Science

by

Gustavo T. Villanueva

May 2015

© 2015

Gustavo T. Villanueva

ALL RIGHTS RESERVED

## The Designated Thesis Committee Approves the Thesis Titled

## 30 GHZ ADAPTIVE RECEIVER EQUALIZATION DESIGN USING 28 NM CMOS TECHNOLOGY

by

## Gustavo T. Villanueva

### APPROVED FOR THE DEPARTMENT OF ELECTRICAL ENGINEERING

## SAN JOSÉ STATE UNIVERSITY

## May 2015

| Dr. Shahab Ardalan          | Department of Electrical Engineering |

|-----------------------------|--------------------------------------|

| Dr. Sotoudeh Hamedi-Hagh    | Department of Electrical Engineering |

| Dr. Robert Morelos-Zaragoza | Department of Electrical Engineering |

| Dr. Thuy T. Le              | Department of Electrical Engineering |

#### **ABSTRACT**

## 30 GHZ ADAPTIVE RECEIVER EQUALIZATION DESIGN USING 28 NM CMOS TECHNOLOGY

by Gustavo T. Villanueva

This thesis consists of a 28 nm submicron circuit design for high speed transceiver circuits used in high-speed wireline communications that operate in the 60 Gb/s range. This thesis is based on research done on high speed equalizer standards for the USB 3.1 SuperSpeed Differential Channel Loss Receiver Equalizer or Peripheral Component Interconnect (PCI) Express® Base Specification Revision 3.0. As of 2015, USB 3.1 and PCI Express® 3.0 are technologies with possibilities to be implemented in emerging technology targeted to consumer applications that demand improvements in signal integrity for high speed serial data communication of baud rates above 20 Gb/s. This thesis proposes a circuit design for an adaptive equalizer capable of adjusting its voltage gain, bandwidth, and boost for high speed data communications. The proposed design is implemented with a novel variable gain amplifier (VGA), a digitally controlled continuous time linear equalizer (CTLE), and a digitally controlled decision feedback equalizer (DFE), which is believed to provide circuit power and signal integrity improvements in the differential receiver and equalization subsystem that operate at 60 Gb/s.

#### **ACKNOWLEDGEMENTS**

This work was founded in part by Lockheed Martin Space Systems Company (LMSSC) under the company's employee educational program and in part by the United States Navy through the Montgomery GI Bill.

I specially thank my friends and colleagues who provided me with the technical advised and the guidance needed for the creation of this thesis. Albeit, I specially appreciate the help and guidance from the faculty and staff of the department of electrical engineering at San José State University who helped me understand and appreciate complex circuitry design. I specially thank Professor Robert Morelos Zaragoza for his guidance in explaining the fundamental theory behind channel modeling, Professor Sotoudeh Hamedi-Hagh for teaching me simple techniques to analyze and understand CMOS analog design, and most importantly Professor Shahab Ardalan for his persistent guidance and mentorship that lead to the creation of this work. There is not enough space in this document to individually thank those who became an integral part to my success which consisted of all my professors, my professional colleges, my friends and my family.

This thesis is especially dedicated to my mother, Refugio Tostado Alejandre, a smart woman who inspired me with her exemplary knowledge, education, professionalism, and perseverance and who instilled in me the courage to write this thesis. I also dedicate this thesis to my two nephews, Román and Iñaki Villanueva in the

hope that one day they find the desire and inspiration to obtain any type of higher education so that they can also become a beacon of inspiration to others.

## TABLE OF CONTENTS

| 1 | Intro | luction                                                                 | 1    |

|---|-------|-------------------------------------------------------------------------|------|

|   | 1.1   | Historical Background                                                   | 1    |

|   | 1.2   | Fundamental Transmission Frequency (Nyquist Frequency) and the Unit     | t    |

|   |       | Interval (UI)                                                           | 3    |

|   | 1.3   | Transmission Reliability, 8b/10b Data Symbols Coding, and Transfers per | er   |

|   |       | Second (T/s) Measurement                                                | 7    |

|   | 1.4   | USB 3.1 Architecture Impact on Future Electronic Equipment 1            | 11   |

|   |       | 1.4.1 USB Technology Transfer Rates 1                                   | 14   |

|   |       | 1.4.2 The SuperSpeed USB 3.0 Standard                                   | 17   |

|   |       | 1.4.3 The SuperSpeed+ USB 3.1 Standard 1                                | 17   |

|   |       | 1.4.4 USB 3.0 and USB 3.1 Specification Standard Documentation 1        | 18   |

|   |       | 1.4.5 USB 3.0 and 3.1 Physical Interface Architecture                   | 19   |

|   |       | 1.4.6 Standard Definition of the USB 3.0 Transmission Channel, the Fu   | ʻull |

|   |       | Link Channel Model 2                                                    | 20   |

|   | 1.5   | 2014 State of the Art Circuits in Analog Front-End Design for Gb/s      |      |

|   |       | Wireline Receivers 2                                                    | 23   |

|   |       | 1.5.1 Technology Challenges 2                                           | 23   |

|   |       | 1.5.2 State of the Art Equalizer Circuits 2                             | 24   |

| 2 | Chan  | nel Model                                                | 33  |

|---|-------|----------------------------------------------------------|-----|

|   | 2.1   | Types of Printed Transmission Lines                      | 33  |

|   | 2.2   | The FR4 Microstrip Wire Line                             | 36  |

|   | 2.3   | Channel Capacity                                         | 39  |

|   | 2.4   | Modeled FR4 PCB Traces of 1-oz Microstrip Lines          | 41  |

|   | 2.5   | Simplified Circuit Model for FR4 Microstrip Channel      | 43  |

| 3 | Equa  | lizer Design                                             | 53  |

|   | 3.1   | Equalizer Bandwidth Limitations                          | 55  |

|   | 3.2   | Transit Frequency ( $fT$ ) and Transit Time ( $\tau T$ ) | 56  |

|   | 3.3   | Transit Frequency Using the NMOS Diode Setup Model       | 75  |

|   | 3.4   | Important NMOS Parameters Needed to Design an Amplifier  | 86  |

|   | 3.5   | Current Sources                                          | 90  |

|   | 3.6   | Basic Amplifier                                          | 93  |

|   | 3.7   | Amplification Chain Biasing                              | 107 |

|   | 3.8   | Differential Amplifier Configuration.                    | 110 |

|   | 3.9   | Pulse Shaping                                            | 111 |

|   | 3.10  | 30 GHz Equalizer Circuit Elements                        | 117 |

| 4 | Resul | lts                                                      | 119 |

|   | 4.1   | High Pass Filter                                         | 119 |

| 6 | Refer | ences                              | 127   |

|---|-------|------------------------------------|-------|

| 5 | Concl | usion                              | 124   |

|   | 4.4   | 30 GHz Equalizer, 28 nm Technology | . 122 |

|   | 4.3   | Pulse Shape Filter                 | . 121 |

|   | 4.2   | Low Pass Filter                    | . 120 |

## LIST OF FIGURES

| Figure 1-1  | NRZ Differential Data Transmission                                                                                                                                                                                                                                                         |    |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|

| Figure 1-2  | Serial Transmission of a 10 Gb/s Signal with Repeating Code "0110"5                                                                                                                                                                                                                        |    |  |  |

| Figure 1-3  | Transmission Examples of Serial Data at a Baud Rate of 10 Gb/s. (a) Transmission of <i>All-zeroes</i> in 11 UIs, (b) Transmission of <i>All-ones</i> in 11 UIs, (c) Transmission of "01100011100" Bit Data, and (d) Transmission of the Nyquist or Fundamental Frequency "010101010101010) |    |  |  |

| Figure 1-4  | Example of Received Data if the Data Signal is Shifted by One UI. (a) Transmitted Data Example; (b) Decimal and Hexadecimal Values of Transmitted Data (a); (c) Example of Received Data Wrongly Shifted by One UI; and (d) Decimal and Hexadecimal Value of Buffered Data (c)             |    |  |  |

| Figure 1-5  | Overall Block Diagram for the USB 3.0 Physical Layer Design                                                                                                                                                                                                                                | 20 |  |  |

| Figure 1-6  | USB 3.0 and USB 3.1 Short Channel Application Range                                                                                                                                                                                                                                        | 21 |  |  |

| Figure 1-7  | Full Link Model for Short Channel Application Range on USB 3.0 and USB 3.1                                                                                                                                                                                                                 | 22 |  |  |

| Figure 1-8  | Full Link Model for Long Channel Application Range on USB 3.0 and USB 3.1                                                                                                                                                                                                                  | 22 |  |  |

| Figure 1-9  | Analog Front End (AFE) Design of a Receiver CTLE Equalizer. Figure Adapted by Author from [6]                                                                                                                                                                                              |    |  |  |

| Figure 1-10 | Transimpedance Gain. Frequency Response for the AFE. Figure Create by Author from Data in [6]                                                                                                                                                                                              |    |  |  |

| Figure 1-11 | Transimpedance Gain. Frequency Response for the AFE. Figure Adapt by Author from [7]                                                                                                                                                                                                       |    |  |  |

| Figure 1-12 | Charge-Based Sample-and-Hold (S/H) with Clocked Adaptive Loads. Figure Adapted by Author from [7]28                                                                                                                                                                                        |    |  |  |

| Figure 1-13 | Trans-Impedance Equalizer. Figure Adapted by Author from [9]                                                                                                                                                                                                                               | 29 |  |  |

| Figure 1-14                                                                                                                                                          | Pseudo-Differential CMOS Push-Pull Trans-Impedance Equalizer. Fig Adapted by Author from [10]                                                                                                                   |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Figure 1-15                                                                                                                                                          | TAS-TIA CTLE. Figure Adapted by Author from [11]32                                                                                                                                                              |  |  |

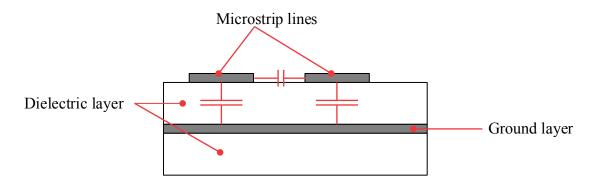

| Figure 2-1                                                                                                                                                           | Typical Microstrip Line Configuration for Differential Transmission Lines                                                                                                                                       |  |  |

| Figure 2-2                                                                                                                                                           | Microstrip Lines Interelement Capacitance                                                                                                                                                                       |  |  |

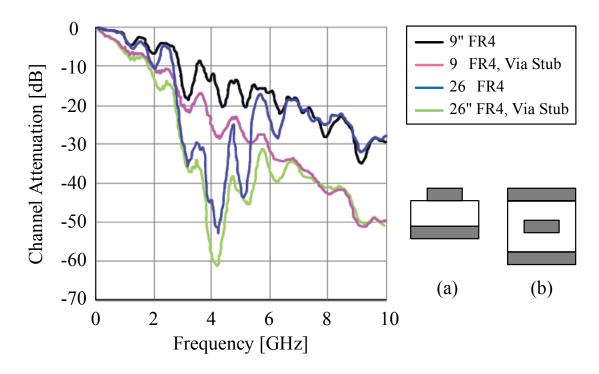

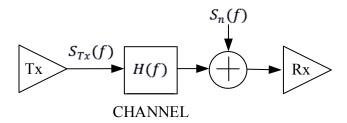

| Figure 2-3                                                                                                                                                           | FR4 Channel Interconnection                                                                                                                                                                                     |  |  |

| Figure 2-4                                                                                                                                                           | FR4 Channel Loss for 9" (22.86 cm-long) and 26" (66.04 cm-long) Wirelines. (a) Cross Section of an FR4 Microstrip Wireline; (b) Cross Section of a Stripline Wireline. Frequency is Displayed in Linear Form.38 |  |  |

| Figure 2-5                                                                                                                                                           | PCB Layout of an FR4 Microstrip and Stripline Wirelines Connected Using Vias. Via Stubs Create Additional Interelement Capacitances39                                                                           |  |  |

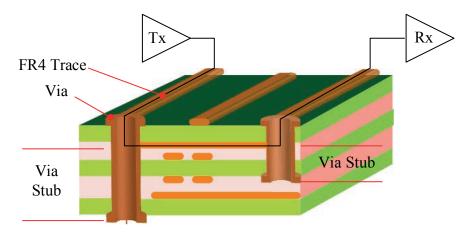

| Figure 2-6                                                                                                                                                           | Channel Capacity System Model                                                                                                                                                                                   |  |  |

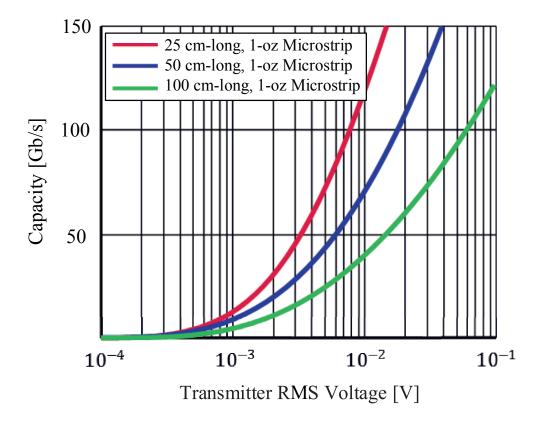

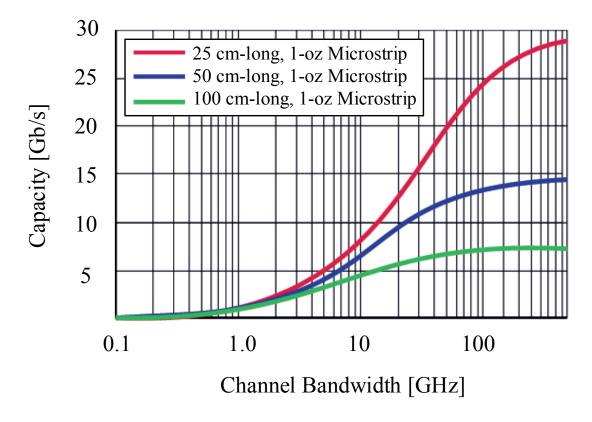

| Figure 2-7                                                                                                                                                           | Channel Capacity for Various Lengths of 1-oz Microstrip Wirelines with Noiseless Environment. Data Adapted by Author from [12]42                                                                                |  |  |

| Figure 2-8                                                                                                                                                           | Channel Capacity for Various Lengths of 1-oz Microstrip Wirelines with Noise Environment Caused by Signal Crosstalk and Ambient Electromagnetic Noise. Data Adapted by Author from [12]                         |  |  |

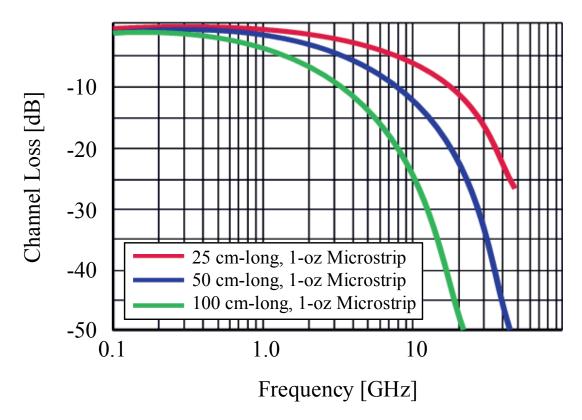

| Figure 2-9                                                                                                                                                           | Modeled Channel Transfer Function Response $(H(f))$ of a $56\Omega$ Impedance Noiseless FR4 Microstrip or Stripline. Data Adapted by Author from [12]                                                           |  |  |

| Figure 2-10                                                                                                                                                          | Modeled Channel Transfer Function Response ( $H(f)$ ) of a 66.04 cm-long Copper Microstrip that has a -50 dB Response at 10 GHz47                                                                               |  |  |

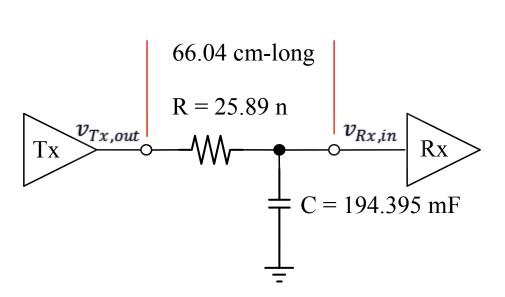

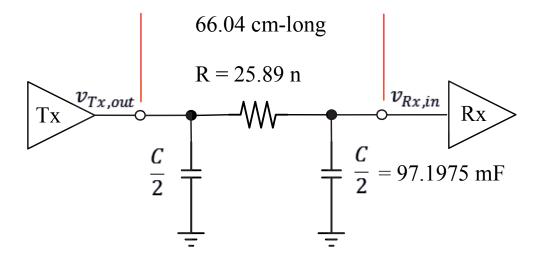

| Figure 2-11 Simplified Pi-Model for Channel Transfer Function Response ( <i>H</i> ( <i>f</i> )) 66.04 cm-long Copper Microstrip that Has a -50 dB Response at 10 GHz |                                                                                                                                                                                                                 |  |  |

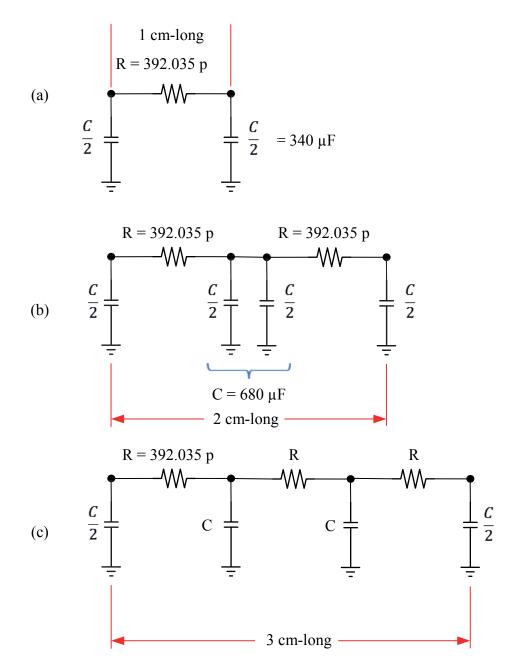

| Figure 2-12 | Simplified Pi-Model for Channel Transfer Function Response ( <i>H</i> ( <i>f</i> ) cm-long Copper Microstrip Segments. (a) Simplified 1 cm-long Cha Segment; (b) Combination of Two Simple Segments to Increase the Length of the Channel; (c) Model of a 3 cm-long Channel Using the Simple Channel Model                                  |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

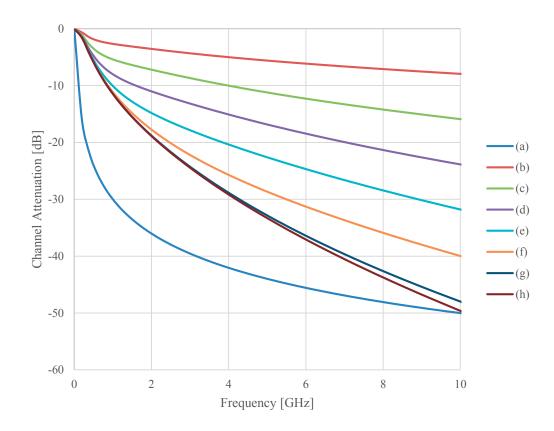

| Figure 2-13 | Channel Attenuation Results for Proposed Simple Model. (a) Channel Attenuation for One Segment Pi-model; (b) 10 cm-long Channel; (c) 20 cm-long Channel; (d) 30 cm-long Channel; (e) 40 cm-long Channel; (f) 50 cm-long Channel; (g) 60 cm-long Channel; and (h) 66 cm-long Channel 52                                                      |  |  |

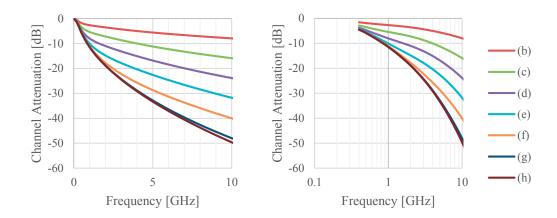

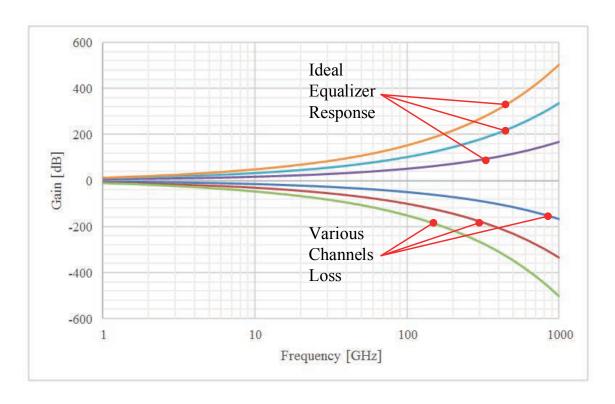

| Figure 3-1  | Channel Attenuation Results for Proposed Simple Model. The Graph on the Left X-axis Has a Linear Display while the Graph on the Right has a Logarithmic Display. (b) 10 cm-long Channel; (c) 20 cm-long Channel; (d) 30 cm-long Channel; (e) 40 cm-long Channel; (f) 50 cm-long Channel; (g) 60 cm-long Channel; and (h) 66 cm-long Channel |  |  |

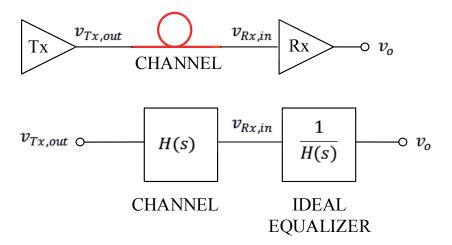

| Figure 3-2  | System Model for an Ideal Equalizer54                                                                                                                                                                                                                                                                                                       |  |  |

| Figure 3-3  | Ideal Equalizer Response                                                                                                                                                                                                                                                                                                                    |  |  |

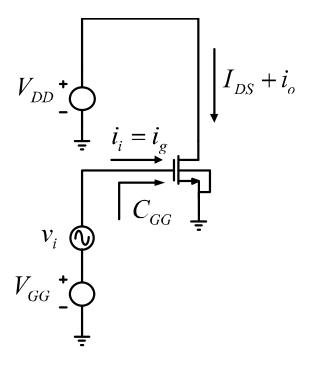

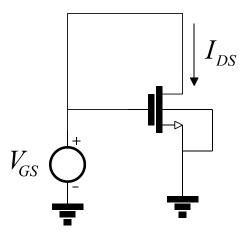

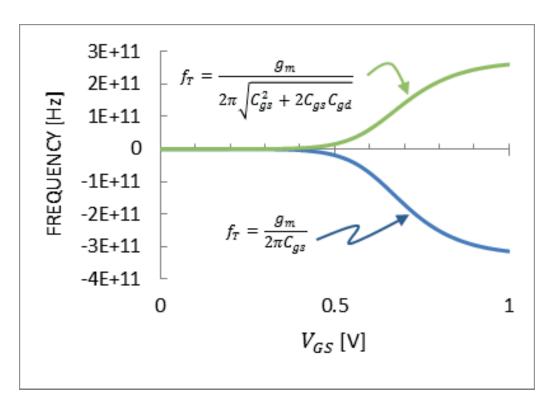

| Figure 3-4  | Circuit Model Setup to Measure the Transistor's Transit Frequency57                                                                                                                                                                                                                                                                         |  |  |

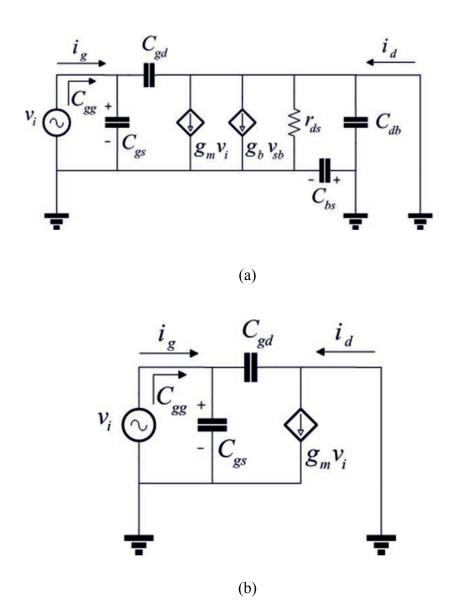

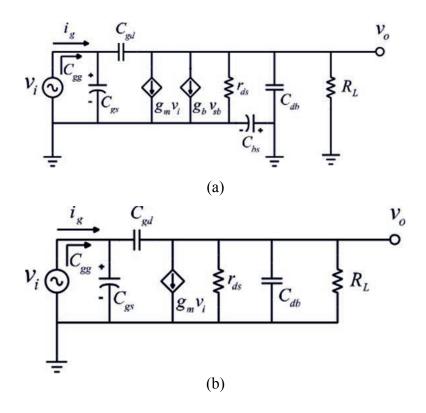

| Figure 3-5  | Small Signal π-Model for Circuit Model to Measure Transit Frequency. (a) All Intrinsic Transistor Components Shown, and (b) Intrinsic Transistor Elements Affected by the Circuit Test Model (Simplified)60                                                                                                                                 |  |  |

| Figure 3-6  | Bode Plot for Equation (3-18)                                                                                                                                                                                                                                                                                                               |  |  |

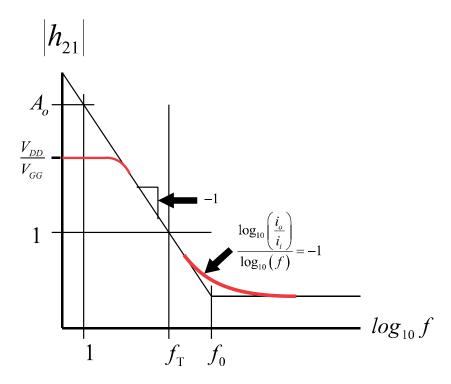

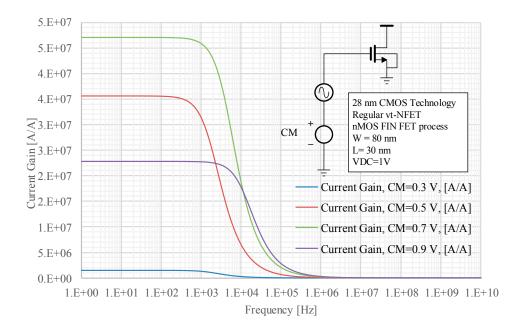

| Figure 3-7  | Current Gain for a 28 nm NMOS. Voltage Gate bias Creates Different Current Gain Profiles                                                                                                                                                                                                                                                    |  |  |

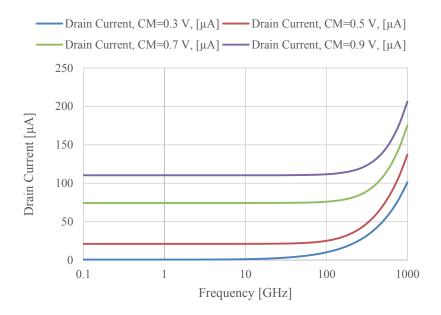

| Figure 3-8  | Drain Current for a 28 nm NMOS. Voltage Gate Bias Creates Different Current Gain Profiles                                                                                                                                                                                                                                                   |  |  |

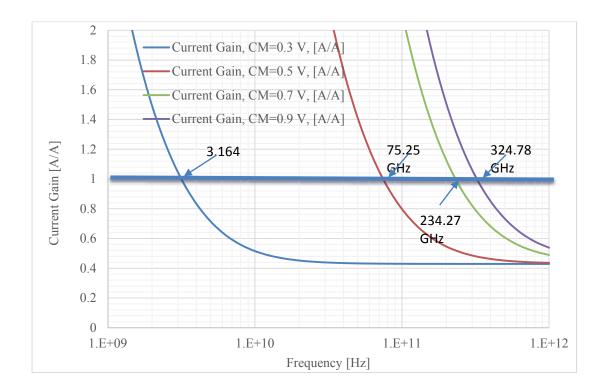

| Figure 3-9  | Transit Frequency. Current Gain for a 28 nm NMOS. Transit Frequency is the Frequency that Intersect the Gain of 1 A/A73                                                                                                                                                                                                                     |  |  |

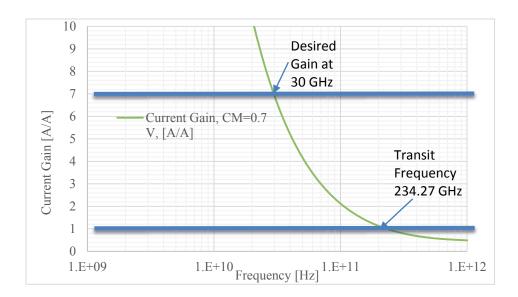

| Figure 3-10 | Current Gain for a 28 nm NMOS. Common Mode Voltage ( <i>VGG</i> ) set at 0.7 V. Transit Frequency at Current Gain of 1. A/A is 234.27 GHz                                                                                                                                                                                                   |  |  |

|             | Desired Current Gain at 30 GHz is Around 7 A/A. Drain Current at Desired Design Frequency of 30 GHz is 74.48 µA74                                         |  |  |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Figure 3-11 | NMOS Diode Configuration to Extract Transistor Technology Parameters                                                                                      |  |  |  |  |

| Figure 3-12 | NMOS Diode Configuration. (a) Small Signal Model for Figure 3-11 Circuit. (b) $\pi$ -Model for NMOS Diode Configuration                                   |  |  |  |  |

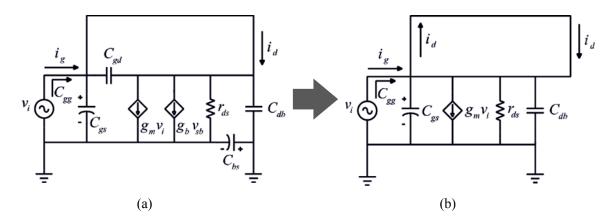

| Figure 3-13 | Difference Between Classic Transit Frequency—Shown with Negative Frequencies—and Transit Frequency Proposed in this Paper—Shown with Positive Frequencies |  |  |  |  |

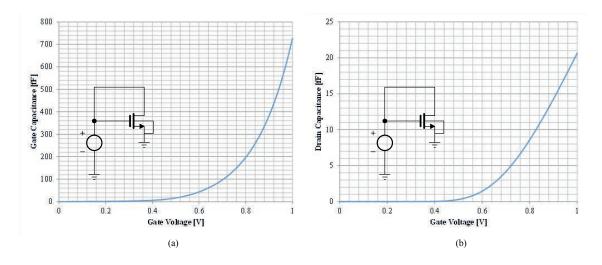

| Figure 3-14 | 28 nm NMOS Technology. (a) Gate Capacitance; (b) Drain Capacitance                                                                                        |  |  |  |  |

| Figure 3-15 | 28 nm NMOS Technology. Transconductance Gain ( <i>gm</i> ) for NMOS Connected in the Diode Configuration                                                  |  |  |  |  |

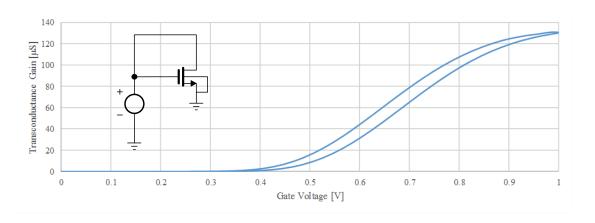

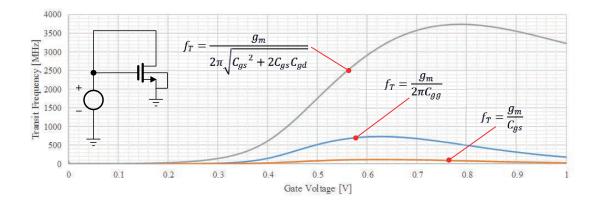

| Figure 3-16 | 28 nm NMOS Technology. Different Derivations Comparison for Transit Frequency when the NMOS is Connected in the Diode Configuration86                     |  |  |  |  |

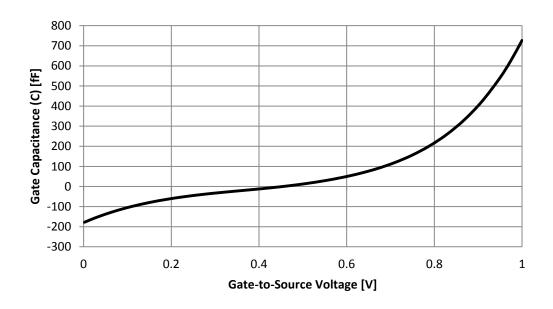

| Figure 3-17 | Gate Capacitance for 28 nm NMOS Technology. Small Signal Parameter                                                                                        |  |  |  |  |

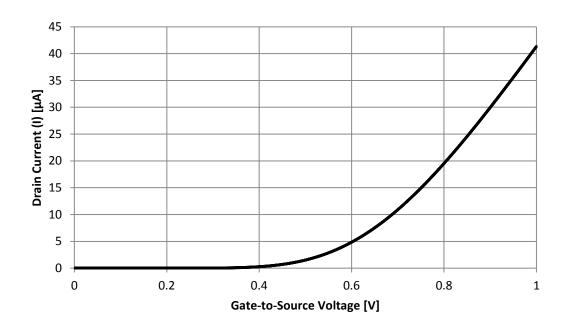

| Figure 3-18 | Maximum Drain Current for 28 nm NMOS Technology. Large Signal Parameter. NMOS Intrinsic Transistor Sized to 30 nm Width and 80 nm Length                  |  |  |  |  |

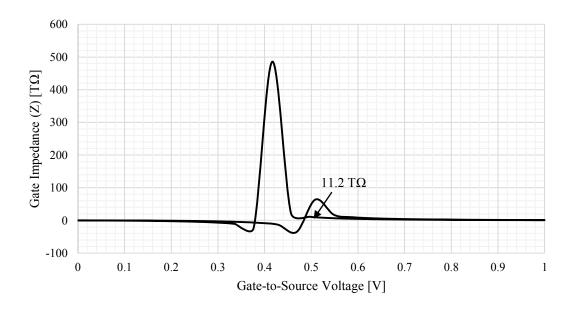

| Figure 3-19 | Hysteresis Gate Impedance for 28 nm NMOS Technology. Large Signal Parameter                                                                               |  |  |  |  |

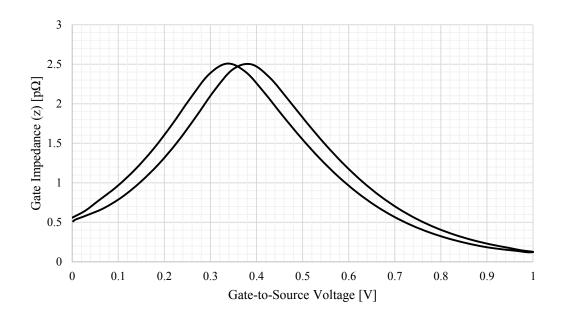

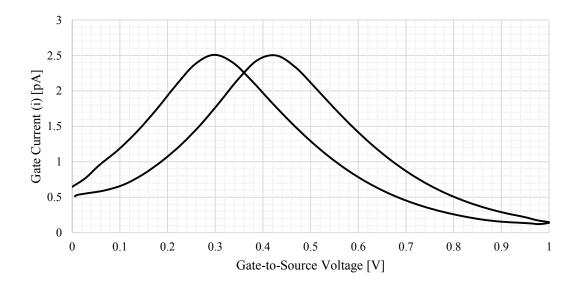

| Figure 3-20 | Hysteresis Gate Impedance for 28 nm NMOS Technology. Small Signal Parameter                                                                               |  |  |  |  |

| Figure 3-21 | 28 nm NMOS Technology. Different Derivations Comparison for Transit Frequency when the NMOS is Connected in the Diode Configuration89                     |  |  |  |  |

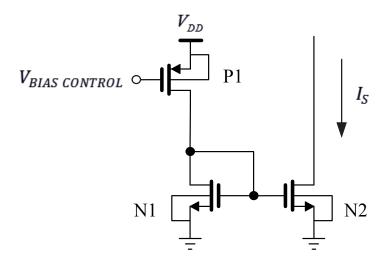

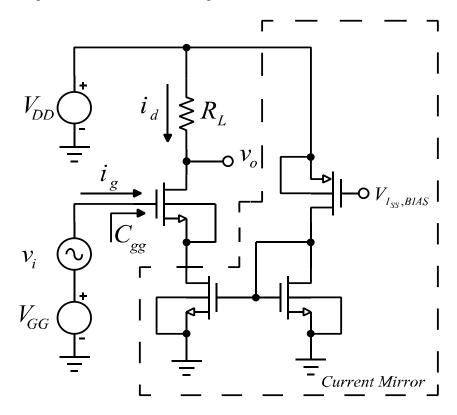

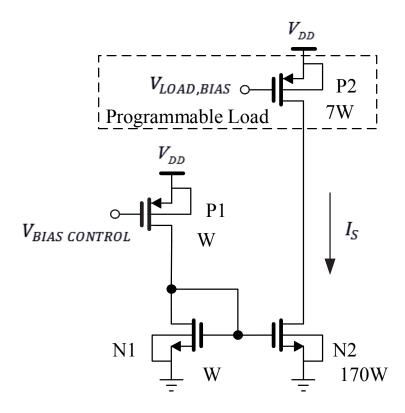

| Figure 3-22 | Programmable Current Mirror to Provide a Source Current ( <i>IS</i> )91                                                                                   |  |  |  |  |

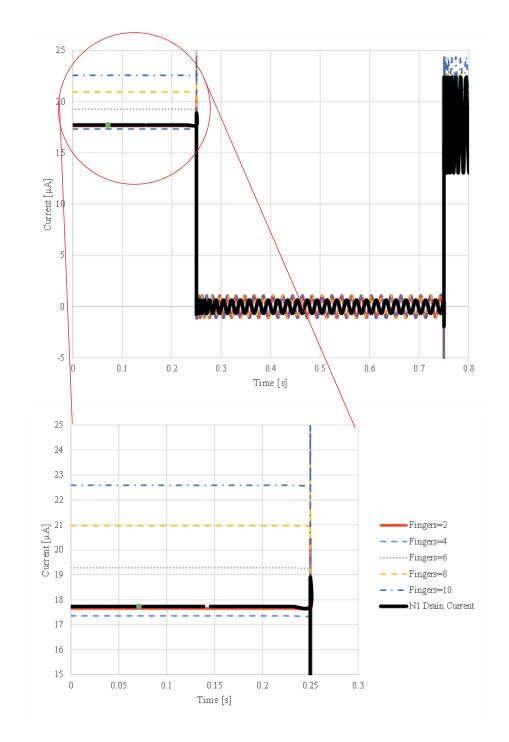

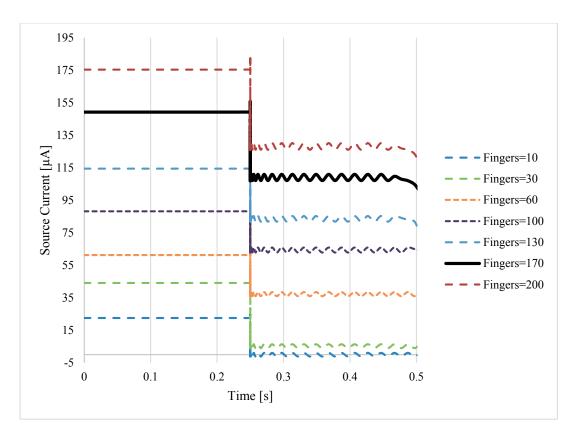

| Figure 3-23 | Increasing the Number of Gate Fingers Parameter in the N2 Transistor9                                                                                                   |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

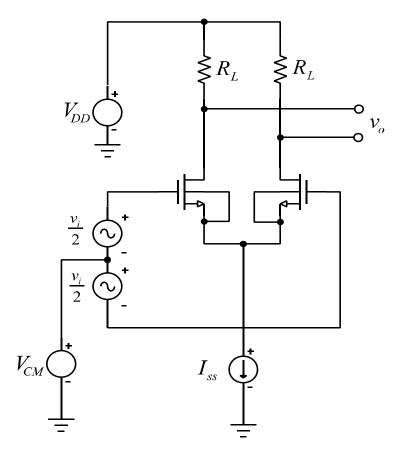

| Figure 3-24 | Common Source NMOS Differential Amplifier                                                                                                                               |  |  |

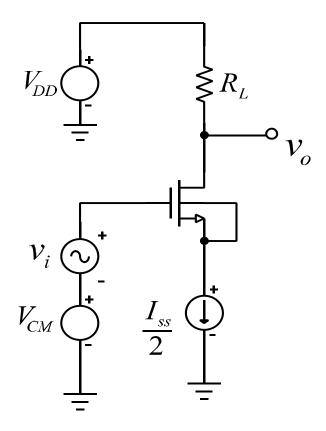

| Figure 3-25 | Simplified Common-source NMOS Circuit Leg for a Differential Amplifier                                                                                                  |  |  |

| Figure 3-26 | Common Source NMOS Differential Amplifier                                                                                                                               |  |  |

| Figure 3-27 | Amplifier's Source Current. Solid Line Represents Desired Finger Size 96                                                                                                |  |  |

| Figure 3-28 | Amplifier Circuit Current Source                                                                                                                                        |  |  |

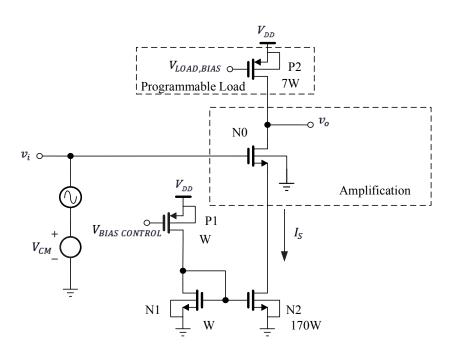

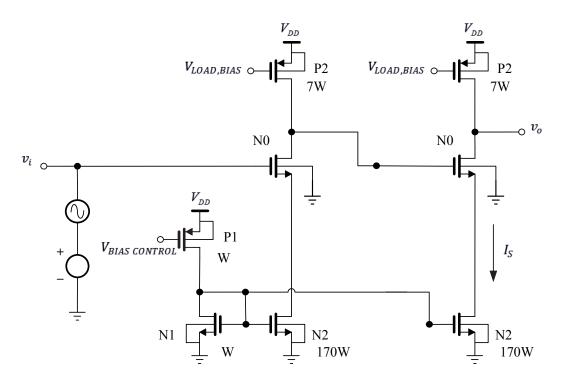

| Figure 3-29 | High-bandwidth Common Source Amplifier with Programmable Load and Current Source Control. Common Mode Voltage is Setup at 0.7 V98                                       |  |  |

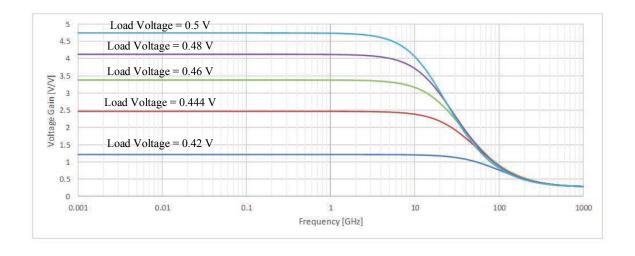

| Figure 3-30 | High-bandwidth Amplifier Design with Various Voltage Gain Outputs98                                                                                                     |  |  |

| Figure 3-31 | Small Signal Model for Simplified NMOS Amplifier. (b) Simplified Small Signal Model for NMOS Amplifier                                                                  |  |  |

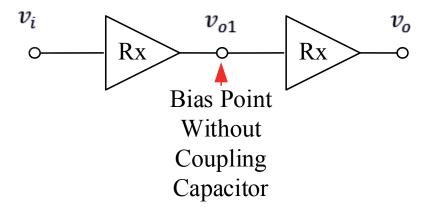

| Figure 3-32 | Connection of Two Identical Amplifiers Coupled without the Need of a Coupling Capacitor. Quiescent Point of First Amplifier Bias the Gate Input to the Second Amplifier |  |  |

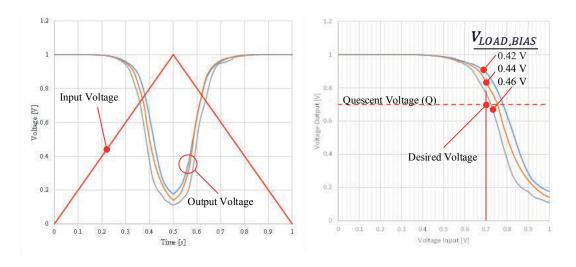

| Figure 3-33 | Evaluation of Amplifier Quiescent Point Voltage (Q). The Quiescent Point of the First Amplifier Stage Affects the Input Gate Bias of the Second Stage                   |  |  |

| Figure 3-34 | Two Stage Amplifier with No Coupling Capacitance between the Stages is Necessary                                                                                        |  |  |

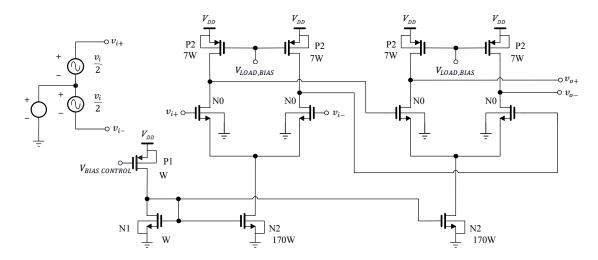

| Figure 3-35 | Two Stage Differential Amplifier with No Coupling Capacitance between the Stages is Necessary. Active Load and Output Power Control111                                  |  |  |

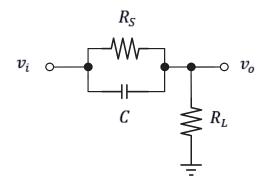

| Figure 3-36 | Hi Pass Filter112                                                                                                                                                       |  |  |

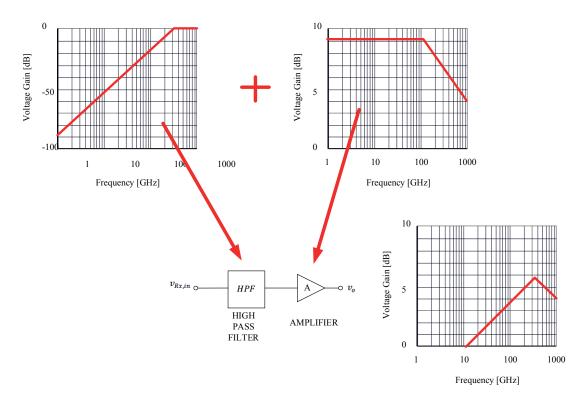

| Figure 3-37 | Equalizer Model Using a High Pass Filter in Series with an Amplifier113                                                                                                 |  |  |

| Figure 3-38 Bode Plot Representation of a Pulse Shape Signal using a Low Par |                                                                                                                           |     |

|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----|

|                                                                              | High Pass Filter Connected in Series                                                                                      | 114 |

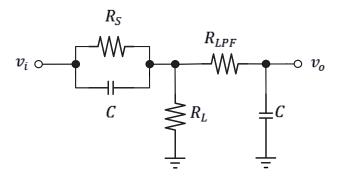

| Figure 3-39                                                                  | Passive Pulse Shape Filter                                                                                                | 115 |

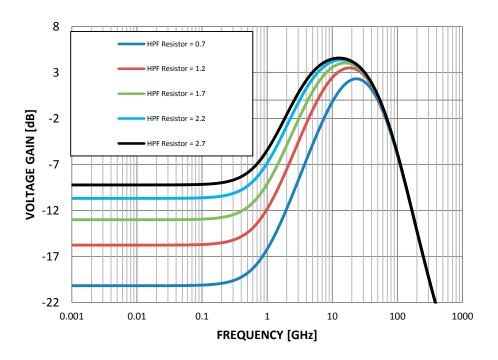

| Figure 3-40                                                                  | Variable Passive Pulse Shape Filter. HPF Resistor is Programmed or Varied to Add Attenuation to the Lower Frequency Range | 116 |

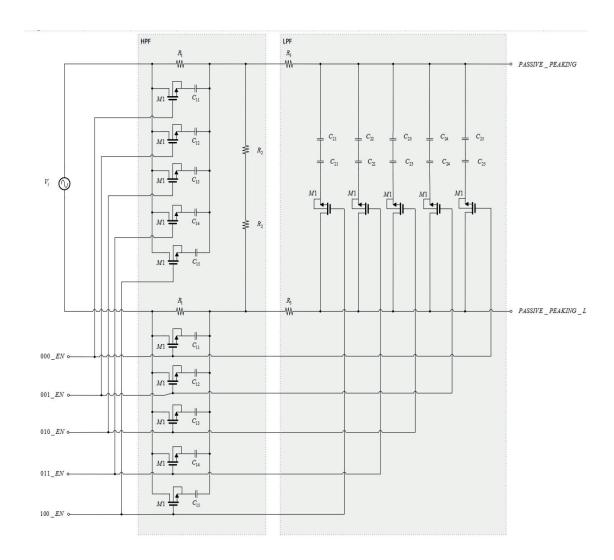

| Figure 3-41                                                                  | Programmable Differential Pulse Shape Filter                                                                              | 117 |

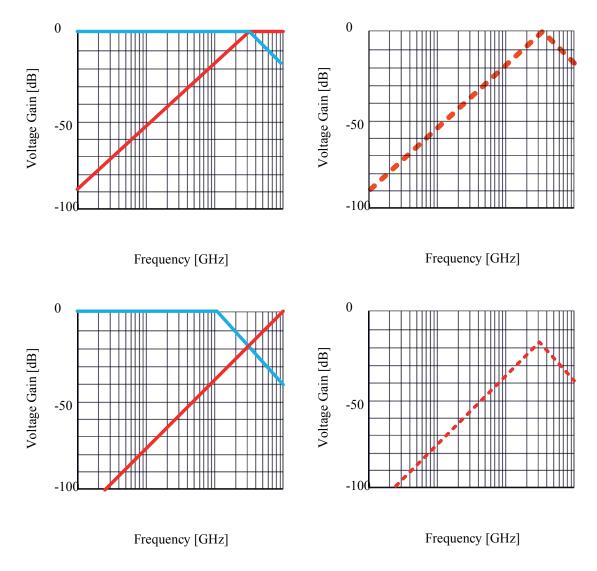

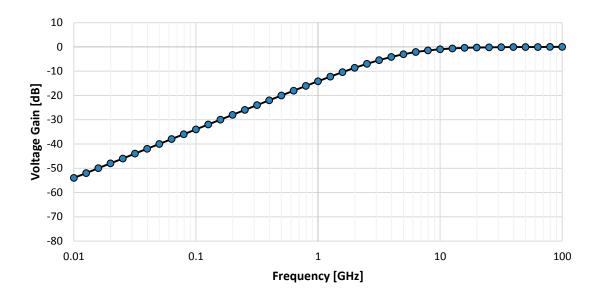

| Figure 4-1                                                                   | Frequency Response for High Pass Filter (HPF) Design                                                                      | 120 |

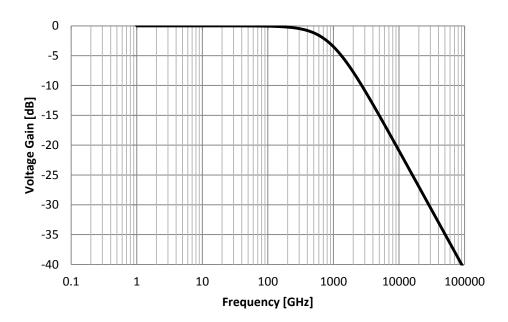

| Figure 4-2                                                                   | Frequency Response for Low Pass Filter (LPF) Design                                                                       | 121 |

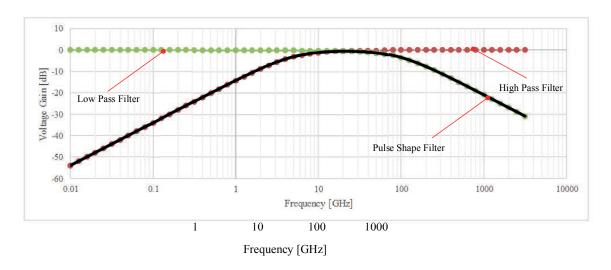

| Figure 4-3                                                                   | Frequency Response for Pulse Shape Filter (PSF) Design                                                                    | 122 |

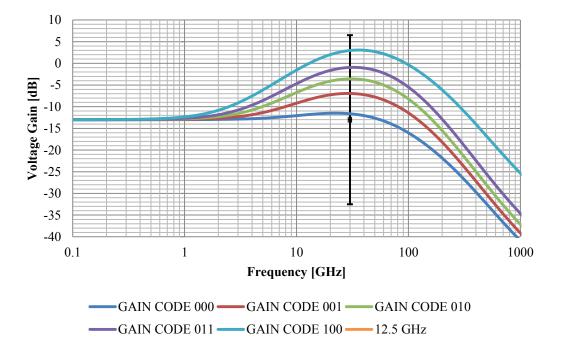

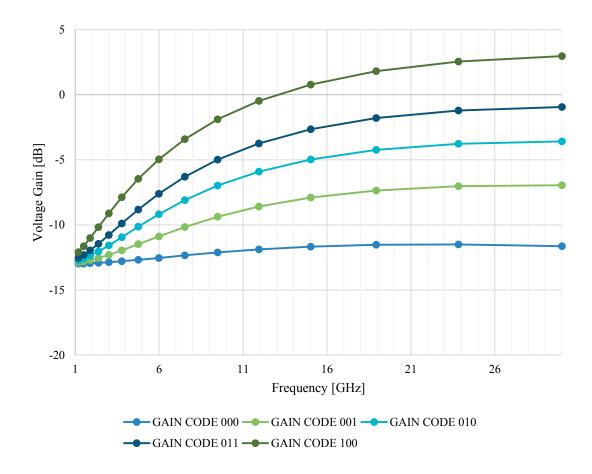

| Figure 4-4                                                                   | This Thesis Equalizer Voltage Gain Response—Logarithmic Frequency                                                         | 122 |

| Figure 4-5                                                                   | This Thesis Equalizer Voltage Gain Response—Linear Frequency                                                              | 123 |

## LIST OF TABLES

| Table 1-1 | An 8b/10b Data Symbol Coding for Serial Data Transmitted over USB 3.X and PCIe® 3.0. This Table only Shows Eight Data Byte Names out of More than 256 Allowable Coded Symbols |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 3-1 | Transfer Function Results for a 28 nm NMOS Capacitor using Cadence® Virtuoso® Tools.                                                                                          |

| Table 3-2 | Measured DC Parameters for Amplifier in Figure 3-21 Using Cadence® Virtuoso® Analog Design Environment—Transient Analysis                                                     |

| Table 4-1 | High Pass Filter Calculated Values for Passive Filter Elements119                                                                                                             |

| Table 4-2 | Low Pass Filter Calculated Values for Passive Filter Elements121                                                                                                              |

## 1 Introduction

#### 1.1 Historical Background

Since the advent of high speed serial digital communications, consumers have been able to transfer data from computers to a variety of electronic devices such as printers, fax machines, portable communication devices, and storage devices without the use of bulky cables. To date, the most recognized portable device interface among consumers worldwide is the Universal Serial Bus (USB) device interface. However, there are other types of similar serial communications. Perhaps the most recognized serial communication used between microcircuit devices is the PCI Express®. This thesis uses the fundamental theory used behind two well-known high speed serial communication standards.

Millions of USB consumer interface devices have been designed worldwide to communicate with portable computers, smart phones, portable music or data devices and most recently to communicate with luxury vehicle entertainment systems. In recent years, there has been an increasing demand to build electronic systems that contain microcircuit components that use the USB serial communication standard to transmit data, voice or video signals at an increasing transmission rate. The USB standard is commonly used to transmit information between two open system architectures—between two products used by a consumer. However, a common standard that is intended to enhance data communication between electronic components made by different vendors is the PCI Express® (a.k.a. PCIe®) because it provides high speed communications that are higher than what the USB standard offers. The PCIe®

communication standard allows point-to-point communication between microcircuit chips to minimize timing issues caused by multiple signal wires. Unlike the USB standard that is intended to have a maximum of three meters in length for link connections<sup>1</sup> between two USB devices, the PCIe® is designed to facilitate short length communication between two or more microcircuit devices within a printed circuit board which result in making a physical connection with a much shorter length.

Recently, the technological trend and challenge have been to design circuits that reduce the amount of power, jitter, and design area while increasing the single data signal<sup>2</sup> transmission speeds, data and signal reliability, and bandwidth. However, serial data transmission between USB or PCIe® devices is susceptible to the transmission line loss (hereon referred as "channel loss") which directly affects the signal integrity. To compensate for the channel loss, a USB or PCIe® receiver design rely on a receiver front end electronic circuit design called the differential deceiver and equalization subsystem—which is the focus of this thesis.

\_

<sup>&</sup>lt;sup>1</sup> In standard network communication theory, a *link connection* is a point-to-point connection between two and independent physical ports. Each port belongs to a communication element in a network system.

<sup>&</sup>lt;sup>2</sup> The term *single data signal* is also referred to as *serial data* which is information or data that travel in a single transmission line. When testing or probing data information on a single transmission line, data are displayed across a time or frequency domain—each datum becomes a bit or frequency depending on how the data signal is displayed. However, every bit, frequency, datum, or piece of information is stitched and displayed into a single signal which forms the *data signal*. Therefore, many authors, this thesis—and the industry in general—use the term *data* as if it were a singular term—instead of a plural term—because it refers to a singular concept which is the *data signal*—a singular term—traveling in a *single line*. The single term for a piece of information is a *datum*. Therefore, the term "*data*" is correctly applied as a singular term when the context refers to probing electronic data from a single line. A datum is a *bit of data* while *data* is just the voltage or frequency signal in a single metallic line that changes with time.

## 1.2 Fundamental Transmission Frequency (Nyquist Frequency) and the Unit Interval (UI)

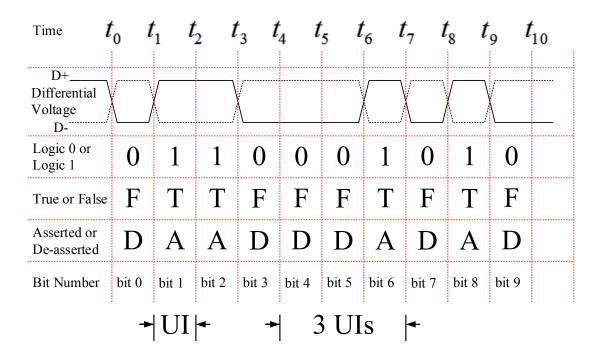

Serial binary data communication between two devices can be accomplished electronically in many ways. The USB and PCIe® standards rely on communicating data using the *non-return-to-zero* (NRZ) line code. In binary serial communication, a data signal is sent through a wire by changing the voltage of the wire with respect to time. When a logical data signal is asserted or is true, the voltage in the wire is driven to the transmitter driver's highest possible voltage—the datum or bit of data is a logical one. Conversely, when the logical data is de-asserted or not true, the voltage in the wire is driven to the transmitter's lowest possible voltage—the datum or bit is a logical zero. As a result, the transmission line requires either a high voltage to represent a logical one or a low voltage to represent a logical zero. When using a differential transmission line (two-wire communication), a change in voltage in the transmission line always indicates a data bit transition and a data bit is always asserted or de-asserted for a predetermined period of time called the unit interval (UI) (Figure 1-1).

Figure 1-1 NRZ Differential Data Transmission

Baud rate refers to the speed at which logical ones and logical zeroes can be transmitted and detected over the line per a specified UI time interval. Baud rate is also known as the data signaling rate or simply bit rate. In the telecommunication industry, when describing a receiver's bit rate (baud rate), the bit rate is measured using the bit-per-second (b/s) standard.

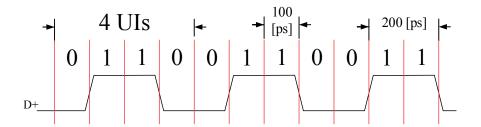

Let us consider a scenario where four bits are transmitted over a data line in 400 ps. Therefore, each bit would require a time of 100 ps to be transmitted. In this scenario there are 2<sup>4</sup> or 16 combinations of *ones* and *zeroes* of possible combinations that are serially transmitting four bits in 400 ps. In other words, every 400 ps there are four serial bits that are transmitted. The receiver may receive the "0000" combination or a low voltage for a period of 400 ps, or the transmitter may send a combination of "0110"

which in this case it means that for the first 100 ps, the receiver sees a low voltage followed by a transition of a high voltage for 200 ps and ends with a transition of a low voltage for the last 100 ps (Figure 1-2).

Figure 1-2 Serial Transmission of a 10 Gb/s Signal with Repeating Code "0110"

The unit interval for a 10 Gb/s is calculated by simply dividing one second by the number of bits in that second. Therefore, the unit interval for a 10 Gb/s receiver is 100 ps. The time interval for each bit in this example is 100 ps. The time interval for one bit in the data transmission is also known as the unit interval (UI). For example, in a differential transmission line where each bit is transmitted using NRZ line code at a baud rate of 10 Gb/s, the unit interval (UI) is calculated as follows:

$$UI_{10\frac{Gb}{s}} = \frac{1[b]}{10\left[\frac{Gb}{s}\right]} = \frac{1}{(10)(10^9)}[s] = 0.1 \times 10^{-9}[s] = 0.1[ns]$$

$$= 100[ps]$$

(1-1)

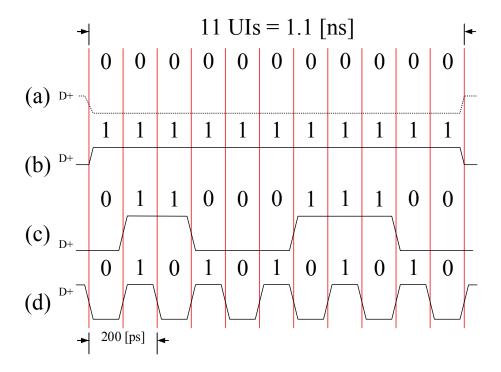

This means that in every 100 ps, the voltage signal could be a *logic one* or a *logic zero*. This also means that the receiver may see a series of logical zeroes ("0000...0000"), a series of logical ones ("1111111...11111"), a combination of zeroes and ones ("0110001110...00011100"), or simply a combination of ones and zeroes ("01010101...01010101") (Figure 1-3).

Figure 1-3 Transmission Examples of Serial Data at a Baud Rate of 10 Gb/s. (a) Transmission of *All-zeroes* in 11 UIs, (b) Transmission of *All-ones* in 11 UIs, (c) Transmission of "01100011100" Bit Data, and (d) Transmission of the Nyquist or Fundamental Frequency "01010101010101010...)

If the UI for a 10 Gb/s is 100 ps, and the data signal transmitted is a combination of ones and zeroes ("01010101...0101010"), then the cyclic change or time period of the data pattern "01" occurs every 200 ps (Figure 1-3d). This means that the highest data frequency in terms of cyclic voltage change is 5 GHz which is known as the Nyquist frequency or fundamental frequency. In other words, the Nyquist frequency in a NRZ communication circuit is calculated by dividing the baud rate by two but the measure is in Hertz instead of bits-per-second.

Equalizer circuits are designs that take under consideration the Nyquist frequency. For USB 3.0 devices that transmit at a baud rate of 5 Gb/s, the Nyquist frequency is 2.5 GHz. For USB 3.1 devices that transmit at a baud rate of 10 Gb/s, the Nyquist frequency is 5 GHz. For the PCIe® 3.0 devices that transmit at a baud rate of 10 Gb/s, the Nyquist frequency is 5 GHz. This thesis proposes a design that works at a Nyquist frequency of 30 GHz. Therefore, the maximum transmission data rate of this thesis circuit is 60 Gb/s.

An important observation made is that if data is sent over a line with a baud rate of 60 Gb/s, the random data may take a form of any frequency of frequencies below 30 GHz.

## 1.3 Transmission Reliability, 8b/10b Data Symbols Coding, and Transfers per Second (T/s) Measurement

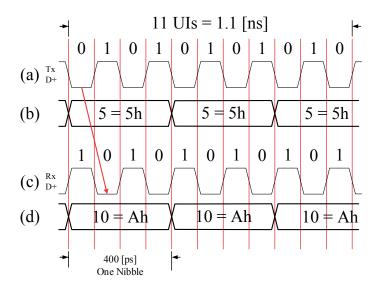

In PCIe® 3.0 or USB 3.0, for every 8 bits (1 Byte) transferred, an additional 2 bits are added to increase the reliability of the read data. This is done in an effort to increase the reliability of the transmitted data by encoding bytes in the following manner. A combination of 8 serial bits (one serial Byte) is known as a *data symbol*. The total number of combinations of data symbols in one transmitted Byte is 2<sup>8</sup> or 256 symbols. The symbols range from decimal values 0 to 255. However, there are symbols that may look similar to the receiver. For example, symbol "01010101" may be seen by the receiver as "101010101" or symbol "00100101" may be confused by the receiver as "01001010" or "10010010" if the receiver is reading the data signal at the wrong time. In

other words, if a receiver buffers serial data every nibble<sup>3</sup> is received, and if the serial data is a series of nibbles with the bit value of 5b or hexadecimal value of 5h, then by just shifting the data by one UI the receiver will buffer the data with the wrong bit value of 10b or hexadecimal value of Ah (Figure 1-4).

Example of Received Data if the Data Signal is Shifted by One UI. (a) Transmitted Data

Example; (b) Decimal and Hexadecimal Values of Transmitted Data (a); (c) Example of

Received Data Wrongly Shifted by One UI; and (d) Decimal and Hexadecimal Value of

Buffered Data (c)

One way to minimize the error in the data received, or to increase the reliability of the data received, is by adding a couple of bits to the serial symbol to create a larger number of combinations which creates a total of  $2^{10}$  or 1024 combinations instead of the

8

<sup>&</sup>lt;sup>3</sup> A nibble is four bits or half a Byte. Data with nibble bits [0101b] has a bit value of 5 or a hexadecimal value of Ah. The letter "b" (bit power number) and letter "h" (hexadecimal power number) abbreviates the power number. No letter after the number indicates the number is the decimal power form.

256 valid data combinations. The probability of error is reduced by decreasing the possible valid outcomes from a universe of 1024 combinations.

The PCIe® 3.0 and USB 3.0 (Gen 1) architecture uses the 8b/10b data symbol coding per ANSI X3.230-1994 (also refereed as ANSI INCITS 230-1194) specification (see Table 1-1). As mentioned above, for every Byte of serial information, a couple of bits are added hence creating 1024 possible combinations whereby only 256 combinations are valid. Every Byte valid data combination is given a *data Byte name*. Every bit in the valid Byte is given a letter designation from letter "A" to letter "H." The encoder inserts a bit "L" between the letters "E" and "F" and inserts a bit "J" after the letter "H" to create the 10 bit.

For example, eight bits or one byte is represented by " $b_7b_6b_5b_4b_3b_2b_1b_0$ " where  $b_7$  is the most significant bit (MSB) and  $b_0$  is the least significant bit (LSB). Each bit is assigned a capital letter:  $[b_7b_6b_5b_4b_3b_2b_1b_0] = [H G F E D C B A]$ . If most of the bits are zeroes, then the *Running Disparity* (RD) of the symbol sequence on a per-lane basis is considered negative; else, most of the bits are ones and the RD is positive; otherwise there are an equal amount of ones and zeroes which means that the RD is zero. Data are scrambled every two bytes using the linear feedback shift register (LFSR) algorithm with the  $16^{th}$  degree polynomial  $x^{16} + x^5 + x^4 + x^3 + x^0$ . This means that bits 0, 3, 4, 5, and 16 are inverted and shifted.

After LFSR is applied, a couple of bits are inserted between  $b_4$  and  $b_5$  and after  $b_7$  to form:  $[b_9b_8b_7b_6b_5b_4b_3b_2b_1b_0] = [j h g f l e d c b a]$ —the inserted bits are represented

in red by lower case letters "j" and "l". Here is an example of several data symbols transmitted using the 8b/10b data symbol coding (see Table 1-1).

Table 1-1 An 8b/10b Data Symbol Coding for Serial Data Transmitted over USB 3.X and PCIe® 3.0. This Table only Shows Eight Data Byte Names out of More than 256 Allowable Coded Symbols

| Data<br>Byte<br>Name | Data<br>Byte<br>Value<br>[hex] | Bits<br>HGF EDCBA<br>[binary] | Current RD-<br>abcdeifghj<br>[binary] | Current RD+<br>abcdei fghj<br>[binary] |

|----------------------|--------------------------------|-------------------------------|---------------------------------------|----------------------------------------|

| D0.0                 | 00                             | 000 00000                     | 100111 0100                           | 011000 1011                            |

| D1.0                 | 01                             | 000 00001                     | 011101 0100                           | 100010 1011                            |

| D2.0                 | 02                             | 000 00010                     | 101101 0100                           | 010010 1011                            |

| D3.0                 | 03                             | 000 00011                     | 110001 1011                           | 110001 0100                            |

| D4.0                 | 04                             | 000 00100                     | 110101 0100                           | 001010 1011                            |

| D5.0                 | 05                             | 000 00101                     | 101001 1011                           | 101001 0100                            |

| D6.0                 | 06                             | 000 00110                     | 011001 1011                           | 011001 0100                            |

| D7.0                 | 07                             | 000 00111                     | 111000 1011                           | 000111 0100                            |

The transfers per second (T/s) measure relates to the effective transfer rate of valid bits per second. In the 8b/10b data symbol coding, for every 10 bits transmitted, only 8 bits are valid. Therefore, the effective transmission rate is 8-bits in a time allocated for 10-bits. If the transmitter transmits at a rate of 5 Gb/s, the Transfers per second is calculated as follow:

$$\left(5\left[\frac{Gb}{s}\right]\right)\left(\frac{8\left[T\right]}{10\left[b\right]}\right) = 4\left[\frac{GT}{s}\right] \tag{1-2}$$

Perhaps the most important data Byte name in the 8b/10b data symbol coding is "D10.2." Although its 8-bit input is "01001010b," the 10-bit output is "0101010101b"

which is the Nyquist frequency. There is no other 8-bit symbol that can create the pattern "0101010101." In the event that the pattern is seen shifted as "1010101010," the receiver will shift the data by one UI and assume that the correct data was symbol "D10.2."

Although the 8b/10b data symbol coding is effective to increase the reliability of the received signal, the system slows down the rate at which useful data is transmitted. In the event that the 8b/10b data symbol coding is used in a 20 Gb/s transmission line, the actual transfer rate is 16 GT/s. Every second, 4 Gb are discarded. This represents 20% of the transmission time is used to pass invalid data.

The 8b/10b coding is normally used for data transfer rates of less than 5 Gb/s.

USB 3.1 (Gen 2) uses a 128b/132b line encoding to transmit serial frames at a rate of 10 Gb/s which means that its Nyquist or fundamental frequency is 5 GHz. Each frame contains data and control information. Each frame is made of a 4-bit header and 12-bit payload. The 4-bit header identifies whether the frame is for data ("0011b")4 or control ("1100b"). As frames are received, data is aligned into 128 block; each block is made of 132 bits. Description of the transmission frame is beyond the scope of this thesis.

However, it can be said that the effective data transfer to an application after the serial data has been decoded can be as high as 9.6 GT/s.

### 1.4 USB 3.1 Architecture Impact on Future Electronic Equipment

To understand the impact that USB and PCIe® have over the present electronic technology, a historical background is needed. Beginning with USB architecture, the USB serial interfaces replaced slow speed parallel interfaces used by printers and other

11

<sup>&</sup>lt;sup>4</sup> The letter "b" at the end of the bit sequence indicates that this is a binary number.

parallel interfaced devices that connected to desktops or laptop computers. Since 1996, USB version 1.0 technology has allowed consumer electronics devices to become more portable because USB technology replaced the bulky parallel interfaces or ports. The 25 pin printer ports were quickly replaced by 4 pin USB ports. The USB version 1.0 technology only supported data transfer rates (also known as "baud rates") from 10 kb/s to 10 Mb/s.<sup>5</sup> As a result, the USB 1.0 technology could only be used by a limited array of consumer devices such as keyboards, game peripherals, e.g. joysticks, and audio devices. In other words, a 4 MB song or picture can be transferred between two USB 1.1 devices in 5.3 seconds but in contrast a 25 GB high definition (HD) movie would take about 9.3 hours to be transferred.

One of the most important attributes of the USB interface technology is its easeof-use among portable device users because it allows the end user the capability of using plug-and-play devices capable of self-configuring when connecting to a computer. Older technology such as parallel interfaces required a more complex hardware and software implementation. The second most important attribute is its port physical size, cost, and device adaptation. The USB port expansion attribute allowed manufacturers to design and adapt devices that were considered low-speed devices such as a keyboard to use the same port interface of a mid-speed devices for instance a storage devices.

Nevertheless, innovations in technology, for example the invention of submicron technology, 6 enabled the possibility to design faster serial interfaces because such

<sup>&</sup>lt;sup>5</sup> For purposes of this thesis, all data rates or baud rates are measured in bits per second (b/s). A small letter "b" represents bits while an upper letter "B" represents bytes.

<sup>&</sup>lt;sup>6</sup> A submicron technology is a technology whereby the smallest transistor length is below 1 μm.

technology can operate with a higher frequency bandwidth. A USB version 3.0 interface allows devices to transfer a 4 MB song or picture in just 10 milliseconds or a 25 GB HD movie in just 70 seconds because under this standard revision the transmission bout rate can reach 5 Gb/s or 4 GT/s. As of 2014, USB version 3.0 gave the possibility to vide stream high definition video between two USB 3.0 devices. As a result, the higher speed serial communication that resulted from the USB 3.0 specification expanded its market opportunity to a variety of consumer devices such as digital cameras and camcorders, flash-based digital media and video players, smart phones, etcetera.

Because consumers are now constantly relying on portable devices such as smart phones, portable storage devices, and other portable devices, consumers have to recharge or power these devices. Under the USB 3.0 standard there is an added functionality to power devices that require power management. Power management is the ability to provide power to a device only when the device requires it, thus conserving energy.

Consumers value the importance of buying electronic devices that have the USB 3.0 interface with hardware applications that include having external mass storage devices used to stream high definition video.<sup>7</sup> As of 2014, the USB standard organization has projected a shipment of more than 4,250,000,000 USB devices worldwide.

According to a Global Industry Analysts Inc. (GIA)<sup>8</sup> detailed market report, the USB 3.0

<sup>&</sup>lt;sup>7</sup> Western Digital, a portable media drive manufacturer, markets a line of USB 3.0 portable hard drives of the size of a travel passport and capable to store up to 150 hours of high definition digital movies in 2TB capacity.

<sup>&</sup>lt;sup>8</sup> According to MarketResearch.com, "Global Industry Analysts, Inc., (GIA) is a leading publisher of off-the-shelf market research. Founded in 1987, the company currently publishes more than 1300 full-scale research reports and analyzes 40,000+ market and technology trends while monitoring more than 126,000 Companies worldwide. GIA is recognized today as one of the world's largest and reputed market research firms serving over 9500 clients in 27 countries."

market is yet to render its full potential since its technology is predicted a global increase of sales of as many of 3 Billion USB 3.0 enabled devices by 2018 which will result in revenues in the tenths of trillions of dollars [1] Global Industry Analyst, Inc. *USB* 3.0 – A Global Strategic Business Report. March 2013.

The Universal Serial Bus 3.1 Specification was released by the USB Implementers Forum, Inc., on July 26, 2013. The SuperSpeed USB 3.1 delivers baud rates of 10 Gb/s. As of March 2014—when this thesis was written—no published or manufactured microcircuit components that would satisfy this standard were found. This specific standard offers a solution to users to exchange large files between devices in minutes while maintaining power management efficiency.

The USB 3.1 technology is still considered a deployed emerging technology with possibilities of implementation in new USB Flash Drives by 2015, USB Hub devices, on-the-fly Encryption for External USB devices, medical devices, automotive industry, etc.

The fact that these implementations have yet to be created by 2014 suggests that there are still challenges in implementing the USB 3.1 that near the 10 Gb/s transfer rates.

### 1.4.1 USB Technology Transfer Rates

The USB standard is maintained and regulated by the nonprofit corporation called USB Implementers Forum, Inc. (<a href="www.usb.org">www.usb.org</a>). The corporation was formed by companies that developed the USB standard whose main goal is to promote the benefits of using USB peripherals in high speed serial communication. These companies are Hewlett-Packard (DBA HP), Intel Corporation, LSI Corporation, Microsoft Corporation,

Renesas Electronics, and STMicroelectronics. USB Implementers Forum, Inc., created and supports the following standards:

- (a) SuperSpeed+ USB 3.1

- (b) SuperSpeed USB 3.0

- (c) Wireless USB (WUSB)

- (d) On-The-Go Hi-Speed USB

- (e) On-The-Go Basic-Speed USB

- (f) Hi-Speed USB

- (g) Basic-USB

- (h) ExpressCard®<sup>9</sup>

USB version 1.0 was released providing two data speeds: 1.5 Mb/s and 12 Mb/s.

USB 1.0 was limited to interface with keyboard, printers, and similar interface devices.

As personal computers (PCs) became smaller and more portable, users demanded a wider range of interface connectivity which included portable storage media—commonly known as memory sticks or thumb drives. To address this demand, the USB

Implementers Forum, Inc. released the USB 2.0 specification in the year 2000 that allowed not only backward-compatibility but also increased the serial transfer rate to 480 Mb/s. Five years later, in 2005, demand for free-of-all-wires wireless technology inspired the release of Wireless USB making the USB peripheral the most used and versatile PC peripheral in the world.

\_

<sup>&</sup>lt;sup>9</sup> The ExpressCard® standard was created by PCMCIA Association member companies formed by Dell, Hewlett Packard (DBA HP), IBM, Intel, Lexar Media, Microsoft, SCM Microsystems and Texas Instruments (DBA TI) with a collaboration and assistance of the USB Implementers Forum, Inc., and the collaboration of the Peripheral Component Interconnect-Special Interest Group (a.k.a. PCI-SIG).

The year of 2006 became the year where the world was entered the age of smart mobile technology. Products such as smart phones, the iPad, the notebooks, and book readers became an everyday household item. The word "USB" became a popular word and advances in network routing and communication were necessary to provide connectivity service to what was then 2 billion USB devices. USB 2.0 adopted network routing technology similar to what is used in Ethernet network communications to allow USB devices negotiate with one another for the purpose of self-setup and speed up communication in shared USB architectures. The On-the-Go USB communication relies on USB hosts, USB servers, and USB hubs that follow the 4 layer USB transmission protocol rules. By using a USB protocol, the communication capability extended the consumer market of the USB serial port to industrial applications and security systems.

By the year 2011, consumers were hungry for shared content products capable to video stream on demand, or store large amounts of information. High definition photography, HD camcorders, and similar devices required storage spaces that were in the tenths of Giga Bytes. Transmission rates of large amount of data required a faster than the available 480 Mb/s transfer rates. This was resolved by introducing SuperSpeed USB 3.0 to free users from the consuming process of transferring large amounts of information. The transmission rates of a SuperSpeed USB 3.0 connection can provide transfer rates of up to 5 Gb/s.

Currently, the State-of-the-Art communications demand faster transfer data rates for the USB interface. In August 2013, the USB Implementers Forum, Inc. completed the SuperSpeed+ USB 3.1 standard to enable transmission data rates of up to 10 Gb/s.

However, by the first quarter of 2014, the author was not able to find any manufacturer that had implemented a SuperSpeed+ USB 3.1 solution.

It is argued that if a SuperSpeed USB 3.0 architecture design has an adaptive receiver front-end implementation, then it is possible that the receiver may improve the common inter-symbol interference (ISI) created by the transmission line between the transmitter and the receiver.

#### 1.4.2 The SuperSpeed USB 3.0 Standard

The SuperSpeed USB 3.0 standard [2] is compatible to earlier revisions of the USB standard. However, to support higher transmission rates, an additional 5 wires were added to the USB 3.0 transmission line. A USB 2.0 plug has 4 terminals while a USB 3.0 has 9 terminals.

The SuperSpeed (SS) USB 3.0 standard supports data rates of up to 5Gb/s. As of the first quarter of 2014, the SS USB3.0 standard is a deployed technology that has both software and hardware support for consumers. However, the USB Implementers Forum, Inc., recently introduced the new SuperSpeed+ USB 3.1 standard that supports up to 10GB/s transfer rates.

### 1.4.3 The SuperSpeed+ USB 3.1 Standard

The SuperSpeed+ USB 3. Standard [3] is a backward compatible standard that supports data rates of up to 10 Gb/s and enhanced data encoding efficiency. The standard allows data rated commonly found in Solid State Drives (SSDs) and High Definition (HD) displays. This standard introduces the term "Gen 1," which is used to reference the receiver front end architecture and data requirements for the USB 3.0 standard to receive

a 5 Gb/s signal. The term "Gen 2" describes the receiver front end design for the SuperSpeed+ USB 3.1 that allows baud rates of 10 Gb/s or effective data rate of as high as 9.6 GT/s. The term "Gen X" refers to either Gen 1 or Gen 2 architectures.

#### 1.4.4 USB 3.0 and USB 3.1 Specification Standard Documentation

This thesis project and proposal were inspired in part by the Universal Serial Bus 3.0 Specification which included errata and Engineering Change Notices (ECNs) through May 1, 2011, Revision 1.0, June 6, 2011 [2]. Detailed specifications for the equalizer design are described by the USB 3.0 SuperSpeed Equalizer Design Guidelines documentation and by the Universal Serial Bus 3.1 Specification provided by the USB Implementers Forum, Inc.

The authors of the USB 3.0 specification include the following companies: Hewlett-Packard Company, Intel Corporation, Microsoft Corporation, NEC Corporation, ST-Ericsson, and Texas Instruments. The authors for the USB 3.1 specification include the following companies: Hewlett-Packard Company, Intel Corporation, Microsoft Corporation, Renesas Corporation, ST-Ericsson, and Texas Instruments.

The USB 3.0 standard augments the basic architectural design of the USB 2.0 standard in functionality and data transmission rate. The USB 3.0 physical connection is backwards and forward compatible. The USB 3.1 equalizer specification is different for Gen 1 and Gen 2. The USB 3.0 and USB 3.1 standard defines a composite cable whereby four of the lines are dedicated to support backwards compatibility to USB 2.0 and an additional five lines are used to provide the extended functionality of the USB 3.0 interface.

### 1.4.5 USB 3.0 and 3.1 Physical Interface Architecture

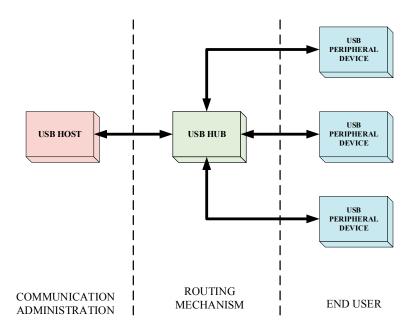

The USB 3.0 and USB 3.1 has adopted standard network communication terminology and similar design organization as used in more mature and stable technology such as Ethernet Communication Networks. The USB 3.0 communication is arranged with a *star topology*. This means that *point-to-point* communications between USB *ports* require that one port act as a *host port* while the other port act as a *peripheral device port*. USB *hubs* may be used to drive and route communications between a USB host and a USB peripheral device (Figure 1-5).

\_

<sup>&</sup>lt;sup>10</sup> The terms "star topology," "host," and "point-to-point" are common technical terms used in the network communication industry and definition and description of these terms are outside the scope of this thesis. To have a better technical understanding of these terms, the reader is advised to read recommended training material from the Computing Technology Industry Association (CompTIA) at <a href="www.comptia.org">www.comptia.org</a>. The term "peripheral device port" is a term compatible to the term "user port" as commonly used between network communication designs that is based on layered protocol architecture.

#### **USB STAR COMMUNICATION TOPOLOGY**

Figure 1-5 Overall Block Diagram for the USB 3.0 Physical Layer Design

# 1.4.6 Standard Definition of the USB 3.0 Transmission Channel, the Full Link Channel Model

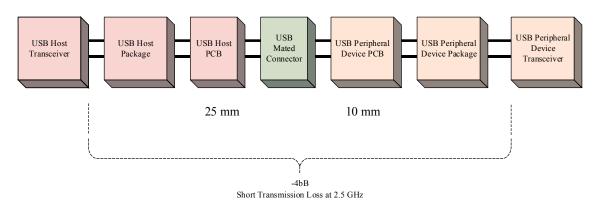

When two electronic devices use a USB wire interface, they must be interconnected directly through USB connectors (hereon referred as a "short channel")—without a cable—or via USB connectors and a differential cable that is no longer than 3 meters long (hereon referred as "long channel"). The front end design must be able to either meet the short channel design specifications or meet both the short and long channel specifications.

A short channel interface consists of the wires from the USB transmitter to the die pads, the connection from the die pad to the mother board—these connections pertain to

the component package—followed by the Printed Circuit Board (PCB) connections to the USB connector, the connector and its mate, the PCB wire connection from the mate connector to the receiver component package, the component package connections to the receiver die pads, and the connection between the die pad to the USB receiver (Figure 1-6).

Figure 1-6 USB 3.0 and USB 3.1 Short Channel Application Range

The USB 3.0 standard specifies a maximum attenuation of -4dB between the USB Host Transceiver to the USB Peripheral Device Transceiver at the fundamental transmission frequency of 2.5 GHz.

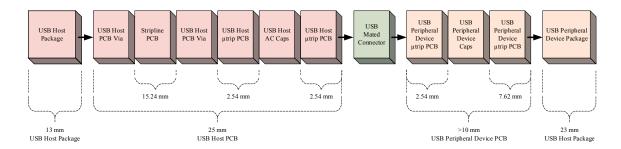

A detailed representation of the USB transmission for a short channel is defined as *the full link short channel model* (Figure 1-7).

Figure 1-7 Full Link Model for Short Channel Application Range on USB 3.0 and USB 3.1

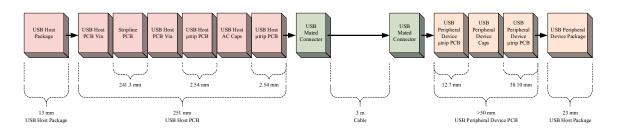

As mentioned above, a long channel model includes a three meter connector and a device connector the host connector and the device. The long channel full link model PCB striplines<sup>11</sup> are longer than the striplines used in the short channel (Figure 1-8).

Figure 1-8 Full Link Model for Long Channel Application Range on USB 3.0 and USB 3.1

22

<sup>&</sup>lt;sup>11</sup> The term *stripline* refers to a type of transmission line used in PCB designs whereby the transmission line is contained within the PCB substrate and sandwiched between two ground planes to minimize electromagnetic interference (EMI) or white noise.

# 1.5 2014 State of the Art Circuits in Analog Front-End Design for Gb/s Wireline Receivers

Front-end design refers to the transmitter or receiver end of the microcircuit design. This thesis concentrates on the receiver front-end microcircuit design.

According to the International Solid-State Circuits Conference (ISSCC), a group of the Institute of Electrical and Electronics Engineers (IEEE), the highest Nyquist frequency in fast speed communication between devices is 30 GHz [4]. However, stable designs in the industry achieve Nyquist frequencies of no more than 2.5 GHz. For example, the Texas Instruments (TI) DS125BR820 is a low-power 12 Gbps 8-channel liner repeater with equalization, the TI TLK2711-SP is a 1.6 Gbps to 2.5 Gbps Class V Transceiver, the TI DS100BR111A is an ultra-low power 10.3 Gbps 2-channel repeater with input equalization. Fujitsu reported at the annual ISSCC conference to have achieve the world's fastest transceiver of 32 Gbps for inter-processor data communication on February 18, 2013 [5].

### 1.5.1 Technology Challenges

Signal degradation increases as the transmission rate increases because the channel attenuation increases due to an increase in channel impedance. As a result, equalizer circuits are needed to compensate for the loss in the signal.

Semiconductor technology has limitations as to the highest frequency it can amplify. Equalizers must be able to match the loss of the signal by amplifying its signal. This thesis will describe how to determine the highest frequency for the 28 nm complementary metal-oxide semiconductor (CMOS) technology. Amplifiers have a

limited frequency bandwidth for amplification which is limited by the smallest intrinsic length property of the CMOS transistor.

Power consumption increases as the Nyquist frequency increases. Power dissipation and minimum power limitations may dictate the maximum baud rate.

The loss of the signal is increased as the transmission line length is increased because the overall resistivity of the signal is increased. Signal crosstalk and reflections are minimized by shielding the line and terminating the line with the correct impedance matching respectively. However, for USB technologies, the length of the transmission wire is variable while the impedance matching at the receiver end is fixed.

### 1.5.2 State of the Art Equalizer Circuits

This section illustrates the latest advances in equalizer circuitry. Most of the circuits described here were demonstrated at the 2014 International Solid-State Circuits Conference held every year in San Francisco, California.

### 1.5.2.1 28 Gbps 560 mW Multistandard Equalizer in 28 nm CMOS

This is a high-speed Continuous Time Linear Equalization-only (CTLE) equalizer [6] that operates at transmission baud rate of 28 Gbps or at a maximum Nyquist frequency of 56 Ghz in a 28 nm CMOS technology.

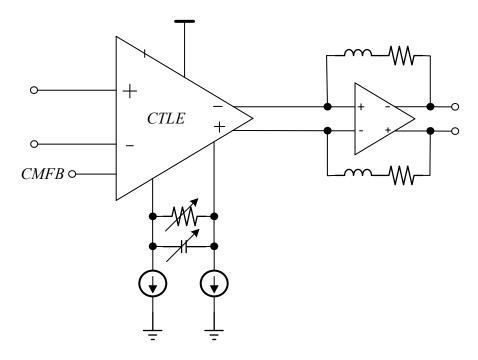

The analog front end (AFE) design is a comprised of a CTLE and a second stage amplifier with inductive bust. It is not clear from the paper how the resistance and the capacitance is varied in the CTLE circuit bit this type of circuit creates a boost at the Nyquist frequency (Figure 1-9).

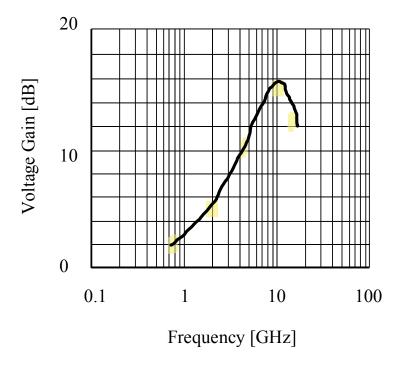

Figure 1-10 shows the transimpedance gain<sup>12</sup> of a little bit less than 15 dB for the AFE design at a Nyquist frequency of 10 Ghz. However, it is not clear from the white paper as to what is the effective amplification of a Nyquist signal at 56 GHz.

CMFB: common-mode feedback

Figure 1-9 Analog Front End (AFE) Design of a Receiver CTLE Equalizer. Figure Adapted by

Author from [6]

It is important to note that this design relies on the fact that 28 nm CMOS technology allows for the amplification of frequencies as high as 60 GHz. This thesis will show how this frequency is measured.

<sup>12</sup> The transimpedance gain is the relationship between the system output voltage with respect to the system input current. This is also known as the Y-parameter.

It is assumed that the insertion loss of the channel is 36 dB at Nyquist frequency of 56 GHz. The insertion loss is typically given as a voltage loss. The equalizer is assumed to amplify the signal loss created by the channel. Ideally, the amplification of the AFE should have been given in terms of voltage amplification terms rather than a transimpedance gain to see if the equalizer is compensating for the loss.

Figure 1-10 Transimpedance Gain. Frequency Response for the AFE. Figure Created by Author from Data in [6]

### 1.5.2.2 25 Gbps 5.8 mW CMOS Equalizer in 45 nm CMOS

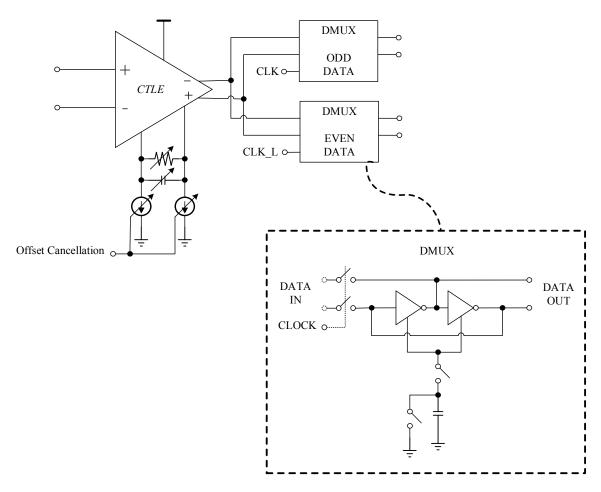

This design was made in part by Professor Behzad Razavi, a worldwide well-recognized CMOS design instructor at the University of California. Won Jung and Razavi's approach was to create an AFE design [7] powered by a 1 V power supply. The AFE consists of a CTLE that feeds to a linear de-multiplexer (DMUX) that has sufficient

bandwidth to operate at the Nyquist frequency of 50 GHz. The CTLE equalizer is clamed to boost 8 dB at high frequency though inductive peaking.

Figure 1-11 Transimpedance Gain. Frequency Response for the AFE. Figure Adapted by Author from [7]

### 1.5.2.3 16 Gbps 4 mW CMOS Desition Feedback Equalizer in 65 nm CMOS

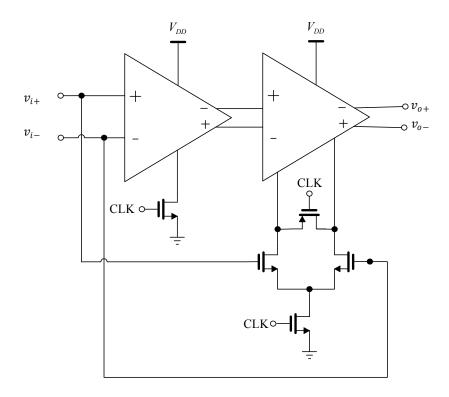

This circuit claims to "improve the energy efficiency of power-constrained systems" [7] Won Jung and Razavi, *A 25 Gb/s 5.8 mW CMOS Equalizer*. (Reference [4] Session 2.4) [8] by incorporating a low voltage charge-based latch and a charge-based sample-and-hold (S/H) (Figure 1-12). This particular circuit depends on a switching

clock (CK) to sample the transmitted signal UI. The implications are that the clock must be aligned to the input signal. The switching clock must be detected using a clock recovery circuit which is not represented by this system.

Figure 1-12 Charge-Based Sample-and-Hold (S/H) with Clocked Adaptive Loads. Figure Adapted by Author from [7]

# 1.5.2.4 25 Gbps 90 mW Power-Scalable with Tunable Active Delay Line Equalizer in 28 nm CMOS

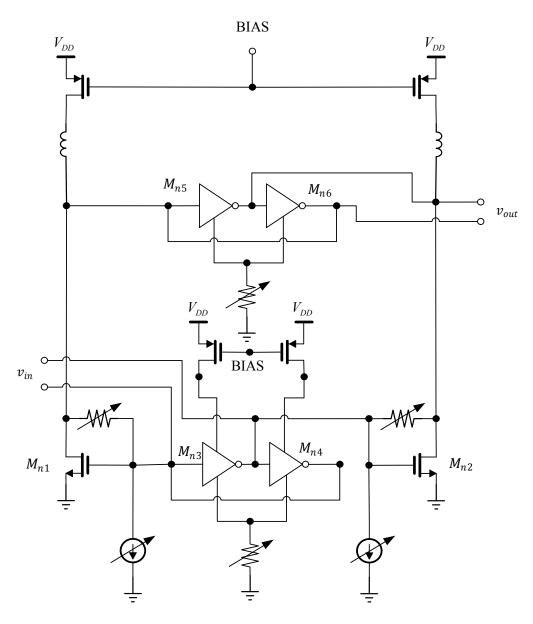

This section describes a cost effective adaptive equalizer circuit design to compensate for the channel loss variations found commonly in multi-mode fiber (MMF) channels. Figure 1-13 illustrates a common source transimpedance amplifier or active circuit with peaking inductors [9]. This circuit is capable to program its bandwidth and

gain dissipation. The CMOS gain  $(g_m/g_{ds})$  for the common source transistors  $(M_{n1}$  and  $M_{n2})$  is approximately 5.

Negative resistance is applied to the output by circuits with transistors  $M_{n3}$ ,  $M_{n4}$ ,  $M_{n5}$ , and  $M_{n6}$  to cancel the output inductance. As a result, it allows the circuit to have a 2.5 times trans-resistance result with half times the input noise.

Figure 1-13 Trans-Impedance Equalizer. Figure Adapted by Author from [9]

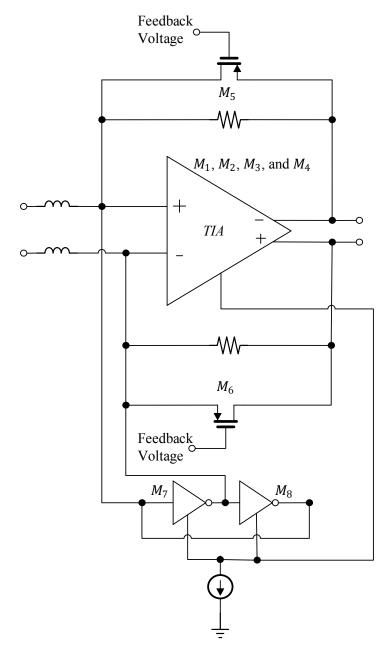

# 1.5.2.5 28 Gbps 28.8 mW Trans-Inductance Amplifier (TIA) Equalizer in 28 nm CMOS

A CMOS TIA equalizer circuit [10] allows for high signal gain with a low power supply. However, this circuit is sensitive to supply noise due to its high gain (Figure 1-14). The circuit shows a push-pull TIA with series-peaking inductors ( $L_{IN}$ ). The source current tail ( $I_B$ ) makes the transconductance gain ( $g_m$ ) of transistors  $M_1$ ,  $M_2$ ,  $M_3$ , and  $M_4$  refer to the bias current as a substitute of the supply voltage which allows for a better noise reduction. Transistor  $M_7$  and  $M_8$  act as a common-source amplifier that provides negative voltage gain through the feedback resistor ( $R_F$ ). Transistors  $M_5$  and  $M_6$  act as an active variable capacitor and controlled by the feedback voltage ( $V_F$ ).

Figure 1-14 Pseudo-Differential CMOS Push-Pull Trans-Impedance Equalizer. Figure Adapted by

Author from [10]

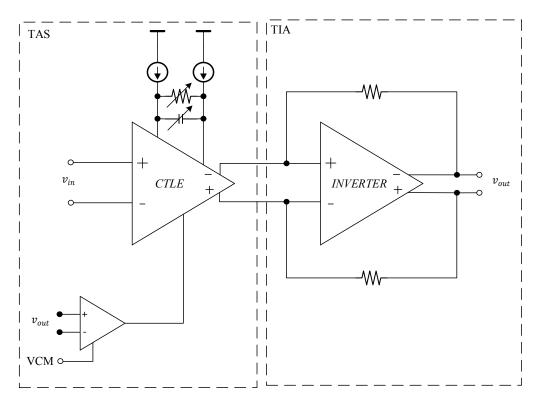

# 1.5.2.6 20 Gbps 0.9 mW Trans-Admittance Stage (TAS) Trans-Inductance (TIA) CTLE in 28 nm CMOS

The TAS-TIA single stage CTLE circuit (Figure 1-15) [11] allows low impedance at the TIA input and output. The circuit gain is approximately the TAS transconductance gain ( $g_{m,TAS}$ ) multiplied by the CTLE resistance feedback (R). The reported gain peaking at 8.5 GHz is 8 dB. The TAS acts as a first stage source-degenerated PMOS circuit that provides the main boosting at Nyquist frequency. The receiver CTLE is programmable by controlling the input voltage to the TIA ( $V_X$ ). The CTLE boosts high frequency signals to compensate for the channel loss. Low output impedance to the TAS is achieved by an active-shunt load controlled by a CMOS inverter feedback (CMFB).

Figure 1-15 TAS-TIA CTLE. Figure Adapted by Author from [11]

### 2 Channel Model

The communication link between a transmitter and a receiver is called the *transmission line* or *communication channel*. In the case of the USB 3.1 or PCIe® standards, the connection between the transmitter and the receiver is called the *transmission channel* or simply "the channel". The channel is composed of many parts as described in section 1.4.6 herein, but a more simplistic model can be modeled to test the design as proposed in this thesis.

### 2.1 Types of Printed Transmission Lines

There are six commonly used basic types of printed transmission lines used in the industry and each basic type has respective modifications:

- (a) Microstrip lines

- (1) Suspended microstrip line

- (2) Inverted microstrip line

- (3) Shielded microstrip line

- (b) Striplines

- (1) Double-conductor stripline

- (c) Suspended striplines

- (1) Shielded suspended stripline

- (2) Shielded suspended double-substrate stripline

- (d) Slotlines

- (1) Antipodal slotline

- (2) Bilateral finline

- (e) Coplanar waveguides

- (1) Shielded coplanar waveguide

- (f) Finlines

- (1) Bilateral slotline

- (2) Antipodal finline

- (3) Antipodal overlapping finline

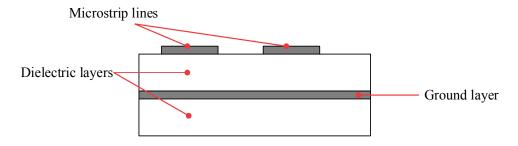

Each type of transmission line differs from one another based on their dimensional parameters and electrical properties. For purposes of modeling a transmission line, this thesis will focus on the microstrip lines which have a single transmission line geometry made of a single conductor trace separated from a ground plane by a dielectric substrate (Figure 2-1).

Figure 2-1 Typical Microstrip Line Configuration for Differential Transmission Lines

Assuming the connection between the transmitter and the receiver is a single straight microstrip line with 10 mm length, and the microstrip material is cupper, then it can be assumed that the microstrip line has a resistance associated with the resistivity of the material. The resistivity coefficient of copper is  $168 \times 10^{-18} \frac{\Omega}{m}$ . Therefore, every millimeter of microstrip line has a resistance of  $16.8 \times 10^{-12} \Omega$  (Equation (2-1).

$$(1)[mm](168)(10^{-18})\left[\frac{\Omega}{m}\right]\frac{(1)[m]}{(1000)[mm]} = 16.8 \times 10^{-12} \left[\Omega\right]$$

(2-1)

However, the microstrip line has an interelement capacitance between the stripline and the ground plane and an interelement capacitance between the microstrip lines (Figure 2-2). As a result, the interelement capacitance creates a system whereby its impedance is affected by the signal frequency. At low frequencies or d.c. voltage, the interelement capacitance is negligible. However, at data rates where signals approach the 10 GHz or above, the interelement capacitance increases the impedance of the transmission line to such extent that the signal is greatly attenuated.

Figure 2-2 Microstrip Lines Interelement Capacitance

The interelement capacitance and resistivity of the microstrip material have an impedance that varies with the voltage frequency of the signal. The capacitance depends on the geometrical factors of the microstrip line and the dielectric permittivity between metals. As a result, creating a precise model for the microstrip line in a computer aided design (CAD) tool is outside the scope of this thesis. However, a simple model can be created by comparing the measured results of microstrip lines.

### 2.2 The FR4 Microstrip Wire Line