## San Jose State University SJSU ScholarWorks

## Master's Theses

Master's Theses and Graduate Research

2003

# A survey of hardware design verification

Liping Guo San Jose State University

Follow this and additional works at: https://scholarworks.sjsu.edu/etd theses

## **Recommended** Citation

Guo, Liping, "A survey of hardware design verification" (2003). *Master's Theses*. 2442. DOI: https://doi.org/10.31979/etd.6v4h-e6xv https://scholarworks.sjsu.edu/etd\_theses/2442

This Thesis is brought to you for free and open access by the Master's Theses and Graduate Research at SJSU ScholarWorks. It has been accepted for inclusion in Master's Theses by an authorized administrator of SJSU ScholarWorks. For more information, please contact scholarworks@sjsu.edu.

## A SURVEY OF HARDWARE DESIGN VERIFICATION

A Thesis

Presented to

The Faculty of the Department of Computer Engineering

San Jose State University

In Partial Fulfillment

Of the Requirements for the Degree

Master of Science

by

Liping Guo

August 2003

## UMI Number: 1417478

## INFORMATION TO USERS

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

UMI Microform 1417478

Copyright 2004 by ProQuest Information and Learning Company. All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

> ProQuest Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

© 2003

Liping Guo

## ALL RIGHTS RESERVED

## APPROVED FOR THE DEPARTMENT OF COMPUTER ENGINEERING

Dr. Donald L. Hung

Scinon the Dr. Simon Shim

Dr. Xiao Su

## APPROVED FOR THE UNIVERSITY

Joseph Perel

## ABSTRACT

## A SURVEY OF HARDWARE DESIGN VERIFICATION

by Liping Guo

The move from schematic-based design to hardware description language-based design has enabled hardware designers to easily manage the complexity of designs that were impossible to handle by manual methods. However, barely a decade after this revolutionary design methodology shift, today's hardware development industry is facing a more severe challenge. The main cause of this is that the complexity of state-of-the-art hardware devices is climbing much faster than the capacity of the techniques and tools that are used to verify them.

In the past few years, due to the effort from both academia and industry, verification techniques and tools have advanced in many ways but a fundamental breakthrough in hardware verification methodology has not yet arrived.

This thesis report presents a general survey of hardware design verification. Four important aspects of hardware design verification are covered by the survey: simulation acceleration, simulation vector generation, verification environment construction, and cosimulation in co-design.

## ACKNOWLEDGEMENTS

I would first like to express my sincere appreciation to my advisor, Professor Donald L. Hung, for leading me into this interesting field and acting as my intellectual lighthouse throughout the thesis work. This thesis would not have been possible without his constant guidance and encouragement.

I would also like to thank my thesis committee members, Professor Simon Shim and Professor Xiao Su, for their valuable feedback and insightful comments.

At the final stage of my thesis work, Prasanth Kumar gave me great help by proofreading my thesis. I would like to thank him for his kindness and friendship.

Finally, I want to take this chance to thank my husband, Dr. Min Zhong. With his inexhaustible patience, he has supported me unconditionally through the ups-and-downs during my shift from Chemistry to Computer Engineering. I would not have come this far without his precious love and advice.

v

## TABLE OF CONTENT

| LIS | ST OF | FIGURES                                                            | viii |

|-----|-------|--------------------------------------------------------------------|------|

| LIS | ST OF | TABLES                                                             | ix   |

| 1   | INT   | RODUCTION                                                          |      |

| ~   | 1.1   | The Hardware Development Crisis                                    |      |

|     | 1.2   | Motivation and Goals.                                              |      |

|     | 1.3   | Scope of the Thesis                                                |      |

|     | 1.4   | Thesis Outline                                                     |      |

| 2   | BA    | CKGROUND                                                           |      |

|     | 2.1   | Introduction                                                       |      |

|     | 2.2   | Simulation-based Verification                                      |      |

|     |       | 2.2.1 Software-only Simulation                                     | 7    |

|     |       | 2.2.2 Hardware-accelerated Simulation                              | 10   |

|     |       | 2.2.3 In-circuit Emulation                                         | 11   |

|     | 2.3   | Formal Verification                                                | 13   |

|     |       | 2.3.1 Formal Methods                                               | 14   |

|     |       | 2.3.2 Formal Methods in Hardware Verification                      |      |

|     |       | 2.3.3 Formal Hardware Verification Tools                           | 18   |

| 3   | SIM   | ULATION ACCELERATION                                               |      |

|     | 3.1   | Introduction                                                       |      |

|     | 3.2   | Using Faster Simulators                                            |      |

|     | 3.3   | Using Simulation Server Farms                                      |      |

|     | 3.4   | Using Simulation-Emulation Co-operation                            |      |

|     |       | 3.4.1 Motivation                                                   |      |

|     |       | 3.4.2 Examples                                                     |      |

|     | 3.5   | Using Rapid Construction of Verification Environment               |      |

| 4   | SIM   | ULATION-VECTOR GENERATION                                          | 33   |

|     | 4.1   | Introduction                                                       | 33   |

|     | 4.2   | Borrowing Test Sets from Physical Fault Testing                    | 35   |

|     |       | 4.2.1 Motivation                                                   | 35   |

|     |       | 4.2.2 Examples                                                     |      |

|     | 4.3   | Simulation-vector Generation via Semi-formal Methods               |      |

|     |       | 4.3.1 Motivation                                                   |      |

|     |       | 4.3.2 Example: Coverage Guided Random-simulation-vector Generation | 38   |

|     |       | 4.3.2 Example: Coverage Guided Simulation Vector Transformation    |      |

|     |       | 4.3.3 Example: Other Semi-formal Approaches                        |      |

| 5   | VEI   | RIFICATION ENVIRONMENT CONSTRUCTION                                |      |

| 2   | 5.1   | Introduction                                                       |      |

|     | 5.2   | Hardware Verification Languages (HVL)                              |      |

|     |       | 5.2.1 Motivation                                                   |      |

|     |       | 5.2.2 Examples of the Existing HVLs                                |      |

|     |       | 5.2.2.1 DGL                                                        |      |

|     |       | 5.2.2.3 e-language                                                 |      |

|     |       | 5.2.2.4 Jeda                                                       | 47   |

|   |      |     | 5.2.2.5 Libero                                                         | . 48 |

|---|------|-----|------------------------------------------------------------------------|------|

| • |      |     | 5.2.2.6 Murphi                                                         | 48   |

|   |      |     | 5.2.2.7 RAVE                                                           | 49   |

|   |      |     | 5.2.2.8 Solidify                                                       | . 49 |

|   |      |     | 5.2.2.9 Spin                                                           | 50   |

|   |      |     | 5.2.2.10 SUPERLOG                                                      |      |

|   |      |     | 5.2.2.11 SystemC                                                       | . 51 |

|   |      |     | 5.2.2.12 SystemVerilog                                                 | . 51 |

|   |      |     | 5.2.2.13 SpecC                                                         |      |

|   |      |     | 5.2.2.14 TestBuilder                                                   |      |

|   |      |     | 5.2.2.15 OpenVera                                                      |      |

|   |      | 5.3 | The Reality of Industry-Standard Verification Languages                | . 54 |

|   |      | 5.4 | Layered Testbench Architecture                                         |      |

|   |      |     | 5.4.1 Motivation                                                       | . 56 |

|   |      |     | 5.4.2 Examples                                                         | . 57 |

|   |      | 5.5 | Verification Intellectual Property (VIP)                               | . 60 |

|   | 6    | CO- | SIMULATION IN CO-DESIGN                                                |      |

|   | •    | 6.1 | Introduction                                                           |      |

|   |      | 6.2 | Co-simulation Approaches                                               |      |

|   |      |     | 6.2.1 Requiring Processor Models vs. Requiring no Processor Models     |      |

|   |      |     | 6.2.1.1 Processor Models                                               |      |

|   |      |     | 6.2.1.2 Techniques Require Processor Model                             | . 73 |

|   |      |     | 6.2.1.3 Techniques Require No Processor Model                          | . 77 |

|   |      |     | 6.2.1.4 The Choice of Co-simulation Techniques                         |      |

|   |      |     | 6.2.2 Homogeneous Co-simulation vs. Heterogeneous Co-simulation        | . 79 |

|   |      |     | 6.2.2.1 Homogeneous Co-simulation                                      | . 80 |

|   |      |     | 6.2.2.2 Heterogeneous Co-simulation                                    | . 81 |

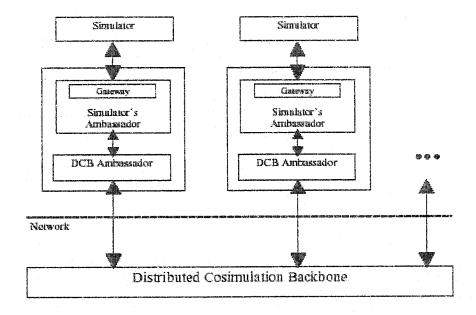

|   |      |     | 6.2.3 Geographically Distributed Co-simulation vs. Local Co-simulation | . 82 |

|   |      |     | 6.2.3.1 Co-simulation Environment Structure                            |      |

|   |      |     | 6.2.3.2 The Benefits of Geographically Distributed Co-Simulation       |      |

|   |      |     | 6.2.3.3 Performance Issue in Geographically Distributed Co-Simulation  |      |

|   |      | 6.3 | Co-simulation Tools                                                    |      |

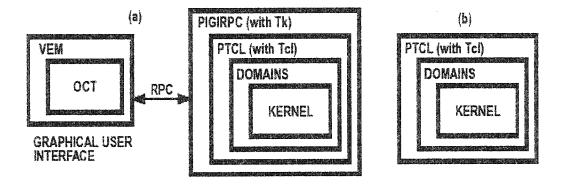

|   |      |     | 6.3.1 Ptolemy                                                          |      |

|   |      |     | 6.3.2 POLIS                                                            |      |

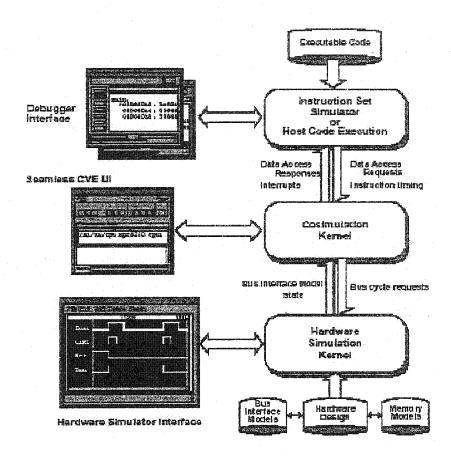

|   |      |     | 6.3.3 Seamless CVE                                                     |      |

|   |      |     | 6.3.4 Eaglei                                                           |      |

|   |      |     | 6.3.5 Other Co-simulation Tools                                        | . 96 |

|   | 7    | CON | ICLUSION                                                               | . 98 |

|   | LIST | OF  | ACRONYMS1                                                              | 101  |

|   | BIBI | IOG | RAPHY1                                                                 | 103  |

## LIST OF FIGURES

| Figure 1: Simulation server farm topology                                            | . 25 |

|--------------------------------------------------------------------------------------|------|

| Figure 2: Siavash et al.'s method of simulation-emulation co-operation               | . 27 |

| Figure 3: Canellas and Moreno's co-simulation/emulation                              | . 28 |

| Figure 4: Cadambi et al.'s acceleration system                                       | . 29 |

| Figure 5: Conventional simulation scheme                                             | . 33 |

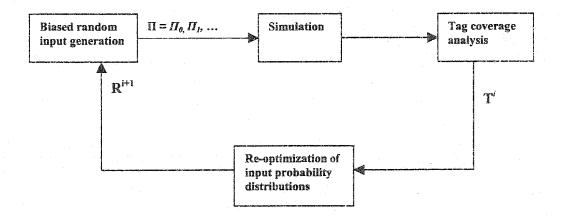

| Figure 6: Tasiran and Fallah's biased-random simulation with coverage feedback       | . 39 |

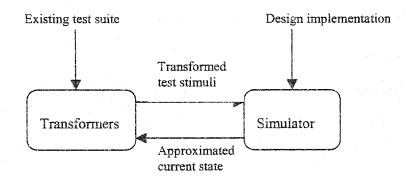

| Figure 7: C. Norris Ip's test stimulus transformation                                | . 41 |

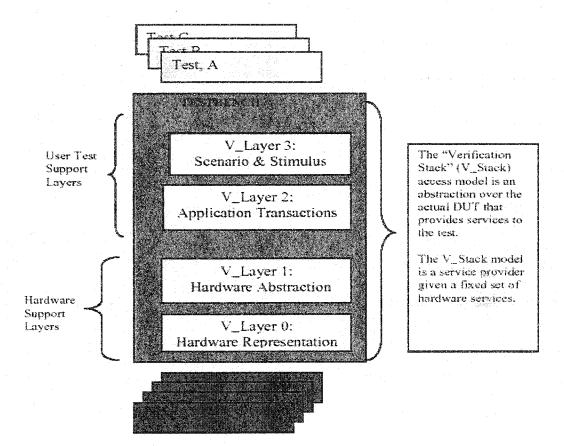

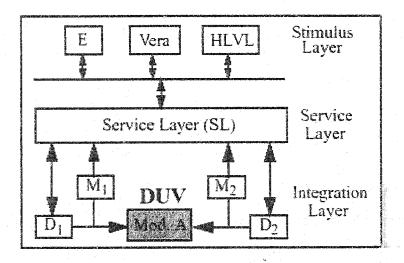

| Figure 8: Hawana and Schutten's layered solution                                     | . 58 |

| Figure 9: Bernd Stohr et al.'s FlexBench architecture                                | . 60 |

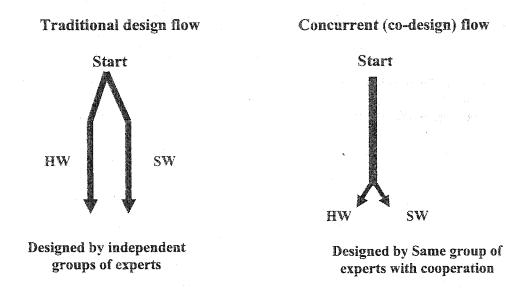

| Figure 10: Traditional design flow vs. co-design flow                                | . 65 |

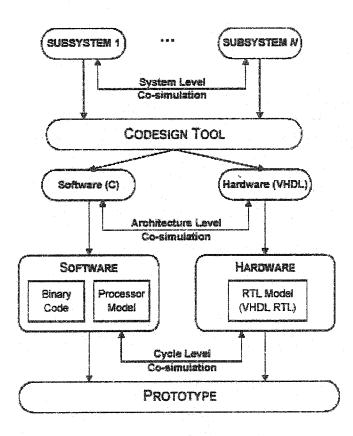

| Figure 11: Co-design flow highlighting co-simulation at different abstraction levels | . 66 |

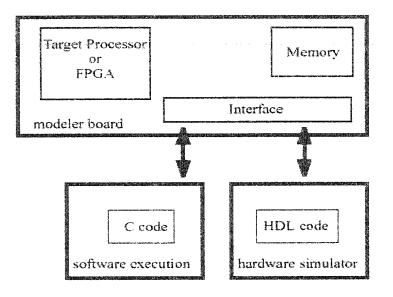

| Figure 12: Hardware modeler                                                          | . 70 |

| Figure 13: Séméria and Ghosh's untimed co-simulation model                           | . 74 |

| Figure 14: Séméria and Ghosh's cycle-accurate co-simulation model                    | . 75 |

| Figure 15: General structure of Amory et al.'s co-simulation environment             | . 82 |

| Figure 16: Architecture of the DCB                                                   | , 85 |

| Figure 17: The overall organization of Ptolemy version 0.7                           | . 88 |

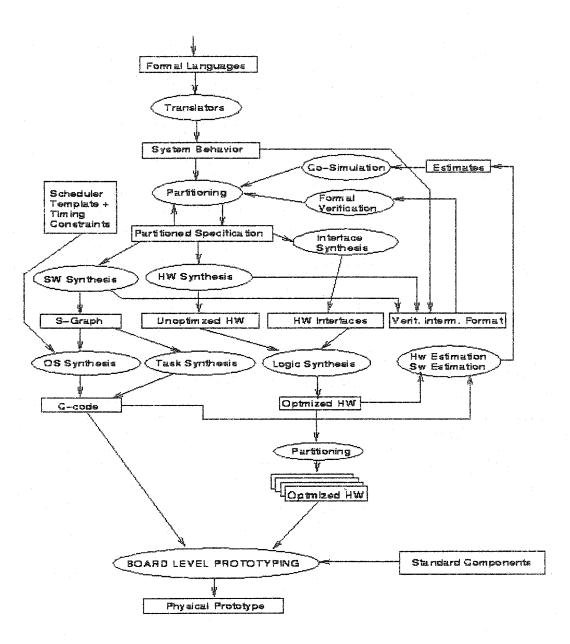

| Figure 18: Design flow implemented in the POLIS system                               | . 91 |

| Figure 19: Seamless CVE architecture                                                 | . 93 |

## LIST OF TABLES

| Table 1: Commercially available simulators                                 | 8  |

|----------------------------------------------------------------------------|----|

| Table 2: Commercially available accelerators                               | 10 |

| Table 3: Commercially available emulators                                  | 12 |

| Table 4: Commercially available property checkers, Lars Philipson 2001     | 20 |

| Table 5: Commercially available equivalence checkers, Lars Philipson 2001  | 21 |

| Table 6: OpenVera verification IP solutions                                | 61 |

| Table 7: Rowson's comparison of hardware/software co-simulation techniques | 79 |

| Table 8: Simulation domains implemented in Ptolemy                         | 89 |

| Table 9: Seamless CVE processor families                                   | 94 |

| Table 10: Co-simulation tools                                              | 96 |

## 1 INTRODUCTION

## 1.1 The Hardware Development Crisis

In the recent decade, the advancement of semiconductor materials and processing technologies has allowed circuit designs of multi-million gates to be able to fit on a single chip. As a consequence, electronic devices are shrinking in physical size while significantly enhancing in capabilities and speed. However, this technology advancement also brought an unprecedented verification challenge for hardware development. While the increasing silicon capacity allows design complexity to grow rapidly, verification complexity is rising at a much faster pace than the staggering design complexity [1].

Unfortunately, the existing verification methodologies and tools have not kept up with the climbing verification complexity, and the situation is further aggravated by products' shortening time-to-market and consumer's insatiable demand for new product features. This troublesome reality can be vividly illustrated by the famous and notorious Pentium microprocessor's FDIV bug found in 1994: a design error not caught during the verification process forced Intel to set aside a reserve of \$420 million to cover the costs, hire hundreds of customer service personnel to handle customer requests, and dedicate four fulltime employees to read Internet newsgroups and respond immediately to any postings about Intel or its products [2]. Now, a decade has past since the discovery of Pentium's FDIV bug; the inadequacy of the verification methods still severely impedes the productivity of today's hardware development industry: about 60% to 80% of the

hardware design groups' effort is dedicated to verification [3] [4], and 80% of the second and subsequent chip re-spins are caused by design errors that are not captured by verification [5].

According to Joan Bartlett [6], in order to enable hardware engineers to design and implement chips of multi-million gates forecasted by Moore's Law, at least three major problems must be addressed: (1) the large volume of design detail demands a higher level of design abstraction; (2) the shortening time-to-market demands improved simulation performance and debugging techniques; and (3) the huge cost incurred by respin due to the un-captured bugs demands early software/hardware integration and verification in the development process.

Undeniably, in today's hardware development, verification has already become a bigger challenge than design. The pressing need for verification solutions widely affects many entities of the hardware development community. For example, the electronic design automation companies are spending more on research and development of verification tools; and in system design houses, the team of verification engineers is quickly expanding. Even though much progress has been made, finding solutions to the problems of hardware verification still has a long way to go.

## **1.2** Motivation and Goals

While the hardware development industry is struggling to survive the verification crisis, many engineering students haven't been aware of its severity. This worrisome situation is mainly due to three reasons: (1) the long existing negative sentiment towards verification deeply influences engineers of the next generation, and many engineering

students still think that design is more important than verification and believe that the best engineers get to work on design; (2) despite the fact that formal verification has been around as an active research topic in the universities for many years, few verification-oriented courses can be seen in the engineer's curriculum and very limited verification skills are taught in the universities; (3) in the past few years, several books on hardware verification were published, but most of these books focus on specific verification topic and require considerable background knowledge to grasp the contents that the books present.

This thesis is initiated based on the awareness of the situation described above. The survey will contribute in three ways: (1) for engineering students who haven't been exposed to hardware verification, it can serve as an introductory reading material to hardware design verification; (2) for engineers who worked in industry and had experiences in hardware verification, it provides updated information on the topics that are covered by the survey; and (3) for the author herself, it establishes the foundation for her continued research in this field.

## **1.3** Scope of the Thesis

During the course of a hardware development, at least three levels of validation must be undertaken to ensure the correctness of the final product [7]. These three levels of validation are design verification, implementation verification, and manufacturing testing.

*Design verification* is a process of ensuring that a design exhibits intended behavior [8]. There are two broad approaches to hardware design verification:

simulation-based methods and formal methods. Because design verification targets the initial hardware description language (HDL) description, usually the first description of a design, it is of crucial importance in the design process.

Implementation verification checks if the design is correctly implemented with respect to its specification. Once an initial HDL description of a design is validated through extensive simulation or formal property verification, it proceeds through a varied set of optimization and transformation operations. Implementation verification is to check whether or not the optimized and transformed design is functionally equivalent to the original one. Equivalence checking tools are often used in various stages of the design cycle to verify equivalence of different implementations of the same design.

*Manufacturing testing* detects manufacturing defects in a fabricated chip. At this stage, the design description has been validated and the implementation of the design has also been verified. So, the purpose of manufacturing testing is to capture errors resulting from flaws in the chip fabrication process, rather than design errors.

Among these three levels of validation, *design verification* is the main concern of this thesis. Particularly, the survey is centered on simulation-based design verification approach. Since it is impossible to touch every aspect of hardware *design verification*, the thesis focuses on four important subjects, namely, simulation acceleration, simulation-vector generation, verification environment construction, and hardware-software co-simulation. For each subject, the basic background information is introduced; the current research progress and industry trend are described; the research examples selected from

various publications are presented; and the updated information on available tools in that area is provided.

### 1.4 Thesis Outline

This thesis report is organized in seven chapters:

Chapter 1 describes today's hardware development crisis and explains where this thesis fit in.

Chapter 2 contains background information on hardware design verification.

Chapter 3 presents methods that are used to accelerate the simulation process. Among these methods, hardware-accelerated simulation techniques are discussed in detail.

Chapter 4 surveys techniques for simulation vector generation. Several semiformal vector generation methods are introduced.

Chapter 5 discusses verification environment construction. A collection of hardware verification languages is introduced, and topics, such as layered testbench architecture, testbench automation, and verification intellectual property (VIP), are also included.

Chapter 6 describes the hardware-software co-simulation in co-design domain. Background information on co-design is provided; co-simulation techniques and available tools are presented.

Chapter 7 summarizes the survey.

## 2 BACKGROUND

#### 2.1 Introduction

To cope with the verification challenge in hardware design, tremendous effort has been made, by hardware development industry and research institutions all over the world, to find solutions to the problems of hardware verification. In general, the available solutions to hardware design verification can be categorized into two broad approaches: formal verification and simulation-based verification [9]. Formal verification methods, such as theorem proving, model checking, equivalence checking, etc., attempt to mathematically prove the correctness or incorrectness of the designed systems. On the other hand, simulation-based verification models the design, in either software or hardware, and tries to detect the design errors by applying tests to the modeled design and observing its behavior.

In the past, formal hardware verification has been around mainly as an academic exercise. Its steep learning curve, low automation level, and inability of handling designs of large size have prohibited formal verification from being adopted in the hardware design flow. Only in the recent two to three years, have commercial formal verification tools started emerging into the market and the employment of formal methods in industry begun making promising progress. Meanwhile, as an unsolved problem, formal verification will remain as a hot academic research topic for some time. In contrast, simulation-based verification, which holds an imperative status, has been the industry's

mainstream approach to hardware design verification for many years. However, as the size of a design grows the effectiveness of the traditional software-only simulation decays rapidly.

This chapter contains necessary background information on both simulation-based verification and formal verification. In section 2.2, three major approaches of simulation-based verification are described, and the tools commonly used in each approach are presented; in section 2.3, formal verification methods and tools are briefly introduced.

## 2.2 Simulation-based Verification

As described in section 2.1, simulation-based verification attempts to detect the design errors by modeling the design in either software or hardware, applying tests to the modeled design, and observing its faulty behavior. There are three major approaches used in today's simulation-based verification [10]: software-only simulation, hardware-accelerated simulation, and in-circuit emulation. The later two methods, hardware-accelerated simulation and in-circuit emulation, are also referred as hardware-based simulation.

## 2.2.1 Software-only Simulation

#### Advantages and Disadvantages

In *software-only simulation*, the hardware design along with its testbench is completely modeled in software. Besides being cost-effective, this approach also offers another two benefits [11]: (1) it provides the possibility of observing and controlling the internal signals of the design under test (DUT); and (2) it allows performing simulation at

the early stage of designs, regardless the model being synthesizable or non-synthesizable. Because of its beneficial features, software-only simulation is by far the most popular functional verification method employed in hardware development industry.

The software-only simulation has some drawbacks. Firstly, it requires long computation times and capacities, and the situation gets worse as the design complexity increases. Secondly, although many fault coverage metrics have been developed, there is still no practical way to directly associate simulation coverage with the confidence in a design that is gained through simulation (in fact for many complex designs total coverage is impossible to reach). As a result, when the simulation of a design can be stopped is often dictated by the time-to-market, not the simulation coverage. Thirdly, software-only simulation normally does not consider the physical environment that the designed circuit is employed in. In such a situation, it is impossible to observe the circuit's real performance because the circuit is isolated from its real environment during simulation.

### Simulators

Table 1 contains a collection of commercially available simulators. A detailed description for each included simulator can be found at the web link provided under "comments."

| Simulator | Vendor  | Comments                                                                                                                                                                                                        |

|-----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Incisive™ | Cadence | Single-kernel architecture natively supports Verilog,<br>VHDL, SystemC, SystemC Verification library (SCV),<br>and PSL/Sugar assertions.<br>http://www.cadence.com/products/incisive_unified_simul<br>ator.html |

| NC-VHDL   | Cadence | A VHDL simulator.<br>http://www.cadence.com/products/ncvhdl.html                                                                                                                                                |

Table 1: Commercially available simulators

| NC-<br>Verilog            | Cadence                               | A compiled Verilog simulatorand good for gate level simulation.<br>http://www.cadence.com/products/neverilog.html                                                                                                                                                                                                                                      |  |  |  |

|---------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NC-<br>SystemC®           | Cadence                               | First commercial implementation of the SystemC Verification Library.                                                                                                                                                                                                                                                                                   |  |  |  |

| 5,5,5,6,110,0             |                                       | http://www.cadence.com/products/ncsystemc.html                                                                                                                                                                                                                                                                                                         |  |  |  |

| Verilog-XL                | Cadence                               | The most standard simulator in the market, as this is the sign off simulator.                                                                                                                                                                                                                                                                          |  |  |  |

|                           |                                       | http://www.ence.umd.edu/class/ence408c/Verilog-XL/                                                                                                                                                                                                                                                                                                     |  |  |  |

| VCS <sup>TM</sup>         | Synopsys Inc.                         | A Verilog simulator.<br>http://www.synopsys.com/products/simulation/simulation.<br>html                                                                                                                                                                                                                                                                |  |  |  |

| Scirocco <sup>TM</sup>    | Synopsys Inc.                         | A VHDL simulator.<br>http://www.synopsys.com/products/simulation/scirocco/sc<br>irocco.html                                                                                                                                                                                                                                                            |  |  |  |

| VCS-MX                    | Symonetic Inc.                        | Supports mixed-HDL simulation.                                                                                                                                                                                                                                                                                                                         |  |  |  |

| VCS-IVLA                  | Synopsys Inc.                         | http://www.synopsys.com/products/simulation/vcs-<br>sci/vcs-sci.html                                                                                                                                                                                                                                                                                   |  |  |  |

| Scirocco-                 | Synopsys Inc.                         | Supports mixed-HDL simulation.                                                                                                                                                                                                                                                                                                                         |  |  |  |

| MX                        | Synopsys ne.                          | http://www.synopsys.com/products/simulation/vcs-<br>sci/mixed_hdl_ds.html                                                                                                                                                                                                                                                                              |  |  |  |

| Finsim                    | Fintronic USA Inc.                    | A Verilog simulator. Supports the entire Verilog HDL<br>including all behavioral, gate and switch level constructs,<br>user defined primitives, specify blocks, system tasks and<br>functions, PLI 1.0, VCD and SDF; runs on Linux,<br>Windows, and Solaris; supports compiled, interpreted and<br>any mixture of compiled and interpreted simulation. |  |  |  |

|                           |                                       | http://www.fintronic.com/frame_products.html                                                                                                                                                                                                                                                                                                           |  |  |  |

| Modelsim                  | Model Technology<br>A Mentor Graphics | Supports VHDL and Verilog with Single Kernel Simulation; good for block level verification.                                                                                                                                                                                                                                                            |  |  |  |

| - · · ·                   | Company                               | http://www.model.com/products/default.asp                                                                                                                                                                                                                                                                                                              |  |  |  |

| Smash Dolphin Integration |                                       | Mixed-signal simulation performed with a mixed-signal netlist; Single-engine simulation for both the analog and logic parts; Complete language support and mixity with SPICE, VHDL, VDHL-AMS, VERILOG, C and soon VERILOG-AMS.                                                                                                                         |  |  |  |

|                           |                                       | http://www.dolphin.fr/medal/smash/smash_overview.html                                                                                                                                                                                                                                                                                                  |  |  |  |

## 2.2.2 Hardware-accelerated Simulation

Advantages and Disadvantages

澀

The *Hardware-accelerated simulation* method is employed to speed up the simulation process. In hardware-accelerated simulation, the DUT is mapped to field programmable gate arrays (FPGAs) or special-purpose computing engines, and a testbench is used to provide stimulus (simulation vectors) to the DUT. Depending on the implementation of the testbench, either leaving the software-modeled testbench in the simulation environment or loading the synthesized testbench onto the accelerator, hardware-accelerated simulation can be 10 to 100,000 times faster than software-only simulation [12][13].

| Accelerator            | Vendor                            | Comments                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hammer™                | Tharas Systems                    | ASIC-based hardware accelerator for Verilog, VHDL and mixed language simulations; offers debugging capability comparable to that of software simulators.                                                                                                                                                                                                                   |

|                        |                                   | http://www.tharas.com/products/index.html                                                                                                                                                                                                                                                                                                                                  |

| Xcite®                 | Axis Systems                      | Based on Axis' patented ReConfigurable Computing<br>(RCC) technology, delivers simulation and acceleration in<br>a single system using one design database; offers<br>simulation performance of up to 100K cycles/second on a<br>design capacity of up to 10M ASIC gates; provides RTL<br>simulation acceleration.                                                         |

|                        |                                   | http://www.axiscorp.com/products/xcite.html                                                                                                                                                                                                                                                                                                                                |

| Cobalt <sup>plus</sup> | Quickturn<br>A Cadence<br>Company | A custom processor-based, compiled code logic emulation<br>system; offers a capacity of up to 20 million emulation<br>gates, 2 Gbytes DRAM and 256 Kbytes SRAM memory<br>in a single chassis; comes in two configurations: The CE<br>series (CE1000-CE8000) with one million gate granularity<br>and the CL series (CL10000-CL20000) with 2.5 million<br>gate granularity. |

|                        |                                   | http://www.quickturn.com/products/cobaltplus_data_<br>sheet.htm                                                                                                                                                                                                                                                                                                            |

Table 2: Commercially available accelerators

Unfortunately, hardware-accelerated simulation is much more costly than software-only simulation. It requires a design or a portion of a design be modeled in a synthesizable way before conducting simulation. Moreover, the DUT is still isolated from its real application environment during simulation since the design is exercised through stimulus provided by the testbench, not the real life data.

#### Accelerators

Table 2 contains information on a collection of commercially available accelerators. Features of each accelerator provided in Table 2 are not comprehensive. A detailed product description can be found at the web link listed under "comments" for each accelerator.

### 2.2.3 In-circuit Emulation

#### Advantages and Disadvantages

Despite its high cost, *in-circuit emulation* offers the highest run-time performance among the three simulation-based verification approaches. Different from hardwareaccelerated simulation, with in-circuit emulation, the stimulus to the DUT is not provided by testbench; instead, it comes from the live electrical connections consistent with the application environment [13]. In-circuit emulation allows the DUT to be verified within its real application environment, and thus makes hardware-software co-verification and system-level verification possible.

However, in-circuit emulation can only provide a limited visibility of the internal signals of the DUT [9], and, like hardware-accelerated simulation, it also requires the design to be synthesizable before verification can be performed.

## Emulators

A detailed product description can be found at the web link listed under

"comments" for each accelerator. Also, emulators annotated as *hybrid product* can be used as either accelerators or emulators.

Emulator Vendor Comments Provides Internet-based verification service System Explorer Aptix Corp http://www.aptix.com/products/product overview.htm Supports up to 64 independent clock domains; offers CelaroPRO Mentor multi-user shared capabilities and remote network Graphics access with queuing support. http://www.mentor.com/celaro/ Provides capacity of up to 20 million ASIC gates and a Quickturn memory system with up to 2 gigabytes of memory that Mercury<sup>Plus</sup> supports large testbenches and software code for High-A Cadence Performance regression testing. Company http://www.quickturn.com/products/mercuryplusspec.ht m Speeds emulation performance up to 500K cycles per second Supports three modes of in-circuit verification Xtreme Axis Systems (ICV): in-circuit simulation (ICS), in-circuit acceleration (ICA), and in-circuit emulation (ICE). Hybrid Product http://www.axiscorp.com/products/xtreme.html Uses patented VirtualWires<sup>™</sup> technology to ensure that Vstation-5MX Mentor the same database can be implemented in every Graphics replicate VStation hardware solution. Up to 15 million Hybrid Product (Ikos) usable ASIC gates (4.5 million on a VStation-5Mx); performance in the MHz range http://www.mentor.com/vstation/vstation5mx.html Provides up to 100x to 10,000x RTL performance; Palladium Quickturn provides simulation acceleration and in-circuit emulation in a single system; supports multiple users Hybrid Product A Cadence and remote access; maximize efficiency with fast Company compiles on a single workstation. http://www.cadence.com/products/palladium\_new.html

| Table 3: | Commercially | available | emulators |

|----------|--------------|-----------|-----------|

|----------|--------------|-----------|-----------|

## 2.3 Formal Verification

Simulation-based verification methods have a major drawback: they cannot fully verify every aspect of a system's functionality due to the fact that exhaustively simulating a design is infeasible, unless the design is an extremely simple one. Consequently, only the portion of the possible behaviors of a design is simulated; and serious design errors often remain undetected and later cause catastrophic problems.

The evolution of the application of formal methods in hardware verification directly results from the inability of the simulation-based methods in fully verifying a system's functionality. As a complementary approach, formal methods use mathematical means to prove that a design is correct without applying huge sets of test vectors. In [14], Mcfarland vividly described the difference between formal verification and simulationbased verification: "The difference between formal verification and simulation to the difference between deriving laws in physics from first principles and performing experiments."

Since formal verification is not the main concern of this survey, this section only provides a brief introduction to formal hardware verification techniques and tools. However, there exist a large number of publications addressing this topic. In particular, several surveys (e.g., [7], [15], [16], [17], [18], [19], and [20]) provide comprehensive coverage of both theoretical and practical aspects of formal hardware verification. Also, a new book titled "Introduction to Formal Hardware Verification" authored by Thomas Kropf was released recently. As claimed in its description, this advanced textbook presents an almost complete overview of existing techniques for formal hardware verification.

### 2.3.1 Formal Methods

Ideally, a formal method consists of a formal language, tools, and a proof system, which can be used to specify and verify systems [21]. A formal language refers to a language where every well-formed statement has a mathematically defined meaning; and tools are used to help the designers to describe systems and requirements in the formal language; finally, a proof system provides facilities to be used in reasoning about statements in the formal language.

In a design process, there are two main aspects to the application of formal methods [15][21]: one is the *specification oriented* formal framework, for example temporal logic, predicate logic, etc., which provides a rich and mathematically precise language that is used to specify intended properties of a design; the other is the *verification oriented* formal techniques and tools, which are used to reason about the relationship between a specification and its corresponding implementation. There exist quite a few formal techniques, such as automata-theoretic technique, automated theorem proving, model checking, equivalence checking, symbolic trajectory evaluation, as well as many hybrid ones that integrate these formal techniques with a hope of improving verification performance [22] [23] [24] [25].

Having a specification for a system written in a formal way brings many benefits to a design project [21]. The formal frame work forces the desired properties of a system to be specified in a precise description, which eliminates ambiguity that often exists in

the informal specifications, especially the ones written in natural languages, such as English; also, when a specification is written in a formal language, it becomes possible to reason about whether or not the specification matches the true intention of the designers. On the other hand, the *verification oriented* formal techniques and tools attempt to make sure that an implementation confirms to its corresponding specification [15]. In order to check this conformance, formal descriptions for both the specification and the implementation must be created first, and formal tools can then be used to establish the conformance.

It is important to note that formal methods are applied to the models of systems, not to the real systems themselves [21]. In other words, the usefulness of the verification results obtained via formal methods heavily relies on the correctness of the models and the specifications. For instance, if a model or a specification fails to accurately capture the behaviors of a system, then proofs acquired through formal methods are meaningless. This fact simply demonstrates how critical it is to create an authentic model/specification for a system. Unfortunately, obtaining such a model or a specification is still a challenge [26].

## 2.3.2 Formal Methods in Hardware Verification

Applications of formal methods in hardware verification domain are often formulated in two forms [27]. One form is the so called *property check* or *property verification*, which is concerned with properties and a model of a design; and verification on this respect attempts to show that all of the system's possible behaviors captured in the model satisfy the temporal properties of its specification [15]. The other hardware formal

verification form is known as the *implementation check* or *implementation verification*, which addresses relationship between two models of a system. In this case, verification is to show that each possible behavior of a system's implementation (a model) is consistent with some behavior of its high-level specification (a high-level model of the system).

In practice, *property verification* and *implementation verification* are often used in conjunction [15]. The property verification is usually conducted first to prove that a high-level model of a system satisfies a set of desired temporal properties defined by its specification; then, a lower level model with more detailed implementation is developed, and implementation verification is carried out to verify if the lower level model is an implementation of the high-level model. The later process is iterated as the design development proceeds: a series of models are developed, and each of them is an implementation of the model at the next higher level.

Three formal hardware verification methods are commonly used: theorem proving, model checking, and equivalence checking. Among these three approaches, theorem proving and model checking deal with the problem of *property verification*; and equivalence checking addresses the *implementation verification* issue.

**Theorem proving** is one of the earliest formal approaches used in hardware verification [7]. In this approach, the implementation (e.g. a high-level model of a system) and the specification of a system are both described in some kind of formal logic, such as higher-order logic, first-order logic, etc.; and the relationship between them is regarded as a theorem in the formal logic [16]. The goal of the proving process is to establish that the

theorem, which expresses the relationship between the implementation and the specification of a system, is a logical truth in the system.

Theorem proving approach is structural rather than behavioral [7]. This distinctive feature allows a circuit to be described hierarchically, where a component defined at one level in the hierarchy serves as an interconnection of components defined at lower levels.

As a general approach, theorem proving places no restriction on applications. It also offers powerful logic expressiveness and allows a circuit's behaviors to be described and related at many different levels of abstraction. However, theorem proving is an interactive method. Verification techniques based on theorem proving demand considerable effort on users' part in developing specifications and guiding the theorem proved through all the lemmas. Unfortunately, this demand often exceeds the capabilities of industrial hardware designers.

**Model checking**, opposite to theorem proving, is behavioral rather than structural, since only the behavior of a system is checked to satisfy certain properties [7]. In this approach, properties of a system are specified in the language of temporal logic, and the system is modeled as finite state machine. The goal of the checking process is to establish whether properties hold by exhaustively searching through the state space of the model [21].

Model checking is one of the most widely used automatic methods of verifying hardware [21]. The major strength of it, besides being an automated method, is its ability to produce counterexamples that can be used as a critical aid to debugging [27]. However, because the state space of any non-trivial system is extremely large, especially when the

system consists of many asynchronous communicating state machines, model checking faces the so called "state explosion" problem, which limits its applications to the large systems and at low abstraction level [7]. Techniques, such as symbolic methods [28], are developed by various groups to alleviate the problems of state explosion, and some of them show promising results.

**Equivalence Checking** uses mathematical techniques to determine whether one design representation is functionally equivalent to another. This formal approach is often applied at the last stages of a design cycle to ensure that the final design implementation does what the register transfer-level (RTL) code specifies [29].

The main strength of equivalence checking is that the checking process can be fully automated. Also, equivalence checking can be used as a good replacement of regression tests, since it is most effective in verifying the functional equivalence of slightly different designs [27], for example, the slightly changes introduced at the last stages of a design to optimize performance.

Because verifying a system via equivalence checking relies on the comparison between two representations of the system, it is helpful only if one of the representations of the system is correct. This correct representation is also referred as the so called "golden reference." Unfortunately, equivalence checking is not able to verify the correctness of the golden reference itself, and other means must be utilized to ensure the correctness of the golden reference.

2.3.3 Formal Hardware Verification Tools

Although formally verifying an entire design is not generally possible in today's hardware development, formal verification techniques are making their ways into the design flows for complex systems [30]. This promising progress, at least to some extent, should attribute to the recent proliferation of commercial verification tools.

A few years ago, formal verification tools were used merely within the academic scope, and the deployment of formal tools in industry was often seen as discouraging. This situation was mainly caused by the weakness of these formal tools: they usually provided limited capacity and poor usability, and many hardware engineers found them hard to use and difficult to integrate into the existing design flow.

While simulation-based verification techniques are losing their effectiveness in verifying designs of large size, more and more hardware design companies, including large systems houses and semiconductor suppliers, start seriously considering deploying formal techniques in their hardware verification processes. The demands for better formal verification tools encouraged EDA vendors, from well-established companies like Cadence and Mentor Graphics to some start-ups, to invest more in research and development on formal verification tools. As a result, a number of formal verification tools, such as equivalence checker and property checker, are commercially available today; and formal verification tools are gaining more acceptance and support in the hardware development industry. This claim can be well supported by the list of customers of a small EDA company called *Verplex* (Milpitas, CA), which produces both equivalence checker and property checker. According to Michael Chang [29], president and chief executive officer of Verplex Systems, Inc., in the first half of 1999, Verplex

only had seven customers, but today 150 different electronics companies worldwide are using Verplex' formal verification tools.

| Product                    | Released<br>&<br>Current<br>Version | Vendor<br>&<br>Web Site                      | Strong Points According to Vender                                                                                                                                     |

|----------------------------|-------------------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| @Verifier                  | 2001<br>2.1                         | @HDL<br>www.athdl.com                        | 1. Automatic Property Extraction; 2.<br>Automatic Testbench generation; 3.<br>Multiple clock domins; 4. Incremental<br>checking; 5. Bounded and unbounded<br>checking |

| BlackTie                   | 2000<br>2.10                        | Verplex Systems<br>www.verplex.com           | 1. Ease of use; 2. Automatic checks; 3.<br>Capacity & performance                                                                                                     |

| Design<br>Verity-<br>Check | 2000<br>1.1                         | Veritable<br>www.veritable.com               | 1. Ease of use; 2. Capacity & performance                                                                                                                             |

| Formal<br>Check            | 1997<br>3.1                         | Cadence Design<br>Systems<br>www.cadence.com | 1. Capacity; 2. Large installed base; 3.<br>Sophisticated Methods; 4. Ease of use                                                                                     |

| Formal<br>Model<br>Checker | 1997<br>2001.2                      | Avanti<br><u>www.avanticorp.com</u>          | 1. Mature technology; 2. Supports safety, liveness, and faimess                                                                                                       |

| Improve-<br>HDL            | 2001<br>1.2 beta                    | TNI-Valiosys<br>www.valiosys.com             | 1. Capacity; 2. Accepts non-<br>synthesizable HDL; 3. Properties &<br>constraints in a single language                                                                |

| Solidify                   | 1999<br>2.5                         | Averant<br>www.averant.com                   | <ol> <li>Practicality; 2. Language easy to use;</li> <li>Capacity&amp; performance; 4.</li> <li>Incremental use</li> </ol>                                            |

| Verix                      | 2000<br>3.0                         | Real Intent<br>www.realintent.com            | 1. Ease of use; 2. Hierarchical<br>verification; 3. High error coverage; 4.<br>Synthesis of simulation checkers; 5.<br>Multiple formal engines                        |

Table 4: Commercially available property checkers, Lars Philipson 2001

Lars Philipson, a professor at Lunds Tekniska Hogskola University in Lund, Sweden, has done an excellent survey on formal model checking and equivalence checking tools [26]. In the survey, Philipson collected almost all the current commercially available equivalence checkers and model checkers that specifically target at hardware verification. The total of ten EDA vendors were identified, and four equivalence checkers and eight property checkers were included in Philipson's survey. Table 4 contains information about the eight property checkers (model checkers); and Table 5 provides information of the four equivalence checkers. All the information shown in Table 4 and Table 5 were extracted from Philipson's survey [26], which was originally published in Swedish in the *Elektronik I Norden* magazine in November 2001, and later the English-language version was made available to *EEdesign*.

| Product            | Released &<br>Current Version | Vendor & Web Site                   | Strong Points According to<br>Vendor                                                                                                                           |

|--------------------|-------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Conformal<br>LEC   | 1998<br>3.0                   | Verplex Systems<br>www.verplex.com  | 1. Capacity & performance; 2.<br>Usability; 3. Integrated transistor<br>extraction                                                                             |

| Design<br>Verifyer | 1993<br>2001.2                | Avanti<br>www.avanticorp.com        | 1. Accuracy; 2. Large database<br>of customer examples; 3. Large<br>selection of available options; 4.<br>Speed and ease of use                                |

| Formality          | 1998<br>2001.06               | Synopsys<br><u>www.synopsys.com</u> | <ol> <li>Capacity performance; 2.</li> <li>Debugging environment; 3.</li> <li>Mixed language support; 4. Uses</li> <li>Verilog simulation libraries</li> </ol> |

| FormalPro          | 2000<br>3.1                   | Mentor Graphics<br>www.mentorg.com  | <ol> <li>Capacity; 2. Debug features;</li> <li>Mixed HDL; 4. Automation;</li> <li>Save session</li> </ol>                                                      |

| Table 5: Commercially | v available e | auivalence | checkers. | Lars | Philipson | 2001 |

|-----------------------|---------------|------------|-----------|------|-----------|------|

|                       |               |            |           |      |           |      |

## **3** SIMULATION ACCELERATION

### 3.1 Introduction

The advancement of the CMOS technology has drastically changed the way that the electronic products are designed, verified, and manufactured. On one hand, engineers are able to quickly produce smaller, faster, and more sophisticated products; on the other hand, the task of verifying a design becomes unprecedented heavy and complex. This increased verification load can be simply illustrated by looking at the number of simulation vectors needed to simulate a design. Comparing to the designs of a few years ago, the number of simulation vectors required to verify today's hardware designs has more than doubled [13].

Obviously, exercising a design with more simulation vectors requires more simulation time. This nature of the simulation-based verification approach seriously affects its effectiveness in handling large designs and meeting today's short time-tomarket requirement. Before formal methods becoming the industry's mainstream verification means, hardware design verification has to largely depend on simulation. In order to make simulation-based approach more capable in verifying designs of large sizes, solutions to speedup simulation must be found.

This chapter surveys techniques used to speedup the simulation process. Section 3.2 discusses simulation acceleration by using faster simulators; Section 3.3 introduces the use of simulation server farms; Section 3.4 describes approaches based on simulation-

emulation co-operation; and Section 3.5 briefly illustrates the issues of creating the verification environment.

## 3.2 Using Faster Simulators

Hardware simulation can be conducted in two ways: (1) simulating a design without considering timing and (2) simulating the models including timing [31]. The tradeoffs between these two approaches are performance and accuracy.

Traditional event-driven simulators calculate every active signal for every device it propagates through during a clock cycle. By examining detailed timing information, event-driven simulators provide higher accuracy in verification and therefore the rich functionality of the DUT can be verified through this type of simulation [31]. However, due to the high signal activity within a clock cycle, the performance of event-driven simulation, in terms of speed, is relatively poor.

Cycle-based simulator, on the other hand, provides an inexpensive method of accelerating functional simulation [32]. Typically, cycle-based simulators are five to ten times faster than conventional event-driven simulators. Such performance improvement is achieved through the following: (1) cycle-based simulators compute only two logic states: 1s and 0s; (2) cycle-based simulators calculate the results only at the clock edges; and (3) the inter-phase timing is ignored during simulation. In addition to performance improvement, because of the elimination of the inter-cycle calculations, cycle-based simulators also reduce the memory utilization to about one-fifth up to one-third comparing to the event-driven simulators.

Cycle-based simulators have their limitations. For example, cycle-based simulators are mainly used for synchronous designs; when components of an asynchronous design are simulated using cycle-based simulators, the performance penalty is high. However, as the complexity of hardware verification increases exponentially, correctly employing the cycle-based simulation definitely offers a relief in terms of speed and memory usage.

In the past few years, the performance of software simulators has improved constantly: compiled simulators increases simulation speed by more than ten times over the interpreted simulators [33] [34]; and cycle-based simulators boost simulation performance by avoiding detailed event processing overhead. Unfortunately, simulators' performance improvement cannot cope with the climbing complexity of the verification tasks. To further improve the speed and increase the capacity of functional simulation, 4 other methods must be utilized.

### **3.3 Using Simulation Server Farms**

In the past, when hardware design complexity reached 100k gates, traditional interactive simulation was replaced by batch-level simulation to achieve better performance [35]. Now, as the design complexity of a typical electronic system often exceeds a million gates, many hardware design companies are turning to simulation server farms for massive simulation performance gain.

Basically, a simulation server farm consists of a group of computers that run multiple simulations of a design simultaneously. Comparing to single computer simulation, the use of simulation server farms can increase simulation throughput by

several orders of magnitude [36]. Among various approaches to speeding up simulation, server farm technology has become a proven and reliable solution for simulating large and complex designs. The server farm technology offers many benefits [35]: it provides more simulation capacity; it allows the utilization of cost effective hardware and software resources; it offers a way of maximizing the utilization of workstations and licenses; and it is scalable.

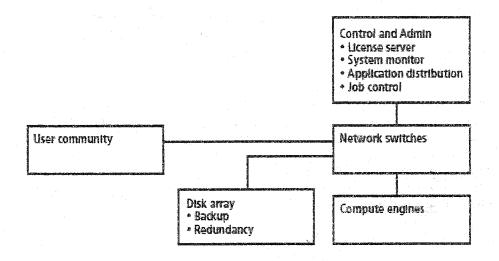

Figure 1: Simulation server farm topology

A typical simulation sever farm, at its most basic level, is a collection of hardware that is managed by some specialized software [37]. The collection of hardware normally includes compute engines, storage servers, administrative servers, and networks [37]. Figure 1 (from [37]) shows an example of a simulation farm topology. Although a simulation server farm can start from any size or price spectrum, issues, such as verification plan, equipment selection, installation, and configuration, must be properly addressed to ensure the success of a newly built server farm. Professional help can also be acquired from some EDA vendors. For instance, Cadence offers services of setting up simulation farms, which include planning, equipment selection, and installation. More information on design and implementation of a simulation farm can be found in Cadence's white paper [37]; and Synopsys' white paper [35] also contains information on hardware selection and setup for a simulation farm.

### 3.4 Using Simulation-Emulation Co-operation

# 3.4.1 Motivation

Both software-only simulation and in-circuit emulation have advantages and disadvantages. Software-only simulation offers good observability and controllability, and it can be used to simulate both synthesizable and non-synthesizable design models. In contrast, in-circuit emulation provides good performance in terms of speed, and it can have the DUT simulated within its real application environment.

The motivation of simulation-emulation cooperation, also termed as "hardwareaccelerated simulation," stems from the desire of combining the advantages of both software-only simulation and in-circuit emulation.

### 3.4.2 Examples

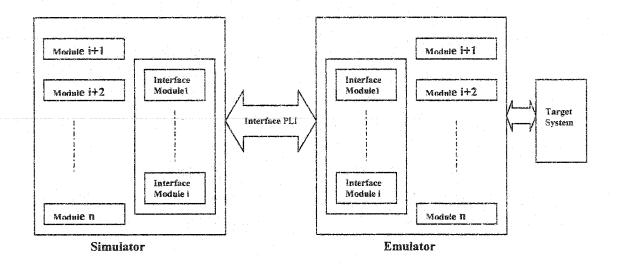

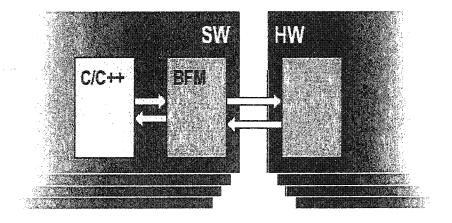

In [11], Siavash et al. reported a simulation-emulation co-operation method for Verilog and VHDL models, and their experimental results show that the proposed method can significantly reduce the simulation time. The reported method utilizes a general simulator as well as a general emulator: a PCI-based PLDA board is used for the emulation part and the ModelSim simulator (Version 5.5 a) is used for the simulation part. The overall co-operation environment is illustrated by Figure 2.

Figure 2: Siavash et al.'s method of simulation-emulation co-operation

The simulator (ModelSim 5.5a) resides on a host computer, which is connected to the emulator (the PLDA board) via a PCI (Peripheral Component Interconnection) expansion slot. The FPGA mounted on the PLDA board can be configured through the PCI bus, and the PCI bus then serves as the communication channel between the configured FPGA and the host computer. On the emulator side, the user-defined logic (portion of the DUT) communicates with the PCI bus through the PCI core (the *Interface Modules*), which handles all bus events; on the simulator side, the simulator communicates with the FPGA chip by means of the PLI routines (the *Interface Modules*), which access the PLDA board via memory-mapped I/O technique.

To use the simulation environment presented in [11], the system description, either in VHDL or Verilog, needs to be partitioned into the simulation part and the emulation part. Both parts are then compiled or compiled and configured into sub-circuits for simulation and emulation respectively. During the simulation process, the simulator controls and coordinates the activities of the emulators through the PLI routines, and the corresponding PLI routine is invoked by the simulator when information from the emulator is needed.

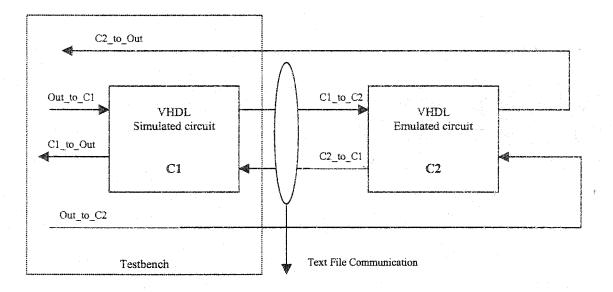

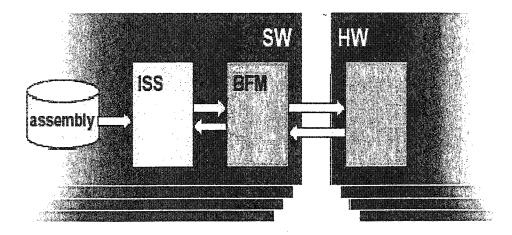

In [38], Canellas and Moreno proposed a simulation-emulation co-operation method of for VHDL models. Unlike [11], no actual physical emulator is used in Canellas and Moreno's co-operation environment; instead, another simulator is utilized to act as a logical emulator. Figure 3 shows the basic idea of the simulation environment.

Figure 3: Canellas and Moreno's co-simulation/emulation

The to-be-verified design is split into two parts: VHDL simulated circuit and VHDL emulated circuit. The simulator and the emulator run on different computers. The communication between the simulator and the emulator is achieved by means of text files; in this case, the TEXTIO package available in the standard VHDL library is used as the communication text files. Since no actual physical emulator is employed, this method is relatively costeffective; however, the use of text files as a way of inter-processes communication can be a bottleneck of this approach, and thus the communication overhead prevents the method from being applicable to large designs.

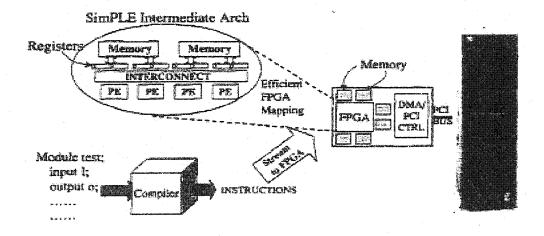

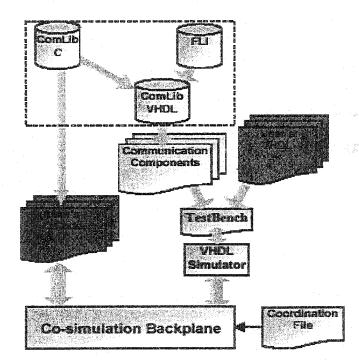

In [39], a hardware acceleration scheme for functional logic simulation is presented by Cadambi et al. In this work, a standard "off-the-shelf" PCI-board (ADC\_RC1000 from AlphaData) with a single FPGA is used as the hardware accelerator? Instead of synthesizing the DUT directly onto the FPGA, an intermediate simulation processor, called SimPLE, is mapped onto the FPGA, which acts as an execution engine for the netlist during the simulation. The overall acceleration system is illustrated in Figure 4.

Figure 4: Cadambi et al.'s acceleration system

The DUT is compiled into VLIW-type instructions by a fast SimPLE compiler, and each instruction represents a slice of the netlist of the DUT. The compiled instructions along with a set of simulation vectors are then transfer to the on-board memory via direct memory access (DMA). For each simulation vector, SimPLE executes all instructions to assure that the entire netlist is tested, and the simulation result is stored back to the on-board memory. After all the simulation vectors are exercised, the simulation results are sent back from the board memory to the host, again via DMA.

The whole simulation process is controlled by the host through application program interface (API). Scalability can be obtained at the price of sacrificing performance, by breaking up the instructions into smaller portions and transfers them separately to the on-board memory.

The authors reported that the proposed scheme can obtain speedups of up to 2000x over zero-delay event-driven simulation and up to 1000x over cycle-based simulation on benchmarks and industrial circuits. The authors attributed the simulation speed gain to the following factors: the SimPLE's parallel architecture, the large number of registers and memory in SimPLE, the high bandwidth between the FPGA and on-board memory, and the high clock speed of the FPGA.

In [40], Kirovski, Potkonjak, and Guerra reported a cut-based functional debugging paradigm that leverages the advantages of both emulation and simulation. In this approach, test vectors are applied to the DUT by emulation tool to achieve simulation speed improvement. When the design error is detected during emulation, the computation can be switched over to simulation tool for full design visibility and controllability. The execution can be rolled-back to any arbitrary instance in run time, which eases debugging process. The authors claimed that, with a low hardware overhead, the proposed approach

along with its accompanying algorithms demonstrated effectiveness when used on a set of benchmark designs.

There are many other publications on simulation-emulation co-operation, and here only some representative ones are presented. As analyzed before, the purpose of this cooperation is to take advantages of both simulation and emulation. Simulation provides good controllability and observability for signals in the design, but its slow speed prevents it from effectively handling large designs; in-circuit emulation, on the contrary, can achieve high execution speed, but its poor controllability and observability makes debugging much more difficult. The desired solution would be a simulation method that offers high speed and, at the same time, maintains good controllability and observability.

### 3.5 Using Rapid Construction of Verification Environment

A verification environment is an infrastructure for simulation-based verification. Before conducting simulation using any simulation oriented techniques, a verification environment must be properly constructed. The way that a verification environment is architected has an immediate impact on simulation efficiency, and, more importantly, it affects the possibility of reusing the same verification environment, or certain components of it, for verification of other designs.

However, creating a verification environment is a time-consuming process. When a new product's time-to-market is shrinking in a never-ending manner, the time spent on creating a verification environment and the time actually used on simulating a design have to be well-balanced, so as to achieve satisfactory verification productivity. Among the endeavor s of accelerating the overall simulation-based verification process, searching

for means to reduce the time consumed on constructing a verification environment is absolutely an imperative one.

In recent years, issues of improving the effectiveness of a verification environment and reducing the time spent on constructing it have been intensively addressed. For example, verification specific languages, such as Vera and the e-language, were developed to remedy the deficiency of using hardware description languages to handle verification tasks; the increased automation level has ever changed the traditional concept of a testbench; and the desire of reusing verification components became a reality with the introduction of verification intellectual property (VIP). All those topics are discussed separately in Chapter 5: Verification Environment Construction. 4

# SIMULATION-VECTOR GENERATION

#### 4.1 Introduction

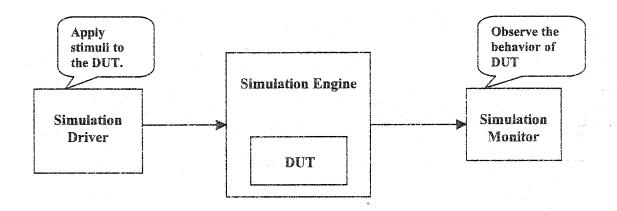

Simulation-based verification attempts to capture design errors by applying simulation vectors (test patterns) to the design-under-test (DUT) and observing its faulty behavior.

Figure 5: Conventional simulation scheme

Simulation vectors are simply input vectors to the DUT that causes the presence of a design error to be observable during simulation. Because of the increasing size of the design and the growing demand for bug-free product, the amount of the simulation vectors required to verify a design is growing larger and larger. The magnitude of the testing space has reached the level that it is impossible to probe every single point in it due to the time and resource constraints. Therefore, to reduce simulation time without sacrificing the verification quality, the most effective simulation vectors must be obtained

such that the least amount of simulation vectors can be used to uncover the greatest number of design errors. Usually, the effectiveness of a set of simulation vectors is measured by coverage metrics, such as code-based metrics, functionality-based metrics, spec-based metrics, observability-based coverage, etc. [41].

An ideal approach to verifying a design would be *exhaustive testing*, in which all possible input vectors and their combinations are applied to the DUT. Theoretically, this method can achieve the highest design error coverage; realistically, however, it is infeasible to exercise all input combinations unless the DUT is a combinatorial logic of very small size, which is often not the case in reality.