## San Jose State University SJSU ScholarWorks

Master's Theses

Master's Theses and Graduate Research

1992

## Chemical vapor deposition of polycrystalline silicon in a rapid thermal processor

Jimmy C. Liao San Jose State University

Follow this and additional works at: https://scholarworks.sjsu.edu/etd theses

#### Recommended Citation

Liao, Jimmy C., "Chemical vapor deposition of polycrystalline silicon in a rapid thermal processor" (1992). *Master's Theses.* 337. DOI: https://doi.org/10.31979/etd.86t7-2d3h https://scholarworks.sjsu.edu/etd\_theses/337

This Thesis is brought to you for free and open access by the Master's Theses and Graduate Research at SJSU ScholarWorks. It has been accepted for inclusion in Master's Theses by an authorized administrator of SJSU ScholarWorks. For more information, please contact scholarworks@sjsu.edu.

#### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

U·M·I

University Microfilms International A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 313/761-4700 800/521-0600

#### Order Number 1348698

## Chemical vapor deposition of polycrystalline silicon in a rapid thermal processor

Liao, Jimmy Chinhuan, M.S. San Jose State University, 1992

# CHEMICAL VAPOR DEPOSITION OF POLYCRYSTALLINE SILICON IN A RAPID THERMAL PROCESSOR

#### A Thesis

Presented To

The Department of Materials Engineering

San Jose State University

In Partial Fulfillment

of the Requirements for the Degree

Master of Science

By Jimmy C. Liao May, 1992

## APPROVED FOR THE DEPARTMENT OF MATERIALS ENGINEERING

DR K Sroe Hareha

Dr. John L. Crowley

Dr. Peter S. Gwozdz

APPROVED FOR SAN JOSE STATE UNIVERSITY

#### ABSTRACT

### CHEMICAL VAPOR DEPOSITION OF POLYCRYSTALLINE SILICON IN A RAPID THERMAL PROCESSOR

#### by Jimmy C. Liao Dr. K. Sree Harsha, advisor

A rapid thermal processor, which heats silicon wafers with high intensity light, was used to chemically deposit silicon from silane gas. The process was characterized.

The properties of this thin film were investigated. The kinetics of the deposition was determined from a matrix of time, temperature, and silane partial pressure. The amorphous to polycrystalline transition temperature of the deposition process was determined. Film surface roughness and crystallographic texture were also measured.

The optical absorption of the film and its response to the light radiation was measured and modeled as a function of film growth.

Electronic capacitors were made by growing a thermal oxide in the rapid thermal processor, then depositing the silicon electrode in-situ, or in the same chamber. The advantages of in-situ processing were demonstrated to be higher yield and reliability of these devices, due to the carefully controlled environment which did not expose the oxide to air.

#### TABLE OF CONTENTS

|                       |         |                                         | Page |

|-----------------------|---------|-----------------------------------------|------|

| List of Tab           | les     |                                         | vi   |

| List of Illustrations |         |                                         | vii  |

| Chapter               |         |                                         |      |

| 1.                    | Introdu | ction                                   | 1    |

| 2.                    | Experir | nental                                  | 6    |

|                       | 2.1     | Kinetic and Material Analysis           | 10   |

|                       | 2.2     | Optical Absorption Analysis             | 14   |

|                       | 2.3     | Electrical Evaluation of POS Capacitors | 16   |

|                       | 2.3.1   | RTCVD vs LPCVD                          | 18   |

|                       | 2.3.2   | In-situ RTCVD vs Ex-situ RTCVD          | 20   |

| 3.                    | Results |                                         | 23   |

|                       | 3.1     | Kinetic and Material Analysis           | 23   |

|                       | 3.1.1   | Growth Kinetics                         | 23   |

|                       | 3.1.2   | UV-Visible Reflectometry                | 24   |

|                       | 3.1.3   | X-Ray Diffraction                       | 27   |

|                       | 3.2     | Optical Absorption Analysis             | 30   |

|                       | 3.2.1   | Thermocouple Measurements               | 30   |

|                       | 3.2.2   | The Model                               | 36   |

|                       | 3.2.2.1 | Calculations                            | 36   |

|                       | 3.2.2.2 | Discussion of the Model                 | 38   |

|                       | 3.3     | Electrical Evaluation of POS Capacitors | 40   |

|                       | 3.3.1   | RTCVD vs LPCVD                          | 40   |

|                       |         | •                                       | _0   |

|    |        | P                                          | age  |

|----|--------|--------------------------------------------|------|

|    | 3.3.2  | In-situ vs Ex-situ RTCVD Polysilicon       | 46   |

|    | 3.3.3  | Summary                                    | 47   |

| 4. | Discus | ssion                                      | . 52 |

|    | 4.1    | Morphology                                 | 52   |

|    | 4.2    | Optical Monitoring                         | 55   |

|    | 4.3    | In-Situ Capacitors                         | 56   |

|    | 4.4    | Equipment Design                           | 58   |

|    | 4.5    | Suggested Modifications                    | 62   |

|    | 4.5.1  | Prevent Deposition on the Wafer Backside   | 62   |

|    | 4.5.2  | Closed-loop Recording / Open-loop Playback | 62   |

|    | 4.5.3  | Absorption Model and Feedback              | 63   |

|    | 4.5.4  | Emissivity-Independent Temperature         |      |

|    |        | Measurement                                | 64   |

| 5. | Summa  | ary                                        | 65   |

| 6. | Refere |                                            | 20   |

#### TABLES

| Table | F                                                                 | age |

|-------|-------------------------------------------------------------------|-----|

| 1     | Temperature, Time, Silane Partial Pressure<br>Experimental Matrix | 11  |

| 2     | C-V Results of POS Capacitors, LPCVD vs RTCVD                     | 42  |

#### **FIGURES**

| Figure |                                                                                                 | Page |

|--------|-------------------------------------------------------------------------------------------------|------|

| 1.     | Examples of Applications of Polycrystalline Silicon                                             | 5    |

| 2.     | Diagram of the RTCVD Chamber                                                                    | . 7  |

| 3.     | Spectral Output of the RTP Arc Lamp                                                             | . 8  |

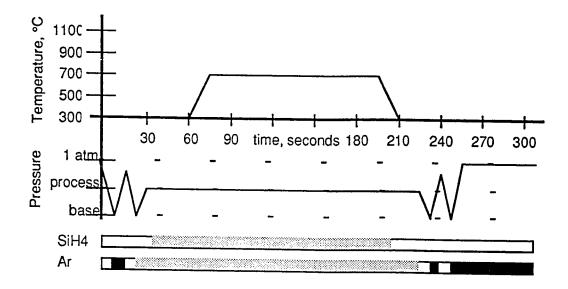

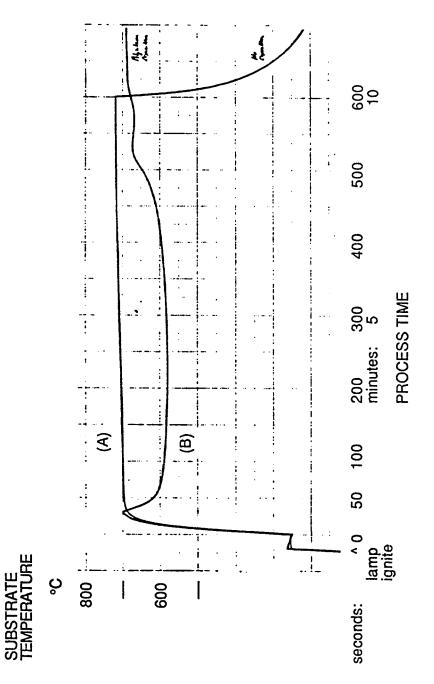

| 4.     | RTCVD Polysilicon Recipe                                                                        | . 12 |

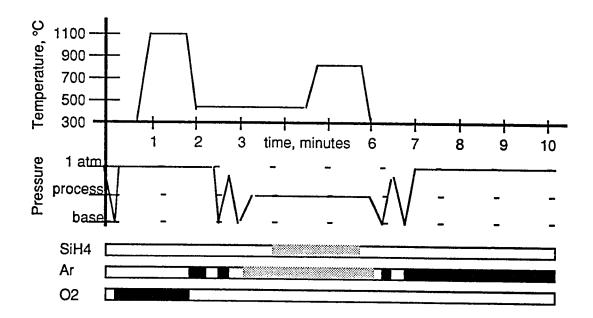

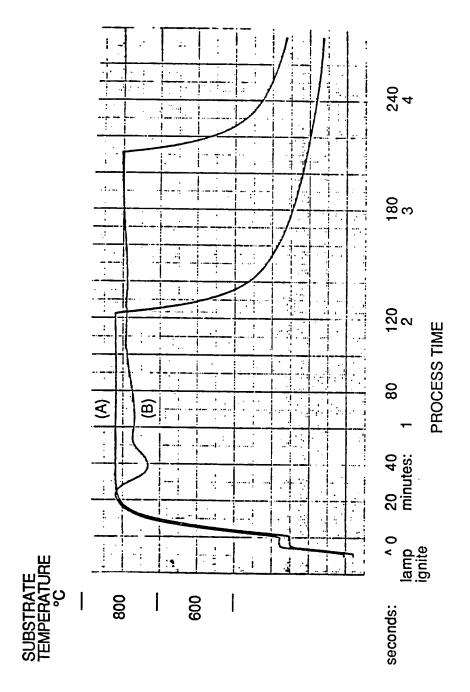

| 5.     | RTO / RTCVD In-situ Recipe                                                                      | . 17 |

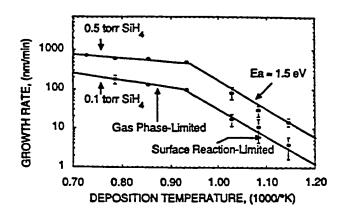

| 6.     | RTCVD Polysilicon Kinetics Curves                                                               | . 25 |

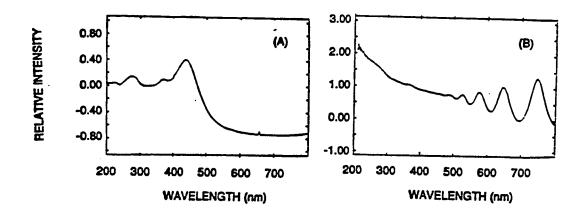

| 7.     | Optical Reflectance Spectra of 2 RTCVD Polysilicon<br>Samples Around the Transition Temperature | 25   |

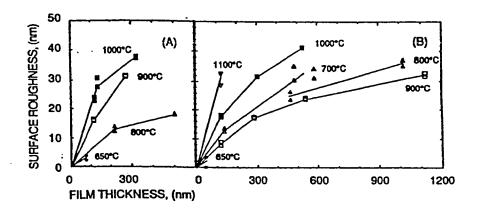

| 8.     | Surface Roughness vs Film Thickness                                                             | 27   |

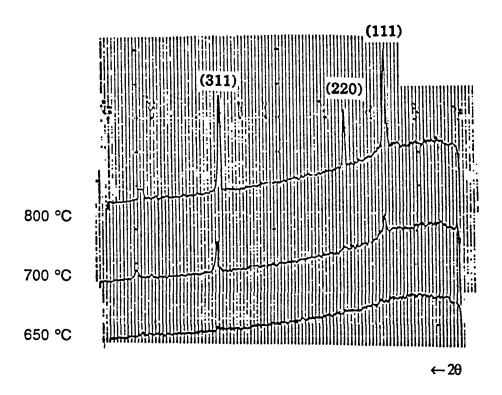

| 9.     | X-Ray Diffraction Raw Data of 3 RTCVD Samples Around the Transition Temperature                 | 28   |

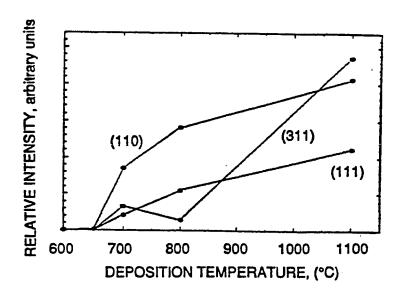

| 10.    | Normalized X-Ray Intensity vs Deposition Temperature                                            | 29   |

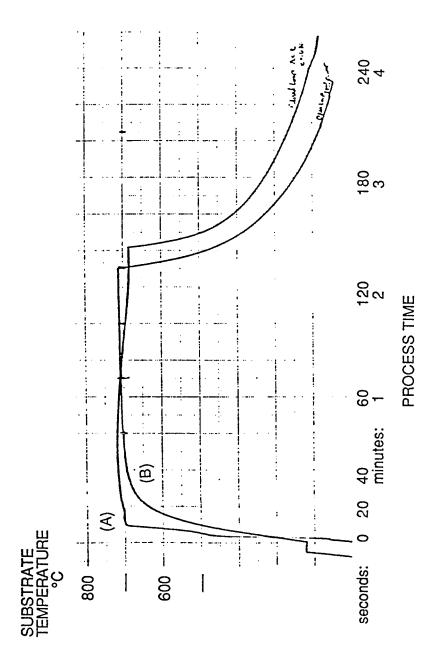

| 11.    | Open-loop Deposition Temperature Measured by a Thermocouple Embedded in an Oxide Wafer          | 32   |

| 12.    | Embedded Thermocouple Measurements at a Higher Lamp Power                                       | 33   |

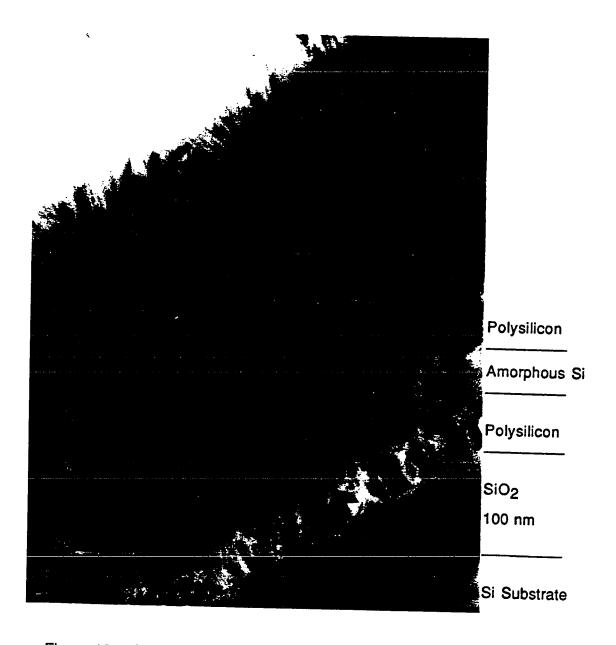

| 13.    | Cross-section TEM of RTCVD Poly Deposited During a Temperature Modulation                       | 34   |

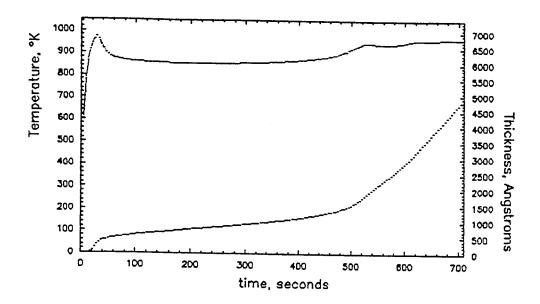

| 14.    | Model of Deposition Based on Measured Temperature.                                              | 35   |

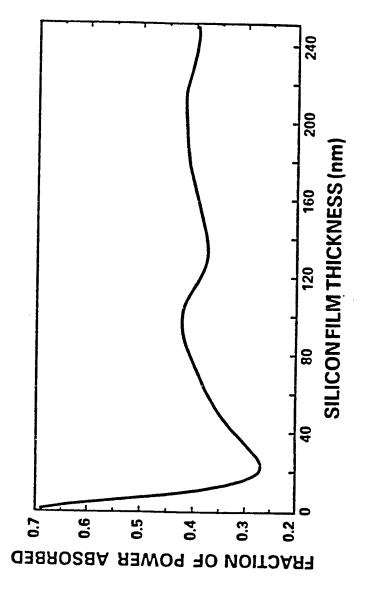

| 15.    | Model of Absorbed Lamp Power During Open-loop<br>Deposition                                     | 39   |

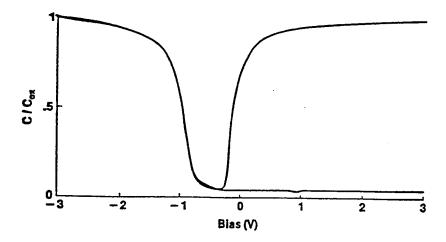

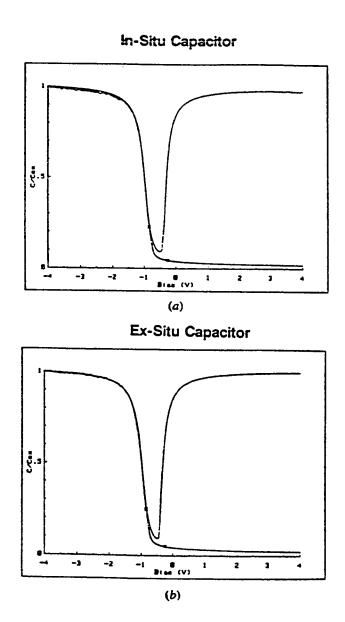

| 16.    | C-V Curve for In-situ RTO / RTCVD POS Capacitor                                                 | 43   |

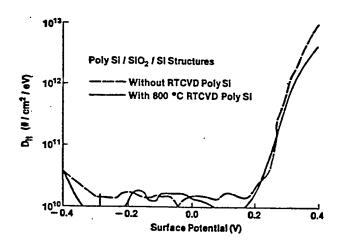

| 17.    | Dit Comparison of LPCVD vs RTCVD POS                                                            | 43   |

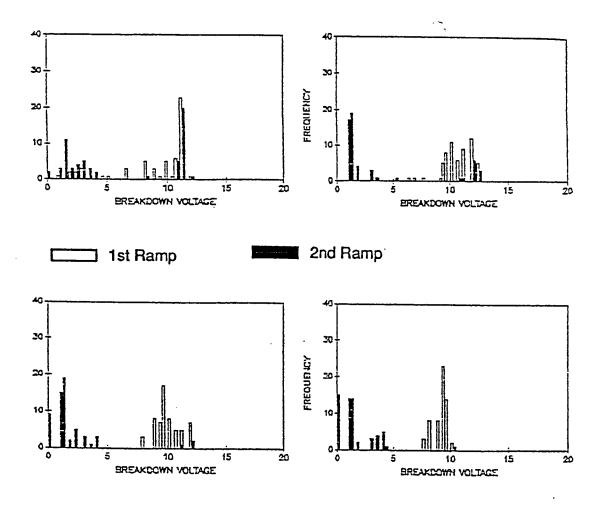

| 18.    | Vbd Histograms of LPCVD POS Capacitors                                                          | 44   |

| 19.    | Vbd Histograms of RTCVD POS Capacitors                                                          | 45   |

|     | P                                                                                        | age |

|-----|------------------------------------------------------------------------------------------|-----|

| 20. | C-V Curves for In-situ vs Ex-situ POS Capacitors                                         | 48  |

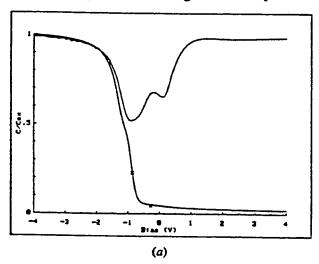

| 21. | C-V Curves After Constant Current Stress                                                 | 49  |

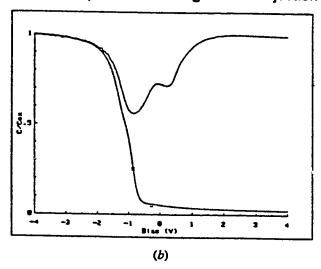

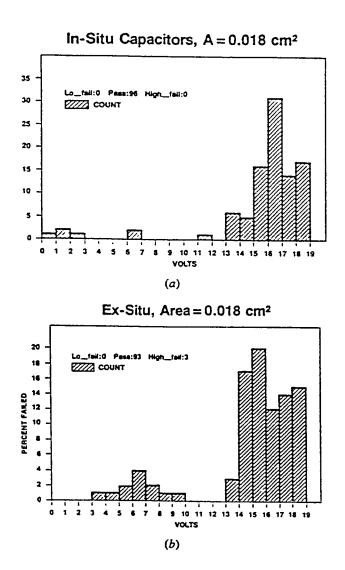

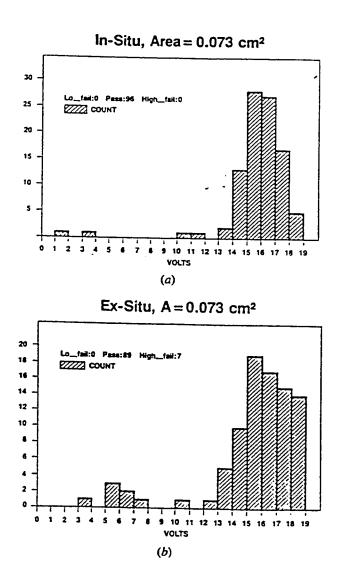

| 22. | V <sub>bd</sub> Histograms for small In-situ vs Ex-situ POS                              | 50  |

| 23. | V <sub>bd</sub> Histograms for large In-situ vs Ex-situ POS                              | 51  |

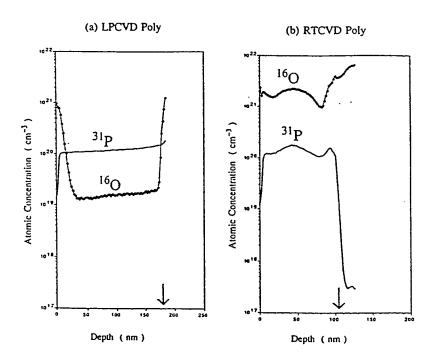

| 24. | SIMS Comparing Oxygen Contents of RTCVD and LPCVD Polysilicon                            | 54  |

| 25. | Closed-loop Deposition Temperature Measured by a Thermocouple Embedded in an Oxide Wafer | 57  |

#### Chapter 1

#### INTRODUCTION

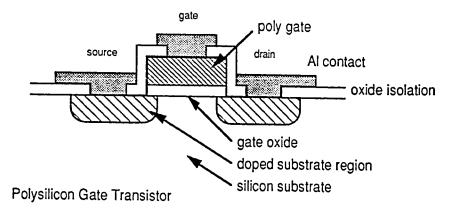

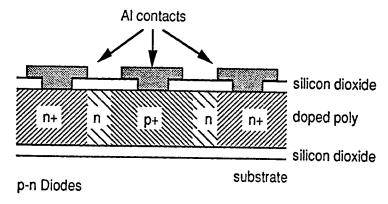

Polycrystalline silicon (polysilicon, or poly) is a material which is widely used in the fabrication of integrated circuits (ICs) because it is compatible with single-crystal silicon, can possess a wide range of resistivities depending on its dopant concentration 1, and can also be used to form dielectrics 2. In ICs, it has uses as a MOS gate, resistor, metal contact, and insulation for electrical isolation 3. Diagrams of some devices are illustrated in figure 1. For IC fabrication, it is typically deposited as a thin film using a technique known as chemical vapor deposition performed in a furnace 4-6.

In an isothermal furnace, a silicon-containing gas, usually diluted with an inert carrier gas, is flowed over a wafer. The gas decomposes into atomic silicon on the wafer. This is typically done under vacuum (< 5 torr) at a temperature range of 500°C - 700°C using silane (SiH<sub>4</sub>) or dichlorosilane (SiCl<sub>2</sub>H<sub>2</sub>) <sup>7</sup>. Because vacuum is used in the furnace, the process just described is referred to as low pressure chemical vapor deposition (LPCVD). In this process, the furnace temperature is first allowed to stabilize in an inert ambient. Then, when the desired temperature is reached, the reactive gas mixture is flowed from one end of the reactor and exhausted at the opposite end. Deposition of poly occurs on all surfaces within the reactor, including the furnace walls and the wafer holder. Periodic maintenance of the reactor is required to prevent a

build-up of film on the furnace. There is also a problem with the generation of particulates from homogeneous nucleation reactions within the reactor. The deposition reaction is terminated by cutting off the gas supply and replacing it with an inert gas. Then, the furnace is cooled and the wafers are unloaded.

In this work, poly is deposited from silane under vacuum using a rapid thermal processor to heat the wafer, rather than a resistance-heated furnace. An RTP system uses a lamp to heat the wafer by optical and UV absorption 8, so that the temperature of the wafer varies with the intensity of the lamp light. The direct absorption of light allows rapid temperature changes in the wafer. This can be done in a water-cooled steel, or quartz chamber, where the light is selectively absorbed by only the wafer. Since CVD is a thermally activated process, the deposition occurs only on the wafer, and not on the chamber walls.

With the ability to change temperatures quickly, RTP has many advantages over furnace heating. Drastically reduced transient times (time required to reach temperature) allow ultra thin films (< 100 Å) to be formed. Since CVD is thermally activated, the reaction can be terminated about as quickly as turning off the lamp, rather than waiting for the slow depletion of silane. The reduced thermal exposure also minimizes diffusion between thin film layers, which is time-dependent. The ability to change temperatures rapidly also allows several processes to be carried out sequentially. For example, silicon can be deposited at a low temperature (600°C) and subsequently annealed at a high temperature

(1000°C). This deposition method has been used to control the grain size of the material 9.

By combining RTP with a small chamber volume and a vacuum pump, a wide range of temperatures, ambients, and pressures can be set and quickly changed. As a result, several different processes can be combined in the same chamber (in-situ processing). One application of in-situ processing is the formation of capacitors using rapid thermal oxidation (RTO) of exposed silicon in an oxygen ambient followed by a deposition of polysilicon for the electrode 10. Typically, this is done in two different machines with a wafer transport step performed by a human operator. By combining the process in-situ, the wafer will be free of airborne particulates and contaminates which could adversely affect device performance if found in the oxide-poly interface. The deposited silicon electrode can either be the full thickness required for the poly step, or merely a thin poly cap to protect the oxide film while it is being transported into a conventional LPCVD furnace. For conventional device geometries which typically require 0.4 -  $1.0~\mu m$  polysilicon, the latter might be a better approach, since RTP processes are designed for short process times and hence, thinner films. Also, the film thickness uniformity and doping capabilities are well established in a furnace 6.

The first part of this work involves an analysis of the polysilicon deposition process in an RTP environment and a study of the resultant film properties. The deposition is performed at a matrix of time and temperature and two partial pressures of silane in order to determine the

dependence of these variables on growth rate and morphology.

Since RTP is an optical process, the second part of this work will focus on absorption studies. The absorption of the film at various thicknesses is important for both the heating of the wafer and the measurement of temperature during the process, which depends on the emissivity of the wafer. The more energy that is absorbed rather than reflected, the higher the wafer temperature (which in turn affects the deposition rate, as well as the morphology of the film). Thus, the focus of the investigation will be on relating the wafer temperature with the lamp power absorption and resultant film thickness.

Lastly, electronic devices are fabricated to evaluate the advantages of using the new poly material, as well as the advantages of in-situ processing. Two studies of RTO capacitors with polysilicon electrodes are performed using capacitance-voltage (C-V) techniques 11. In the first study, the in-situ RTCVD capping poly layer is compared to an LPCVD layer of polysilicon. The purpose is to compare the new process with an established one. In the second study, the affect of in-situ vs ex-situ processing was compared directly using RTCVD polysilicon entirely. The purpose was to determine the merits of in-situ processing.

Figure 1 Examples of some applications for polycrystalline silicon.

#### Chapter 2

#### EXPERIMENTAL

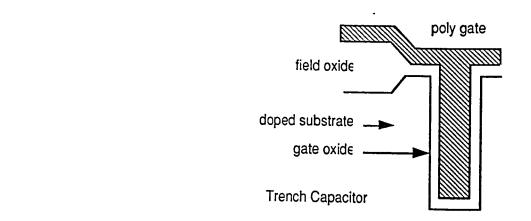

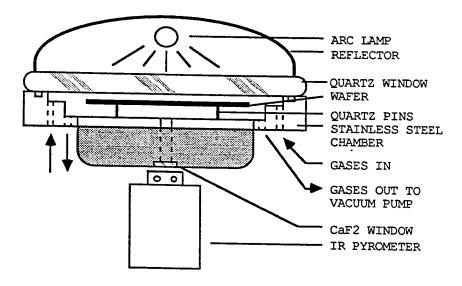

The rapid thermal processor used in the experiments was a commercially available Peak Systems Inc. ALP 6000 which was modified for vacuum processing by attaching a gate valve and 40 cfm mechanical pump to the exhaust manifold, and adding a silane gas manifold consisting of silane and and inert gas line. The configuration of the RTP chamber is shown in figure 2. The rectangular chamber is water-cooled, polished stainless steel with a volume of approximately 0.7 liters. The wafer is centered in the chamber, thermally isolated by resting on three quartz pins. Gases enter the chamber from the top four corners, and exhaust to a mechanical pump from the corner side walls. The ceiling of the chamber is a half inch thick quartz window, which is transparent to the lamp radiation. The reflector assembly rests on top of the window and is focused on the wafer plane. It is contoured with precision optical design to deliver a distribution of lamp radiation which provides uniform heating throughout the wafer. A 35 KW long arc discharge lamp is mounted in the reflector, surrounded by a quartz water jacket.

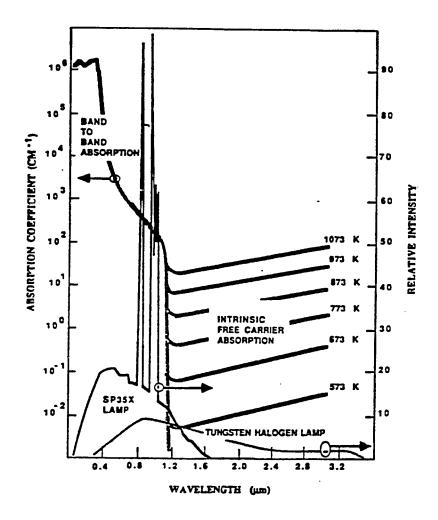

The spectral output of the lamp (SP35X) ranges from approximately 0.2 to 1.6 µm. This is shown in figure 3. It is compared to the output of a common tungsten halogen lamp, which also gives off high intensities of infrared (IR) as well as visible light. The SP35X lamp, on the other hand, is a xenon arc discharge lamp which cuts off abruptly in the near IR. These

Figure 2 Cross sectional diagram of the RTP chamber, looking along the length of the long arc discharge lamp.

outputs are plotted as relative intensity on the right ordinate axis. On the left ordinate axis, plotted on the same coordinate, is the relative absorption of silicon. At short wavelengths, below 1.2  $\mu$ m, the mode of absorption is direct excitation of silicon electrons. This absorption has a sharp edge, above which absorption is carried out by free carriers. Direct band to band

Figure 3 Spectral output of the SP35X xenon arc lamp compared to tungsten halogen lamps, plotted as relative intensity vs wavelength. Superimposed on the ordinate axis is the absorptivity of silicon at various wavelengths. An absorption edge occurs around 1.2  $\mu$ m, above which only free carriers are absorbed.

absorption is preferable to free-carrier absorption because the heating efficiency is not dependent on the dopant concentration in the material or on the temperature of the wafer, making for a more repeatable process. Therefore, the output of the arc lamp is more specifically tuned for silicon heating than the tungsten halogen filament lamp.

Centered on the floor of the chamber (refer to figure 2) is a quarter inch aperture, sealed with a thin calcium fluoride (CaF<sub>2</sub>) window, which is transparent to infrared absorption. The temperature of the wafer is measured and monitored by an IR pyrometer mounted below. Emitted radiation from the hot wafer is collected by an indium-arsenide photodetector in the pyrometer, which drives the lamp current in a closed loop PID control until the desired temperature is reached. The detection band of the InAs detector is 2.5-3.5 µm, which is completely out of the range of the lamp's spectral output, so that the temperature of the wafer can be measured without radiative interference from the lamp. The sampling rate for the control loop is 10 milliseconds. The temperature setpoint is programmed in the software and temperature ramps can also be controlled to 1 °C/sec. A central computer stores and executes process recipes which integrate temperature and inert gas flow. The vacuum gate valve and the silane gas manifold are manually controlled.

When the pyrometer is used to feed back to a controller, it is known as "closed-loop control." An alternate mode of processing in "open-loop control." In this mode, a fixed lamp power is set, regardless of the wafer temperature, for a set period of time. The pyrometer in this case can be

used as a passive IR monitor.

The substrates used were p-type boron-doped (100)-oriented silicon wafers. The diameter of the wafers was 100 mm. The resistivities of the starting silicon was greater than 10  $\Omega$ -cm.

#### 2.1 Kinetic and Material Analysis (Experiment 1)

Before polysilicon deposition, 100 nm thermally grown oxide was formed on the wafers in a separate tube furnace to allow for easier thickness measurement of the subsequent polysilicon film using a UV-visible spectrophotometer (200-800 nm) 12, as well as to prevent epitaxial realignment of silicon at higher temperatures 13.

For a study of deposition kinetics, silane was mixed with argon at volume ratios of approximately 1:20 and 1:3 at a pressure of 2.0 torr. (This translates to an approximate partial pressure of 0.1 torr and 0.5 torr of silane, respectively). Depositions were carried out at temperatures from 600 to 1100°C and deposition times of 10 to 300 seconds. The matrix variables are given in Table 1. One wafer was processed per condition. A diagram of the typical process recipe is shown in figure 4, which depicts temperature, relative pressure, and gas status as a function of time. In the gas diagram, a lightly shaded bar indicates a much lower flow than a darkly shaded bar. The recipe begins with a pump down to a base pressure of 10 millitorr, then a purge with argon gas in order to eliminate oxygen

Table 1

EXPERIMENTAL MATRIX

| 600       300       0.1         650       120       0.1         650       300       0.1         700       120       0.1         700       300       0.1         800       60       0.1         800       300       0.1         800       300       0.1         900       30       0.1         900       60       0.1         900       120       0.1         1000       10       0.1         1000       10       0.1         1000       30       0.1         1000       120       0.1         1000       120       0.1         600       300       0.5         650       300       0.5         650       300       0.5         650       300       0.5         700       60       0.5         700       120       0.5         700       300       0.5         800       300       0.5         800       300       0.5         900       10       0.5         900       10       0.5 </th <th>Temperature, °C</th> <th>time, seconds</th> <th>SiH4 partial pressure, torr</th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Temperature, °C | time, seconds | SiH4 partial pressure, torr |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------|-----------------------------|

| 650                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 600             | 300           |                             |

| 650 300 0.1 700 120 0.1 700 300 0.1 800 60 0.1 800 120 0.1 800 300 0.1 800 300 0.1 800 0.1 800 0.1 800 0.1 800 0.1 800 0.1 900 0.1 900 0.1 900 0.1 900 120 0.1 1000 10 0.1 1000 30 0.1 1000 10 0.1 1000 120 0.1 1000 120 0.5 600 300 0.5 * 650 120 0.5 650 300 0.5 * 700 60 0.5 700 120 0.5 800 0.5 * 800 0.5 * 800 0.5 * 900 10 0.5 * 900 10 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * 900 0.5 * | 650             |               |                             |

| 700         120         0.1           700         300         0.1           800         60         0.1           800         120         0.1           800         300         0.1           900         30         0.1           900         60         0.1           900         120         0.1           1000         10         0.1           1000         30         0.1           1000         60         0.1           1000         120         0.5           600         300         0.5           650         120         0.5           650         300         0.5           700         60         0.5           700         60         0.5           700         120         0.5           700         300         0.5           800         300         0.5           800         300         0.5           800         300         0.5           900         10         0.5           900         10         0.5           900         0.5         0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 650             |               |                             |

| 700       300       0.1         800       60       0.1         800       300       0.1         800       300       0.1         900       30       0.1         900       60       0.1         900       120       0.1         1000       10       0.1         1000       30       0.1         1000       60       0.1         1000       60       0.1         1000       120       0.5         600       300       0.5         650       120       0.5         650       300       0.5         700       60       0.5         700       300       0.5         700       300       0.5         800       300       0.5         800       300       0.5         800       300       0.5         900       10       0.5         900       10       0.5         900       10       0.5         900       10       0.5         1000       10       0.5         1000       10       0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 700             |               |                             |

| 800       60       0.1         800       120       0.1         800       300       0.1         900       30       0.1         900       60       0.1         900       120       0.1         1000       10       0.1         1000       30       0.1         1000       60       0.1         1000       120       0.5         600       300       0.5         650       120       0.5         650       120       0.5         700       60       0.5         700       120       0.5         800       300       0.5         800       300       0.5         800       300       0.5         900       10       0.5         900       10       0.5         900       10       0.5         1000       10       0.5         1000       10       0.5         1000       10       0.5         1000       10       0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 700             |               |                             |

| 800       120       0.1         800       300       0.1         900       30       0.1         900       60       0.1         900       120       0.1         1000       10       0.1         1000       30       0.1         1000       60       0.1         1000       120       0.5         600       300       0.5       *         650       120       0.5       *         650       300       0.5       *         700       60       0.5       *         700       120       0.5       *         800       60       0.5       *         800       300       0.5       *         900       10       0.5       *         900       30       0.5       *         900       10       0.5       *         1000       10       0.5       *         1000       10       0.5       *         1000       10       0.5       *         1000       10       0.5       *         1000       0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 800             |               |                             |

| 800       300       0.1         900       30       0.1         900       60       0.1         900       120       0.1         1000       10       0.1         1000       30       0.1         1000       60       0.1         1000       120       0.5         600       300       0.5         650       120       0.5         650       300       0.5         700       60       0.5         700       120       0.5         700       300       0.5         800       60       0.5         800       300       0.5         900       10       0.5         900       10       0.5         1000       10       0.5         1000       10       0.5         1000       10       0.5         1000       10       0.5         1000       10       0.5         1000       10       0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 800             | 120           |                             |

| 900       30       0.1         900       60       0.1         900       120       0.1         1000       10       0.1         1000       30       0.1         1000       60       0.1         1000       120       0.5         600       300       0.5         650       120       0.5         650       300       0.5         700       60       0.5         700       120       0.5         700       300       0.5         800       60       0.5         800       300       0.5         900       10       0.5         900       10       0.5         900       120       0.5         1000       120       0.5         1000       10       0.5         1000       30       0.5         1000       60       0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 800             | 300           |                             |

| 900       60       0.1         900       120       0.1         1000       10       0.1         1000       30       0.1         1000       60       0.1         1000       120       0.5         600       300       0.5         650       120       0.5         650       300       0.5         700       60       0.5         700       120       0.5         700       300       0.5         800       60       0.5         800       300       0.5         900       10       0.5         900       30       0.5         900       120       0.5         1000       10       0.5         1000       30       0.5         1000       50       0.5         1000       60       0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 900             | 30            |                             |

| 900       120       0.1         1000       10       0.1         1000       30       0.1         1000       60       0.1         1000       120       0.1         600       120       0.5         600       300       0.5         650       120       0.5         650       300       0.5         700       60       0.5         700       120       0.5         700       300       0.5         800       60       0.5         800       300       0.5         900       10       0.5         900       30       0.5         900       10       0.5         1000       10       0.5         1000       10       0.5         1000       60       0.5         1000       60       0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 900             | 60            |                             |

| 1000       10       0.1         1000       30       0.1         1000       60       0.1         1000       120       0.1         600       120       0.5         600       300       0.5         650       120       0.5         650       300       0.5         700       60       0.5         700       120       0.5         700       300       0.5         800       60       0.5         800       300       0.5         800       300       0.5         900       10       0.5         900       30       0.5         900       120       0.5         1000       10       0.5         1000       30       0.5         1000       60       0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 900             | 120           |                             |

| 1000       30       0.1         1000       60       0.1         1000       120       0.1         600       120       0.5         600       300       0.5         650       120       0.5         650       300       0.5         700       60       0.5         700       120       0.5         700       300       0.5         800       60       0.5         800       120       0.5         800       300       0.5         900       10       0.5         900       30       0.5         900       120       0.5         1000       10       0.5         1000       10       0.5         1000       30       0.5         1000       0.5       0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1000            | 10            |                             |

| 1000       60       0.1         1000       120       0.1         600       120       0.5         600       300       0.5       *         650       120       0.5       *         700       60       0.5       *         700       120       0.5       *         800       300       0.5       *         800       120       0.5       *         800       300       0.5       *         900       10       0.5       *         900       30       0.5       *         900       120       0.5       *         1000       10       0.5       *         1000       30       0.5       *         1000       30       0.5       *         1000       60       0.5       *         1000       10       0.5       *         1000       60       0.5       *         1000       60       0.5       *         1000       60       0.5       *         1000       60       0.5       *         1000       60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1000            | 30            |                             |

| 1000       120       0.1         600       120       0.5         600       300       0.5       *         650       120       0.5       *         700       60       0.5       *         700       120       0.5       *         800       300       0.5       *         800       300       0.5       *         900       10       0.5       *         900       30       0.5       *         900       30       0.5       *         900       120       0.5       *         1000       10       0.5       *         1000       10       0.5       *         1000       30       0.5       *         1000       60       0.5       *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1000            | 60            |                             |

| 600       120       0.5         600       300       0.5         650       120       0.5         650       300       0.5         700       60       0.5         700       120       0.5         700       300       0.5         800       60       0.5         800       120       0.5         800       300       0.5         900       10       0.5         900       30       0.5         900       120       0.5         1000       10       0.5         1000       10       0.5         1000       30       0.5         1000       0.5       0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1000            | 120           |                             |

| 600       300       0.5       *         650       120       0.5       *         650       300       0.5       *         700       60       0.5       *         700       120       0.5       *         800       60       0.5       *         800       120       0.5       *         800       300       0.5       *         900       10       0.5       *         900       30       0.5       *         900       120       0.5       *         1000       10       0.5       *         1000       30       0.5       *         1000       30       0.5       *         1000       60       0.5       *         1000       5       *       *         1000       60       0.5       *         1000       5       *       *         1000       60       0.5       *         1000       60       0.5       *         1000       60       0.5       *         1000       60       0.5       * <td>600</td> <td>120</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 600             | 120           |                             |

| 650       120       0.5         650       300       0.5         700       60       0.5         700       120       0.5         700       300       0.5         800       60       0.5         800       120       0.5         800       300       0.5         900       10       0.5         900       30       0.5         900       120       0.5         1000       10       0.5         1000       30       0.5         1000       30       0.5         1000       0.5       0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 600             | 300           |                             |

| 650       300       0.5       *         700       60       0.5       *         700       120       0.5       *         800       60       0.5       *         800       120       0.5       *         800       300       0.5       *         900       10       0.5       *         900       30       0.5       *         900       120       0.5       *         1000       10       0.5       *         1000       30       0.5       *         1000       30       0.5       *         1000       60       0.5       *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 650             | 120           |                             |

| 700       60       0.5         700       120       0.5         700       300       0.5         800       60       0.5         800       120       0.5         800       300       0.5         900       10       0.5         900       30       0.5         900       60       0.5         900       120       0.5         1000       10       0.5         1000       30       0.5         1000       60       0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 650             | 300           |                             |

| 700       120       0.5         700       300       0.5         800       60       0.5         800       120       0.5         800       300       0.5         900       10       0.5         900       30       0.5         900       60       0.5         900       120       0.5         1000       10       0.5         1000       30       0.5         1000       60       0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 700             | 60            |                             |

| 700       300       0.5       *         800       60       0.5         800       120       0.5         800       300       0.5         900       10       0.5         900       30       0.5         900       60       0.5         900       120       0.5         1000       10       0.5         1000       30       0.5         1000       60       0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 700             | 120           |                             |

| 800       60       0.5         800       120       0.5         800       300       0.5         900       10       0.5         900       30       0.5         900       60       0.5         900       120       0.5         1000       10       0.5         1000       30       0.5         1000       60       0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 700             | 300           |                             |

| 800       120       0.5         800       300       0.5         900       10       0.5         900       30       0.5         900       60       0.5         900       120       0.5         1000       10       0.5         1000       30       0.5         1000       60       0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 800             | 60            |                             |

| 800       300       0.5         900       10       0.5         900       30       0.5         900       60       0.5         900       120       0.5         1000       10       0.5         1000       30       0.5         1000       60       0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 800             | 120           |                             |

| 900       10       0.5         900       30       0.5         900       60       0.5         900       120       0.5         1000       10       0.5         1000       30       0.5         1000       60       0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 800             | 300           |                             |

| 900       30       0.5         900       60       0.5         900       120       0.5         1000       10       0.5         1000       30       0.5         1000       60       0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 900             | 10            |                             |

| 900 60 0.5<br>900 120 0.5<br>1000 10 0.5<br>1000 30 0.5<br>1000 60 0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 900             | 30            |                             |

| 900 120 0.5<br>1000 10 0.5<br>1000 30 0.5<br>1000 60 0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 900             | 60            |                             |

| 1000     10     0.5       1000     30     0.5       1000     60     0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 900             | 120           |                             |

| 1000 30 0.5<br>1000 60 0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1000            | 10            |                             |

| 1000 60 0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1000            |               |                             |

| 4488                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1000            | 60            |                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1100            | 10            |                             |

<sup>\*</sup> Samples submitted for X-ray analysis

Figure 4 Graphical presentation of a typical process recipe for the deposition experiments of experiment 1.

from the chamber. Oxygen would readily combust with the silane causing a highly dangerous situation. After the purge, the set process pressure of 2 torr was established with the required ratio of silane to argon. After gas stabilization, the lamp was ignited and ramped in closed loop until the temperature was reached. Typical ramp rates were 75 °C/sec. After holding at the desired temperature for the desired time, the lamp was idled and turned off, allowing the wafer to radiatively cool. The deposition gas was then turned off, and the chamber was flushed with inert gas before being opened to the atmosphere for wafer handling.

After deposition, the thicknesses of the grown polysilicon films were measured with a spectrophotometer. Five measurements were taken for each wafer at different sites across the wafer, then averaged. However, if the film thickness uniformity was poor in a certain location on a wafer (as evidenced by a color difference of more than one interference order), then that area was avoided during measurement. The deposition rate was calculated by dividing the mean polysilicon film thickness with the deposition time.

In addition to film thickness, the spectrophotometer was also used to measure the reflectivity of the surface <sup>14</sup>. In this set-up, a deuterium lamp source was passed through a chopper which contained a cut-out section on one half and a silicon reference on the other. The light which passed through the chopper wheel was reflected off the surface of the polysilicon sample. Both signals were sent to a detector to determine the difference in signals. There was found to be a linear correlation between this difference and the root-mean-square surface roughness, which is characteristic of the grain size of the polycrystalline silicon. The reflectance was measured at two wavelengths; 200 and 321 nm (extracted from a spectrum of data, from 200 to 800 nm). The surface roughness parameter, (h) was evaluated using the equation <sup>15</sup>

$h = C \lambda (\Delta A) 0.5$

where C = 0.099 is a geometrical factor

$\lambda$  is the wavelength

$\Delta A = -2 \log_{10} (R / R_{Si})$

R is the reflectance of the sample

RSi is the reflectance of single-crystal silicon.