## San Jose State University SJSU ScholarWorks

Master's Theses

Master's Theses and Graduate Research

2007

# Design and analysis of an ultra low power UHF RFID front-end

Maryam Tabesh San Jose State University

Follow this and additional works at: https://scholarworks.sjsu.edu/etd theses

### Recommended Citation

Tabesh, Maryam, "Design and analysis of an ultra low power UHF RFID front-end" (2007). *Master's Theses*. 3718. DOI: https://doi.org/10.31979/etd.2fz7-by99 https://scholarworks.sjsu.edu/etd\_theses/3718

This Thesis is brought to you for free and open access by the Master's Theses and Graduate Research at SJSU ScholarWorks. It has been accepted for inclusion in Master's Theses by an authorized administrator of SJSU ScholarWorks. For more information, please contact scholarworks@sjsu.edu.

## DESIGN AND ANALYSIS OF AN ULTRA LOW POWER UHF RFID FRONT-END

## A Thesis

## Presented to

The Faculty of the Department of Electrical Engineering

San Jose State University

In Partial Fulfillment

of the Requirements for the Degree

Master of Science

by

Maryam Tabesh

August 2007

**UMI N**umber: 1448902

Copyright 2007 by Tabesh, Maryam

All rights reserved.

#### INFORMATION TO USERS

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

### UMI Microform 1448902

Copyright 2007 by ProQuest Information and Learning Company.

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

ProQuest Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

©2007

Maryam Tabesh

ALL RIGHTS RESERVED

## APPROVED FOR THE DEPARTMENT OF ELECTRICAL ENGINEERING

Advisor

Dr. Sotoudeh Hamedi-Hagh

Co-Advisor

Dr. Khosrow Ghadiri

Co-Advisor

Dr. Masoud Mostafavi

APPROVED FOR THE UNIVERSITY

#### **ABSTRACT**

## DESIGN AND ANALYSIS OF AN ULTRA LOW POWER UHF RFID FRONT-END by Maryam Tabesh

Recently, Ultra High Frequency (UHF) Radio Frequency Identification (RFID) has been coined as the next wave of technology that will revolutionized many industry sectors and applications, such as supply chain management, access control, public transportation, library checkout and airport baggage control.

This thesis describes the design of an ultra low power analog front-end circuitry for UHF passive RFID transponder. The overall circuits include voltage multiplier, voltage regulator, demodulator, power-on-reset, ring oscillator, and matching and backscatter modulator.

This thesis presents a novel charge-pump circuit for improved voltage gain and power efficiency of RFID tags. The charge pump is fully integrable and takes advantage of both passive and active multiplication to reduce the required input power. The minimum required input power for a 1.2V supply voltage in the case of a  $50\Omega$  antenna is -20.45 dBm. Simulation results using a .13 $\mu$ m Atmel CMOS process shows that the analog front-end consumes only  $1.828\mu$ W of power.

## **ACKNOWLEDGEMENTS**

I would like to thank my MSEE thesis advisor Professor Sotoudeh Hamedi-Hagh for his continuous support on this thesis. He provided me essential guidance and advice on my thesis.

I also appreciate my co-advisors, Professor Khosrow Ghadiri and Professor Masoud Mostafavi, for their generous support and help.

Last but not least, I would like to thank my husband, Amin Arbabian, and my parents for their support in all aspects of my life.

## **TABLE OF CONTENTS**

| ACKNOWLEDGEMENT                                        | vi |

|--------------------------------------------------------|----|

| CHAPTER 1. INTRODUCTION                                | 1  |

| 1.1 Introduction to RFID Systems                       | 1  |

| 1.2 RFID Applications                                  | 4  |

| 1.3 Active and Passive RFID                            | 6  |

| 1.4 RFID Frequency Range                               | 8  |

| 1.5 Objectives.                                        | 11 |

| CHAPTER 2. RFID TRANSPONDER ARCHITECTURE               | 13 |

| 2.1 Antenna                                            | 14 |

| 2.2 V <sub>DD</sub> Generator                          | 18 |

| 2.2.1 RF-Limiter                                       | 19 |

| 2.2.2 Voltage Multiplier                               | 19 |

| 2.2.3 DC-Limiter                                       | 24 |

| 2.2.4 Regulator                                        | 24 |

| 2.3 Demodulator                                        | 24 |

| 2.3.1 PWM Signal                                       | 25 |

| 2.3.2 Demodulator Block Diagram                        | 26 |

| 2.4 Modulator                                          | 27 |

| 2.4.1 Power Efficiency and Backscatter Modulated Power | 28 |

| 2.4.2 Different Types of Backscatter Modulation        | 30 |

| 2.4.2.1 ASK                                            | 30 |

| 2.4.2.2 PSK                                            | 32 |

| 2.4.3 Matching Network                                 | 33 |

| 2.5 Clock and POR Generator                            | 35 |

| 2.5.1 Clock Generator                                  | 35 |

| 2.5.2 Power on Reset                                   | 35 |

| 2.6 Digital Section                                    | 36 |

| CHAPTER 3. RFID FRONT-END DESIGN                       | 38 |

| 3.1 V <sub>DD</sub> Generator                          | 38 |

| 3.1.1 RF Clamp Circuit                                 | 39 |

| 3.1.2 Voltage Multiplier                               | 41 |

| 3.1.2.1 Design Issues                                  | 43 |

| 3.1.2.2 Proposed Rectifier Circuit                     | 45 |

| 3.1.3 DC-Limiter                                       | 54 |

| 3.1.4 Regulator                                        | 57 |

| 3.1.4.1 Reference Current and Voltage Generator | 59  |

|-------------------------------------------------|-----|

| 3.1.4.2 Series Voltage Regulator                | 65  |

| 3.2 Demodulator                                 | 72  |

| 3.2.1 Envelope Detector                         | 72  |

| 3.2.2 Schmitt Trigger                           | 78  |

| 3.2.3 Integrator                                | 85  |

| 3.2.3.1 Op-Amp                                  | 87  |

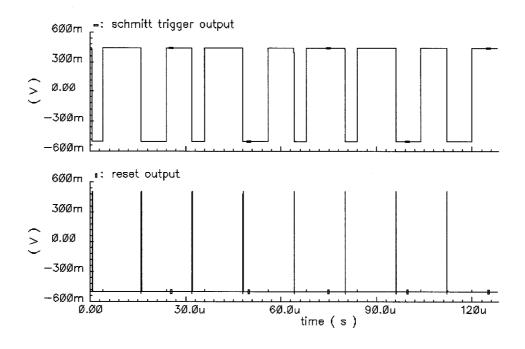

| 3.2.3.2 Integrator Simulation Results           | 90  |

| 3.2.4 Reset Circuit                             | 95  |

| 3.2.5 Comparator                                | 102 |

| 3.2.6 Demodulator Simulation Result             | 105 |

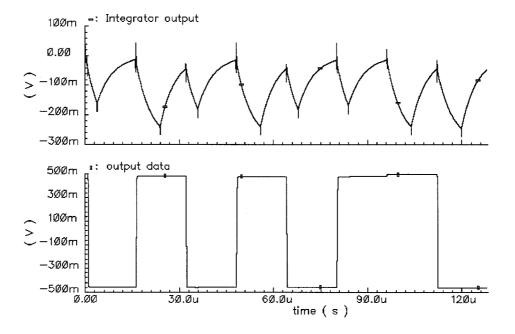

| 3.3 Clock Generator                             | 107 |

| 3.4 Power-on-Reset                              | 115 |

| 3.5 Backscatter Modulation and Matching Network | 118 |

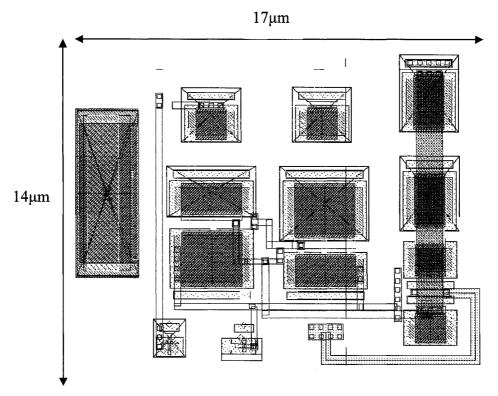

| CHAPTER 4. LAYOUT                               | 122 |

| 4.1 General Layout Issues and Precautions       | 122 |

| 4.2 Inductor Design and Layout                  | 124 |

| CHAPTER 5. CONCLUSION                           | 131 |

| REFERENCES                                      | 133 |

| ADDENIDIV                                       | 126 |

## LIST OF TABLES

| Table 1.1: Characterization of passive and active RFID tags                   | 9   |

|-------------------------------------------------------------------------------|-----|

| Table 1.2: Different RFID frequency ranges and their applications             | 11  |

| Table 3.1: The component values of the RF clamp circuit                       | 42  |

| Table 3.2: Performance comparison of RFID charge pump                         | 53  |

| Table 3.3: The component values of the rectifier circuit                      | 54  |

| Table 3.4: The component values of the positive (negative) DC-limiter circuit | 59  |

| Table 3.5: The component values of the regulator circuit                      | 71  |

| Table 3.6: Regulator parameters                                               | 72  |

| Table 3.7: The component values of the envelope detector circuit              | 77  |

| Table 3.8: The component values of the Schmitt trigger circuit                | 84  |

| Table 3.9: Schmitt trigger parameters                                         | 85  |

| Table 3.10: The component values of the integrator circuit                    | 94  |

| Table 3.11: Integrator parameters                                             | 94  |

| Table 3.12: The component values of the reset circuit                         | 100 |

| Table 3.13: The component values of the comparator circuit                    | 105 |

| Table 3.14: The component values of ring oscillator                           | 113 |

| Table 3.15: The ring oscillator parameters                                    | 115 |

| Table 3.16: The component values of POR circuit                               | 117 |

| Table 4.1: The inductors layout specifications                                | 127 |

| Table 4.2: Inductors extracted pi model parameters                            | 130 |

| Table 4.3: Inductor parameters                                                | 130 |

## LIST OF FIGURES

| Figure 1.1: The RFID system                                                                  | 3 |

|----------------------------------------------------------------------------------------------|---|

| Figure 1.2: RFID application chart                                                           | 5 |

|                                                                                              | 7 |

| Figure 1.4: Inductive coupling and backscatter RFI systems                                   | 0 |

| Figure 2.1: Block diagram of RFID transponder                                                | 3 |

| Figure 2.2: Block diagram of a far-field RFID system                                         | 5 |

| Figure 2.3: Antenna impedance, chip impedance, and range as a function of                    |   |

| frequency for a typical RFID tag                                                             | 6 |

| Figure 2.4: Contours of constant range on gain-transmission coefficient plane as             |   |

| a function of their normalized value to $R_0$                                                | 6 |

| Figure 2.5: Block diagram of a near-field RFID system                                        | 7 |

| Figure 2.6: Block diagram of V <sub>DD</sub> generator                                       | 9 |

| Figure 2.7: Simple circuit of voltage multiplier (a) without loading (b) with                |   |

| loading. 2                                                                                   | 1 |

| Figure 2.8: A 6-stage charge pump voltage multiplier                                         |   |

| Figure 2.9: A single stage voltage multiplier                                                | 2 |

| Figure 2.10: The n <sup>th</sup> stage of the voltage multiplier (a) general topology (b) In |   |

| negative cycles of the input voltage (c) In positive cycles of the input                     |   |

| voltage                                                                                      |   |

| Figure 2.11: Block diagram and waveform of PWM generator                                     |   |

| Figure 2.12: Block diagram of demodulator section                                            |   |

| Figure 2.13: The equivalent circuit for the antenna and circuit                              |   |

| Figure 2.14: Anti-collision scheme                                                           |   |

| Figure 3.1: RF clamp circuit                                                                 |   |

| Figure 3.2: Input voltage after RF clamp circuit                                             |   |

| Figure 3.3. RF-limiter layout.                                                               |   |

| Figure 3.4: The input and output modeling of the charge pump voltage multiplier 4:           |   |

| Figure 3.5: Schematic of the first stage of the charge pump with inductor 4'                 | 7 |

| Figure 3.6: Equivalent circuit of a single stage voltage multiplier (a) Negative             | _ |

| cycles of the input voltage (b) Positive cycles of the input voltage 4                       |   |

| Figure 3.7: Output of the 1-stage voltage multiplier with and without inductor               |   |

| Figure 3.8: Voltage gain after inductor                                                      |   |

| Figure 3.9: Output voltage of the multiplier as a function of input power                    | 0 |

| Figure 3.10: Output voltage of the multiplier for input power of -19.1dBm and                | _ |

| $R_{load}$ of $1M\Omega$                                                                     |   |

| Figure 3.11: Output voltage at different stages of the multiplier                            |   |

| Figure 3.12: Output voltage as a function of the load resistance                             |   |

| Figure 3.13. Voltage rectifier layout                                                        |   |

| Figure 3.14: The crude clamp circuit acting as the positive voltage limiter                  | 4 |

| Figure 3.15: Rectifier output voltage before and after using limiter as a function           | _ |

| of input power                                                                               | ŏ |

| Figure 3.16. DC-limiter layout                                                             |

|--------------------------------------------------------------------------------------------|

| Figure 3.17: The circuit of the voltage regulator                                          |

| Figure 3.18: Block diagram of a self-biasing current source and its                        |

| characterization plot                                                                      |

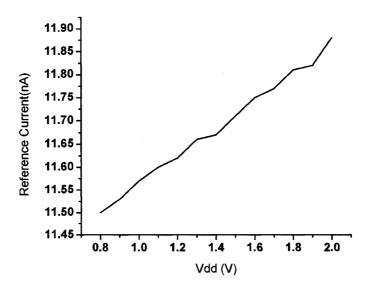

| Figure 3.19: Reference current as a function of DC voltage variation                       |

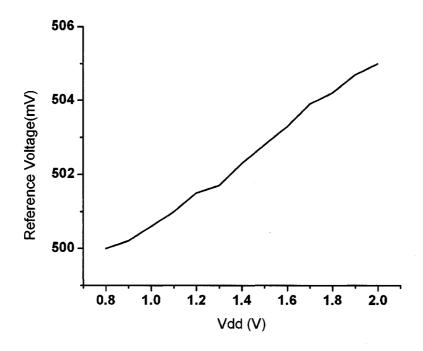

| Figure 3.20: Reference voltage as a function of DC voltage variation                       |

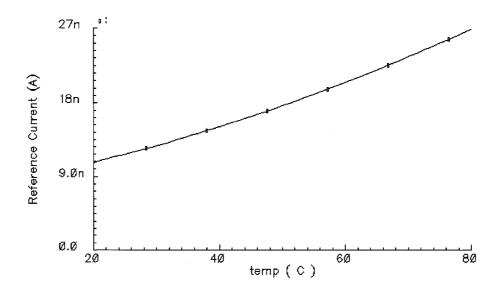

| Figure 3.21: Reference current as a function of temperature                                |

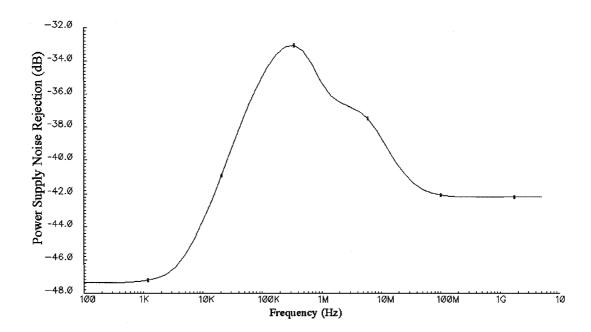

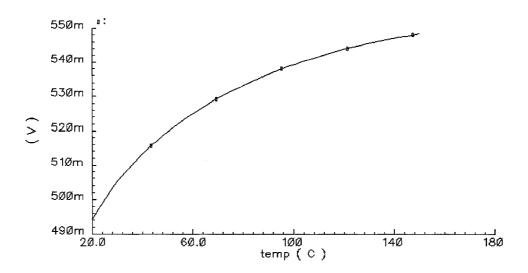

| Figure 3.22: The PSNR of the regulator                                                     |

| Figure 3.23: The positive output of the voltage regulator as a function of                 |

| temperature                                                                                |

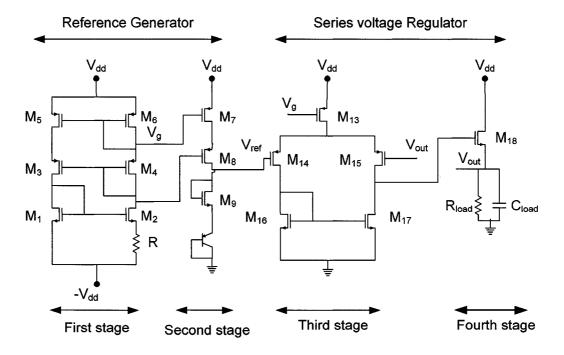

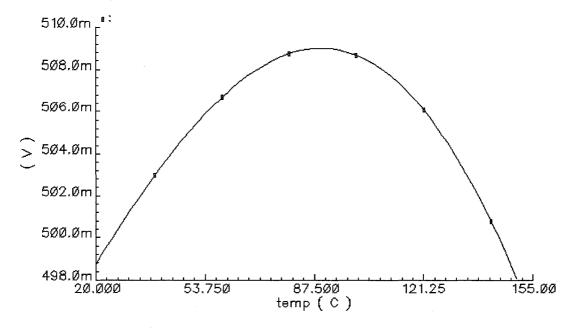

| Figure 3.24: Circuit of less-temperature sensitive voltage regulator                       |

| Figure 3.25: The output voltage of less-temperature sensitive voltage                      |

| regulator as a function of temperature                                                     |

| Figure 3.26. Layout of the positive part of regulator circuit                              |

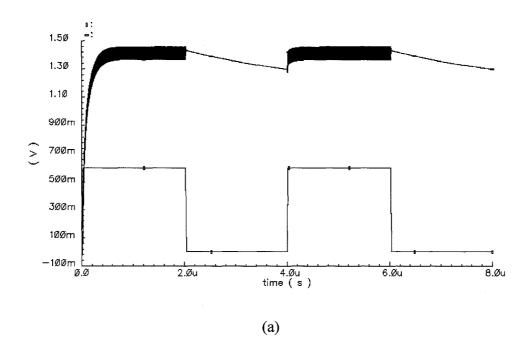

| Figure 3.27: Input voltage envelope and output voltage of the envelope                     |

| detector for (a) high input voltage and high gain multiplier (b)                           |

| low input voltage and low gain multiplier                                                  |

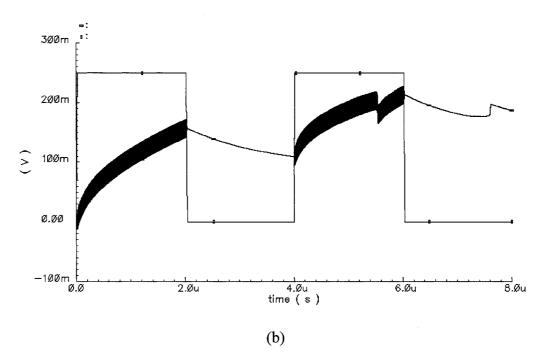

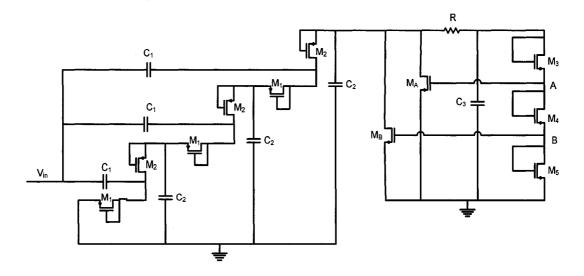

| Figure 3.28: The envelope detector circuit                                                 |

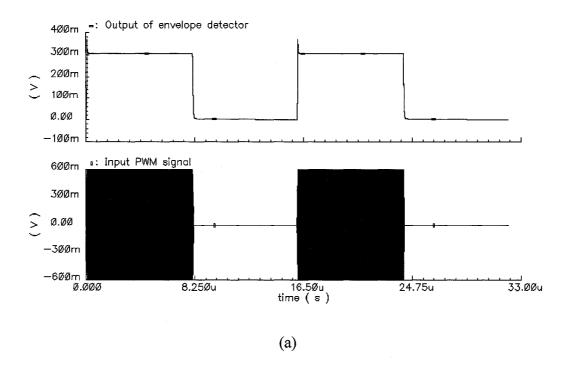

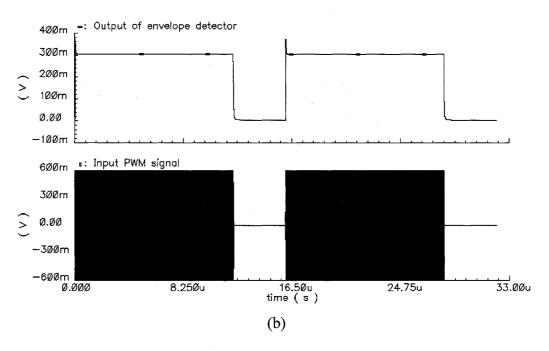

| Figure 3.29: Input PWM signal and output of envelope detector for (a) "zero"               |

| input (b) "one" input                                                                      |

| Figure 3.30. Envelope detector layout                                                      |

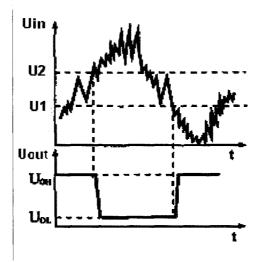

| Figure 3.31: Input and output waveform of a schmitt trigger circuit                        |

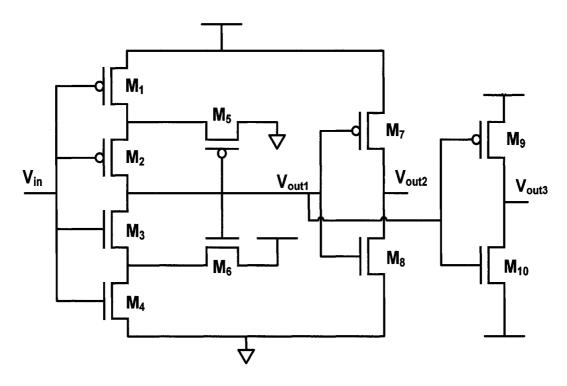

| Figure 3.32: A standard CMOS Schmitt Trigger circuit                                       |

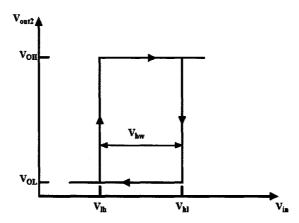

| Figure 3.33: CMOS Schmitt Trigger voltage transfer characteristic                          |

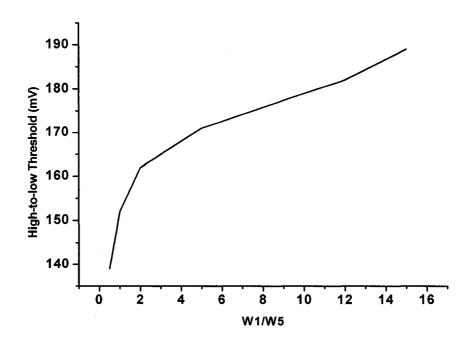

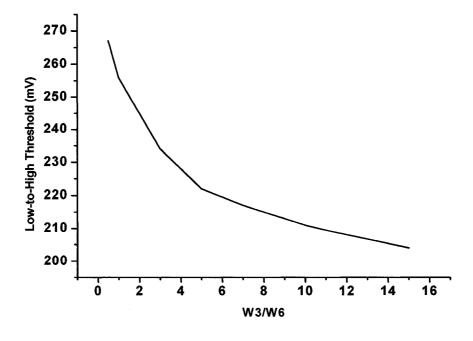

| Figure 3.34: High-to-low voltage threshold as a function of W <sub>1</sub> /W5             |

| Figure 3.35: Low-to-high voltage threshold as a function of W <sub>3</sub> /W <sub>6</sub> |

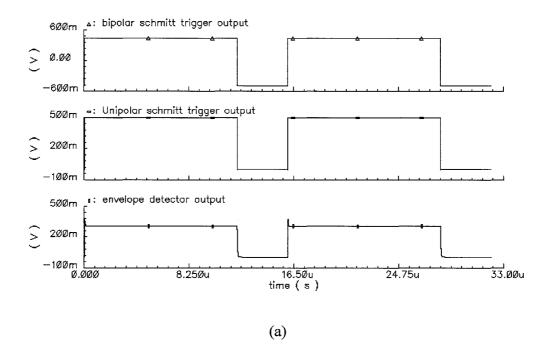

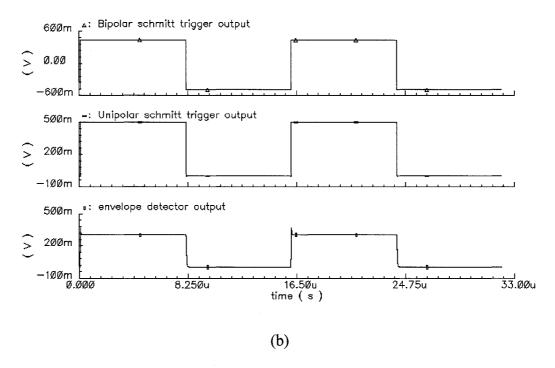

| Figure 3.36: Input and output signals of Schmitt trigger circuit for (a) "zero"            |

| input (b) "one" input                                                                      |

| Figure 3.37. Schmitt Trigger layout                                                        |

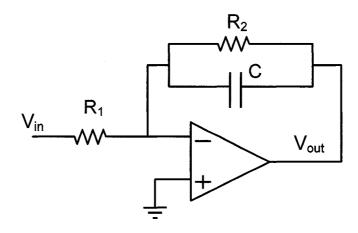

| Figure 3.38: Integrator circuit                                                            |

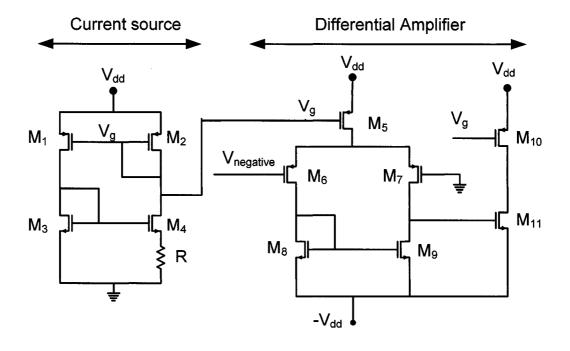

| Figure 3.39: The schematic of the two-stage op-amp circuit used in integrator              |

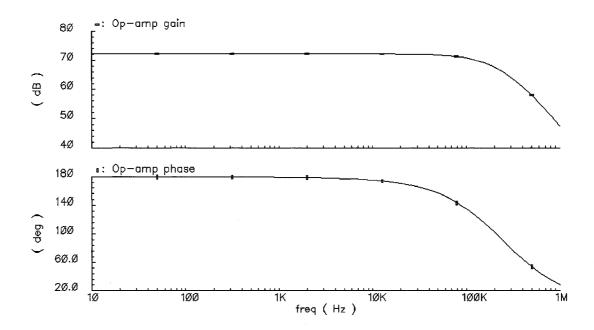

| Figure 3.40: Gain and phase response of the op-amp as a function of                        |

| frequency                                                                                  |

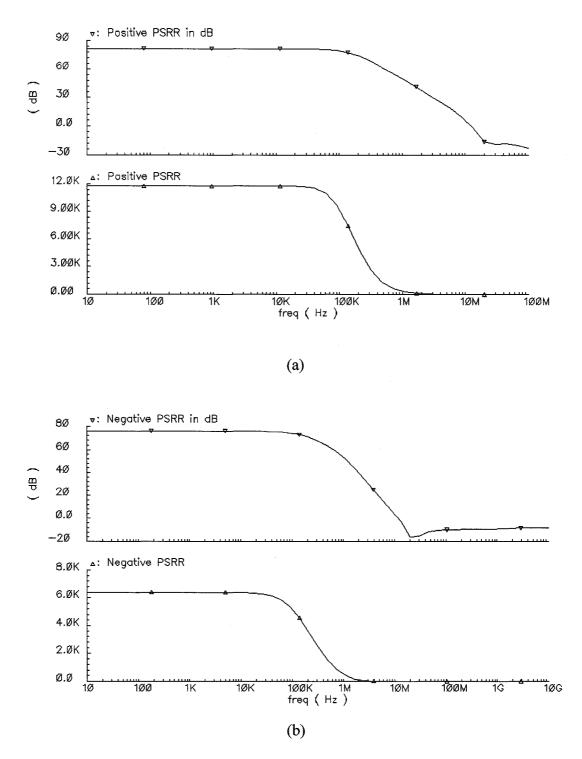

| Figure 3.41: PSRR of the op-amp (a) positive PSRR (b) negative PSRR                        |

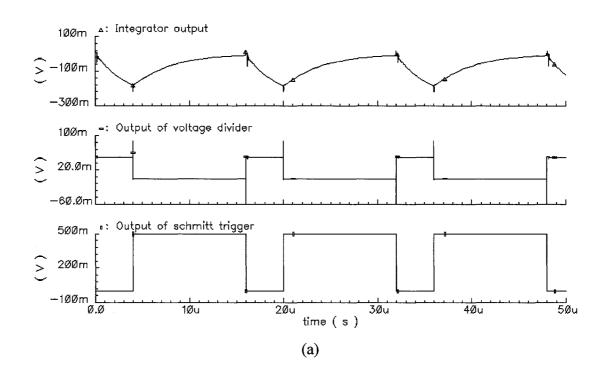

| Figure 3.42: Output of integrator circuit and voltage divider for (a) "one"                |

| input (b) "zero" input                                                                     |

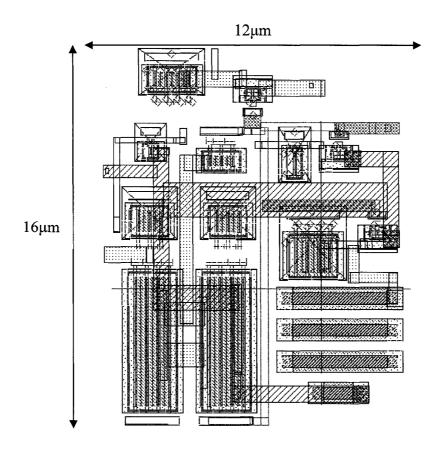

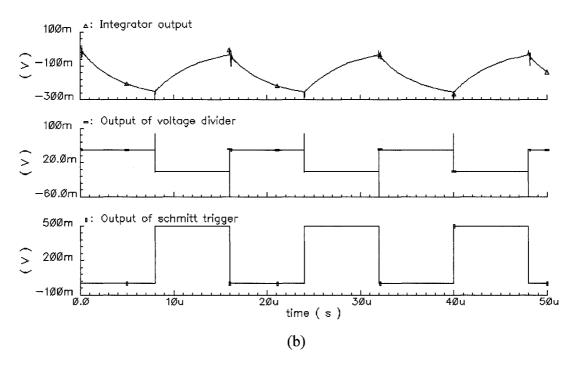

| Figure 3.43. The integrator layout                                                         |

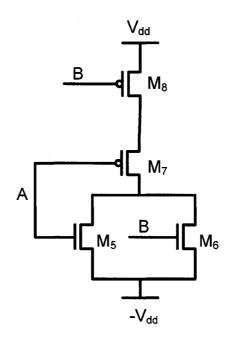

| Figure 3.44: Schematic of the reset circuit                                                |

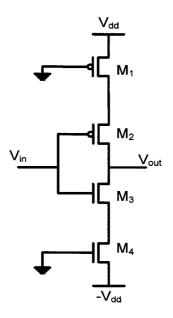

| Figure 3.45: The current-starved inverter used in reset circuit                            |

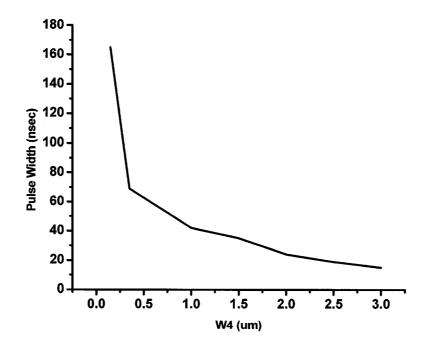

| Figure 3.46: The pulse width as a function of W4                                           |

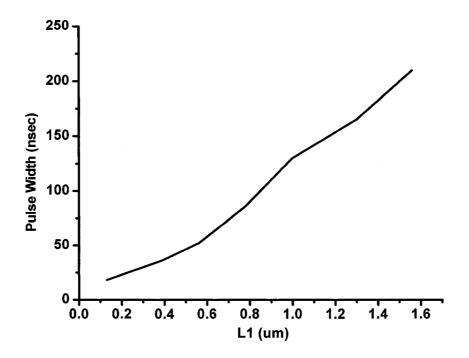

| Figure 3.47: The pulse width as a function of L1                                           |

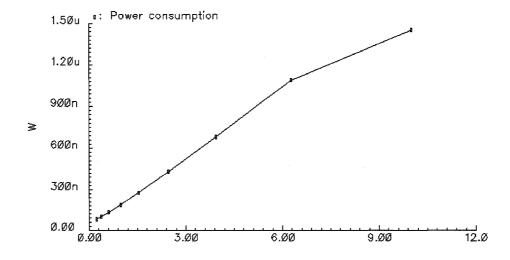

| Figure 3.48: The power consumption of reset circuit as a function of W3                    |

| Figure 3.49: Schematic of NOR gate                                                         |

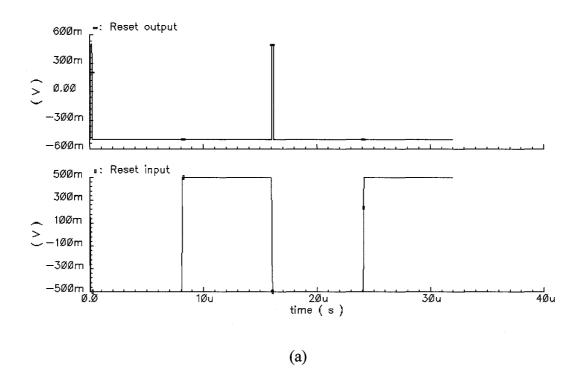

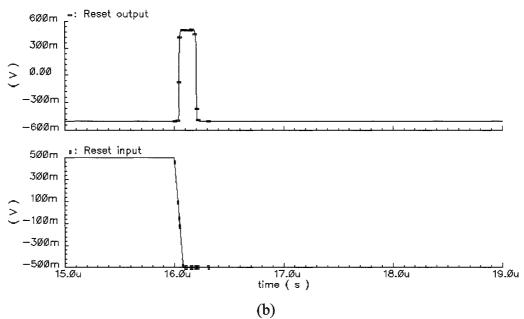

| Figure 3.50: Input and output of the reset circuit (a) zoom out (b) zoom in  | 10  |

|------------------------------------------------------------------------------|-----|

| Figure 3.51. The reset layout                                                | 102 |

| Figure 3.52: The comparator circuit                                          | 103 |

| Figure 3.53: Gain and phase of the comparator circuit                        | 104 |

| Figure 3.54. The comparator layout                                           | 104 |

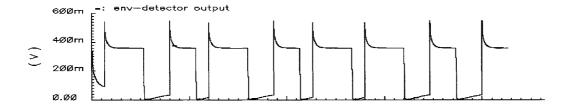

| Figure 3.55: Demodulator simulation result                                   | 100 |

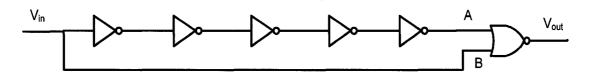

| Figure 3.56: The five-stage ring oscillator                                  | 10' |

| Figure 3.57: Model of an inverter circuit                                    | 10  |

| Figure 3.58: The current-starved inverter                                    | 110 |

| Figure 3.59: The schematic of ring oscillator                                | 11  |

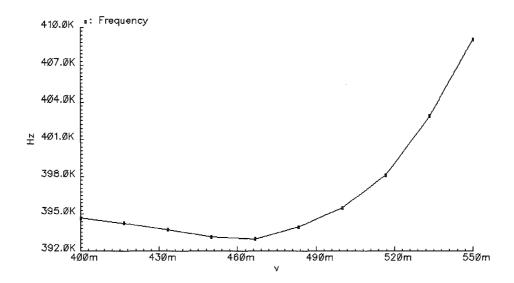

| Figure 3.60: The frequency of oscillation as a function of Vdd               | 112 |

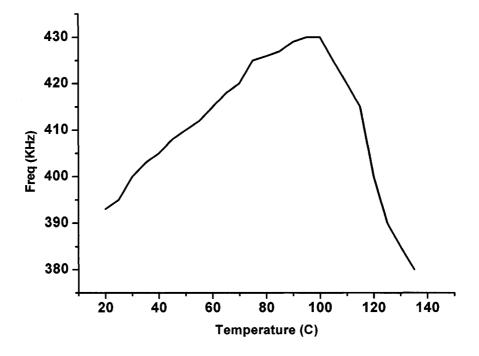

| Figure 3.61: The frequency of oscillation as a function of temperature       | 112 |

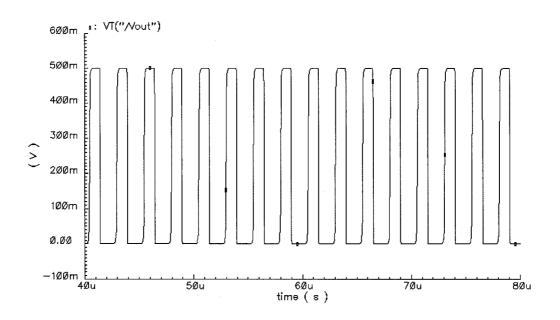

| Figure 3.62: Output of the ring oscillator                                   | 114 |

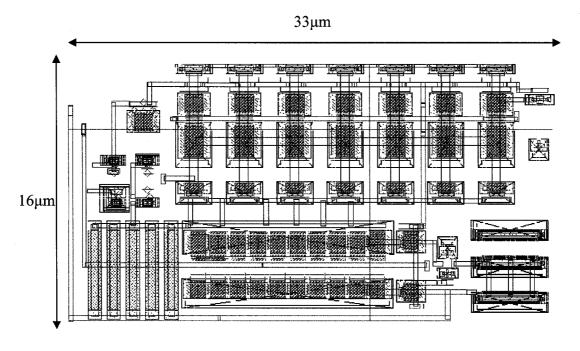

| Figure 3.63. Ring oscillator layout                                          | 11  |

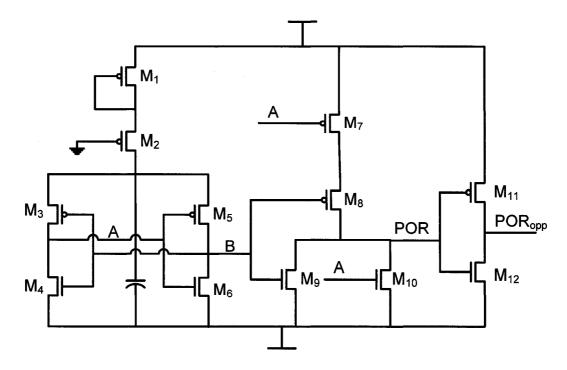

| Figure 3.64: The power on reset circuit                                      | 11  |

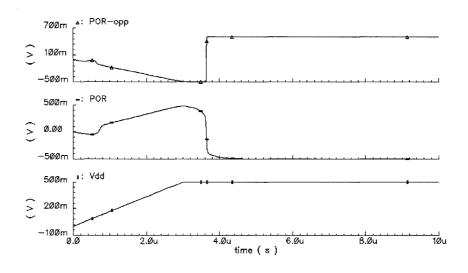

| Figure 3.65: The output signal of the power on reset circuit                 | 11  |

| Figure 3.66. POR layout                                                      | 11  |

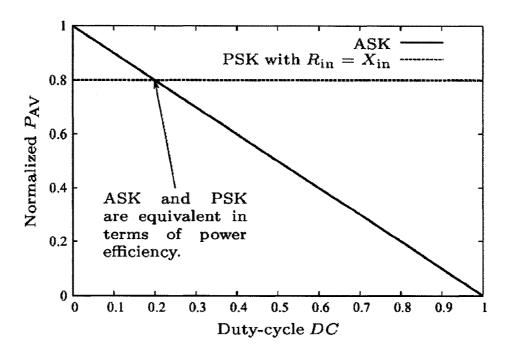

| Figure 3.67: Average available input power as a function of DC normalized to |     |

| P <sub>av</sub>                                                              | 11  |

| Figure 3.68: Parallel modulator configuration                                | 12  |

| Figure 3.69: The matching network                                            | 12  |

| Figure 3.70: The input $S_{11}$ as a function of frequency                   | 12  |

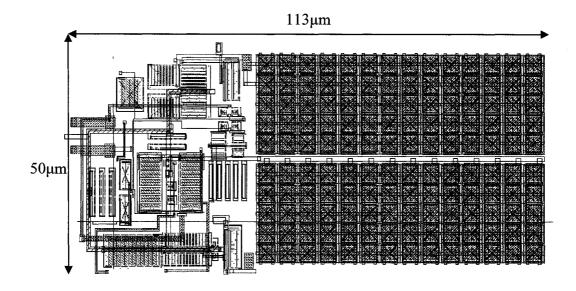

| Figure 4.1: The RFID front-end layout                                        | 12  |

| Figure 4.2: The inductor pi model                                            | 12  |

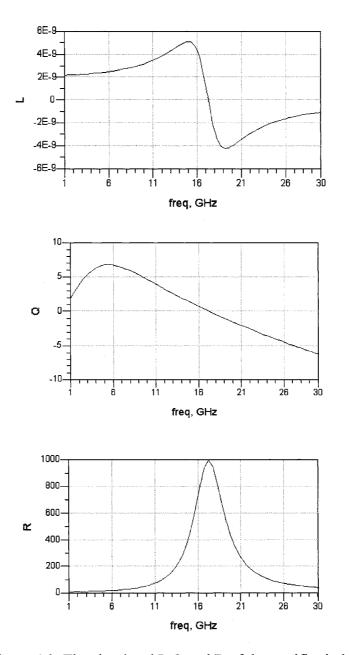

| Figure 4.3: The simulated L,Q and R of the rectifier inductor                | 12  |

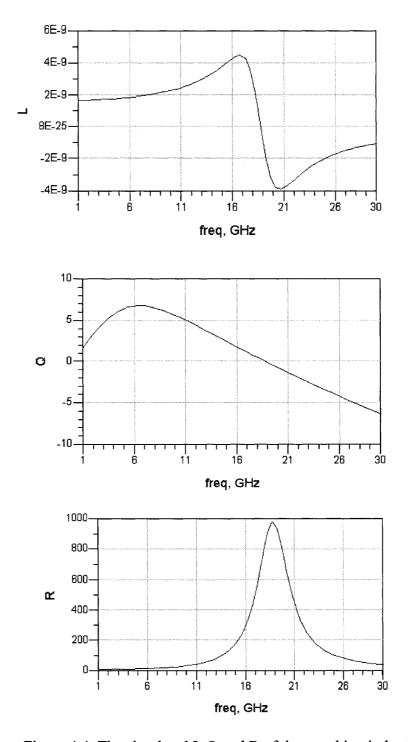

| Figure 4.4: The simulated L,Q and R of the matching inductor                 | 12  |

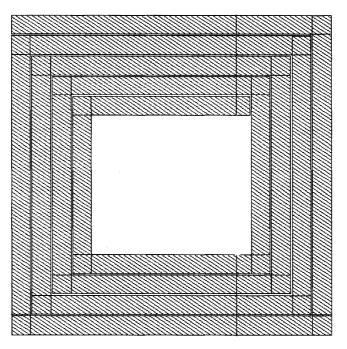

| Figure 4.5: Rectifier-inductor layout                                        | 13  |

#### **CHAPTER 1. INTRODUCTION**

This chapter is about the Radio Frequency Identification (RFID) standards and its applications in the era of automatic identification systems. Section 1.1 introduces the RFID system and describes the block diagram of RFID tag and reader briefly. Section 1.2 discusses the RFID applications. Section 1.3 provides overview of different kinds of RFID tags in term of power supply. Section 1.4 discussed about the available frequency ranges for RFID technology. Finally, section 1.5 gives the overview of main objectives of the thesis.

## 1.1 Introduction to RFID Systems

Radio frequency identification (RFID) is a term that is often utilized for systems which transmit the ID of a certain object using wireless technology. Previous to RFID systems, barcode technology was widely used for the purpose of identification.

However, barcodes fail to provide many strategic advantages and are currently being replaced in many areas. Barcodes are very cheap but their main disadvantage is due to the low capacity and the fact that they cannot be programmed. A feasible solution to the problem of data capacity is putting the data on chips. The ideal case would be the contactless data transfer between the device (product) and the reader. The required power to operate the chip could also be transferred using radio waves. This would lead to the concept of RFID technology.

Some of the advantages of the RFID systems over the barcodes are non-line of sight communication, ability to identify moving elements, large area of coverage and automatic integration with back end solutions which provides end to end integration of data in real time.

The RFID systems are more expensive compare to the barcodes. Also, they are bulkier, due to embedding of electronic components in the tag. Furthermore, the RFID system tags should be designed for specific applications because they are prone to electrical/physical damages due to the environmental conditions [1].

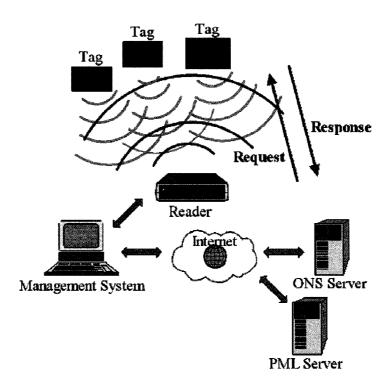

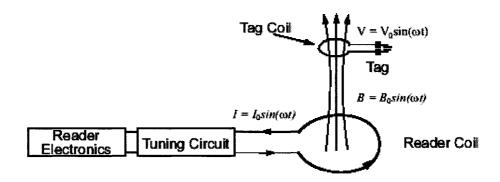

In a general RFID system, the tag generates a signal containing the required information used by the tag reader. This signal is passed to the digital processor section for further processing depending on the specific application [2]. An RFID system is shown in Figure 1.1.

A typical RFID system contains these three main blocks:

- RFID tag or transponder

- RFID reader or transceiver

- Data processing subsystem

The tag consists of the antenna, the wireless transponder circuitry and also the encapsulating material. The RFID tag systems could be active or passive depending on the specific application. The active tags have power supply embedded in them. The passive tags however, have on chip transducers that transform the incoming RF power to the required DC power. The RF power may be transferred by magnetic coupling or far

field electromagnetic radiation. Passive tags tend to be cheaper and have theoretically infinite life time. Their range is lower (typically less than ten meters) and they are more sensitive to regulatory constraints.

Figure 1.1. The RFID system

An RFID reader (or integrator) consists of an antenna, an RF transceiver and a decoder, which sends periodic signals to inquire about any tag in vicinity. It detects the tags in the working range and identifies their ID signals. This could be used to look for a specific product, create an inventory list or even program the tags.

The data processing subsystem also provides the means of processing and storing the data [2].

## 1.2 RFID Applications

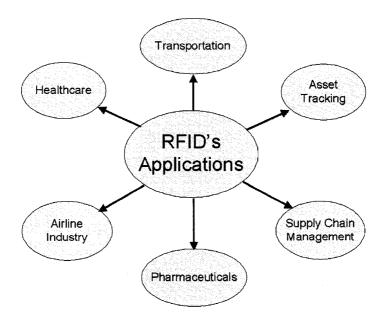

There are two main areas of applications, defined as short range and long range. Long range applications can be categorized as track and trace applications but RFID technology can provide extra functionality for specific product tracking and even authentication. RFID is a big step towards the automation of data collection process.

Companies spend a great deal of time and effort to identify the objects in their inventory.

RFID technology can help these companies organize their search with a lot less effort.

RFID helps the companies transfer their data safely. Companies use independent suppliers, data from each of these suppliers are to be carried on tags and then uploaded to the Company's central system securely.

Companies will have a great deal of control over the product throughout the life cycle. Product failures could be detected and better understood through effective tracking. In cases where product recall is necessary because of some unanticipated problem, RFID technology can ease the process significantly.

With this technology becoming more and more popular, there would be better data about the performance of products after they are produced. As an example, a car could have individually tagged parts. The essential date could be collected at the point of accident for processing of the source of failure or even for statistical purposes.

The eventual aim of RFID in retail and manufacturing is eliminating the intermediary.

A perfect supply chain would require no distribution center. Products would be delivered directly from the factory to the retail center [2].

RFID systems have been used in hospitals for tracking patient's location and also to provide effective localization of doctors and nurses. Expensive equipment in hospital environments could be tracked using RFID technologies.

RFID chips are used for animals where devices are injected under the animal's skin.

Under a government initiative to control rabies, all Portuguese dogs must be RFID tagged by 2007 [3]. The tag contains critical information regarding the dog's history and also the information on the owner of the dog.

The Orlando/Orange County Expressway Authority (OOCEA) is using an RFID based traffic-monitoring system, which uses roadside RFID readers to collect signals from transponders that are set up in almost 1 million E-Pass and SunPass customer vehicles [3].

Different RFID applications are shown in Figure 1.2. It shows that RFID applications are increasing in different areas.

Figure 1.2. RFID application chart

#### 1.3 Active and Passive RFID

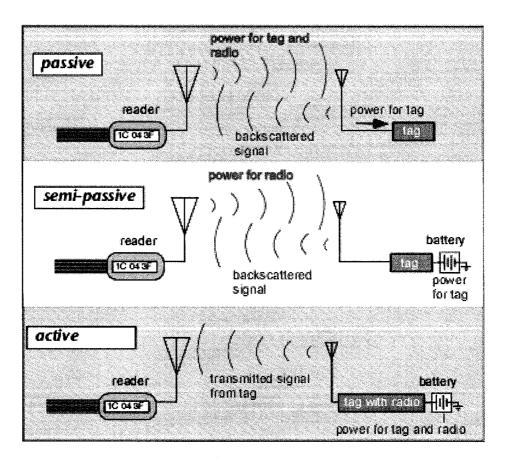

As it was briefly described in the previous section RFID tags are categorized into three main types: Passive, Semi-Passive and Active. Passive RFID tags have no internal power supply in the chip. Energy is transferred through radio waves and is then rectified on the chip once it is absorbed by the antenna or the coupling medium. The tag circuitry must consume as little energy as possible in order for the power transfer to be feasible. Most passive tags use backscatter as method of communicating with the reader. The antenna is designed to be able to work in two modes, one where power is absorbed and the other in which it is reflected. Through the change of the reflection coefficient of the antenna, the tag communicates with the reader. The response of a passive RFID tag is not just an ID number (GUID): tag chip can contain nonvolatile EEPROM (Electrically Erasable Programmable Read-Only Memory) for storing data [4].

Semi-passive RFID tags have an additional small battery. This battery allows the tag

IC to be constantly powered. The small battery removes the need for power recovery

circuits that are employed in passive tags. In this case the antenna could be optimized for

backscatter operation. Semi-passive tags operate in longer distance scenarios and are

faster to respond, however their life time is limited and also they cost more.

Unlike passive and semi-passive RFID tags, active RFID tags (also known as beacons), have their own internal power source which is used to power any ICs and generate the outgoing signal. They are often called beacons because they broadcast their own signal instead of using backscatter modulation for their communication. Active tags have longer range as well as being able to send information independently. They have a

better data processing power and generally contain larger memory arrays. Many active tags have practical ranges of tens of meters, and a battery life of up to 10 years [4]. Passive, active, and semi-passive RFID systems are shown in Figure 1.3.

The choice of active versus passive tags has consequences for overall system cost, initial tag cost, tag life and battery life.

Figure 1.3. Passive, active, and semi-passive RFID systems (Courtesy of Dr. Daniel Dobkin, Enigmatics, Sunnyvale, CA)

In comparison, passive tags have a lower cost due to low-cost tags and long tag life.

They are also easier to mount and install on packages and products. The passive tags

have indefinite lifespan as they do not operate on batteries. The choice between active tags and passive tags is related to other system design issues. Active tags support higher data rates and can have larger memories, but passive tags also support acceptable bit rate and data handling capabilities required by many applications. Active tags can send data at any instance of time that they need to and this provides them with a great deal of flexibility. One disadvantage of passive RFID tags is the fact that some countries do not permit enough radiation power and also suitable frequency bands for the support of these tags [3].

Active tags generally cost more and a part of this is due to the cost of battery and its connection. Battery life causes reliability issues for the tags and this will raise the overall cost. An overall view of tag cost must definitely take into account the whole tag or in some other cases the battery replacement costs [5]. A comparison between active and passive RFID tags is illustrated in Table 1.1.

## 1.4 RFID Frequency Range

RFID tags fall into many different sub-categories based on their operating frequency, coupling method and the expected range of the system. RFID systems operate in the frequency range of 135kHz to 5.8GHz. Electric, magnetic and electromagnetic fields are used for the physical coupling. The range of the system varies from a few millimeters to above 15m depending on various parameters [6].

Table 1.1. Characterization of passive and active RFID tags

|                                              | Active RFID                   | Passive RFID                              |

|----------------------------------------------|-------------------------------|-------------------------------------------|

| Tag power source                             | Internal to tag               | Energy transferred from the reader via RF |

| Tag battery                                  | Yes                           | No                                        |

| Availability of tag power                    | Continuous                    | Only within field of reader               |

| Required signal strength from reader to tag  | Low                           | High                                      |

| Available signal strength from tag to reader | High                          | Low                                       |

| Communication range                          | Long range (100m)             | Short range (up to 15m)                   |

| Data storage                                 | Large read/write data storage | Small read/write data storage             |

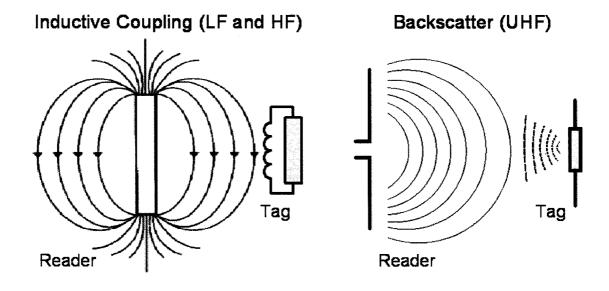

Systems that achieve a small range (less than 1cm) are generally known as close coupling systems. These systems require the tag to be inserted into the reader or to be brought to close proximity of it. Close coupling systems generally operates in frequencies between DC and 30MHz and are coupled using electric and magnetic fields (capacitive and inductive coupling).

RFID Systems that have ranges close to one meter are known as remotely coupled systems. Most of remotely coupled devices operate based on magnetic (inductive) coupling mechanisms. Usual frequencies for these systems are from 135kHz to 13.56MHz.

RFID systems with ranges above 1m are known as long-range systems. Nearly all of these RFID systems work using electromagnetic far-field radiation of waves in the UHF and microwave range. A great percentage of these systems are widely known as backscatter systems. Most of these tags are operating in the UHF bands (868MHz in Europe and 915MHz in USA) and at lower microwave frequencies of 2.4GHz and 5.8GHz. Inductive coupling and backscatter systems are shown in Figure 1.4.

System level constraints and applications dictate the use of specific tag systems. For example, the UHF RFID tags are generally utilized for long range or high data rate applications. The frequency ranges and their applications are listed in Table 1.2 [1].

Figure 1.4. Inductive coupling and backscatter RFID systems

Table 1.2. Different RFID frequency ranges and their applications

| Frequency range                  | Description                                              | Typical applications                                                                                                          |

|----------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| <135KHz                          | Low Frequency, Inductive coupling                        | Access Control & Security Widgets identification through manufacturing processes Ranch animal identification OEM applications |

| 13.56 MHz                        | High Frequency, Inductive coupling                       | Access Control Library books Laundry identification OEM applications                                                          |

| 868 to 870 MHz<br>902 to 928 MHz | Ultra High Frequencies<br>(UHF), Backscatter<br>coupling | Supply chain tracking                                                                                                         |

| 2.400 to 5.8 GHz                 | SHF, Backscatter coupling                                | Asset tracking Highway toll tags Vehicle tracking                                                                             |

## 1.5 Objectives

This thesis mainly focused on the UHF RFID front-end for long range applications. The main challenges in the passive RFID tags are supply voltage generation and power efficiency. So, most parts of the circuit operate in subthreshold to operate in low power regime. The 2.4GHz frequency is chosen for this project to achieve high data rate and small antenna size.

Chapter 2 of the thesis talks about the RFID transponder architecture and explains the RFID transponder fundamentals and its important specifications. Chapter 3 illustrates the

RFID tag's front-end schematic design and simulation results. Chapter 4 starts with the layout issues and discusses the inductor design analysis and post-layout simulation results achieved using Atmel .13 $\mu$ m CMOS technology. Chapter 5 concludes the thesis and summarizes the results.

## **CHAPTER 2. RFID TRANSPONDER ARCHITECTURE**

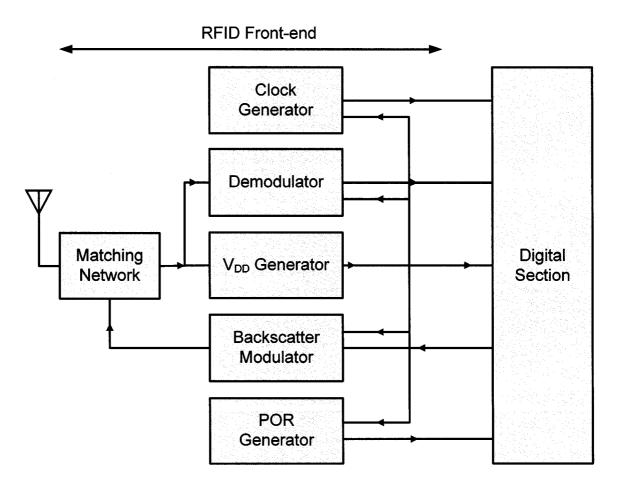

The block diagram of an RFID system is shown in Figure 2.1. In this chapter a brief description of each block is presented. Section 2.1 is about the antenna part. Section 2.2 discussed about the  $V_{DD}$  generator block. Section 2.3 leads to the detail description of the demodulator part. The modulator and matching blocks are described in section 2.4. Section 2.5 discusses about the clock and power-on-reset generator and finally an overview of the digital part is provided in section 2.6.

Figure 2.1. Block diagram of RFID transponder

## 2.1 Antenna

As discussed in chapter one, depending on the application and the frequency of operation, the tag antenna can either operate in the near-field (coupling) or far-field regions. In near-field operation the tag usually communicates using inductive coupling mechanism. In the far-field operation, electromagnetic radiation of radio-frequency waves transmits the required data and energy between the tag and the antenna.

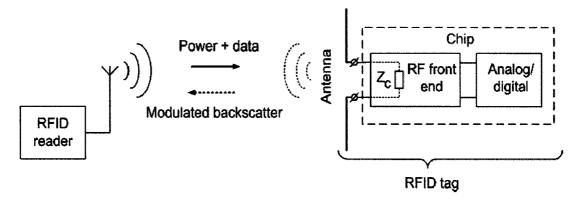

In high frequency RFID systems, the far-field antennas have been used. The block diagram of such systems is shown in Figure 2.2. One of the most important characteristics of RFID systems is their operation range and this is greatly affected by the antenna design. The read range is also sensitive to the specific tag orientation, the material that the tag is placed on, and to the propagation environment between the tag and the reader [7]. The read range can be calculated using Friis free-space formula as

$$R = \frac{\lambda}{4\pi} \sqrt{\frac{P_t G_t G_r \tau}{P_{th}}}$$

(Eq. 2.1)

Where  $\lambda$  is the wavelength,  $P_t$  is the power transmitted by the reader,  $G_t$  is the gain of the transmitting antenna,  $G_r$  is the gain of the receiving antenna,  $P_{th}$  is the minimum threshold power necessary to provide enough power to the RFID tag chip, and  $\tau$  is the power transmission coefficient given by [7]

$$\tau = \frac{4R_{\text{chip}}R_{\text{ant}}}{\left|Z_{\text{chip}} + Z_{\text{ant}}\right|^2}$$

(Eq. 2.2)

Where  $Z_{chip}=R_{chip}+jX_{chip}$  is chip impedance and  $Z_{ant}=R_{ant}+jX_{ant}$  is antenna impedance.

Figure 2.2. Block diagram of a far-field RFID system (Courtesy of Dr.Seshagiri Rao from paper "Antenna Design for UHF RFID Tags: A Review and a Practical Applications," *IEEE Transactions on Antennas and Propagation*. © IEEE 2005. Reprinted with permission)

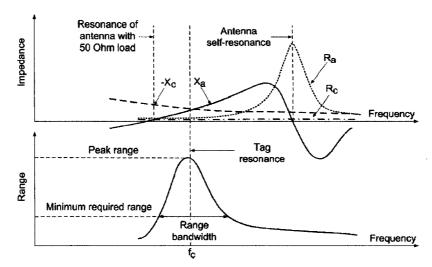

Qualitative behavior of antenna impedance, chip impedance, and read range for a typical RFID tag is illustrated in Figure 2.3 as a function of frequency [7]. A tag range bandwidth can be defined as being the frequency bandwidth over which the tag sustains an acceptable minimum range.

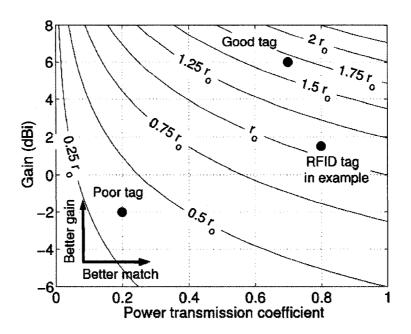

In general the range of an RFID system is mostly determined by the  $\tau$  and its dependency on frequency. The best achievable range occurs in the case where the antenna is matched to the input impedance of the chip. Contours of constant range are plotted on gain-transmission coefficient plane as a function of their normalized value to  $R_0$  in Figure 2.4 [7].  $R_0$  is the maximum range when the antenna impedance is totally matched to the chip impedance.

The RFID tag antenna design process involves inevitable tradeoffs between antenna gain, impedance, and bandwidth as well cost issues with the size of the antenna and the substrate being used.

Figure 2.3. Antenna impedance, chip impedance, and range as a function of frequency for a typical RFID tag

(Courtesy of Dr.Seshagiri Rao from paper "Antenna Design for UHF RFID Tags: A Review and a Practical Applications," *IEEE Transactions on Antennas and Propagation*. © IEEE 2005. Reprinted with permission)

Figure 2.4. Contours of constant range on gain-transmission coefficient plane as a function of their normalized value to  $R_0$

(Courtesy of Dr.Seshagiri Rao from paper "Antenna Design for UHF RFID Tags: A Review and a Practical Applications," *IEEE Transactions on Antennas and Propagation*. © IEEE 2005. Reprinted with permission)

There are various types of antennas that can be used for RFID applications. The most popular one is the well known dipole antenna. The radiation resistance of a short electric dipole of length l, which operates at a specific frequency for which the free space propagation constant has magnitude  $\beta$ , is given by (under the assumption that the current distribution of the antenna is uniform and equal to the feed point current)

$$R_{r} = 20(\beta l)^{2} \qquad \Omega \tag{Eq.2.3}$$

The other types of antenna are loop antennas. Also, sometimes for decreasing the size of the antenna some fractal patterns may be used that employ self-similar structures.

In general low frequency passive tags use an induced voltage for their operation.

Figure 2.5 shows a simple geometry of an RFID inductive system. As described in the figure, in close proximity operation of the tag and the reader, the time varying magnetic field strength induces a voltage on the tag coil. The induced voltage is given by

$$V_{\text{induced}} = -N \frac{d\psi}{dt}$$

(Eq. 2.4)

Figure 2.5. Block diagram of a near-field RFID system (Courtesy of Microchip Technology Inc., Chandler, AZ)

Where

$$\psi = \int B.dS$$

(Eq.2.5)

Where S is the surface area of the coil and N is the number of turns in the coil.

To operate with maximum induced voltage, the two coils should be placed in parallel so that the flux coupling is optimized. This condition will result in the maximization of the coupled voltage and from there the read range of the tag.

From the equation (2.4) and by substituting the magnetic field formula, the induced voltage in tags coil can be as follows [8]

$$V_{induced} = -N_{tag} \frac{d\psi}{dt} = -N_{tag} \frac{d}{dt} (\int\!\! B.dS) = - \left[ \frac{\mu_0 N_{tag} N_{reader} a^2 (\pi b^2)}{2(a^2 + r^2)^{3/2}} \right] \frac{di_{reader}}{dt} = -M \frac{di_{reader}}{dt} \ (Eq. 2.6)$$

Where "a" is the radius of the reader coil, "b" is the radius of tag coil, r is the distance between the two coil and M is the mutual inductance between the tag and reader coil.

The above equation shows that the tag coil voltage is largely dependent on the mutual inductance between the two coils. Mutual inductance is a function of tag position and the distance between the coils. The induced voltage in the tag coil decreases with r<sup>-3</sup>.

Therefore, the read range also decreases in the same way.

#### 2.2 V<sub>DD</sub> Generator

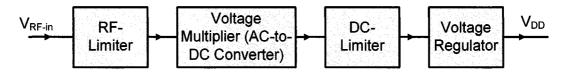

The  $V_{DD}$  generator block diagram is shown in Figure 2.6. The blocks in the  $V_{DD}$  generator are RF-clamp circuit (RF-limiter), voltage multiplier (rectifier), DC-limiter, and regulator.

Figure 2.6. Block diagram of V<sub>DD</sub> generator

## 2.2.1 RF-Limiter

The voltage at the input of the voltage multiplier can change from 350mV to 20V, depending on the vicinity of the reader to tag. To prevent any damage to the chip transistors in high voltage levels, an RF-limiter is used to ensure that under large RF power levels the voltage swing at the chip input is limited to a fixed value. The RF-limiter acts like a bypass system for the extra current during the large input power.

## 2.2.2 Voltage Multiplier

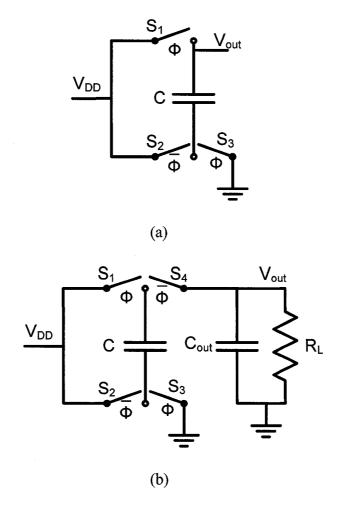

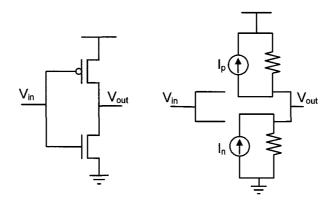

The voltage multiplier converts a part of the incoming RF signal power to DC for power supply for all active circuits on the chip. One of the most popular voltage multipliers are charge pump circuits. Charge pumps are circuits that generate a voltage larger than the supply voltage from which they operate. To see how they work, we consider the simple circuit in Figure 2.7.a that consist a single capacitor and three switches [9].

During clock phase  $\phi$ , switches  $S_1$  and  $S_3$  are closed and capacitor is charged to the supply voltage,  $V_{DD}$ . Next, during the  $\overline{\phi}$  switch  $S_2$  is closed and the bottom plate of the capacitor assumes a potential  $V_{DD}$ , while the capacitor maintains its charge of  $Q=V_{DD}$ . C from the previous phase. This means that based on charge conservation we will have

$$(V_{out} - V_{DD})C = V_{DD}C$$

(Eq.2.7)

or

$$V_{out} = 2V_{DD}$$

(Eq. 2.8)

Thus, in the absence of a DC load, an output voltage has been generated that is twice the supply voltage.

In order to accommodate a load at the output, the circuit would be modified by adding an output capacitance as shown in Figure 2.7.b.

In this case, the ideal output voltage is given by

$$V_{\text{out}} = \frac{C}{C + C_{\text{out}}} 2V_{\text{DD}}$$

(Eq.2.9)

If a load  $R_L$  is presented, then a ripple voltage,  $V_R$ , is generated at the output. The ripple voltage can be reduced by making  $C_{out}$  sufficiently large so that  $V_R$  is negligible compared to  $V_{out}$ . Voltage multiplication greater than twice the supply voltage can be achieved by cascading more than one capacitor in series.

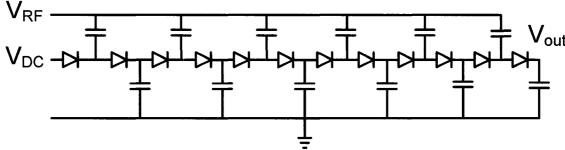

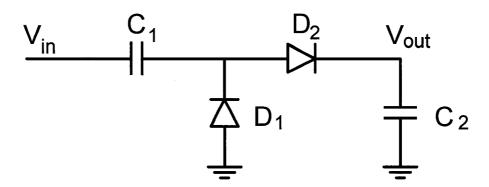

The switches in the Figure 2.7 can be implemented by diodes that characterized by their forward bias voltage V<sub>D</sub>. This multiplier is called Dickson rectifier. Figure 2.8 shows a six-stage Dickson charge pump circuit using for RFID applications. The multiplier operates by pumping charge along the diode chain as the capacitors are successively charged and discharged during each period of the input RF signal.

A single stage charge pump circuit is shown in Figure 2.9. When the input signal of a single stage voltage multiplier is in the negative cycles, the voltage  $V_{c1}$  across capacitor  $C_1$  is charged through  $D_1$  diode to the peak of the input signal. In the positive cycles,  $D_1$

Figure 2.7. Simple circuit of voltage multiplier (a) without loading (b) with loading

Figure 2.8. A 6-stage charge pump voltage multiplier

is OFF and  $D_2$  rectifies the voltage sum of the  $V_{c1}$  and  $V_{in}$  and produces a DC voltage  $(V_1)$  equal to twice the peak of the input signal  $(V_p)$  minus the ON voltage drop  $(V_D)$  across the two diodes. The output voltage provided by the single stage voltage multiplier can be expressed by

$$V_{1-Stage} = 2(V_P - V_D)$$

(Eq. 2.10)

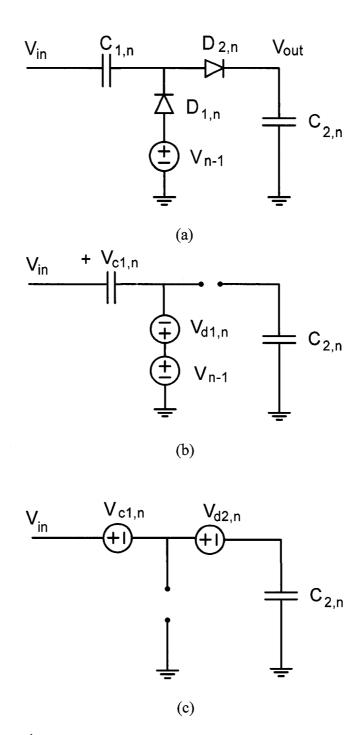

The operations of the n<sup>th</sup> stage of the voltage multiplier in negative and positive cycles of input RF signal are shown in Figure 2.10.

In the negative cycles, the first diode  $(D_{1,n})$  becomes ON and charges the capacitor  $C_{1,n}$  to

$$V_{C1,n} = -(V_p - V_{D_{1,n}} + V_{n-1})$$

(Eq.2.11)

Where  $V_{n\text{--}1}$  is the output voltage from the  $(n\text{--}1)^{th}$  stage.

In the positive cycles, the second diode  $(D_{2,n})$  becomes ON and rectifies the voltage seen from capacitor  $C_{1,n}$  to

$$V_n = V_p - (V_{Cl,n}) - V_{D2,n} = 2(V_p - V_D) + V_{n-l}$$

(Eq. 2.12)

Figure 2.9. A single stage voltage multiplier

Figure 2.10. The n<sup>th</sup> stage of the voltage multiplier (a) general topology (b) In negative cycles of the input voltage (c) In positive cycles of the input voltage

Considering the input of the first stage is only an RF signal and by replacing  $V_{n-1}$  recursively, the following formula for an n-stage voltage multiplier can be extracted

$$V_n = 2n(V_{in} - V_D)$$

(Eq. 2.13)

#### 2.2.3 DC-Limiter

The output voltage of the voltage multiplier depends on the RF input voltage so varies in a wide range. To limit the range of the changes in the output of the charge pump, a DC limiter is used. During the low power input, the limiter does not change the output of the voltage multiplier. In the high RF energy periods, the limiter makes a bypass path for current and limits the output voltage to a certain value. The limiter bounds the rectifier output voltage variation to 1V.

# 2.2.4 Regulator

The regulator circuit comes after the DC limiter. The regulator does two major functions. One is to regulate the front-end output voltage to a preferred value and within a preferred range. The other is to protect the inner circuits from breaking at high RF input power. The output of the voltage regulator will be used as the circuit's  $V_{DD}$  voltage.

#### 2.3 Demodulator

There are different modulation schemes for sending data to an RFID transponder such as ASK, PSK, PWM or OOK. ASK involves the simplest form of RF detection, using a

basic envelope detector, implemented by a diode-capacitor network. An ASK demodulator demodulates information in the form of amplitude changes or "dips." The demodulator is actually an edge detector. PSK is not usually used in an RFID system's forward link because PSK demodulation employs superheterodyne detection, which calls for a local-oscillator (LO), mixer and filter circuits. Such circuits are complex and require large die area. OOK (ON\_OFF\_Keying) is the simplest digital modulation where the amplitude of the carrier corresponds to one of two digital states. Nonzero amplitude represents a digital one while zero amplitude is a digital zero. OOK has the advantage of simplicity and low cost but it looses the power up signal for the whole symbol period. The PWM (Pulse Width Modulation) is an OOK signal with different duty cycles for digital signal "zero" and "one" and cause not loosing the power during the whole "zero" signal so it is more power efficient than the OOK modulation.

In this project, a PWM signal which is modulated with ASK is used for forward link.

### 2.3.1 PWM Signal

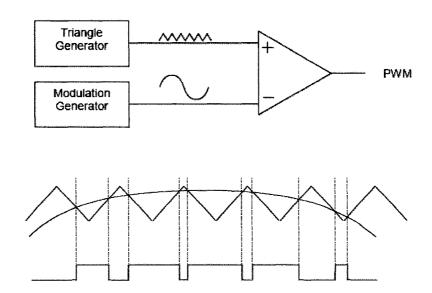

Pulse-width modulation (PWM) of a signal involves the modulation of its duty cycle, to either convey information over a communications channel or control the amount of power sent to a load. Three different types of pulse-width modulation (PWM) are possible. In the first method the center of the pulse may be chosen to be fixed to the center of the time window. In this method both edges of the pulse move to change the width of the pulse. In the second method, the leading edge of the pulse is held tied to the

leading edge of the pulse and the tail edge is modulated for pulse with variations. In the third method the tail edge is fixed and the lead edge is modulated.

The block diagram and waveform of a system that generates PWM signal is shown in Figure 2.11. The system employs a comparator and a sawtooth-wave generator. The output of the comparator is zero except when the message waveform exceeds the sawtooth wave, in which case the output is a positive constant.

Figure 2.11. Block diagram and waveform of PWM generator

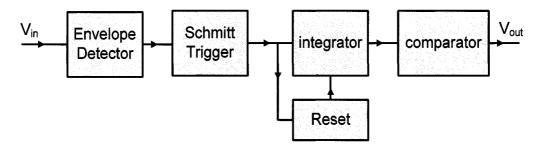

## 2.3.2 Demodulator Block Diagram

Figure 2.12 demonstrates the block diagram of the demodulator section. The transponder uses an envelope detector and a pulse width demodulator for demodulation. The input carrier waveform is passed through a rectifier and an envelope detector to extract the envelope of the signal. To filter out the ripple on this signal, usually a low-pass filter is employed. The current sink after the envelope detector together with the

lowpass filter capacitor determine the minimum width of gaps that can be detected by the circuit. The signal is then fed to a hysteresis comparator to generate the input to the integrator. The integrator integrates the signal to distinguish between the zero and one signals. The signal will be compared with a reference voltage and this procedure determines the data bits.

Two factors must be considered during edge-detection design: the hysteresis level of the comparator, and comparator sensitivity. The RFID reader determines the lowpass filter parameters during the tagging of the data rate, coding, and the envelope mask. The filter bandwidth should be smaller than the signal bandwidth. Specifications for the data envelope are described in the RFID air interface protocol.

Figure 2.12. Block diagram of demodulator section

#### 2.4 Modulator

The modulation in RFID systems is based on backscattering. Backscatter enables the tag to reader communication by varying the impedance presented to the transponder's antenna in order to modulate the reflected power.

The backscatter modulation can be phase or amplitude modulation (PSK or ASK).

These modulation types are different in term of available power to the IC and the backscatter power. In the next section we will show these parameters and the tradeoffs for both modulation schemes.

#### 2.4.1 Power Efficiency and Backscatter Modulated Power

The backscatter modulation is achieved by changing the input impedance between two different states:  $Z_1=R_1+X_1j$  and  $Z_2=R_2+X_2j$ . Two important things that need to be taken into account for choosing the modulation scheme are power efficiency and backscatter modulated power. Power efficiency is shown by the RF power available for DC supply power generation. Backscatter modulation power is the power of signal obtained from the demodulation of the voltage directly applied to the radiation resistance of the antenna [10].

The input power available to the rectifier for DC voltage generation is given by [11]

$$P_{RE,in,1,2} = \frac{1}{2} Re(\hat{v}_{in}^* \hat{i}_{in}) = \frac{1}{2} Re(\frac{\hat{v}_0^2 (R_{1,2} - jX_{1,2})}{|R_{1,2} + R_{ant} + j(X_{1,2} + X_{ant})|^2}) = \frac{\hat{v}_0^2}{8R_{ant}} (1 - \frac{|Z_{1,2} - Z_{ant}^*|}{|Z_{1,2} + Z_{ant}^*|^2}) (Eq. 2.14)$$

Where  $v_{in}$  is the peak voltage at the IC's input,  $i_{in}$  is the peak current flowing between antenna and IC and  $v_0$  is the peak source voltage that would be observed if the antenna where not loaded by the IC.

The available power from the antenna and the reflection coefficient from the antenna have the following equations

$$P_{\text{avail}} = \frac{{v_0}^2}{8R_{\text{aut}}}$$

(Eq.2.15)

$$\Gamma_{1,2} = \frac{Z_{1,2} - Z_{ant}^*}{Z_{1,2} + Z_{ant}^*}$$

(Eq. 2.16)

So by using equations (2.15) and (2.16) in equation (2.14), the input RF power would simplify as

$$P_{RF,in,1,2} = P_{avail} (1 - |\Gamma_{1,2}|^2)$$

(Eq. 2.17)

Because of the need for two different impedances, the input RF power could have different amount and the average input power becomes important. If the IC is in state 1 and 2 for a fraction of  $p_1$  and  $p_2$  of the time, the average input power available for the power supply is [11]

$$P_{RF,in} = p_1 P_{RF,in,1} + p_2 P_{RF,in,2} = P_{avail} [p_1 (1 - |\Gamma_1|^2) + p_2 (1 - |\Gamma_2|^2)]$$

(Eq. 2.18)

To find the modulation backscatter power, we will assume that both states are active an equal amount of time. The modulation backscatter power is found to be [10]

$$P_{bs} = \frac{(V_{bs1} - V_{bs2})^2}{8R_{rad}} = \frac{|i_2 - i_1|^2}{8}R_{rad}$$

(Eq.2.19)

Where  $i_{1,2}$  are the complex amplitude of the current flowing between antenna and IC for two states 1 and 2 and  $R_{rad}$  is the radiation resistance of the antenna.

The current flowing between antenna and IC can be obtained by following equation

$$i_{1,2} = \frac{V_0}{Z_{ant} + Z_{1,2}} = \frac{V_0}{2R_{ant}} (1 - \Gamma_{1,2})$$

(Eq.2.20)

By assuming that the antenna is lossless ( $R_{ant}=R_{rad}$ ) and using equation (2.20), the equation (2.19) can be expressed in term of reflection coefficients [11]

$$P_{bs} = \frac{P_{avail}}{4} \left| \Gamma_1 - \Gamma_2 \right|^2$$

(Eq.2.21)

Equation (2.21) shows the total power of the two sidebands of the backscatter wave, excluding the carrier power.

# 2.4.2 Different Types of Backscatter Modulation

There are two types of backscatter modulation: amplitude and phase shift keying. The first one modulates the signal by changing the real part of the IC impedance. In the PSK the signal would be modulated by changing the imaginary part of the input impedance. The advantages and disadvantages of each modulation scheme will be discussed in this section.

#### 2.4.2.1 ASK

There are two different ASK backscatter modulation. At one of them the power will be matched in one of the two states and in the other state the power reflects totally. The other ASK modulation scheme has an equal amount of mismatch in both states.

When we have total reflection in one of the states, the input is shorted or opened so the input impedance is zero or infinity ( $Z_1$ =0 or  $Z_1$ = $\infty$ ). By using equation (2.20),  $|\Gamma_1|$ =1. As the antenna is matched in the other state, the reflection coefficient of state 2 is zero ( $|\Gamma_2|$ =0).

By equations (2.18) and (2.21) and also assuming equal amount of activation time for both states, the RF input power and backscatter power are [11]

$$P_{RF,in,ask,on off} = p_1 P_{avail}$$

(Eq. 2.22)

And

$$P_{bs,ask,on\_off} = \frac{P_{avail}}{4}$$

(Eq.2.23)

From the above equations, it is obvious that 50% of the available power is available for rectification, 25% is used as backscattered modulated power and the remaining 25% is wasted.

In the ASK with the same amount of power mismatch, the reflection coefficient in both states are real and given by

$$\Gamma_{1,2} = \frac{R_{1,2} - R_{ant}}{R_{1,2} + R_{ant}}$$

(Eq. 2.24)

To have equal mismatch in both states, it is sufficient to choose  $R_2=R^2_{ant}/R_1$  [10]. In this case  $\Gamma_1=-\Gamma_2=m$ , where m is the modulation index. In such a condition, in both states, the same power is transferred from the antenna to the load. This situation can be easily achieved by switching a resistor in series or parallel to the IC's input.

By equation (2.17) the input power in states 1 and 2 are given by

$$P_{RF,in,ask,1} = P_{RF,in,ask,2} = (1 - m^2)P_{avail}$$

(Eq. 2.25)

One of the main disadvantages of this kind of modulation compared to the PSK is the power lost in the series or parallel transistor. Here we assume that  $R_2 > R_1$  and we use a parallel resistance for modulation ( $R_1 = R_2 \parallel R_{MOD}$ ). In this case, when  $R_{MOD}$  is not connected, the antenna sees a resistance  $R_2$  and all the power  $P_{RF,in,ask,2}$  used for rectification. But when the resistor  $R_{MOD}$  is connected, the antenna sees resistor  $R_1$  and

only a fraction of the power transferred from the antenna to the load can be used for rectification. So the input power that can be used for DC supply generation can be obtained as [10]

$$P_{\text{rec},2} = P_{\text{avail}} \frac{4R_{\text{ant}}R_2}{(R_2 + R_{\text{ant}})^2}$$

(Eq. 2.26)

$$P_{\text{rec},1} = P_{\text{avail}} \frac{4R_{\text{ant}}R_1}{(R_1 + R_{\text{ant}})^2} \frac{R_{\text{MOD}}}{R_{\text{MOD}} + R_2}$$

(Eq.2.27)

The backscatter power for the state 1 and 2 and also for both sidebands are given by [10]

$$P_{bs2} = P_{avail} \frac{R_{ant}^2}{(R_{ant} + R_2)^2}$$

(Eq. 2.28)

$$P_{bs1} = (\frac{R_2}{R_{ant}})^2 P_{sb2}$$

(Eq.2.29)

And

$$P_{bs} = m^2 P_{avail} = P_{avail} \left( \frac{R_2 - R_{ant}}{R_2 + R_{ant}} \right)^2$$

(Eq. 2.30)

#### 2.4.2.2 PSK:

In the PSK modulation, the real part of the input impedance should be equal to the real part of the antenna impedance and the imaginary part will be modulated. In this case, the reflection coefficient becomes purely imaginary. By choosing two states symmetric by respect to zero the reflection coefficients in state 1 and 2 become equal in amount and different in phase ( $\Gamma_{1,2}=\pm jm$ ).

In this case, from (2.17) and (2.21), the backscattered power and RF input power are found to be

$$P_{bs,psk} = m^2 P_{avail} = P_{avail} \frac{X^2}{4R_{ant}^2 + X^2}$$

(Eq.2.31)

And

$$P_{RF,in,psk,1} = P_{RF,in,psk,2} = (1 - m^2)P_{avail} = P_{avail} \frac{4R^2_{ant}}{4R^2_{ant} + X^2}$$

(Eq. 2.32)

Where X is the imaginary part of the IC's impedance.

Here we see that all power in PSK is used either for rectification or for backscatter.

Also the input power remains constant in both cases.

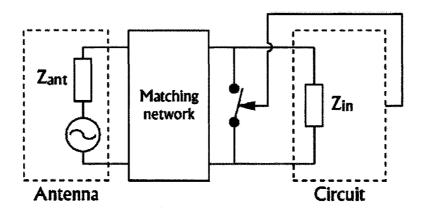

# 2.4.3 Matching Network

Matching network is used to deliver maximum power to the  $V_{DD}$  generator circuit. If a circuit is not perfectly matched, less power will be transferred. If a circuit is perfectly matched, maximum possible power will be transferred from the antenna to the load.

If we assume that an appropriate series reactance has been interposed between a source of impedance  $Z_S$  and a load of impedance  $Z_L$  to provide zero total series reactance, we can define a reflection factor from the load back to the source as shown in equation (2.16).

It has been shown that with a perfect matching between the antenna and the circuit, there will be a maximum power transfer. Also, a prefect match will result in 0 voltage reflection factor.

However, if a wider bandwidth compared with the bandwidth of a matched circuit is required, the antenna resistance can be increased to obtain a wider bandwidth. By doing this, there will be (of course) some reduction in the amount of power transferred, but

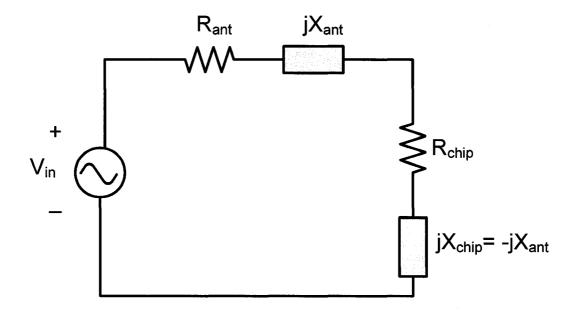

usually the amount is small and is in an acceptable level. Figure 2.13 is an equivalent circuit for the combined RFID antenna and the RFID circuit:

Figure 2.13. The equivalent circuit for the antenna and circuit

If  $R_{ant} = R_{chip}$ , the circuit is considered matched and has a voltage reflection factor of 0. In other words, 100% of the maximum possible power will be transferred to the load. The quality factor will be  $\frac{1}{2}$  of  $Q_{chip}$ , where  $Q_{chip}$  is the quality factor for just the chip.

If  $R_{ant}$  is increased to  $2R_{chip}$ , the voltage reflection factor will be -1/3 and 1/9 of the power will reflected and the efficiency will be around 89%. The quality factor will be 1/3 of  $Q_{chip}$ .

This shows that by increasing the value of  $R_{\text{ant}}$ , the quality factor will reduce and hence the bandwidth will increase. The trade-off is that the efficiency will decrease but may still be within the acceptable range.

#### 2.5 Clock and POR Generator

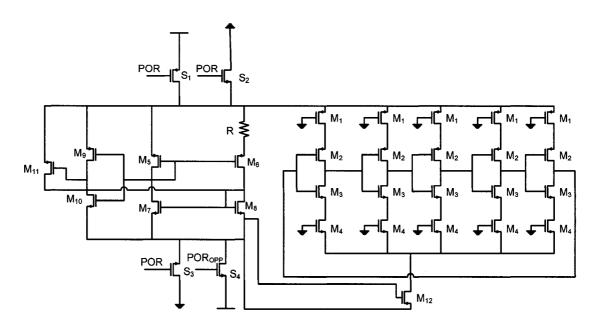

#### 2.5.1 Clock Generator

The base-band digital section of the chip needs a system clock to be able to run the state machine or to decode the data. All RFID systems require a clock generator. Some use a modulation on their carrier signal for the clock signal transmission and others generate the clock signal on chip [12].

For HF system, it is generally relatively easier to detect and extract the required clock signal from the carrier wave using dividers. The reason for which this is possible is that the data rate is relatively close to the carrier frequency and this allows the extraction of clock.

In the UHF systems, the direct extracting approach can not be utilized. This is because the carrier signal is operating at a high frequency and the power consumption of the chip will increase significantly once any part of the circuit starts to work with this carrier [12]. In this case, we have to implement an on chip oscillator to generate the system clock in UHF tag chips. The oscillator should be very low power and less sensitive to  $V_{DD}$ . The other option would be to modulate the carrier signal with an AM or FM signal that transfers the clock frequency.

#### 2.5.2 Power on Reset

The power on reset circuit has two main functions that are essential for the correct operation of the chip. One is generating the reset signal for the digital section of the chip

and the other function is to disconnect the chip when the required power falls below a critical level.

The POR circuit measures the power supply level and then compares this level to a certain required threshold. If the power supply voltage exceeds the required threshold, the POR circuit generates the required command signals so that the operation of the chip would begin. The POR circuit has a delay element that generates a timing difference between the time that the supply is no longer adequate and that where the reset disable signal is set [12].

## 2.6 Digital Section

The baseband section of the RFID transponder can have different structures based on the RFID applications. The three most important parts in RFID digital section are sequencer and data encoder, anti-collision circuit, and EEPROM.

The sequencer and data encoder provide signals to address the memory array and to encode the output data, respectively.

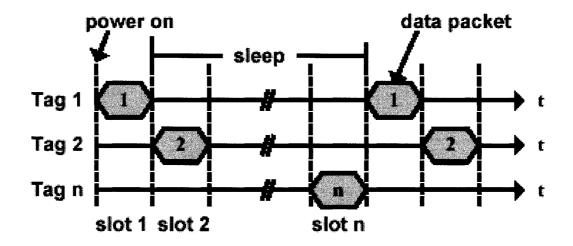

In order to read multiple transponders simultaneously, the anti-collision feature is applied. The anti-collision scheme is shown in Figure 2.14. The transponder starts transmission of the data packet after receiving its power in a different time slot selected randomly by each ID itself, and then goes into sleep mode after sending a data packet [13].

Figure 2.14. Anti-collision scheme

The EEPROM is used to save the tag ID that may later be used for the identification purposes of the tag in many applications. As an example in consumer product bar code applications, the lot number, product number, expiration date and etc could be saved on the tag.

#### **CHAPTER 3. RFID FRONT-END DESIGN**

In this chapter the RFID front-end schematic and the simulation results are described. Section 3.1 presents the V<sub>DD</sub> generator part. Section 3.2 discusses the demodulator block. Section 3.3 leads to the detail description of the clock generator. The power on reset circuit is described in section 3.4. Finally, section 3.5 discusses the modulator and matching network.

### 3.1 V<sub>DD</sub> Generator

The block diagram of  $V_{DD}$  generator section was shown in Figure 2.6. As discussed previously, the passive RFID tags derive their power supply from the incoming power instead of a battery. At the first stage of the  $V_{DD}$  generator, a RF-clamp circuit limits the amplitude of the input RF voltage to prevent any damage to the reset of the circuit caused by the high input power (breaking down of the transistors). Then a voltage multiplier produces a DC voltage based on the amplitude of the input RF voltage. Due to the huge variation of the rectified voltage (by as much as ten volts), a voltage limiter is employed at the output of the rectifier. The limiter at the rectifier output clamps the rectifier voltage to a narrower range. A fine regulator, then, regulates the supply voltage to a value of one volt.

The operation of different blocks of  $V_{DD}$  generator and their simulation results are described in this section.

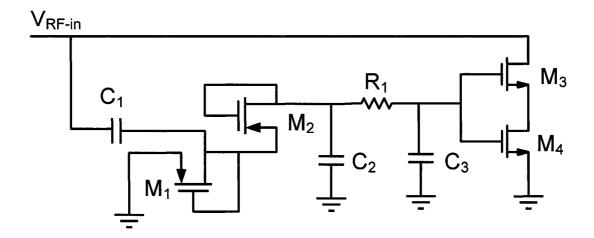

## 3.1.1 RF Clamp Circuit

The input voltage of the RFID system can vary from several millivolts to tens of volts based on the distance between the reader and the transponder. In CMOS technology, the breakdown voltage of the MOS transistors is approximately 1.5-2 volts with the 0.13µm technology. The excessive voltage on the RF input of the tag could easily damage the chip structure. On the other hand, when the input voltage is large, the output voltage of the rectifier circuit will have a large variation (perhaps a decade) and the regulator design would be more challenging with the voltage overhead and the power consumption budget in hand. This shows the necessity of having an RF clamping circuit that will limit the RF input signal to approximately 1 volt. Of course the voltage regulator can then stabilize this voltage to a desired value once the variation is limited.

The schematic of proposed RF clamp circuit is shown in Figure 3.1. The designed voltage clamp uses feedback to sense the input voltage at the RF port and to close the loop in such a way that the input voltage could not exceed one volt. The design consists of a one stage voltage multiplier and two series transistors at the input RF to clamp the voltage. The gate of the clamp transistors are controlled by the output of the one stage rectifier followed by a low pass filter that cleans the high frequency variations on the signal. When the input signal experiences a large value of swing (say in orders of volts) the one stage rectifier and filter produces a large voltage and in turn this will turn on the clamp transistors. The clamp transistors will draw a large current from the input based on their gate voltage and this will result in the limitation of voltage. The sizing of the transistors and the rectifier design is such that the input is clamped to approximately one

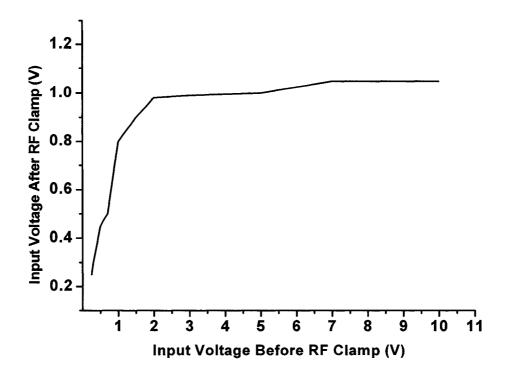

volt. On the other hand the clamp circuit should be designed so that in the case of small input voltages the performance of the rectifier circuit is not affected. This means a good turn off of the clamp devices when the input has not exceeded the set level. The voltage after using a clamped circuit as a function of the amplitude of the input signal is shown in Figure 3.2.

Figure 3.1. RF clamp circuit

Unlike any other parts of the circuit, the transistors in the clamp section should be able to withstand currents in the order of tens of milliamps. This requires careful layout and the use of large transistors so that the spike DC current does not cause damage to the transistor or metal layers. Also, having the clamp transistors in series helps improving the break down voltage limit of the devices. The component values of the RF clamp circuit are presented in Table 3.1.

Figure 3.2. Input voltage after RF clamp circuit

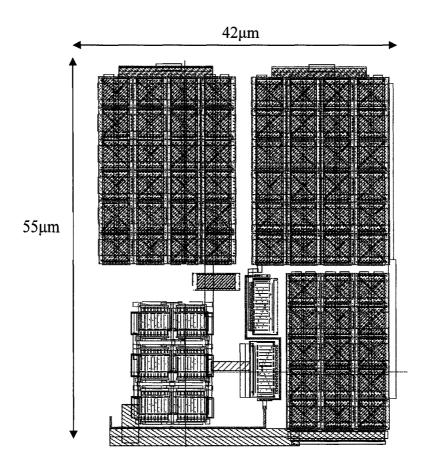

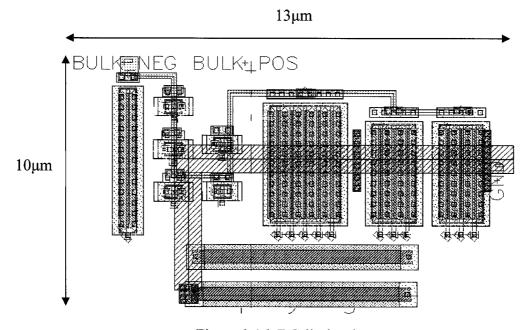

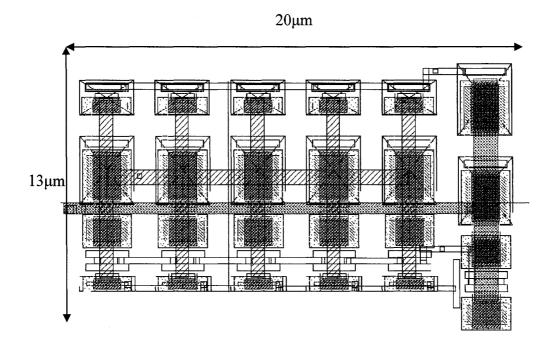

A final plot of the RF-limiter layout is shown in Figure 3.3. The large block at the right of the layout is the one-stage voltage multiplier. The capacitor at the top-left side is the lowpass filter capacitor and the transistors at the bottom-left side are the current bypass transistors.

# 3.1.2 Voltage Multiplier (Rectifier)

The charge pump circuit of an RFID system, also called a voltage multiplier, converts the received input signal to a stable DC voltage. In the following sections, the design issues of a charge pump circuit and the proposed architecture is described.

Table 3.1. The component values of the RF clamp circuit

| M <sub>1</sub> -M <sub>2</sub> | PMOSLVT, 30μm/.13μm,<br>No. of Fingers=15 |

|--------------------------------|-------------------------------------------|

| M <sub>3</sub> -M <sub>4</sub> | NMOSHVT, 20μm/.13μm,<br>No. of Fingers=1  |

| C <sub>1</sub>                 | 1pF                                       |

| C <sub>2</sub> -C <sub>3</sub> | 1.5pF                                     |

| R <sub>1</sub>                 | 1ΚΩ                                       |

Figure 3.3. RF-limiter layout

### 3.1.2.1 Design Issues

One of the most important factors in design of RF to DC converters in RFID systems is the minimum required DC voltage to ensure proper operation of the digital and analog circuits. Given the range specifications and also the FCC power level requirements in the 2.4GHz band, the required DC voltage level determines the number of stages in the charge pump circuit. Using double polarity supply voltage circuits ( $\pm V_{dd}/2$ ) instead of single polarity ( $V_{dd}$ ) decreases the required input signal level by half. The well known equation expressing the voltage level ( $V_{rf}$ ) of an RF signal at antenna is given by

$$V_{rf} = \sqrt{8P_r R_{ant}}$$

(Eq. 3.1)

Where  $P_r$  is the received power at the antenna and  $R_{\text{ant}}$  is the equivalent antenna impedance.

Using double polarity for supply voltages decreases the required number of stages to reach  $V_{dd}/2$  and this improves the overall efficiency of the charge pump circuit. However, the disadvantage would be increasing the area because two charge pumps are required for the positive and negative supply circuits.

The power efficiency of charge pump circuits describes how much power is lost during the RF to DC conversion process. This efficiency depends on the number of stages, the performance of the diodes and also the input power of the multiplier. It is interesting to note that a decrease in the input power level of the charge pump circuit, decreases the efficiency and significantly lowers the output voltage. For diode based charge pumps, the efficiency could be described by [14]

$$\eta = \frac{V_{dd} I_{laod}}{2nI_{s} V_{p} B_{1} (\frac{V_{p}}{V_{T}}) exp(\frac{-V_{dd}}{2nV_{T}})}$$

(Eq. 3.2)

Where  $V_{dd}$  is the generated output DC voltage,  $I_{laod}$  is the output DC current,  $I_s$  is the saturation current,  $V_p$  is the peak of the input signal,  $V_T$  is the thermal voltage, n is the number of stages and  $B_1(x)$  is the first order modified Bessel function.

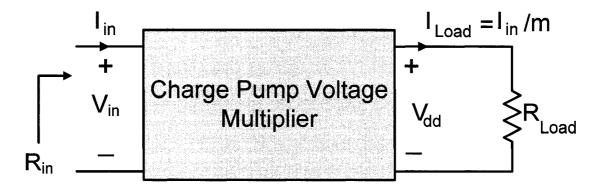

Designing a voltage multiplier to operate from low RF power levels, as is the case here, leaves a very limited choice of variables considering the constraints. The ratio of the output DC voltage to the input AC voltage determines the impedance transformation of the charge pump which is also affected by the loss factor of the circuit. The input resistance ( $R_{in}$ ) of the charge pump voltage multiplier, shown in Figure 3.4, can be described by

$$R_{in} = \frac{V_{in}}{I_{in}} = \frac{R_{load}}{n^2_{eff}} \eta$$

(Eq. 3.3)

and

$$\eta = \frac{V_{dd}I_{load}}{V_{in}I_{in}} = \frac{n_{eff}}{m}$$

(Eq. 3.4)

Where  $n_{eff}$  is the effective voltage gain of the multiplier, m is the output to input current ratio and  $R_{load}$  is the load resistance at the output of the voltage multiplier. The value of  $R_{load}$  can be obtained by the power consumption of the baseband circuits. The input impedance ( $R_{in}$ ) of the voltage multiplier can be calculated using (3.3) and (3.4) when  $R_{load}$  and the current and voltage ratios are known. For most cases,  $R_{load}$  and  $R_{ant}$

are not equal which mandates using a matching network and in turn, alters the voltage at the input of the voltage multiplier.

Another factor in designing the charge pump is the time constant associated with the discharge of the capacitors. This time constant must be sufficiently larger than the signal period to ensure the change in the supply voltage caused by transistors activity is minimal.

Figure 3.4. The input and output modeling of the charge pump voltage multiplier

### 3.1.2.2 Proposed Rectifier Circuit

In conventional charge pump circuits, RF signals of the different stages are equal to the input RF signal (taking the matching network effect into account). For the case when the RF signal applied to the last stage of the voltage multiplier is k times larger than the RF signal applied to other stages, equation (2.13) can be rewritten as

$$V_n = 2[(n+k-1)V_p - nV_D]$$

(Eq. 3.5)

As seen from (3.5), increasing the input signal  $V_P$  at the last stage by k factor will increase the output voltage  $V_n$ .

The above analysis shows that the increase in the amplitude of the RF signal at the last stage of the charge pump has a tremendous effect on the DC voltage level of the output. This suggests that using a highly efficient RF amplification at the n<sup>th</sup> stage could be very beneficial to achieve higher DC voltage at the output of the voltage multiplier. Using an amplifier in the n<sup>th</sup> stage to achieve this objective will introduce a considerable loading to the charge pump circuit. Furthermore, the gain of a tuned amplifier in a low power RFID front-end is usually too low in the subthreshold region to introduce a noticeable voltage difference at the output of the voltage multiplier.

A novel technique to increase the RF signal level is to use passive tuned elements at the input of the voltage multiplier. This technique will introduce no extra loading on the multiplier stages and also does not need any biasing current. The voltage  $(V_c)$  across the capacitor C of a simple series RLC circuit is given by

$$V_{C} = \frac{I}{i\omega C} = \frac{V_{in}}{R + i\omega L + (i\omega C)^{-1}} \cdot \frac{1}{i\omega C}$$

(Eq. 3.6)

At the resonance frequency, the impedance of the RLC circuit becomes equal to the resistance R and the voltage across the capacitor becomes

$$V_{\rm C} = jV_{\rm in}Q \tag{Eq. 3.7}$$

Where Q is the quality factor of the series RLC circuit.

This analysis shows that if an RC circuit is connected to a source, the RF signal across the capacitor can be boosted by a factor of Q if a series inductor is placed between the source and the load. This will help to increase the output voltage of a charge pump since the load can be effectively modeled by an RC circuit.

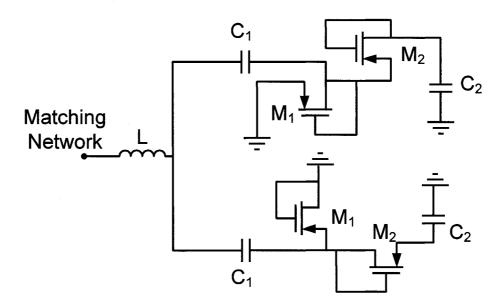

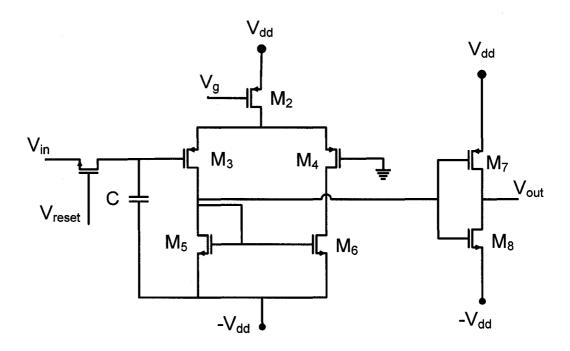

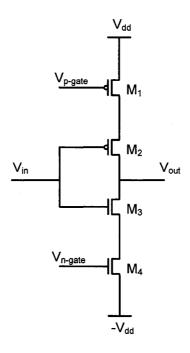

The schematic of the first stage of the charge pump circuit by replacing the diodes with MOS transistors and also using inductive elements to boost the voltage is shown in Figure 3.5.

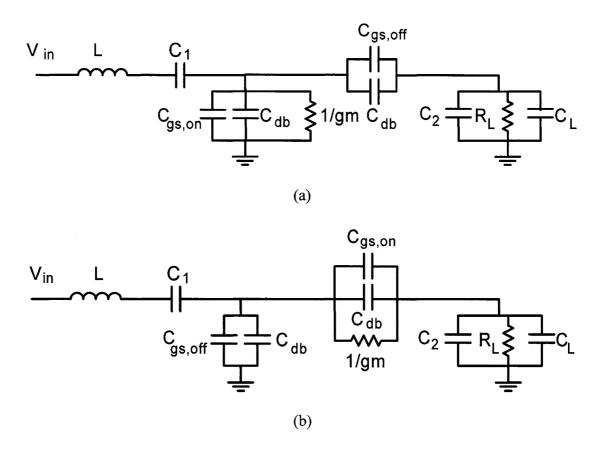

The AC small signal models of a single stage multiplier in the two positive and negative signal cycles are shown in Figure 3.6. Using parallel to series transformation, as shown in Appendix, the input capacitance and series resistance of the circuit can be extracted. The addition of an inductor to the charge pump circuit with respect to the R and C values derived in Appendix, improves the gain of the voltage multiplier. The

Figure 3.5. Schematic of the first stage of the charge pump with inductor

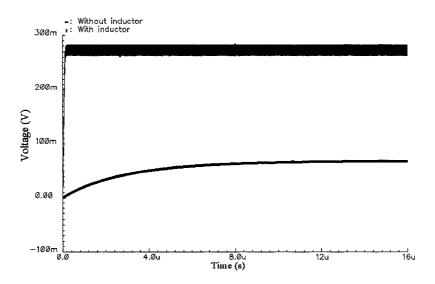

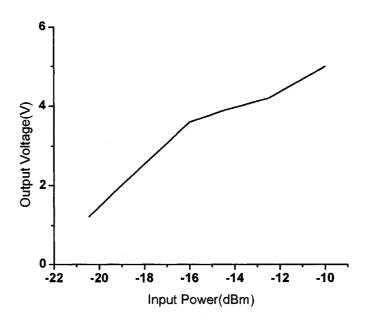

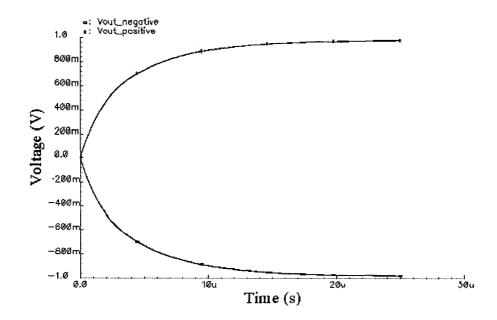

simulation result of single stage voltage multiplier with the input power of -19.5dBm both with and without the inductor is shown in Figure 3.7. As can be seen in this figure, the DC output voltage is larger by a factor of 4.2 when the inductor is used.

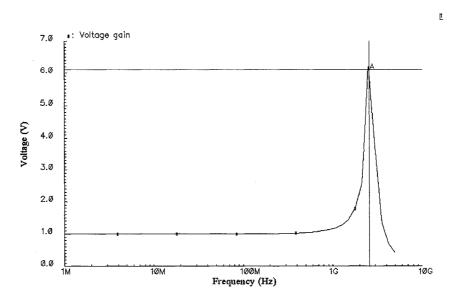

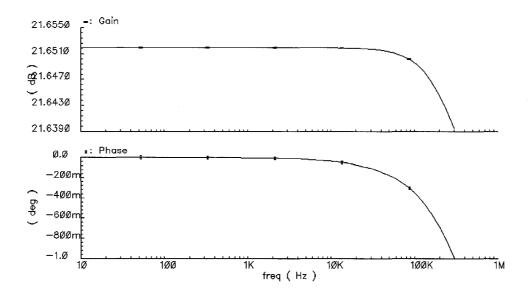

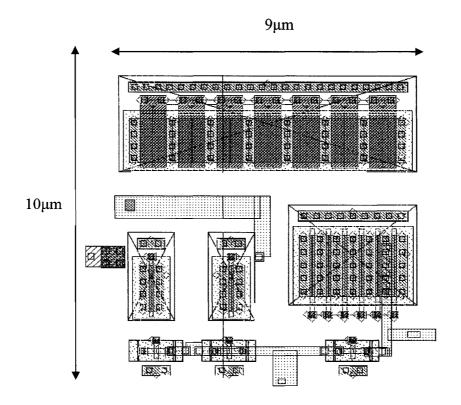

In the same manner the input capacitance and resistance of a multi-stage charge pump circuit could be derived. These values are used to derive the size of the inductance used for the passive multiplication at 2.4 GHz which is 2.1nH for the 6-stage charge pump used in this work. The gain at input of the charge pump circuit after the addition of the inductors is shown in Figure 3.8.

Figure 3.6. Equivalent circuit of a single stage voltage multiplier (a) Negative cycles of the input voltage (b) Positive cycles of the input voltage

Figure 3.7. Output of the 1-stage voltage multiplier with and without inductor

Figure 3.8. Voltage gain after inductor

In the proposed topology, the series inductor also helps in bringing the input impedance level closer to the  $50\Omega$  of the antenna. Generally one of the main issues with a typical charge pump circuit in an RFID application is with the input matching. The real

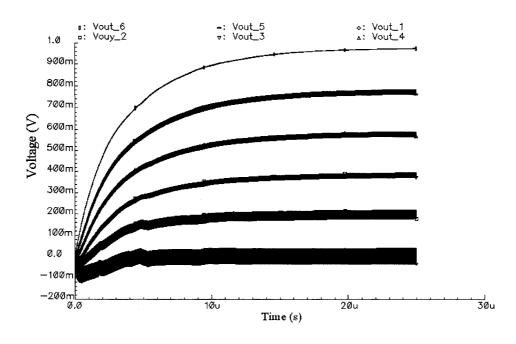

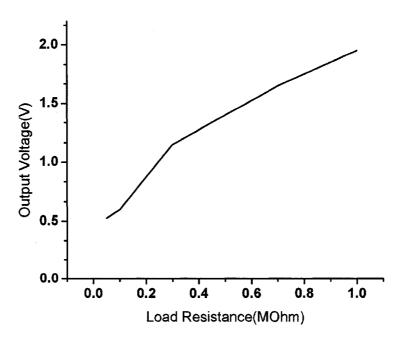

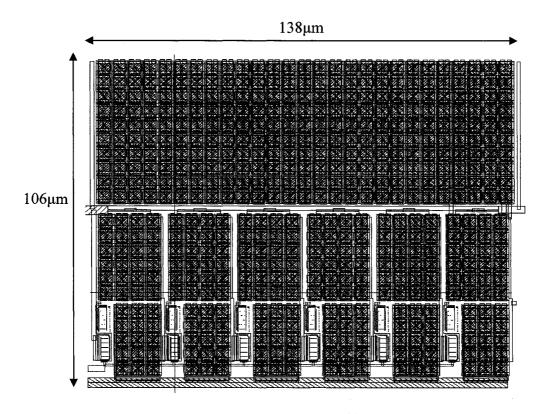

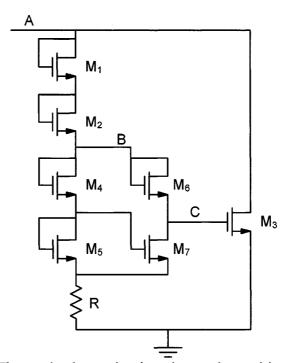

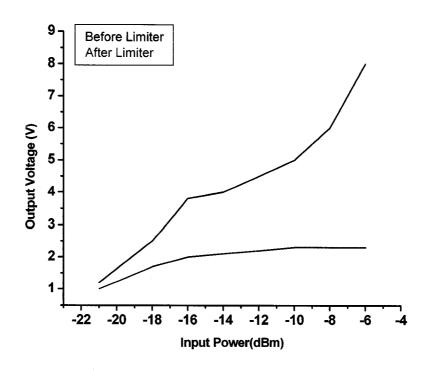

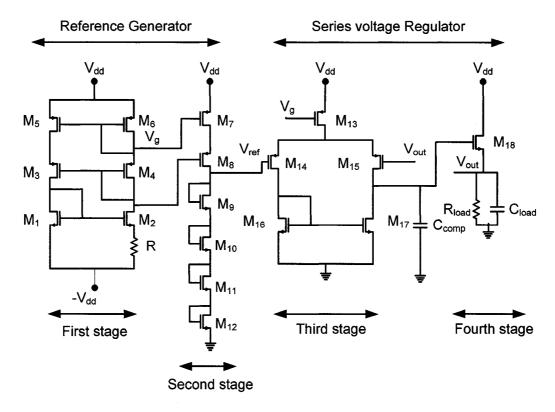

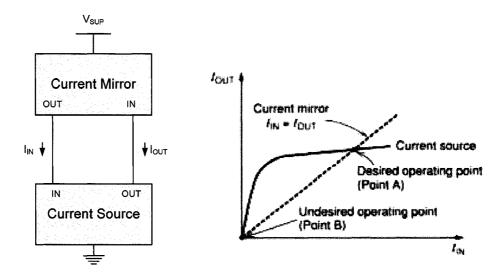

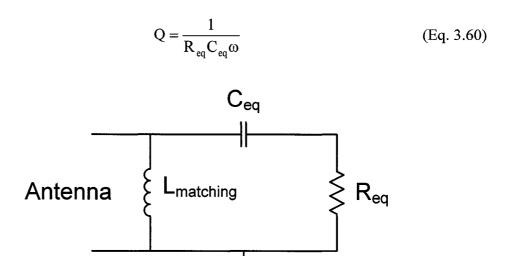

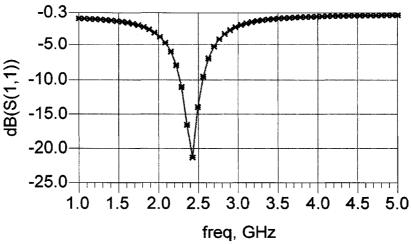

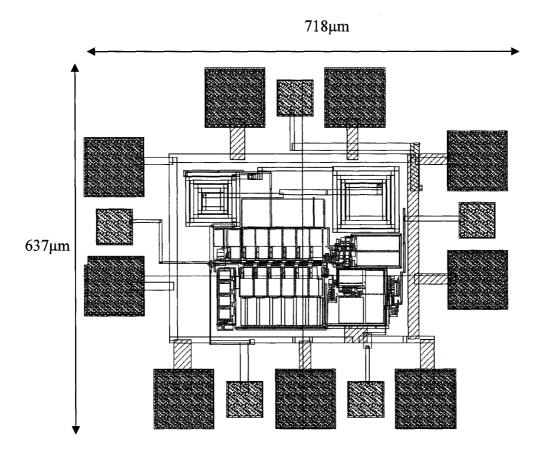

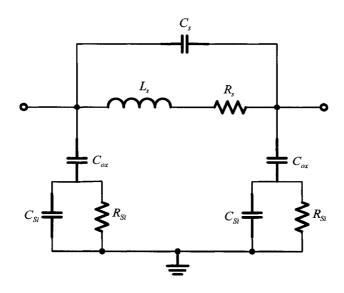

part of the input impedance is low at the source side and needs to be increased with a matching network. In this topology, the two effects of voltage multiplication and impedance transformation are achieved at the same time because of the embedded LC matching network.