### San Jose State University SJSU ScholarWorks

Master's Theses

Master's Theses and Graduate Research

1991

## Charge injection cancellation in analog-to-digital converters

Michael K. Mayes San Jose State University

Follow this and additional works at: https://scholarworks.sjsu.edu/etd theses

#### Recommended Citation

Mayes, Michael K., "Charge injection cancellation in analog-to-digital converters" (1991). *Master's Theses*. 147. DOI: https://doi.org/10.31979/etd.cc7n-pjb9 https://scholarworks.sjsu.edu/etd\_theses/147

This Thesis is brought to you for free and open access by the Master's Theses and Graduate Research at SJSU ScholarWorks. It has been accepted for inclusion in Master's Theses by an authorized administrator of SJSU ScholarWorks. For more information, please contact scholarworks@sjsu.edu.

#### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

|  | , |  |

|--|---|--|

|  |   |  |

#### Order Number 1344293

#### Charge injection cancellation in analog-to-digital converters

Mayes, Michael Keith, M.S. San Jose State University, 1991

# Charge Injection Cancellation in Analog-to-Digital Converters

A Thesis

Presented to

The Department of Electrical Engineering

San Jose State University

In Partial Fulfillment

of the Requirements for the Degree

Master of Science

By Michael K. Mayes May, 1991

#### APPROVED FOR THE DEPARTMENT OF

**ELECTRICAL ENGINEERING**

Dr. Ray Chen

Dr. Art Davis

Dr. Rangaiya Rao

M. Low Lewandowski

#### Abstract

#### Charge Injection Cancellation in Analog to Digital Converters

#### by Michael K. Mayes

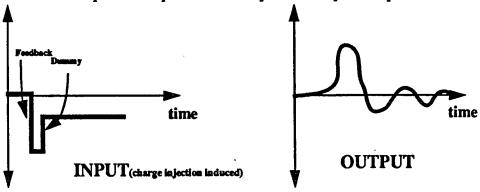

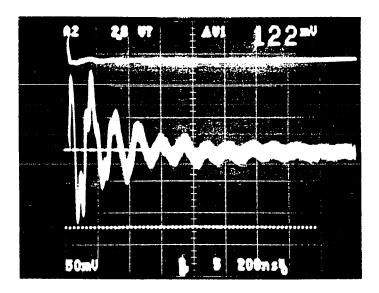

Charge injection cancellation techniques using inverter delays to stagger the auto zero signals of multistage comparators exhibit varied offsets over supply, process, and temperature. Typically, these variations result from insufficient delay times between auto zero signals. By replacing the inverter delays with a programmable delay circuit, a better understanding of delay vs. offset is achieved. Further studies include the effect of forced voltage swing auto zero signals for reduction of offset sensitivity with respect to the supply voltage. Single ended and differential type comparators were designed using these techniques for charge injection cancellation. A working prototype was fabricated and tested for effectiveness.

The results find the offset of a comparator is a function of the delay time between auto zero signals and the output transient response of individual amplifier stages making up the comparator. The amplifier transient response is a function of charge injection induced step inputs. Further studies show charge injection errors are dominated by MOS mismatched channel charge in circuits using dummy device compensation.

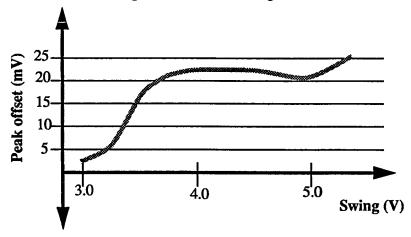

An optimum delay between staggering auto zero signals is achieved by extending the delay beyond the worst case settling time of the amplifier. Constant voltage swings across MOS switches do not eliminate charge injection sensitivity to supply voltage due the effective threshold shift of the switches. However, as the swing is reduced, the transient response settles sooner due to reduced peak output voltages.

#### TABLE OF CONTENTS

| Statement of Problem                                              | 1         |

|-------------------------------------------------------------------|-----------|

| Staggered Auto Zeroes                                             | 2         |

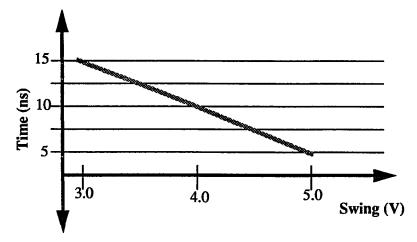

| Forced Voltage Swing of Auto Zero Signals                         | 5         |

| Background                                                        | 7         |

| Charge Injection                                                  | 7         |

| Analog-to-Digital Converter Basics                                | 13        |

| Comparator building block in Analog-to-Digital Converters         | 15        |

| Single Ended Comparators                                          | 17        |

| Charge injection in a Single Ended Comparator                     | 19        |

| Differential Comparators                                          | 22        |

| Characterization of Analog-to-Digital Converters                  | 25        |

| Linearity Plot                                                    | 25        |

| Power Supply Rejection Ratio                                      | 29        |

| Analog-to-Digital Converter Architectures                         | 31        |

| Successive Approximation Analog-to-Digital Converters             | 31        |

| Charge Injection in Successive Approximation Converters           | 35        |

| Flash Analog-to-Digital Converters.                               | 36        |

| Charge injection in Flash Analog-to-Digital Converters            | 38        |

| Charge Injection Cancellation Techniques                          | 40        |

| Dummy Device Cancellation                                         | 40        |

| Staggered auto zero signals                                       | 42        |

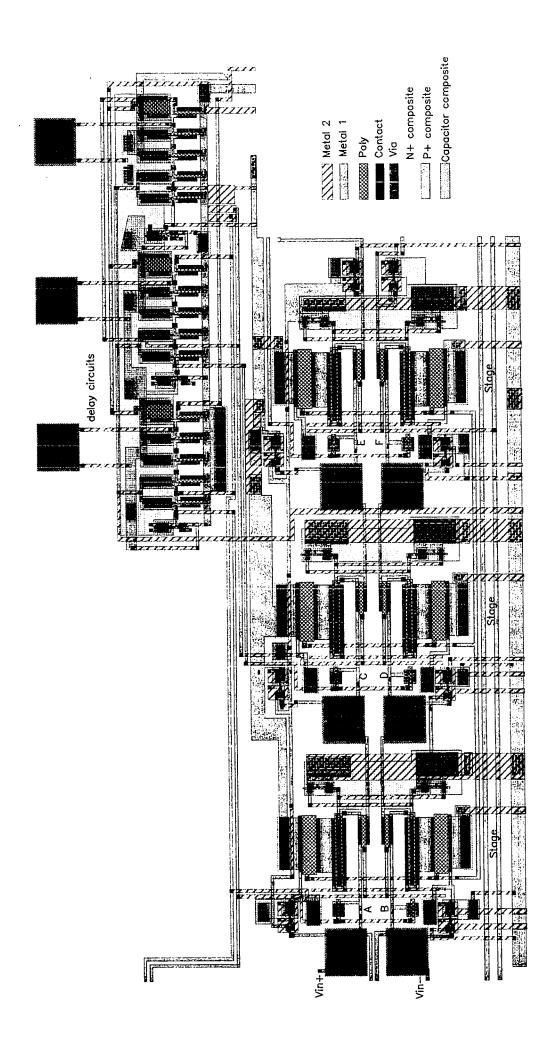

| Programmable Delay Staggered Auto Zero Signals                    | 44        |

| Supply Independent Swing                                          | 45        |

| Methodology                                                       | 46        |

| process                                                           | 46        |

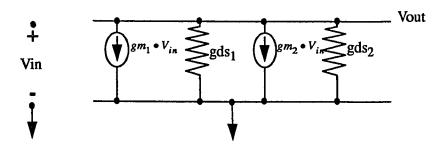

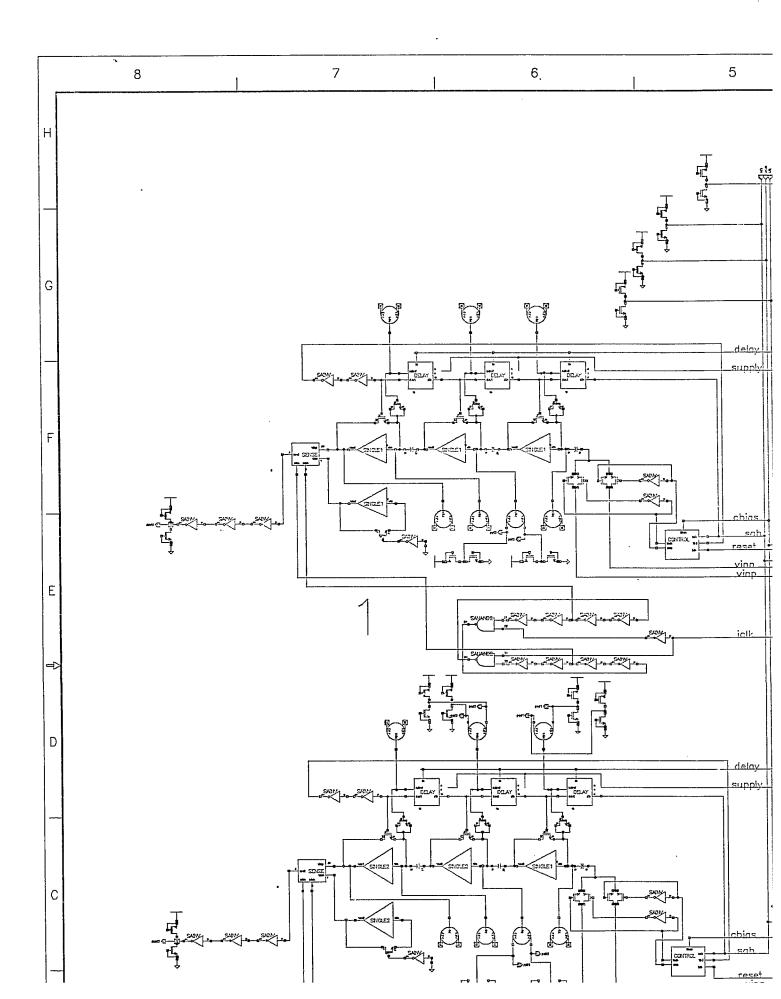

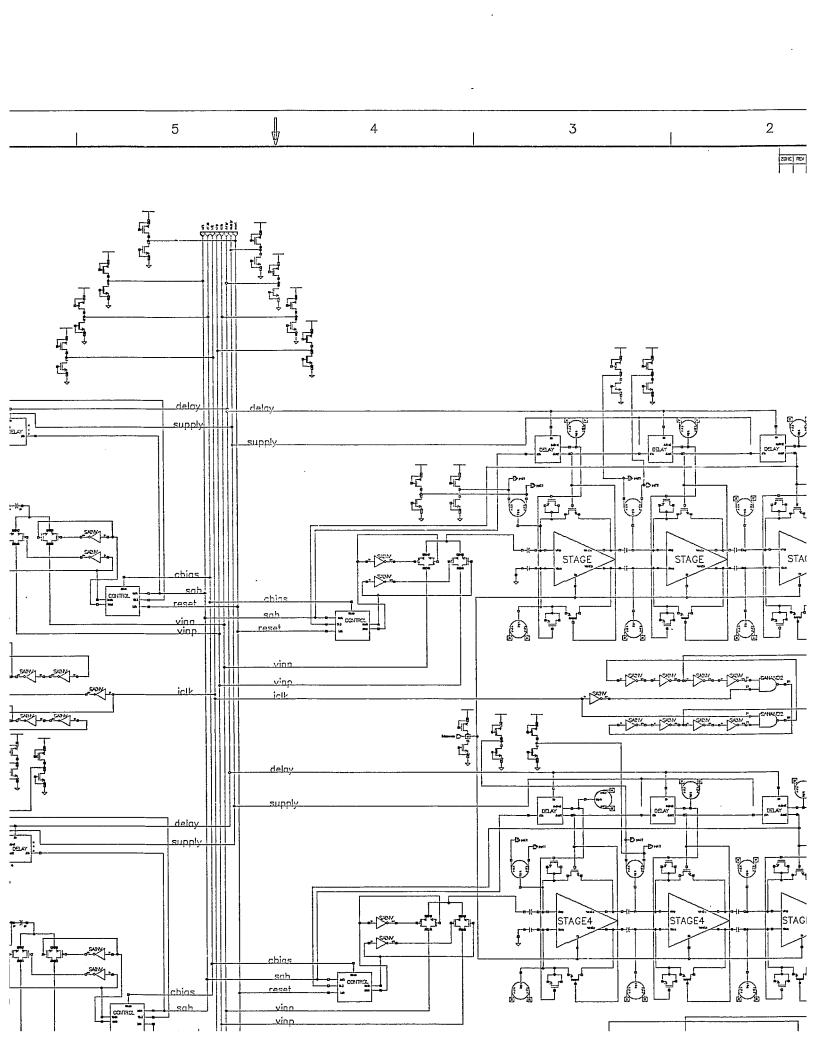

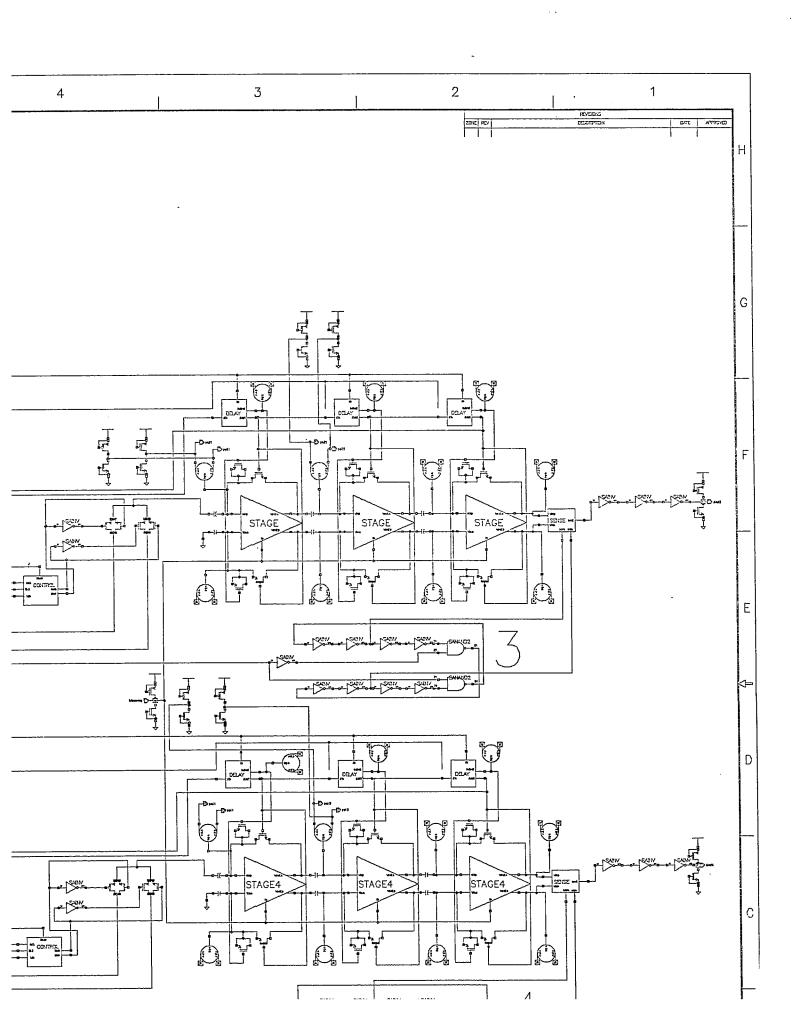

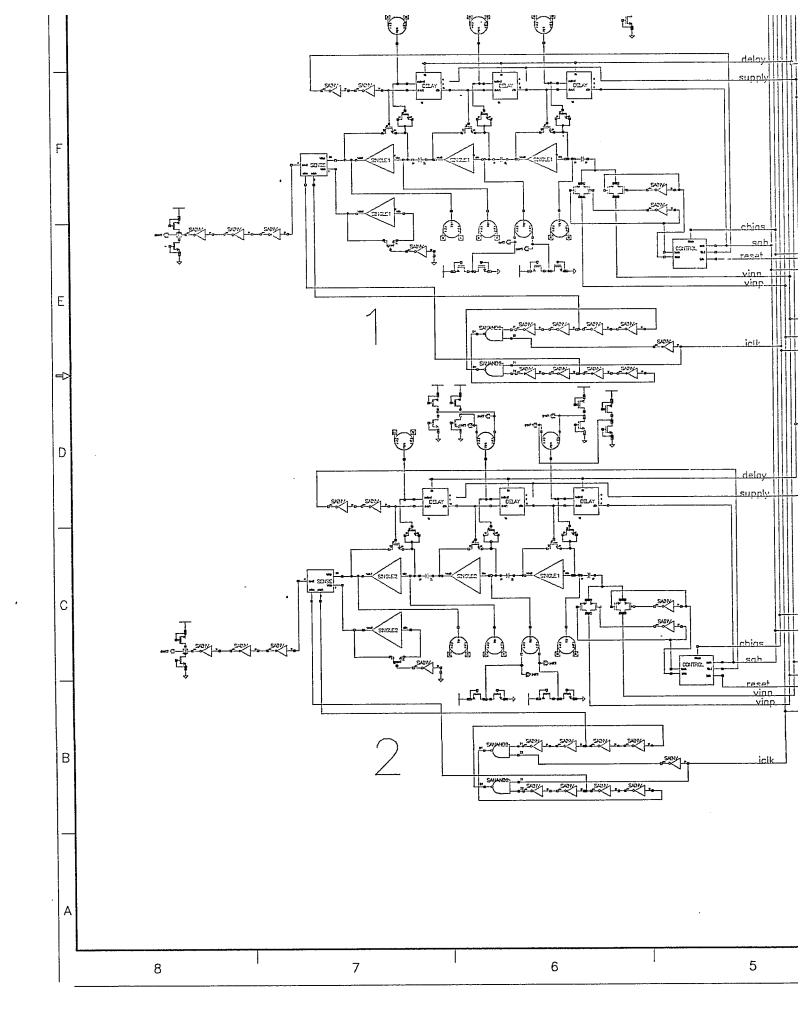

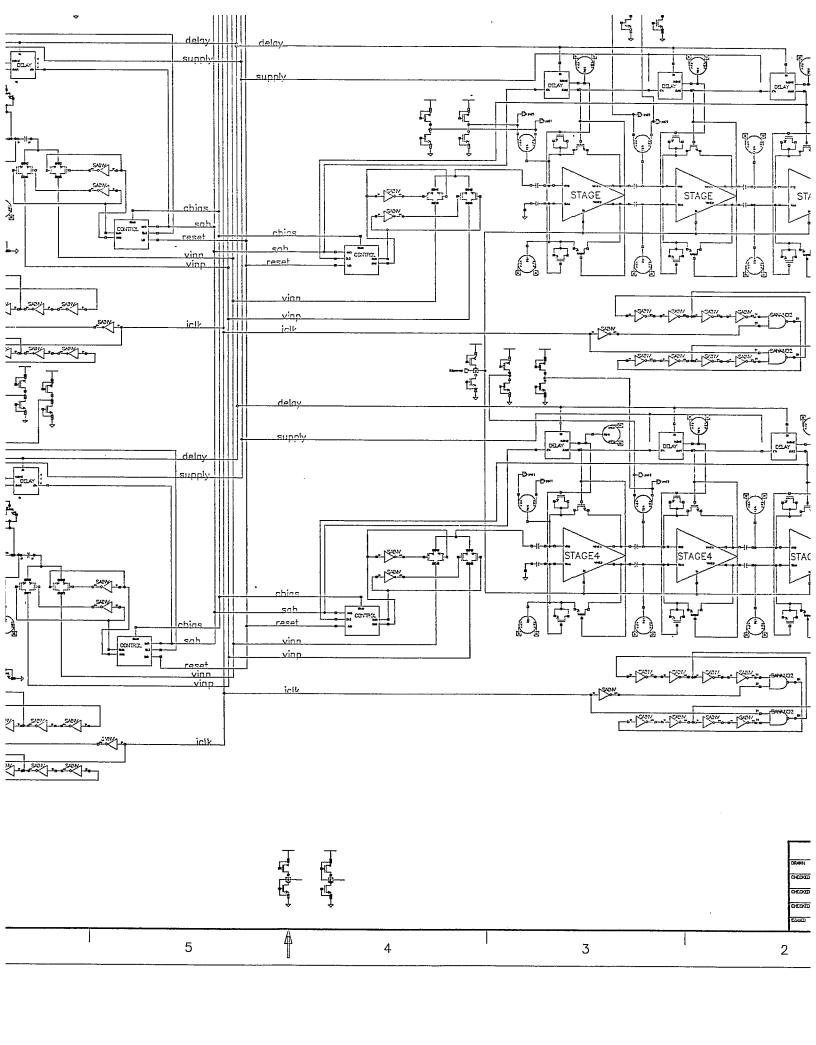

| Test Chip Overview                                                | 48        |

| Circuits                                                          | 50        |

| Single Ended Comparator                                           | 50        |

| Differential Comparators                                          | 58        |

| Forced Charge Injection Circuits                                  | 67        |

| Programmable Delay Circuit                                        | 70        |

| Source Follower Probe Circuits                                    | <b>75</b> |

| Sense Amplifier                                                   | 78        |

| Control                                                           | 81        |

| Results                                                           | 87        |

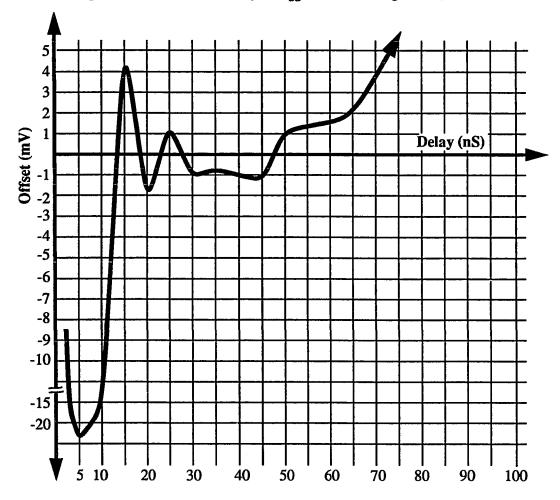

| Experiment 1: Direction of Offset Shift                           | 87        |

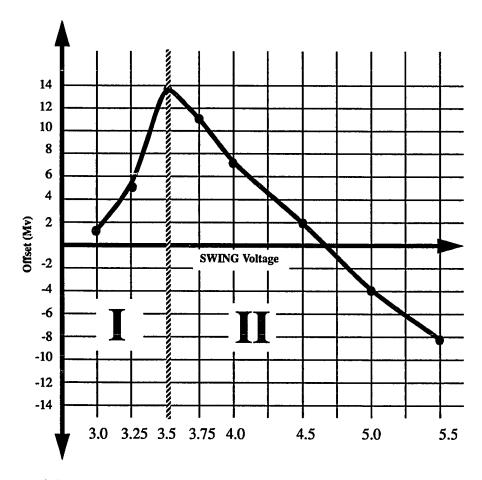

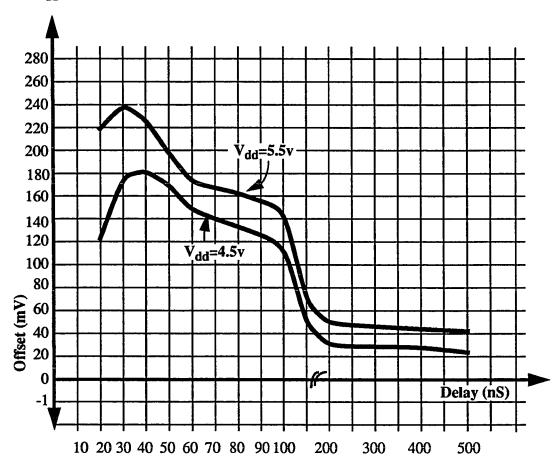

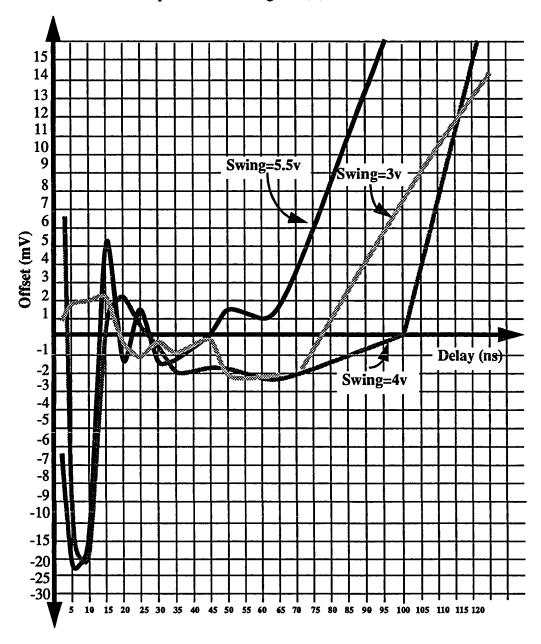

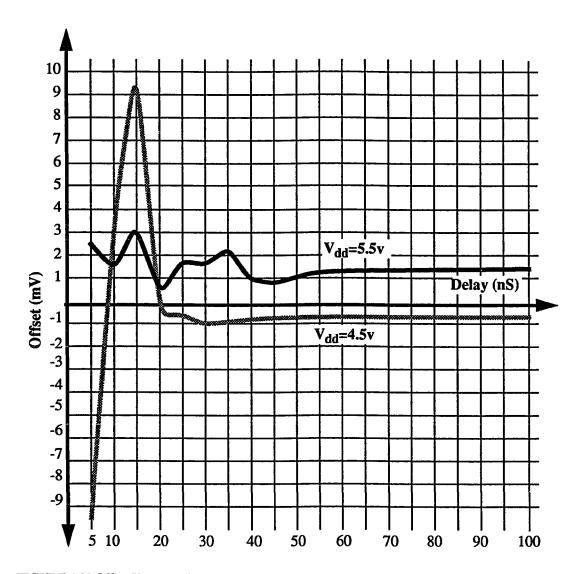

| Experiment 2: Swing Vs. Offset                                    | 91        |

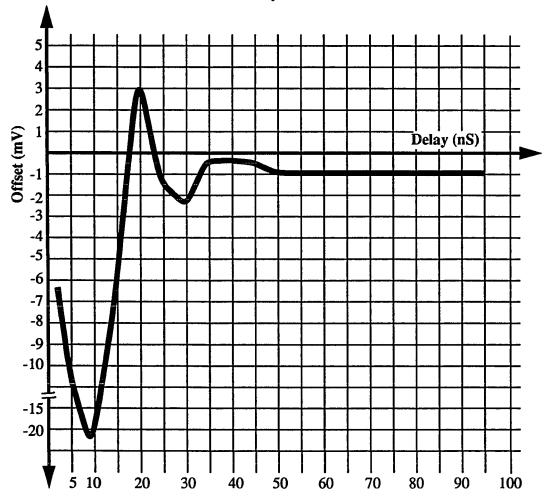

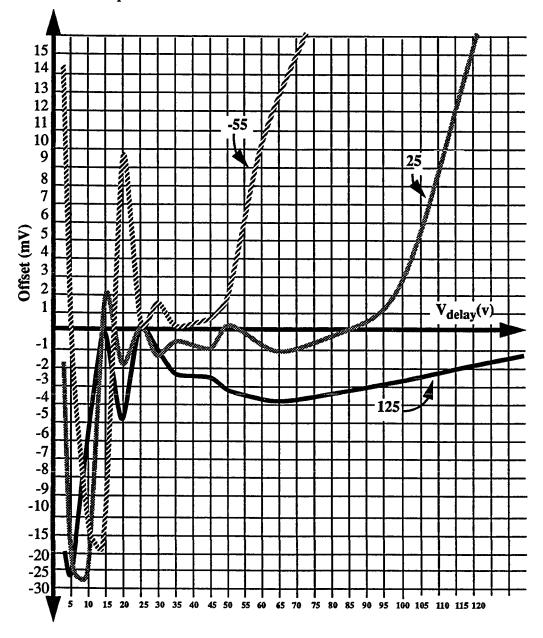

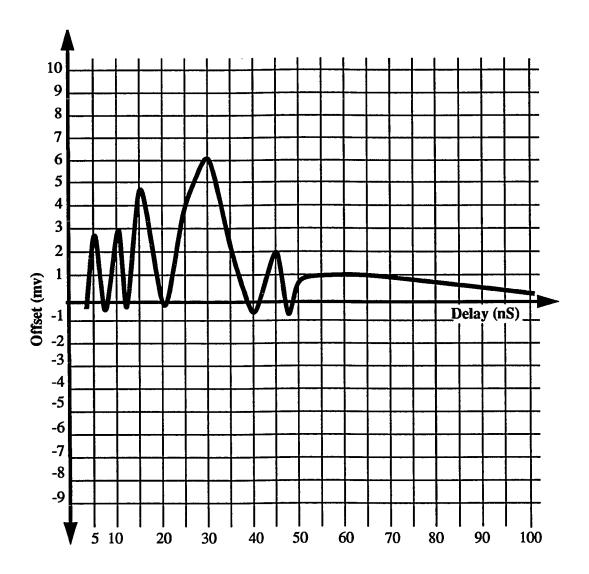

| Experiment 3: Offset Vs. Delay                                    | 94        |

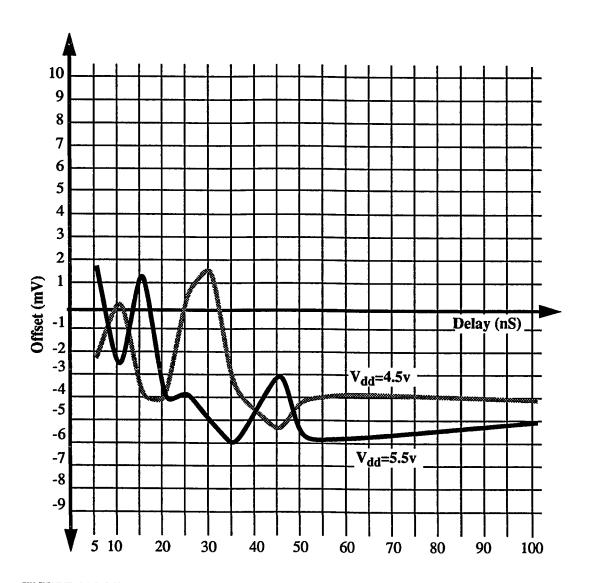

| Power Supply Rejection Ratio Vs. Delay                            | 98        |

| Experiment 5: Transient Response vs. Step Size Changes            | 103       |

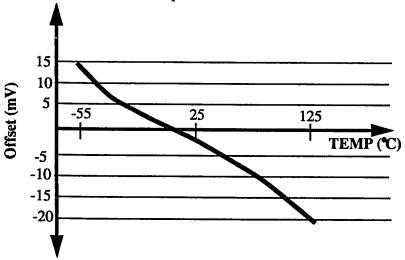

| Experiment 6: Temperature Sensitivity                             | 103       |

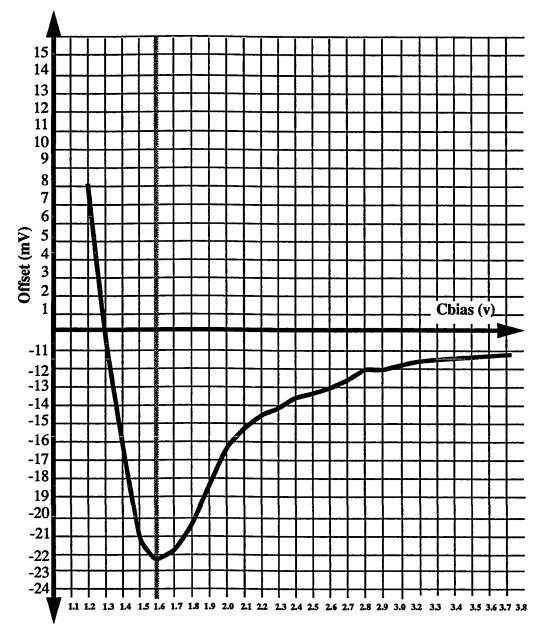

| Experiment 7: Offset Vs. Bias Current for Differential Comparator | 10        |

| Experiment & Offset and PSRR for Differential Comparator          | 111       |

| Experiment 9: Power Supply Rejection Ratio at a Forced Swing |     |

|--------------------------------------------------------------|-----|

| Conclusion                                                   | 115 |

| References                                                   | 117 |

| Appendix                                                     | 119 |

| Acknowledgments                                              | 120 |

#### 1.0 Statement of Problem

Charge injection is a phenomena which effects the accuracy of analog integrated circuits. MOS analog circuits using transistor switching schemes to sample high precision voltage levels suffer degradations in performance due to charge injection [1].

In circuits using sample-data comparators, analog voltages are sampled and held on high impedance capacitive nodes using MOS switches. Once the input has been sampled, the MOS switch turns off in order to hold the signal. During switching, the MOS transistor couples charge into the high impedance storage node altering the acquired voltage. This voltage change causes an unwanted offset on the comparator input.

The sample-data comparator is used in analog integrated circuits requiring a sample-and-hold circuit and comparator. One such circuit is the analog-to-digital converter. Analog-to-digital converters use the sample-data comparator to acquire an input voltage and compare this voltage to an algorithmically generated reference voltages [2]. After acquisition, the analog voltage is converted to a digital code. Charge injection effects the offset of the analog-to-digital converter, leading to incorrect mapping between the analog and digital domains.

The comparator offset, due to charge injection, must be cancelled in order to eliminate excessive analog-to-digital converter offsets. This thesis examines charge injection cancellation techniques and how they fail to satisfactorily eliminate  $V_{os}$ . A new method of charge injection cancellation is proposed. The technique was confirmed by working silicon prototypes.

In prior experimentation culminating three years of work, two analog-to-digital converters were designed using known techniques of charge injection cancellation. The first, an 8-bit resolution ADC used a single ended, inverter type comparator design. The second used a differential type comparator for a 10-bit resolution ADC. In both cases, charge injection was the main contributor to offset problems delaying production of the parts. Three years of experimentations have led to several novel circuit techniques.

An analog test chip was designed containing single ended and differential comparators. The following circuit design techniques have been developed for charge injection cancellation:

- 1. Current controlled delays of staggered auto zero signals.

- 2. Forced voltage swing of auto zero signals.

#### 1.1 Staggered Auto Zeroes

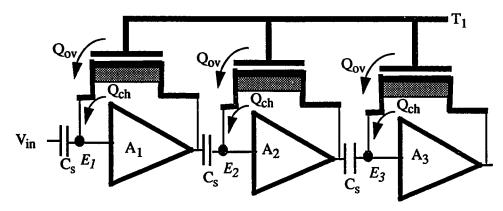

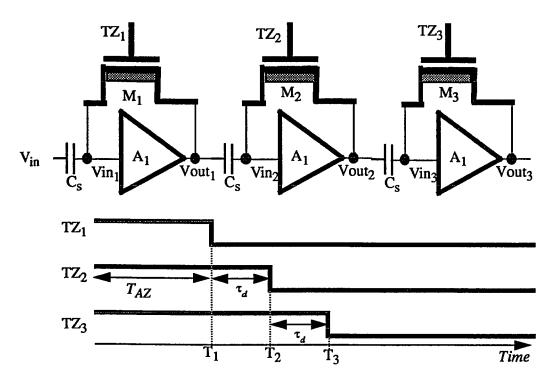

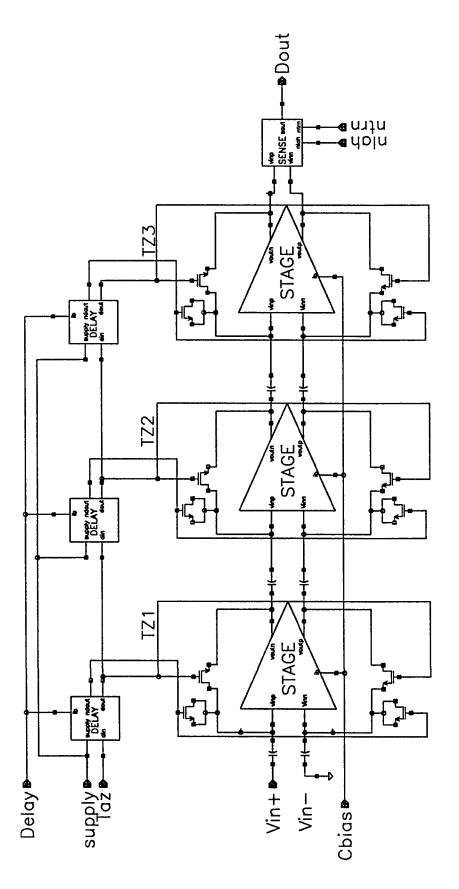

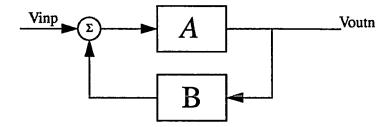

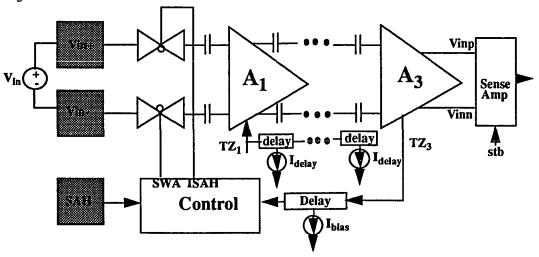

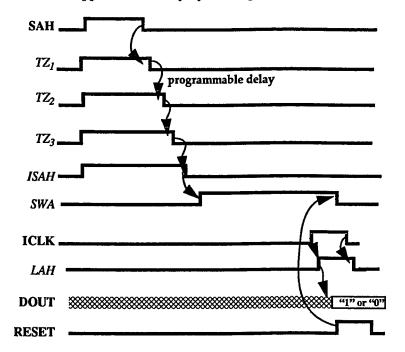

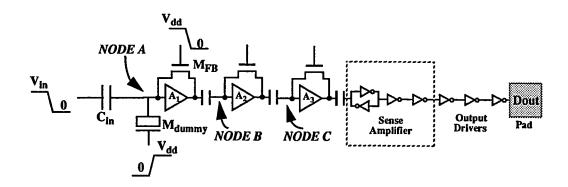

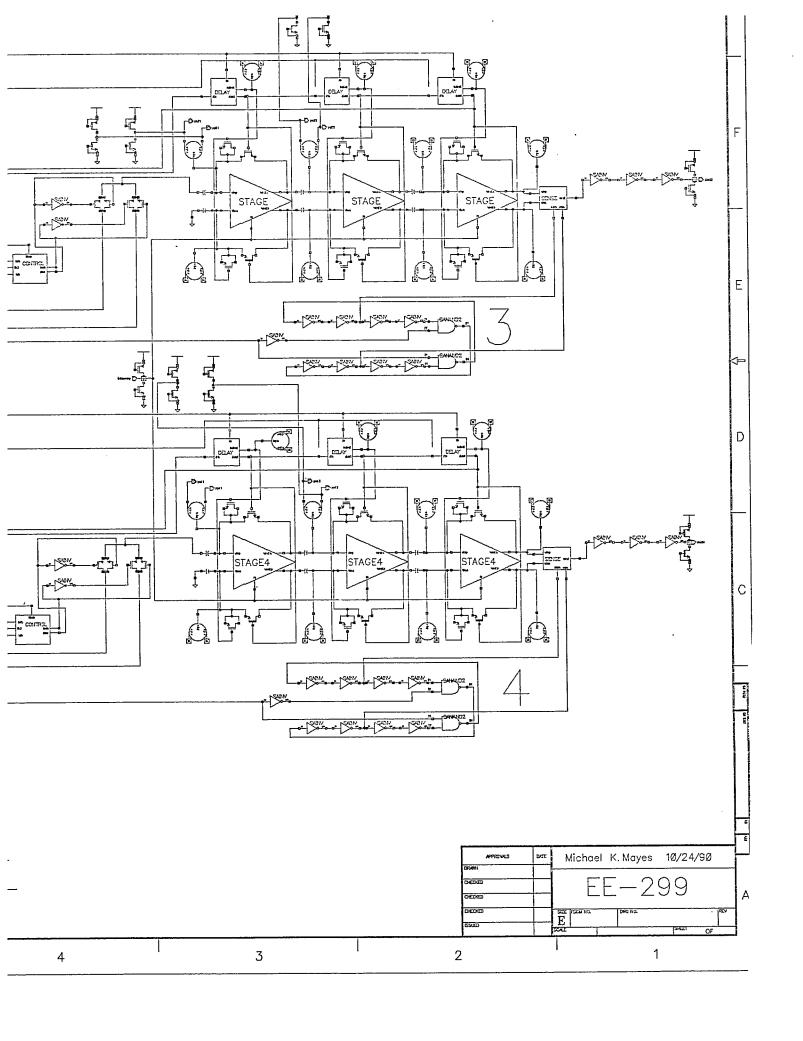

Since the gain of a single comparator is finite, typical ADC comparator designs use three stages of comparators to increase the overall gain (see figure 1.1). Each of the three stages requires a feedback switch to bias that individual stage. When  $T_1$  is high, each

FIGURE 1.1 Three Stage Comparator

comparator is biased to its trip-point. Each stage is capacitively coupled with  $C_s$  in order to independently store the DC bias point of that stage while passing the AC signals. Once  $T_1$  goes low, the comparator enters its high gain region of operation. For this comparator the overall gain is the product of the three individual gain stages

$$A_{\nu} = A_1 \times A_2 \times A_3 \tag{1.1}$$

$A_v$  is typically 1000. On the falling edge of  $T_1$ , charge is injected into each of the three comparators high impedance input nodes.  $E_1$ , the first stage error voltage, contributes directly to the overall offset of the comparator. Since  $E_2$  is isolated from the input by amplifier  $A_1$ , its contribution to the overall error is reduced by a factor of  $A_1$ . Similarly, the error voltage generated by the third feedback switch,  $E_3$ , is reduced by  $A_1 \times A_2$ . The overall error voltage as seen by the input to the comparator is

$$E_{in} = E_1 + \frac{E_2}{A_1} + \frac{E_3}{A_1 \times A_2}$$

1.2

For single stage gains greater than 1, the dominate error in  $E_{in}$  is  $E_1$ . Therefore, the charge injection of the first stage is the most significant contributor to offset voltage.

Since there are three stages of comparators, one known way to cancel the effect of the first stage error,  $E_1$ , is to delay turning off the feedback switch of the second stage until the first stage has settled to its charge injection altered trip point. If the second stage feedback switch is on while the first stage is settling, the error  $(E_1)$  generated by the first stage charge injection does not effect the output of the overall comparator.

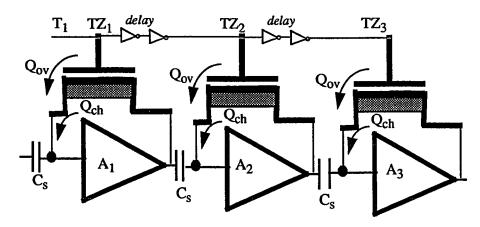

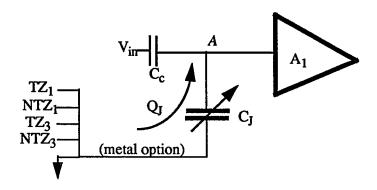

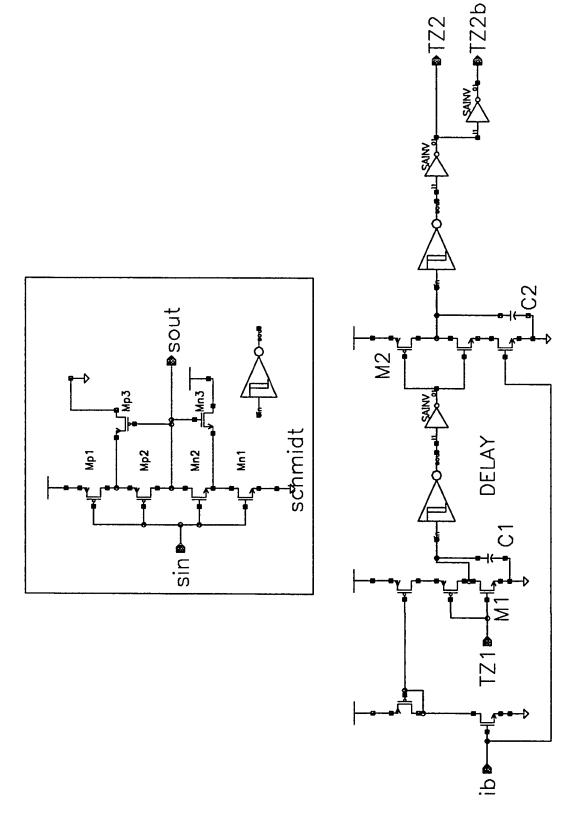

One method of delaying or staggering the auto zero signals is to add several inverter delays between the gates of the feedback switches (see figure 1.2).

FIGURE 1.2 Staggered Auto Zero Signals

By adding two gate delays between  $TZ_1$  and  $TZ_2$  the second stage auto zero switch is on two gate delay times after charge injection has altered the first stage offset. Since the second stage is still forcing  $V_{out}=V_{in}$ , any error introduced by the first stage will not effect the bias point of the second stage.

When  $TZ_1$  goes low, charge is injected into the input of amplifier  $A_1$ . This error voltage is amplified by  $A_1$  and output to the input terminal of  $A_2$ , If  $TZ_2$  is still "1" then the trip point of  $A_2$  is not changed. If  $TZ_2$  is "0" then the trip-point of  $A_2$  is offset by the output of amplifier  $A_1$ . Too short a delay will not cancel the charge injection, while too long will reduce the maximum conversion time of the ADC. A typical design may use several mask sets to determine the optimum delay.

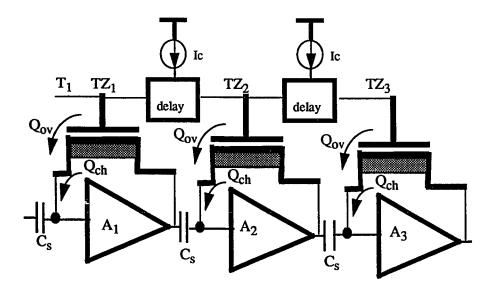

The problem with inverter delays is the limited control of their delay. To increase the delay, more inverters are required between auto zero signals. Rather than using inverters to delay the signals, a current programmable delay circuit can be used to externally control the delay. Delay vs. comparator offset can be determined with a precision delay circuit. The inverters would simply be replaced by delay blocks, see figure 1.3.

FIGURE 1.3 Programmable Delay Staggered Auto Zeroes

An external controllable current is used to adjust the delay between staggered auto zeroes from 1ns to 100ns. In this case, the second stage feedback switch is turned off after the first stage switch. The time difference between successive auto zero switches turning off is externally controllable through  $I_c$ . An option also exists to short the auto zeroes together for 0ns of delay.

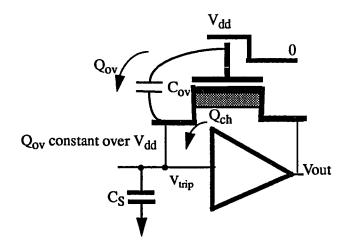

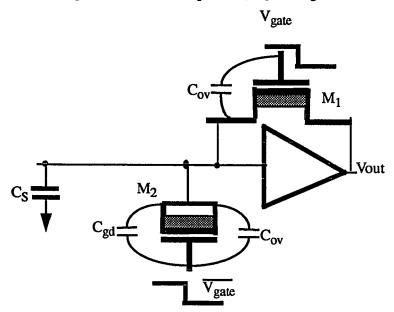

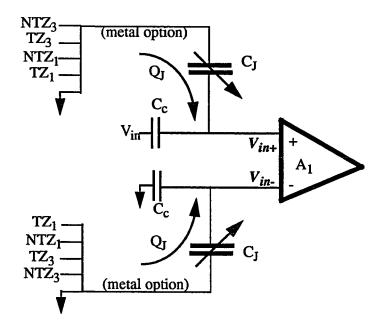

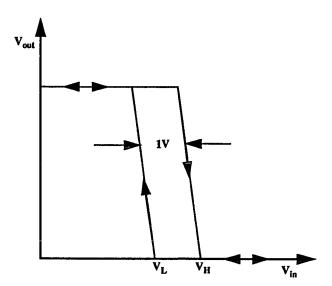

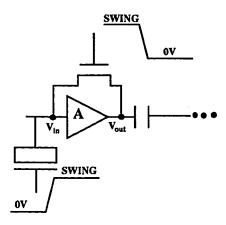

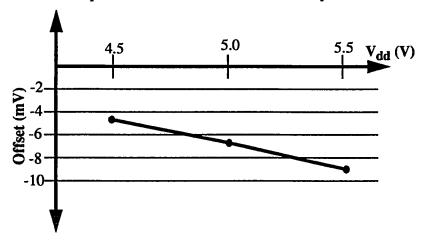

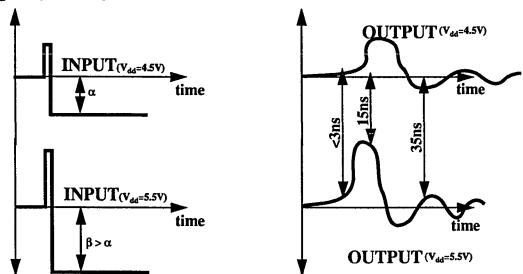

#### 1.2 Forced Voltage Swing of Auto Zero Signals

Not only does the offset change as a result of charge injection, but it also varies over supply voltage ( $V_{dd}$ ). Most ADC's have a power supply rejection ratio (PSRR) specification. PSRR is defined as the offset variation as  $V_{dd}$  varies  $\pm 10\%$

$$4.5v \le V_{dd} \le 5.5v \tag{1.3}$$

The offset varies with  $V_{dd}$  because the signals driving the MOS feedback switches are swinging from  $V_{dd}$  to ground (figure 1.4), leading to variations in charge injection

$$Q_{inj} = Q_{ch} + V_{dd} \times C_{ov} 1.4$$

where  $Q_{ch}$  is channel charge injection and  $C_{ov}$  is the gate to source overlap capacitance of the MOS switch. These variations in charge injection lead to variations in comparator offset voltage

$$V_{os} = \frac{Q_{inj}}{C_{s}}$$

1.5

Since the trip point of comparators is typically designed to half supply

$$V_{trip} \approx \frac{V_{dd}}{2}$$

1.6

the minimum signal required to turn on the feedback switch is

$$V_{az} = V_{in} + \frac{V_{dd}}{2} \tag{1.7}$$

where V<sub>tn</sub> is the N-channel threshold voltage.

Instead of driving the feedback switches with an inverter swinging from  $V_{dd}$   $\pm 10\%$  to 0v, The feedback switches are driven with a  $V_{dd}$  independent bias voltage.

$$V_{bias} \ge V_{tn} + \frac{V_{dd (max)}}{2}$$

1.8

In this case,  $\Delta V$  across  $C_{ov}$  is fixed with respect to supply. As  $V_{dd}$  varies,  $V_{bias}$  remains constant, reducing offset variations over supply.

$$Q_{ov} = V_{bias} \times C_{ov} \Rightarrow CONSTANT$$

1.9

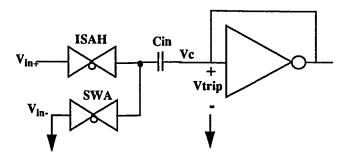

FIGURE 1.4 Constant Swing Auto Zero Signal

A typical specification for PSRR is 1/2 LSB. The first silicon from an 8-bit ADC with 2 inverter delays between each auto zero signal had a PSRR of 5 LSB. A fully differential 10-bit ADC had a PSRR of 10 LSB. These results were very discouraging; however, by changing the design several times the PSRR was significantly reduced. The proceeding circuits were developed to eliminate this problem without post adjustments of the mask set.

#### 2.0 Background

#### 2.1 Charge Injection

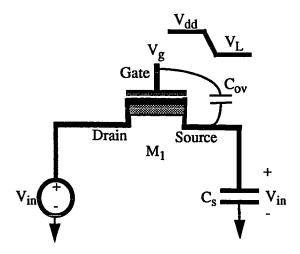

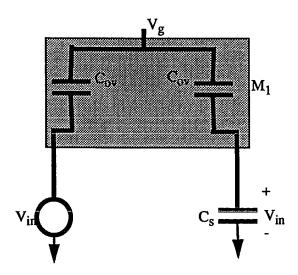

In precision analog circuits, such as analog-to-digital converters, MOS switches are used to sample voltage levels on capacitive storage nodes. The accuracy of this sampling is essential for proper analog processing of the acquired signal. Charge injection occurs when the MOS switch tied to the capacitive storage node is opened. As shown in figure 2.1,  $M_1$  is on when  $V_g=V_{dd}$ . While  $M_1$  is on, capacitor  $C_s$  is charged to  $V_{in}$ . At some time after  $C_s$  has charged to  $V_{in}$ ,  $V_g$  is pulled low ( $V_g=V_L$ ) forcing  $M_1$  to turn off. Since  $M_1$  is off,  $V_{in}$  can change without effecting the voltage stored on  $C_s$ . While  $V_g$  is changing from  $V_{dd}$  to  $V_L$ , charge injection causes the stored voltage across capacitor  $C_s$  to change. The charge injection is a combination of clock feed through and mobile charges in the channel [3].

**FIGURE 2.1 Simple Data Acquisition Circuit**

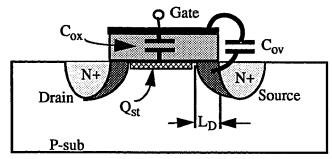

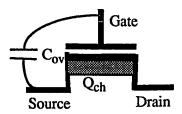

Clock feed through is due to the overlap capacitance ( $C_{ov}$ ) of the MOS switch. The overlap capacitance is due to the lateral diffusion ( $L_D$ ) of the MOS transistor, see figure 2.2.

FIGURE 2.2 Overlap Capacitance of a MOS Switch

The overlap capacitance of an MOS device is

$$C_{ov} = C_{ox} \times W \times L_D$$

2.1

Where  $C_{ox}$  is the gate oxide capacitance per unit area, W is the transistor width and  $L_D$  is the lateral diffusion. Since the gate voltage is changing from  $V_{dd}$  to  $V_L$ during turn off, charge is coupled from the gate to the source through  $C_{ov}$  altering the voltage stored on  $C_s$ .

In order for an MOS switch to be conductive, an inversion layer of charge  $(Q_{st})$  exists in the channel between the source and drain. When the MOS switch is turned off, this inversion layer collapses forcing the charge to exit into the source and drain [4]. A fractional part of this charge is injected into the source node adding to the clock feed through induced error on capacitor  $C_s$ .

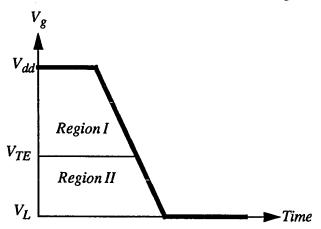

When  $V_g$  is falling from  $V_{dd}$  to  $V_L$ , the MOS transistor goes through two regions of operation. These regions are shown in figure 2.3, and are defined by the following:

Region I

$$V_{TE} < V_g < V_{dd}$$

2.2

Region II

$$O < V_{\varrho} < V_{TE}$$

2.3

where  $V_{TE}$  is the effective threshold of the MOS device including the source voltage ( $V_s$ ).

FIGURE 2.3 MOS Switching Regions of Operation

During the first region of switching, the transistor is turning off. Hence, all the channel charge is leaving the MOS switch in this region.  $C_{ov}$  is also coupling  $V_g$  to  $C_s$ . Once  $V_g$  falls below  $V_{TE}$  the transistor is off; hence, the channel charge  $(Q_{st})$  no longer exists. However,  $C_{ov}$  continues to couple voltage to the storage capacitor  $C_s$ .

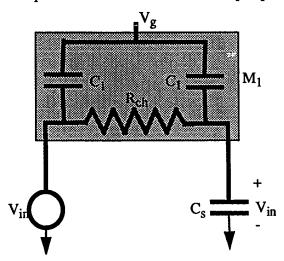

While in region I, the MOS switch ( $M_1$  of figure 2.1) can be replaced by a combination of capacitors and a resistor [5], see figure 2.4. The Resistor ( $R_{ch}$ ) is the on channel resistance of the MOS switch.  $C_1$  is the combination of the overlap capacitance ( $C_{ov}$ ) and

FIGURE 2.4 Charge Injection Model of a MOS Switch in Region I

the effective capacitance due to charge stored in the channel (Cox).

$$C_1 = C_{ov} + \frac{C_{ox}}{2}$$

2.4

where it is assumed half the channel charge exits through the drain and half through the source. The total charge stored in the channel is given by

$$Q_{st} = (V_{dd} - V_{TE}) \times C_{ox} \bullet W \bullet L$$

2.5

where L is the channel length. The channel charge is the accumulation of electrons (absence of holes) on the gate capacitor's bottom plate, the channel.

Using the fundamental equation for charge coupling,

$$dQ = C \times dV 2.6$$

The total charge injected into the capacitor  $C_s$  in region I is

$$Qtot_I = Q_{ch} + Q_{ov} 2.7$$

The charge injection due to channel charge is

$$Q_{ch} = \frac{C_{ox}}{2} \times (V_{dd} - V_{TE})$$

2.8

where  $Q_{ch}$  is assumed to be half the charge in the conductive channel  $(Q_{st})$ . This assumption is only valid for a gate voltage  $(V_g)$  with a long fall time. The magnitude of the charge injection due to mobile channel charges  $(Q_{ch})$  depends on  $V_{TE}$ ,  $V_{dd}$ , and  $C_{ox}$ .  $C_{ox}$  is process dependent, changing as the oxide thickness  $(T_{ox})$  varies.

$$C_{ox} = \frac{\varepsilon \cdot \varepsilon_{si} \cdot W \cdot L}{T_{ox}}$$

2.9

where  $\varepsilon = 1.04 \times 10^{-12}$ , the permittivity of free space and  $\varepsilon_{si} = 2.9$ , the relative permittivity of silicon dioxide.

As the device gets larger (W and L increase), the charge injection due to  $Q_{ch}$  also increases. By reducing the width of the MOS switch,  $Q_{ch}$  is reduced; however, the on channel resistance of the MOS switch ( $R_{ch}$ ) is increased.

$$R_{ch} = \frac{L}{k'_n \cdot W \cdot (V_{gs} - V_{TE})}$$

2.10

where  $k'_n$  is a process parameter of the transistor, and  $V_{gs}$  is the gate to source voltage. This increase in  $R_{ch}$  slows down the acquisition of  $V_{in}$ , since  $V_{in}$  charges  $C_s$  through  $R_{ch}$ , refer to figure 2.4. Therefore, there is a system limit as to how small W can be. Reduction in channel length (L) is limited by process technology currently at  $1\mu$ .

The channel charge injection ( $Q_{ch}$ ) is also dependent on  $V_{TE}$ , the effective threshold voltage of the MOS switch. The MOS switch has a process controlled zero bias threshold voltage ( $V_{TO}$ ). The effective threshold voltage ( $V_{TE}$ ) alters the zero bias threshold voltage as a function of  $V_{in}$  and effect coefficient ( $\gamma$ ). The effective threshold of the MOS device is given by[6].

$$V_{TE} = V_{TO} + V_{in} + \gamma (\sqrt{|-2\phi_f + V_{in}|} - \sqrt{|-2\phi_f|})$$

2.11

where  $2\phi_f$  is the substrate fermi level.  $\phi_f$ ,  $\gamma_f$ , and  $V_{TO}$  are process dependent. The zero bias threshold ( $V_{TO}$ ) typically ranges from 0.5 to 1 volt.

Since the body effect coefficient is positive for N-channel enhancement devices,  $V_{TE}$  increases as  $V_{in}$  increases. Therefore, the charge injection due to channel charge decreases as  $V_{in}$  increases. Combining 2.6, 2.8, 2.10, and 2.12, the net voltage change on the storage node as a result of channel charge is

$$V_{ch} = \frac{W \cdot L \cdot \varepsilon \cdot \varepsilon_{si}}{2 \cdot C_{ox} \cdot C_{s}} \left( \left( V_{dd} - V_{in} - V_{in} \right) - \gamma \left( \sqrt{\left| -2\phi_{f} + V_{in} \right|} - \sqrt{\left| -2\phi_{f} \right|} \right) \right)$$

2.12

Typically,  $V_{dd}$  is equal to the supply voltage ( $V_{dd}$ ); therefore, the channel charge injection is dependent on the value of  $V_{dd}$ . Charge injection is also a function of temperature, because  $V_{TO}$  is dependent on temperature.

$$V_{TO}(T) = V_{TO} - \alpha (T - T_o)$$

2.13

where  $V_{TO}$  is the zero bias threshold at room temperature ( $T_o = 300^{\circ}K$ ) and T is the actual temperature.  $\alpha$  is typically 2.3mv/°C [7].  $V_{TO}$  decreases 2.3mv for every 1°C increase in temperature.

Clock feed through also contributes to charge injection in region I. The voltage change on the gate causes a charge of

$$Q_{ov_t} = C_{ov} \cdot (V_{dd} - V_{TE}) \tag{2.14}$$

to be injected into the storage node. This is also dependent on  $V_{dd}$ . However, the contribution of  $Q_{ov}$  in region II will make the overall contribution of clock feed through independent of  $V_{TE}$ .

Once the MOS switch has turned off, the transistor enters into *region II* of operation, see equation 2.3. Since the transistor is off, the charge injection due to channel charges is zero.

$$Q_{ch}=0 2.15$$

However, Cov still exists as shown in the model of the MOS switch of figure 2.5.

FIGURE 2.5 Charge Injection Model of MOS Switch in Region II

The net charge injected into the storage node for region II is

$$Qtot_{II} = C_{ov} \cdot (V_{TE} - V_L)$$

2.16

Combining 2.7, 2.8, and 2.16, the total charge injection is

$$Q_{inj} = C_{ov} \cdot (V_{dd} - V_L) + \frac{C_{ox}}{2} \cdot (V_{dd} - V_{TE})$$

2.17

From equations 2.14 and 2.16, the total charge injection due only to clock feed through is

$$Q_{ov} = C_{ov} \cdot (V_{dd} - V_L)$$

2.18

Consequently, the overall charge injection due to clock feed through is independent of  $V_{\text{TE}}$ .

The effect of the combination of clock feed through and channel charge is to change the voltage stored on capacitor  $C_s$  from its original value  $V_s$  to  $V_s$ .

$$V_s = V_s + \frac{Q_{ov} + Q_{ch}}{C_s} = V_s + \frac{Qtot_I + Qtot_{II}}{C_s}$$

2.19

This error can be reduced by increasing  $C_s$ , but this effects the acquisition time of  $V_{in}$ . The time constant limiting the acquisition time of the input signal is

$$T_c = R_{ch} \times C_s 2.20$$

where  $R_{ch}$  is the on resistance of the MOS device given by 2.10 and  $C_s$  is the total capacitance tied to the storage node.

#### 2.2 Analog-to-Digital Converter Basics

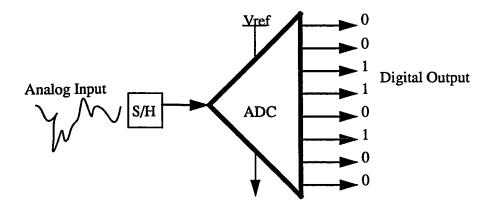

An analog-to-digital converter (ADC) is a type of electronic circuit which functionally digitizes a continuous analog input voltage into a discrete digital word. The block diagram of a typical system consisting of an ADC is shown in figure 2.6.

FIGURE 2.6 Analog-to-Digital Converter System Block Diagram

A typical ADC uses a Sample-and-hold circuit to acquire an analog voltage level at some instance in time. The acquired discrete voltage is then fed to the algorithmic circuitry responsible for converting this voltage level to its digital equivalent. The sample-and-hold circuit is necessary because the ADC algorithmic block requires some non-zero amount of time to determine the digital equivalent of the applied input. Fundamentally, this non-zero time corresponds to the maximum conversion rate of the ADC.

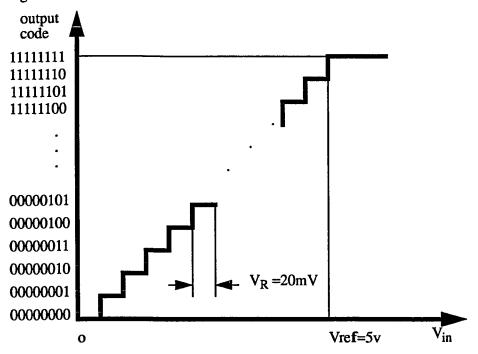

Once the continuous input is held, the corresponding analog voltage is applied to the input of the ADC. For a resolution of N-bits,  $2^N$  possible output codes exist. For example, an 8-bit ADC (N=8) has  $2^8$  =256 possible output codes. Digitally, this corresponds to binary outputs 00000000, 00000001, 00000010,..., 11111111. The analog input range is determined by a reference voltage (Vref). If the analog input  $V_{in} \ge Vref$  the ADC will output 11111111. The lower end of the input range occurs at  $V_{in} \le 0v$ , yielding the output 00000000. As the input changes linearly from 0v to Vref, the digital output changes discretely from 00000000 to 111111111. At an input voltage of Vin=Vref/2, the equivalent digital output is 10000000. The analog resolution (V<sub>R</sub>) is the magnitude of each voltage quantization step required to change the output by one bit. This is related to the ADC's resolution (N) by the following

$$V_R = \frac{Vref}{2^N}$$

2.21

Ideally, the value of V<sub>R</sub> is the same for each output code transition.

As shown in figure 2.7, the transfer curve of an 8-bit ADC is a plot of the digital output code vs. analog input voltage.  $V_R$  corresponds to the width of the staircase; the smaller the width, the higher the resolution.

FIGURE 2.7 ADC Transfer curve

In a typical application, the reference voltage (Vref) is 5 volts. For an 8-bit resolution ADC, Vref is divided into  $2^8$  equal quantization steps. This corresponds to 20 mv of quantization voltage between each step. Referring to figure 2.7, as the input voltage increases from 0v to 5v, the digital output increases from 00000000 to 111111111. With each 20mv increase in Vin, the output increases by +1 binary code. There are many circuit design techniques and architectures for implementing the ADC transfer function of figure 2.7, but for now the ADC will be treated as a black box. Within that black box are analog decision blocks made of comparators and voltage dividing networks made of resistors and/or capacitors.

#### 2.3 Sample-Data Comparator

#### 2.3.1 Comparator building block in Analog-to-Digital Converters

One main element contained within the ADC is the sample-data comparator. In complementary metal oxide semiconductor (CMOS) integrated circuits, the comparator serves two functions. First, it is used to sample-and-hold the analog input voltage. ADC's using CMOS processes and sample-data comparators do not require an external sample and hold circuit. The second, and most important function of the sample-data comparator, is analog comparison. The analog comparator bridges the gap between real analog voltages and the mathematical digital words.

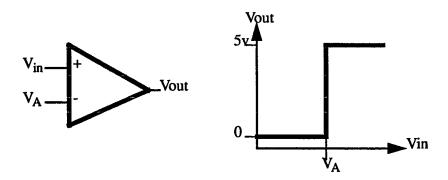

The analog comparator (figure 2.8) simply determines if the voltage potential at the positive input is larger than the voltage applied to the negative input.

FIGURE 2.8 Ideal Analog Comparator and Transfer Function

The output of the comparator is determined by the following relationship.

if

$$V_A > V_{in}$$

then  $V_{out} = 0v$  2.22

if

$$V_A < V_{in}$$

then  $V_{out} = 5v$  2.23

The comparator is used as an analog decision block interfacing analog inputs to digital outputs. CMOS comparators can be designed with nearly zero input current. This allows the comparator to function as both a sample-and-hold and an analog decision block.

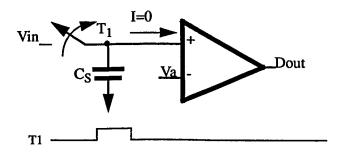

FIGURE 2.9 Comparator used as Sample-and-Hold

As shown in figure 2.9, the analog input voltage (Vin) is sampled on the capacitor  $C_S$  while signal  $T_1$  is high. Once  $T_1$  goes low and as long as  $T_1$  remains low, the instantaneous input voltage remains stored on  $C_S$ . This type of built in sample-and-hold is possible in CMOS and NMOS integrated circuits because the MOS gate current is negligible. For bipolar type comparators the base current ( $I_B$ ) would discharge the stored voltage; hence, CMOS is a common process used for ADC's with on board sample-and-holds.

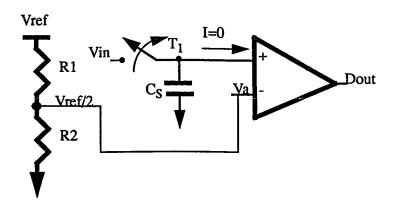

A complete analog-to-digital converter may consist of resistors, comparators, and logic devices. Figure 2.10 shows the usefulness of a comparator in a 1-bit analog-to-digital converter. In this example, a resistor ladder is used to divide the reference voltage into a quantized decision voltage level used as an input to the comparator. This reference level is compared to the sampled input voltage.

FIGURE 2.10 A 1-Bit Analog-to-Digital Converter

The output of the 1-bit ADC is either a digital "1" or a digital "0". If the sampled voltage, Vin>Vref/2 then the comparator output is a "1". If the input voltage is smaller then Vref/2, then the ADC output is a "0". For a 1-bit ADC (N=1), corresponding to an analog quantization step of  $V_R=Vref/2$ . Figure 2.11 shows the transfer curve of the 1-bit ADC. Notice how this resembles the transfer curve of the ideal comparator of figure 2.8.

FIGURE 2.11 Transfer Curve of a 1-Bit ADC

In an N-bit ADC, resistors or capacitors must divide the reference voltage into 2<sup>N</sup> equal quantization points. This leads to more complex circuits than that of figure 2.10. Regardless of the resolution, the comparator is a key element in most ADC architectures. The non-ideal behavior of the comparator is a major limiting factor in the resolution and conversion speed of the analog-to-digital converter.

#### 2.3.2 Single Ended Comparators

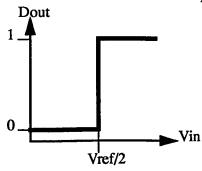

The simplest CMOS comparator is an inverter. By biasing the inverter to its trip point, the inverter acts as a high gain amplifier. The trip point of a CMOS inverter is given by

The inverter trip point occurs when the inverter's output equals its input, this point serves as the bias point of the comparator. Figure 2.12 shows the transfer characteristics of a typ-

ical inverter. Except for finite gain, this curve is identical to that of an ideal comparator (figure 2.8) with  $V_A=V$ trip.

FIGURE 2.12 Transfer function of a CMOS Inverter

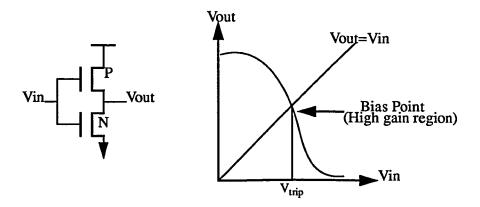

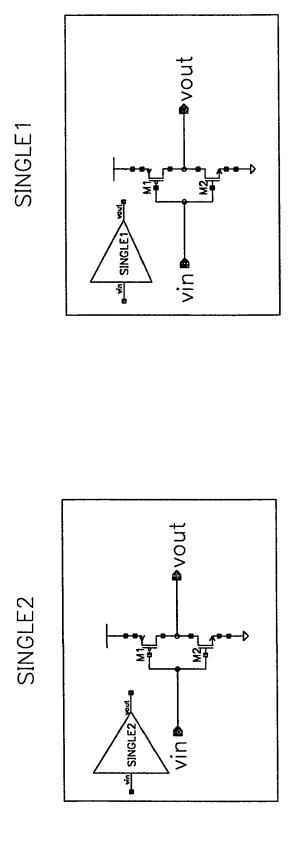

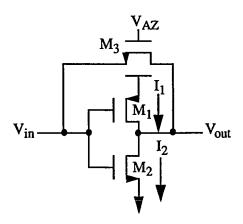

In order to use an inverter as a comparator, several additional circuit elements are required, as shown in figure 2.13.

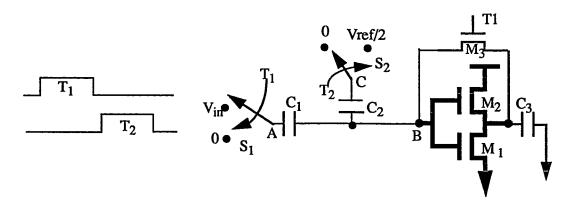

FIGURE 2.13 Detailed CMOS Comparator and Timing

The inverter, or gain element of figure 2.13, is comprised of  $M_1$  and  $M_2$ .  $M_3$  is known as the feedback or auto zero switch. When signal  $T_1$  is high, Transistor  $M_3$  is on, forcing the inverter into its high gain region: Vout=Vin=Vtrip. When  $T_1$  goes low,  $M_3$  turns off, but Vtrip is stored on capacitors  $C_1$  and  $C_2$ . The inverter trip point remains stored on these capacitors throughout the conversion; thus, keeping the comparator in its high gain region. During the auto zeroing time  $(T_1=1)$  the analog input voltage (Vin) is sampled on capacitor  $C_1$  through switch  $S_1$ . After  $T_1$  goes low,  $T_2$  goes high switching  $S_1$  to ground and  $S_2$  from ground to Vref/2. The fundamental equation for charge injection is

$$dQ = C \times dV 2.25$$

By switching node A from Vin to 0v a net charge of value

$$dQ_1 = C_1 \times (Vin - 0) \tag{2.26}$$

is injected into node B. Simultaneously, node C is switched from 0v to Vref/2. This injects a net charge of

$$dQ_2 = C_2 \times \left(0 - \frac{Vref}{2}\right)$$

2.27

into node B. Applying superposition, the total charge displacement at node B is given by:

$$dQ_{total} = dQ_2 + dQ_1 2.28$$

This yields a net charge injected into node B of:

$$dQ_{net} = C_1 \times V_{in} - C_2 \times \frac{Vref}{2}$$

2.29

Any net positive change in charge,  $dQ_{net} > o$ , on node B will raise the voltage at that point by

$$dV = \frac{dQ_{net}}{C_{nodeR}}$$

2.30

driving the inverter output low. Any net loss of charge,  $dQ_{net} < 0$ , will lower the voltage at node B forcing the output of the inverter to its high state. If  $C_1 = C_2$  then Vin will be compared to Vref/2. If Vin>Vref/2 then the net charge ( $dQ_{net}$  from equation 2.30) is positive and the inverter will output a "0". On the other hand, if Vin<Vref/2 the net charge is negative forcing the inverter output to "1". By logically inverting the comparator output, a transfer function similar to that of a 1-bit ADC has been achieved (see figure 2.11).

This inverter comparator behaves like the ideal comparator of figure 2.8 except it has finite gain limited by the output impedance of transistors  $M_1$  and  $M_2$  of figure 2.13. Along with finite gain, the comparator circuit also has an offset voltage. Conceptually, the offset voltage of a single ended comparator is the variation in trip point over supply, temperature, and process. During the auto zeroing phase  $(T_1=1)$  the feedback transistor accounts for these variations automatically and stores the exact trip point on the coupling capacitors  $C_1$  and  $C_2$ . Since the inverter is always forced to the point Vin=Vout=Vtrip regardless of process and operating conditions, the inherent offset is 0. However, charge injection resulting from turning off feedback transistor  $M_3$  effects the initial voltage at node B such that  $V_{in} \neq V_{out}$ , leading to an input offset voltage.

#### 2.3.3 Charge injection in a Single Ended Comparator

Ideally, for a single ended comparator, the trip point will always be  $V_{out}=V_{in}$ . The only way an offset can exist is if some disturbance forces  $V_{in}$  to increase or decrease from its quiescent value. In this case,

$$v_{out} = V_{in} + V_{os} \times A_{v} 2.31$$

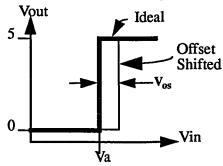

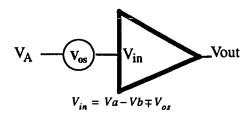

where  $V_{os}$  is the offset voltage or voltage change from quiescence as a result of some external disturbance and  $A_v$  is the comparator gain. In MOS inverters using feedback switches for auto zeroing, charge injection changes the comparator trip point from  $V_{trip}$  to  $V_{trip}+V_{os}$ . The result of this change in trip point leads to an initial offset on the comparator. Figure 2.14 shows how this effects the ideal comparator transfer curve.

FIGURE 2.14 Transfer Curve of Ideal Comparator with Offset

This offset voltage  $(V_{os})$  can be modeled as a voltage source tied to the input of the ideal comparator (see figure 2.15). In this case, a larger input voltage than  $V_A$  is required to overcome the offset voltage before the output can go high. The polarity of  $V_{os}$  can also be negative depending on the disturbance. For negative  $V_{os}$ , a smaller input voltage than  $V_a$  will force the comparator output high.

FIGURE 2.15 Ideal Comparator with Offset

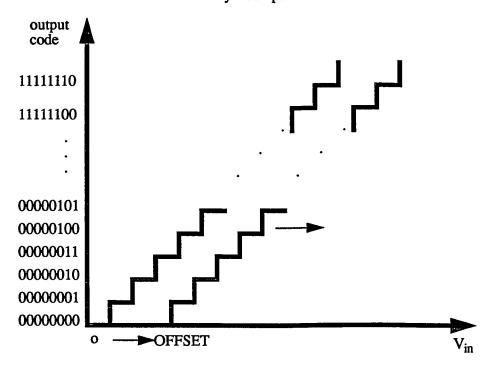

The comparator offset causes an inherent offset in the ADC. Figure 2.16 shows how the ideal ADC transfer curve is effected by a comparator offset.

FIGURE 2.16 Ideal ADC Transfer Curve with Offset

The quantization between each step is unaffected by comparator offset in some ADC architectures; however, the zero point of the ADC has changed. A larger (or smaller) input voltage is required for the output of the ADC to change from 00000000 to 00000001. For many system designs using ADC's, a large offset error is undesirable; thus, circuit design techniques must be utilized to eliminate comparator offset.

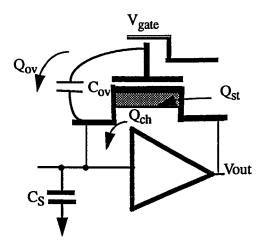

As shown in figure 2.17, charge injection is due to the overlap capacitance ( $C_{ov}$ ) and charge forming the conductive channel ( $Q_{st}$ ) in the MOS feedback switch.

FIGURE 2.17 Cov and Qch in an MOS Switch

The input node of a comparator is a high impedance capacitive node. Therefore, any charge injected into that node will change the voltage at that node (figure 2.18).

FIGURE 2.18 Charge Injection in a Single Ended Comparator

Charge is coupled to this node through  $C_{ov}$  of the MOS feedback switch. When the feedback switch is turned off, the gate voltage changes from supply  $(V_{dd})$  to 0v. The total charge coupled through  $C_{ov}$  is

$$Q_{ov} = V_{dd} \times C_{ov}$$

2.32

When the MOS switch is on, there is some charge stored in the channel. When the switch is turned off, a fraction of that charge is injected into the input node of the comparator. This charge is  $Q_{ch}$ . The total charge injected into the input of the comparator is the sum of the fractional channel charge and charge coupled through  $C_{ov}$ :

$$Q_{inj} = Q_{ch} + Q_{gs} 2.33$$

From 2.25, the total change in voltage at the input is given by

$$dV_{in} = \frac{Q_{inj}}{C_s} 2.34$$

Substituting 2.32 and 2.33 into 2.34, the comparator offset is

$$V_{os} = \frac{(V_{dd} \times C_{ov} + Q_{ch})}{C_s}$$

2.35

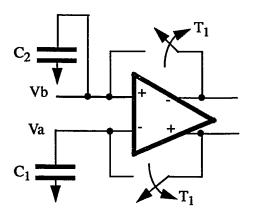

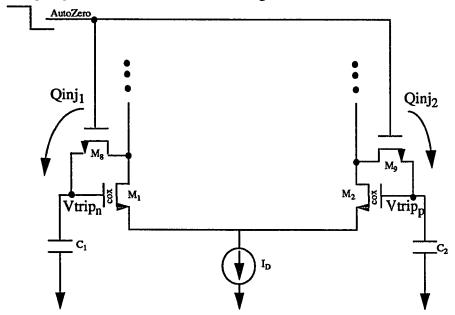

#### 2.3.4 Differential Comparators

In addition to the single ended comparator, a fully differential comparator structure can also be used in analog-to-digital converters. For differential type comparators, an initial offset exists due to mismatches between the two inputs. These mismatches are due to

input transistors, coupling capacitors, and load differences in the symmetrical circuit. When auto zeroing a differential comparator both outputs are shorted to the inputs of the comparator (see figure 2.19). This forces all inherent mismatches to be stored on the input capacitors,  $C_1$  and  $C_2$ . Once auto zeroed, the comparator offset, due to input mismatches, becomes zero.

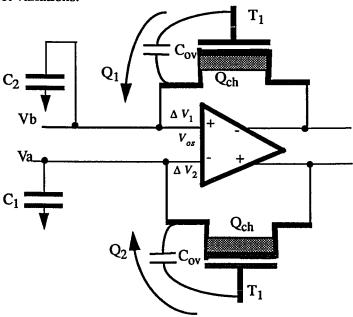

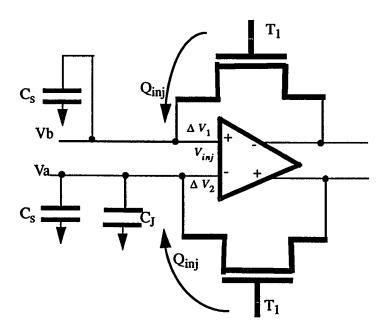

#### FIGURE 2.19 Differential Comparator

Once the feedback switches are opened, charge injection forces the high impedance input nodes to change voltage (see figure 2.20). If  $Q_1=Q_2$ , the overall effect of charge injection is a common mode change. The offset will not change since the comparator is fully differential. In a real circuit,  $Q_1 \neq Q_2$  due to mismatches in the two feedback transistors, and mismatches in the coupling capacitors,  $C_1$  and  $C_2$ . Therefore,  $\Delta V_1 \neq \Delta V_2$  leading to an offset voltage  $V_{OS}$  given by:

$$V_{os} = \Delta V_1 - \Delta V_2 \tag{2.36}$$

The fully differential structure is less sensitive to charge injection than the single ended type comparator. But for high resolution ADC's, N>8-bits, charge injection can still lead to significant offset variations.

FIGURE 2.20 Differential Comparator with Charge Injection

#### 2.4 Characterization of Analog-to-Digital Converters

#### 2.4.1 Linearity Plot

The transfer curve of an analog-to-digital converter represents an ideal plot of the output code vs. input voltage. By plotting the transfer curve of a real ADC, linearity, offset, fullscale, and gain errors can be determined for characterization of its performance.

The linearity error of an ADC at an arbitrary code is the difference between the ideal input voltage required to give that code and the actual voltage. The actual voltage is determined by slowly ramping the input voltage from 0v to Vref. The digital output of the ADC is monitored and the input voltage is measured when the output of the ADC is making a transition. This voltage is subtracted from the ideal transition voltage for that code. The error voltage is

$$V_{E} = V_{measured} - V_{ideal} 2.37$$

$v_{\xi}$  is determined for every code transition and converted from a voltage error to an LSB error

$$LSB_{\xi} = V_{\xi} \times \frac{2^{N}}{Vref}$$

2.38

where N is the resolution in bits. One LSB unit corresponds to the width of the ideal ADC transfer function's staircase. Ideally, one LSB change in the input voltage will change the output code by one bit.

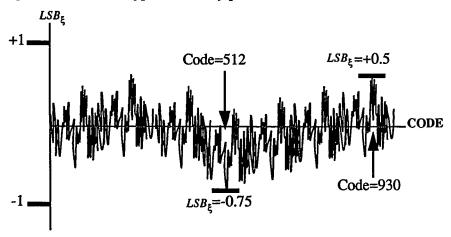

A linearity plot is used to show the accuracy of an ADC. Rather than plotting the transfer curve to characterize the ADC, a plot of linearity error in LSB's, is plotted for each input code. Figure 2.21 shows a typical linearity plot of a 10-bit ADC.

FIGURE 2.21 Linearity Plot of a 10-Bit ADC

In this plot, the horizontal axis corresponds to the codes 0 to 1023. The vertical axis corresponds to the linearity error at each code in LSB's. For this particular ADC, the worst error occurred at code 512. For this code, an error of -0.75 LSBs occurred.

For a 10-Bit ADC, the width of each step on its transition curve is

$$1LSB = V_R = \frac{Vref}{2^N}$$

2.39

For Vref=5v,

$$1LSB = \frac{5V}{1024} \cong 5mV \tag{2.40}$$

At each possible output code, the ideal input voltage is

$$V(Code)_{ideal} = \frac{Vref}{2^N} \times Code$$

2.41

The ideal input voltage required to give an output of 512 is

$$V(512)_{ideal} = \frac{5V}{1024} \times 512 = 2.5V$$

2.42

The error voltage at any given code is

$$V_{\xi} = LSB_{\xi} \times \frac{Vref}{2^{N}}$$

2.43

From figure 2.22, the error at code 512 is -0.75 LSB. This corresponds to an input error voltage of

$$V_{\xi} = \frac{5V}{1024} \times (-0.75) = -3.66 mV$$

2.44

The actual input voltage required for the ADC to output a given code is the sum of the ideal voltage at that code and the error voltage at the same code. The input required for this ADC to change from code 511 to 512 is

$$V_{measure} = 2.5V - 3.66mV$$

2.45

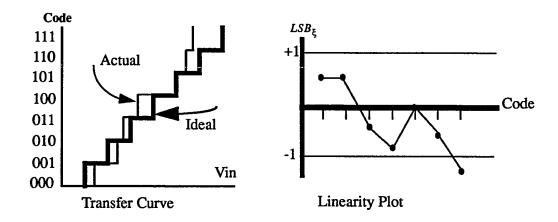

A linearity plot is more useful than a transfer plot for determining the linearity of an ADC. Figure 2.22 shows the transfer curve of a 3-bit ADC and its corresponding linearity plot.

FIGURE 2.22 3-Bit Linearity Plot and Transfer Curve.

As resolution increases, the transfer curve of an ADC becomes difficult to interpret. The linearity plot is the conventional method of examining the linearity of the ADC. For large resolutions, the linearity plot is simpler to extract data for characterization of the ADC.

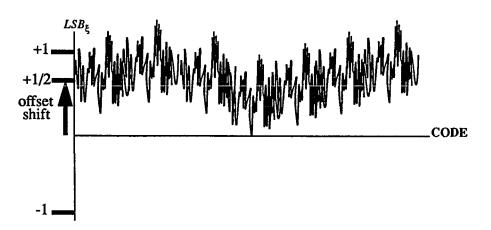

Along with linearity, the offset of the ADC can be determined from the linearity plot. Figure 2.23 shows the linearity plot of an ADC with a +1/2 LSB offset.

FIGURE 2.23 Linearity Plot of ADC with Offset

The offset error is the linearity error calculated at code 1. The ideal offset voltage from 2.41 is

$$V_{offset} = \frac{Vref}{2^N} \times 1$$

2.46

The actual offset is the difference between  $V_{\text{offset}}$  and the measured input voltage at code 1 converted to an LSB error.

$$OFFSET = [V_{offset} - V_{code = 1}] \times \frac{Vref}{2^N}$$

2.47

The result of an offset in some ADC architectures is to shift the entire linearity curve by that offset. Typically, this offset is due to *charge injection*. An ADC with no offset error would have a linearity error of zero at code 1.

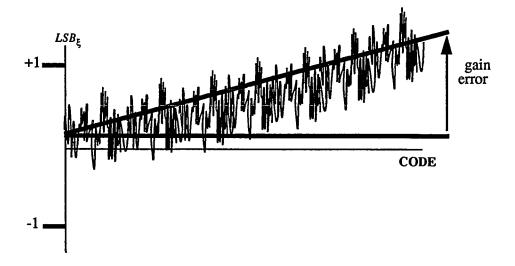

In addition to offset and linearity, the fullscale and gain error of an ADC can be determined from the linearity plot. The fullscale error of an ADC is defined as the linearity error at Code  $2^{N}$ -1. In LSB's the fullscale error is

$$FS = \frac{Vref}{2^N} \times (2^N - 1) - V_{measure}(code = 2^N - 1)$$

2.48

The gain error of an ADC is

$$GAINERROR = FS - OFFSET 2.49$$

Figure 2.24 shows an ADC with gain error.

FIGURE 2.24 ADC Linearity Plot with Gain Error

The gain error shows up as a slope in the linearity curve. The larger the slope, the larger the gain error. An ADC with an equal offset error and fullscale error will not have a slope. Unlike offset, gain errors are not due to charge injection, they are a phenomena due to problems with the reference voltage.

## 2.4.2 Power Supply Rejection Ratio

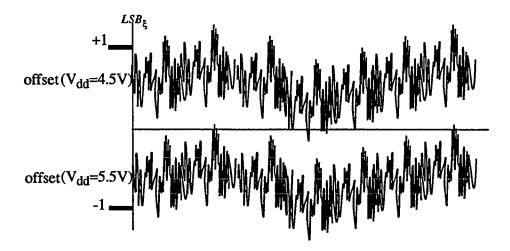

With a linearity plot, many ADC errors can be easily extracted from the shape of the plot and the scales. Among them are offset, fullscale, gain, and linearity errors. An important piece of information that can be extracted from several linearity plots is the power supply rejection ratio (PSRR). For a typical CMOS ADC, the supply voltage ( $V_{dd}$ ) is defined to be  $5V \mp 10\%$ . PSRR is defined as the difference in offset errors measured when  $V_{dd}$ =4.5V and  $V_{dd}$ =5.5V. Figure 2.25 shows two overlaid linearity plots of an ADC operating at two supply voltages.

FIGURE 2.25 Overlaid Linearity Plots of an ADC Operating at Two Different Supply Voltages

From these linearity plots, it can be seen that the offset has shifted the entire curve when the supply is varied from 4.5V to 5.5V. The power supply rejection ratio is defined as

$$PSRR = |offset(V_{dd}=4.5V) - offset(V_{dd}=5.5V)|$$

2.50

For a typical ADC, the PSRR limit is 1/4 LSB. This means the offset in LSB's can shift by 1/4 LSB when the supply is changed from 4.5V to 5.5V. From 2.43, 1/4 LSB is approximately 1.25mv for a 10-Bit ADC

The main contributor to the PSRR error is charge injection. Charge injection leads to a comparator offset voltage, which leads to ADC offset errors. Charge injection is due to the feedback switch in the comparator coupling charge through its gate to source overlap capacitance and channel charges leaving the collapsing depletion region during shut off. The signal driving the gate of the feedback switch is swinging from  $V_{dd}$  to ground. Referring to equations 2.8 and 2.32, the charge injection is proportional to  $V_{dd}$ .

$$Q_{ini} \propto V_{dd}$$

2.51

As V<sub>dd</sub> increases, the charge injection increases forcing the comparator offset to increase in magnitude. Since charge injection is proportional to the supply voltage, the overall

ADC offset is also a function of supply. Therefore, the problems with the PSRR are due to charge injection. By eliminating charge injection or making charge injection independent of supply, the PSRR can be reduced.

# 2.5 Analog-to-Digital Converter Architectures

In order to fully understand the errors associated with analog-to-digital converters, the black box function for converting analog voltages to digital codes will be examined.

## 2.5.1 Successive Approximation Analog-to-Digital Converters

One method of converting analog voltages to digital codes is by the successive approximation algorithm [8], [9]. For an N-bit successive approximation (SAR) type analog-to-digital converter, N algorithmic steps (one for each bit of resolution) are required for conversion. The SAR algorithm determines the output code one bit at a time from the most significant bit (MSB) to the least significant bit (LSB). The detailed output takes the form

$$D_{out} = [b_N, b_{N-1}, b_{N-2}, ..., b_2, b_1]$$

2.52

where  $b_N$  is the MSB and  $b_1$  is the LSB. The successive approximation algorithm requires one comparator, a voltage dividing array of resistors or capacitors, and a digital register.

The first step of the successive approximation algorithm is to compare the input voltage  $(V_{in})$  to Vref/2. This is done by generating a residual voltage

$$Vres_1 = V_{in} - \frac{Vref}{2}$$

2.53

Vres<sub>1</sub> is applied to the input of an analog comparator. The comparator will output a "1" if Vres<sub>1</sub> is positive and a "0" if Vres<sub>1</sub> is negative. The comparator output is defined by

Comp=1 if

$$V_{in}$$

>Vref/2 2.54

Comp=0 if

$$V_{in}$$

The MSB output of the ADC is determined by the comparator output.

$$b_N = Comp 2.56$$

This result  $(b_N)$  is stored in a successive approximation register (SAR) to be used for subsequent successive approximation steps.

Once  $b_N$  has been stored, the next bit can be determined. A new residual voltage is generated.

$$Vres_2 = V_{in} - \frac{Vref}{2} \bullet b_N - \frac{Vref}{4}$$

2.57

This second step compares Vref/4 to the input voltage minus the result of the first comparison. For  $b_N=0$ , the voltage (Vref/2) subtracted for the first comparison is added back to the residual cancelling the subtraction. For  $b_N=1$ , Vref/2 remains subtracted from the residual voltage. The comparator will now output Comp. Comp will be stored as bit  $b_{N-1}$  in the SAR. These comparisons continue until the LSB is determined. In the last comparison, a residual voltage is generated based on all previous steps.

$$Vres_N = V_{in} - \frac{Vref}{2} \bullet b_N - \frac{Vref}{4} \bullet b_{N-2} - \dots - \frac{Vref}{2^{N-1}} b_2 - \frac{Vref}{2^N}$$

2.58

Each successive step brings the value of Vres closer to the zero. The quantization error of the ADC is defined as

$$V_{quant} = V_{in} - \frac{Vref}{2} \bullet b_N - \frac{Vref}{4} \bullet b_{N-1} - \dots - \frac{Vref}{2^{N-1}} \bullet b_2 - \frac{Vref}{2^N} \bullet b_1$$

2.59

The quantization error is limited by the resolution of the ADC

$$V_{quant} \le \frac{Vref}{2^{N+1}}$$

2.60

In terms of LSB's, the quantization error of an ADC is

$$LSB_{quant} \le \frac{1}{2}LSB \tag{2.61}$$

The successive approximation algorithm is similar to the mathematical algorithm for determining the binary equivalent of a decimal number. If a decimal number can take on the values 0 to 255, the binary equivalent range would be 00000000 to 111111111. Letting Vref=256 and the binary output of the form [b<sub>8</sub>, b<sub>7</sub>, b<sub>6</sub>, b<sub>5</sub>, b<sub>4</sub>, b<sub>3</sub>, b<sub>2</sub>, b<sub>1</sub>], the successive approximation algorithm can mathematically determine b[8:1] for any decimal number from 0 to Vref=256.

For example, let Vin=123. The first step of the successive approximation algorithm is to compute

$$Vres_1 = V_{in} - \frac{Vref}{2} \rightarrow 123 - 128$$

$$2.62$$

Since Vres<sub>1</sub><0, b<sub>8</sub>=0. This result is stored in a register and passed on to the second step

$$Vres_2 = V_{in} - \frac{Vref}{2} \cdot 0 - \frac{Vref}{4} = (123 - 0 - 64) \ge 1 :: b_7 = 1$$

2.63

$$Vres_3 = V_{in} - \frac{Vref}{2} \cdot 0 - \frac{Vref}{4} \cdot 1 - \frac{Vref}{8} = (123 - 0 - 64 - 32) \ge 1 :: b_6 = 1$$

2.64

• • •

$$Vres_8 = V_{in} - \frac{Vref}{2} \bullet 0 - \frac{Vref}{4} \bullet 1 - \frac{Vref}{8} \bullet 1 - \frac{Vref}{16} \bullet 1 - \frac{Vref}{32} \bullet 1 - \frac{Vref}{64} \bullet 0 - \frac{Vref}{128} \bullet 1 - \frac{Vref}{256}$$

2.65

The final residual voltage is an approximation of the input voltage. The quantization error of the algorithm is  $\pm 1/2$ . Another step would be required to determine if 01111011 represented 123 or 123.5. For an 8-bit ADC, the quantization is  $\pm 1/2$  LSB. For Vref=5v, this corresponds to a quantization error of 10mv.

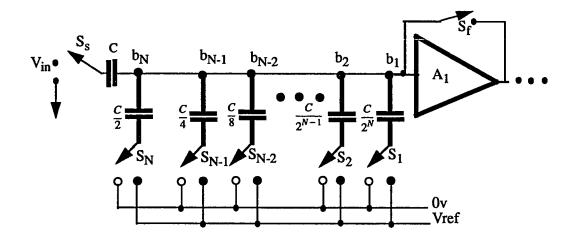

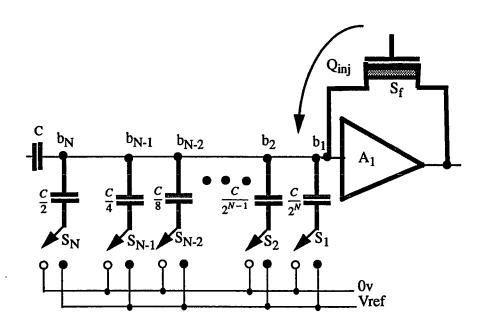

The actual ADC consists of a binary weighted array of capacitors used to generate Vref/2, Vref/4,... (see figure 2.26).

FIGURE 2.26 Successive Approximation ADC

The binary weighted capacitors are used to subtract Vref/2, Vref/4,...,  $Vref/2^n$  from  $V_{in}$ , while the comparator is used to determine if the result ( $V_{res}$ ) is positive or negative.  $A_1$  is the first stage of a three stage sample-data comparator.

The first step of the conversion algorithm is to auto zero the comparator and sample the input voltage. The comparator is auto zeroed when the feedback switch  $(S_f)$  is closed. During sampling, switches  $S_1$  through  $S_N$  are tied to 0v and  $S_S$  is tied to  $V_{in}$ . After acquisition,  $S_f$  and  $S_S$  are opened. A total charge of

$$Q_{in} = C \times V_{in} + Q_{ini}$$

2.66

is stored in the capacitor array, where Qini is the error due to charge injection.

Once  $V_{in}$  has been stored in the capacitor array, the MSB of data (bit  $b_N$ ) is determined. This is done by switching  $S_N$  from 0v to Vref. This forces a charge of

$$Q_N = -Vref \times \frac{C}{2}$$

2.67

to be injected into the input node of the comparator. This is added to the previous charge giving a residual charge stored in the capacitor array of

$$Q_{res_n} = C \times \left(Vin - \frac{Vref}{2}\right) + Q_{inj}$$

2.68

The resulting voltage change on the input of the comparator is

$$\Delta V_n = \frac{C \times \left(V_{in} - \frac{Vref}{2}\right)}{C_{total}} + E_1$$

2.69

where the error voltage on the input to the first stage due to charge injection is

$$E_1 = \frac{Q_{inj}}{C_{total}} 2.70$$

and C<sub>total</sub> is the total capacitance on the comparator input node.

If  $\Delta V_n$  is positive, the comparator output is "1" and if  $\Delta V_n$  is negative, the comparator output is "0". Therefore,

Comp=1 if

$$V_{in}$$

>Vref/2 2.71

Comp=0 if

$$V_{in}$$

The result of the first comparison (Comp) is stored in a digital register as  $b_N$ . If  $b_N$  is "1", then  $S_N$  remains at Vref for the extent of the conversion. On the other hand, if  $b_N$  is "0", then  $S_N$  is switched back to ground. By switching  $S_N$  back to ground, the charge removed from the capacitor array  $(Q_N)$  is injected back into the array. This leads to a residual charge, dependent on the result of the first comparison.

Switch  $s_{n-1}$  is now switched to Vref for the determination of the second bit of data. the net charge on the input node is

$$Q_{res_{N-1}} = C \times \left(V_{in} - \frac{Vref}{2} \cdot b_N - \frac{Vref}{4}\right) + Q_{inj}$$

2.73

The resulting voltage change is

$$\Delta V_{N-1} = \frac{C \times \left(V_{in} - \frac{Vref}{2} \bullet b_N - \frac{Vref}{4}\right)}{C_{total}} + E_1$$

2.74

The comparator will now output Comp based on the sign of  $\Delta V_{n-1}$ . The value of Comp is stored as  $b_{N-1}$  in the SAR to be used for all *successive* steps that follow.  $b_{n-1}$  controls switch  $S_{N-1}$ .

This algorithm continues until the LSB of data  $(b_1)$  is determined. Switches  $S_N$  through  $S_2$  are driven by the previous results  $b_N$  through  $b_2$ . Switch  $S_1$  is tied to Vref. This results in a residual voltage of

$$\Delta V_1 = \frac{C \times \left(V_{in} - \frac{Vref}{2} \bullet b_n - \frac{Vref}{4} \bullet b_{n-1} - \dots - \frac{Vref}{2^{n-1}} \bullet b_2 - \frac{Vref}{2^n}}{C_{total}} + E_1$$

2.75

The result of this comparison is stored as b<sub>1</sub>.

#### 2.5.2 Charge Injection in Successive Approximation Analog-to-Digital Converters

Since the successive approximation type ADC uses only one comparator, it is the simplest architecture to study the effects of charge injection.

Once auto zeroing has completed, the feedback transistor must turn off. A net charge of  $Q_{inj}$  is injected into the high impedance storage node of the comparator, see figure 2.27.

FIGURE 2.27 Charge Injection in Successive Approximation ADC's

The input voltage stored on this node is altered by the error voltage  $(E_1)$ , from equation 2.70. This error voltage is independent of  $V_{in}$  because it equally effects all successive steps of the conversion (2.73-2.75). However, it is dependent on the trip point of  $A_1$ . Looking at the ADC as a black box, charge injection alters the input by

$$V'_{in} = V_{in} + E_1$$

2.76

For a given input voltage, the error voltage  $(E_1)$  is added then the conversion is started. For all output codes, the expected voltage required to give those codes is shifted by  $E_1$ . The offset of the overall ADC is shifted from its ideal value by

$$Offset = E_1 \times \frac{2^N}{Vref}$$

2.77

As the resolution (N) increases, or the reference voltage (Vref) decreases, the offset change due to charge injection increases. For large resolution ADC's (N>10), charge injection significantly degrades the successive approximation analog-to-digital converter by altering the offset.

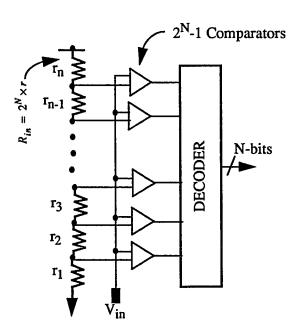

#### 2.5.3 Flash Analog-to-Digital Converters

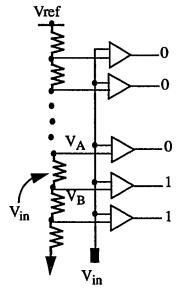

Conceptually, the flash type ADC is the most straight forward architecture, see figure 2.28. An N-bit flash ADC uses  $2^N$ -1 comparators and  $2^N$  resistors to determine which of  $2^N$  possible output codes  $V_{in}$  corresponds to [10], [11].

FIGURE 2.28 N-bit Flash Analog-to-Digital Converter

An N-bit Flash ADC consists of 2<sup>N</sup> equal valued resistors spanning from ground to Vref. The voltage drop across each resistor is

$$V_{drop} = \frac{Vref}{2^N}$$

2.78

This voltage drop is equal to the quantization voltage of an N-bit ADC, see equation 2.21. The Resistor ladder represents the quantized analog voltage steps of the ADC transfer function. If the discrete voltage points at the top of each resistor were measured, they would increase from 0v to Vref in  $V_R$  sized steps. These discrete tap point voltages are compared to the input voltage. This comparison requires  $2^N$ -1 comparators. Somewhere

along the resistor ladder, one of the tap voltages will be larger than the input voltage (see figure 2.29). All comparators tied to resistor tap points with voltage levels greater than  $V_{in}$  will output a "0", while all comparators tied to tap points with voltage levels less than  $V_{in}$  will output "1".

FIGURE 2.29 Comparator Outputs for V<sub>B</sub><V<sub>in</sub><V<sub>A</sub>

$V_{in}$  is a continuous analog voltage in the range defined by Vref. The comparators determined  $V_B < V_{in} < V_A$  by changing their outputs from "1's" to "0's" for all comparators tied above  $V_A$  on the resistor ladder. The comparator outputs drive a decoder which maps the position along the ladder where the comparators *flip* from "1's" to "0's" to the digital output code. This mapping is similar to an ADC transfer curve with the horizontal axis replaced by resistor tap points, see figure 2.30.

FIGURE 2.30 Resistor Ladder Mapping to ADC Output

For a flash ADC, the resistor ladder divides the reference voltage into the discrete voltages on the  $V_{in}$  axis of the ADC transfer curve. Analog comparators determine which tappoints are larger than  $V_{in}$  and which are smaller. A digital decoder network looks at the comparator outputs,  $C_{out} = C_1, C_2, C_3, ..., C_{2^{N}-1}$ , and determines the point where two adjacent comparator outputs are not equal. This flip point is decoded to generate the output code.

This type of ADC architecture is known as a *flash* type because its conversion takes place in one analog comparison step, unlike the successive approximation type ADC requiring N-steps. The advantage of a flash ADC is fast conversion rate, but the disadvantage is large numbers of comparators leading to high power consumption and increased die size.

In order to reduce comparator count without significantly sacrificing speed, architectures using several sub-flash steps are used. An N-bit half-flash ADC consists of two N/2-bit flash ADC's [12]. This type of converter significantly reduces the comparator, but increases the conversion time by slightly more than 2. By adding more flash steps, multistep ADC architectures further reduce comparator count in order to save on die area and power consumption [13].

## 2.5.4 Charge injection in Flash Analog-to-Digital Converters

Unlike the single comparator structure of the successive approximation ADC, the flash analog-to-digital converter uses 2<sup>N</sup>-1 comparators. Each of these comparators is used to determine the transistion of one digital output code. Since each output code changes state when one comparator changes state, charge injection effects each code independently.

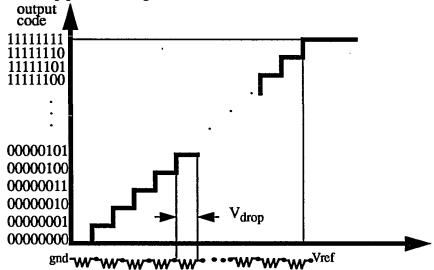

The charge injection of each comparator makes the resistor tap-point voltage it is tied to look larger or smaller, see figure 2.31.

FIGURE 2.31 Charge Injection in a Flash ADC

Assuming the charge injection is different for each comparator. This leads to offsets in each comparator such that the response becomes

$$C_1=1 \text{ if } V_a < V_{in} + \frac{Qinj_1}{C_{total}}$$

2.79

C2=1 if

$$V_b < V_{in} + \frac{Qinj_2}{C_{total}}$$

2.80

where Qinj<sub>1</sub> and Qinj<sub>2</sub> are charge injection of two adjacent comparators. These Qinj<sub>x</sub> terms will change the linearity error at each code independently. Not only does charge injection effect the offset of a flash ADC, it also effects the linearity by forcing unpredictable changes on each step of the transfer curve. The offset is determined by the first comparator error, while the linearity is effected by each individual comparator.

# 2.6 Charge Injection Cancellation Techniques

Several methods for charge injection cancellation exist. These include the addition of dummy devices and staggered auto zeroes. Typically, these may not be enough for effective cancellation. Two alternative methods of cancellation are presented. The first is programmable delay auto zeroes, and the second is  $V_{\rm dd}$  independent auto zero signals.

## 2.6.1 Dummy Device Cancellation

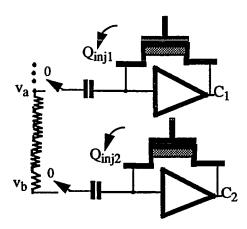

One method of cancelling the effects of charge injection is by adding a dummy switch to the high impedance input node of the comparator [14], see figure 2.32.

#### FIGURE 2.32 Dummy Device cancellation

The charge injection, due to clock feed through, can be cancelled by matching the overlap capacitance of  $M_1$ 's source with the total overlap capacitance of  $M_2$ . If the lateral diffusion is the same for the source and drain, then

$$C_{gd} = C_{gs} = C_{ov} ag{2.81}$$

where the gate to source overlap capacitance is defined as

$$C_{oy} = W \cdot L_D \cdot C_{ox}$$

2.82

Matching is achieved geometrically by setting the ratio between M<sub>1</sub> and M<sub>2</sub> as follows:

$$W_1 = 2 \times W_2 \tag{2.83}$$

$$L_1 = L_2 2.84$$

Driving the gate of  $M_2$  by the inverse signal driving  $M_1$ , the total charge injection due to clock feed through in figure 2.32 becomes

$$Q_{ov} = (C_{gd2} + C_{gs2}) (V_L - V_H) + C_{gs1} (V_H - V_L)$$

2.85

Assuming  $M_1$  and  $M_2$  have matching  $C_{ox}$  and  $L_D$ , substituting equations 2.81-2.84 into 2.85 yields

$$Q_{ov} = \left[\frac{2 \cdot W \cdot L_D \cdot C_{ox}}{2} - W \cdot L_D \cdot C_{ox}\right] (V_H - V_L) = 0$$

2.86

Therefore, the total charge injection due to clock feed through is cancelled by the dummy device if M<sub>1</sub> perfectly matches M<sub>2</sub>.

The problem with this technique is the channel charge injection  $(Q_{ch})$ .  $M_1$  and  $M_2$  must be driven by signals 180° out of phase with each other in order to cancel the clock feed through. This is typically done with an inverter whose input is the signal  $V_{gate}$  and output drives the gate of  $M_2$ . Since an inverter has finite delay,  $M_1$  is turned off an instant sooner then  $M_2$  is turned on. For small delays,  $M_1$  may still be on when  $M_2$  is turning on. This results in  $M_2$  acquiring its channel charge from the comparator output node rather than the charge leaving  $M_1$ .

For large delays, the entire charge required to turn  $M_2$  on is pulled out of the high impedance node. This charge is equal to the charge leaving  $M_1$  during turn off if  $Q_{st}$  is split symmetrically between the source and drain. Typically, the charge is not split equally between the source and drain. The fractional part  $(\chi)$  leaving the drain is dependent on the slew rate of the signal driving the gate  $(\alpha)$  [15].

$$\chi = \sqrt{\frac{\mu_n \bullet C_{ox} \bullet W \bullet L}{\alpha \bullet C_s}} (V_H - V_{TE})$$

2.87

where  $\mu_n$  is the electron mobility. The net charge injection due only to channel charges becomes

$$Q_{inj} = \chi Q_{ch} - \frac{1}{2}Q_{ch} = Q_{ch} \left(\chi - \frac{1}{2}\right)$$

2.88

Complete cancellation only occurs when  $\chi = 1/2$ , the case where half the charge stored in  $M_1$  leaves the source and half leaves the drain.  $\chi$  is dependent on  $V_{trip}$  since  $V_{TE}$  increases as  $V_{trip}$  increases (see equation 2.11). It is also dependent on temperature, since the mobility of electrons  $(\mu_n)$  decreases with temperature.

$$\mu_n \propto T^{-1.5} \tag{2.89}$$

$\chi$  is also dependent on process parameters. Therefore,  $\chi$  varies over the normal operating conditions of the device. Consequently, dummy devices will not completely cancel charge injection. For circuits requiring <5mv of accuracy over supply and temperature, the dummy device fails.

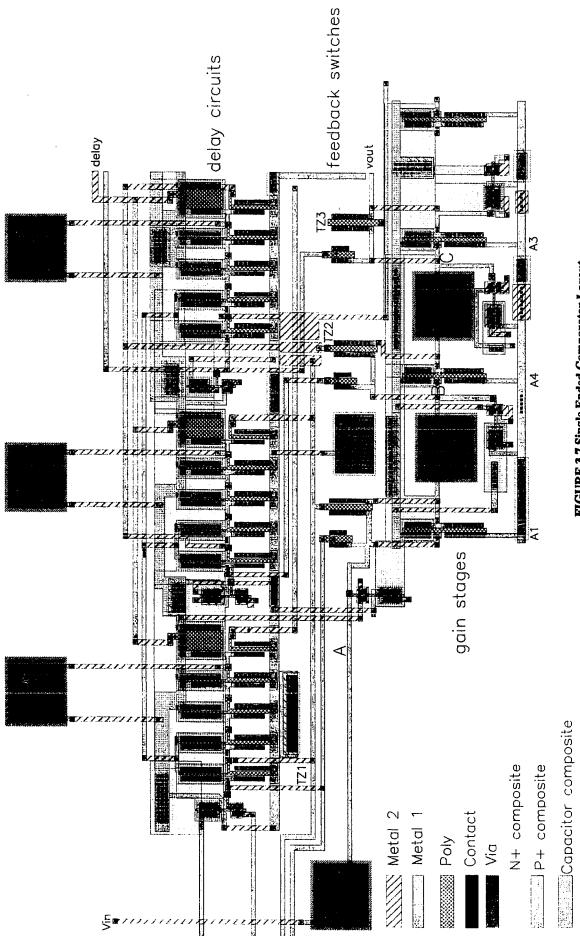

#### 2.6.2 Staggered auto zero signals

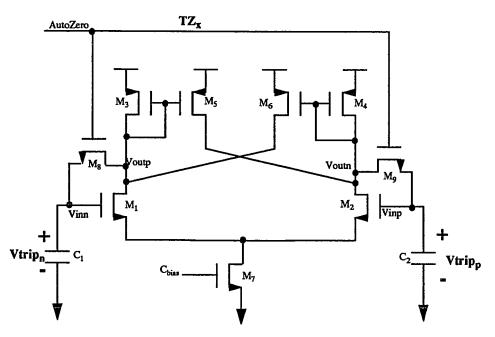

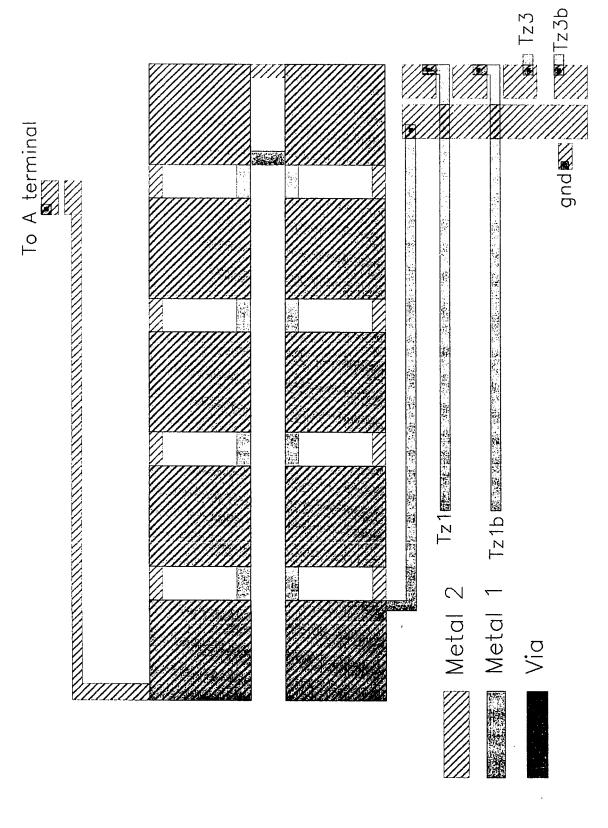

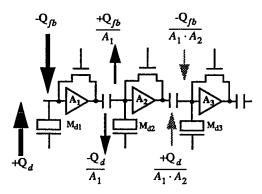

Another method of charge injection cancellation is possible in circuits using sample-data comparators. This cancellation technique involves breaking the gain elements of the comparator into stages and delaying the falling edge of the auto-zero signals driving the feedback switches of each stage [16]. Figure 2.33 shows a typical 3-stage sample-data comparator and its staggered auto zero timing.

FIGURE 2.33 3-Stage Sample-Data Comparator with Staggered Auto Zero Signals

The first stage feedback switch is driven by  $TZ_1$  which goes low before the signal  $(TZ_2)$  driving the feedback switch of the second stage. Similarly,  $TZ_2$  goes low before the signal driving the third stage feedback switch. In other words,  $M_1$  is turned off while  $M_2$  is still on and  $M_2$  is turned off while  $M_3$  is still on.

During time  $T_{AZ}$ , all three feedback transistors are on, this is known as the auto zero time. While the transistors are on, each of the individual stages  $A_1$ ,  $A_2$ , and  $A_3$  are biased to their trip points  $Vtrip_1$ ,  $Vtrip_2$ , and  $Vtrip_3$ , respectively. These trip points are stored on the amplifier input nodes  $Vin_1$ ,  $Vin_2$ , and  $Vin_3$ , and output nodes  $Vout_1$ ,  $Vout_2$ , and  $Vout_3$ .

At time  $T_1$ ,  $TZ_1$  goes low turning off transistor  $M_1$ . On the falling edge of  $TZ_1$ , charge  $Qinj_1$  is injected into the input of stage  $A_1$ . This alters the stored trip point voltage on node  $Vin_1$  by

$$E_1 = \frac{Qinj_1}{C_s}$$

2.90

This error voltage is amplified by  $A_1$ , altering the output of the first stage

$$Vout_1 = Vtrip_1 - E_1 \bullet A_1$$

2.91

This change in voltage is coupled through the capacitor  $C_s$  to the input of the second stage. If  $M_2$  is still on, the error voltage  $(-E_1 \cdot A_1)$  will not effect the bias point of  $A_2$ . While  $M_2$  is on, any change at the input of  $A_2$  will go to ground through the switch tied to the amplifier's output node.  $M_2$  will continue to force  $Vin_2$  to its trip point  $Vtrip_2$ .

Some time later  $(\tau_d)$ ,  $TZ_2$  will go low.  $\tau_d$  is defined as the delay time between auto zero signals. The falling edge of  $TZ_2$  injects a charge of Qinj<sub>2</sub> into the input of  $A_2$ . Since the input of each amplifier stage is high impedance, this leads to a stored error voltage of

$$E_2 = \frac{Qinj_2}{C_{\bullet}}$$

2.92

This error is amplified by  $A_2$  and coupled to the input of amplifier  $A_3$ . The bias point of  $A_3$  (Vtrip<sub>3</sub>) is not effected if  $TZ_3$  is still high.

Once TZ<sub>3</sub> goes low, a charge of Qinj<sub>3</sub> is injected into the input of amplifier A<sub>3</sub>. This error is

$$E_3 = \frac{Qinj_3}{C_s}$$

2.93

Amplifier A<sub>3</sub> amplifies this error voltage and the output of the last stage becomes

$$Vout_3 = Vtrip_3 - A_3 \bullet E_3$$

2.94

The output of the last stage is not altered by the charge injection induced errors  $E_1$  and  $E_2$  of the first and second stages, respectively. Referring the error at the output of sample data comparator back to the input gives the output error in terms of input voltage levels. This input error is the offset of the sample-data comparator.

$$V_{offset} = \frac{Vout_3}{-A_1 \cdot A_2 \cdot A_3} = \frac{E_3}{A_1 \cdot A_2} - \frac{Vtrip_3}{A_1 \cdot A_2}$$

2.95

The total error due to charge injection is reduced by the gain factor  $A_1 \cdot A_2$ . This is typically 100. The net result of staggered auto zero signals is to remove the effects of the charge injection induced errors of the first and second stages, while attenuating the offset of the third stage.

If the switches are opened at the same time,

$$TZ_1 = TZ_2 = TZ_3 2.96$$

then the error generated by the first stage  $(-E_1 \cdot A_1)$  is amplified by the second and third stages. Similarly, the error voltage generated by the second stage  $(-E_2 \cdot A_2)$  is amplified by the third stage. The error voltage generated at the output of the third stage is

$$Vout_3 = Vtrip_3 - A_1 \circ A_2 \circ A_3 \circ E_1 + A_2 \circ A_3 \circ E_2 - A_3 \circ E_3$$

2.97

Relative to the input, the overall offset of the sample-data comparator with no staggering is

$$V_{offset} = E_1 - \frac{E_2}{A_1} + \frac{E_3 + Vtrip_3}{A_1 \cdot A_2}$$

2.98

Not only is the charge injection of the first stage not cancelled, but it is also not attenuated. The effect of charge injection on the offset increases significantly when the auto zero switches are not staggered.

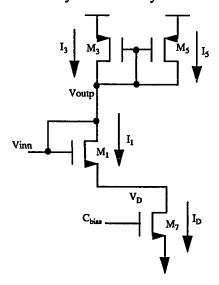

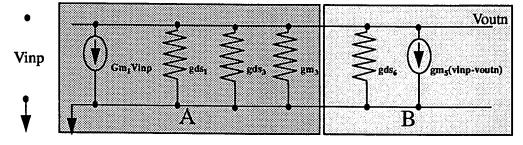

#### 2.6.3 Programmable Delay Staggered Auto Zero Signals

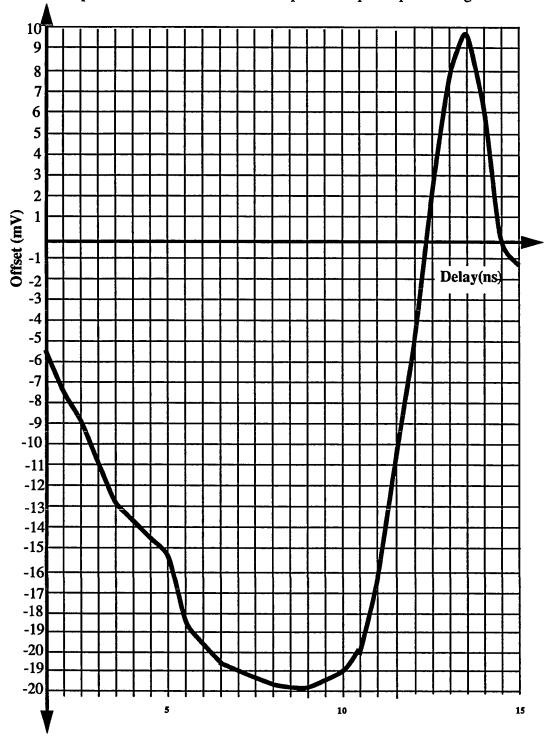

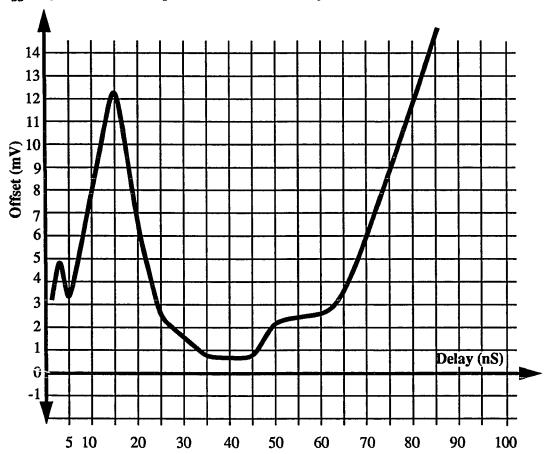

Once charge is injected into the input node of an amplifier, the amplifier responds by generating an output error voltage. This output voltage is a replica of the input error voltage scaled by the gain of the amplifier. The amplifier stage requires a settling time  $\tau_s$ , in order to generate the stable output error voltage. During this time, the output of the comparator is changing from its DC bias point to the final error induced bias point. This error voltage is coupled to the input of the second amplifier stage. If the second stage auto zero signal (TZ<sub>2</sub>) goes low before the first stage amplifier has settled, then complete charge injection cancellation will not occur. The extent of offset cancellation is a function of the delay between auto zero signals relative to amplifier response times.

The delay between auto zero signals must be larger than the settling time of the amplifier.

$$\tau_d > \tau_s$$

2.99

If the delay time is not sufficient, then  $V_{offset}$  will be some value between those predicted in equations 2.95 and 2.98.

The delay between auto zero signals is typically generated with several inverters. The signal delay induced by inverter stages does not track the small signal response time of the amplifier stages. The inverter delay varies over temperature, process, and supply voltage independently of the amplifier response time. Unless the inverter delay is made excessively large, cases exist where the delay is too short to completely cancel the charge injection effects of the first and second stages. This results in offset variations as the temperature, supply, or process is altered.

One alternative is to use many inverter stages to guarantee worst case delays are much larger than amplifier response times. The problem with this approach is the excessive delays lead to reduced speed performance of the comparator. In circuits requiring high speed

sampling, this excessive delay will become the limiting factor in the overall speed of the circuit. The acquisition time is increased by  $2 \cdot \tau_d$ .

A second alternative is to design a bias controlled delay circuit with constant delay over temperature, supply voltage, and process. By externally trimming the bias circuit, various delays from excessive to minimum can be tested in order to determine the delay vs. offset variation. From this data, an optimum bias point can be established such that maximum speed can be achieved with minimum offset variations.

#### 2.6.4 Supply Independent Swing

If the signals driving the auto zero switches are swinging from rail to rail, the overall charge injection is a function of the supply voltage (see equation 2.17). Many times a constant offset of a system can be cancelled if enough data is analyzed, but offset variations over supply voltage cannot easily be cancelled. Instead of driving the auto zero switches with signals swinging rail to rail, a supply independent swing from  $V_{bias}$  to 0v can eliminate offset drifts with respect to supply voltage. The only constraint on  $V_{bias}$  is that it be sufficiently large enough to insure the N-channel feedback switches are on. When driven with a signal swinging from  $V_{bias}$  to ground, the MOS switches induced charge injection becomes

$$Q_{inj} = C_{gs} \cdot V_{vias} + \frac{Cox}{2} \cdot (V_{bias} - V_{TE})$$

2.100

thus eliminating all first order effects of supply voltage.

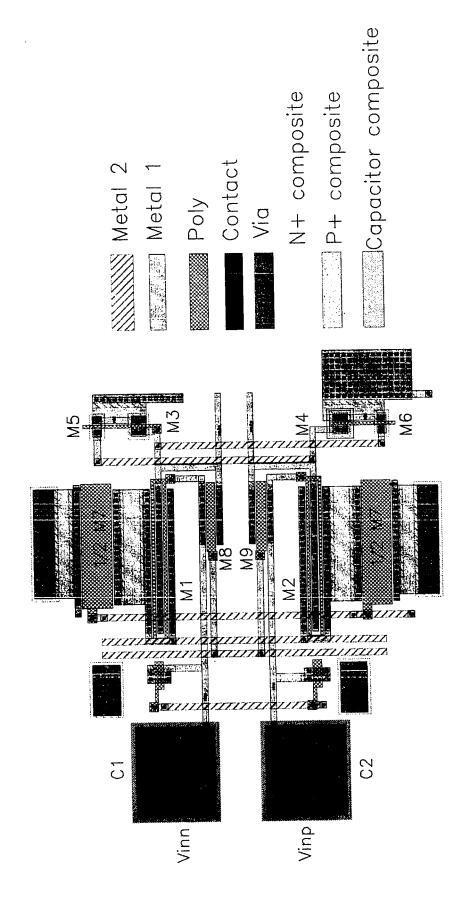

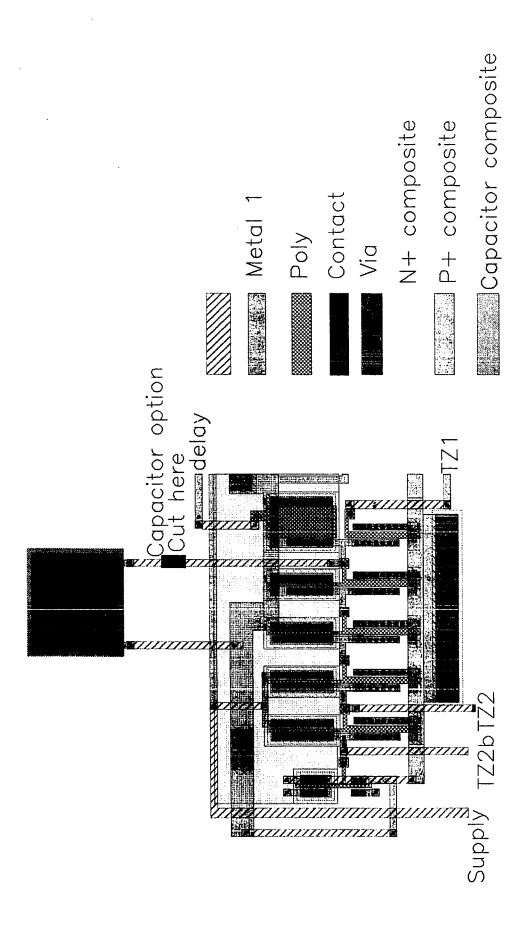

# 3.0 Methodology

# 3.1 process

$A_{1\mu}$ , N-well, double metal CMOS process was used in the characterization of charge injection.

The MOS gates are self aligned poly (poly before diffusion) with a minimum channel length (L) of  $1\mu$ . This process is described in more detail by cacharelis [17]. Table 3.1 lists typical key process parameters of the MOS devices, capacitors, and parasitic elements.

In addition to the P-channel and N-channel MOS devices, This process also contains a poly diffusion capacitor. The capacitor area is defined by poly which is the top plate. The capacitor dielectric is a process controlled silicon dioxide growth between the N+ diffusion bottom plate and the poly top plate. The terminals of the device are defined by contacts made to the poly and N+ implant. Aluminum is then used as the interconnect layers.

The poly-N+ capacitors are commonly used in MOS analog-to-digital converters as storage and ratiometric capacitors. The matching between capacitors is more important than their absolute value. It is this matching which limits the resolution in capacitive redistribution ADC's.

**TABLE 3. 1 Typical Device Process Parameters**

| PARAMETER         | Typical Value                     | Description                               |

|-------------------|-----------------------------------|-------------------------------------------|

| $V_{\mathrm{TP}}$ | -1.113 V                          | P-channel threshold voltage               |

| $\gamma_p$        | -0.0456 V <sup>1/2</sup>          | P-channel body effect coefficient         |

| C <sub>ox</sub>   | 1.73E-15 <i>F</i> /μ <sup>2</sup> | P-channel gate oxide capacitance          |

| $\beta_p$         | 2.15E-5 $A/V^2$                   | $\mu_p \cdot C_{ox}$                      |

| $\lambda_p$       | 0.371                             | Early voltage (SPICE Level 3)             |

| L <sub>D</sub>    | 0.07                              | P-channel Lateral Diffusion               |

| $V_{ m TN}$       | 0.808 V                           | N-channel threshold voltage               |

| $\gamma_n$        | 0.126 V <sup>1/2</sup>            | N-channel body effect coefficient         |

| C <sub>ox</sub>   | 1.73E-15 <i>F</i> /μ <sup>2</sup> | N-channel gate oxide capacitance          |

| $\beta_n$         | 7.3E-5 $A/V^2$                    | $\mu_n \cdot C_{ox}$                      |

| $\lambda_n$       | 0.0463                            | Early voltage (SPICE Level 3)             |

| L <sub>D</sub>    | 0.10                              | N-channel Lateral Diffusion               |

| C <sub>1,2</sub>  | 0.049E-15 F/μ <sup>2</sup>        | Metal1 to Metal 2 inter layer capacitance |

| C <sub>c</sub>    | 0.822E-15 F/μ <sup>2</sup>        | Poly-Diffusion Capacitor                  |

|                   |                                   |                                           |

|                   |                                   |                                           |

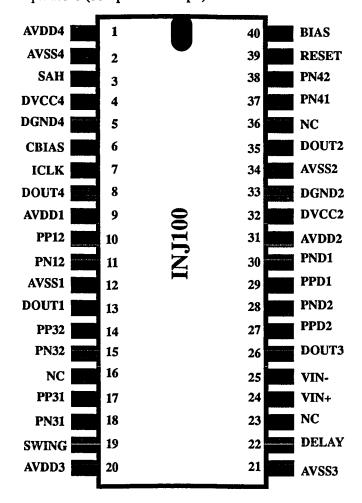

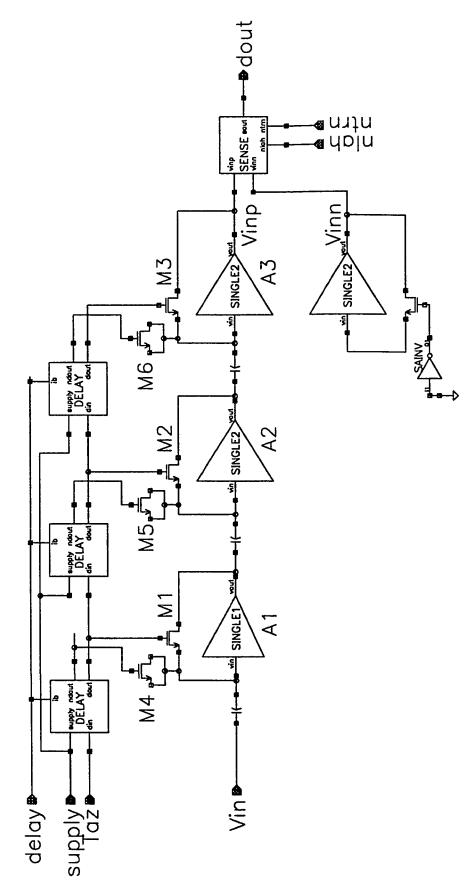

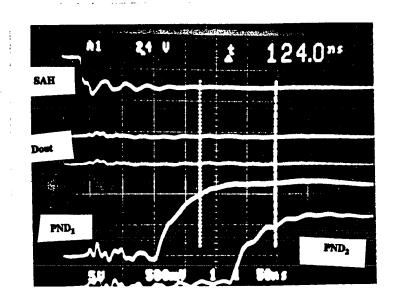

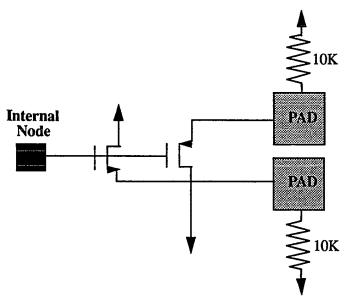

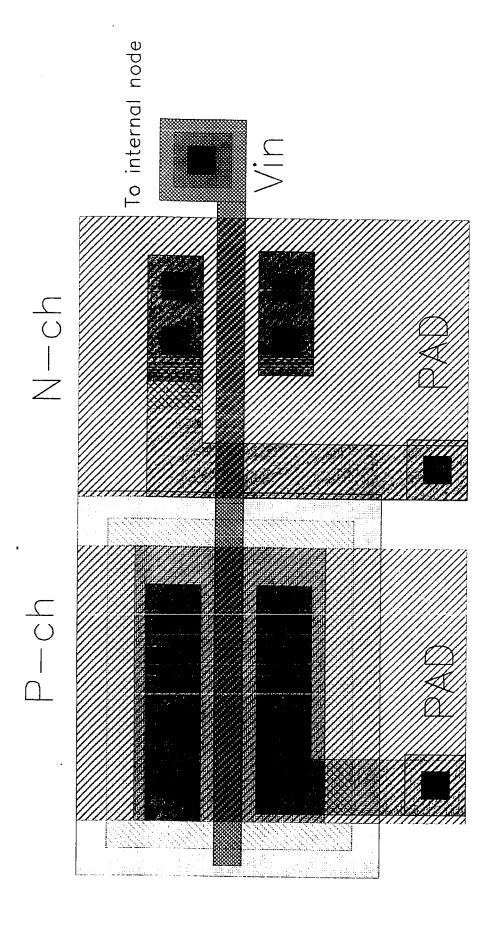

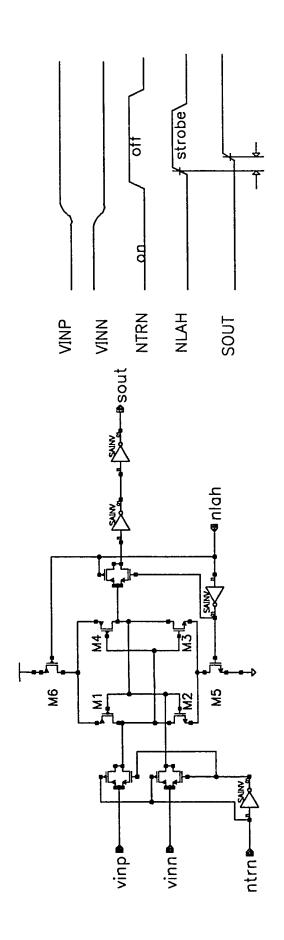

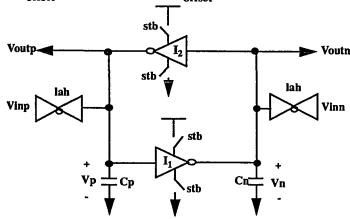

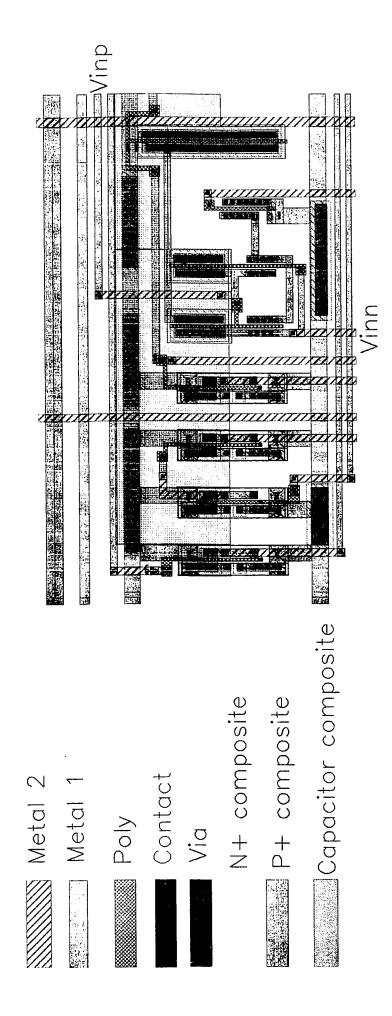

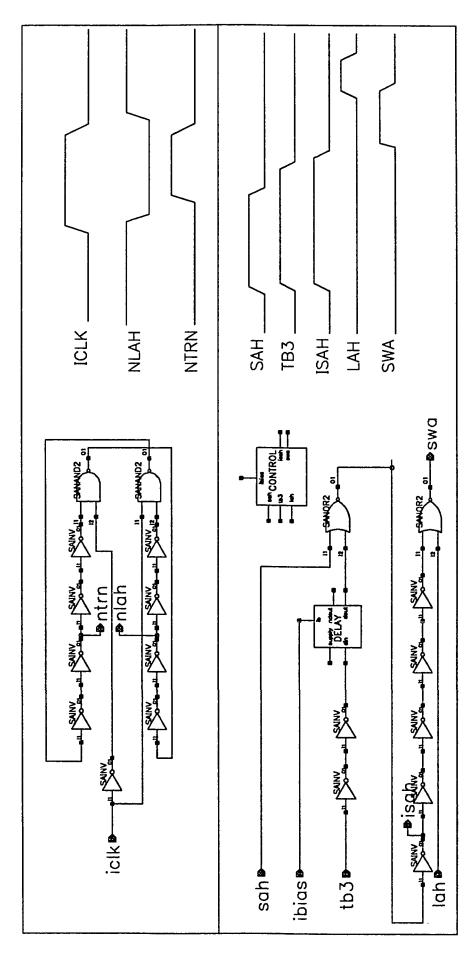

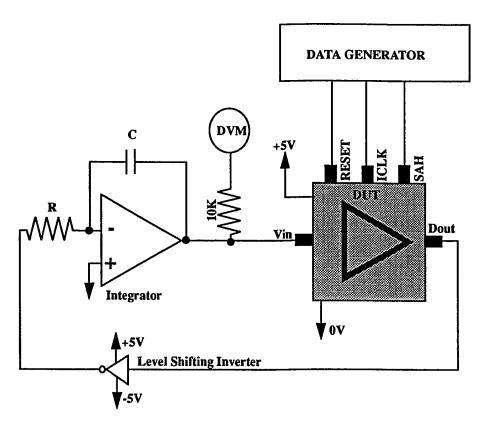

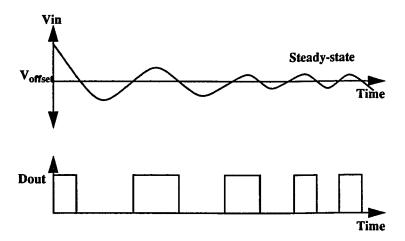

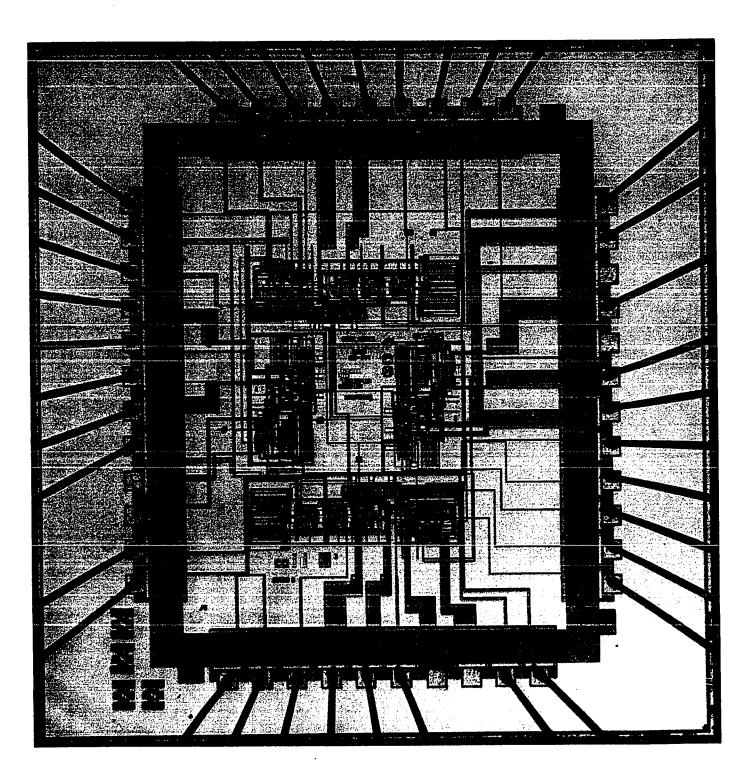

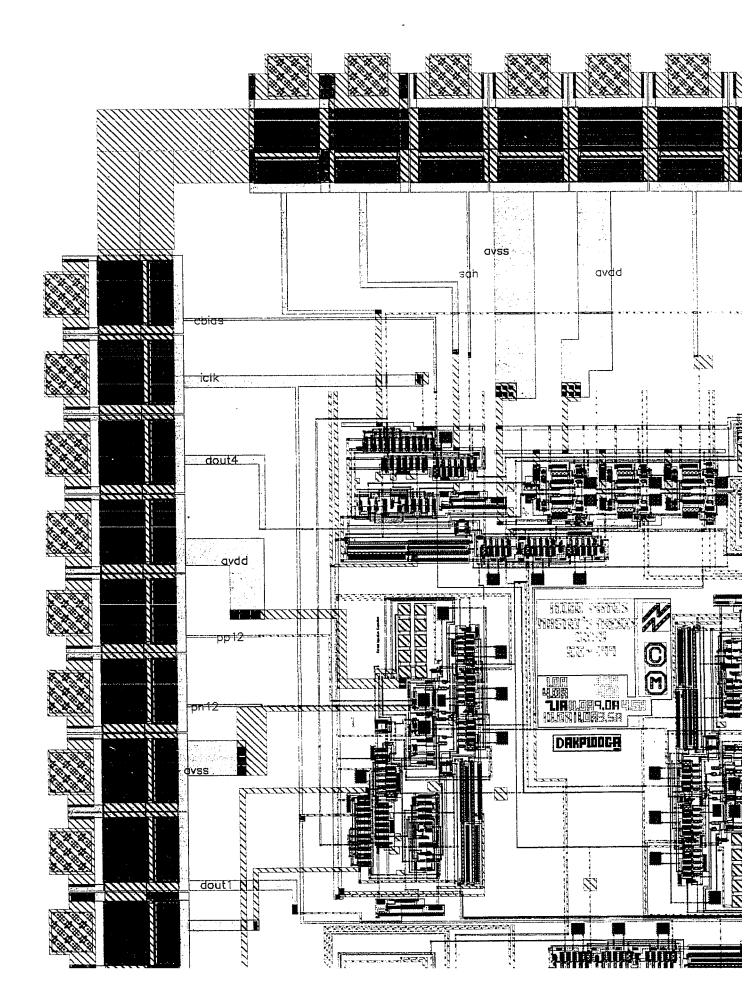

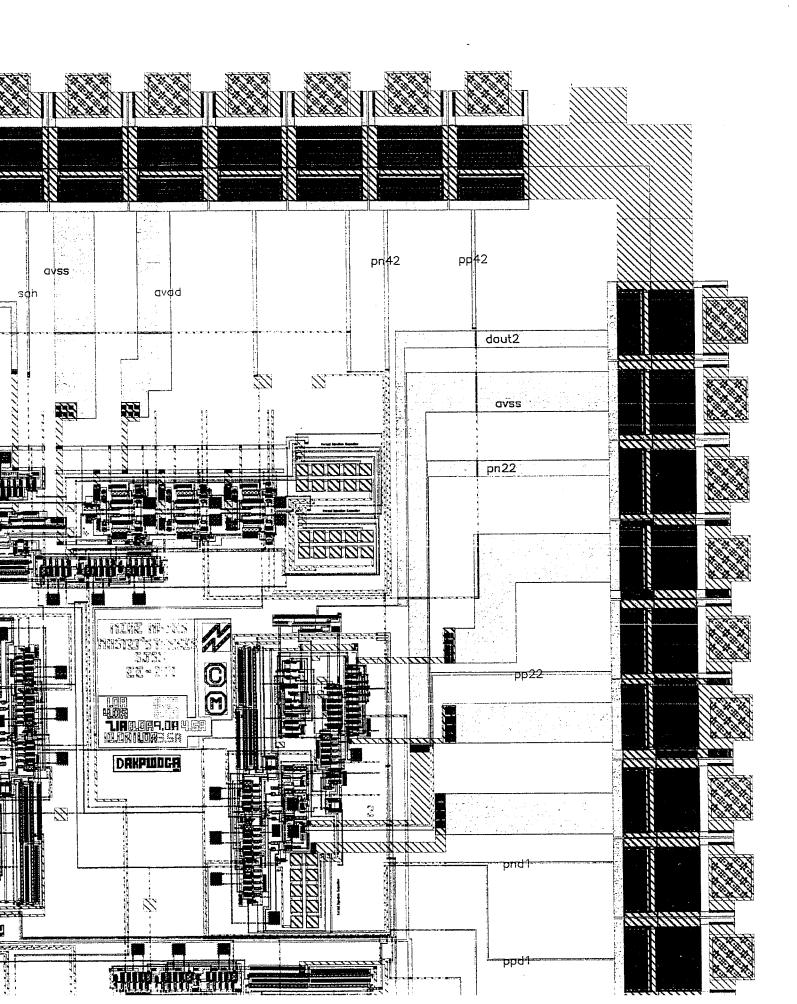

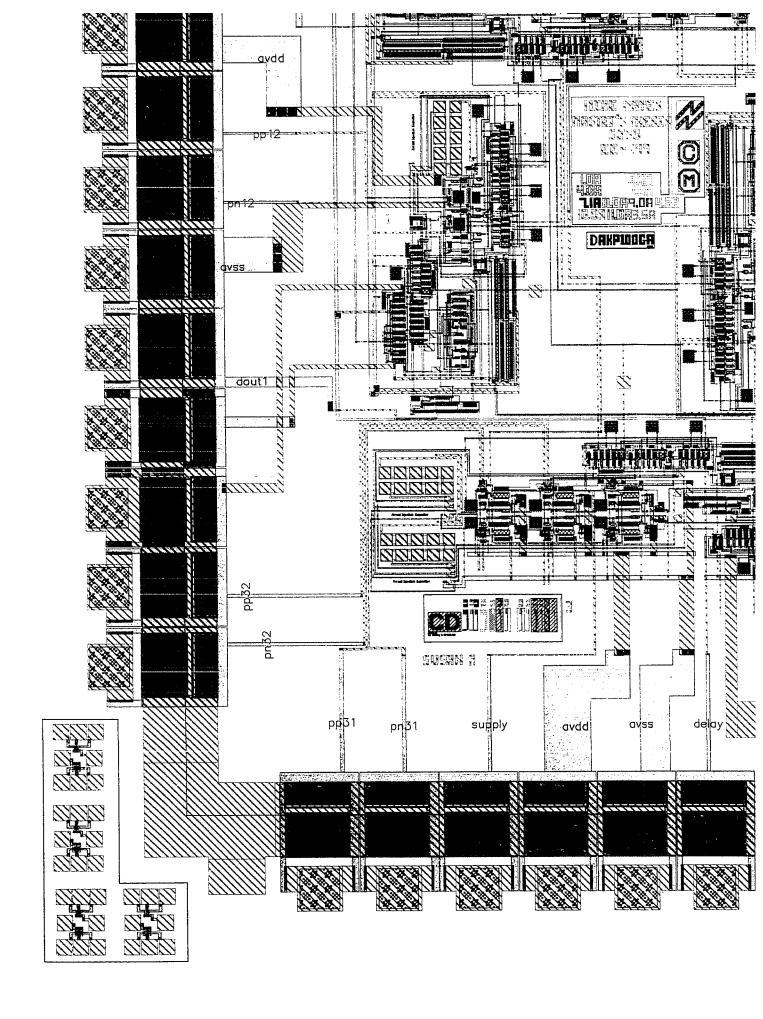

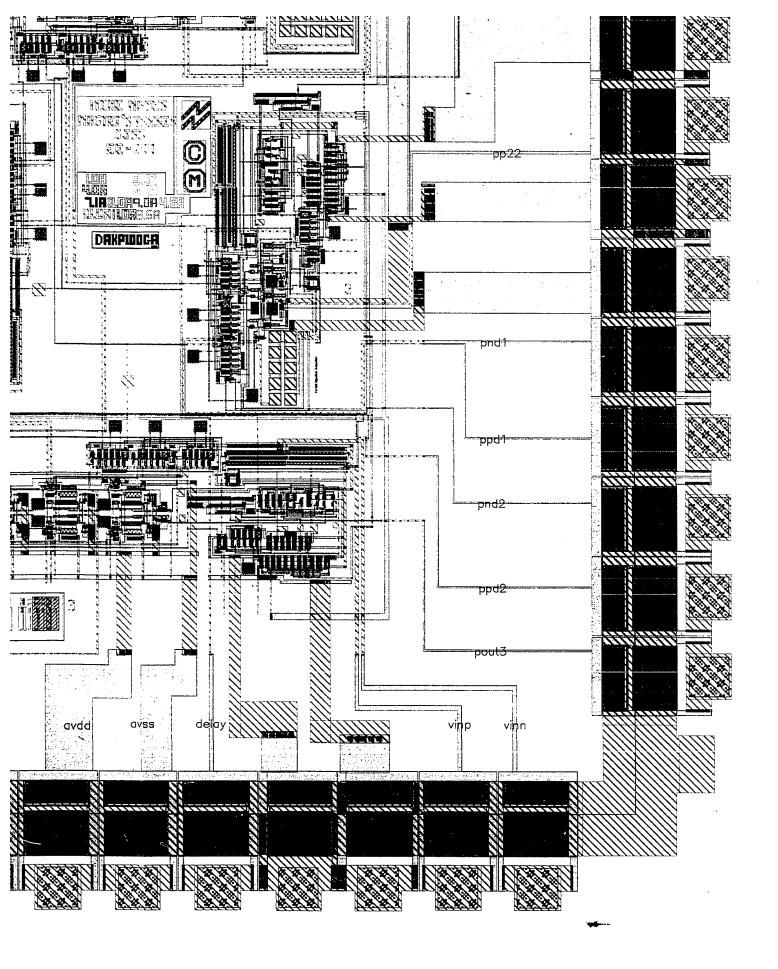

# 3.1.1 Test Chip Overview