# Marquette University e-Publications@Marquette

Master's Theses (2009 -)

Dissertations, Theses, and Professional Projects

# A Message-Passing, Thread-Migrating Operating System for a Non-Cache-Coherent Many-Core Architecture

Michael W. Ziwisky Marquette University

**Recommended** Citation

Ziwisky, Michael W., "A Message-Passing, Thread-Migrating Operating System for a Non-Cache-Coherent Many-Core Architecture" (2012). *Master's Theses* (2009 -). Paper 156. http://epublications.marquette.edu/theses\_open/156

# A MESSAGE-PASSING, THREAD-MIGRATING OPERATING SYSTEM FOR A NON-CACHE-COHERENT MANY-CORE ARCHITECTURE

by

Michael W. Ziwisky

A Thesis Submitted to the Faculty of the Graduate School, Marquette University, in Partial Fulfillment of the Requirements for the Degree of Master of Science

Milwaukee, Wisconsin

August 2012

# **ABSTRACT** A MESSAGE-PASSING, THREAD-MIGRATING OPERATING SYSTEM FOR A NON-CACHE-COHERENT MANY-CORE ARCHITECTURE

Michael W. Ziwisky

Marquette University, 2012

The difference between emerging many-core architectures and their multi-core predecessors goes beyond just the number of cores incorporated on a chip. Current technologies for maintaining cache coherency are not scalable beyond a few dozen cores, and a lack of coherency presents a new paradigm for software developers to work with. While shared memory multithreading has been a viable and popular programming technique for multi-cores, the distributed nature of many-cores is more amenable to a model of share-nothing, message-passing threads. This model places different demands on a many-core operating system, and this thesis aims to understand and accommodate those demands.

We introduce Xipx, a port of the lightweight Embedded Xinu operating system to the many-core Intel Single-chip Cloud Computer (SCC). The SCC is a 48-core x86 architecture that lacks cache coherency. It features a fast mesh network-on-chip (NoC) and on-die "message passing buffers" to facilitate message-passing communications between cores. Running as a separate instance per core, Xipx takes advantage of this hardware in its implementation of a message-passing device. The device multiplexes the message passing hardware, thereby allowing multiple concurrent threads to share the hardware without interfering with each other. Xipx also features a limited framework for transparent thread migration. This achievement required fundamental modifications to the kernel, including incorporation of a new type of thread. Additionally, a minimalistic framework for bare-metal development on the SCC has been produced as a pragmatic offshoot of the work on Xipx.

This thesis discusses the design and implementation of the many-core extensions described above. While Xipx serves as a foundation for continued research on many-core operating systems, test results show good performance from both message passing and thread migration suggesting that, as it stands, Xipx is an effective platform for exploration of many-core development at the application level as well.

#### ACKNOWLEDGMENTS

#### Michael W. Ziwisky

I simply could not have accomplished this feat without the incredible family, friends, and colleagues that I'm so lucky to have in my life. I am honored to express my sincerest gratitude to:

- My parents, Patricia and Ronald Ziwisky, for their love, encouragement, support, dependability, and money.

- My sister, Carrie Marino, for all of the above except money (though she'd have given that too if I had needed it).

- My extraordinary advisor, Dennis Brylow, for patient guidance, endless inspiration, money, and just being awesome.

- My committee members, George Corliss, Adam Welc, and Mike Johnson, for constructive questions and comments, and for guidance even beyond the scope of this thesis.

- My friend and labmate, Kyle Persohn, for his memory and organizational aptitude, which surely spared me an extra semester or two.

- My friend and lab squatter, Adam Mallen, for excellent conversations, some relevant to the thesis, some enlightening, but most just entertaining.

- My former advisor, Chung-Hoon Lee, for a wealth of guidance and wisdom in my first foray into academic research.

- My favorite hypergeek, Devin Townsend, for unbounded energy, inspiration, and entertainment.

- Evolution, for producing both the coffee bean and the man who discovered the coffee bean.

Thank you all – it's been an amazing time!

# TABLE OF CONTENTS

| ACKNOW    | /LEDGI | MENTS                                              | i  |

|-----------|--------|----------------------------------------------------|----|

| LIST OF ' | TABLE  | S                                                  | V  |

| LIST OF I | FIGURI | ES                                                 | vi |

| CHAPTE    | R      |                                                    |    |

| 1         | INTR   | ODUCTION                                           | 1  |

|           | 1.1    | Thesis Statement                                   | 1  |

|           | 1.2    | Problem Statement                                  | 1  |

|           | 1.3    | Contributions                                      | 4  |

|           | 1.4    | Thesis Organization                                | 5  |

| 2         | OVER   | RVIEW OF MANY-CORE COMPUTING                       | 7  |

|           | 2.1    | Origins of Many-Core Computers and Cache Coherency | 7  |

|           |        | 2.1.1 Cache Operation                              | 8  |

|           |        | 2.1.2 Chip Parallelism and Coherency               | 8  |

|           | 2.2    | Terminology: Processes and Threads                 | 10 |

|           | 2.3    | Sharing Data                                       | 14 |

|           |        | 2.3.1 Shared Memory                                | 15 |

|           |        | 2.3.2 Message Passing                              | 20 |

|           | 2.4    | Promises and Asynchronous Calls                    | 22 |

|           |        | 2.4.1 ActionScript Promises                        | 22 |

|           | 2.5    | Intel Single-Chip Cloud Computer                   | 25 |

|           |        | 2.5.1 Many-Core Alternatives                       | 29 |

|           | 2.6    | Summary of Many-Core Computing                     | 31 |

| 3         | RELA   | ATED WORK IN DISTRIBUTED ARCHITECTURES             | 33 |

|           | 3.1    | Operating Systems for Many-Core Architectures      | 33 |

|           | 3.2    | Inter-Core Communications                          | 38 |

|   |      | 3.2.1    | Message Passing                                | 38  |

|---|------|----------|------------------------------------------------|-----|

|   |      | 3.2.2    | Computation Migration                          | 42  |

|   | 3.3  | Summar   | ry of Related Work                             | 48  |

| 4 | XIPX | : A MAN  | Y-CORE OPERATING SYSTEM                        | 50  |

|   | 4.1  | Original | System                                         | 50  |

|   | 4.2  | Extensio | ons for Many-Core Support                      | 51  |

|   | 4.3  | Message  | Passing                                        | 53  |

|   |      | 4.3.1    | Message Passing with the MPB                   | 53  |

|   |      | 4.3.2    | MPB Driver                                     | 57  |

|   | 4.4  | Comput   | ation Migration                                | 63  |

|   |      | 4.4.1    | User Threads                                   | 63  |

|   |      | 4.4.2    | Virtual Memory, Protection, and System Calls   | 66  |

|   |      | 4.4.3    | Indirect Device References                     | 69  |

|   |      | 4.4.4    | User Thread Migration                          | 71  |

|   | 4.5  |          | chael and MikeTerm: A Bare-Metal Framework for | 83  |

|   |      | 4.5.1    | Platform Initialization                        | 84  |

|   |      | 4.5.2    | MikeTerm                                       | 88  |

|   |      | 4.5.3    | Build Environment and Dependencies             | 89  |

|   | 4.6  | Integrat | ion with RCCE                                  | 93  |

|   |      | 4.6.1    | Availability                                   | 94  |

| 5 | PERF | ORMAN    | CE ANALYSIS                                    | 95  |

|   | 5.1  | Message  | Passing                                        | 96  |

|   |      | 5.1.1    | Comparison to RCCE                             | 96  |

|   |      | 5.1.2    | SCC-Specific Device Optimization               | 101 |

|   | 5.2  | Thread   | Migration                                      | 102 |

| 6        | SUMMARY AND FUTURE WORK                                                         | 105 |

|----------|---------------------------------------------------------------------------------|-----|

|          | 6.1 Future Work                                                                 | 106 |

| BIBLIOGF | АРНҮ                                                                            | 108 |

| APPENDE  | X                                                                               |     |

| А        | IMPLEMENTATION DETAILS: VIRTUAL MEMORY, PRIVI-<br>LEGE LEVELS, AND SYSTEM CALLS | 116 |

| В        | SCC L2 CACHE FLUSH ROUTINE                                                      | 125 |

|          | B.1 The PLRU Replacement Policy                                                 | 126 |

|          | B.2 Analysis of the L2 Cache Behavior                                           | 128 |

|          | B.3 Effect of L1 Write-Backs                                                    | 129 |

|          | B.4 The Routine                                                                 | 130 |

## LIST OF TABLES

| 4.1 | Message header format.                  | 58 |

|-----|-----------------------------------------|----|

| 4.2 | System address sub-destination ID ports | 74 |

## LIST OF FIGURES

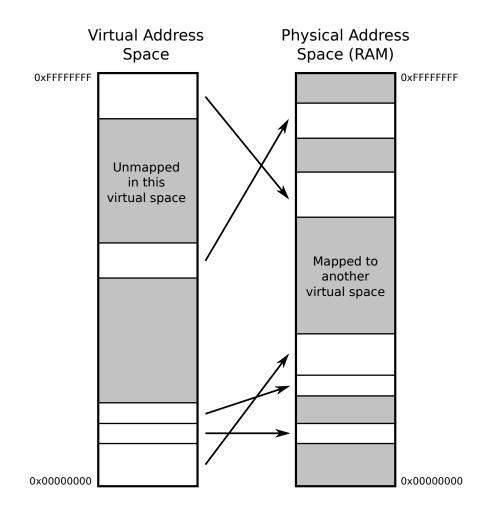

| 2.1  | Virtual memory management maps addresses in a virtual address space to physical addresses in main memory.      | 12  |

|------|----------------------------------------------------------------------------------------------------------------|-----|

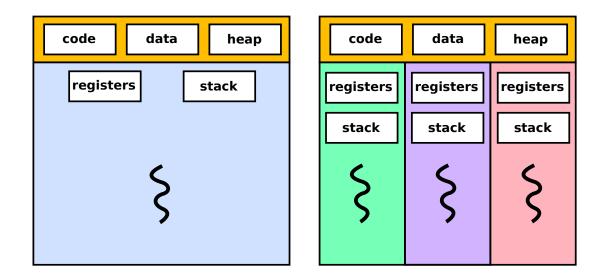

| 2.2  | A single-threaded process and a multi-threaded process                                                         | 13  |

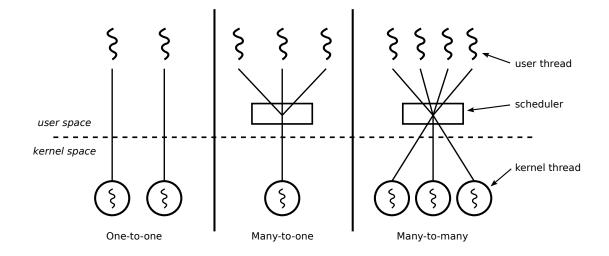

| 2.3  | Three ways to map user threads to kernel threads                                                               | 14  |

| 2.4  | A C program that is vulnerable to a race condition                                                             | 16  |

| 2.5  | The vulnerable C function implemented in x86 assembly                                                          | 16  |

| 2.6  | The definition of the test-and-set operation.                                                                  | 18  |

| 2.7  | Protecting a critical section with a test-and-set lock.                                                        | 19  |

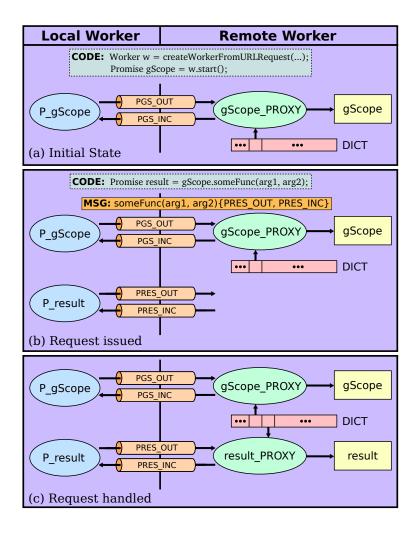

| 2.8  | Asynchronous remote method invocation                                                                          | 24  |

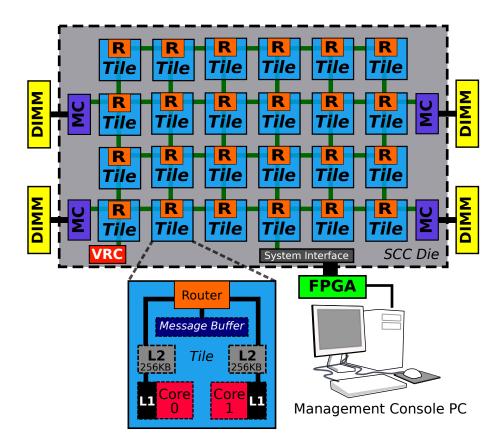

| 2.9  | Schematic diagram of the 48-core Intel SCC                                                                     | 26  |

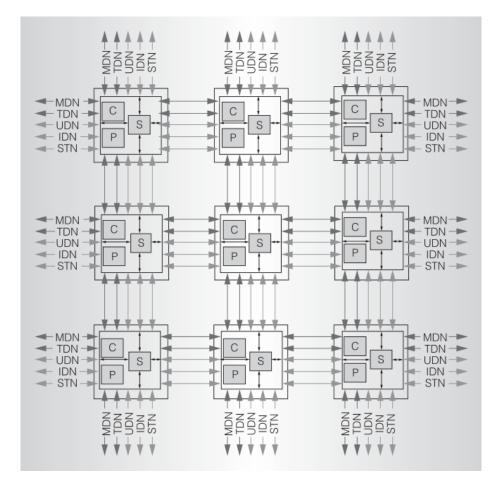

| 2.10 | Schematic 3 x 3 array of tiles connected by five separate networks on the TILE64 architecture.                 | 30  |

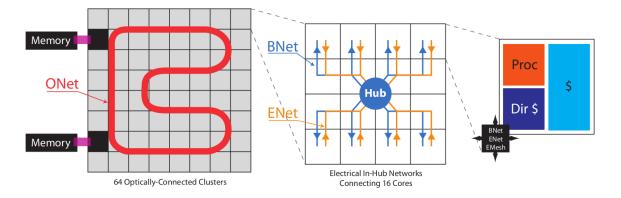

| 2.11 | Block diagram of the hierarchical on-chip network of the ATAC                                                  | 31  |

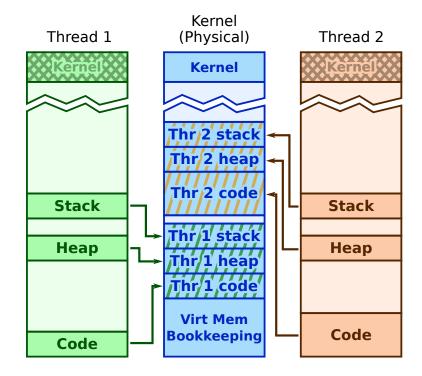

| 4.1  | User threads are isolated in virtual memory spaces                                                             | 67  |

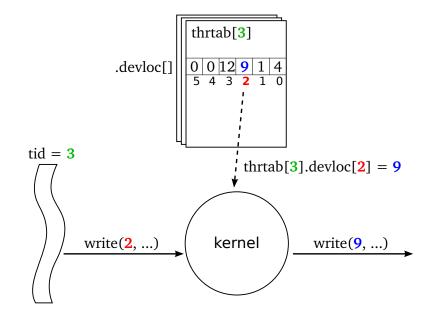

| 4.2  | The kernel translates thread-local device IDs to system device IDs before calling device functions.            | 70  |

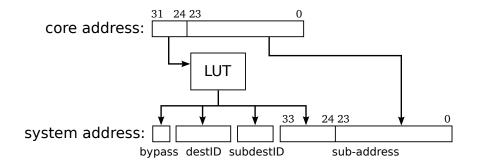

| 4.3  | Address translation on the SCC.                                                                                | 73  |

| 4.4  | Default LUT configuration for an SCC system with 32 GiB RAM                                                    | 75  |

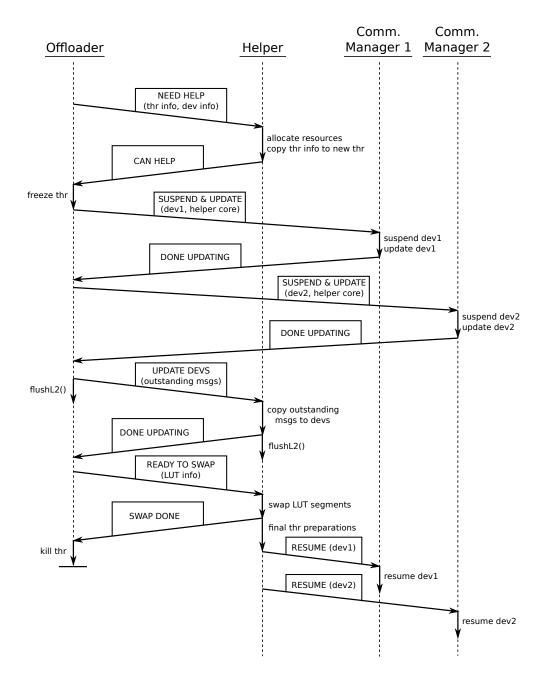

| 4.5  | Control and communication flow of the Xipx thread migration protocol                                           | 79  |

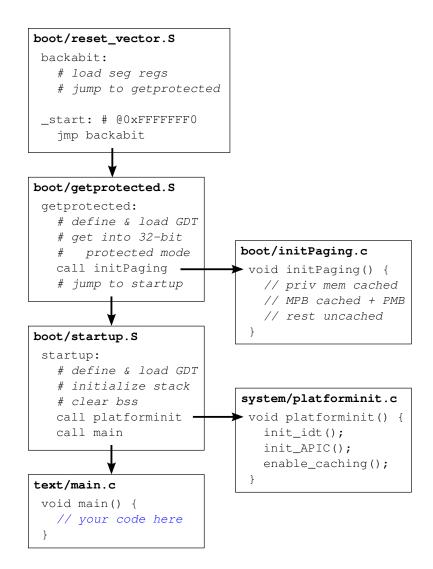

| 4.6  | Per-core initialization procedure of BareMichael                                                               | 85  |

| 4.7  | Sample output from MikeTerm                                                                                    | 89  |

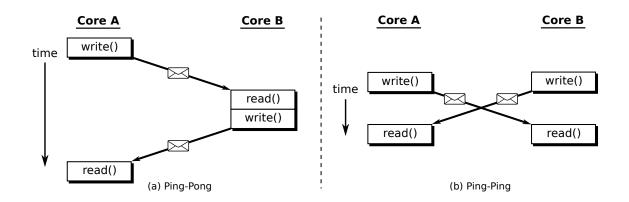

| 5.1  | Comparison of the communication patterns for (a) the ping-pong bench-<br>mark and (b) the ping-ping benchmark. | 97  |

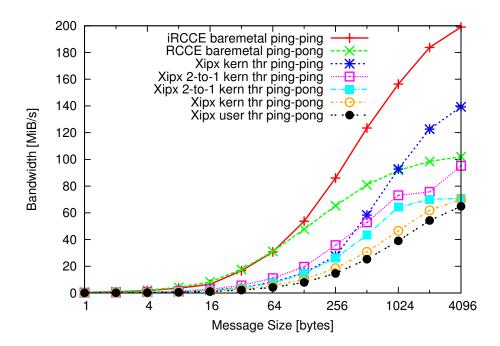

| 5.2  | Benchmark performance of the asynchronous Xipx MPB device                                                      | 99  |

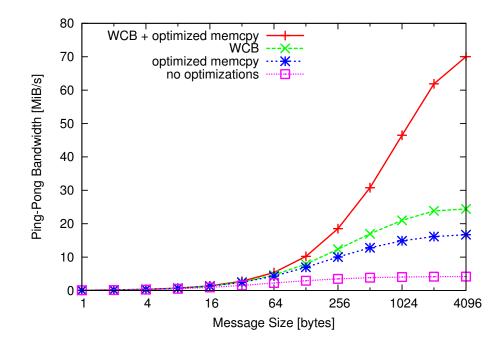

| 5.3  | The impact of SCC-specific optimizations on message-passing device bandwidth.                                  | 101 |

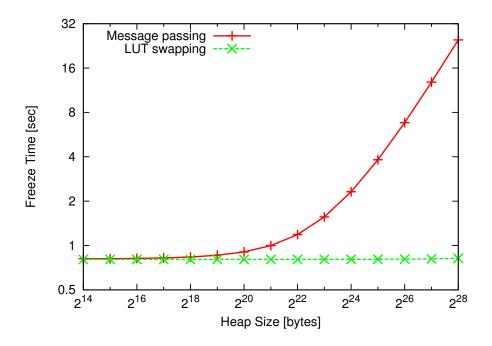

| 5.4  | Freeze time of migrating Xipx user threads.                                                                    | 103 |

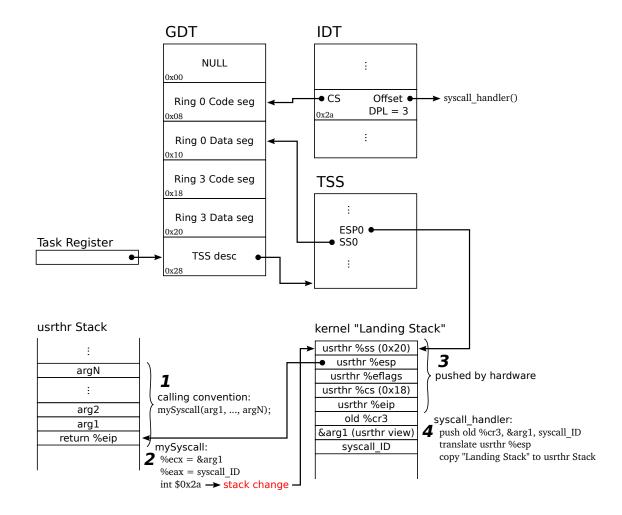

| A.1 | Xipx CPU configuration and system call handling on an x86 architecture.                                                                                                    | 116 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| A.2 | Code listing for the set of default interrupt handlers. $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                | 123 |

| A.3 | Code listing for a macro that an interrupt handler uses to ensure the CPU is in a flat-mapped view of memory and to undo the effects of an interrupt-induced stack change. | 124 |

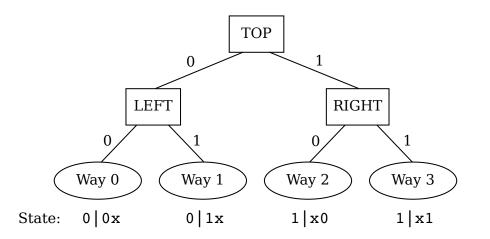

| B.1 | Binary decision tree for a PLRU cache replacement policy                                                                                                                   | 126 |

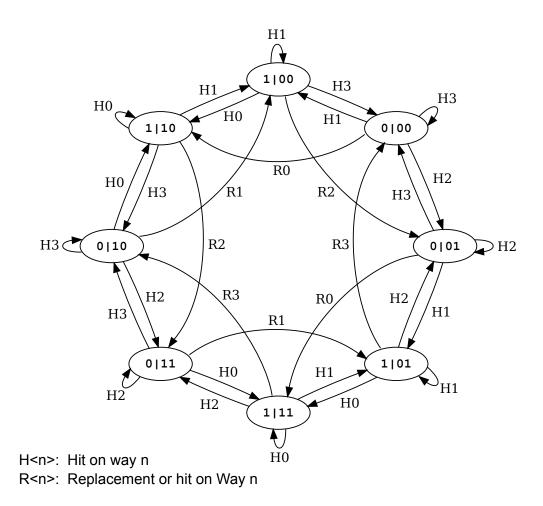

| B.2 | State machine for a PLRU cache replacement policy                                                                                                                          | 127 |

| B.3 | Software routine to flush the L2 cache                                                                                                                                     | 132 |

#### CHAPTER 1

#### Introduction

#### 1.1 Thesis Statement

Xipx, a port of the Embedded Xinu operating system to a distributed x86 architecture, is an effective host for exploring a computational model of concurrent, migratable, promise-based threads on the many-core Intel Single-chip Cloud Computer (SCC).

#### 1.2 Problem Statement

Multi-core processors are ubiquitous, and further scaling in parallelism has led to the emergence of *many-core* architectures. Many-core chips feature dozens of cores communicating with each other via a Network on Chip (NoC) technology. These architectures present a new domain in computation that is ripe for exploration. How does one take advantage of such parallelism? Traditional multi-core machines are cache-coherent, allowing concurrent lightweight threads to access resources in a shared memory space. In contrast, many-core architectures may be non-cache-coherent and are rather suited to executing isolated threads with message-passing communications. Additionally, like any distributed memory system, many-core chips can benefit from computation migration – the ability to transfer an in-execution unit of computation from one processing core to another. Among other advantages, migration enables active load balancing, which can enhance system throughput and power management.

As a foundational step toward experimentation on a many-core platform, this thesis introduces *Xipx*, a port of the Embedded Xinu operating system [1; 2] to the 48-core Intel Single-chip Cloud Computer (SCC) [3]. Xipx serves as a viable environment for supporting a scalable concurrent computation model centered around migratable message-passing threads – a model well-suited to the emerging class of many-core processors.

As evidence of present interest in such a computational model, Adobe developers currently are building concurrency constructs into the *Tamarin* ActionScript virtual machine [4; 5]. The concurrent computational model is based on share-nothing message-passing threads with "promise-based" inter-thread communications. In general, a *promise* is a placeholder for a value that will exist in the future [6]. In the context of Tamarin, it may also be thought of as a local reference to an object in another thread's address space. Behind the scenes, a promise interacts with an *object proxy* in the other address space, and these two objects communicate via a pair of message-passing channels. While these concurrency constructs may be new to the ActionScript language, JavaScript already supports the model with promise-based "web workers" [7]. With its fast message-passing router mesh, the SCC is a naturally advantageous architecture for this distributed computational model. Providing a suitable platform for experimental exploration of the model is a primary motivation for our work on Xipx.

The main problems addressed by our initial work on Xipx are how to support efficient message passing between threads and how to support migration of threads. Since message passing is such an elemental component of the many-core paradigm, there has been significant research focused on efficient message-passing implementations for the SCC platform (see Section 3.2.1). However, much of the current research focuses on message passing at the application level, which results in implementations that fully consume the SCC's message-passing hardware to execute just a single parallel application. An important goal for Xipx is to support concurrent execution of multiple parallel programs whose constituent threads may be distributed arbitrarily among the many cores. Our kernel therefore treats the SCC's message-passing hardware as a shared resource that must be managed at the system level.

As an enabling technology with numerous benefits for distributed systems (see Section 3.2.2), computation migration is another important topic in the realm of many-core architectures. An interesting feature of the SCC is that each core has the ability to remap dynamically the logical memory space of any of the cores to a large system-wide memory space. This behavior is exploited in Xipx to reduce dramatically the latency of inter-core data movement. As data transfers are typically the most expensive part of a migration procedure, realizing an efficient data transfer procedure helps to achieve very low "freeze times" for migrating threads.

Finally, of the numerous modern operating systems targeting many-core architectures (see Section 3.1), the current offerings with ports to the SCC are bloated and complex. The SCC port of Barrelfish is composed of over 450,000 lines of code, while SCC Linux version 1.4.1.2 tops 20,000,000 lines. Such overwhelming codebases make these kernels difficult to understand and modify. In contrast, the agile Xipx kernel comprises under 15,000 lines of code, while providing many of the same features as mainstream kernels such as multitasking with a preemptive priority scheduler, thread isolation and kernel protection, and an API for inter-thread communication. The flexibility offered by Xipx allows for relatively easy development of system-level constructs to exploit SCC-specific hardware features for ground-up support of our target computational model.

#### **1.3** Contributions

Although this work has been focused primarily on developing an environment to provide support for a particular model of computation, the fruits of our labor have resulted in a foundation that opens avenues for a wide range of research opportunities. Concretely, the work comprising this thesis makes the following contributions:

• Many-Core Port of Embedded Xinu. Xipx is the first port of the

lightweight and agile Embedded Xinu operating system to a platform in the emerging class of many-core architectures.

- Message-Passing Device Implementation. We present a scalable, efficient message-passing device for the Intel SCC that is able to service multiple concurrent threads per core.

- Messaging Performance Analysis. Experimental bandwidth measurements of our kernel-level message-passing device reveal its competitiveness with a less flexible user-level library alternative. Iterative measurements during the device's development quantify the performance benefits of SCC-specific caching mechanisms.

- Thread Migration Implementation. We present a simple thread migration protocol and two implementations. One is portable to any distributed system, while the other takes advantage of SCC-specific hardware for extremely low-latency inter-core data transfers.

- SCC "Bare-Metal" Development Framework. A bare-metal development framework has been created as a launching pad for operating-system-free development of applications targeting the Intel SCC.

#### 1.4 Thesis Organization

The remaining chapters of this thesis are organized as follows.

- Chapter 2 presents an overview of some history and background of many-core computing including cache coherency, sharing data, asynchronous semantics, and parallel architectures.

- Chapter 3 summarizes recent related work in many-core operating systems, message passing implementations, and computation migration.

- Chapter 4 describes the design and implementation of Xipx, a many-core port of the Embedded Xinu operating system, and *BareMichael*, a bare-metal programming framework for the Intel SCC architecture.

- Chapter 5 discloses the measured performance of message passing and thread migration implementations in Xipx.

- Chapter 6 summarizes the thesis and offers suggestions for future work on Xipx.

#### CHAPTER 2

#### **Overview of Many-Core Computing**

This chapter outlines the history and concepts surrounding many-core computing that are relevant to this thesis.

#### 2.1 Origins of Many-Core Computers and Cache Coherency

In the beginning, computers were simple. Early computers only had one central processing unit (CPU), no more than one single instruction could be executed in a single clock cycle, and accesses to random access memory (RAM) occurred at the same speed as executions of CPU instructions [8]. However, the advancement of CPU execution speeds far outpaced that of RAM speeds, and memory accesses soon became a major bottleneck for computers. To address this issue, manufacturers introduced a faster storage medium called *cache* memory [9]. Because it typically is located on the same die as the CPU, and therefore is an expensive commodity, cache memory generally comes in very limited quantity [10]. In contrast, RAM is comparatively plentiful. As such, cache is not a replacement for RAM, but a staging area between RAM and the CPU. It does not provide additional memory space, but redundant space, as it is used to hold copies of data from RAM for low-latency access from the CPU.

#### 2.1.1 Cache Operation

Cache memory has well-established operational principles and terminology [9, 10]. It is organized as a number of fixed-size segments that are called *lines* (one line may be 32 bytes in a typical system [11]), and data copies between RAM and cache occur one entire line at a time. The first time a processor wants to read some data from memory, it simultaneously loads the data into the CPU and loads the line-sized chunk of RAM containing that data into a cache line. If the caching policy is *write-back*, subsequent writes to that cached memory address only update the cache, and RAM will contain outdated data. This condition is recorded by setting a control bit which marks the cache line as *dirty*. Since the size of RAM is so much greater than that of cache, each cache line must be shared between many line-sized sections of RAM, and eventually, an occupied line will need to hold a different section of RAM. When this happens and the current line is dirty, the line gets written back to RAM before it is overwritten by the new section. If the line was not dirty, no write-back occurs. Alternatively, executing a write instruction on a CPU with a *write-through* cache causes RAM to be updated immediately to keep it synchronized with the cache.

#### 2.1.2 Chip Parallelism and Coherency

Advancing technologies in silicon fabrication throughout the late twentieth century enabled the creation of smaller and smaller transistors. With smaller size came faster switching speeds, and CPU manufacturers were able to realize performance gains by, among other tricks [12], continually increasing the clock frequencies of their chips [13]. However, a chip's power consumption scales linearly with its operating frequency, and heat dissipation becomes a major challenge with clocks operating beyond a few GHz. In response to this situation, a new paradigm has emerged for CPU design. Transistors continue to shrink, but rather than scaling up chip clock frequency, manufacturers now take advantage of the smaller devices by scaling up chip parallelism [14]. Clock speeds remain stagnant, but the number of computational cores on a single die is increasing. An N-core processor can execute N simultaneous instructions each clock cycle, leading to an N-fold performance increase under ideal circumstances.

This paradigm shift has some undesirable consequences. In particular, the combination of cache memory and multiple computing cores introduces some additional complexity into a system [15]. Each core in a multi-core system has its own independent cache and therefore has its own "idea" of what is in RAM. If two or more cores have each cached a copy of the same resource and one core modifies its copy, then all other cores with a copy must be informed of the change so they know not to operate on their stale idea of what that resource is. In a *cache coherent* multi-core system, hardware exists to ensure that when a resource in one cache is modified, the other caches with a copy of that resource know about it [10]. If one of those other cores needs to use the resource again, it will first update its copy to

maintain consistency with the core that modified it. The particular method and timing of this update is a policy decision made by the cache designer [9].

Cache coherency hardware frees the system programmer from much of the burden of dealing with cache, making its existence nearly transparent. Unfortunately, current hardware techniques for maintaining coherency have difficulty scaling beyond a handful of cores [16]. The accompanying hardware overhead, bus use, and power consumption of coherency hardware is significant. Therefore, as the number of cores on a chip increases and we move from the multi-core class to the *many-core* class, the difference between the two is not simply a matter of scale. Current many-core architectures either make no attempt to maintain coherency in hardware, or they use a network-on-chip (NoC) technology to do the job. In addition, inter-core communication and RAM accesses on a many-core typically are carried out over a NoC rather than via a traditional bus [3; 17; 18].

#### 2.2 Terminology: Processes and Threads

Having explored some important aspects of multicore hardware, we will now discuss relevant software concepts involved in parallel programming. In this section, we cover some terminology that typically is used in the literature [19].

A process is an instance of a computer program that is executing in a multiprocessing computer. This includes the code and static data of the written program along with stack and heap memory that are used during execution. With a technique called *virtual memory management*, modern CPUs have the ability to map system addresses to physical addresses arbitrarily (with a certain granularity). For example, if the CPU executes an instruction to read a value from some memory address, the virtual memory management hardware translates that address before going to RAM to request the read. This ability to remap memory addresses is used to isolate each process both from other processes in the system and from the operating system kernel itself. Therefore, each process exists in its own unique memory space. A schematic illustration of virtual memory mapping is seen in Figure 2.1.

Every process consists of one or more flows of execution, or *threads*. A thread is the thing that "does the work" in a process. It is a logical division of a process' work. A process may be composed of multiple threads, each of which can execute concurrently. ("Concurrently" means "at the same time," but it can refer both to threads executing truly in parallel on multiple cores, or to threads sequentially sharing time on a single core [20].) All threads in a particular process exist in the same memory space and therefore share program code and global data. However, each thread has its own state, which includes a stack and register values (including a stack pointer and an instruction pointer). A schematic diagram depicting the relationship of threads and processes is given in Figure 2.2. Shared memory space may be used to share data between concurrent threads, but this practice can lead to certain pitfalls as discussed in Section 2.3.1. Threads are considered to be

Figure 2.1: Virtual memory management maps addresses in a virtual address space to physical addresses in main memory (after [19]).

"lightweight" in comparison to "heavy" processes mainly because the cost of context switching between two threads is much lower than that of switching between two processes. The increased cost of a process switch comes from the need to change the virtual memory space [21]. While this alone makes the process switch more expensive than a thread switch, another costly side effect is that an entirely new memory space cannot use any cached data, so most memory accesses performed soon after the process switch have to go to RAM. On top of that, the translation lookaside buffer (TLB), which is a cache for the tables that are used to translate virtual addresses to physical addresses, contains useless data for the incoming process and has to be refilled just to be able to translate the new memory addresses. This results in even more accesses to RAM rather than cache memory.

Figure 2.2: A single-threaded process and a multi-threaded process (after [19]). All threads in a multi-threaded process share the same code, static data, and heap space, but each one has its own stack and registers.

Our description of threads so far is fairly general, but we must make a distinction between *kernel threads* and *user threads* [19]. A kernel thread is an operating system construct that is managed and scheduled by the kernel. A user thread is managed in user space without kernel support. Ultimately, a user thread must be associated with a kernel thread in order to be dispatched to a processor. There are three common ways in which user threads get mapped to kernel threads, as illustrated in Figure 2.3. The one-to-one model maps a each user thread to a

kernel thread. The many-to-one model incorporates a user-space scheduler that maps many user threads to a single kernel thread. The many-to-many model also involves a user-space scheduler, but the scheduler multiplexes many user threads to a smaller or equal number of kernel threads. Further discussion, including tradeoffs for each of the models, is given in [19] and [20].

Figure 2.3: Three ways to map user threads to kernel threads (after [19]).

#### 2.3 Sharing Data

This section describes some typical methods for sharing data between concurrent threads or processes.

#### 2.3.1 Shared Memory

Perhaps the most straightforward way for threads to share a resource is to have that resource located in an area of memory that is accessible by all of the threads that want to share it [22]. Since threads of a single process exist in the same memory space, any thread needing access to the shared resource would simply need to know its address. A read-only shared resource may be accessed by any thread at any time without consequence. However, if the resource is able to be modified by executing threads, some synchronization constructs are necessary to ensure that concurrent threads do not see an inconsistent view of the resource.

To see what can go wrong when modifying shared resources, consider spawning two threads of the simple function increment\_var() shown in Figure 2.4. One would expect the global variable var to equal 2 after the threads finished executing. However, looking in Figure 2.5 at the x86 assembly that could implement this C code, we see that the increment is actually split into three instructions: read the data from memory, add one, and write back to memory. Consider two threads executing this code concurrently with the following timing. Thread 1 executes line 5 and 6, then gets preempted. Upon preemption, the value of register eax is 1, and this value gets saved during the context switch. Thread 2 then executes the entire increment\_var function, reading var from memory, incrementing it to 1, then storing it as 1. Some time later, Thread 1 resumes execution at line 7, where it writes the value of register **eax**, which is 1, to **var** in memory.

```

int var = 0;

1

2

void increment_var(void);

3

4

void main()

5

{

6

spawn_thread(increment_var);

spawn_thread(increment_var);

7

8

9

void increment_var()

10

11

{

12

var++;

13

}

```

Figure 2.4: A C program that is vulnerable to a race condition.

```

1

var:

2

.word 0

3

4

increment_var:

var, %eax

\# load var to register eax

5

mov

$1, %eax

# increment the value of eax

6

add

7

\# store eax to var

%eax, var

mov

8

ret

```

Figure 2.5: The vulnerable C function implemented in x86 assembly.

We see that the particular timing of the execution of these two threads has led to an unexpected result. Although we intended for **var** to equal 2 in the end, it turned out to be 1. When the result of the execution of concurrent threads is unexpectedly dependent on the timing of the execution, the situation is referred to as a *race condition* [23]. Because the timing of concurrent thread execution is generally variable, race conditions can be difficult both to detect and to debug. However, once identified, a race condition can be remedied by ensuring execution of the multiple threads does not occur in a problematic sequence. We define a *critical section* of code as a section that accesses a shared resource that must not be concurrently accessed by multiple threads. In our simple example, the critical section is actually the whole body of increment\_var – line 12 in Figure 2.4, and lines 5–7 in Figure 2.5.

In a single-core environment, a critical section can be protected simply by disabling interrupts during its execution. This ensures that the thread will not be preempted during the critical section, and a race will not occur. However, this is insufficient in a multi-core environment, where multiple threads are executing simultaneously on separate cores. We need some additional means to enforce *mutual* exclusion – to ensure that no more than one core accesses the critical resource at a time.

Most modern architectures provide mechanisms that may be used to protect critical sections in a multi-core system. (These mechanisms may also be used in a single-core system when disabling interrupts is undesirable.) At the heart of these operations is the ability to update atomically a memory location. An *atomic* update is one that appears to happen instantaneously. I.e., the procedure of reading, modifying, and writing a location happens all together, uninterrupted, during which all other processors in the system are disallowed access to the location. A simple example of an atomic hardware primitive is a *test-and-set* instruction, the definition of which is given in Figure 2.6 [19]. Passing it a memory location, target, test\_and\_set() sets the value at that location to FALSE and returns its previous value. Note that this operation is written out in C code for illustration purposes only – the actual execution of the operation must be atomic in order for it to serve its purpose.

```

bool test_and_set(bool *target)

{

bool ret = *target;

*target = FALSE;

return ret;

}

```

Figure 2.6: The definition of the test-and-set operation [19].

If the value at target is initialized to TRUE, we see that the first time test\_and\_set() is called it returns TRUE and sets target to FALSE. Any subsequent calls will return FALSE until target is reset to TRUE (which can be done by a normal, non-atomic write). A test-and-set therefore may be used to protect a critical section as seen in Figure 2.7. The critical section is not entered until a call to test\_and\_set(&lock) returns TRUE, at which time we say we've acquired the lock. Upon exiting the critical section, we release the lock by resetting lock to TRUE. Because of its atomic operation, proper use of test\_and\_set() guarantees that only one caller acquires the lock at any time.

```

bool lock = TRUE;

void my_function()

{

while (!test_and_set(&lock))

; /* loop until lock is acquired */

... /* critical section */

lock = TRUE; /* release the lock */

}

```

Figure 2.7: Protecting a critical section with a test-and-set lock.

This issue of ensuring mutual exclusion is a separate problem from that of cache coherency. Coherency generally is taken care of automatically by the hardware, but it is necessarily the programmer's responsibility to avoid race conditions in the software.

While using shared memory for inter-thread communication may seem straightforward, it is prone to pitfalls, such as race conditions, which may be difficult to detect. In the following section, we explore an alternative.

#### 2.3.2 Message Passing

Message passing is fundamentally different from shared memory [22]. Conceptually, each actor in the system owns a mailbox. (By "actor," we mean any entity that can affect memory, including computational cores and memory-mapped I/O hardware, but also including the abstractions of processes, threads, and worker threads.) These mailboxes can be thought of as real-world mailboxes – those that can hold many letters from many different senders. When one actor wants to communicate with another, it sends a message to the other's mailbox. While any actor can send a message to any mailbox, a mailbox can only be opened and read from by its owner. In this way, memory locations are not "shared" because none are ever accessible to more than one actor. Rather, when one actor passes a message to another, the message data is copied directly into the private memory space of the recipient.

Because it does not require a shared memory space, message passing is well suited both for inter-process communication and for communication between worker threads. Abandoning a shared memory model also eliminates the possibility of race conditions since any object may only be accessed by a single thread. Furthermore, when using message passing for communication in a multi-core environment, cache coherency hardware is unnecessary because all memory locations are private to a single core. In distributed systems, in which separate computational cores have no means to share memory, message passing is the only option for data sharing.

Some message passing APIs offer both synchronous and asynchronous send and receive functions. Beyond just data sharing, synchronous message passing can be used for synchronization of actors. This is particularly useful in an environment where both message-passing and shared memory are in use. For example, before accessing some shared resource, one actor may wait to receive a message from another which indicates that it is safe to do so.

When implementing a message passing system, the properties of the actual message channels must be taken into account. For example, it is generally required that messages sent from one point to another must arrive at their destination in the order in which they were sent. If delivery order is not guaranteed by the hardware, then additional software constructs are needed to resolve the issue. Other channel properties to consider are reliability (can one count on a sent message to always arrive at its destination) and data integrity (is there a chance that a sent message becomes corrupted before it is received).

Further discussion of message passing implementation considerations may be found in Section 4.3.

#### 2.4 Promises and Asynchronous Calls

It is generally agreed upon [19; 24; 25] that concurrent programs are more difficult to write and to understand than sequential programs. However, concurrent programming is necessary to take advantage of the increasing parallelism of computer architectures. Thus, there is a demand for language constructs that make concurrent programs easy to understand and reason about. Asynchronous calls are an example of a high-level abstraction that help make a concurrent program look more like a sequential one from the programmer's perspective. When a task makes an asynchronous function call, it immediately receives a returned object, called a *promise*, and continues executing. At the same time, the called function may execute in parallel as an independent task. In general, a promise is a placeholder for a value that will exist in the future [6]. The promise in this case is a placeholder for the return value that is being calculated by the called function. Sometime later in its execution, when the caller needs the return value itself, it uses the promise to retrieve it.

#### 2.4.1 ActionScript Promises

Adobe researchers recently began incorporating concurrency constructs into the ActionScript language and building support for these new constructs into the open source Tamarin virtual machine [5]. These extensions follow a model of computation that is based upon concurrent worker threads interacting with each other via promises. An initial worker thread – which we will refer to as the local worker – can create another worker thread – a remote worker – from a file containing a worker description. The local worker invokes the **start()** function on the remote worker, which returns a promise representing the remote worker's global scope. The global scope promise gives the local worker access to all globally exposed methods and members of the remote worker.

When a local worker invokes a method call in a remote worker, a promise is always returned, and the local worker continues working immediately. The remote worker exists outside of the local worker's memory space, and therefore an ActionScript promise is a handle to an object in an external memory space. Hidden from the programmer is the fact that the promise interacts, via a pair of one-way message passing channels, with an *object proxy* in the external memory space. The object proxy interacts with the actual object and services requests from the promise to act on or retrieve results from the object. In case the remote method call results in an uncaught exception, the exception is propagated to the caller where it is re-thrown when the caller attempts to retrieve the result of the original call. A graphical illustration of an ActionScript asynchronous remote method invocation is shown in Figure 2.8.

Promise results may be retrieved by the local worker either synchronously, in which case the local worker sends a request to the remote worker and blocks until

Figure 2.8: Asynchronous remote method invocation (from [5]). (a) Initially, the local worker creates and starts a remote worker; as a result, the local worker holds a promise representing the remote worker's global scope. (b) The local worker creates a new promise which implicitly initializes a pair of message-passing channels ('PRES\_OUT and 'PRES\_INC'). Then the local worker issues a request to invoke the someFunc() function of the remote worker. Arguments ('arg1' and 'arg2') are passed explicitly while channel information is passed implicitly. (c) Upon completing the requested computation, the remote worker creates an object proxy for the result and links the proxy to the established communication channels.

the result is received, or asynchronously in a slightly more complex fashion. Before issuing an asynchronous result request, a sender creates a local callback function – a promise resolution handler – and an object proxy for the callback. The sender then issues the asynchronous result request on the local promise, which implicitly passes to the remote object proxy the channel information for its callback object proxy. When the remote worker has the result ready, it creates and links a promise with the local callback object proxy and uses it to invoke the callback function. The callback resolves the result of the original promise, and result retrieval is complete.

The semantics of promises allows ActionScript worker threads to be location transparent; i.e., the source code looks the same no matter where workers are physically executing, whether on a single local processor, on a hardware accelerator, or on distributed resources accessed over a network. Thus there is the potential for a single source code to take advantage dynamically of whatever computational resources happen to be available at runtime.

#### 2.5 Intel Single-Chip Cloud Computer

The Single-Chip Cloud Computer (SCC) experimental processor is a "concept vehicle" created by Intel Labs as a platform for many-core software research [3; 26]. It features 48 *GaussLake* processing cores based on the Pentium P54C and a 256 Gb/s bisection bandwidth network-on-chip (NoC) routing mesh. The chip is organized into 24 tiles, each of which contains two cores, a router, and 16 kB of shared memory that is accessible to all tiles via the NoC. This fast, on-chip memory is referred to as the "message-passing buffer" (MPB). A schematic representation of the SCC is seen in Figure 2.9.

Figure 2.9: Schematic diagram of the 48-core Intel SCC [26].

To reduce hardware overhead and power consumption and to achieve high scalability, cache coherency hardware for shared memory is nonexistent in the SCC. Without coherency, shared RAM is not a viable method for high-performance data sharing between cores. However, access latencies for MPB memory are much lower than they are for RAM, and the MPB therefore offers relatively high performance without caching. In lieu of coherency hardware, the SCC provides the NoC and MPBs as a means to implement an efficient message-passing system for inter-core communications.

The SCC die includes four memory controllers to interface with RAM; a

voltage regulator controller (VRC) capable of scaling chip voltage levels at a granularity of four tiles per domain; and a system interface that interacts, through a field programmable gate array, with a management console PC (MCPC), which is a computer that serves as the user's interface to the SCC. Each of these on-die components is connected to the mesh network and therefore is potentially addressable by any of the 48 cores.

In addition to the cores and NoC hardware, each SCC tile contains a set of configuration registers. These registers include:

- LOCK0 & LOCK1 a pair of test-and-set locks,

- GLCFG0 & GLCFG1 a pair of core configuration registers,

- GCBCFG a global clock configuration register,

- MYTILEID a read-only unique identifier, and

- LUT0 & LUT1 a pair of system address lookup tables.

The LOCK0/1 registers are atomic test-and-set locks that can be used to enforce mutual exclusion. These are particularly useful as a tool to prevent race conditions when accessing MPBs for a message-passing implementation.

The GLCFG0/1 registers each have two bits connected to the LINT0 and LINT1 pins of the local advanced programmable interrupt controller (APIC) for their corresponding cores. Each core has access to these bits for all of the cores in the system and therefore can trigger a hardware interrupt on any core. The GCBCFG register allows a programmer to set the clock frequency of the local tile and of the local router. While all routers in the system must have the same clock to prevent data loss and corruption in the NoC, tiles are able to be clocked heterogeneously. Together with the voltage scaling capabilities provided by the VRC, this frequency scaling allows for fine-grained power management across the chip. The GCBCFG register also has a bit linked to each of the cores' reset pins. Offering the capability to reset discrete cores allows for even greater control over power consumption and facilitates recovery from faults in individual cores.

The MYTILEID register contains a unique identifier for the local tile in the form of its (x,y) location in the  $6\times4$  grid of the chip. The value read from this register differs by a single bit depending on which of the two cores on the tile reads it, allowing each core to identify itself. The most common way to program the SCC is to load the same single image into the private memory of all of the cores. For such homogeneous image configurations, the MYTILEID register can be used to differentiate code paths for different cores via conditional jumps.

On top of the standard segmentation and paging features of a typical P54C core, the SCC has an additional layer of address translation that maps a core's 32-bit physical address into a 46-bit system address. A system address includes the identification of a router and one of the router's ports, and it can refer to RAM, MPBs, configuration registers, the VRC, or the system interface. Each core's LUT register contains 256 entries, one for each of the 16 MiB segments that make up a

core's 4 GiB physical address space. Each entry is able to point to any system address including the LUT itself, which enables dynamic system memory mapping. Exploitation of this ability, along with further details of the LUT and system addresses, is discussed in Section 4.4.4.

#### 2.5.1 Many-Core Alternatives

The SCC is the architecture upon which this thesis work was developed. However, it is worth mentioning a few of its contemporaries to compare the features of the platforms and illustrate some viable alternatives in design.

The Tilera TILE64 is a commercially available processor with 64 cores and multiple independent mesh NoCs [28]. Whereas the SCC has a single mesh for handling traffic generated from events such as memory accesses, I/O accesses, data streaming, and servicing cache misses, the TILE64 distinguishes between these different events by using a different mesh for each one. Five on-chip meshes – called the user dynamic network, I/O dynamic network, static network, memory dynamic network, and tile dynamic network – each serve a particular purpose [27]. A schematic representation of these networks is shown in Figure 2.10.

Tilera has released the TILEPro64 as the successor to the TILE64. Unlike the TILE64 and the SCC, the TILEPro64 maintains cache coherency between cores. The messaging traffic generated by the coherency protocol is significant enough to

Figure 2.10: Schematic  $3 \ge 3$  array of tiles connected by five separate networks on the TILE64 architecture (from [27]).

cause Tilera to dedicate an entire additional mesh network solely to this purpose [17].

Another cache-coherent design, the MIT ATAC is an unrealized architecture focused in part on how to provide inter-core communication when the processor scales beyond 1000 cores [29]. As illustrated in Figure 2.11, it is a tiled architecture featuring a hierarchical interconnection network. The chip is divided into clusters of cores. Each cluster consists of a hub connecting several cores in a star configuration,

Figure 2.11: Block diagram of the hierarchical on-chip network of the ATAC (from [29]).

and the clusters are linked together by connecting all of the hubs in a ring topology via an optical waveguide medium. While the ATAC architecture provides cache coherency, it does so with a reliance upon this chip-scale optical communication network, an unproven technology that has yet to be successfully mass produced.

## 2.6 Summary of Many-Core Computing

The evolution of semiconductor fabrication processes has driven computer architectures from single-core processors to cache-coherent multi-core systems, and it is now leading to non-cache-coherent many-core platforms. While some modern architectures with dozens of cores are able to maintain coherency, the technologies used to do so are not scalable. Therefore as chips scale further in parallelism, it is important to figure out how non-coherent architectures can be leveraged by system software for performance gains. Since the absence of coherency precludes efficient shared memory processing, distributed memory paradigms, such as message-passing communications, offer promising models for the many-core era. The following chapter discusses recent work focused on distributed architectures, with a particular emphasis on work related to the Intel SCC.

#### CHAPTER 3

#### **Related Work in Distributed Architectures**

#### 3.1 Operating Systems for Many-Core Architectures

There are three general approaches to designing an operating system for non-cache-coherent many-core architectures. The first is to manage coherency in software so that traditional symmetric multi-processing (SMP) paradigms may be used, such as employing a shared-memory kernel with data structures protected by locks. The second approach is to abandon shared memory, make inter-core communications strictly explicit, and design the system around this new paradigm. While Boyd-Wickizer et al. argue that the latter is not necessary with currently available hardware [30], they acknowledge that the status quo design would lack performance in a future consisting of processors without high-performance cache coherency. The third design approach is to view a many-core chip as a distributed system and run a separate OS instance on each core. Insights from the fields of networking and traditional distributed systems may benefit such on-chip clusters. While Xipx fits into this last category, this chapter summarizes work that has been done in each of the three domains.

Sobania et al. analyze the aspects of the SCC that fall short of the *Intel MultiProcessor specification* [31], an accepted standard for SMP hardware support in x86 systems [32]. Two such deficiencies are the architecture's lack of cache coherency and inability to transfer an interrupt vector number as a part of an inter-processor interrupt (IPI) signal. The authors introduce *RockyVisor*, a distributed hypervisor that emulates the necessary support in a virtual layer. RockyVisor could be implemented as either a Type 1 (running directly on the physical hardware) or a Type 2 (running as a process within a host operating system) hypervisor [33]. A Type 2 prototype implementation is still in early stages of development, so it remains to be seen how effective this solution is for distributed architectures.

Lankes et al. are developing *MetalSVM*, a hypervisor that is based on a shared virtual memory (SVM) management system [34]. The authors are implementing MetalSVM as a Type 1 hypervisor and therefore have the freedom to interact directly with the SCC hardware. As a result, much of their published work discusses the low-level mechanisms, such as synchronization [35] and inter-core communications [36], on which the hypervisor will depend. Again, the hypervisor itself is not yet developed to a level that reveals the efficacy of the solution. Our Xipx OS disallows memory sharing between cores and, therefore, has no need for a coherency-enforcing hypervisor layer.

Rather than trying to cast many-core architectures into the cache-coherent mold of their multi-core ancestors, some choose to rethink the mold. Allowing many individual cores to operate within isolated memory spaces begets the likeness of a distributed system, not a unified system with multiple computing elements. While the latter is traditionally managed by a "single system image" (SSI) kernel, the former demands a new model. Baumann et al. introduce the term "multikernel" to describe their kernel model that is tailored to distributed systems [37]. The three guiding design principles of the model are: making all inter-core communications explicit (via message passing), making OS structure hardware-neutral, and replicating rather than sharing system state. The authors realize a multikernel with their implementation of the *Barrelfish* OS. Originally written for x86-64 multi-core systems, Barrelfish also has been ported to the SCC [38]. While the OS assumes a "shared nothing" paradigm for kernel functionality, it does not enforce the same for applications. Because many modern parallel programs are based on a model of many concurrent threads operating in a shared memory space, Barrelfish implements a shared virtual address space over the multikernel.

Also taking a non-traditional approach, the Factored Operating System, or fos [39], is designed specifically for multi-core, many-core, and cloud computing systems, but it does not fit the model of a multikernel. The distinguishing design philosophy of fos is to employ space sharing rather than time sharing. Instead of having user applications compete with kernel services for CPU time, the two are executed on separate, dedicated cores. The kernel itself is similarly factored with different cores hosting different services such as page allocation, process management, and file serving. Space sharing offers a reduction or elimination of context switching, which in turn enhances cache locality and results in a more efficient use of implicit resources such as caches and TLBs. To ensure scalability and manage protection, for uses message passing for interactions between cores. The for design depends upon the existence of systems of sufficiently large scale to justify complete dedication of cores to individual services, and it depends upon a sufficiently low-latency messaging system to ensure that the benefits of cache locality outweigh the overhead of inter-core communications [40]. In contrast, Xipx still runs all OS services along with applications on each core and therefore employs time sharing as much as a traditional OS.

Finally, Intel provides a modern port of the Linux kernel (version 3.1) which, running on the SCC as a separate instance per core, is able to load and launch user applications [41]. SCC Linux is neither a traditional SSI, because it runs as a separate instance per core, nor a multikernel, because the kernel instances are fully separated without global state. Rather, SCC Linux treats the cores of the chip like nodes in a cluster. Parallelism is recognized at the application level, not at the kernel level. RockyVisor uses SCC Linux as its host OS. Xipx is similar to SCC Linux as it is also a distributed OS with a separate kernel instance running per core. Lacking in SCC Linux is built-in support for process migration, an important feature of our Xipx OS.

As the SCC is strictly a prototype platform, it lacks certain hardware that is typically found in a multi-core computer and expected by the Linux kernel, such as a Basic Input Output System (BIOS). Therefore, SCC Linux entails some non-standard kernel modifications to work with the unique hardware. Intel's original approach to adapt the kernel involved, for example, compiling it with hard-coded values for certain parameters that otherwise would be filled through queries to the BIOS. Non-Intel researchers have since proposed some more portable solutions, including BIOS emulation [42], which are incorporated into later versions of the OS.

Another consideration for many-core OS design is overall system efficiency. While many researchers in the field focus on keeping many cores actively performing useful work in parallel, few focus on the efficiency of each individual core. Vasudevan et al. advise us not to forget about exploitable single instruction, multiple data (SIMD) [43] parallelism, such as SSE vector instructions and GPU resources, in the MIMD world of many-cores [44]. While their Vector Operating System (VOS) design is certainly able to increase performance by eliminating redundancy in parallel operations, it leaves some significant open questions. Should OS designers break from long-standing system call interfaces and force application developers to specify work in terms of vectors of resources? If not, how can the OS recognize and exploit vectorizable operations? As the SCC lacks vector processing hardware, the questions of whether and how to increase SIMD parallelism in Xipx are moot points.

#### 3.2 Inter-Core Communications

The most common form of inter-core communication in a distributed system is message passing. However, computation migration is essentially another form of communication in which the data transferred between cores represent a unit of computation. This section surveys work done in each of these realms.

#### 3.2.1 Message Passing

Message passing is a form of inter-process communication that has roots in the early days of distributed computing [45; 46]. It is useful in systems that consist of communicating processes that reside in disjointed memory spaces. The Intel SCC features a distributed memory layout with hardware to support low-latency inter-core message passing, and there are several researchers investigating how to best take advantage of that hardware. While section 2.3.2 discusses the paradigm in detail, this section discusses some of the research that has been focused on message passing both in general and in the context of the Intel SCC.

The Message Passing Interface (MPI) standard is a library specification for message passing [47]. Completed in 1994, MPI Version 1.0 was proposed by an international committee of vendors, researchers, implementors, and users. The standard aims to describe portable primitives for communication in distributed memory systems of various scales. These primitives include functions for point-to-point communications, collective communications, synchronization, and management of channels. With efficient implementations for a wide range of hardware, MPI has become the *de facto* standard for message-passing-based parallel programming [22; 48].

There have been a few independent efforts to develop an MPI implementation for the SCC. The RCKMPI library [49] features three SCC-specific MPICH2 [50] channels: SCCMPB, which uses the message passing buffer exclusively; SCCSHM, which uses off-chip RAM exclusively; and SCCMULTI, which uses a combination of the two. In general, MPI programs can benefit from user-supplied communication topology information, but this feature was not supported in the original RCKMPI. Christgau et al. enabled the feature by rearranging and resizing data structures in the MPB [51]. Separately, the SCCMPB channel later was improved with the addition of dynamic process support (a part of the MPI Version 2 standard) and a more efficient communication protocol [52].

Based on MP-MPICH [53], the SCC-MPICH library [54] stands as another MPI implementation for the SCC. The developers have demonstrated acceptable performance from this library, but they refuse to share it with the community for fear that they may lack the human resources for user support [55].

The proven MPI standard has been influential in the design of other SCC message passing protocols. RCCE [41] (pronounced "rocky") is a message passing library with a semantics based on a subset of the MPI standard. Developed by Intel, RCCE was co-designed with the SCC hardware. In addition to the communications primitives, RCCE provides an API for SCC power management operations such as frequency and voltage scaling. Although the library offers high performance in terms of message passing bandwidth, it is subject to certain restrictions including that only one parallel RCCE program may be executing on the chip at a time [56]. Additionally, RCCE send and receive calls are synchronous and blocking. In contrast, our device-layer management of the message-passing hardware, discussed in Section 4.3.2, is asynchronous and allows for an arbitrary number of parallel applications to share the hardware concurrently.

The RCCE library can be compiled both for SCC Linux and for "bare metal." Because bare-metal RCCE is merely a library and not an entire execution environment, it alone does not provide the framework needed to run bare-metal applications. Rather, it depends upon a bare-metal environment that will configure an SCC core for 32-bit protected mode execution and provide a few particular POSIX functions, file operations, and C library functions. In Section 4.5, we introduce *BareMichael*, a minimalistic framework for bare-metal program execution on the SCC. BareMichael serves as the foundation for Xipx, and it (optionally) provides sufficient support for the bare-metal RCCE library.

Clauss et al. developed some useful extensions to the RCCE library [57]. Dubbed iRCCE (for "improved RCCE"), their extensions not only add new non-blocking send and receive functions, but also improve the performance of the standard blocking versions of the functions by optimizing memory copies between MPBs and private RAM. For message lengths above a certain threshold, iRCCE uses pipelining to further improve bandwidth. In addition, iRCCE introduces two wildcard arguments, one of which may be used to receive messages of arbitrary size, the other to receive from arbitrary senders. Standard RCCE requires that both of these parameters are specified explicitly for calls to the receive function. While the non-blocking primitives of iRCCE offer performance benefits, the library requires the user to call a pushing function to make progress. This makes for more complicated code compared to our Xipx device, which implicitly makes progress in the background. Performance comparisons between RCCE, iRCCE, and the Xipx MPB device are given in Section 5.1.

As another improvement on RCCE, Chandramowlishwaran and Vuduc developed efficient collective communication algorithms, namely broadcast and reduce, that outperform those of the RCCE library by a factor of 22 and 6.4 respectively [58]. The improved algorithms were guided by a performance model the authors built from micro-benchmarks of the SCC NoC.

Also using micro-benchmarks, Rotta measured various latencies in the SCC and used the results to analyze the tradeoffs involved in a number of design choices for a message passing implementation [59]. In addition, he produced a quantitative analysis of several existing protocols. However, the Xipx implementation does not fit well into the design space proposed by Rotta, and therefore it is not easily analyzed by his methods.

The Barrelfish OS implements a unique message passing layer that uses MPB space only for inter-core notifications [38]. Payloads are transferred via off-chip RAM. This design decision was motivated in part by the limited size of MPB memory, the need to support multiple message channels simultaneously, and the lack of fine-grained cache control. Like our Xipx MPB driver, the Barrelfish driver is interrupt-driven.

#### 3.2.2 Computation Migration

Computation migration is the act of moving an executing unit of computation (e.g., a process or a thread) between two processors in a distributed memory system. Some applications of migration include:

- dynamic load balancing, which is useful for enhanced throughput [60], reduced power consumption [61], and control of thermal balance [62];

- reduction of communication latency, which is gained by moving communicating entities closer together [63];

- and fault tolerance, which is enhanced by migrating work away from failing cores [64].

With the increasing parallelism of new architectures, efficient migration is becoming more important than ever.

Different challenges are faced depending on the migration granularity that is pursued. The state of an executing process consists of many resources including code, static data, dynamically allocated data, local stack data, and register state. It also incorporates communication state, which includes open communication channels and pending outgoing and incoming network messages, and kernel state, which includes open devices and files [19]. In general, all of this state must be transferred to migrate a process. On the other hand, a given thread may not need all of the resources of its associated process, and therefore thread migration has the potential to be a more lightweight procedure. However, a significant challenge in thread migration is determining just how much state needs to go with the thread for it to operate in its new home, and how to deal with the resources that are not migratable [65]. In Xipx, migration is only supported for user threads (Section 4.4.1), which are similar to single-threaded processes. Process migration is therefore the more relevant field of study for the purposes of this thesis, however we will also touch on a couple of recent developments at the coarser- and finer-grained ends of the spectrum.

In a straightforward migration implementation, a process is frozen, then its complete state and address space is transferred to the destination machine, and finally it is resumed at its new location. However, as data transfer is typically the most expensive operation in a migration [66], this protocol incurs significant latency. As an alternative strategy, the V kernel pre-copies memory pages while allowing a process to continue executing on the source machine [67]. After a complete pre-copy, the process is frozen and its state is migrated, then any pages that were modified during the pre-copy period must be updated on the destination before resuming the process. Copying some pages twice increases the communication overhead, but this strategy greatly reduces the freeze time of the migrated process. Xipx user thread migration is done in the straightforward manner, but it uses unique SCC hardware features to perform rapid bulk data transfer between cores.

An alternative strategy for data transfer is a lazy protocol, in which a minimal amount of resources and address space is transferred initially, and further memory pages get shipped on-demand when they are needed. This approach, used in Accent [68], offers reduced freeze time at the time of migration but incurs many short delays later when additional pages are migrated. A significant advantage is that a process often may not reference a substantial portion of its address space after migration, so many pages may not need to be transferred at all. However, a disadvantage is that the source processor needs to retain the yet-unreferenced resources of any processes that have migrated away. This is one example of a *residual dependency*, which is, in general, a resource on the source machine upon which a migrated process continues to rely. Besides adding complexity and overhead to a system, residual dependencies decrease reliability. A failing processor may take down not only its local processes, but also any processes for which it holds residual dependencies. A process that makes multiple hops in its lifetime may leave residual dependencies scattered throughout the system and therefore become increasingly fragile as it becomes sensitive to the potential failure of more and more processors [66].

Sprite [69] uses a variation of the lazy data transfer approach which eliminates the residual dependencies discussed above. It relies upon a networked file server to which a process's dirty pages get flushed before the process is migrated. The destination core then retrieves pages from the server rather than from the source core when page faults occur. Dirty pages get transferred twice, both from the source to the server and from the server to the destination, which incurs some increased overhead.

Sprite, however, is not devoid of residual dependencies. The kernel is largely focused on *transparency* in the sense that a process should always appear, both to the user and to all processes in the system, as though it is executing on its "home machine," the machine on which it was created. In other words, from outside of the kernel, it should look like migration never happens. Sprite achieves this goal at the expense of some residual dependencies. For example, a user or process may send the kill signal to a process at any time, and, in a transparent system, this signal would be directed to the home machine. If the process has been migrated, then the home machine is responsible for forwarding that signal to its new location. Similarly, some system calls, such as gettimeofday, get forwarded to and serviced by the home node so that migration is transparent to the migrated process itself. To mitigate the problem, Sprite ensures that subsequent migrations after an initial one do not leave residual dependencies on the intermediate nodes, thereby limiting them to the home machine only.

The type of residual dependency just described, that which is due to communication redirection, commonly arises from the effort to enforce migration transparency [70]. The Amoeba OS [71] avoids communication-based dependencies by use of the Fast Local Internet Protocol (FLIP) [72], which associates a network address with a particular process rather than with a host, thus making the address itself migratable. Both LOCUS [73] and V [67] maintain local caches of last-known locations of recently-accessed processes and are therefore able to bypass the home node. While V corrects for stale process location information by broadcasting a request for it, LOCUS retrieves updated information from the home node and therefore retains a dependency. Our initial implementation of migration in Xipx leaves no residual dependencies but sacrifices a degree of transparency. Inter-process message passing remains transparent, but some system calls do not. For example, the kill system call can only kill local threads, so a thread may not realize that a once-local thread has migrated away and therefore that it cannot be killed.

In addition to being pursued at the granularity of individual processes, migration has also attracted interest from the virtual machine (VM) community. With many of the same motivations that drive process migration – including load balancing, fault tolerance, communication latency reduction, and power management – investigators have developed ways to migrate entire VMs across hosts [74; 75; 76]. A VM conveniently encapsulates all of the state of hardware and software running within, thereby simplifying migration by moving not only a set of processes, but also the entire context in which they are executing. Furthermore, this approach enables migration even when the source and destination host machines are running different operating systems. VM migration has been used in practice to move, for example, active web servers [77]. "Live migration" is achieved using the pre-copying introduced in V, and local-area network migrations have been demonstrated with server downtime of only a few seconds. Wide-area network migrations achieve downtimes of tens of seconds.

On the other end of the spectrum from VM migration, task migration involves movement of very fine-grained units of computation. The task parallel programming model [78] prescribes the use of a number of concurrent worker threads to execute a great number of individual tasks. The feasibility of this model is investigated specifically in the context of the SCC by both [79] and [80]. Two common scheduling strategies for task parallelism are *work sharing* and *work stealing*. The work sharing approach uses a single centralized queue from which all worker threads retrieve tasks to execute. The work stealing strategy employs a separate work queue for each worker thread, and threads that exhaust their queue may attempt to steal tasks from others to stay busy. The authors in [80] assert that work stealing is the superior strategy on the SCC, but the experiments in [79] show that work sharing exhibits better performance when there is a high variation in the amount of work done per task. While these papers do not focus on the technical challenges of process migration, fine-grained task migration is nonetheless a common practice in which a workload is shifted between processing cores.

The distributed Barrelfish Inter-core Adaptive Scheduling (BIAS) scheduler [81], a two-layer extension of the RBED scheduler [82], performs task migration for load balancing. Two different methods of pre-migration task suspension are performed depending on the implementation details of the worker thread framework that is used. In spite of being an unoptimized implementation, the adaptive load-balancing scheduler shows improved throughput for some of the tested benchmarks.

### 3.3 Summary of Related Work

This chapter has discussed recent work in many-core operating systems of various designs, message passing implementations, and solutions for computation migration in distributed systems. Most of the work covered has been directly related to the Intel SCC. Throughout the chapter, we have mentioned ways in which our work on Xipx compares to the work being discussed. The following chapter describes Xipx in detail, first introducing the Embedded Xinu kernel from which it is derived, then explaining the many-core extensions that adapt it for use on the SCC.

### **CHAPTER 4**

## Xipx: A Many-Core Operating System