## <u>ISTANBUL TECHNICAL UNIVERSITY</u> ★ INFORMATICS INSTITUTE

# REAL TIME FPGA IMPLEMENTATION OF A TRAINING BASED CONTENT ADAPTIVE VIDEO RESOLUTION UP-CONVERSION ALGORITHM

M.Sc Thesis by Muzaffer Barış UYAR, B.Sc.

**Department: Advanced Technologies in**

Engineering

**Program:** Computer Science

### <u>ISTANBUL TECHNICAL UNIVERSITY</u> ★ INFORMATICS INSTITUTE

# REAL TIME FPGA IMPLEMENTATION OF A TRAINING BASED CONTENT ADAPTIVE VIDEO RESOLUTION UP-CONVERSION ALGORITHM

M.Sc. Thesis by

Muzaffer Barış UYAR, B.Sc.

(704031013)

Date of submission: 7 May 2007

Date of defence examination: 11 June 2007

Supervisor (Chairman): Prof. Dr. Bülent ÖRENCİK

Members of the Examining Committee Prof. Dr. Ali ZEKİ

Asst. Prof. Dr. D. Turgay ALTILAR

# <u>ISTANBUL TEKNİK ÜNİVERSİTESİ ★ BİLİŞİM ENSTİTÜSÜ</u>

# EĞİTİM TABANLI, İÇERİK UYARLAMALI BİR VİDEO ÇÖZÜNÜRLÜĞÜ DÖNÜŞTÜRME ALGORİTMASININ GERÇEK ZAMANLI OLARAK, SAHADA PROGRAMLANABİLİR KAPI DİZİLERİ(SPKD(FPGA)) İLE GERÇEKLENMESİ

YÜKSEK LİSANS TEZİ Müh. Muzaffer Barış UYAR (704031013)

Tezin Enstitüye Verildiği Tarih: 7 Mayıs 2007

Tezin Savunulduğu Tarih: 11 Haziran 2007

Tez Danışmanı: Prof. Dr. Bülent ÖRENCİK

Diğer Jüri Üyeleri Prof. Dr. Ali ZEKİ

Yrd. Doç. Dr. D. Turgay ALTILAR

#### **ACKNOWLEDGEMENT**

First I would like to thank my supervisor Prof. Dr. Bülent Örencik, for his guidance and support during this thesis study. I would also like to thank Toygar Akgün, and Murat Sayinta for their technical support, my manager in Vestek R&D, Ali Sayinta for his technical support, guidance and tolerance during this thesis work.

I would finally like to thank my grand mother and my family for their endless support and love.

May 2007

Muzaffer Barış UYAR

## **CONTENTS**

| TABLE LIST<br>FIGURE LIST<br>ÖZET<br>SUMMARY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V<br>VII<br>VIII<br>IX                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| <ul><li>1. INTRODUCTION</li><li>1.1 Motivation</li><li>1.2 Organization of Thesis</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>1</b><br>1<br>2                                                                 |

| <ul> <li>2. INTRODUCTION TO DIGITAL VIDEO</li> <li>2.1 Digital Image Basics</li> <li>2.2 Algorithms in Digital Video Processing</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>3</b> 3 5                                                                       |

| 3. VIDEO RESOLUTION UP-CONVERSION ALGORITHMS 3.1 Sampling Structure Conversion 3.1.1 Reducing Sampling Rate by an Integer Factor 3.1.2 Increasing Sampling Rate by an Integer Factor 3.1.3 SD to HD Sampling Rate Conversion 3.2 Linear methods for up-scaling 3.2.1 Zero order hold interpolation 3.2.2 Linear Interpolation 3.2.3 Cubic Interpolation 3.3 Advanced Methods for up scaling 3.3.1 Content Adaptive Training Based Methods 3.3.1.1 Digital Reality Creation (Kondo's method) 3.3.1.2 Resolution Synthesis (Atkins' Method) 3.3.1.3 Example Based Super Resolution 3.3.2 Directional Interpolation Methods 3.3.3 Other Methods 3.4 Video Performance Evaluation of the Methods | 7<br>7<br>7<br>9<br>10<br>11<br>13<br>14<br>15<br>15<br>16<br>18<br>21<br>21<br>23 |

| <ul> <li>4. MODIFIED RESOLUTION SYNTHESIS</li> <li>4.1 Overview</li> <li>4.2 Algorithm Description</li> <li>4.2.1 Offline Training Phase</li> <li>4.2.2 Online Content Adaptive Filtering Phase</li> <li>4.2.2.1 Feature Extraction</li> <li>4.2.2.2 Context classification</li> <li>4.2.2.3 Filtering</li> <li>4.3 Visual Quality Results</li> <li>4.4 Complexity Analysis</li> <li>4.4.1 Complexity of RS and Modified RS algorithms</li> <li>4.4.1.1 Feature Extraction:</li> <li>4.4.1.2 Context Classification</li> <li>4.4.1.3 Interpolation</li> <li>4.4.2 Complexity Comparison of RS and MRS algorithm</li> </ul>                                                                   | 26<br>26<br>27<br>27<br>29<br>31<br>31<br>32<br>34<br>35<br>35<br>35<br>37<br>37   |

| 5. PROPOSED HARDWARE ARCHITECTURE                         | 40    |

|-----------------------------------------------------------|-------|

| 5.1 Performance Requirements                              | 40    |

| 5.1.1 Throughput Constraints                              | 40    |

| 5.1.2 Logic Area Constraints                              | 43    |

| 5.1.3 Resource Sharing Options                            | 43    |

| 5.2 Hardware Blocks                                       | 44    |

| 5.2.1 Top Level                                           | 44    |

| 5.2.2 Control Unit (CU)                                   | 45    |

| 5.2.3 Color Space Conversion Unit (CSC)                   | 46    |

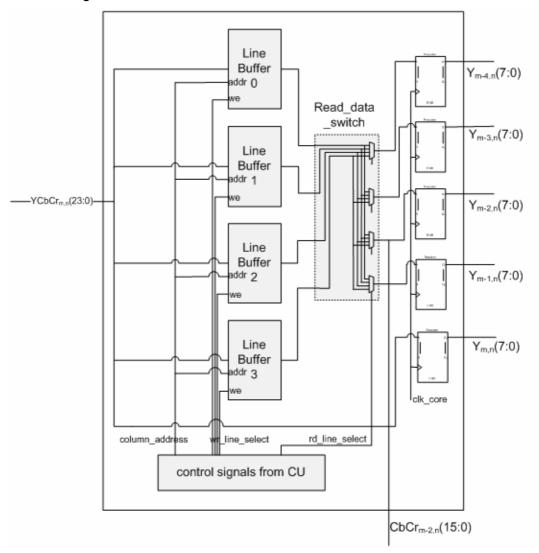

| 5.2.4 Input Memory Unit (IM)                              | 47    |

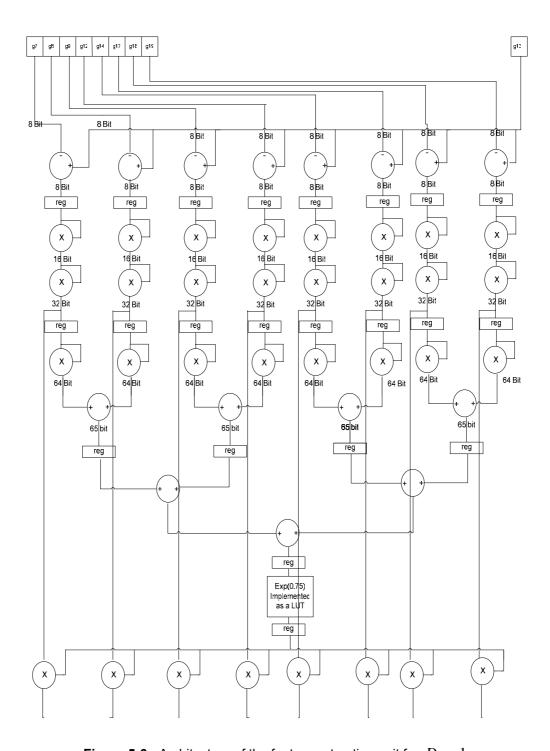

| 5.2.5 Feature Extraction Unit (FE)                        | 48    |

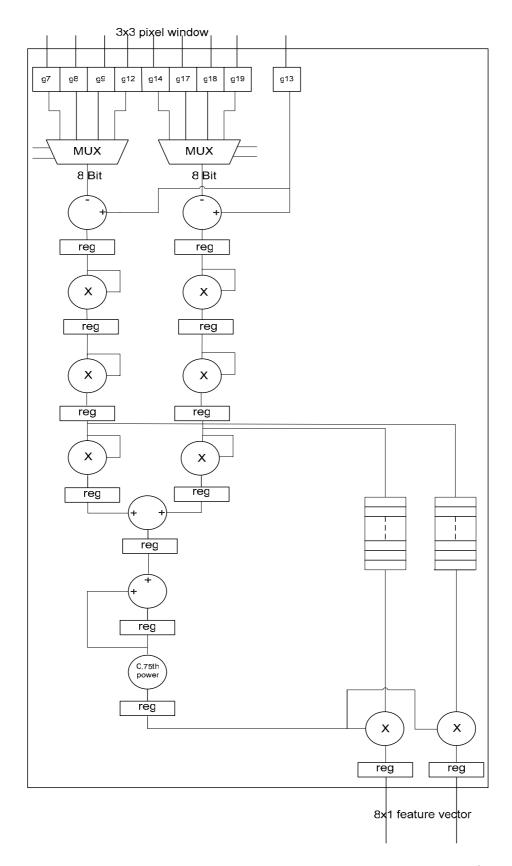

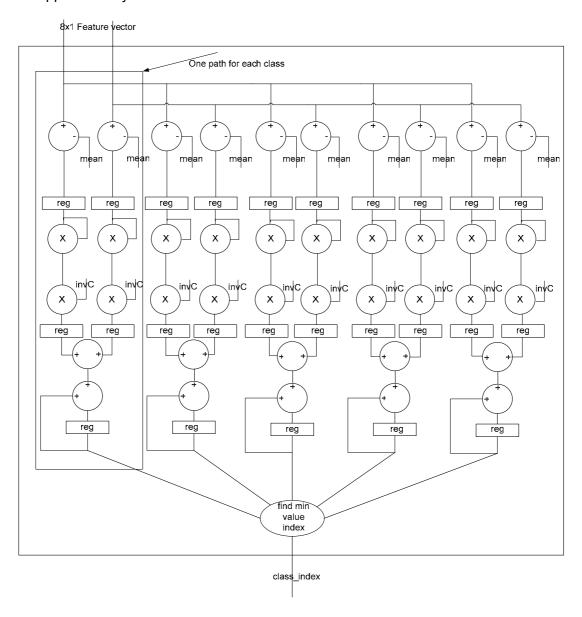

| 5.2.6 Classification Unit (CL)                            | 51    |

| 5.2.7 Interpolation Unit (IN)                             | 52    |

| 5.2.8 Output Memory Unit (OM)                             | 52    |

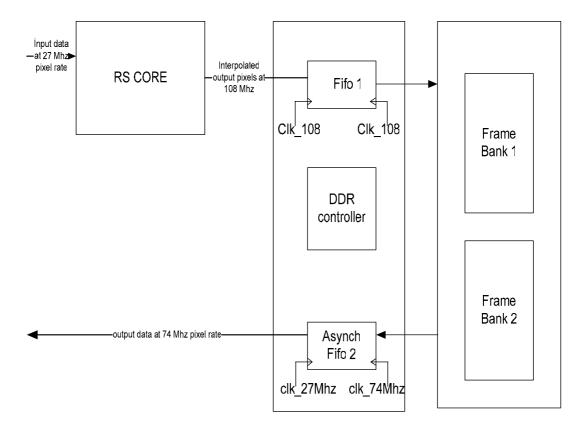

| 5.2.9 Asynchronous Buffers and DDR Frame Buffer           | 53    |

| 6. FUNCTIONAL VERIFICATION, FPGA MAPPING & REAL TIME TEST | TS 57 |

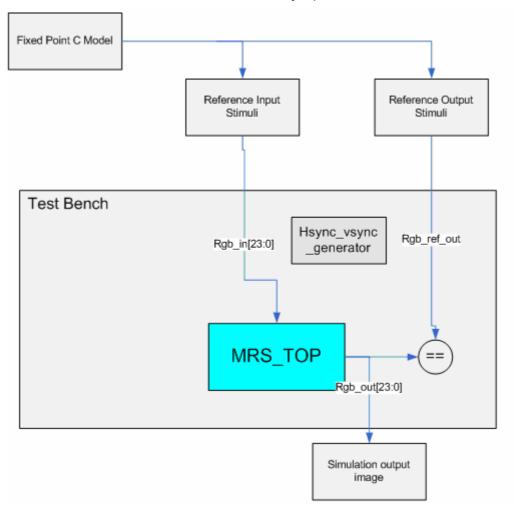

| 6.1 Functional Verification                               | 57    |

| 6.1.1 Simulation Platform                                 | 57    |

| 6.1.2 Simulation Results                                  | 58    |

| 6.2 FPGA Mapping                                          | 59    |

| 6.2.1 FPGA Mapping Methodology                            | 59    |

| 6.2.2 FPGA Mapping Results                                | 60    |

| 6.3 Real Time Tests                                       | 63    |

| 6.3.1 Real Time Test Platform                             | 63    |

| 6.3.2 Test Results                                        | 63    |

| 7. CONCLUSION AND FUTURE WORK                             | 66    |

| 7.1 Concluding Remarks                                    | 66    |

| 7.2 Future Work                                           | 66    |

| REFERENCES                                                | 68    |

| BIOGRAPHY                                                 | 70    |

## **TABLE LIST**

|                                                                     | <u>Page No</u> |

|---------------------------------------------------------------------|----------------|

| Table 3-1: MSE performance evaluation performed in [3]              | 24             |

| Table 4-1: Number of arithmetic operations in RS and MRS algorithms | 39             |

| <b>Table 6-1</b> : FPGA mapping results for $D_r$ values 2, and 4   | 61             |

| Table 6-2 : Performance results of the implementation               | 61             |

| Table 6-3 : Comparison of the implementation with previous work     | 62             |

## **FIGURE LIST**

|                                                                                                                                               | Page No            |

|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Figure 2-1 : Structure of a digital image                                                                                                     | 3                  |

| Figure 2-2: 8 bit coding of the image in Figure 2.1                                                                                           | 4                  |

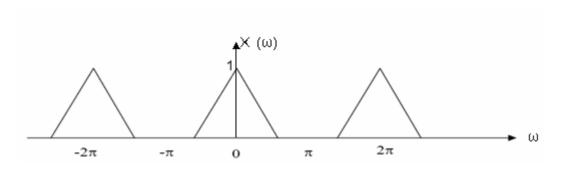

| <b>Figure 3-1 :</b> $X(\omega)$ , frequency spectrum of the $x[n]$ signal                                                                     | 8                  |

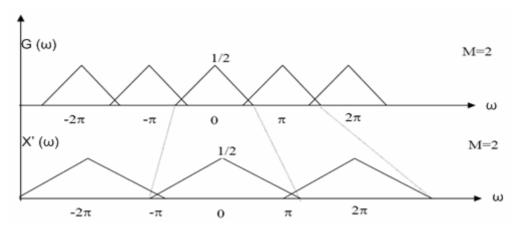

| <b>Figure 3-2 :</b> $G(\omega)$ , frequency spectrum of the intermediate signal $g[n]$                                                        | and $X'(\omega)$ , |

| frequency spectrum of the decimated signal $x'[n]$ for $M=2$                                                                                  | 8                  |

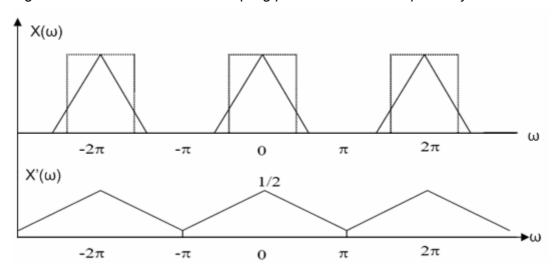

| <b>Figure 3-3</b> : a) $X(\omega)$ , frequency spectrum of the input signal $x[n]$ (Dott                                                      | _                  |

|                                                                                                                                               |                    |

| represent the antialising low pass filter) and $X'(\omega)$ , frequency                                                                       | ·                  |

| the decimated signal $x'[n]$ .                                                                                                                | 9                  |

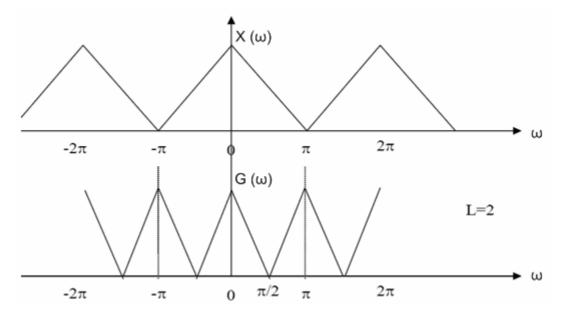

| <b>Figure 3-4</b> : $X[\omega]$ , frequency spectrum of the input signal $x[n]$ and $G(\omega)$                                               | $(\omega)$ ,       |

| frequency spectrum of the filled in signal $g[n]$ for $L=2$                                                                                   | 10                 |

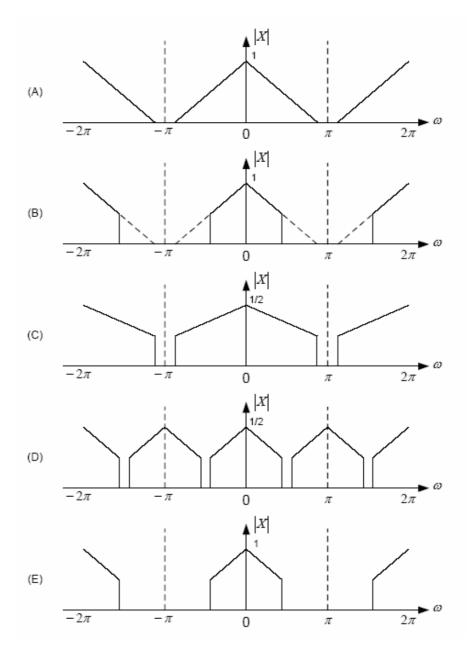

| Figure 3-5: Frequency characteristics of decimation-interpolation process                                                                     | ess.               |

| Frequency spectrum of A) The original signal B) Low pass filte                                                                                |                    |

| Down sampled signal D) Up sampled signal E) Low pass filtered                                                                                 | ed signal 12       |

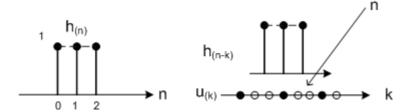

| <b>Figure 3-6:</b> $h[n]$ , the impulse response of the zero order hold interpola                                                             | ation function     |

| for $L=3$ , and illustration of convolution using this kernel                                                                                 | 13                 |

| <b>Figure 3-7:</b> $h[n]$ , impulse response of the linear interpolation kernel for                                                           | L=3 and            |

| illustration of convolution using this kernel                                                                                                 | 14                 |

| <b>Figure 3-8:</b> Impulse response of cubic interpolation function for $L=2$                                                                 | 14                 |

| Figure 3-9: Training process performed in Kondo's method                                                                                      | 16                 |

| Figure 3-10: Aperture used in Kondo's method. The HD pixels A,B,C,D                                                                           |                    |

| interpolated using nine SD pixels, (F <sub>00</sub> to F <sub>22</sub> )                                                                      | 17                 |

| <b>Figure 3-11:</b> 5x5 pixel neighborhoods identified as a vertical edge <b>Figure 3-12:</b> Structure of the RS predictor.                  | 18<br>19           |

| <u>→</u> ·                                                                                                                                    |                    |

| <b>Figure 3-13:</b> Extraction of the $\tilde{y}$ vector                                                                                      | 20                 |

| Figure 3-14: Aperture used in NEDI                                                                                                            | 22                 |

| <b>Figure 3-15 :</b> Subjective evaluation performed in [3] ( A : Cubic B-splir interpolation, B: Kondo's method, C: Li's method, D: Tegenbos |                    |

| method )                                                                                                                                      | 24                 |

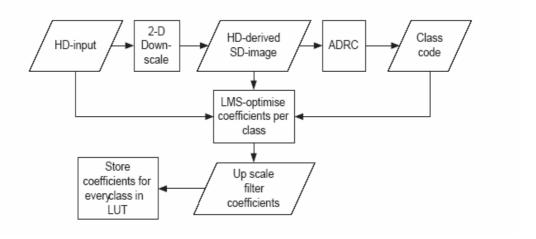

| Figure 4-1: Proposed training scheme in [1]                                                                                                   | 27                 |

| Figure 4-2: Up conversion of SD resolution image to HD resolution im                                                                          | age <b>29</b>      |

| Figure 4-3: Aperture used in Modified Resolution Synthesis                                                                                    | 30                 |

| Figure 4-4: Pseudo code of the Modified RS algorithm                                                                                          | 33                 |

| Figure 4-5: Input image with 200x200 resolution                                                                                               | 34                 |

| <b>Figure 4-6:</b> MRS output image with 400x400 resolution <b>Figure 4-7:</b> Bicubic scaler output image with 400x400 resolution            | 34<br>35           |

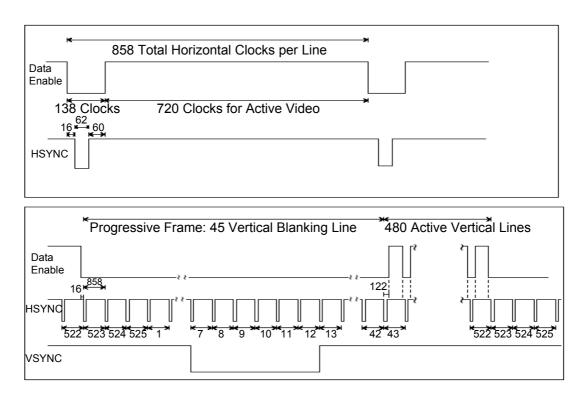

| Figure 5-1: Timing diagram for NTSC 480p@60 Hz video standard                                                                                 | 41                 |

| Figure 5-2: Timing diagram for 720p@60 Hz video standard                                                                                      | 41                 |

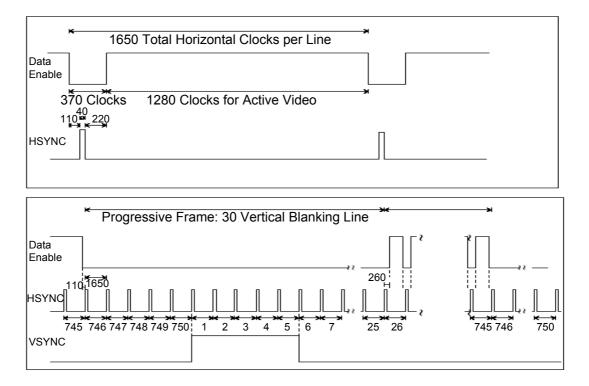

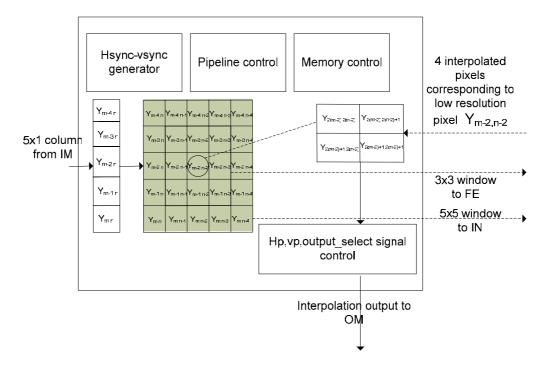

| Figure 5-3: Top level block diagram of the proposed hardware                                                                                  | 45                 |

| Figure 5-4 : Control unit block diagram                                                                                                       | 46                 |

| Figure 5-5: Input memory unit block diagram                                                                                                   | 47                 |

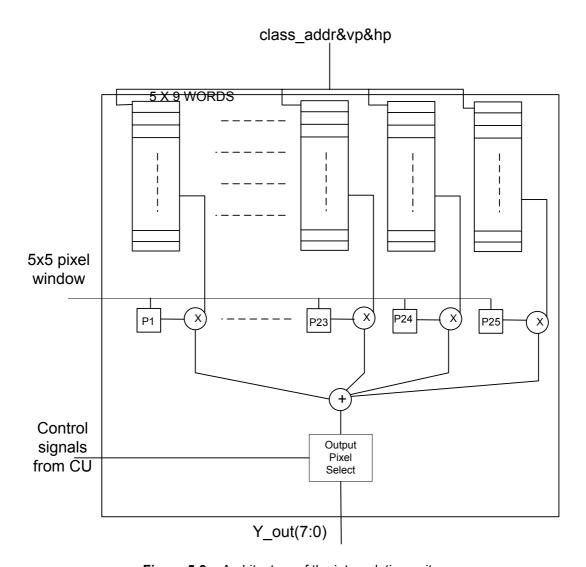

| <b>Figure 5-6</b> : Architecture of the feature extraction unit for $D_r = 1$     | 49 |

|-----------------------------------------------------------------------------------|----|

| <b>Figure 5-7</b> : Architecture of the feature extraction unit for $D_r = 4$     | 50 |

| <b>Figure 5-8</b> : Architecture of the context classification unit for $D_r = 4$ | 51 |

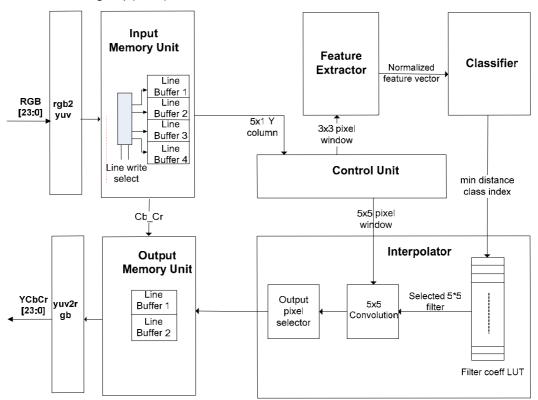

| Figure 5-9: Architecture of the interpolation unit                                | 52 |

| <b>Figure 5-10 :</b> Output memory unit operation for $L = 1.5$                   | 53 |

| Figure 5-11 : DDR frame buffer and asynchronous buffers                           | 55 |

| Figure 6-1 : Functional verification platform                                     | 58 |

| Figure 6-2: 200x200 portion of the input image                                    | 59 |

| Figure 6-3: 300x300 portion of the scaled output image                            | 59 |

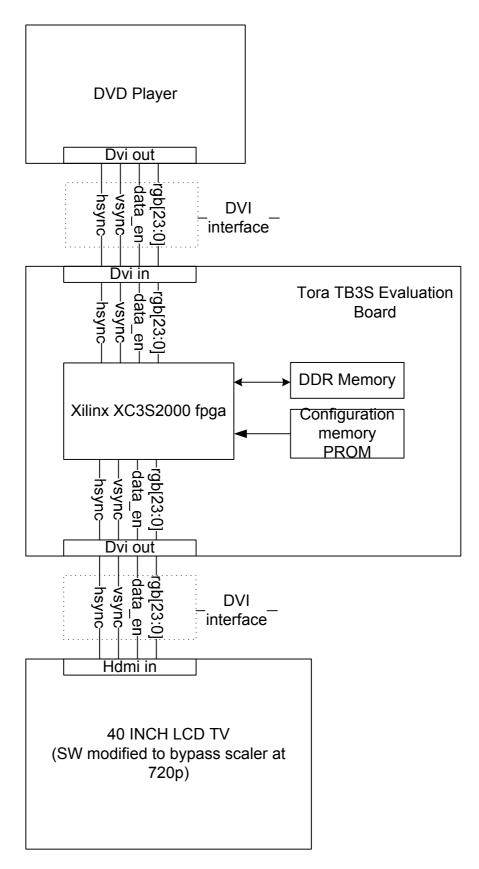

| Figure 6-5: Real time test platform                                               | 65 |

# EĞİTİM TABANLI, İÇERİK UYARLAMALI BİR VİDEO ÇÖZÜNÜRLÜĞÜ DÖNÜŞTÜRME ALGORİTMASININ GERÇEK ZAMANLI OLARAK, SAHADA PROGRAMLANABİLİR KAPI DİZİLERİ(SPKD (FPGA)) İLE GERÇEKLENMESİ

#### Ö7FT

Bu çalışmada, eğitim tabanlı, içerik uyarlamalı bir video çözünürlük yükseltme algoritması için, iş hattı ve kaynak paylaşımı kullanan yüksek performanslı bir donanım mimarisi önerilmiş ve önerilen yapı, 480x720 çözünürlükteki videonun 720x1280 cözünürlükte videoya dönüstürülmesi uygulaması için düsük maliyetli bir sahada programlanabilir kapı dizisinde (SPKD (FPGA)) gerçeklenmiştir. İçerik uyarlamalı video cözünürlük yükseltme algoritmaları temel olarak alt örnekleme işlemi sürecinde video sinyalinde kaybolan yüksek frekans bileşenlerinin, geçmişte elde edilen istatistiksel bilgiden yararlanarak geri kazanılmasını hedefler. Bu çalışmada donanım yapısı önerilen ve gerçeklenen, modifiye edilmiş çözünürlük sentezi (MRS) algoritması, kaybolan yüksek frekans bilgisini geri kazanmak için geniş bir video görüntü kümesi üzerinde yapılan eğitim sürecinden faydalanır. MRS algoritması çıkış görüntüsünü oluşturan her piksel için 137 çarpma ve 120 toplama işlemi içeren kompleks bir algoritmadır. 480x720 çözünürlükteki standart çözünürlük (SC (SD)) videonun 720x1280 çözünürlükteki yüksek çözünürlük (YÇ (HD)) videoya dönüştürülmesi problemi, 27 Mhz giriş saat çevriminde üretilen piksel datası ile gerçek zaman kısıtları içerir. Önerilen donanım mimarisi, içerideki çekirdek blokların, girişteki piksel saat frekansının tam sayı katı bir frekansta çalıştırılması yöntemi ile kavnak paylasımına olanak sağlar. Hedeflenen FPGA icin. tasarım, giris piksel saat frekansının dört katı olan 108 Mhz saat frekansında çalışacak biçimde iş hattı yapısı kurulmuştur. Bu sayede içerideki çarpma ve toplama işlemleri için kaynak paylaşımı yapılmış ve, iş hattındaki saklayıcılarda ve kontrol lojiğinde küçük bir artış ile çarpıcı ve toplayıcı sayısı dörtte birine indirilmistir. Tasarım akısı sürecinde, donanım kısıtları ve algoritma performansı gözönüne alınarak, algoritmanın kayan noktalı yazılım modelinden, sabit noktalı yazılım modeli çıkarılmıştır. Önerilen yapının, saklayıcı transfer seviyesindeki tanımı, VHDL dili ile yazılmış; sabit noktalı C modeli ile VHDL modeli çıktıları karşılaştırılarak donanım yapısı doğrulanmıştır. Doğrulanan tasarım, Xilinx XC3S2000 FPGA çipi kullanılarak gerçeklenmiş ve likit kristal ekranlı TV üzerinde SD giriş videosunun HD videoya dönüştürülmesi uygulaması için test edilmiştir. Gerçeklenen tasarım, 1.6 ms zaman içerisinde, SD çözünürlükteki görüntüyü HD cözünürlükte görüntüye dönüstürerek video cözünürlük dönüstürme probleminin gerçek zaman kısıtlarını sağlamaktadır. Tasarım, FPGA içerisinde 3533 dilim ve yaklaşık 60 KB blok RAM yapısı kullanmaktadır. Tasarımın lojik kapı sayısı cinsinden karmaşıklığının, literatürdeki mevcut lineer video boyutlandırma algoritmaları ile yaklaşık aynı ölçekte olduğu görülmüştür. TV üzerinde gerçekleştirilen gerçek zamanlı testler sonucunda, uygulamanın geleneksek bikubik interpolasyon tabanlı video boyutlandırıcılardan daha başarılı detay koruma özelliğine sahip olduğu gözlenmiştir.

# REAL TIME FPGA IMPLEMENTATION OF A TRAINING BASED CONTENT ADAPTIVE VIDEO RESOLUTION UP-CONVERSION ALGORITHM

#### **SUMMARY**

In this study, a high performance, pipelined, resource shared hardware architecture was proposed for a training based content adaptive video resolution up-conversion algorithm, and the proposed architecture was implemented in a low cost field programmable gate array (FPGA), for a video standards conversion application where the input resolution is 480x720 and the output resolution is 720x1280. Content adaptive video resolution up-conversion methods aim to recover the missing spectrum at the down sampled image, by using prior information obtained by statistical analysis. Modified resolution synthesis (MRS), which was implemented in this study is one such method, which makes use of statistical data obtained by training with large set of images. Modified resolution synthesis is a complex algorithm which requires 137 multiplications and 120 additions per output pixel. For 480x720 standard definition (SD) video to 720x1280 high definition (HD) video conversion, the design is constrained by the input pixel rate which is 27 Mhz. The proposed architecture can make use of resource sharing by running the core blocks at an integer multiple of the input pixel rate. For the targeted FPGA, the design was pipelined to work at 108 Mhz, which is four times the input pixel clock rate. Number of multipliers and adders were reduced by a factor of 4, with a minor increase in the pipeline stages and the control logic complexity. A fixed point model of the design was generated from the floating point model, by considering the hardware constraints imposed by the target FPGA, and by considering the performance of the algorithm with different bit precisions. Register transfer level (RTL) description of the proposed architecture was written in VHDL and RTL model was verified with fixed point C model outputs. The verified design was mapped to Xilinx XC3S2000 FPGA, and was tested on a 40 inch liquid crystal display (LCD) for 480p to 720p resolution up-conversion. The implemented design performs scaling of a frame in 1.6ms, which meets the real time constraints for target video up conversion application. The design uses 3533 slices, and 60KByte of block RAMS available in the FPGA. The logic gate count of the design is in the order of gate counts for bicubic scalers proposed previously. Real time tests on LCD TV shows that the performance of the algorithm is better in preserving the details when compared with conventional bicubic interpolation based scalers.

#### 1. INTRODUCTION

#### 1.1 Motivation

Recent advances in flat panel displays and the advent of high definition TV (HDTV) standard led to more emphasis on several video processing issues. Spatial resolution up-conversion of the input video is one such issue playing a more important role with current technological advancements. Flat panel displays, with the native resolution that supports high definition (HD) video input with resolution of 1080\*1920 or 720\*1280 are now starting to dominate the market, with many of the high-end TV companies, investing only on flat panel displays rather than Cathode Ray Tubes (CRT). However, those flat panel displays with HD resolution, lack from appropriate input source compatible with the native resolution of the TVs. Although the current TV sets are capable of displaying video signals on HD resolution, most of the existing content and current video broadcasting is still in SD resolution, and those high resolution flat panel displays are fed with SD video input. In such cases, the resolution of the SD input video source must be up-converted to the native resolution of the flat panel display using a mathematical method. The performance of the up-conversion method used has a considerable effect on the video quality and the effect is becoming more obvious with the fast growth rate of the size of the flat panel displays, forcing the TV set manufacturers to focus more on the issue. Apart from the video quality performance of the up-conversion algorithm, there are two other constraints, namely the real time requirements and the cost. Video processing standards are set considering the human visual system, and a pre-defined refresh rate is listed in the standards that constraints the throughput of the video system. The tight real time constraints and the need for a high performance, high complexity scaling algorithm requires high performance processing elements capable of fast parallel processing, eliminating the option of software based, sequential processing. Therefore the video up-conversion algorithms are mostly implemented in fixed hardware blocks, which are a part of the video processor inside the TV set. In this work, several high complexity, high performance video up-scaling algorithms are evaluated and Modified Resolution Synthesis (MRS) algorithm proposed in [1] is chosen to be implemented in a high end flat panel display. A novel, resource shared, pipelined hardware architecture is proposed to implement the algorithm in fixed

hardware and the proposed architecture is implemented in a low cost FPGA family, Xilinx XC3S2000 targeting the consumer electronics market.

#### 1.2 Organization of Thesis

This thesis presents an optimized, pipelined, resource shared architecture for a training based content adaptive video up-conversion algorithm, and utilizes that architecture to implement a real time video up-conversion system integrated into a flat panel LCD display with 768\*1366 native resolution.

Chapter 2 presents basics of digital video and current trends in design and implementation of video enhancement algorithms in flat panel displays.

Chapter 3 is a review of video up-conversion algorithms in the literature. Performance evaluation of the algorithms obtained from previous work on the subject is presented.

Chapter 4 describes the Modified Resolution Synthesis algorithm, which was selected to be implemented in this thesis.

Chapter 5 presents the hardware architecture proposed for the Modified Resolution Synthesis algorithm. Details of the proposed architecture are given for each sub block.

Chapter 6 presents the simulation and implementation results in FPGA platform. Real-time tests performed on TV are also presented.

Chapter 7 concludes the thesis giving a brief overview of the contribution of the thesis study, and possible feature work.

#### 2. INTRODUCTION TO DIGITAL VIDEO

#### 2.1 Digital Image Basics

Digital video is composed of digital image frames. The structure of a digital image is illustrated in Figure 2-1. The image taken from [2] is acquired by microwave radar from an orbiting space probe.

Figure 2-1: Structure of a digital image

The image shown is represented by 256 samples arranged in a two-dimensional array of 16 columns by 16 rows. In imaging jargon, each sample is called a pixel, which is an abbreviation of picture element. The value of each pixel in the example is between 0 and 255. When displaying this as a visual image, the value of each pixel is converted into a grayscale, where 0 is black, 255 is white and intermediate values are grey levels. The mapping of the grey levels in Figure 2-1 to 8 bit numbers in the range of 0-255 is illustrated in Figure 2-2.

|     |     | Column |         |     |     |     |     |     |     |     |     |     |     |     |     |     |

|-----|-----|--------|---------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|     | 150 |        | 155 160 |     |     |     |     |     |     |     |     | 165 |     |     |     |     |

| 50  | 183 | 183    | 181     | 184 | 177 | 200 | 200 | 189 | 159 | 135 | 94  | 105 | 160 | 174 | 191 | 196 |

|     | 186 | 195    | 190     | 195 | 191 | 205 | 216 | 206 | 174 | 153 | 112 | 80  | 134 | 157 | 174 | 196 |

|     | 194 | 196    | 198     | 201 | 206 | 209 | 215 | 216 | 199 | 175 | 140 | 77  | 106 | 142 | 170 | 186 |

|     | 184 | 212    | 200     | 204 | 201 | 202 | 214 | 214 | 214 | 205 | 173 | 102 | 84  | 120 | 134 | 159 |

|     | 202 | 215    | 203     | 179 | 165 | 165 | 199 | 207 | 202 | 208 | 197 | 129 | 73  | 112 | 131 | 146 |

| 55  | 203 | 208    | 166     | 159 | 160 | 168 | 166 | 157 | 174 | 211 | 204 | 158 | 69  | 79  | 127 | 143 |

| _   | 174 | 149    | 143     | 151 | 156 | 148 | 146 | 123 | 118 | 203 | 208 | 162 | 81  | 58  | 101 | 125 |

| Row | 143 | 137    | 147     | 153 | 150 | 140 | 121 | 133 | 157 | 184 | 203 | 164 | 94  | 56  | 66  | 80  |

| Ξ.  | 164 | 165    | 159     | 179 | 188 | 159 | 126 | 134 | 150 | 199 | 174 | 119 | 100 | 41  | 41  | 58  |

|     | 173 | 187    | 193     | 181 | 167 | 151 | 162 | 182 | 192 | 175 | 129 | 60  | 88  | 47  | 37  | 50  |

| 09  | 172 | 184    | 179     | 153 | 158 | 172 | 163 | 207 | 205 | 188 | 127 | 63  | 56  | 43  | 42  | 55  |

|     | 156 | 191    | 196     | 159 | 167 | 195 | 178 | 203 | 214 | 201 | 143 | 101 | 69  | 38  | 44  | 52  |

|     | 154 | 163    | 175     | 165 | 207 | 211 | 197 | 201 | 201 | 199 | 138 | 79  | 76  | 67  | 51  | 53  |

|     | 144 | 150    | 143     | 162 | 215 | 212 | 211 | 209 | 197 | 198 | 133 | 71  | 69  | 77  | 63  | 53  |

|     | 140 | 151    | 150     | 185 | 215 | 214 | 210 | 210 | 211 | 209 | 135 | 80  | 45  | 69  | 66  | 60  |

| 65  | 135 | 143    | 151     | 179 | 213 | 216 | 214 | 191 | 201 | 205 | 138 | 61  | 59  | 61  | 77  | 63  |

Figure 2-2: 8 bit coding of the image in Figure 2-1

A typical digital image is composed of about 500 rows by 500 columns. This is the image quality encountered in television, personal computer applications, and general scientific research. Images with fewer pixels, are regarded as having unusually poor resolution. These low resolution images look noticeably unnatural, and the individual pixels can often be seen. On the other end, images with more than 1000 by 1000 pixels are considered exceptionally good. This is the quality of the best computer graphics, high-definition television, and 35 mm motion pictures. The strongest motivation for using lower resolution images is that there are fewer pixels to handle which reduces both the transmission and processing complexity. It is common for 256 grey levels (quantization levels) to be used in image processing, corresponding to a single byte per pixel. This choice is mainly due to the fact that a brightness step size of 1/256 is smaller than the human eye can perceive. However some images are now stored with 10 bits, and current video processors start using

10 bit processing as well . This is mainly done to reduce the undesired effects of 8 bit processing(e.g. false contours, quantization noise) [2].

Color is added to digital images by using three numbers for each pixel, representing the intensity of the three primary colors: red, green and blue. Mixing these three colors generates all possible colors that the human eye can perceive. A single byte is frequently used to store each of the color intensities, allowing the image to capture a total of  $256 \times 256 \times 256 = 16.8$  million different colors [2].

#### 2.2 Algorithms in Digital Video Processing

Raw video data at the inputs of a TV set pass through several processing steps in the TV processors' pipeline. The main stages in the video processing pipeline can be listed as

- Video format conversion

- Interlaced to progressive conversion

- Resolution up-conversion

- · Coding artifact reduction

- · Contrast enhancement

- Sharpness enhancement

- Color saturation enhancement

- Spatial and temporal denoising

Video format conversion refers to the issue of converting video signals which are recorded at different frame rates. Video cameras use a picture rate of 50 or 60Hz, while movie films are recorded at 24, 25 or 30Hz. The picture rate of TV and PC displays lie between 50 to 120Hz. High quality picture rate conversion methods make use of motion estimation and compensation techniques to predict the missing information [3].

With interlaced scanning, only half of the scanning lines of individual pictures are transmitted and reproduced at a TV receiver. The first field is made of the odd scanning lines and the second field is made of the even scanning lines. It has been shown that interlaced video display matches the demands of the human visual system very well however; the interlacing procedure is a complication for many digital processing tasks and also most modern displays cannot handle interlaced signals well. Therefore, de-interlacing, or interlaced-to-progressive conversion,

doubles the vertical-temporal sampling density to produce a suitable signal for the display [3].

With the introduction of HDTV-capable TV receivers, the transmission of SDTV material does not stop immediately, which requires up-conversion at the TV set. A similar situation occurs with PCs that have a screen resolution that is higher than required for television. In general the price of high resolution screens has come down to a level that it becomes affordable, even for TVs that have no HDTV reception. Consequently, resolution up-conversion is a hot topic to provide HD image quality from SD video source [3].

Coding artifacts and noise are two important issues apparent in video. Coding artifacts are apparent in digital video if the video is coded with low bit rate. Noise is introduced when either acquiring the video data, or in conversion steps (e.g. analog to digital conversion, quantization etc.) Both coding artifact reduction techniques and denoising techniques are also available in the current video processor chipsets. To improve the perceived image quality, current video processors also have color, contrast and sharpness enhancement blocks.

#### 3. VIDEO RESOLUTION UP-CONVERSION ALGORITHMS

#### 3.1 Sampling Structure Conversion

Video up-conversion problem can be defined as a subset of "sampling structure conversion" problem. A continuous time signal  $x_c(t)$  can be represented as a discrete-time signal

$$x[n] = x_c[nT] \tag{3.1}$$

where T is the sampling period. A 1D discrete time signal with sampling period of T can be converted into a discrete time signal with sampling period of T'

$$x'[n] = x_c[nT']$$

(3.2)

One approach to obtain x'[n] from x[n] is to reconstruct  $x_c(t)$  by using a reconstruction filter, and a digital to analog converter, and than re-sampling the resultant analog signal with sampling period T'. However, this approach is usually not preferred due to the non ideal characteristic of the reconstruction filter and A/D, D/A filters [4].

#### 3.1.1 Reducing Sampling Rate by an Integer Factor

Sampling rate of the discrete time signal, x[n], in equation (3.1), with sampling period of T, can be reduced by a factor of M by down sampling x[n] at a sampling period of T' = M.T. This process is referred as decimation. Decimation process can be modeled in two steps.

1. Multiplication by an impulse train to replace M-1 samples between every  $M^{th}$  sample with zero to obtain an intermediate signal g[n]

$$g[n] = x[n] \sum_{k=-\infty}^{\infty} \delta(n - kM)$$

(3.3)

2. Discarding the zero samples to obtain the down sampled signal

$$x'[n] = g(Mn) \tag{3.4}$$

Fourier transforms of the signals g[n] and x'[n] can be computed as,

$$G(\omega) = 1/M \sum_{k=0}^{M-1} X(\omega - \frac{2\pi}{M}k) \qquad -\pi \le \omega < \pi$$

(3.5)

$$X'(\omega) = 1/M \sum_{k=0}^{M-1} X(\frac{\omega - 2\pi k}{M}), \quad -\pi \le \omega < \pi$$

(3.6)

The frequency spectrum of the input, and decimated signals for M=2, are illustrated in Figure 3-1 and Figure 3-2 respectively. It must be noted that horizontal axis  $\omega$  in Figure 3-1 and Figure 3-2 is scaled with the sampling period T and T' respectively.

Figure 3-1 :  $X(\varpi)$  , frequency spectrum of the x igl[ n igr] signal

**Figure 3-2 :**  $G(\omega)$ , frequency spectrum of the intermediate signal g[n] and  $X'(\omega)$ , frequency spectrum of the decimated signal x'[n] for M=2

As it can be seen from Figure 3-2 the spectra of the intermediate signal, consists of M replicas of the input signal spectrum in the interval  $[-\pi,\pi]$ , and the frequency spectrum of the decimated signal is expansion of the frequency axis of the intermediate signal spectrum. If the bandwidth of the input signal is greater than 1/2M, then aliasing is observed at the decimated signal. To prevent aliasing at the decimated signal, either the input signal x[n] which was sampled from  $x_c(t)$  must have been over sampled by a factor of M (M times the Nyquist rate), or a digital low pass filter with cut-off frequency of 1/2M must be applied to x[n] prior to decimation. Frequency spectrum of the decimated signal (with antialias filtering) is illustrated in Figure 3-3. It must be noted that horizontal axis  $\omega$  in Figure 3-3-a and Figure 3-3-b is scaled with the sampling period T and T' respectively.

**Figure 3-3**: a)  $X(\omega)$  ,frequency spectrum of the input signal x[n] (Dotted lines represent the antialising low pass filter) and  $X'(\omega)$ , frequency spectrum of the decimated signal x'[n].

#### 3.1.2 Increasing Sampling Rate by an Integer Factor

Sampling rate of the discrete time signal x[n] in Eq. ( 3.1 ), with sampling period of T, can be increased by a factor of L to obtain  $x'[n] = x_c[nT']$  where T' = T/L. This operation is referred as interpolation and using discrete-time operations, the process can be performed in two steps.

1. Up-sampling by zero filling where L-1 zeros are filled between every sample of the input signal. The operation can be modeled as,

$$g(n) = \begin{cases} x[n/L], & \text{if } n=k.L \text{ where } k \text{ is an integer} \\ 0, & \text{otherwise} \end{cases}$$

(3.7)

2. Low pass filtering of the filled in signal.

To analyze the frequency spectrum of the filled-in signal g[n], Fourier transform of the g[n] signal can be written as

$$G(\omega) = X(\omega L) \tag{3.8}$$

The frequency spectrum of the input signal and the filled in signal for L=2, is illustrated in Figure 3-4. It must be noted that horizontal axis  $\omega$  in Figure 3-4-a and Figure 3-4-b is scaled with the sampling period T and T' respectively.

**Figure 3-4 :**  $X[\omega]$ , frequency spectrum of the input signal x[n] and  $G(\omega)$ , frequency spectrum of the filled in signal g[n] for L=2

As it can be seen from Figure 3-4, the filled-in signal spectrum is a compressed version of the input signal spectrum by a factor of L. To remove the replications caused by zero filling, the signal must be filtered using the appropriate low pass filter with cut off frequency of 1/2L.

#### 3.1.3 SD to HD Sampling Rate Conversion

Spatial resolution up-conversion problem is basically the 2D version of the interpolation problem discussed in section 3.1.2 . In the case of SD to HD resolution up-conversion, the problem can be stated as "reverse process of the 2D decimation performed when down scaling the HD video to SD resolution". In theory, it is possible to reconstruct the original HD signal, after decimation and interpolation process, however there are practical limitations.

- 1) To avoid antialising after decimation of the HD resolution signal to SD resolution signal, the HD signal must be over sampled by a factor of M times the Nyquist rate or it must be low pass filtered with  $f_c=1/2M$ . In practice, it is not possible to over sample the original signal by a factor M times the Nyquist rate since video signal is not a band limited signal. Therefore to avoid anti-aliasing, it is common to pass the original signal through a low pass filter, which will remove high frequency components in the signal spectrum. It is not possible to recover these high frequency components in the interpolation process.

- 2) Both decimation and interpolation process requires low pass filtering, and the filtering operations mentioned in section 3.1.2 assume ideal low-pass filters available. However the impulse response of an ideal low pass filter is a *sinc* function and its implementation requires infinite number of input samples, which is not possible in practice. The impulse response of the *sinc* function is approximated by several methods, which are discussed in the following sections.

Figure 3-5 [3] illustrates decimation of a 1-D signal followed by interpolation. It must be noted that the horizontal axis  $\omega$  is scaled with the sampling period. It is clearly seen that the high frequency part of the original signal spectrum is lost. HD - SD -HD conversion is similar to the steps involved in Figure 3-5, the difference being the video signals are 2D signals. The input signal at Figure 3-5a can be treated as the HD signal acquired from a camera, and Figure 3-5c can be treated as the down sampled SD signal which is broadcasted using an SD channel. The output signal at Figure 3-5e can be treated as the HD signal reconstructed from the broadcasted SD signal, using interpolation. Flat panel TV sets' spatial resolution up- conversion performance vary depending on the interpolation performed on the SD signal. Spatial resolution up-conversion problem had been solved in theory [5, 6] and approximations to the theory had been published in [7-10]. Several evaluations and implementations of these approximations are also available in [6-13]. More recently, more advanced methods on spatial resolution up-conversion problem had been published in [14-23] to improve performance on either subjective metrics, or mean squared error(MSE) performance. The conventional linear methods aim to approximate the ideal low pass filter behavior discussed previously, and try to find the optimal low-pass filter, while more advanced methods try recovering the missing spectral component[3].

#### 3.2 Linear methods for up-scaling

Linear up-scaling is performed by convolving an interpolation kernel h[n] with the sampled signal x[n].

$$F(n) = \sum x(k)h(n-k) \tag{3.9}$$

Here, h[n] is basically the time domain impulse response of the low pass filter mentioned in section 3.1.2. For an ideal low pass filter, impulse response must be a *sinc* function, however it is already mentioned that such a filter can not be implemented at practice. Approximations to such a filter are obtained by constructing the convolution kernel based on piecewise polynomial functions.

Figure 3-5: Frequency characteristics of decimation-interpolation process. Frequency spectrum of A) The original signal B) Low pass filtered signal C) Down sampled signal D) Up sampled signal E) Low pass filtered signal

#### 3.2.1 Zero order hold interpolation

This is the simplest method of spatial up-scaling. The 1-D impulse response of the zero order hold interpolation kernel is given as

$$h[n] = \begin{cases} 1, -0.5 \le n \le L - 1 \\ 0, otherwise \end{cases}$$

(3.10)

where L is the scaling ratio.

**Figure 3-6:** h[n], the impulse response of the zero order hold interpolation function for L=3, and illustration of convolution using this kernel

Impulse response of the zero order hold interpolation kernel is given in Figure 3-6. As it can be easily seen from Figure 3-6, the result of performing convolution using the zero older hold interpolation kernel with the SD signal, is the replication of the SD pixels at the output image. Therefore the method is also known as pixel replication. This method is rarely used in TV scalers due to its low image quality.

#### 3.2.2 Linear Interpolation

Another low cost method is to use a first degree piecewise polynomial function, which is obtained by convolving the nearest neighborhood kernel with itself. 1-D impulse response of the linear interpolation kernel is given as;

$$h[n] = \begin{cases} \frac{L - |n|}{L}, & \text{if } 0 \le |n| \le L - 1\\ 0, & \text{otherwise} \end{cases}$$

(3.11)

Figure 3-7 illustrates the impulse response of the linear interpolation kernel for L=3. As it can be seen from the convolution of the impulse response with the input signal, the interpolation process determines the missing signal value by taking the weighted linear average of the neighbor pixels, and the weights of neighbor pixels are proportional to the their distance to the interpolated pixel. For 2D applications,

linear interpolation is referred as bilinear interpolation, and despite its rather low image quality, it is widely used due to its low cost.

Figure 3-7: h[n], impulse response of the linear interpolation kernel for L=3 and illustration of convolution using this kernel

#### 3.2.3 Cubic Interpolation

In cubic interpolation, the impulse response of the ideal low pass filter is approximated using three cubic polynomial pieces. The continuous interpolation kernel of cubic interpolation given in [7] is,

$$h(t) = \begin{cases} 3/2 |t|^3 - 5/2 |t|^2 + 1, & ,0 \le |t| \le 1 \\ -1/2 |t|^3 + 5/2 |t|^2 - 4 |t| + 2 & ,1 \le |t| \le 2 \\ 0 & ,|t| \ge 2 \end{cases}$$

(3.12)

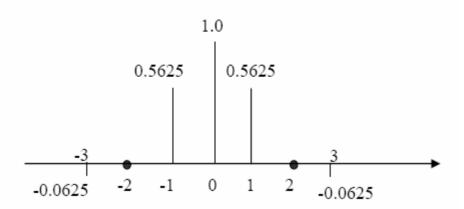

Discrete time impulse response of the cubic convolution interpolation can be obtained sampling h(t) with 4L+1 samples in the interval  $-2 \le t \le 2$ . Figure 3-8 shows the discrete time impulse response sampled in this manner for L=2.

**Figure 3-8:** Impulse response of cubic interpolation function for L=2

#### 3.3 Advanced Methods for up scaling

In section 3.2, conventional linear up-conversion methods were described. The main idea behind these methods is to approximate the time domain impulse response of a *sinc* function, which serves as a low pass filter in frequency domain. As mentioned in section 3.1, even if the low pass filter used in the interpolation stage is ideal, there is still loss of high frequency components, since an antialising low pass filter is used prior to decimation. The main idea behind advanced methods is to recover the missing spectrum at the down sampled image.

#### 3.3.1 Content Adaptive Training Based Methods

The idea behind training based content adaptive methods is to use prior information obtained from training with large sets of images in order to recover the missing spectrum at the down sampled image. Natural images are structured signals and they have considerably less variability than random signals [24]. Training based methods try to exploit the spatial characteristics of image signals prior to interpolation, using large sets of training images. This type of interpolation is performed in two steps, namely the training and the filtering steps.

Computationally intensive training step can be performed offline to reduce implementation complexity and cost. A large set of selected images are processed to extract statistical information about the spatial image characteristics. The information extracted consists of learned spatial structures, typically referred as context classes, and the way these structures are distorted during HD to SD conversion. Investigating the class specific distortions, one can design methods to restore degraded image components (typically high frequency components). Least Mean Square (LMS) method and Expectation Maximization (EM) algorithm are two commonly used techniques in the training stage.

Filtering step is performed on the fly, and typically consists of feature extraction, classification and interpolation stages. Appropriate type of filter kernel is selected at the end of the feature extraction and classification stages, and the selected kernel is used to interpolate the HD pixel from the SD pixel neighborhood.

Several training based interpolation methods are proposed in the literature. In [18] Atkins *et al* proposed a training based method, whose optimization method at the training step is based on expectation maximization algorithm. In [17], Kondo *et al* proposed a training based method where coefficients are obtained based on LMS criterion. In [25], Freeman *et al* proposed a method where HD image is synthesized

block by block, where the blocks are chosen from a database generated during the training step. These methods are briefly described in the following sections.

#### 3.3.1.1 Digital Reality Creation (Kondo's method)

Kondo's method [17] is a training based, content adaptive interpolation method. The coefficients used during interpolation depend on the local content of the image. A classification is performed based on the pattern of the local neighborhood of the processed pixel, and interpolation is performed using the coefficients for the selected class. Filter coefficients are obtained by a training process performed offline. Figure 3-9 illustrates the training process performed. Training process uses the HD video and the SD video as the training material, and uses Least Mean Squares (LMS) criterion to obtain the optimal coefficients. Training process is computationally intensive; however it will not cause any trouble since it is performed only once and offline.

Figure 3-9: Training process performed in Kondo's method

Classification is performed using Adaptive Dynamic Range Coding (ADRC) [24] and equation (3.13) is used when encoding each pixel into 1 bit Q.

$$Q = \left| \frac{F_{SD} - F_{MIN}}{F_{MAX} - F_{MIN}} + 0.5 \right|, \tag{3.13}$$

where  $F_{SD}$  is the SD pixel's luminance value, and  $F_{MAX}$  and  $F_{MIN}$  are the maximum and minimum luminance values around the 3X3 neighborhood of the centre pixel. In case no encoding was used, the number of classes for a 3X3 window would be  $(2^8)^9$  and using equation (3.13), the number of classes is reduced to  $2^9$ .

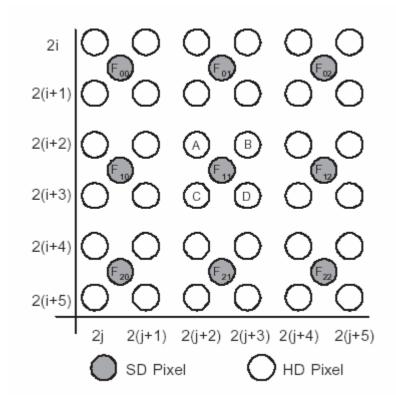

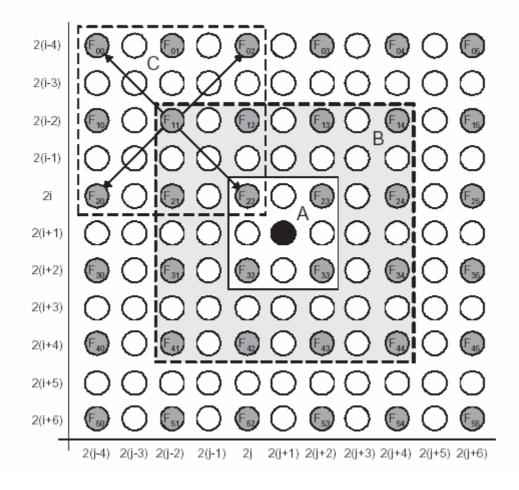

Figure 3-10 illustrates the aperture used in Kondo's method. Gray circles in the figure represent the input SD pixels, and the white circles represent the HD pixels produced. For a scaling factor of L=2, SD pixel  $F_{11}$  will be replaced with 4 HD pixels denoted as A,B,C,D. Gray pixels  $F_{00}$  through  $F_{22}$  illustrate the 3X3 local neighborhood of  $F_{11}$ . The same local neighborhood of the centre pixel is used both in the classification and interpolation steps.

Figure 3-10: Aperture used in Kondo's method. The HD pixels A,B,C,D are interpolated using nine SD pixels,  $(F_{00} \text{ to } F_{22})$

The interpolation of the HD pixels, is performed using equation (3.14);

$$F_{HI}(2(i+2),2(j+2)) = \sum_{k=0}^{2} \sum_{l=0}^{2} W_{kl,c} F_{SD}(2(i+2k)+1),2(j+2l)+1)$$

(3.14)

where  $w_{kl,c}$  are the interpolation filter coefficients for class  $\,c\,$  .

#### 3.3.1.2 Resolution Synthesis (Atkins' Method)

Atkins et al proposed a training based method, referred as Resolution Synthesis(RS), in [18]. The main idea behind RS is stated in [1] as "In a large training set, learn the high resolution image details that correspond to different spatial structures observed at low-resolution, such as edges of different orientations, uniform areas and texture regions, then use those learned relationships to identify and restore the details in other images." The approach is based on recognizing that pixels in natural images can be classified as belonging to a limited number of context classes. These classes are defined by pixel neighborhoods that are visually identifiable such as shown in Figure 3-11. If the size of the local window is 5x5, and each pixel luminance value is quantized at 8 bits, the number of possible patterns is  $2^{8*25}$ , which is practically not possible to deal with.

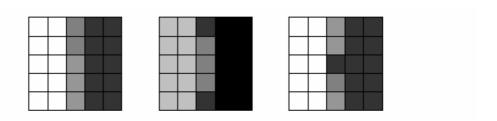

Figure 3-11: 5x5 pixel neighborhoods identified as a vertical edge

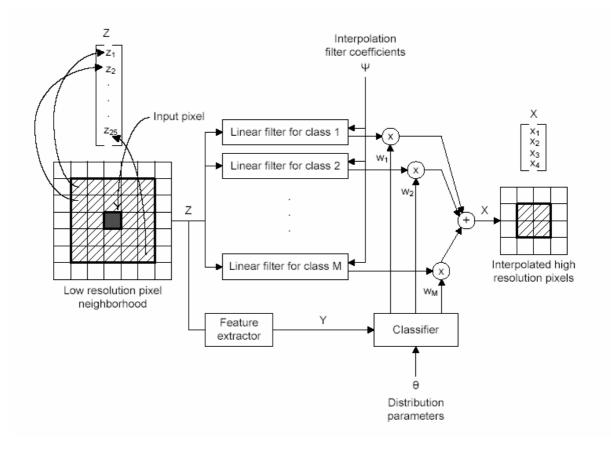

Fortunately, examination of the natural image signals show that number of meaningful spatial structures is limited, and a great rate of the possible patterns can be figured out as noise-like behavior. Even eliminating such noise-like patterns does not reduce the space to be explored; hence one can make use of the dominant spatial structure being the edge direction. If the optimum interpolation filters for the neighborhoods in Figure 3-11 are derived, they would possibly be very close[18]. So instead of assigning a context class to every pixel configuration, a context class can be assigned to large number of configurations with similar spatial structure. In resolution synthesis, number of context classes is fixed and is around 100. Structure of the RS algorithm predictor is depicted in[1] as in Figure 3-12.

As it is seen in the figure, the structures of Kondo's and Atkins' methods are similar, the difference being how classification blocks are implemented. While Kondo's method uses ADRC [24] in classification, Atkins' method uses Expectation Maximization algorithm [26].

Figure 3-12: Structure of the RS predictor.

RS algorithm can be performed in 3 steps:

1) Feature Extraction: This is the first step of the algorithm to obtain the 8x1 classification vector  $\vec{y}$  which is defined as:

$$\vec{y} = \begin{cases} \vec{\tilde{y}} \parallel \vec{\tilde{y}} \parallel^{-0.75} & , \vec{\tilde{y}} \neq 0 \\ 0 & , \text{otherwise} \end{cases}$$

(3.15)

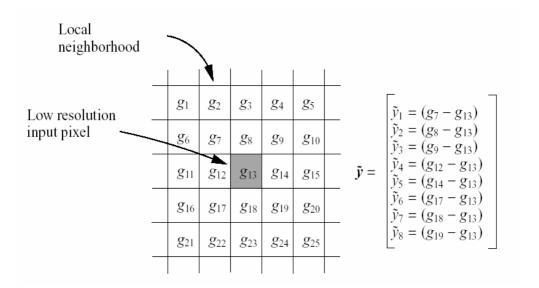

The  $\vec{\tilde{y}}$  vector is an 8x1 vector constructed by the difference of the centre pixel with each neighbor pixel in the classification aperture in Figure 3-13 and  $\vec{y}$  vector is the normalized version of the  $\vec{\tilde{y}}$  vector, whose elements are given as :

$$\frac{\bar{\tilde{y}}_i}{\left[\sum_{i=1}^8 \bar{\tilde{y}}^2\right]^p} \tag{3.16}$$

where p is a parameter to control the amount of normalization. Feature vectors are normalized to unit length when p is selected as 1 and no normalization is performed when p = 0. In [18], p value is obtained as 0.75 experimentally.

Figure 3-13: Extraction of the  $\vec{\tilde{y}}$  vector

**2**) **Context classification**: In this step, classification vector  $\vec{y}$  is compared with the representative vector  $\overrightarrow{RV}_c$  of the  $c^{th}$  class to calculate  $P(c \mid \vec{y})$ , the probability that the current neighborhood belongs to class c, which is given as:

$$P(c \mid \vec{y}) = \frac{CW_c \exp(\frac{-\|\vec{y} - RV_c\|^2}{2VAR})}{\sum_{d=0}^{M} CW_d \exp(\frac{-\|\vec{y} - RV_d\|^2}{2VAR})}$$

(3.17)

Representative vector,  $\overrightarrow{RV}$ , represents the class, class weight, CW, indicates the global probability of the class, and the variance, VAR, indicates the average distance of the representative vector and the mean of the representative vector. These parameters are obtained for each class using EM algorithm at training stage.

3) Filtering: High resolution pixels are calculated by first filtering the low resolution block with filters from each class, and then taking the linear weighted average of the filter outputs, where weighting coefficient of each filter is its corresponding  $P(c \mid \vec{y})$  value. The same aperture in Kondo's method is used for Atkins' method. From the definition, high resolution pixel A is calculated as

$$F_{HI}(2(i+2),2(j+2)) = \sum_{c=0}^{M-1} \sum_{k=0}^{2} \sum_{l=0}^{2} (a_{c,kl} F_{SD}(2(i+2k)+1,2(j+2l)+1) + b_{c,ij}) P(c \mid \vec{y})$$

(3.18)

Where a is a 4x9 matrix and b is a 4x1 matrix of class c, each row corresponding to coefficients to interpolate high resolution pixels A,B,C,D.

#### 3.3.1.3 Example Based Super Resolution

Example based super resolution is different from Kondo's and Atkins' method both in the classification and reconstruction step. In example based super resolution, the input image is decomposed into low frequency and high frequency components. Low frequency image is obtained by first blurring and sub sampling the original high resolution image and then scaling back this image to its original size using a linear interpolation method. By this way, an image of desired size that lacks high resolution detail is obtained. In the training set, the differences between the high resolution image and linear interpolated image are stored. High resolution patches corresponding to every possible low-resolution image patch, typically of 5x5 and 7x7 pixels, are stored. The detail component of the image is obtained by combining the high resolution patches. The prior information obtained at the training step provides statistical information on which low resolution patch typically corresponds to which high resolution patch, and this information is used to reconstruct the high resolution details of the image. For its constraints on huge storage of patches, cost of the method is high for real time implementation.

#### 3.3.2 Directional Interpolation Methods

New Edge Directed Interpolation (NEDI) proposed in [14] is the typical sample of a directional interpolation method. NEDI aims to interpolate along edges rather than across them to prevent blurring. NEDI differs from Kondo's and Atkins' method in the place coefficient optimization is performed. The optimization of the interpolation coefficients is performed by applying an LMS algorithm on-the-fly. The main advantage on performance is that the local neighborhood does not need any simplification. The disadvantage is that more calculations are required for optimization since the original image is not available. Figure 3-14 shows the aperture used in NEDI.

NEDI algorithm uses the following formulae for interpolation.

$$F_{HI}(2(i+1),2(j+1)) = \sum_{k=0}^{1} \sum_{l=0}^{1} w_{2k+l} F_{SD}(2(i+2k),2(j+2l))$$

(3.19)

where w coefficients in the formulae are computed at the runtime using LMS criterion. The sum of squared errors over a set S in the optimization is written as

the sum of squared differences between the original SD pixels and interpolated SD pixels. Sum of squared error(SSE) is given as :

$$SSE = \sum_{i,j} (F_{SD}(2i+2,2j+2) - F_{HI}(2i+2,2j+2))^{2}$$

(3.20)

Substituting  $F_{\rm HI}$  in equation ( 3.20 ) and writing the equation in matrix form, SSE is written as :

$$SSE = ||\vec{y} - \vec{w}C||^2$$

(3.21)

where  $\vec{y}$  is the vector of SD pixels in S, and C is a  $4xS^2$  matrix whose  $k^{th}$  row contains 4 diagonal SD neighbors of the  $k^{th}$  SD pixel in  $\vec{y}$  vector. To find the minimum SSE, the derivative of SSE over  $\vec{w}$  must be 0 hence  $\vec{w}$  is obtained as :

$$\vec{w} = (C^T C)^{-1} (C^T \vec{y}) \tag{3.22}$$

Figure 3-14: Aperture used in NEDI

The computation of the coefficient matrix used at the interpolation step is more costly than the interpolation step itself, which brings a major disadvantage for the real-time implementation of the algorithm.

#### 3.3.3 Other Methods

Other than the training based methods, and the directional interpolation based methods, there exists other advanced algorithms proposed for video up-scaling problem. In [19-21] image interpolation is performed using neural networks. In [16], frequency domain operations are used. In [22], SD image is up scaled using a linear scaling algorithm and a non linear sharpening method, Luminance Transient Improvement (LTI) [27] is applied to the scaled image, to recover the high frequency components lost during the decimation process. There are several other methods which are either similar to or derived from the methods discussed in previous sections. These are out of scope for this study, hence are not mentioned in this section.

#### 3.4 Video Performance Evaluation of the Methods

Evaluation of video enhancement algorithms is quite tricky since the aim of video enhancement algorithms is to improve the perceived image quality which is subjective. After all, the target is the human eye, and the success of the algorithm might differ with the user's taste. There exist subjective evaluation techniques which usually make use of a group of trained and non-trained eyes, to evaluate an algorithm's performance; however such processes are expensive, slow and hard to manage. Several image quality metrics have been proposed in the literature which aims to correlate well with perceived image quality. Though not being closely correlated with perceived image quality, some simple metrics like mean square error (MSE), or Peak Signal to Noise Ratio (PSNR) are also widely used to evaluate an algorithm's performance. In many of the scientific researches, MSE is taken as the major metric to compare the algorithms' performance. In [3], the algorithms discussed in previous sections (Example based super resolution in [25] being the exception) are also compared and evaluated using MSE criterion and subjective tests. In this evaluation, four still images and seven video sequences were used, with several spatial characteristics. In objective evaluation, MSE criterion is used with with the formulae:

$$MSE = \frac{1}{N} \sum_{i,j} (F(i,j) - G(i,j))^{2}$$

(3.23)

where F(i,j) is the luminance value of the  $i^{th}$  row,  $j^{th}$  column in the original high resolution image, and G(i,j) is the luminance value of the same spatial location in the up converted image. N is the number of pixels in the images. Table 3-1 shows the results of objective evaluation, performed in [3].

**Table 3-1**: MSE performance evaluation performed in [3]

|                      | Bilin<br>ear<br>Int. | cubic<br>Int.<br>Keys<br>kernel | cubic int.<br>Mitchell<br>Netravali<br>kernel | Kondo's<br>method | Atkins'<br>met. | Plaziac's<br>met. | Li's<br>met. | Greenspan'<br>s method | Tegen<br>bosch'<br>s met. |

|----------------------|----------------------|---------------------------------|-----------------------------------------------|-------------------|-----------------|-------------------|--------------|------------------------|---------------------------|

| Average<br>MSE Score | 120.<br>2            | 101.2                           | 111.4                                         | 92.3              | 95.0            | 104.2             | 117.0        | 101.4                  | 203.3                     |

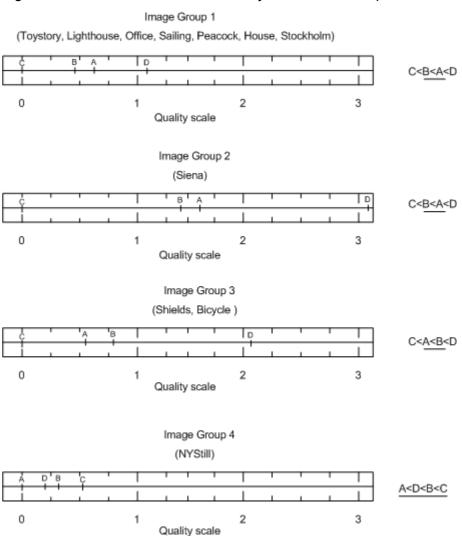

Figure 3-15 illustrates the results of subjective evaluation performed in [3].

**Figure 3-15 :** Subjective evaluation performed in [3] ( A : Cubic B-spline interpolation, B: Kondo's method, C: Li's method, D: Tegenbosch's method )

The subjective comparison is performed for four of the algorithms. In the figure, higher value horizontal scale represents higher perceived image quality. In the subjective evaluation, it is observed that optimal MSE score does not guarantee the best perceived image quality, since Tegenbosch's method [22], which gives poor MSE scores can be found to have a better perceived image quality by user. However it is also stated that MSE is the most appropriate start point for further enhancement in the perceived image quality. It must be also noted that Tegenbosch's method performs LTI over a bicubic based linear interpolation method, and further research on applying appropriate LTI over a training based interpolation may have the potential to get better perceived image quality as well as MSE score. More details on both subjective and objective evaluation of the algorithms, including the test pictures for each image group can be found in [28].

#### 4. MODIFIED RESOLUTION SYNTHESIS

#### 4.1 Overview

In chapter 3, it has been shown that scaling an image by linear filtering can not bring back the high frequency components degraded (reduced to noise level, completely filtered out or aliased) during sampling. This is where advanced resolution upconversion techniques (which are also referred as resolution enhancement techniques) differ from linear scaling techniques. Resolution enhancement techniques can recover the missing or aliased high frequency components to a limited extent by estimating the missing high frequency components through spatially adaptive filtering and use of prior information. The main improvement offered by single frame resolution enhancement is observed around edges and textured areas. Compared to the results obtained by linear scaling filters such as bicubic interpolation combined with unsharpen filtering, techniques such as the resolution synthesis [18] algorithm can offer much smoother, continuous edges with sharp transitions, remove the blurry look from textured areas and rectify slight aliasing artifacts (where aliased signal components can not disturb the dominant spatial structure). Several content adaptive methods were considered to be a start point for the work done in this thesis, and resolution synthesis [18] was taken as the start point since it had performed well in terms of MSE and perceptive image quality. The details of the algorithm had been given in section 3.3.1.2.

In its current form, resolution synthesis is computationally too demanding for systems with limited computational resources and memory. The high computational load is mainly due to the large number of classes required for satisfactory performance (typically anywhere between 30-100) and the requirement for weighted combination (soft filtering) in Eq. (3.18). Linear combination is especially demanding since it requires repeating application of a 5×5 filter, implying 25 additional multiplications and an additional accumulation for every class included in soft filtering. In addition, the combination weights ( $P(c \mid \bar{y})$ 's in equation (3.17) must be computed to obtain the final result. In [1] several trials were performed to reduce the complexity of RS. It is observed that directly reducing the number of classes (below ~30) severely degrades performance. Also using only one class (the class with maximum membership) to compute the high resolution pixels results in degraded performance. It is found out that the discrimination power of the feature vectors

defined by equation (3.15) was severely degraded as the number of context classes was reduced below ~ 25. These shortcomings render resolution synthesis useless for customer grade flat panel displays, where the computational complexity must be kept below some threshold. The goal in [1] is to introduce some modifications so that RS can operate satisfactorily with as low as 5 context classes using hard decision (using a single class in filtering).

# 4.2 Algorithm Description

Modified RS scheme consists of two phases, namely the offline training phase, and the online filtering phase.

# 4.2.1 Offline Training Phase

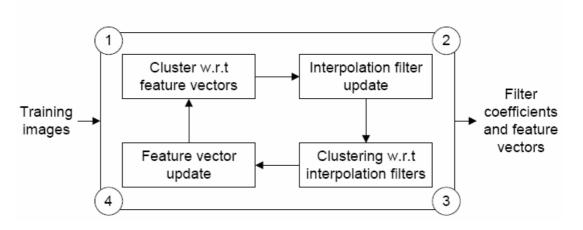

Proposed training method in [1] is shown in Figure 4-1. It is based on the observation that interpolation filter design stage has direct access to the high resolution pixels. If one can couple interpolation filters to the feature extraction and classification stages, the resulting clustering should improve. Given the low and high resolution training images, proposed method iteratively extracts the best interpolation filters and the context class prototypes that are used to determine input pixel's context.

Figure 4-1: Proposed training scheme in [1]

The iterative training works as follows.

#### 0.Initialization:

After extracting the feature vectors of all the low resolution pixels in the training set, class prototypes are initialized randomly. The prototype for class number 1 is manually set to a vector of all zeros. This guarantees that a class is reserved for uniform areas. All covariance matrices are set to identity matrices.

## 1. Clustering with respect to features:

After initialization, the low resolution pixels are classified with respect to their feature vectors. This is done by going through all low resolution pixels, computing the weighted Euclidian distance (the weighting matrix is the inverse of feature covariance matrix) between the pixel's feature vector, which is a representative of the local image characteristic of the low resolution pixel and the cluster prototypes, which are representatives of different context classes. Then the input low resolution pixel is labeled with the index of the cluster whose feature vector is the closest to the low resolution pixel's feature vector.

# 2. Filter update:

Once the low resolution pixels are clustered with respect to their feature vectors (context) the interpolation filters for all clusters are updated with the filter that minimizes the mean squared error between the interpolated and the true high resolution pixels computed for all low resolution pixels in a specific cluster. While preparing the training samples, a small amount of blurring prior to down sampling is necessary to model the camera response and also to avoid aliasing. But completely filtering out the high frequency components effectively creates an inverse problem where the filters are asked to bring back completely removed signal components (this is only possible in multi-frame case), resulting in bad filters.

## 3. Clustering with respect to filters:

After filter update, all the input pixels are clustered with respect to the minimum mean-squared-error interpolation filter. This is accomplished by going through all low-resolution training pixels, computing the interpolated high resolution pixels one by one, and comparing the interpolated pixels to the available high resolution pixels. The low resolution pixel is then labeled with the index of the interpolation filter that gives the minimum mean-squared-error between the interpolated and real high resolution pixels.

## Class prototype update :

Once all the input pixels are classified, the feature vectors of the obtained clusters are updated one by one. This update can be done in various different ways such as taking the average of the median of the feature vectors. Class covariance matrices are updated next. To reduce computational complexity, diagonal covariance matrices are assumed. Then the algorithm steps back to step 1, clustering with respect to features, and iterate in this fashion for predetermined times. In [1] the experiments are done with 2 iterations.

# 4.2.2 Online Content Adaptive Filtering Phase

At the end of offline training phase, for each class i; an 8x1 representative vector  $\bar{C}_i$ , each of which represents a class, an 8x1 variance set,  $\sigma_i$ , which indicates the average distance of each representative vector and the mean of the representative vectors, and four 5x5 interpolation filter kernels  $K_{i00}, K_{i01}, K_{i10}, K_{i11}$  are calculated.

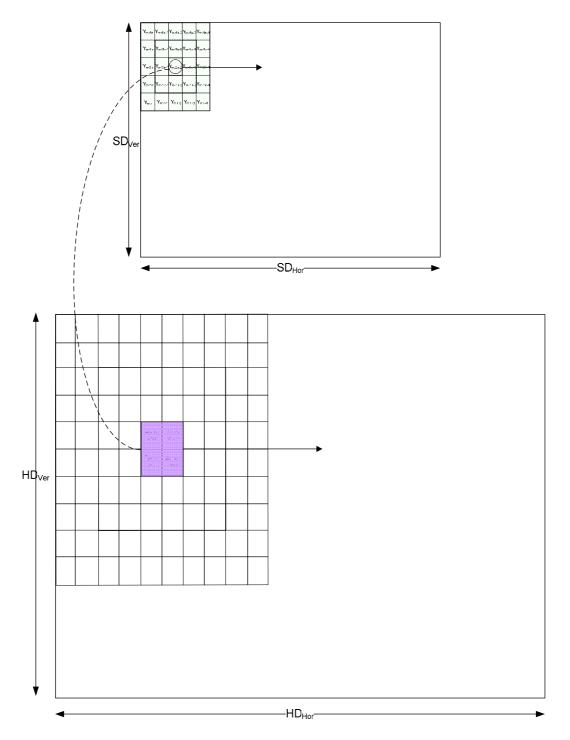

Figure 4-2: Up conversion of SD resolution image to HD resolution image

Once the offline training phase is completed and  $\bar{C}_i$ ,  $\sigma_i$  and  $K_{i00}$ ,  $K_{i01}$ ,  $K_{i10}$ ,  $K_{i11}$  values for each class is computed, online computations can be started to up-convert an SD resolution image to an HD resolution image as shown in Figure 4-2.

# The inputs to the algorithm are

- the image matrix Y of size  $SD_{Hor}xSD_{Ver}$ , with each element  $Y_{mn}$  of the matrix representing the luminance value of  $m^{th}$  row,  $n^{th}$  column of the low resolution image.

- representative vectors  $\vec{C}_i$  of size 8x1 for each class i.

- set of normalization constants  $\sigma_i$  of size 8x1 for each class i.

- Four 5x5 filter kernels  $K_{i00}$ ,  $K_{i01}$ ,  $K_{i10}$ ,  $K_{i11}$  for each class i.

# The output of the algorithm is

• The  $HD_{Ver}xHD_{Hor}$  image matrix Z with each element  $Z_{mn}$  of the matrix representing the luminance value of  $m^{th}$  row,  $n^{th}$  column of the high resolution image.

The algorithm consists of three stages, namely, feature extraction, context classification, and filtering. Feature extraction and context classification is performed for every pixel of the input SD image, and filtering is performed for every pixel of the output HD image. The aperture used in these stages, is shown in Figure 4-3

| Y <sub>m-4,n</sub> | Y <sub>m-4,n-1</sub>        | Y <sub>m-4,n-2</sub> | Y <sub>m-4,n-3</sub> | Y <sub>m-4,n-4</sub> |

|--------------------|-----------------------------|----------------------|----------------------|----------------------|

| Y <sub>m-3,n</sub> | <b>Y</b> <sub>m-3,n-1</sub> | Y <sub>m-3,n-2</sub> | Y <sub>m-3,n-3</sub> | Y <sub>m-3,n-4</sub> |

| Y <sub>m-2,n</sub> | Y <sub>m-2,n-1</sub>        | Y <sub>m-2,n-2</sub> | Y <sub>m-2,n-3</sub> | Y <sub>m-2,n-4</sub> |

| Y <sub>m-1,n</sub> | Y <sub>m-1,n-1</sub>        | Y <sub>m-1,n-2</sub> | Y <sub>m-1,n-3</sub> | Y <sub>m-1,n-4</sub> |

| Y <sub>m,n</sub>   | Y <sub>m,n-1</sub>          | Y <sub>m,r-2</sub>   | Y <sub>m,n-3</sub>   | Y <sub>m,n-4</sub>   |

Figure 4-3: Aperture used in Modified Resolution Synthesis

#### 4.2.2.1 Feature Extraction

In the feature extraction stage, for every SD input pixel, the feature vector of the pixel is extracted from a 3×3 local neighborhood. The feature vectors will be denoted as  $\phi$ . To obtain the feature vector, first, an 8x1 vector is obtained by subtracting the centre pixel value  $Y_{m-2,n-2}$  from its 8 neighbors and taking the 4<sup>th</sup> power of the difference. The elements of the 8x1 feature vector are given as,

$$FV_{1} = (Y_{m-2,n-2} - Y_{m-3,n-1})^{4}$$

$$FV_{2} = (Y_{m-2,n-2} - Y_{m-3,n-2})^{4}$$

$$FV_{3} = (Y_{m-2,n-2} - Y_{m-3,n-3})^{4}$$

$$FV_{4} = (Y_{m-2,n-2} - Y_{m-2,n-1})^{4}$$

$$FV_{5} = (Y_{m-2,n-2} - Y_{m-2,n-3})^{4}$$

$$FV_{6} = (Y_{m-2,n-2} - Y_{m-1,n-1})^{4}$$

$$FV_{7} = (Y_{m-2,n-2} - Y_{m-1,n-2})^{4}$$

$$FV_{8} = (Y_{m-2,n-2} - Y_{m-1,n-3})^{4}$$

Then the resultant vector FV is normalized obtain the normalized feature vector  $\phi$ . The following equation shows the mapping used to obtain each element of the normalized feature vector  $\phi$

$$\phi_i = \frac{FV_i}{(\sum_{i=1}^8 FV_j^2)^{0.75}} \tag{4.2}$$

## 4.2.2.2 Context classification

In the context classification stage, the feature vector  $\phi$  obtained in the previous step is compared to five predetermined  $\vec{C}_i$  vectors namely the representative vectors of each class. The distance between the feature vector  $\phi$  and the representative vector of class i,  $\vec{C}_i$  is computed as

$$d_{i} = \|\phi - \vec{C}_{i}\| = \sum_{j=1}^{8} \frac{(\phi_{j} - C_{i,j})^{2}}{\sigma_{i,j}}$$

$i = 1,2,3,4,5$  (4.3)

That is, the distance between  $\phi$  and  $\bar{C}_i$  is the sum of squared differences between the corresponding entries of each vector divided by normalizing constants. The context class that is closest to the  $\phi$  vector (with minimum  $d_i$ ) is declared as the context of the current low resolution pixel  $Y_{m-2,n-2}$ , and its index cl is passed to the

interpolation stage. It must be noted that the  $\bar{C}_i$  vectors and the  $\sigma_i$  normalizing constants are different for every class and they are pre-computed in the training phase.

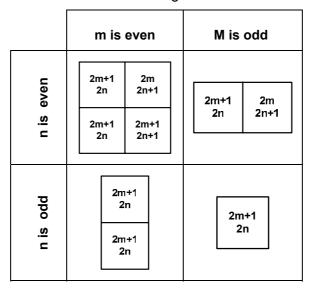

## 4.2.2.3 Filtering

In the filtering stage, index passed by the context classification step is used to pick the interpolation filter corresponding to the context class of the current low resolution pixel. Interpolation is performed for every HD pixel, therefore the iteration is not performed in the SD input image, but on the HD output image to be created. For every output pixel at the HD output image, first the corresponding vertical and horizontal SD image coordinates  $y_{\nu}$  and  $y_h$ , are computed using the following formula:

$$y_{v} = \left| \frac{z_{v}}{L} \right|, y_{h} = \left| \frac{z_{h}}{L} \right| \tag{4.4}$$

where,  $z_v$  and  $z_h$  are the horizontal and vertical coordinates of the HD pixel and L is the scaling ratio. Then the horizontal and vertical phases hp and vp of the output pixel is computed using the following formula:

$$hp = \left| Q_h x \left( \frac{z_h}{L} - y_h \right) + \varepsilon \right| \tag{4.5}$$

$$vp = \left| Q_{v}x(\frac{z_{v}}{L} - y_{v}) + \varepsilon \right|$$

(4.6)

where  $Q_v$  and  $Q_h$  are the vertical and horizontal quantization values set as 2 in [1].

Using the context class index cl, horizontal phase hp and vertical phase vp, 5x5 interpolation kernel  $K_{cl,hp,vp}$  is selected for the output pixel, and the interpolation of the output pixel is performed by convolving the 5x5 neighborhood of the corresponding SD coordinates, with the selected kernel. For the output pixel coordinate of  $Z_{2(m-2),2(n-2)}$  the corresponding SD input pixel will be  $Y_{m-2,n-2}$ , from Eq.( 4.4 ) and hp and vp will be both zero from Eq.( 4.5 ) and Eq.( 4.6 ). The selected filter will be  $K_{cl,00}$  (denoted as K in Eq.( 4.7 )) and the interpolation output will be computed by

$$Z_{2(m-2),2(n-2)} = \sum_{i=-2}^{2} \sum_{j=-2}^{2} Y_{m-2+i,n-2+j} K_{ij}$$

(4.7)

Pseudo code of the online filtering phase of the modified resolution synthesis algorithm is given in Figure 4-4.

```

Inputs: Y = (SD_{hor}xSD_{ver}) input image matrix, \vec{C}_c (8x1 representative

vector for each class), \sigma_{c} (8x1 normalization constant set for each

class), K_{c00}, K_{c01}, K_{c10}, K_{c11} (four kernel of size 5x5 for each class),

c = 1, 2, 3, 4, 5

Output: Z = HD_{Ver}xHD_{Hor} output image matrix

for m from 2 to SD_{ver}-2 do

for n from 2 to SD_{hor}-2 do

SFV := 0

for i = -1 to 1 do

for j = -1 to 1 do

FV_{3(i+1)+(j+1)} = (Y_{m,n} - Y_{m+i,n+j})^4

SFV = SFV + (FV_{3(i+1)+(j+1)})^2

SFV = SFV^{0.75}

for i = -1 to 1 do

for j = -1 to 1 do

\phi_{3(i+1)+(i+1)} = FV_{3(i+1)+(i+1)} / SFV

for c = 1 to 5 do

for k=1 to 8 do

d_c = d_c + \frac{(\phi_k - C_{c,k})^2}{\sigma_{c,k}}

\mathtt{cl}_{\mathtt{m,n}} = index_of( Min (d_c))

c = 1, 2, 3, 4, 5

for s from 2 to HD_{ver}-4 do

for t from 2 to HD_{hor}-4 do

compute SD coordinates m,n corresponding to s,t

Select the class of the filter {\tt cl_{m,n}}

Select the vertical and horizontal phase of the filter

Select the appropriate filter K using vp,hp, and cl_{m,n}

for x = -2 to 2 do

for y= -2 to 2 do

Z_{s,t} = Z_{s,t} + Y_{m-x,n-y} * K_{x,y}

```

Figure 4-4: Pseudo code of the Modified RS algorithm

# 4.3 Visual Quality Results