## <u>İSTANBUL TECHNICAL UNIVERSITY</u> ★ <u>INSTITUTE OF SCIENCE AND TECHNOLOGY</u>

## A NOVEL MICRO PIEZOELECTRIC ENERGY HARVESTING SYSTEM

Ph.D. Thesis by Tolga KAYA, M.Sc.

**Department:** Electronics and Communication Engineering

**Programme:** Electronics Engineering

## <u>İSTANBUL TECHNICAL UNIVERSITY</u> ★ <u>INSTITUTE OF SCIENCE AND TECHNOLOGY</u>

# A NOVEL MICRO PIEZOELECTRIC ENERGY HARVESTING SYSTEM

Ph.D. Thesis by Tolga KAYA, M.Sc. (504022101)

Date of submission: 19 July 2007

Date of defence examination: 15 August 2007

Supervisor (Chairman): Prof. Dr. Ali ZEKİ

Co-supervisor: Assist.Prof.Dr. Hür KÖŞER (Yale U.)

Members of the Examining Committee: Prof.Dr. Uğur ÇİLİNGİROĞLU

(Yeditepe U.)

Prof.Dr. Ali TOKER

Prof.Dr. Oğuzhan ÇİÇEKOĞLU (B.U.)

Assoc. Prof.Dr. Serdar ÖZOĞUZ

Assist.Prof.Dr. Devrim YILMAZ AKSIN

**AUGUST 2007**

## <u>İSTANBUL TEKNİK ÜNİVERSİTESİ</u> ★ FEN BİLİMLERİ ENSTİTÜSÜ

## YENİ BİR MİKRO PİEZOELEKTRİK ENERJİ HARMANLAYICI SİSTEMİ

## DOKTORA TEZİ Y. Müh. Tolga KAYA (504022101)

Tezin Enstitüye Verildiği Tarih: 19 Temmuz 2007

Tezin Savunulduğu Tarih: 15 Ağustos 2007

Tez Danışmanı: Prof. Dr. Ali ZEKİ

Eş Danışman: Yrd.Doç.Dr. Hür KÖŞER (Yale Ü.)

Diğer Jüri Üyeleri: Prof.Dr. Uğur ÇİLİNGİROĞLU

(Yeditepe Ü.)

Prof.Dr. Ali TOKER

Prof.Dr. Oğuzhan ÇİÇEKOĞLU (B.Ü.)

Doç.Dr. Serdar ÖZOĞUZ

Yrd.Doç.Dr. Devrim YILMAZ AKSIN

**AĞUSTOS 2007**

#### **ACKNOWLEDGEMENT**

First of all, I would like to thank my supervisors Prof. Dr. Ali Zeki and Assist. Prof. Dr. Hür Köşer for their great support. I am grateful to my thesis committee, Prof. Dr. Ali Toker, Prof. Dr. Uğur Cilingiroğlu, Prof. Dr. Oğuzhan Çiçekoğlu, Assoc. Prof. Dr. Serdar Özoğuz and Assist. Prof. Dr. Devrim Yılmaz Aksın for their valuable inputs and recommendations.

I am very thankful to ETA Asic Design Center and Micro where I have gained a lot of design insight and experience since 1998.

My colleagues at Yale; Bozidar, Muhammet, Leidong and at ITU; Uğur, Başak, Özgür, they have all supported me not only with their friendship but with their useful helps as well. Halil has worked a lot for the design of the mechanical switch for his M.Sc. study under my supervision which helped me a lot.

All my professors at ITU have believed in me and their belief made me work harder. My cheerful VLSI students have always made me laugh and reminded me why I'm happy in the academic life.

I have not only enjoyed during these years but also suffered a lot. I am sure my departed grandmother would really like to see me graduate. Therefore, I have to thank my grandfather whom I felt he is always with me. My family, dad and mom, you are so great, I'm proud of being your children and I'm sure you will always with me whatever it happens. My brother, you always loved me and supported me even if I couldn't be with you as much. Melissa, my dear niece, you are my flower, your love always kept me alive.

I guess I have to thank Funda. I have never regretted spending 5 years of marriage and sharing life with her. My grandmother used to say "The phoenix chirps once a year for only one couple and you are the one!" I hope both of us will be happy in the future without each other.

I was trying to recover from a long sleep of deep sadness when Ayşen shone to my life and her joyful love woke me up. Unfortunately, I couldn't carry this relationship. I can just expect her to forgive me. Thank you for everything.

One of my biggest gain is our wine degustation group. Fidel and Tarık, then Keklik, Barış and Fatma; you helped me to spend a lot of great moments during my unproductive social life.

My long term friends; Volkan, Baran, Burcu, Ebru, Sertaç and Roda; you are so great and you were always there when I needed you.

August, 2007 Tolga KAYA

## TABLE OF CONTENTS

| ABBREVIATIONS LIST OF TABLES LIST OF FIGURES ABSTRACT ÖZET       | vii<br>viii<br>ix<br>xiii<br>xv |

|------------------------------------------------------------------|---------------------------------|

| 1. INTRODUCTION                                                  | 1                               |

| 1.1 History and Motivation                                       | 1                               |

| 1.2 MEMS Energy Scavenger Concept                                | 4                               |

| 1.2.1 Introduction                                               | 4                               |

| 1.2.2 Examples of commercial energy harvesters                   | 4                               |

| 1.2.3 Piezoelectricity                                           | 7                               |

| 1.2.4 Vibration energy scavengers                                | 9                               |

| 1.2.5 Current state of the art in piezoelectric-based harvesters | 10                              |

| 1.2.6 Fundamental limitations and a solution potential           | 11                              |

| 1.3 Contribution                                                 | 13                              |

| 1.4 Thesis Organization                                          | 15                              |

| 2. A NOVEL MEMS ENERGY HARVESTER SYSTEM DESIGN                   | 16                              |

| 2.1 The Underlying Concept                                       | 16                              |

| 2.2 Inherent Advantages of the Proposed Design                   | 17                              |

| 2.3 Analytical Modeling                                          | 20                              |

| 2.3.1 Basic simplification for models                            | 20                              |

| 2.3.2 Small deflection linear model                              | 20                              |

| 2.3.3 Large deflection, nonlinear model                          | 24                              |

| 2.3.4 Optimization of the non-linear spring constant             | 26                              |

| 2.4 Simulink Model                                               | 27                              |

| 2.4.1 Simulation results for continuous vibration inputs         | 34                              |

| 2.4.2 Simulation results for shock inputs                        | 37                              |

| 2.5 Mechanical Switch                                            | 39                              |

| 2.5.1 The hysteresis behavior                                    | 41                              |

| 2.5.2 The frequency response                                     | 44                              |

| 3. FABRICATION                                                   | 47                              |

| 3.1 Fabrication Flow                                             | 47                              |

|   | 3.2 MEMS Back-Side Fabrication                        | 48 |

|---|-------------------------------------------------------|----|

|   | 3.2.1 Bulk etchant alternatives                       | 48 |

|   | 3.2.2 KOH etch overview                               | 50 |

|   | 3.2.3 Back side etch procedure                        | 51 |

|   | 3.2.4 Design of the back side mask                    | 52 |

|   | 3.2.5 Front side protection                           | 57 |

|   | 3.3 MEMS Front Side Fabrication                       | 58 |

|   | 3.3.1 PDMS patterning                                 | 59 |

|   | 3.3.2 Reactive ion etching                            | 60 |

|   | 3.4 A Novel MEMS Packaging Method                     | 62 |

|   | 3.5 Silicon Stress Tests                              | 64 |

|   | 3.6 PZT Deposition                                    | 65 |

|   | 3.6.1 Fabrication method for the metal electrodes     | 66 |

|   | 3.6.2 Fabrication of the electrodes for $d_{33}$ mode | 67 |

|   | 3.7 Ongoing Fabrication and Tests                     | 69 |

| 4 | . COMBINING "SMART SAND" WITH THE RFID CONCEPT        | 72 |

|   | 4.1 Wireless Data Transmission Possibilities          | 72 |

|   | 4.2 Introduction to RFID Systems                      | 73 |

|   | 4.2.1 Current uses of rfid tags                       | 76 |

|   | 4.2.2 Potential uses of active and passive rfid tags  | 77 |

|   | 4.3 A New Proposed RFID Concept: Smart RFID           | 78 |

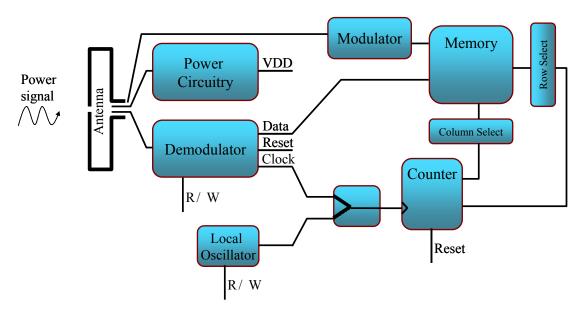

|   | 4.3.1 System overview                                 | 78 |

|   | 4.3.2 Antenna and the matching network                | 79 |

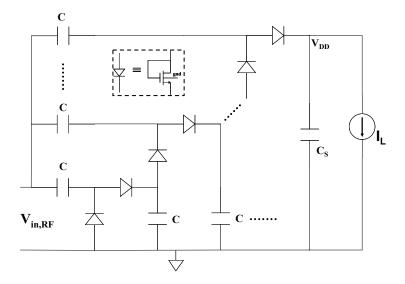

|   | 4.3.3 Voltage multiplier and rectifier                | 80 |

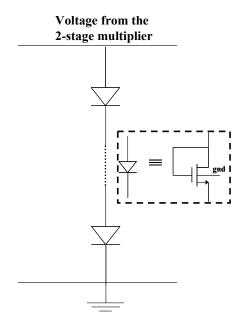

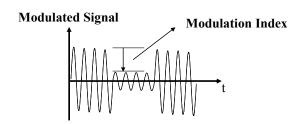

|   | 4.3.4 Demodulator                                     | 82 |

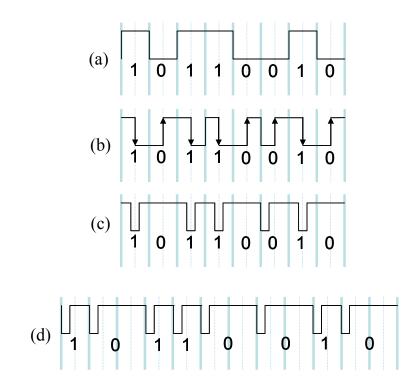

|   | 4.3.5 Modulator and clock generation                  | 84 |

|   | 4.3.6 Control logic                                   | 86 |

|   | 4.3.7 Memory                                          | 86 |

|   | 4.3.7.1 Floating gate nvram topologies                | 87 |

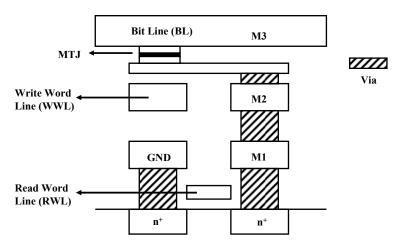

|   | 4.3.7.2 Magnetic ram cells                            | 88 |

|   | 4.3.7.3 Other memory alternatives                     | 90 |

|   | 4.3.7.4 Comparison of the memory cells                | 91 |

|   | 4.4 Potential Applications of "smart RFID"            | 92 |

|   | 4.4.1 Package delivery: drop sensor                   | 92 |

|   | 4.4.2 Homeland security: surveillance monitoring      | 93 |

|   | 4.4.3 Perishable food: temperature monitoring         | 95 |

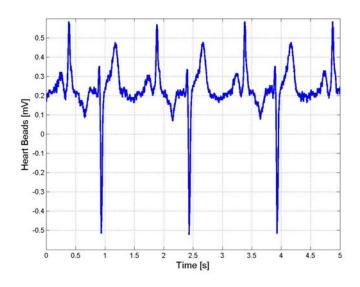

|   | 4.4.4 Heart rate sensor                               | 96 |

|   | 4.5 RFID Circuit Design                               | 97 |

| 4.5.1 System overview and design considerations        | 98  |

|--------------------------------------------------------|-----|

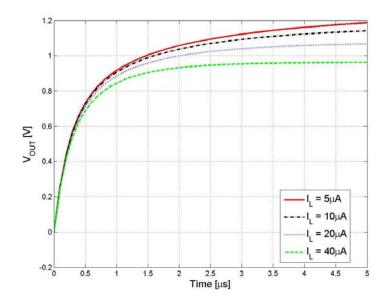

| 4.5.2 2-stage voltage multiplier and clamper           | 99  |

| 4.5.3 Demodulator circuit                              | 103 |

| 4.5.4 Control logic                                    | 110 |

| 4.5.5 64-bit mram                                      | 114 |

| 4.5.5.1 Memory write                                   | 114 |

| 4.5.5.2 Local oscillator                               | 116 |

| 4.5.5.3 Memory read                                    | 118 |

| 4.5.5.4 Memory read/write select                       | 120 |

| 4.5.6 Power budget for the online mode of "smart rfid" | 121 |

| 5. CONCLUSION and FUTURE WORK                          | 122 |

| REFERENCES                                             | 125 |

| APPENDIX A: BULK ETCHANTS                              | 134 |

| APPENDIX B: RECIPES                                    | 135 |

| APPENDIX C: MPPC ANALYSIS                              | 139 |

| CURRICULUM VITAE                                       | 144 |

#### **ABBREVIATIONS**

**ALF** : Assisted Living Facilities

**ANSI** : American National Standards Institute

**ASK** : Amplitude Shift Keying

**AWGN** : Additive White Gaussian Noise

BCB : Benzo Cyclo Butene

**BER** : Bit Error Rate

**BOE** : Buffered Oxide Etch

**DARPA**: The Defense Advanced Research Projects Agency

**DFF** : D-Type Flip Flop

DOD : Department of DefenseDRIE : Deep Reactive Ion Etching

**ECG** : Electro Cardiogram

**EEPROM**: Electrically Erasable and Programmable Read Only Memory

**EPC** : Electronic Product Code

**EPROM** : Electrically Programmable Read Only Memory

FCC : Federal Communications Commission

**FEA** : Finite Element Analysis

**FeRAM** : Ferroelectric Random Access Memory

**FLIR** : Forward Looking Infrared

FN: Fowler-Nordheim

HEI: Hot Electron Injection

**HVAC** : Heating Ventilating and Air Conditioning

IC : Integrated Circuit

**ICAO** : International Civil Aviation Organization

**IEEE** : Institute of Electrical and Electronics Engineering

**KOH** : Potassium Hydroxide

**LF** : Low Frequency

**MEMS** : Micro Electro Mechanical Systems

MNOS : Metal Nitride Oxide Silicon MPPC : Modified Pulse Pause Coding

**MR** : Magnetoresistivity

MRAM : Magnetic Random Access Memory

MTJ : Magnetic Tunneling Junction

NRZ : Non-Return to Zero NVM : Non-volatile Memory **NVRAM**: Non-Volatile Random Access Memory

OOK : On-Off Keying

PDF : Probability Density Function PDMS : Poly Di Methyl Siloxane

**PECVD**: Plasma Enhanced Chemical Vapor Deposition

PPC : Pulse Pause Coding

PSK : Phase Shift Keying

PVDF : Poly Vinylidene FluoridePZT : Lead Zirconate Titanate

**RFID** : Radio Frequency Identification

**RIE** : Reactive Ion Etching

SCCM : Cubic Centimeters per Minute SEM : Scanning Electron Microscopy

**SOI** : Silicon on Insulator

**SONOS** : Silicon Oxide Nitride Oxide Silicon

**TREAD**: Transportation Recall Enhancement, Accountability, and

Documentation Act

**UHF** : Ultra High Frequency

**UMC** : United Microelectronics Corporation

**UPS** : United Parcel Service

**UWB** : Ultra Wide Band

## LIST OF TABLES

|                  | <u>Page No</u>                                                                                                                                                                                                                                             |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 1.1        | Comparison of the fixed-energy and ambient energy sources (Roundy et al., 2005)                                                                                                                                                                            |

| <b>Table 1.2</b> | Comparison of vibration scavenging approaches                                                                                                                                                                                                              |

| Table 1.3        | Vibration frequencies and amplitudes on the surface of various typical vibration sources (Roundy and Wright, 2004). The peak acceleration is at frequency below 200 Hz for almost all sources, with the peak displacement being at even lower in frequency |

| Table 2.1        | SIMULINK <sup>TM</sup> model parameters of the "smart sand" system                                                                                                                                                                                         |

| Table 2.2        | Performance comparison of various vibration energy harvesters 36                                                                                                                                                                                           |

| Table 3.1        | Various design parameters for corner compensation schemes55                                                                                                                                                                                                |

| Table 4.1        | Bias conditions during operation modes of a typical Flash cell, adapted from Pavan et al., (1997)                                                                                                                                                          |

| Table 4.2        | The comparison of the memory devices (Lenssen et al, 2000)91                                                                                                                                                                                               |

| Table 4.3        | Demodulator front-end design parameters                                                                                                                                                                                                                    |

| Table 4.4        | Worst case simulation results                                                                                                                                                                                                                              |

| Table A.1        | Comparison of example bulk Silicon etchants is given below, adapted from Kovacs et al., (1998)                                                                                                                                                             |

| Table C.1        | Different n ratios with respect to the different time constants for logic "1" and logic "0"                                                                                                                                                                |

## LIST OF FIGURES

|             | Page No                                                                                                                                                                                                                                                                           |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

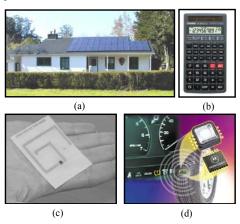

| Figure 1.1  | : Examples of commercially available energy harvesters: (a) Solar panels for powering home appliances (BP Solar, 2000); (b) Light-powered calculators (Casio); (c) RFID tags (Microchip); (d) Tire pressure monitoring sensors (Motorola Inc., 2000)                              |

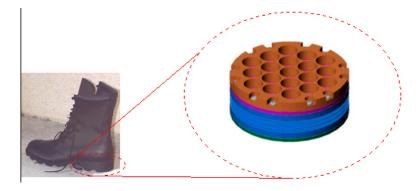

| Figure 1.2  | : In a DARPA funded project, SRI International is developing heelstrike generators that will eventually reduce the battery weight that a soldier needs to carry during a mission                                                                                                  |

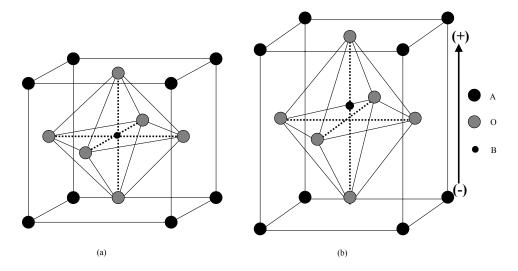

| Figure 1.3  | : Perovskite crystalline structure which is the form of ABO <sub>3</sub> ; (a) cubic symmetry above the Curie temperature, (b) tetragonal symmetry after polarization below the Curie temperature                                                                                 |

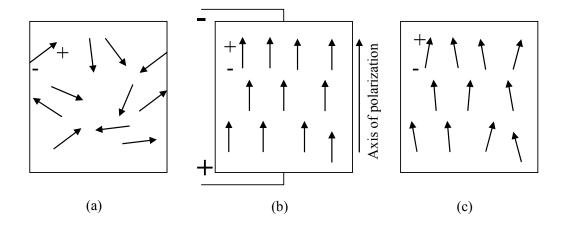

| Figure 1.4  | : Poling procedure of the piezoelectric crystal: (a) Prior to polarization, dipoles are random oriented, (b) A large DC electric field polarizes the structure so that dipoles are oriented in the same direction, (c) Permanent polarization remains after removing the DC field |

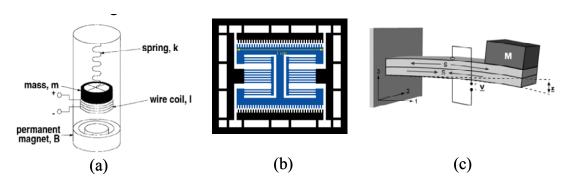

| Figure 1.5  | : Examples of different types of vibration energy scavengers: (a) Electromagnetic (Williams and Yates, 1996); (b) Electrostatic (Miranda, 2004); (c) Piezoelectric (Roundy et al., 2005)                                                                                          |

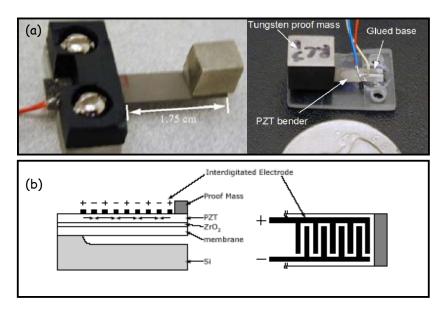

| Figure 1.6  | : Piezoelectric vibration energy scavengers, both at (a) meso-scale (Roundy and Wright, 2004) and (b) micro-scale (Jeon et al., 2005) $11$                                                                                                                                        |

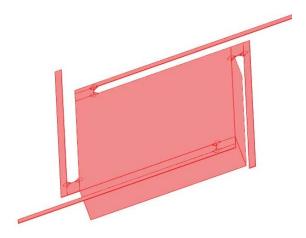

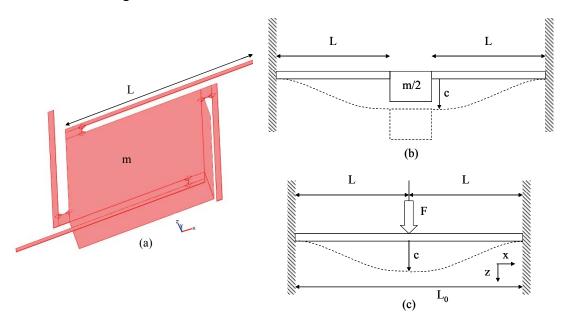

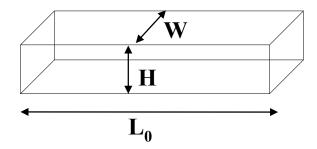

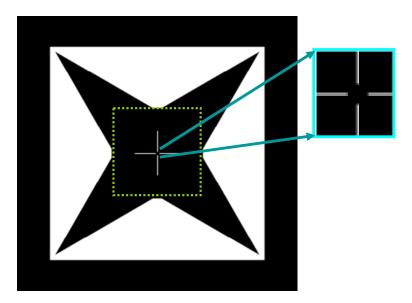

| Figure 2.1  | : The mechanical transducer part of the "smart sand" depicting one possible design. Tethers are 3.5mm long, $100\mu m$ wide and $5\mu m$ thick. $16$                                                                                                                              |

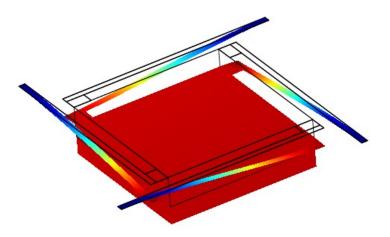

| Figure 2.2  | : A finite element simulation that illustrates a large, nonlinear deflection (100 $\mu$ m) of the proof mass. Tether clamp points not deflected are denoted with blue. Proof mass is deflected 100 $\mu$ m which is red 17                                                        |

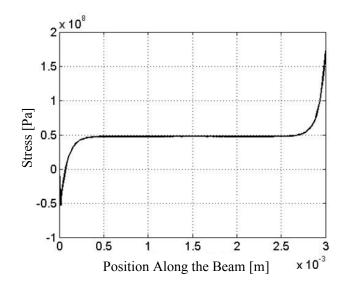

| Figure 2.3  | : Surface stress along the length of one of the 3mm long tethers under a 100µm deflection                                                                                                                                                                                         |

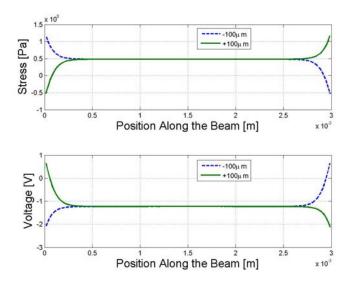

| Figure 2.4  | : Stress and voltage values along one of the tethers                                                                                                                                                                                                                              |

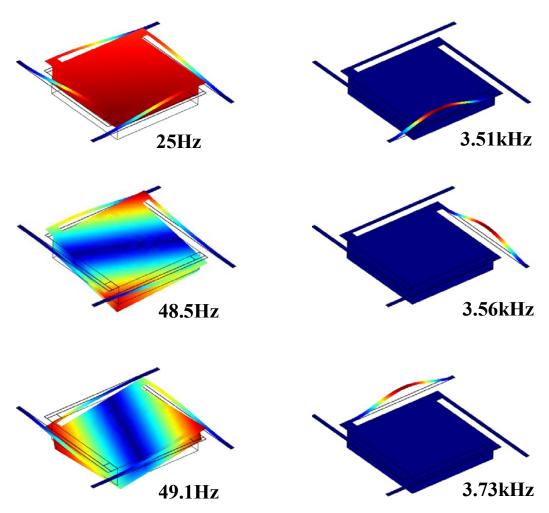

| Figure 2.5  | : First 6 eigenmodes and eigenfrequencies of the "smart sand" 19                                                                                                                                                                                                                  |

| Figure 2.6  | : The simplification flow of the modeling procedure                                                                                                                                                                                                                               |

| Figure 2.7  | : Specified beam dimensions of the beam                                                                                                                                                                                                                                           |

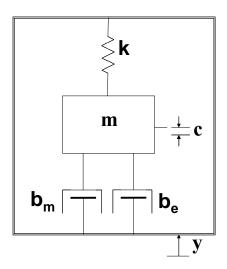

| Figure 2.8  | : Spring-mass-dashpot model of the beam. 22                                                                                                                                                                                                                                       |

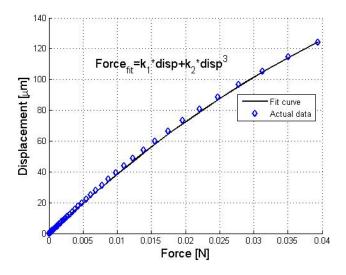

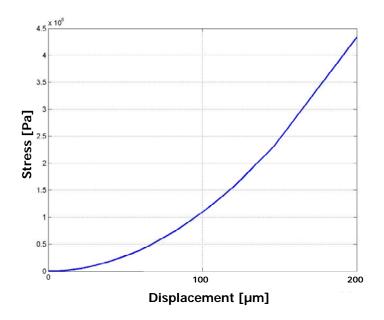

| Figure 2.9  | : Actual force versus displacement curve on one of the tethers that are $5\mu m\ Si/2\mu m\ PZT$ with the fit curve                                                                                                                                                               |

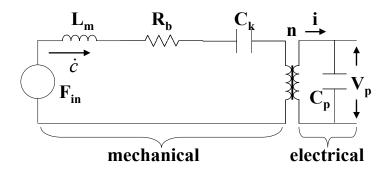

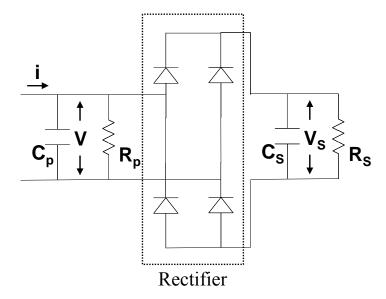

| Figure 2.10 | : Circuit representation of the electromechanical coupling of the cantilever beam with PZT layer                                                                                                                                                                                  |

| Figure 2.11 | : Displacement versus the average stress along one of the tethers $31$                                                                                                                                                                                                            |

| Figure 2.12 | : Modified electrical part of the lumped modeling                                                                                                                                                                                                                                 |

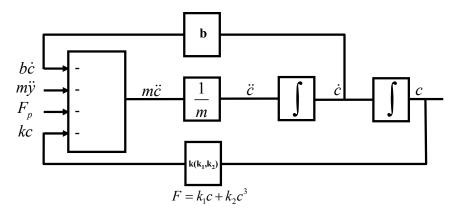

| Figure 2.13 | • The suspended mass-spring-dashnot system model 32                                                                                                                                                                                                                               |

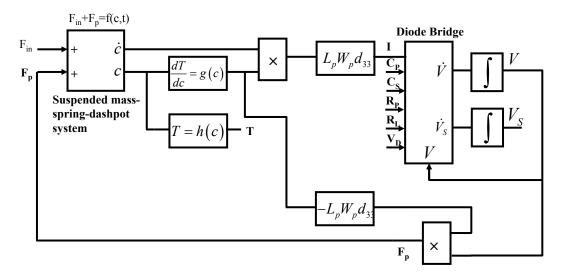

| Figure 2.14 | : The block diagram of the "smart sand".                                                                                                                                                                                                                                               |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

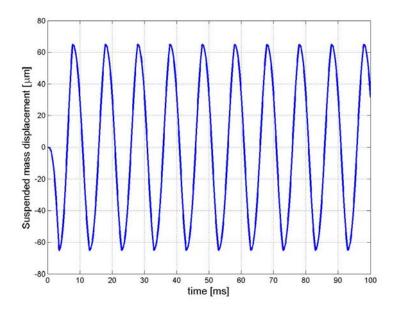

| Figure 2.15 | : The displacement of the suspended proof mass under a $60\mu m@100Hz$ of base excitation                                                                                                                                                                                              |

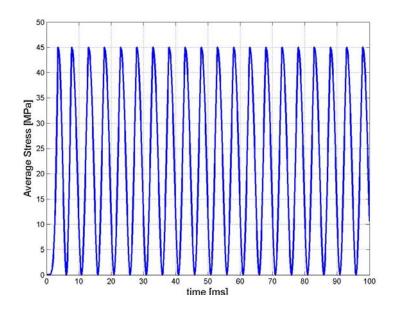

| Figure 2.16 | : The average stress on the tethers                                                                                                                                                                                                                                                    |

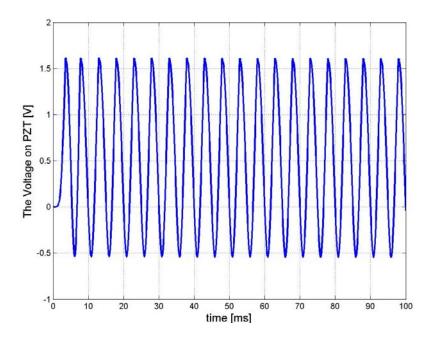

| Figure 2.17 | : The voltage on the PZT layer                                                                                                                                                                                                                                                         |

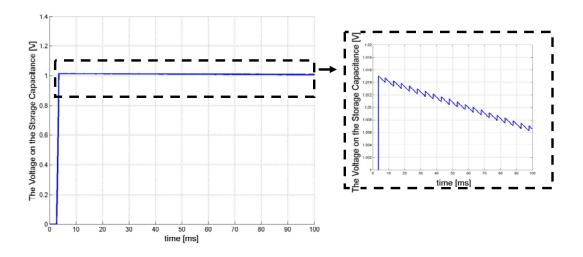

| Figure 2.18 | : The voltage on the storage capacitance                                                                                                                                                                                                                                               |

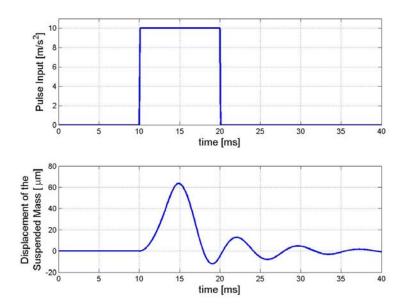

| Figure 2.19 | : The resulting displacement of the proof mass for a $\sim 1g$ pulse input 37                                                                                                                                                                                                          |

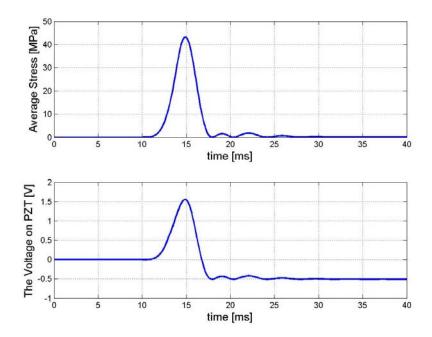

| Figure 2.20 | : The stress on the PZT film and resulting voltage out in response to $\sim 1g$ pulse input                                                                                                                                                                                            |

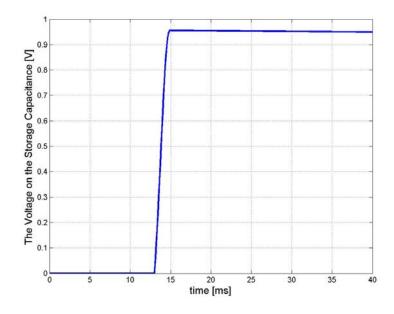

| Figure 2.21 | : The voltage on the storage capacitance in response to $\sim 1g$ pulse input                                                                                                                                                                                                          |

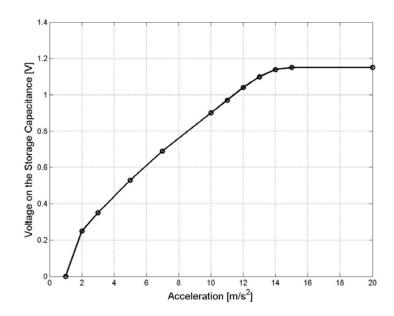

| Figure 2.22 | : The voltage on the storage capacitance with the acceleration amplitudes.                                                                                                                                                                                                             |

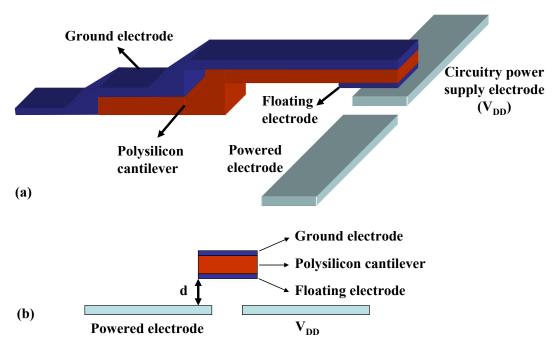

| Figure 2.23 | : One possible design of the mechanical switch; a) 3-d view, b) 2-d front view                                                                                                                                                                                                         |

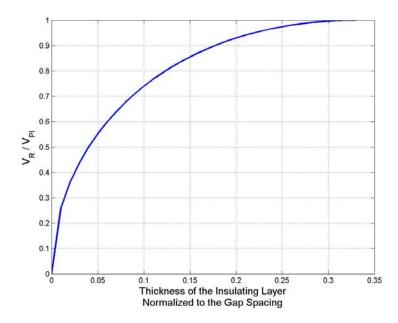

| Figure 2.24 | : $V_R/V_{PI}$ ratio with respect to the normalized thickness of the insulating layer                                                                                                                                                                                                  |

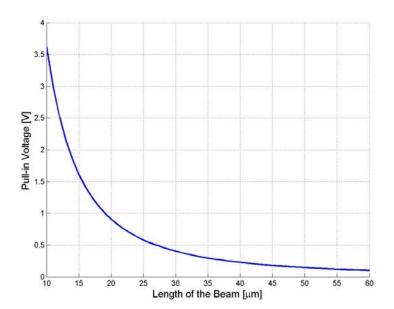

| Figure 2.25 | : Pull-in voltage variation with respect to the beam length for various beam thicknesses                                                                                                                                                                                               |

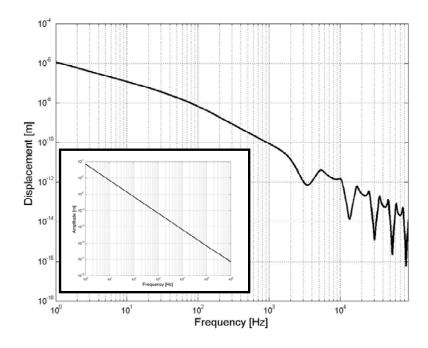

| Figure 2.26 | : The frequency response of the cantilever beam. The base excitation at $200 Hz$ is $50 \mu m. \dots 46$                                                                                                                                                                               |

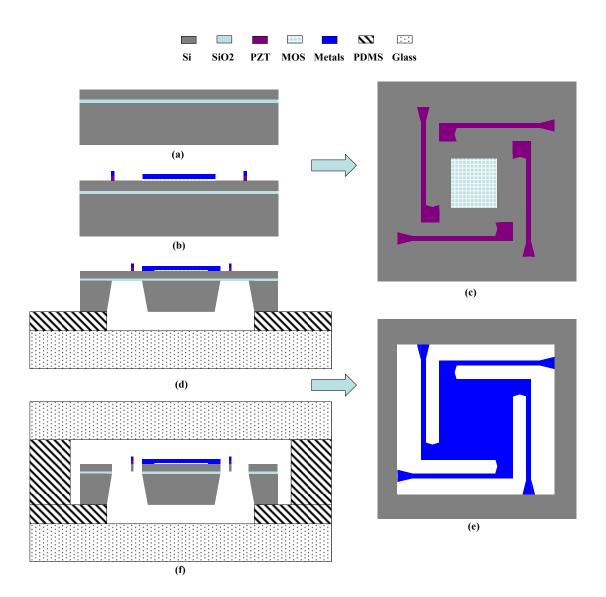

| Figure 3.1  | : Fabrication flow for the "smart sand" devices                                                                                                                                                                                                                                        |

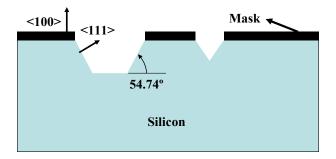

| Figure 3.2  | : Anisotropic etching of silicon creating V-grooves and inclined wells.                                                                                                                                                                                                                |

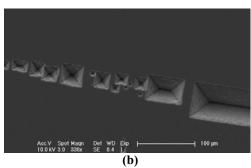

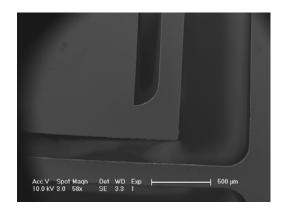

| Figure 3.3  | : SEM observation of KOH etched shapes; a) inclined wells, b) V-groove shapes                                                                                                                                                                                                          |

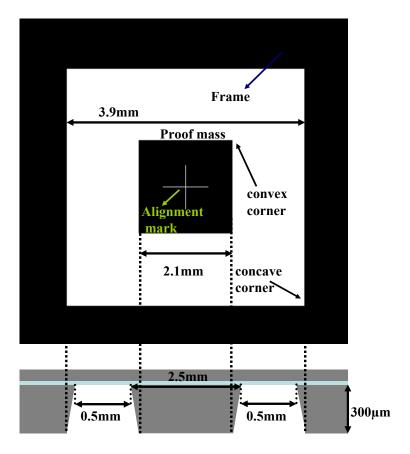

| Figure 3.4  | : Back side mask for KOH etch. 53                                                                                                                                                                                                                                                      |

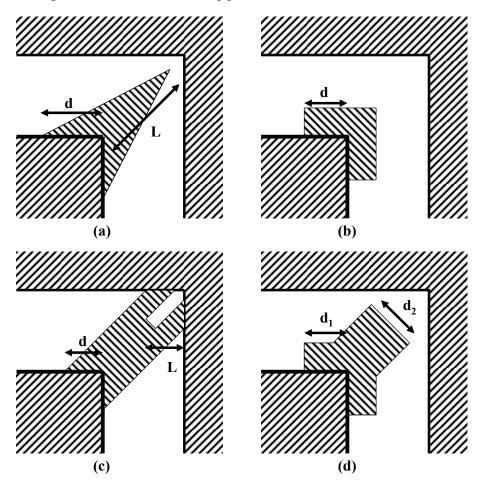

| Figure 3.5  | : The undercutting phenomena of the convex corners                                                                                                                                                                                                                                     |

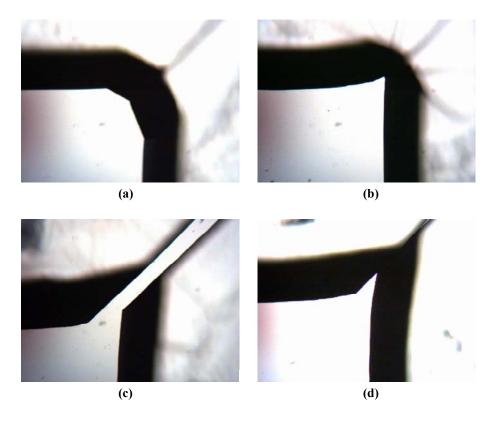

| Figure 3.6  | : Corner compensation schemes; a) Triangular (Long et al., 1999), b) Square (Puers and Sansen, 1990), c) Strip with slit (Enoksson, 1997), d) Square strip (Puers and Sansen, 1990)                                                                                                    |

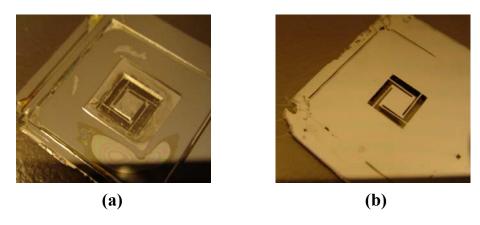

| Figure 3.7  | : Photographs of the KOH etched samples with different corner compensation schemes; a) Triangular ( $d$ =950 $\mu$ m, $L$ =1.8mm), b) Square ( $d$ =750 $\mu$ m), c) Strip with slit ( $d$ =450 $\mu$ m, $L$ =850 $\mu$ m), d) Square strip ( $d_1$ =500 $\mu$ m, $d_2$ =750 $\mu$ m). |

| Figure 3.8  | : The mask for the KOH etch with the triangular corner compensation.                                                                                                                                                                                                                   |

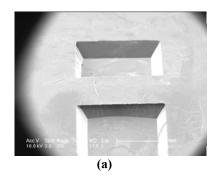

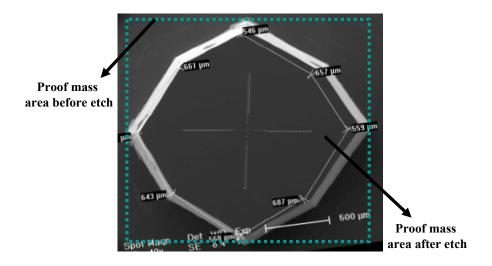

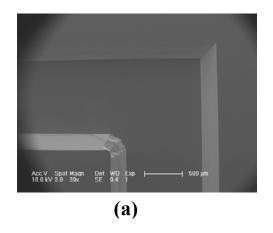

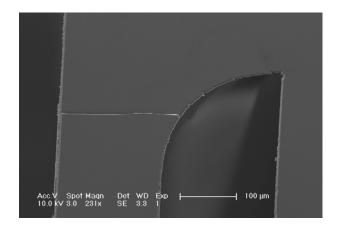

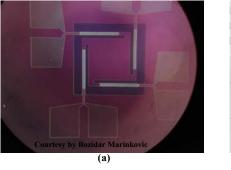

| Figure 3.9  | : The SEM photographs of the proof mass after successful corner compensation; a) Zoomed to the edges of the proof mass and frame, b)  The whole proof mass                                                                                                                             |

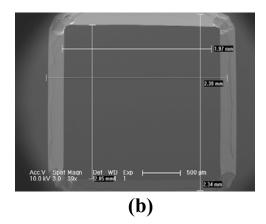

| _           | : PDMS film thickness with the successive spins                                                                                                                                                                                                                                        |

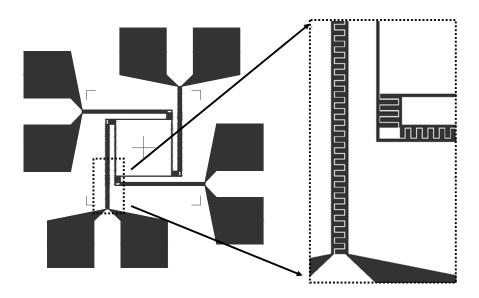

| Figure 3.11 | : Front side mask of the smart sand                                                                                                                                                                                                                                                    |

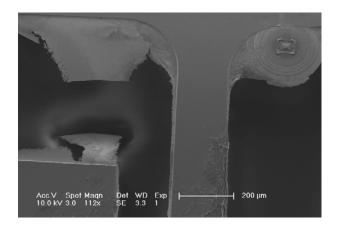

| O           | : SEM photograph of the successfully released beam structure $61$                                                                                                                                                                                                                      |

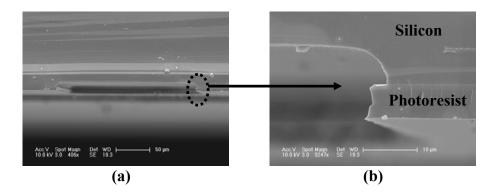

| Figure 3.13 | : Undercut phenomena of the anisotropic RIE process; a) Side view of the well, b) Side view of the etched sidewall                                                                                                                                                                     |

| Figure 3.14 | : SEM photograph of an under-etched beam structure during RIE                                                                                                                                         | 62 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

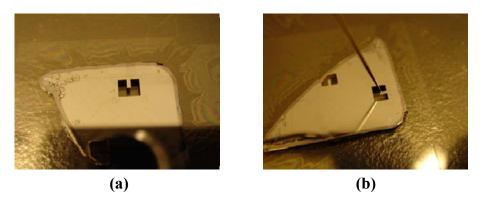

| Figure 3.15 | : Photographs of the beam structure; a) Back side view, b) Front side                                                                                                                                 |    |

|             | view                                                                                                                                                                                                  |    |

| _           | : SEM photograph of a cracked sample.                                                                                                                                                                 | 63 |

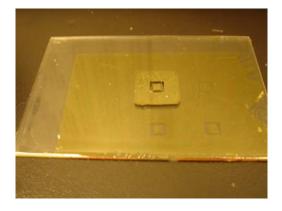

| Figure 3.17 | : The proposed packaging method including "smart sand" and two PDMS patterned glass slides                                                                                                            | 63 |

| Figure 3.18 | : Silicon cantilever failure tests.                                                                                                                                                                   | 64 |

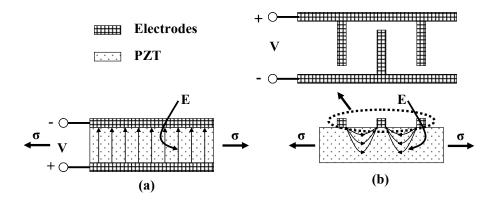

| Figure 3.19 | : Two modes of the piezoelectric conversion from the mechanical stress; a) $d_{31}$ mode, b) $d_{33}$ mode (Jeon et al., 2005)                                                                        | 66 |

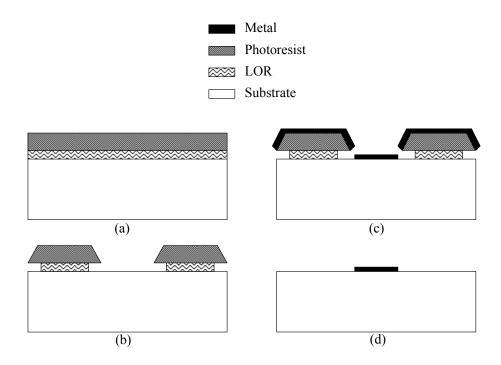

| Figure 3.20 | : Lift-off process flow; a) LOR and photoresist are coated and baked, Photoresist is exposed and developed, LOR is isotropically developed c) Metal is deposited, d) Photoresist and LOR are stripped | ,  |

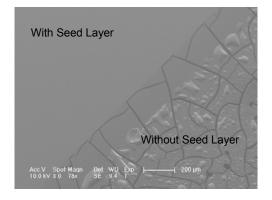

| Figure 3.21 | : SEM photograph of sol-gel PZT coated silicon wafer. There are crac where no seed layer exists                                                                                                       |    |

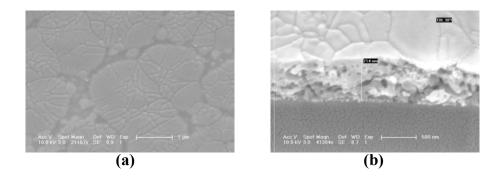

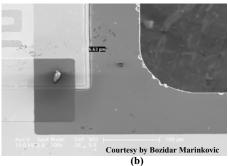

| Figure 3.22 | : SEM photographs of 750nm (3 coats) of PZT film, a) top view, b) cu view                                                                                                                             |    |

| Figure 3.23 | : Electrodes mask used for the top layer of the PZT film.                                                                                                                                             | 69 |

| Figure 3.24 | : The SEM photograph of the beam; a) Whole device, b) Zoomed to the edge of the tethers with interdigitated electrodes                                                                                |    |

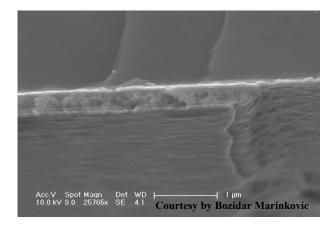

| Figure 3.25 | : Cross-section of the PZT film.                                                                                                                                                                      | 70 |

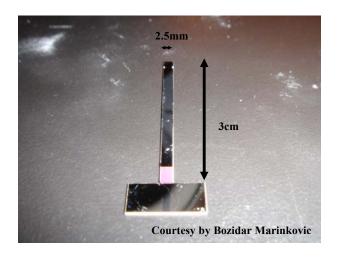

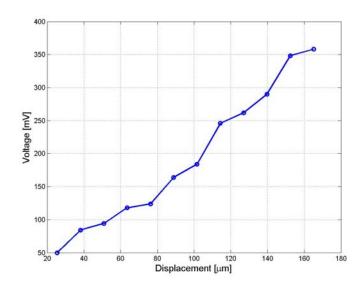

| Figure 3.26 | : Silicon cantilever beam used for voltage tests                                                                                                                                                      | 71 |

| Figure 3.27 | : Displacement versus peak voltage coming from PZT courtesy by Bozidar Marinkovic.                                                                                                                    | 71 |

| Figure 4.1  | : A simplified block diagram of the RFID system.                                                                                                                                                      | 74 |

| Figure 4.2  | : The architecture of the passive RFID transponder.                                                                                                                                                   | 79 |

| Figure 4.3  | : An N-stage voltage multiplier                                                                                                                                                                       | 81 |

| Figure 4.4  | : The clamping circuit representation.                                                                                                                                                                | 82 |

| Figure 4.5  | : ASK modulated carrier signal                                                                                                                                                                        | 82 |

| Figure 4.6  | : Different coding schemes; a) Non-return to zero (NRZ), b) Manchester, c) Modified Miller, d) Pulse-Pause (PPC)                                                                                      | 83 |

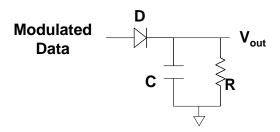

| Figure 4.7  | : A simple envelope detector.                                                                                                                                                                         | 84 |

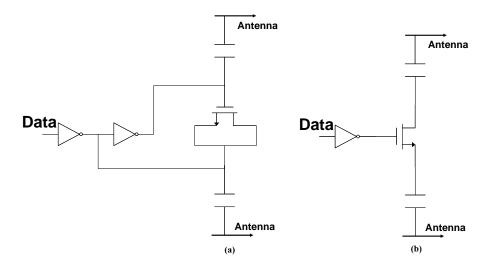

| Figure 4.8  | : The load modulation schemes, a) PSK, b) ASK                                                                                                                                                         | 85 |

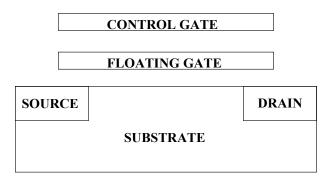

| Figure 4.9  | : The floating gate NVRAM device.                                                                                                                                                                     | 87 |

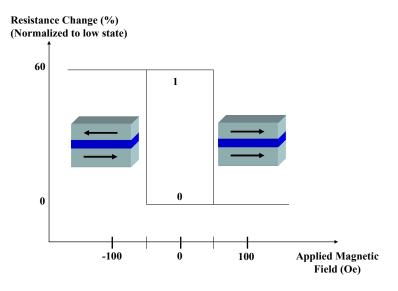

| Figure 4.10 | : MTJ device switching characteristic (Maffitt et al., 2006)                                                                                                                                          | 90 |

| Figure 4.11 | : 1T1MTJ architecture for MRAM array (Gallagher and Parkin, 2006)                                                                                                                                     |    |

| Figure 4.12 | : Border areas from a) US-Mexico and b) Turkey-Iraq                                                                                                                                                   |    |

| _           | : FLIR cameras (FLIR Systems, 2000).                                                                                                                                                                  |    |

| O           | : An ECG data provided by ANSI.                                                                                                                                                                       |    |

| Figure 4.15 | : The block diagram of the RFID transponder.                                                                                                                                                          | 98 |

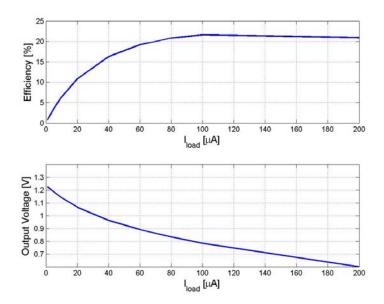

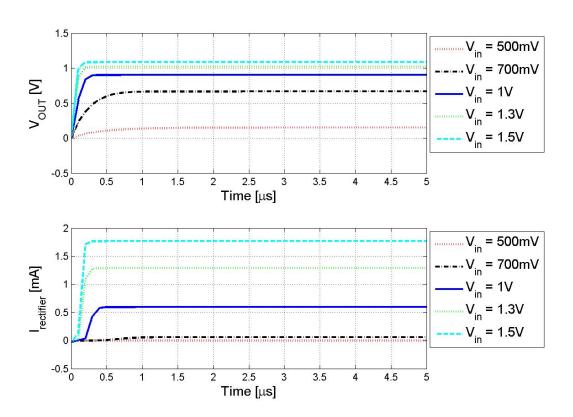

| Figure 4.16 | : The output voltage of the 2-stage multiplier for different load current                                                                                                                             |    |

| Figure 4.17 | : Power efficiency together with the settled output voltage with respec                                                                                                                               |    |

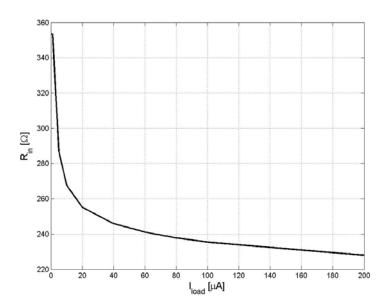

| Figure 4.18        | : The input resistance of the 2-stage multiplier for the optimized desparameters.               |            |

|--------------------|-------------------------------------------------------------------------------------------------|------------|

| Figure 4.19        | : Effect of the process and temperature variations on the multiplier efficiency.                |            |

| Figure 4.20        | : The clamping circuit representation.                                                          |            |

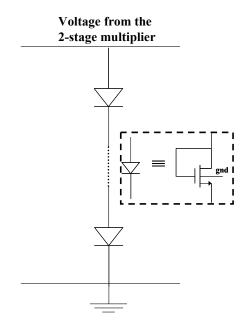

|                    | : The output voltage of the 2-stage multiplier connected to the rectif                          |            |

| _                  |                                                                                                 |            |

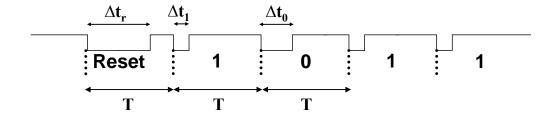

| _                  | : Modified pulse-pause coding (MPPC).                                                           |            |

| Figure 4.23        | : The generation of the modulated input signal. Serial inputs are resologic "0" and logic "1"   |            |

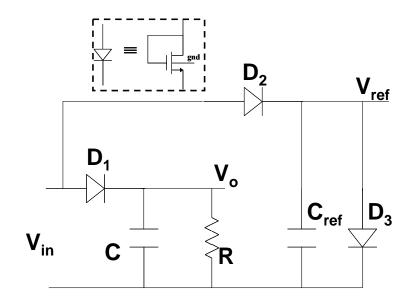

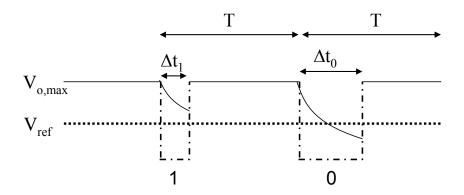

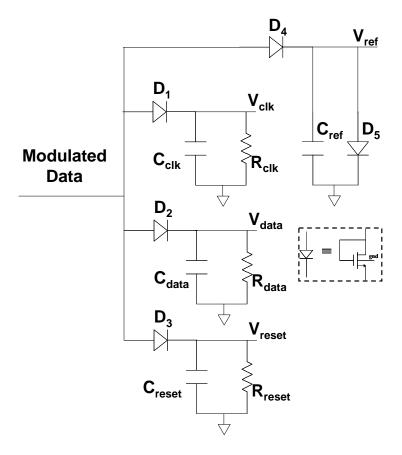

| Figure 4.24        | : Demodulation circuit for MPPC.                                                                | . 105      |

| Figure 4.25        | : The principle of the demodulation of "1" and "0"                                              | . 105      |

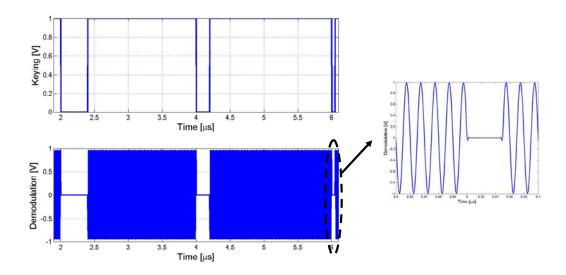

| Figure 4.26        | : The demodulator analog front-end circuit.                                                     | . 107      |

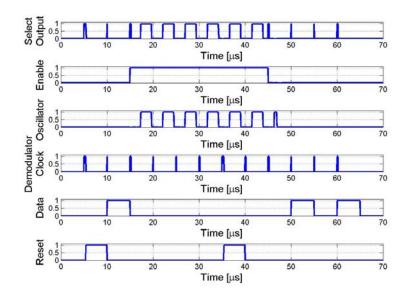

| Figure 4.27        | : Demodulator front-end simulated output waveforms.                                             | . 108      |

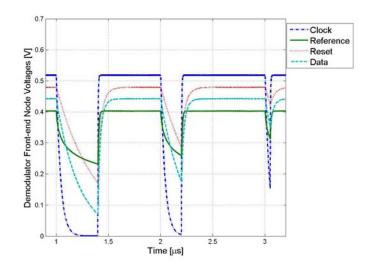

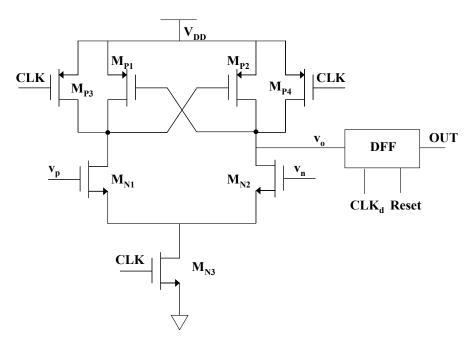

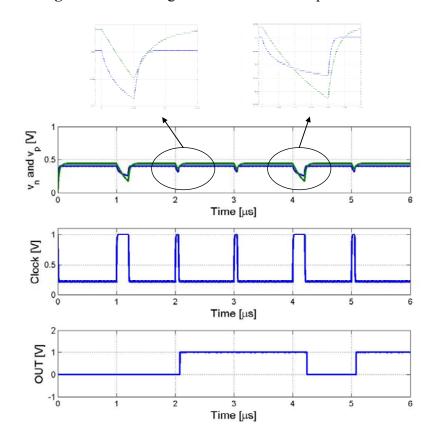

| Figure 4.28        | : The regenerative latched comparator circuit.                                                  | . 109      |

| Figure 4.29        | : The input and output voltages of the comparator for the data signa                            |            |

| Figure 4.30        | : The digital output generation from the demodulator front-end outp                             | ut         |

| Figure 4.31        | : The outputs of the demodulator.                                                               | . 110      |

| Figure 4.32        | : The control logic of the memory R/W                                                           | . 112      |

| Figure 4.33        | : The truth table and a possible synthesis of the 1-of-8 encoder                                | . 112      |

| Figure 4.34        | : Building a counter from cascaded flip-flops                                                   | . 112      |

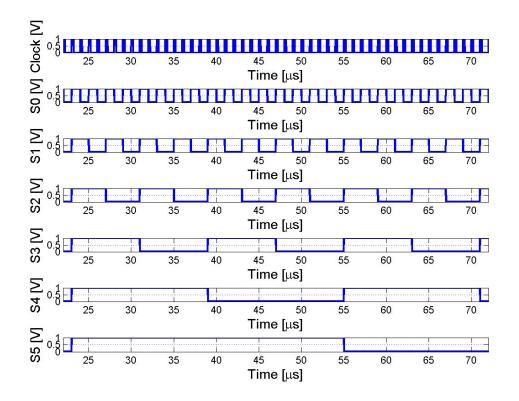

| <b>Figure 4.35</b> | : The clock signal and the outputs of the counter.                                              | . 113      |

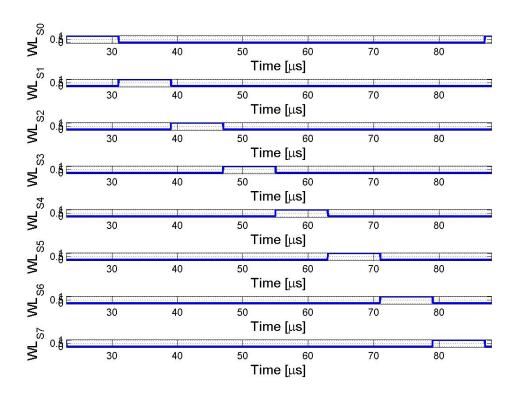

| <b>Figure 4.36</b> | : Word line select encoder outputs                                                              | . 113      |

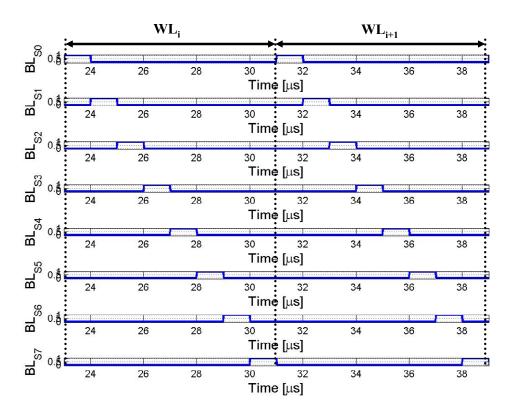

| <b>Figure 4.37</b> | : Bit line select encoder outputs.                                                              | . 114      |

| Figure 4.38        | : MRAM writing circuit.                                                                         | . 115      |

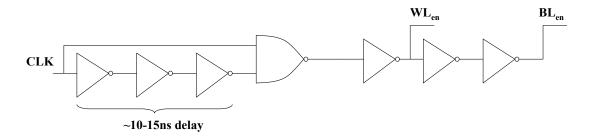

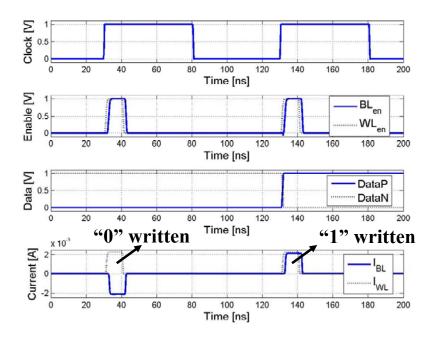

| Figure 4.39        | : The pulse generator for the MRAM enable signals                                               | . 115      |

| Figure 4.40        | : The simulation results for an individual MRAM cell                                            | . 116      |

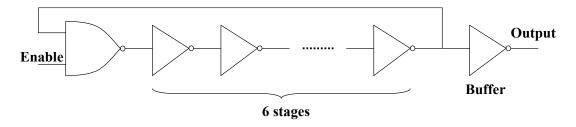

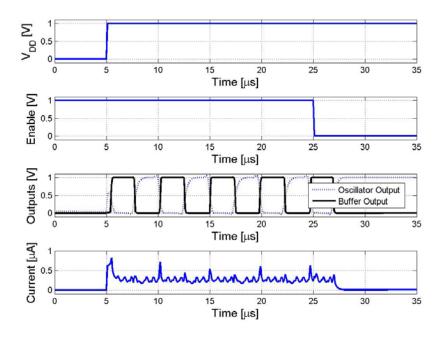

| _                  | : The schematic representation of the ring oscillator                                           | . 117      |

| Figure 4.42        | : The response of the ring oscillator to the sudden $V_{DD}$ and $enable$ switchings            | . 117      |

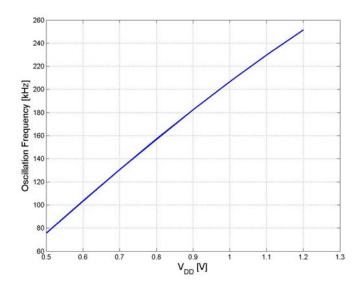

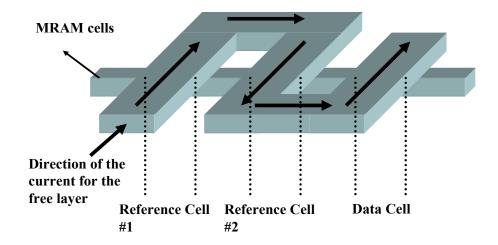

| Figure 4.43        | : Oscillation frequency variation with the changing power supply                                | . 118      |

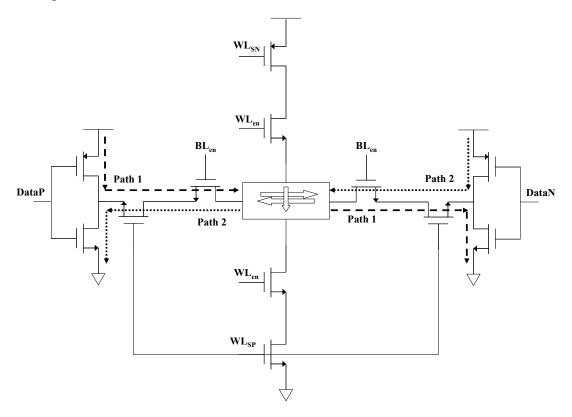

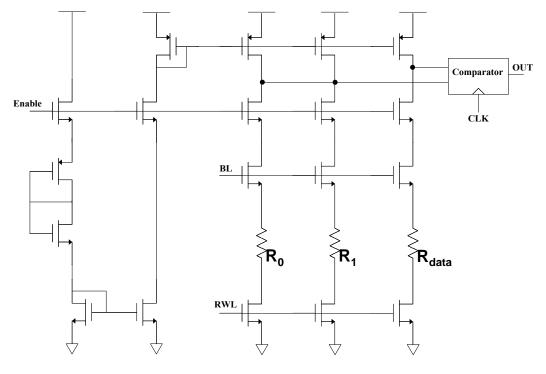

| Figure 4.44        | : The concept of reading an individual MRAM cell.                                               | . 119      |

| Figure 4.45        | : The MRAM reading circuitry.                                                                   | . 119      |

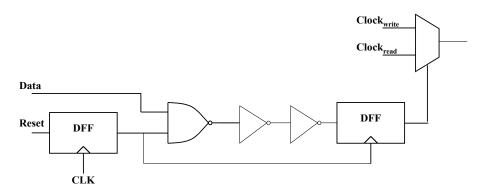

| Figure 4.46        | : The schematic representation of the read/write select                                         | . 120      |

| Figure 4.47        | : The read/write selection procedure.                                                           | . 120      |

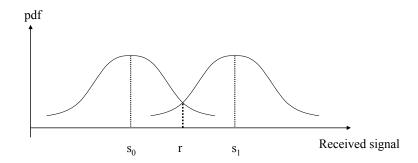

| Figure C.1         | : Probability density functions (pdf) of two received signals for "1" "0" from the demodulator. |            |

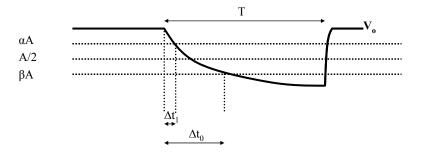

| Figure C.2         | : Zoomed view of the discharged output voltage of the demodulator                               | . 142      |

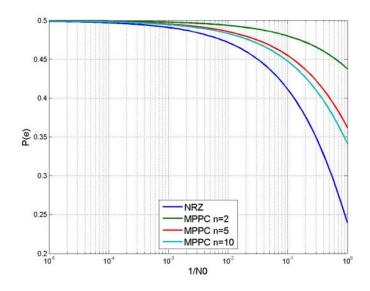

| Figure C.3         | : The probability of errors for NRZ and MPPC with different n ratio                             | os.<br>143 |

#### A NOVEL MICRO PIEZOELECTRIC ENERGY HARVESTING SYSTEM

#### **ABSTRACT**

In this thesis, a novel, vibration based micro energy harvester system has been proposed. The modeling, design and fabrication of the devices have been carried out. There are several propositions in this thesis. The biggest claim is to achieve high power density levels with a mm<sup>3</sup> device by using a novel vibration based mechanical structure. The operating regime is non-linear unlike its conventional counterparts, which yields to generate more electrical energy. The proposed packaging method of the device is very simple and easy to realize. In addition to the mechanical propositions, a novel batteryless active RFID transponder based on the proposed design has been suggested. In this context, a new modulation method has also been proposed.

The mechanical structure of the device is based on a clamped-clamped beam where four tethers share a thick proof mass. The proof mass is used in order to bring the first eigenfrequency of the system below 50Hz; this enlarges the operating frequency range. The surface of the proof mass also acts as a platform for the sensor circuits.

Vibrations or sudden movements force the mechanical structure to not only bend but also stretch, thus it works in the non-linear regime. The piezoelectric thin film layer on the silicon tethers converts the mechanical stress into electrical energy. Microwatts of power can be achieved with a mm<sup>3</sup> device which yields power density levels on the same order those of solar panels. This device is named as "smart sand", because it has sensor capabilities that can store information, its size is almost that of a sand grain and the main material used for the fabrication is silicon.

The modeling and design of the mechanical structure has been developed by using COMSOL<sup>TM</sup> (a finite element analysis (FEA) tool) and SIMULINK<sup>TM</sup> (an extension tool of MATLAB<sup>TM</sup>). Firstly, the stress levels have been calculated and the transient response of the structure has been investigated. Then, the theoretical analysis has been combined with these two tools and expected power density levels have been found.

The fabrication of the "smart sand" has also been developed in this thesis. Bulk micromachining techniques have been used in order to form the proof mass. The piezoelectric thin film layer has been deposited onto the tethers by a sol-gel method. Electrodes of the piezoelectric layer have been fabricated by the lift-off process. The packaging has been embedded into the fabrication process, which reduces the handling issues during the process. An elastomer (poly dimethyl siloxane, PDMS) which is cheap and very easy to pattern and handle has been used for the packaging which has not been tried before.

The "smart sand" serves as a typical accelerometer which senses the continuous vibrations or sudden accelerations. In order to further develop the sensor capabilities of the system, a new approach called "smart RFID" has been proposed; this is a

platform where the device has been combined with the RFID concept. In this context, a self-powered, energy harvesting RFID transponder has been designed. The circuitry has the capabilities of sending and receiving 64 bits of data. The 64-bit memory has been constructed with the magnetic random access memory (MRAM) cells. Several bits have been reserved for the acceleration or temperature data. When a sudden or continuous acceleration happens, the "smart sand" generates voltage and this voltage is used to write the memory bits without the need of a battery. Therefore, the "smart RFID" platform behaves like a batteryless active RFID transponder. In order to determine whether the adequate voltage level is reached or not, a mechanical relay has been proposed and its design has been investigated.

Several applications have been proposed to use the "smart RFID" platform, such as continuous acceleration monitoring in package delivery, self-powered sensors for homeland security, temperature monitoring of perishable food item delivery and a batteryless heart rate sensor. Their feasibilities have been investigated and discussed.

As a result, mechanical structure has been designed, modeled and fabricated. On the other hand, circuit level simulations have been performed but not implemented.

At the end of this work, attained results have been discussed and recommended future works have been given.

#### YENİ BİR MİKRO PİEZOELEKTRİK ENERJİ HARMANLAYICI SİSTEMİ

#### ÖZET

Bu tezde, yeni bir titreşim tabanlı mikro enerji harmanlayıcı sistemi önerilmiştir. Elemanların modellemesi, tasarımı ve üretimi gerçekleştirilmiştir. Tez içerisinde bir çok yeni öneri getirilmiştir. En büyük iddia; yeni, titreşim temelli mm³ boyutunda mekanik bir yapı kullanarak yüksek güç yoğunluğuna ulaşmaktır. Sistem, geleneksel eşdeğerlerinden farklı olarak doğrusal olmayan bir çalışma rejiminde çalışarak daha çok elektrik enerjisi üretmektedir. Önerilen kılıflama yöntemi çok basittir ve gerçeklemesi kolaydır. Mekanik önerilere ek olarak, önerilen yapı tabanlı yeni bir pilsiz aktif RFID etiketi düşünülmüştür. Bu bağlamda, yeni bir modülasyon yöntemi de önerilmiştir.

Elemanların mekanik kısmı iki taraftan kıskaçlı bir kiriş yapısına benzer; dört adet ince bağlantı kalın bir kütleyi paylaşmaktadır. Bu kütle, ilk özdeğer frekansını 50Hz'in altına çekerek çalışma aralığını genişletmek için kullanılır. Kütlenin yüzeyi aynı zamanda algılayıcı devreleri için bir zemin görevi görür.

Titreşimler ve ani hareketler mekanik yapının sadece eğilmesine değil, aynı zamanda gerilmesine yol açarak doğrusal olmayan rejimde çalışmayı sağlar. Silikon bağlantılar üzerindeki piezoelektrik ince film tabakası mekanik gerilmeyi elektrik enerjisine çevirir. Mikrowatt mertebesinde güç seviyeleri mm³'lük elemanlarla elde edilebilir, bu da güneş panellerinde elde edilen güç yoğunlukları kadar yüksektir. Algılayıcı kabiliyeti sayesinde bilgi depolayabilen, kum tanesi büyüklüğünde olan ve üretiminde kullanılan temel malzeme silikon olan bu elemanlar "zeki kum" olarak isimlendirilmistir.

Mekanik elemanların modelleme ve tasarımı COMSOL<sup>TM</sup> (bir sonlu eleman analizi programı) ve SIMULINK<sup>TM</sup> (MATLAB<sup>TM</sup> programının bir uzantısı) kullanılarak geliştirildi. İlk olarak, gerilme seviyeleri hesaplandı ve yapının geçici hal cevabı incelendi. Daha sonra, teorik analiz, bu iki program ile birleştirildi ve beklenen güç yoğunluk seviyeleri bulundu.

Bu tezde "zeki kum" elemanlarının üretimi de yapılmıştır. Kütlenin oluşturulmasında taban aşındırma yöntemleri kullanılmıştır. İnce piezoelektrik film tabakası jel çözeltisi kullanılarak serilmiştir. Piezoelektrik tabakanın elektrotları ise kaldırma yöntemi kullanılarak yapılmıştır. Kılıflama işlemi, üretim sürecinin içine gömülmüştür; bu da süreç esnasındaki taşıma problemlerini azaltmıştır. Kılıflamada, daha önce denenmemiş bir yöntem olarak şekillendirilmesi çok kolay ve ucuz bir malzeme olan bir elastomer (poly dimethyl siloxane, PDMS) kullanılmıştır.

Zeki kum elemanları sürekli titreşimleri ya da ani ivmelenmeleri algılayan tipik bir ivmeölçer gibi davranmaktadır. Sistemin algılayıcı kabiliyetlerini daha da geliştirmek için yeni bir yaklaşım olan ve RFID kavramını içeren "zeki RFID" platformu önerilmiştir. Bu bağlamda, bir RFID etiketi tasarlanmıştır. Devre 64 bitlik bir veriyi gönderebilmekte ve alabilmektedir. 64 bitlik bu bellek manyetik yaz-oku bellek

(MRAM) hücreleri ile oluşturulmuştur. Bazı bitler ivme veya sıcaklık bilgisi için ayrılmıştır. Ani veya sürekli bir ivme oluştuğunda, "zeki kum" elemanları gerilim üretir ve bu gerilim pile ihtiyaç duymadan bellek bitlerinin yazılması için kullanılır. Bu nedenle, "zeki RFID" platformu pilsiz aktif RFID etiketleri gibi davranır. Yeterli gerilim seviyesine ulaşılıp ulaşılmadığını belirlemek amacıyla mekanik bir röle önerilmiş ve tasarımı incelenmiştir.

"Zeki RFID" platformunun kullanılması mümkün birçok uygulama önerilmiştir. Bu uygulamalar, paket taşımacılığında sürekli ivme denetleme, sınır güvenliği için kendinden beslemeli algılayıcılar, çabuk bozulan yiyeceklerin taşımacılığında sıcaklık denetleme ve pilsiz kalp atışı algılayıcı olarak sayılabilir.

Sonuç olarak, mekanik yapının tasarımı, modellemesi ve fabrikasyonu yapılmıştır. Öte yandan, devre düzeyi benzetimler gerçekleştirilmiş fakat üretime gidilmemiştir.

Bu çalışmanın sonunda, ulaşılan sonuçlar tartışılmış ve gelecekte yapılması öngörülen çalışmalar verilmiştir.

#### 1. INTRODUCTION

#### 1.1 History and Motivation

The development of Micro Electro-Mechanical Systems (MEMS) has opened up the possibility of making and using micro sensor networks and actuators in many application fields, which has led to a large research effort recently. Most current designs use batteries as power sources, which have a relatively short life time and require replacement after depletion. However, the micro sensor devices are often placed at locations without easy access, and true micro devices are of very tiny sizes (~mm³). For these devices, battery changing is not easy, often impractical, and even impossible for some applications. Concerns over relatively short battery life have restricted wireless device applications. Therefore, researchers have been looking for alternative power sources. A possible and promising solution is based on the idea of harvesting or scavenging ambient energy from the environment and converting it to electricity, thus eliminating the need for batteries and extending the device lifetime deployment duration dramatically or even indefinitely.

Among the many ambient energy sources, solar power has been considered and studied intensively. It is environmentally friendly; life time is potentially infinite, and has a relatively high energy density. There have been quite a few successful designs utilizing solar energy (Raffaelle et al., 2000). However, the applications are limited to outdoors or outer space applications where sun light is abundant.

Vibration energy is a good alternative where direct sunlight or large collection surfaces are not available. HVAC systems (heating, ventilating and air conditioning), motors, heavy traffic, military equipments, human movements, etc. can all be considered as vibration energy sources. Various research groups have been working on development of micro harvesters using vibration as an energy source.

The conversion of mechanical vibration energy to electrical energy using electromagnetic coil (Williams et al., 1996), variable capacitors (Meninger et al., 2001) or piezoelectric material (Umeda et al., 1994) have been studied. Kymissis et

**al.** (1998) demonstrated that heel strikes can be used as a vibration source by inserting piezoelectric stacks into shoe heels and energy can be collected by a human walking.

Other energy harvesting mechanisms include electricity generation through gas flow using a MEMS rotor (Wiegele, 1996). Holmes et al. (2004) combines an axial-flow turbine with an axial-flux electromagnetic generator to generate electrical power when placed in an air-stream. Strasser et al. (2003) demonstrated a micro-scale thermoelectric generator based on polysilicon surface micromachining converting waste heat into electrical power. Qu et al. (2001) demonstrated the fabrication of thermoelectric generators on flexible foil substrates. Yang et al. (2004) showed that electricity can be generated by forcing water through a ceramic rod with no moving parts or emissions; the system utilizes the natural occurring phenomena of charge separation near a solid-liquid interface. More interestingly, energy can be also harvested from microorganisms (Tayhas and Palmore, 2004, Rabaey et al., 2003) by utilizing glucose as a carbon source in a microbial fuel cell. However, automated power generation from microbial glucose has not been implemented.

Among the collectable ambient energy sources discussed above, mechanical vibration energy is a very promising power source. Basically, vibration is ubiquitous in ambient environment. Under many circumstances, such as on most transportation vehicles (cars, airplanes, submarines and so on) or in many public constructions (dams, bridges, buildings and so on), vibration is significant and can be easily utilized as energy sources to support MEMS devices for various purposes.

Besides the ambient environment, human body is also a vibration source. Heart beats (~1Hz) can also create an infinite vibration which can be used as temperature and heart rate monitoring.

Sudden accelerations can also be thought as vibration sources. Considering package delivery, sudden acceleration means that the package is dropped or hit somewhere that may cause damage. This information can be written on a non-volatile memory embedded in a MEMS vibration energy harvester, and may be probed when desired. On the other hand, if those MEMS chips are spread out to the soil along the borders, human or animal tracking can be performed for surveillance monitoring.

Embedded smart sensors are used extensively from batteryless tire pressure sensors for cars to package transportation. Smart RFID tags can store their own history such as temperature changes or acceleration that the system is exposed to. Many applications are possible for such kind of tags. For example, those tags would greatly reduce the efforts on insurance issues during package delivery.

Wireless tire pressure sensors embedded with RFID technology monitor each tire pressure continuously and inform the driver in case a replacement or air is needed. U.S. Transportation Recall Enhancement, Accountability, and Documentation Act (TREAD) mandated that such kind of sensors should be embedded into front panel of each new car (TREAD, 2004). Therefore, those sensors have become popular. Roundy (2003) has demonstrated a system that charges the sensor battery through vibrations of the moving car.

Mechanical vibrations have received great attention from various researchers as a promising power source for energy harvesting applications. The conversion from vibration energy to electric energy can be of many forms. Electrostatic energy harvesting devices are the easiest to integrate in micro systems, but they need a separate voltage source, which brings practical difficulties in many cases (Meninger et al., 2001, Roundy et al., 2002, Miyazaki et al., 2003). Unlike electrostatic design, electromagnetic devices can work independently and don't require external voltage sources. But electromagnetic energy conversion can only provide an electric potential up to several tenths of a volt (Roundy et al., 2003, Williams et al., 1996, Shearwood and Yates, 1997, Amirtharajah and Chandrakasan, 1998, El-hami et al., 2001). Even if piezoelectric conversion based vibration energy harvesters are claimed to be more difficult to integrate with MEMS, designs have attractive advantages including no need for voltage source and relatively high output voltage, as high as 8 Volts (Roundy et al., 2003, Schmidt, 1986, Shenck et al., 2001, Glynne et al., 2001, Ottman et al., 2003).

In the rest of Chapter 1, a brief overview on energy harvesters is given. Vibration energy harvester systems are discussed and state of the art works are introduced. Examples of some commercial applications are also investigated.

#### 1.2 MEMS Energy Scavenger Concept

#### 1.2.1 Introduction

Wireless sensor networks are widely used for gathering and processing the information from environment (Philipose et al., 2005). Using self-powered, batteryless wireless sensor nodes would greatly minimize the cost of monitoring and controlling.

In order for these nodes to be cheap and easily deployable, some specifications for the batteries can be given as follows:

- Long life time,

- Small size and form factor<sup>1</sup>,

- No need of changing or recharging especially at hard-to-reach locations.

Due to these requirements, chemical battery cells, solar panels or other fixed energy sources are not suitable for wireless sensor nodes. Therefore, nodes that are using ambient energy sources other than solar have attracted interest in recent years.

A comparison of ambient and fixed energy sources are given in Table 1.1, adopted from **Roundy et al., (2005)**. Upper part of the table shows the fixed-energy sources and lower part (gray entries) displays the ambient energy sources.

#### 1.2.2 Examples of Commercial Energy Harvesters

Solar panels are one of the most commonly used energy harvesters. Each solar panel cell consists of photodiodes which generate current when exposed to light. Those semiconductor components are connected in series and parallel in a matrix form in order to get high power. The BP Solar panel shown in Figure 1.1a occupies 1593mm x 790mm area and 5cm of thickness and generates 170W under direct sunlight which corresponds to 2.7μW/mm³ (BP Solar, 2000). They are warranted to 25-40 years. By covering the house roof with those panels, electricity necessary for home use can be generated. This system, including rechargeable batteries and converters, costs about \$30000. Besides home use, they can be used for water

<sup>&</sup>lt;sup>1</sup> The linear dimensions and configuration of a device, as distinguished from other measures of size.

pumping, marine and highway information panels. Another solar panel example is the light-powered calculators as shown in Figure 1.1b (Casio).

**Table 1.1:** Comparison of the fixed-energy and ambient energy sources (**Roundy et al., 2005**).

| Power Source                    | Power density (μW/cm³) | Energy density<br>(Joules/cm³) | Power density<br>per year<br>(µW/cm³/yr) | Secondary<br>storage<br>needed? | Voltage regulation? | Readily available? |

|---------------------------------|------------------------|--------------------------------|------------------------------------------|---------------------------------|---------------------|--------------------|

| Primary battery                 | N/A                    | 2,880                          | 90                                       | No                              | No                  | Yes                |

| Secondary<br>battery            | N/A                    | 1,080                          | 34                                       | N/A                             | No                  | Yes                |

| Micro fuel cell                 | N/A                    | 3,500                          | 110                                      | Maybe                           | Maybe               | No                 |

| Ultra capacitor                 | N/A                    | 50-100                         | 1.6-3.2                                  | No                              | Yes                 | Yes                |

| Heat engine                     | 1 x 10 <sup>6</sup>    | 3,346                          | 106                                      | Yes                             | Yes                 | No                 |

| Radioactive ( <sup>63</sup> Ni) | 0.52                   | 1,640                          | 0.52                                     | Yes                             | Yes                 | No                 |

| Solar (outside)                 | 15,000*                | N/A                            | N/A                                      | Usually                         | Maybe               | Yes                |

| Solar (inside)                  | 10*                    | N/A                            | N/A                                      | Usually                         | Maybe               | Yes                |

| Temperature                     | 40*†                   | N/A                            | N/A                                      | Usually                         | Maybe               | Soon               |

| Human power                     | 330                    | N/A                            | N/A                                      | Yes                             | Yes                 | Soon               |

| Air flow                        | 380 <sup>‡</sup>       | N/A                            | N/A                                      | Yes                             | Yes                 | No                 |

| Pressure variation              | 17*                    | N/A                            | N/A                                      | Yes                             | Yes                 | No                 |

| Vibrations                      | 375                    | N/A                            | N/A                                      | Yes                             | Yes                 | No                 |

<sup>\*</sup> Measured in power per square centimeter, rather than power per cubic centimeter.

<sup>‡</sup> Assumes an air velocity of 5m/s and 5 % conversion efficiency.

Figure 1.1: Examples of commercially available energy harvesters: (a) Solar panels for powering home appliances (BP Solar, 2000); (b) Light-powered calculators (Casio); (c) RFID tags (Microchip); (d) Tire pressure monitoring sensors (Motorola Inc., 2000).

<sup>†</sup> Demonstrated from a 5°C temperature differential.

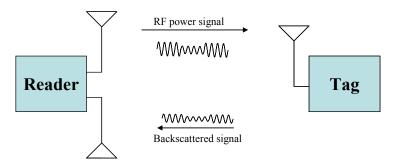

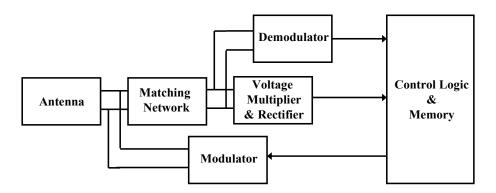

Radio frequency powered identification (RFID) tags are used to track and monitor packages, assets, people and animals (Sorrels, 1998). Passive RFID tags are battery-less as shown in Figure 1.1c. A reader sends power pulse at a specific frequency (Commonly used frequencies are 130kHz, 13.56MHz, 900MHz, 2.45GHz.) to "wake up" the reader. This power signal is converted to energy by inductive or magnetic coupling through a coil (antenna) and harvested energy is stored in a capacitor and used for powering communication circuitry. During communication, electronic product code (EPC) can be written on the memory embedded in the tag or a written data can be sent via backscattering. Therefore, RFID tags can be considered as energy harvesters, but not energy scavengers because they do not use ambient energy sources.

**Motorola (2000)** has already developed wireless tire pressure sensors combining RFID energy harvesters with battery powered sensors to report on the pressure of each tire to a central computer in a vehicle (Figure 1.1d). Efforts have been carried out to create a tire pressure monitoring system that recharges the battery through a vibration energy scavenger (**Roundy, 2003**).

Smart shoes convert the heel-strike energy of a walking or running person into electricity. **Shenck and Paradiso (2001)** reported that their prototype produces 8.4mW/foot strike using Lead-Zirconate-Titanate (PZT) stacks. Taking into account the given dimensions, proposed harvester yields to 0.2μW/mm<sup>3</sup> of power density. Department of Defense (DOD) of U.S. is also interested in using these transducers in order to decrease the heavy battery load of a soldier (A 40kg equipment consists of 1-2kg of battery.) as shown in Figure 1.2 (**DARPA, 2002**). Sport shoes companies (such as Nike Corporation) also find the idea attractive and work on it (**Adidas**).

**Figure 1.2:** In a DARPA funded project, SRI International is developing heel-strike generators that will eventually reduce the battery weight that a soldier needs to carry during a mission.

There are few companies that have been developing piezoelectric transducers including energy scavengers. Mide Company's product, called "Volture", is capable of generating 20mW power in the presence of a significant vibration (10mm@50Hz) but the package is very large degrading the power density to 3.2nW/mm<sup>3</sup> (Mide, 2005). Perpetuum Company has also developed piezoelectric microgenerators that have the power density of 2.7µW/mm<sup>3</sup> (Perpetuum, 2004).

#### 1.2.3 Piezoelectricity

The piezoelectric effect was discovered by Jacques and Pierre Curie in 1880. Piezoelectric behavior is defined as the generation of electricity from a material under pressure; it is also referred to as "direct piezoelectricity". "Converse piezoelectricity" can be defined as the phenomenon where applied voltage causes a material to change its shape. This behavior has been used in many applications such as transducers, microphones, buzzers, sensors and actuators (Senturia, 2001).

There are many crystals and ceramic structures that exhibit the piezoelectric phenomena, such as crystalline quartz (SiO<sub>2</sub>), zinc oxide (ZnO), lithium niobate (LiNbO<sub>3</sub>), poly-vinylidene fluoride (PVDF), lead-zirconate-titanate (Pb[Zr<sub>x</sub>Ti<sub>1-x</sub>]O<sub>3</sub> 0<x<1, also called PZT), barium titanate (BaTiO<sub>3</sub>), lead titanate (PbTiO<sub>3</sub>, called PT).

Piezoelectric crystals have perovskite structures. Above the Curie temperature<sup>2</sup>, the crystal has a cubical symmetry and does not have a piezoelectric effect (Figure 1.3a). Below this critical temperature polarization creates a net dipole as illustrated in Figure 1.3b.

A typical piezoelectric ceramic crystal lacks inversion symmetry; it can consist of an array of aligned electric dipoles within its structure when polarized as explained in Figure 1.3. Figure 1.4 illustrates the polarization effect. Without polarization, electric dipoles in the piezoelectric crystal are randomly oriented as shown in Figure 1.4a. When a strong electric field is applied, dipoles are well-oriented along the polarization axis (Figure 1.4b). Removing the electric field partially randomizes the dipoles but the crystal still consists of an electric charge because of the structure (Figure 1.4c).

<sup>2</sup> Above the Curie temperature, perovskite ceramic exhibits a simple cubic symmetry with no dipole moment (Moheimani and Fleming, 2006). This temperature changes with the material propery, however, it ranges between 200°C to 400°C (Ferroperm Piezoceramics).

**Figure 1.3:** Perovskite crystalline structure which is the form of ABO<sub>3</sub>; (a) cubic symmetry above the Curie temperature, (b) tetragonal symmetry after polarization below the Curie temperature.

After polarization, if a strain is applied to the ceramic along the polarization axis, a voltage will be generated. However, if the strain is quasi-static or DC, this voltage will be discharged through the parasitics of small DC leakage currents (Arnau, 2004). Therefore piezoelectric materials are mostly effective for sensing of vibratory or resonant motions (Senturia, 2001).

Analytical formulations will be given in Section 2.4.

**Figure 1.4:** Poling procedure of the piezoelectric crystal: (a) Prior to polarization, dipoles are random oriented, (b) A large DC electric field polarizes the structure so that dipoles are oriented in the same direction, (c) Permanent polarization remains after removing the DC field.

#### 1.2.4 Vibration Energy Scavengers

Vibration energy is a very promising alternative to solar energy where direct sunlight is not available. Furthermore, vibration based energy scavengers take outperform of solar systems at hard-to-reach locations where small form factor (~1mm³) nodes are needed. There are three types of transducers that convert vibration into electricity: electromagnetic, electrostatic and piezoelectric, as shown in Figure 1.5.

Figure 1.5: Examples of different types of vibration energy scavengers: (a) Electromagnetic (Williams and Yates, 1996); (b) Electrostatic (Miranda, 2004); (c) Piezoelectric (Roundy et al., 2005).

Electromagnetic scavengers consist of a coil and a permanent magnet as shown in Figure 1.5a. When vibration occurs, coil moves and changing magnetic field causes a current to flow along the coil. The voltage on the coil is simply determined by Faraday's Law. Considering low-level vibrations (up to 200Hz) and a form factor of 1cm<sup>3</sup>, an output voltage of only about 100mV can be generated. Therefore, electromagnetic vibration harvesters are not suitable for micro scale.

Electrostatic generation depicted in Figure 1.5b relies on the change of the capacitor value between its conductor layers which are moving relative to one another. Even if micro scale electrostatic transducers can generate voltages on the order of volts, there is a disadvantage that a separate voltage source is needed to start-up the charge sharing.

Piezoelectric generation uses a piezoelectric material which generates a voltage under a mechanical stress. Cantilever-based beam structures are generally used as illustrated in Figure 1.5c. The main disadvantage of this type of transducers is the fabrication complexity. If it can be tolerated, those would be very attractive for wireless sensor nodes. Table 1.2 compares these three vibration scavenging approaches.

**Table 1.2:** Comparison of vibration scavenging approaches.

| Mechanism       | Advantages                                   | Disadvantages                               |  |  |

|-----------------|----------------------------------------------|---------------------------------------------|--|--|

| Piezoelectric   | No voltage source needed Output voltage 1-8V | More difficult to integrate in microsystems |  |  |

| Electrostatic   | Easier to integrate in microsystems          | Separate voltage source needed              |  |  |

| Electromagnetic | No voltage source needed                     | Output voltage 0.1-0.2V                     |  |  |

#### 1.2.5 Current State of the Art in Piezoelectric-based Harvesters

As mentioned in the previous section, piezoelectric transducers are one of the most attractive miniature energy harvesters. Therefore, various research groups have been working to develop such transducers to use them in sensors, low-power microprocessors and wireless communication nodes (Amiratharajah et al., 1998, Lal et al., 2005, Jeon et al., 2005, Roundy and Wright, 2004). Most of designs use a cantilever beam undergoing deflections and a proof-mass to tune the system to work at resonance. Resonance frequency of the transducer is adjusted to the dominant frequency component in the ambient where the system is planned to work. This tuning ensures that the mechanical response and resulting harvested energy is maximized under linear limits.

The frame where the beam is clamped is excited by the ambient vibrations. Mechanical bending of the beam creates stress and it is converted to electric energy by the piezoelectric material.

Diode bridge rectifiers are used to generate a DC voltage which is stored on a large capacitor (up to micro farads) that is used to power the wireless sensor node circuitry.

These types of transducers can be built in cm scale; however, if mm-sized devices are of concern, scaling issues arise. In order for a system to maintain the same resonant frequency after scaling, thickness of the cantilever beam should be decreased with length and width. Doing this makes the beam thickness comparable with the piezoelectric thin-film layer and affects the mechanical response of the system. Because the ambient vibration amplitude is inversely proportional to the frequency, high quality factors (Q) are needed for low frequencies. Further than a few kHz, vibration amplitudes are only on the order of nanometers.

Figure 1.6 illustrates two piezoelectric-based transducer designs. Figure 1.6a shows a cm-scale device (Roundy and Wright, 2004). The 365 $\mu$ m thick PZT bimorph is used as a cantilever and a heavy Tungsten proof mass is attached on it to lower the resonance frequency. The vibration of the base or frame is 200 $\mu$ m@100Hz. Transducer generates 80 $\mu$ W at 13.1V for a 200 $\mu$ C load which corresponds to 40 $\mu$ W/cm<sup>3</sup> considering the packaging and the external capacitor (32 $\mu$ F). Figure 1.6b is a MEMS cantilever with a smaller proof mass comparing the form factor of the previous design, thus higher resonance frequency of 13.9kHz (Jeon et al., 2005). The device is 170 $\mu$ m x 260 $\mu$ m without the packaging and electronics. It is reported to generate 1 $\mu$ W at 2.4V for a 5.2M $\Omega$  load.

#### 1.2.6 Fundamental Limitations and a Solution Potential

There are several physical obstacles to achieve high-power density and small form factor devices with those state-of-the-art piezoelectric-based transducers. As depicted in Table 1.3, most ambient vibration sources have vibration frequencies below 200Hz. It is difficult to achieve low resonances with linear design approaches. In order to get high power efficiency, system should be operated at resonance and have high quality factor (Q) which introduces tight design specifications.

Figure 1.6: Piezoelectric vibration energy scavengers, both at (a) meso-scale (Roundy and Wright, 2004) and (b) micro-scale (Jeon et al., 2005).

**Table 1.3:** Vibration frequencies and amplitudes on the surface of various typical vibration sources (**Roundy and Wright, 2004**). The peak acceleration is at frequency below 200 Hz for almost all sources, with the peak displacement being at even lower in frequency.

| Vibration source                    | a (m/s²) | $ m f_{peak}$ |

|-------------------------------------|----------|---------------|

| Car engine compartment              | 12       | 200           |

| Base of 3-axis machine tool         | 10       | 70            |

| Blender casing                      | 6.4      | 121           |

| Clothes dryer                       | 3.5      | 121           |

| Person nervously tapping their heel | 3        | 1             |

| Car instrument panel                | 3        | 13            |

| Door frame just after door closes   | 3        | 125           |

| Small microwave oven                | 2.5      | 121           |

| HVAC vents in office building       | 0.2-1.5  | 60            |

| Windows next to a busy road         | 0.7      | 100           |

| CD on notebook computer             | 0.6      | 75            |

| Second storey floor of busy office  | 0.2      | 100           |

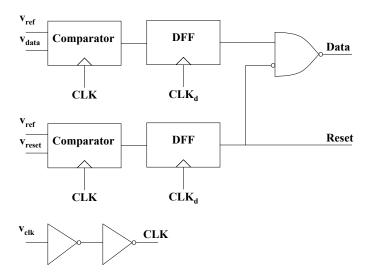

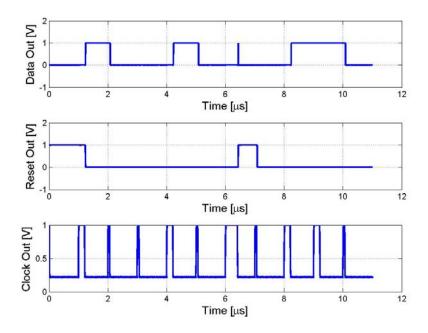

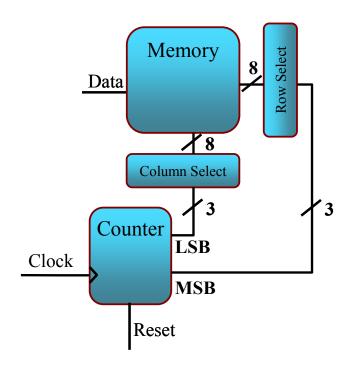

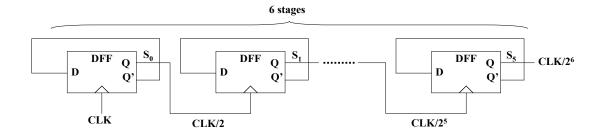

Furthermore, ambient vibration sources are practically stochastic; frequency and amplitude may vary, which shifts the optimum power generation operating point. **Elvin et al. (2001)** have proposed an adaptive tuning approach to alleviate this problem but it obviously increases the design complexity and degrades the small form factor approach.