# ISTANBUL TECHNICAL UNIVERSITY ★ GRADUATE SCHOOL OF SCIENCE ENGINEERING AND TECHNOLOGY

## DESIGN AND IMPLEMENTATION OF RSA CRYPTOSYSTEM USING PARTIALLY INTERLEAVED MODULAR KARATSUBA-OFMAN MULTIPLIER

**M.Sc. THESIS**

Ahmet ARIŞ

**Department of Computer Engineering**

**Computer Engineering Programme**

**JUNE 2012**

# ISTANBUL TECHNICAL UNIVERSITY ★ GRADUATE SCHOOL OF SCIENCE ENGINEERING AND TECHNOLOGY

### DESIGN AND IMPLEMENTATION OF RSA CRYPTOSYSTEM USING PARTIALLY INTERLEAVED MODULAR KARATSUBA-OFMAN MULTIPLIER

**M.Sc. THESIS**

Ahmet ARIŞ (504091501)

**Department of Computer Engineering**

**Computer Engineering Programme**

Thesis Advisor: Assoc. Prof. Dr. S. Berna ÖRS YALÇIN

**JUNE 2012**

## İSTANBUL TEKNİK ÜNİVERSİTESİ ★ FEN BİLİMLERİ ENSTİTÜSÜ

## İKİ PARÇALI ÖRGÜ MODÜLER KARATSUBA-OFMAN ÇARPICISI KULLANARAK RSA KRİPTOSİSTEMİ TASARIMI VE GERÇEKLEMESİ

YÜKSEK LİSANS TEZİ

Ahmet ARIŞ (504091501)

Bilgisayar Mühendisliği Anabilim Dalı

Bilgisayar Mühendisliği Programı

Tez Danışmanı: Doç. Dr. S. Berna ÖRS YALÇIN

HAZİRAN 2012

Ahmet ARIŞ, a M.Sc. student of ITU Graduate School of Science 504091501 successfully defended the thesis entitled "DESIGN AND IMPLEMENTATION OF RSA CRYPTOSYSTEM USING PARTIALLY INTERLEAVED MODULAR KARAT-SUBA-OFMAN MULTIPLIER", which he prepared after fulfilling the requirements specified in the associated legislations, before the jury whose signatures are below.

| Thesis Advisor : | Assoc. Prof. Dr. S. Berna ÖRS YALÇIN<br>Istanbul Technical University |  |

|------------------|-----------------------------------------------------------------------|--|

| Jury Members :   | <b>Prof. Dr. Ece Olcay GÜNEŞ</b><br>Istanbul Technical University     |  |

|                  | Asst. Prof. Dr. D. Turgay ALTILAR<br>Istanbul Technical University    |  |

Date of Submission :4 May 2012Date of Defense :6 June 2012

To the gorgeous people in my life,

### FOREWORD

Without the help and support of some gorgeous people in my life, I do not think I would able to achieve anything.

During this thesis and my masters degree, Assoc. Prof. Dr. S. Berna Örs Yalçın has been an ideal advisor for me. Her support, ideas and comments always ignited me to work better. My other advisor, who accepted me to his career project and gave me chance to implement his original algorithm is Assis. Prof. Dr. Gökay Saldamlı. He has been an excellent advisor too. He was always going in front of me, coming up with new implementation ideas. His knowledge and experience served me as a model.

I would like to thank to my family(my dad, mum and brothers Osman and Aziz) and my girlfriend Mairi. They were always with me although we were mostly hundreds of kms far from each other physically. I always felt their support in troublesome situations and always celebrated my successes with them. In addition to my biological family and Mairi, there is also another family, namely Çaçaron family, who have been helping and supporting me since the English prep year of high school till now. They have always accepted me as a member of their family and I have always seen them as my family. I am wishing our relation to last for many more years. I would love to thank to all of them especially to Uğur Çaçaron.

I would also like to thank to my teachers from primary school and high school, namely Gürzat Kışlak, Yücel Erdoğan, Ozan Özel. Also my very close friends Şaban and Adem never left me alone for more than 15 years. Although primary school and high school years have already passed, they have always been great friends.

Lastly, I am grateful to my friends working in GSTL laboratory and my flatmates for their company and İnce Minare Cami foundation for their support.

June 2012

Ahmet ARIŞ Computer Engineer

### **TABLE OF CONTENTS**

## Page

| FOREWORD                                                         | ix   |

|------------------------------------------------------------------|------|

| TABLE OF CONTENTS                                                | xi   |

| ABBREVIATIONS                                                    | xiii |

| LIST OF TABLES                                                   | XV   |

| LIST OF FIGURES                                                  | kvii |

| LIST OF SYMBOLS                                                  | xix  |

| SUMMARY                                                          | xxi  |

| ÖZETx                                                            | xiii |

| 1. INTRODUCTION                                                  | 1    |

| 2. THEORETICAL BACKGROUND                                        | 5    |

| 2.1 The RSA Cryptosystem                                         | 5    |

| 2.2 Modular Exponentiation                                       | 7    |

| 2.2.1 The binary method                                          | 8    |

| 2.3 Modular Multiplication                                       | 10   |

| 2.3.1 Classic modular multiplication                             | 10   |

| 2.3.2 Montgomery Multiplication                                  | 12   |

| 2.3.3 Bipartite Modular Multiplication                           |      |

| 2.4 Partially Interleaved Modular Karatsuba-Ofman Multiplication | 17   |

| 2.4.1 Karatsuba-Ofman multiplication                             |      |

| 2.4.2 Interleaving BMM and KO multiplication                     |      |

| 2.5 Integer Multiplication                                       |      |

| 2.5.1 Shift and accumulate method                                |      |

| 2.6 Booth Encoding                                               |      |

| 3. IMPLEMENTATION ENVIRONMENT                                    |      |

| 3.1 Device Technologies                                          |      |

| 3.1.1 FPGA                                                       | 30   |

| 3.1.2 ASIC                                                       | 31   |

| 3.2 Maple                                                        |      |

| 3.3 FPGA Design Tools                                            | 34   |

| 3.4 ASIC Design Tools                                            |      |

| 4. HARDWARE IMPLEMENTATION                                       |      |

| 4.1 Dot Diagrams                                                 | 37   |

| 4.2 Adder Structures                                             | 40   |

| 4.2.1 Carry Lookahead Adder                                      | 42   |

| 4.2.2 Carry Save Adder                                           | 43   |

| 4.3 Partially Interleaved Modular KO Multiplier            | 44 |

|------------------------------------------------------------|----|

| 4.3.1 Radix-2 Classic Modular Multiplier                   | 46 |

| 4.3.2 Radix-2 Montgomery Multiplier                        | 49 |

| 4.3.3 Radix-4 Integer Multiplier                           | 49 |

| 4.3.4 Implementation Results                               | 53 |

| 4.4 High Radix Partially Interleaved Modular KO Multiplier | 55 |

| 4.4.1 Control Signals                                      | 56 |

| 4.4.2 High Radix Choice                                    | 56 |

| 4.4.3 Radix-4 Classic Modular Multiplier                   | 57 |

| 4.4.4 Radix-4 Booth Encoded Montgomery Multiplier          | 60 |

| 4.4.5 Radix-8 Integer Multiplier                           | 64 |

| 4.4.6 Integration of Multipliers                           | 65 |

| 4.4.7 Implementation Results                               | 68 |

| 5. CONCLUSION                                              | 71 |

| REFERENCES                                                 |    |

| CURRICULUM VITAE                                           | 77 |

### ABBREVIATIONS

| AES  | : Advanced Encryption Standard               |  |

|------|----------------------------------------------|--|

| ASIC | : Application Specific Integrated Circuit    |  |

| BMM  | : Bipartite Modular Multiplication           |  |

| CLA  | : Carry Lookahead Adder                      |  |

| CPLD | : Complex Field Programmable Logic Device    |  |

| CSA  | : Carry Save Adder                           |  |

| FA   | : Full Adder                                 |  |

| FPGA | : Field Programmable Gate Array              |  |

| HA   | : Half Adder                                 |  |

| IC   | : Integrated Circuit                         |  |

| КО   | : Karatsuba-Ofman                            |  |

| LSB  | : Least Significant Bit                      |  |

| MSB  | : Most Significant Bit                       |  |

| РКС  | : Public Key Cryptosystem                    |  |

| RSA  | : Rivest-Shamir-Adleman                      |  |

| RTL  | : Register Transfer Level                    |  |

| TSMC | : Taiwan Semiconductor Manufacturing Company |  |

| VHDL | : VHSIC Hardware Description Language        |  |

|      |                                              |  |

### LIST OF TABLES

## Page

| 2.1 | :                                                                                                                                                         | Public-key Directory, adapted from (Koç, 1994).                                                 | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2 | :                                                                                                                                                         | Binary Method Steps, adapted from (Koç, 1994).                                                  | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.3 | :                                                                                                                                                         | Total Number of Multiplication for Binary Method, adapted                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |                                                                                                                                                           | from(Koç, 1994)                                                                                 | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.4 | :                                                                                                                                                         | Modified Booth Encoding Scheme.                                                                 | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.1 | :                                                                                                                                                         | FPGA Implementation Results.                                                                    | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.2 | :                                                                                                                                                         | Comparison of 1024-bit Implementations                                                          | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.3 | :                                                                                                                                                         | Montgomery Encoding Scheme.                                                                     | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.4 | :                                                                                                                                                         | Multiplexing Scheme for Partial Products.                                                       | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.5 | :                                                                                                                                                         | Implementation Results of Modular Multiplier                                                    | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.6 | :                                                                                                                                                         | Comparison of 1024-bit Implementations                                                          | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.7 | :                                                                                                                                                         | Implementation Results of RSA encryption ( $e = 2^{16} + 1$ )                                   | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.8 | :                                                                                                                                                         | Comparison of 1024-bit RSA Encryptions.                                                         | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.9 | :                                                                                                                                                         | Comparison of 1024-bit RSA Decryptions.                                                         | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | <ul> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> </ul> | 2.2 :<br>2.3 :<br>2.4 :<br>4.1 :<br>4.2 :<br>4.3 :<br>4.4 :<br>4.5 :<br>4.6 :<br>4.7 :<br>4.8 : | <ul> <li>2.1 : Public-key Directory, adapted from (Koç, 1994).</li> <li>2.2 : Binary Method Steps, adapted from (Koç, 1994).</li> <li>2.3 : Total Number of Multiplication for Binary Method, adapted from(Koç, 1994).</li> <li>2.4 : Modified Booth Encoding Scheme.</li> <li>4.1 : FPGA Implementation Results.</li> <li>4.2 : Comparison of 1024-bit Implementations.</li> <li>4.3 : Montgomery Encoding Scheme.</li> <li>4.4 : Multiplexing Scheme for Partial Products.</li> <li>4.5 : Implementation Results of Modular Multiplier.</li> <li>4.6 : Comparison of 1024-bit Implementations.</li> <li>4.7 : Implementation Results of RSA encryption (<i>e</i> = 2<sup>16</sup> + 1).</li> <li>4.8 : Comparison of 1024-bit RSA Encryptions.</li> </ul> |

### LIST OF FIGURES

## Page

| Figure 1.1 : Sy | ymmetric Key Cryptography.                                      | 1  |

|-----------------|-----------------------------------------------------------------|----|

| Figure 1.2 : Pu | ublic Key Cryptography                                          | 2  |

| Figure 2.1 : Lo | eft-to-Right Modular Multiplication, adapted from (Saldamlı,    |    |

| 20              | 11)                                                             | 12 |

| Figure 2.2 : R  | ight-to-Left Modular Multiplication, adapted from (Saldamlı,    |    |

| 20              | 11)                                                             | 15 |

| Figure 2.3 : B  | ipartite Modular Multiplication, adapted from (Saldamlı, 2011)  | 16 |

| Figure 2.4 : K  | aratsuba-Ofman Multiplication, adapted from (Saldamlı, 2011)    | 19 |

| Figure 2.5 : Pa | artially Interleaved Modular Karatsuba-Ofman Multiplication,    |    |

| ada             | apted from (Saldamlı, 2011).                                    | 21 |

| Figure 2.6 : B  | lock Diagram of the Method, adapted from (Saldamlı, 2011)       | 22 |

| Figure 2.7 : SI | hift and Accumulate Method, adapted from (Parhami, 2000)        | 23 |

| Figure 2.8 : 82 | x8 Modified Booth Multiplication, adapted from (Bewick, 1994)   | 25 |

| Figure 2.9 : 82 | x8 Booth Multiplication with Positive Partial Products, adapted |    |

| fro             | om (Bewick, 1994)                                               | 26 |

| Figure 2.10: 82 | x8 Booth Multiplication with Negative Partial Products, adapted |    |

| fro             | om (Bewick, 1994)                                               | 27 |

| -               | egative Partial Products with Summed Sign Extension, adapted    |    |

| fro             | om (Bewick, 1994)                                               | 27 |

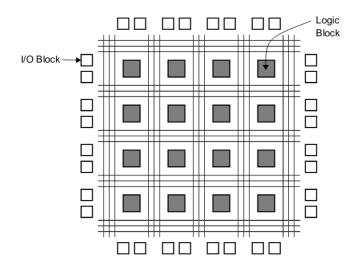

| _               | PGA Architecture, adapted from (Brown, 1996).                   | 30 |

| Figure 4.1 : 8- | -bit Multiplication Dot Diagram, adapted from (Bewick, 1994)    | 38 |

| Figure 4.2 : R  | adix-2 Montgomery Multiplication Dot Diagram                    | 39 |

| Figure 4.3 : Fu | ull Adder and A 4-bit Ripple Carry Adder, adapted from (Koren,  |    |

| 20              | 02)                                                             | 40 |

| Figure 4.4 : 4- | -bit Carry Lookahead Adder, adapted from (Pedroni, 2004)        | 42 |

| Figure 4.5 : A  | (3,2) Carry Save Adder, adapted from (Koren, 2002)              | 44 |

| Figure 4.6 : A  | (4,2) Carry Save Adder and (5;3) Compressor.                    | 44 |

| Figure 4.7 : B  | lock diagram of Partially Interleaved Modular KO Multiplier     | 45 |

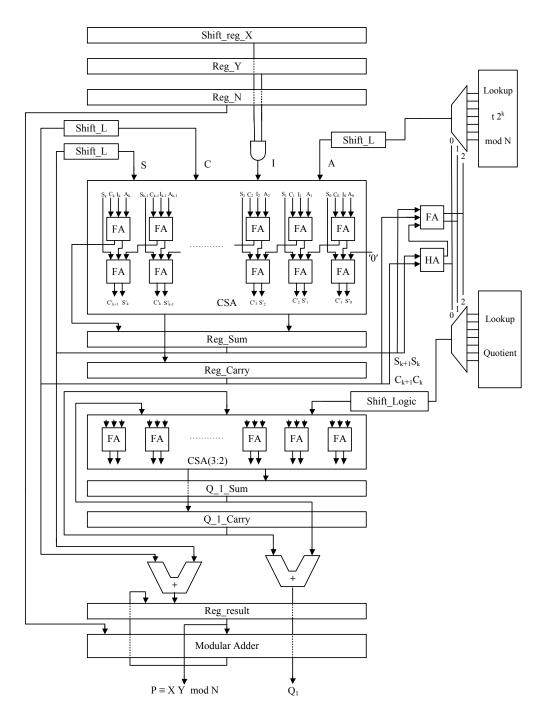

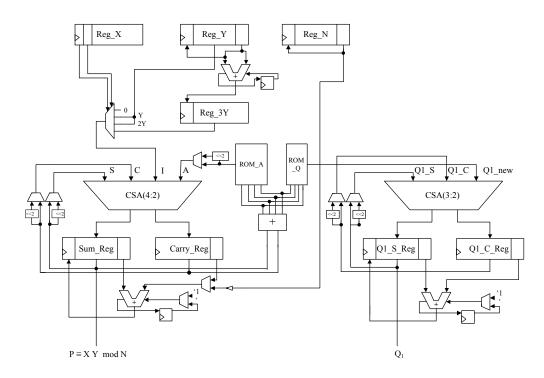

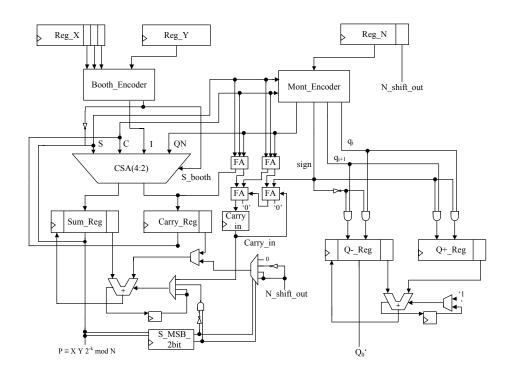

| 0               | lock diagram of Radix-2 Classic Modular Multiplier with         |    |

| Qu              | notient Calculation                                             | 50 |

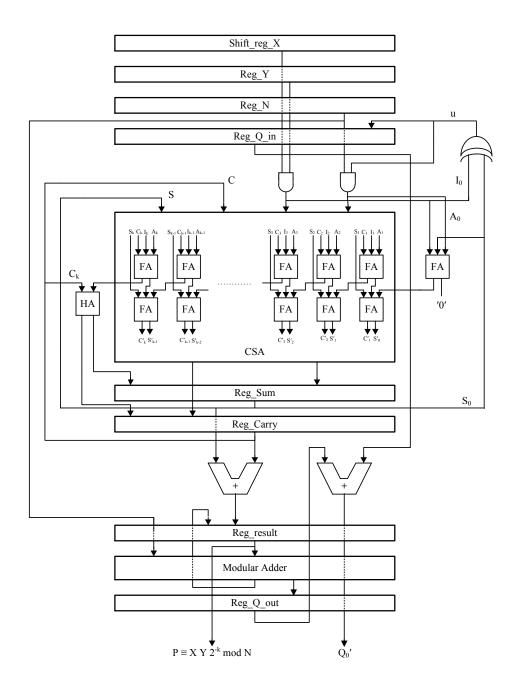

| -               | lock diagram of Radix-2 Montgomery Multiplier with $Q'_0$       |    |

| Ca              | llculation.                                                     | 52 |

| 0               | ritical Path of a Design                                        | 56 |

|                 | lock Diagram of the Radix-4 Classic Modular Multiplier with     |    |

| Qu              | otient Calculation                                              | 59 |

| Figure 4.12: | Block Diagram of the Radix-4 Montgomery Multiplier with $Q'_0$ |    |

|--------------|----------------------------------------------------------------|----|

|              | Calculation.                                                   | 63 |

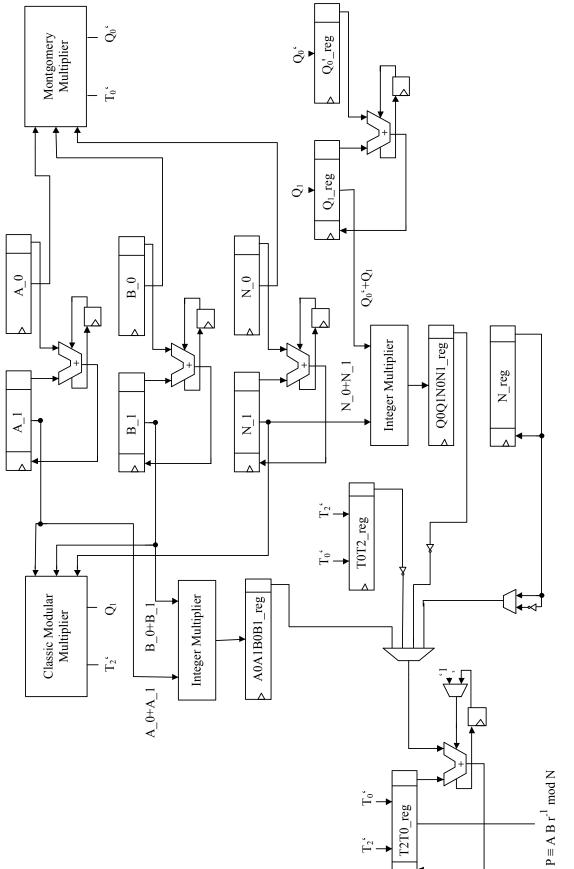

| Figure 4.13: | High Radix Partially Interleaved Modular KO Multiplier         | 66 |

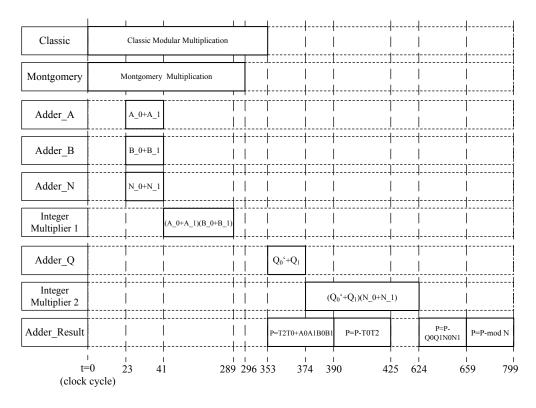

| Figure 4.14: | Job Scheduling Table                                           | 67 |

## LIST OF SYMBOLS

gcd:Greatest Common Divisor $\mathscr{H}(E)$ :Hamming Weight of E: number of 1's in the binary expansion of E $\phi(N)$ :Euler's Totient Function of N

### DESIGN AND IMPLEMENTATION OF RSA CRYPTOSYSTEM USING PARTIALLY INTERLEAVED MODULAR KARATSUBA-OFMAN MULTIPLIER

#### SUMMARY

Importance of cryptography is becoming more and more important day by day. Secure communication will always be a crucial need independent from the technology in use. Applications of cryptography can be seen in online banking, purchases of goods and services by means of credit cards, ID cards, remote lock and start systems for cars, telecommunication, and in many more places. Different cryptosystems are employed according to different needs and different security levels.

Rivest-Shamir-Adleman(RSA) Algorithm is one of the most popular cryptosystem that is used in many sectors like banking. It takes its strength from factorization of very large integers. Briefly, it consists of modular exponentiations with large integers which are 1024-bit or 2048-bit numbers. As modular exponentiation operations are fundamentally composed of modular multiplications, designing a fast RSA cryptosystem becomes possible only with a fast modular multiplier implementation. Due to security and speed issues, modular exponentiation in RSA is implemented in software and modular multiplications are carried out in modular multipliers which are implemented in hardware.

Many methods exist in the literature in order to perform modular exponentiation. These methods try to reduce the total number of multiplications that are required for a modular exponetiation operation. In addition to modular exponentiation algorithms, there are several techniques to do modular multiplication as well. Modular multiplication may be carried out either by multiplying first and performing reduction later on, or by interleaving multiplication and reduction stages. In order to reach compact hardware designs the latter approach is utilized. According to the direction of reduction operation, modular multiplication algorithms may be classified into two groups, which are algorithms reducing from left-to-right and from right-to-left. The most well known examples of left-to-right approach are Blakley and Barrett algorithms, whereas Montgomery multiplication is the only member of the right-to-left modular multiplication. Although fast multiplication algorithms, such as Karatsuba-Ofman(KO), Schönhage-Strassen exist, these multiplication methods can not be interleaved with reduction algorithms. This is caused from the reduction approaches not allowing parallel processing. However, Bipartite Modular Multiplication(BMM) method introduced by Kaihara and Takagi proposes a partial solution to the parallel reduction problem. This reduction method modifies a feature of Montgomery algorithm. This modification separates the multiplier bits into two halves so that a product can be reduced from left and right simultaneously without a dependency issue.

The first method which combines Karatsuba-Ofman multiplication with bipartite reduction was proposed by Gökay Saldamlı. His algoritm, namely Partially Interleaved Modular Karatsuba-Ofman Multiplication, interleaves KO multiplier with the bipartite reduction on the uppermost layer of KO's recursion. Implementation of this new method requires Montgomery multiplier, Blakley multiplier and standard integer multipliers. However, for this approach, both Montgomery and Blakley multipliers are needed to be designed in a way that, they compute not only the modular multiplication result, but also quotient values, what is somewhat different than existing implementations.

In this thesis, two hardware implementations of Partially Interleaved Modular KO Multiplication and an RSA implementation utilizing the designed multiplier are proposed. The first design is Radix-2 implementation on FPGA technology. The second hardware implementation explores the design methodologies in order to reach a faster modular multiplier. These design methodologies include employing high radices, optimization of critical path according to the effect of control signals and analyzing parameter dependencies in Partially Interleaved Modular KO Multiplier and scheduling jobs effectively. Improved design was implemented on ASIC technology using 90 nm TSMC standard cell libraries in Design Compiler.

Hardware implementations proposed in this thesis are the first hardware implementations of Partially Interleaved Modular KO Multiplication method. Montgomery and Blakley multiplication algorithms were modified in order to produce desired results. Maple libraries which emulate the operation of hardware building blocks were written and both hardware implementations were firstly implemented in Maple. Tests were run with random input vectors and when correct operation of Maple implementations were verified, hardwares were described in VHDL and implemented using FPGA and ASIC design tools respectively. The second implementation of Partially Interleaved Modular KO multiplier was used as a modular multiplier for RSA cryptosystem and very promising results which are comparable with commercial RSA chips were achieved.

## İKİ PARÇALI ÖRGÜ MODÜLER KARATSUBA-OFMAN ÇARPICISI KULLANARAK RSA KRİPTOSİSTEMİ TASARIMI VE GERÇEKLEMESİ

### ÖZET

Kriptografinin, yani şifreleme biliminin önemi gün geçtikçe artmaktadır. Kullanılan teknoloji ne olursa olsun güvenli iletişim her zaman en başta gelen ihtiyaçlardan birisi olacaktır. Günümüzde şifreleme, sistemlere kullanıcı hesabıyla giriş yapılıyorken, internetten herhangi bir hizmet ya da ürün satın alınıyorken, iletişim araçları kullanılıyorken, araçların kapıları uzaktan kilitlenip açılıyorken ve daha birçok yerde kullanılmaktadır. Kullanım alanına ve güvenlik ihtiyacının niteliğine göre değişik şifreleme algoritmaları farklı teknolojilerle karşımıza çıkmaktadır. Bu algoritmaların bir tanesi de Rivest-Shamir-Adleman(RSA) şifreleme sistemidir. RSA bankacılık başta olmak üzere birçok sektörde şifreleme ve sayısal imza işlemleri için sıklıkla kullanılmaktadır.

RSA algoritması gücünü çok büyük sayıların asal çarpanlarına ayrılmalarındaki zorluktan almaktadır. Özetle çok büyük sayılarla yapılan modüler üs alma işlemlerinden oluşmaktadır. Modüler üs alma işlemleri de özünde modüler çarpma işlemlerinden ibaret olduğu için hızlı bir RSA gerçeklemesi ancak hızlı modüler çarpma işlemi yapan bir tasarımla mümkün olmaktadır. Güvenlik ve hız gibi sebeplerden ötürü RSA kriptosistemi genellikle modüler üs alma işleminin yazılımda gerçeklenmesi ve modüler çarpma işlemlerinin de donanımda tasarlanan özel bloklarla yapılması yoluyla gerçeklenir.

Modüler üs alma işlemi için birçok yöntem mevcuttur. Bu yöntemler modüler üs alma işlemi esnasında yapılan modüler çarpma işlemi sayısını değişik yöntemlerle en aza indirmeye çalışırlar. Modüler çarpma işlemi için de bilim dünyasında epeyi calışmalar yapılmıştır. Modüler çarpma, önce çarpıp sonra indirgeme yapma ya da çarpma ve indirgeme işlemlerini iç-içe yapma gibi iki yöntemle mümkündür. Alan kısıtlamaları sebebiyle çoğunlukla ikinci metot tercih edilmektedir. İndirgeme işleminin uygulanma yönüne göre modüler çarpma algoritmaları soldan sağa doğru işleyenler ve sağdan sola doğru işleyenler olmak üzere ikiye ayrılır. Soldan sağa doğru işleyen yöntemlerin en bilindik örnekleri Blakley ve Barrett algoritmalarıdır. Sağdan sola doğru indirgeme yapan sınıfa ise tek örnek Montgomery yöntemidir. Hızlı çarpma yapan Karatsuba-Ofman, Schönhage-Strassen gibi yöntemler olsa da bu hızlı çarpıcılar indirgeme algoritmalarıyla birleştirilememektedirler. Bu sorun paralel çalışmaya izin vermeyen indirgeme yöntemlerinden kaynaklanmaktadır. Ancak Kaihara ve Takagi tarafından bilim dünyasına sunulan İki Parçalı Modüler çarpma yöntemi bu soruna bir nebze de olsa çözüm bulmaktadır. Bu indirgeme metodu Montgomery algoritmasının sahip olduğu bir özelliği kullanarak modüler çarpmadaki çarpanı ikiye ayırmakta ve böylelikle Blakley ve Montgomery paralel olarak çalışabilmektedir.

Hızlı çarpma algoritmalarından birisi olan Karatsuba-Ofman yöntemiyle İki Parçalı indirgemeyi birleştiren ilk çalışma Gökay Saldamlı tarafından ortaya atılmıştır. İki Parçalı Örgü Karatsuba-Ofman çarpıcısı iki parçalı indirgemeyi Karatsuba-Ofman rekürsif çarpma yönteminin en üst katmanında birleştirmektedir. Bu yeni yöntemin gerçeklenmesinde Montgomery çarpıcısına, Blakley modüler çarpıcısına ve standart çarpma yapan bloklara ihtiyaç vardır. Ancak bu algoritma Montgomery ve Blakley modüllerinde literatürdeki daha önceki gerçeklemelerde bulunmayan değerlerin de hesaplanmasına gereksinim duymaktadır.

Bu tezde İki Parçalı Modüler Örgü Karatsuba-Ofman çarpıcısının donanımda gerçeklenmesine ait iki çalışma ve bu tasarımlardan birisi kullanılarak gerçeklenen RSA kriptosistemi anlatılmaktadır. Bu çalışmalardan ilki çarpanı birer bit işleyen gerçeklemedir. FPGA teknolojisinde gerçeklenmiştir. İkinci gerçekleme ise ilk tasarımdaki eksikleri kapatan ve daha hızlı bir modüler çarpma için kodlama yöntemleri, daha fazla sayıda bit işleme, donanımın çalışma frekansını arttırmak için en büyük gecikmeye sahip yolu kontrol sinyallerini kullanarak optimize etmeye çalışan bir ASIC gerçeklemesidir.

Bu tezdeki donanım tasarımları İki Parçalı Örgü Karatsuba-Ofman çarpma yönteminin ilk gerçeklemeleridirler. Montgomery ve Blakley algoritmaları bu yeni yöntem için yeniden düzenlenmiştir. Tasarımların ikisi için de Maple'da kütüphaneler oluşturulmuş ve iki tasarım da Maple ortamında donanımla aynı yapıda gerçeklenmiş, gerekli testler yapılmış ve simülatörlerden gelen sonuçlarla yazılım gerçeklemesinden gelen sonuçlar karşılaştırılarak tasarımların doğru çalıştığı kanıtlanmıştır. İkinci modüler çarpma gerçeklemesi RSA kriptosistemi içinde modüler çarpıcı olarak kullanılmış ve piyasadaki RSA kırmıklarıyla karşılaştırılabilir sonuçlara ulaşılmıştır.

#### **1. INTRODUCTION**

The importance of cryptography dates back to the time of Julius Caesar. Since then, the communication medium has been changing from letter to radio, radio to telephone, personal computers and Internet, and currently smart phones. But the need for communicating securely remained crucial, independent from the underlying technology.

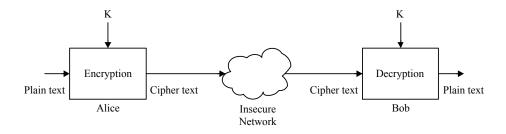

Cryptosystems may be classified into two categories: Symmetric Key Cryptosystems and Public Key Cryptosystems(PKC). In symmetric key cryptosystems, same secret key is used both for encryption and decryption operations. AES [1] is the most famous algorithm used in this class. A simple diagram can be seen in the Figure 1.1

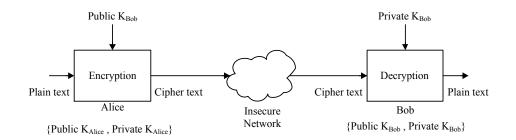

In PKC, there are key pairs for each communication endpoints, namely public key and private key. As shown in the Figure 1.2, when Alice wants to send a message to Bob, Alice encrypts her message(plain text) with the public key of Bob which is public to everybody. She sends the encrypted message(cipher text) over an insecure channel. Underlying mathematical properties of PKC allow only Bob to decrypt it with his private key, which is only known by him.

RSA [2] is the most popular PKC. It gets its strength from the difficulty of large integer factorization. In exchange for providing a robust security, it has the drawback of modular exponentiation operation with very large integers (i.e. 1024, 2048-bit). Due to

Figure 1.1: Symmetric Key Cryptography.

Figure 1.2: Public Key Cryptography.

the timing and security requirements, RSA cyrptosystem has been widely implemented on dedicated hardware, rather than software, either on FPGA or ASIC chips.

Modular exponentiation with large modulus in RSA consists of modular multiplication operations. Favorably, modular exponentiation is implemented in software, using modular multipliers that are implemented in hardware. In order to perform fast encryption or decryption, one has to decrease the total number of modular multiplications within a modular exponentiation by means of scanning techniques like m-ary method.

The key point in reaching a fast RSA cryptosystem is implementing a fast modular multiplier and using it with a modular exponentiation method which allows RSA to be performed in the least number of modular multiplications in the shortest amount of time.

Modular multiplication operation can be performed in two ways: either multiplying first and then reducing the product later or, interleaving the multiplication and reduction stages. In order to reach compact hardware designs, second approach is generally preferred by designers. There are various methods of applying reduction. There are also many ways to perform fast multiplication. The logical way to design a fast modular multiplier would be selecting best candidates from each set. But because of the dependency issue of the reduction algorithms which does not allow parallel reduction, fast multipliers such as Karatsuba-Ofman (KO) [3] could not be interleaved with these methods. However, couple of recent studies [4], [5] demonstrated a partial method of interleaving KO multiplier with the bipartite reduction on the uppermost layer of KO's recursion. Bipartite Modular Multiplication (BMM) method [6], [7]

which was originally introduced by Kaihara and Takagi, outlines a global method of parallel reduction in the way that, a product can be reduced from left and right simultaneously without a dependency issue.

In this thesis, two hardware implementations and an RSA cryptosystem employing the designed fast multiplier will be presented. The first multiplier design implements Partially Interleaved Modular KO Multiplier on FPGA platform. The second one explores the optimizations for the algorithm and for the previous design and implements the high radix version of the multiplier on ASIC, in order to reach a very fast RSA with the help of selected modular exponentiation methods. This work also aims to propose a new design methodology to the cryptographic hardware developers that has never been paid attention to. Up until now, the effect of control path to the critical path of a design has always been neglected. But, when a critical path of a design is analyzed, the impact of control path shows itself with extra logic gates inserted into the critical path, which was not an issue that designer counts. This study emphasizes control-path-aware digital design which will hopefully help designers to achieve faster cryptographic hardware designs.

This thesis is organized in a way that, firstly preliminaries will be given in Chapter 2. Then in Chapter 3, implementation environment and design tools will be presented. Hardware implementations of Partially Interleaved Modular KO Multiplication method will be explained in detail in Chapter 4. Chapter 5 will conclude the thesis.

#### 2. THEORETICAL BACKGROUND

In this chapter, preliminaries will be given about RSA cryptosystem, modular exponentiation and modular multiplication operations, Partially Interleaved Modular Karatsuba-Ofman Multiplication algorithm, standard multiplication algorithm and Booth Encoding.

### 2.1 The RSA Cryptosystem

The RSA is one of the most famous public key cryptosystem. It was invented by Rivest, Shamir and Adleman [2]. It is used both to exchange private messages and sign digital documents. In RSA every communication endpoint has a key pair, particularly public key and private key. These keys are calculated as follows [8]:

Let *p* and *q* be two distinct large random primes. The modulus *n* is the product of these two primes: n = pq. Euler's totient function of n is given by

$$\phi(n) = (p-1)(q-1)$$

(2.1)

Now, select a number  $1 < e < \phi(n)$  such that

$$gcd(e,\phi(n)) = 1$$

and compute d with

$$d \equiv e^{-1} \bmod \phi(n)$$

using the extended Euclidean algorithm [9]. Here, *e* is the public exponent and *d* is the private exponent. Usually one selects a small public exponent, e.g.,  $e = 2^{16} + 1$ . The modulus *n* and the public exponent *e* are published. The value of *d* and the prime numbers *p* and *q* are kept secret. With public exponent e and modulus n and private exponent d, encryption and decryption operations of RSA are performed as follows:

Let plain text and cipher text are denoted by M and C respectively. Then, RSA encryption is the operation of

$$C = M^e(\bmod n) \tag{2.2}$$

where  $0 \le M < n$ . Retrieval of the original message, which is simply RSA decryption is carried out as

$$M = C^d (\bmod n) \tag{2.3}$$

The correctness of RSA algorithm follows from Euler's theorem : Let n and a be positive, relatively prime integers. Then,

$$a^{\phi(n)} = 1 \pmod{n}.$$

(2.4)

Since we have  $ed = 1 \mod \phi(n)$ , i.e.,  $ed = 1 + K\phi(n)$  for some integer K, we can write

$$C^{d} = (M^{e})^{d} \pmod{n}$$

$$= M^{ed} \pmod{n}$$

$$= M^{1+K\phi(n)} \pmod{n}$$

$$= M \cdot (M^{\phi(n)})^{K} \pmod{n}$$

$$= M \cdot 1 \pmod{n}$$

provided that gcd(M, n) = 1.

Public-key directory, as shown in the Table 2.1, contains the pairs (e,n) for each user. The pair  $n_a$  and  $e_a$  are the modulus and public exponent for Alice respectively. If Alice wants to send a private message to Bob, then she executes the following steps [8]:

| User  | Public Keys  |

|-------|--------------|

| Alice | $(e_a, n_a)$ |

| Bob   | $(e_b, n_b)$ |

|       |              |

| •••   | •••          |

Table 2.1: Public-key Directory, adapted from (Koç, 1994).

- 1. Alice obtains Bob's public-key exponent and modulus  $(e_b, n_b)$  from the directory.

- 2. Alice computes  $C = M^{e_b} (\mod n_b)$ .

- 3. Alice sends *C* to Bob over the network.

- 4. Bob receives *C* and uses his private-key exponent and modulus and computes  $M = C^{d_b} (\mod n_b)$  in order to obtain *M*.

RSA provides robust security by means of its large distinct primes p and q. Large modulus n and d makes integer factorization infeasible using the current technology. As processing capabilities of computers increase, security parameters of RSA change in parallel.

In exchange for ensuring a strong security, RSA has a drawback of modular exponentiation operations with very large integers(i.e., 1024-bit). Due to the timing and security requirements RSA cyrptosystem is widely implemented on dedicated hardware(either on FPGA or ASIC chips), rather than software.

### 2.2 Modular Exponentiation

As Koç states in his report [8], the first rule of modular exponentiation is not to compute

$$C = M^e \pmod{n}$$

by first exponentiating

#### $M^e$

and then performing a division to obtain the remainder

$$C = M^e(\% n).$$

Due to the space requirements, temporary results must be reduced modulo n at each step of the exponentiation. This means modular exponentiation operation has to consist of series of modular multiplications.

Accompanying different methods for modular exponentiation yields different performances. In order to speed up the modular exponentiation operation, a scanning method for the exponent must be chosen which allows modular exponentiation to be performed in the least number of modular multiplications. The simplest way to compute  $C = M^e \pmod{n}$  would be starting with  $C = M \pmod{n}$  and then performing  $C = C \cdot M \pmod{n}$  for e - 1 times. For example, assume e = 20, then using this approach, one modular exponentiation would be completed in 19 multiplications:

$$M \rightarrow M^2 \rightarrow M^3 \rightarrow M^4 \rightarrow M^5 \rightarrow \cdots \rightarrow M^{20}$$

However, not all powers of *M* are needed to be computed in order to obtain  $M^{20}$ . For example a faster method to compute  $M^{20}$  is shown below:

$$M \to M^2 \to M^4 \to M^5 \to M^{10} \to M^{20}$$

As it can be seen clearly, only 5 multiplications are needed to calculate  $M^{20}$ . This approach is known as *binary method* or *square and multiply method* and it can be used to compute  $M^e$  for any e [8].

#### 2.2.1 The binary method

The binary method scans the exponent bit by bit either from left to right(MSB to LSB) or right to left. At it can be understood from the name, a squaring is performed at each step and then according to the scanned exponent bit, either a multiplication is done or not. Let k denote the number of bits in the exponent, then the binary method can be seen in the Algorithm 1.

For example, let e = 116 = (1110100). Here k = 7. Since  $e_{k-1} = e_6 = 1$  initially C = M. The binary method proceeds as shown in the Table 2.2.

Algorithm 1 The Binary Method.

**Require:** M, e, n**Ensure:**  $C = M^e \pmod{n}$ 1: **if**  $e_{k-1} = 1$  **then** 2: C := M;3: else C := 1;4: 5: **end if** 6: for i = k - 2 downto 0 do  $C := C \cdot C( \mod n)$ 7: if  $e_i = 1$  then 8:  $C := C \cdot M(\mod n)$ 9: end if 10: 11: end for 12: return C

Table 2.2: Binary Method Steps, adapted from (Koç, 1994).

| i | e <sub>i</sub> | Step 7                 | Step 9                    |

|---|----------------|------------------------|---------------------------|

| 5 | 1              | $(M)^2 = M^2$          | $M^2 \cdot M = M^3$       |

| 4 | 1              | $(M^3)^2 = M^6$        | $M^6 \cdot M = M^7$       |

| 3 | 0              | $(M^7)^2 = M^{14}$     | $M^{14}$                  |

| 2 | 1              | $(M^{14})^2 = M^{28}$  | $M^{28} \cdot M = M^{29}$ |

| 1 | 0              | $(M^{29})^2 = M^{58}$  | $M^{58}$                  |

| 0 | 0              | $(M^{58})^2 = M^{116}$ | $M^{116}$                 |

As shown in the Table 2.2, in order to compute  $M^{116}$  6 + 3 = 9 multiplications are needed. For an arbitrary *k*-bit number *e* with  $e_{k-1} = 1$ , the binary method requires [8]:

- Squarings(Step 7): k 1

- Multiplications(Step 9): H(e) 1 where H(e) is the Hamming Weight of e.

$0 \le H(e) - 1 \le k - 1$ , assuming e > 0. Total number of multiplications is found as shown in the Table 2.3 below:

**Table 2.3**: Total Number of Multiplication for Binary Method, adapted from(Koç, 1994).

| Case    | Number of Multiplications                     |

|---------|-----------------------------------------------|

| Maximum | (k-1) + (k-1) = 2(k-1)                        |

| Minimum | (k-1) + 0 = (k-1)                             |

| Average | $(k-1) + \frac{1}{2}(k-1) = \frac{3}{2}(k-1)$ |

# 2.3 Modular Multiplication

In the literature, there are various proposals and enhancements for carrying out the modular multiplication operations in RSA. These proposals can be divided into two simple categories with respect to their reduction approach: namely, algorithms reducing from left-to-right and from right-to-left [4]. In fact, for left-to-right approach, several proposals exist [10], [11]. Algorithms including the standard division can be put into this category. Whereas Montgomery multiplication [12] is the only example of right-to-left reduction.

# 2.3.1 Classic modular multiplication

Algorithms including the standard division can be put into this category [4], [5]. Assume that A, B and N are positive numbers; division algorithm states that there exist positive integers Q and T (namely quotient and remainder) such that

$$A \cdot B = Q \cdot N + T \text{ for } 0 \le T < N \tag{2.5}$$

Blakley [10] describes one of the simplest algorithm in this class. As presented in the following paragraphs, the computation of  $AB \mod N$  is achieved by interleaving the shift-add steps of the standard multiplication and the shiftsubtract steps of the usual reduction.

Let  $a_i$  and  $b_i$  represent the bits of the *k*-bit numbers *A* and *B*, respectively. Then, the product, which is a 2k-bit number can be written as [8]:

$$A \cdot B = (\sum_{i=0}^{k-1} a_i 2^i) \cdot B = \sum_{i=0}^{k-1} (a_i \cdot B) 2^i$$

(2.6)

Blakley's algorithm is based on the above formulation of the product; it interleaves the shift-add steps of the standard multiplication and the shift-subtract steps of the usual reduction to make sure that the remainder is less than the modulus N.

In the Algorithm 2, reduction operation is performed between the steps 4 and 9. These steps of the algorithm can also be denoted as  $R := R \mod N$  or :

$$q_i := \lfloor \frac{R}{N} \rfloor$$

Algorithm 2 Blakley's Algorithm.

**Require:** Integers *A*, *B* and *N* **Ensure:**  $P = AB \pmod{N}$ 1: R := 02: for i = k - 1 downto 0 do  $R := 2R + a_i \cdot B$ 3: 4: if  $R \ge N$  then 5: R := R - Nend if 6: 7: if R > N then R := R - N8: 9: end if 10: end for 11: return R

$$R := R - q_i \cdot N$$

Note that, if the last representation is used for the reduction step of the Blakley algorithm, then  $q_i$ s can be accumulated to constitute the Q value, which is the quotient in the standard division algorithm.

Let *A*, *B*, *N* and *Q* are represented with k = 2h bits for some positive integer *h*. They can be partitioned into their least and most significant *h* bits as:

$$A = A_1 \cdot 2^h + A_0 = A_1 \cdot r + A_0$$

$$B = B_1 \cdot 2^h + B_0 = B_1 \cdot r + B_0$$

$$N = N_1 \cdot 2^h + N_0 = N_1 \cdot r + N_0$$

$$Q = Q_1 \cdot 2^h + Q_0 = Q_1 \cdot r + Q_0$$

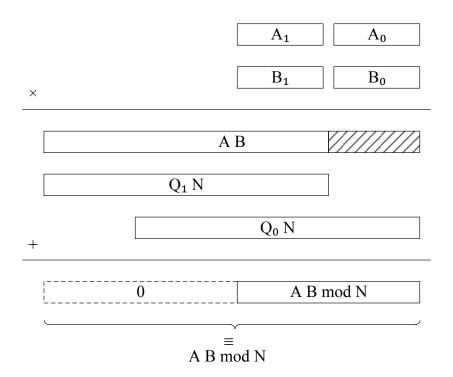

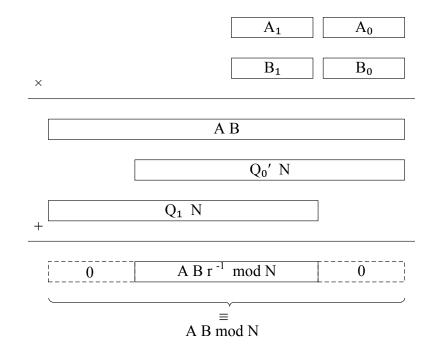

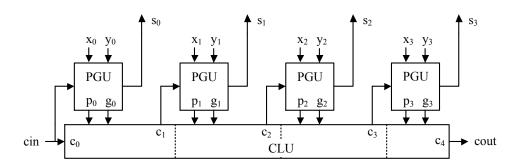

where  $r = 2^{h}$ . Operation of Blakley, namely left-to-right modular multiplication , can be illustrated as shown in the Figure 2.1 [4].

The interpretation of the Figure 2.1 can be made as classic modular multiplication consists of multiplication and reduction stages and in order to compute the result *AB* mod *N*, *QN* which is  $Q_1N2^h + Q_0N$ , is subtracted from the product of *AB*. During the first *h* cycles of the algorithm  $Q_1N2^h$  is subtracted from *AB* and the least significant *h* bits of *AB*, that is filled with dashed pattern in the figure is not manipulated.

Figure 2.1: Left-to-Right Modular Multiplication, adapted from (Saldamlı, 2011).

# 2.3.2 Montgomery Multiplication

Montgomery multiplication, which was proposed by Peter L. Montgomery [12] is the only example of right-to-left reduction and the most preferable method of modular multiplication in comparison with left-to-right methods. It replaces costly compare and reduce step of the classic modular multiplication with simple add and shift operations.

Let *A*, *B*, and *N* are *k*-bit binary numbers. The Montgomery reduction computes  $R = AB \mod N$  without performing a division by the modulus *N*. Assuming that modulus *N* is a *k* bit number, i.e.  $2^{k-1} \le N < 2^k$ , let *R* be  $2^k$  [8]. Montgomery reduction algorithm requires *R* and *N* to be relatively prime, i.e.  $gcd(R,N) = gcd(2^k,N) = 1$ . This is satisfied when *N* is odd.

*N*-residue of an integer A ( $0 \le A < N$ ) with respect to *R* is defined as:

$$\bar{A} = A \cdot R \mod N.$$

Montgomery reduction of A modulo N with respect to R is defined as:

$$A \cdot R^{-1} \mod N.$$

Then, Montgomery reduction of two *N*-residues  $\overline{A}$ , and  $\overline{B}$  is  $\overline{ABR}^{-1} \mod N = ABR \mod N$ . This observation is used for modular exponentiation [9]. For example, in order to compute  $A^5 \mod N$ , firstly *N*-residue of A,  $\overline{A} = A \cdot R \mod N$ , is computed. Then the Montgomery reduction of  $\overline{AA}$ , which is  $X = \overline{A^2R^{-1}} \mod N$ , is computed. The Montgomery reduction of  $X^2$  is  $X^2R^{-1} \mod N = \overline{A^4R^{-3}} \mod N$ . Finally, the Montgomery reduction of  $(X^2R^{-1} \mod N)\overline{A}$  is  $(X^2R^{-1})\overline{AR^{-1}} \mod N = \overline{A^5R^{-4}} \mod N = A^5R \mod N$ . Multiplying this value by  $R^{-1} \mod N$  and reducing modulo *N* gives  $A^5 \mod N$ .

If *N* is represented as a base *b* integer of length *k*, then a typical choice for *R* is  $b^k$  [9]. In order to describe the Montgomery reduction algorithm, an additional quantity, *N'*, is needed, which is an integer with the property of [8]

$$R \cdot R^{-1} - N \cdot N' = 1.$$

(2.7)

The integers  $R^{-1}$  and N' can both be computed by the extended Euclidian algorithm [9]. The Montgomery reduction algorithm which computes  $AR^{-1} \mod N$  is given in the Algorithm 3.

# Algorithm 3 Montgomery Reduction Algorithm.

**Require:** Integers  $A = (a_{2k-1}a_{2k-2}\cdots a_0)_b < NR$ ,  $N = (n_{k-1}n_{k-2}\cdots n_0)_b$  with  $gcd(N,b) = 1, R = b^k, N' = -N^{-1} \mod b.$ **Ensure:**  $AR^{-1} \pmod{N}$ 1: T := A2: for i = 0 to (k - 1) do  $q_i := t_i N' \mod b$ 3: 4:  $T := T + q_i N b^i$ 5: end for 6:  $T := T/b^k$ 7: if T > N then T := T - N8: 9: **end if** 10: return T

Montgomery reduction of the product of two integers, namely Montgomery multiplication is outlined in Algorithm 4. Montgomery multiplication algorithm pieces Montgomery reduction and ordinary multiplication up together. In its reduction steps, firstly, a multiple of the modulus is determined by the least significant digit of the partial sum and partial product. This multiple is then added to the partial sum making the least significant digit 0 which means a trivial right shift is applicable for reduction.

Algorithm 4 Montgomery Multiplication Algorithm.

**Require:** Integers  $X = (x_{k-1}x_{k-2}\cdots x_0)_b$ ,  $Y = (y_{k-1}y_{k-2}\cdots y_0)_b$ ,  $N = (n_{k-1}n_{k-2}\cdots n_0)_b$  with  $0 \le X, Y < N$ ,  $R = b^k$  with gcd(N,b) = 1 and  $N' = -N^{-1} \mod b$ . **Ensure:**  $XYR^{-1} (\mod N)$ 1:  $A := 0(Notation: A := (a_k a_{k-1} \cdots a_0)_b)$ 2: **for** i = 0 **to** (k-1) **do** 3:  $q_i := (a_0 + x_i y_0)N' \mod b$ 4:  $A := (A + x_i Y + q_i N)/b$ 5: **end for** 6: **if**  $A \ge N$  **then** 7: A := A - N8: **end if** 9: **return** A

Let  $q_i$  values are accumulated throughout the Montgomery multiplication and stored to constitute the Q' value. As mentioned in the previous section, let A, B, N and Q' are represented with k = 2h bits for some positive integer h. They can be partitioned into their least and most significant h bits as:

$$A = A_1 \cdot 2^h + A_0 = A_1 \cdot r + A_0$$

$$B = B_1 \cdot 2^h + B_0 = B_1 \cdot r + B_0$$

$$N = N_1 \cdot 2^h + N_0 = N_1 \cdot r + N_0$$

$$Q' = Q'_1 \cdot 2^h + Q'_0 = Q'_1 \cdot r + Q'_0$$

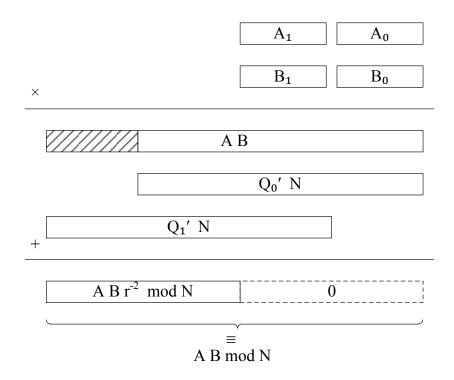

where  $r = 2^{h}$ . Operation of Montgomery multiplication, namely left-to-right modular multiplication, can be illustrated as shown in the Figure 2.2 [4].

As illustrated in the Figure 2.2, Montgomery multiplication combines multiplication and reduction stages. In order to get the result  $ABr^{-2} \mod N$ ,  $Q'N = Q'_0N + Q'_1Nr$  is added to the product of *AB*. Note that, during the first *h* cycles of the algorithm  $Q'_0N$ is added to the product of *AB* and the most significant *h* bits of *AB*, that is shaded in the figure is not modified.

Figure 2.2: Right-to-Left Modular Multiplication, adapted from (Saldamli, 2011).

### 2.3.3 Bipartite Modular Multiplication

Bipartite Modular Multiplication(BMM) method introduced by Kaihara and Takagi in [6] and [7], presents a semi parallel reduction based on an observation that a product could simultaneously be reduced from left and right without a dependency issue. Although, the dependency exists within each direction, BMM algorithm outlines a global method of parallel reduction [4], [5].

In the previous sections left-to-right and right-to-left reduction approaches were explained. In order to boost the speed up, BMM method links these two approaches by setting the R parameter in Montgomery algorithm less than the modulus N. This condition enables the multiplier to be split into two parts, which can be processed separately in parallel [7].

Let  $X = (x_{k-1}x_{k-2}\cdots x_0)_b$  and  $Y = (y_{k-1}y_{k-2}\cdots y_0)_b$  be *k*-digit *N*-residue integers with  $N = (n_{k-1}n_{k-2}\cdots n_0)_b$ ,  $0 \le X, Y < N$ , gcd(N,b) = 1,  $R = b^t$  and 0 < t < k. Now consider the multiplier *B* in Montgomery multiplication of  $ABR^{-1} \mod N$  to be split into two parts  $B_H$  and  $B_L$ , so that  $B = B_H \cdot b^t + B_L$ . Then, Montgomery multiplication of the *N*-residue integers *A* and *B* with respect to  $R = b^t$  can be computed as follows:

$$ABR^{-1} \mod N = A(B_H \cdot R + B_L)R^{-1} \mod N$$

$$= (AB_H RR^{-1} + AB_L R^{-1}) \mod N$$

$$= (AB_H \mod N + AB_L R^{-1} \mod N) \mod N$$

The left term inside the last parentheses,  $AB \mod N$ , can be calculated using the classical modular multiplication algorithm that processes the upper part of the split multiplier  $B_H$ . The second term,  $AB_LR^{-1} \mod N$ , can be calculated using the Montgomery algorithm that processes the lower part of the split multiplier  $B_L$  [7]. Since left-to-right and right-to-left reductions do not have any dependency during the first half of their reduction steps as stated in Blakley and Montgomery sections, they could be combined as seen in Figure 2.3. In fact, the figure gives a sketch of the bipartite reduction [5].

Figure 2.3: Bipartite Modular Multiplication, adapted from (Saldamlı, 2011).

In the Fig. 2.3,  $Q'_0N$  represents the reduction value that is to be added to the lower part of the product *AB* in Montgomery multiplication and  $Q_1N$  corresponds to the reduction value which is subtracted from the upper part of the product in Blakley multiplication. They can be applied in parallel without any dependency issue.

#### 2.4 Partially Interleaved Modular Karatsuba-Ofman Multiplication

Partially Interleaved Modular Karatsuba-Ofman(KO) Multiplication was proposed by Gökay Saldamlı. His algorithm [4] combines KO multiplier and bipartite modular reduction and presents an interleaved processing on the uppermost layer of KO's recursion. As stated in the introduction section, this thesis proposes two hardware implementations which are based on Saldamlı's algorithm and applicable improvements to the algorithm. In the following subsections, preliminaries will be given related to this algorithm.

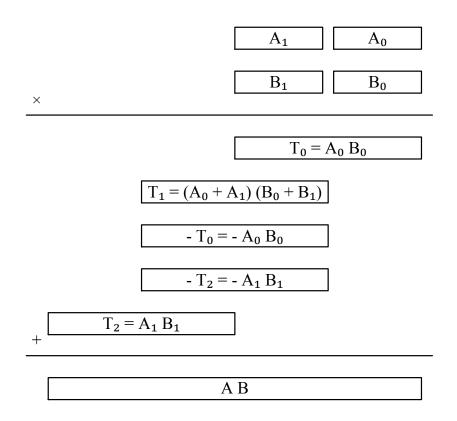

### 2.4.1 Karatsuba-Ofman multiplication

Karatsuba-Ofman algorithm [3] presents a recursive method that requires asymptotically fewer bit operations than the standard multiplication. For a brief explanation, firstly, decompose A and B into two equal-size parts:

$$A := 2^h A_1 + A_0,$$

$B := 2^h B_1 + B_0,$

i.e.,  $A_1$  and  $A_0$  represent the most and least significant *h* bits of *A* respectively, assuming *k* is even and 2h = k [4], [5]. The Karatsuba-Ofman multiplication algorithm breaks the multiplication of *A* and *B* into multiplication of the parts  $A_1$ ,  $A_0$ ,  $B_1$  and  $B_0$  [8]. Since,

$$T := A \cdot B$$

$$:= (2^{h}A_{1} + A_{0})(2^{h}B_{1} + B_{0})$$

$$:= 2^{2h}(A_{1}B_{1}) + 2^{h}(A_{1}B_{0} + A_{0}B_{1}) + A_{0}B_{0}$$

$$:= 2^{2h}T_{2} + 2^{h}T_{1} + T_{0}.$$

standard multiplication of two 2h-bit numbers seems to require the multiplication of four h-bit numbers, Karatsuba-Ofman algorithm is based on the observation that only three multiplications suffice to achieve the same purpose as seen in

$$T_0 := A_0 \cdot B_0$$

$$T_2 := A_1 \cdot B_1$$

$$T_1 := (A_0 + A_1)(B_0 + B_1) - T_0 - T_2$$

$$:= A_0 \cdot B_1 + A_1 \cdot B_0.$$

Karatsuba-Ofman recursive multiplication algorithm(KORMA) is shown below [8]:

function KORMA(A, B)  $T_0 := KORMA(A_0, B_0)$   $T_2 := KORMA(A_1, B_1)$   $U_0 := KORMA(A_0 + A_1, B_0 + B_1)$   $T_1 := U_0 - T_0 - T_2$ return  $(2^{2h}T_2 + 2^hT_1 + T_0)$

Note that, one has the option of stopping at any point during the recursion [4]. For example, one level of recursion can be applied first and then required three multiplications can be computed using the standard nonrecursive multiplication algorithm. Operation of KO multiplication can be seen in the Figure 2.4.

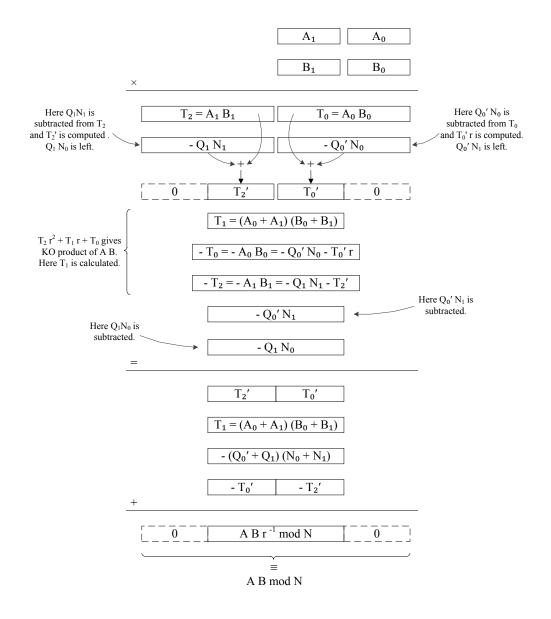

# 2.4.2 Interleaving BMM and KO multiplication

As mentioned in the introduction section, because of the reduction algorithms not allowing parallel reduction due to data dependency issues, these methods can not be interleaved with fast multipliers. But, Saldamlı's algorithm [4] solves this problem to an extend by interleaving bipartite reduction with Karatsuba-Ofman multiplier on the uppermost layer of KO recursion [5].

Q, Q' and N in Bipartite reduction can be rewritten as:

Figure 2.4: Karatsuba-Ofman Multiplication, adapted from (Saldamlı, 2011).

$$N := 2^h N_1 + N_0$$

$$Q := 2^h Q_1 + Q_0$$

$$Q' := 2^h Q'_1 + Q'_0$$

Following partial products are defined as:

$$T'_0 \cdot r = A_0 \cdot B_0 - Q'_0 \cdot N_0 = T_0 - Q'_0 \cdot N_0$$

$T'_2 = A_1 \cdot B_1 - Q_1 \cdot N_1 = T_2 - Q_1 \cdot N_1$

Using these values,  $T'_1$  can be calculated as follows [4];

$$\begin{split} T_1' &= T_1 + T_0' + T_2'r - Q_0'N_1 - Q_1N_0 \\ &= (A_0 + A_1)(B_0 + B_1) - T_0 - T_2 + T_0' + T_2'r - Q_0'N_1 - Q_1N_0 \\ &= (A_0 + A_1)(B_0 + B_1) - (T_0'r + Q_0'N_0) - (T_2' + Q_1N_1) + T_0' + T_2'r - Q_0'N_1 - Q_1N_0 \\ &= (A_0 + A_1)(B_0 + B_1) - (Q_0' + Q_1)(N_0 + N_1) + T_0' - T_0'r - T_2' + T_2'r \,. \end{split}$$

In fact,  $T'_1$  gives the desired modular reduction,  $ABr^{-1} \mod N$ . For a simpler explanation of  $T'_1$  calculation, remember the Fig. 2.3 of Bipartite reduction. In order to compute the result  $ABr^{-1} \mod N$ , Montgomery and Blakley reduction values  $Q'_0N$ ,  $Q_1N$  had to be subtracted respectively from the product AB. As Karatsuba-Ofman calculates the product AB using the following equation:

$$A \cdot B := 2^{2h}T_2 + 2^hT_1 + T_0$$

:=  $2^{2h}A_1B_1 + 2^h((A_0 + A_1)(B_0 + B_1) - T_2 - T_0) + A_0B_0$

Subtracting the Bipartite reduction values  $Q'_0N$  and  $Q_1N$  from KO product *AB* gives the desired modular reduction of  $ABr^{-1} \mod N$ . Partially Interleaved Modular KO multiplication is shown in the Figure 2.5.

As shown in the Fig. 2.5, firstly  $Q'_0N_0$  and  $Q_1N_1$  are subtracted from  $T_0 = A_0B_0$  and  $T_2 = A_1B_1$  respectively. And  $T'_0r$  and  $T'_2$  are computed as results. These operations are simply half-sized reductions of right-to-left(Montgomery) and left-to-right(Classic). Remember that Partially Interleaved Modular KO multiplier combines bipartite reduction with KO multiplication. As bipartite reduction values are  $Q'_0N = Q'_0N_1r + Q'_0N_0$  and  $Q_1N = Q_1N_1r + Q_1N_0$ , half of these reduction values  $\operatorname{are}(Q'_0N_0 \text{ and } Q_1N_1)$  used up here and  $Q'_0N_1r$  and  $Q_1N_0$  are left.  $T_1$  and  $-Q'_0N_1$  and  $-Q_1N_0$  are summed up with the calculated  $T_2$  and  $T'_0$  values to give the modular reduction,  $ABr^{-1} \mod N$ . These operations are rearranged in the second half of the figure. At it can be seen, the desired modular reduction can be computed as:  $ABr^{-1} \mod N = (T'_2r\& T'_0) + (A_0 + A_1)(B_0 + B_1) - (Q'_0 + Q_1)(N_0 + N_1) - (T'_0r\& T'_2)$ , where & is the concatenation operation.

Figure 2.5: Partially Interleaved Modular Karatsuba-Ofman Multiplication, adapted from (Saldamli, 2011).

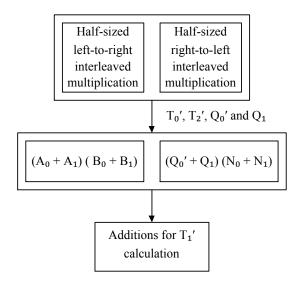

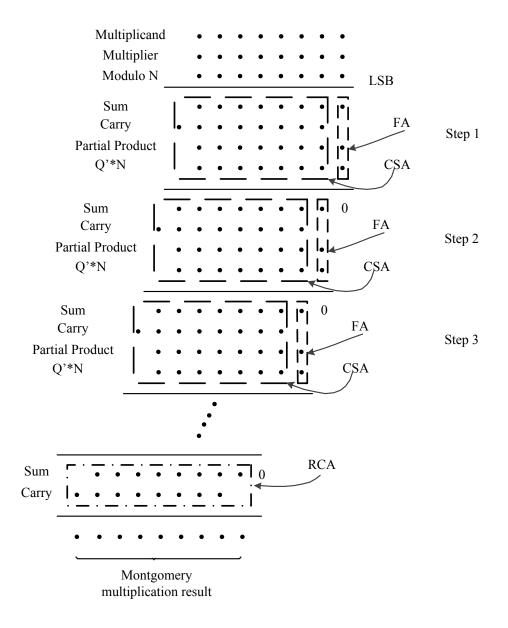

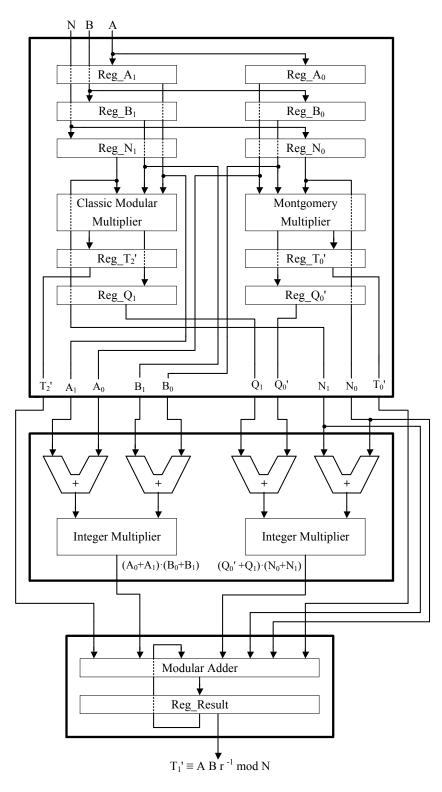

Block diagram of the method can be seen in Figure 2.6. As shown in the figure, firstly using the half-sized left-to-right interleaved multiplication and right-to-left interleaved multiplication  $T'_2$ ,  $T'_0$ ,  $Q_1$  and  $Q'_0$  are calculated. Then, standard multiplication operations  $(A_0+A_1)(B_0+B_1)$  and  $(Q'_0+Q_1)(N_0+N_1)$  are done. And finally, additions are made in order to get the modular multiplication result.

Figure 2.6: Block Diagram of the Method, adapted from (Saldamli, 2011).

Neglecting the addition operations, implementation of this method can be done by using Classic modular multiplication for left-to-right reduction, Montgomery multiplication for right-to-left reduction and integer multiplication for the multiplication operations of  $(A_0 + A_1)(B_0 + B_1)$  and  $(Q'_0 + Q_1)(N_0 + N_1)$ . In the next section, preliminaries about the multiplication algorithms will be presented.

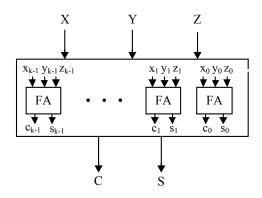

# 2.5 Integer Multiplication

Various multiplication algorithms exist in the literature in order to perform fast multiplication. Examples of such methods are Karatsuba-Ofman [3], Schönhage-Strassen [13] and Fürer [14]. Among these, Karatsuba-Ofman multiplication was explained in Section 2.4.1. In order to use the similar hardware structures and balance the delays of hardware modules, basic shift-and-accumulate method was accomodated in this work. Shift-and-accumulate approach is explained in the following subsection.

# 2.5.1 Shift and accumulate method

Let multiplicand *A*, multiplier *B* be *k*-bit, and product *P* be 2*k*-bit numbers as follows:

$$A := (a_{k-1}a_{k-2}\cdots a_0)$$

$$B := (b_{k-1}b_{k-2}\cdots b_0)$$

$$P := AB = (p_{2k-1}p_{2k-2}\cdots p_0)$$

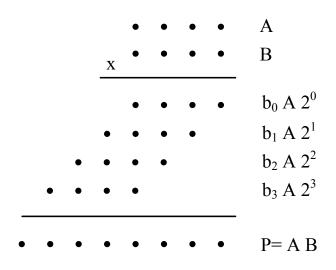

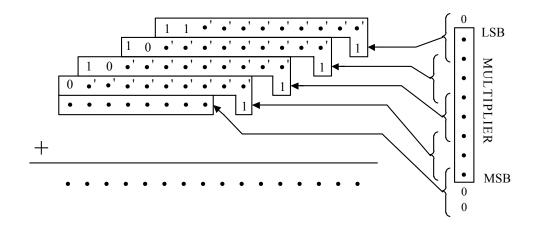

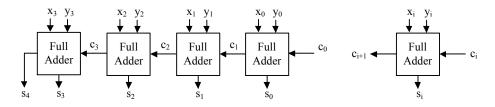

Figure 2.7 shows the multiplication of two 4-bit unsigned binary numbers in dot notation [15]. Multiplicand A and multiplier B are shown at the top. Each of the following four rows of dots corresponds to the product of A and a single bit of B, where each dot represents the product of two bits. Since numbers are in binary form, each dot can either be 0 or 1 and each row can either be A or 0. Thus the binary multiplication problem reduces to adding a set of numbers, each of which is 0 or a shifted version of the multiplicand A.

Figure 2.7: Shift and Accumulate Method, adapted from (Parhami, 2000).

Sequential or bit-at-a-time multiplication can be done in two directions, either from left-to-right, or right-to-left. In case of left-to-right, a cumulative partial product, which

is initialized to 0 is shifted left at each step and proper  $b_iA$  is added to it. Left-to-right operation can be shown as:

$$P = ((((P + b_3A) \cdot 2 + b_2A) \cdot 2 + b_1A) \cdot 2 + b_0A), (P = 0 \text{ initially})$$

In right-to-left operation, at each step, a cumulative partial product, again initialized to 0 is summed up with the proper  $b_iA$  and least significant bit of it is stored in another variable, namely right part of the product. This operation goes on until the end of the multiplication. At the end, right part of the product and cumulative partial product is concatenated to get the product.

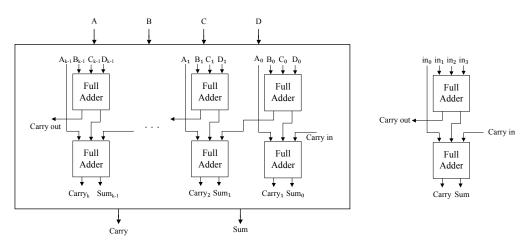

Here, number of partial products is equal to the bit length of the multiplier. As multiplier is k-bit long, product P is computed via addition of k generated partial product one by one. This operation can be accelerated by grouping the bits of the multiplier into pairs, triples or quadruples and so on. The way of grouping the multiplier bits widens the partial product set and bring advantages and disadvantages. A very famous encoding method, namely Booth Encoding which groups the multiplier bits effectively will be presented in the following section.

## 2.6 Booth Encoding

A generator that creates a smaller number of partial products will allow the partial product summation to be faster and use less hardware [16]. A basic way of reducing the number of partial products could be grouping the multiplier bits into pairs. In this way, partial products would be selected from the set of  $\{0, A, 2A, 3A\}$ , where *A* is the multiplicand. This reduces the number of partial products by half but brings a problem: generation of 3*A*. 0, *A*, 2*A* are very easy to generate. But, 3*A* generation needs either 2A + A precomputed and stored, or on the fly calculation. Instead of this, a method known as Modified Booth's Algorithm [17], [16] is used, which reduces the number of partial products by about a factor of two and does not require 3*A* neither to be precomputed, nor on the fly computation. The idea of Booth's algorithm is doing a little more work when decoding the multiplier such that the required multiples of multiplicand come from the set of  $\{0, A, 2A, 4A + -A\}$ . All of the elements of this set can be generated by simple shift operations.

| $b_{i+1}$ | $b_i$ | $b_{i-1}$ | Ι  | $b_{i+1}$ | $b_i$ | $b_{i-1}$ | Ι   |

|-----------|-------|-----------|----|-----------|-------|-----------|-----|

| 0         | 0     | 0         | 0  | 1         | 0     | 0         | -2A |

| 0         | 0     | 1         | A  | 1         | 0     | 1         | -A  |

| 0         | 1     | 0         | A  | 1         | 1     | 0         | -A  |

| 0         | 1     | 1         | 2A | 1         | 1     | 1         | 0   |

Table 2.4: Modified Booth Encoding Scheme.

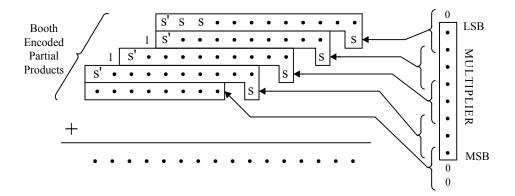

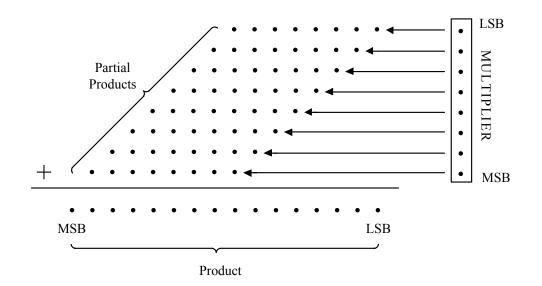

3*A* either by 4A - A. Depending on the adjacent multiplier bits either 4*A* is pushed into the next most significant group(becoming *A* because of the different arithmetic weight of the group) or -A is pushed into the previous least significant group, becoming -4A [16]. Figure 2.8 shows the dot diagram of 8*x*8 multiplication using the 2 bit version of the algorithm.

Figure 2.8: 8x8 Modified Booth Multiplication, adapted from (Bewick, 1994).

As shown in the Fig. 2.8, multiplier is partitioned into overlapping groups of 3 bits. Each group starting from LSB is decoded to select a single partial product(*I*) according to the selection Table 2.4. Corresponding multiple of the multiplicand is determined according to the addition of  $(-2 \cdot b_{i+1} + b_i + b_{i-1})$ , where  $b_{-1}$ ,  $b_k$  and  $b_{k+1}$  bits are padded with 0. Booth encoded partial products are showns as horizontal row of dots in the figure. Each partial product is shifted 2 bit positions with respect to its neighbours. Number of partial products are reduced to 5, instead of 8. In general, the number of partial products is  $\lfloor \frac{k+2}{2} \rfloor$ , where *k* is the length of the multiplier [16].

All partial products shown in the Table 2.4 can be generated by simple operations like shift and complement. Negative partial products can be easily generated by bit-by-bit complementing the corresponding positive product and adding 1 to the least significant position of the partial product, which is shown as *s* at the LSB position of partial products.

In the Fig. 2.8, it can be seen that some partial products' MSB positions are padded with s, s' or 1. This padding is called as *sign extension*. As Booth encoding scheme generates both positive and negative multiples of the multiplicand, it is difficult to control the sign and guarantee the product to have the desired sign. Incorporating sign extension solves this problem by padding s, s' and 1 to corresponding partial products' MSB positions. The logic of sign extension is providing a general form, which works in any combination of positive and negative multiples.

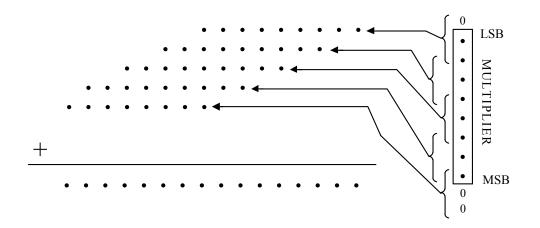

The partial products for the 8x8 multiplication example, assuming that all partial products are positive, are shown in the Figure 2.9. Each partial product, except for the bottom one, is 9 bits long, since numbers as large as 2 times the multiplicand must be dealt with [16]. The bottom partial product is 8 bits long, because multiplier is padded with two zeroes in order to guarantee the positive result.

Figure 2.9: 8x8 Booth Multiplication with Positive Partial Products, adapted from (Bewick, 1994).

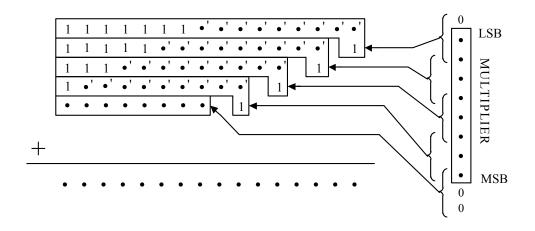

Figure 2.10 shows the partial products if they all happen to be generated negative. Using 2's complement, every bit of the negated partial products is complemented, including any leading zeroes and 1 is added at the LSB. The bottom partial product is never negated, because zero padding assures that it is always positive [16]. Triangle of 1's on the left handside can be summed to produce the Figure 2.11, which is exactly equivalent to the situation shown in Fig. 2.10.

Figure 2.10: 8x8 Booth Multiplication with Negative Partial Products, adapted from (Bewick, 1994).

Figure 2.11: Negative Partial Products with Summed Sign Extension, adapted from (Bewick, 1994).

Now, suppose that a particular partial product turns out not be negative. The leading string of 1's in that particular partial product can be converted back to a leading of zeroes, by adding a single 1 at the least significant bit of the string. In addition to this, a 1 is added into the least significant bit of a partial product, only if it is negative. Figure 2.8 illustrates this configuration. The s' bits represent the 1's that are needed to clear the sign extension bits for positive partial products, and the s bits represent the 1's that are needed to 1's that are added at the least significant bit of each partial product if it is negative [16].

## 3. IMPLEMENTATION ENVIRONMENT

In this section, implementation environment will be described. Implementation environment includes device technologies(FPGA and ASIC), and design & verification tools which were used throughout the hardware implementations.

Two hardware designs are proposed in this thesis. The first one is FPGA implementation of Partially Interleaved Modular KO Multiplier [5]. The second one is ASIC implementation of high radix and optimized version of the first design and incorporation of it in RSA cryptosystem. VHDL was used as a hardware description language. Before coding of the design elements in VHDL, Maple library of building blocks and primitives, which emulate the hardware components, were prepared. Then, same hardware designs were implemented in Maple using these building blocks. Maple implementation of the design is tested and verified. In the next step, design was coded in VHDL. According to the implementation technology, Xilinx(for FPGA implementation), or Synopsys tools(for ASIC implementation) were used for synthesis, mapping, placing and routing operations. Behavioral and gate level simulations were performed using Modelsim and VCS simulators. Verification of correct operation was done according to the results computed in Maple and results produced in simulations. In the following subsections these device technologies and design tools will be briefly described.

### **3.1 Device Technologies**