### Universidade de Santiago de Compostela

Departamento de Electrónica e Computación

### PhD THESIS

# MODELLING AND CHARACTERIZATION OF SMALL PHOTOSENSORS IN ADVANCED CMOS TECHNOLOGIES

Author:

Beatriz Blanco Filgueira

PhD supervisor:

Paula López Martínez

Santiago de Compostela, July 2012

**Dr. Paula López Martínez**, associate professor at the Department of Electronics and Computer Science of the University of Santiago de Compostela

#### HEREBY CERTIFIES:

That the dissertation entitled **Modelling and characterization of small photosensors in advanced CMOS technologies** has been developed by **Mrs. Beatriz Blanco Filgueira** under my direction at the Department of Electronics and Computer Science of the University of Santiago de Compostela in fulfillment of the requirements for the Degree of Doctor of Philosophy.

Santiago de Compostela, July 2012

Dra. Paula López Martínez, Profesora Contratada Doctora del área de Electrónica de la Universidad de Santiago de Compostela

#### HACE CONSTAR:

Que la memoria titulada **Modelling and characterization of small photosensors in advanced CMOS technologies** ha sido realizada por **Dña. Beatriz Blanco Filgueira** bajo mi dirección en el Departamento de Electrónica y Computación de la Universidad de Santiago de Compostela, y constituye la Tesis que presenta para optar al título de Doctor por la Universidad de Santiago de Compostela.

Santiago de Compostela, julio de 2012

Paula López Martínez

Directora de la tesis

Beatriz Blanco Filgueira Autora de la tesis

A Juan, Guille, Amparo e Carlos, o meu fogar.

### **Acknowledgements**

Research is a fascinating experience. Despite moments of frustration, it is a very rewarding job. But it becomes really interesting when you have the opportunity to share knowledge with other people. Now is the time to show my gratitude to all those who have left their mark on this work.

I would like to thank my supervisor Dr. Paula López Martínez for her constant guidance and advice during the development of this work. I admire her professionalism, determination and willpower to face new challenges. I have not known the limit of her optimism yet (if it exists). It has been a pleasure to work alongside her. Also very enriching were the many discussions and meetings with Dr. Víctor Brea Sánchez, associate professor at the Department of Electronics and Computer Science of the University of Santiago de Compostela. The mature experience of Dr. Diego Cabello Ferrer, professor at the Department of Electronics and Computer Science of the University of Santiago de Compostela, has facilitated this journey as well. I am very grateful to Dipl.-Ing. Johann Hauer (Hans) and the members of his group at the Fraunhofer Institute for Integrated Circuits IIS in Erlangen (Germany). Their support and experience were crucial to carry out an important part of this work. I would also like to thanks Hans for his wonderful hospitality. Thanks to Dr. Jens Döge at the Fraunhofer Institute for Integrated Circuits IIS, Design Automation Division EAS for his support and effort during some intensive and enriching working days in Dresden, and for showing me such beautiful city. This work was also done in collaboration with Dr. Juan B. Roldán Aranda, associate professor at the Department of Electronics and Computer Technology of the University of Granada. I am very grateful for his support and advice. It is admirable the willingness of Dr. Vicente Moreno de las Cuevas, professor at the Optics Area of the Department of Applied Physics of the University of Santiago de Compostela. His help and support played a decisive role during the last stage of this work. Thanks to Dr. Alberto Cabada Fernández, professor at

the Department of Mathematical Analysis of the University of Santiago de Compostela, for his guidance.

The work related to this PhD thesis was partially supported by the Spanish Ministry of Science and Education under Project TEC 2009-12686, Xunta de Galicia under project 10PXIB206037PR and Programa de Recursos Humanos do Plan Galego de Investigación, Desenvolvemento e Innovación Tecnolóxica de Galicia (INCITE 2006-2010) under a *Lucas Labrada* contract, and the University of Santiago de Compostela, the Computer Vision Group and Centro Singular de Investigación en Tecnoloxías da Información (CITIUS) of the same university under a predoctoral contract. Additional funds for research activities were provided by the University of Santiago de Compostela, the Fraunhofer Institute for Integrated Circuits IIS and the German Academic Exchange Service (DAAD).

Máis alá do ámbito profesional, as nosas vidas están cheas de persoas que dunha maneira ou doutra inflúen positivamente en todo o que facemos. Persoas coas que compartimos risas, que celebran os nosos logros, que nos levantan cada vez que caemos, coas que podemos contar sempre. Máis alá de agradecerlle dende aquí todo o que levan aportado á miña vida, espero agradecerllo cos meus actos, día a día, e estar á altura do que se merecen. Vós sodes o verdadeiramente importante.

Santiago de Compostela, July 2012

## **Contents**

| List of | Figures  |                                                                       | xiii |

|---------|----------|-----------------------------------------------------------------------|------|

| List of | Tables   |                                                                       | xvii |

| Resum   | en       |                                                                       | 1    |

| Introd  | uction   |                                                                       | 11   |

| Chapte  | er 1 Sol | lid-state image sensors                                               | 17   |

| 1.1     | Evoluti  | ion                                                                   | 17   |

| 1.2     | Basics   |                                                                       | 21   |

|         | 1.2.1    | Photoconversion                                                       | 21   |

|         | 1.2.2    | Charge collection efficiency                                          | 22   |

|         | 1.2.3    | Quantum Efficiency (QE), Responsivity (R) and Sensitivity (S)         | 23   |

|         | 1.2.4    | Full-well capacity, capacitance $(C_{PD})$ and Conversion Gain $(CG)$ | 25   |

|         | 1.2.5    | Signal-to-Noise Ratio (SNR), Dynamic Range (DR) and crosstalk         |      |

|         |          | (CTK)                                                                 | 27   |

|         | 1.2.6    | Modulation Transfer Function (MTF)                                    | 28   |

|         | 1.2.7    | Colour Filter Array (CFA)                                             | 28   |

|         | 1.2.8    | On-chip Microlens Array (OMA)                                         | 29   |

|         | 1.2.9    | Fill Factor (FF)                                                      | 30   |

|         | 1.2.10   | Reflection $(R_c)$ and Transmission $(T_c)$ coefficients              | 31   |

|         | 1.2.11   | Noise                                                                 | 31   |

|         |          | Spatial Noise or Fixed-Pattern Noise (FPN)                            | 31   |

|         |          | Temporal Noise                                                        | 32   |

x Contents

|                                     |                                                                         | Smear and Blooming                                                                                                                                                                                                                                                                        | 33                                                              |

|-------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

|                                     |                                                                         | Image lag                                                                                                                                                                                                                                                                                 | 33                                                              |

| 1.3                                 | Techno                                                                  | logies                                                                                                                                                                                                                                                                                    | 34                                                              |

|                                     | 1.3.1                                                                   | CCD image sensors                                                                                                                                                                                                                                                                         | 34                                                              |

|                                     |                                                                         | Implementation and operation                                                                                                                                                                                                                                                              | 35                                                              |

|                                     |                                                                         | Frame Transfer CCD (FTCCD)                                                                                                                                                                                                                                                                | 37                                                              |

|                                     |                                                                         | Interline Transfer CCD (ITCCD)                                                                                                                                                                                                                                                            | 37                                                              |

|                                     |                                                                         | Field-Interline-Transfer CCD (FITCCD)                                                                                                                                                                                                                                                     | 38                                                              |

|                                     | 1.3.2                                                                   | CMOS image sensors                                                                                                                                                                                                                                                                        | 39                                                              |

|                                     |                                                                         | Implementation and operation                                                                                                                                                                                                                                                              | 40                                                              |

|                                     |                                                                         | Passive Pixel Sensor (PPS)                                                                                                                                                                                                                                                                | 41                                                              |

|                                     |                                                                         | Active Pixel Sensor (APS)                                                                                                                                                                                                                                                                 | 41                                                              |

|                                     | 1.3.3                                                                   | CMOS vs. CCD                                                                                                                                                                                                                                                                              | 47                                                              |

| 1.4                                 | Outline                                                                 | of the thesis                                                                                                                                                                                                                                                                             | 49                                                              |

|                                     | 1.4.1                                                                   | CHIP 1 and CHIP 2: 3T-APS in 180 nm and 90 nm                                                                                                                                                                                                                                             | 50                                                              |

|                                     | 1.4.2                                                                   | CHIP 3 and CHIP 4: $p-n^+$ junctions in 180 nm and 65 nm $\ldots \ldots$                                                                                                                                                                                                                  | 55                                                              |

| Chapte                              | r 2 Pho                                                                 | otodiode semianalytical model                                                                                                                                                                                                                                                             | 59                                                              |

| 2.1                                 | Test str                                                                | uctures and experimental set-up                                                                                                                                                                                                                                                           | 61                                                              |

|                                     |                                                                         |                                                                                                                                                                                                                                                                                           |                                                                 |

| 2.2                                 | Semian                                                                  | alytical model                                                                                                                                                                                                                                                                            | 64                                                              |

| 2.2                                 | Semian 2.2.1                                                            | alytical model                                                                                                                                                                                                                                                                            | 64<br>65                                                        |

| 2.2                                 |                                                                         |                                                                                                                                                                                                                                                                                           |                                                                 |

| 2.2                                 | 2.2.1                                                                   | Conversion gain                                                                                                                                                                                                                                                                           | 65                                                              |

| 2.2                                 | 2.2.1<br>2.2.2<br>2.2.3                                                 | Conversion gain                                                                                                                                                                                                                                                                           | 65<br>66                                                        |

|                                     | 2.2.1<br>2.2.2<br>2.2.3                                                 | Conversion gain                                                                                                                                                                                                                                                                           | 65<br>66<br>67                                                  |

|                                     | 2.2.1<br>2.2.2<br>2.2.3<br>Results                                      | Conversion gain                                                                                                                                                                                                                                                                           | 65<br>66<br>67<br>71                                            |

|                                     | 2.2.1<br>2.2.2<br>2.2.3<br>Results<br>2.3.1<br>2.3.2                    | Conversion gain                                                                                                                                                                                                                                                                           | 65<br>66<br>67<br>71<br>71                                      |

| 2.3                                 | 2.2.1<br>2.2.2<br>2.2.3<br>Results<br>2.3.1<br>2.3.2<br>Conclus         | Conversion gain                                                                                                                                                                                                                                                                           | 65<br>66<br>67<br>71<br>71<br>76                                |

| 2.3                                 | 2.2.1<br>2.2.2<br>2.2.3<br>Results<br>2.3.1<br>2.3.2<br>Conclust        | Conversion gain  Responsivity: active area contribution, $R_A$ Responsivity: peripheral contribution, $R_P$ p-n <sup>+</sup> photodiodes  p-N <sub>well</sub> photodiodes  sions                                                                                                          | 65<br>66<br>67<br>71<br>71<br>76<br>77                          |

| 2.3<br>2.4<br><b>Chapte</b> i       | 2.2.1 2.2.2 2.2.3 Results 2.3.1 2.3.2 Conclust r 3 Pho                  | Conversion gain  Responsivity: active area contribution, $R_A$ .  Responsivity: peripheral contribution, $R_P$ .  p-n <sup>+</sup> photodiodes  p-N <sub>well</sub> photodiodes  sions  cotodiode analytical model: point source illumination                                             | 65<br>66<br>67<br>71<br>71<br>76<br>77                          |

| 2.3<br>2.4<br><b>Chapter</b><br>3.1 | 2.2.1 2.2.2 2.2.3 Results 2.3.1 2.3.2 Conclust  Test stru Analyti       | Conversion gain  Responsivity: active area contribution, $R_A$ Responsivity: peripheral contribution, $R_P$ p-n+ photodiodes  p-N <sub>well</sub> photodiodes  sions  cotodiode analytical model: point source illumination  uctures and experimental set-up                              | 65<br>66<br>67<br>71<br>71<br>76<br>77<br><b>79</b><br>81       |

| 2.3<br>2.4<br><b>Chapter</b><br>3.1 | 2.2.1 2.2.2 2.2.3 Results 2.3.1 2.3.2 Conclust  Test strr Analyti 3.2.1 | Conversion gain  Responsivity: active area contribution, $R_A$ .  Responsivity: peripheral contribution, $R_P$ .  p-n <sup>+</sup> photodiodes  p-N <sub>well</sub> photodiodes  sions  ctodiode analytical model: point source illumination  uctures and experimental set-up  cal model. | 65<br>66<br>67<br>71<br>71<br>76<br>77<br><b>79</b><br>81<br>84 |

Contents xi

|          | 3.2.4     | Surroundings                                        | 88  |

|----------|-----------|-----------------------------------------------------|-----|

| 3.3      | Results   |                                                     | 89  |

|          | 3.3.1     | Experimental validation                             | 89  |

|          | 3.3.2     | Simulation results                                  | 93  |

| 3.4      | Conclu    | sions                                               | 95  |

| Chapte   | r4 Pho    | otodiode analytical model: uniform illumination     | 97  |

| 4.1      | Test str  | ructures and experimental set-up                    | 101 |

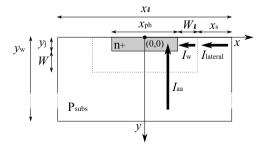

| 4.2      | Analyti   | ical model of the lateral photocurrent              | 104 |

|          | 4.2.1     | Problem formulation                                 | 104 |

|          | 4.2.2     | Mathematical solution to lateral collection         | 105 |

| 4.3      | Model     | validation                                          | 111 |

|          | 4.3.1     | Simulation results                                  | 111 |

|          | 4.3.2     | Experimental validation                             | 117 |

| 4.4      | Conclu    | sions                                               | 122 |

| Chapte   | r 5 HD    | L implementation and circuit simulation             | 123 |

| 5.1      | Verilog   | g-AMS implementation                                | 125 |

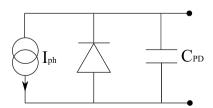

|          | 5.1.1     | $p\text{-}n^+$ junction photodiode                  | 125 |

|          | 5.1.2     | Gate-Enclosed Layout Transistors (ELTs)             | 127 |

| 5.2      | Integra   | tion of Verilog-AMS language into Cadence framework | 129 |

| 5.3      | Results   |                                                     | 131 |

|          | 5.3.1     | $p\text{-}n^+$ junction photodiode                  | 131 |

|          | 5.3.2     | Gate-Enclosed Layout Transistors (ELTs)             | 134 |

| 5.4      | Conclu    | sions                                               | 136 |

| Conclus  | sions and | d future work                                       | 137 |

| Append   | ix A N    | omenclature and symbols                             | 141 |

| Append   | ix B M    | lodels parameters                                   | 145 |

| Append   | ix C V    | erilog-AMS codes                                    | 153 |

| Bibliogi | raphy     |                                                     | 161 |

# **List of Figures**

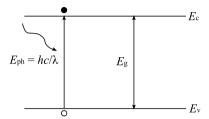

| Figure 1.1  | Photogeneration                                                          | 21 |

|-------------|--------------------------------------------------------------------------|----|

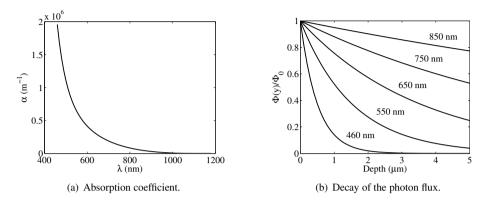

| Figure 1.2  | Absorption of light in silicon at room temperature                       | 23 |

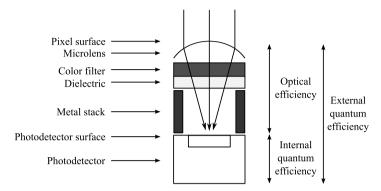

| Figure 1.3  | Cross-section scheme of a pixel                                          | 24 |

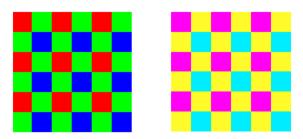

| Figure 1.4  | Bayer and CMY complementary colour pattern filters                       | 28 |

| Figure 1.5  | Microlenses                                                              | 30 |

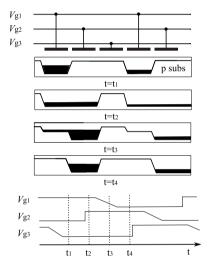

| Figure 1.6  | CCD stage with three polysilicon layers                                  | 36 |

| Figure 1.7  | Charge transfer in CCD: potential wells and timing diagram               | 36 |

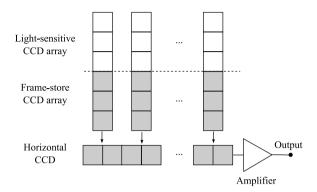

| Figure 1.8  | Frame Transfer CCD (FTCCD)                                               | 38 |

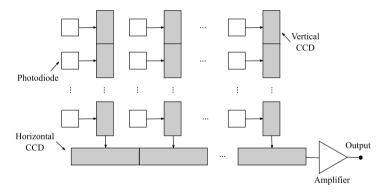

| Figure 1.9  | Interline Transfer CCD (ITCCD)                                           | 38 |

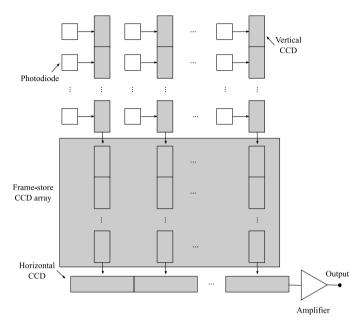

| Figure 1.10 | Field-Interline-Transfer CCD (FITCCD)                                    | 39 |

| Figure 1.11 | Overall CMOS image sensor architecture                                   | 40 |

| Figure 1.12 | Passive Pixel Sensor (PPS) architecture                                  | 42 |

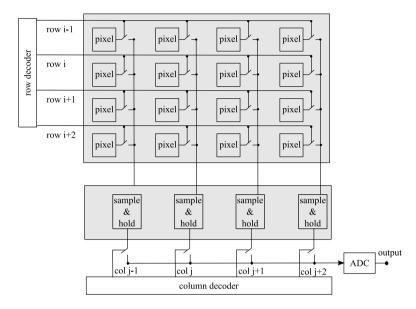

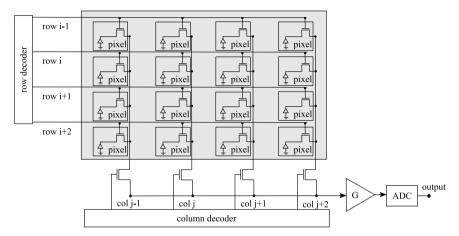

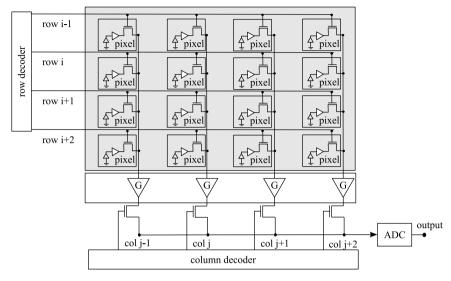

| Figure 1.13 | Active Pixel Sensor (APS) architecture.                                  | 43 |

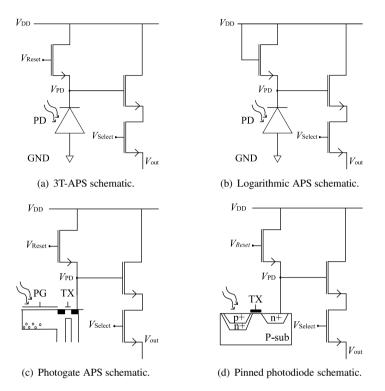

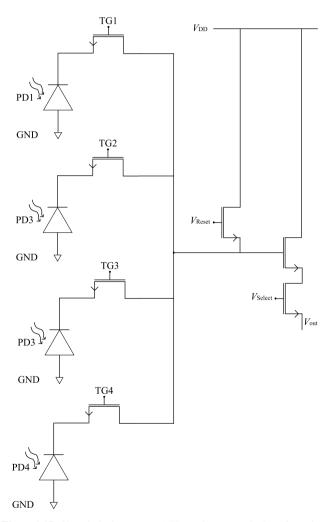

| Figure 1.14 | Different Active Pixel Sensor (APS) structures                           | 44 |

| Figure 1.15 | Shared-pixel structure: 1.75 transistors per pixel configuration         | 48 |

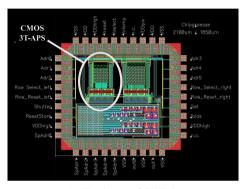

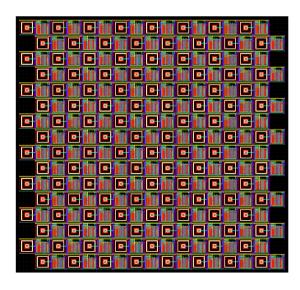

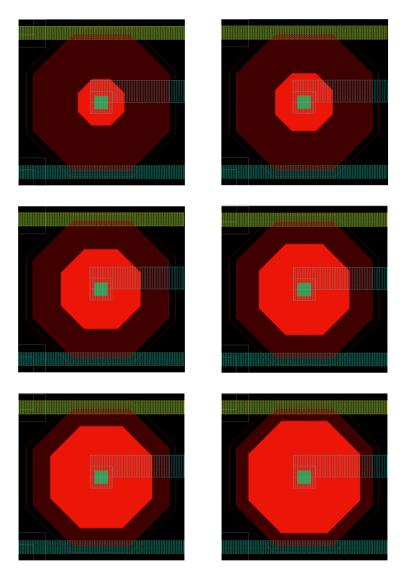

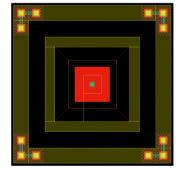

| Figure 1.16 | Top layout of the test chips in UMC 180 nm CIS (left) and UMC 90 nm      |    |

|             | (right) standard technologies                                            | 51 |

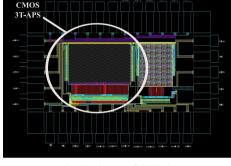

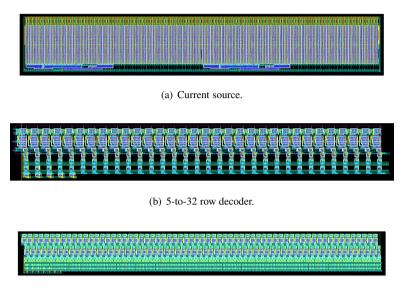

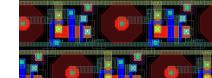

| Figure 1.17 | Layout of the peripheral electronics surrounding the arrays of pixels in |    |

|             | CHIP 2                                                                   | 52 |

| Figure 1.18 | Layout of a subarray of 8x16 identical pixels in CHIP 2                  | 52 |

| Figure 1.19 | Chessboard configuration of the arrays of pixels                         | 53 |

| Figure 1.20 | Layout of a pixel in UMC 180 nm CIS (left) and UMC 90 nm (right)         |    |

|             | standard technologies                                                    | 53 |

xiv List of Figures

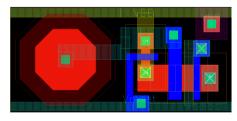

| Figure 1.21 | Layout of p-n <sup>+</sup> photodiodes with different diffusion areas in UMC 180 nm CIS technology | 54  |

|-------------|----------------------------------------------------------------------------------------------------|-----|

| Figure 1.22 | Layout of p-N <sub>well</sub> photodiodes with the same diffusion area and different               |     |

| E: 1.00     | size of the well in UMC 90 nm standard technology                                                  | 55  |

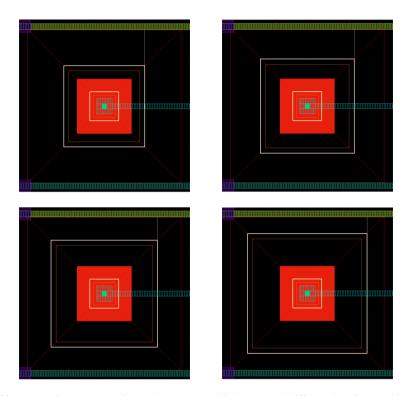

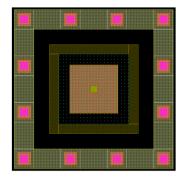

| Figure 1.23 | Top layout of the test chips in AMS 180 nm (left) and UMC 65 nm (right)                            | ~ ~ |

| F: 104      | standard technologies                                                                              | 56  |

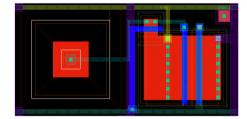

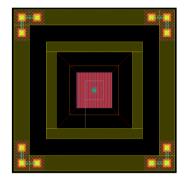

| Figure 1.24 | Photodiode layout including a substrate ground ring in AMS 180 nm and                              |     |

|             | UMC 65 nm standard technologies                                                                    | 56  |

| Figure 1.25 | Photodiode layout including an optical shield over the diffusion in AMS                            |     |

|             | 180 nm and UMC 65 nm standard technologies                                                         | 57  |

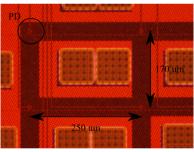

| Figure 1.26 | Microphotographs of the isolated square $p-n^+$ photodiodes                                        | 57  |

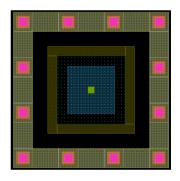

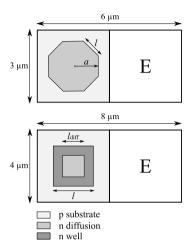

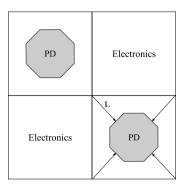

| Figure 2.1  | Pixel schemes with octagonal and square photodiodes                                                | 62  |

| Figure 2.2  | Output voltage curve of a pixel versus time                                                        | 64  |

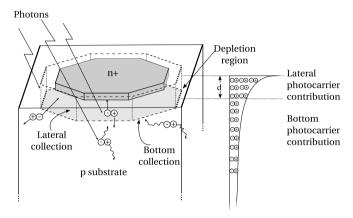

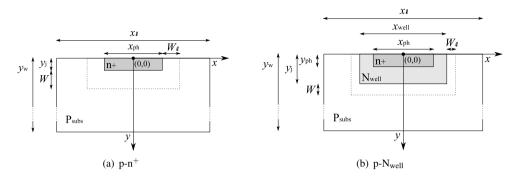

| Figure 2.3  | Diagram of the octagonal p-n $^+$ junction photodiode                                              | 68  |

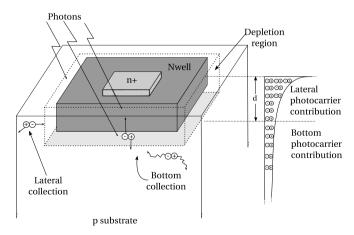

| Figure 2.4  | Diagram of the square p-N $_{well}$ junction photodiode                                            | 68  |

| Figure 2.5  | Different lateral contribution of the depletion region side-walls                                  | 69  |

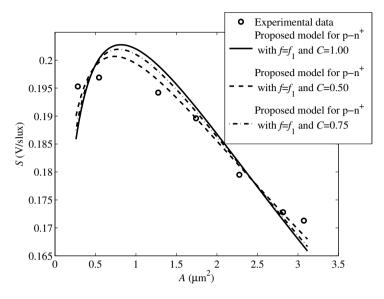

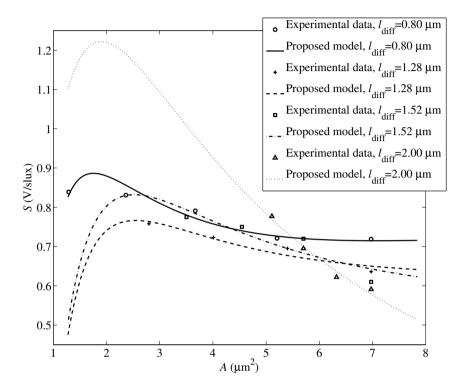

| Figure 2.6  | Sensitivity of the pixel with respect to the size of the p-n <sup>+</sup> photodiode in            |     |

|             | UMC 180 nm CIS technology. Experimental data (markers) are compared                                |     |

|             | to the proposed model in Equation (2.20) (line) using $f = f_1$                                    | 72  |

| Figure 2.7  | Sensitivity of the pixel with respect to the size of the p-n <sup>+</sup> photodiode in            |     |

|             | UMC 180 nm CIS technology. Experimental data (markers) are compared                                |     |

|             | to the proposed model in Equation (2.20) (line) using $f = f_2$                                    | 72  |

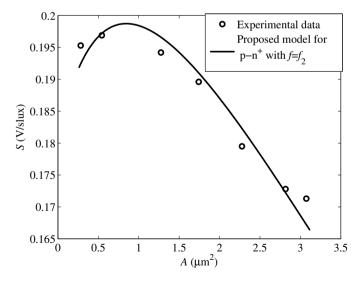

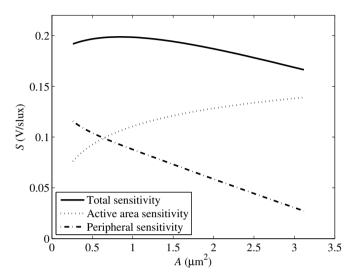

| Figure 2.8  | Sensitivity of the pixel with respect to the size of the p-n <sup>+</sup> photodiode               |     |

|             | in UMC 180 nm CIS technology given by the proposed model in                                        |     |

|             | Equation (2.20) using $f = f_2$ . Active area and peripheral contributions                         |     |

|             | are given separately                                                                               | 73  |

| Figure 2.9  | Comparison of the measured sensitivity of the pixels with respect to the                           |     |

| C           | size of the p-N <sub>well</sub> photodiode in UMC 90 nm standard technology with                   |     |

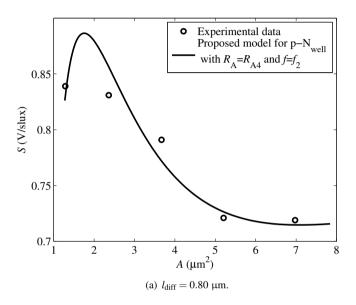

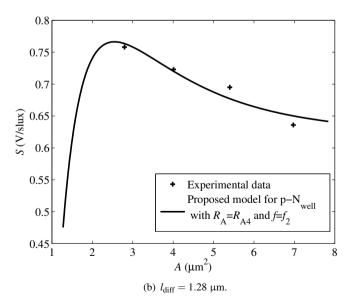

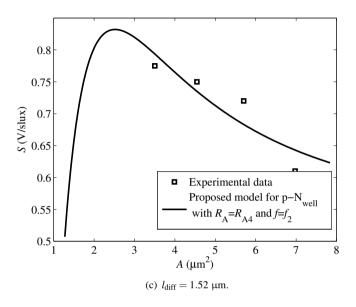

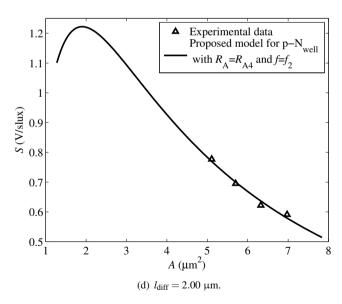

|             | the proposed model in Equation (2.21) using $R_A = R_{A4}$ and $f = f_2$                           | 75  |

| Figure 2.10 | Comparison of the measured sensitivity of the pixels with respect to the                           |     |

| 5           | size of the p-N <sub>well</sub> photodiode in UMC 90 nm standard technology with                   |     |

|             | the proposed model in Equation (2.21) using $R_A = R_{A4}$ and $f = f_2$ for                       |     |

|             | different sizes of the diffusion area                                                              | 76  |

|             | different bizes of the diffusion area                                                              | , 0 |

List of Figures xv

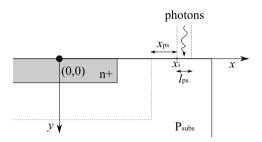

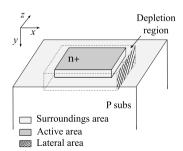

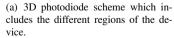

| Figure 3.1  | Photodiode structures                                                                                     | 81  |

|-------------|-----------------------------------------------------------------------------------------------------------|-----|

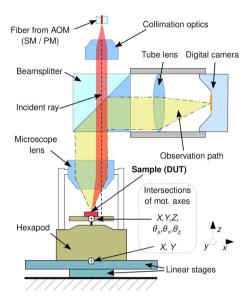

| Figure 3.2  | Scheme of the optical set-up                                                                              | 83  |

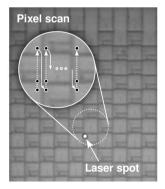

| Figure 3.3  | Microphotograph of the image sensor matrix with the laser spot and the                                    |     |

|             | scanned pixel region within the photodiode                                                                | 83  |

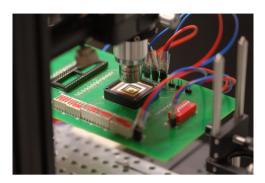

| Figure 3.4  | Optical set-up and DUT                                                                                    | 84  |

| Figure 3.5  | Illumination of the surroundings of the photodiode                                                        | 88  |

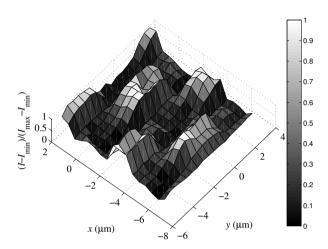

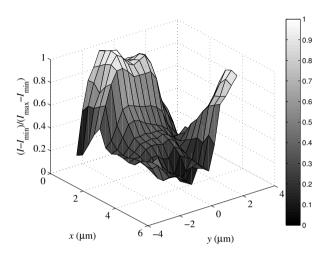

| Figure 3.6  | Normalized local relative photoresponse as a function of scan coordinates                                 |     |

|             | for a region with p-n+ junctions with $x_{\rm ph}=0.76~\mu{\rm m}$ and $x_\ell=4~\mu{\rm m}.~$            | 90  |

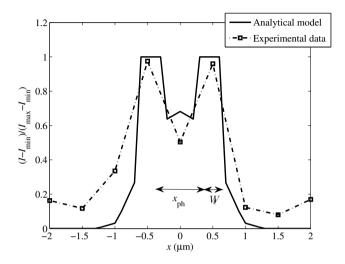

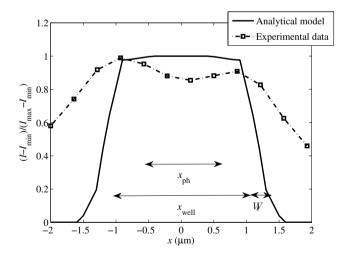

| Figure 3.7  | Experimental versus theoretical local relative photoresponse as a function                                |     |

|             | of scan coordinates for a p-n <sup>+</sup> junction with $x_{ph} = 0.76 \mu m$ and $x_{\ell} = 4 \mu m$ . | 91  |

| Figure 3.8  | Normalized local relative photoresponse as a function of scan coordinates                                 |     |

|             | for a region with p-N <sub>well</sub> junctions with $x_{ph} = 1.28 \mu m$ , $x_{well} = 2.20 \mu m$      |     |

|             | and $x_\ell = 4 \mu m$                                                                                    | 92  |

| Figure 3.9  | Experimental versus theoretical local relative photoresponse as a function                                |     |

|             | of scan coordinates for a p-N <sub>well</sub> junction with $x_{\rm ph}=1.28$ µm, $x_{\rm well}=$         |     |

|             | 2.20 $\mu$ m and $x_{\ell}=4~\mu$ m                                                                       | 92  |

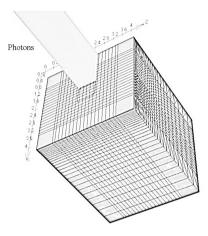

| Figure 3.10 | Scheme of the simulation set-up. Only the surrounding areas of the                                        |     |

|             | junction are illuminated                                                                                  | 93  |

| Figure 3.11 | Comparison of the active area and lateral photocurrents given by the model                                |     |

|             | and the simulation results, respectively, for a p-n <sup>+</sup> junction with $x_{ph} =$                 |     |

|             | $0.76~\mu m$ and $x_\ell = 4~\mu m$ under uniform illumination conditions                                 | 94  |

| Figure 4.1  | Photodiode structure                                                                                      | 101 |

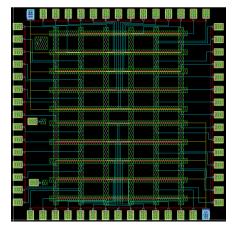

| Figure 4.2  | Printed circuit board designed to measure the CHIP 3 and CHIP 4                                           | 103 |

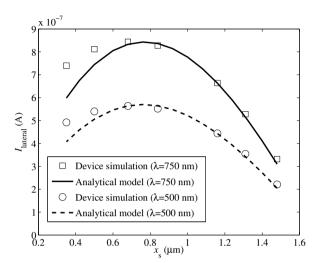

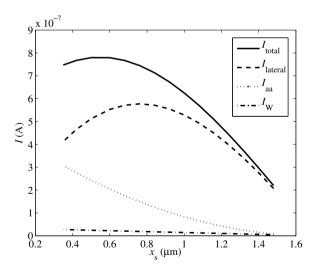

| Figure 4.3  | (a) Model validation by comparison with simulations from ATLAS and (b)                                    |     |

|             | current components for $\lambda = 500$ nm                                                                 | 112 |

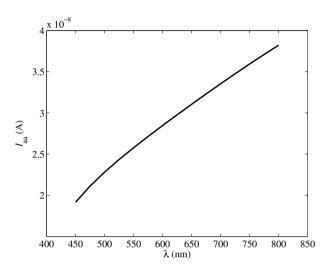

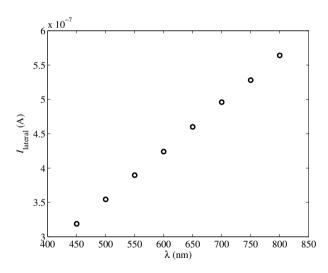

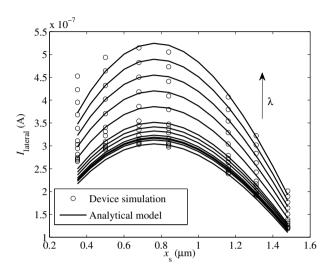

| Figure 4.4  | Simulation and model results for $I_{lateral}$ versus the surrounding area for                            |     |

|             | $\lambda = [470,800] \text{ nm. } \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                | 113 |

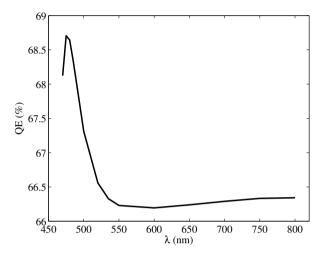

| Figure 4.5  | Total quantum efficiency.                                                                                 | 115 |

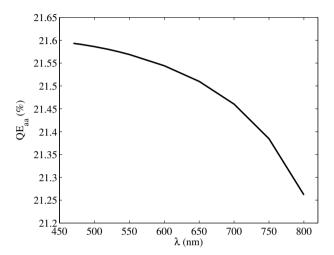

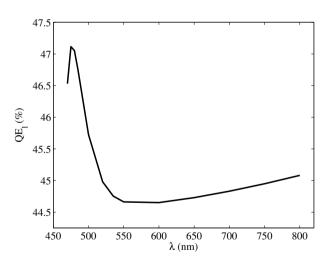

| Figure 4.6  | Quantum efficiency                                                                                        | 116 |

| Figure 4.7  | Contour map of the lateral photocurrent (nA) in UMC 65 nm standard                                        |     |

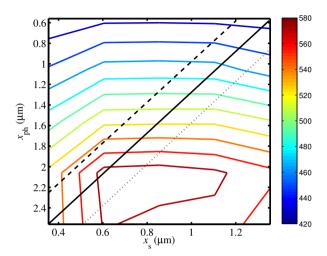

|             | technology (Table 4.5)                                                                                    | 119 |

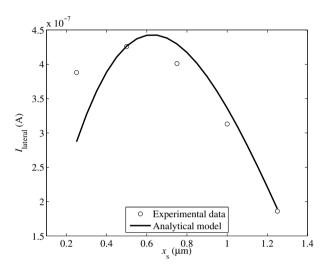

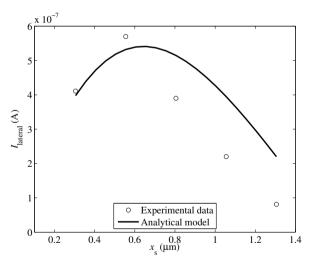

| Figure 4.8  | Model validation by comparison with experimental results of the lateral                                   |     |

|             | response as a function of $x_s$ ( $\lambda = 532$ nm)                                                     | 120 |

xvi List of Figures

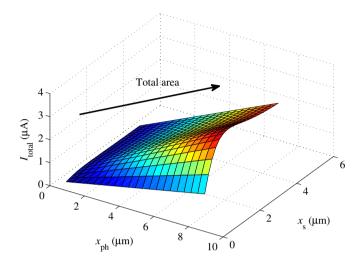

| Figure 4.9 | Surface plot of the total photocurrent given by the proposed model for the                          |     |

|------------|-----------------------------------------------------------------------------------------------------|-----|

|            | p-n <sup>+</sup> junctions in UMC 65 nm standard technology                                         | 121 |

| Figure 5.1 | Electrical equivalent circuit of the photodiode                                                     | 125 |

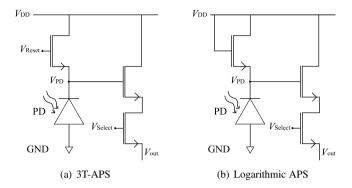

| Figure 5.2 | 3T-APS and logarithmic APS schemes                                                                  | 126 |

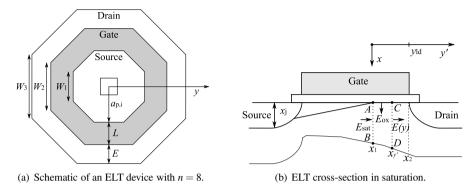

| Figure 5.3 | Enclosed-layout transistor scheme                                                                   | 127 |

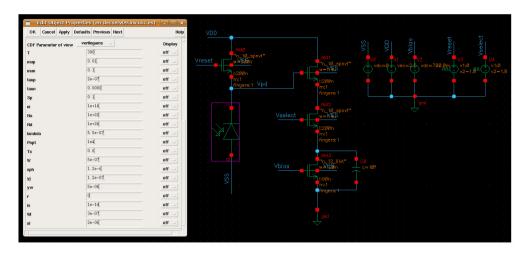

| Figure 5.4 | Screen capture of the 3T-APS circuit simulation showing the parameters                              |     |

|            | in the Verilog-AMS model of the photodiode which can be modified                                    | 130 |

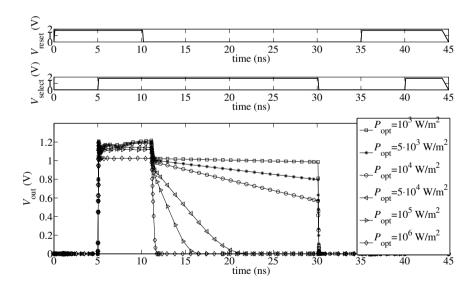

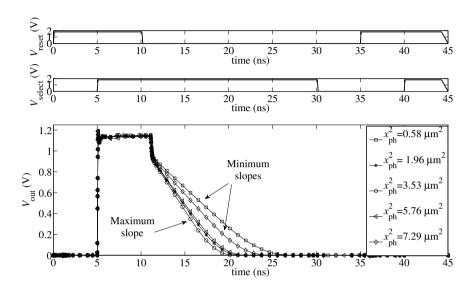

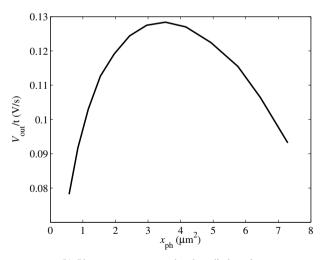

| Figure 5.5 | Circuit simulation results of the 3T-APS with $\lambda = 550$ nm and $x_{ph}^2 =$                   |     |

|            | 1.54 $\mu$ m <sup>2</sup> . Output voltage versus time for different $P_{\text{opt}}$ values in the |     |

|            | integration mode operation regime                                                                   | 131 |

| Figure 5.6 | Circuit simulation results of the 3T-APS with $\lambda = 550$ nm and $P_{\text{opt}} = 5$ .         |     |

|            | $10^4$ W/m <sup>2</sup>                                                                             | 132 |

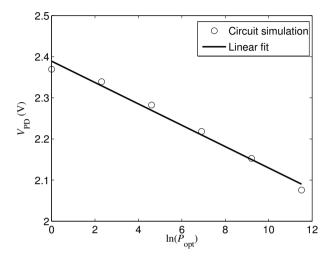

| Figure 5.7 | Semi-log plot of the photodiode voltage versus input optical power in                               |     |

|            | logarithmic mode operation regime. The logarithmic APS was simulated                                |     |

|            | for an incident radiation with $\lambda = 550$ nm                                                   | 134 |

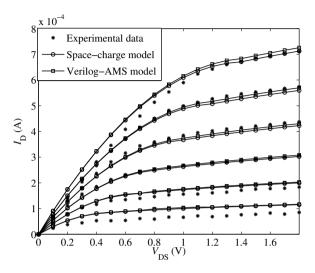

| Figure 5.8 | Comparison of the I–V curves of an ELT device with $n = 8$ , $L = 0.2 \mu m$                        |     |

|            | and $[W/L]_{\rm eff} = 15$ , given by the space-charge and Verilog-A models with                    |     |

|            | experimental data from a CMOS 0.18 μm process                                                       | 135 |

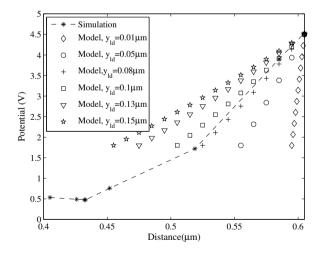

| Figure 5.9 | Estimation of the of the surface channel potential by comparison of the                             |     |

|            | model prediction for different values of $y_{ld}$ with device simulation                            | 135 |

## **List of Tables**

| Table 1.1 | Equation (1.5) parameters to describe the absorption coefficient of silicon .            | 22  |

|-----------|------------------------------------------------------------------------------------------|-----|

|           |                                                                                          |     |

| Table 1.2 | Summary of the main advantages of CCD and CMOS image sensors                             | 49  |

| Table 1.3 | Characteristics of CHIP 1 and CHIP 2                                                     | 51  |

| Table 2.1 | Parameters of the tested pixels in UMC 180 nm CIS technology                             | 62  |

| Table 2.2 | Parameters of the tested pixels in UMC 90 nm standard technology                         | 63  |

| Table 4.1 | Parameters of the fabricated p-n <sup>+</sup> junction photodiodes in AMS 180 nm         |     |

|           | (left) and UMC 65 nm (right) standard technologies                                       | 102 |

| Table 4.2 | Total photocurrent (nA) in AMS180 nm standard technology                                 | 118 |

| Table 4.3 | Lateral photocurrent (nA) in AMS180 nm standard technology                               | 118 |

| Table 4.4 | Total photocurrent (nA) in UMC 65 nm standard technology                                 | 118 |

| Table 4.5 | Lateral photocurrent (nA) in UMC 65 nm standard technology                               | 118 |

| Table A.1 | Physical constants                                                                       | 141 |

| Table A.2 | List of symbols                                                                          | 141 |

| Table B.1 | 180 nm technology                                                                        | 145 |

| Table B.2 | 90 nm technology                                                                         | 146 |

| Table B.3 | $p\hbox{-} n^+ \ photodiodes. \ \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 146 |

| Table B.4 | p-N <sub>well</sub> photodiodes with $l_{diff} = 0.80~\mu m$                             | 146 |

| Table B.5 | p-N <sub>well</sub> photodiodes with $l_{diff} = 1.28 \ \mu m$                           | 146 |

| Table B.6 | p-N <sub>well</sub> photodiodes with $l_{diff} = 1.52 \ \mu m$                           | 147 |

| Table B.7 | p-N <sub>well</sub> photodiodes with $l_{\text{diff}} = 2.00 \mu\text{m}$                | 147 |

xviii List of Tables

| Table B.8  | p-n <sup>+</sup> junction photodiodes under point source illumination in 90 nm    |     |

|------------|-----------------------------------------------------------------------------------|-----|

|            | technology                                                                        | 148 |

| Table B.9  | $p\text{-}N_{well}$ junction photodiodes under point source illumination in 90 nm |     |

|            | technology                                                                        | 149 |

| Table B.10 | 90 nm technology.                                                                 | 150 |

| Table B.11 | 180 nm technology                                                                 | 151 |

| Table B.12 | 65 nm technology.                                                                 | 152 |

Siguiendo el reglamento de los estudios de tercer ciclo de la Universidad de Santiago de Compostela, aprobado en la Junta de Gobierno el día 7 de abril de 2000 (DOG de 6 de marzo de 2001) y modificado por la Junta de Gobierno de 14 de noviembre de 2000, el Consejo de Gobierno de 22 de noviembre de 2003, de 18 de julio de 2005 (artículo 30 a 45), de 11 de noviembre de 2008 y de 14 de mayo de 2009; y, concretamente, cumpliendo las especificaciones indicadas en el capítulo 4, artículo 30, apartado 3 de dicho reglamento, se muestra a continuación un resumen en castellano de la tesis.

El mercado de los sensores de imagen, y en concreto el de las cámaras digitales, continúa dominado por un constante aumento del número de píxeles. Para ello, las tecnologías de sensores de imagen predominantes en la actualidad, CMOS (Complementary Metal-Oxide Semiconductor) y CCD (Charge Coupled Devices), compiten tanto por los segmentos de mercado existentes como por los emergentes adaptándose a esta tendencia de forma que los dispositivos sigan ofreciendo un buen rendimiento en términos de coste, consumo y peso, entre otros. Los beneficios potenciales de los sistemas de imagen CMOS ya fueron pronosticados a finales de los años 90 [1], y solo algunos años más tarde demostraron un rendimiento competitivo en comparación con los CCDs, [2]. Entre las ventajas de los sensores de imagen CMOS, tales como la reducción del consumo de energía y del coste, tal vez la miniaturización y la funcionalidad on-chip sean las que se ven más favorecidas por el escalado de la tecnología CMOS [3]. El principal camino para alcanzar tamaños de píxel cada vez más pequeños y, por tanto, mayor resolución con el mismo área, pasa por utilizar nodos tecnológicos avanzados. Pero, a pesar de que el progreso en la tecnología CMOS ofrece los medios para fabricar píxeles cada vez más pequeños, éstos deben superar algunos problemas electrónicos y ópticos inherentes a estas tecnologías. De hecho, aunque algunos estudios eran optimistas sobre los

beneficios de los sistemas de imagen CMOS a finales de los años 90, también se cuestionaba su calidad más allá del nodo tecnológico de 0.25 µm, si no se realizaba ningún cambio en el proceso, debido al aumento de la corriente de fuga y a la disminución del rango dinámico debido a los efectos del escalado [4]. Hoy en día, muchos de estos problemas se han minimizado gracias a los avances en la ingeniería de procesos, pero el desafío de producir el píxel más pequeño posible con la suficiente sensitividad sigue existiendo. Por otro lado, los componentes fotónico-electrónicos integrados siguen estando dominados por la característica de la reducción de tamaño en las tecnologías CMOS, conocida como Ley de Moore [5]. Debido a que los sistemas de imagen deben interactuar con la luz, el impacto de la Ley de Moore sobre ellos es diferente al que tiene lugar sobre otras aplicaciones de circuitos integrados. De este modo, también debe investigarse cómo la tendencia a la reducción del tamaño de los píxeles interactúa con las propiedades de la luz, tales como el ruido fotónico y la difracción.

El mercado de los sensores de imagen CMOS ha aumentado considerablemente en los últimos años favorecido por los avances en la tecnología de fabricación. Paralelamente a todo esto, ha habido una gran preocupación en relación con el impacto del escalado de la tecnología y el dispositivo en la respuesta global [4], en particular en términos de sensitividad [6], corriente oscura [7] y respuesta espectral [8]. Sin embargo, el estudio de los efectos dimensionales sobre los sensores CMOS cada vez más pequeños es esencial dado que su modelado y simulación representan un punto débil en el diseño de nanosensores de imagen. Esta deficiencia debe ser abordada, ya que constituye una de las pocas metodologías que permiten reducir los tiempos y costes de desarrollo. Por lo tanto, es necesario un esfuerzo con un enfoque que combine el proceso tecnológico, la arquitectura del píxel y el modelado de los sensores CMOS para alcanzar el rendimiento de los CCDs a medida que se reduce el tamaño del píxel [9].

En los últimos años, los esfuerzos para modificar los procesos de fabricación de las tecnologías CMOS estándar y así mejorar el rendimiento de la formación de imágenes, han sido

significativos, [10]. Para mejorar la fotoresponsividad, se han incluido diodos de unión profunda sin siliciuros con perfiles optimizados de dopaje en los procesos estándar. Por otro lado,

la reducción de la corriente oscura se consigue por medio de la implantación de difusiones

dobles de fuente/drenador sin siliciuros así como de estructuras de diodo *pinned*. El recocido

por hidrógeno se utiliza también para reducir las fugas debidas a defectos por pasivación. La

reducción de fugas en los transistores, tanto en el de *reset* como en el seguidor en un sensor de

píxel activo, también se ha considerado a través del uso de óxido de puerta grueso. Además, se

aumenta la tensión umbral del transistor de reset y se disminuye la del seguidor para reducir

su corriente de apagado y para mejorar la oscilación de voltaje, respectivamente. Finalmente, en tecnologías de sensores de imagen (CIS) y después de la pasivación, se pueden depositar sobre el chip un filtro de color y microlentes para mejorar la eficiencia cuántica.

Por otro lado, el escalado de la tecnología también tiene efectos perjudiciales sobre la eficiencia óptica del píxel que han sido igualmente abordados por las mejoras tecnológicas [11]. Por ejemplo, la transmisión de la luz se ve reducida por el uso de dióxido/nitruro de silicio. Además, a medida que la tecnología CMOS escala, la distancia desde la superficie del chip al fotodetector aumenta en relación con el tamaño del pixel más pequeño que se puede fabricar. Esto es debido a una reducción más lenta en el espesor de las capas de interconexión, que escala menos que en las otras dos dimensiones. Como resultado, la luz debe viajar a través de un túnel cada vez más profundo y más estrecho antes de llegar a la superficie del fotodetector. Por otro lado, también se están utilizando óxidos con mejores propiedades para la transmisión de la luz con el propósito de aumentar la eficiencia óptica. Además, el adelgazamiento de las capas de metal y óxido se utiliza para disminuir la relación de aspecto del túnel por encima de cada fotodetector, [12]. Otra técnica para aumentar la eficiencia óptica es la colocación de burbujas de aire alrededor de cada píxel con el fin de crear una guía de onda óptica rudimentaria mediante la cual la luz incidente en la superficie es guiada hasta el píxel correspondiente a través de la reflexión interna total. Las burbujas de aire también sirven para reducir significativamente la contaminación espacial óptica, que puede ser particularmente problemática a medida que el tamaño del píxel disminuye, [13]. Todas estas modificaciones a nivel de proceso han permitido la reducción del tamaño del píxel por debajo de los valores pronosticados.

En cuanto a la arquitectura del píxel, el estudio del escalado de la tensión de alimentación ha contribuido a mejorar la metodología de diseño para sensores de imagen CMOS de bajo voltaje, [14]. También cabe destacar la importancia de la aparición de nuevas configuraciones de píxel, como las denominadas estructuras de píxeles compartidos, en las que varios píxeles comparten la difusión flotante o algunos de sus transistores para reducir el área reservada a la electrónica y aumentar la capacidad del fotodiodo y la sensitividad [15, 16]. Igualmente interesantes son los estudios en los que se caracterizan y comparan diversos píxeles con diferentes combinaciones de fotodetector, transistores y arquitectura, para explorar las ventajas de cada uno de ellos [17, 18]. Así, por ejemplo, la tecnología de iluminación posterior (BSI) ha demostrado ser una buena solución para mejorar la relación señal-ruido [19].

A pesar de los progresos realizados a nivel de proceso y de píxel, la caracterización de sensores de imagen CMOS en tecnologías submicrométricas es escasa. Así, un estudio en los nodos tecnológicos de 0.18 μm y 0.15 μm con modificaciones menores presenta un sensor de imagen CMOS con excelente rendimiento que se caracteriza por su bajo ruido, alta sensitividad, alta velocidad, y funcionamiento en condiciones de baja iluminación, equiparable al estado del arte de los sensores de imagen CCD [20], contradiciendo los malos resultados en una tecnología CMOS estándar de 0.18 μm de hace ya más de una década [21]. De hecho, no sólo los píxeles caracterizados en una tecnología CIS de 0.18 μm han demostrado un buen comportamiento [22], sino también los de tecnologías estándar actuales de 0.18 μm [23, 24]. Más allá de procesos de 0.18 μm, se diseñaron estructuras de píxeles compartidos en procesos de cobre de 0.13 μm y 90 nm para estudiar su sensitividad [25]. También se desarrollaron sensores de imagen en tecnologías CMOS de 90 nm y 65 nm, evaluando nuevas configuraciones de píxel con fotodiodos apilados y alto factor de llenado que exhibieron características competitivas con sensores comerciales en tecnologías convencionales, [26].

A pesar de que es difícil satisfacer todas las características deseables en un diseño, tales como bajo nivel de ruido, alto rango dinámico, alta sensitividad, alto factor de llenado, bajo consumo de energía, operación a bajo voltaje e imagen de alta velocidad, el verdadero reto es mejorar el proceso tecnológico junto con el diseño de los píxeles para garantizar que no hay pérdida de rendimiento a medida que el tamaño del píxel se reduce, [27, 28]. Aunque los fabricantes de electrónica de consumo no suelen proporcionar información sobre el tamaño del píxel de sus productos, y por lo tanto es difícil saber cuál es el píxel más pequeño en el mercado, se estima que está muy por debajo de 2 µm, [29]. Sin embargo, todavía se echa en falta un estudio en profundidad de los principales fenómenos físicos que dominan el comportamiento de los píxeles en estos nodos tecnológicos. En particular, debe prestarse una mayor atención al impacto de la fotorrespuesta periférica en fotodiodos de pequeño tamaño, ya que existen estudios que predicen que su magnitud es comparable a la del área activa del píxel, [30]. Por esta razón, es necesario desarrollar modelos completos de la respuesta de los fotodiodos CMOS con el fin de permitir la elección correcta de la tecnología y la arquitectura de píxel. Por otra parte, desde el punto de vista industrial, el desarrollo de nuevos sensores CMOS no puede existir sin herramientas de diseño asistido por ordenador (CAD). Por lo tanto, son esenciales modelos compactos de fotodiodos CMOS incluyendo efectos periféricos en tecnologías submicrométricas que puedan ser incorporados a estas herramientas. En este sentido, el objetivo de este trabajo es proporcionar un estudio del comportamiento de fotodetectores de pequeño

tamaño en tecnologías CMOS avanzadas, a fin de evaluar el impacto del escalamiento en la fotorrespuesta del píxel.

La denominada captación periférica es la suma de la captación lateral y de fondo debidas a la difusión hacia la región de vaciamiento de las cargas fotogeneradas en el sustrato de los alrededores de la unión. Aunque los primeros estudios en relación a esta componente se remontan varias décadas atrás, el efecto de la captación periférica podía despreciarse cuando los fotodiodos eran de gran tamaño. El primer modelo semianalítico de la fotorrespuesta de un píxel CMOS incluyendo la captación periférica fue presentado en [31] y se utilizó para predecir la respuesta máxima del píxel al escalar la tecnología, [32]. Los mismos autores también estudiaron la respuesta periférica y la contaminación inter-píxel en una tecnología de 0.35 µm CMOS estándar mediante resultados experimentales y de simulación. Sin embargo, no se conocen estudios en nodos tecnológicos más actuales. Con este objetivo, en el trabajo que aquí se presenta se estudió la respuesta de la celda 3T-APS, ampliamente utilizada, por medio de medidas experimentales de diferentes píxeles con fotodiodos de unión p-n<sup>+</sup> y p-N<sub>well</sub> en tecnologías de 180 nm CIS y 90 nm CMOS estándar, respectivamente. Así mismo, se derivó y validó un modelo semianalítico para su fotorrespuesta en términos de sensitividad. El modelo presta especial atención a la captación periférica, modelando este fenómeno como una componente diferente aparte de la captación del área activa. De este modo, se proponen y comparan varias funciones para modelar la contribución del área activa y del fondo de la unión. Los resultados se presentan en el Capítulo 2, que amplía el trabajo presentado en [33, 34, 35, 36].

El estudio preliminar sugiere que una mayor área activa no garantiza necesariamente la respuesta óptima para fotodiodos de pequeño tamaño. Por ello, posteriormente se llevó a cabo un estudio a nivel subpíxel para caracterizar las diferentes regiones por separado. Aunque existen estudios sobre el tamaño y la forma del píxel e incluso algunos modelos semianalíticos de la respuesta del píxel en función del área activa, pocos son los estudios subpíxel. De hecho, las medidas de este tipo requieren de un equipamiento óptico sofisticado y se necesita invertir un tiempo considerable para realizarlas correctamente. Uno de los primeros mapas de la fotorrespuesta a nivel subpíxel se presentó en [37]. Sin embargo, hoy en día la tecnología y el tamaño de los píxeles han quedado obsoletos. En [38] se encuentran medidas más recientes, aunque la tecnología tampoco es actual. La respuesta a una iluminación puntual también se estudió en detectores de infrarrojo, [39], y en fotodiodos BSI, [40]. El estudio a nivel subpíxel que se presenta en este trabajo consistió en la caracterización de la fotorrespuesta de

fotodiodos de unión p-n<sup>+</sup> y p-N<sub>well</sub> fabricados en una tecnología de 90 nm CMOS estándar por medio de una fuente puntual de iluminación. Además, se propuso un modelo analítico para estimar la fotorrespuesta basado en la solución de la ecuación de estado estacionario en las diferentes regiones del dispositivo. El modelo propuesto muestra la importancia de la contribución lateral y fue comparado con éxito con los datos exprimentales. Otra prueba de la importancia de la captación lateral se encontró mediante la simulación de dispositivos bajo iluminación uniforme de los alrededores de la unión. Este análisis se detalla en el Capítulo 3 y fue presentado en [41].

Los estudios previos establecieron la importancia de la captación lateral en fotodiodos de pequeño tamaño, y de ahí la necesidad de encontrar una solución de compromiso entre el área activa y el área que rodea la unión para maximizar su respuesta. Es más, sería deseable disponer de un modelo que tenga en cuenta este fenómeno, y que pueda adaptarse fácilmente a diferentes tamaños y geometrías del fotodiodo y nodos tecnológicos. Sin embargo, no es sencillo contextualizar esta tarea dado que hay una gran variedad de modelos analíticos para fotodetectores en la literatura que pueden clasificarse en base a diferentes criterios tales como la dimensión (1D, 2D o 3D), el tipo de dispositivo (vertical, lateral, mesa, *finger*, iluminación trasera, etc.), el tipo de unión (p-n<sup>+</sup>, n-p<sup>+</sup>, p-N<sub>well</sub>, N<sub>well</sub>-p<sup>+</sup>, p-epi-N<sub>well</sub>, p-epi-P<sub>well</sub>-n<sup>+</sup>, etc.), el rango de aplicación (rayos gamma, rayos-X, ultravioleta, visible, infrarrojo, microondas, etc.), y otras características. Además, las condiciones de contorno y diversos tipos de simplificaciones pueden variar de un modelo a otro complicando aún más su clasificación.

Uno de los primeros modelos analíticos para fotodiodos basado en la resolución de la ecuación de continuidad en estado estacionario data de 1977, [42]. En él ya se hace mención a la captación periférica, aunque el tamaño de los dispositivos considerados es mucho mayor que el de los actuales. En cuanto a modelos bidimensionales de estructuras verticales, como las que son objeto de este trabajo, en [43] se hace una descripción cuantitativa de la fotocorriente de un fotodiodo p-n<sup>+</sup> basándose en [44] y particularizada para el caso de sustrato de película fino. Más allá de este análisis cuantitativo, en [45] se presentó un modelo para evaluar el impacto del tamaño del fotodiodo, el perfil de dopado y la velocidad de recombinación superficial en la eficiencia de una unión p-n<sup>+</sup>, aunque no se deriva totalmente la expresión final, dificultando su aplicación práctica. Otro análisis bidimensional, pero limitado al sustrato, puede encontrarse en [46]. Finalmente, no se encuentran muchos trabajos que aborden esta problemática mediante la resolución de la ecuación de estado estacionario en tres dimensiones. En [47] se desarrolla un modelo analítico tridimensional para fotodiodos n-p<sup>+</sup> verticales

mediante un análisis de Fourier, bajo condiciones periódicas de iluminación y limitado al sustrato. Basándose en este trabajo, otro modelo en tres dimensiones para estructuras de fotodiodo periódicas se utilizó para ilustrar la importancia de la recombinación en superficie y la degradación de la movilidad a lo largo de la interfaz Si-SiO<sub>2</sub>. En esta línea, y tras haber encontrado indicios sobre la importancia de la captación periférica en fotodiodos de pequeño tamaño, en este trabajo se presenta un modelo analítico para fotodiodos de unión p-n<sup>+</sup> verticales, operando en el rango visible y bajo iluminación uniforme, basado en la solución de la ecuación bidimensional de estado estacionario en los alrededores de la unión. El análisis se caracteriza por el tratamiento matemático que se ha hecho de la componente lateral. El modelo propuesto se ajusta con gran precisión a los resultados obtenidos mediante simulación y también fue validado posteriormente con medidas experimentales en tecnologías de 180 nm y 65 nm estándar. Este análisis se detalla en el Capítulo 4 y fue presentado en [48].

El modelo propuesto es compacto, general y escalable. En otras palabras, puede extenderse fácilmente a tamaños diferentes de fotodiodo, a otras geometrías y nodos tecnológicos. Con el fin de ser útil en herramientas para el diseño asistido por ordenador (CAD), el modelo fue implementado en un lenguaje de simulación hardware. De hecho, en la literatura no se han encontrado muchos trabajos acerca de la traducción a este tipo de lenguajes de modelos para fotodetectores y todos ellos son unidimensionales. Así, en [49] se presenta una colección de modelos para dispositivos optoelectrónicos, entre ellos un modelo de fotodiodo, aunque no se proporciona su expresión matemática y éste se basa en un dispositivo comercial. Por otro lado, en el marco del desarrollo de un simulador de circuitos de código abierto soportando el lenguaje Verilog-A, se sugiere un modelo de fotodiodo, pero no en función de parámetros físicos y tecnológicos y necesitando de un importante proceso de caracterización previo, [50]. Finalmente, en [51] se utilizan expresiones clásicas para el modelado de fotodetectores y píxeles en VHDL-AMS. Así, en el Capítulo 5 de este trabajo se muestra la implementación del modelo propuesto en un lenguaje de simulación hardware y su uso para la simulación de circuitos, ilustrando su potencialidad para la optimización del píxel. Un trabajo derivado de este estudio ha sido enviado para su publicación y se encuentra actualmente bajo revisión, [52]. También se aborda en este capítulo la implementación en Verilog-AMS de un modelo de transistor de puerta encerrada (ELT) desarrollado en trabajos previos [53, 54, 55].

### Contribución

A continuación se resumen las principales conclusiones derivadas de este trabajo:

- Las medidas experimentales de celdas 3T-APS con fotodiodos de unión p-n<sup>+</sup> octogonales y p-N<sub>well</sub> cuadrados en tecnologías de 180 nm CIS y 90 nm estándar de UMC, respectivamente, mostraron una dependencia de la sensitividad con la razón entre el área de captación activa y la periférica. Los fenómenos físicos en los alrededores de la unión se describen con un modelo semianalítico que se ajustó a los datos experimentales con gran precisión. Este hecho pone de manifiesto la correcta comprensión de la física del dispositivo y reveló la importancia de la captación lateral en fotodiodos de pequeño tamaño. Por lo tanto, la tendencia a maximizar el área activa del fotodetector con el propósito de obtener la máxima fotorrespuesta debe revisarse.

- Un estudio a nivel subpíxel permitió la caracterización de la fotorrespuesta de las distintas regiones del píxel. De esta forma, celdas 3T-APS con fotodiodos de unión p-n<sup>+</sup> y p-N<sub>well</sub> cuadrados en una tecnología de 90 nm estándar de UMC fueron escaneados y medidos en términos de fotocorriente por medio de una fuente de iluminación puntual. Estas estructuras se modelaron mediante la solución analítica de la ecuación de estado estacionario en las diferentes regiones del píxel. Tanto el modelo como los datos experimentales muestran una importante fotorrespuesta debida a la iluminación del área de captación que rodea a la unión. Para confirmar este aspecto, se llevaron a cabo simulaciones de una unión p-n<sup>+</sup> para diferentes tamaños del área activa y manteniendo constante el tamaño total. Únicamente los alrededores de la unión fueron expuestos a la fuente de iluminación uniforme, mostrando una solución de compromiso entre las áreas de captación activa y periférica que optimizaba la respuesta. También se encontró que la respuesta del área periférica era más importante que la del área activa.

- Se propuso un modelo analítico para la fotorrespuesta lateral, basado en la resolución de la ecuación bidimensional de estado estacionario, que se ajustó de forma excelente a los resultados obtenidos mediante simulación. Posteriormente, las predicciones fueron validadas con medidas experimentales de fotodiodos de unión p-n<sup>+</sup> cuadrados en tecnologías estándar de 180 nm de AMS y de 65 nm de UMC. Para ello se caracterizaron fotodiodos con distinto tamaño del área activa y del área que rodea a la unión bajo iluminación uniforme. Para medir la fotorrespuesta periférica de forma indepen-

diente también se caracterizaron las mismas estructuras y en las mismas condiciones, pero con el área activa protegida frente a la luz. Los datos experimentales confirmaron el comportamiento pronosticado por las simulaciones, y el modelo propuesto reprodujo la respuesta de las estructuras en ambas tecnologías. Como resultado, se obtuvo un modelo para fotodiodos CMOS en el rango visible general, escalable y compacto.

– El modelo propuesto fue implementado en un lenguaje de descripción hardware y utilizado para la simulación de circuitos, demostrando ser una herramienta poderosa para el diseño asistido por ordenador de sensores de imagen CMOS. La potencialidad de este tipo de descripciones para el diseño de circuitos integrados que incluyen dispositivos no estándar fue también ilustrada mediante la implementación de modelos de transistores de topologías especiales de puerta encerrada.

With camera manufacturers marketing their products with ever-increasing pixel counts, Complementary Metal-Oxide Semiconductor (CMOS) and Charge Coupled Devices (CCD) image sensors compete for existing and emerging market segments while at the same time trying to guarantee no loss of performance as the pixel size shrinks. The benefits of CMOS imagers were already predicted in the late 1990s [1], and they demonstrated a competitive behaviour over CCDs some years after [2]. Among the CMOS image sensors advantages, such as the system power and cost reductions, perhaps the miniaturization and the on-chip functionality are the most favoured by the CMOS technology scaling [3]. Advanced technological nodes represent the main course to achieve smaller pixels and thus high resolution in the same area. Even though the progress in CMOS technology offers the means to fabricate them, smaller pixels in advanced technologies must overcome some electrical and optical problems. In fact, although some studies were optimistic about the benefits of CMOS imagers around late 1990s, their quality beyond the 0.25 µm generation technology without any process change was questioned because scaling effects were expected to increase the leakage current and reduce the dynamic range [4]. Today, many of these problems have been minimized by advances in process engineering but the challenge to produce the smallest possible pixel with enough sensitivity remains. On the other hand, integrated photonic-electronic components are still dominated by the feature size reduction in CMOS technologies known as Moore's Law [5]. Because imagers must interact with light, Moore's Law impact differs from its impact on other integrated circuit applications. Thereby, how the trend towards smaller pixels interacts with the properties of light, such as photon noise and diffraction, must also be investigated.

Favoured by advances in technology fabrication, the market of CMOS image sensors has greatly increased over the last years. Parallel to this, a great concern has been raised in relation to the impact of technology and device scaling on the overall response [4], in particular in

terms of sensitivity [6], dark-current [7] and spectral response [8]. However, research on dimensional effects on ever-shrinking CMOS imagers is essential as efficient CMOS image sensor modelling and simulation represent a weak point of CMOS nano imager design. This deficiency needs to be addressed as it constitutes one of the few enabling methodologies that can reduce development cycle times and costs. Thus, an effort on a combined approach to process technology, pixel architecture and modelling for CMOS imagers to match CCD performance as pixel sizes shrink is needed [9].

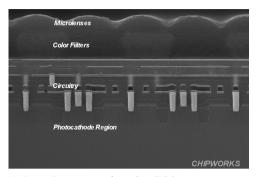

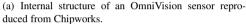

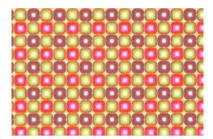

In the last years, there have been significant efforts to modify the fabrication process of standard CMOS technologies to enhance their imaging performance, [10]. To improve photoresponsivity, nonsilicided deep junction diodes with optimized doping profiles have been included in standard processes. Dark current reduction is, on the other hand, achieved by means of nonsilicided, double-diffused source/drain implantation as well as pinned diode structures. Hydrogen annealing is also used to reduce leakage by passivating defects. The reduction of transistor leakage in both the reset and follower transistors in an active pixel sensor has been also considered through the use of thick gate oxides. Besides, the threshold voltage of the reset and follower transistors are increased and decreased to reduce its off-current and to improve voltage swing, respectively. Finally, after passivation, a color filter and microlenses can be formed on chip to improve quantum efficiency in CMOS Image Sensor (CIS) technologies.

Technology scaling also has detrimental effects on pixel optical efficiency that have been addressed by technology improvements [11]. For instance, light transmission is reduced by the use of silicon dioxide/nitride materials. Moreover, as CMOS technology scales, the distance from the surface of the chip to the photodetector increases relative to the size of the smallest pixel that can be fabricated. This is due to a slower reduction in the thickness of the interconnect layers, which scales less than the planar dimensions. As a result, light must travel through an increasingly deeper and narrower tunnel before reaching the photodetector surface. Thinning of metal and oxide layers is used to decrease the aspect ratio of the tunnel above each photodetector, [12]. On the other hand, oxide materials with better light transmission properties are being used to increase the optical efficiency. Another technique to increase the optical efficiency is the placement of air gaps around each pixel in order to create a rudimentary optical waveguide whereby incident light at the surface is guided to the correct pixel below via total internal reflection. The air gaps also serve to significantly reduce optical spatial crosstalk, which can be particularly problematic as pixel sizes decrease, [13]. All these process modifications have allowed the reduction of pixel size below predicted values.

Regarding the pixel architecture, research on the power supply voltage scaling has contributed to improve the design methodology for low voltage CMOS image sensors, [14]. Other studies have reported new pixel structures, the so-called shared pixels, in which several pixels share the floating diffusion or transistors to enhance photodiode capacity, sensitivity and fill factor [15, 16]. Photodetectors with different junctions in combination with different pixel transistors and architectures should also be explored to take advantage of their particular benefits, [17, 18]. In fact, Backside-Illuminated (BSI) technology has been recently adopted as a solution to improve pixel signal-to-noise ratio performance [19].

Despite the progress made at process and pixel level, there is a shortage of CMOS image sensors performance characterization in deep sub-micron technologies. For instance, contrary to the poor results of CMOS sensors in a 0.18 µm standard technology reported one decade ago in [21], a more recent study has demonstrated excellent CMOS imager low-noise, high-sensitivity, low-lag, and low-light performance, matching that of state-of-the-art CCD imagers in 0.18 µm and 0.15 µm technological nodes including minor process modifications [20]. In fact, not only tested pixels in 0.18 µm CIS technology have shown a good behaviour [22], but those in 0.18 µm standard technologies as well [23, 24]. Beyond 0.18 µm processes, shared pixels in 0.13 µm and 90 nm Cu processes were designed, respectively, to study their sensitivity in [25]. Image sensors using 90 nm and 65 nm CMOS technology were also developed, evaluating new pixel configurations with stacked photodiodes and high fill factor which exhibited characteristics competitive with commercial sensors in conventional technologies, [26].

All the desirable features, such as low noise, high dynamic range, high sensitivity, high fill factor, low power consumption, low voltage operation and high speed imaging, are difficult to achieve in one design, but the real challenge is to improve the technological process along with the pixel design to guarantee no loss of performance as the pixel size shrinks, [27, 28]. Although consumer electronics manufacturers do not usually provide pixel size information of their products and thus it is difficult to know what is the current smallest pixel in the market, its pitch has been reduced well under 2 µm thanks to the rapid scaling of CMOS technologies and the development of optimized image sensor processes for CMOS vision products [56]. However, an in-depth study of the main physical phenomena dominating the behaviour of pixels at these technological nodes is still missing. In particular, greater attention needs to be paid to the impact of the peripheral photoresponse on small photodiodes as its magnitude becomes comparable to that of the main active area of the pixel, [30]. For this reason, it is necessary to develop comprehensive models of the CMOS photodiodes response

in order to permit the proper choice of technology and pixel architecture. Furthermore, from an industrial point of view, the development of new CMOS sensor devices solutions cannot exist without computer-aided design (CAD) tools. Therefore, compact models of CMOS photodiodes including peripheral effects in sub-micron technologies are essential.

In this sense, the goal of this work is to provide a study of the behaviour of small photodetectors in advanced CMOS technologies in order to evaluate the impact of the geometry on the pixel photoresponse. With this aim, the response of the widespread used 3T-APS cell was studied by means of experimental measurements of different pixels with p-n<sup>+</sup> and p-N<sub>well</sub> junction photodiodes in 180 nm CIS and 90 nm standard CMOS technologies, respectively. A semianalytical model for their photoresponse in terms of sensitivity was derived and validated. The model pays special attention to the peripheral collection, modelling this phenomenon as a different component apart from the active area collection. In this way, several functions to model the active area and bottom contributions are proposed and compared. The results are reported in Chapter 2 and summarized in [33, 34, 35, 36].

Since the preliminary study suggested that the largest active area no longer necessarily guarantees the optimum response for small photodiodes, a sub-pixel study was developed to study the different regions of the pixel separately. It consisted of the photoresponse characterization of p-n<sup>+</sup> and p-N<sub>well</sub> junction photodiodes fabricated in a 90 nm standard CMOS technology by means of a point source illumination. An analytical model for the photoresponse estimation based on the solution of the steady-state equation in the different regions of the device was proposed and successfully compared with the experimental data, showing the significance of the lateral contribution. Further evidence of the importance of the lateral collection was found by device simulations under uniform illumination of the surroundings of the junction. This analysis is detailed in Chapter 3 and was presented in [41].

The previous studies established the importance of the lateral collection in small photodiodes and hence the need to find a trade-off between the active area and the collecting area surrounding the junction to maximize the response. Based on the solution of the two-dimensional steady-state equation in the surroundings of the junction, an analytical model for uniformly illuminated p-n<sup>+</sup> junction photodiodes was proposed. The model fitted device simulation results with excellent agreement and was also validated with experimental measurements in 180 nm and 65 nm standard technologies. This part of the work is covered by Chapter 4 and was presented in [48].

The proposed model is compact, general and scalable. In other words, it can be easily extended to different photodiode sizes, geometries and technological nodes. In order to be used in Computer Aided Design (CAD) tools, the model was implemented in a Hardware Description Language (HDL) and used for circuit simulations to illustrate the potential of the model for the optimization of the pixel performance. More details are given in Chapter 5 and have been summarized in [52].

### CHAPTER 1

## **SOLID-STATE IMAGE SENSORS**

A solid-state image sensor, also called an imager, is a semiconductor device that converts an optical image into electronic signals. A high quality image is achieved through high resolution, high sensitivity, high speed imaging, wide dynamic range, good linearity for colour processing, low power consumption, low voltage operation and very low noise.

The number of applications using image sensors is growing rapidly. They can detect light within a wide spectral range, from X-rays to infrared wavelength regions, by tuning its detector structures and employing materials which are sensitive to the wavelength region of interest. However, the focus of this work is on visible imaging, corresponding to the spectral response of the human eye, which responds to wavelengths from about 390 to 750 nm. Silicon, the most widely used material for Very Large-Scale Integrated circuits (VLSIs), is also suitable for image sensors on the visible range because the band gap energy of silicon matches the energy of visible wavelength photons.

This chapter reviews the basics of image sensors, their evolution and the current technologies used for their fabrication. Based on this, the framework of this work is presented.

#### 1.1 Evolution