# UNIVERSIDADE DE SANTIAGO DE COMPOSTELA FACULTADE DE FÍSICA

Departamento de Física de Partículas  ${\bf LabCAF}$

# The Front-End Electronics of the HADES timing RPCs wall: design, development and performances analysis

Daniel Belver Fernández Santiago de Compostela, Decembro 2009

#### D. Juan Antonio Garzón Heydt Profesor Titular da Área de Física Atómica Molecular e Nuclear

#### CERTIFICA

Que a tese titulada "The Front-End Electronics of the HADES timing RPCs wall: design, development and performances analysis", foi realizada por D. Daniel Belver Fernández no Departamento de Física de Partículas de Universidade de Santiago de Compostela baixo a súa dirección, para acadar o título de Doutor en Física.

Santiago de Compostela, Decembro de 2009

Asinado:

Juan Antonio Garzón Heydt

"It's better to burn out than to fade away..."

"Hey Hey, My My" - Neil Young

### Agradecementos

A tese é unha carreira de fondo, cos seus momentos altos e baixos, na que non podes nunca deixar de loitar ata o final. Porque ese final sempre chega. Por iso quero agradecer a toda a xente que me axudou a chegar aquí.

En primeiro lugar, quero darlle as gracias ó profesor Juan A. Garzón por darme a oportunidade de participar no experimento HADES, pola súa inestimable axuda e paciencia nestes anos e polas discusións e consellos que van máis aló da física. Tamén quero agradecer ó profesor Paulo Fonte do LIP en Coimbra o apoio prestado no desenvolvemento do traballo e os coñecementos que compartiu comigo. E gracias a Jesús Marín, que me deu a oportunidade de traballar con el no CIEMAT en Madrid e aprender moito cando empezaba a tese.

Of course, I want acknowledge to all the people at GSI with whom I worked along these years, specially Dr. Wolfgang Koenig for the discussions, the advices and the ideas he gave me during our work together. It was a pleasure. Thanks Dr. Michael Traxler and Marek Palka for their collaboration in all the experiments.

E, por suposto, gracias a toda a xente do proxecto coa que tantas tempadas botei no GSI traballando en experimentos e na montaxe dos detectores, sufrindo nevadas e calor, e compartindo cervexas. Alberto, Luis e Américo do LIP de Coimbra, Alex do IFIC de Valencia e a xente relacionada co LabCAF da USC, Martín Zapa (sen o rock n' roll da súa guitarra non funcionaría a electrónica), Elena, Diego, Miguel, Georgy e sobre todo Pablo, por todos eses meses traballando xuntos no GSI, por non decaer nos meus momentos de desesperación e por estar sempre aí.

E como non, lembrarme de toda a xente ca que compartín moitos bos momentos durante estes anos. Ós meus compañeiros da facultade, en especial a Manuel, Noelia e Carme polo seu apoio, e tamén a Héctor, Carlos, David, e Martín. Gracias a Jose por eses momentos no GSI e os concertos que vivimos, sobre todo o do Boss en Santiago, onde compartimos esas noites de cervexas e eses cafés con tabaco mentres soaba música de Neil Young, Zeppelin ou Bolan. Gracias a Juan por todas esas conversas cun licor café na man. E a Maruxa, Fernando, Eva e Iván pola súa amistade ó longo destes anos.

Gracias ós meus pais e á miña irmá Paula, por apoiarme sempre aínda que non saiban moi ben o que fago e por estar sempre ó meu carón.

E sobre todo, gracias a María por todo o que significa na miña vida, por todo o que compartimos xuntos e por todo o que temos por diante. Por ser a mellor persoa que coñezo.

# Contents

| 1 | Intr | oduct  | ion                               | 1  |

|---|------|--------|-----------------------------------|----|

| 2 | The  | HAD    | ES experiment                     | 5  |

|   | 2.1  |        | luction                           | 5  |

|   | 2.2  |        | ADES physics                      | 6  |

|   | 2.3  |        | IADES spectrometer                | 7  |

|   |      | 2.3.1  | The START and VETO detectors      | 10 |

|   |      | 2.3.2  | The RICH detector                 | 10 |

|   |      | 2.3.3  | The MDCs and the magnet           | 11 |

|   |      | 2.3.4  | The TOF wall                      | 11 |

|   |      | 2.3.5  | The SHOWER detector               | 12 |

|   |      | 2.3.6  | The trigger scheme                | 13 |

| 3 | Tim  | ning R | PC detectors: the HADES tRPC wall | 15 |

| J | 3.1  | _      | ical RPC introduction             | 15 |

|   | 0.1  | 3.1.1  | RPCs                              |    |

|   |      | 3.1.2  | Double gap RPC                    | 16 |

|   |      | 3.1.3  | Operation modes                   | 17 |

|   |      | 3.1.4  | Multi-gap RPCs (MRPCs)            | 17 |

|   |      | 3.1.5  | Timing RPCs (tRPCs)               | 18 |

|   |      | 3.1.6  | Gas mixture and operation voltage | 19 |

|   |      | 3.1.7  | Readout electronics               | 19 |

|   | 3.2  |        | g RPC physics                     | 19 |

|   | 0.2  | 3.2.1  | Efficiency and primary ionization | 19 |

|   |      | 3.2.2  | Time response                     | 20 |

|   |      | 3.2.3  | Time-charge correlation           | 21 |

|   |      | 3.2.4  | Space-charge                      | 21 |

|   |      | 3.2.5  | Prompt charge vs induced charge   | 22 |

|   |      | 3.2.6  | Electronics in tRPCs              |    |

|   |      | 3.2.7  | Examples of timing RPC walls      |    |

|   | 3.3  |        | [ADES tRPC wall                   |    |

|   | 5.5  | 3.3.1  | Specifications of the ToF wall    |    |

|   |      | 3.3.2  | Characteristics of the tRPC wall  |    |

|   | 2.4 | 3.3.3 Design and construction of the ToF wall            |    |

|---|-----|----------------------------------------------------------|----|

|   | 3.4 | Conclusions                                              | 31 |

| 4 | Fro | nt-End Electronics for the HADES tRPC Wall: first steps  | 39 |

|   | 4.1 | Introduction of the FEE                                  | 39 |

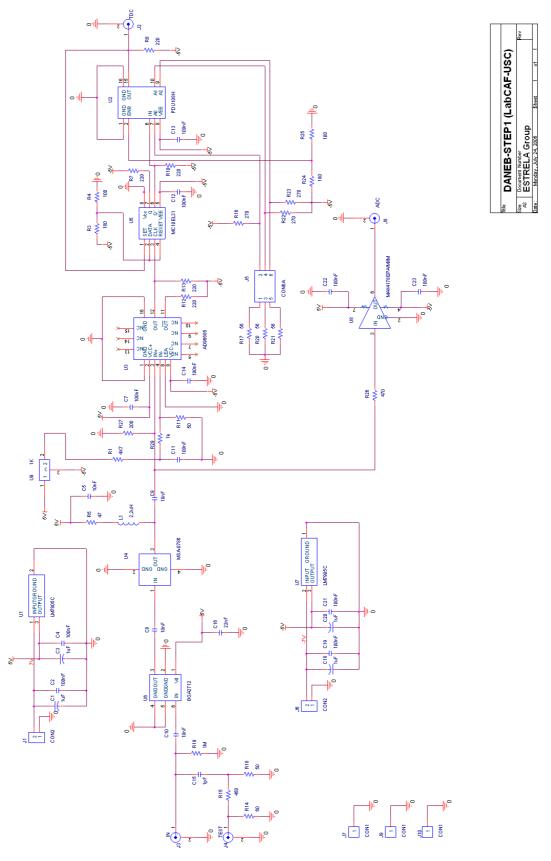

|   | 4.2 | The FEE-STEP1 design                                     | 41 |

|   |     | 4.2.1 Analog and amplification stage                     | 41 |

|   |     | 4.2.2 Digital stage                                      | 43 |

|   |     | 4.2.3 Voltage regulators stage                           | 44 |

|   | 4.3 | FEE-STEP1 performances analysis                          | 44 |

|   |     | 4.3.1 Experimental setup                                 | 45 |

|   |     | 4.3.2 Time Resolution analysis                           | 46 |

|   |     | 4.3.3 Position Resolution analysis                       | 47 |

|   |     | 4.3.4 Charge measurements                                | 48 |

|   | 4.4 | FEE-STEP1 conclusions                                    | 50 |

|   | 4.5 | e e e e e e e e e e e e e e e e e e e                    | 51 |

|   |     |                                                          | 52 |

|   |     |                                                          | 53 |

|   |     |                                                          | 55 |

|   | 4.6 | ı v                                                      | 55 |

|   |     | v                                                        | 55 |

|   |     | v                                                        | 57 |

|   |     |                                                          | 57 |

|   | 4.7 |                                                          | 61 |

|   | 4.8 | FEE first steps conclusions                              | 62 |

| 5 | Sim | ulation of the Front-End Electronics                     | 63 |

|   | 5.1 | DBO-STEP3 simulation for positive signals                | 64 |

|   |     | 5.1.1 DBO-STEP3 simulation circuit description           | 64 |

|   |     | 5.1.2 DBO-STEP3 simulation results                       | 65 |

|   | 5.2 | DBO-STEP5 simulation for negative signals                | 69 |

|   |     |                                                          | 70 |

|   |     | 5.2.2 DBO-STEP5 simulation results                       | 71 |

|   | 5.3 | Simulation conclusions                                   | 78 |

| 6 | Dev | relopment of the FEE-STEP3 and STEP4: design and results | 79 |

|   | 6.1 |                                                          | 79 |

|   | 6.2 |                                                          | 80 |

|   |     |                                                          | 80 |

|   |     |                                                          | 84 |

|   | 6.3 | •                                                        | 91 |

|   | 6.4 |                                                          | 93 |

|   |     | ·                                                        | 93 |

|   |               | 6.4.2   | Crosstalk between channels                    |

|---|---------------|---------|-----------------------------------------------|

|   |               | 6.4.3   | Charge and Time Over Threshold correlation    |

|   | 6.5           | HADE    | ES RPC Nov05 beam test at GSI                 |

|   |               | 6.5.1   | Experimental setup                            |

|   |               | 6.5.2   | Time resolution measurements                  |

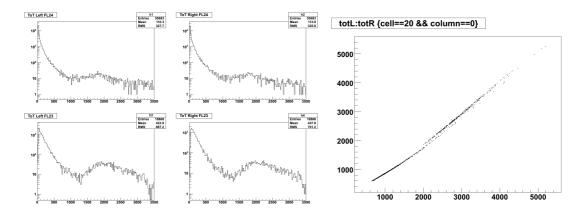

|   |               | 6.5.3   | ToT-charge measurements                       |

|   |               | 6.5.4   | Position resolution measurements              |

|   |               | 6.5.5   | Crosstalk measurements                        |

|   |               | 6.5.6   | Conclusions                                   |

|   | 6.6           | Impro   | vements in the STEP4 design                   |

|   |               | 6.6.1   | FEE stability                                 |

|   |               | 6.6.2   | Time over Threshold algorithm                 |

|   |               | 6.6.3   | Time resolution for small signals             |

|   |               | 6.6.4   | Cosmic rays test                              |

|   | 6.7           | FEE-S   | STEP3 and STEP4 conclusions                   |

|   |               |         |                                               |

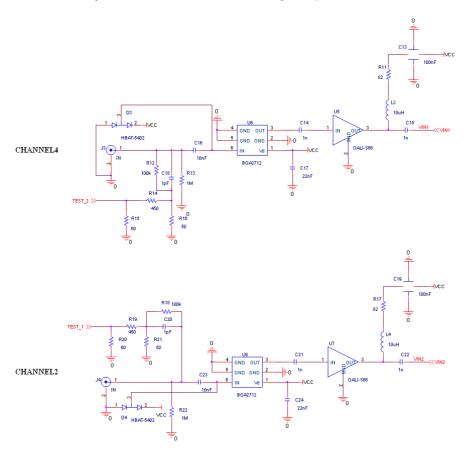

| 7 | $\mathbf{DB}$ | O-STE   | 2P5 version: design, analysis and results 109 |

|   | 7.1           |         | luction                                       |

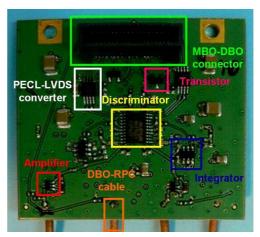

|   | 7.2           | The a   | ctive board: the DaughterBOard STEP5 109      |

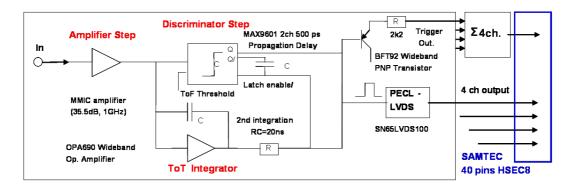

|   |               | 7.2.1   | Analog stage                                  |

|   |               | 7.2.2   | Digital stage                                 |

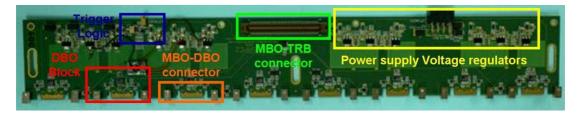

|   | 7.3           | The p   | assive board: the MotherBOard MBOv2           |

|   |               | 7.3.1   | DAC read-back                                 |

|   |               | 7.3.2   | Test signals                                  |

|   |               | 7.3.3   | Supply voltage improvements                   |

|   |               | 7.3.4   | Trigger output signal                         |

|   |               | 7.3.5   | Temperature sensor                            |

|   | 7.4           | Test o  | of the two FEE versions                       |

|   |               | 7.4.1   | Experimental setup                            |

|   |               | 7.4.2   | Test signals analysis                         |

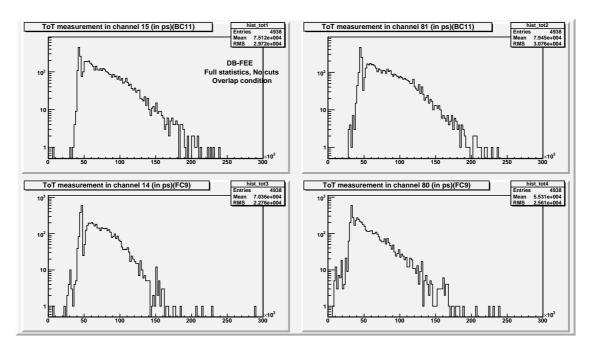

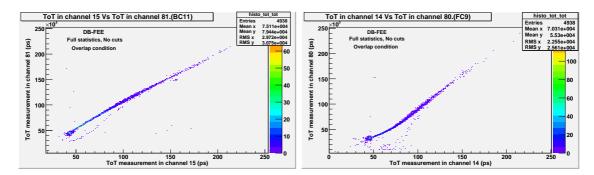

|   |               | 7.4.3   | RPC signals analysis                          |

|   |               | 7.4.4   | Conclusions                                   |

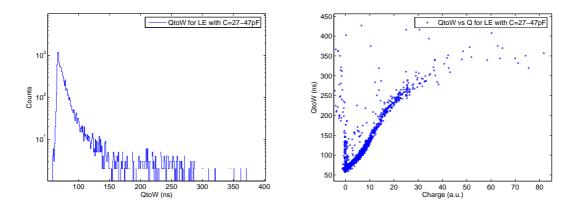

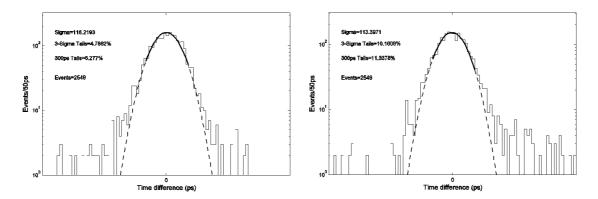

|   | 7.5           | QtoW    | improvements of the DBO-STEP5                 |

|   |               | 7.5.1   | Simulation based in real signals              |

|   |               | 7.5.2   | FEE analysis with test and RPC signals        |

|   |               | 7.5.3   | QtoW improvements in-beam environment         |

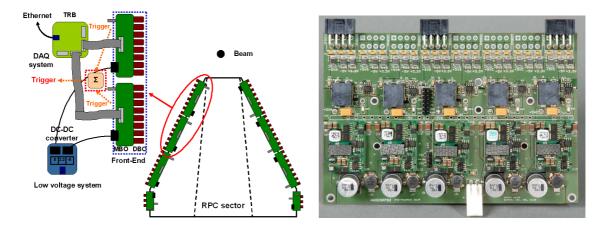

|   | 7.6           | First 1 | RPC sector installed in HADES                 |

|   |               | 7.6.1   | FEE boards                                    |

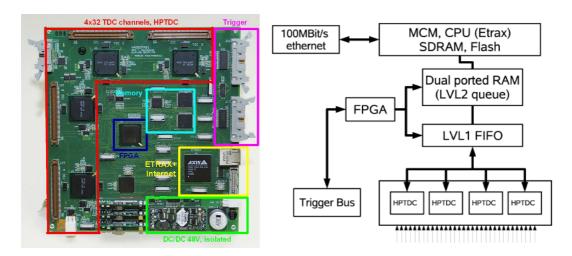

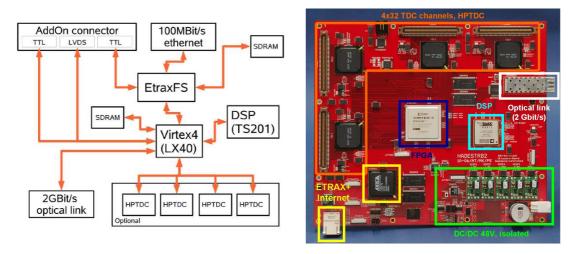

|   |               | 7.6.2   | DAQ board                                     |

|   |               | 7.6.3   | Experimental setup                            |

|   |               | 7.6.4   | Measurements                                  |

|   |               | 7.6.5   | Results                                       |

|   | 7 7           | Concl   |                                               |

| 8            | Con   | nmissioning of the HADES RPC wall with final FEE version | 157   |

|--------------|-------|----------------------------------------------------------|-------|

|              | 8.1   | Introduction                                             |       |

|              | 8.2   | Final version of the FEE boards                          | . 157 |

|              |       | 8.2.1 The DaughterBOard design                           | . 157 |

|              |       | 8.2.2 The passive MotherBOard design                     | . 160 |

|              | 8.3   | Stability test of the FEE final version                  | . 161 |

|              |       | 8.3.1 Time and position resolution measurements          | . 162 |

|              |       | 8.3.2 QtoW measurements                                  | . 163 |

|              |       | 8.3.3 Cosmic rays test                                   |       |

|              |       | 8.3.4 Conclusions                                        | . 165 |

|              | 8.4   | QtoW calibration                                         |       |

|              |       | 8.4.1 Experimental setup                                 | . 167 |

|              |       | 8.4.2 Results with pulser and RPC signals                | . 168 |

|              | 8.5   | Production tests of the final FEE version                |       |

|              |       | 8.5.1 Measurements of different parameters               | . 173 |

|              |       | 8.5.2 Summary of the validation tests                    |       |

|              | 8.6   | Commissioning of the HADES-RPC wall                      |       |

|              |       | 8.6.1 Temperature test of the FEE boards                 | . 176 |

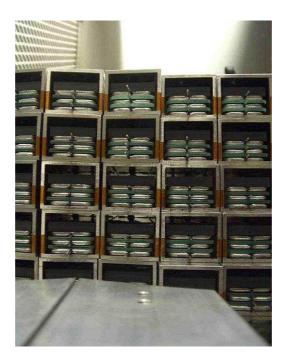

|              |       | 8.6.2 Assembly of all the RPC sectors                    |       |

|              |       | 8.6.3 Installation of the RPC sectors in HADES           |       |

|              | 8.7   | HADES RPC ToF wall conclusions                           |       |

| 9            | Con   | aclusions and Outlook                                    | 181   |

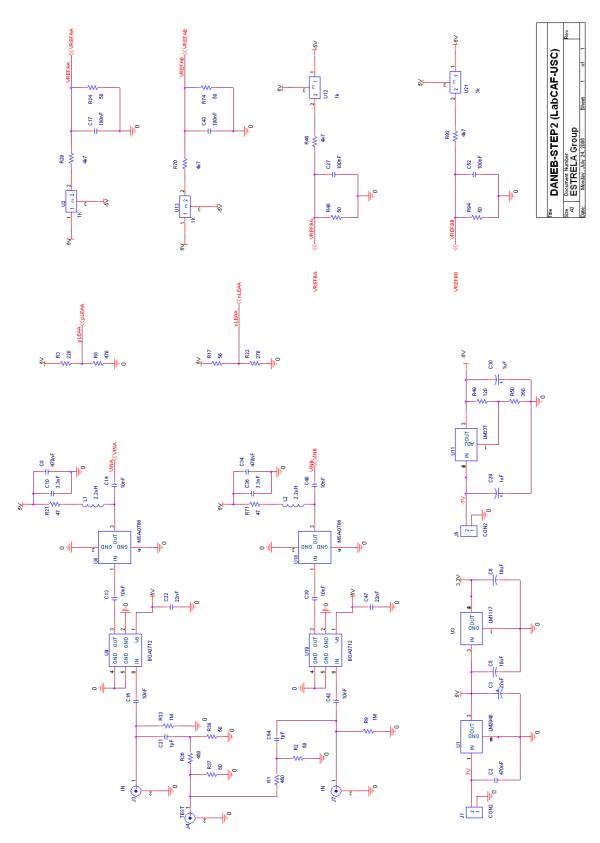

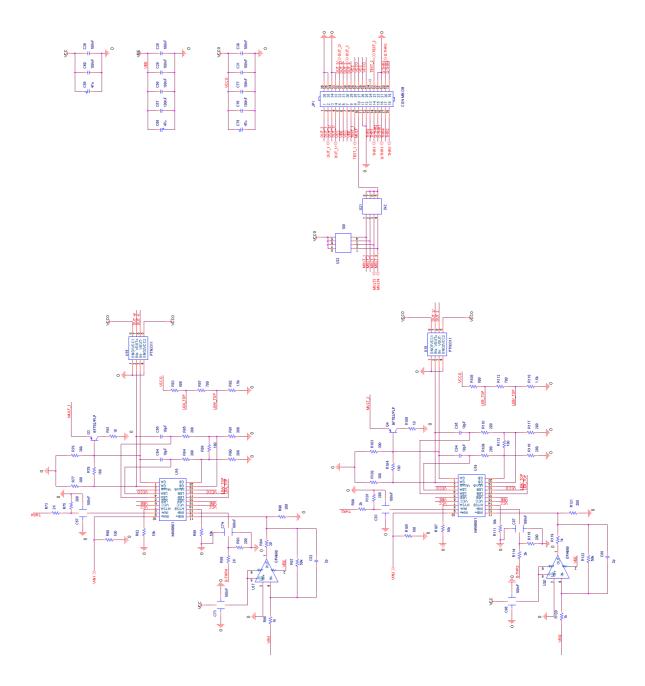

| $\mathbf{A}$ | FEI   | E-STEP1 and STEP2: schematics and layouts                | 183   |

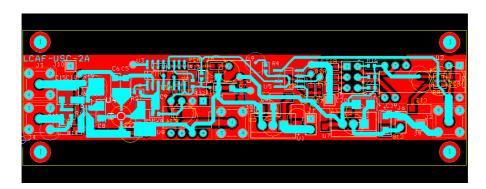

|              | A.1   | FEE-STEP1 schematics and layout                          | . 183 |

|              | A.2   | FEE-STEP2 schematics and layout                          | . 185 |

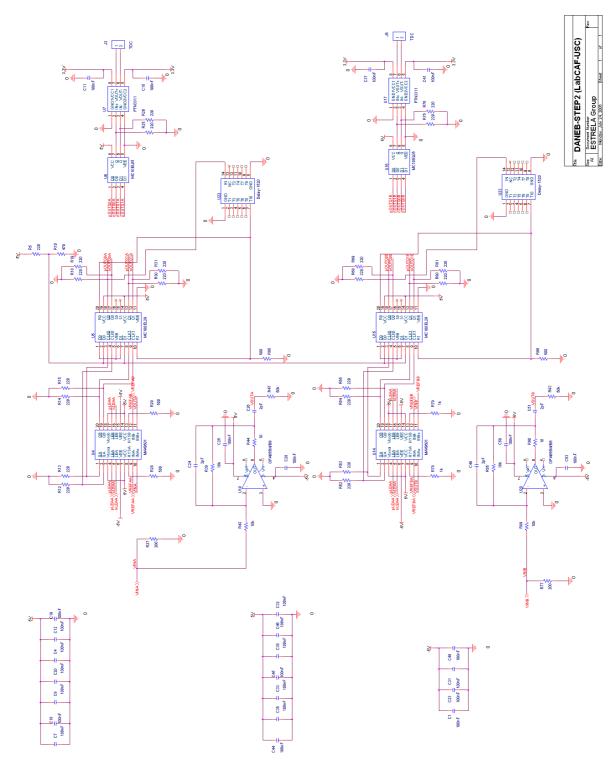

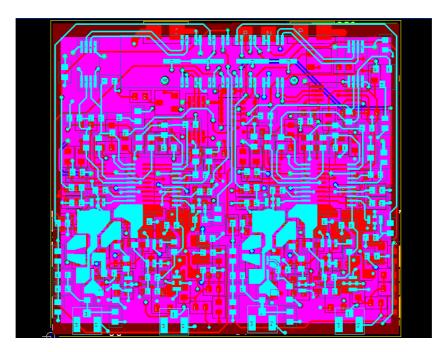

| В            | Diff  | erent designs with DBO-MBO configuration                 | 189   |

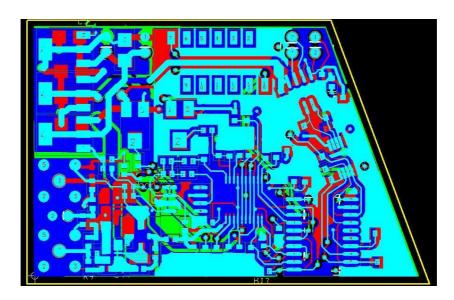

|              | B.1   | DBO-STEP3 schematics and layout                          | . 190 |

|              | B.2   | DBO-STEP5: schematics and layout                         | . 191 |

|              | B.3   | DBO final version: schematics and layout                 | . 193 |

|              | B.4   | MBOv2: schematics and layout                             | . 194 |

| $\mathbf{C}$ | Res   | umo                                                      | 199   |

|              | C.1   | Introducción                                             | . 199 |

|              | C.2   | Electrónica de amplificación e dixitalización            | . 201 |

|              | C.3   | <del>-</del>                                             |       |

|              | C.4   | Conclusións                                              | . 206 |

| Bi           | bliog | graphy                                                   | 207   |

# List of Figures

| 2.1  | 3D and side view of the HADES spectrometer                                                        |

|------|---------------------------------------------------------------------------------------------------|

| 2.2  | GSI accelerator schematic                                                                         |

| 2.3  | The RICH detector                                                                                 |

| 2.4  | TOF and TOFino wall                                                                               |

| 2.5  | SHOWER and TOFino detectors                                                                       |

| 2.6  | $\beta$ vs $p$ distribution for all the reconstructed particles $\ \ldots \ \ldots \ \ldots \ 14$ |

| 3.1  | Single and double gap RPC                                                                         |

| 3.2  | 3 and 4-gap RPC design                                                                            |

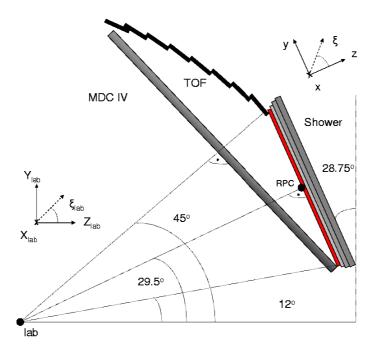

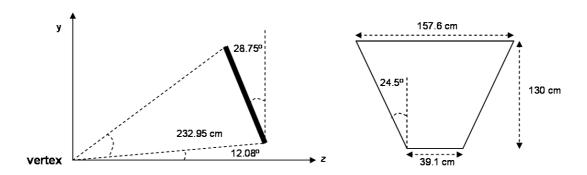

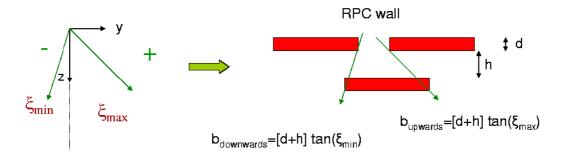

| 3.3  | Reference system of the HADES tRPC wall                                                           |

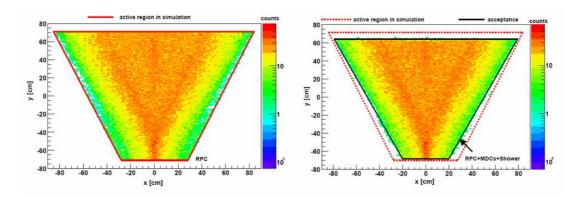

| 3.4  | Acceptance of the HADES tRPC wall for two cases                                                   |

| 3.5  | Acceptance of the HADES tRPC wall                                                                 |

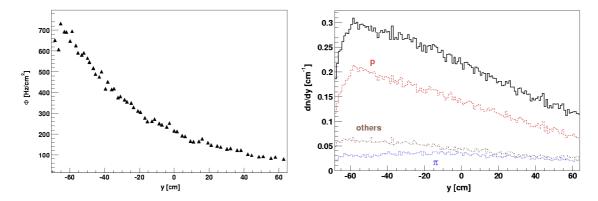

| 3.6  | Expected rate and occupancy in the HADES tRPC wall 31                                             |

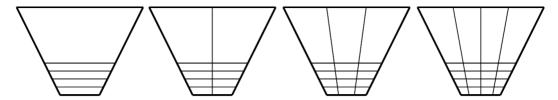

| 3.7  | HADES tRPC wall segmentations in 1-4 columns                                                      |

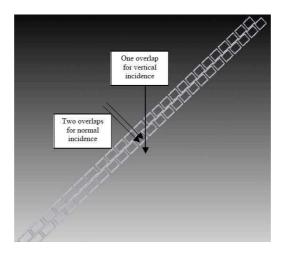

| 3.8  | Overlap cells design of the HADES tRPC wall                                                       |

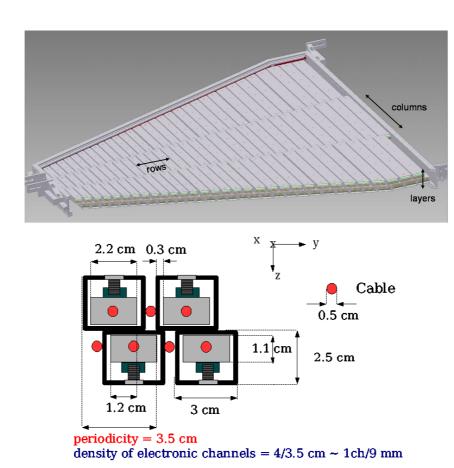

| 3.9  | Final design of the HADES tRPC wall and FEE channels density $$ . $$ 34                           |

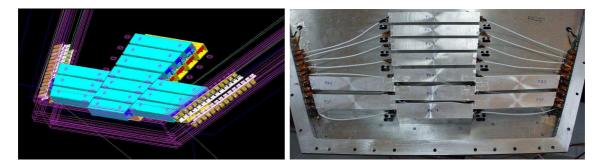

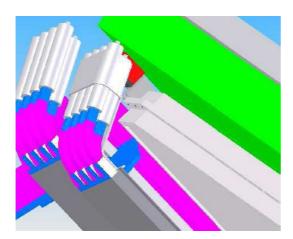

| 3.10 | 3D design of the HADES tRPC wall                                                                  |

| 3.11 | Internal structure of the HADES tRPC cells                                                        |

| 3.12 | Details of the HADES tRPC wall installation                                                       |

| 3.13 | Final installation of the six tRPC sectors                                                        |

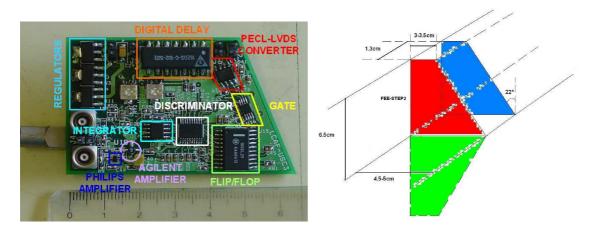

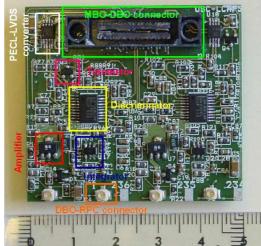

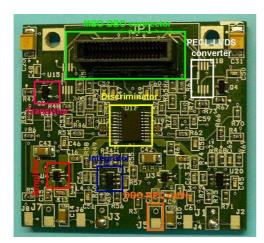

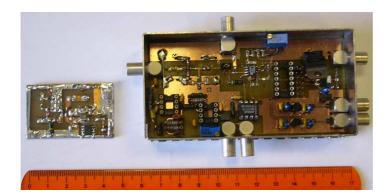

| 4.1  | FEE-STEP1 picture                                                                                 |

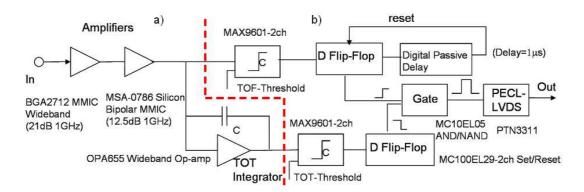

| 4.2  | FEE-STEP1 block diagram                                                                           |

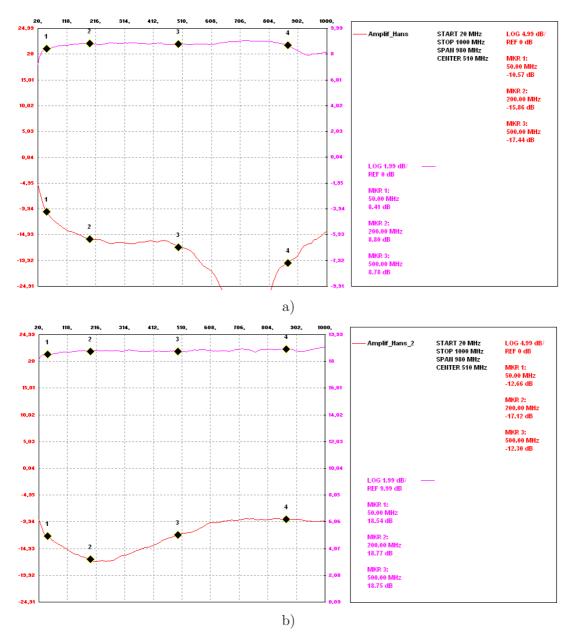

| 4.3  | Gain of the preamplifiers                                                                         |

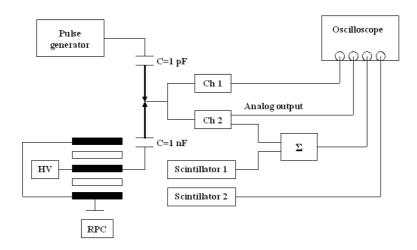

| 4.4  | Experimental setup for the STEP1 and STEP2 tests 45                                               |

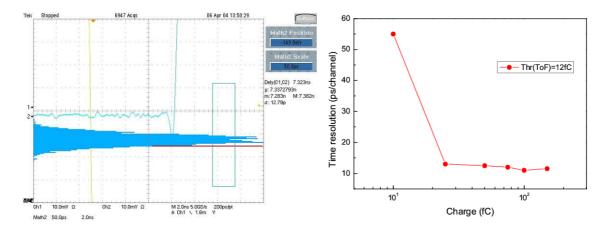

| 4.5  | FEE-STEP1 time resolution with pulser                                                             |

| 4.6  | FEE-STEP1 position resolution                                                                     |

| 4.7  | FEE-STEP1 charge spectrum                                                                         |

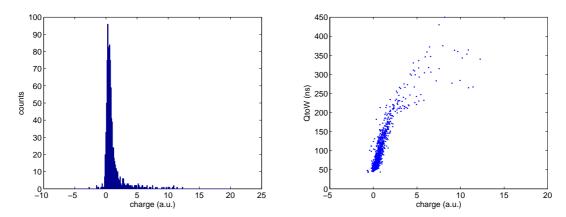

| 4.8  | Q-ToT correlation for the FEE-STEP1 with a RC-CR filter 49                                        |

| 4.9  | Retriggers in the FEE-STEP1 discriminator                                                         |

| 4.10 | FEE-STEP2 picture                                                                                 |

| 4.11 | FEE-STEP2 block diagram                                                                           |

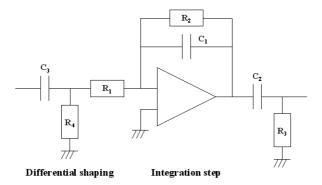

| 4.12 | FEE-STEP2 integration step                                                                        |

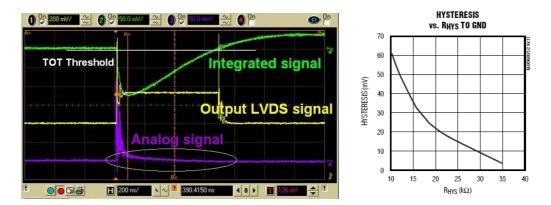

| 4.13 | Different signals in the FEE-STEP2 design                                                         |

| 4.14 | FEE-STEP2 time resolution with pulser and RPC                          | . 56  |

|------|------------------------------------------------------------------------|-------|

| 4.15 | Q-ToT correlation with pulser for the STEP2                            | . 58  |

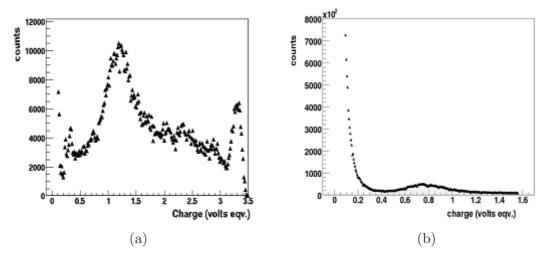

| 4.16 | FEE-STEP2 charge spectra for cosmic and gamma rays                     | . 59  |

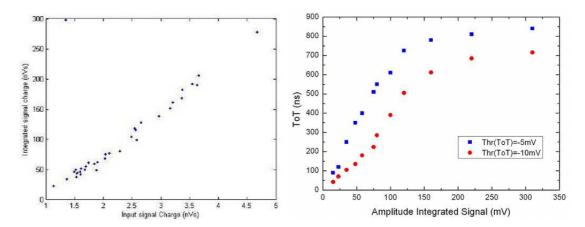

| 4.17 | Amplitude and ToT correlation with RPC signals for the STEP2           | . 60  |

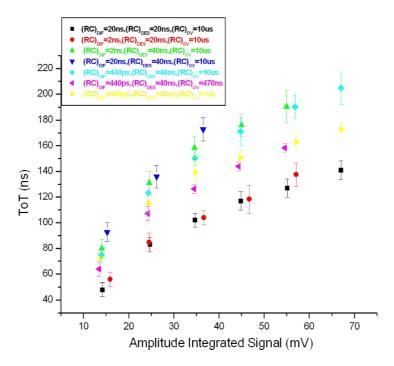

| 4.18 | STEP2 Q-ToT correlation with RPC signals for different RC values       | . 61  |

| 5.1  | DBO-STEP3 simulation schematic design                                  | . 65  |

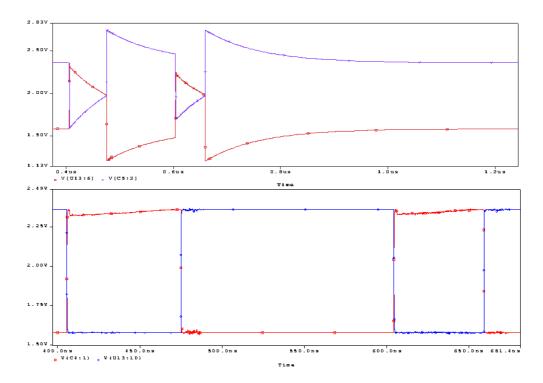

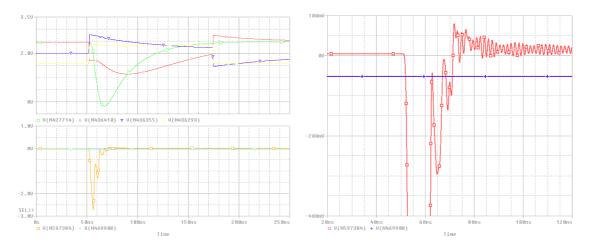

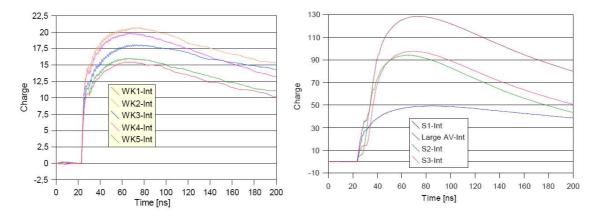

| 5.2  | Analog signals for the DBO-STEP3 simulation                            | . 66  |

| 5.3  | Digital signals of the DBO-STEP3 simulation                            | . 68  |

| 5.4  | Pile-up effect in the DBO-STEP3 simulation                             |       |

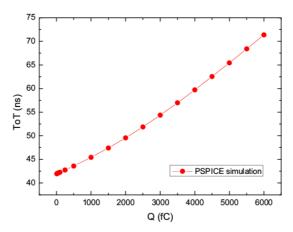

| 5.5  | ToT vs charge correlation for the DBO-STEP3 simulation                 |       |

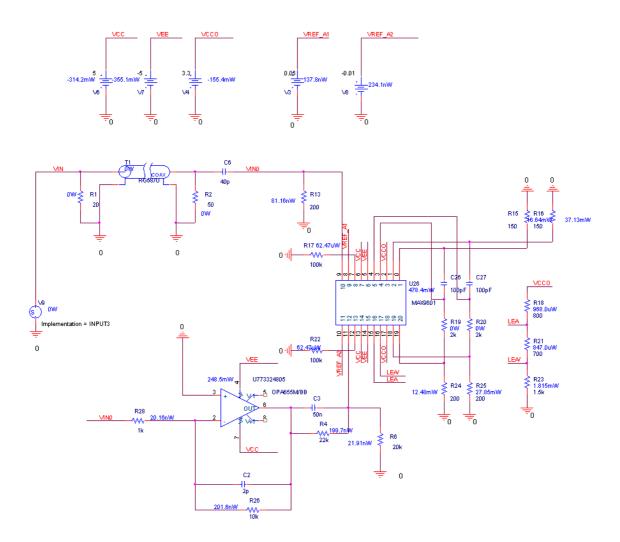

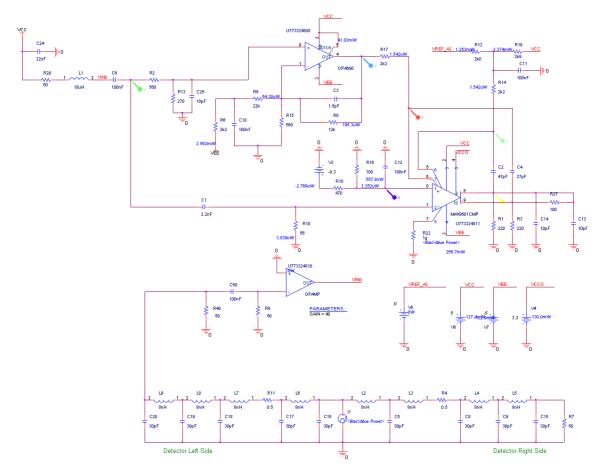

| 5.6  | DBO-STEP5 simulation schematic design                                  | . 71  |

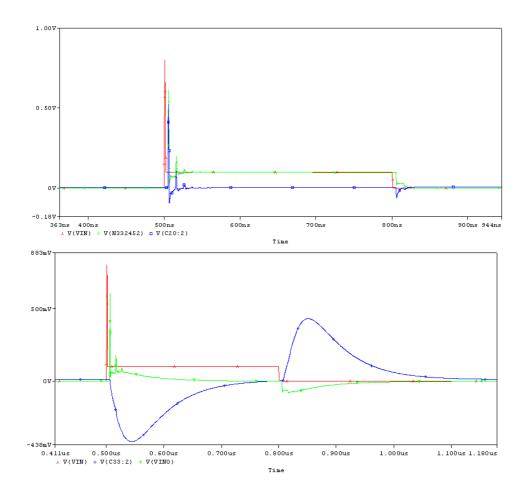

| 5.7  | Analog signals for the DBO-STEP5 simulation                            | . 72  |

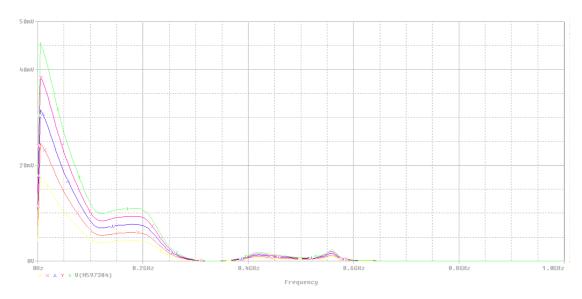

| 5.8  | Fourier analysis of the analog signals in the STEP5 simulation $\dots$ | . 73  |

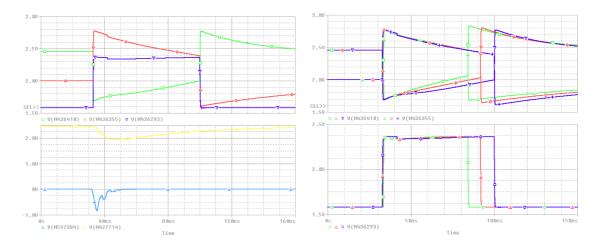

| 5.9  | All signals of the DBO-STEP5 simulation                                | . 74  |

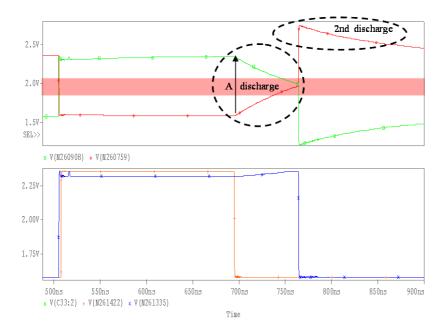

| 5.10 | Digital and $\overline{LE}$ signals of the DBO-STEP5 simulation        |       |

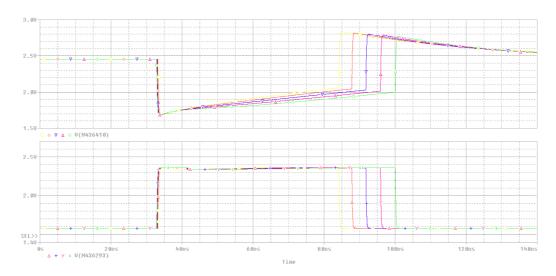

|      | Test signals simulation of the DBO-STEP5 design                        |       |

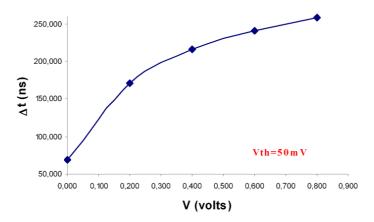

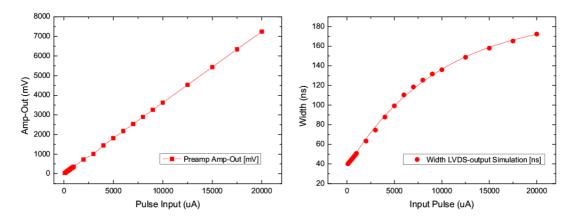

| 5.12 | DBO-STEP5 Q-ToT curve for test signals (normal avalanches)             | . 76  |

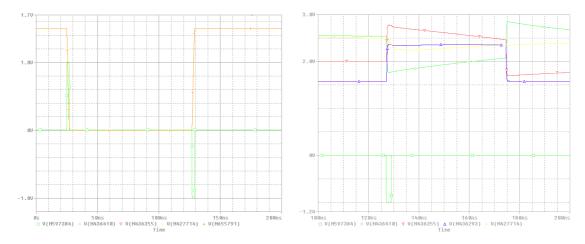

|      | DBO-STEP5 simulation results for big avalanches and streamers          |       |

| 5.14 | DBO-STEP5 Q-ToT curve for test signals (including streamers)           | . 77  |

| 6.1  | Positioning of the FEE-STEP3 and STEP4 in the gas box                  | . 80  |

| 6.2  | FEE-STEP3 and STEP4 DaughterBOards pictures                            |       |

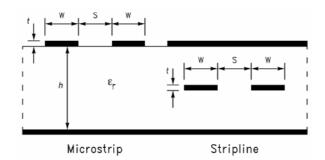

| 6.3  | Impedance matching for the PCB paths                                   |       |

| 6.4  | FEE-STEP3 DBO block diagram                                            | . 83  |

| 6.5  | MBOv1 picture                                                          | . 84  |

| 6.6  | MBOv1 block diagram                                                    |       |

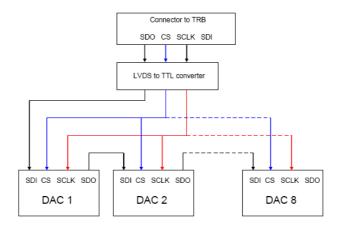

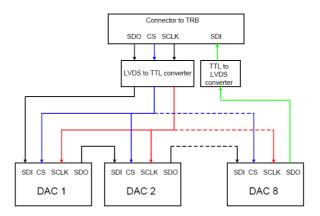

| 6.7  | Diagram block of the DAC configuration                                 |       |

| 6.8  | TRBv1 picture and block diagram                                        |       |

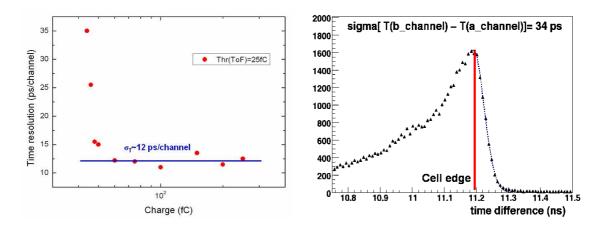

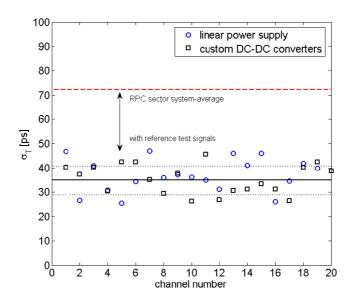

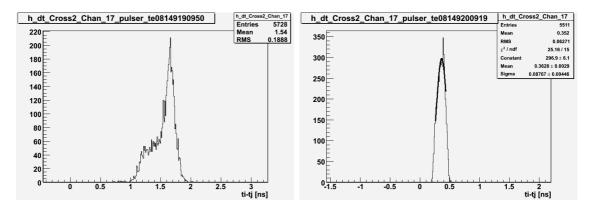

| 6.9  | FEE-STEP3 time resolution per channel with test signals                |       |

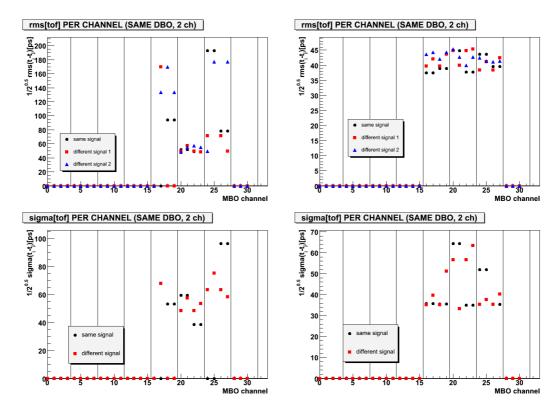

| 6.10 | FEE-STEP3 time resolution with RPC signals                             |       |

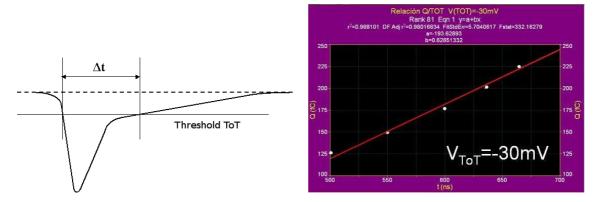

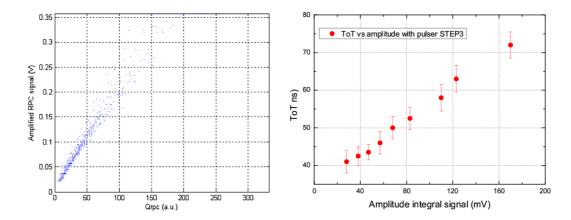

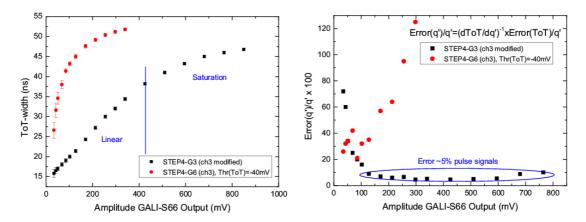

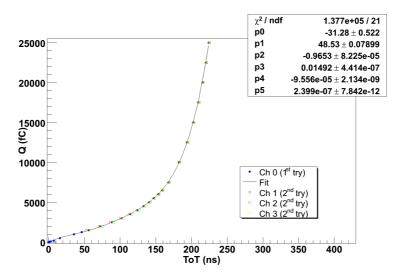

|      | FEE-STEP3 ToT-charge correlation with test signals                     |       |

|      | FEE-STEP3 ToT-charge correlation with RPC signals                      |       |

|      | Experimental setup for the Nov05 beam time                             |       |

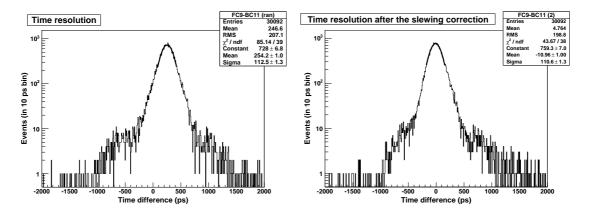

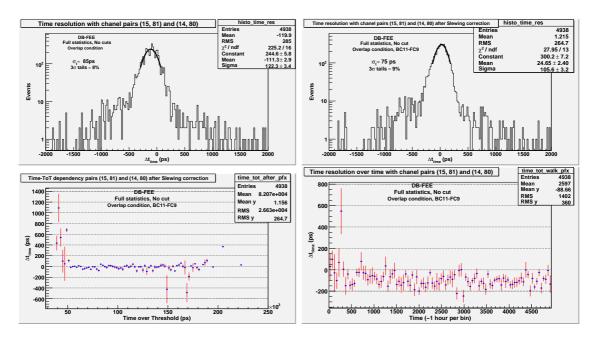

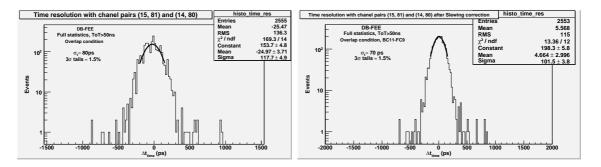

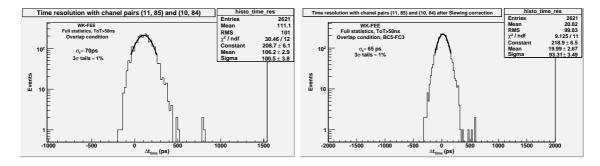

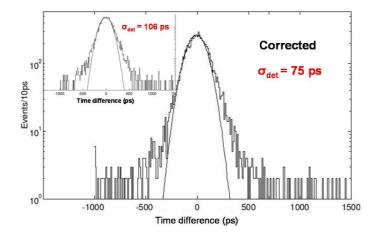

|      | Time resolution measured for the whole chain in beam                   |       |

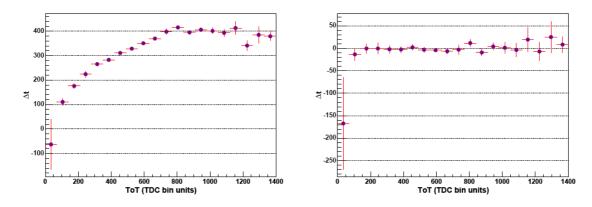

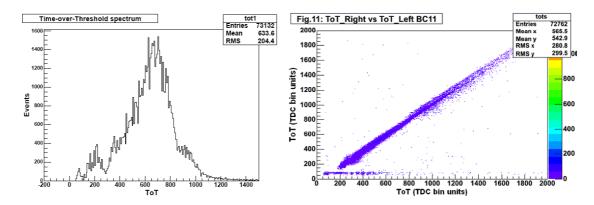

|      | $\Delta t$ vs ToT before and after slewing correction                  |       |

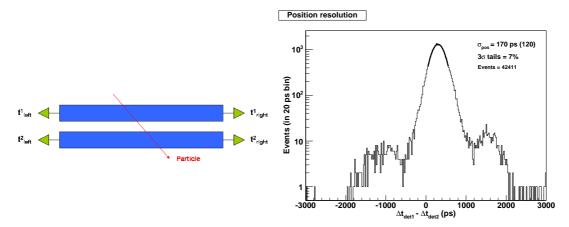

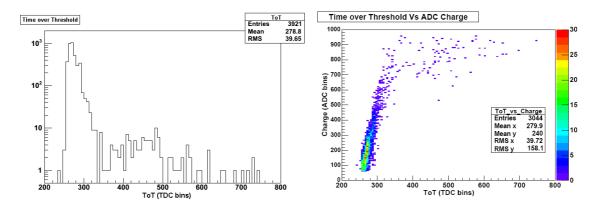

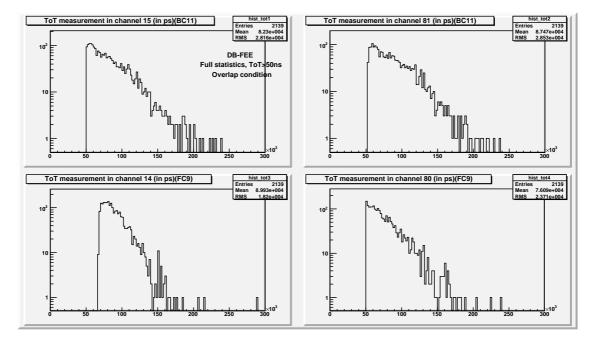

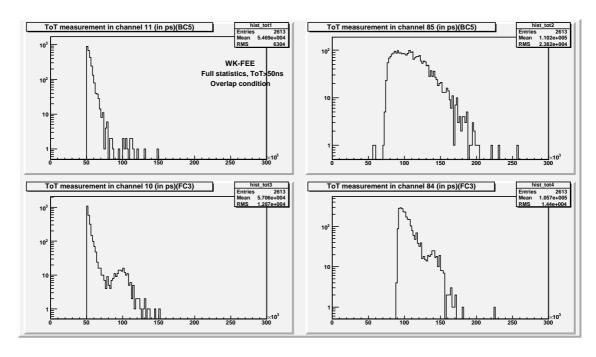

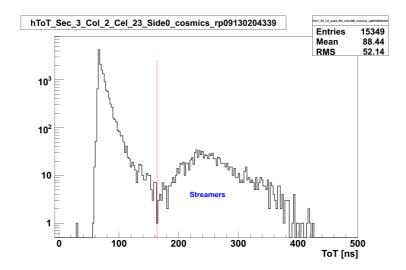

|      | ToT spectrum of one cell                                               |       |

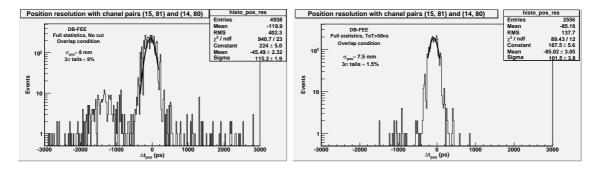

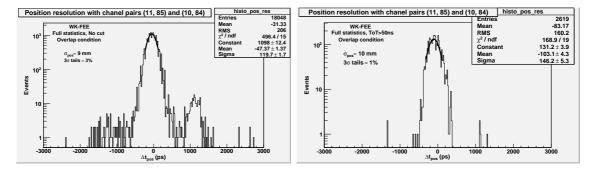

|      | Position resolution measured for the whole chain                       |       |

|      | ToT vs amplitude with test signals for a modified STEP4 channel .      |       |

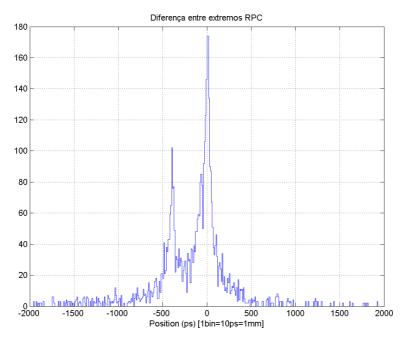

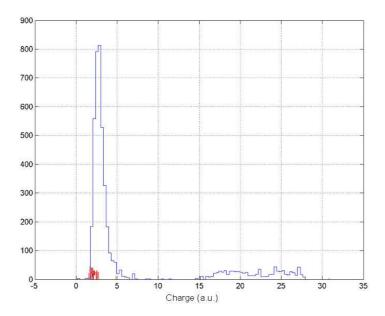

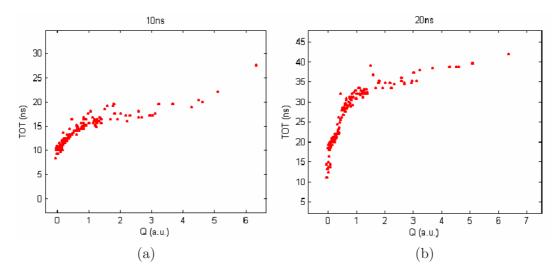

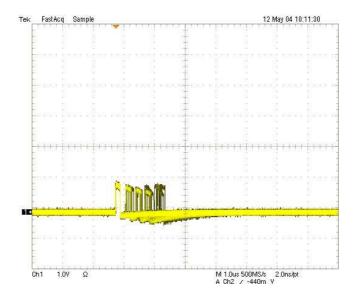

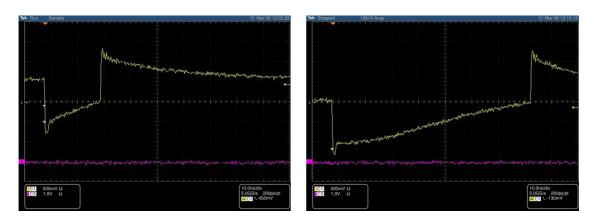

|      | $\overline{LE}$ behaviour for different thresholds                     |       |

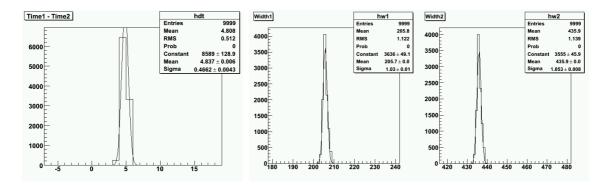

|      | Time resolution of the whole chain with test signals                   |       |

| 6.21 | ToT vs charge with cosmic rays                                         | . 108 |

| 7 1  | DBO-STEP5 pictures                                                     | 110   |

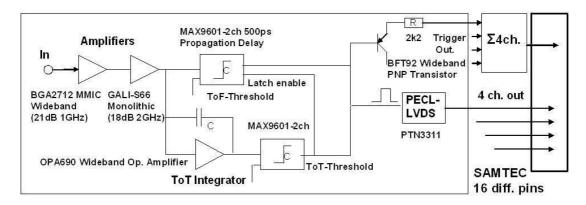

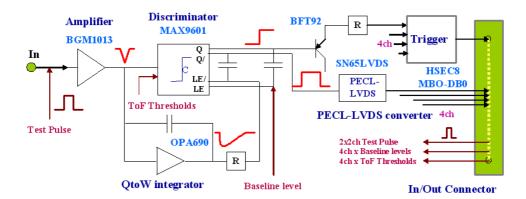

| 7.2  | Block diagram of the DBO-STEP5                                        | . 111 |

|------|-----------------------------------------------------------------------|-------|

| 7.3  | MBOv2 picture                                                         |       |

| 7.4  | Block diagram of the DAC configuration of the MBOv2                   | . 114 |

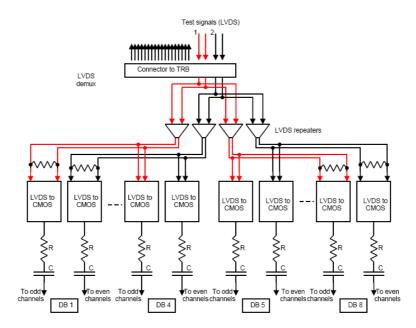

| 7.5  | Test signal distribution of the MBOv2                                 |       |

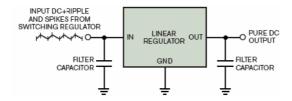

| 7.6  | Filter capacitors in the voltage regulators                           | . 117 |

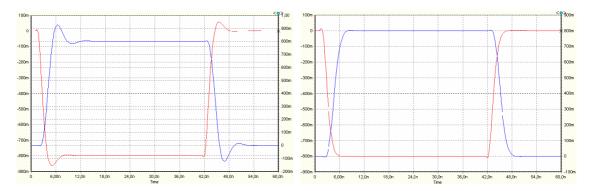

| 7.7  | Trigger signals provided by the MBOv2                                 | . 118 |

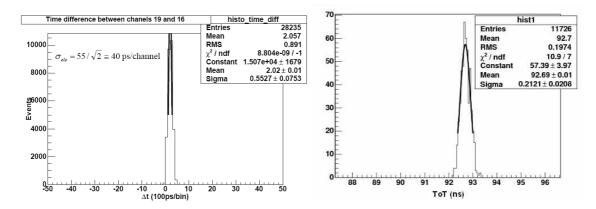

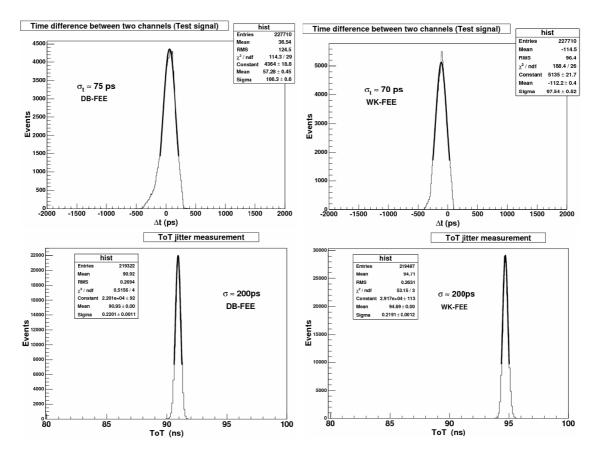

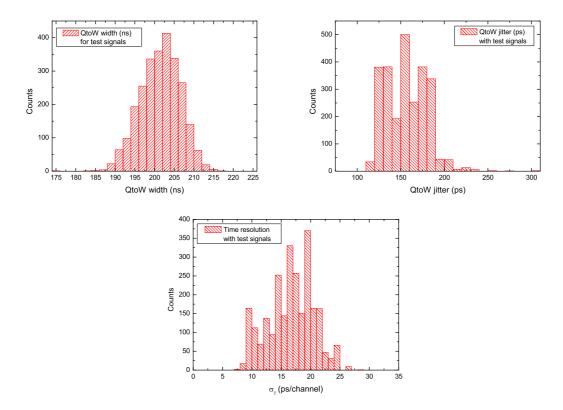

| 7.8  | Test signals analysis: time resolution and QtoW jitter                | . 120 |

| 7.9  | Test signals analysis: time resolution and QtoW jitter with the DBO   |       |

|      | connected to the RPC                                                  | . 121 |

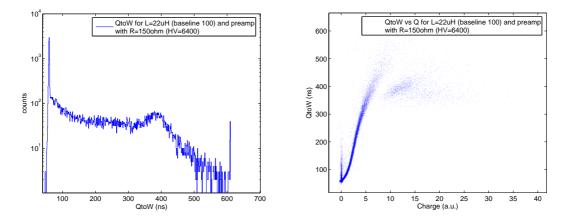

| 7.10 | QtoW spectrum measured with STEP5.1 boards                            | 122   |

| 7.11 | QtoW behaviour at both sides of the cell using STEP5.1 boards $$ . $$ | 122   |

| 7.12 | Time resolution of the whole system using DBOs-STEP5.1                | 123   |

| 7.13 | Time resolution cut for QtoW $>$ 50 ns using STEP5.1 boards           | . 124 |

| 7.14 | QtoW spectrum cut for QtoW>50 ns using STEP5.1 boards                 | . 124 |

| 7.15 | Position resolution with and without QtoW cut using the STEP5.1       | 125   |

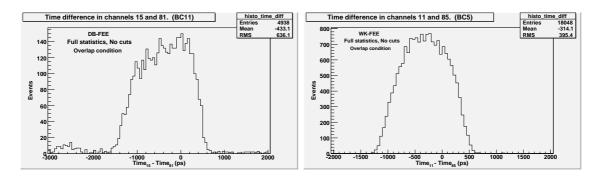

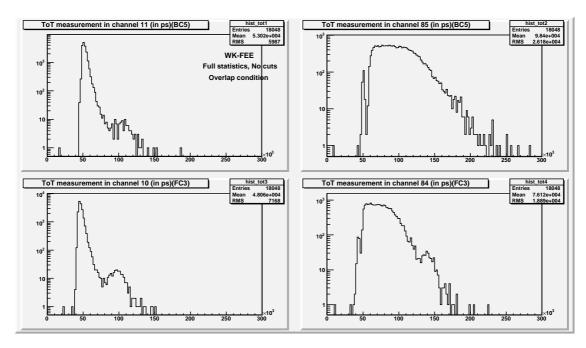

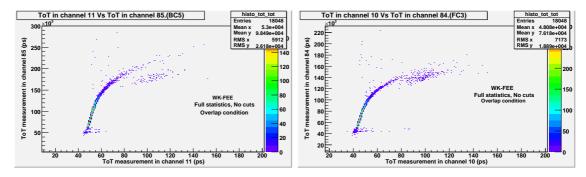

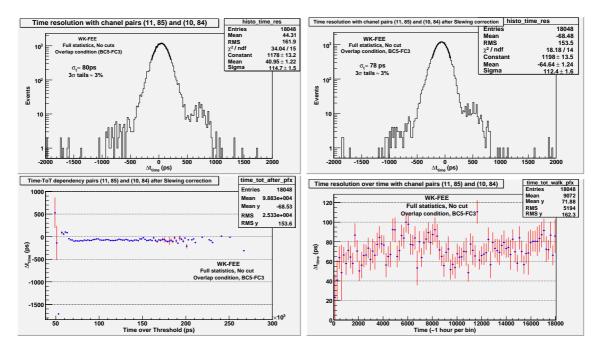

| 7.16 | Time difference of the BC11 and BC5 cells with both FEE designs .     | 125   |

| 7.17 | QtoW spectrum with DBOs-STEP5.2                                       | 126   |

| 7.18 | QtoW behaviour at both sides of the cell using DBOs-STEP<br>5.2 $$    | 126   |

| 7.19 | Time resolution of the whole system using STEP5.2 boards              | . 127 |

| 7.20 | Time resolution cut for QtoW>50 ns using STEP5.2 boards               | . 127 |

| 7.21 | QtoW spectrum using DBOs-STEP5.2                                      | . 128 |

| 7.22 | Position resolution with and without QtoW cut using the STEP5.2       | 128   |

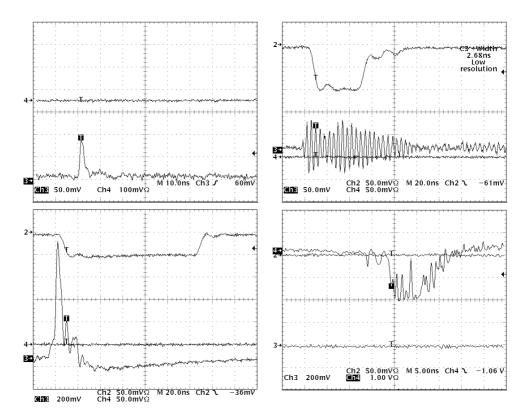

| 7.23 | Some signals examples                                                 | . 129 |

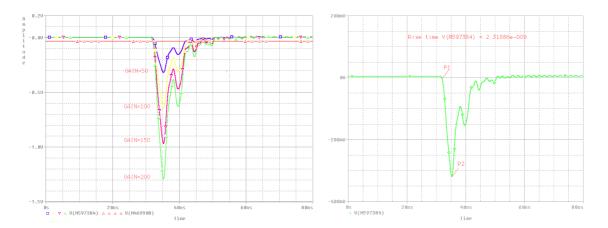

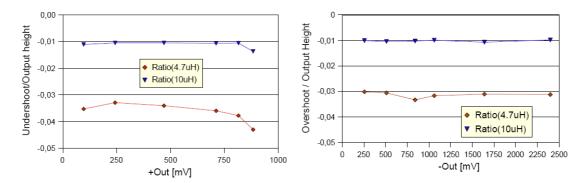

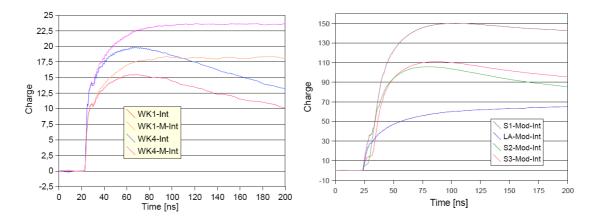

| 7.24 | Time evolution of the simulated charge at the amplifier output $$     | 131   |

| 7.25 | Overshoot/undershoot of the amplifier output for different settings . | 132   |

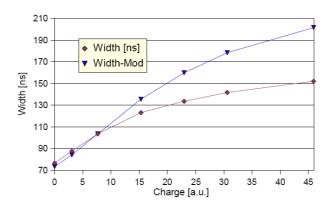

|      | Time evolution of the simulated charge with a larger inductor         |       |

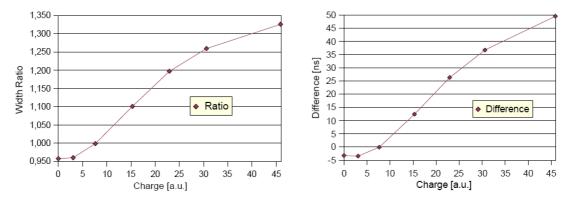

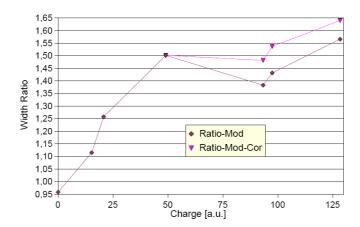

| 7.27 | Width as function of the charge                                       | 134   |

| 7.28 | Difference in the width between original and modified settings        | 134   |

| 7.29 | Width ratio as function of the charge between original and modified   |       |

|      | 0                                                                     | . 135 |

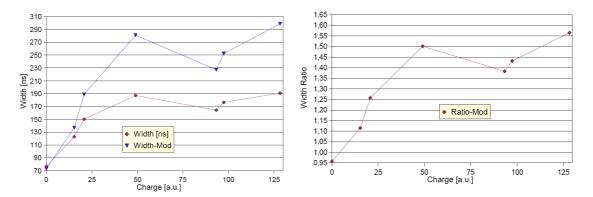

| 7.30 | Examples of streamers signals                                         | 135   |

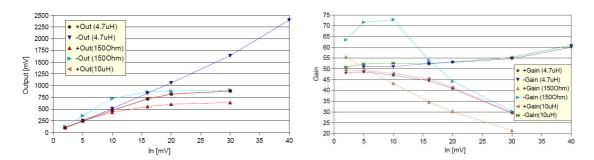

|      | Amplifier/Gain output as function of the input for different cases .  | 136   |

| 7.32 | Width ratio as function of the charge between streamers for modified  |       |

|      | settings and negative signals                                         |       |

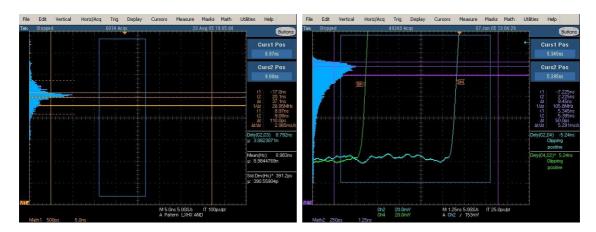

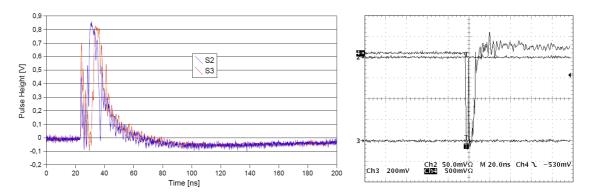

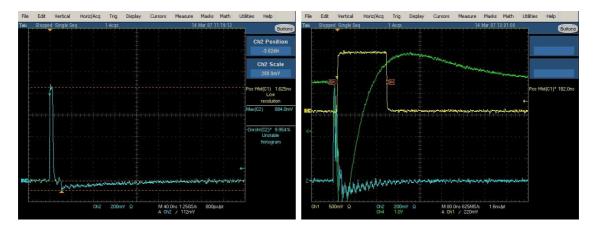

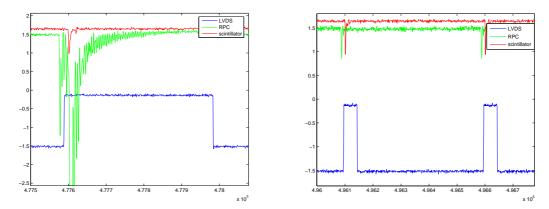

|      | Examples of signals of the DBO-STEP5                                  |       |

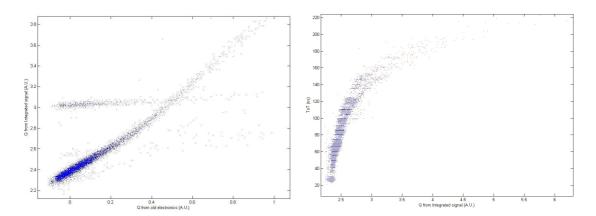

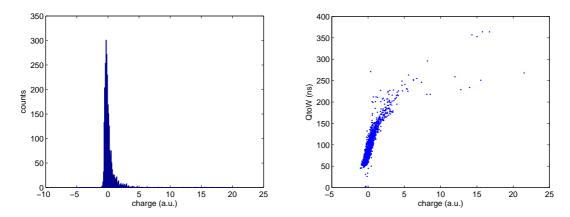

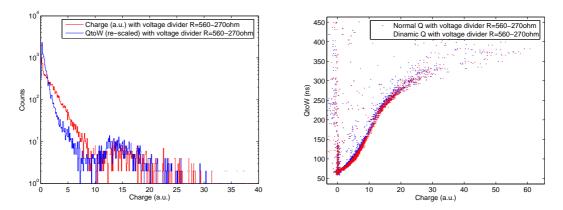

|      | QtoW behaviour using DBO-STEP5                                        |       |

|      | Examples of signals of a modified DBO-STEP5                           |       |

|      | QtoW behaviour using a modified DBO-STEP5 channel                     |       |

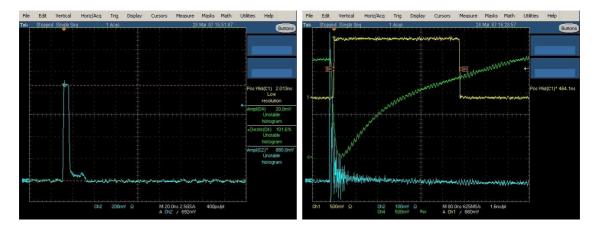

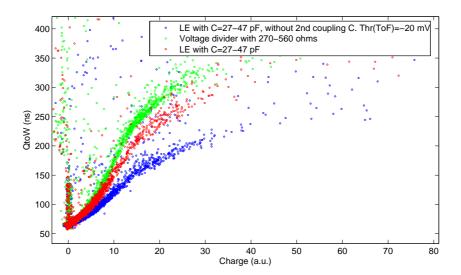

|      | QtoW behaviour in beam environment                                    |       |

|      | QtoW behaviour with a voltage divider using a $^{22}Na$ source        |       |

|      | QtoW behaviour as function of the charge for different cases          |       |

|      | QtoW spectrum and as function of the charge for LE changes            |       |

| 7.41 | Time resolution corrected both with O and OtoW information            | 144   |

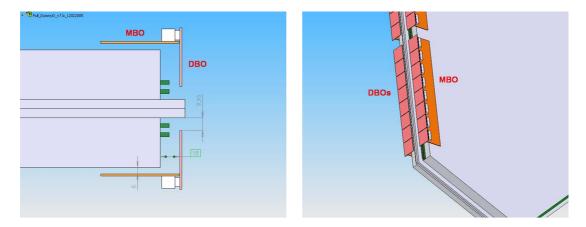

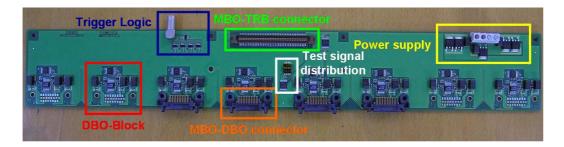

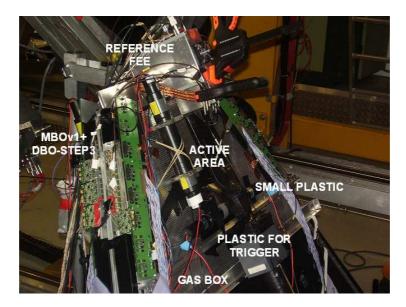

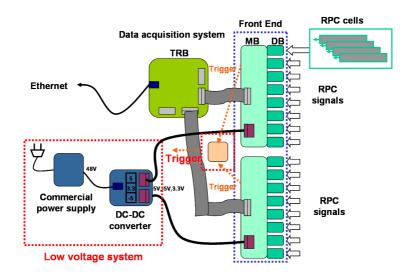

| 7.42 | Block diagram of the first RPC sector installed in HADES                                 | . 145 |

|------|------------------------------------------------------------------------------------------|-------|

|      | Picture of the TRBv2 board                                                               |       |

| 7.44 | Experimental setup of the first RPC sector installed in HADES                            | . 148 |

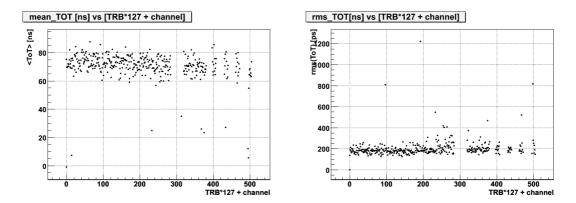

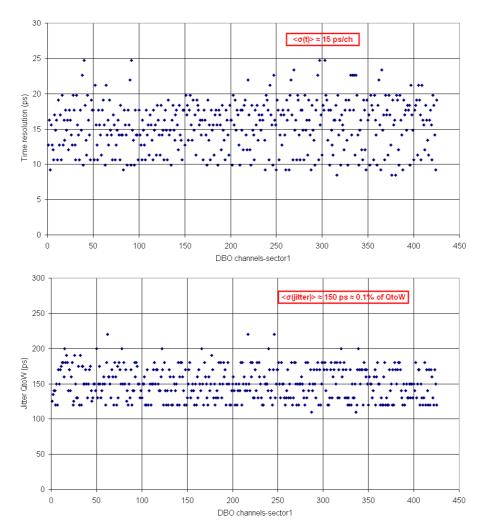

| 7.45 | Time resolution of the FEE+DAQ chain                                                     | . 150 |

| 7.46 | Time resolution per channel for the whole system                                         | . 151 |

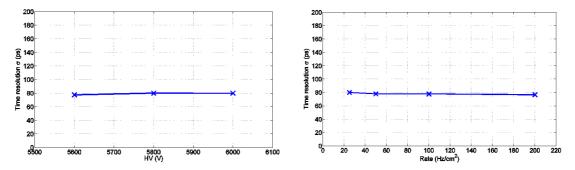

|      | Time resolution as function of the rate and the HV                                       |       |

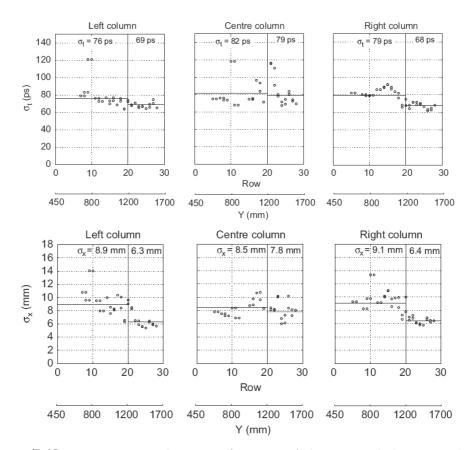

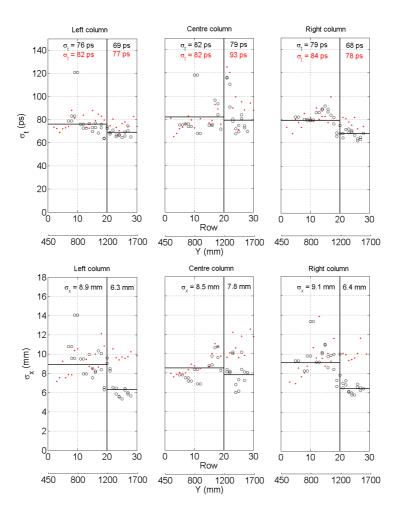

|      | Time/position resolution as function of the row and Y-coordinate .                       |       |

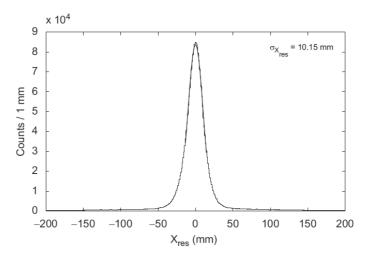

|      | Position resolution during the first installation in HADES                               |       |

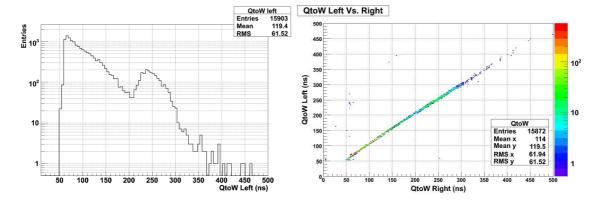

|      | QtoW behaviour during the first installation in HADES                                    |       |

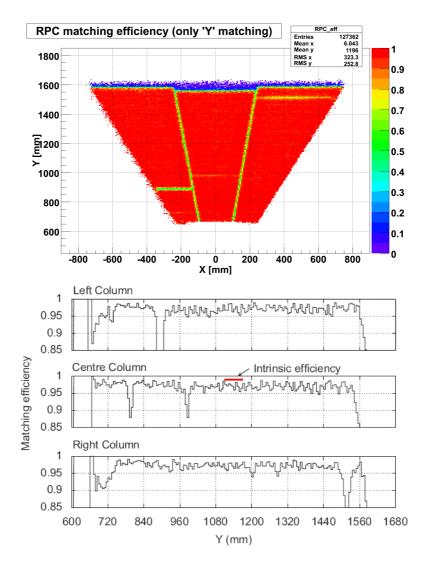

|      | 2D and 1D matching efficiency of the RPC sector                                          |       |

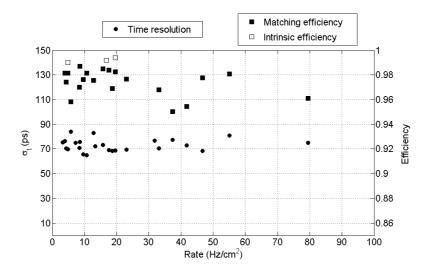

|      | Time resolution and efficiency as function of the rate                                   |       |

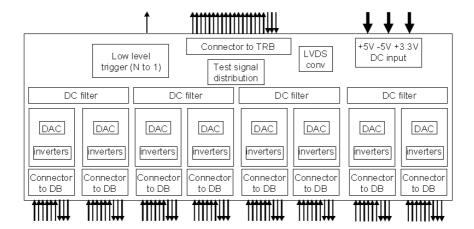

| 8.1  | Block diagram of the system FEE+DAQ                                                      | . 158 |

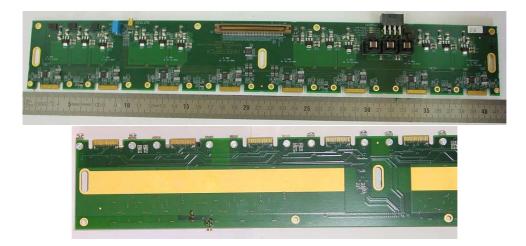

| 8.2  | Picture of the final version of the DBO                                                  | . 159 |

| 8.3  | Block diagram of the final version of the DBO                                            | . 160 |

| 8.4  | Picture of the final version of the MBO                                                  | . 161 |

| 8.5  | Time1-time2 at both sides of the RPC cell                                                | . 162 |

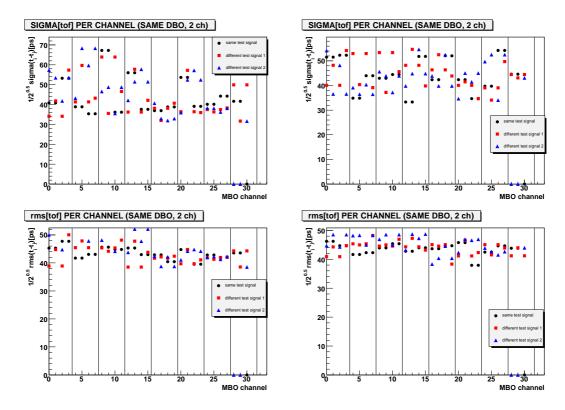

| 8.6  | $\sigma_T$ and $\mathrm{rms}_T$ before and after remove the resistor in the test input . | . 163 |

| 8.7  | QtoW mean and rms with test signal for 4 TRBs                                            | . 164 |

| 8.8  | QtoW behaviour in the cosmic rays run of Jun08                                           | . 164 |

| 8.9  | Cosmic rays incidence                                                                    | . 165 |

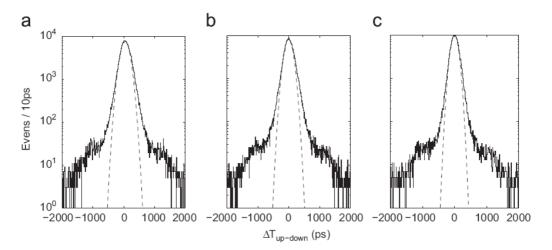

| 8.10 | Time and position resolution in the cosmic rays run of Jun08                             | . 166 |

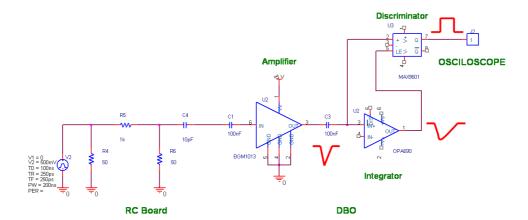

| 8.11 | RC board schematic used for the QtoW calibration                                         | . 167 |

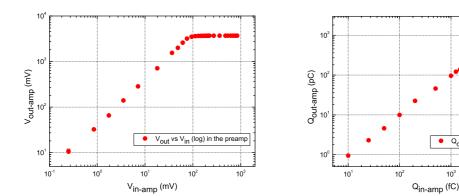

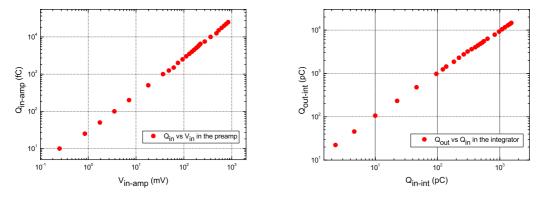

| 8.12 | $V_{out}$ vs $V_{in}$ and $Q_{out}$ vs $Q_{in}$ for the amplifier with pulser            | . 168 |

| 8.13 | $Q_{out}$ vs $Q_{in}$ for the integrator with pulser                                     | . 169 |

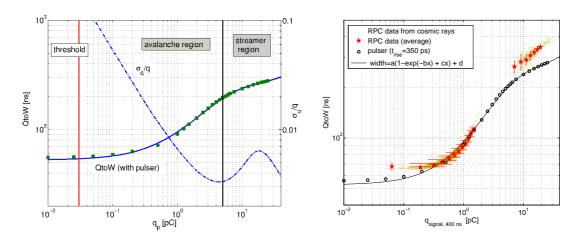

|      | QtoW and $\sigma_q/q$ as function of the Q with pulser and cosmic rays .                 |       |

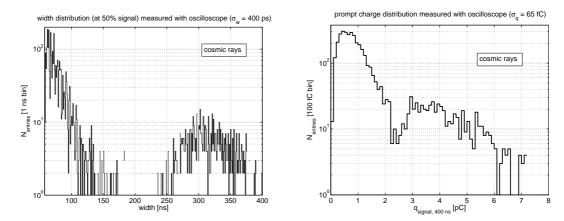

| 8.15 | QtoW and Q spectrums with cosmic rays to calibrate the QtoW                              | . 171 |

| 8.16 | Examples of streamers and normal avalanches                                              | . 171 |

| 8.17 | Q=f(QtoW) calibration done with pulser for four channels                                 | . 172 |

| 8.18 | Measurements of parameters of the final version of the FEE                               | . 174 |

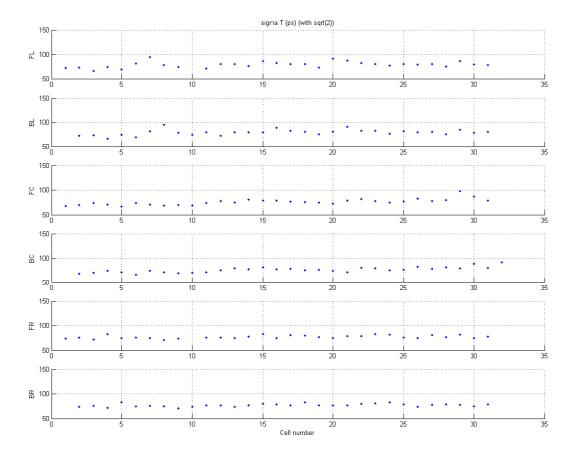

| 8.19 | $\sigma_T$ and rms <sub>T</sub> of the FEE for different temperatures                    | . 177 |

| 8.20 | Experimental setup of the RPC wall commissioning                                         | . 178 |

| 8.21 | Time resolution of all the cells of one RPC sector                                       | . 179 |

| 8.22 | QtoW spectrum with cosmic rays                                                           | . 180 |

|      | FEE-STEP1 layout                                                                         |       |

| A.2  | FEE-STEP1 schematic                                                                      | . 184 |

| A.3  | FEE-STEP2 layout                                                                         | . 185 |

| A.4  | FEE-STEP2 schematics: voltage regulation and analog step                                 | . 186 |

| A.5  | FEE-STEP2 schematics: digital step                                                       | . 187 |

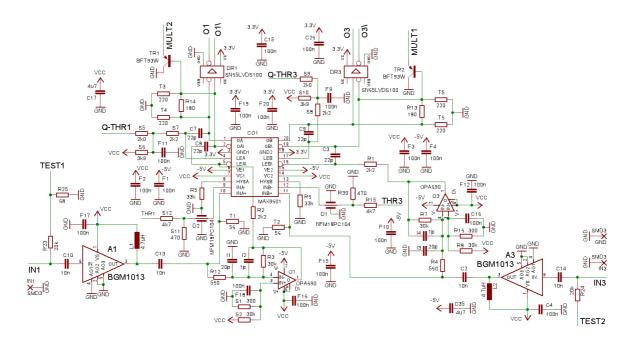

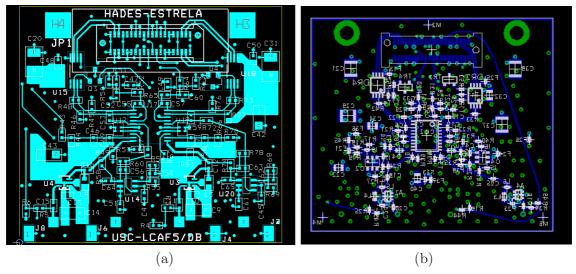

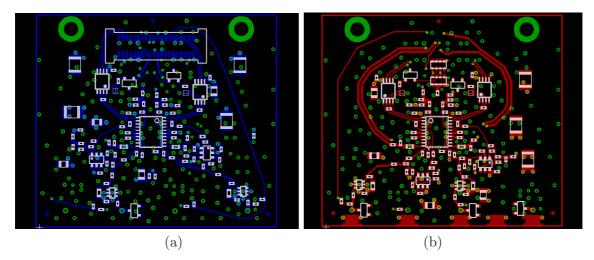

| В.1  | DBO-STEP3 layout                                                                         |       |

|      | DBO-STEP3 schematic: analog part                                                         |       |

| B 3  | DBO-STEP3 schematic: digital part                                                        | 191   |

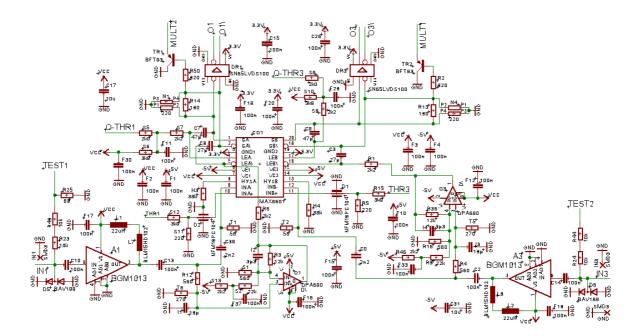

| B.4  | DBO-STEP5 schematic                                                      |

|------|--------------------------------------------------------------------------|

| B.5  | Both DBO-STEP5 layouts                                                   |

| B.6  | Schematic of the final design of the DBO                                 |

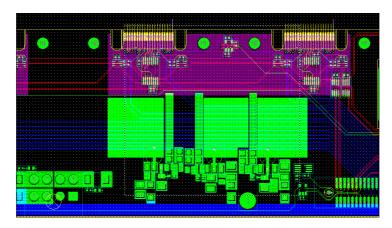

| B.7  | Layout of the final version of the DBO                                   |

| B.8  | MBOv2 layout details                                                     |

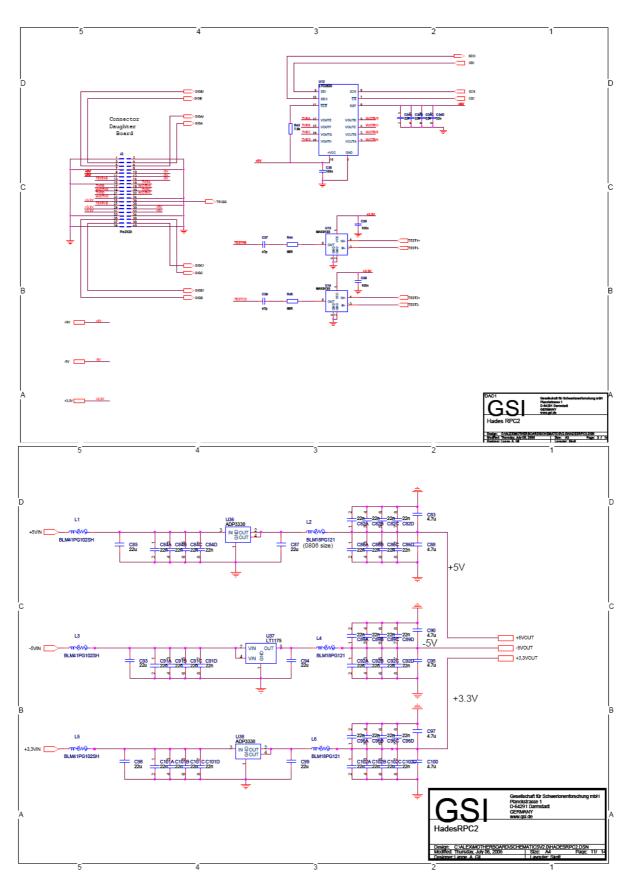

| B.9  | MBOv2 schematics: input block and voltage supply 195                     |

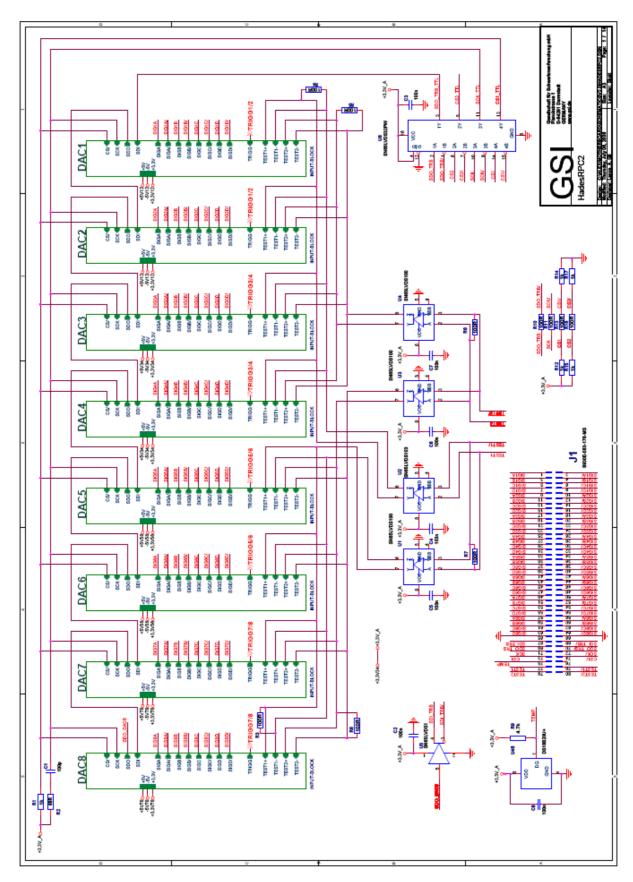

|      | MBOv2 schematic: DAC configuration                                       |

| B.11 | Connection between MBOv2 and DBO-STEP5                                   |

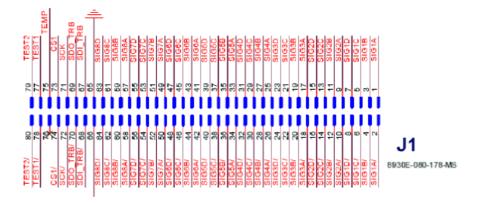

| B.12 | MBOv2-TRB pin-out connector                                              |

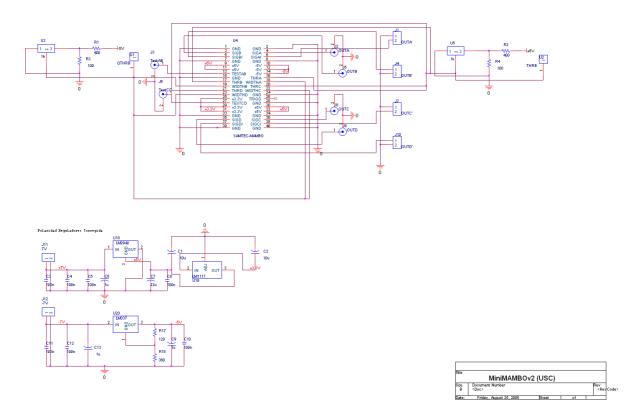

| B.13 | miniMBO schematic                                                        |

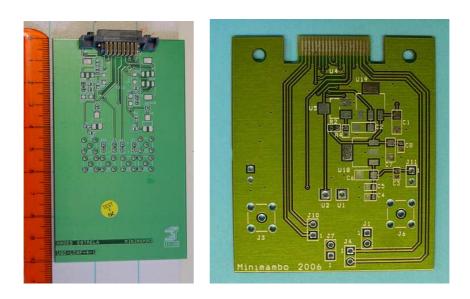

| B.14 | Pictures of both miniMBOs                                                |

| C.1  | Celdas RPC do muro de tempo de voo de HADES 200                          |

| C.2  | Electrónica montada en 2 sectores durante o commissioning 201            |

| C.3  | Fotos da adaptación da electrónica do LIP e da versión final $\dots 202$ |

| C.4  | Resolución temporal e jitter na medida da carga da electrónica 203       |

| C.5  | Resolución temporal FEE+RPC con correccións                              |

| C.6  | Espectro do algoritmo QtoW para unha celda con rayos cósmicos 205        |

# List of Tables

| 2.1                      | Light vector mesons life times                                                                            |

|--------------------------|-----------------------------------------------------------------------------------------------------------|

| 3.1<br>3.2               | Comparison between the FEE of different timing RPC walls 23 Comparison between different timing RPC walls |

| 6.1<br>6.2<br>6.3<br>6.4 | Comparison between LVDS and LVPECL                                                                        |

| 7.1<br>7.2               | Pin-out connector between MBOv2 and DBO-STEP5                                                             |

| 8.1<br>8.2               | Different parameters range measured for the validation of the final version of the FEE                    |

| 9.1                      | Main features of the FEE final version                                                                    |

# Chapter 1

#### Introduction

Modern experiments in Particle and Nuclear Physics are characterized by their complexity. In order to resolve the very small scales that are typical in these fields, very huge and sophisticated equipments are necessary: high energy and high luminosity accelerators, big spectrometers, high resolution and high efficiency detectors together with several analog and digital electronic devices as well as fast and powerful computing equipments. Sometimes the support often requires setting up worldwide initiatives.

The central elements in such structure are the particle detectors. Presently, most detectors used in Particle Physics experiments belong to the family of electronic detectors. Particles going through them start some kind of ionization, excitation or pair-hole creation processes that induce electric pulses which are at the origin of the measurement of its properties: position, trajectory, time of flight, energy, velocity, etcetera.

The Front-End Electronics, FEE, is the first element of a detector to handle the electrically created pulse, and to drive it to the data acquisition system. Normally, its task is to preamplify the electric pulse, while keeping its main characteristics, before entering the amplifying and digitizing electronics. Sometimes, the digitization takes place at the FEE allowing for easy transport of many signals through twisted pair flat cables, several meters away from the detector down to the acquisition system. This is the case of the FEE developed for the new timing RPC wall that is being installed in the HADES experiment, at the GSI Helmholtzentrum in Darmstadt, Germany.

HADES (High Acceptance Di-lEpton Spectrometer) is a new generation spectrometer, designed for analyzing the properties of the vector mesons produced in heavy ion collisions in the range of 1-2 A.GeV. There are theoretical arguments predicting the modification of the properties of the matter at that energies as a consequence of the partial restoration of the Chiral Symmetry. Leptons are not affected by the strong interaction with the dense nuclear matter produced in the

2 Introduction

collision, making the  $e^+e^-$  decay channels of the vector mesons the best the best place to test that predictions. As the dilepton decay chain is highly suppressed (depending on the vector meson, only one in around  $10^4$ - $10^6$  decays follows that channel), a high acceptance and high resolution spectrometer of new generation was built at the GSI for that purpose. The HADES construction started in the middle of the nineties and, some years ago, an upgrade was approved in order to provide the spectrometer with a new high resolution timing detector for trigger and lepton identification purposes. This detector, based on the timing RPCs (Resistive Plate Chambers) technology, has been developed and built in the framework of a collaboration between the LabCAF of the USC, the LIP of Coimbra, the GSI and the IFIC of Valencia.

RPCs were chosen for the timing wall of HADES due to the competitive performances they offer at an affordable price to cover big surfaces. The development of RPCs was consolidated in 1981, when gaseous detectors under parallel geometries were operated at atmospheric pressure and at very high electric fields, providing a very fast narrow time response. This first RPC achieved very promising performances, reaching a 97% efficiency and a time resolution at the level of 1 ns, becoming a low price alternative to the plastic scintillators. In 2000, the importance of the mechanical uniformity of the gap in relation with high precision timing together with the development of fast amplification electronics, made it possible to operate a multi-gap RPC in avalanche mode with thin gaps of 0.3 mm (the timing RPCs or tRPCs), improving the time resolutions up to 50 ps. With time resolutions below 100 ps, the tRPCs found new applications in Nuclear and Particle Physics experiments in the field of particle identification (PID).

The readout preamplifying FEE plays a very important role for achieving the high time resolution that the tRPCs offer. The small gaps implemented in the timing RPCs, together with small charges of their signals, demand a high gain and bandwidth readout electronics in order to the best time resolutions. The fast signals produced in the detector are characterized by rise times at the level of  $\sim 300$  ps, requiring amplifying electronics with a bandwidth over 1 GHz.

The work presented in this memory describes the simulation, design, development, testing, manufacturing, installation and commissioning work of the FEE of the HADES tRPC wall. It covers all the steps starting from an obsolete but high performance 1-channel 2-boards design done at LIP Coimbra, up to a 4-channels, low consuming and compact design based on a motherboard-daughterboard philosophy. The amplifying and digitizing board provides both time and charge measurements codified in the LVDS output signal. The charge is measured through the 'Charge to Width' algorithm (QtoW). Almost 3000 channels have been built in order to instrument the six sectors (plus one spare) needed to cover the 8 m<sup>2</sup> of the small angle region of HADES.

Introduction 3

The readout electronics was developed in collaboration with the CIEMAT of Madrid and the GSI of Darmstadt as a part of a more general project involving also the development at the GSI of the associated data acquisition board based on CERN's HPTDC circuits. FEE have been already installed and tested.

The main requirements the FEE of the HADES tRPC wall was asked to fulfill before undertaking the project were:

- A large bandwidth to deal with very narrow RPC pulses.

- Both precise timing and charge information in a single LVDS digital output signal through the 'Charge to Width' algorithm (QtoW).

- A multiplicity output to provide this information to the HADES trigger logic.

- Stability and a compact design for a moderate power consumption.

The HADES spectrometer and the design of its tRPC wall are presented in chapter 2 and chapter 3. The FEE is introduced in chapter 4 where first steps are also included. A simulation developed for the motherboard-daughterboard configuration can be found in chapter 5. Taking into account this simulation, chapter 6 is devoted to the improvement of the design and to the analysis of the performances of the board, together with a detailed analysis of the data of the first beam time test done at GSI during November 2005 using one of the final RPC prototypes.

Chapters 7 and 8 are devoted to explaining the last designs of the electronics and the analysis of their performances, respectively, together with other some small tests. The results of a detailed analysis of a beam time test done at GSI in October 2007 with a full equipped RPC sector, with 1116 cells and 2232 FEE channels, placed at its nominal position in the HADES spectrometer, are presented in chapter 7. The commissioning of the whole project and the final installation are included in chapter 8.

The final chapter is devoted to the conclusions and a summary of the work done to achieve the final design and the performances reached. Some technical details of the readout electronics, including the schematics and layouts of the different FEE steps, are included in the Appendix sections.

# Chapter 2

# The HADES experiment

#### 2.1 Introduction

The investigation of nuclear at high temperature and high density is one of the major research topics in modern Nuclear Physics. Nucleus-nucleus collisions at relativistic energies offer the unique possibility to create such highly excited nuclear matter in the laboratory [1], [2]. These investigations are essential to understand processes like the birth of the Universe in the Big Bang and its later evolution. This line of investigation contributes also to obtain the equation of state of nuclear matter which is not only important in Nuclear Physics, but also to understand physical processes taking place during the latest stages of stars evolution.

The work presented here has been done in the framework of the international HADES¹ Collaboration, composed of 19 institutions from 9 European countries and with almost two hundred scientists. The High Acceptance Di-Electron Spectrometer (HADES) is the name of the full detector system, consisting on several instruments working together in one spectrometer, and it is placed at the GSI² institute in Darmstadt, Germany, together with the required particle accelerator. HADES is focused to study of in medium modifications to the properties of the vector mesons. Calculations based on QCD (Quantum Chromo Dynamics) and some hadronic models, predict detectable changes in the width and mass of hadrons produced in dense nuclear medium. From the point of view of QCD such modifications could be a signal of the so called *chiral symmetry restoration*. The main goal of HADES is to provide experimental insight for the study of QCD on the non disturbed regime and possibly see a signal of the expected chiral symmetry restoration.

A new timing RPC<sup>3</sup> detector wall was proposed for HADES by LabCAF-USC and LIP-Coimbra to improve the ToF and high level trigger performances at small angles. It is presented in Chapter 3, together with its physics. The electronics developed for this RPC wall and some results are presented along this work.

<sup>&</sup>lt;sup>1</sup>High Acceptance Di-Electron Spectrometer.

<sup>&</sup>lt;sup>2</sup>GSI Helmholtzzentrum für SchwerIonenforschung GmbH.

<sup>&</sup>lt;sup>3</sup>Resistive Plate Chambers.

#### 2.2 The HADES physics

HADES is a unique apparatus assembled at the heavy ion synchrotron SIS at GSI Darmstadt. The main part of the HADES physics program is focused on studies of in-medium properties of the light vector mesons  $\rho$  (770 MeV/c<sup>2</sup>),  $\omega$  (783 MeV/c<sup>2</sup>) and  $\phi$  (1020 MeV/c<sup>2</sup>) [3], [4]. The spectrometer is also able to detect and study the properties of hadrons and this is an important task.

Significant changes of the vector meson spectral functions in hot and/or dense nuclear matter have been predicted by various models. The meson spectral functions inside nuclear matter are directly accessible via a measurement of the dielectron invariant mass distributions of the two-body meson decays because  $e^+e^-$  pairs do not suffer from a strong electron-hadron final state interaction. A low mass dielectron excess observed in heavy ion collisions by the CERES experiment on SPS at CERN [5] launched an exciting dispute about its origin. According to QCD inspired models, this excess can be considered as a signal of the partial chiral symmetry restoration in dense and hot nuclear matter. On the other hand, various hadronic models explains this enhancement by significant in-medium modifications of the  $\rho$  meson spectral function due to strong meson couplings to low lying nucleon resonances [6].

At SIS, energy domain dielectron invariant mass distributions were measured in proton-proton and light and heavy ion reactions by the DLS collaboration at the BEVALAC [7], [8]. Within the given experimental errors bar, the extracted  $e^+e^-$  production rate in p-p reactions could be reasonable reproduced by theoretical calculations assuming free dielectron decays of various hadronic sources [9]. For the heavy collisions Ca+Ca and C+C, a remarkable excess of the dielectron yield in the low mass range 200 MeV/ $c^2 < M_{inv} < 600$  MeV/ $c^2$  as compared to the theoretical calculations was found. This dielectron excess could not be explained neither by hadronic models based on the in-medium modified  $\rho$  meson spectral functions nor by the Brown-Rho scaling [10].

In order to study the high density phase, light vector mesons are a well suited probe. Their lifetimes (see Table 2.1) are short enough for them to have a significant chance of decaying in the same dense medium where they were created. When they decay, they may do so in two leptons. Since leptons do not experiment strong interaction, when they leave the interactions zone they retain memory about how they were produced. Hence they carry information about the properties of the mesons in the dense medium. If their masses or widths have changed due to a partial restoration of chiral symmetry we should be able to observe it by looking at the lepton pairs' invariant masses. Predominant dilepton sources for  $m(e^+e^-)>600 \text{ MeV/c}^2$  are direct or Dalitz decays of the light mesons  $\rho$ ,  $\omega$  and  $\phi$  produced in these collisions.

The main problem is the low branching ratio for the dilepton channel in the vector meson decays. This needs to be compensated with high statistics and a powerful trigger scheme, which translates into a need of a high acceptance spectrometer and high beam intensities. Another problem is the presence of several background

| Meson | Mass                           | Width                          | $c\tau$ (fm) | Dominant channel        | $e^+e^-$              |

|-------|--------------------------------|--------------------------------|--------------|-------------------------|-----------------------|

|       | $\left(\frac{MeV}{c^2}\right)$ | $\left(\frac{MeV}{c^2}\right)$ |              |                         | branching ratio       |

| ρ     | 775.8                          | 150                            | 1.3          | $\pi\pi$                | $4.67 \times 10^{-5}$ |

| ω     | 782.6                          | 8.49                           | 23.4         | $\pi^{+}\pi^{-}\pi^{0}$ | $7.14 \times 10^{-5}$ |

| φ     | 1019.5                         | 4.26                           | 44.4         | $K^+K^-$                | $2.98 \times 10^{-4}$ |

Table 2.1: Life vector mesons life times [11].

sources, like pion Dalitz decays, which also produce leptons and lepton pairs, so that the vector meson signal is sitting on a continuous background.

Vector mesons are hadrons composed by a quark and an anti-quark.  $\rho$ ,  $\omega$  and  $\phi$  mesons have different properties concerning lifetimes, widths or lepton pair branching ratios. It seems that  $\rho$  meson is the more suitable to be used as a probe since it has a large chance of decaying in the dense zone but, nevertheless, all of them contribute and will be studied.

The HADES experiment [4], described below, aims at systematic studies of dielectron production in proton, pion and heavy ion induced reactions. Although beam energies available at the GSI/SIS facility are limited to the kinematic region near the vector meson production threshold, this domain is interesting for confirming the unexplained DLS results as well as for the understanding of vector-meson hadronic couplings involved in the interpretation of the CERES data. The experiment will allow us for the first time to measure several elementary dielectron production channels in nucleon-nucleon and pion-nucleon reactions using exclusive measurements.

#### 2.3 The HADES spectrometer

In order to provide an answer to the 'DLS puzzle' and to further study in medium effects up to Au+Au collisions at  $E_{kin}=1.5 \text{ GeV/A}$ , the High Acceptance Di-Electron Spectrometer HADES was conceived and built at GSI, Darmstadt, Germany [3], [4]. Therefore, it is a second generation experiment in dilepton spectroscopy that aims at measuring the invariant mass of the light pseudovector mesons in heavy ion collisions. That goal puts a number of requirements on the design of HADES.

The design of HADES is governed by the high-multiplicity environment of heavy ion collisions, the production cross sections below threshold and the small branching ratio for the dilepton decay channel due to the electromagnetic coupling constant. Only one of  $10^5$ - $10^6$  central Au+Au collisions will produce an  $e^+e^-$  pair from a meson decay. For this reason, the main features of the new instrument are:

• Large acceptance and sufficient granularity in order to maximize the probability to detect a pair once it is produced. The geometrical acceptance of ~40% [3] represents an improvement by a factor of 100 as compared to the pioneering experiments performed with the DLS spectrometer at Berkeley.

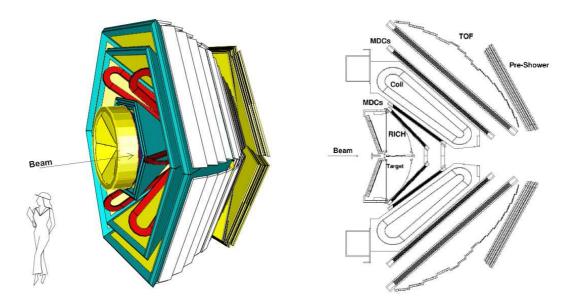

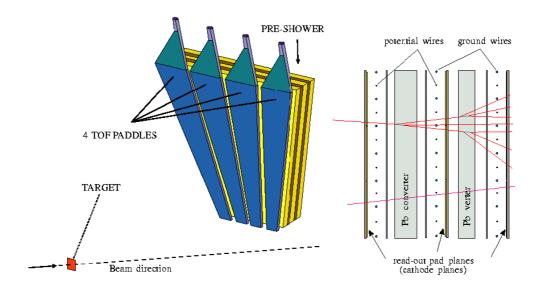

Figure 2.1: Left: 3D view of the HADES spectrometer, showing its hexagonal symmetry. Right: azimuthal cross section of HADES, indicating its detectors.

- High count rates need to be supported. The goal is to be able to operate with beam intensities as high  $2 \times 10^7$  particles per second.

- A trigger system able to downscale the amount of raw data by several orders of magnitude. This trigger scheme in HADES is made of two stages, ideally the joint rejection power would be in the order of 10<sup>4</sup>.

- A high resolution for invariant mass reconstruction, in the order of the  $\omega$  width in the mass region of the  $\omega$ , being  $\frac{\Delta M_{inv}}{M_{inv}} = 1\%$  and a signal to background ratio larger than one for invariant masses up to  $M \simeq 1 \text{ MeV/c}^2$ .

Figure 2.1 shows an schematic view of the HADES spectrometer, where its characteristic hexagonal symmetry (left side) and its constituting detectors (right side) can be appreciated. It shows how it is divided azimuthally in six identical sectors, each covering polar angles between  $18^{\circ} < \theta < 85^{\circ}$ , with practically full azimuthal coverage, besides the shadow regions introduced by the coils and detector frames. This gives an acceptance for lepton pairs of 40%.

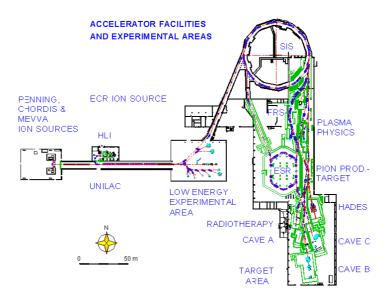

HADES is part of the accelerator system placed at GSI, which consists in a linear accelerator (UNILAC) injecting ions into a 60 m diameter synchrotron (SIS18), from where the beam can be extracted to the Fragment Separator (FRS), to the Electron Storage Rings (ESR) or to the experimental areas. Figure 2.2 shows a picture of the whole GSI accelerator area.

The UNILAC was built in 1975 and upgraded in 1999 thanks to the development of a new high current injector, called HSI. It provides an increase in the beam intensity that is able to fill the synchrotron up to almost its *space charge limit* for

Figure 2.2: GSI's accelerator.

all ions ( $I \simeq 10^{11}$  ions for C beam and  $I \simeq 10^9$  ions for Au beam). After stripping and charge state separation, the beam from the HSI is matched to the UNILAC, which accelerates the nuclei up to a few MeV/A, feeding the SIS. The SIS is a synchrotron with a circumference of 216 m, consisting in 24 bending magnets and 36 magnetic lenses to focalize the beam until each experiment.

The SIS18 is being upgraded towards the so-called SIS200 within the future project FAIR<sup>4</sup>. It will be able to ultimately reach intensities as large as  $I \simeq 10^{12}$  ions/spill for heavy ions and energies up to 30 GeV/A [12].

The story of an ion collision in HADES is as follows:

- 1. An ion beam comes from the SIS accelerator at typical energies  $E_{kin} \simeq 1 \text{ GeV/A}$  and is deviated to HADES cave (coming from the left on Fig. 2.1).

- 2. Before and after interacting with the target, a coincidence/anti-coincidence system (START/VETO) provides a signal corresponding to an interaction.

- 3. The outgoing sub-products cross a threshold RICH blind to hadrons.

- 4. Next, a very high precision MDC system tracks the particle before the toroidal coils of the magnet. After the magnet, two more MDCs track the particle for a good measurement of the bending after the magnet.

- 5. A TOF wall is devised for lepton identification after the magnetic field.

- 6. At low polar angles a SHOWER detector improves the rejection capability of last pions.

<sup>&</sup>lt;sup>4</sup>Facility for Anti-proton and Ion Research.

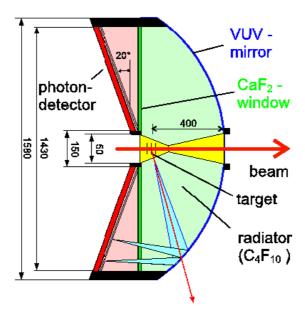

Figure 2.3: Side view of the RICH detector.

Next, we will present in detail the different detector systems of the HADES spectrometer from inner to outer.

#### 2.3.1 The START and VETO detectors

Both detectors, placed 75 cm before (START) and after (VETO) the target, consist on two identical fast diamond detectors. The system is aimed at working such that a valid signal on START and null on VETO results in a valid start signal, that must be delivered faster than 1 MHz. The detector-electronics yields a time resolution up to 29 ps being rate resistant beyond  $10^8$  ions/s per channel for meeting the HADES requirements [13]. The detector is conceived to provide a VETO efficiency  $\varepsilon > 96.5\%$ , over an area A = 2.5 cm×1.5 cm (matching the beam spot).

A new START detector system is needed for high intensity proton beams. It consists on 96 channels of scintillating fibers of 1 mm diameter, featuring high efficiency up to rates of  $10^8/s$ , a time resolution below 500 ps and a high granularity [14]. Two prototypes of 16 channels each and one fully equipped detector were used, respectively, in the HADES proton commissioning beam time in 2003 and in 2004.

#### 2.3.2 The RICH detector

The Ring Imaging CHerenkov (RICH) [15] is the first detector found by the products of the primary interaction. It consists of a gaseous radiator surrounding the target in the forward hemisphere, a spherical mirror and a position sensitive UV detector (see Fig. 2.3). It is a crucial detector for lepton identification, being totally blind to hadrons while providing a very low multiple scattering and  $\gamma$  conversion

probability, due to its gaseous low Z radiator, namely,  $C_4F_{10}$ . The low refraction index of the radiator gas provides a threshold for Cherenkov emission  $\gamma_{th}=18.2$ , sensitive to electrons with momenta above 10 MeV. On the other hand, it is blind to pions up to energies of around  $E_{kin}\simeq 2.5$  GeV, which is by far above the maximum kinetic energies available at SIS.

The Cherenkov radiation is very softly attenuated by absorption within an UV window corresponding to 145 nm $<\lambda<190$  nm. The Cherenkov light emitted in a cone is reflected by a spherical carbon fiber mirror (2 mm thick) to the back part of the system where they are detected, being focused as a ring image on a position sensitive UV photon detector plane.

#### 2.3.3 The MDCs and the magnet

The Multi-wire Drift Chambers (MDCs) [13] are in total  $2\times2\times6$  chambers, namely, 6 sectors with two groups of two MDCs before and after the magnet (I/II and III/IV, respectively). MDCs were designed to provide track reconstruction before and after the magnetic field with position resolution  $\delta y \leq 100~\mu m~(\sigma)$ . This extremely high position resolution allows to obtain a momentum resolution  $\Delta p/p \simeq 1\%$  and therefore  $\Delta M/M \simeq 1\%$  for the invariant mass, fulfilling the requirements of the HADES technical proposal [16].

The MDC chambers consist of six-wire planes at different angles, with cells sizes ranging from  $5\times5$  mm<sup>2</sup> (inner plane) to  $14\times10$  mm<sup>2</sup> (outer plane) and filled with a He/iso-C<sub>4</sub>H<sub>10</sub>. The total thickness of the four MDCs chambers amounts to  $x/X_0$ =0.2% only, comparable to the contribution of the air volume between the target and the outer MDC IV.

In between both groups of MDCs (see Fig. 2.1), a superconducting magnet consisting of six coils, produces an inhomogeneous magnetic field which reaches a maximum value of  $B \simeq 3$  T near the coils, down to  $B \simeq 1.5$  T in the acceptance region. The track momentum is reconstructed from the deflection in this magnetic field.

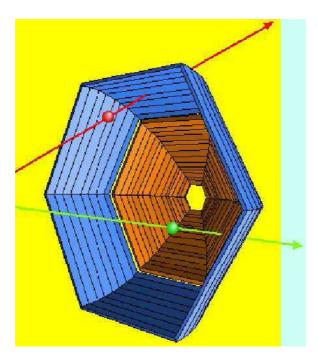

#### 2.3.4 The TOF wall

TOF and TOFino<sup>5</sup> [17] are time of flight detectors aimed at providing a high timing resolution for separation of leptons from fast pions. Both are required for implementing the multiplicity condition to select different centralities of the primary collisions, the so-called first level trigger. Redundant identification of the electron tracks is achieved via time of flight measurement. A 3D picture of the TOF wall system is shown in Fig. 2.4.

The TOF detector is made of plastic scintillator rods (BC408) read at both ends by EMI 9133B photo-multipliers. Therefore, an unbiased estimate of the time of

<sup>&</sup>lt;sup>5</sup>TOFino is being replaced by the tRPC wall we are developing, being the development of the FEE of the RPC the main topic of this work.

Figure 2.4: 3D view of TOF (at high polar angle region) and TOFino (low polar angles) detectors.

flight and impact position can be obtained, yielding  $\sigma_T \simeq 100\text{-}150$  ps and  $\sigma_x \simeq 1.5\text{-}2.3$  cm. The pad profile is a  $2.0 \times 2.0$  cm<sup>2</sup> rectangle for the inner four sets and  $3.0 \times 3.0$  cm<sup>2</sup> for those at larger polar angle. They are grouped in sets of eight, with eight such sets per sector, covering the laboratory large polar angles  $45^{\circ} < \theta_{lab} < 85^{\circ}$ .

At polar angles below 45°, the TOFino time of flight detector is temporary placed in order to fulfill the minimum requirements that allow to explore the low multiplicity reactions, providing a reasonable multiplicity trigger still. TOFino consists on four scintillators with single read-out (see Fig. 2.5) and time resolution  $\sigma_T \simeq 350$  ps after correcting for the position of the interaction.

As was previously explained, in order to cope with the high multiplicities present in typical Au+Au collisions at 1.5 GeV/A, the TOFino is being replaced by a timing RPC wall with a granularity 80 times larger and time resolutions well below 100 ps.

#### 2.3.5 The SHOWER detector

According to [17], fast pions will emulate di-leptons (fake) by an amount of 2-3 per event in Au+Au collisions at  $E_{kin}=1$  GeV/A, for a time resolution os  $\sigma_T=100$  ps. The effect is reduced for the large polar angle region, where less than 1 fake per event is expected. Because of this fact, it was decided to place an electromagnetic shower detector behind the TOFino wall, in order to increase hadron rejection.

Figure 2.5 shows a picture of the SHOWER detector layout, together with the TOFino. Each sector of the SHOWER is constituted by three sensitive planes of

Figure 2.5: The SHOWER detector and the TOFino [18], [22].

wire chambers with signal pick-up in pads of squared shapes, ranging in heights from 3 to 4.5 cm. The sizes ensure an occupancy below 5% for Au+Au collisions [18]. Between the active layers, two lead converters are interposed, aiming at inducing an electromagnetic shower with a high probability, but still keeping the probability of hadronic shower at low levels.

The interposition of lead converters defines in a naturally way the so-called Pre-Shower, Post-Shower1 and Post-Shower2 sub-detectors. Chambers are operated in Self Quenching Streamer mode. A 'shower condition' can be defined through the ratio of the charge collected in each of the two Post-Shower detectors to the one collected in the Pre-Shower, allowing to identify leptons.

#### 2.3.6 The trigger scheme

In order to enhance the 'interesting' events and reduce the collected data to a manageable set, the data acquisition is based on two trigger levels:

- 1. The positive first level trigger (LVL1) is given by a fast  $t_f < 100$  ns hardware analysis of the multiplicity measurement  $M_{ch}$  performed by the TOF modules. It is expected from simulation that, in Au+Au collisions, this multiplicity condition leads to a selection of 10% of the total number of collisions.

- 2. The second level trigger (LVL2) performs a three-steps process:

In the first step a search for electron ring images on the RICH pad plane is made. In parallel, charge clusters with the signature of an electromagnetic shower in the Pre-Shower detector as well as particles with an appropriate time of flight in the scintillator TOF wall are searched for.

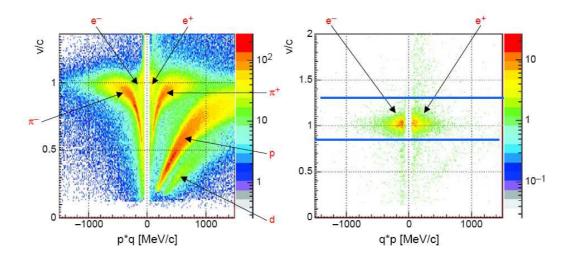

Figure 2.6: Left:  $\beta$  vs p distribution for all reconstructed particles (LVL1) from C+C at 2 GeV/A. Pions and proton branches are clearly resolved. Right: the same plot after imposing all the cuts for rejecting hadrons. The last cut, namely a cut in the time of flight of the particles, is graphically shown. The intensity scale is logarithmic.

The resulting position coordinates of electron candidates in the inner RICH and outer TOF detectors are compared in the Matching Unit (MU) in an appropriate matching window, taking into account the track deflection due to the magnetic field. The matched hits define a valid electron candidate track.

In the third step, the selected electron tracks with opposite charges can be combined into dielectron pairs and their invariant mass can be calculated on the basis of a look-up table which contains a mapping of the polar electron track deflection angles to momenta.

In order to avoid losing too many events after applying both level triggers, the LVL2 trigger must be generated in less than 10  $\mu s$ , allowing for a reduction in the candidate tracks up to a factor 100, and yielding a data flow of 1 KHz. Results in a 2 GeV/A C+C collisions imposing a conservative LVL2 trigger condition requiring at least one electron track, indicate a reduction of a factor 12, providing 92% background event rejection and high electron identification efficiency ( $\varepsilon$ >70%).

An example of this procedure, taken from [4], is shown in Fig. 2.6. The shapes of the momentum spectra for electrons and positrons are very similar to each other, measured with C+C collisions at 2 GeV/A. The extreme capability of hadron rejection is apparent, being the average multiplicity of the lepton tracks as low as  $2 \times 10^{-2}$  per LVL1 event.

# Chapter 3

# Timing RPC detectors: the HADES tRPC wall

#### 3.1 Historical RPC introduction

#### 3.1.1 RPCs

RPC, the acronym for Resistive Plate Chambers detectors, are playing an important role nowadays not only like counter detectors but also like timing detectors (tRPCs). The origin of the RPCs is the Parallel Plate Chamber (PPC), which consists in two parallel metallic electrodes operated at high voltage, thus providing an uniform electric field across its volume. A charged particle crossing the space between electrodes creates electron-ion pairs. If the field is high enough, the released electrons are accelerated towards the anode, regaining enough energy for inducing further ionizations in a cascading process called avalanche (gas multiplication [19]), producing a measurable charge from a reduced number of initial charges.

The operation of parallel geometries with electrodes covered by high resistivity materials was pioneered in 1971 [20]. The Pestov's group used a highly resistive material (glass) for limiting the progress of the spark created, working in quenched spark mode. The so-called 'Pestov counter' [20] was able to achieve ultimately a time resolution of 25 ps, although it was characterized by its high technical complexity.

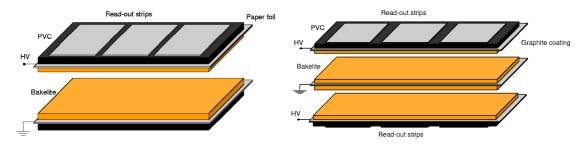

This technology was consolidated in 1981 with the appearance of the Resistive Plate Chambers (RPCs) [21] developed by R. Santonico and R. Cardarelli. The idea was overcame the difficulties of the Pestov counter [20], keeping its more fundamental virtues. This first RPC [21] consisted in two parallel copper electrodes covered with high resistance plates made of a phenolic resin known as Bakelite, with a volume resistivity  $\rho \simeq 10^{10} \Omega \text{cm}$ . The ensemble delimited a single gap of 1.5 mm filled with a gas mixture of  $Ar/iso - C_4H_{10}$  (iso-butane is an UV quencher, while Argon is a noble gas well suited for gaseous detectors due to its high density) in a proportion 1:1 (see single-gap RPC design on Fig. 3.1). The very fast drifting electrons produce a signal with large charge (100 pC) that can be used for timing purposes, whereas the

Figure 3.1: Examples of a single gap RPC [21] (left) and a double gap RPC [23] (right), according to their original designs. Dimensions are not realistic, in particular, the gap has been enlarged (pictures from [22]).

ions drift to the cathode at much smaller velocities, due to their higher mass. The signal was measured with pick-up strips, separated from the High Voltage through PVC<sup>1</sup>, avoiding the use of coupling capacitors. The HV has to be applied through a non-perfect conductor in order to be transparent to the induced signal (Fig. 3.1-left).

Under these conditions, the dark rate of the counter was considerable, contributing to a decrease in the efficiency. For avoiding this effect, the plates were painted with linseed oil and this technique has been kept since then for Bakelite-based RPCs. The main advantage as compared to the Pestov counter is that the gas circulates at atmospheric pressure. The large resistivity of the electrodes limits the current avoiding the progress of damaging processes like sparks or permanent discharges. But the high resistance of the electrodes also represents one of the main limitations of these detectors. Once the signal is produced, the area where the streamer develops is blind during a given transit time (~ms for bakelite electrodes), and during this time the effective field in this region will be lower. As a consequence, if the counting rate is very high, one can expect fluctuations in the local field caused by earlier avalanches, reducing the efficiency and the time resolution.

The basic operation principle of an RPC is already described in [21] and not much has changed since then. The parallel geometry allows to extend the 'multiplication region' to all the detector (the field is high enough for inducing an avalanche at any point), while in proportional detectors it is required a propagation time along the 'drift region' before the multiplication can take place, affecting the timing properties.

The RPC technology achieved very promising performances with this first design, reaching a 97% efficiency and a time distribution of 1.2 ns FWHM, becoming an affordable alternative to the use of plastic scintillators, mainly in big surfaces.

#### 3.1.2 Double gap RPC

Some years later, in 1988, the double gap structure in the RPCs was introduced [23] and the gap increased up to 2 mm, which is the common value nowadays. The setup was symmetric with the ground electrode in the center and the HV applied over

<sup>&</sup>lt;sup>1</sup>Polyvinyl chloride.

the outer layers (Fig. 3.1-right). This 2-gap configuration allowed for an increase in efficiency and confirmed that the time resolution was well at the level of  $\sigma_T \simeq 1$  ns.

# 3.1.3 Operation modes

#### Streamer mode

A streamer is a process of a different nature than avalanche multiplication (see section 3.1.1), releasing a high amount of charge as compared to a normal avalanche (therefore, it limits the rate capability that become a potential problem for RPCs operated in this mode). It requires high operation voltage. The secondary ionizations are so large that the charge created distorts the electric field, causing eventually a streamer in the detector gas. This mode has the advantage of providing larger signals that can be discriminated without amplification, simplifying the readout electronics as compared to the avalanche mode. RPCs in streamer mode are well suited for experiments that work at low rates (BaBar at SLAC [24] that operates  $\sim 1 \text{ Hz/cm}^2$ ) and also for cosmic rays experiments as ARGO at YangBaJing [25].

This mode was also called 'spark mode' [26] but it is probably not a good choice and the term 'streamer mode' became more popular [27].

#### Avalanche mode

The avalanche mode was introduced in 1993 [28] as an attempt to improve the rate capability by reducing the charge released per avalanche (0.2 pC). It was also called 'proportional mode' [27], but this was a bit ambitious and the term 'avalanche mode' prevailed [26]. Gas mixtures with lower amplification are used in this mode, requiring a high-gain fast amplifiers integrated in the Front-End Electronics (FEE) to compensate this effect, being the FEE more complex than in the streamer mode.

RPCs operating in avalanche mode have found application in high energy physics (ATLAS [29] or CMS [30] at LHC) and are often called 'trigger RPCs', allowing for rate capabilities in the range 100-1000 Hz/cm<sup>2</sup>. This RPCs have also found applications in timing detectors (like ALICE [31] at LHC or FOPI at GSI [32]).

# 3.1.4 Multi-gap RPCs (MRPCs)

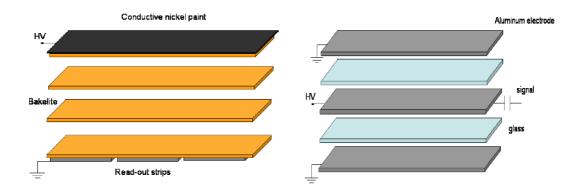

In 1996, a new design appeared [33] developed by M.C.S. Williams' group, consists in a triple set of equally-spaced Bakelite plates separated by gaps of 3 mm, that divide the gas volume into individual gaps (see Fig. 3.2). HV can be applied to external surfaces and internal plates get a voltage which is the voltage applied to the external ones. This configuration allowed for a similar time resolution as a single gap 2 mm chamber reducing the dark current and increasing the efficiency.

It can be roughly expected that the multi-gap increases the efficiency as:

$$\varepsilon = 1 - (1 - \varepsilon_N)^N \tag{3.1}$$

Figure 3.2: Examples of two multi-gap RPCs [22]: the original 3-gap design [33] (left) and the 4-gap timing RPC prototype studied in the next chapters (right).

where N denotes the number of gaps and  $\varepsilon_N$  the efficiency per single gap. Equation 3.1 is exact under the assumption that, for detection, at least one of the gaps must provide a detectable signal with independence of the others. But this assumption is not true, as two independent induced signals falling below the detection threshold can yield a total signal that is above it; therefore the efficiency represented by Eq. 3.1 represents a lower bound to the one expected in reality [22]. On the other hand, the time resolution slightly increases, in a first approach, as:

$$\sigma_T = \frac{\sigma_{T,N}}{\sqrt{N}} \tag{3.2}$$

which is the expected if the fluctuations in time response have a Gaussian origin [22]. It has been observed that  $\sigma_T$  depends on the gap width, typically improving for small gaps [34]. Then, a multi-gap design can provide a good timing, as characteristic of narrow RPCs, keeping the efficiency at high levels, typical of wide RPCs.

# 3.1.5 Timing RPCs (tRPCs)

The realization of the importance of the mechanical uniformity of the gap in relations with high precision timing together the development of fast amplification electronics, made possible to operate a multi-gap RPC in avalanche mode with thin gaps of 0.3 mm and glass electrodes, at fields as high as 100 kV/cm. This was done by P. Fonte, A. Smirnitski and M.C.S. Williams [35] in 2000. A new branch in the field was open, achieving a time resolution at the level of 120 ps, although the possibility to go down to the level of 50 ps for small detectors was soon confirmed [36]. The use of large size tRPCs was later confirmed [37], providing resolutions well below 100 ps, with reasonable homogeneity.

Soon after the first development, it became popular the use of standard window glass in RPCs, also called soda-lime-silica glass or just float glass [37]. It is widely available, affordable and still with a resistivity  $\rho \simeq 10^{12-13} \Omega \text{cm}$ , allowing for operation rates up to around 500 Hz/cm<sup>2</sup>.

#### 3.1.6 Gas mixture and operation voltage

Modern RPCs working in avalanche mode use mostly mixtures of tetrafluorethane  $(C_2H_2F_4)$  with 2% to 5% of isobutane (iso- $C_4H_{10}$ ) and 0.4% to 10% of sulphur hexafluoride  $(SF_6)$ . iso- $C_4H_{10}$  is an UV quencher which prevents from the appearance of secondary avalanches from gas photoionization. The addition of  $SF_6$  extends the streamer free operation region, producing a shift in the efficiency plateau to higher voltages and an improvement in the stability and the time resolution [34].

Most of the timing RPCs used nowadays work with the so-called 'standard mixture' [38], based on the gas mixture explained above and where the proportions are  $C_2H_2F_4$  (85%),  $SF_6$  (10%) and iso- $C_4H_{10}$  (5%), or slight deviations around it [22].

One of the factors which mainly determines the RPC performances is the electric field applied. Timing RPCs usually work at  $E{\sim}100$  kV/cm [22], [35]. The efficiency of a tRPC is higher with high voltages. The problem is that the higher the field, the higher the probability of streamers. The working point has to reach a compromise between high efficiency, good time resolution and low probability of streamers.

#### 3.1.7 Readout electronics

Readout preamplifying electronics (or Front-End Electronics) plays a very important role in the time resolution that can be achieved. This is due to the fact that the intrinsic time resolution of an RPC detector is very good ( $\sigma \sim 50$  ps [34]), therefore the total time resolution will be a quadratic sum of the intrinsic and electronics resolution. Different electronics chains have been developed in order to reduce this contribution to the total time resolution (see for example [78], [39]). Section 3.2.6. shows different readout electronics developed for timing RPC walls.

A compact and low-noise amplifying and digitizing FEE for the HADES tRPC wall has been developed, and will be more thoroughly described in the next chapters.

# 3.2 Timing RPC physics

As timing RPCs is the design used in our HADES RPC wall, its description will be developed in more detail in this section. However, most of the characteristics mentioned in the following can be extrapolated to standard RPCs.

# 3.2.1 Efficiency and primary ionization

The efficiency of an RPC is related to the average number of ionization clusters produced per unit length  $n_0/g=1/\lambda$ , being  $n_0$  the average number of clusters, g the gap width and  $\lambda$  the mean free path for ionization of the primary particle. In the ideal limit where any cluster is detected, the intrinsic efficiency of the RPC is [22]:

$$\varepsilon_{int} = 1 - e^{-g/\lambda} = 1 - e^{-n_0}$$

(3.3)

and, by analogy, the efficiency measured in the laboratory is:

$$\varepsilon_{exp} = 1 - e^{-n_0'} \tag{3.4}$$

The measured efficiency is smaller that the theoretical one because the lowest value achievable for the threshold of the discriminator is limited by the noise level and the avalanches that induce signals compatible with noise can not be measured. Furthermore, there is always a probability that the electrons in a cluster are attached and no electron signal is collected.

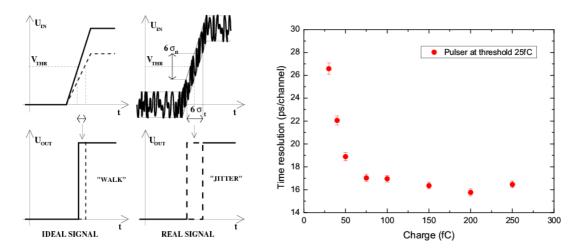

#### 3.2.2 Time response

There is a model [40] that explains the main dependencies of the intrinsic time response of an RPC. It allows to obtain the time response function in terms of  $n'_0$  (related to the measured efficiency) and the growth coefficient  $S = (\alpha - \eta)v_e$  ( $\alpha$  is the Townsend coefficient,  $\eta$  is the attachment coefficient and  $v_e$  is the drift velocity):

$$\rho_T(t) = \frac{n'_{\theta}}{e^{n'_{\theta}} - 1} \frac{e^{(\tau_{th} - St) - \exp(\tau_{th} - St)}}{\sqrt{n'_{\theta} e^{(\tau_{th} - St)}}} I_1\left(2\sqrt{n'_{\theta} e^{(\tau_{th} - St)}}\right)$$

(3.5)

where  $\tau_{th} = \ln[m_t(1-\eta/\alpha]]$  and  $I_1$  is the modified Bessel function. The rms<sup>2</sup> (time resolution) can be extracted from Eq. 3.5:

$$rms_T = \frac{K(n_0')}{S(V)} \tag{3.6}$$