# High Performance Java for Multi-core Systems

Sabela Ramos Garea

Department of Electronics and Systems University of A Coruña, Spain

# Department of Electronics and Systems University of A Coruña, Spain

## PhD Thesis

# High Performance Java for Multi-core Systems

Sabela Ramos Garea

June 2013

PhD Advisors: Guillermo López Taboada Juan Touriño Domínguez

Dr. Guillermo López Taboada Profesor Contratado Doutor Dpto. de Electrónica e Sistemas

Universidade da Coruña

Dr. Juan Touriño Domínguez Catedrático de Universidade Dpto. de Electrónica e Sistemas Universidade da Coruña

#### **CERTIFICAN**

Que a memoria titulada "High Performance Java for Multi-core Systems" foi realizada por Dna. Sabela Ramos Garea baixo a nosa dirección no Departamento de Electrónica e Sistemas da Universidade da Coruña e conclúe a Tese de Doutoramento que presenta para a obtención do título de Doutora pola Universidade da Coruña coa Mención de Doutor Internacional.

Na Coruña, o 25 de Xuño de 2013

Asdo.: Guillermo López Taboada Asdo.: Juan Touriño Domínguez Director da Tese de Doutoramento Director da Tese de Doutoramento

Asdo.: Sabela Ramos Garea Autora da Tese de Doutoramento

# Resumo da Tese de Doutoramento

#### Introducción

O interese que a comunidade da computación de altas prestacións (High Performance Computing, HPC) vén demostrando na linguaxe Java, aumentou considerablemente nos últimos anos grazas á mellora experimentada en canto a rendemento e ás características que fan de Java unha linguaxe altamente productiva. Entre elas, cabe destacar a portabilidade e independenza da plataforma, a simplicidade, a robustez, a seguridade, a orientación a obxectos e contar cunha grande comunidade de desarrolladores, tanto no mundo académico coma no empresarial. Ademais da mellora de rendemento, hai dúas características cruciais que propiciaron a progresiva adopción de Java na computación de altas prestacións: o soporte para redes de interconexión e a incorporación de multithreading no núcleo da linguaxe. Estas dúas calidades fan de Java unha linguaxe idónea para a programación en contornos paralelos.

Dentro dos contornos paralelos actuais, os sistemas de memoria compartida volven a cobrar forza nun escenario que, ata hai pouco, estaba dominado por clusters de sistemas monoprocesador, que permitían construír contornos de computación de altas prestacións reducindo os costes. Non obstante, o incremento de rendemento dos procesadores empezou a acadar límites físicos, o que levou á aparición de problemas de disipación de calor e de alta ineficiencia enerxética. Para superar estes obstáculos, os fabricantes de hardware comezaron a centrarse na mellora do rendemento dos procesadores mediante o incremento do número de núcleos presentes en cada un deles, o que se coñece como procesadores multi-core ou multi-núcleo. De feito, na actualidade, procesadores de catro ou máis núcleos son comúns en ordenadores de

uso persoal.

O incremento progresivo no número de núcleos está conducindo tamén á xeralización de procesadores many-core para a computación de ámbito xeral. E neste eido volve a aparecer o problema do consumo enerxético, xa que ter un grande número de núcleos por procesador en situacións nas que só se precisa unha pequena parte, provoca unha grande ineficiencia enerxética. Para solventar este problema, aparecen os aceleradores de uso específico, como as tarxetas gráficas (Graphics Processing Unit, GPU), arquitecturas many-core que só se utilizan para tareas específicas de procesamento de gráficos mentres outro procesador (host) é o que se encarga da computación xeral. As características destes aceleradores e as súas elevadas capacidades de cómputo fixeron que fosen adoptadas para a aceleración de códigos vectoriais non necesariamente relacionados coa computación gráfica. Sen embargo, as dificultades de programación destes aceleradores favoreceron a aparición de aceleradores de arquitecturas x86 que soportan linguaxes e paradigmas tradicionais de programación, coma o coprocesador Xeon Phi comercializado por Intel.

O éxito das arquitecturas multi- e many-core indica a necesidade de ferramentas e librerías de programación que exploten o rendemento en memoria compartida, onde Java, co soporte para multithreading, presenta unha grande vantaxe. O principal problema é que a API de manexo de threads é complicada, sendo o usuario o que ten que lidiar coa creación/destrucción de threads e, o que é máis importante, coa posibilidade de aparición de race conditions e inconsistencias. Para solventar isto, Java inclúe unha librería de concorrencia na que se traballa con pools de threads e cun paradigma de programación orientado á descomposición da carga de traballo en tarefas (que pode ser recursiva utilizando a funcionalidade de fork/join). Este paradigma obliga a que os algoritmos paralelos non orientados a tarefas teñan que ser reescritos ou utilizar estas ferramentas de maneira non eficiente.

Esta Tese presenta unha análise detallada do estado da arte en canto á situación de Java para a programación de sistemas de memoria compartida, centrándose en solucións axeitadas para a computación de altas prestacións. Os principais obxectivos deste traballo son a análise do estado do soporte Java á computación de altas prestacións en memoria compartida e o desenvolvemento de middleware para mellorar tanto o rendemento como a productividade. En consecuencia, levouse a cabo un estudo do soporte software disponible para a programación multi-núcleo en Java

e realizouse o deseño, implementación e avaliación dun dispositivo de comunicacións de paso de mensaxes en Java optimizado para memoria compartida. Este dispositivo proporciona unha API de alto nivel que elimina a necesidade de manexar threads ou a descomposición en tarefas. Esta API segue a especificación Java de paso de mensaxes (Message Passing in Java, MPJ) baseada no estándar MPI, amplamente utilizado en computación de altas prestacións. Tamén se inclúe unha optimización de patróns de comunicacións entre procesos ou threads (operacións colectivas), tanto bloqueantes coma non bloqueantes, para contornos baseados en sistemas multinúcleo, alén dunha análise da adecuación e potencial das colectivas non bloqueantes en contornos de memoria compartida. Por outra banda, fíxose un estudo e avaliación de solucións dispoñibles para a explotación de sistemas many-core en aplicacións Java. A principal conclusión deste estudo é que o uso de Java en contornos many-core é productivo e pode proporcionar resultados de alto rendemento.

#### Metodoloxía de Traballo

A metodoloxía de investigación seguida na presente Tese de Doutoramento consistiu en:

- Definir a lista de obxectivos identificando as tarefas necesarias para acadalos, tendo en conta os traballos previos e os recursos dispoñibles.

- Determinar a secuencia de execución das tarefas aténdose ás restriccións que puidesen existir e buscando a orde máis axeitada.

- Establecer a duración das tarefas e a oportunidade de desenvolvemento nun momento determinado.

- Organizar os obxectivos e tarefas en bloques de certa entidade que definan etapas.

- Definir, para cada etapa, os fitos, ou metas a acadar en tempo definido, tendo en conta que cada etapa pode constar dunha ou varias metas.

Os obxectivos e tarefas foron definidos de maneira iterativa para poder aproveitar o coñecemento adquirido en etapas previas.

A continuación, enumérase a lista de obxectivos ( $\mathbf{O}$ ), agrupados en bloques ( $\mathbf{B}$ ), detallando as tarefas (T) que foron desenvolvidas na Tese para acadar cada un dos obxectivos.

- **B 1.** Análise das capacidades da linguaxe Java para a programación de altas prestacións en memoria compartida.

- O 1.1. Análise da programación en Java para memoria compartida.

- T 1.1.1. Estudo da usabilidade e rendemento de Java para programación de altas prestacións.

- T 1.1.2. Análise das caraterísticas internas de Java para programación paralela en memoria compartida.

- T 1.1.3. Análise doutros modelos de programación paralela utilizados en Java actualmente.

- T 1.1.4. Avaliación das necesidades de optimización do soporte Java para arquitecturas de memoria compartida.

- O 1.2. Análise do estado actual de dispoñibilidade do soporte en Java para programación heteroxénea.

- T 1.2.1. Búsqueda bibliográfica de solucións e proxectos existentes que den soporte á programación heteroxénea en Java.

- T 1.2.2. Análise do soporte dispoñible e identificación de carencias.

- **B** 2. Estudo das principais arquitecturas de memoria compartida dispoñibles.

- O 2.1. Estudo e avaliación de arquitecturas de memoria compartida con soporte para a execución de instruccións x86.

- T 2.1.1. Análise detallada de arquitecturas multi-core dispoñibles.

- T 2.1.2. Análise detallada de arquitecturas many-core x86 dispoñibles.

- O 2.2. Estudo e avaliación doutras arquitecturas de memoria compartida.

- T 2.2.1. Análise detallada de unidades de procesamento gráfico (Graphics Processing Units, GPU) para programación de propósito xeral.

- **B 3.** Análise, deseño e implementación dunha solución de paso de mensaxes en Java para memoria compartida.

- O 3.1. Avaliación do estado da arte do paso de mensaxes en Java para memoria compartida.

- T 3.1.1. Análise de proxectos de paso de mensaxes noutras linguaxes con soporte específico para memoria compartida.

- T 3.1.2. Análise do soporte para paso de mensaxes en Java.

- O 3.2. Deseño e implementación dunha solución de paso de mensaxes en Java para memoria compartida.

- T 3.2.1. Deseño da solución tendo en conta as características específicas de Java e o seu soporte para programación paralela en memoria compartida.

- T 3.2.2. Implementación do deseño de paso de mensaxes proposto.

- T 3.2.3. Optimización da solución implementada facendo especial fincapé nos puntos de sincronización entre threads.

- O 3.3. Avaliación da solución proposta.

- T 3.3.1. Deseño do conxunto de probas a realizar e selección das librerías máis relevantes entre as atopadas no punto **O** 3.1 para comparar coa solución proposta.

- T 3.3.2. Análise e selección dos contornos de probas e do hardware dispoñible.

- T 3.3.3. Realización de probas e análise de resultados coa consecuente extracción de conclusións e posible re-optimización.

- **B 4.** Análise do rendemento e optimización de operacións colectivas para memoria compartida en Java.

- O 4.1. Análise e implementación de operacións colectivas para contornos con procesadores multi-core.

- T 4.1.1. Análise do estado da arte das operacións colectivas, tanto en Java coma en linguaxes nativas, e da súa adecuación a contornos multicore.

- T 4.1.2. Implementación de algoritmos de operacións colectivas optimizados para sistemas con nodos multi-core, tanto aislados (memoria compartida) coma conectados mediante redes de interconexión (memoria compartida-distribuída).

- O 4.2. Análise do potencial das operacións colectivas non bloqueantes para memoria compartida en Java.

- T 4.2.1. Estudo das implementacións existentes e da adecuación dunha implementación para memoria compartida utilizando Java.

- T 4.2.2. Deseño e implementación dunha librería de colectivas non bloqueantes para Java optimizada para memoria compartida.

- O 4.3. Avaliación e análise do rendemento das librerías de colectivas implementadas.

- T 4.3.1. Deseño do conxunto de probas.

- T 4.3.2. Análise e selección dos contornos de probas e do hardware dispoñible.

- T 4.3.3. Realización de probas e análise de rendemento coa consecuente extracción de conclusións e posible re-optimización.

- B 5. Análise da situación actual de Java para programación heteroxénea.

- O 5.1. Avaliación da programación heteroxénea en Java utilizando coprocesadores con arquitectura x86.

- T 5.1.1. Análise bibliográfica de solucións existentes.

- T 5.1.2. Avaliación do rendemento das solucións identificadas a través do deseño dun conxunto de benchmarks.

- O 5.2. Avaliación da programación heteroxénea en Java utilizando aceleradores gráficos.

- T 5.2.1. Análise bibliográfica de solucións existentes para a programación de propósito xeral en GPUs e noutros aceleradores utilizando Java.

- T 5.2.2. Avaliación dunha selección das solucións atopadas a través do deseño dun conxunto de benchmarks.

- O 5.3. Análise da productividade das solucións para programación heteroxénea en Java.

- T 5.3.1. Análise bibliográfica de métricas existentes para a avaliación da productividade.

- T 5.3.2. Avaliación da productividade mediante o deseño dun conxunto de medidas.

- **B 6.** Conclusións e análise das futuras liñas de traballo.

- O 6.1. Exposición das principais leccións aprendidas.

- T 6.1.1. Resumo do traballo feito, principais aportacións e conclusións.

- T 6.1.2. Análise das posibles liñas de traballo futuro.

- O 6.2. Elaboración da memoria final da Tese de Doutoramento.

- T 6.2.1. Estructuración e organización dos informes do traballo realizado.

- T 6.2.2. Redacción da memoria.

#### Medios

Para a elaboración desta Tese de Doutoramento utilizáronse os medios descritos a continuación:

- Material de traballo e financiamento económico proporcionados polo Grupo de Arquitectura de Computadores da Universidade da Coruña, o Ministerio de Educación (bolsa predoutoral FPU AP2009-2112) e a Universidade da Coruña (contrato de profesor axudante).

- Proxectos de investigación que financiaron esta Tese:

- Con financiamento europeo: European Network of Excellence on High Performance and Embedded Architecture and Compilation HiPEAC-2 (7° PM, ICT-217068), HiPEAC-3 (7° PM, ICT-287759) e Open European Network for High Performance Computing on Complex Environments (ComplexHPC, COST Action ref. IC0805).

- Con financiamento estatal: proxectos do Plan Nacional de I+D "Arquitecturas, sistemas y herramientas para computación de altas prestaciones" (TIN2010-16735) e "Soporte hardware y software para computación de altas prestaciones" (TIN2007-67537-C03-02).

- Con financiamento autonómico: Programa de Consolidación e Estructuración de Unidades de Investigación Competitivas da Xunta de Galicia, na modalidade de Grupos de Referencia Competitiva (Grupo de Arquitectura de Computadores, refs. 2010/6 e 2006/3) e na modalidade de Redes

- de Investigación (Rede Galega de Computación de Altas Prestacións, refs. 2010/53 e 2007/147).

- Con financiamento privado: proxecto High Performance Computing for High Performance Trading (HPC4HPT), financiado pola Fundación Barrié, e o proxecto FastMPJ Cloud, financiado por Amazon mediante unha AWS Research Grant.

- Clusters e supercomputadores utilizados (detállanse só os recursos utilizados de cada sistema):

- Clúster pluton (Grupo de Arquitectura de Computadores da Universidade da Coruña), 8 nodos con 2 procesadores Intel Xeon E5520 de 4 núcleos a 2.27 GHz con ata 8 GB de RAM e rede de interconexión InfiniBand; e 16 nodos con 2 procesadores Intel Xeon E5-2660 de 8 núcleos a 2.20 GHz con 64 GB de RAM, GPUs NVIDIA K20m e coprocesadores Intel Xeon Phi 5110P.

- Clúster *DAS-4* (Advanced School for Computing and Imaging, ASCI, Vrije University Amsterdam), formado por recursos de diversas institucións holandesas. Para a Tese, utilizouse un nodo con procesador AMD Magny-Cours de 48 núcleos e 128 GB de RAM, e ata 16 nodos con 2 procesadores Intel Xeon E5620 de 4 núcleos a 2.40 GHz con ata 24 GB de RAM e rede de interconexión InfiniBand.

- Supercomputador Finis Terrae (Centro de Supercomputación de Galicia): 144 nodos con procesador Itanium2 Montvale de 16 núcleos a 1.6 GHz con 128 GB de RAM e rede de interconexión InfiniBand, e 1 nodo Superdome con procesador Itanium2 Montvale de 128 núcleos a 1.6 GHz con 1 TB de RAM.

- Estancia de tres meses na ETH Zürich no Scalable Parallel Computing Lab do profesor Torsten Hoefler, que favoreceu a colaboración no desenvolvemento da librería de colectivas non bloqueantes e o estudo de algoritmos de operacións colectivas para memoria compartida, así como a profundización na arquitectura do coprocesador Intel Xeon Phi. Esta estancia estivo financiada por unha Collaboration Grant da rede HiPEAC-3 no 2012.

#### Conclusións

Esta Tese de Doutoramento, "High Performance Java for Multi-core Systems", presenta unha análise da adecuación de Java para a programación de altas prestacións en arquitecturas multi-núcleo, así como un estudo das principais arquitecturas de memoria compartida dispoñibles, proporcionando a implementación dun middleware de paso de mensaxes en Java para a programación paralela de sistemas multi-núcleo e unha librería de operacións colectivas optimizadas, tanto bloqueantes coma non bloqueantes. Ademais, realizouse unha análise detallada das posibilidades actuais de programación orientada a sistemas heteroxéneos utilizando Java.

Como principal conclusión extraída, Java permite obter un alto rendemento en sistemas de memoria compartida mediante o uso da API de multithreading. Pero, pese a elevada productividade que proporciona a linguaxe Java en xeral, a API de multithreading é complicada e propensa a erros, e o manexo da sincronización pode dar lugar a códigos ineficientes ou, o que é peor, inconsistentes. Por outra banda, aínda que existe a posibilidade de utilizar ferramentas de concorrencia de alto nivel incluídas na linguaxe, estas están orientadas a obter un elevado largo de banda e non baixa latencia, esixindo a restructuración de algoritmos en base a tarefas. A solución proposta nesta Tese pasa por aproveitar o soporte para multithreading, que permite explotar os sistemas multi-núcleo eficientemente, para desenvolver ferramentas e librerías de alto rendemento que proporcionen interfaces sinxelas manexando, de forma transparente ao usuario, a API de threads.

Ademais, as optimizacións desenvolvidas, tanto no middleware de paso de mensaxes coma na librería de operacións colectivas, mostran que á hora de intentar maximizar o rendemento das aplicacións Java non podemos centrarnos únicamente nas características do hardware. Tamén é necesario ter en conta as peculiaridades da JVM (Java Virtual Machine), xa que os costes de inicialización ou a falta de compilación poden provocar un aumento da latencia que non compense a mellora obtida mediante técnicas tradicionais de aproveitamento do hardware. Non obstante, a JVM presenta avances neste aspecto que permiten certa optimización do rendemento tendo en conta o hardware, como por exemplo o mapeo de threads da JVM a threads do sistema operativo, o que permite ter en conta a afinidade dos threads a núcleos específicos nun código Java.

Finalmente, aínda que os fabricantes non proporcionan soporte específico en Java para arquitecturas many-core, existen librerías que permiten programar en Java baseándose en soportes nativos que combinan a alta eficiencia coa productividade. Non obstante, existe unha diferencia de rendemento con respecto a solucións nativas debido á falla de soporte directo destas arquitecturas en Java.

En canto ás liñas de traballo futuro, en primeiro lugar estaría a análise dos beneficios e principais problemas do soporte Java directo para arquitecturas many-core. Xa que o soporte para GPUs depende principalmente dos fabricantes e dos responsables do desenvolvemento das JVMs, é de esperar que, xa que o Intel Xeon Phi presenta unha arquitectura x86, nun futuro cercano será posible executar máquinas virtuais Java neste coprocesador. Ademais, tanto as operacións colectivas coma o dispositivo de paso de mensaxes en Java para sistemas multi-núcleo poderían optimizarse incorporando unha maior caracterización hardware ou parametrización nos algoritmos e implementando un sistema de selección de algoritmos en tempo de execución para as operacións colectivas máis preciso e mediante o modelado das interaccións de threads. Outra liña interesante sería unha exploración da posibilidade de implementar un dispositivo de comunicacións híbrido de memoria compartidadistribuída. Aínda que esta posibilidade foi analizada en [109] a partir do soporte para comunicacións en memoria compartida incluido na librería de paso de mensaxes MPJ Express [118], esta análise estivo limitada polos problemas de eficiencia na sincronización de MPJ Express e pola falta de códigos adaptados á explotación do rendemento de arquitecturas clúster multi-núcleo (é dicir, minimizando as comunicacións inter-nodo).

### Principais Contribucións

As principais contribucións desta Tese de Doutoramento son:

- Análise do estado da arte de Java para computación de altas prestacións [121].

- Implementación dunha solución eficiente e escalable de comunicacións en memoria compartida utilizando Java e proporcionando unha API de paso de mensaxes [108, 109].

- Optimización de operacións colectivas bloqueantes para memoria compartida e clusters de procesadores multi-núcleo [122].

- Implementación de colectivas non bloqueantes en Java, e estudo do rendemento en sistemas de memoria compartida [107].

- Estudo do rendemento e productividade das solucións dispoñibles para programación Java en contornos heteroxéneos utilizando arquitecturas manycore [25, 106].

# Publications from the Thesis

## Journal Papers (8)

- S. Ramos, G. L. Taboada, R. R. Expósito, and J. Touriño. Nonblocking Collectives for Scalable Java Communications, 2013 (Submitted for journal publication).

- R. R. Expósito, S. Ramos, G. L. Taboada, J. Touriño, and R. Doallo. FastMPJ: a Scalable and Efficient Java Message-Passing Library, 2013 (Submitted for journal publication).

- R. R. Expósito, G. L. Taboada, S. Ramos, J. Touriño, and R. Doallo. General-Purpose Computation on GPUs for High Performance Cloud Computing. *Concurrency and Computation: Practice and Experience*, 2013 (In press).

- R. R. Expósito, G. L. Taboada, S. Ramos, J. Touriño, and R. Doallo. Evaluation of Messaging Middleware for High-Performance Cloud Computing. *Personal and Ubiquitous Computing*, 2013 (In press).

- S. Ramos, G. L. Taboada, R. R. Expósito, J. Touriño, and R. Doallo. Design of Scalable Java Communication Middleware for Multi-Core Systems. The Computer Journal, 56(2): 214–228, 2013.

- G. L. Taboada, S. Ramos, R. R. Expósito, J. Touriño, and R. Doallo. Java in the High Performance Computing Arena: Research, Practice and Experience. Science of Computer Programming, 78(5): 425–444, 2013.

- R. R. Expósito, G. L. Taboada, S. Ramos, J. Touriño, and R. Doallo. Performance Analysis of HPC Applications in the Cloud. Future Generation Computer Systems, 29(1): 218–229, 2013.

- G. L. Taboada, S. Ramos, J. Touriño, and R. Doallo. Design of Efficient Java Message-passing Collectives on Multi-core Architectures. *Journal of Super-computing*, 55(2): 126–154, 2011.

## International Conferences (3)

- S. Ramos, T. Hoefler. Modeling Communication in Cache-Coherent SMP Systems A Case-Study with Xeon Phi. In Proc. 22nd ACM Intl. Symposium on High-Performance Parallel and Distributed Computing (HPDC'13), pages 97–108, New York City, NY, USA, 2013.

- J. Docampo, S. Ramos, G. L. Taboada, R. R. Expósito, J. Touriño, and R. Doallo. Evaluation of Java for General Purpose GPU Computing. In *Proc.* Intl. Workshop on Engineering Object-Oriented Parallel Software (EOOPS'13), pages 1398–1404, Barcelona, Spain, 2013.

- S. Ramos, G. L. Taboada, J. Touriño, and R. Doallo. Scalable Java Communication Middleware for Hybrid Shared/Distributed Memory Architectures. In Proc. 13th Intl. Conf. on High Performance Computing and Communications (HPCC'11), pages 221–228, Banff, Alberta, Canada, 2011.

# National Conferences (3)

- J. Docampo, S. Ramos, G. L. Taboada, R. R. Expósito, J. Touriño, and R. Doallo. Evaluación de Java para Computación de Propósito General en GPU. In Proc. XXIV Jornadas de Paralelismo, Madrid, Spain, 2013.

- S. Ramos, G. L. Taboada, J. Touriño, and R. Doallo. Comunicaciones Escalables en Memoria Compartida para Paso de Mensajes en Java. In Proc. XXII Jornadas de Paralelismo, pages 439–444, La Laguna, Tenerife, Spain, 2011.

S. Ramos, G. L. Taboada, J. Touriño, and R. Doallo. Biblioteca de Primitivas Colectivas de Paso de Mensajes para Java en Sistemas Multicore. In Proc. XX Jornadas de Paralelismo, pages 511–516, A Coruña, Spain, 2009.

# Abstract

The interest in Java within the High Performance Computing (HPC) community has been rising during the last years thanks to its noticeable performance improvements and its productivity features. In a context where the trend to increase the number of cores per processor is leading to the generalization of many-core processors and accelerators, multithreading as an inherent feature of the language makes Java extremely interesting to exploit the performance provided by multi- and manycore architectures. This PhD Thesis presents a thorough analysis of the current state of the art regarding multi- and many-core programming in Java and provides the design, implementation and evaluation of several solutions to enable Java for the many-core era. To achieve this, a shared memory message-passing solution has been implemented to provide shared memory programming with the scalability of distributed memory paradigms, also with the benefits of a portable programming model that allows the developed codes to be run on distributed memory systems. Moreover, representative collective operations, involving computation and communication among different processes or threads, have been optimized, also introducing in Java new features for scalability from the MPI 3.0 specification, namely nonblocking collectives. Regarding the exploitation of many-core architectures, the lack of direct Java support forces to resort to wrappers or higher-level solutions to translate Java code into CUDA or OpenCL. The most relevant among these solutions have been evaluated and thoroughly analyzed in terms of performance and productivity. Guidelines for taking advantage of shared memory environments have been derived during the analysis and development of the proposed solutions, and the main conclusion is that the use of Java for shared memory programming on multi- and many-core systems is not only productive but also can provide high performance competitive results. However, in order to effectively take advantage of the underlying multi- and many-core architectures, the key is the availability of optimized middleware that abstracts multithreading details from the user, like the one proposed in this Thesis, and the optimization of common operations like collective communications.

# Acknowledgments

I would like to start saying thank you to Guillermo and Juan for their valuable help and support during the elaboration of this PhD, and, of course, to all my colleagues in the Computer Architecture Group, both the ones from the ground floor and those from the upper floor. I do not want to leave anybody, but I have to make a special mention to Jorge, Jose, Raquel, CH, Toño, Pablo, Iván, Jacobo, Moisés, Rober, Dani and Sasi.

Of course, I do not want to forget other people that have also been there supporting me during these years, especially my parents and my sister Elena, Juan, and all my closest friends.

I gratefully thank Dr. Torsten Hoefler for hosting me during my visit to the Scalable Parallel Computing Laboratory at the ETH Zürich, Switzerland, and the CSCS people for their efficient and useful support.

Moreover, I want to thank the Supercomputing Center of Galicia (CESGA), and the Advanced School for Computing and Imaging (ASCI) and Vrije University Amsterdam, for the access to their computational resources (Finis Terrae supercomputer and DAS-4 cluster, respectively).

Last, but not least, I want also to express my gratitude to the following institutions for providing financial support for this work: the Computer Architecture Group, the Department of Electronics and Systems and the University of A Coruña for the human and material support; the HiPEAC network (EU FP7 ICT-217068 and ICT-287759) and its collaboration grants program, the Open European Network for High Performance Computing on Complex Environments (ComplexH-PC, COST Action ref. IC0805) for providing financial support to attend the ComplexHPC Spring School, the Ministry of Education and Culture and the Ministry of Economy and Competitiveness of Spain for the projects TIN2007-67537-C03-02 and TIN2010-16735, and the FPU Grant AP2009-2112.

It is not the task of the University to offer what society asks for, but to give what society needs.

(Non é labor da Universidade ofrecer o que a sociedade pide, senón o que a sociedade necesita)

Edsger W. Dijkstra.

# Contents

| Pr | etace | 2                                                           | 1  |

|----|-------|-------------------------------------------------------------|----|

| 1. | Java  | a for High Performance Computing                            | 5  |

|    | 1.1.  | Parallel Programming in Java                                | 6  |

|    |       | 1.1.1. High Performance Utilities in Java                   | 8  |

|    | 1.2.  | Message Passing in Java (MPJ)                               | 8  |

|    | 1.3.  | Heterogeneous Programming in Java                           | 11 |

| 2. | Sha   | red Memory Architectures                                    | 15 |

|    | 2.1.  | Multi-core Architectures                                    | 15 |

|    |       | 2.1.1. Thread Affinity Control in Java                      | 19 |

|    | 2.2.  | Many-core Architectures                                     | 19 |

|    |       | 2.2.1. Many-core x86 Architectures: Intel Xeon Phi          | 20 |

|    |       | 2.2.2. Graphics Processing Units (GPUs)                     | 22 |

|    | 2.3.  | Java Support for Shared Memory Architectures                | 25 |

| 3. | A S   | hared Memory Communication Device for MPJ                   | 27 |

|    | 3.1.  | State of the Art of Message Passing for Shared Memory       | 28 |

|    | 3.2.  | Design and Implementation of the Shared Memory Device smdev | 29 |

XXX CONTENTS

|    |       | 3.2.1.  | Low-level Message-Passing API: xxdev                 | . 30  |

|----|-------|---------|------------------------------------------------------|-------|

|    |       | 3.2.2.  | Class Loading in smdev                               | . 31  |

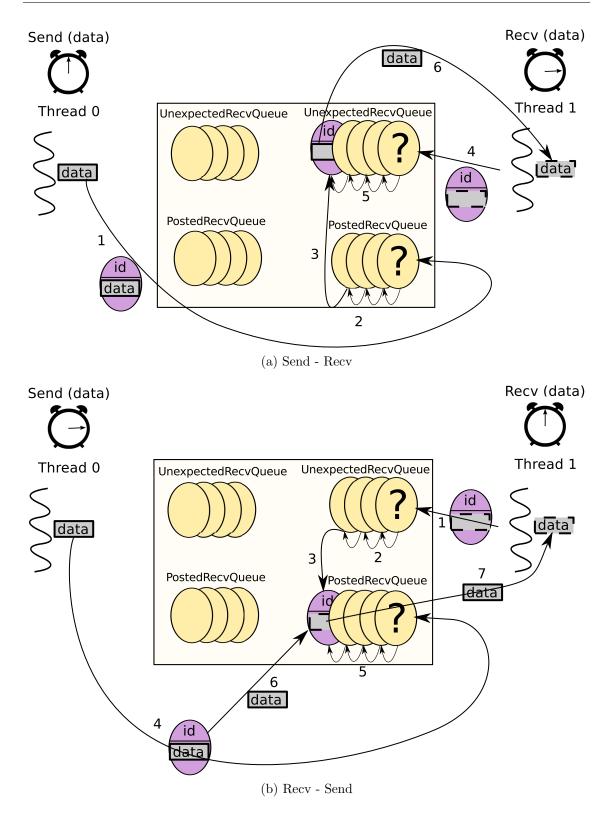

|    |       | 3.2.3.  | Message Queues                                       | . 32  |

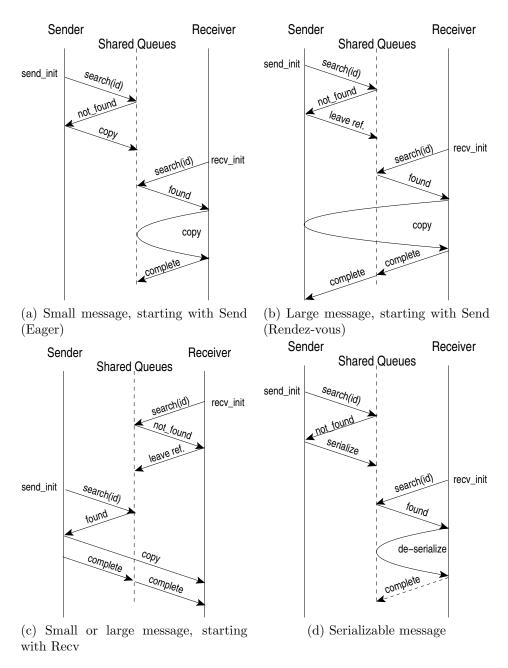

|    |       | 3.2.4.  | Message Transfer Protocols                           | . 33  |

|    |       | 3.2.5.  | Synchronization                                      | . 39  |

|    |       | 3.2.6.  | Integration of smdev in FastMPJ                      | . 40  |

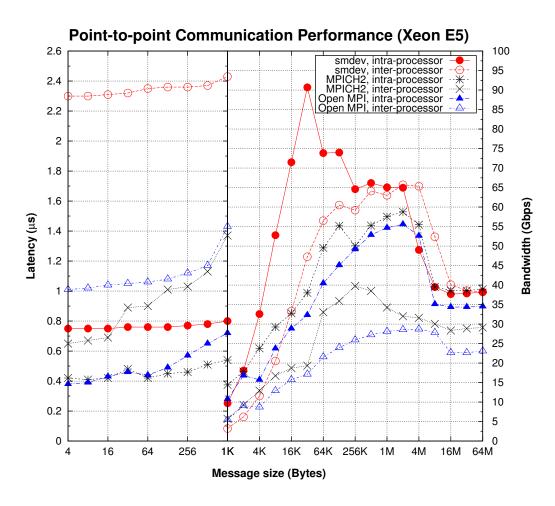

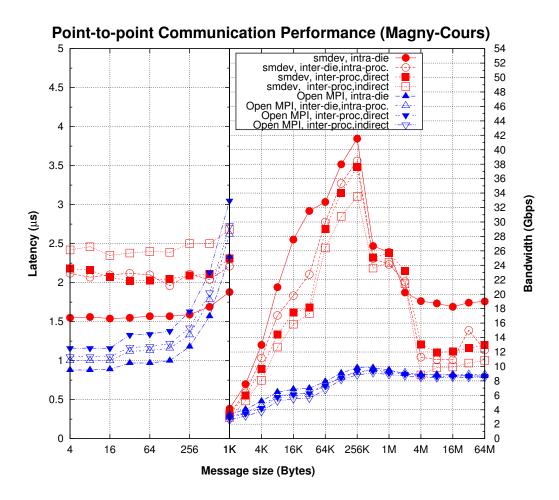

|    | 3.3.  | Perfor  | mance Evaluation                                     | . 40  |

|    |       | 3.3.1.  | Experimental Configuration                           | . 40  |

|    |       | 3.3.2.  | Point-to-point Micro-benchmarking                    | . 41  |

|    |       | 3.3.3.  | Impact of smdev on the Scalability of Parallel Codes | . 48  |

|    | 3.4.  | Main    | Contributions of the smdev Device                    | . 51  |

| 4. | Effic | cient S | Support of Collective Communications in Java         | 53    |

|    | 4.1.  | Blocki  | ng Collectives for Multi-core Systems                | . 54  |

|    |       | 4.1.1.  | State of the Art of MPJ Collectives                  | . 56  |

|    |       | 4.1.2.  | Multi-core Aware Collectives                         | . 58  |

|    |       | 4.1.3.  | Performance Evaluation                               | . 68  |

|    | 4.2.  | Nonble  | ocking Collectives in Java                           | . 83  |

|    |       | 4.2.1.  | State of the Art of Nonblocking Collectives          | . 84  |

|    |       | 4.2.2.  | Nonblocking MPJ Collectives                          | . 86  |

|    |       | 4.2.3.  | Performance Evaluation                               | . 93  |

|    | 4.3.  | Main    | Contributions of the MPJ Collectives Support         | . 100 |

| 5. | Java  | a Hete  | rogeneous Computing                                  | 103   |

|    | 5.1.  | Genera  | al Purpose GPU Computing in Java                     | . 103 |

| CONTENTS | XXXI |

|----------|------|

|----------|------|

|            | 5.1.1.  | Experimental Configuration                                  | . 104 |  |  |

|------------|---------|-------------------------------------------------------------|-------|--|--|

|            | 5.1.2.  | Analysis of Experimental Results                            | . 105 |  |  |

| 5.2.       | Many-   | core x86-based Computing in Java                            | . 110 |  |  |

|            | 5.2.1.  | Experimental Configuration                                  | . 110 |  |  |

|            | 5.2.2.  | Analysis of Experimental Results                            | . 111 |  |  |

| 5.3.       | Analys  | sis of Productivity of Java Heterogeneous Computing Codes . | . 115 |  |  |

|            | 5.3.1.  | Characterization of the Manual Effort                       | . 117 |  |  |

|            | 5.3.2.  | Characterization of the Conceptual Effort                   | . 118 |  |  |

| 5.4.       | Lesson  | as Learned from Java Heterogeneous Computing                | . 122 |  |  |

| Conclu     | sions a | and Future Work                                             | 123   |  |  |

| References |         |                                                             |       |  |  |

# List of Tables

| 1.1. | Available solutions for GPGPU computing in Java                                                           |

|------|-----------------------------------------------------------------------------------------------------------|

| 3.1. | MOPS of NPB codes on a single core                                                                        |

| 4.1. | Algorithms implemented in the MPJ collectives library 62                                                  |

| 4.2. | Algorithms that maximize collectives performance on the DAS-4 multi-<br>core cluster                      |

| 4.3. | Latency of Barrier algorithms (time in $\mu$ seconds) 83                                                  |

| 5.1. | Selected kernels for Java GPGPU performance analysis                                                      |

| 5.2. | MaxFlops performance on the NVIDIA K20 GPU (in GFLOPS) $106$                                              |

| 5.3. | MaxFlops performance on the Intel Xeon Phi (in GFLOPS) 111                                                |

| 5.4. | Manual effort for the development of the Aparapi and jCuda implementations of representative SHOC kernels |

| 5.5. | Conceptual effort in MaxFlops                                                                             |

| 5.6. | Conceptual effort in matrix multiplication (GEMM)                                                         |

| 5.7. | Conceptual effort in Stencil2D                                                                            |

| 5.8. | Conceptual effort in FFT                                                                                  |

# List of Figures

| 1.1. | FastMPJ communication devices on shared memory and cluster networks                                                      | 11 |

|------|--------------------------------------------------------------------------------------------------------------------------|----|

| 2.1. | Architecture of an Intel Xeon E5-2670 Sandy Bridge-based system                                                          | 17 |

| 2.2. | Architecture of a Magny-Cours AMD Opteron 6172-based system $$                                                           | 18 |

| 2.3. | Architecture of the Intel Xeon Phi coprocessor                                                                           | 22 |

| 2.4. | Architecture of the Kepler GK110 SMX, basic block of the NVIDIA K20                                                      | 24 |

| 3.1. | Java communications on a dual-core dual processor using distributed (left) and shared (right) memory-oriented middleware | 30 |

| 3.2. | Communication protocols in smdev                                                                                         | 34 |

| 3.3. | Send/Recv operations in smdev                                                                                            | 36 |

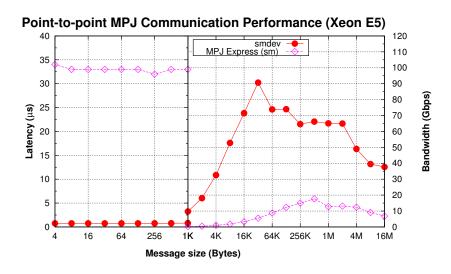

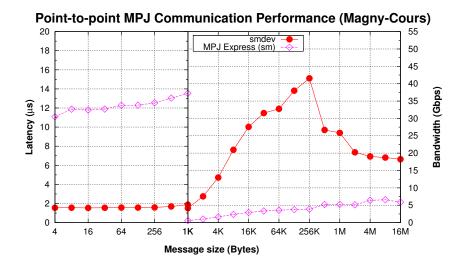

| 3.4. | smdev performance on the Xeon E5                                                                                         | 42 |

| 3.5. | smdev performance on the Magny-Cours                                                                                     | 44 |

| 3.6. | Message Passing in Java performance on the Xeon E5                                                                       | 45 |

| 3.7. | Message Passing in Java performance on the Magny-Cours                                                                   | 45 |

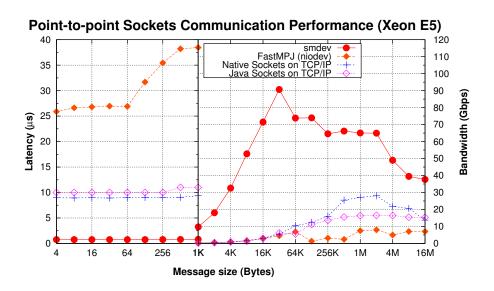

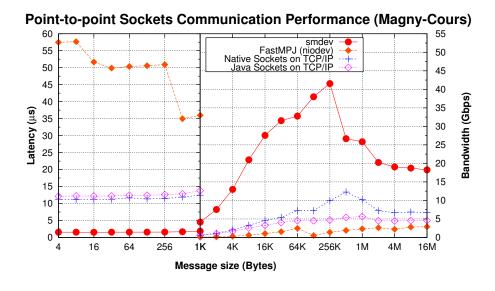

| 3.8. | Sockets performance on the Xeon E5                                                                                       | 46 |

| 3.9. | Sockets performance on the Magny-Cours                                                                                   | 46 |

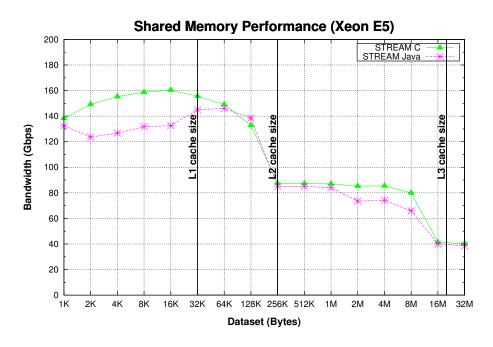

| 3.10. | Memory performance on the Xeon E5                                       | 47 |

|-------|-------------------------------------------------------------------------|----|

| 3.11. | Memory performance on the Magny-Cours                                   | 48 |

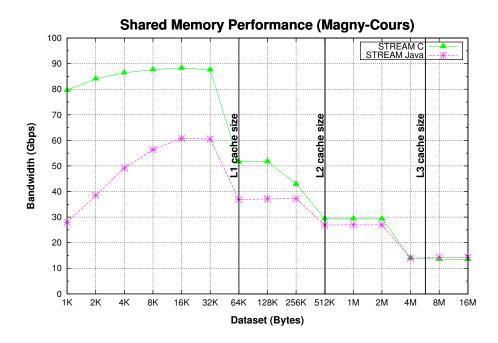

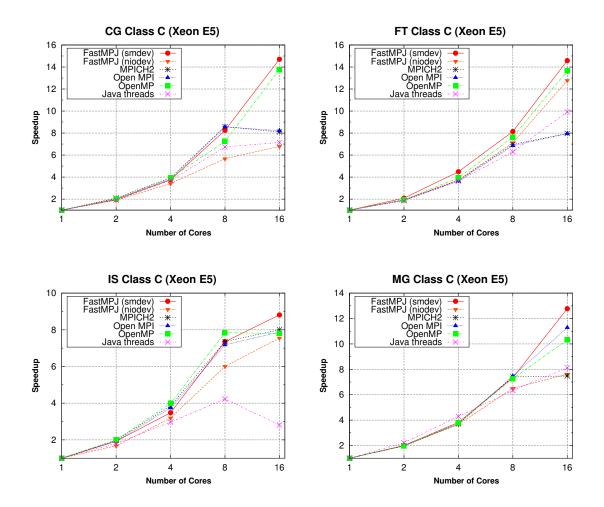

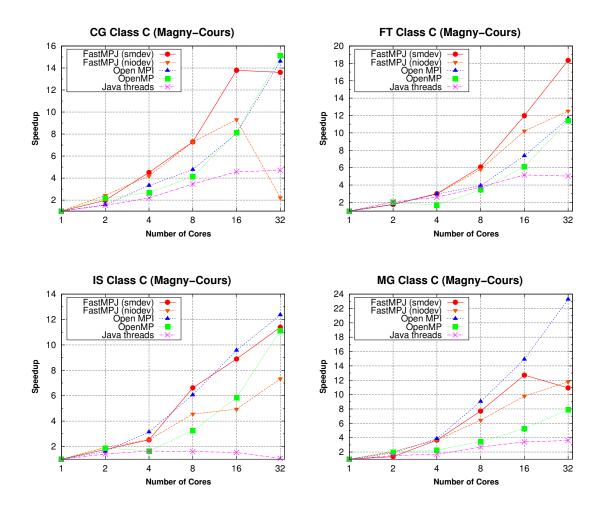

| 3.12. | NAS Parallel Benchmarks performance on the Xeon E5                      | 50 |

| 3.13. | NAS Parallel Benchmaks performance on the Magny-Cours                   | 51 |

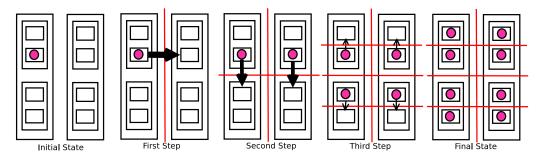

| 4.1.  | Overview of the Broadcast MST algorithm                                 | 60 |

| 4.2.  | Overview of the Gather MST algorithm                                    | 61 |

| 4.3.  | Overview of the Allgather BDE algorithm                                 | 61 |

| 4.4.  | Overview of the Allgather BKT algorithm                                 | 62 |

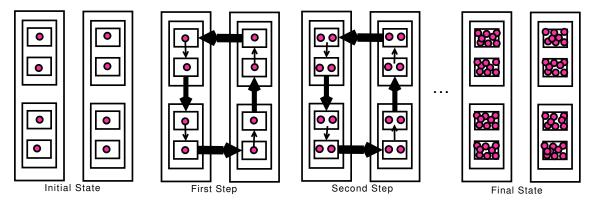

| 4.5.  | Threaded Broadcast                                                      | 65 |

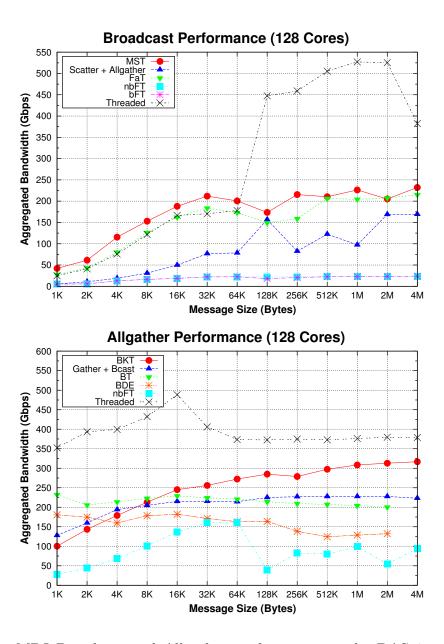

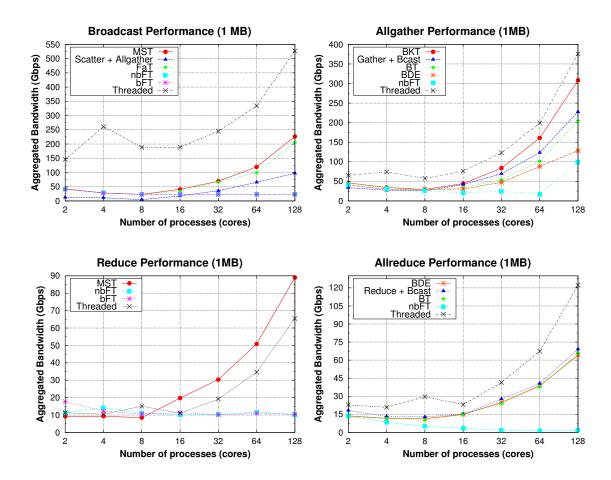

| 4.6.  | MPJ Broadcast and Allgather performance on the DAS-4 multi-core cluster | 71 |

| 4.7.  | MPJ Reduce and Allreduce performance on the DAS-4 multi-core cluster    | 72 |

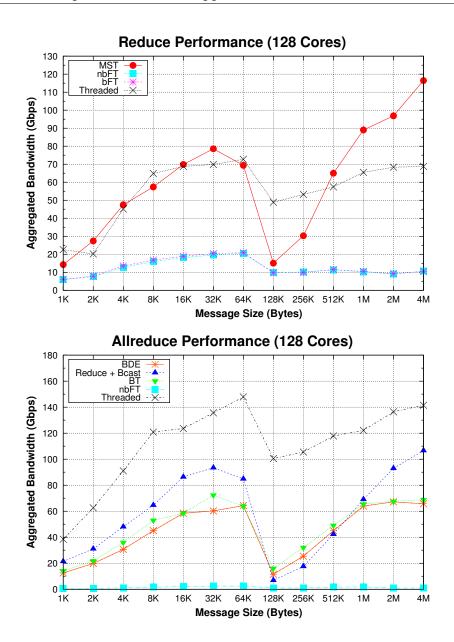

| 4.8.  | Scalability of MPJ collectives for a 1-KByte message                    | 73 |

| 4.9.  | Scalability of MPJ collectives for a 32-KByte message                   | 74 |

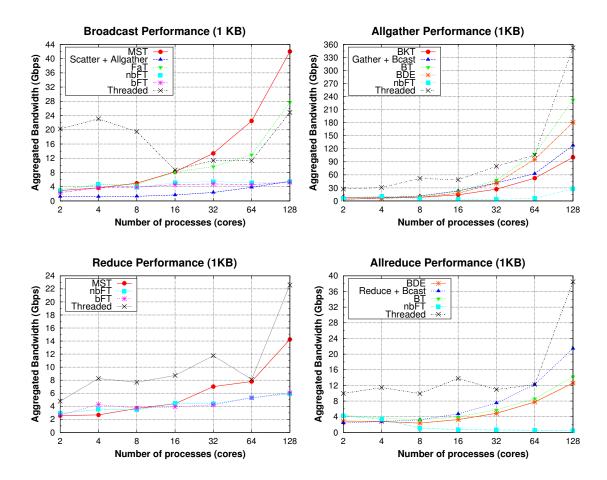

| 4.10. | . Scalability of MPJ collectives for a 1-MByte message                  | 75 |

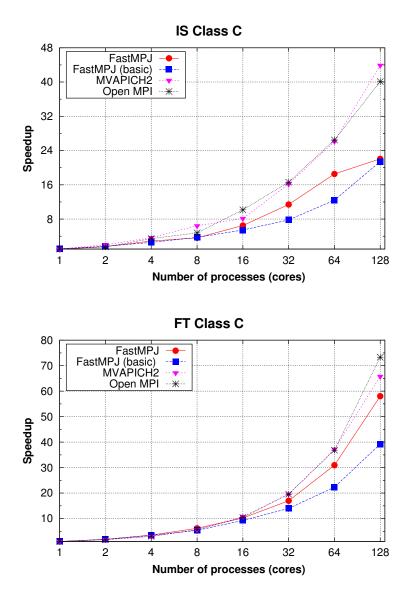

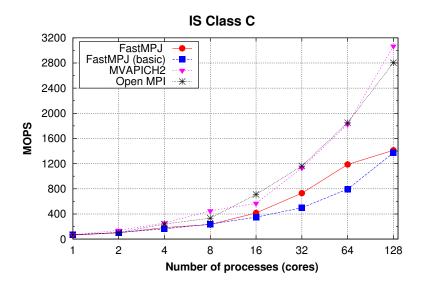

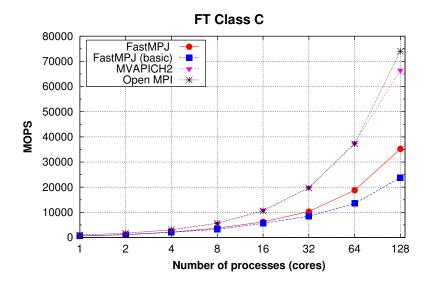

| 4.11. | . Scalability of NPB kernels on the DAS-4 multi-core cluster            | 77 |

| 4.12. | . Performance (in MOPS) of NPB kernels on the DAS-4 multi-core cluster  | 78 |

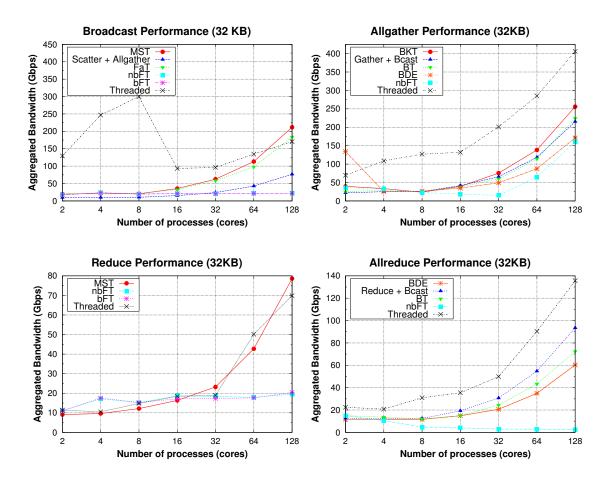

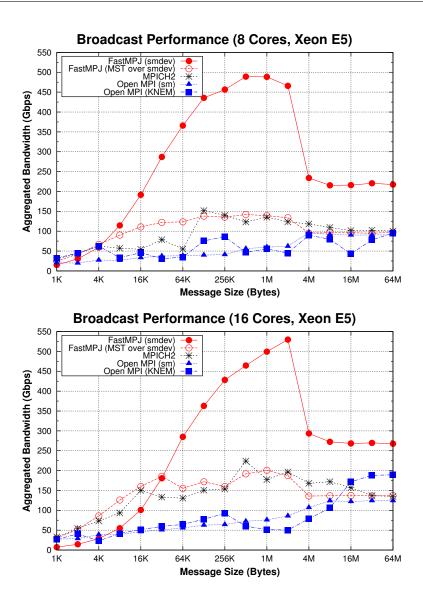

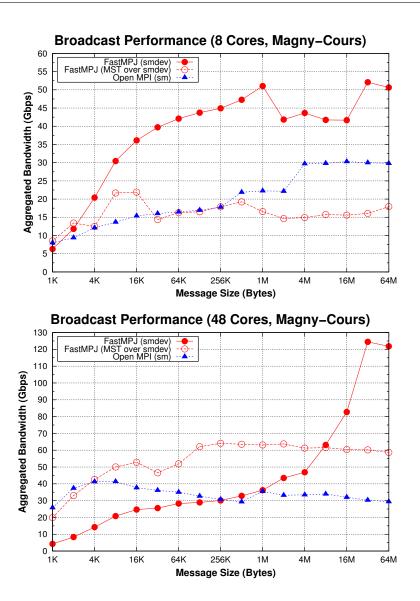

| 4.13. | Broadcast performance on 8 and 16 cores (Xeon E5)                       | 80 |

| 4.14. | . Broadcast performance on 8 and 48 cores (Magny-Cours)                 | 81 |

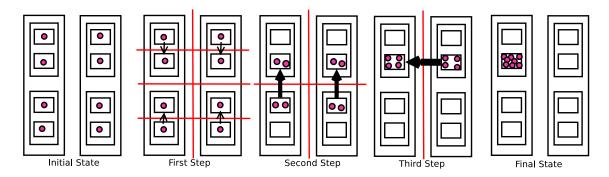

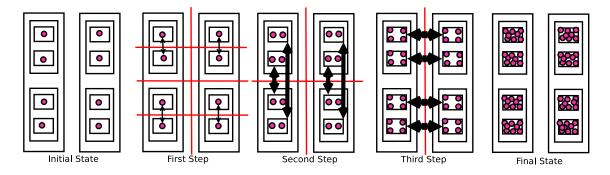

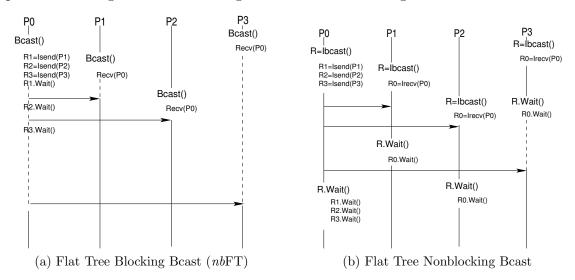

| 4.15. | . Flat Tree-based Blocking and Nonblocking Broadcast implementation     | 87 |

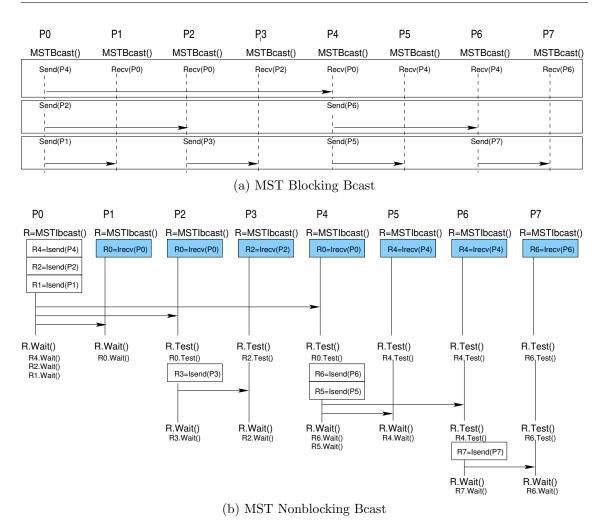

| 4.16. | MST-based Blocking and Nonblocking Broadcast Implementation             | 89 |

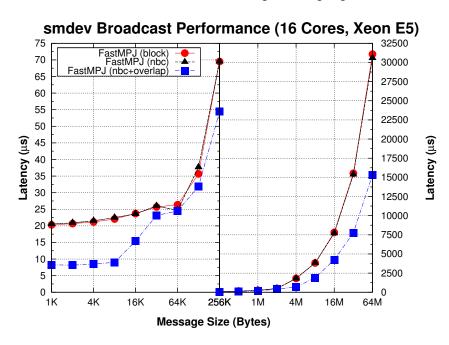

| 4.17. | Shared memory Broadcast: Blocking vs. Nonblocking                       | 94 |

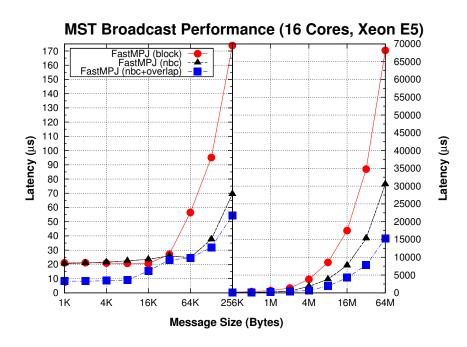

| 4.18. | MST Broadcast vs. Shared memory Nonblocking Broadcast                   | 95 |

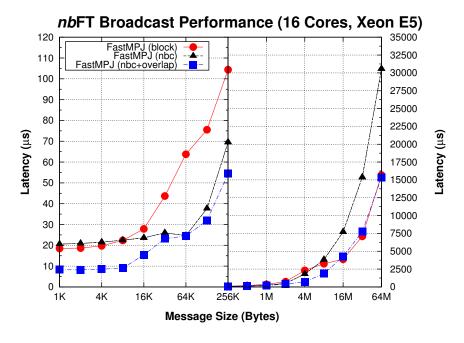

| 4 | 19. $nb$ FT Broadcast vs. Shared memory Nonblocking Broadcast 95                                                               |

|---|--------------------------------------------------------------------------------------------------------------------------------|

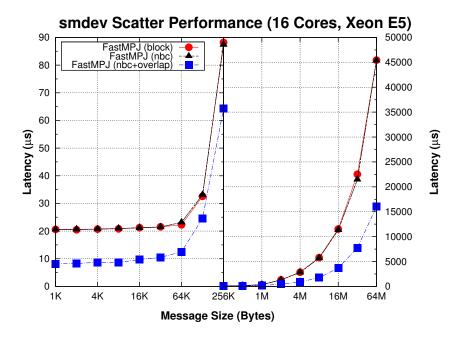

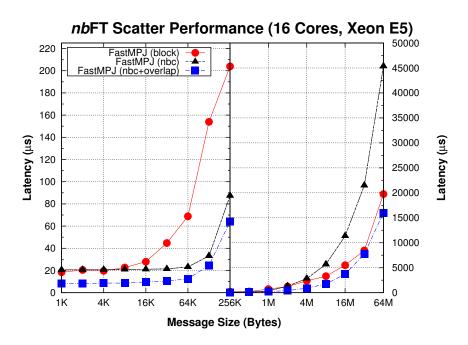

| 4 | 20. Shared memory Scatter: Blocking vs. Nonblocking                                                                            |

| 4 | 21. $nb$ FT Scatter vs. Shared memory Nonblocking Scatter 97                                                                   |

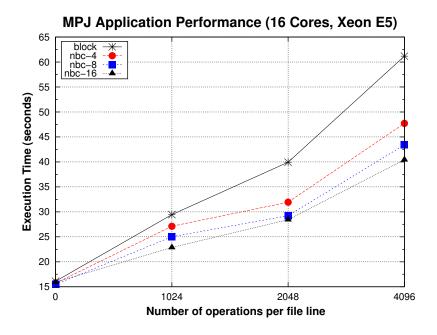

| 4 | 22. Performance comparison of an I/O-intensive MPJ application using Blocking ("block") and Nonblocking ("nbc") collectives 99 |

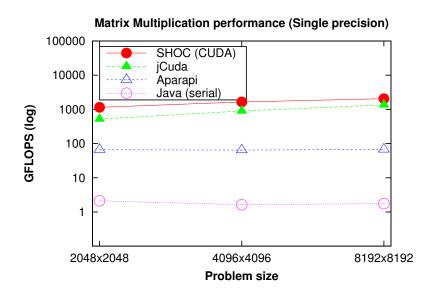

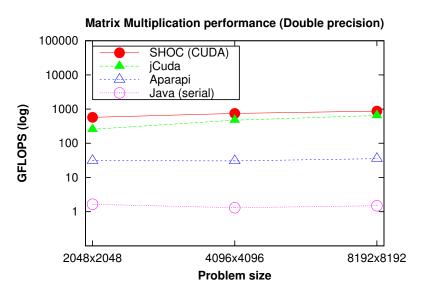

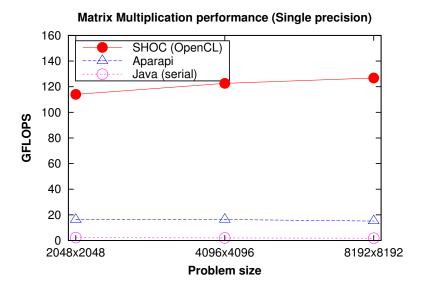

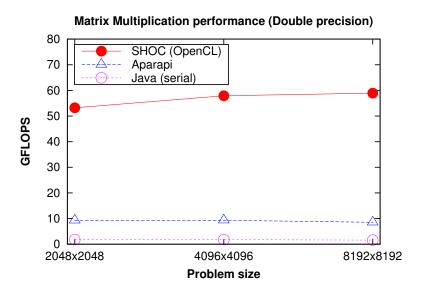

| 5 | 1. Matrix multiplication (GEMM) kernel performance on the NVIDIA K20 GPU                                                       |

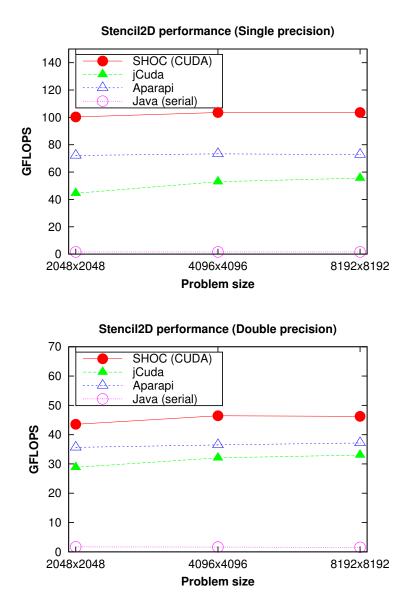

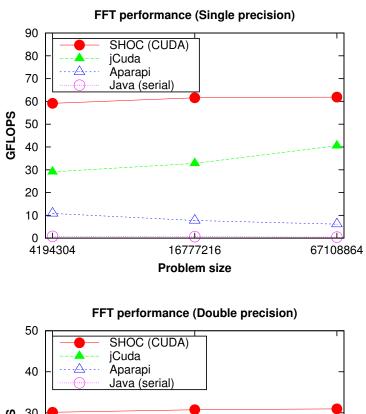

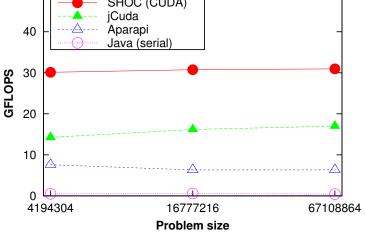

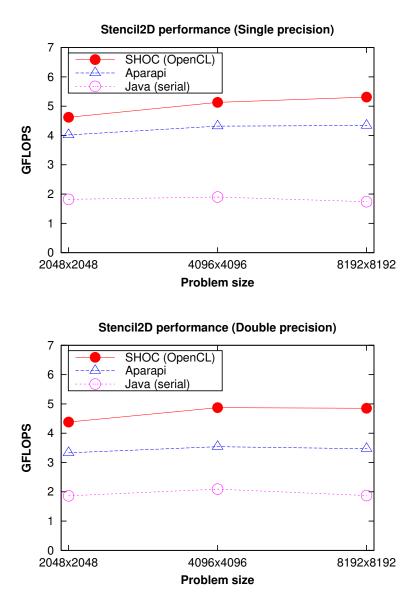

| 5 | 2. Stencil2D kernel performance on the NVIDIA K20 GPU 108                                                                      |

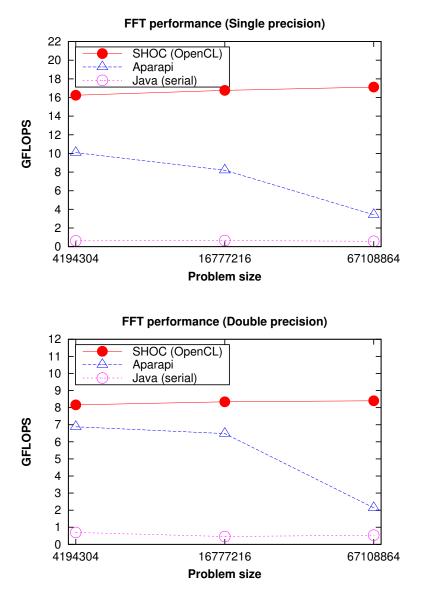

| 5 | 3. FFT kernel performance on the NVIDIA K20 GPU 109                                                                            |

| 5 | 4. Matrix multiplication (GEMM) kernel performance on the Intel Xeon Phi                                                       |

| 5 | 5. Stencil2D kernel performance on the Intel Xeon Phi                                                                          |

| 5 | 6. FFT kernel performance on the Intel Xeon Phi                                                                                |

#### Introduction and Motivation

The Java language has become an interesting choice for High Performance Computing (HPC) due to its significant performance improvements and the features that make it a highly productive language. Among them, it is worth mentioning portability and platform independence, simplicity, robustness, security, object orientation and having a large development community both in industry and academia. Besides performance improvements, there are two crucial properties that favor the adoption of Java for HPC: the network and the multithreading support in the core of the language. These qualities make Java a perfect candidate for parallel programming.

Among current parallel environments, shared memory systems have become very popular due to the physical limits that performance scaling reached in uni-core processors, with dissipation issues and lack of energy efficiency. To overcome these drawbacks, hardware manufacturers increased performance by including more cores per processor, leading to the generalization of multi-core processors. In fact, processors with four or more cores are getting popular in commodity personal computers.

Furthermore, the increase in the number of cores is leading to the spread of many-core processors for general purpose computation. In this area, again, energy consumption emerges as an important concern because the large number of cores causes these processors to be inefficient when only a small amount of cores is needed. To deal with this issue, specific purpose accelerators, such as Graphics Processing Units (GPUs), appeared to offload specific parallel tasks while a host processor tackles general purpose computation. In the case of GPUs, their features and high compute capabilities made them also suitable for streaming programming,

not necessarily related to graphics processing. However, programming difficulties associated with the peculiarities of these accelerators favored the birth of x86-based coprocessors, such as the Intel Xeon Phi, that can be programmed with traditional paradigms and languages.

The success of multi- and many-core architectures points out the need for languages and tools to exploit shared memory performance, where Java, with its intrinsic multithreading support, has a tremendous advantage over other languages. The main drawback is that the threading API is difficult to manage, making the user responsible for dealing with the scheduling of threads, and race conditions and inconsistencies may arise. As a potential solution, Java provides a high-level concurrency library to work with thread pools and oriented to task programming or to a fork/join approach, with load balancing achieved by work-stealing techniques. These paradigms are throughput oriented and parallel algorithms have to be rewritten or programmed directly with the basic threading API.

This PhD Thesis presents a detailed analysis of the state of the art regarding the use of Java in shared memory systems programming, focusing on suitable HPC solutions. The main goals of this work are the analysis of the Java support for shared memory HPC programming and the development of middleware to improve performance and productivity. To achieve this, a thorough review of available libraries for multi-core programming has been carried out. As a result, the Thesis presents the design, implementation and evaluation of a Java message-passing communication device optimized for shared memory. This device provides a high-level message-passing API avoiding the need for managing threads or using a task-based approach. This API follows the Message Passing in Java (MPJ) specification, based on the MPI standard widely used in HPC. Moreover, the Thesis includes an optimization of communication operations among processes or threads (collective operations) for multi-core environments, also providing nonblocking collectives support and a thorough analysis regarding the feasibility of nonblocking collectives for shared memory environments. In addition, this Thesis presents an evaluation of currently available solutions to exploit many-core architectures using Java. The main conclusion is that the use of Java in shared memory environments is highly productive and can provide high performance results, but it is necessary to provide optimized middleware that abstracts multithreading details from the user, like the one proposed in the Thesis,

and the optimization of widely used operations like collective communications.

#### Main Contributions of the Thesis

The main original contributions derived from the Thesis are the following:

- Analysis of the state of the art regarding Java for High Performance Computing (HPC) [121].

- Implementation of an efficient and scalable communication solution for shared memory systems using Java and supporting a message-passing API [108, 109].

- Optimization of blocking collective operations for shared memory and multicore clusters [122].

- Implementation of nonblocking message-passing collectives in Java and performance study on a shared memory system [107].

- Performance and productivity evaluation of available solutions for Java programming in heterogeneous environments with many-core architectures [25, 106].

#### Structure of the Thesis

The Thesis is organized in the following chapters:

Chapter 1, Java for High Performance Computing, summarizes the state of the art regarding Java HPC programming for multi- and many-core systems. Different parallel programming frameworks and tools are studied, focusing on message passing, due to its scalability and extended use in HPC. Moreover, it provides an overview of current heterogeneous programming solutions for Java.

■ Chapter 2, Shared Memory Architectures, analyzes some of the most popular shared memory architectures. First, it provides some insight on architectural aspects of two multi-core processors from the two main manufacturers, Intel and AMD. Then, it goes through similar aspects regarding many-core systems, analyzing the last NVIDIA GPU architecture and the recently released x86-based Intel Xeon Phi.

- Chapter 3, A Shared Memory Communication Device for Message Passing in Java, presents the design, implementation and performance evaluation of a shared memory communication device for message passing in Java. This device provides efficient communications relying on shared memory transfers among threads, instead of processes, using zero-copy protocols and minimizing synchronizations.

- Chapter 4, Efficient Support of Collective Communications in Java, includes a collectives library with blocking and nonblocking operations support and optimizations for multi-core systems. Blocking collectives are optimized not only for shared memory systems, but also for multi-core clusters, exploring the combination of process communication across the network and the use of threads within each node. Moreover, the nonblocking support assesses the feasibility of using nonblocking collectives in Java for shared memory programming.

- Chapter 5, Java Heterogeneous Computing, studies the currently available solutions to program many-core accelerators with Java. It provides a thorough analysis of efficiency and productivity of current projects that allow us to take advantage of these accelerators using Java.

- Finally, the Thesis presents the main conclusions, guidelines and future work derived from the research carried out.

## Chapter 1

# Java for High Performance Computing

Java is the leading programming language both in academia and industry environments. The success of Java is motivated by its appealing features such as built-in networking and multithreading support, automatic memory management, platform independence, portability, security, object orientation, an extensive API and a wide community of developers. Moreover, it is increasingly being adopted by the High Performance Computing (HPC) community [121] due to its improvements in performance, which makes it competitive in comparison with natively compiled languages like C/C++, enabling the use of Java in performance-bounded scenarios.

The physical limits in frequency scaling has favored the trend to increase the number of available cores per processor and the use of specific accelerators and coprocessors to improve performance and energy efficiency. This leads to the need for scalable parallel programming paradigms to exploit the characteristics of the underlying hardware in order to reflect the performance improvements in real applications. Although this is not a new situation since clusters of processors are widely used to build more powerful computers that meet the needs of the HPC community, the particularities of multi-core processors have to be addressed not only in an isolated manner, but also to increase performance on clusters of multi-core processors (e.g., heterogeneity of performance for communications within cores on the same processor and on different processors).

This chapter presents an analysis of the state of the art of HPC programming in Java focusing on solutions for shared memory multi- and many-core systems.

#### 1.1. Parallel Programming in Java

Current trends in hardware evolution make it unavoidable to any HPC language to provide parallel tools that allow programmers to exploit the underlying architectures. Multithreading support in the core of the Java language makes it inherently parallel which, combined with the built-in networking, turns Java into a more than suitable choice for the development of projects that aim to take advantage of parallel architectures [121].

This multithreading support allows Java to exploit shared memory architectures without having to resort to external projects or libraries. Nevertheless, its threading API generally requires low-level programming skills. The concurrency framework, included in the core of the language since Java 1.5, simplifies the management of threads hiding part of the complexity and providing a task-oriented programming paradigm based on thread pools. However, the task management targets the scheduling of a high number of tasks instead of reducing the task start-up time (the initialization overhead). Moreover, it is limited to the execution in parallel of individual tasks, so the developer has to resort to threads for high performance parallel codes, where threads cooperate to reduce the runtime of a workload. Java 1.7 extends the concurrency framework by including the fork/join utilities developed by Doug Lea [70] to favor parallel programming oriented to the fragmentation of a complex problem into recursive tasks following the divide-and-conquer strategy. The fork/join structure is based on work-stealing techniques that automatically balance the workload among the available threads.

However, codes developed using threads or tasks cannot run on distributed memory environments, as it happens for the traditional approach followed in compiled languages, such as C/C++, with the use of shared memory models like POSIX threads (Pthreads) or OpenMP directives. In order to overcome this limitation, natively compiled languages resort to several tools that execute multithreaded applications on distributed memory architectures but, up to now, either their imple-

mentation is based on software translations to message-passing models like MPI [11] or it relies on Distributed Shared Memory (DSM) systems [84]. Another option is the use of a hybrid shared/distributed memory programming model combining MPI for inter-node communications and a shared memory model to take advantage of intra-node parallelism [143]. Additionally, new programming paradigms such as PGAS (Partitioned Global Address Space) arise for programming hybrid shared/distributed memory systems, although generally their performance is lower than MPI [78]. In Java, the use of Java DSM implementations generally involves portability issues due to the need for modified Java Virtual Machines (JVMs). The Parallel Java project [58] provides several abstractions over the concurrency utilities, also implementing the message-passing paradigm for distributed memory but with its own interface instead of a standard one like MPI. There are also OpenMP-like Java implementations such as JOMP [16] and JaMP [63]. Both systems are "pure" Java and thread-based, but the second one also takes advantage of concurrency utilities overcoming some efficiency problems of JOMP. JaMP is part of Jackal [141], a software-based Java DSM implementation, and its main drawback is the lack of portability since it cannot run on standard JVMs.

Java communication middleware, such as Java Message Service (JMS) and Remote Method Invocation (RMI), always resort to JVM sockets, which currently have two implementations: the standard I/O sockets (the counterpart of the widely available POSIX sockets), and the New I/O (NIO) sockets, an implementation focused on the scalability of communications in servers introduced in Java 1.4. However, programming with sockets requires a significant effort due to their low-level API. Moreover, performance is generally limited as sockets rely on TCP/IP. In order to overcome these limitations, parallel programmers generally develop their codes using message-passing libraries, which provide a higher-level API, scalability and relatively good performance.

Another project, recently released, that provides high performance capabilities in Java is Disruptor [132], based on a cyclic queue (or ring buffer) and a consumer-provider programming paradigm. Disruptor aims to provide a low-latency and high-throughput solution for data interchange among threads, taking into account low-level features such as cache sizes and lock-free strategies.

#### 1.1.1. High Performance Utilities in Java

There are also other tools that support HPC programming although they are not intrinsically parallel. The best example are mathematical libraries, very useful especially on scientific environments. Although it has been proven that Java is able to compete with Fortran in high performance numerical computing [12, 54, 85], the development of a competitive numerical Java library is still an ongoing effort. In fact, in [7] the authors evaluate Java for numerical computing showing that the performance of Java can be significantly enhanced by delegating numerically intensive tasks to native libraries such as Intel MKL. There are some active projects that tackle different numerical operations, such as the Universal Java Matrix Package (UJMP) [5, 140], the Efficient Java Matrix Library (EJML) [27], the Matrix Toolkits Java (MTJ) [81], the Java Algebra System (JAS) Project [64, 65] and jblas [74], which are replacing more traditional frameworks like JAMA [52].

Another useful tool for HPC is the data management support in terms of collections and optimizations of common operations like insertion, sort, deletion, etc. In this field, there are several projects that attempt to provide with high performance collections, such as the High Performance Primitive Collections for Java (HPPC) [47] or TROVE [137]. However, some of them have programmability or thread-safety limitations.

#### 1.2. Message Passing in Java (MPJ)

Message passing is the most widely used parallel programming paradigm as it is highly portable, scalable and usually provides good performance. It is the preferred choice for parallel programming in distributed memory systems such as clusters, and it is becoming popular also for shared memory architectures with a high number of cores or threads, due to its scalability, flexibility and interesting cost/performance ratio.

MPI is the standard message-passing interface for languages compiled to native code (e.g., C and Fortran). Regarding Java, there have been several implementations of message-passing libraries from its inception [121]. Although initially each project

developed its own MPI-like binding for the Java language, current projects generally adhere to one of the two main proposed APIs: (1) the mpiJava 1.2 API [20], which supports an MPI C++-like interface for the MPI 1.1 subset, and (2) the JGF MPJ API [8], which is the proposal of the Java Grande Forum (JGF) [53] to standardize the MPI-like Java API. The collective communication primitives are essential part of the different MPJ APIs, both in terms of number of methods and widespread use.

MPJ libraries can be implemented in two ways: (1) wrapping an underlying native messaging library like MPI through the Java Native Interface (JNI); or (2) using a "pure" Java (100% Java) approach, based on RMI or sockets. Each solution fits with specific situations, but presents associated trade-offs. On the one hand, the use of the pure Java approach ensures portability, but it might not be the most efficient solution, especially in the presence of high-speed communication hardware and when using RMI or JMS, as these technologies are oriented to distributed computing on loosely coupled peers and show high start-up latencies. On the other hand, the use of JNI has portability problems, although usually in exchange for higher performance.

The mpiJava library [9] is a wrapper implementation which provides efficient communication resorting to an underlying native MPI library, adding a reduced JNI overhead. However, despite its usually high performance, mpiJava currently only supports some native MPI implementations, as wrapping a wide number of functions (especially the collectives) and heterogeneous runtime environments entails an important maintenance effort. Additionally, this implementation presents instability problems, derived from the native code wrapping, and it is not thread-safe, being unable to take advantage of multi-core systems through multithreading.

As a result of these drawbacks, the mpiJava project maintenance has been superseded by the development of MPJ Express [116], a "pure" Java message-passing implementation of the mpiJava 1.2 API specification. MPJ Express is thread-safe and presents a modular design which includes a pluggable architecture of communication devices that allows to combine the portability of the "pure" Java NIO communications (niodev device) with a high performance Myrinet support (through the native Myrinet eXpress –MX– communication library in the mxdev device), and a specific device for shared memory. Furthermore, this project is the most active in terms of adoption by the HPC community, presence in academia and production environ-

ments, and available documentation. The project is also stable and publicly available along with its source code at http://sourceforge.net/projects/mpjexpress/.

There are additional MPJ implementations, such as MPJ/Ibis [13], based on the JGF API. This library supports "pure" Java and native communications on Myrinet. In addition, they use two low-level communication devices based on Ibis: TCPIbis, based on Java IO sockets (TCP/IP), and NIOIbis, which provides blocking and nonblocking communications through Java NIO sockets. Nevertheless, it lacks thread safety and provides limited performance.

The increasing interest in Java is also evidenced by the recent efforts of Open MPI [128, 129], one of the main open source MPI projects, that has announced its Java interface motivated by a request of the Hadoop community. While it is still bounded to the MPI 1.2 API (using the mpiJava 1.2 API and the mpiJava library bindings), they plan to extend it to the full MPI 3.0 specification. Although this Java support could benefit from a large community of users and developers, and from the highly optimized MPI support of Open MPI, it is still a wrapper to a native implementation with no pure Java support, thus lacking portability and with instability issues that has put off its release until these issues are solved.

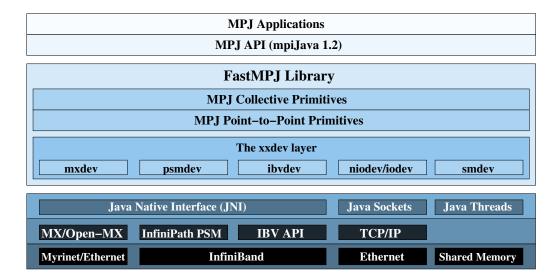

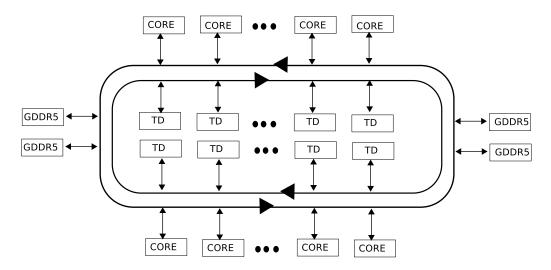

The most recent "pure" Java MPJ project is our FastMPJ library [29, 123], with a modular design that can be seen in Figure 1.1. It is similar to MPJ Express, which has a pluggable architecture of communication devices that allows to combine the portability of the "pure" Java communication devices with high performance network support wrapping native communication libraries through JNI. Figure 1.1 shows the communication support implemented in FastMPJ, either on JVM threads (smdev), sockets over the TCP/IP stack (niodev and iodev), or on native communication layers such as Open-MX (mxdev), InfiniPath PSM (psmdev) and InfiniBand Verbs (IBV) (ibvdev), which are accessed through JNI. The main advantages over MPJ Express are the more stable runtime framework and higher performance and scalability.

Figure 1.1: FastMPJ communication devices on shared memory and cluster networks

#### 1.3. Heterogeneous Programming in Java

Besides multi-core processors, another successful trend in hardware development is the inclusion of coprocessors to increase the performance of specific regions of parallel codes. Most of them are composed by a large number of small and specialized cores, such as the Graphics Processing Units or GPUs. These accelerators provide high performance and energy efficiency since they are external units only used when necessary.

The most popular coprocessors are the GPUs, with a heavy and increasing presence in the Top 500 list of supercomputers [134]. The massively parallel architecture of the GPU, together with its floating point capability, has motivated the growth of GPGPU (General Purpose computing on GPU) [71], along with different programming models, such as Compute Unified Device Architecture (CUDA) [91] or Open Computing Language (OpenCL) [120], to enable the use of GPUs as many-core accelerators for non-graphics workloads. Hence, the adoption of GPUs as accelerators in HPC environments [34] is increasing, since many scientific applications present a huge degree of parallelism that can take advantage of GPU's features.

The recently released Intel Xeon Phi, from the Intel MIC family, aims to share this popularity by providing many-core coprocessors with a x86 architecture to enable the use of traditional programming languages and paradigms to exploit its performance. As the Xeon Phi accelerator has just been released, there is no Java support yet, although given its architecture it should be possible to have JVMs running in this system in the short term. Moreover, it supports traditional shared memory programming paradigms, including OpenCL, allowing it to be used as a mere coprocessor with OpenCL accessed via JNI.

Unfortunately, this situation is not exclusive of the Xeon Phi accelerator. GPGPU programming models are provided as libraries and intended to be used as C/C++ extensions, whereas languages like Java must resort to wrappers (via JNI) to be able to take advantage of GPUs as accelerators. This has motivated the growth of several projects that aim to ease Java GPGPU programming by providing frameworks to deal with C/C++ extensions. Moreover, there is an ongoing effort within the OpenJDK community, together with Oracle and AMD, to include GPGPU support directly in the JVM [96].

Among the Java GPGPU projects, we can distinguish two approaches: the ones that provide Java bindings to a lower-level language (CUDA or OpenCL), or those with a user-friendly API that abstracts GPU programming along with a runtime system which translates Java bytecode into CUDA or OpenCL in a transparent manner. While Java bindings are meant to provide better performance, the second approach makes it possible to find a trade-off between performance and productivity.

Table 1.1 summarizes the most relevant projects for GPGPU computing in Java classified by the underlying native library used. Among the CUDA-related projects, JCUDA [144] has its own interface to invoke certain CUDA functions and user developed kernels. Nevertheless, it is not included in the "User-friendly projects" group since it still requires low-level programming skills and certain knowledge of CUDA functions.

jCuda [55] is the most active Java GPGPU project. It provides a direct wrapper over CUDA 4.2 runtime and driver API, allowing the direct interaction with the device, including memory management, and providing support to launch CUDA kernels from Java. The main strength of this project is that it provides support for several optimized libraries from CUDA like CUBLAS (CUDA Basic Linear Algebra Subprograms), CUFFT (Fast Fourier Transforms), CUDPP (Data Parallel Prim-

|        | Java bindings    | User-friendly projects |

|--------|------------------|------------------------|

| CUDA   | JCUDA [144]      | Java-GPU [18]          |

|        | jCuda [55]       | Rootbeer [104]         |

| OpenCL | JOCL [56]        | Aparapi [4]            |

|        | JogAmp JOCL [57] |                        |

Table 1.1: Available solutions for GPGPU computing in Java

itives), CURAND (Random Number Generation), CUSPARSE (Sparse Matrices) and NPP (NVIDIA Performance Primitives). The jCuda API consists of a group of static methods which are very similar to the native library functions since the aim of jCuda is to keep the API as close to the original as possible, including also functions in order to use user defined kernels in CUDA language, as well as pointer handling functions.

Java-GPU [18] introduces directives to offload Java code into the GPU, whereas Rootbeer [104], which has recently been published, provides a specific high-level API for Java and translates the generated bytecode into CUDA.

Java OpenCL binding solutions include JOCL [56] and JogAmp JOCL [57]. The main difference between them is that while the former provides support for OpenCL 1.2, the latter only handles OpenCL 1.1.

Finally, Aparapi [4] is the most up-to-date Java OpenCL project and provides OpenCL 1.2 support. The Aparapi programmer is provided with a high-level API to express data parallel workloads in Java, being released from all the GPU implementation details. Nevertheless, in order to obtain higher performance, the user must be aware of some architectural details, although no OpenCL knowledge is needed. The runtime system translates Java parallel workloads to OpenCL and offload them on an OpenCL device (a GPU or a CPU) or on a pool of threads (in this case, no translation is needed). Aparapi is supported by AMD and its source code has been released with a GPL license.

## Chapter 2

## **Shared Memory Architectures**

The lack of frequency scaling has motivated the increase in the number of cores per processor, and thus current shared memory architectures aim to provide higher computational power by the aggregation of smaller processing units. In this chapter, in order to analyze the shared memory architectures used in this Thesis, we have classified them in multi- and many-core processors. Although it is not clear the number of cores that determine the division, we considered as multi-core the stand-alone processors, i.e., those providing parallel features by the combination of general purpose cores. And, as many-core, accelerators or coprocessors with an aggregation of specific purpose cores that are not expected to be efficient for sequential computation.

#### 2.1. Multi-core Architectures

Multi-core architectures appeared as a solution to the lack of power scaling and dissipation issues that arose when trying to increase the clock frequency on unicore processors. Thus, multi-core systems provide more computational power by combining several processing cores within the same chip. Some of them can also be combined within a node using high-speed connectors such as the Intel QuickPath Interconnect (QPI) or the AMD HyperTransport (HT) technology.

Usually, these cores are arranged as NUMA systems where the cores within the

same chip get access to the memory regions through a shared bus. When there are several processes connected by QPI or HT, cores from one processor have to go through these links to access the NUMA regions of another processor, thus experiencing a higher access overhead. Within each chip, cores are linked in different manners, e.g., Intel Nehalem uses a crossbar system, which is highly efficient but not scalable in terms of cost, and Intel Sandy Bridge uses a ring bus which is slower but more scalable. Another feature of these multi-core architectures is that cache coherency is kept in each node (using links among processors with this purpose). Usually, cores have some private caches and a larger shared cache used to maintain coherency within each processor.

The rest of this section focuses on describing two representative up-to-date multicore systems, based on the Intel Sandy Bridge (Xeon E5) and on the AMD Magny-Cours. Both of them will also be used for the performance evaluation of the libraries developed in this Thesis, along with others with similar characteristics, so their main architectural features are detailed. On the one hand, the Xeon E5 processor presents a quite recent micro-architecture (Intel Sandy Bridge) for high performance shared memory systems, achieving up to 20.8 GFlops of peak performance per CPU core in the model used (2.6 GHz), which represents one of the best peak performances per core amongst the currently available systems. On the other hand, the 48-core Magny-Cours-based system has one of the highest aggregated performance numbers in a shared memory system (403.2 GFlops), although its performance per core is quite reduced (8.4 GFlops). Hence, the Xeon E5 system has allowed us to analyze a quite recent Intel micro-architecture, whereas the Magny-Cours system presents the issues associated with the integration of multiple multi-core processors.

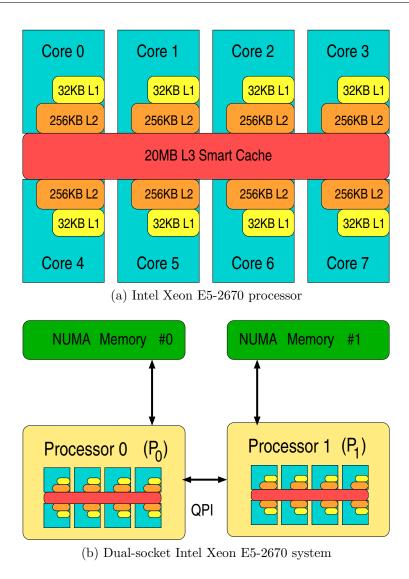

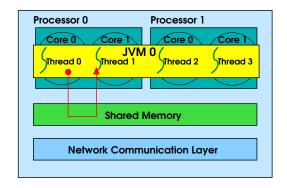

Figure 2.1a presents the layout of an 8-core Xeon E5 processor, based on the Sandy Bridge-EP architecture, where up to 16 threads can run simultaneously thanks to hyperthreading. The eight cores in this processor share the L3 cache (called LLC or Last Level Cache), implemented as an Intel Smart Cache, where each core can access the whole cache when the rest of the cores are idle. This cache is divided in physical slices connected to an internal ring bus. Figure 2.1b shows the interconnection layout in a dual-socket Intel Xeon E5-2670 system where the processors and the memory are linked by a QuickPath Interconnect (QPI). This NUMA system supports DDR3-1600 MHz memory.

Figure 2.1: Architecture of an Intel Xeon E5-2670 Sandy Bridge-based system

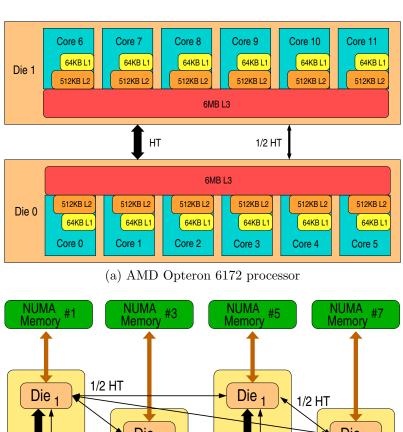

The second system, a fat node from the DAS-4 cluster [24], has 48 cores in 4 AMD Opteron 6172 processors (Magny-Cours), each one with 12 cores [3, 77] and 128 GBytes of RAM. Figure 2.2a presents the layout of the 12-core Magny-Cours processor, which is composed of two 6-core AMD Opteron Istanbul dies (the 6 cores share the L3 cache) interconnected by HyperTransport (HT) links. Figure 2.2b shows the HT interconnections between the different dies as well as the direct access of each die to its memory region with DDR3-1333 MHz support. Thin arrows represent half HT links (8 bits), whereas thick ones represent full HT links (16

bits). As each 12-core processor is a NUMA system with 2 NUMA regions, this quad-socket system has eight NUMA regions.

Figure 2.2: Architecture of a Magny-Cours AMD Opteron 6172-based system

#### 2.1.1. Thread Affinity Control in Java

A consequence of the popularization of NUMA architectures for multi-core systems is that the control of the location of running threads within a node or a processor can have significant effects on performance. For instance, if two threads are communicating through shared memory transfers and they share the last level of cache, transfers will go through this cache instead of across an interconnection link.

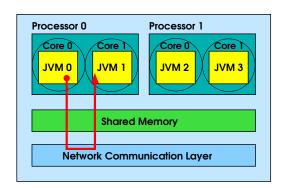

If the communication is performed between two JVMs (thus between two different processes), OS utilities can be used when launching the processes to state the core in which each process is running (e.g., the numactl tool can be used in UNIX). However, when using threads within a single JVM, these tools only support to bound the JVM execution to a set of cores, but the thread mapping within this set is managed internally by the JVM. Thus, if a more accurate mapping is needed, such as a thread-to-core mapping, it would have to be controlled by the application.

Unfortunately, Java does not provide any affinity or pinning control over threads. Nevertheless, JVM threads are directly mapped to native OS threads and, taking advantage of this property, it was possible to develop an affinity tool in order to enable a fine-grained thread mapping control within the JVM. This tool accesses native OS primitives (in particular, pthread\_setaffinity\_np) through JNI, thus supporting affinity management in a Java multithreaded application. In the experimental evaluations included in the following chapters, this tool will be used to improve performance by defining optimal thread-to-core mappings. In fact, in the next chapter, the effects of thread mapping will be evaluated and analyzed in detail.

#### 2.2. Many-core Architectures

Multi-core processors provide high aggregated computational performance but, when the number of cores is large, the probabilities of taking full advantage of all cores at the same time are reduced, because parallel codes have also sequential parts and many of them cannot exploit all the potential provided by a multi-core processor more than in a small portion of the code. A more common situation is a parallel code with unbalanced and heterogeneous parts that will not take advantage

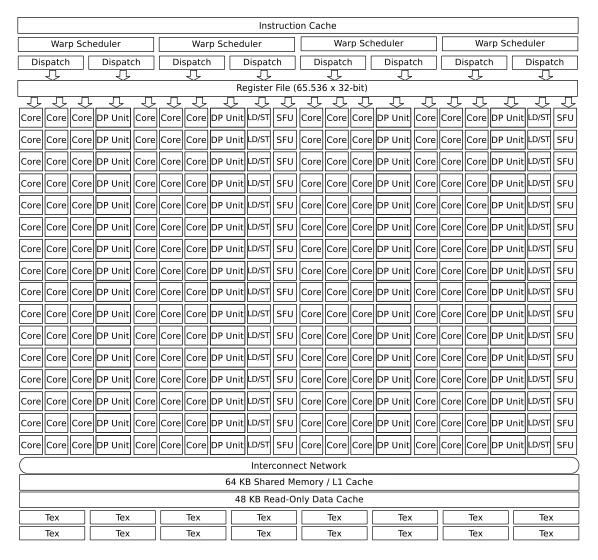

of having several similar cores. In this scenario, having a large number of cores is highly inefficient in terms of energy consumption, and even in terms of cost because it could be solved by having a cheaper set of smaller cores that provide a specific functionality. This is the aim of many-core accelerators or coprocessors. They provide massively parallel architectures with simple computing units or cores to accelerate sections of an application that is run in a general purpose processor. Among these many-core architectures, this section is focused on two of them that are highly interesting: the Intel Xeon Phi, the main accelerator with a x86 architecture, and the GPUs (specifically, the Kepler architecture), which are currently present in the most powerful supercomputers [134].

#### 2.2.1. Many-core x86 Architectures: Intel Xeon Phi

The Intel Xeon Phi is the latest and most scalable many-core x86 coprocessor. It is the first commercial product of the MIC (Many Integrated Cores) architecture, and reflects the efforts made by Intel to develop a many-core coprocessor. The main goal was to provide an accelerator to be programmed with traditional paradigms and languages, avoiding the need to resort to GPGPU computing and complex programming models. This approach was also explored by the IBM Cell Broadband Engine [49], which implemented a new architecture also used in popular video game consoles such as Sony's PlayStation3 and that even reached the 1st position in the Top 500 list [134] in June 2008 with the IBM Roadrunner, but finished its production in 2009.

The precursor of the Xeon Phi is the Larrabee architecture [115], a project that started in 2006 (it was canceled in 2010) and aimed to provide, in a single chip, a combination of GPU and vector accelerator (64-byte VPU unit with scatter and gather loads/stores and mask registers) with a bidirectional ring bus (512 bits per direction), private L1 and 256-KByte L2 sliced caches. Moreover, it implemented the support for running 4 threads per core in some sort of Intel hyperthreading. However, as the performance obtained was below the expected results, the chip was never commercialized. Although the Xeon Phi has inherited most of its features, the main changes are the lack of graphics processing support, the OS running on the coprocessor instead of on the host and that main memory is GDDR5 (it was

#### DRAM on Larrabee).

In the meantime (around 2009), Intel was also involved in the development of the Single-chip Cloud Computer (SCC) processor [100], with multiple independent cores (48) without cache coherency and interconnected with a 2D mesh network. The cores (Pentium I P54C at 800 MHz) have 16-KByte L1 and 256-KByte L2 caches and access to off-chip private DDR3 memories (physically shared). The cores are organized in tiles that contain two cores and a message-passing buffer (MPB, 8 KBytes), and each tile is connected to a router. The main goal of this architecture was to achieve high scalability, but it turned out to be harder to program than a cache coherent architecture.