## DUAL-INPUT DC-TO-DC CONVERTER TOPOLOGIES AND CONTROL SCHEMES

by

Shaun Alan Stickel

A thesis

submitted in partial fulfillment

of the requirements for the degree of

Master of Science in Electrical Engineering

Boise State University

December 2015

© 2015

Shaun Alan Stickel

## ALL RIGHTS RESERVED

## BOISE STATE UNIVERSITY GRADUATE COLLEGE

## DEFENSE COMMITTEE AND FINAL READING APPROVALS

of the thesis submitted by

Shaun Alan Stickel

Thesis Title: Dual-Input DC-to-DC Converter Topologies and Control Schemes

Date of Final Oral Examination: 15 October 2015

The following individuals read and discussed the thesis submitted by student Shaun Alan Stickel, and they evaluated his presentation and response to questions during the final oral examination. They found that the student passed the final oral examination.

| Said Ahmed-Zaid, Ph.D. | Chair, Supervisory Committee  |

|------------------------|-------------------------------|

| Vishal Saxena, Ph.D.   | Member, Supervisory Committee |

| Kurtis Cantley, Ph.D.  | Member, Supervisory Committee |

The final reading approval of the thesis was granted by Said Ahmed-Zaid, Ph.D., Chair of the Supervisory Committee. The thesis was approved for the Graduate College by John R. Pelton, Ph.D., Dean of the Graduate College.

# ACKNOWLEDGEMENTS

Dr. Said Ahmed-Zaid

Dr. Vishal Saxena

Dr. Kurtis Cantley

### AUTOBIOGRAPHICAL SKETCH OF AUTHOR

Shaun Stickel attended Oregon State University from 2004 through 2010 and received two bachelor's degrees. His first degree in electrical engineering emphasized analog circuit design and power electronics, and the second in computer engineering with a minor in computer science emphasized embedded systems. While at Oregon State University, Shaun participated in the MECOP program, which included two internships. The first internship was at Micro Power Electronics from April 2007 to September 2007, developing battery management PCBAs for medical applications. His second internship was at Intel Corporation developing test hardware for video products from June 2008 to January 2009.

In June of 2010, Shaun started at Micron Technology as a product engineer working on the development of enterprise PCIe SSDs. During his first year at Micron, his responsibilities were focused on test script development and automation of performance testing. In 2011, Shaun moved to the SSD hardware design group at Micron and since then has lead the design of multiple enterprise PCIe SSDs including the Micron P420m.

In August of 2010, Shaun started his master's program at Boise State University, pursuing a master's of engineering in electrical engineering. The first four years consisted of coursework focused on analog circuit design, high speed interface design, and digital systems. In 2014, work on his master's thesis began based upon previous work done investigating the viability of dual input power supplies.

v

### ABSTRACT

Dual-input DC-to-DC converters are power supplies that draw power from two sources simultaneously and deliver power to a single load, the ratio of power drawn from each source and be held constant with changes in the load. Applications for dual-input power supplies are computer systems, mobile systems using energy harvesting, and systems needing redundant power supplies. This writing covers the operation and control of dual-input DC-to-DC converters that implement a non-inverting buck-boost function and utilize only a single power path.

Traditionally, a dual-input power supply is created by placing two standard power paths in parallel. This adds considerable control complexity associated with synchronizing the two converters. Four new power path topologies are presented: dualinput four-FET buck-boost, dual-input zeta, dual-input SEPIC, and alternate dual-input SEPIC. The single power path approaches require fewer components than the traditional approaches, however, the efficiency is slightly lower.

These converters can be controlled using any of the standard power supply control approaches, including: voltage mode, current mode, and constant on-time. Each control method does need to be modified slightly. The biggest difference in the control of these converters is in the logic that is used to control the switches in the power path. The ratio of current drawn from each input source can be held constant and can be adjusted in an open loop fashion if some variability is allowed, otherwise a sensor and feedback control can be implemented to fix the input current or input power ratio.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTS iv                                                        |

|----------------------------------------------------------------------------|

| AUTOBIOGRAPHICAL SKETCH OF AUTHOR v                                        |

| ABSTRACTvi                                                                 |

| LIST OF TABLES x                                                           |

| LIST OF FIGURES xii                                                        |

| LIST OF ABBREVIATIONSxviii                                                 |

| CHAPTER ONE: INTRODUCTION TO DUAL-INPUT DC-TO-DC CONVERTERS 1              |

| Topic Overview1                                                            |

| Applications for Dual-Input DC-to-DC Converters                            |

| Computer System Applications for Dual-Input DC-to-DC Converters            |

| Battery Equipped System Applications for Dual-Input DC-to-DC<br>Converters |

| Redundant Power Source Applications for Dual-Input DC-to-DC<br>Converters  |

| Thesis Scope                                                               |

| Definitions and Terminology                                                |

| CHAPTER TWO: BACKGROUND ON DC-TO-DC CONVERTERS 10                          |

| Theory of Operation10                                                      |

| Power Path                                                                 |

| The Four-FET Buck-Boost Converter14                                        |

| The SEPIC Converter                                      | 20 |

|----------------------------------------------------------|----|

| The Zeta Converter                                       | 23 |

| Control Scheme                                           | 25 |

| Voltage Mode Control                                     | 26 |

| Current Mode Control                                     | 27 |

| Constant On-Time Control                                 | 27 |

| CHAPTER THREE: DUAL-INPUT DC-TO-DC CONVERTER POWER PATHS | 29 |

| Traditional Approach                                     | 32 |

| Dual-Input Four-FET Buck-Boost                           | 35 |

| Dual-Input Zeta Converter                                | 41 |

| Dual-Input SEPIC Converter                               | 46 |

| Alternate Dual-Input SEPIC Converter                     | 52 |

| Power Path Comparison                                    | 57 |

| CHAPTER FOUR: DUAL-INPUT DC-DC CONVERTER CONTROL SCHEMES | 74 |

| Input Current Ratio Control                              | 74 |

| Voltage Mode Control                                     | 83 |

| Current Mode Control                                     | 86 |

| Constant On-Time Control                                 | 88 |

| CHAPTER FIVE: DESIGN EXAMPLE                             | 92 |

| Design Overview                                          | 92 |

| Requirements                                             | 92 |

| Power Path                                               | 93 |

| Logic Block                                              | 96 |

| Analog Control           |     |

|--------------------------|-----|

| Characterization Results | 100 |

| CHAPTER SIX: CONCLUSION  | 105 |

| BIBLIOGRAPHY             | 108 |

## LIST OF TABLES

| Table 1.  | Based System Power Utilization by Interface                                                    | 5  |

|-----------|------------------------------------------------------------------------------------------------|----|

| Table 2.  | Equations for Losses in Four-FET Buck-Boost DC-to-DC Converter in Full Buck-Boost Mode         | 17 |

| Table 3.  | Equations for Losses in Four-FET Buck-Boost DC-to-DC Converter in<br>Hybrid Buck or Boost Mode | 20 |

| Table 4.  | Losses in a SEPIC Converter                                                                    | 23 |

| Table 5.  | Table of Operation for Dual-Input DC-to-DC Converters                                          | 30 |

| Table 6.  | Assumptions for Component Properties                                                           | 32 |

| Table 7.  | Assumptions for Component Parasitic Properties                                                 | 32 |

| Table 8.  | Dual-Input Four-FET Regulation Test Results                                                    | 41 |

| Table 9.  | Dual-Input Zeta Regulation Test Results                                                        | 46 |

| Table 10. | Dual-Input SEPIC Regulation Test Results                                                       | 52 |

| Table 11. | Alternate Dual-Input SEPIC Regulation Test Results                                             | 57 |

| Table 12. | Regulator Power Path Component Makeup                                                          | 58 |

| Table 13. | Regulator Power Path Component Makeup Rearranged                                               | 59 |

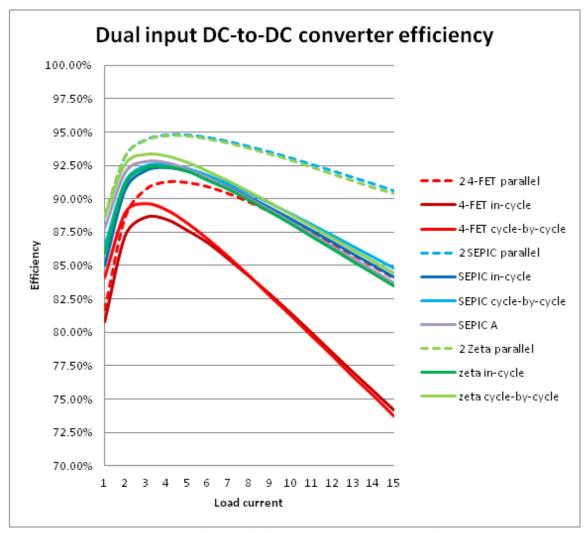

| Table 14. | Converter Efficiency Simulation Conditions                                                     | 60 |

| Table 15. | Converter Efficiency Simulation Results                                                        | 71 |

| Table 16. | Converter Efficiency Simulation Results Line Meaning List                                      | 71 |

| Table 17. | Converter Efficiency Simulation Results Summary                                                | 72 |

| Table 18. | Converter Efficiency Simulation Results Summary Sorted by Average Efficiency                   | 72 |

| Table 19. | Example Control Comparison                              | 90    |

|-----------|---------------------------------------------------------|-------|

| Table 20. | Converter Example Design Requirements                   | 93    |

| Table 21. | Converter Example Design Power Path Components          | 93    |

| Table 22. | Converter Example Design Component Properties           | 95    |

| Table 23. | Converter Example Design Component Parasitic Properties | 96    |

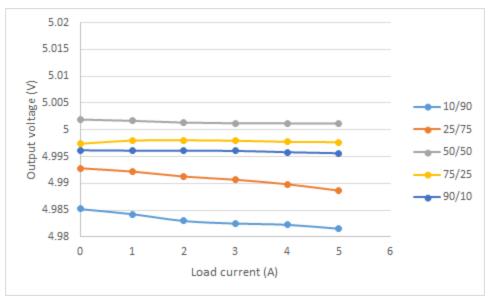

| Table 24. | Example Converter DC Output Voltage Results             | . 103 |

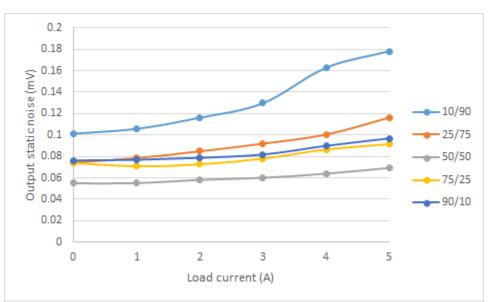

| Table 25. | Example Converter Output Voltage Ripple Results         | . 104 |

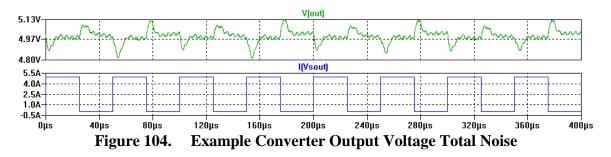

| Table 26. | Example Converter Total Output Voltage Noise Results    | . 104 |

## LIST OF FIGURES

| Figure 1.  | Dual-Input Power Supply                                                        | 2  |

|------------|--------------------------------------------------------------------------------|----|

| Figure 2.  | PCIe Add-In Card Application Example                                           | 3  |

| Figure 3.  | PCIe Add-In Card Application Example with Power Limited to 25W Peak            | 4  |

| Figure 4.  | Typical Buck Converter Schematic                                               | 11 |

| Figure 5.  | Graphs of DC-to-DC Converter Operation                                         | 11 |

| Figure 6.  | DC-to-DC Converter Power Path Current                                          | 13 |

| Figure 7.  | Four-FET Buck-Boost DC-to-DC Converter Power Path                              | 14 |

| Figure 8.  | Current Flow in Full Buck-Boost Mode Four-FET Buck-Boost<br>DC-to-DC Converter | 15 |

| Figure 9.  | Current Flow in Buck Mode Four-FET Buck-Boost DC-to-DC Converter               | 18 |

| Figure 10. | Current Flow in Boost Mode Four-FET Buck-Boost DC-to-DC Converter              | 19 |

| Figure 11. | SEPIC Converter Power Path                                                     | 21 |

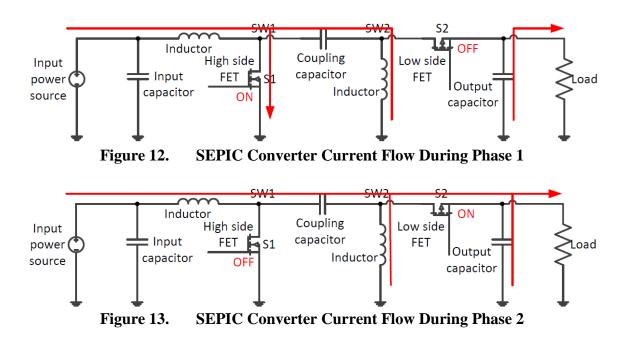

| Figure 12. | SEPIC Converter Current Flow During Phase 1                                    | 22 |

| Figure 13. | SEPIC Converter Current Flow During Phase 2                                    | 22 |

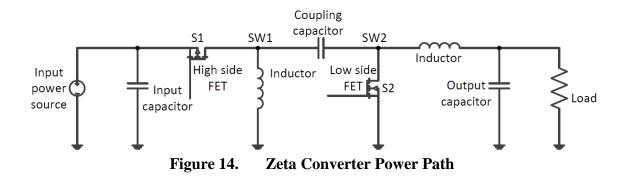

| Figure 14. | Zeta Converter Power Path                                                      | 23 |

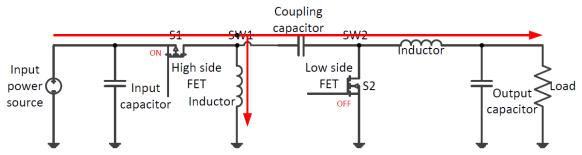

| Figure 15. | Current Flow in a Zeta Converter During Phase 1                                | 25 |

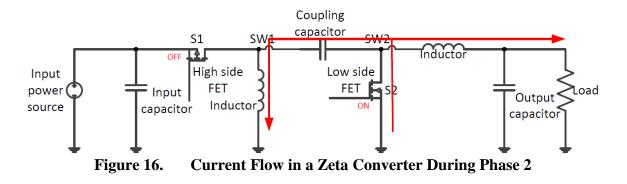

| Figure 16. | Current Flow in a Zeta Converter During Phase 2                                | 25 |

| Figure 17. | Diagram of a Generic Control Loop for a DC-to-DC Converter                     | 26 |

| Figure 18. | Charge and Discharge Stages in a Typical DC-to-DC Converter                    | 29 |

| Figure 19. | Charge and Discharge Stages in a Dual-Input DC-to-DC Converter 30                          |

|------------|--------------------------------------------------------------------------------------------|

| Figure 20. | Two Four-FET Buck-Boost DC-to-DC Converters in Parallel                                    |

| Figure 21. | Two SEPIC DC-to-DC Converters in Parallel                                                  |

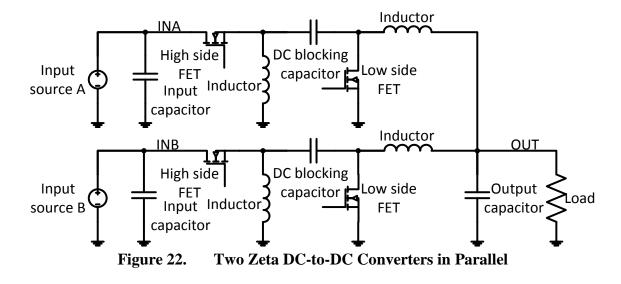

| Figure 22. | Two Zeta DC-to-DC Converters in Parallel                                                   |

| Figure 23. | Dual-Input Four-FET Buck-Boost Converter                                                   |

| Figure 24. | Dual-Input Four-FET Buck-Boost Charging From Input A                                       |

| Figure 25. | Dual-Input Four-FET Buck-Boost Charging From Input B                                       |

| Figure 26. | Dual-Input Four-FET Buck-Boost Discharging to the Output Load 37                           |

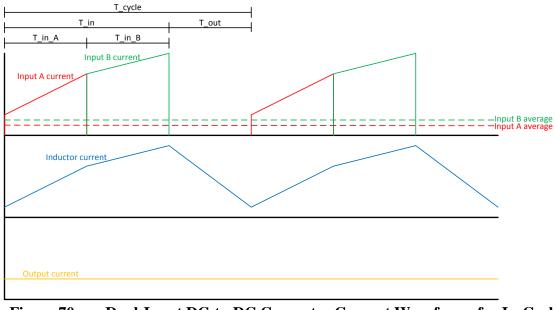

| Figure 27. | Dual-Input Four-FET Buck-Boost In-Cycle Operational Waveforms 38                           |

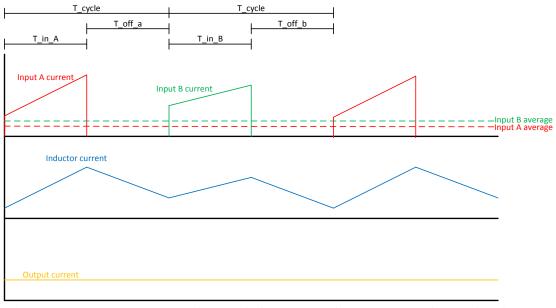

| Figure 28. | Dual-Input Four-FET Buck-Boost Cycle-By-Cycle Operational<br>Waveforms                     |

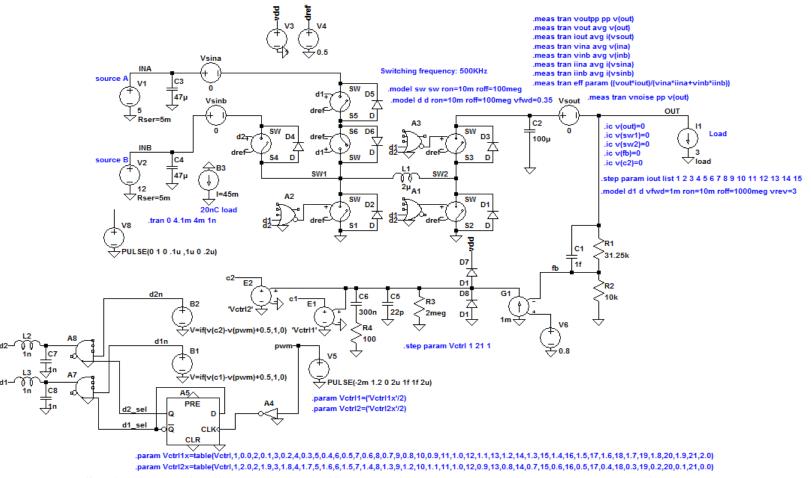

| Figure 29. | SPICE Circuit for Conceptual Verification of Dual-Input Four-FET<br>Buck-Boost Converter   |

| Figure 30. | SPICE Waveforms for Conceptual Verification of Dual-Input<br>Four-FET Buck-Boost Converter |

| Figure 31. | Dual-Input Four-FET Regulation Test Output Voltage Waveform                                |

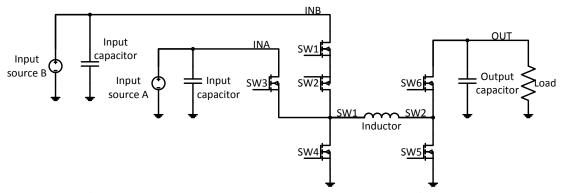

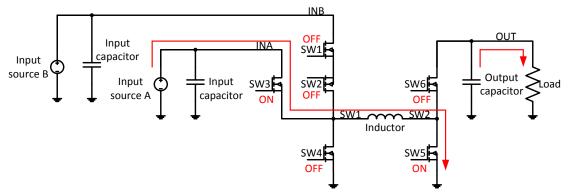

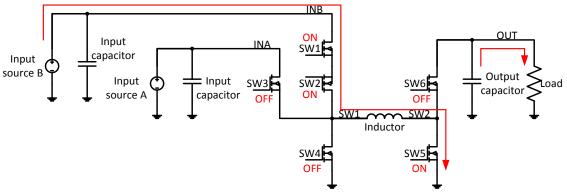

| Figure 32. | Dual-Input Zeta Converter                                                                  |

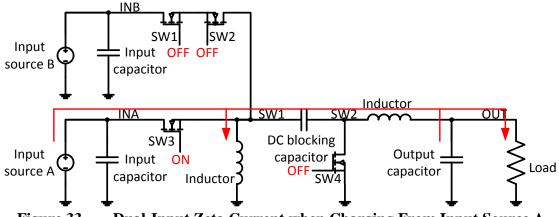

| Figure 33. | Dual-Input Zeta Current when Charging From Input Source A 42                               |

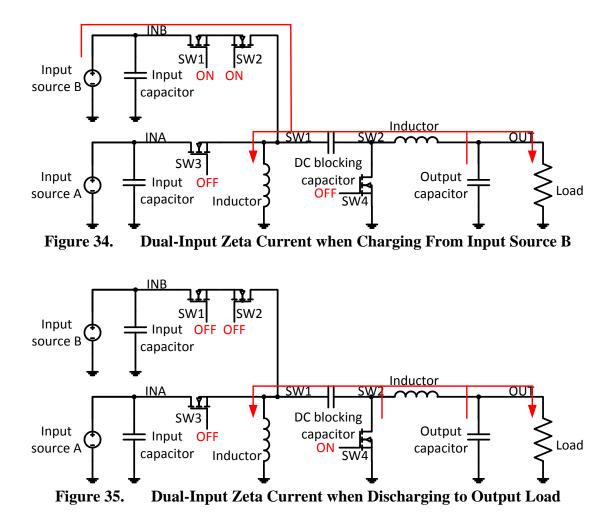

| Figure 34. | Dual-Input Zeta Current when Charging From Input Source B 43                               |

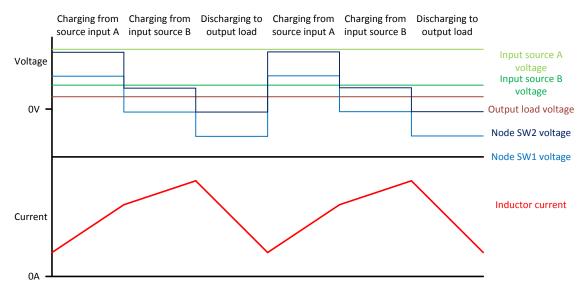

| Figure 35. | Dual-Input Zeta Current when Discharging to Output Load 43                                 |

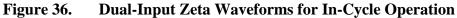

| Figure 36. | Dual-Input Zeta Waveforms for In-Cycle Operation 44                                        |

| Figure 37. | Dual-Input Zeta Waveforms for Cycle-By-Cycle Operation                                     |

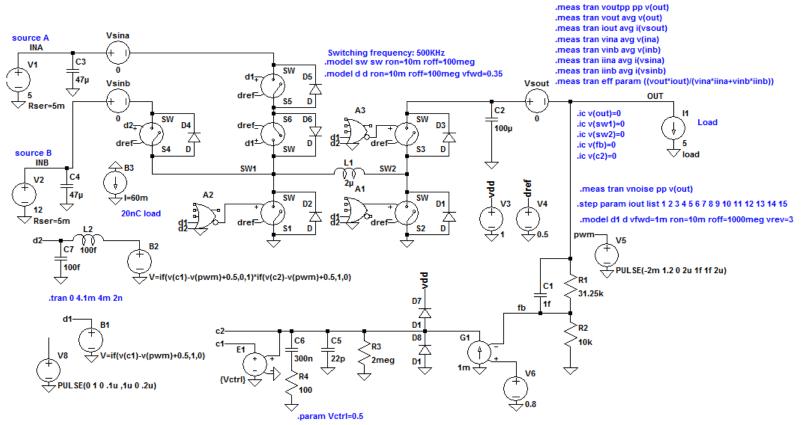

| Figure 38. | SPICE Circuit for Conceptual Verification of Dual-Input Zeta<br>Converter                  |

| Figure 39. | SPICE Waveforms for Conceptual Verification of Dual-Input Zeta<br>Converter                |

| Figure 40. | Dual-Input Zeta Regulation Test Output Voltage Waveform                                                             | 46 |

|------------|---------------------------------------------------------------------------------------------------------------------|----|

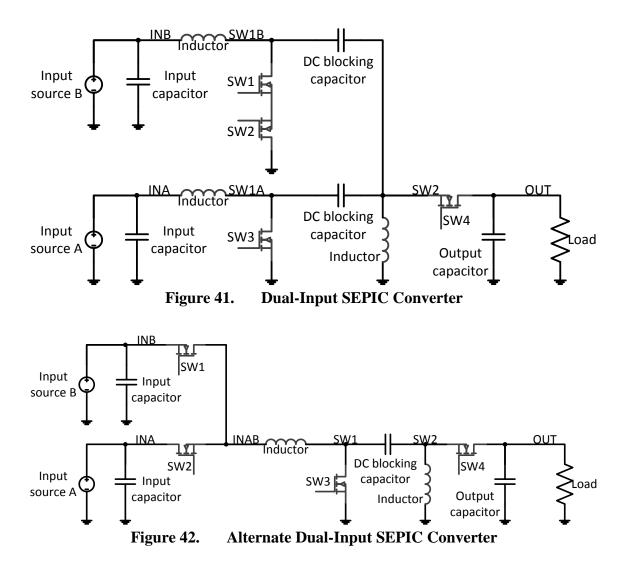

| Figure 41. | Dual-Input SEPIC Converter                                                                                          | 47 |

| Figure 42. | Alternate Dual-Input SEPIC Converter                                                                                | 47 |

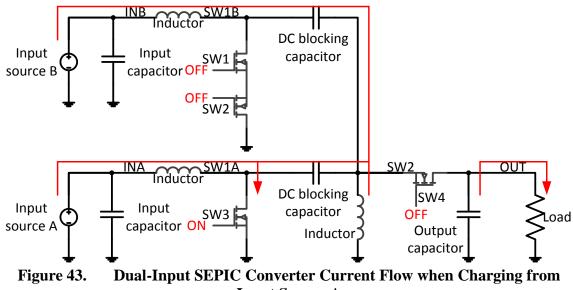

| Figure 43. | Dual-Input SEPIC Converter Current Flow when Charging from<br>Input Source A                                        | 48 |

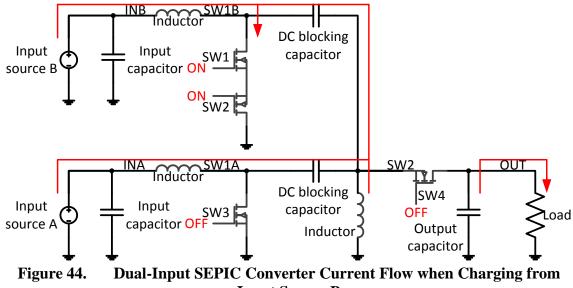

| Figure 44. | Dual-Input SEPIC Converter Current Flow when Charging from<br>Input Source B                                        | 48 |

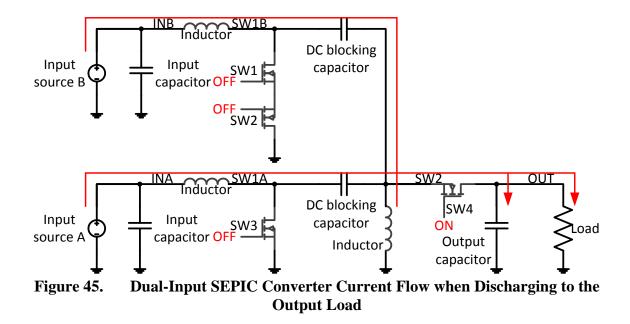

| Figure 45. | Dual-Input SEPIC Converter Current Flow when Discharging to the Output Load                                         | 49 |

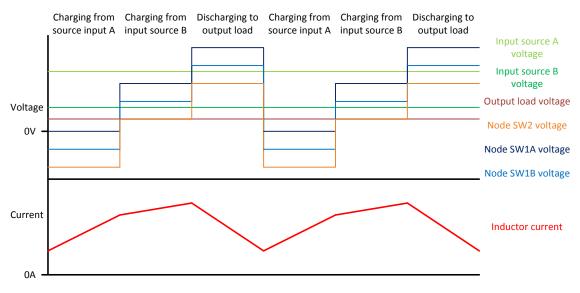

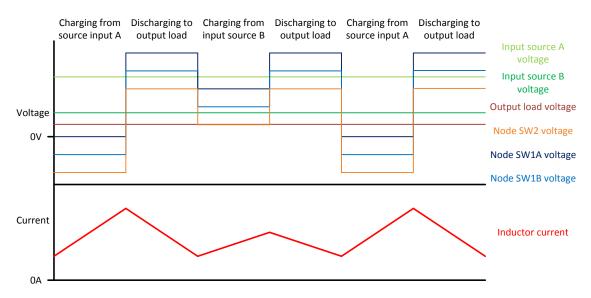

| Figure 46. | Dual-Input SEPIC Converter Waveforms for In-Cycle Operation                                                         | 50 |

| Figure 47. | Dual-Input SEPIC Converter Waveforms for Cycle-By-Cycle<br>Operation                                                | 50 |

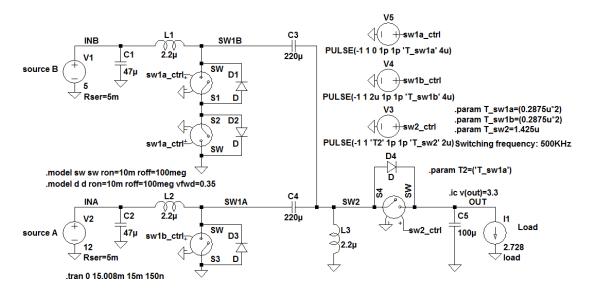

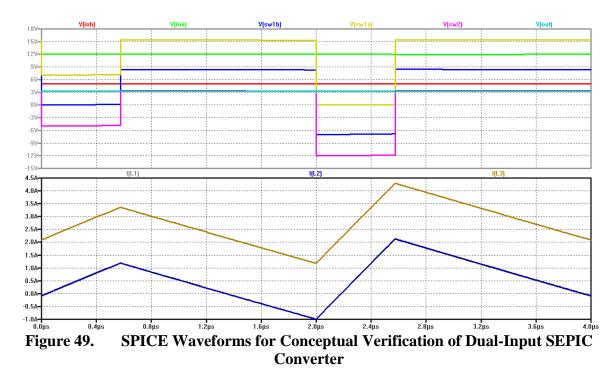

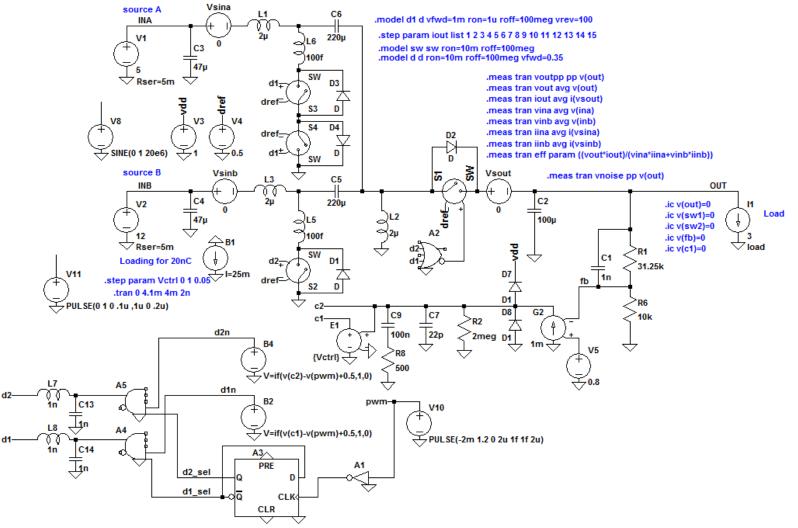

| Figure 48. | SPICE Circuit for Conceptual Verification of Dual-Input SEPIC Converter                                             | 51 |

| Figure 49. | SPICE Waveforms for Conceptual Verification of Dual-Input SEPIC Converter                                           |    |

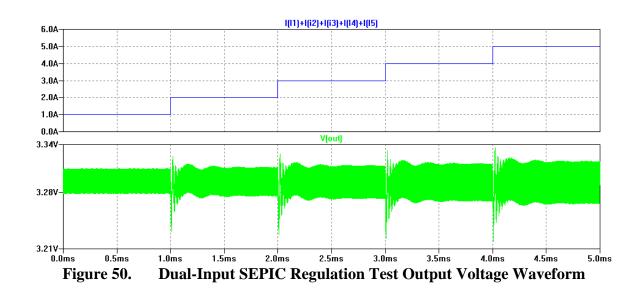

| Figure 50. | Dual-Input SEPIC Regulation Test Output Voltage Waveform                                                            | 52 |

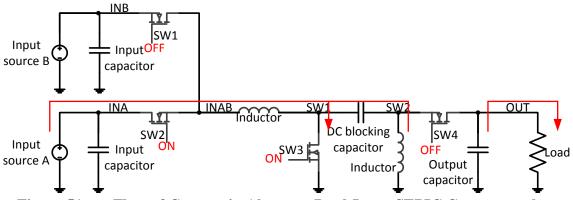

| Figure 51. | Flow of Current in Alternate Dual-Input SEPIC Converter when<br>Charging while Drawing Power from Input Source A    | 54 |

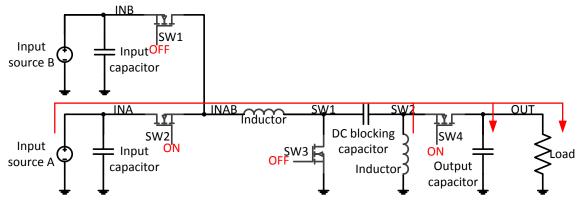

| Figure 52. | Flow of Current in Alternate Dual-Input SEPIC Converter when<br>Discharging while Drawing Power from Input Source A | 54 |

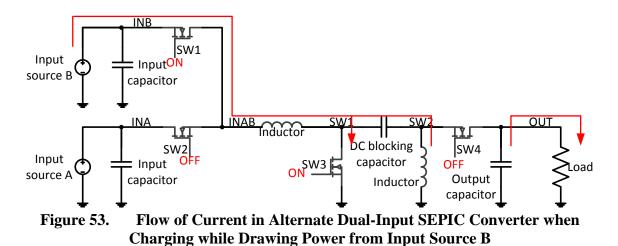

| Figure 53. | Flow of Current in Alternate Dual-Input SEPIC Converter when<br>Charging while Drawing Power from Input Source B    | 54 |

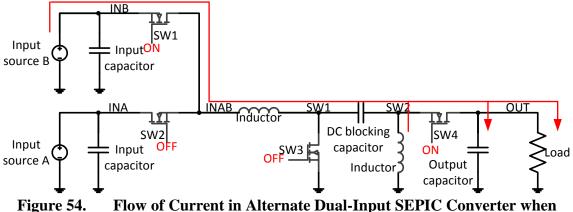

| Figure 54. | Flow of Current in Alternate Dual-Input SEPIC Converter when<br>Discharging while Drawing Power from Input Source B | 55 |

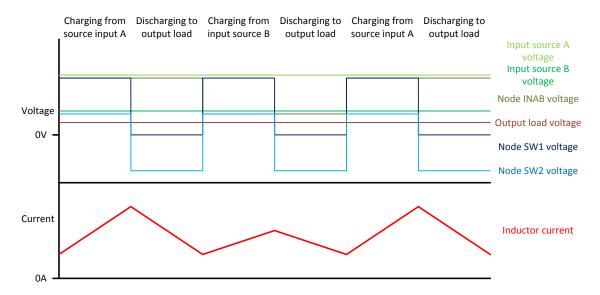

| Figure 55. | Operational Waveforms for Alternate Dual-Input SEPIC Converter                                                      | 55 |

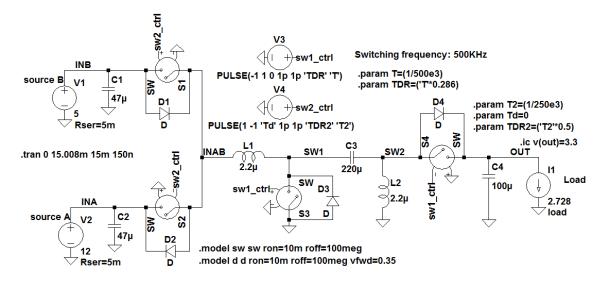

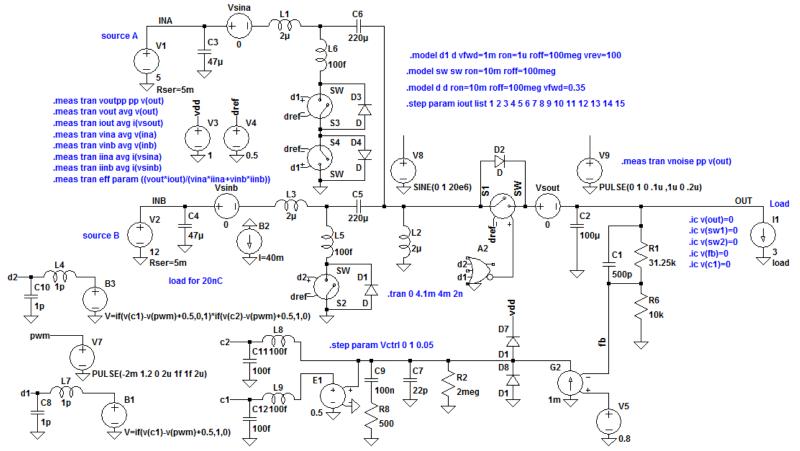

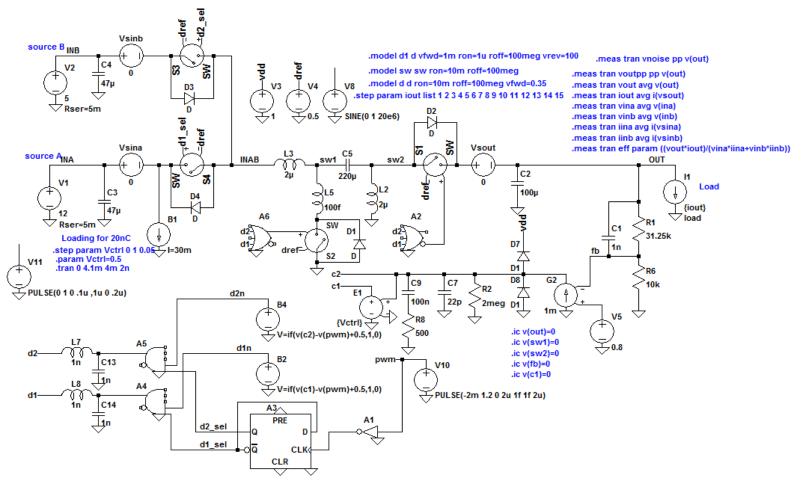

| Figure 56. | SPICE Circuit for Conceptual Verification of Alternate Dual-Input SEPIC Converter                                   | 56 |

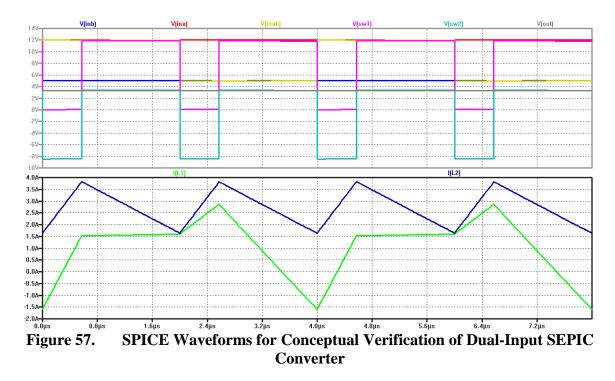

| Figure 57. | SPICE Waveforms for Conceptual Verification of Dual-Input SEPIC<br>Converter                                                      |

|------------|-----------------------------------------------------------------------------------------------------------------------------------|

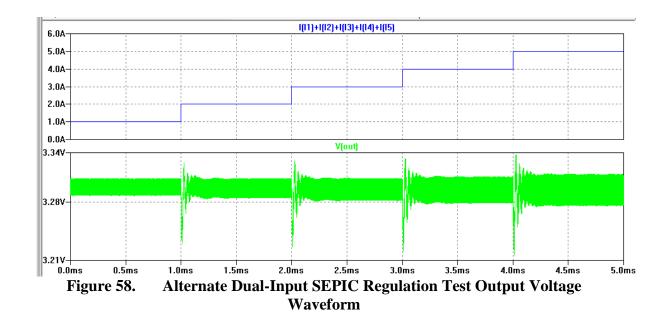

| Figure 58. | Alternate Dual-Input SEPIC Regulation Test Output Voltage<br>Waveform                                                             |

| Figure 59. | SPICE Circuit for Simulating the Efficiency of Dual Four-FET<br>Buck-Boost Converter Topology61                                   |

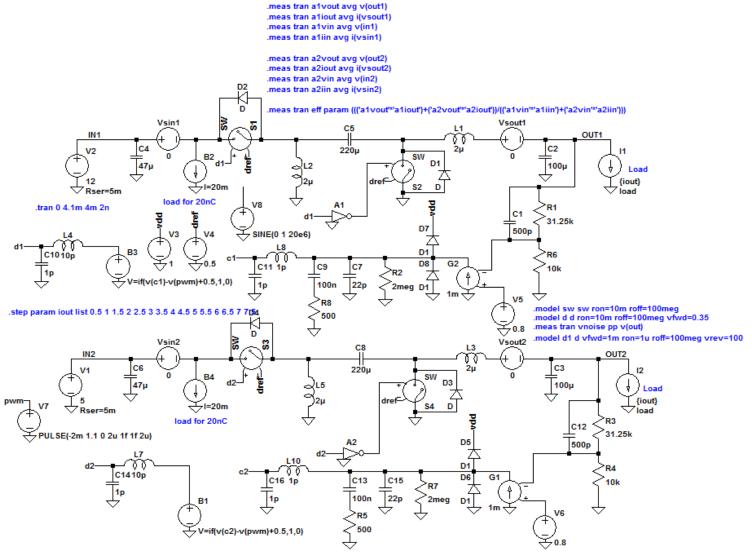

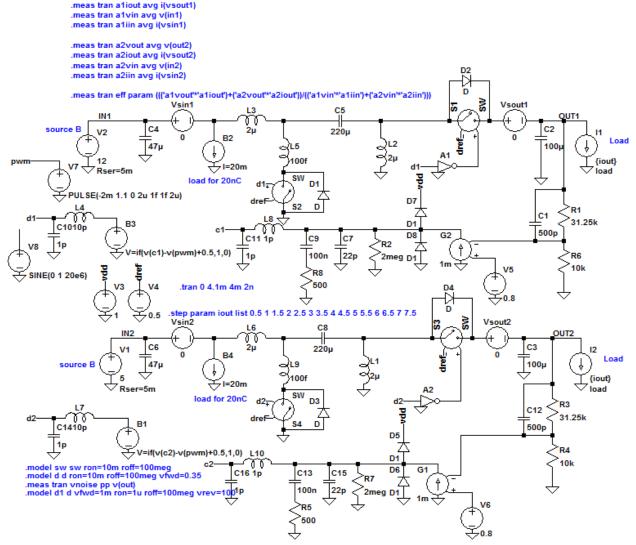

| Figure 60. | SPICE Circuit for Simulating the Efficiency of Dual Zeta Converter<br>Topology                                                    |

| Figure 61. | SPICE Circuit for Simulating the Efficiency of Dual SEPIC Converter<br>Topology                                                   |

| Figure 62. | SPICE Circuit for Simulating the Efficiency of Dual-Input Four-FET<br>Buck-Boost Converter Topology with Cycle-By-Cycle Operation |

| Figure 63. | SPICE Circuit for Simulating the Efficiency of Dual-Input Four-FET<br>Buck-Boost Converter Topology with In-Cycle Operation       |

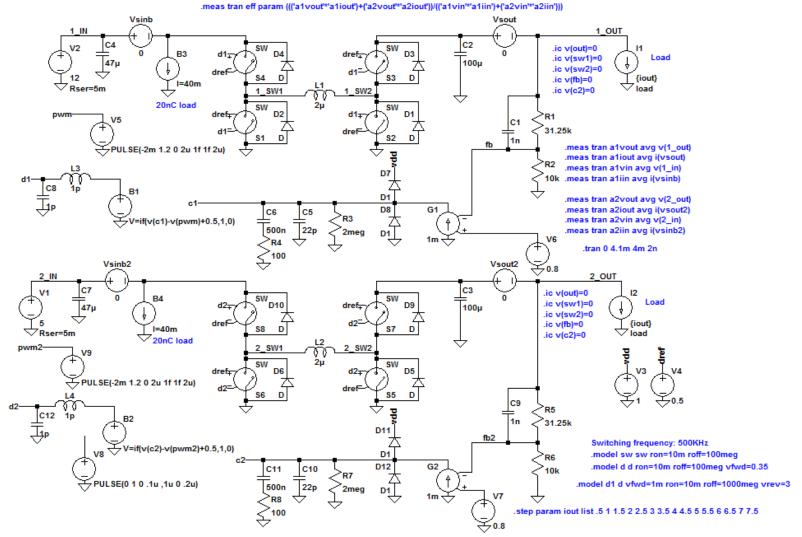

| Figure 64. | SPICE Circuit for Simulating the Efficiency of Dual-Input SEPIC<br>Converter Topology with Cycle-By-Cycle Operation               |

| Figure 65. | SPICE Circuit for Simulating the Efficiency of Dual-Input SEPIC<br>Converter Topology with In-Cycle Operation                     |

| Figure 66. | SPICE Circuit for Simulating the Efficiency of Dual-Input Zeta<br>Converter Topology with Cycle-By-Cycle Operation                |

| Figure 67. | SPICE Circuit for Simulating the Efficiency of Dual-Input Zeta<br>Converter Topology with In-Cycle Operation                      |

| Figure 68. | SPICE Circuit for Simulating the Efficiency of Alternate Dual-<br>Input SEPIC Converter Topology with Cycle-By-Cycle Operation    |

| Figure 69. | Dual-Input DC-to-DC Converter Power Path Efficiency with Respect<br>to Input Current                                              |

| Figure 70. | Dual-Input DC-to-DC Converter Current Waveforms for In-Cycle<br>Operation                                                         |

| Figure 71. | Dual-Input DC-to-DC Converter Current Waveforms for Cycle-By-<br>Cycle Operation                                                  |

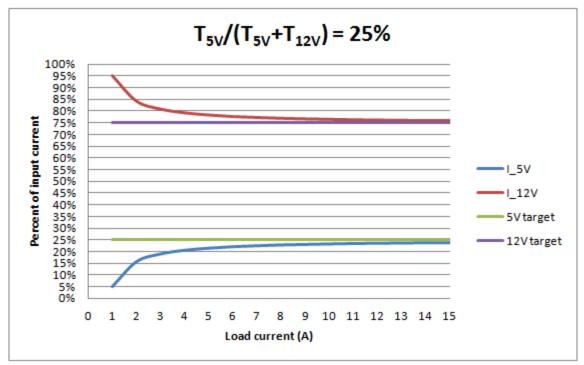

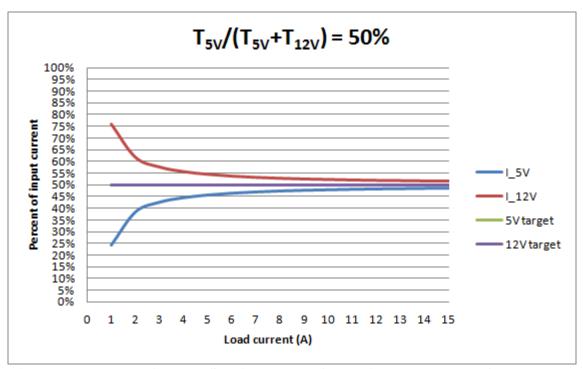

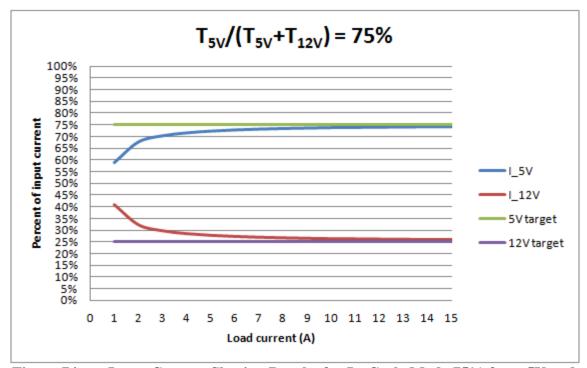

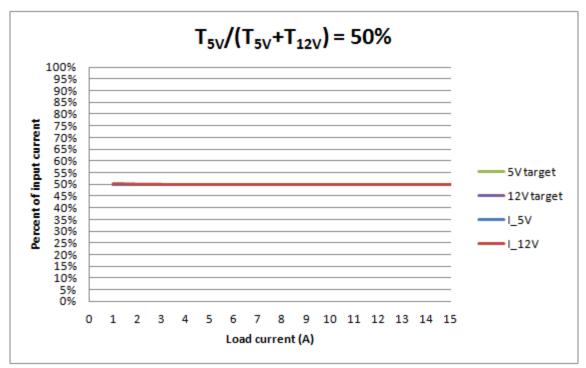

| Figure 72. | Input Current Sharing Results for In-Cycle Mode 25% from 5V<br>and 75% from 12V    | 78   |

|------------|------------------------------------------------------------------------------------|------|

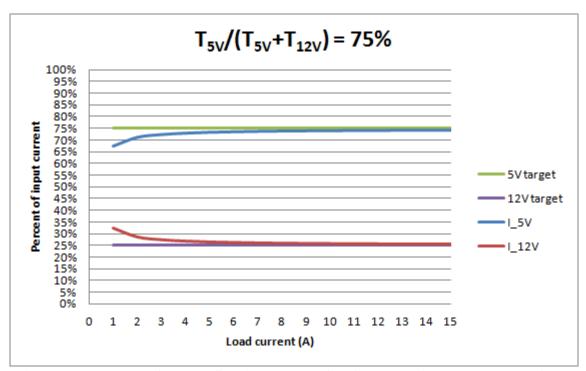

| Figure 73. | Input Current Sharing Results for In-Cycle Mode 50% from 5V and 50% from 12V       | 78   |

| Figure 74. | Input Current Sharing Results for In-Cycle Mode 75% from 5V and 25% from 12V       | 79   |

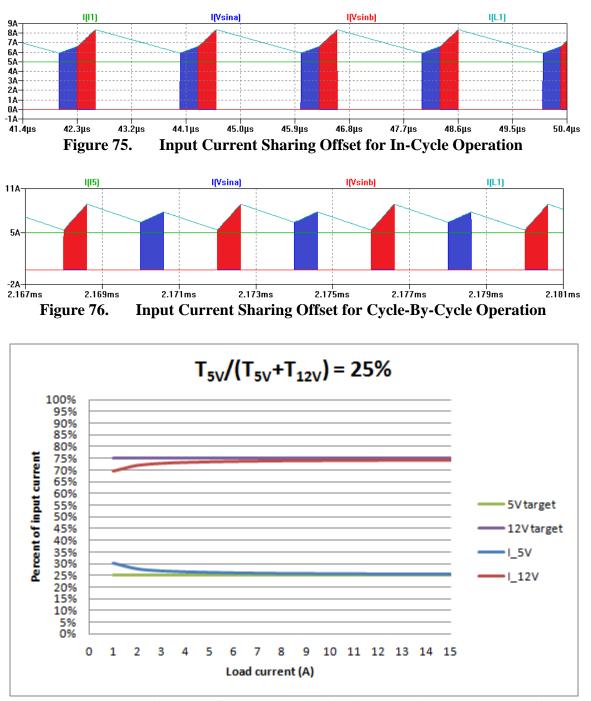

| Figure 75. | Input Current Sharing Offset for In-Cycle Operation                                | 80   |

| Figure 76. | Input Current Sharing Offset for Cycle-By-Cycle Operation                          | . 80 |

| Figure 77. | Input Current Sharing Results for Cycle-By-Cycle Mode 25% from 5V and 75% from 12V | . 80 |

| Figure 78. | Input Current Sharing Results for Cycle-By-Cycle Mode 50% from 5V and 50% from 12V | 81   |

| Figure 79. | Input Current Sharing Results for Cycle-By-Cycle Mode 75% from 5V and 25% from 12V | 81   |

| Figure 80. | Input Current Sharing Control Linearity for In-Cycle Mode                          | 82   |

| Figure 81. | Input Current Sharing Control Linearity for Cycle-By-Cycle Mode                    | . 83 |

| Figure 82. | Example of Voltage Mode Control of a Dual-Input DC-to-DC Converter                 | 85   |

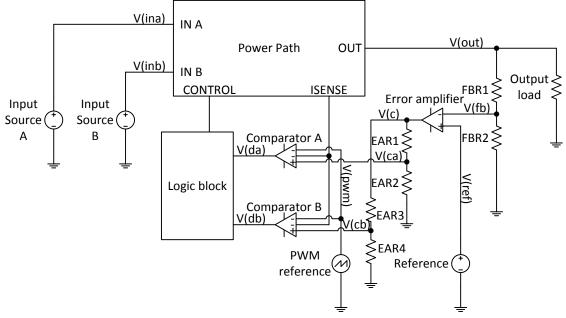

| Figure 83. | Example Voltage Mode Control Diagram                                               | . 86 |

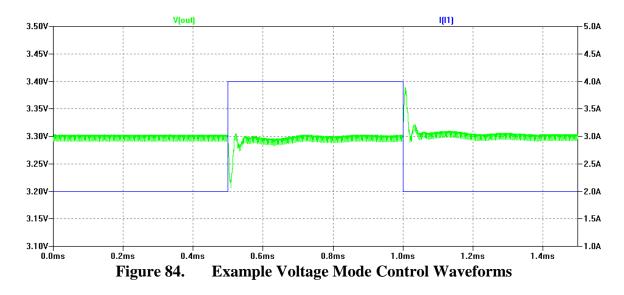

| Figure 84. | Example Voltage Mode Control Waveforms                                             | . 86 |

| Figure 85. | Example of Current Mode Control of a Dual-Input DC-to-DC Converter                 | 87   |

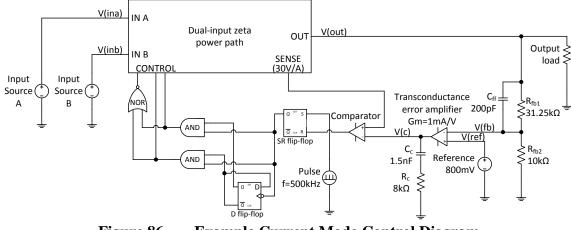

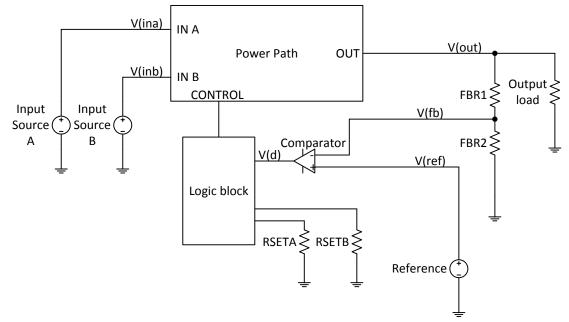

| Figure 86. | Example Current Mode Control Diagram                                               | 88   |

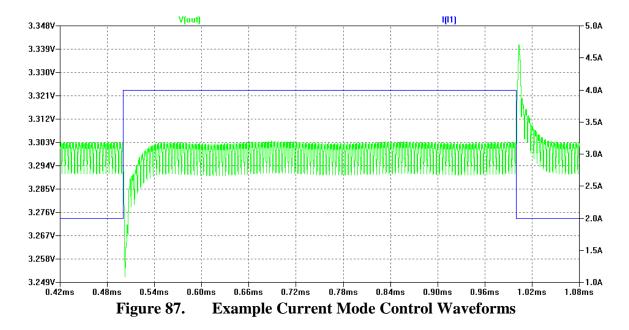

| Figure 87. | Example Current Mode Control Waveforms                                             | . 88 |

| Figure 88. | Example of Constant On-Time Control of a Dual-Input DC-to-DC Converter             | 89   |

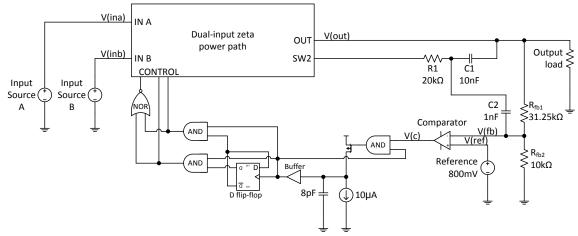

| Figure 89. | Example Constant On-Time Control Diagram                                           | . 90 |

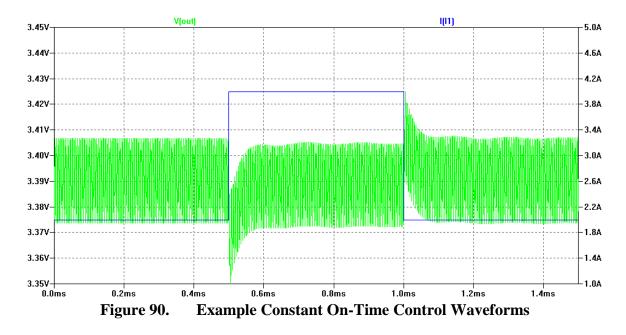

| Figure 90. | Example Constant On-Time Control Waveforms                                         | . 90 |

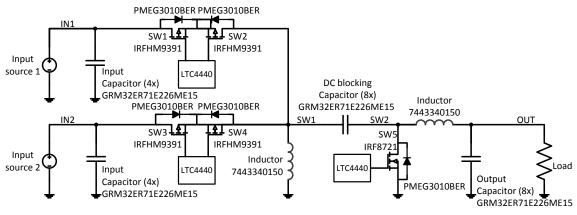

| Figure 91.  | Dual-Input Converter Example Power Path Design                   |

|-------------|------------------------------------------------------------------|

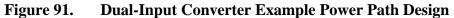

| Figure 92.  | Dual-Input Converter Example LTSpice Schematic                   |

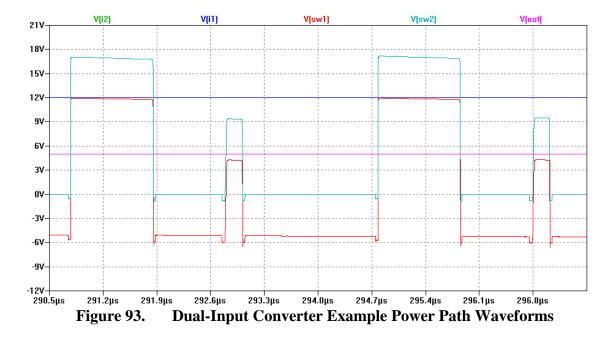

| Figure 93.  | Dual-Input Converter Example Power Path Waveforms                |

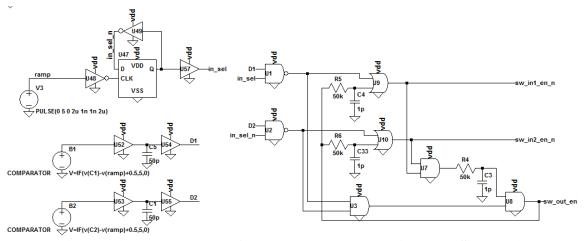

| Figure 94.  | Dual-Input Converter Example Logic Block Schematic               |

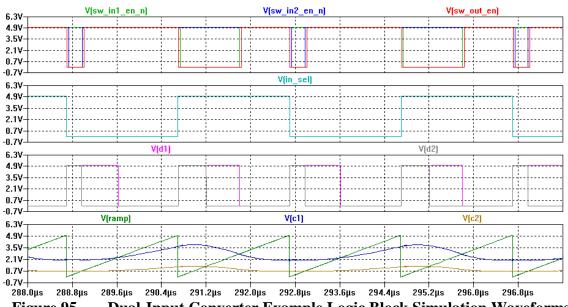

| Figure 95.  | Dual-Input Converter Example Logic Block Simulation<br>Waveforms |

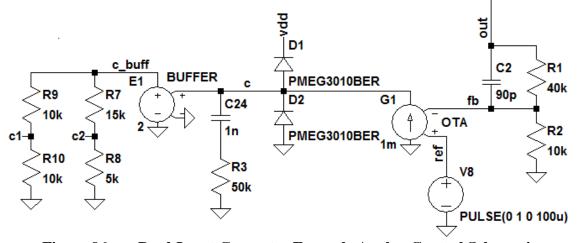

| Figure 96.  | Dual-Input Converter Example Analog Control Schematic            |

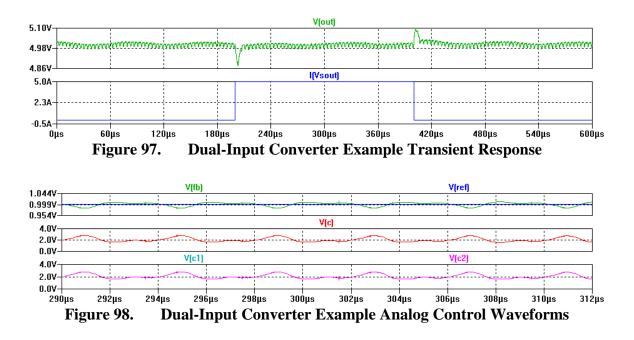

| Figure 97.  | Dual-Input Converter Example Transient Response 100              |

| Figure 98.  | Dual-Input Converter Example Analog Control Waveforms 100        |

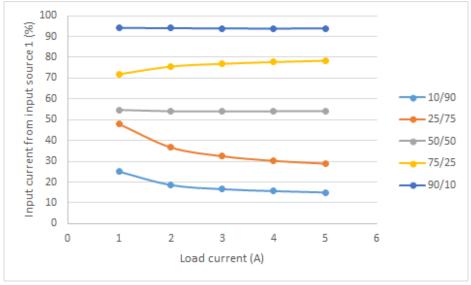

| Figure 99.  | Percentage of Input Current Drawn from Input 1 101               |

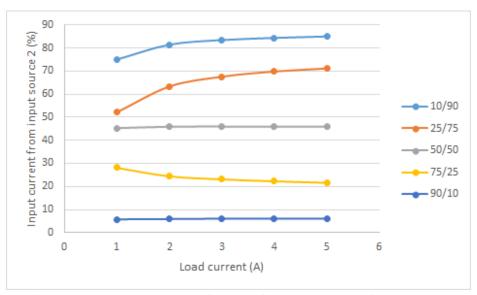

| Figure 100. | Percentage of Input Current Drawn from Input 2 101               |

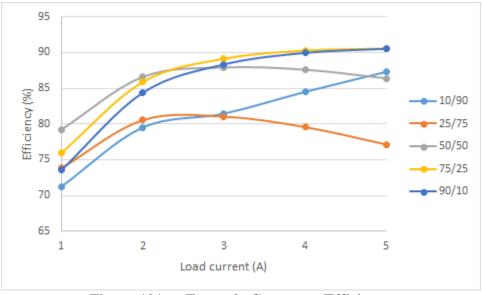

| Figure 101. | Example Converter Efficiency 102                                 |

| Figure 102. | Example Converter DC Output Voltage 103                          |

| Figure 103. | Example Converter Output Voltage Ripple 103                      |

| Figure 104. | Example Converter Output Voltage Total Noise                     |

## LIST OF ABBREVIATIONS

| MECOP  | Multiple Engineering Co-Op Program                |

|--------|---------------------------------------------------|

| DC     | Direct Current                                    |

| SEPIC  | Single Ended Primary Inductance Converter         |

| AT     | Advanced Technology                               |

| ATX    | Advanced Technology Extended                      |

| HDD    | Hard Disk Drive                                   |

| SSD    | Solid State Drive                                 |

| PCIe   | Peripheral Component Interconnect Express         |

| SAS    | Serial Attached SCSI                              |

| SCSI   | Small Computer System Interface                   |

| DRAM   | Dynamic Random Access Memory                      |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor |

| JFET   | Junction Field Effect Transistor                  |

| IGBT   | Insulated Gate Bipolar Transistor                 |

| MTTF   | Mean Time To Failure                              |

| PWM    | Pulse Width Modulator                             |

| OTA    | Operational Transconductance Amplifier            |

| LDO    | Low Dropout Regulator                             |

| SW     | Switch                                            |

### CHAPTER ONE: INTRODUCTION TO DUAL-INPUT DC-TO-DC CONVERTERS

**Topic Overview**

The goal of a dual-input power supply in the context of this writing is to provide power to a single load from two input power sources either simultaneously or alternately. This objective can be met using simple diodes or paralleled low dropout regulators (LDOs) with some control logic, however, as the power requirements of the load increase, these approaches can become highly inefficient or inviable.

A DC-to-DC converter is typically employed when the requirements for power and or efficiency are such that simpler topologies are not sufficient to meet these requirements. The complexities associated with the design of DC-to-DC converters make it difficult to design dual-input converters using those topologies. Currently the most common strategy used to design dual-input DC-to-DC converters is to place multiple converters in parallel and to synchronize them using complex analog control loops.

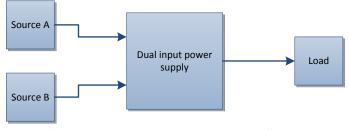

As shown in Figure 1 a dual-input power supply has two inputs or power sources and a single output also called a load. The output typically has a regulated voltage set by the power supply itself and current is supplied to the load on demand. The inputs are typically a loosely fixed voltage and may or may not be the same as the output voltage; current drawn from these inputs is determined by the power supply itself. In a dual-input power supply the current or power drawn from the inputs is drawn from both sources either simultaneously or alternately.

Figure 1. Dual-Input Power Supply

As an example, consider that the power supply shown in Figure 1 is an ideal (100% efficiency) power supply and is supplying power to the load with a regulated voltage of 5V. The input source A is supplying power at 5V and input source B is supplying power at 15V. Consider that the load is drawing 5A. In this example the load power is 25W. By definition the power being delivered to the load by the power supply must be drawn from the available sources A and or B as shown in Equation (1) which applies for ideal power supplies. With the load drawing 25W, the sources must together be supplying 25W to the power supply.

$$P_{load} = P_{sourceA} + P_{sourceB} \tag{1}$$

It is up to the power supply to decide how much of the 25W will be drawn from each of the available input power sources. The power supply may decide to draw an equal current from both sources, in which case 1.25A would be drawn from each source and source A would be supplying 6.25W while source B would be supplying 18.75W. The power supply may also decide to draw an equal amount of power from both sources, in which case each source would be supplying 12.5W and source A would be supplying 2.5A while source B would be supplying 0.833A. The actual ratio of current or power drawn from the sources is arbitrary and is typically dictated by the design constraints for the power supply and for the system as a whole.

#### **Applications for Dual-Input DC-to-DC Converters**

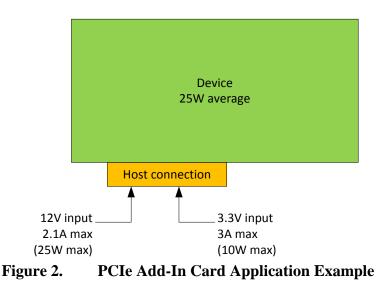

The idea for a dual-input DC-to-DC converter was initially conceived of while working on a product design for a PCIe add-in card (i.e. a video card or solid state drive) for which there were two input power sources available shown in Figure 2. Taken together each input power source could supply instantaneously 35W of power. Due to mechanical limitations the average power consumed could be not more than 25W. The peak power that could be drawn from one of the input sources was 25W, the other could supply an additional 10W.

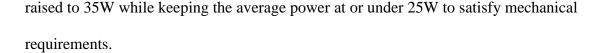

Being limited to a single input source in this case limits the peak power to 25W. The thermal limitation was only for average power. As a result of this limitation the device would need to reduce its average power to below 25W to keep the peak power at or below 25W as shown in Figure 3. The consequence of this being reduced performance as the devices average power would need to be limited to something less than 25W in order to guarantee that the peak power does not exceeded 25W. Exceeding the 25W limit while using only the 12V input would exceed the 2.1A current limit on that input source. Making use of the second input source would allow the instantaneous power limit to be

Figure 3. PCIe Add-In Card Application Example with Power Limited to 25W Peak

Dual-input converters are useful in applications where there is more than one power source and there is a benefit in drawing power from multiple sources either simultaneously or alternately. This benefit can take the form of improved energy efficiency, an increase in the maximum average or peak energy that can be consumed, or in reducing the current being drawn through each input connection to the system. There can also be benefits in terms of redundancy or in mobile systems that may use multiple sources for operation and for battery charging.

## Computer System Applications for Dual-Input DC-to-DC Converters

Computer systems conforming to the various derivatives of the AT specification contain a variety of examples where multiple power sources are provided to computer components such as hard drives, video cards, and memory. The most common derivative of AT is ATX, which supplies 12V, -12V, 5V, and 3.3V as well as a low power 5V auxiliary source supplying power to the components of a computer system. Some interfaces such as PCIe step the 5V auxiliary input down to a 3.3V auxiliary supply. Table 1 shows a breakdown of the power rails and common sources in ATX based computer systems.

| Source            | SATA | SAS | PCIe         | DRAM         | SFF-8639     |

|-------------------|------|-----|--------------|--------------|--------------|

| 12V               |      |     |              |              | $\checkmark$ |

| 5V                |      |     |              |              | $\checkmark$ |

| 3.3V              |      |     |              |              |              |

| 1.5V/1.35V        |      |     |              |              |              |

| 5V/3.3V auxiliary |      |     | $\checkmark$ | $\checkmark$ |              |

Table 1.Based System Power Utilization by Interface

SATA and SAS hard disk drives (HDDs) and more recently solid state drives (SSDs) are supplied with both 5V and 3.3V with a power limit of about 9W. SAS storage devices especially are often required to use each input (12V and 5V) equally either in terms of current or power in order to reach their maximum power with minimal loading on both supplies.

PCIe cards are allowed to draw up to 25W unless an additional 12V input is provided through a dedicated connector other than the primary hot connector. This power limit is however an average and the peak current allowed on the 12V input is 2.1A, which puts a peak power limit on PCIe cards of 25W, and puts the average power somewhat below this. If some power is drawn from the 3.3V input if it is present, then the average would truly be at 25W with peaks above 25W without violating the maximum current limit on the input power sources.

High power PCIe cards can draw 150W or even 350W as of the third generation of PCIe. These power demands are met by supplying additional power to the card through an additional 12V input power source from an auxiliary connector that is explicitly stated cannot be shorted to the 12V input source on the edge connector. Because these two power sources are often both used by video cards to reach their full performance and they cannot be tied together some form of dual-input power supply is required.

Other interfaces exist as well which have multiple power inputs such as the SFF-8639 connector and DRAM modules. In all of these types of devices there are some common benefits to using multiple input power sources. By using two sources, the input current stress on connector contacts can be reduced, the loading on each rail of the host power supply can be reduced, and in some cases the peak power that the component is allowed to use can be increased.

### Battery Equipped System Applications for Dual-Input DC-to-DC Converters

In mobile systems there are often at least two power sources for a device, its internal battery, and an external charger. In some mobile systems there is more than one external power source, for example an electric vehicle may use solar power, regenerative breaking, an on-board generator, and external power as a means of charging the internal battery. In most of these systems only one input power source at a time is used to power the device, such as in a cell phone where either the battery or an external charger is used to power the device, but never both.

When there are multiple input power sources, it may be useful to power the device from both sources simultaneously to minimize the loading on each source, especially if one source is susceptible to brown-out due to overloading. In such an application a dual-input DC-to-DC converter could be used to control the amount of power drawn from each input source in order to either minimize loading on sensitive power sources, or to maximize efficiency.

Another possibility is in systems with two batteries which may not have the same capacity or state of health. In such a system it may be advantageous to draw the full system power from both batteries at the same time with a given ratio of power from each battery in order to either reduce loading on a failing battery to extend its life or to load both batteries in such a way that the system can operate at full power for as long as possible.

Some mobile devices such as calculators and wearable devices, use various forms of energy harvesting to supplement battery power and extend the functional life of the device when operating without an external power supply. In this application some type of dual-input DC-to-DC power supply would be needed in order to draw as much power as possible from external sources such as solar, and draw the minimum possible amount of power from the devices internal battery.

## Redundant Power Source Applications for Dual-Input DC-to-DC Converters

Some systems use multiple input power sources for redundancy. In these systems, it is common to use only one of the input sources at a time. When one fails the other is activated as a backup. It may be beneficial for systems with multiple redundant power sources to use both supplies simultaneously.

If each supply can source 100% of the system power demand, then the system could draw 50% of its power from each source thereby increasing the lifetime (reducing the MTTF) of each source by reducing the loading on each power source. In the event of a failure of one of the sources 100% of the power can then be drawn from the other source. Switching from one power source to another can sometimes cause the system power to brown out. Having a dual-input DC-to-DC converter with a single power path reduces the chance of this occurring.

#### **Thesis Scope**

This writing will discuss topologies of DC-to-DC converters which can draw power from two sources using a single power path and will compare with more traditional approaches using two power paths. The power paths discussed will be buckboost types, meaning that the output voltage is not bounded by either of the input voltages. Details of the power paths, their operation, and control schemes will be presented. Operational modes for the proposed dual-input power paths will be in-cycle and cycle-by-cycle. Control schemes discussed will be voltage mode, current mode, and constant on-time. Finally a simulation of a real-world design will be shown to illustrate how such a device might perform if implemented.

### **Definitions and Terminology**

The term DC-to-DC converter is used here to define any type of energy converter that draws energy from one or more sources and delivers that energy to one or more loads by way of using an inductor as an energy storage and release mechanism. A "buck boost" converter is any type of DC-to-DC converter which can generate a fixed output voltage that is not bounded by the input voltage(s). The power path of a DC-to-DC converter is the components through which the energy flows from source(s) to load. The operating mode of a dual-input converter is the method in which the power path switches are controlled so as to draw energy from two input sources simultaneously. The control scheme of the converter is the concept and circuits that control the converters switches in order to achieve a stable output voltage. The term "switch" in this writing will generally be assumed to mean a MOSFET type device. In general a switch could also be a MOSFET, IGBT, JFET, bipolar transistor, or other type of device which can have a low resistance "on" state and a high resistance "off" state.

It is assumed in this writing that the reader knows all of the units of measure contained within such as the volt, ohm, and watt among others.

### CHAPTER TWO: BACKGROUND ON DC-TO-DC CONVERTERS

### **Theory of Operation**

A DC-to-DC converter operates primarily by charging and discharging an energy storage device, typically an inductor, in such a way as to control the voltage going to a load while supplying the amount of current (or power) that is demanded by that load. In an ideal lossless DC-to-DC converter the power supplied to the load is the same as the power drawn from the source.

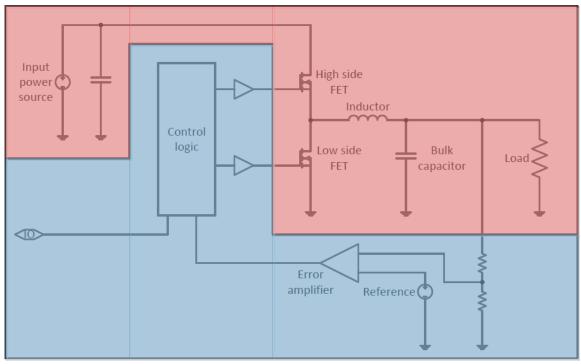

To illustrate the operation of a DC-to-DC converter a buck converter will be used as an example. A diagram of a typical buck converter is shown in Figure 4 The power path highlighted in red is the portion of the circuit that actively transfers power from the input power source to the load and performs the voltage translation to the fixed output voltage. The control portion highlighted in blue is the portion of the circuit which controls the turn-on and turn-off of the power switches in such a way that the converter maintains a constant output voltage; it does this by sensing the output voltage and comparing it with a reference voltage.

For the context of this writing, only synchronous DC-to-DC converters are considered. Asynchronous converters use a diode in place of one of the FETs in order to simplify the design. As a result their power handling capability is limited. In synchronous converters power can actually move either from output to input or from input to output as they are bidirectional. Asynchronous converters can only move power from input to output.

Figure 4. Typical Buck Converter Schematic

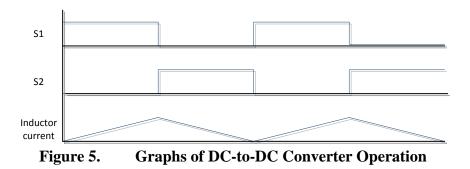

Energy is moved from the input power source to the output by storing it in an inductor and then subsequently discharged to the output. The ratio of time between energy being stored in the inductor and energy being released to the load will determine the output voltage.

In the buck converter the high side switch in the Figure 1 charges the inductor as shown in the graph above, the inductor current grows because the input voltage is greater than the output voltage. When the low side switch is activated and the high side switch deactivated the inductor current begins to decrease as stored energy is released to the load.

In an ideal DC-to-DC converter the Equation that governs the output voltage is Equation (2) where D is the duty cycle of the high side switch S1 which can be expressed as Equation (3) where  $T_{S1}$  is the on-time for S1 and  $T_{S2}$  is the on-time for S2. For nondeal DC-to-DC converters the duty ratio must be adjusted slightly (higher than for an ideal converter) to compensate for losses within the converter.

$$V_{OUT} = D * V_{IN} \tag{2}$$

$$D = \frac{T_{S1}}{T_{S1} + T_{S2}}$$

(3)

Figure 6 shows how currents flow through the power path of a DC-to-DC converter. The output capacitor is charged while S1 is turned on, and discharged while S2 is turned on. It is intended to stabilize the output voltage and reduce voltage ripple.

Figure 6. DC-to-DC Converter Power Path Current

## **Power Path**

This writing will focus on three topologies which have the same input to output voltage relationship: the four-FET buck-boost, SEPIC, and ZETA DC-to-DC converter topologies. Each of these has the property that both the input and output voltage be positive, but the output voltage may be greater than, less than, or equal to the input voltage. To simplify the efficiency Equations below, it is assumed that all switches are FETs with the same properties of on state resistance and gate charge and all inductors are the same with identical DC resistances.

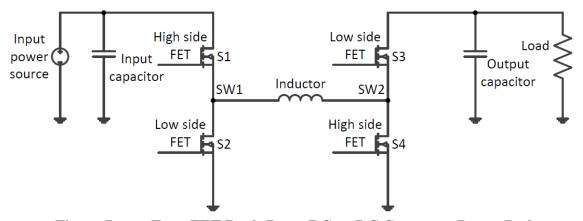

#### The Four-FET Buck-Boost Converter

The four-FET buck-boost converter is actually a hybrid of the buck and boost converter topologies. It consists of four FETs and a single inductor in its power path in addition to the usual input and output bulk capacitors. In this topology the switch node SW1 experiences voltages from ground to the input voltage, and the second switch node SW2 experiences voltages from ground to the output voltage; this is an advantage of this topology over the SEPIC and ZETA topologies.

Figure 7. Four-FET Buck-Boost DC-to-DC Converter Power Path

In the four-FET buck-boost converter there are two ways that the converter can be operated. The first way is as a full buck-boost converter wherein all four switches are being switched all the time. The second way is a hybrid buck or boost wherein only two of the switches are being actuated at any given time depending on whether or not the input voltage than is greater or less than the input voltage.

When operated as a full buck-boost converter the relationship between duty ratio and output voltage is as shown by Equation (4) which means that for a duty ratio of  $\frac{1}{2}$  the input and output voltages are equal, for D < 0.5 the output voltage is less than the input voltage and for D > 0.5 the output voltage is greater than the input voltage. A big advantage of this mode is that there is no distinction between buck and boost mode as there is in the hybrid mode which simplifies control loop design.

$$V_{OUT} = V_{IN} * \frac{D}{1 - D} \tag{4}$$

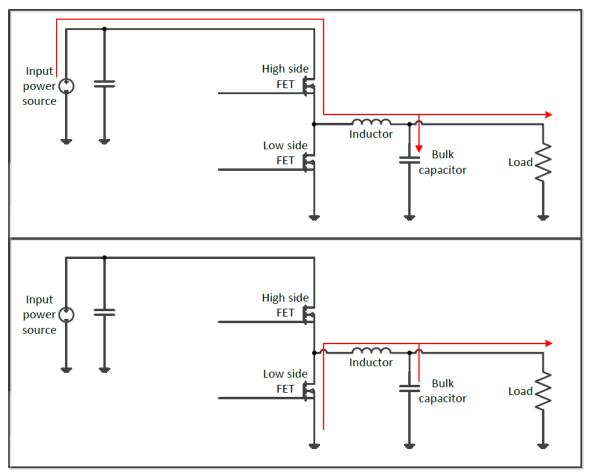

Figure 8 shows the flow of current through the four-FET converter in this mode of operation. The top half of Figure 8 shows the flow of current when the inductor is being charged through S1 and S4. The bottom half shows the flow of current when the stored energy in the inductor is being discharged to the load through S2 and S3.

Figure 8. Current Flow in Full Buck-Boost Mode Four-FET Buck-Boost DC-to-DC Converter

In the full buck-boost mode of operation the power path losses are contributed to primarily by the inductor series resistance, on resistance of all four FETs, and the gate charge of all four FETs. The inductor losses can be estimated as Equation (5) where  $I_L$  is

the average inductor current and  $R_L$  is the series resistance of the inductor, for the full buck-boost the magnitude of the average inductor current  $I_L$  is actually the sum of the average input and output currents which can be expressed as Equation (6) The losses due to the on state resistance of the FETs can be expressed as Equation (7) where  $R_{FET}$  is the on state resistance of the FETs; this is because the current through the power path is at any given time flowing through two of the FETs. The FETs also dissipate energy due to their gate charge which is a representation of the energy required to turn the FETs on and off, this power dissipation can be expressed as Equation (8) where f is the switching frequency in Hz of the converter and  $Q_G$  is the gate charge of the FETs in coulombs (C).

$$P_L = I_L^2 * R_L \tag{5}$$

$$I_L = I_{IN} + I_{OUT} \tag{6}$$

$$P_{FET} = 2 * I_L^2 * R_{FET} \tag{7}$$

$$P_{FETSW} = V_{IN} * f * 2 * Q_G \tag{8}$$

There are additional sources of loss such as conduction during the transition between the on and off states of the FETs, FET off-state leakage, and magnetic saturation of the inductor at high currents which contribute to losses in the power path of a converter. To keep the analysis of the losses simple enough for comparison sake these additional losses will not be analyzed in this writing. Table 2 shows the Equations for losses in the four-FET converter running in full buck-boost mode which are covered in this writing.

| Source                     | Equation                           |

|----------------------------|------------------------------------|

| Inductor series resistance | $P_L = I_L^2 * R_L$                |

| FET on state resistance    | $P_{FET} = 2 * I_L^2 * R_{FET}$    |

| FET gate charge            | $P_{FETSW} = V_{IN} * f * 2 * Q_G$ |

Table 2.Equations for Losses in Four-FET Buck-Boost DC-to-DC Converterin Full Buck-Boost Mode

When operated in the hybrid buck or boost mode the four-FET converter is operated as either a buck converter when the output voltage is less than the input voltage or as a boost converter when the output voltage is greater than the input voltage. This mode has the benefit of improved efficiency as the losses are reduced from the full buckboost mode. However, it has an issue when the input and output voltages are equal to one another. The converter can thrash between modes causing an increase in output noise.

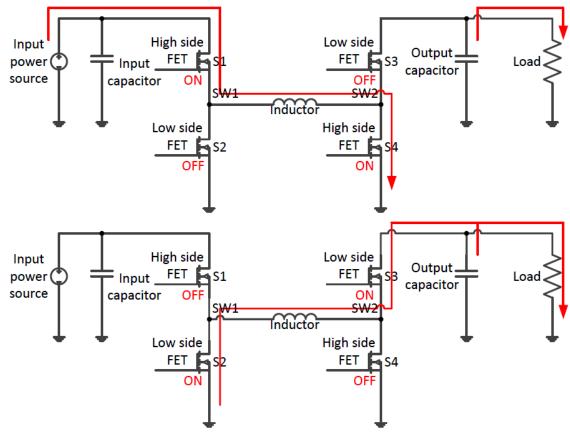

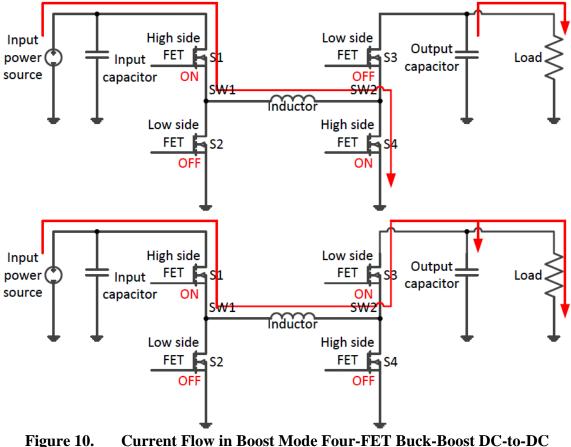

Figure 9 shows the flow of current in this power path in buck mode and Figure 10 shows the flow of current in boost mode. This converter essentially puts the un-used FETs in a fixed state and only actuates the FETs that are needed during either buck or boost mode.

Figure 9. Current Flow in Buck Mode Four-FET Buck-Boost DC-to-DC Converter

Figure 10. Current Flow in Boost Mode Four-FET Buck-Boost DC-to-DC Converter

In buck mode only S1 and S2 are actuated, S3 is left on and S4 is left off, making the converter appear very similar to a buck converter with an input to output relationship given as Equation (2) In boost mode only S3 and S4 are switched, S1 is left on and S2 is left off, making the converter look very much like a boost converter with an input to output relationship given by Equation (9) efficiency of the four-FET buck boost when operated this way is the same in either buck or in boost mode. Table 3 shows the equations for the losses of efficiency of the four-FET buck-boost DC-to-DC converter when operated in hybrid buck or mode. The key difference is that with ½ of the switches actually switching at any given time, the losses due to gate charge are cut in half. This especially come in to play during low current (low power) operation.

$$V_{OUT} = V_{IN} * \frac{1}{D} \tag{9}$$

# Table 3.Equations for Losses in Four-FET Buck-Boost DC-to-DC Converterin Hybrid Buck or Boost Mode

| Source                     | Equation                        |

|----------------------------|---------------------------------|

| Inductor series resistance | $P_L = I_L^2 * R_L$             |

| FET on state resistance    | $P_{FET} = 2 * I_L^2 * R_{FET}$ |

| FET gate charge            | $P_{FETSW} = V_{IN} * f * Q_G$  |

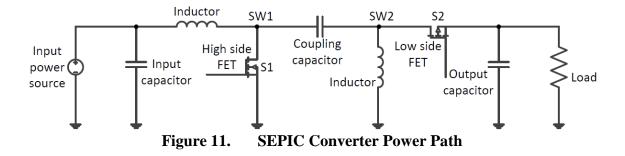

## The SEPIC Converter

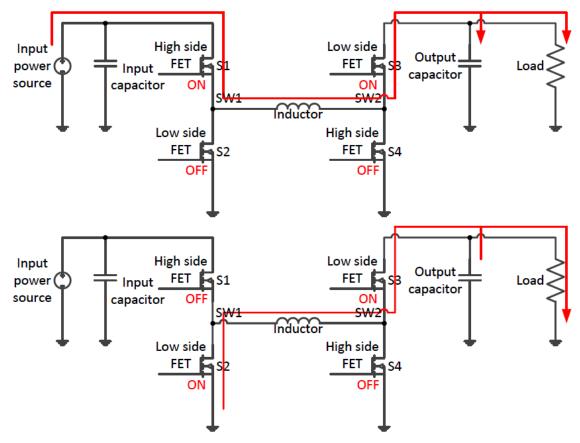

A SEPIC converter has the same transfer function as a four-FET buck-boost converter with only two switches but two inductors and a DC blocking capacitor. With this type of converter, there is only one way to operate the converter unlike the four-FET design. The main drawback of this converter over the four-FET design is that the switch nodes SW1 and SW2 experience a greater range of voltages and the FETs must be able to withstand much higher voltages than they would in a four-FET configuration. In the SEPIC configuration SW1 must withstand voltages from ground to the sum of the input and output voltages, the second switch node SW2 must withstand a voltage range from the negative of the input voltage to the output voltage. The reason for this is that the average voltage across both inductors must be zero. Node SW1 experience a voltage of 0V for time D \* T and in order to keep the average at 0 by Equation (10) the voltage  $V_{SW1}$ must equal  $V_{out} + V_{in}$  when substituting Equation (11). The same logic can be applied to show that the voltage swing on SW2 goes from  $-V_{in}$  to  $V_{out}$ . Figure 11 shows the power path of the SEPIC converter.

$$\frac{D * (V_{in} - 0) + (1 - D) * (V_{in} - V_{sw1})}{2} = 0$$

<sup>(10)</sup>

$$D = \frac{V_{out}/V_{in}}{1 + V_{out}/V_{in}} \tag{11}$$

Another design consequence of the SEPIC converter which also applies to the ZETA converter is that, for switch S2, floating drivers must be used if S2 is an n-channel FET, or a p-channel FET must be used in order to be able to turn this switch on and off. In the case of a zeta converter this is true for S1. The drawings of both the SEPIC and zeta converters in this chapter show a p-channel for S2 in the SEPIC converter and for S1 in the zeta converter.

The SEPIC converter always operates in full buck-boost mode and its transfer function and characteristics are otherwise the same as for the four-FET buck-boost when operated in full buck-boost mode. One design constraint of the SEPIC is that the coupling capacitor must be sized sufficiently large in order to prevent oscillations of the output voltage. Another design note about this converter is that the two inductors may be coupled for improved response time when designing the control circuits.

The current flow in a SEPIC converter is somewhat non-intuitive due to the DC blocking capacitor. The SEPIC converter operates in two phases; in the first phase energy is taken from the input power source and stored in the inductors, in the second phase that energy is released to the load. Bulk capacitors supply energy to the load during the first phase. During the first phase, S1 is on and current is flowing to ground through S1 from

the first inductor and the DC blocking capacitor. Output current is being supplied by the output bulk capacitor. During the second phase, S2 is on and current is flowing from input to output and from ground to output through the second inductor. Figures 12 and 13 shows the current flows in a SEPIC converter. Note that the input current in the SEPIC is being drawn during both phases.

Sources of power loss in the SEPIC power path are the same as those for a four-FET converter with the addition of the coupling capacitor; the Equations are however somewhat different due to the different number of FETs and inductors. The losses in the inductors follow the same Equation as for the inductor in the four-FET buck-boost converter with the exception that there are two inductors. The FETs also follow the same Equations with the exception that there are just two FETs. The losses in the coupling capacitor are less straightforward as they depend on the capacitance of the coupling capacitor and the RMS current through the capacitor. Typically the losses in the coupling capacitor are less than those of the other components in the system. Table 4 shows the Equations for loss in a SEPIC converter.

| Source                                | Equation                                                          |

|---------------------------------------|-------------------------------------------------------------------|

| Inductor series resistance            | $P_{L1} = 2 * I_{L1}^2 * R_{L1}$ $P_{L2} = 2 * I_{L2}^2 * R_{L2}$ |

| FET on state resistance               | $P_{FET1} = I_{L1}^{2} * R_{SW1} P_{FET2} = I_{L2}^{2} * R_{SW2}$ |

| FET gate charge (applies to each FET) | $P_{FETSW} = \frac{1}{2} * V_{IN} * f * Q_G$                      |

Table 4.Losses in a SEPIC Converter

Typically, if the same inductors and FETs are used, a SEPIC converter will be slightly more efficient than a four-FET buck-boost converter due to only having two FETs which saves power in both FET resistances and reduces switching losses.

# The Zeta Converter

The zeta converter is the inverse of the SEPIC converter. It is a consequence of the fact that the SEPIC converter is bi-directional and as such the zeta converter can be thought of as a SEPIC converter with the input and output swapped and the high side and low side FET assignments reversed. All of the characteristics of losses shown in Table 4 and the transfer function for the SEPIC converter apply to the zeta converter as well. Figure 14 shows the power path of the zeta converter.

The chief difference between the zeta and SEPIC converters has to do with the nature of the current at the input versus the output. The SEPIC converter has an inductor in series with the input which provides a filter for the input current and reduces the switching noise radiated to the input. The zeta converter has the series inductor at the output which provides the same filtering but on the output side.

Operation of a zeta converter is similar to a SEPIC. The high side and low side FETs are reversed along with the circuit direction: low side FET is on the left and high side FET is on the right. The relationship between duty cycle, input voltage, and output voltage is the same as for a SEPIC converter. The operation of a zeta converter is in two phases, the first phase is a charging phase where energy is taken from the input power source and stored in the two inductors. The second phase is where the energy is then delivered to the output load. A bulk capacitor acts to supply energy to the output load during the first phase. Figures 15 and 16 show the flow of current in the zeta converter during phase 1 and phase 2 respectively. During the first phase current flows from the input power source through S1 into both the left side inductor and DC blocking capacitor and right side inductor to the load. During the second phase the input current is cut off and S2 is closed, current then flows from ground through S2 into the DC blocking capacitor (moving right to left now) and also through the right side inductor to the load. One feature of the Zeta converter is that the output current is not interrupted which can reduce output noise.

Figure 15. Current Flow in a Zeta Converter During Phase 1

## **Control Scheme**

The control portion of a DC-to-DC converter is primarily responsible for regulating the output voltage of the converter as well as a number of secondary functions. Some of the secondary functions include soft start, an output power-good indicator, and an input under voltage lockout. This chapter is only concerned with the primary responsibility of the control which is regulation of the output voltage. There are three types of control circuits commonly used in DC-to-DC converters; voltage mode, current mode, and constant on-time.

The basic constituents of a regulator control loop are the reference voltage, the error amplifier, and the PWM/logic circuit. The reference voltage is used as a fixed known reference to compare the output voltage against. The error amplifier performs the comparison of the output voltage or a scaled version of it by way of a resistor divider to the reference voltage and provides a signal to the PWM/logic circuit. In the constant on-

time control scheme the error amplifier is actually a comparator instead of an amplifier. The PWM/logic circuit controls the power path FETs through some FET drivers based on input from the error amplifier. Figure 17 shows a generic control loop for a DC-to-DC converter with the components mentioned above.

## Figure 17. Diagram of a Generic Control Loop for a DC-to-DC Converter

This writing does not focus heavily on DC-to-DC converter control loops; however, they are shown to illustrate how dual-input DC-to-DC converters can be controlled and then highlight the challenges associated with controlling them in various configurations with a few common control loop types.

## Voltage Mode Control

Voltage mode control is the simplest method for controlling the output voltage of a DC-to-DC converter. The voltage mode control loop uses an integrator for the error amplifier which can be built from an opamp or an operational transconductance amplifier (OTA). The integrator compares the feedback voltage with a reference and based on the error polarity and magnitude the output, also known as the control voltage, will track up or down to compensate for error in the output with respect to the reference voltage. The control voltage is compared with a PWM saw-tooth waveform which produces a digital signal much like a clock whose duty cycle is controlled by the magnitude of the control voltage. The duty cycle of this clock signal is the duty cycle of the high side and low side FETs in the converter power path. The clock signal is an input either directly to the power path FETs or to FET drivers which turn the power path FETs on and off.

#### Current Mode Control

Current mode control adds a second and inner control loop to the basic voltage mode control scheme which senses the inductor current and feeds that information to the error amplifier. This has the effect of turning the inductor into a current source in the control loop transfer function which improves stability and eases the requirements on compensation.

#### Constant On-Time Control

Constant on-time control works in a very different fashion that the more traditional voltage and current mode control schemes. This control mode replaces the error amplifier with a comparator which compares the converter output voltage with a reference voltage. Any time the output voltage goes below the reference level the comparator changes its output state which triggers the control logic to switch on the high side FET for a fixed on-time, otherwise the low-side FET is turned on unless discontinuous current mode is used. This control mode often does not require compensation, however, the logic behind it can be far more complicated than in voltage and current mode converters. Another advantage of the control scheme is that it offers a faster transient response than the others as the converter can compensate for loading changes on a cycle-by-cycle basis.

## CHAPTER THREE: DUAL-INPUT DC-TO-DC CONVERTER POWER PATHS

In most applications where two power sources are being used to supply power to a single load, a pair of DC-to-DC converters will be placed in parallel. The subject of this chapter is to show alternative topologies for achieving this using a single power path. These alternate topologies include a dual-input four-FET buck-boost converter, two types of dual-input SEPIC converters, and a dual-input zeta converter.

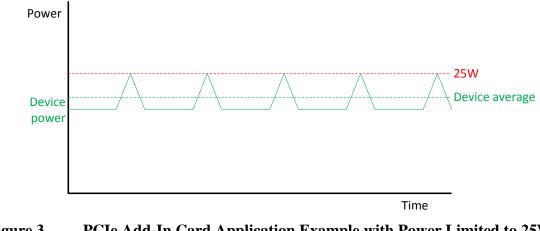

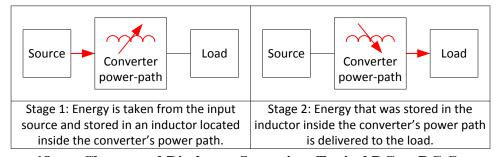

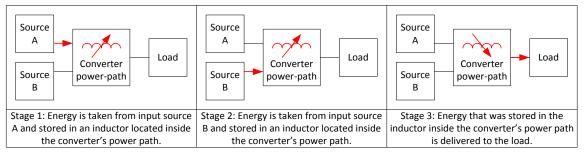

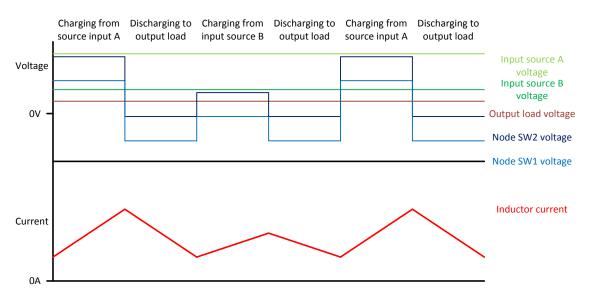

The general theory of operation for these converters is that power is drawn alternately from each input power source. In a traditional DC-to-DC converter there are two phases: one where energy is drawn from the input and stored in an inductor: and a second where that energy is released from the inductor to the load as shown in Figure 18. In these topologies a third phase is added where power is drawn from the second input power source. Figure 19 shows the addition of a third phase for the dual-input converter. During the phase where power is being drawn from the input power source(s) a bulk capacitor at the load supplies power to the load, this is shown in the detailed schematics that follow.

Figure 18. Charge and Discharge Stages in a Typical DC-to-DC Converter

Figure 19. Charge and Discharge Stages in a Dual-Input DC-to-DC Converter

Because there are three phases of operation there are two ways in which they can be combined during the cyclic operation of a DC-to-DC converter. One way is to draw the input power from both sources during the same cycle which will be referred to as incycle operation. The other way is to draw energy from each source every other cycle, this will be referred to as cycle-by-cycle operation. Table 5 shows the sequences of these phases for the dual-input DC-to-DC converters covered in this writing. Each series of phases repeats continuously as shown during operation of the converter.

Table 5.Table of Operation for Dual-Input DC-to-DC Converters

| In-cycle operation       |                                                       |

|--------------------------|-------------------------------------------------------|

| 1. Input A               | Energy is drawn from input source A and stored in the |

|                          | inductor(s)                                           |

| 2. Input B               | Energy is drawn from input source B and stored in the |

|                          | inductor(s)                                           |

| 3. Output                | Energy is discharged from the inductor(s) to the load |

| Cycle-by-cycle operation |                                                       |

| 1. Input A               | Energy is drawn from input source A and stored in the |

|                          | inductor(s)                                           |

| 2. Output                | Energy is discharged from the inductor(s) to the load |

| 3. Input B               | Energy is drawn from input source B and stored in the |

|                          | inductor(s)                                           |

| 4. Output                | Energy is discharged from the inductor(s) to the load |

In-cycle operation has the advantage of moving the fundamental frequency of the current noise radiated to the input source to a higher frequency than in cycle-by-cycle operation. This is because in-cycle operation pulls a pulse of current from the source at the same frequency that the converter is operating, whereas cycle-by-cycle operation pulls current as one half of the frequency of operation of the converter. The advantage for out-of-cycle control is that there are only two phases used per cycle which causes fewer off-on and on-off transitions per cycle which leads to improved efficiency due to lower switching losses when compared to in-cycle operation.

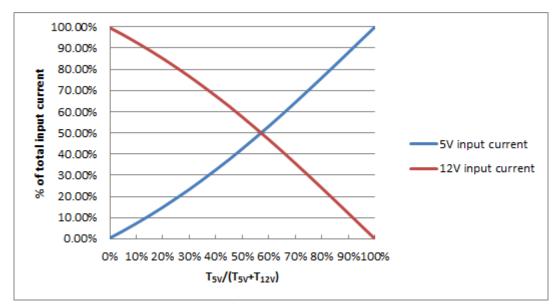

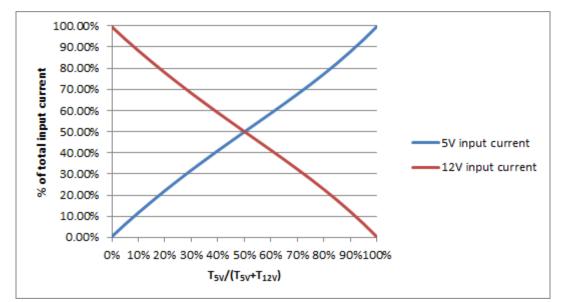

To make the comparison between each one, all simulations are done with the same assumptions about the characteristics of the converters; those assumptions are listed below in Tables 6 and 7. Each converter has been designed around a common set of input and output requirements in order to provide a fair comparison of each topology. These requirements are that the inputs are 12V and 5V, the output is 3.3V, and approximately half of the input current is drawn from each source.

The FET gate charge is included for the power path simulations to capture its impact on efficiency between in-cycle and cycle-by-cycle operation. The gate charge is modeled by placing a constant current load in the 12V input to the converter with a current draw that matches the power draw of the FET gate charge for the number of FETs, switching pattern, and switching frequency of each power path. The Equation used to determine this current is shown in Equation (12) where  $N_{SW}$  is the number of FETs that switch in a given cycle,  $F_{SW}$  is the switching frequency, and  $Q_G$  is the gate charge of each FET.

$$I_{CHG} = N_{SW} * F_{SW} * Q_G \tag{12}$$

| Inductor inductance               | 2μH   |

|-----------------------------------|-------|

| DC blocking capacitor capacitance | 220µF |

| Input capacitor capacitance       | 47µF  |

| Output capacitor capacitance      | 100µF |

Table 6.Assumptions for Component Properties

Table 7.

Assumptions for Component Parasitic Properties

| FET on resistance                       | 10mΩ                             |

|-----------------------------------------|----------------------------------|

| FET off resistance                      | 100ΜΩ                            |

| FET body diode on resistance            | 10mΩ                             |

| FET body diode forward voltage          | 350mV                            |

| FET body diode off resistance           | 100ΜΩ                            |

| FET gate charge                         | 20nC, modeled with constant load |

| Inductor DC resistance                  | 10mΩ                             |

| DC blocking capacitor series resistance | 10mΩ                             |

| Input capacitor series resistance       | $1m\Omega$                       |

| Output capacitor series resistance      | 1mΩ                              |

## **Traditional Approach**

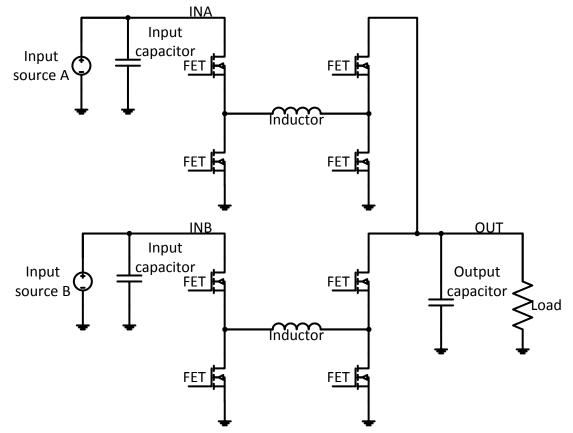

Typically when a load must draw power simultaneously from two power sources the solution is to take two independent DC-to-DC converters and run them in parallel. In the case of buck-boost regulators which are the focus of this writing, the configuration would look like what is shown in Figure 20 implemented with four-FET buck-boost converters. Because the two converters are synchronous (power can flow in either direction) care must be taken that one converter does not begin to conduct in the reverse direction. This reverse flow can happen if one converter is trying to move the output voltage even slightly higher than the other. As the higher output voltage converter sources current from the input power supply to raise the voltage, the other converter will sink current back to its input power supply to lower the output voltage. Preventing reverse conduction in this situation can require complex current sensing circuitry at the output of one or both converters.

Figure 20. Two Four-FET Buck-Boost DC-to-DC Converters in Parallel

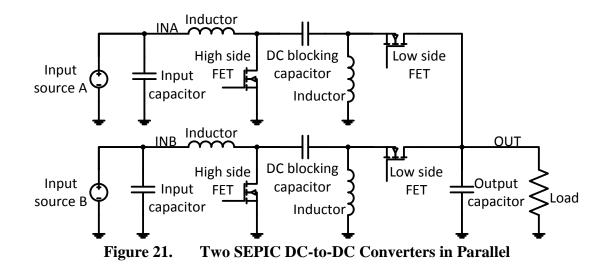

In the traditional approach, the operation of the two converters does not need to be synchronized. There are, however, benefits to synchronizing both converters. If each converter operates out of phase with the other (one is pulling energy from the input power source while the other is pushing energy out to the load), the output voltage ripple can be greatly reduced. This type of operation is sometimes referred to as dual phase operation. Depending on the control scheme used to prevent reverse current, synchronization of the converters may be beneficial or even necessary for the operation of the control loop that regulates the output current. The traditional approach of paralleling multiple converters can also be achieved using SEPIC and zeta converters as shown in Figures 21 and 22, respectively. These configurations share the same concerns with reverse current flows as mentioned previously. The differences in the design considerations between using two four-FET buck-boost converters and two SEPIC or zeta converters are the same as those for single input converters. Most commonly, however, the configuration of two four-FET buckboost converters is chosen for the applications mentioned in this writing for the simplicity of FET drivers required to drive the four-FET buck-boost compared to the SEPIC and zeta converters.

One advantage of the traditional approach that is not shared by the dual-input converter is that there is no penalty for supporting either input voltage being greater than the other. This is because each input is tied to an independent power path and is therefore fully isolated from the other input so long as reverse current flow does not occur. The dual-input topologies as explained below do have a penalty if supporting the characteristic that either input power source may be at a higher voltage than the other source.

#### **Dual-Input Four-FET Buck-Boost**

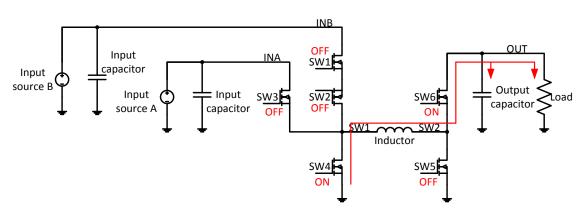

The dual-input four-FET buck boost converter achieves the dual-input function using a single power path as opposed to the traditional approach which uses two power paths. The power path for a dual-input four-FET buck-boost converter is shown in Figure 23 The difference from the single input four-FET buck boost is the addition of the extra input transistor(s) to connect the second input power source.

The purpose of the dual FETs SW1 and SW2 are to provide reverse blocking during the time when SW1 and SW2 are disabled and SW3 is enabled, at this time the voltage at node SW1 is the same as that of node INA, if the voltage at INA is greater than the voltage at INB then a single FET in place of SW1 and SW2 would be reverse biased and would begin to conduct through its body diode. This would effectively shunt current from the input source with the higher voltage to the input source with the lower input voltage which would potentially damage the input sources and the converter. By using back to back FETs connected as shown the body diodes are opposing each other and reverse conduction when the FETs are turned off is prevented; additionally by having dual FETs on input B, the voltage of input A may be the same or higher than the voltage of input B. If back to back FETs were used on both input A and input B, then either input could be higher than the other. The drawback of using back to back FETs in that they will contribute to higher conduction losses due to on-state resistance and higher switching losses due to the increase in gate charge.

Figure 23. Dual-Input Four-FET Buck-Boost Converter

This converter operates by storing energy from each of the two input sources in the inductor and releasing that energy to the output load. Figures 24, 25, and 26 show the flow of current through the converter during the three states of the converter: charging from input A, charging from input B, and discharging to the output load. Either cycle-bycycle or in-cycle operation may be used as described earlier in this chapter.

Figure 24. Dual-Input Four-FET Buck-Boost Charging From Input A

Figure 25. Dual-Input Four-FET Buck-Boost Charging From Input B

Figure 26. Dual-Input Four-FET Buck-Boost Discharging to the Output Load

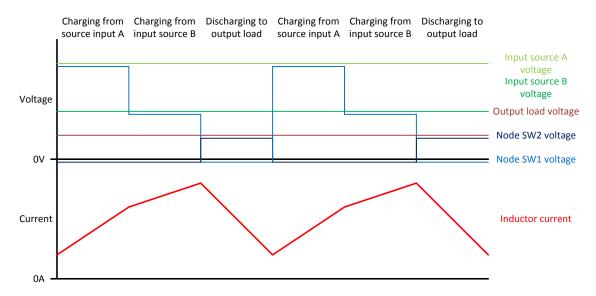

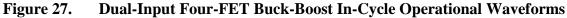

Operational waveforms of this converter are shown in Figure 27 detailing what operation would look like for in-cycle mode operation. Figure 28 shows cycle-by-cycle operation. During a charging phase from either input source the voltage across the inductor will cause the current to steadily increase, during this time energy is being stored in the magnetic field of the inductor. During an output phase the voltage across the inductor is reversed and the current begins to decrease as the stored energy is released to the output load.

Figure 28. Dual-Input Four-FET Buck-Boost Cycle-By-Cycle Operational Waveforms

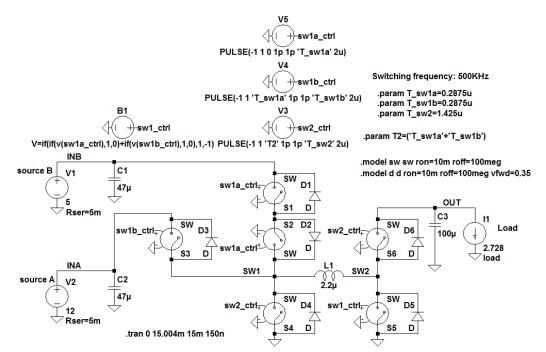

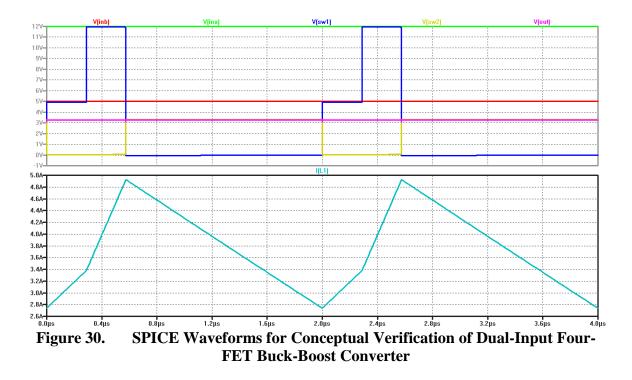

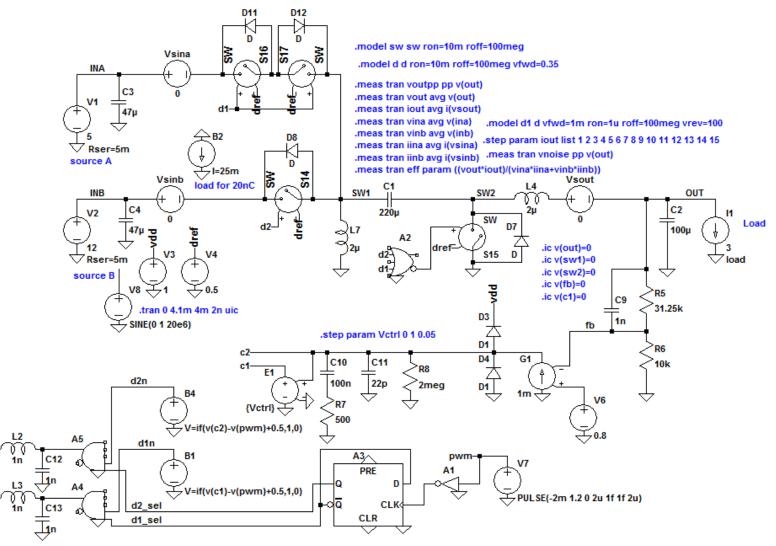

Operational demonstration of the dual-input four-FET buck-boost converter is done using LTSpice as a circuit simulation engine. Figure 29 shows the SPICE schematic used to prove operation of the converter with 12V and 5V inputs supplying ~3.26V to a 2.728A load. This simulation demonstrates in-cycle operation of the dual-input four-FET buck-boost converter. Ideal circuit elements are combined with some parasitic values to create a semi-realistic simulation of the power path of the converter as if constructed using MOSFETs. In-cycle operation is used for the purposes of this simulation. The resulting efficiency for this power path (neglecting gate charge effects) is approximately 95% with an output load of 2.728A (8.89W).

Figure 29. SPICE Circuit for Conceptual Verification of Dual-Input Four-FET Buck-Boost Converter

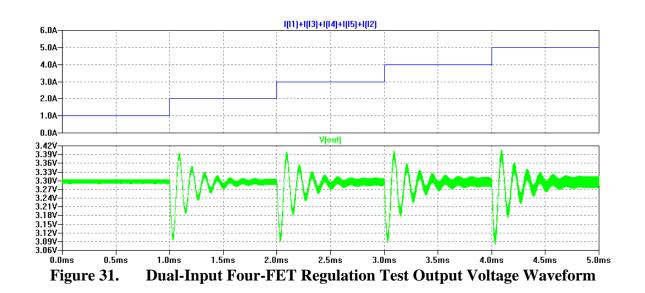

An additional simulation is done to demonstrate that the converter continues to regulate the output voltage and maintains the input current sharing ratio across different loads. The simulation is done using cycle-by-cycle operation and a voltage mode control loop regulates the output voltage. Figure 31 shows the results of this simulation. Simulation conditions are the same as in the previous simulation with the difference being that the load steps from 1A to 5A in 1A steps each lasting 1ms. Figure 31 shows the output voltage of the dual-input four-FET converter during this test, the graph does show that the control loop used for this test is not precisely tuned, however, this does not impact the results for the power paths efficiency or it's input current sharing.

| Output      | Output      | Input current | Input     | Input current | Input     | Efficiency |

|-------------|-------------|---------------|-----------|---------------|-----------|------------|

| current (A) | voltage (V) | A (A)         | current A | B (A)         | current B |            |

| 1           | 3.299       | 0.198         | 50%       | 0.199         | 50%       | 98%        |

| 2           | 3.298       | 0.397         | 49%       | 0.412         | 51%       | 95%        |

| 3           | 3.298       | 0.616         | 50%       | 0.618         | 50%       | 94%        |

| 4           | 3.298       | 0.837         | 50%       | 0.839         | 50%       | 93%        |

| 5           | 3.298       | 1.053         | 49%       | 1.083         | 51%       | 90%        |

Table 8.Dual-Input Four-FET Regulation Test Results

## **Dual-Input Zeta Converter**

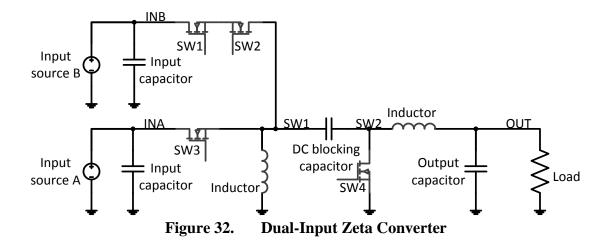

The zeta converter can be converted to a dual-input converter by using the same principles as those applied to the four-FET buck-boost. A second input FET path is added to connect an additional input power source. Figure 32 shows the dual-input zeta converter power path. Due to the inherent buck-boost nature of the zeta (and SEPIC) converter there is no distinction between buck or boost and buck-boost operation for this type of converter which simplifies the control requirements when using this power path topology.

Input source A in this example may be the same as or higher voltage than input source B. For the same reasons as described in the section on the dual-input four-FET buck-boost converter, a second FET is added to one of the input legs to prevent current from flowing from input source A to input source B. To remove the input voltage restriction a second FET can be added in line with input source A (next to SW3).

Operation of the dual-input zeta is the same as for the dual-input four-FET buckboost. There are three possible states or phases of operation. Charging from input source A, charging from input source B, and discharging to the output load. Figures 33, 34, and 35 show the flow of current in the power path during these phases of operation.

Figure 33. Dual-Input Zeta Current when Charging From Input Source A

The dual-input zeta converter has the same current flow characteristics in its two inductors as the single input zeta does. The input side inductor (connected to node SW1) always has current flowing towards ground and the output side inductor (connected to node SW2) always has current flowing towards the output load. Waveforms for the dualinput zeta converter are shown in Figure 36 for in-cycle operation and Figure 37 for cycle-by-cycle operation. The inductors of a zeta converter will typically have the same AC current. The DC current of the input inductor will be equal to the sum of the average input currents and the output inductors DC current will be equal to the average output current. For simplicity only one waveform is shown which represents the inductor current.

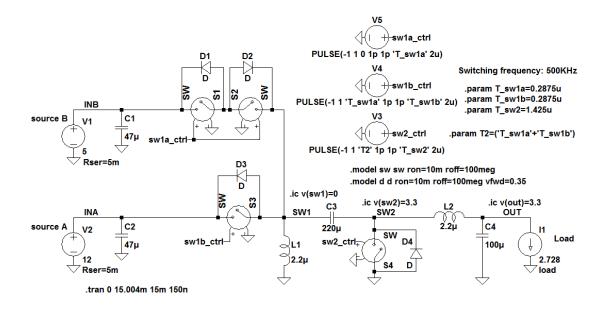

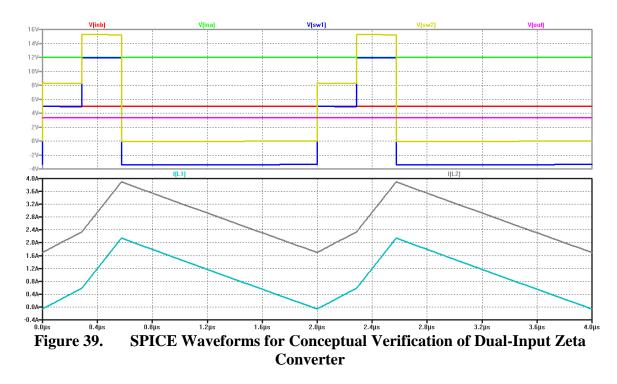

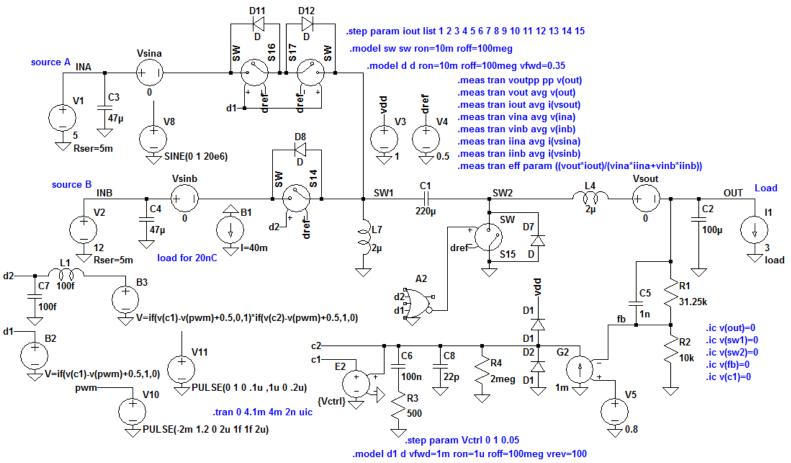

To verify the operation the dual-input zeta an LTSpice simulation is done using the same methods as is done for the dual-input four-FET buck-boost converter. The simulation conditions are input voltages of 12V and 5V and the output voltage is approximately 3.33V. Figure 38 shows the SPICE schematic and Figure 39 shows the resulting waveforms. The resulting efficiency for this power path (neglecting gate charge effects) is approximately 97% with an output load of 2.728A (9.08W).

Figure 38. SPICE Circuit for Conceptual Verification of Dual-Input Zeta Converter

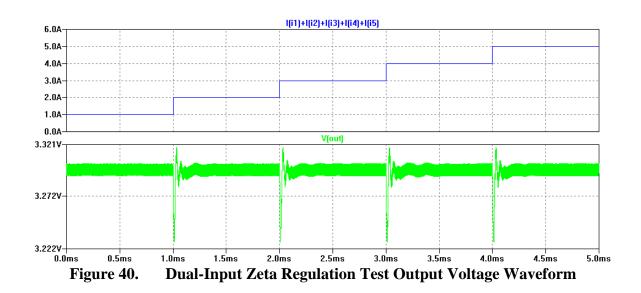

An additional simulation is done to demonstrate that the dual-input zeta converter continues to regulate the output voltage and maintains the input current sharing ratio across different loads. As with the dual-input four-FET converter the simulation is done using cycle-by-cycle operation and a voltage mode control loop regulates the output voltage. Table 9 shows the results of this simulation. Simulation conditions are the same as in the previous simulation with the difference being that the load steps from 1A to 5A in 1A steps each lasting 1ms. Figure 40 shows the output voltage of the converter during the test, there is some oscillation due to the voltage mode control loop not being precisely tuned for this test.

| Output      | Output      | Input current | Input     | Input current | Input     | Efficiency |

|-------------|-------------|---------------|-----------|---------------|-----------|------------|

| current (A) | voltage (V) | A (A)         | current A | B (A)         | current B |            |

| 1           | 3.299       | 0.196         | 49%       | 0.201         | 51%       | 97%        |

| 2           | 3.299       | 0.402         | 50%       | 0.396         | 50%       | 98%        |

| 3           | 3.299       | 0.600         | 50%       | 0.609         | 50%       | 96%        |

| 4           | 3.299       | 0.809         | 50%       | 0.821         | 50%       | 95%        |

| 5           | 3.299       | 1.024         | 50%       | 1.037         | 50%       | 94%        |

Table 9.Dual-Input Zeta Regulation Test Results

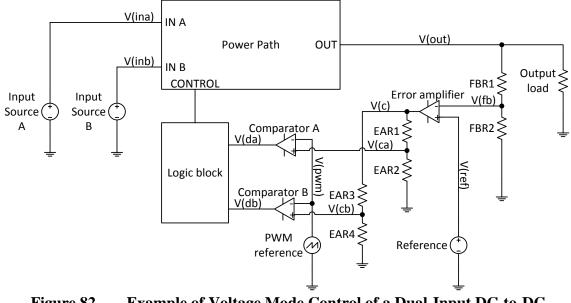

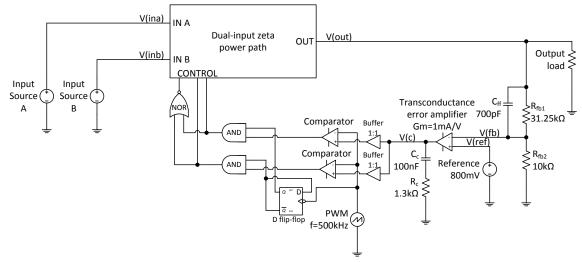

## **Dual-Input SEPIC Converter**