# HARDWARE IMPLEMENTATION OF REAL-TIME OPERATING SYSTEM'S

# THREAD CONTEXT SWITCH

by

Deepak Kumar Gauba

A thesis

submitted in partial fulfillment

of the requirements for the degree of

Master of Science in Computer Engineering

Boise State University

August 2010

© 2010

Deepak Kumar Gauba

# ALL RIGHTS RESERVED

# BOISE STATE UNIVERSITY GRADUATE COLLEGE

# DEFENSE COMMITTEE AND FINAL READING APPROVALS

of the thesis submitted by

Deepak Kumar Gauba

Thesis Title: Hardware Implementation of Real-Time Operating System's Thread Context Switch

Date of Final Oral Examination: 10 May 2010

The following individuals read and discussed the thesis submitted by student Deepak Kumar Gauba, and they evaluated his presentation and response to questions during the final oral examination. They found that the student passed the final oral examination.

| Nader Rafla, Ph.D.           | Chair, Supervisory Committee  |  |  |

|------------------------------|-------------------------------|--|--|

| Jennifer A. Smith, Ph.D.     | Member, Supervisory Committee |  |  |

| James R. Buffenbarger, Ph.D. | Member, Supervisory Committee |  |  |

The final reading approval of the thesis was granted by Nader Rafla, Ph.D., Chair of the Supervisory Committee. The thesis was approved for the Graduate College by John R. Pelton, Ph.D., Dean of the Graduate College.

To my father...

# ACKNOWLEDGEMENTS

I would like to thank my professors and colleagues at Boise State University for their support, guidance and encouragement. In particular, I would like to sincerely thank my advisor, Dr. Nader Rafla, for his valuable guidance and support while completing my graduate education. The thesis could never have been completed without him.

I would also like to thank Dr. James R. Buffenbarger and Dr. Jennifer A. Smith for being on my thesis committee, and guiding and encouraging me throughout my research work. I am very grateful to Dr. James R. Buffenbarger for his guidance and valuable suggestions during my research work, which helped me, finish my work on time.

Finally, I would like to thank my family for their unwavering support and encouragement. Thank you all.

## ABSTRACT

Increasingly, embedded real-time applications use multi-threading. The benefits of multi-threading include greater throughput, improved responsiveness, and ease of development and maintenance. However, there are costs and pitfalls associated with multi-threading.

In some of hard real-time applications, with very precise timing requirements, multi-threading itself becomes an overhead cost mainly due to scheduling and contextswitching components of the real-time operating system (RTOS). Different scheduling algorithms have been suggested to improve the overall system performance. However, context-switching still consumes much of the processor's time and becomes a major overhead cost especially for hard real-time embedded systems.

A typical RTOS context switch consumes 50 to 80 processor clock cycles (depending on processor architecture and context size) to store and restore the thread context. If a real-time application needs to respond to an event repeatedly less than this time, then the overall system performance may not be acceptable. The suggested approach in this thesis improves the context-switching time drastically. This technique has been implemented in hardware, as part of the processor state along with new central processing unit (CPU) instructions to take care of the context-switching process without interacting with external memory. With the suggested approach, the thread contextswitch can be achieved in 4 CPU clock cycles independent of context size. This is a significant improvement to thread context switching.

vi

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTSv                          |

|--------------------------------------------|

| ABSTRACTvi                                 |

| LIST OF FIGURES                            |

| LIST OF TABLES                             |

| CHAPTER 1 – INTRODUCTION                   |

| 1.1 Organization                           |

| 1.2 Contributions of This Thesis           |

| CHAPTER 2 – RTOS OVERVIEW                  |

| 2.1 Plasma MIPS Processor Architecture     |

| 2.1.1 CPU Hardware Architecture 4          |

| 2.1.2 MIPS Instruction Format              |

| 2.2 Real-Time Operating System             |

| 2.2.1 RTOS Functionality 10                |

| 2.2.2 Context Switching                    |

| 2.2.3 Co-Operative Operating System        |

| 2.3 Summary                                |

| CHAPTER 3 – PROBLEM STATEMENT AND SOLUTION |

| 3.1 Cost of Context Switching              |

| 3.2 Current Approaches 15                  |

| 3.2 Proposed Solution                                     | 20 |

|-----------------------------------------------------------|----|

| 3.3 Summary                                               | 22 |

| CHAPTER 4 – HARDWARE DESIGN AND IMPLEMENTATION            | 23 |

| 4.1 Register File Design                                  | 23 |

| 4.2 Context-Switching Instruction Design                  | 24 |

| 4.3 Context-Switching Instruction Hardware Implementation | 25 |

| 4.4 Hardware Synthesis and Implementation                 | 26 |

| 4.5 Summary                                               | 28 |

| CHAPTER 5 – SOFTWARE DESIGN                               | 29 |

| 5.1 Co-Operative Operating System Design                  | 29 |

| 5.1.1 Operating System Design                             | 30 |

| 5.1.2 Operating System Operation                          | 31 |

| 5.2 Assembler Modifications                               | 34 |

| 5.3 Software System Implementation                        | 36 |

| 5.4 Summary                                               | 36 |

| CHAPTER 6 – EXPERIMENTAL RESULTS AND ANALYSIS             | 38 |

| 6.1 Hardware Verification                                 | 38 |

| 6.3 Test Applications                                     | 45 |

| 6.3.1 Test Application – 1                                | 45 |

| 6.3.2 Test Application – 2                                | 48 |

| 6.3.3 Test Application – 3                                | 50 |

| CHAPTER 7 – CONCLUSIONS AND FUTURE WORK                   | 53 |

| BIBLIOGRAPHY | 56 |

|--------------|----|

| APPENDIX A-1 | 57 |

| APPENDIX A-2 | 66 |

| APPENDIX B-1 | 75 |

| APPENDIX B-2 | 79 |

| APPENDIX B-3 | 82 |

| APPENDIX B-4 | 84 |

| APPENDIX B-5 | 85 |

| APPENDIX C-1 | 86 |

| APPENDIX C-2 | 90 |

# LIST OF TABLES

| Table 2. 1: MIPS Registers                                                       | 7   |

|----------------------------------------------------------------------------------|-----|

| Fable 2. 2: Instruction Format for Instruction Type R                            | . 8 |

| Table 2. 3: Instruction Format for Instruction Type I                            | . 8 |

| Fable 2. 4: Instruction Format for Instruction Type J                            | . 9 |

| Table 4. 1: The cnxt_switch Signal Bit Map                                       | 24  |

| Table 4. 2: Save Context Instruction Bit Map    2                                | 25  |

| Table 4. 3: Restore Context Instruction Bit Map                                  | 26  |

| Table 4. 4: FPGA Device Resource Usage for Original Plasma MIPS Architecture and |     |

| Modified MIPS Architecture 2                                                     | 27  |

| Table 5. 1: Operating System Interface Functions                                 | 30  |

| Table 5. 2: "mips_opcode" Structure Data Members                                 | 35  |

| Fable 5. 3: 'scxt' and 'rcxt' Instruction Assembler Values                       | 35  |

# LIST OF FIGURES

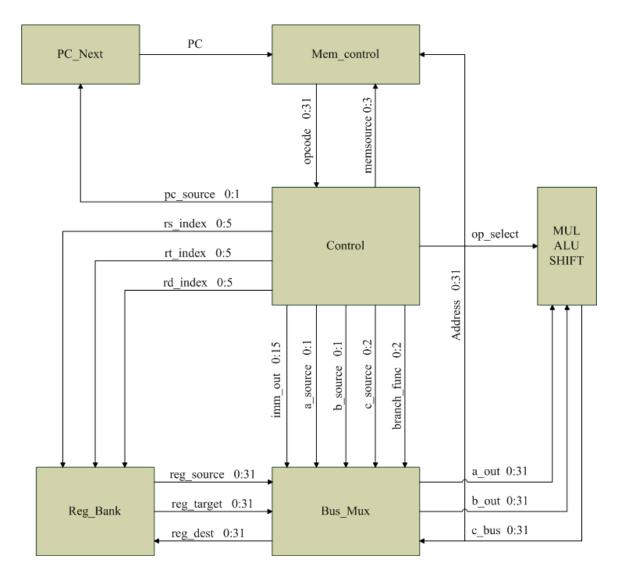

| Figure 2. 1: Plasma MIPS Processor Architecture                            |

|----------------------------------------------------------------------------|

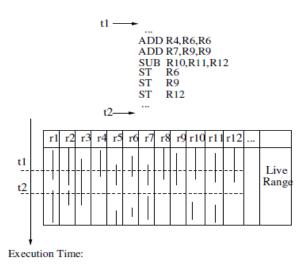

| Figure 3. 1: Context Switching using Variable Context Size [4] 16          |

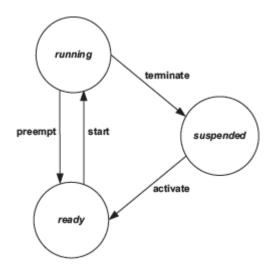

| Figure 3. 2: Thread State Diagram of OSEK Operating System [2] 17          |

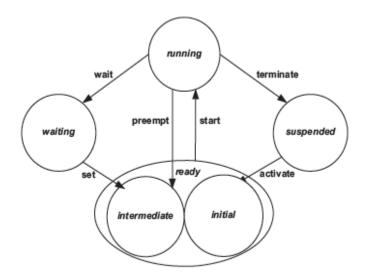

| Figure 3. 3: Modified Thread State Diagram of OSEK Operating System [2] 18 |

| Figure 3. 4: Modified Thread State Diagram of OSEK Operating System [5] 19 |

| Figure 3. 5: Modified MIPS Processor Architecture                          |

| Figure 5. 1: Task Structure                                                |

| Figure 5. 2: Co-Operative Operating System's Flow Chart                    |

| Figure 5. 3: MIPS Instruction Structure Format in GNU Assembler            |

| Figure 6. 1: Waveform for 'scxt \$4' Instruction                           |

| Figure 6. 2: Waveform for 'rext \$4' Instruction                           |

| Figure 6. 3: Waveform to Verify an Out-of-Range Instruction Operand        |

| Figure 6. 4: Context Switch Instructions Waveform                          |

| Figure 6. 5: Flowchart for Test Application – 1                            |

| Figure 6. 6: Serial Debug Log from Test Application – 1                    |

| Figure 6. 7: Serial Debug Log from Test Application – 2 50                 |

| Figure 6. 8: Serial Debug Log from Test Application – 3A                   |

| Figure 6. 9: Serial Debug Log from Test Application – 3B                   |

#### CHAPTER 1 – INTRODUCTION

Context switching is a very important part of any multi-tasking operating system. In most hard real-time operating systems, running with time-critical applications, contextswitching becomes an overhead due to its timing requirements. Two factors contribute to this overhead cost: direct and indirect. The direct cost of context switching includes moving contents of the Central Processing Unit (CPU) registers to and from external memory or cache. Indirect cost includes perturbation of cache, CPU pipeline, etc. [1]. In general, it is difficult to measure the total cost of context-switching. In the case of a hard real-time operating system (RTOS), with linear memory architecture, the direct cost of context switching constitutes a major part of the total context-switching cost. Many algorithms have been developed to reduce the direct cost of context switching [2, 3, 4]. These algorithms are either executed on specific high performance processors with cache or suggest examining the processor state and then deciding whether or not it is actually required to save the entire processor state/context [3, 4]. This latter approach is good for improving overall system performance. But if an application needs to save and restore the complete state frequently with hard real-time requirements, then this approach would not be effective. In addition, even if the context size is reduced, the basic context registers (like the program counter, stack pointer, global pointer, etc.) still need to be saved and restored. As context size changes from thread to thread, it would be difficult to design a deterministic system, which is another basic requirement of a hard RTOS. Since these

registers are being saved and restored to and from external memory or cache, this will consume some clock cycles depending upon the number of these registers.

This thesis is divided into two major components: hardware and software. The hardware component mainly involves the implementation of a number of register files to hold the operating system's thread contexts inside the processor and the development of the hardware support for new instructions to store and restore the contexts to and from the newly implemented register files. This concept is verified by actually implementing the register files in a Very high speed integrated circuit Hardware Description Language (VHDL) and executing the new CPU instructions to ensure the correct data movement.

The software component has been further divided into two sub-parts. The first software sub-part is the implementation of a small co-operative operating system that executes the threads in a round-robin fashion, and to develop test applications. These applications need to call the operating system's scheduler function whenever it needs to switch to the next thread. This co-operative operating system and test applications have been executed on a modified, as well as on a traditional, MIPS processor for a proof of concept and to measure the performance improvement.

The second software sub-part is the addition of newly implemented MIPS instructions to the MIPS assembler so that the correct executable file can be generated automatically to include the newly implemented context-switch instructions on the modified processor hardware.

# 1.1 Organization

This thesis is organized in seven chapters. Chapter 1 gives a brief introduction and outline. Chapter 2 explains the MIPS processor architecture and its instruction types; RTOS's basic design with its scheduler and context-switch components; and, cooperative operating system design. Chapter 3 provides the problem statement and a description of the proposed approach. Chapter 4 talks about the hardware implementation, which includes modifications in the MIPS processor architecture and details of newly implemented context-switch CPU instructions. Chapter 5 talks about software components, which includes details of the newly implemented co-operative operating system and MIPS assembler modifications. Chapter 6 explores and analyzes the test results generated from the hardware simulation and software test applications. Finally, Chapter 7 concludes the research and describes some future work based on this thesis.

## **1.2 Contributions of This Thesis**

This thesis provides a review and an in-depth discussion of the different techniques and components required for the context-switching of a RTOS. It also provides a core framework design for context-switching implementation in the hardware along with the instructions used by the CPU for this purpose. A test operating system is developed to prove the proposed concept, which is expandable to general operating systems.

#### CHAPTER 2 – RTOS OVERVIEW

A typical real-time embedded system basically consists of two components: an embedded processor and a RTOS. To achieve a required performance, specially designed applications need to be developed as per the processor and RTOS. In this chapter, the architecture of a commonly used processor and the basic functionality of a RTOS are described.

For this research, a Plasma MIPS processor implementation [6] has been chosen for experimentation. The hardware implementation of the Plasma MIPS processor is done in VHDL for Xilinx© and Altera© Field Programmable Gate Array (FPGA) boards. The development work and implementation are carried out on a Xilinx Spartan-3E Starter kit board due to its availability.

# 2.1 Plasma MIPS Processor Architecture

The Plasma MIPS processor architecture is divided into two parts. The first part describes the hardware architecture, which deals with different modules, buses, and registers. The second part describes the CPU instruction formats and types of instructions.

#### 2.1.1 CPU Hardware Architecture

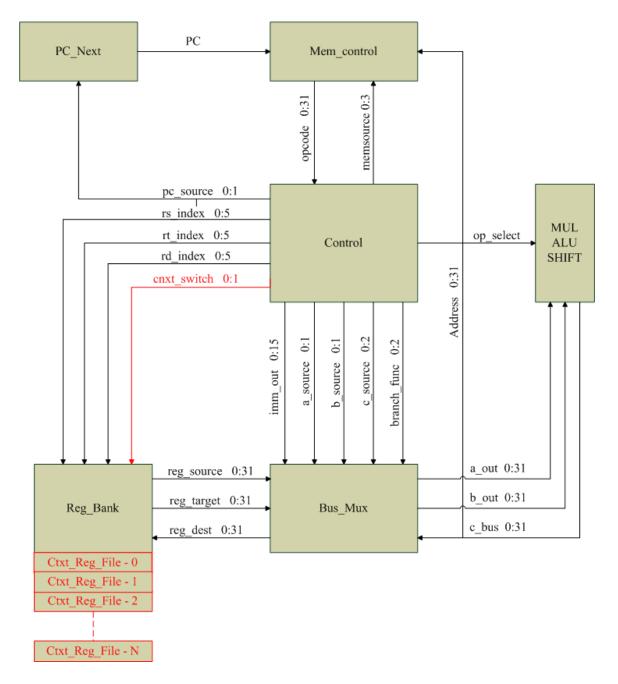

Figure 2.1 shows a block diagram of the plasma MIPS processor architecture. The "*control*" module is the heart of this implementation. The "*mem\_control*" module fetches

instructions from external memory at the address specified by the program counter (PC) register and sends it out in the form of a 32-bit code to the "*control*" module. The control module processes the code and creates a 60-bit Very Large Word Instruction (VLWI) code and sends it out to other processor modules such as "*Reg\_Bank*", "*Bus\_Mux*", "*PC\_Next*", and "*MUL-ALU-SHIFT*" for further processing. Out of the 60-bit VLWI code generated by the "*control*" module, 26 bits are sent out to the "*Bus\_Mux*" module, which includes 16 bits for immediate data "*imm\_out*", 7-bit bus control signals, and 3 bits to indicate the type of branch instructions. The "*MUL-ALU-SHIFT*" unit performs the necessary arithmetic operations selected by the 16-bit signal "*op\_select*" received from the "*control*" module.

Figure 2. 1: Plasma MIPS Processor Architecture

The "*reg\_bank*" module implements all the registers, including program counter (pc), stack pointer (sp), and global pointer (gp), as described in Table 2.1. In the case of the Plasma implementation, all registers in the "*reg\_bank*" module have been implemented in the FPGA's block random access memory (RAM). So, only one register can be accessed at a time.

The "*control*" module also generates three sets of signals (rs\_index, rt\_index, and rd\_index); each is 6 bits wide. These are used to access the registers in the "*reg\_bank*" module. The "*reg\_bank*" module outputs the requested data to the "*bus\_mux*" module from the requested register.

| Register    | Register Name   | Function                                   |  |

|-------------|-----------------|--------------------------------------------|--|

| \$0         | zero            | Always contains 0                          |  |

| \$at        | at              | Assembler temporary                        |  |

| \$2 - \$3   | v0 - v1         | Function return value                      |  |

| \$4 - \$7   | a0 – a3         | Function parameters                        |  |

| \$8 - \$15  | t0-t7           | Function temporary values                  |  |

| \$16 - \$23 | s0 - s7         | Saved registers across function calls      |  |

| \$24 - \$25 | t8-t9           | Function temporary values                  |  |

| \$26 - \$27 | k0 – k1         | Reserved for interrupt handler             |  |

| \$28        | gp              | Global Pointer                             |  |

| \$29        | sp              | Stack Pointer                              |  |

| \$30        | s8              | Saved register across function calls       |  |

| \$31        | ra              | Return address from function call          |  |

| HI-LO       | lo-hi           | Multiplication/division results            |  |

| PC          | Program Counter | Points at 8 bytes past current instruction |  |

| EPC         | ерс             | Exception program counter return address   |  |

Table 2. 1: MIPS Registers

# 2.1.2 MIPS Instruction Format

There are three types of basic instruction formats in the MIPS processor. These are defined as R-Type, I-Type, and J-Type. The R-Type instruction format is used to create instructions with register operations like load and store instructions; the I-Type instruction format is used to implement instructions that involve immediate data; and, the J-Type is used to implement jump or branch instructions. In the R-Type instruction format, the 6 high order bits (opcode) are 0 and the 6 low order ones (funct) define the function being performed by the instruction. The middle bits indicate indexes of different registers. This is detailed in Table 2.2.

Table 2. 2: Instruction Format for Instruction Type R

| Instruction Format for Type R                                                                             |        |    |    |    |       |       |  |

|-----------------------------------------------------------------------------------------------------------|--------|----|----|----|-------|-------|--|

| Bit Position         31 - 26         25 - 21         20 - 16         15 - 11         10 - 6         5 - 0 |        |    |    |    |       |       |  |

| Name                                                                                                      | opcode | rs | rt | rd | shamt | funct |  |

Table 2.3 shows the basic Type-I instruction format. The lower-order 16 bits are the immediate data and 6 high order bits (opcode) define the operation. Middle bits represent indexes of source and target registers.

| Table 2. 3: Instruction | ı Format for | <sup>•</sup> Instruction Type I |

|-------------------------|--------------|---------------------------------|

|-------------------------|--------------|---------------------------------|

| Instruction Format for Type I                      |        |    |    |                |  |  |  |

|----------------------------------------------------|--------|----|----|----------------|--|--|--|

| <b>Bit Position</b> 31 – 26 25 - 21 20 - 16 15 - 0 |        |    |    |                |  |  |  |

| Name                                               | opcode | rs | rt | immediate data |  |  |  |

Table 2.4 shows the Type-J instruction format where the lower-order 26 bits indicates the address and remaining bits (opcode) define the operation.

Instruction Format for Type JBit Position31 – 2625 - 0NameopcodeAddress

Table 2. 4: Instruction Format for Instruction Type J

#### 2.2 Real-Time Operating System

In general, an operating system (**OS**) is responsible for managing the hardware resources of a computer and hosting applications that run on the computer. A **RTOS** is a specialized type of OS that performs different tasks, but is specially designed to run applications with very precise timing and a high degree of reliability. They are intended for real-time applications. Such applications include embedded systems such as programmable thermostats, household-appliance controllers, industrial robots, spacecrafts, and industrial-control and scientific-research equipment.

Furthermore, RTOS can be divided into two categories, hard real-time and soft real-time operating systems. In a hard real-time or immediate real-time operating system, the completion of an operation, after its deadline, is considered useless and this may cause a critical failure of the complete system and can lead to an accident. The ECU (Engine Control Unit) of a car and CNC (Computer Numeric Control) machine control are some of the examples of hard real-time systems. On the other hand, a soft real-time system will tolerate such lateness and may respond with decreased service quality. Mobile-phone application and ink-jet printers are examples of a typical soft real-time system.

#### 2.2.1 RTOS Functionality

A RTOS always contains multi-tasking, also known as multi-threading. Multitasking is a technique used for processor time allocation. Applications are divided into logical pieces commonly called threads and a kernel (core of the operating system) that coordinates their execution. A thread can be defined as an executing instance of an application and its context is the contents of the CPU registers and program counter at any instant of time. A register is a small fast memory inside a CPU (as opposed to the slower memory outside of the CPU) and is used to speed up the execution of programs by providing quick access to commonly used values, generally those in the midst of a calculation.

All threads in a hard RTOS are not equal. Some threads of an application have greater importance or priority than others. The high-priority threads must meet their deadlines; otherwise, the system may lead to a complete failure or a deadly accident. A scheduler, in the real-time operating system's kernel, schedules the threads based upon their priority. It also arranges a list of threads ready for execution, based upon their priority, and schedules them from the top of the list. There are many scheduler algorithms available to perform the scheduling activity efficiently and fairly. The most commonly used scheduler algorithm for RTOS is priority-based preemptive scheduling. This algorithm enables the scheduler to preempt the current running thread if a high-priority

10

thread becomes ready to execute. If a number of threads in the system have the same priority, then the scheduler will schedule these threads in a round-robin fashion.

## 2.2.2 Context Switching

Scheduling threads is done based upon their priority and the scheduler invokes the context-switching module of the OS. The context-switching module suspends the current running thread and starts executing the next eligible thread from the scheduler's ready queue. The context-switching activity can be described in slightly more detail as the kernel performing the following activities with regard to threads on the CPU:

- 1. Suspends the progression of one thread and store the CPU's state (context) for that thread somewhere in memory.

- 2. Retrieves the context of the next thread in the scheduler's ready list from memory and restore it in the CPU's registers.

- 3. Returns to the location indicated by the program counter (the point at which the thread was suspended in an earlier context switch) in order to resume the thread's execution.

Accordingly, the context switch can be described as the kernel suspending execution of one thread on the CPU and resuming execution of some other thread of a higher or same priority. Context switching is an essential feature of multi-tasking operating systems. So by definition, a multi-tasking operating system is one in which multiple threads execute on a single CPU seemingly simultaneously and without interfering with each other. This illusion of concurrency is achieved by means of context switches that are occurring in rapid succession (tens or hundreds of times per second).

Context switching occurs as a result of threads voluntarily relinquishing their time in the CPU or as a result of the scheduler making the switch when a process has used up its allocated CPU time slice. A context switch can also occur as a result of a hardware interrupt, which is a signal from a hardware device to the kernel indicating that an event has occurred.

#### 2.2.3 Co-Operative Operating System

A hard real-time operating system cannot be designed without priority-based preemptive scheduling. On the other hand, soft real-time systems can be designed using round-robin scheduling in which all threads are scheduled in round-robin fashion and threads relinquish their CPU time voluntarily after reaching a logical end of the task or after executing for a fixed amount of time. Operating systems with this type of scheduler design are called co-operative operating systems, as threads cooperate with others running on the system.

#### 2.3 Summary

RTOSs are the most common component of today's typical real-time embedded systems. RTOSs use multi-threading to share the CPU time to achieve multi-tasking. The scheduler module of a RTOS does the required context switching to achieve a specified CPU time sharing among all threads. There are performance issues with the tradition context- switching implementations. Those issues, and a possible solution, will be discussed in the following chapters.

## CHAPTER 3 – PROBLEM STATEMENT AND SOLUTION

As described in the previous chapter, context switching is an important part of any multi-tasking OS. It is computationally intensive because it requires considerable processor time. Thus, context switching represents a substantial cost to the system in terms of CPU time. The cost of context switching goes even higher for a hard real-time system, as that makes it difficult to meet the thread's deadline.

# **3.1 Cost of Context Switching**

Research has been previously done to measure the cost of context switching in general [1]. The direct cost of context switching includes saving the CPU register data to/from external memory or cache and indirect cost includes perturbation of cache, CPU pipeline, etc [1]. That makes it difficult to measure the total cost of context switching. For a typical hard real-time system, with linear memory architecture, the direct cost of context switching constitutes the major part of the total context-switching cost. That is why many algorithms have been implemented to reduce the direct cost of context switching [2, 3, 4].

The direct cost of context switching depends upon the CPU architecture and the OS design. It is directly proportional to the number of CPU temporary (scratch) registers to be saved and restored, and the OS design. For example, in the case of the Advanced RISC Machine (ARM) processor, there are sixteen temporary registers (including program counter), apart from one status register, which are required to be saved and

restored during the context switching [1]. Similarly, for the MIPS processor, there are eleven registers that need to be saved, apart from program counter. So, context-switching time varies from processor to processor.

Similarly, a number of commercially available RTOSs like VxWorks, ThreadX, and QNX claim different context-switching times in terms of micro-seconds for different processors. Because of these variables, it is difficult to measure the total contextswitching time in general. That is why, for this research, measurement of contextswitching time is presented in terms of clock cycles.

To explain context-switching overhead, a hypothetical application that requires frequent context switching in a small amount of time is considered. Assume a real-time system with three threads; A, B and, C. Thread 'A' reads and samples input data from an analog input; thread 'B' processes each sampled datum and generates some control signals; and, thread 'C' generates the output signals based upon the control signals generated by thread 'B'. The sequence of operations is described as follows:

- Thread 'A' reads analog input data and releases CPU control by issuing an OS system call.

- The Kernel saves the context of thread 'A' somewhere in external memory by copying CPU temporary registers, the stack pointer, the program counter, etc. These registers are saved individually in sequence as the CPU is only able to generate one address at a time.

- 3. The Kernel restores the context of thread 'B' from the external memory, by restoring CPU temporary registers, the program counter and the stack pointer in

sequence from external memory. After restoring the context, thread 'B' starts executing and processing the received sample and then generates the control data. Finally, thread 'B' releases the CPU control by executing a system call.

4. Now, the kernel saves the context of thread 'B' and restores the context of thread 'C' to and from the external memory, respectively. Thread 'C' then sends out the control data and releases the CPU control to thread 'A' to read the next sample.

If input analog data must be sampled at a higher frequency rate, and each sample is very important, then the context switch poses a large overhead, as each context switch would consume many CPU cycles. A typical context switch consumes 50 – 80 clock cycles and if a system needs to respond to an event in less than context-switching time, then that can be done by implementing the event response in an interrupt service routine (ISR) and useing an interrupt-driven system instead. But if those events are happening continuously, then the overall performance of the system will be degraded tremendously, as most threads may not get a chance to execute.

Since the registers are being saved in external memory, only one register could be saved at a time. Consequently, for N registers to be saved and restored, this approach would take at least 2 x 2 x N CPU clock cycles for a complete context switch. Practically, during these many clock cycles, the CPU normally remains idle, not doing any work assigned by the applications. That reduces the overall efficiency of the system.

## **3.2 Current Approaches**

To improve responsiveness, the context-switching time needs to be reduced. Many software and hardware based solutions have been proposed to reduce contextswitching time [2, 4, 5]. The software-based solutions mainly reduce the average contextswitching time by reducing the context size. The approach suggested by Xiangrong Zhou and Peter Petrov suggests achieving a low cost context-switching by using compiler, micro-architecture, and an OS kernel [4]. This technique identifies the switch points in the executing code, at compile time, at which a minimum number of context registers needs to be saved. If an interrupt occurs and the system needs to do a context switch, then the scheduler defers the context switch untill the execution reaches the next switch point where less context-registers need to be saved. The compiler identifies switch points and also provides the custom software routines to kernel for context switching. The authors used an example to explain the approach, as shown in Figure 3.1[4]. If an interrupt occurs at time t1, then all registers need to be saved as all registers are live at that point [4]. But if the context switching is deferred untill time t2, then only 3 registers need to be saved, as shown.

Figure 3. 1: Context Switching using Variable Context Size [4]

The good part of this approach is that the system is doing the actual task between time t1 and t2, but the duration between t1 and t2 is not fixed and can be longer as interrupt is an asynchronous event and a RTOS thread may miss a deadline. That can be taken care by a good RTOS kernel design but that would lead to a complex and non-deterministic system.

The other software-based approach is for a specific RTOS but can be implemented for any RTOS. The approach suggested by Zhaohui Wu, Hong Li, Zhigang Gao, Jie Sun, and Jiang Li, creates new thread states, and based upon the thread's state, the scheduler decides if context save or restore is actually required [2]. It helps in reducing the average context-switch time of the system.

Figure 3. 2: Thread State Diagram of OSEK Operating System [2]

Figure 3.2 shows the thread's state diagram of the OSEK OS. The original OSEK OS thread's state diagram shows three states. If a thread is waiting for a resource or if a

thread is terminated, then it goes to a *suspended* state. The authors suggested one new state called *waiting* state, in which the thread goes into waiting state if the thread is waiting for a resource, and it goes into suspended state when it is being terminated. The thread's *ready* state is further divided into two states: *initial* and *intermediate*.

Figure 3. 3: Modified Thread State Diagram of OSEK Operating System [2]

As shown in Figure 3.3, when a thread becomes active in the suspended state, it will be in the *initial* state, and when a thread becomes ready from the waiting state, it will be in the *intermediate* state. When a thread's state changes from a running state to a *suspended* state, then there is no need to save the context as in that case the thread gets terminated. On the other hand, when a thread's state changes from *suspended* to *ready/initial* state, then there is no need to restore the context as thread would start executing from the beginning. This approach improves the average context-switch time

and thus the overall throughput of the system. As the context-switching time would be reduced in some cases, designing a deterministic system with this approach would lead to a very complex design.

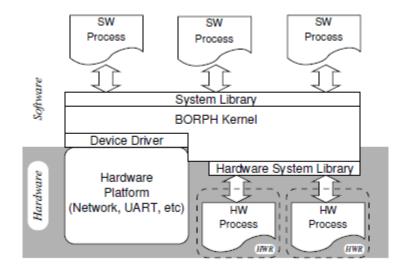

Current hardware-based solution use reconfigurable hardware. Research by Hyden Kwok-Hay So, at Berkeley University, uses BORPH (Berkeley Operating system for ReProgrammable Hardware) OS [5]. This operating system is specially designed for FPGA-based reconfigurable hardware. The BORPH kernel supports FPGA applications similar to conventional OS support for programs. The FPGA resources are managed by a kernel similar to other system resources.

Figure 3. 4: Modified Thread State Diagram of OSEK Operating System [5]

The BORPH is a UNIX-based OS with a virtual file system that allows users to communicate with a running gateware design through UNIX file system access. Figure

3.4 shows the basic block diagram of this reconfigurable hardware-based approach. Since different processes can be created in hardware, which can execute in parallel and keep their state, there is no need of real context-switching for the processes running in the hardware. The OS tasks that require fast context-switching can be implemented as hardware processes to avoid context-switching overhead. This approach is good for hard real-time systems and this would provide good throughput, and also would be deterministic. But this approach would take lot of hardware resources and it would be difficult to design and maintain such a system.

# **3.2 Proposed Solution**

The proposed approach reduces the context-switch time drastically to a fixed number of clock cycles independent of the number of context registers, because the context is saved in a newly created context register file. These context-register files are implemented in the processor hardware itself, as a part of the register bank module. The proposed modified MIPS processor architecture is shown in Figure 3.5.

Figure 3. 5: Modified MIPS Processor Architecture

To save and restore a thread's context in the internal register files, two new CPU instructions have been implemented in the processor hardware. Additional software needs

to be developed to use these instructions to exploit the suggested hardware design. Since new instructions are being added to the processor architecture, the MIPS assembler has to be modified to support the new instructions.

# 3.3 Summary

Context switching is a major bottleneck for hard RTOS-based systems, especially for applications that require frequent context switching, and have stringent deadlines for different threads. Many software approaches try to reduce context-switching overhead, but this leads to making the system non-deterministic, although a deterministic system is one of the basic requirements of a hard RTOS.

As per the suggested approach, the context-switching module of the RTOS is implemented in the processor hardware. That does not only reduce context switching but also makes the system more reliable. The hardware implementation of the suggested approach is described in detail in the next chapter.

#### CHAPTER 4 – HARDWARE DESIGN AND IMPLEMENTATION

Hardware implementation for the proposed architecture is divided into two parts. The first part describes the implementation of context register files to save the CPU state in the processor itself and the second part describes the hardware implementation of savecontext (*scxt*) and restore-context (*rcxt*) CPU instructions.

# **4.1 Register File Design**

The Plasma MIPS processor, used for this thesis, implements the "*reg\_bank*" module in the FPGA's block RAM [9]. This design won't work with the suggested approach, as all the context registers must be saved on a register file in one CPU clock cycle, and that cannot be achieved if registers are implemented as RAM locations. To achieve this task, the original Plasma MIPS design is modified by implementing all the "*reg\_bank*" registers in FPGA's logic blocks. This design requires more FPGA logic resources but provides fast access to registers as compared to the original design.

To prove this concept, only 4 register files are implemented in the "*reg\_bank*" module. These register files are indexed from 0 to 3. Each register file can hold up to 12 registers, which is the size of a thread's context for the MIPS architecture. A thread's context includes 9 saved or temporary registers (\$16 - \$23 and \$30), the stack pointer register (\$28), the global pointer register (\$29), and the link register (\$31). As previously shown, in Figure 3.5, new register files have been added in the "*reg\_bank*" module to save the context registers. Their registers are initialized to 0 at reset.

The number of register files can be extended, depending on the available FPGA resources, to accommodate more threads. To access the register files, two context-switch instructions have been implemented in the hardware. The design of these context-switch instructions is described in the next section, and the VHDL source code for the *"reg\_bank"* module is placed in APPENDIX A-1.

#### **4.2 Context-Switching Instruction Design**

The "*mem\_control*" module of the processor fetches 32-bit machine-code instructions from the memory and passes them to the "*control*" module for further processing. The control module generates a 62-bit VLWI instruction code, which includes two additional bits for the "*cnxt\_switch*" signal. As shown in Figure 3.5, the 2bit signal (*cnxt\_switch* 0: 1) is sent out to "*reg\_bank*" module that processes "*scxt*" and "*rcxt*" context-switch instructions, based upon the "*cnxt\_switch*" signal value. Table 4.1 shows the "*cnxt\_switch*" signal's bit map.

| Instruction        | cnxt_switch |       |  |  |

|--------------------|-------------|-------|--|--|

|                    | Bit 1       | Bit 0 |  |  |

| scxt               | 0           | 1     |  |  |

| rcxt               | 1           | 0     |  |  |

| Other instructions | 0           | 0     |  |  |

Table 4. 1: The cnxt\_switch Signal Bit Map

Before executing the "*scxt*" and "*rcxt*" instructions, software needs to save the index of the register file in any temporary register (\$t), and then execute these instructions with the corresponding \$t register as an operand of the instruction. For example, if temporary register \$4 contains the index of the register file in which the

context needs to be saved, then the instruction to save the context would be "*scxt* \$4"; and, similarly, if register \$4 contains the index of the register file from which the context needs to be restored, then the instruction to restore the context would be "*rcxt* \$4".

## 4.3 Context-Switching Instruction Hardware Implementation

As discussed in Chapter 2, three formats of MIPS processor instructions are available. Since we need to store the index of the register file in a temporary register and pass the register as an operand of the instruction, the newly implemented context-switch instructions should be in instruction format Type-R. Table 4.2 shows the bit map designed for the "*scxt*" instruction where register "*rt*" contains the index of the register file in which the current context needs to be saved.

Table 4. 2: Save Context Instruction Bit Map

| Save Context Instruction (scxt rt)                                                                        |        |       |               |       |       |        |  |

|-----------------------------------------------------------------------------------------------------------|--------|-------|---------------|-------|-------|--------|--|

| Bit Position         31 - 26         25 - 21         20 - 16         15 - 11         10 - 6         5 - 0 |        |       |               |       |       |        |  |

| Name                                                                                                      | opcode | rs    | rt            | rd    | shamt | funct  |  |

| <b>Bit Values</b>                                                                                         | 000000 | 00000 | 00001 - 10111 | 00000 | 00000 | 111100 |  |

Similarly, Table 4.3 shows the designed bit map for the "*rcxt*" instruction. Again, register "*rt*" contains the index of the register file from which the next thread's context needs to be restored.

|                                                                                                         | Restore Context Instruction (rcxt rt) |       |               |       |       |        |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------|---------------------------------------|-------|---------------|-------|-------|--------|--|--|--|--|--|--|

| Bit Position         31 - 26         25 - 21         20 - 16         15 - 11         10 - 6         5 - |                                       |       |               |       |       |        |  |  |  |  |  |  |

| Name                                                                                                    | opcode                                | rs    | rt            | rd    | shamt | funct  |  |  |  |  |  |  |

| Bit Values                                                                                              | 000000                                | 00000 | 00001 - 10111 | 00000 | 00000 | 111101 |  |  |  |  |  |  |

Table 4. 3: Restore Context Instruction Bit Map

The software must set the register "*rt*" correctly, by setting the operand value within the range of available register files, before executing these instructions. Since we have implemented four register files to save contexts, if the value in register "*rt*" is set out of range (greater than 3), then these instructions would be executed as a No Operation (NOP) instruction and would not harm or change any thread's context data. This will ensure the overall system's continuity.

### 4.4 Hardware Synthesis and Implementation

The Plasma MIPS VHDL implementation for Xilinx Spartan-3E FPGA board is chosen to implement the suggested approach [9]. The implementation and verification is done using ISE version 10.1 and ModelSim XE III 6.3C, respectively. As discussed, the "*control*" and "*reg\_bank*" modules are modified to implement the suggested MIPS processor architecture. The context-switch register files have been implemented in the "*reg\_bank*" module to the maximum capacity of the available FPGA resources. With four register files, the suggested MIPS architecture has consumed 99% of the slices and 89% of the 4-input LUTs (Look-Up Table) of the FPGA resources. This addition has reduced the maximum speed of the processor from 27.421 MHz to 25.716 MHz. To accommodate the four context-switch register files and control logic along with the

original MIPS processor in the FPGA, the "*Ethernet*" peripheral module of the original Plasma MIPS implementation has been removed from the design, as this peripheral is not a part of the processor design, nor needed for our intended usage. Table 4.4 compares the FPGA resource usage between the original and proposed MIPS architecture, respectively.

|                            | Total |       | lization for<br>rchitecture | Device Utilization for<br>Modified Architecture |             |  |  |

|----------------------------|-------|-------|-----------------------------|-------------------------------------------------|-------------|--|--|

| Device Resource Type       |       | Used  | Utilization                 | Used                                            | Utilization |  |  |

| Number of Slice Flip Flops | 9312  | 783   | 8%                          | 3017                                            | 32%         |  |  |

| Number of 4 input LUTs     | 9312  | 3754  | 40%                         | 8329                                            | 89%         |  |  |

| Number of occupied Slices  | 4656  | 2066  | 44%                         | 4654                                            | 99%         |  |  |

| Minimum Period             |       | 36.4  | 68 ns                       | 38.886 ns                                       |             |  |  |

| Maximum Frequency          |       | 27.42 | 1 MHz                       | 25.716 MHz                                      |             |  |  |

Table 4. 4: FPGA Device Resource Usage for Original Plasma MIPS Architecture

and Modified MIPS Architecture

For simplicity, the system has been implemented as XIP (execute in place), as the processor reads the software instructions directly from the FPGA's block RAM and executes. To place an executable in block RAM, specially designed tools ("*convert\_bin*" and "*toimage*") have been used [9]. The "*convert\_bin*" tool reads the MIPS executable

file and generates a text file containing MIPS hexadecimal instructions in ASCII (American Standard Code for Information Interchange) format. Then, the "*toimage*" tool reads the MIPS 32-bit instructions from the text file, breaks them into four 8-bit segments, and places them in the block RAM source file ("*ram\_image.vhd*") at appropriate locations. This VHDL file is used to synthesize and implement the processor design, using Xilinx ISE tools, with the software executable in the FPGA block RAM.

## 4.5 Summary

To reduce context-switching time, register files have been implemented in the processor hardware to store the CPU state of a thread. Special instructions have been implemented to allow the access of these register files through software. Details of this hardware and instruction implementation have been described in this chapter. Software needed to exploit this newly implemented processor feature is explained in the following chapter.

### CHAPTER 5 – SOFTWARE DESIGN

Software design for this research can be divided into two parts. The first part describes the design and development of a co-operative operating system, which uses the newly implemented CPU instructions for context switching, and three test applications to measure the performance improvement. The second part deals with the modifications in the GNU MIPS tool-chain to support "*scxt*" and "*rcxt*" context-switch instructions. For this thesis, these instructions are added in the GNU-MIPS assembler.

## **5.1 Co-Operative Operating System Design**

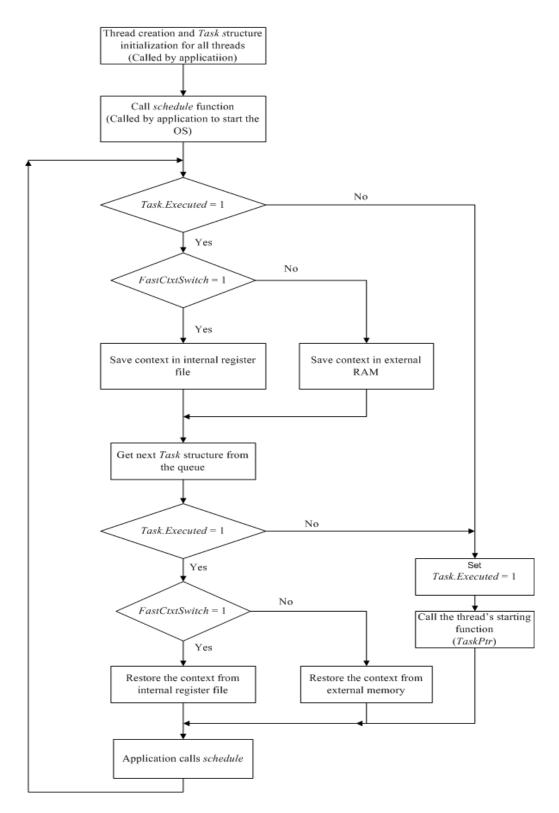

To prove the validity of the suggested approach and measure the performance improvement, a small basic co-operative OS for the modified MIPS processor has been developed. This OS provides interface functions for application development mainly to initialize, create, and schedule different threads. Table 5.1 lists the interface functions.

Since it is a co-operative OS, each thread does its allocated task and releases the thread's control voluntarily by calling the OS interface function "*schedule*". This function does the actual context switching by saving the current thread's context, and then restoring the context of the next thread in the queue. The OS supports context switching using external memory, as well as internal register files.

| Function Name  | Description                                                         |

|----------------|---------------------------------------------------------------------|

| initOS()       | This function initializes the Task structure for each thread in the |

|                | system to the default values.                                       |

|                | This function initializes the Task structure of the thread for the  |

| CreateThread() | thread's requirements. It takes parameters as follows;              |

|                | TaskID - Thread ID                                                  |

|                | funcptr - Pointer to thread's starting function                     |

|                | FastCtxtSwitch - Context switching property setting of the thread   |

| Schedule()     | This function schedules the next thread in the queue                |

**Table 5.1: Operating System Interface Functions**

### 5.1.1 Operating System Design

The current implementation of the OS supports four threads but can be easily extended as needed. These threads are initialized by the application. The application needs to call "*InitOS*" to initialize each thread's "*Task*" structure. Figure 5.1 shows the operating system's "*Task*" structure. The "*FastCtxtSwitch*" member of the "*Task*" structure identifies the context-switching property of a thread. If "*FastCtxtSwitch*" is set to a value greater than 0, then the OS save/restore the context of that thread to/from internal register files, respectively. Otherwise, external memory is used by the context switching for that particular thread. This feature is required for applications with more than four threads. In that case, an application can decide whether a thread needs fast context switching or not. For our experimentation, this feature is used to compare the

performance between the traditional context-switching approach and the suggested approach.

Figure 5. 1: Task Structure

At the time of system initialization, all four threads are initialized with "*FastCtxtSwitch*" to 0. To achieve the context switch using internal register files, an application has to set the "*FastCtxtSwitch*" member of the "*Task*" structure, for that thread, to a value greater than 0. So, it is the application's responsibility to use the context-switching method carefully, based upon the thread's requirements and the number of internal register files available in the processor hardware.

# 5.1.2 Operating System Operation

After initializing the OS by calling "*InitOS*", the application needs to call the "*createTask*" OS function to create different threads. While creating threads, the application needs to pass parameters: a thread identification number, a pointer to the thread's starting function, and the context-switching property of the thread. After creating

all threads, the application needs to call the "*schedule*" OS function to start executing threads.

The "*schedule*" function schedules threads for execution in round-robin fashion. It picks the next thread in the queue and calls the thread's starting function if the thread is going to be executed for the first time. Otherwise, it saves the context of the current thread and restores the context of the next thread in the queue. Again, if the restored thread is going to execute for the first time, then the scheduler calls the thread's starting function. Otherwise, it restores the context of the next thread from the internal register files or from external memory depending on the "*FastCtxtSwitch*" value of the thread's task structure.

After completing the assigned task, a thread must call "*schedule*" to release the CPU control voluntarily. Figure 5.2 shows a detailed flow chart for our co-operative OS. The source code is listed in APPENDIX B-1 to APPENDIX B-5.

Figure 5. 2: Co-Operative Operating System's Flow Chart

## **5.2 Assembler Modifications**

The GNU tool chain for the MIPS processor is used to compile the co-operative OS and the test applications. To automate the build process, the newly implemented context- switch instructions are added to the GNU MIPS assembler.

These instructions are added to GNU "*binutils*" version 2.19 [9]. The "*binutils*-2.19/gas" (GNU assembler) folder contains the source code for the MIPS assembler. The file "*mips-opc.c*" in "*binutils-2.19/opcode*" contains all the instructions supported by the MIPS processor. The new instructions have been added in the file "*mips-opc.c*".

The GNU MIPS assembler is implemented in the 'C' programming language. Figure 5.3 describes the basic structure of MIPS instructions implementation in the assembler.

const struct mips\_opcode

{

name, args, match, mask, pinfo, pinfo2, membership

}

Figure 5. 3: MIPS Instruction Structure Format in GNU Assembler

The "*mips-opc.c*" file defines an array of "*mips\_opcode*" structures and each array element contains one MIPS machine OP-code. Table 5.2 describes the "*mips-opcode*" structure elements and Table 5.3 describes the "*scxt*" and "*rcxt*" instruction implementation in the array of "*mips\_opcode*" structures.

| Structure Member | Description                                                 |

|------------------|-------------------------------------------------------------|

| name             | Instruction string e.g. "add"                               |

| args             | A string describing the arguments to the instruction.       |

| match            | Match hex value of the instruction                          |

| mask             | Bit mask of the instruction                                 |

| pinfo            | A collection of additional bits describing the instruction. |

| pinfo2           | Additional bits describing the instruction.                 |

| membership       | MIPS version information                                    |

Table 5. 2: "mips\_opcode" Structure Data Members

Table 5. 3: 'scxt' and 'rcxt' Instruction Assembler Values

| Structure Member | Instruction scxt values | Instruction rext values |  |  |  |  |

|------------------|-------------------------|-------------------------|--|--|--|--|

| name             | "scxt"                  | "rext"                  |  |  |  |  |

| args             | "'t''                   | "'t''                   |  |  |  |  |

| match            | 0x000003c               | 0x000003d               |  |  |  |  |

| mask             | Oxfffffff               | Oxffffffff              |  |  |  |  |

| pinfo            | RD_t                    | RD_t                    |  |  |  |  |

| pinfo2           | 0                       | 0                       |  |  |  |  |

| membership       | 1                       | 1                       |  |  |  |  |

A message is also added to the assembler source code that gets printed on the screen when using the modified assembler.

#### **5.3 Software System Implementation**

The software components developed in this thesis have been implemented in 'C' and the MIPS assembly programming language. The source code for the co-operative OS and test applications are compiled using the GNU MIPS tool-chain under cygwin environment on a Windows-based computer.

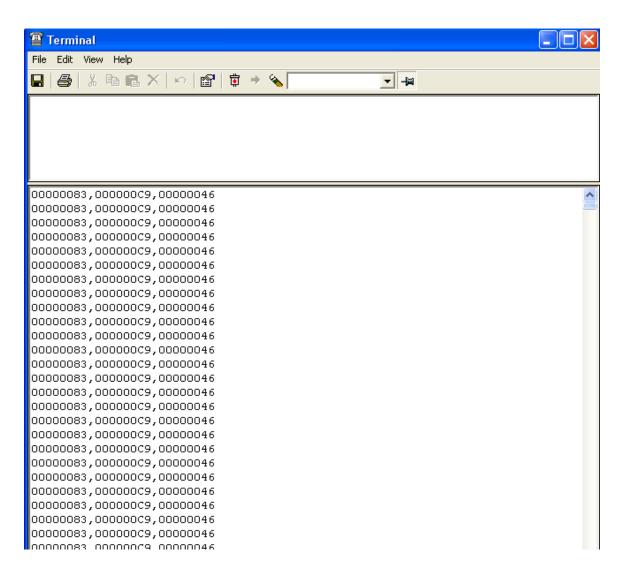

To debug the software, debug messages are added. The debug messages are sent to the Universal Asynchronous Receiver Transmitter (UART) serial port. The terminal program on the computer connected to the Xilinx FPGA board through serial cable receives and displays these messages on a computer screen. The same debug serial port is used to send the test application's results for analysis.

# 5.4 Summary

A multi-threaded OS is required to test the suggested approach of context switching. A small co-operative OS that supports four threads has been implemented. The context switching between these threads can be achieved using internal register files as well as external memory based on the context-switching property setting in the "*Task*" structure of that thread. The GNU MIPS assembler also has been modified to support the newly implemented context-switching instructions.

To measure the performance improvement with the suggested approach, test applications are required. These applications execute on top of the implemented OS and exploit the context-switching features supported by the OS and the processor. The next chapter describes these test applications and analyzes the test results.

### CHAPTER 6 - EXPERIMENTAL RESULTS AND ANALYSIS

This chapter describes the verification process of the hardware implementation of the proposed approach. It also explains the software used for testing the complete system. The performance of the suggested approach is also evaluated and the results are compared with traditional context-switching methods.

## **6.1 Hardware Verification**

To verify the correct operation of the context-switch instructions, software using the "*scxt*" and "*rcxt*" instructions was developed in the MIPS assembly language and executed on the modified processor in a simulation environment. This verification software first initializes all nine temporary registers of the thread's context with values from 1 to 9. Register \$4 is then set to 2, which is the index of the register file in which the context will be stored, and then the "*scxt*" instruction is executed. It is expected that the instruction should move all the contents of the context registers to context register file 2 (*ctxt\_reg2*) in 2 clock cycles. Simulation for the "*scxt* \$4" instruction verified this expectation as shown in Figure 6.1

To verify the "*rcxt*" instruction, the values 2 through 10 are stored in the 9 temporary registers of the processor. Then, the "*rcxt*" instruction is executed with register \$4 value set to 2, indicating the context needs to be restored from the context-register file 2. The contents of register file 2 are moved into the CPU context registers and the previously saved context is restored in 2 clock cycles. Figure 6.2 shows the simulation waveform for the "*rcxt* \$4" instruction. As expected, the values of the correct context registers replace the previous context.

| Context saved in cont          | ext registe  | er file 2 (ctxt_reg2XX)                                 |

|--------------------------------|--------------|---------------------------------------------------------|

| Register file index (rt        | _index = ·   | 4) \$4 is having register file index 🚽                  |

| cnxt_switch signal for         | r 'scxt' ins | struction                                               |

| Context register file i        | ndex in re   | $2gister \ 4(reg04 = 2)$                                |

| Initial values in conte        | xt registe   | rs                                                      |

| Messages                       | :            |                                                         |

| u1_cpu/u4_reg_bank/clk         | 0            |                                                         |

| u1_cpu/u4_reg_bank/reset_in    | 0            |                                                         |

| u1_cpu/u4_reg_bank/rt_index    | 00           | <u>) 10 11 12 13 14 15 16 17 00 1E 04</u> 10 10 00 02 0 |

| u1_cpu/u4_reg_bank/cnxt_switch | 0            |                                                         |

| 'u1_cpu/u4_reg_bank/reg04      | 00000002     | 00000470 () () () () () () () () () () () () ()         |

| 'u1_cpu/u4_reg_bank/reg16      | 00000001     |                                                         |

| 'u1_cpu/u4_reg_bank/reg17      | 00000002     | 00000000 0000002                                        |

| 'u1_cpu/u4_reg_bank/reg18      | 00000003     | 00000000 )0000003                                       |

| 'u1_cpu/u4_reg_bank/reg19      | 00000004     | 00000000 )0000004                                       |

| 'u1_cpu/u4_reg_bank/reg20      | 00000005     | 00000000 000000000000000000000000000000                 |

| 'u1_cpu/u4_reg_bank/reg21      | 00000006     | 00000000 000000000000000000000000000000                 |

| 'u1_cpu/u4_reg_bank/reg22      | 00000007     | 00000000 000000000000000000000000000000                 |

| 'u1_cpu/u4_reg_bank/reg23      | 80000008     | 00000000 000000000000000000000000000000                 |

| 'u1_cpu/u4_reg_bank/reg30      | 00000009     | 00000000 0000009                                        |

| 'u1_cpu/u4_reg_bank/reg31      | 000000A4     | 000)000000A4                                            |

| u1_cpu/u4_reg_bank/reg28       | 00008254     | 00008254                                                |

| u1_cpu/u4_reg_bank/reg29       | 00000440     | 00000440                                                |

| u1_cpu/u4_reg_bank/ctxt_reg21  | 00000000     | 00000000                                                |

| u1_cpu/u4_reg_bank/ctxt_reg22  | 00000000     | 00000000                                                |

| u1_cpu/u4_reg_bank/ctxt_reg23  | 00000000     | 00000000                                                |

| u1_cpu/u4_reg_bank/ctxt_reg24  | 00000000     | 00000000 000000000000000000000000000000                 |

| u1_cpu/u4_reg_bank/ctxt_reg25  | 00000000     | 00000000                                                |

| u1_cpu/u4_reg_bank/ctxt_reg26  | 00000000     |                                                         |

| u1_cpu/u4_reg_bank/ctxt_reg27  | 00000000     | 00000000                                                |

| u1_cpu/u4_reg_bank/ctxt_reg28  | 00000000     |                                                         |

| u1_cpu/u4_reg_bank/ctxt_reg29  | 00000000     | 0000000 0000254                                         |

| u1_cpu/u4_reg_bank/ctxt_reg210 | 00000000     | 00000000 000000000000000000000000000000                 |

| u1_cpu/u4_reg_bank/ctxt_reg211 | 00000000     | 00000000                                                |

| u1_cpu/u4_reg_bank/ctxt_reg212 | 00000000     | ОООООООО СООООООО СООООООООООООООООООО                  |

Figure 6. 1: Waveform for 'scxt \$4' Instruction

Context restored from context register file 2 ( $ctxt\_reg2XX$ ) Register index ( $rt\_index = 4$ ) that is holding register file index " $cnxt\_switch$ " signal for 'rcxt' instruction Context register file index in register 4(reg04 = 2)

Initial values in context registers

|                                  |          |                  |            |           |        | -        |         |       |             |               |                      |

|----------------------------------|----------|------------------|------------|-----------|--------|----------|---------|-------|-------------|---------------|----------------------|

| /u1_cpu/u4_reg_bank/clk          | 0        | ллл              |            |           |        | ЛЛ       | ЛГ      |       |             |               |                      |

| /u1_cpu/u4_reg_bank/reset_in     | 0        |                  |            |           |        |          |         |       |             |               |                      |

| ı/u1_cpu/u4_reg_bank/rt_index    | 17       | <u>)00 (10 )</u> | 11 (12 (13 | (14 (15 ) | 16 (17 | )00 (1E  | )04     | 00    | <b>)</b> 04 | 00            | 02 )0 <mark>0</mark> |

| /u1_cpu/u4_reg_bank/cnxt_switch  | 0        | 0                |            |           |        |          |         |       | 12          | )0            |                      |

| ı/u1_cpu/u4_reg_bank/reg04       | 00000002 | 00000002         |            |           |        |          |         | 00000 | 0002        | نه            |                      |

| /u1_cpu/u4_reg_bank/reg16        | 00000002 | 00000001         | 00000002   |           |        |          |         |       |             | ) <u>0000</u> | 00001                |

| ı/u1_cpu/u4_reg_bank/reg17       | 00000003 | 00000002         | 2000000    | )3        |        |          |         |       |             | )0000         | 00002                |

| ı/u1_cpu/u4_reg_bank/reg18       | 00000004 | 00000003         | )000       | 00004     |        |          |         |       |             | ) <u>0000</u> | 00003                |

| ı/u1_cpu/u4_reg_bank/reg19       | 00000005 | 00000004         |            | 0000000   | 5      |          |         |       |             | )0000         | 00004                |

| ı/u1_cpu/u4_reg_bank/reg20       | 00000006 | 00000005         |            | )000(     | 00006  |          |         |       |             | <u>)000(</u>  | 00005                |

| ı/u1_cpu/u4_reg_bank/reg21       | 00000007 | 00000006         |            |           | 000000 | )7       |         |       |             | )0000         | 00006                |

| ı/u1_cpu/u4_reg_bank/reg22       | 8000000  | 00000007         |            |           | )000   | 00008    |         |       |             | ) <u>0000</u> | 00007                |

| ı/u1_cpu/u4_reg_bank/reg23       | 8000000  | 00000008         |            |           |        | )0000000 | 09      |       |             | )0000         | 00008                |

| ı/u1_cpu/u4_reg_bank/reg30       | 0000009  | 0000009          |            |           |        |          | )000000 | DÓA   |             | )0000         | 00009                |

| ı/u1_cpu/u4_reg_bank/reg31       | 000000B8 | 0 (000000B       | 8          |           |        |          |         | )0    | 000         | ) <u>0000</u> | 000B0                |

| ı/u1_cpu/u4_reg_bank/reg28       | 00008254 | 00008254         |            |           |        |          |         |       |             |               |                      |

| ı/u1_cpu/u4_reg_bank/reg29       | 00000440 | 00000440         |            |           |        |          |         |       |             |               |                      |

| ı/u1_cpu/u4_reg_bank/ctxt_reg21  | 00000001 | 00000001         |            |           |        |          |         |       |             |               |                      |

| /u1_cpu/u4_reg_bank/ctxt_reg22   | 00000002 | 00000002         |            |           |        |          |         |       |             |               |                      |

| ı/u1_cpu/u4_reg_bank/ctxt_reg23  | 00000003 | 00000003         |            |           |        |          |         |       |             |               |                      |

| ı/u1_cpu/u4_reg_bank/ctxt_reg24  | 00000004 | 00000004         |            |           |        |          |         |       |             |               |                      |

| ı/u1_cpu/u4_reg_bank/ctxt_reg25  | 00000005 | 00000005         |            |           |        |          |         |       |             |               |                      |

| /u1_cpu/u4_reg_bank/ctxt_reg26   | 00000006 | 0000006          |            |           |        |          |         |       |             |               |                      |

| ı/u1_cpu/u4_reg_bank/ctxt_reg27  | 00000007 | 00000007         |            |           |        |          |         |       |             |               |                      |

| ı/u1_cpu/u4_reg_bank/ctxt_reg28  | 00000008 | 00000008         |            |           |        |          |         |       |             |               |                      |

| ı/u1_cpu/u4_reg_bank/ctxt_reg29  | 00008254 | 00008254         |            |           |        |          |         |       |             |               |                      |

| /u1_cpu/u4_reg_bank/ctxt_reg210  | 00000440 | 00000440         |            |           |        |          |         |       |             |               |                      |

| /u1_cpu/u4_reg_bank/ctxt_reg211  | 00000009 | 0000009          |            |           |        |          |         |       |             |               |                      |

| //u1_cpu/u4_reg_bank/ctxt_reg212 | 000000В0 | 000000B0         |            |           |        |          |         |       |             |               |                      |

|                                  |          |                  |            |           |        |          |         |       |             |               |                      |

|                                  |          |                  |            |           |        |          |         |       |             |               |                      |

Figure 6. 2: Waveform for 'rcxt \$4' Instruction

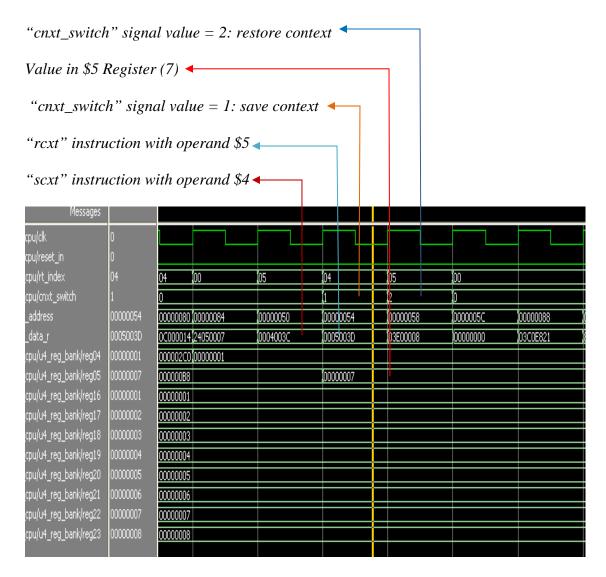

As discussed in Chapter 4, if the context-switch instructions executed with the operand register have an out-of-range value, then these instructions are executed as NOP instructions and do not change context state. A test case is designed to verify this as folows: register \$4 is initialized with the value 1 and register \$5 with 7 before executing the "*scxt*" instruction. These instructions are then executed in sequence. Since the value 7 is loaded into register \$5, the operand of the "rcxt" instruction, is out of range. No change in context registers is expected for this test case. Figure 6.3 verifies this functionality. The "*rcxt*" instruction (0x0005003D) is executed to restore the context from register file index 7 as specified in register \$5. After the execution of this instruction, there is no change in the context registers.

# Figure 6. 3: Waveform to Verify an Out-of-Range Instruction Operand

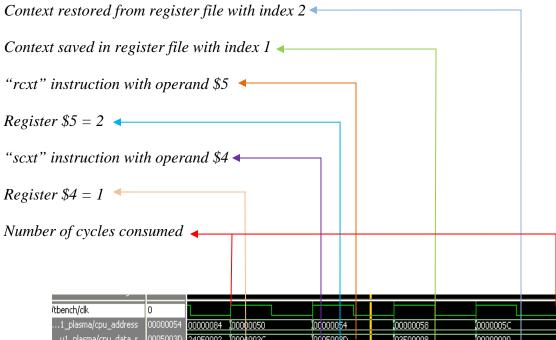

To determine the number of clock cycles consumed by a complete context switch, a test program is implemented and executed on the modified MIPS processor soft-core in the simulation environment. This program initializes the CPU context registers with known non-zero values and then executes "*scxt*" and "*rcxt*" instructions in sequence. The "*scxt*" instruction saves the CPU context in register file 1 and the "*rcxt*" instruction restores the context from register file 2. As shown in the simulation output in Figure 6.4, the "*scxt*" and "*rcxt*" instructions consume 2 clock cycles each to store and restore the context in the register file 1 (ctxt\_reg 1) and from register file 2 (cntxt\_reg 2), respectively. So the complete context switch takes place in 4 clock cycles. This value is independent of the number of registers used by the context.

Figure 6.4 also shows that the scratch registers (reg16 to reg23) are initialized with values 1 to 8, respectively, and context-register file 1 is initialized with 0s. The figure also shows that register 4 is initialized with the value of 1, the index of the context-register file. After executing the "*scxt*" instruction (0x0004003C) the context is saved in register file 1, as expected. The "*rcxt*" instruction (0x0005003D) is executed next showing that the register-file index from which context needs to be restored is saved in register 5. Since register 5 is initialized with the value 2, the context needs to be restored from the register file 2 that was initialized with 0 at reset. The figure shows that the context registers are loaded with 0s after "*rcxt*" execution.

| rebenchycik           | 0        |          |             | L     |        | 4    |          | L        |    |

|-----------------------|----------|----------|-------------|-------|--------|------|----------|----------|----|

| 1_plasma/cpu_address  | 00000054 | 00000084 | <u>1000</u> | 00050 | 00000  | 54   | 00000058 | 0000005C | 10 |

| u1_plasma/cpu_data_r  | 0005003D | 24050002 | 000         | 4003C | 000500 | 3D ' | 03E00008 | 00000000 | 3  |

| /u4_reg_bank/rt_index | 04       | 00       | 05          |       | 04     |      | 05       | 00       |    |

| reg_bank/cnxt_switch  | 1        | 0        |             |       | 1      |      | 2        | ()       |    |

| pu/u4_reg_bank/reg04  | 00000001 | 00000001 |             | İ     |        |      |          |          |    |

| pu/u4_reg_bank/reg05  | 00000002 | 000000B8 |             |       | 000000 | 02   |          |          |    |

| pu/u4_reg_bank/reg16  | 00000001 | 00000001 |             |       |        |      |          | 00000000 |    |

| pu/u4_reg_bank/reg17  | 00000002 | 00000002 |             |       |        |      |          | 00000000 |    |

| pu/u4_reg_bank/reg18  | 00000003 | 00000003 |             |       |        |      |          | 00000000 |    |

| pu/u4_reg_bank/reg19  | 00000004 | 00000004 |             |       |        |      |          | 00000000 |    |

| pu/u4_reg_bank/reg20  | 00000005 | 00000005 |             |       |        |      |          | 00000000 |    |

| pu/u4_reg_bank/reg21  | 00000006 | 00000006 |             |       |        |      |          | 00000000 |    |

| pu/u4_reg_bank/reg22  | 00000007 | 00000007 |             |       |        |      |          | 00000000 |    |

| pu/u4_reg_bank/reg23  | 80000008 | 00000008 |             |       |        |      |          | 00000000 |    |

| reg_bank/ctxt_reg11   | 00000000 | 00000000 |             |       |        |      | 00000001 |          |    |

| reg_bank/ctxt_reg12   | 00000000 | 00000000 |             |       |        |      | 00000002 |          |    |

| reg_bank/ctxt_reg13   | 00000000 | 00000000 |             |       |        |      | 00000003 |          |    |

| reg_bank/ctxt_reg14   | 00000000 | 00000000 |             |       |        |      | 00000004 |          |    |

| reg_bank/ctxt_reg15   | 00000000 | 00000000 |             |       |        |      | 00000005 |          |    |

| reg_bank/ctxt_reg16   | 00000000 | 00000000 |             |       |        |      | 00000006 |          |    |

| reg_bank/ctxt_reg17   | 00000000 | 00000000 |             |       |        |      | 00000007 |          |    |

| reg_bank/ctxt_reg18   | 00000000 | 00000000 |             |       |        |      | 00000008 |          |    |

|                       |          |          |             |       |        |      |          |          |    |

**Figure 6. 4: Context Switch Instructions Waveform**

# **6.3 Test Applications**

As discussed earlier, it is difficult to measure the actual cost of context switching due to variables like processor speed, processor architecture, RTOS design, and etc. So, the actual cost of context switching may vary among different systems. The overall impact on system performance, due to context-switching overhead, also depends on the type of application. If an application requires frequent context switching, then the system will spend more time in managing and switching the threads and that will degrade overall performance.

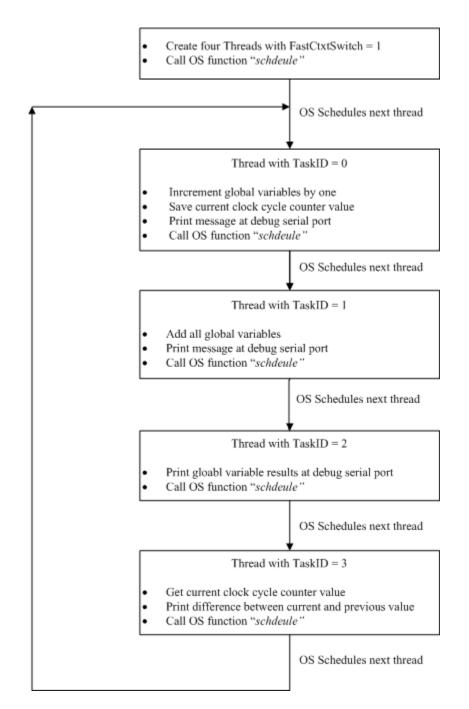

For this thesis, three test applications have been implemented, which require frequent context switching, and each application tests and measures the different aspects of the suggested approach. These test applications use the interface functions provided by the co-operative OS to access the proposed hardware features. Each application implements four threads and each thread is running in a never-ending loop. Each thread executes a specific task by manipulating global variables in a loop and calls the operating system's "*schedule*" function to release control to the next thread. These applications are designed to test the functionality and measure the performance improvement of the proposed approach. The following sections describe the test applications and their results in detail.

## <u>6.3.1 Test Application – 1</u>

This application tests the successful operation of the proposed approach by switching four threads using internal register files. This test is used to ensure that data between threads is not corrupted and thread's context switching is correct. The flow chart of this application is shown in Figure 6.5.