## Western University Scholarship@Western

Digitized Theses

**Digitized Special Collections**

1992

# Experimental Study Of Cmos Structures: Design For Reliability In Hostile Environments

Kenneth Chum

Follow this and additional works at: https://ir.lib.uwo.ca/digitizedtheses

#### Recommended Citation

Chum, Kenneth, "Experimental Study Of Cmos Structures: Design For Reliability In Hostile Environments" (1992). Digitized Theses. 2104.

https://ir.lib.uwo.ca/digitizedtheses/2104

This Dissertation is brought to you for free and open access by the Digitized Special Collections at Scholarship@Western. It has been accepted for inclusion in Digitized Theses by an authorized administrator of Scholarship@Western. For more information, please contact tadam@uwo.ca, wlswadmin@uwo.ca.

## **Experimental Study of CMOS Structures: Design for Reliability in Hostile Environments**

by

#### Kenneth Chum

Department of Electrical Engineering

Submitted in partial fulfilment of the requirements for the degree of Doctor of Philosophy

Faculty of Graduate Studies

The University of Western Ontario

London, Ontario

February 1992

© Kenneth Chum 1992

Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada K1A 0N4

> The author has granted an irrevocable nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

> The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission.

L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-71998-2

#### **ABSTRACT**

Complementary Metal Oxide Silicon (CMOS) technology has been the fastest growing fabrication process for the Very Large Scale Integrated (VLSI) circuits in the last few years, and long term predictions confirm its future importance. The minimum CMOS feature size is presently about one micron and it is certain that feature dimensions will reach the submicron range in mid nineties.

Smaller dimensions yield advantages, namely greater speed, higher device complexity and performance, and disadvantages such as greater susceptibility to electrical damage. During the past few years, the reliability of CMOS integrated circuits has received much attention, matched by publications on the subject. Higher reliability hardened integrated circuits have been developed as a response to demands for simplified shielding and demands for more reliable systems operating in hostile environments. The key step in developing hardened integrated circuits is the study of the mechanisms that make them fail. By understanding the failure conditions one can design more reliable components, select more suitable materials, and improve in-process control and screening. Also, it allows to develop test patterns, or accelerated test strategies for the evaluation of the integrated circuits susceptibility to damage.

In this study, a series of measurements were performed on a variety of custom fabricated CMOS Charge-Coupled Devices (CCDs) and dedicated modular test structures to investigate the latent mode of failure due to Electrostatic Discharge (ESD). Test devices were stressed using the current injection method and measurements of the quiescent current were used to detect the failure thresholds. The fault sites were further isolated and the failure mechanisms studied by measuring the electrical characteristics

before and after thermal and optical interaction. The measurements of oxide trapped charge was performed using capacitance-voltage profiles. A model was proposed to explain the observed phenomena, based on charge injection and trapping in the gate oxide. The experimental methods developed for locating, measuring and analysis of the failure sites have been found sufficiently robust to be generally useful.

#### **ACKNOWLEDGEMENTS**

The author would like to express his sincere appreciation to his chief advisor, Professor W. D. Greason, for his support and guidance throughout the project. The author thanks Professor Z. Kucerovsky for his valuable suggestions and discussions. Appreciation is also extended to fellow graduate students Adrain Li, Paul Smeulders, Frederick Tang and Anthony Wu for their technical advice and assistance.

This research was supported by grants from the National Science and Engineering Research Council of Canada and the EOS/ESD Association Inc. The custom integrated circuits were fabricated by Northern Telecom Electronics, Ottawa, in conjunction with the Canadian Microelectronics Corporation.

This project would not be possible without the continuous support from my parents to achieve higher education. Finally, the author is included to Katherine Lo for her indispensable support and encouragement over the years, sharing his frustration and happiness from this project.

### TABLE OF CONTENTS

|                                                    | Page  |

|----------------------------------------------------|-------|

|                                                    |       |

| CERTIFICATE OF EXAMINATION                         | ii    |

| ABSTRACT                                           | iii   |

| ACKNOWLEDGEMENTS                                   | v     |

| TABLE OF CONTENTS                                  | VI    |

| LIST OF TABLES                                     | X     |

| LIST OF FIGURES                                    | xi    |

| LIST OF APPENDICES                                 | xviii |

| ABBREVIATIONS AND SYMBOLS                          | xix   |

| NOMENCLATURE                                       | XX    |

| CHAPTER 1 - THE PHYSICS AND RELIABILITY OF         |       |

| CHARGE-COUPLED DEVICES (CCDs)                      | 1     |

| CITAROL COOL DED DE VICE y (CCDs)                  | •     |

| 1.1 Introduction                                   | 1     |

| 1.2 Review of Metal-Oxide-Semiconductor Capacitor  |       |

| 1.2.1 The Equilibrium MOS-C                        | 2 5   |

| 1.2.2 The Deep-Depletion MOS-C                     | 12    |

| 1.2.3 Non-Ideal MOS Structures                     | 15    |

| 1.2.3.1 Silicon-Silicon Dioxide Interface Traps    | 17    |

| 1.2.3.1.1 Fixed Charges                            | 18    |

| 1.2.3.1.2 Interface Traps                          | 18    |

| 1.2.3.2 Bulk Oxide Traps                           | 20    |

| 1.3 Fundamentals of Charge-Coupled Devices (CCDs)  | 23    |

| 1.3.1 Input Configuration of CCDs                  | 24    |

| 1.3.2 Multiphase CCD Structures                    |       |

| 1.3.3 Surface and Bulk Channel CCDs.               |       |

| 1.3.4 Output Structure of CCDs                     |       |

|                                                    |       |

| 1.4 Summary                                        |       |

| 1.5 Project Objectives                             | .,, / |

| CHAPTER 2 - FAILURE MECHANISMS IN                  |       |

| METAL-OXIDE-SEMICONDUCTOR (MOS)                    | 38    |

|                                                    |       |

| 2.1 Introduction                                   | 38    |

| 2.2 Failure Mechanisms                             | 39    |

| 2.2.1 Electrical Stress Related Failure Mechanisms | 39    |

| 2.2.1.1 Types of Electrical Stress Related Damage  | 42    |

| 2.2.1.1.1 Latent Failures                          | 43    |

| 2.2.1.2 ESD Protection Circuits                    | 49    |

| 2.2.2 Intrinsic Failure Mechanisms                 | 50    |

| 2.2.2.1 Charge Effects                             |       |

| 2.2.3 Extrinsic Failure Mechanisms                 | 51    |

| 2.3 Failure Analysis Techniques                    | 51    |

| 2.3.1 Methodology for Failure Analysis             |       |

## **TABLE OF CONTENTS (Cont.)**

|                                                   | Page |

|---------------------------------------------------|------|

|                                                   | 53   |

| 2.3.2 Electrostatic Discharge Simulation          | 52   |

| 2.3.3 Quiescent Current Measurements              | 56   |

| 2.3.4 Capacitance-Voltage Measurements            | 57   |

| 2.4 Summary                                       | 58   |

| CHAPTER 3 - CIRCUIT DESIGN                        | 59   |

| 3.1 Charge-Coupled Devices                        | 59   |

| 3.2 Protection Circuits                           | 75   |

| 3.2.1 Input Protection Circuits                   | 75   |

| 3.2.2 Output Protection Circuits                  | 84   |

| 3.3 Summary                                       | 87   |

| CHAPTER 4 - DEVICE ELECTRICAL CHARACTERISTICS     | 88   |

| 4.1 MOSFETs                                       | 89   |

| 4.2 Charge-Coupled Devices                        | 94   |

| 4.3 Protection Circuits                           | 103  |

| 4.3.1 Input Protection Circuits                   | 104  |

| 4.3.2 Output Protection Circuits                  | 111  |

| 4.4 Summary                                       | 113  |

| CHAPTER 5 - DEVICE FAILURE ANALYSIS               | 114  |

| 5.1 Introduction                                  | 114  |

| 5.2 Test Devices                                  | 116  |

| 5.2.1 CMOS B Series                               | 116  |

| 5.2.2 CMOS High-Speed Series                      | 117  |

| 5.2.3 Custom Fabricated CMOS Devices              | 119  |

| 5.2.3.1 Charge-Coupled Devices                    | 119  |

| 5.2.3.2 Protection Circuits                       | 122  |

| 5.3 Failure Criterion                             | 124  |

| 5.4 Experimental Setup and Procedure              | 124  |

| 5.4.1 Electrical Stress Test                      | 125  |

| 5.4.1.1 New Devices                               | 126  |

| 5.4.1.1.1 Threshold Test                          | 126  |

| 5.4.1.1.2 Step-Stress Test                        | 127  |

| 5.4.1.1.3 Constant Amplitude Multiple Stress Test | 127  |

| 5.4.1.2 Pre-Stressed Devices                      | 127  |

| 5.4.1.2.1 Threshold Test                          | 127  |

| 5.4.1.2.2 Step-Stress Test                        | 127  |

| 5.4.2 Thermal Shock Test                          | 127  |

|                                                   | 128  |

| 5.4.3 Ultraviolet Light Test                      | 120  |

## **TABLE OF CONTENTS (Cont.)**

|                                                  | Page       |

|--------------------------------------------------|------------|

| S.S. D Iv                                        | 1.70       |

| 5.5 Results                                      | 129        |

| 5.5.1 Commercial Devices                         | 129        |

| 5.5.1.1 Electrical Stress Test                   | 129        |

| 5.5.1.1.1 New Devices                            | 130        |

| 5.5.1.1.1.1 Threshold Test                       | 130        |

| 5.5.1.1.1.2 Step-Stress Test                     | 130        |

| 5.5.1.1.3 Constant Amplitude Multiple Stress     | 131<br>131 |

|                                                  |            |

| 5.5.1.1.2.1 Threshold Test                       | 131        |

| 5.5.1.1.2.2 Step-Stress Test                     | 131<br>132 |

| 5.5.1.2 Thermal Shock Test                       |            |

| 5.5.1.3 Ultraviolet Light Test                   | 132        |

| 5.5.1.4 Thermal Annealing Test                   | 132        |

| 5.5.2 UWO Test Chips                             | 133        |

| 5.5.2.1.1 Protection Circuits                    | 133        |

| 5.5.2.1.2 MOS-C/CCDs                             |            |

| 5.5.2.2 Thermal Shock Test                       |            |

| 5.5.2.2.1 Protection Circuits                    |            |

| 5.5.2.2.2 MOS-C/CCDs                             |            |

| 5.5.2.3 Ultraviolet Light/Thermal Annealing Test |            |

| 5.5.2.3.1 Protection Circuits                    | 143        |

| 5.5.2.3.2 MOS-C/CCDs                             |            |

| 5.6 Charge Injection Model                       |            |

| 3.0 Charge injection Model                       | 17/        |

| CHAPTER 6 - CONCLUSIONS AND RECOMMENDATIONS      | 148        |

| 6.1 Summary and Conclusions                      | 148        |

| APPENDIX A - EFFECT OF CHARGE ON MOS STRUCTURES  | 154        |

| A.1 Ideal System                                 | 154        |

| A.1.1 Uniform Charge Distribution                |            |

| A.1.1.1 Threshold Voltage Calculation            |            |

| A.1.2 Linear Charge Distribution                 |            |

| A.1.3 Exponential Charge Distribution            |            |

| A.2 Non-Ideal System                             |            |

| A.2 Non-lucal System                             | 102        |

| APPENDIX B - C-V ANALYSIS TECHNIQUES             | 167        |

| R 1 C-V Analysis                                 | 167        |

| B.1.1 Low-Frequency C-V Measurements             | 168        |

| B.1.1.1 Ramp Method                              | 169        |

| R 1 1 2 Feedback Method                          | 171        |

## **TABLE OF CONTENTS (Cont.)**

|                                                                                                                                                   | Page              |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| B.1.2 High Frequency C-V Measurement B.1.3 Simultaneous High/Low Frequency Measurement B.1.4 Interface Trap and Oxide Trapped Charge Calculations | 174<br>174<br>175 |

| B.2 C-V Analysis Program  B.2.1 Listing of the Program                                                                                            | 178<br>179        |

| APPENDIX C - CMOS PROCESSING TECHNOLOGY                                                                                                           | 190               |

| REFERENCES                                                                                                                                        | 200               |

| VITA                                                                                                                                              | 206               |

#### LIST OF TABLES

| Table | Description                                              | Pige |

|-------|----------------------------------------------------------|------|

| 1.1   | Advantages of Two and Four Phase CCDs                    | 30   |

| 1.2   | Characteristics of Buried and Surface Channel Structures | 34   |

| 2.1   | Triboelectric Series                                     | 41   |

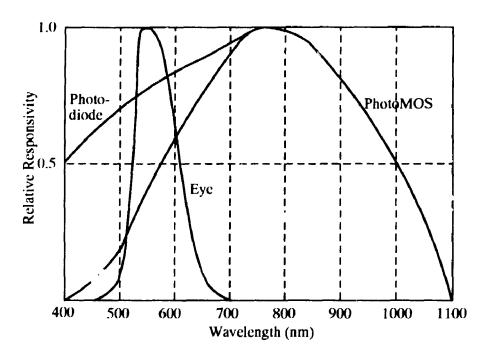

| 3.1   | Comparison of PhotoMOS and Photodiode Elements           | 66   |

| 4.1   | Electrical Characteristics of MOSFETs                    | 94   |

| 4.2   | Switching Characteristics of Input Pads                  | 109  |

| 4.3   | Switching Characteristics of Output Pad                  | 113  |

| 5.1   | ESD Performance of Test Devices                          | 130  |

| C.1   | CIF Layer Names and Colours                              | 195  |

| C.2   | CIF: Minimum Dimensions                                  | 197  |

| C.3   | CIF: Minimum Spacing                                     | 197  |

| C.4   | CIF: Enclosures                                          | 198  |

| C.5   | CIF: Minimum Separations                                 | 198  |

| C.6   | CIF: Overlaps                                            | 199  |

| C.7   | CIF: Pad Rules                                           | 199  |

## LIST OF FIGURES

| Figure | Description                                                                           | Page |

|--------|---------------------------------------------------------------------------------------|------|

| 1.1    | Metal-Oxide-Semiconductor Capacitor                                                   | 2    |

| 1.2    | Individual Energy Band Diagram for the Different Components of the MOS Structure      | 4    |

| 1.3    | Energy Band Diagram for an Ideal MOS Structure in Equilibrium                         | 5    |

| 1.4    | P-Type Substrate MOS Capacitor                                                        | 6    |

| 1.5    | Capacitance-Gate Voltage Curves for a p-Type MOS-C                                    | 9    |

| 1.6    | Energy-Band and Charge-Distribution Diagram for a p-Type MOS-C                        | 10   |

| 1.7    | Space-Charge Region for a p-Type MOS-C in Deep Depletion Mode                         | 13   |

| 1.8    | Energy-Band and Charge-Distribution Diagram for a p-Type MOS-C in Deep Depletion Mode | 14   |

| 1.9    | Charges in Si-SiO <sub>2</sub> Interface System                                       | 16   |

| 1.10   | Physical Model of Interface Traps                                                     | 19   |

| 1.11   | Electrical Model of Interface Traps                                                   | 19   |

| 1.12   | Charge Trapping by Interface Traps                                                    | 20   |

| 1.13   | Hot-Carrier Injection                                                                 | 22   |

| 1.14   | Basic Structure of a MOS-C                                                            | 23   |

| 1.15   | Operating Principle of a 3-Phase CCD                                                  | 25   |

| 1.16   | Operating Principle of a 4-Phase CCD with Alternative Clocking                        | 26   |

| 1.17   | Operating Principle of a 4-Phase CCD                                                  | 27   |

| 1.18   | Basic Structure of a 2-Phase CCD                                                      | 28   |

| 1.19   | Operating Principle of a 2-Phase CCD                                                  | 29   |

| Figure | Description 1                                                         | Page |

|--------|-----------------------------------------------------------------------|------|

| 1.20   | Surface Channel CCD                                                   | 31   |

| 1.21   | Bulk Channel CCD                                                      | 33   |

| 1.22   | Output Structure of CCDs                                              | 35   |

| 2.1    | Static Induction                                                      | 42   |

| 2.2    | Basic Concept of a Protection Network                                 | 50   |

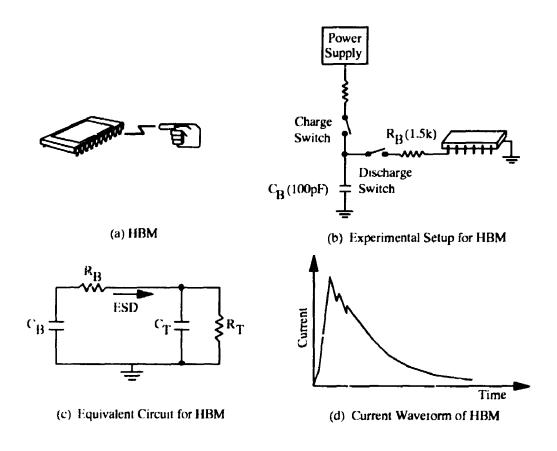

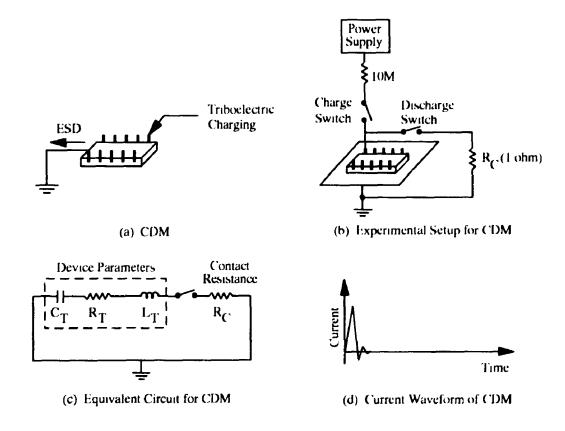

| 2.3    | Human Body Model (HBM)                                                | 53   |

| 2.4    | Charged Device Model (CDM)                                            | 54   |

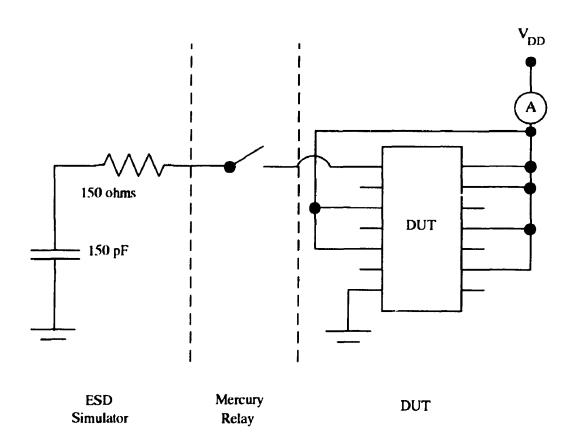

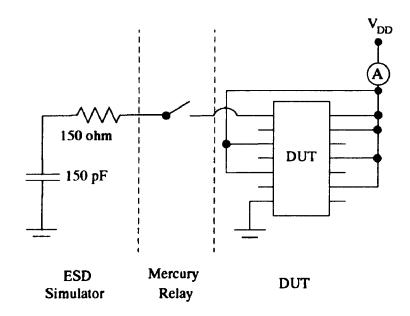

| 2.5    | Test Circuit for Measuring the Electrical Characteristics of a Device | 55   |

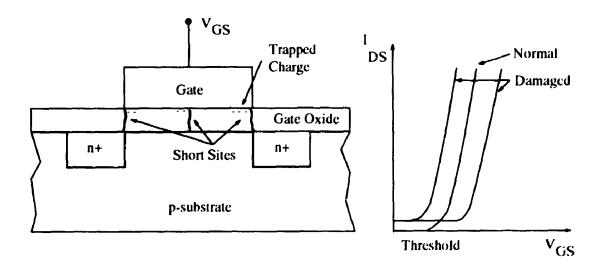

| 2.6    | Typical Defects in MOS Structures                                     | 56   |

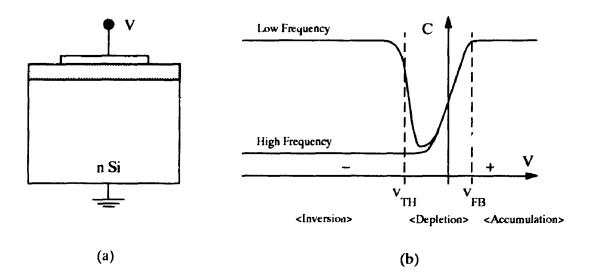

| 2.7    | Typical C-V Characteristics of a n-type Material                      | 57   |

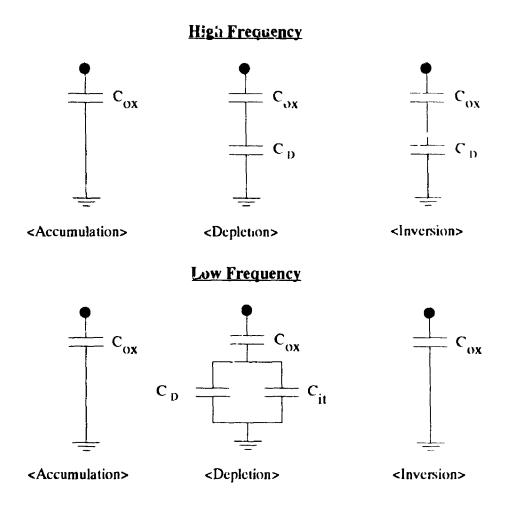

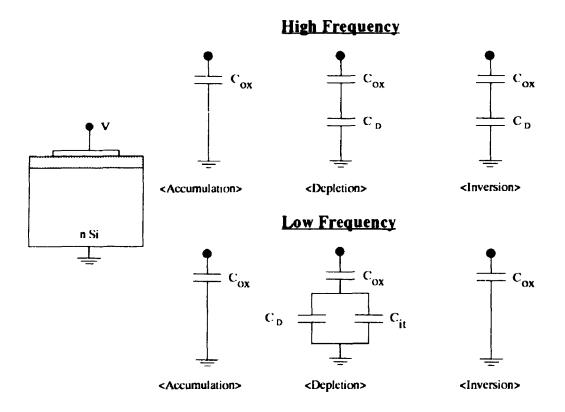

| 2.8    | Equivalent Circuits of a MOS Capacitor                                | 58   |

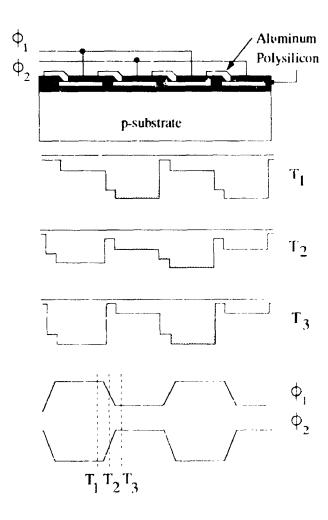

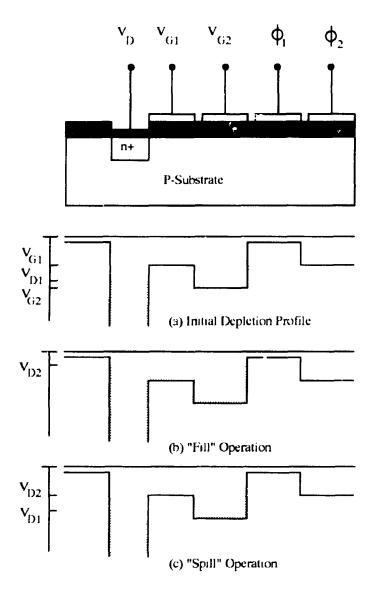

| 3.1    | A Shift Register with Overlapping Gate Structure                      | 60   |

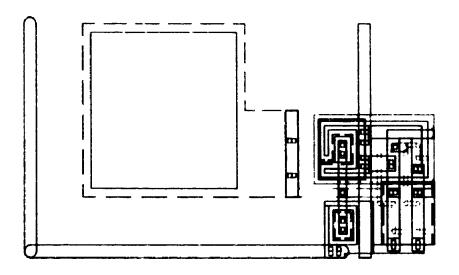

| 3.2    | Layout of the Shift Register                                          | 61   |

| 3.3    | Input Configuration of CCD                                            | 63   |

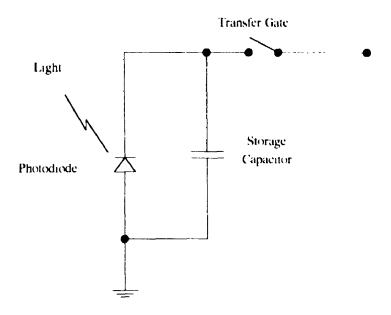

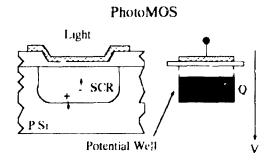

| 3.4    | Equivalent Circuit of a Photo Sensing Region                          | 64   |

| 3.5    | Photodetection Using Silicon                                          | 64   |

| 3.6    | Typical Spectral Response for Photoelements                           | 65   |

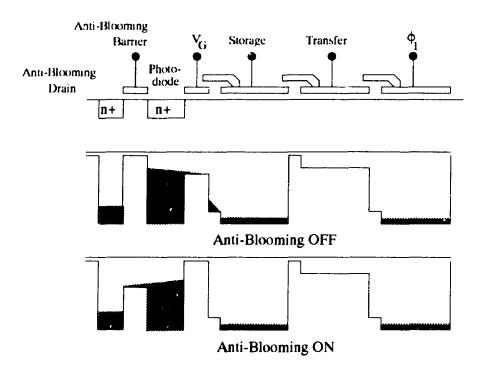

| 3.7    | Photodiode Circuit with Anti-Blooming Control                         | 67   |

| 3.8    | Layout of the Photodiode with Anti-Blooming Structure                 | 68   |

| 3.9    | Output Structure of CCD                                               | 69   |

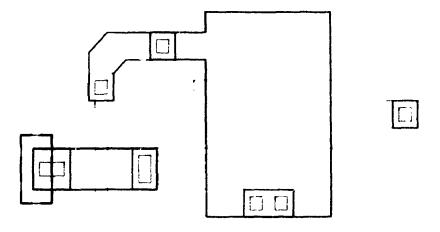

| 3.10   | Layout of the Output Structure                                        | 70   |

| Figure | Description I                                                      | Page |

|--------|--------------------------------------------------------------------|------|

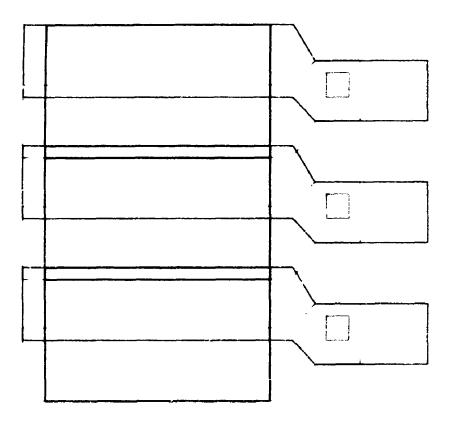

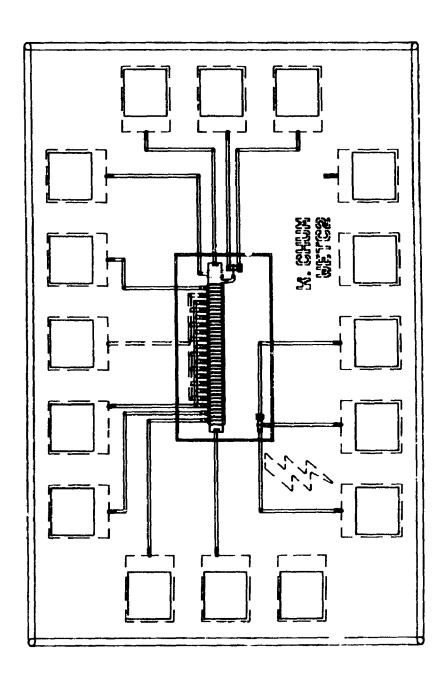

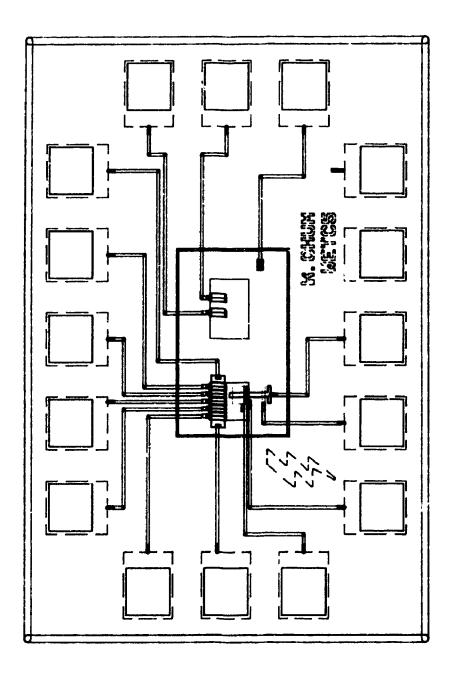

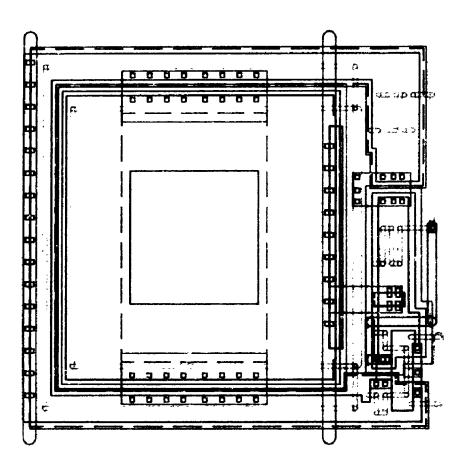

| 3.11   | Layout of a 16-stage, 2-Phase Surface Channel CCD with Input Diode | 72   |

| 3.12   | Layout of a 16-stage, 2-Phase Surface Channel CCD with Photodiode  | 73   |

| 3.13   | Layout of Individual Elements Used in the Surface Channel CCD      | 74   |

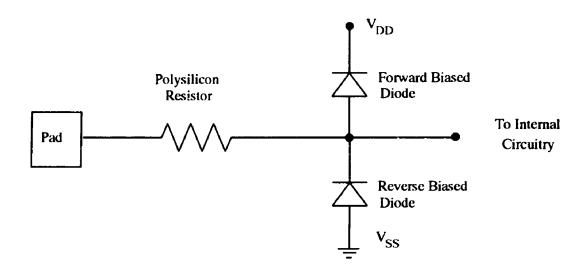

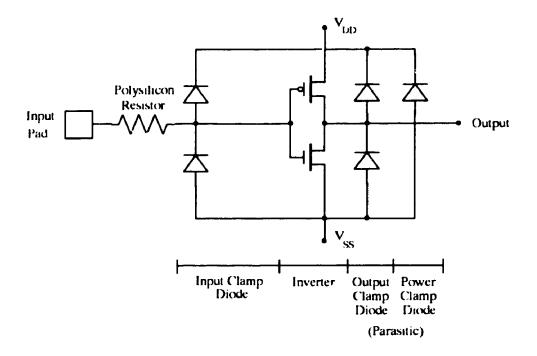

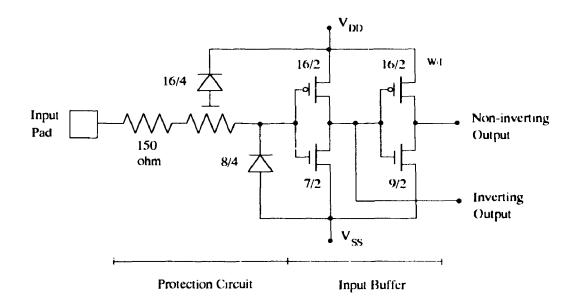

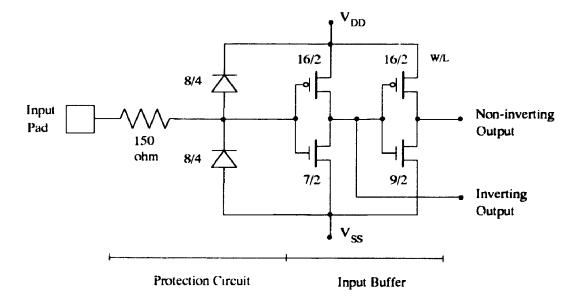

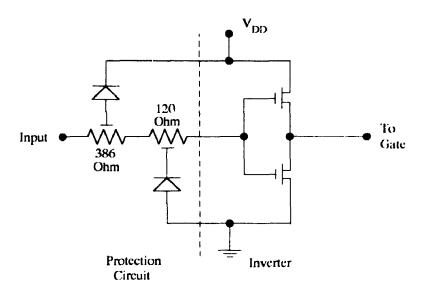

| 3.14   | Schematic of the Input Protection Circuit                          | 76   |

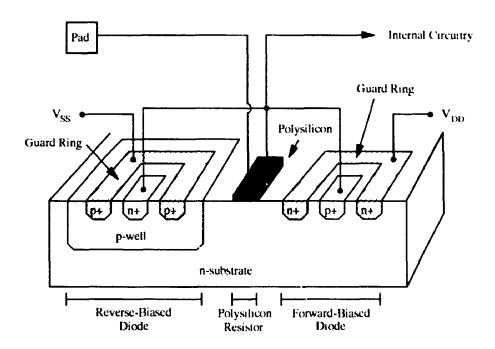

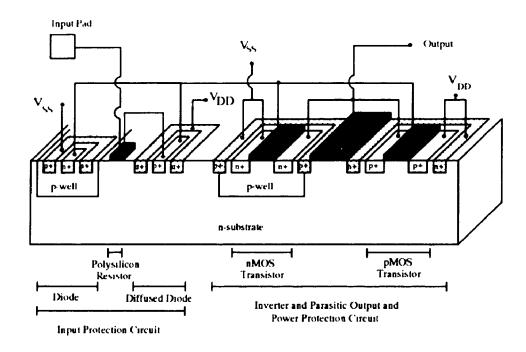

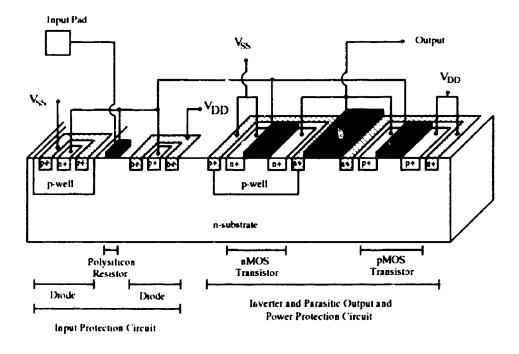

| 3.15   | Cross-Sectional View of the Input Protection Circuit               | 77   |

| 3.16   | Schematic of the Diffused Diode Protection Circuit                 | 78   |

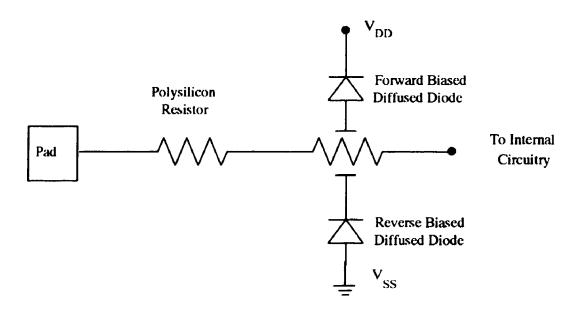

| 3.17   | Cross-Sectional view of the Diffused Diode Protection Circuit      | 78   |

| 3.18   | Schematic of the Diffused Diode Input Pad                          | 79   |

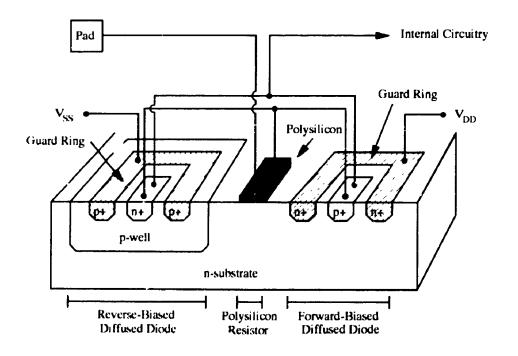

| 3.19   | Cross-Sectional View of the Diffused Diode Input Pad               | 80   |

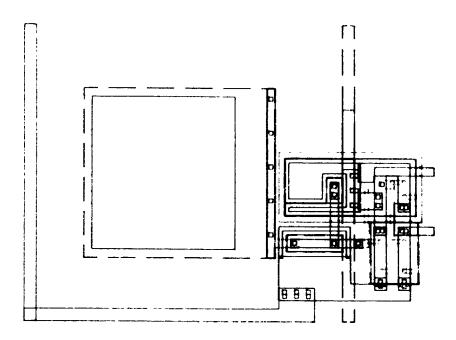

| 3.20   | Layout of the Diffused Diode Input Pad                             | 81   |

| 3.21   | Schematic of the Diode Input Pad                                   | 82   |

| 3.22   | Cross-Sectional View of the Diode Input Pad                        | 82   |

| 3.23   | Layout of the Diode Input Pad                                      | 83   |

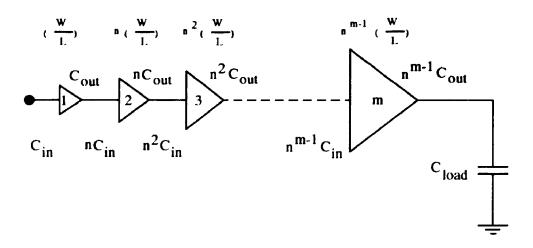

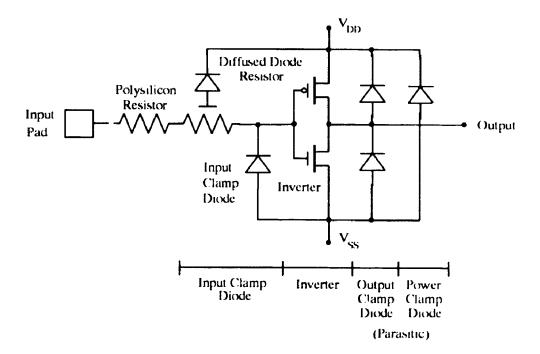

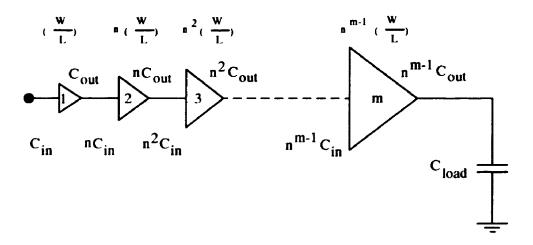

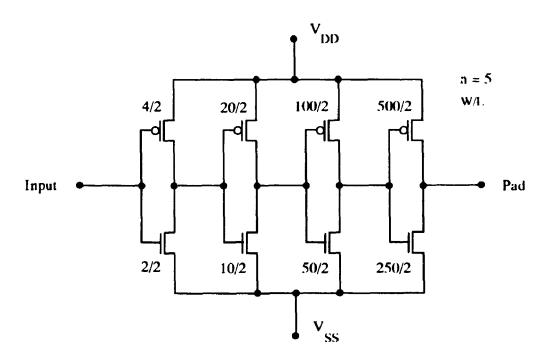

| 3.24   | A Cascaded Output Buffer Circuit                                   | 84   |

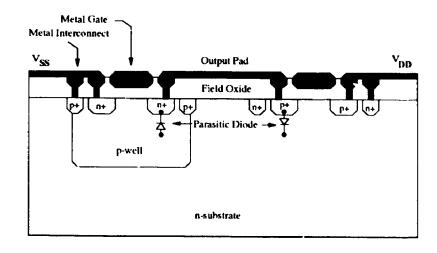

| 3.25   | Parasitic Diodes in Output Pad                                     | 85   |

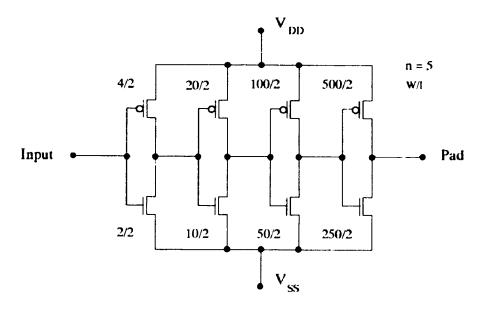

| 3.26   | Circuit Diagram for the Output Pad                                 | 85   |

| 3.27   | Layout of the Output Pad                                           | 86   |

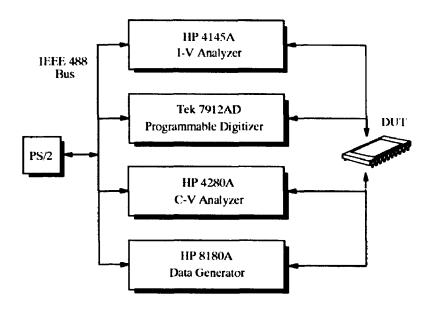

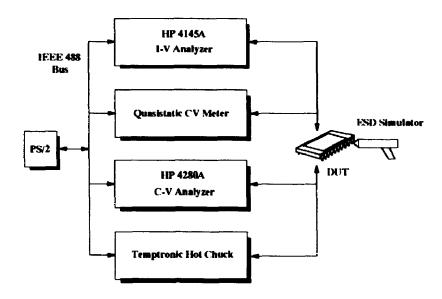

| 4.1    | Block Diagram of the Experimental Setup                            | 89   |

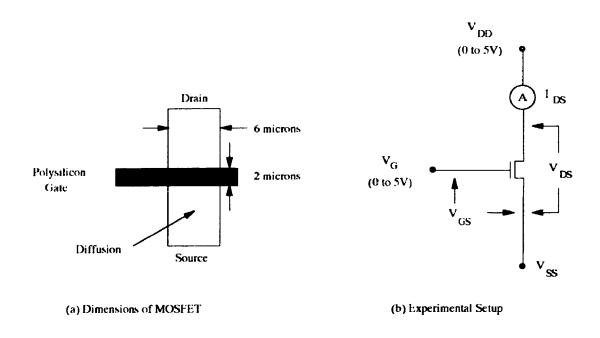

| 4.2    | MOSFET Test Circuit                                                | 90   |

| Figure | Description                                                                           | Page |

|--------|---------------------------------------------------------------------------------------|------|

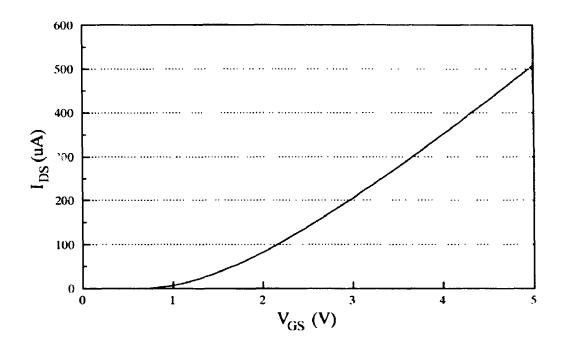

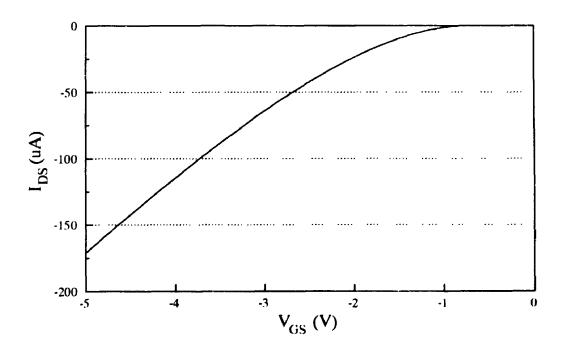

| 4.3    | Typical Drain Current Versus Gate-Source Voltage of the nMOSFET                       |      |

| 4.4    | Typical Drain Current versus Gate-Source Voltage of the pMOSFET                       | 91   |

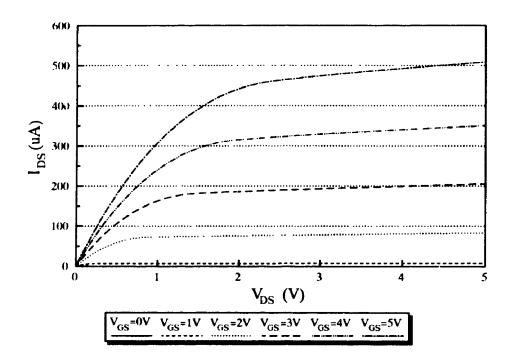

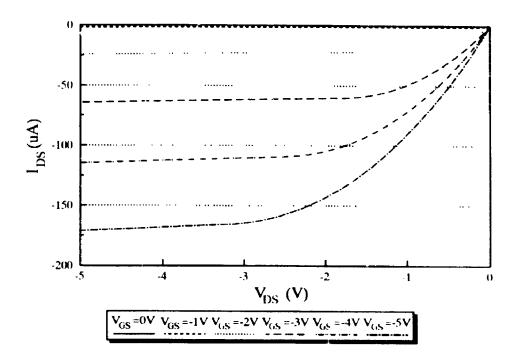

| 4.5    | Typical V-I Characteristics of the nMOSFET                                            | 92   |

| 4.6    | Typical V-I Characteristics of the pMOSFET                                            | 92   |

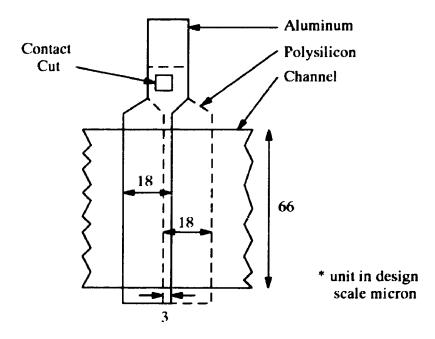

| 4.7    | Layout of CCD Shift Register Cell                                                     | 94   |

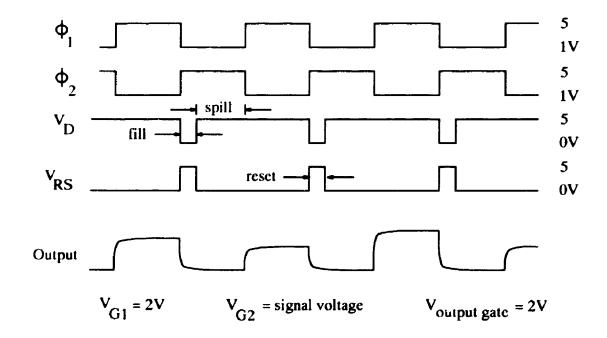

| 4.8    | Operating Input and Output Voltage Waveforms                                          | 96   |

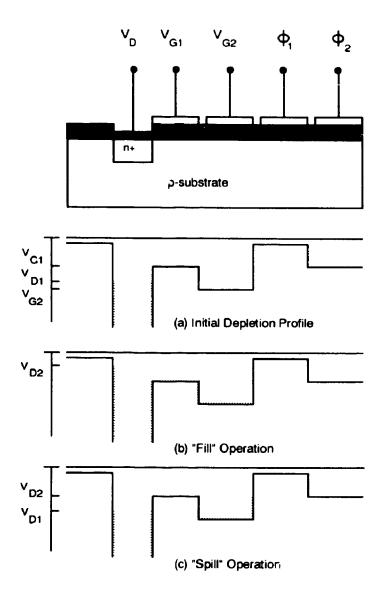

| 4.9    | Input Structure of CCDs Used in the Experiments                                       | 97   |

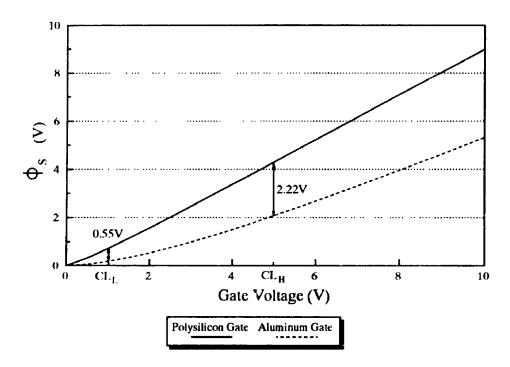

| 4.10   | Surface Potential versus Gate Voltage for $N_A = 5.0 \times 10^{15}$ cm <sup>-3</sup> | 100  |

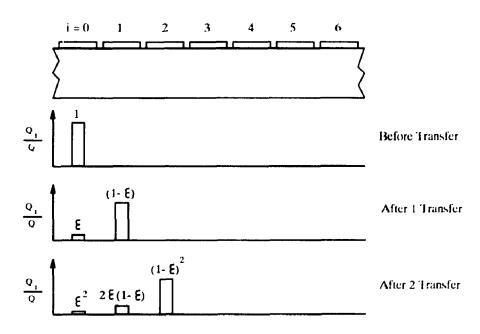

| 4.11   | Measurement of Charge Transfer Inefficiency                                           | 101  |

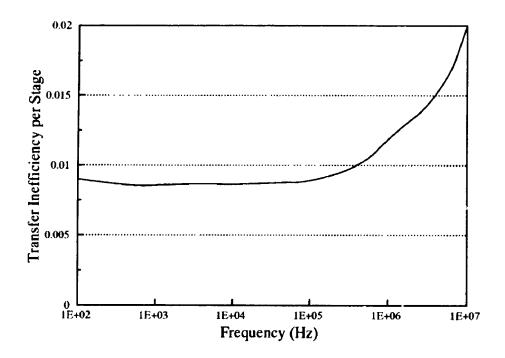

| 4.12   | Typical Charge Transfer Inefficiency versus Clock Frequency                           | 102  |

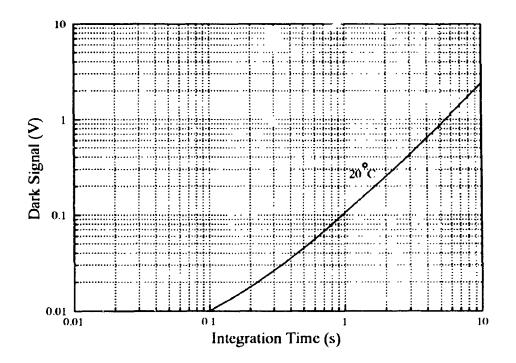

| 4.13   | Typical Dark Charge Buildup versus Integration Time                                   | 103  |

| 4.14   | Typical I-V Characteristics of the Custom Fabricated pn Diode                         | 104  |

| 4.15   | Typical I-V Characteristics of the Custom Fabricated pn<br>Diffused Diode             | 105  |

| 4.16   | Typical I-V Characteristics of the Custom Fabricated np Diode                         | 106  |

| 4.17   | Typical I-V Characteristics of the Custom Fabricated np Diffused Diode                | 106  |

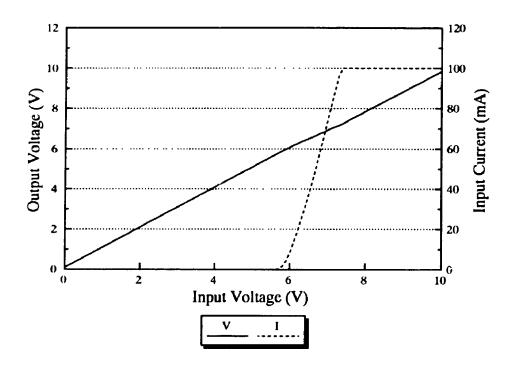

| 4.18   | Circuit Diagram of the Input Pad #1                                                   | 107  |

| 4.19   | Typical I-V Characteristics of Input Pad #1                                           | 108  |

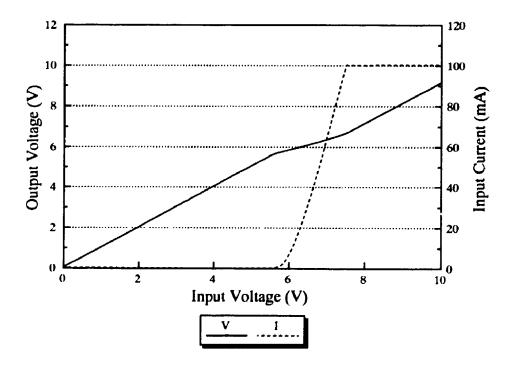

| 4.20   | Circuit Diagram of the Input Pad #2                                                   | 108  |

| Figure | Description                                                                     | Page |

|--------|---------------------------------------------------------------------------------|------|

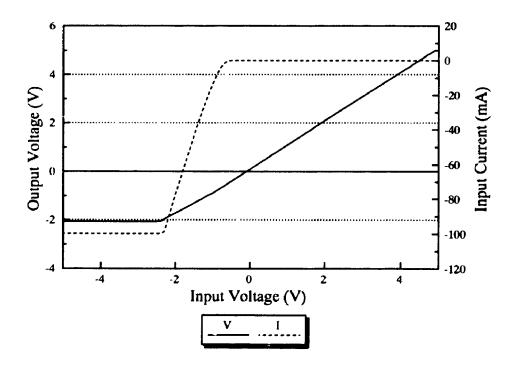

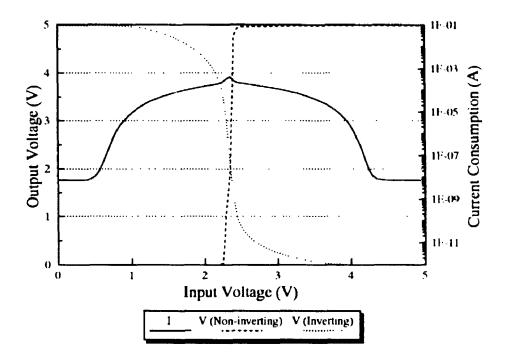

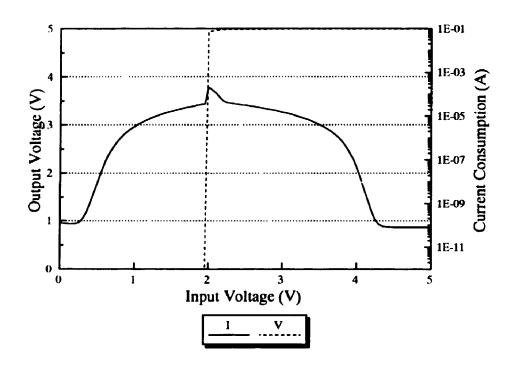

| 4.21   | Typical I-V Characteristics of Input Pad #2                                     | 109  |

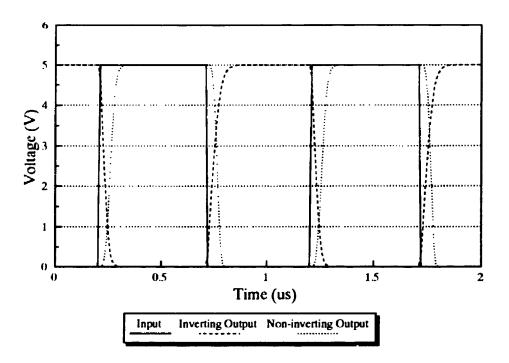

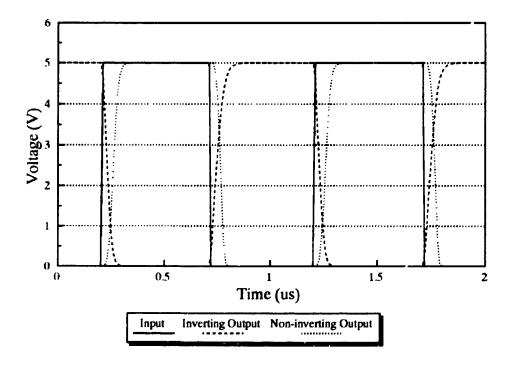

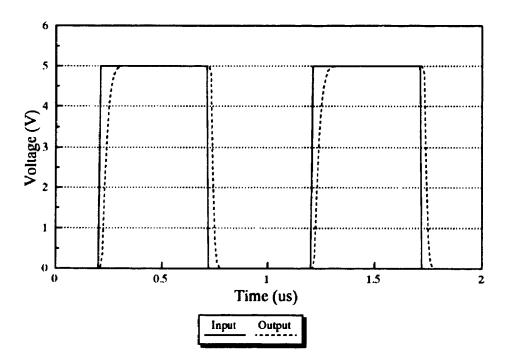

| 4.22   | Typical Dynamic Response of Input Pad #1                                        | 110  |

| 4.23   | Typical Dynamic Response of Input Pad #2                                        | 110  |

| 4.24   | Schematic of Output Pad                                                         | 111  |

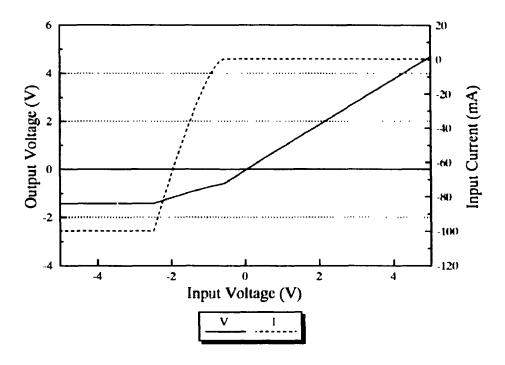

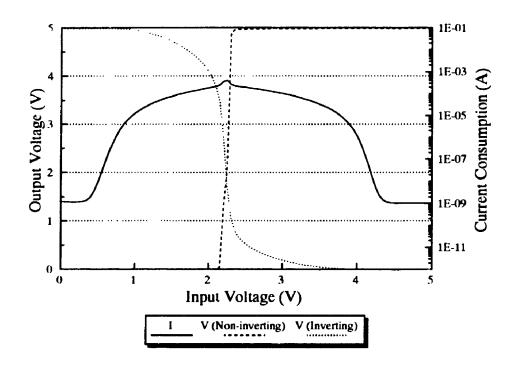

| 4.25   | Typical I-V Characteristics of Output Pad                                       | 112  |

| 4.26   | Typical Frequency Response of Output Pad                                        | 112  |

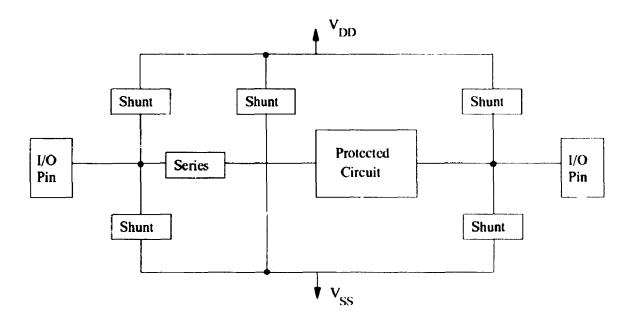

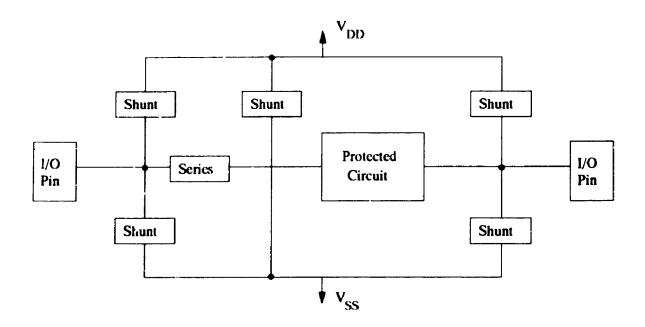

| 5.1    | Typical Protection Structure of an Integrated Circuit                           | 115  |

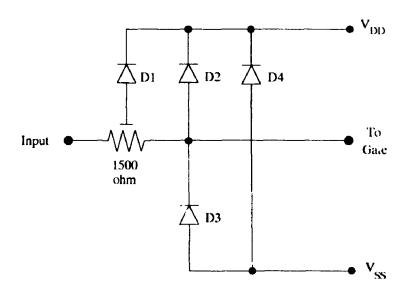

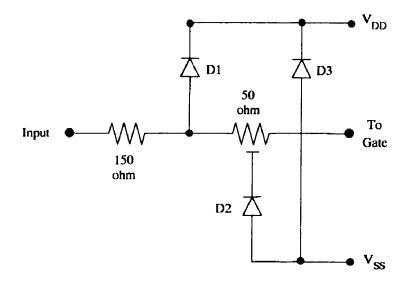

| 5.2    | Input Protection Circuit of 14069UB                                             | 117  |

| 5.3    | Input Protection Circuit of 74HCU04                                             | 118  |

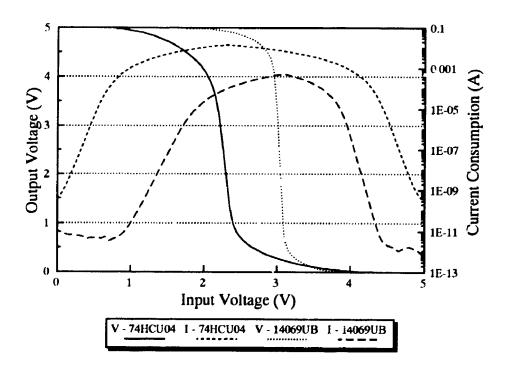

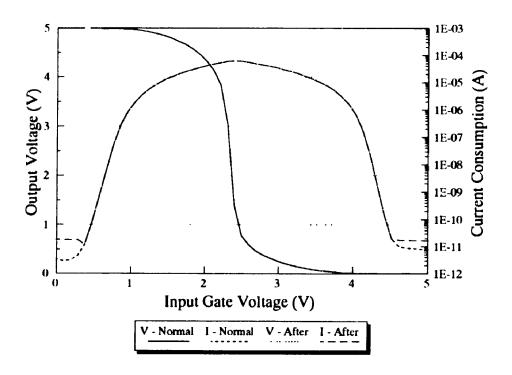

| 5.4    | Typical Electrical Characteristics of Several Commercial Devices                | 118  |

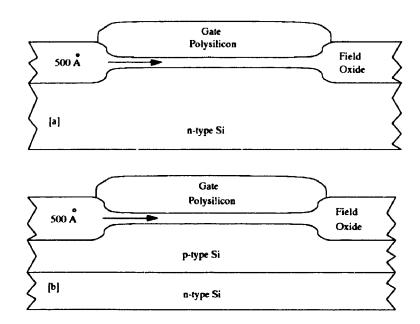

| 5.5    | E-mode (a) n-Type and (b) p-Type Substrate MOS-C                                | 120  |

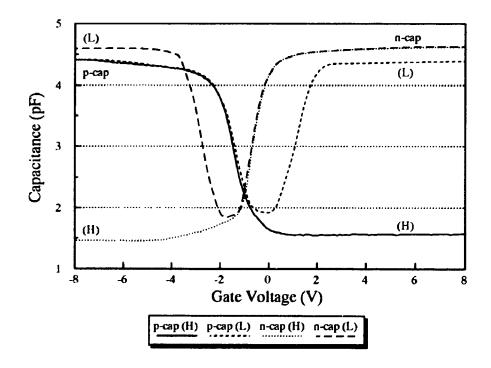

| 5.6    | Typical C-V Characteristics of a 120x120μm <sup>2</sup> MOS-C                   | 120  |

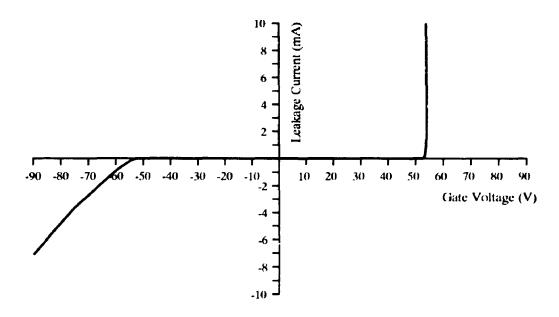

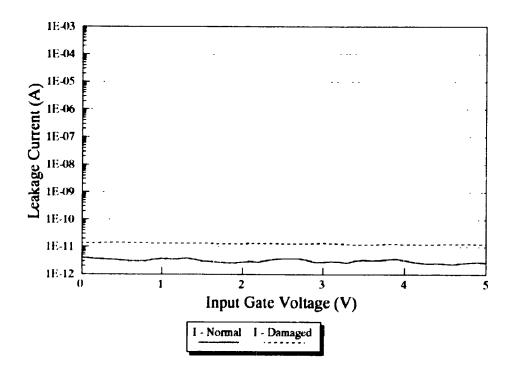

| 5.7    | Typical Leakage Current for n-Type Si MOS-C                                     | 121  |

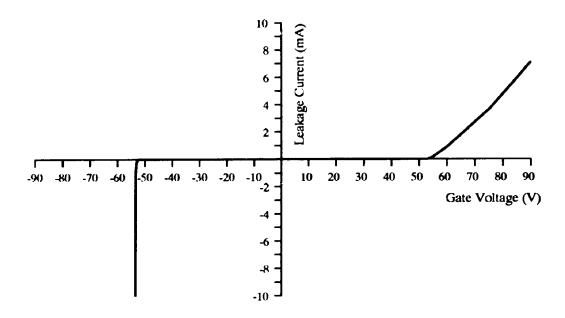

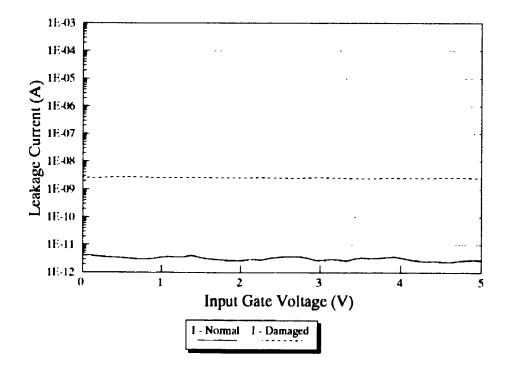

| 5.8    | Typical Leakage Current for p-Type Si MOS-C                                     | 122  |

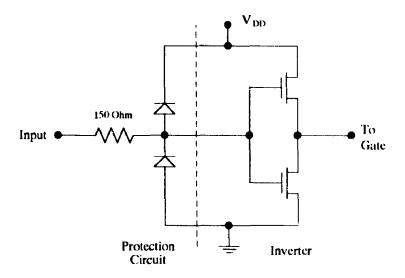

| 5.9    | Equivalent Circuit of Custom Protection Circuit #1                              | 123  |

| 5.10   | Equivalent Circuit of Custom Protection Circuit #2                              | 123  |

| 5.11   | Block Diagram for the Experimental Setup                                        | 125  |

| 5.12   | Test Circuit for Measuring the Electrical Characteristics of a Device           | 126  |

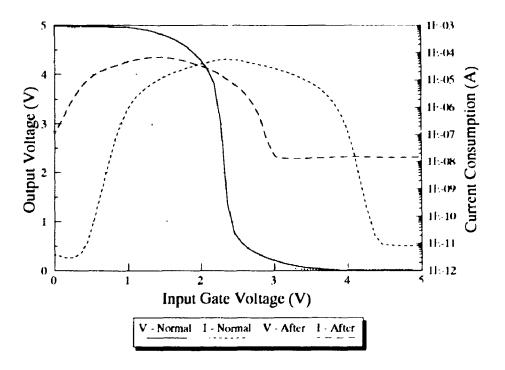

| 5.13   | Typical I-V Characteristics of a Custom Device Before and After a Low Level ESD | 134  |

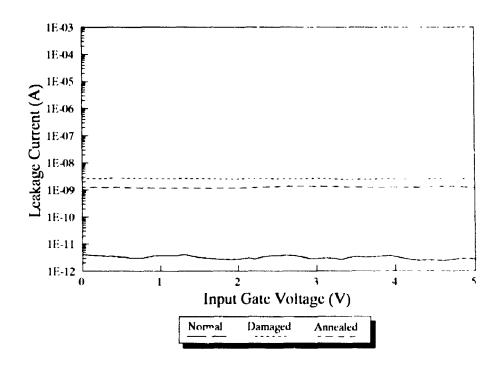

| 5.14   | Comparison of Leakage Current in Protection Diode Before and After ESD          | 134  |

| Figure      | Description                                                                            | Page |

|-------------|----------------------------------------------------------------------------------------|------|

| 5.15        | Typical I-V Characteristics of a Protection Circuit Before and After High Level ESD    | 135  |

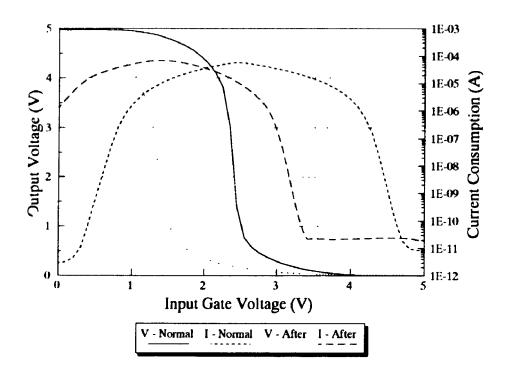

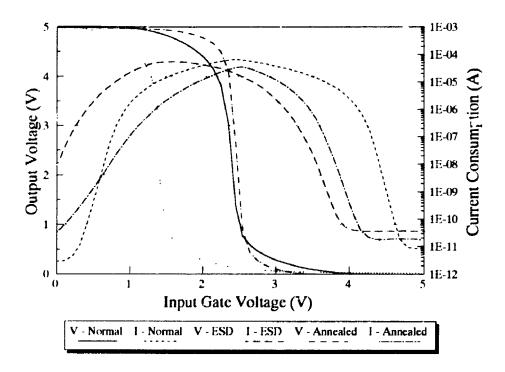

| 5.16        | Typical I-V Characteristics of Transistor Cell Before and After ESD                    | 136  |

| 5.17        | Comparison of Leakage Current in Protection Diode<br>Before and After ESD              | 136  |

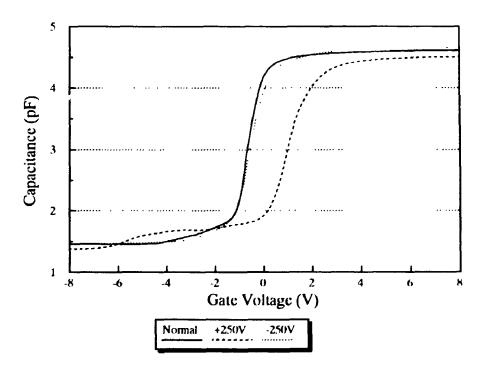

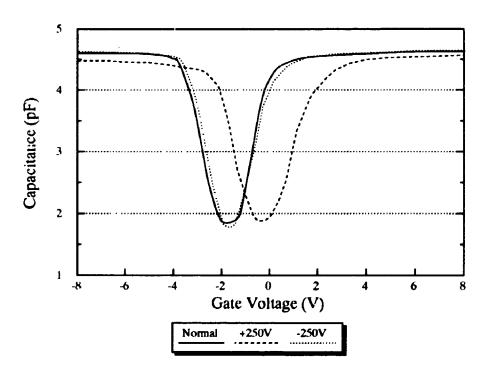

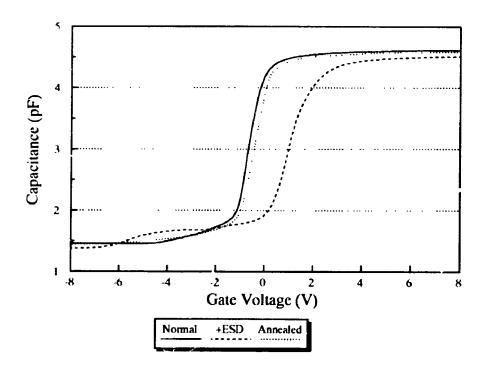

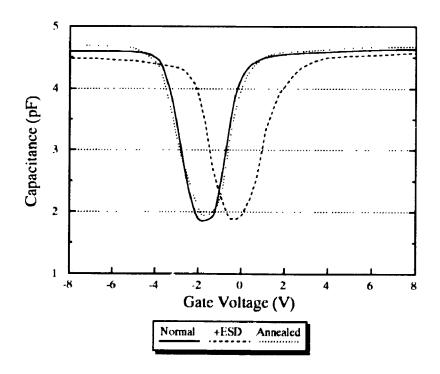

| 5.18        | High Frequency C-V Curves of a n-Type MOS-C After ±250V ESD                            | 137  |

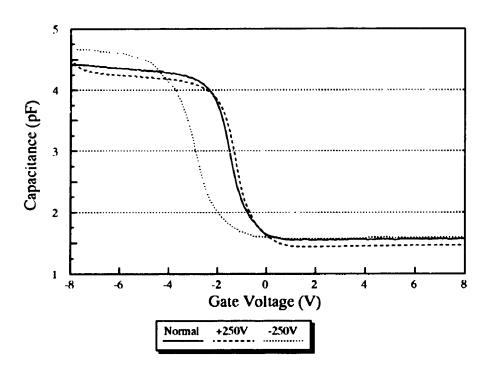

| 5.19        | High Frequency C-V Curves of a p-Type MOS-C After ±250V ESD                            | 138  |

| 5.20        | Low Frequency C-V Curves of a n-Type MOS-C After ±250V ESD                             | 138  |

| 5.21        | Low Frequency C-V Curves of a p-Type MOS-C After ±250V ESD                             | 139  |

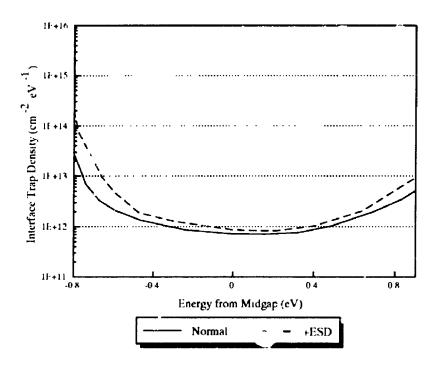

| 5.22        | Interface Trap Density versus Trap Energy of a n-Type MOS-C Before and After +250V ESD | 142  |

| 5.23        | Typical I-V Characteristics of an Annealed Transistor Cel                              |      |

| 5.24        | Typical I-V Characteristics of an Annealed Protection<br>Network Circuit               | 145  |

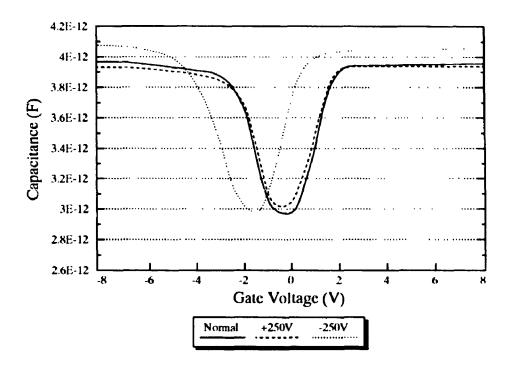

| 5.25        | Typical High Frequency C-V Characteristics of a n-type MOS-C After Annealing Process   | 146  |

| 5.26        | Typical Low Frequency C-V Characteristics of a n-Type MOS-C After Annealing Process    | 146  |

| 6.1         | Typical Protection Structure of an Integrated Circuit                                  | 152  |

| A.1         | A p-type MOS Capacitor                                                                 | 154  |

| <b>B</b> .1 | Typical C-V Characteristics of n-type MOS-C                                            | 167  |

| B.2         | Equivalent Circuits of n-type MOS-C                                                    | 168  |

| Figure | Description                                                 | Page  |

|--------|-------------------------------------------------------------|-------|

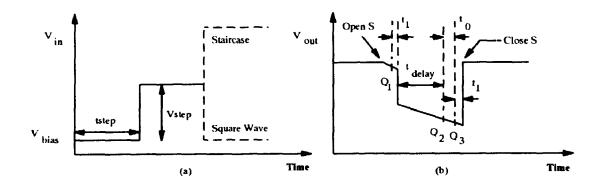

| В.3    | Low Frequency Capacitance Measurement using Ramp Method     | . 170 |

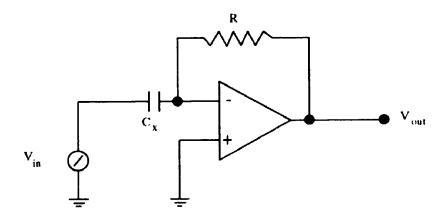

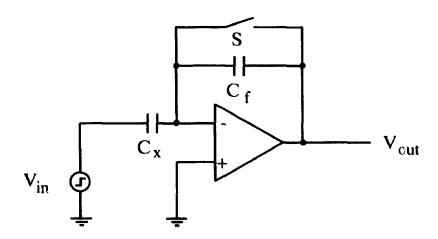

| B.4    | Low Frequency Capacitance Measurement using Feedback Method |       |

| B.5    | (a) Input and (b) Output Waveforms of a Feedback Integrator | . 173 |

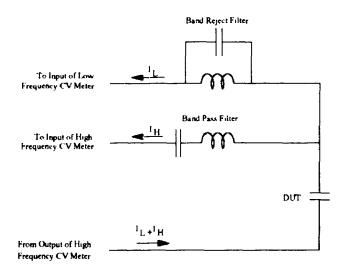

| B.6    | Simultaneous High/Low Frequency Measurement                 | . 175 |

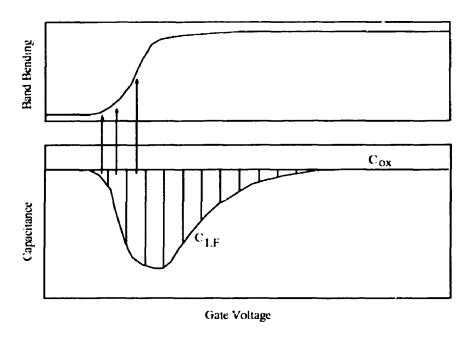

| B.7    | Band Bending versus Gate Voltage                            | . 177 |

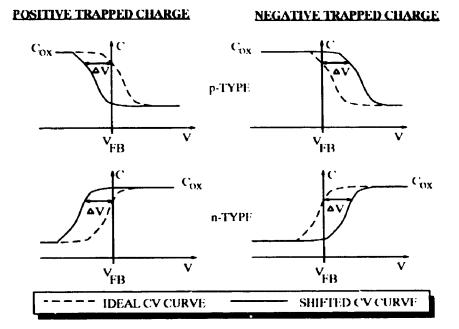

| B.8    | Effect of Trapped Charges on High Frequency CV Curve        | . 178 |

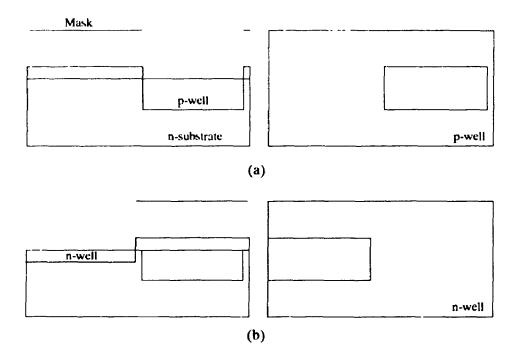

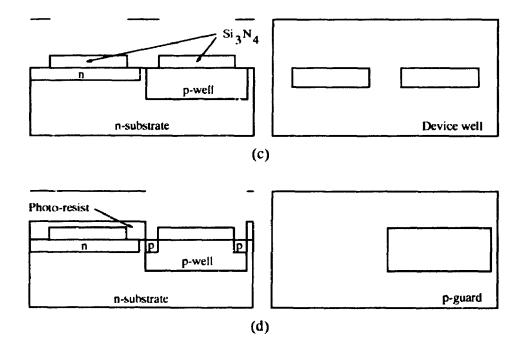

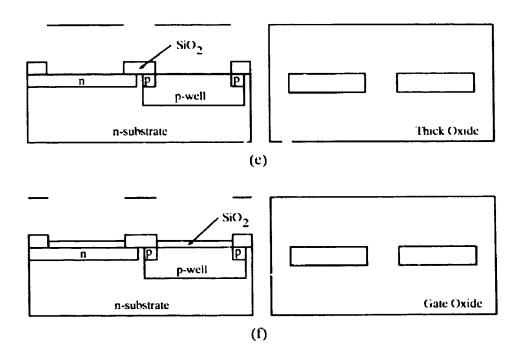

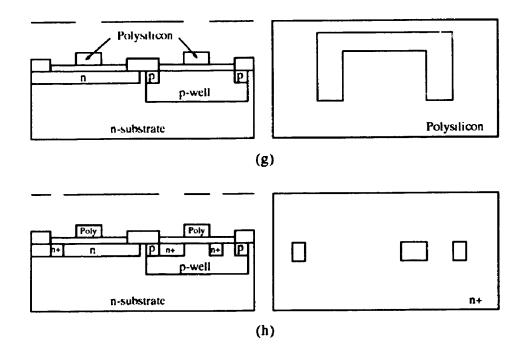

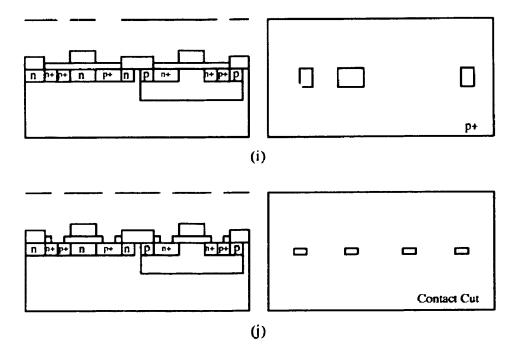

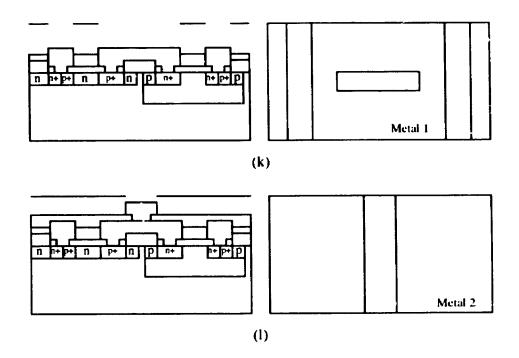

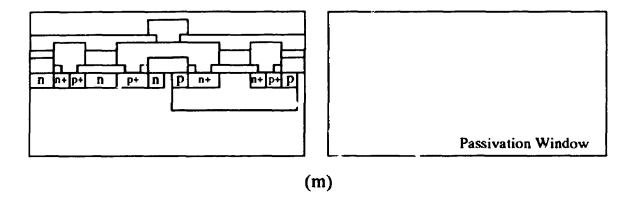

| C.1    | CMOS Processing Steps                                       | . 191 |

#### **LIST OF APPENDICES**

| ∆ppendix   |                                    | Page |

|------------|------------------------------------|------|

| APPENDIX A | Effect of Charge on MOS Structures | 154  |

| APPENDIX B | C-V Analysis Techniques            | 167  |

| APPENDIX C | CMOS Processing Technology         | 190  |

#### ABBREVIATIONS AND SYMBOLS

BCCD Bulk-channel charge-coupled device

CCD Charge-coupled device

CMOS Complementary metal-oxide semi: onductor

C-V Capacitance-Voltage

ehp Electron-hole pair

G-R Generation-recombination

HF High-frequency

LF Low-frequency

MOS Metal-oxide semiconductor

MOS-C Metal-oxide-semiconductor capacitor

MOSFET Metal-oxide-semiconductor field-effect transistor

SCCD Surface channel charge-coupled device

scr Space-charge region (depletion region)

Si Silicon

#### **NOMENCLATURE**

A Gate area (cm<sup>2</sup>)

C<sub>D</sub> Depletion layer capacitance per unit area (pF/cm<sup>2</sup>)

C<sub>FB</sub> Flatband capacitance per unit area (pF/cm<sup>2</sup>)

C<sub>g</sub> Gate-to-substrate capacitance per unit area (pF/cm<sup>2</sup>)

$C_{ex}$  Oxide capacitance per unit area (pF/cm<sup>2</sup>)

d<sub>ov</sub> Oxide thickness (cm)

D<sub>it</sub> Interface-state density (cm<sup>-2</sup>eV<sup>-1</sup>)

E<sub>c</sub> Minimum conduction band energy (eV)

E<sub>F</sub> Fermi energy or Fermi level (eV)

E, Intrinsic Fermi level (eV)

E<sub>N</sub> Electron quasi-Fermi level (eV)

E<sub>P</sub> Hole quasi-Fermi level (eV)

$E_{s}$  Electric field strength of silicon (V/m)

E, Maximum valence band energy (eV)

E<sub>vacuum</sub> Vacuum level, minimum energy an electron must process to

completely free itself from a material (eV)

g<sub>m</sub> Transconductance of MOSFET

I<sub>DS</sub> Drain-to-source current (A)

$K_0$  Oxide dielectric constant (3.9 for  $SiO_2$ )

K Semiconductor dielectric constant (11.8 for Si)

L<sub>ch</sub> MOSFET, CCD gate length (cm)

L<sub>D</sub> Intrinsic Debye length (cm)

n Number of elemental CCD transfers

n electron concentration (cm<sup>-3</sup>)

#### **NOMENCLATURE** (Cont.)

N<sub>A</sub> Acceptor doping concentration (cm<sup>-3</sup>)

N<sub>D</sub> Donor doping concentration (cm<sup>-3</sup>)

q Magnitude of electron charge  $(1.602 \times 10^{-19} \text{ C})$

Q Charge density (C/cm<sup>2</sup>)

$Q_t$  Fixed exide charge (C)

Q<sub>it</sub> Interface trapped charge (C)

Q<sub>m</sub> Mobile ionic charge (C)

Q<sub>ot</sub> Oxide trapped charge (C)

$Q_{S_1-S_1O_2}$  Charge in Si-SiO<sub>2</sub> system (C)

V<sub>DS</sub> Drain voitage (V)

$V_{DD}$  Supply voltage (V)

$V_{GS}$  Gate-to-source voltage (V)

$V_G$  Gate voltage (V)

V<sub>out</sub> Output voltage (V)

$V_{\text{sub}}$  Substrate voltage (V)

V<sub>S</sub> Input signal voltage (V)

V<sub>SS</sub> Ground

V<sub>1</sub> Threshold or turn-on voltage (V)

W Depletion width (cm)

W<sub>ch</sub> Width of channel in MOSFET(cm)

ε CCD elemental transfer inefficiency

$\varepsilon_0$  permittivity of free space (8.85x10<sup>-14</sup> F/cm)

$\varepsilon_{s_0}$  permittivity of silicon (1.035x10<sup>-12</sup> F/cm)

## NOMENCLATURE (Cont.)

| $\epsilon_{SiO_2}$ | permittivity of silicon dioxide (0.345x10 <sup>-12</sup> F/cm) |

|--------------------|----------------------------------------------------------------|

| η                  | CCD transfer efficiency                                        |

| λ                  | CCD charge loss                                                |

| ρ                  | Charge density (C/cm³)                                         |

| $\psi_{B}$         | Bulk potential (V)                                             |

| $\phi_i$           | CCD gate connection as phase                                   |

| $\Phi_S$           | Semiconductor surface potential (V)                            |

| $\Phi_{ms}$        | Metal-semiconductor work function difference (V)               |

| $\Phi_{FN}$        | Electron quasi-Fermi potential (V)                             |

| $\Phi_{FP}$        | Hole quasi-Fermi potential (V)                                 |

| $\phi_R$           | Reset gate phase                                               |

The author of this thesis has granted The University of Western Ontario a non-exclusive license to reproduce and distribute copies of this thesis to users of Western Libraries. Copyright remains with the author.

Electronic theses and dissertations available in The University of Western Ontario's institutional repository (Scholarship@Western) are solely for the purpose of private study and research. They may not be copied or reproduced, except as permitted by copyright laws, without written authority of the copyright owner. Any commercial use or publication is strictly prohibited.

The original copyright license attesting to these terms and signed by the author of this thesis may be found in the original print version of the thesis, held by Western Libraries.

The thesis approval page signed by the examining committee may also be found in the original print version of the thesis held in Western Libraries.

Please contact Western Libraries for further information:

E-mail: <u>libadmin@uwo.ca</u>

Telephone: (519) 661-2111 Ext. 84796

Web site: <a href="http://www.lib.uwo.ca/">http://www.lib.uwo.ca/</a>

### Chapter 1

## The Physics and Reliability of Charge-Coupled Devices (CCDs)

This chapter describes the physics and technology of charge-coupled devices. It includes a review of ideal and non-ideal MOS capacitors, a description of the basic principles of charge-coupled devices (CCDs), and an investigation of the reliability of CCDs. Finally, the objectives of this project are presented.

#### 1.1 Introduction

After the invention of charge-coupled devices (CCDs) in the early 1970s, the technology has been extensively employed in the fields of image sensing, analog signal processing and analog memories. However, CCDs have had most significant impact in the field of imaging. CCD Linear Imaging Devices (LIDs) and Area Imaging Devices (AIDs) are used in many \_pplications ranging from lightweight, low-power television cameras to spectrometers. CCDs are simple to fabricate and are suitable for a variety of applications; relatively standard silicon wafer manufacturing technology is employed in their manufacture. In principle, the CCD array is a microelectronic structure consisting of MOS capacitors (MOS-C) connected in parallel, that use diodes on the input and the output for injecting or detecting the capacitor charges. In the following sections, the physical properties of MOS-C are reviewed and the basic principles of charge-coupled devices discussed.

#### 1.2 Review of Metal-Oxide-Semiconductor Capacitor (MOS-C)

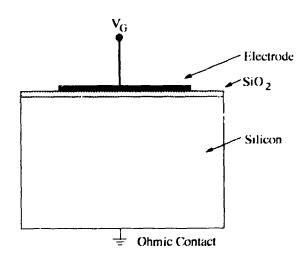

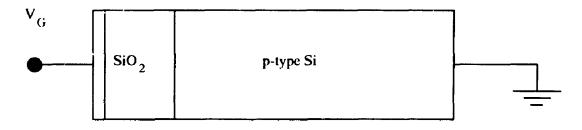

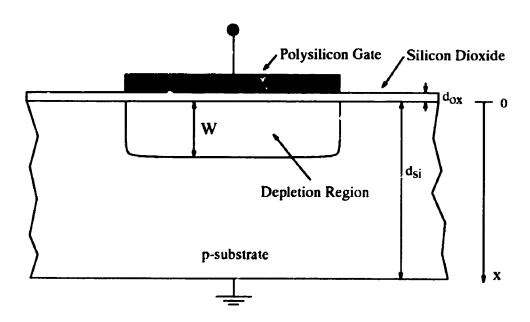

Most modern integrated circuits are based on the metal-oxide-semiconductor (MOS) technology. Among MOS devices, the simplest structure is the MOS-Capacitor. It can be used as a test structure or as the fundamental building block in more complex MOS systems. As a building block, it is used as the unit cell of the Dynamic Random Access Memory (DRAM) and Charge-Coupled Devices (CCDs). If used as a test structure, it provides detailed information about the oxide and the semiconductor. The MOS-C, as shown in Figure 1.1, is a two terminal device consisting of a thin silicon dioxide (SiO<sub>2</sub>) layer sandwiched between an electrode and a silicon substrate. The electrode can be aluminum or heavily doped polycrystalline silicon (polysilicon). The silicon substrate is grounded by an ohmic contact. The ohmic contact on the substrate, called the back contact, is normally grounded. MOS capacitors are different from the capacitors made by two conducting parallel plates; characteristics strongly depend on the voltage applied on the gate.

Figure 1.1 Metal-Oxide-Semiconductor Capacitor

In an ideal MOS-C structure, one assumes that: (1) the oxide is a perfect insulator and therefore no current flows through the oxide layer under all bias conditions; (2) there are no recombination-generation (R-G) centers located at the oxide-semiconductor interface and inside the oxide; (3) the semiconductor is uniformly doped; (4) the gate electrode is sufficiently thick to be considered as equipotential under all bias conditions. In the following discussion, the MOS-C is assumed to be an ideal structure.

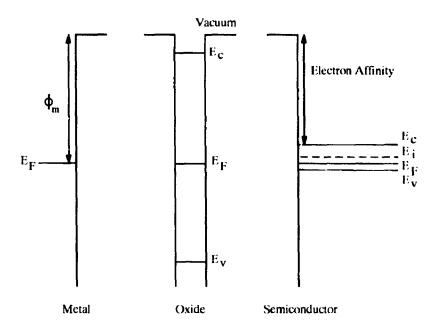

The energy band diagrams for the individual components of the MOS structure are shown in Figure 1.2. The vacuum level, shown at the top of the vertical line, denotes the minimum energy that an electron must possess to completely free itself from the material.  $E_c$ ,  $E_F$ ,  $E_i$  and  $E_v$  correspond to the energy level for the conduction-band, Fermi energy, intrinsic energy and valence-band, respectively. In a metal, the energy difference between the vacuum and the Fermi energy ( $E_{vacuum} - E_F$ ) is called the metal work function,  $\Phi_M$ , and is constant for a specific metal. However, for semiconductors, the Fermi energy level is a function of doping and if voltage is applied to the gate, the energy bands bend accordingly. Therefore, the height of the surface energy barrier is defined in terms of the electron affinity which is defined as the energy difference between the vacuum level and the conduction band edge at the surface of the semiconductor.

A MOS structure is formed when the metal, oxide and semiconductor are brought together. Since under equilibrium conditions, the Fermi level inside a material, or a group of materials in contact, is invariant of position, it must line up inside the MOS structure. From Figure 1.2, the metal work function is defined as the electron affinity plus the difference between the conduction-band and the Fermi level in the

Figure 1.2 Individual Energy Band Diagram for the Different Components of the MOS Structure

semiconductor at infinity. The vacuum levels of the metal and semiconductor components must be in perfect alignment. The energy band diagram for an ideal MOS structure in equilibrium is shown in Figure 1.3.

The charge and potential distribution of MOS capacitor can be determined by solving Laplace's and Poisson's equations:

$$\nabla^2 V = 0 \qquad \text{(oxide)} \qquad \dots (1.1)$$

$$\nabla^2 V = -\frac{\rho}{\varepsilon_{Si}} \qquad (semiconductor) \qquad ...(1.2)$$

where  $\varepsilon_{S_t}$  = permittivity of semiconductor

V = electrostatic potential

$\rho$  = charge density

Figure 1.3 Energy Band Diagram for an Ideal MOS Structure in Equilibrium

#### 1.2.1 The Equilibrium MOS-C

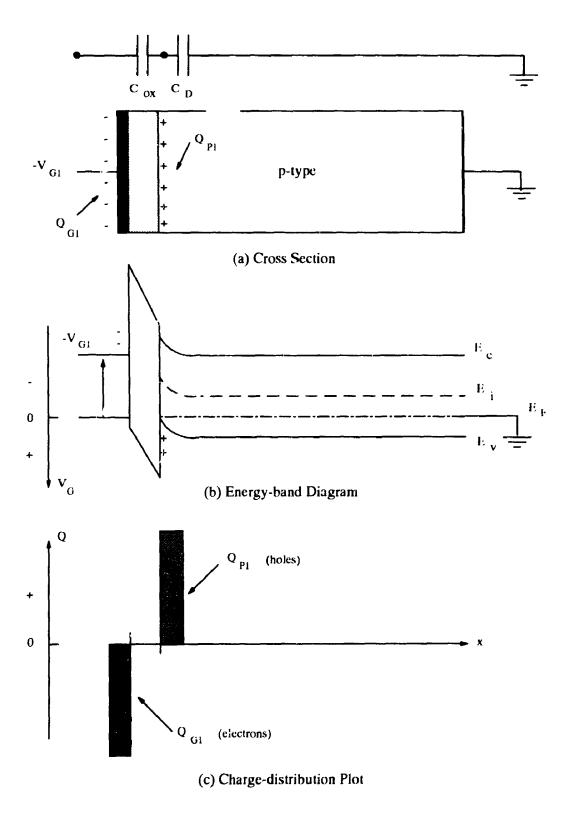

Consider Figure 1.4 which shows the cross section, energy-band diagram and charge-distribution plots of a p-type substrate MOS-C under a negative gate voltage. The negative gate voltage,  $-V_{G1}$ , causes the gate surface to accumulate electrons. This is indicated in Figure 1.4(a) and Figure 1.4(c) by "-" and by the charge density  $Q_{G1}$ , respectively. If one assumes that the structure is ideal, *i.e.* there are zero oxide charges and interface states and no metal-semiconductor work-function difference, there will be an equal density of holes in the surface of semiconductor. This is shown in Figure 1.4(b) and Figure 1.4(c) by "+" and the charge density  $Q_{P1}$  respectively.

As a negative voltage is applied to the gate, the energy bands are bent upward and the majority carriers, holes in this case, accumulate near the semiconductor surface.

Figure 1.4 P-Type Substrate MOS Capacitor

An "accumulation" layer is formed underneath the gate oxide. In terms of its electrical characteristics, this MOS capacitor behaves like a parallel plate capacitor, with the gate electrode forming one plate and the substrate forming the other plate. The oxide capacitance per unit area can be calculated using Laplace's Equation [Appendix A].

$$C_{ox} = \left(\frac{\varepsilon_{SiO_2}}{d_{ox}}\right) \qquad \dots (1.3)$$

where  $C_{ox}$  = oxide capacitance per unit area  $\epsilon_{SiO_2}$  = permittivity of SiO<sub>2</sub>  $d_{ox}$  = oxide thickness

Since there is no depletion layer formed, the depletion capacitance per unit area,  $C_D$ , is 0. Therefore, the total gate-to-substrate capacitance per unit area,  $C_g$ , of the MOS-C in the accumulation mode is  $C_{ox}$ .

$$C_g = C_{ox}$$

$$= \frac{\varepsilon_{SiO_7}}{d_{ox}} \qquad \dots (1.4)$$

where  $C_g$  = gate-to-substrate capacitance per unit area  $C_{ox}$  = oxide capacitance per unit area  $\varepsilon_{SiO_2}$  = permittivity of silicon  $d_{ox}$  = oxide thickness

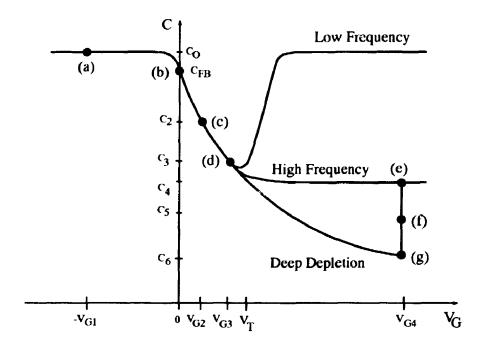

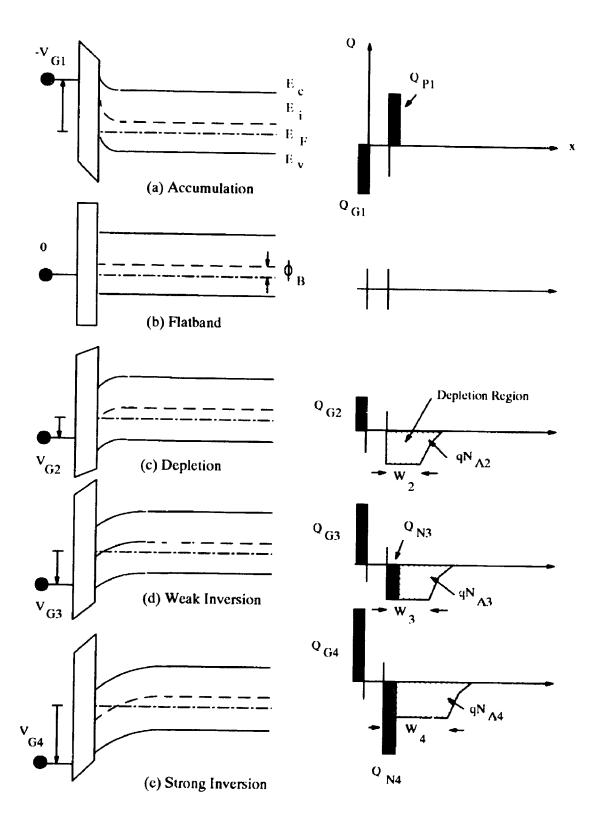

If the gate voltage varies from negative to positive, the behaviour of the p-type substrate MOS-C is shown in Figure 1.5 and 1.6. At a gate voltage of  $-V_{GI}$ , the device is in the accumulation mode and the gate-to-substrate capacitance is given by the oxide capacitance  $C_{ox}$ . This is shown in Figure 1.6(a). If the gate voltage is zero, the device

is at flatband and the capacitance is  $C_{FB}$ ; no energy bands bend at flatband voltage. As the gate voltage becomes positive, i.e. at  $V_{G2}$ , the energy bands bend downward and the majority carriers are depleted. This region is called the depletion region or space-charge region (scr). The depletion region consists of negatively charged acceptor ions and an equal amount of positive gate charge. The width of depletion region, W, increases as the magnitude of the gate voltage is increased. The magnitude of the charge density per unit area in the depletion region depends on the doping concentration, electron charge and the depth of the scr. In general, the depletion capacitance per unit area,  $C_D$ , is obtained by solving Poisson's Equation [Appendix A].

$$C_D = \frac{\varepsilon_{Si}}{W} \qquad \dots (1.5)$$

where  $C_D$  = depletion layer capacitance per unit area

$\varepsilon_{Si}$  = permittivity of silicon

W = depletion width

The total gate-to-substrate capacitance,  $C_8$ , under depletion conditions can be approximated by the gate oxide capacitance,  $C_{ox}$ , in series with  $C_D$ .

$$C_g = \left(\frac{1}{C_{ox}} + \frac{1}{C_D}\right)^{-1} \qquad \dots (1.6)$$

where  $C_g$  = gate-to-substrate capacitance per unit area

C<sub>D</sub> = depletion layer capacitance per unit area

$C_{ox}$  = oxide capacitance per unit area

Figure 1.5 Capacitance-Gate Voltage Curves for a p-Type MOS-C

As the gate voltage increases, the energy bands bend downward and eventually the intrinsic level,  $E_i$ , at the semiconductor surface touches the Fermi level,  $E_F$ . At this particular point, the semiconductor surface is inverted, i.e. from p-type to n-type.

An additional increase in gate voltage will further bend the energy bands downward and attract more minority carriers to the semiconductor surface. The point where the intrinsic energy at the semiconductor surface moves below the Fermi energy level by one bulk potential ( $\phi_B = E_i - E_F$ ), is called the onset of inversion. The surface electron volume concentration equals the hole volume concentration in the bulk and the corresponding gate voltage is called threshold voltage,  $V_T$  [Appendix A].

Figure 1.6 Energy-Band and Charge-Distribution Diagram for a p-Type MOS-C

$$V_{I} = \frac{\sqrt{4\varepsilon_{si}qN_{A}\phi_{B}}}{C_{cor}} + 2\phi_{B} \qquad \dots (1.7)$$

where  $V_{\tau}$

$V_T$  = threshold voltage

$\varepsilon_{yy}$  = permittivity of silicon

q = charge of electron

$N_A$  = acceptor impurity density

$\phi_B$  = bulk potential

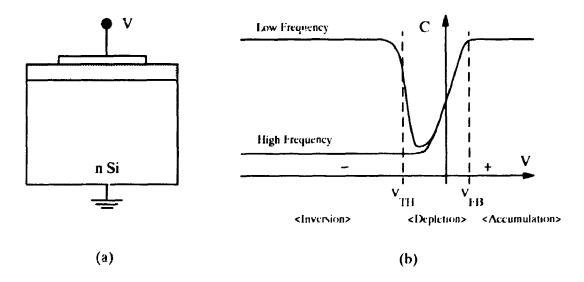

A further increase in the gate voltage will attract more minority electrons towards the surface, but will not widen the depletion region significantly because the inversion layer shields the substrate from further gate voltage changes. Under low frequency conditions, the MOS-C behaves like a parallel plate capacitor, since the surface charge created by the inversion layer is able to respond to the slowly changing gate voltage. The dynamic or high-frequency capacitance remains the same as for the maximum depletion condition, since the surface charge cannot respond to the rapidly changing gate voltage.

$$C_g = C_{ox}$$

for low frequency (<10Hz) ...(1.8)

$$C_g = \left(\frac{1}{C_{ox}} + \frac{1}{C_D}\right)^{-1}$$

for high frequency ...(1.9)

where

C<sub>g</sub> = gate-to-substrate capacitance per unit area

$C_{ox}$  = oxide capacitance per unit area

C<sub>D</sub> = depletion layer capacitance per unit area at maximum depletion width

#### 1.2.2 The Deep-Depletion MOS-C

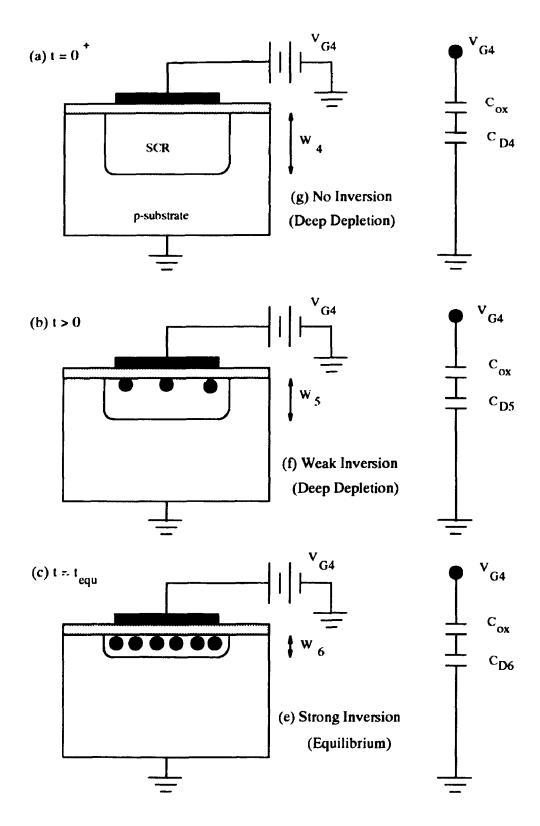

The capacitance-voltage curve (a) to (e) or (e) to (a) in Figure 1.5 is obtained by changing the bias from negative to positive very slowly so that the capacitor under test can be considered to be in a quasi-equilibrium state. However, if a positive voltage is suddenly applied to the gate, *i.e.* during pulse excitation, majority holes are repelled from the semiconductor surface. Generation-recombination processes are not possible due to insufficient time. The device in this condition is said to be in a deep depletion (DD) mode; this is the operational condition for charge-coupled devices (CCDs). This corresponds to point (g) in Figure 1.5.

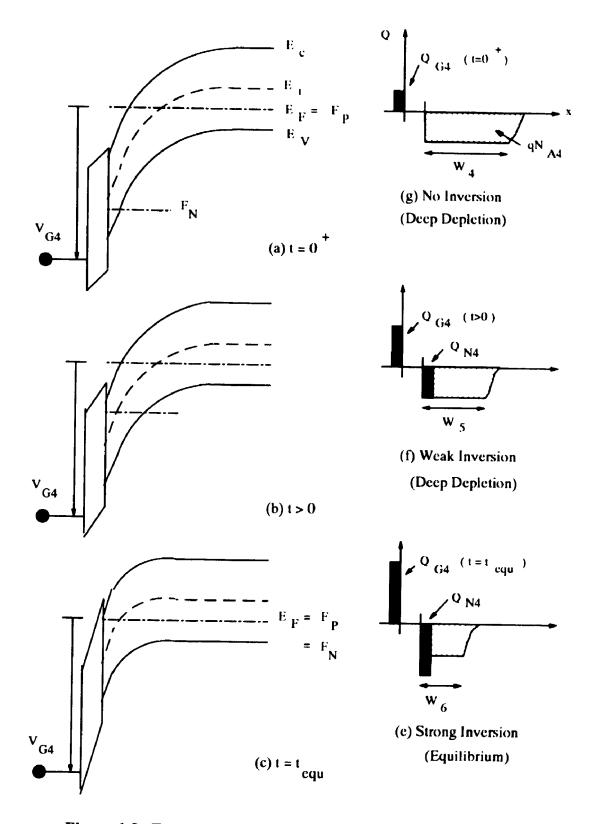

Consider the situation shown in Figure 1.7 where the capacitor under test is initially biased at zero volts. At t=0, a positive voltage,  $V_{64}$ , is applied to the gate. At this particular moment, majority holes are repelled from the semiconductor surface; the corresponding depletion width is  $W_4$ .

From the energy-band diagrams and charge-distribution plots shown in Figure 1.8, one can discover that the Fermi level has divided into the hole and electron quasi-Fermi levels. The only minority carriers which are attracted to the surface after the voltage is applied are the ones in the depletion region before the voltage is applied. The MOS-C will return to an equilibrium state from the deep-depletion state through electron-hole pair generation. The electrons generated by this process drift to the surface and are accumulated. At some intermediate level, as shown in Figure 1.7(b), an inversion layer is formed. The capacitance, as shown in Figure 1.7, can range anywhere from  $C_{D4}$  to  $C_{D6}$  in the deep-depletion state. As this process continues, the width of the depletion region and the bulk charge,  $qN_{A4}$ , decreases as the inversion charge,  $Q_{N4}$ , increases. Finally, the capacitor is returned to equilibrium.

Figure 1.7 Space-Charge Region for a p-Type MOS-C in Deep Depletion Mode

Figure 1.8 Energy-Band and Charge-Distribution Diagram for a p-Type MOS-C in Deep Depletion Mode

#### 1.2.3 Non-ideal MOS Structures

Ideal silicon-silicon dioxide systems consist of a crystal, silicon, and a glassy material, silicon dioxide. The interface between these two materials is often characterized as a continuous random network structure because of the flexibility of silicon dioxide. In reality, the situation is more complex. Real Si-SiO<sub>2</sub> systems differ from ideal systems in electrical properties which are influenced by the processing technology. For example, large concentrations of hydrogen and chlorine ions often exist near the interface and cause defects in the structure.

There are two classes of trapping states in the real silicon-silicon dioxide system. Interface traps capture and release electrons and holes with time constants, at room temperature, in the range from picoseconds to hours. These affect a number of device properties, such as leakage current and MOS capacitor storage time. On the other hand, bulk oxide traps usually have very large time constants (years) and these affect device stability. If electrons or holes are captured in these traps, the charge in the oxide will change and device properties will be modified. The induced charge will last almost indefinitely.

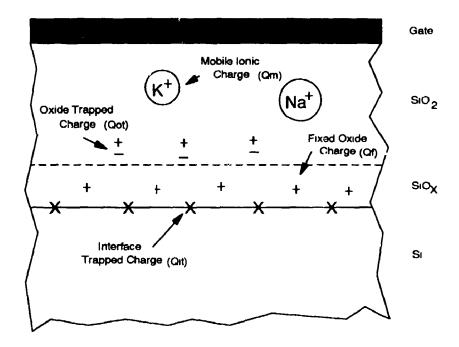

In an ideal MOS system, there is no band bending at zero gate voltage; the flatband voltage, *i.e.* the voltage which has to be applied on the gate to achieve the flat band condition, is zero. As shown in Figure 1.9 [1][2], for a real MOS system, the work function difference, and the charges in the oxide and the traps at the Si-SiO<sub>2</sub> interface, can cause a non-zero flatband voltage. The flatband voltage for a non-ideal MOS system is equal to the work function difference and the voltage shift generated by the charges in the Si-SiO<sub>2</sub> system.

Figure 1.9 Charges in the Si-SiO, Interface System

$$V_{FB} = \phi_{ms} - \frac{Q_{Si-SiO_2}}{C_{ox}} = \phi_{ms} - \frac{Q_f + Q_m + Q_{oi} + Q_{it}}{C_{ox}}$$

...(1.10)

where  $V_{FB}$  = flatband voltage  $\phi_{ms}$  = metal-semiconductor work function difference  $Q_{Si-SiO_2}$  = charges in Si-SiO<sub>2</sub> system  $Q_f$  = fixed oxide charge  $Q_m$  = mobile ionic charge  $Q_{ot}$  = oxide trapped charge  $Q_{it}$  = interface trapped charge Therefore, the threshold voltage for a non-ideal MOS system is

$$V_{I} = V_{FB} + \frac{\sqrt{4\varepsilon_{sI}qN_{A}\varphi_{B}}}{C_{ox}} + 2\varphi_{B} \qquad ...(1.11)$$

where  $V_T$  = threshold voltage

$\varepsilon_{,i}$  = permittivity of silicon

q = charge of electron

$N_A$  = acceptor impurity density

$\phi_B$  = bulk potential

In an ideal MOS-C structure, one assumes that the semiconductor is uniformly doped. However, in practice, the doping profile in the semiconductor is seldom uniform; the dopant impurity distribution is not the same at the semiconductor surface as in the bulk. This may be caused by a dopant impurity redistribution during thermal oxidation or a diffusion/implantation of dopant ions into the surface region. The nonuniform doping profile can alter the electrical properties of the MOS-C structure. A review of the effect of various dopant impurity distributions, namely uniform, linear and exponential, on the threshold voltage of a basic p-type substrate MOS-C is discussed in Appendix A. The theoretical analysis presented in this thesis assumes an uniform distribution; the exact distribution, if required, could be obtained from the results of C-V measurements.

# 1.2.3.1 Silicon-Silicon Dioxide Interface Traps

Peal Si-SiO<sub>2</sub> systems differ from ideal systems in various ways. The occurrence of di' rent defects depends on the processing technology. The defects in the

interface can be caused by fixed oxide charges, interface trapped charges, oxide trapped charges and mobile ionic charges. The interface charges are shown in Figure 1.9.

#### 1.2.3.1.1 Fixed Charges

The fixed charge is positive and located at the interface. It is independent of the oxide thickness, the semiconductor doping concentration and doping type. The fixed charge varies as a function of the Si surface orientation. Studies [1] have found that it is largest on {111} crystal surfaces and smallest on {100} crystal surfaces. The ratio of the fixed charge on the two surfaces is approximately 3:1. It affects the threshold voltage of the MOS transistor and the flatband voltage of MOS capacitors because it alters the semiconductor surface field. The fixed charge is usually very stable, not affected by hydrogen or water vapor in the oxidation, by annealing atmospheres, or by low-temperature hydrogen annealing. The fixed charge is controlled by device fabrication processes.

# 1.2.3.1.2 Interface Traps

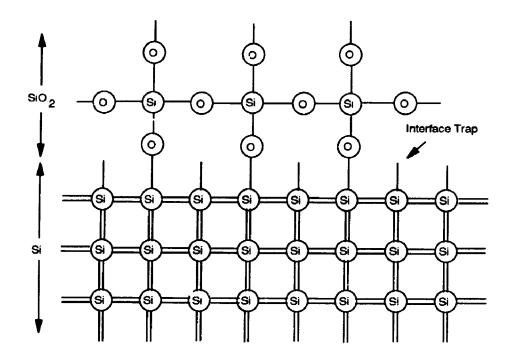

Interface traps are electron or hole capture sites located at the silicon-silicon dioxide interface, with energy levels positioned inside the silicon forbidden gap. Interface traps are allowed energy states in which electrons or holes are localized in the vicinity of a material surface. Although detailed models for the electrical behaviour of the interface traps exist, the physical origin of the traps has not been satisfactorily explained. Experiments have shown that the interface traps arise primarily from unsatisfied chemical bonds at the surface of the semiconductor. The silicon lattice is disrupted at the Si-SiO<sub>2</sub> interface and some Si-surface bonds are

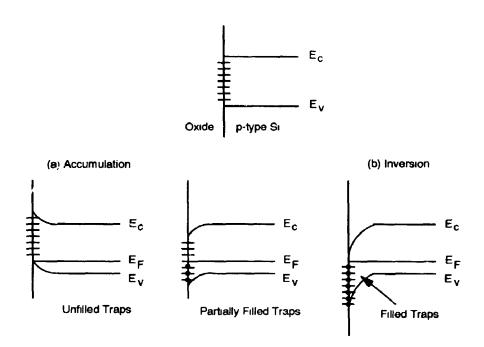

created, becoming the interface traps. The model of interface traps is shown in Figure 1.10 [3]. Filling of the interface traps is illustrated in Figure 1.11; the total amount of charge in these traps depends on the surface potential.

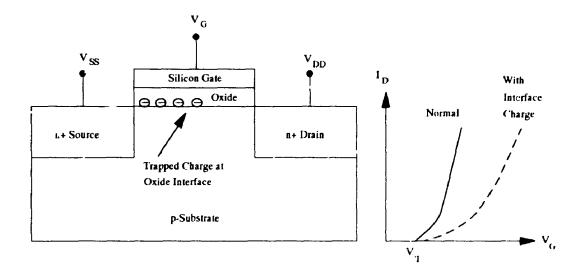

Figure 1.10 Physical Model of Interface Traps

The interface traps affect device characteristics in many ways. For example, the operation of a MOS transistor requires induction of charge carriers in the channel. However, in the presence of interface traps, some of the induced charges are captured by the interface traps, becoming thus unavailable to the current transport mechanism, as shown in Figure 1.12. Transistor gain decreases, since current versus voltage curve of the transistor is shifted along the voltage axis and becomes less steep. For MOS capacitors, this time dependent trapping phenomenon results in time or frequency dependent CV curves. The interface traps act as generation-recombination centres that affect all silicon devices and increase leakage

Figure 1.11 Electrical Model of Interface Traps

current in transistors, increase the loss in charge-coupled devices and increase noise.

Figure 1.12 Charge Trapping by Interface Traps

#### 1.2.3.2 Bulk Oxide Traps

The existence of bulk oxide traps is related to defects in this material. The oxide often has a large defect density near the interface because this is the first area reached by the electrons or holes injected from the substrate or the gate electrode.

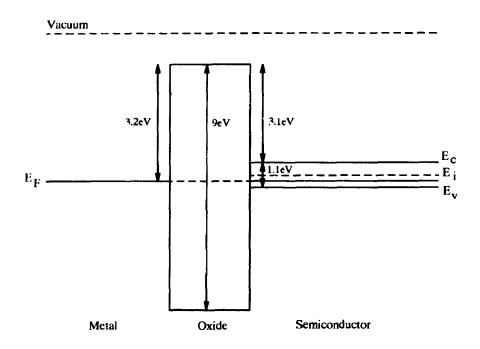

In general, carriers can be injected into the bulk/oxide by photogeneration or In the photogeneration process, electron-hole pairs are hot-carrier injection. generated as a result of photon absorption. Since the bandgap of the silicon dioxide is about 9eV, photons with a wavelength of at least 130nm ( $\lambda = hc/E$ ), are required for this process. Radiation usually has higher energy and, therefore, bulk generation and carrier trapping is mostly caused by the radiation effect. Other phenomena, such as electrical overstress/electrostatic discharge (EOS/ESD), can also result in induced charges in the bulk/oxide. Charges captured during these processes can create more interface traps and oxide traps because the primary charge may release considerable energy upon trapping. For example, if the charge originates from an electron-hole pair in the oxide with a latent energy of about 9eV, it may release up to 9eV upon recombination. Experiments [3] have shown that photons of 10eV energy (ultraviolet) are absorbed very effectively in the outer 30nm layer. For energy ranges from 3 to 10eV, the absorption is throughout the whole oxide. For ultrahigh energy photons, oxide damage, such as atom displacement and the generation of electron-hole pairs, can occur.

Similarly, if photons with an appropriate energy are absorbed in the semiconductor, they may excite electrons to an energy high enough for the electron to escape into the oxide conduction band. Usually photons of 3 to 5eV are needed to exceed the energy barrier.

Hot-carrier injection, as shown in Figure 1.13, occurs in cases where charge carriers are accelerated towards the interface in a high field region in the silicon. The charge carriers can be initiated by illumination, avalanche breakdown or high electric fields. The injection of holes occurs by a similar mechanism. Since the energy barrier for holes (about 5eV) is much higher than for electrons (about 3.1eV), it requires more energy to initiate the hole injection process.

Figure 1.13 Hot-Carrier Injection

Charge injection and trapping can lead to oxide charging and cause MOS threshold voltages to change. Since the oxide is a good insulator, the trapped charges may be very stable and can lead to secondary phenomena such as the creation of additional interface traps and oxide traps.

## 1.3 Fundamentals of Charge-Coupled Devices (CCDs)

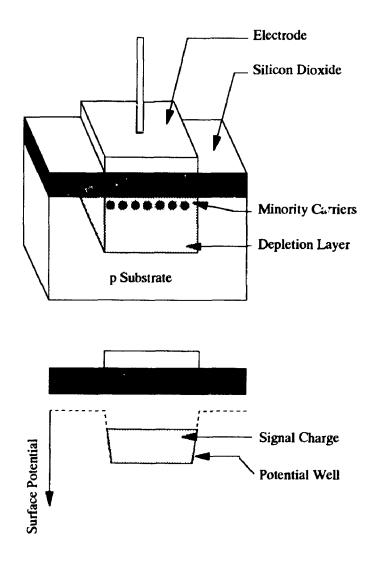

The fundamental structure of a CCD consists of a MOS capacitor (MOS-C), as shown in Figure 1.14, which operates in the deep-depletion region. When voltage is suddenly applied to the electrode and substrate, a depletion layer is created; if charges are now injected into this depletion layer, they will be temporarily stored and "memorized" as analog quantities.

Figure 1.14 Basic Structure of a MOS-C

## 1.3.1 Input Configuration of CCDs

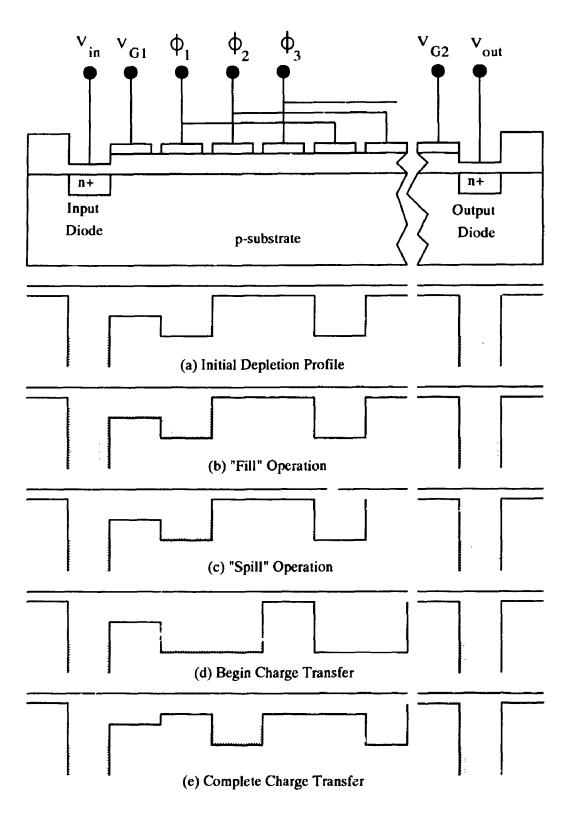

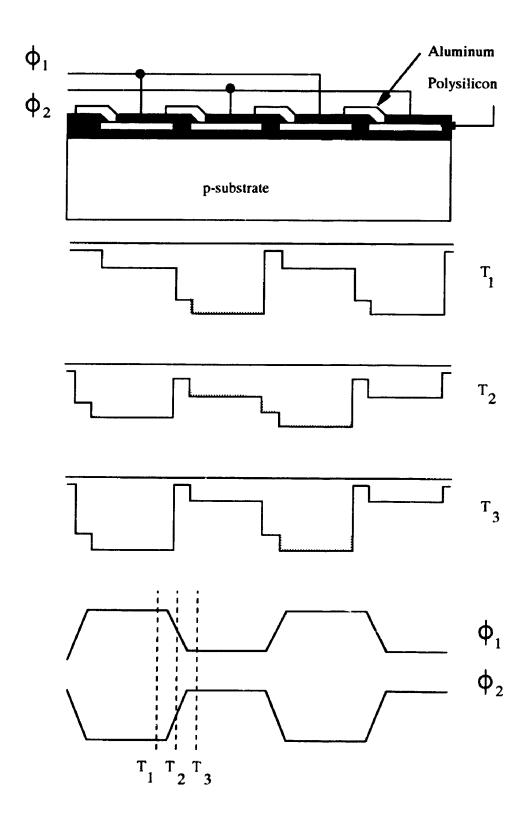

A charge coupled device is operated as an analog shift register which stores a signal in the form of charges on a series of capacitors. The transfer of charge from one capacitor to the next is controlled by an applied voltage pulse. This concept of charge transfer is illustrated in Figure 1.15 [4] that shows a series of closely spaced MOS capacitors fabricated in a p-type substrate. The charge packet is stored under the gate with the highest potential. By placing the storage elements, *i.e.* the MOS capacitors, adjacent to each other, voltages on the gate electrodes can be raised and lowered sequentially which causes the individual charge packets beneath them to be passed from one storage element to the next.

The charge is injected or removed from the depletion well by the n-type diffusion areas located at both ends of the capacitors. To inject charge, the phase one clock is held at positive potential while the phase two and three clocks are held at zero. This creates a surface potential shown in Figure 1.15(a). The input diode is initially reversed biased, then briefly grounded. During the sequence, the minority carriers flow from the diode region to the depletion well under the phase one electrode. The well under the phase one electrode "fills" with charge and overflows. This corresponds to Figure 1.15(b). When the diode is returned to a positive potential, any charge above the  $V_{G1}$  surface potential level "spills" back into the diode. The charge injected into the well is determined by the difference between the phase one clock and the input gate voltage. Similarly, the signal charge can be detected by a MOSFET connected to the output diode.

Figure 1.15 Operating Principle of a 3-Phase CCD

## 1.3.2 Multiphase CCD Structures

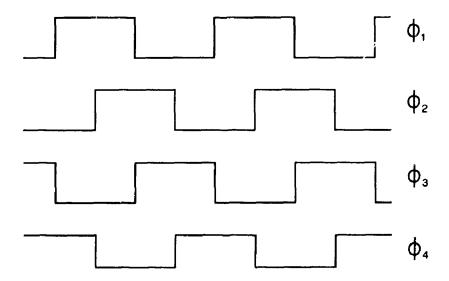

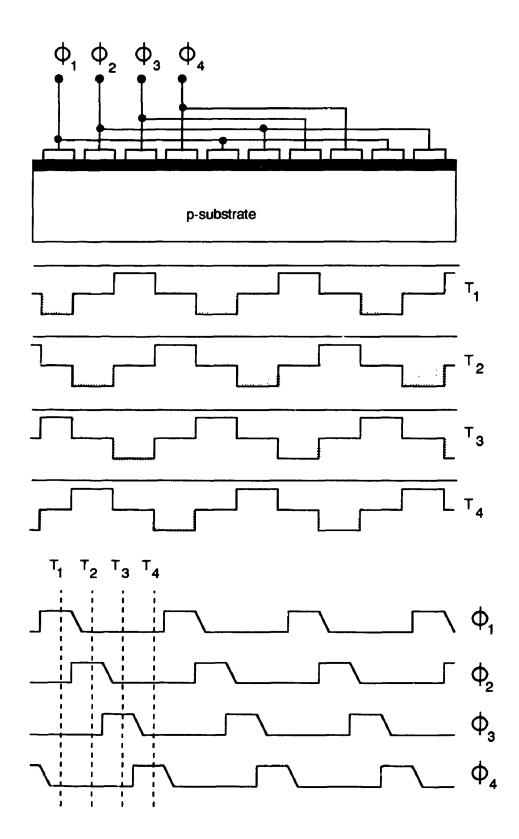

As shown in Figure 1.15, the minimum number of phases required to achieve a directional charge flow in a CCD with uniform oxide thickness is three. However, this scheme suffers from certain drawbacks. In order to prevent the stored charge from being transferred backwards or injected into the substrate, the fall time of the clock must be carefully controlled. A four-phase CCD eliminates some of these problems and can be effected by two different clock types. The first clocking scheme, similar to the one in a three-phase CCD, shown in Figure 1.17, can be implemented by using two flip-flops. The second clocking principle, as shown in Figure 1.16, is easier to implement because  $\phi_3$  and  $\phi_4$  are the inverse of  $\phi_1$  and  $\phi_2$ . Moreover, the fall time requirement is relaxed and the charge storage capacity is approximately doubled. Using two layers of polysilicon, gap problems can be eliminated by the overlapping gate structure.

Figure 1.16 Operating Principle of a 4-Phase CCD with an Alternative Clocking

Figure 1.17 Operating Principle of a 4-Phase CCD

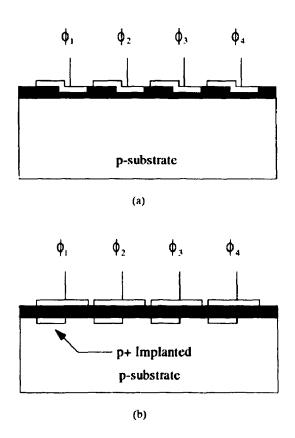

By varying the oxide thickness or heavily doping the region under half of each gate, a two-phase CCD can be implemented using the structure asymmetry. This basic structure and the operating principle of a two-phase CCD are shown in Figures 1.18 and 1.19 respectively.

Figure 1.18 Basic Structure of a 2-Phase CCD

As shown in the preceding analysis, in a three/four-phase CCD with uniform oxide thickness, the direction of charge flow is externally controlled by the clocking scheme and can be bi-directional whereas an asymmetrical two-phase CCD is undirectional. The main differences between two and four-phase CCDs characteristics are summarized in Table 1.1.

Figure 1.19 Operating Principle of 2-Phase CCD

Table 1.1 Advantages of Two and Four Phase CCDs

| Characteristics                   | Two-Phase | Four-Phase |

|-----------------------------------|-----------|------------|

| High Charge Handling<br>Capacity  |           | *          |

| High Dynamic Range                |           | *          |

| High Clocking Frequency           | *         |            |

| Drive Circuit Simplicity          | *         |            |

| Bidirectional Transfer Capability |           | *          |

#### 1.3.3 Surface and Bulk Channel CCDs

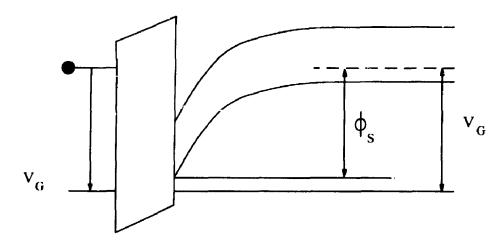

A surface channel CCD, shown in Figure 1.20, has a uniformly doped substrate. When the gate is biased, a depletion region is formed beneath the oxide layer. The lowest energy state for a photoelectron is at the oxide-substrate interface. Charges reside at the semiconductor surface as minority carriers and are exposed to the silicon-dielectric surface states. Since interface states act as active generation-recombination centres, some of the charge wil! be captured as charge packets are transferred through the device and cause charge loss or imperfect transfer efficiency.

The problems encountered by the surface channel CCD devices can be solved by moving the charge packets away from the surface into a buried n-channel as illustration in Figure 1.21. In this case, the charge packets reside as majority carriers and interest.

(a) Cross-sectional View of a Surface Channel MOS-C

(b) Potentials Insider MOS-C (No Charge Packets)

(c) Potentials Insider MOS-C (With Charge Packets)

Figure 1.20 Surface Channel CCD

with the bulk generation-recombination centres. Usually, the bulk oxide traps can be more easily controlled than the silicon-silicon dioxide interface traps. For buried channel CCDs, the n-channel island is fabricated by ion implantation or epitaxial growth process, and the thickness is usually less than one micron.

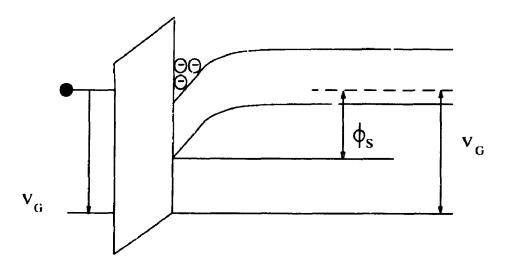

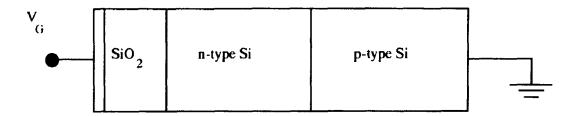

As shown in Figure 1.21, a buried channel MOS structure has a thin n-type doped layer between the oxide interface and the p-type substrate. Therefore, the potential gradient beneath the biased gate reaches a maximum value within the n layer. Photoelectrons will reside in the lowest energy state which corresponds to the bottom of the potential wells and is inside the n zone. This means that the charge consists of majority instead of minority carriers and resides in the bulk, resulting in higher device performance.

Although the bulk channel CCD increases the fabrication complexity and decreases the charge handling capacity, almost all of today's devices are BCCDs due to their enhanced performance. The characteristics of buried and surface channel CCDs are tabulated in Table 1.2.

(a) Cross-sectional View of a Bulk Channel MOS-C

(b) Potentials Insider MOS-C (No Charge Packets)

(c) Potentials Insider MOS-C (With Charge Packets)

Figure 1.21 Bulk Channel CCD

Table 1.2 Characteristics of Buried Channel and Surface Channel Structures

| Characteristic                   | Buried Channel | Surface Channel |

|----------------------------------|----------------|-----------------|

| High Transfer Efficiency         | *              |                 |

| High Operating Frequency         | *              |                 |

| Low Intrinsic Noise              | *              |                 |

| Large Charge Handling Capability |                | *               |

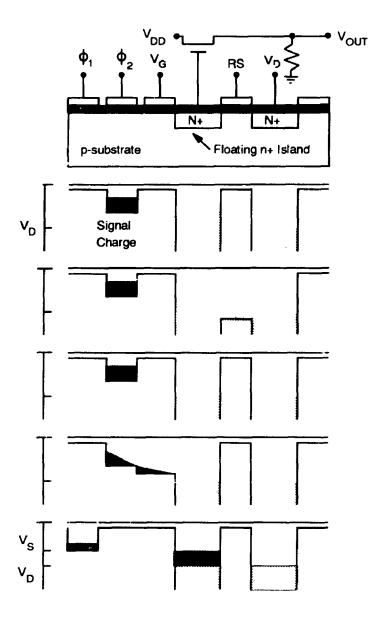

# 1.3.4 Output Structure of CCDs

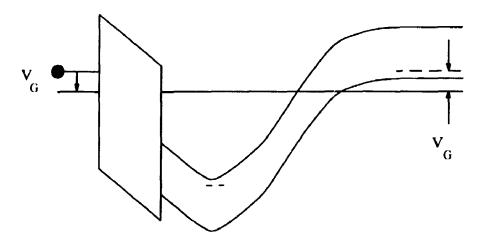

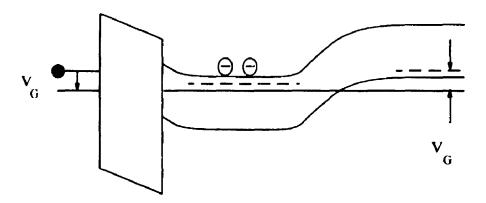

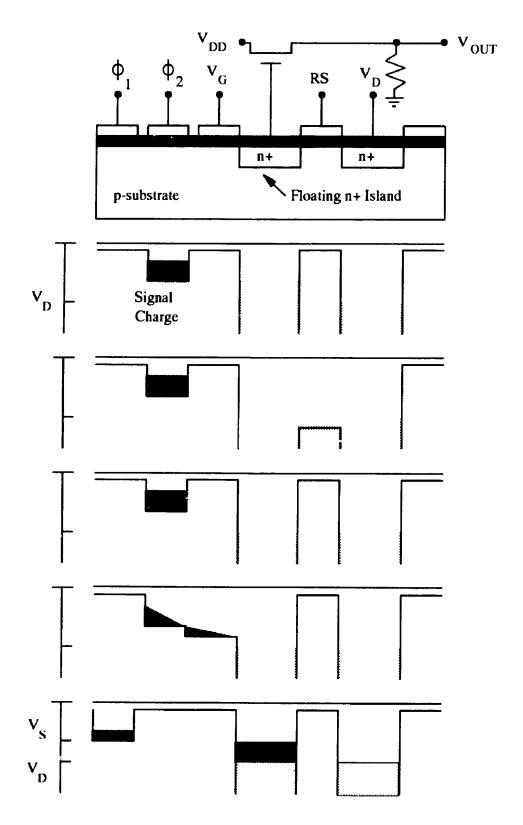

The signal charge is converted into voltage by means of a source-follower MOSFET connected to a floating n+ island. The output circuit, shown in Figure 1.22, consists of an output gate, a source-follower MOSFET connected to a floating diffusion, a reset gate (RS) and a voltage biased drain. An initial short reset pulse is applied to the reset gate to ensure the floating n+ island remains at  $V_D$ . Shortly afterwards, the surface potential of the output gate  $V_G$  is lowered to allow the signal charge to flow into the floating n+ island and is converted into a voltage by the source-follower MOSFET.

Figure 1.22 Output Structure of CCDs

#### 1.4 Summary

In principle the CCD array is a MOS structure consisting of parallel capacitors (MOS-C) with diodes at the input and output that inject or detect the capacitor charges. Since the MOS capacitor (MOS-C) is the heart of the CCD device, its thorough understanding is important. In this chapter, the device physics of a MOS-C essential for CCD operation has been discussed. The charges associated with the silicon/silicon diode interface, surface states and the bulk are also studied. For MOS-C, the gate is separated from the rest of the circuit by a gate oxide; the input capacitance is very high and can be easily damaged by Electrostatic Overstress (EOS) or Electrostatic Discharge (ESD). In fact, CCDs are classified by the DOD-HDBK-263 [5] as the most susceptible device during EOS/ESD. The configuration of CCDs is similar to that of standard MOS devices and the failure mechanisms of MOS devices are also common to CCDs. In order to fully understand the nature these failure mechanisms, one must perform experiments at the chip and device levels, i.e. CCDs with input and output pads. The performance and reliability of the I/O pads are equally as important as those of the CCDs. A more detailed discussion on the failure mechanisms of MOS devices is presented in chapter 2.

#### 1.5 Project Objectives

For a number of years, concerns have been expressed that low level electrical overstress and electrostatic discharge (EOS/ESD) can generate hidden damage in semiconductor devices. This type of "latent" damage can be defined as a flaw in the structure that is not apparent at the time of its onset, but that will reveal itself by facilitating a hard failure at a subsequent, normally nonfatal discharge stress to which the device is subjected during ordinary use. Accumulated statistical evidence supports the concerns, and mechanisms have been proposed explaining several simple types of latent damage, such as those associated with the semiconductor-dielectric interface or those related to packaging. However, explanations of the more complicated latent failure causes have remained controversial and leave much space for a more rigorous approach combining experiment and theory.

The fundamental objective of this project was to study the reliability of microelectronic structures with emphasis on latent failure mechanisms in CMOS CCDs, subjected to EOS/ESD. Since CCDs are classified as the most susceptible device during EOS/ESD, a model of the latent failure mechanism was postulated, formulated mathematically and verified by measurements in which protection circuit elements, CCDs and related designs were used as test devices. In addition, a more advanced failure analysis instrumentation method was developed to study and analyze microstructures in the failure region and their vicinity.

# Chapter 2

# Failure Mechanisms in Metal-Oxide-Semiconductor (MOS) Devices

This chapter describes various techniques used in the failure analysis of semiconductor devices. It begins with a discussion of the different failure mechanisms in semiconductor devices and the causes associated with these failures. Finally, various analytical techniques used in the experiments are presented.

#### 2.1 Introduction

Failures in electronic components are an important issue. As the trends in the technology are towards higher complexity of components, increased packaging densities and thinner dielectric layers between active elements, the demand for higher reliability becomes more and more difficult to achieve. The submicron technology design and fabrication processes have resulted in structures which are more susceptible to failures, such as thermal and voltage failure modes associated with electrostatic discharge (ESD).

In most cases, failure models are used to estimate the expected lifetime or reliability of a component. However, developing a viable reliability model is not an easy task. For example, the estimation of reliability is obtained via various modelling methods which, in turn, are based on laboratory or field data. One drawback of this analysis is that it does not provide the cause of failure and the data obtained are only as good as the failure analysis of the defective devices. Therefore, the essential

requirement of the analysis is to study the failure mechanisms of the process. By understanding the conditions and the physics of these processes, one can then improve the reliability of components.

#### 2.2 Failure Mechanisms

The failure mechanisms in semiconductor devices can be classified into three main categories, namely (1) electrical stress related failure mechanisms; (2) intrinsic failure mechanisms; (3) extrinsic failure mechanisms.

#### 2.2.1 Electrical Stress Related Failure Mechanisms

These types of failures are usually caused by electrical overstress (EOS) and electrostatic discharge (ESD). The term electrostatic discharge refers to the sudden transfer of charge between objects at different electrostatic potentials. A familiar example is the spark generated when a person walks across a synthetic carpet on a dry day and then touches a metal door knob. Although this event seems insignificant and can occur frequently, it can have serious and harmful effects on microelectronic devices. For example, studies have shown that the minimum potential for a person to feel the discharge is about 3kV; during this discharge, the energy of several hundred microjoules is transferred from the metal doorknob to the human body. If an integrated circuit is in the path of this discharge, a current of several amperes will flow through the circuit's tiny silicon junction, gate oxide and interconnections. This is more than enough to melt silicon, rapture oxide layers, fuse the interconnection aluminum metallization, cause polysilicon to evaporate, create electromigration and change the surface state of the device. EOS/ESD can cause voltage and current induced failures. Voltage induced failures can cause dielectric breakdown predominantly in MOS

devices because the inputs of MOS devices are directly connected to gates which are separated from the rest of the circuit only by a thin gate oxide. The silicon dioxide will break down when electric fields are in the 5MV/cm to 10MV/cm range. For a typical 3 micron CMOS process with a 500 Å gate oxide, the oxide breakdown voltage is between 25V to 50V (or less because of oxide imperfections). These voltages are much lower than those due to the static charge build-up in a typical working environment. On the other hand, current induced failures are dominant in bipolar devices, where EOS/ESD creates hot-spots at a particular point in a semiconductor junction, due to an increase in current flow. As the junction temperature increases resistivity decreases and more current flow results which in turn heats the junction further.

Electrostatic charge can be generated by either triboelectrification or induction processes. Triboelectric charging occurs whenever two different materials come into contact and are then separated. The amount of charge transferred after contact and separation depends on the contact potential difference which exists at the time of contact; contact potential difference is proportional to the difference in work functions. The material with the higher work function becomes negatively charged while the material with the lower work function has an equal but opposite positive charge. If the materials are insulator/insulator or insulator/metal, the charge becomes trapped in surface states near the surface of the insulator during contact. After separation, the materials are left with equal but opposite charges. However, if two metals interact no charge is trapped and no net charge remains on either metal after separation, because of the charge "backflow" process. A material at the top of the triboelectric series table,

shown in Table 2.1 [5], will tend to charge positively with respect to materials below them because of their lower work function value. From Table 2.1, it is of interest to know that both insulators and conductors can be charged.

**TABLE 2.1 Triboelectric Series**

| Material    | Polarity | Material        | Polarity |

|-------------|----------|-----------------|----------|

| Air         | +        | Sealing Wax     | <b>↓</b> |

| Human Hands |          | Hard Rubber     | <u> </u> |

| Asbestos    |          | Nickel, Cop, 3r | 1        |

| Rabbit Fur  |          | Brass, Silver   | 1        |

| Glass       |          | Gold, Platinum  | 1        |

| Mica        |          | Sulfur          |          |

| Human Hair  |          | Acetate Rayon   | l        |

| Nylon       |          | Polyester       |          |

| Wool        |          | Celluloid       |          |

| Fur         |          | Orlon           | 1        |

| Lead        |          | Saran           | l        |

| Silk        | 1        | Polyurethane    |          |

| Aluminum    | 1        | Polyethylene    |          |

| Paper       |          | Polypropylene   | 1        |

| Cotton      |          | PVC             |          |

| Steel       |          | KEL F           |          |

| Wood        | 1        | Silicon         | _ ↓      |

| Amber       | J        | Teflon          | _        |

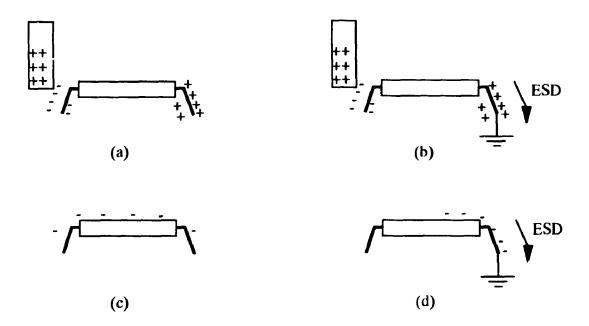

Similarly, a neutral object, such as an integrated circuit, can also become charged by induction. In this process, as shown in Figure 2.1, a neutral object is placed in an electric field produced by a static charge which residing on an insulator in the work

area. The field from this static charge will cause a charge separation on the neutral object. If the object is momentarily grounded, a discharge will occur and the object will acquire a net charge. This process will continue until the acquired net charge is dissipated into the air, or the object is grounded in a subsequent step.

Figure 2.1 Static Induction

# 2.2.1.1 Types of Electrical Stress Related Damage

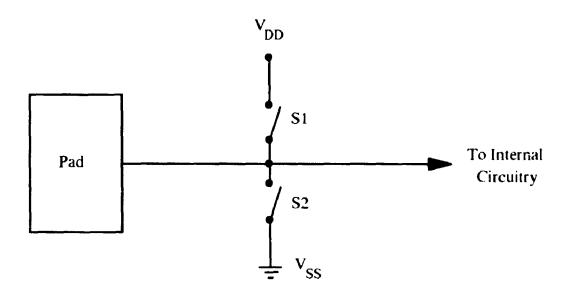

As the EOS/ESD can cause direct, indirect and latent failure in semiconductor devices [6], a protection network must be integrated with the device to provide some degree of immunity.

Direct or hard failure is defined as physical destruction or irreversible degradation of a device which results from a high amplitude current or voltage pulse during ESD.

For indirect failure, the faults, such as false triggering, are introduced as a result of conducted or radiated electromagnetic interference (EMI) from ESD. The damage is usually reversible; for example, it can be corrected by resetting the system.

Studies have shown that up to 90% of ESD damages are "soft" failures generated by a fraction of the ESD level required for direct destruction. These "soft" or "latent" failures can cause increased leakage current and reduced switching characteristics. Considerable controversy exists concerning the detection and nature of latency effects.

#### 2.2.1.1.1 Latent Failures