# Western University Scholarship@Western

Digitized Theses

**Digitized Special Collections**

1985

## Multichannel Radiofrequency Lock-in Detection For Coherent Processing Of Optical Signals

Gregory Wilson

Follow this and additional works at: https://ir.lib.uwo.ca/digitizedtheses

## Recommended Citation

Wilson, Gregory, "Multichannel Radiofrequency Lock-in Detection For Coherent Processing Of Optical Signals" (1985). Digitized Theses. 1469.

https://ir.lib.uwo.ca/digitizedtheses/1469

This Dissertation is brought to you for free and open access by the Digitized Special Collections at Scholarship@Western. It has been accepted for inclusion in Digitized Theses by an authorized administrator of Scholarship@Western. For more information, please contact tadam@uwo.ca, wlswadmin@uwo.ca.

The author of this thesis has granted The University of Western Ontario a non-exclusive license to reproduce and distribute copies of this thesis to users of Western Libraries. Copyright remains with the author.

Electronic theses and dissertations available in The University of Western Ontario's institutional repository (Scholarship@Western) are solely for the purpose of private study and research. They may not be copied or reproduced, except as permitted by copyright laws, without written authority of the copyright owner. Any commercial use or publication is strictly prohibited.

The original copyright license attesting to these terms and signed by the author of this thesis may be found in the original print version of the thesis, held by Western Libraries.

The thesis approval page signed by the examining committee may also be found in the original print version of the thesis held in Western Libraries.

Please contact Western Libraries for further information:

E-mail: <u>libadmin@uwo.ca</u>

Telephone: (519) 661-2111 Ext. 84796

Web site: <a href="http://www.lib.uwo.ca/">http://www.lib.uwo.ca/</a>

## CANADIAN THESES ON MICROFICHE

## THÈSES CANADIENNES SUR MICROFICHE

National Library of Canada Collections Development Branch

Canadian Theses on Microfiché Service

Ottawa, Canada K1A 0N4 Bibliothèque nationale du Canada Direction du développement des collections

Service des thèses canadiennes sur microfiche

#### NOTICE

The quality of this microfiche is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy

Previously copyrighted materials (journal articles, published tests, etc.) are not filmed

Reproduction in full or in part of this film is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30. Please read the authorization forms which accompany this thesis.

#### **AVIS**

La qualité de cette microfiche dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages onginales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

Les documents qui font déjà l'objet d'un droit d'auteur (articles de revue, examens publiés, etc.) ne sont pas microfilmes

La reproduction, même partielle, de ce microfilm est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c C-30 Veuillez prendre connaissance des formules d'autorisation qui accompagnent cette thèse

THIS DISSERTATION

HAS BEEN MICROFILMED

EXACTLY AS RECEIVED

LA THÈSE A ÉTÉ

MICROFILMÉE TELLE QUE

NQUS L'AVONS REÇUE

# MULTICHANNEL RADIO FREQUENCY LOCK-IN DETECTION FOR COHERENT PROCESSING OF OPTICAL SIGNALS

bу

Gregory Wilson

Faculty of Engineering Science

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Faculty of Graduate Studies

The University of Western Ontario

London, Ontario

September 1985

© Gregory Wilson 1985.

#### Abstract

The thesis deals with the extraction of weak radio frequency signals buried in noise by the technique of multichannel spectral analysis based on radio frequency lock-in detection. The technique and the developed instrument find extensive use in the fields of radio astronomy, remote sensing, and spectroscopy.

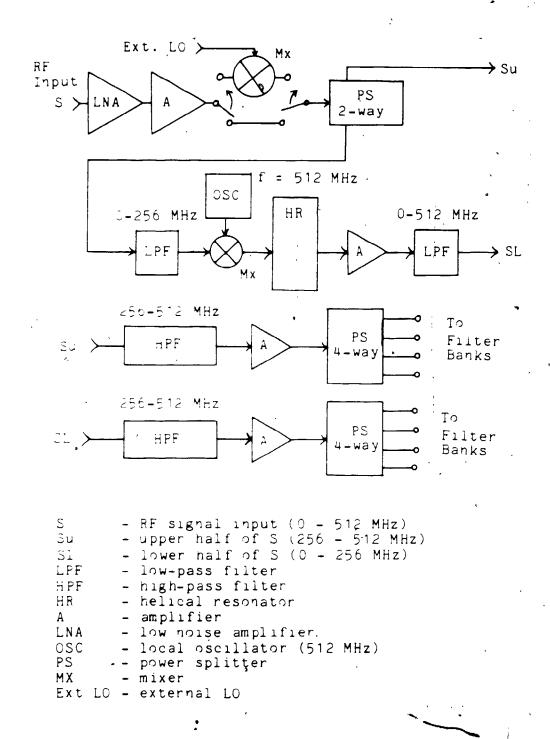

Radio frequency spectual resolution over a reception range of 0 - 512 MHz was achieved with a multichannel spectrum analyzer consisting of a radio-frequency pre-processor and a set of 64 parallel lock-in receivers. The reception range is divided uniformly into 64 evenly spaced channels of 8 MHz bandwidth. The pre-processor consists of wideband low noise amplifiers, wideband filters, RF mixing, and power splitting, providing preconditioning of the RF input signal for detection by the channel receivers. Each of the channel receivers are superheterodyne receivers and consist of a capacitively tapped strip transmission line filter, a thermally compensated square-law detector # a synchronous detector. A software controlled electronic scanner sweeps the outputs of the receivers for data acquisition to take place. System control was facilitated through a user programmable microcomputer which performs data acquisition, data preprocessing, graphic display, and tape storage.

The technique for resolving weak radio frequency signals has been improved by the application of the concepts of parallel processing, modularity, and symmetry.

The concepts of parallel processing as applied to RF processing of weak signals were successfully employed in the multichannel spectrum analyzer. The resulting system is characterized by reduced hardware complexity, low-noise electronic circuitry, and improved reliability. The concepts of modularity and symmetry proved advantageous in reducing design and hardware development time.

The channel receiver is a novel design based on the principles of superheterodyne reception incorporating improved detection stages. A dual square-law detection scheme for thermal compensation significantly reduced the problem of thermal drift. The gated synchronous detector scheme eliminated contaminating noise that was asynchronous with the chopping signal and also chopper transition noise.

The minimum detectable power across all channels was measured to be -138 dBm + 1 dB. In addition, across all channels, a noise figure of  $3.05 \pm 0.3 \text{ dB}$  and a receiver noise temperature of  $306 \pm 43 \text{ K}$  was measured. Through software control, the system can perform auto-calibration, address any combination of receivers, perform preprocessing of data for graphical display, and perform digital integration for extended periods of time.

## Acknowledgements

I would like to thank my supervisor, Dr. Z. Kucerovsky, for his guidance and support throughout this work.

I would like to thank Dr. E. Brannen of the Department of Physics for his continuing interest and support.

I would like to express my sincere appreciation to my loving wife, Julie, who devoted countless hours in the construction, testing, and typing phases of the project. Completion of my graduate work was only possible with her continuing patience and encouragement.

## Table of Contents

| ,        | , •      |                                       | Page |

|----------|----------|---------------------------------------|------|

| CERTIFIC | ATE OF   | EXAMINATION                           | ii   |

| ABSTRACT | ı        | •                                     | iii  |

| ACKNOWLE | DG EMEN' | rs , , ,                              | ٠V   |

| TABLE OF | CONTE    | NTS                                   | νi   |

| LIST OF  | TABLES   | •                                     | iх   |

| LIST OF  | FIGURE:  | 5                                     | x    |

| LIST OF  | APPEND:  | ICES                                  | xvi  |

| GLOSSARY | OF SY    | MBOLS AND ABBREVIATIONS               | xvii |

| CHAPTER  | 1        | RECEPTION OF SPECTRALLY RESOLVED      |      |

| *        |          | SIGNALS                               | 1    |

|          | 1.1      | Introduction                          | 1    |

| CHAPTER  | 2        | THE MULTICHANNEL SPECTRUM ANALYZER    |      |

|          |          | SYSTEM                                | 12   |

|          | 2.1      |                                       | 12   |

|          |          | Swept Spectrum Analyzers              | 21   |

|          | 2.3      | Lock-in Amplification                 | 2 4  |

| CHAPTER  | 3        | OVERVIEW OF THE MULTICHANNEL SPECTRUM |      |

|          |          | ANALYZER                              | 3 0  |

|          | 3.1      | Noise, Shielding, and Ground          | ,    |

|          |          | Considerations                        | 3 0  |

|          | 3.2      | Front-end Module                      | 43   |

|          | 3.3      | Filter Bank Realization               | 5 2  |

|          | 3.4      | Channel Receiver Operation            | 55   |

|          | 3.5      |                                       | 68   |

|          | 3.6      |                                       |      |

|          |          | Multiplier Operation                  | 7.5  |

|          | 3.7      |                                       | 80   |

|          |          | Overview of the Microcomputer System  | 8.3  |

| •        | 3.9      |                                       |      |

| •        |          | Board                                 | 86   |

|          |          | Overview of the Input/Output Board    | 88   |

| •        | 3.11     | _                                     |      |

|          |          | Board                                 | 90   |

|          | 3.12     | Overview of the Erasable Programmable |      |

|          | 2 22     | Read-only Memory Board                | 92   |

|          | 3.13     | Overview of the Controller Board      | 9 4  |

| •        | 3.14     | Overview of the Analog*to-Digital     |      |

|          | 2 15     | Converter Board                       | 96   |

| •        | 3.15     | Overview of the Real Time Clock and   |      |

|          |          | Programmable Timer Module Board       | 98   |

|          | 3.16     | Software Considerations               | 100  |

| CHAPTER  | 4 ·      | IMPLEMENTATION OF THE MULTICHANNEL    |      |

|          |          | SPECTRUM ANALYZER                     | 103  |

|          | 4:1      | Shielding and Grounding               | 103  |

| ,        | 4 2      | Front-end Module                      | 107  |

|         | 4.3        | Filters Banks and Channel Filters       | 118  |

|---------|------------|-----------------------------------------|------|

|         | 4.4        |                                         | 122  |

|         |            | Synchronous Detector                    | 130  |

|         |            | Local Oscillator and Frequency          |      |

|         |            | Multiplier                              | 136  |

|         | 4.7        | Front-end Local Oscillator              | 147  |

| ,       | 4.8        | Microcomputer System                    | 152  |

|         |            | Central Processing Unit Board           | 154  |

|         |            | Input/Output Board                      | 156  |

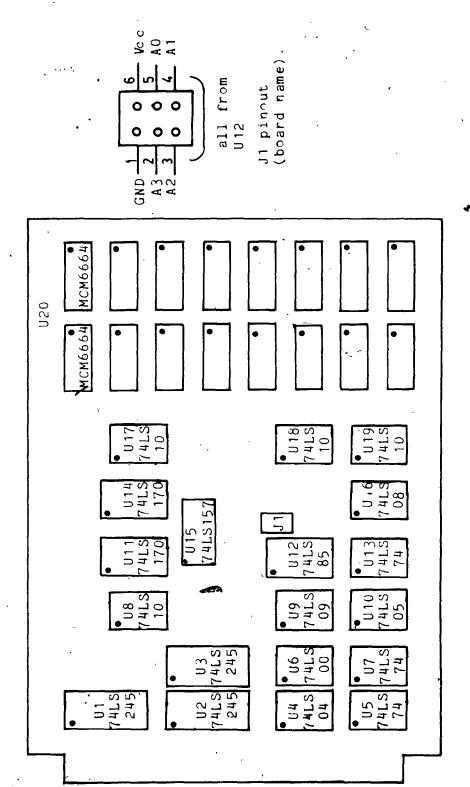

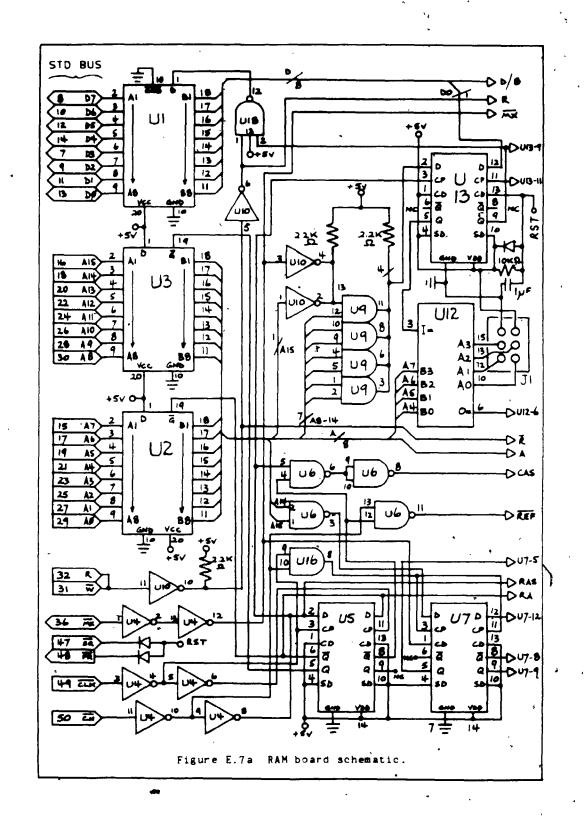

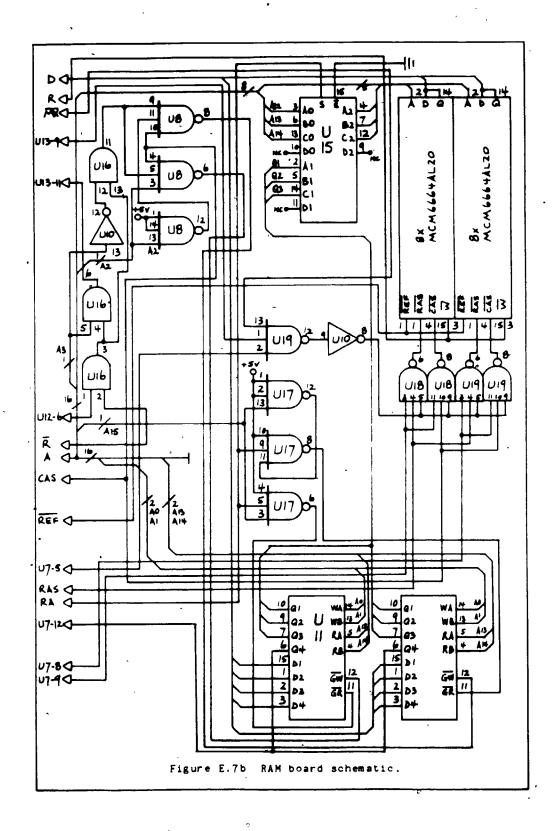

| 1       |            | Random Access Memory Board              | 15.8 |

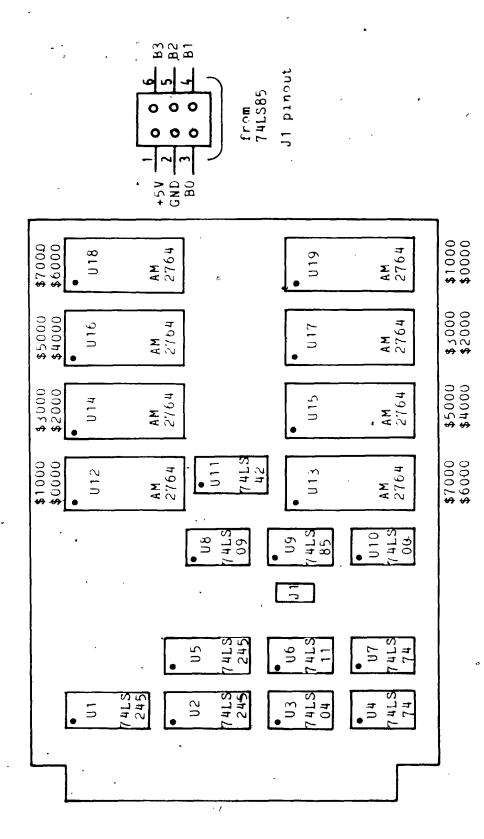

|         |            | Erasable Programmable Read-only Memory  |      |

| •       |            | Board                                   | 159  |

|         | 4.13       | Controller Board                        | 160  |

|         | 4.14       | Analog-to-Digital Conversion Board      | 162  |

|         | 4.15       | Real Time Clock and Programmable Timer  |      |

|         |            | Module Board                            | 164  |

| ,       | 4.16       | Software Implementation                 | 165  |

|         | •,         | •                                       |      |

| CHAPTER | 5          | SYSTEM TESTS AND CALIBRATIONS           | 169  |

|         |            | Front-end Module Tests and              |      |

|         |            | Calibrations                            | 169  |

|         | 5.2        | Filter Bank and Channel Filter Tests    |      |

|         | •          | and Results                             | 187  |

|         | 5.3 .      | Channel Receiver Tests and Results      | 200  |

|         |            | Synchronous Detector Tests and Results  | 209  |

| •       |            | Local Oscillator and Frequency          |      |

|         | 7          | Multiplier                              | 213  |

| -       | 5.6        |                                         |      |

|         |            | and Results                             | 216  |

|         | 5.7        |                                         |      |

|         | , -        | and Results                             | 218  |

|         | 5.8        | System Tests and Results                | 220  |

|         |            |                                         |      |

| CHAPTER | 6          | AN OPTICAL HETERODYNE SPECTROMETER      | 239  |

|         | 6.1        | Introduction                            | 239  |

|         | 6.2        | Method                                  | 243  |

|         | 6.3        | Results and Discussion                  | 248  |

|         |            |                                         |      |

| CHAPTER | · 7        | DISCUSSION OF THE MULTICHANNEL SPECTRUM |      |

|         |            | ANALYZER                                | 253  |

|         | 7.1        | Discussion of System Concepts           | 253  |

|         | 7.2        | Discussion of the RF Subsystems         | 258  |

| •       | 7.3        | Discussion of the Detection Subsystem   | 263  |

|         | 7.4        | Discussion of the Data Acquisition      |      |

|         |            | System and Microcomputer System         | 265  |

| •       | •          |                                         |      |

| CHAPTER | 8          | CONCLUSIONS                             | 267  |

|         | <b>9</b> 1 | Conclusions                             | 267  |

| APPENDICES |   |   | 272 |

|------------|---|---|-----|

| REFERENCES |   |   | 327 |

| VITÅ       | * | ř | 331 |

# List of Tables

| Table | Description                                                                                  | Page    |

|-------|----------------------------------------------------------------------------------------------|---------|

| 3.1   | Channel numbers tabulated with channel addresses, centre frequencies, and local oscillators. | ,<br>57 |

| 3.2   | Components of the Diode Equation.                                                            | 63      |

| 4.1   | Filter Bank Component Values.                                                                | 120     |

| B.1   | RF Transistor (2N3866) Characteristics.                                                      | 276     |

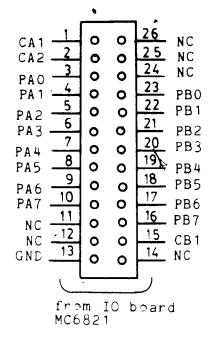

| E.1   | Pin designations of STD bus.                                                                 | 284     |

| F.1   | List of FORTH Routines According to Type.                                                    | 315     |

| F.2   | List of FORTH Routines in Dictionary.                                                        | 316     |

## List of Figures

| F    | igure | Description                                                         | Page ·      |

|------|-------|---------------------------------------------------------------------|-------------|

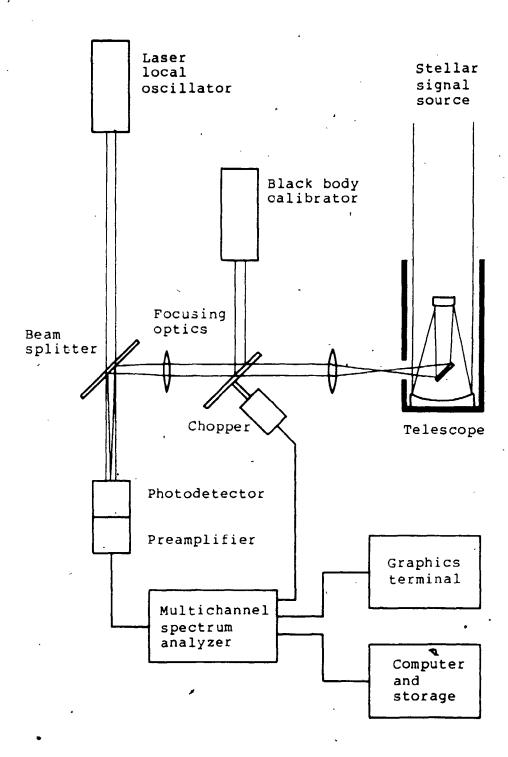

|      | 1.1   | An Optical Heterodyne Spectrometer                                  | 2           |

|      | 2.1   | The Multichannel Spectrum Analyzer System.                          | 14 🖔        |

|      | 2.2   | Block Diagram of Lock-in Amplifier.                                 | 26          |

|      | 3.1   | Electromagnetic interference in a common heterodyne radio receiver. | 31          |

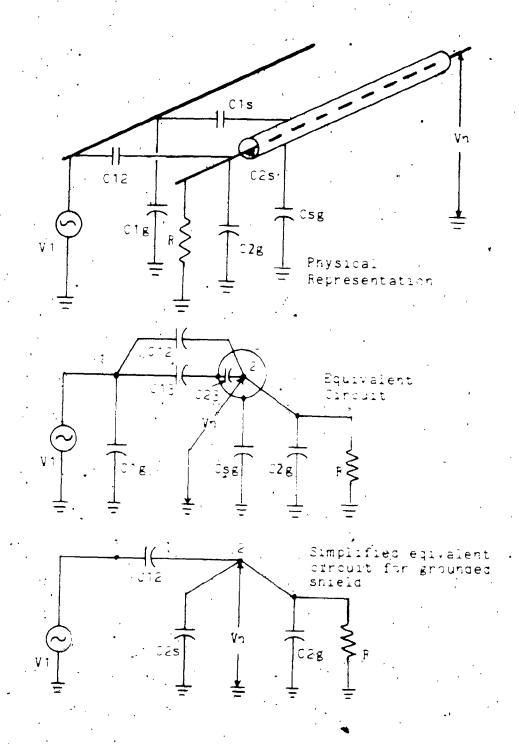

|      | 3.2   | Capacitive coupling between a conductor and a shielded conductor.   | <b>34</b> ′ |

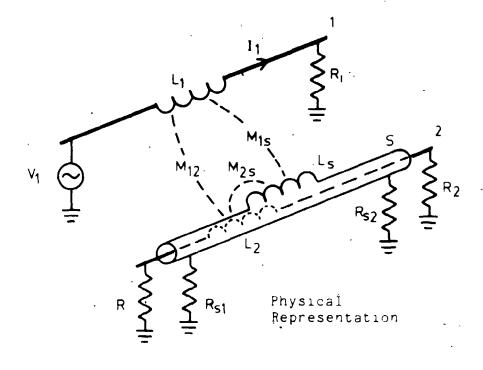

|      | 3.3   | Magnetic coupling between a conductor and a shielded conductor.     | 36          |

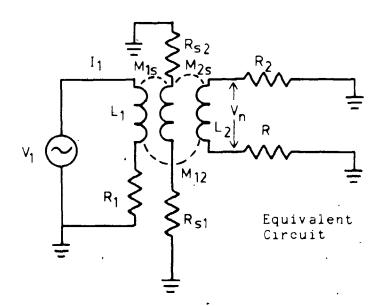

|      | 3.4   | Front-end of the MCSA.                                              | 44          |

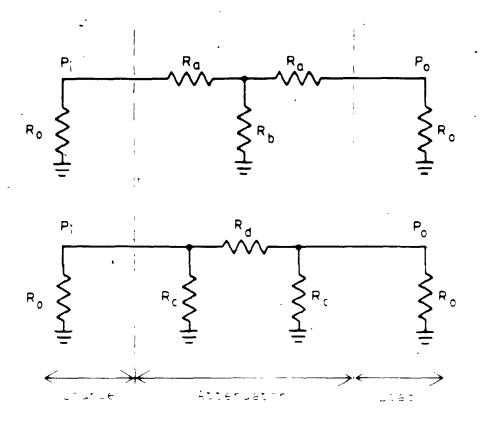

|      | 3.5   | 'T' and ' $\pi$ ' attenuator design.                                | 48          |

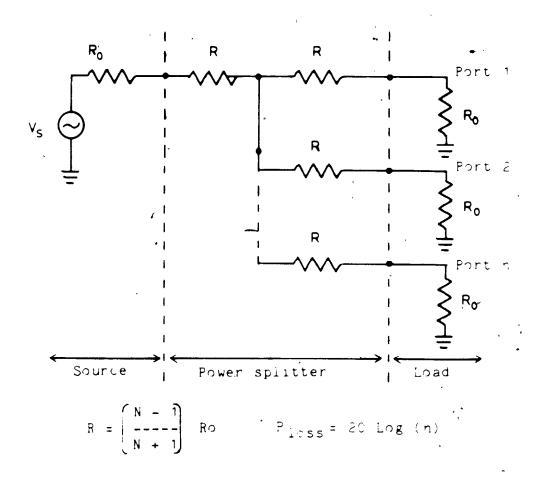

|      | 3.6   | Resistive power splitter design.                                    | 51          |

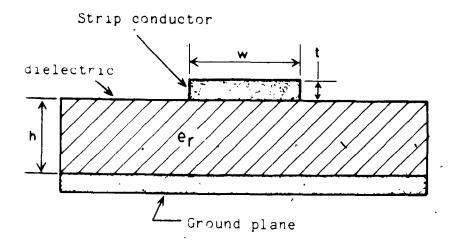

| d in | 3.7   | Strip transmission line cross-section and characteristic impedance. | 5 <b>4</b>  |

|      | 3.8   | Receiver functional block diagram.                                  | 56          |

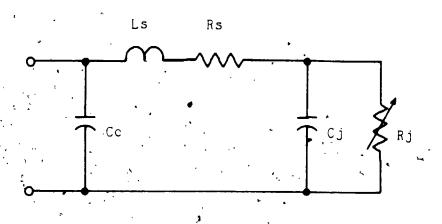

|      | 3.9   | Equivalent circuit for Schottky diode.                              | 64          |

|      | 3.10  | Dicke receiver.                                                     | 69          |

|      | 3.11  | Synchronous detector block diagram.                                 | 74          |

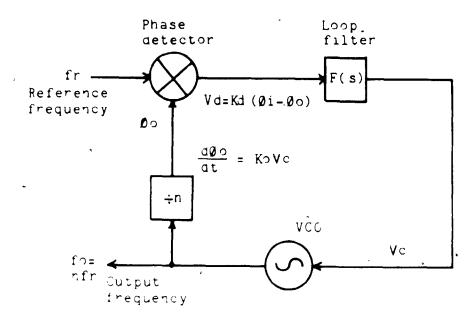

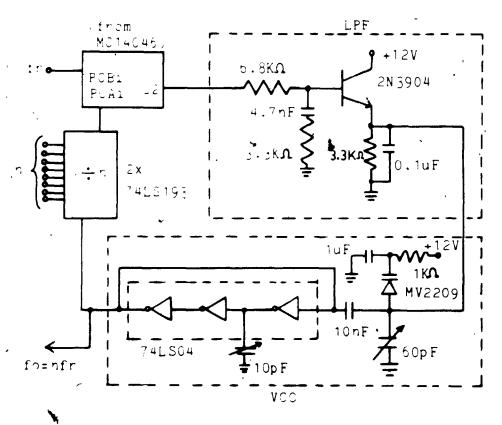

|      | 3.12  | Local oscillator synthesis block diagram.                           | 76          |

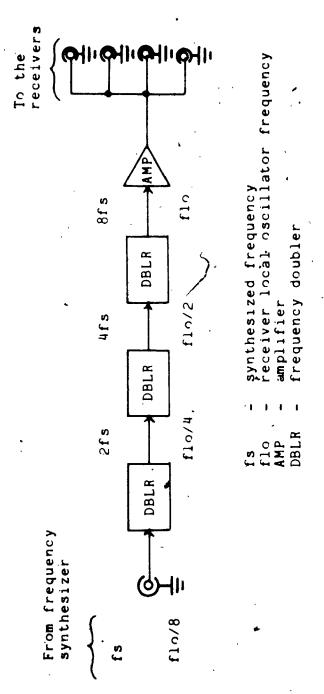

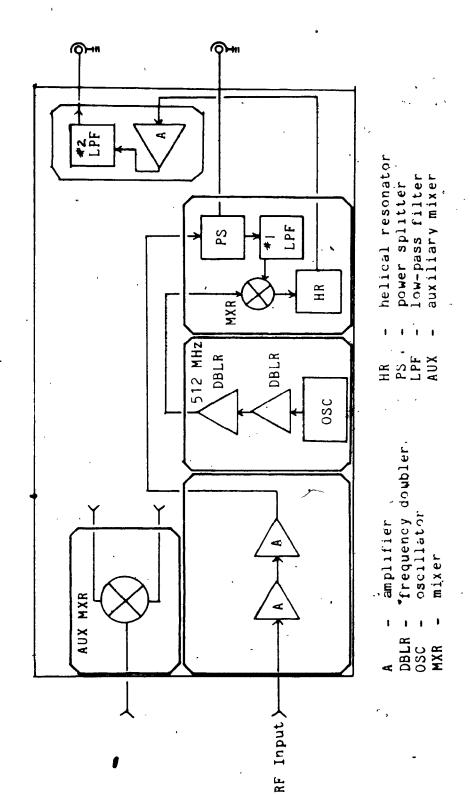

|      | 3.13  | Frequency multiplier block diagram.                                 | 79          |

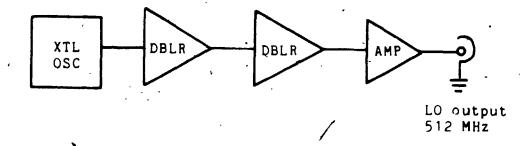

|      | 3.14  | Front-end local oscillator block diagram.                           | 81          |

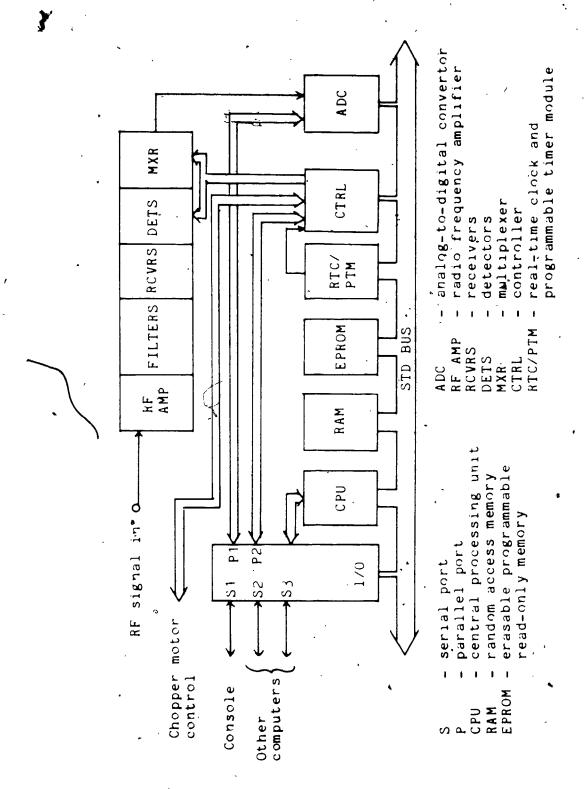

|      | 3.15  | Block diagram of microcomputer with RF portion of MCSA.             | 84          |

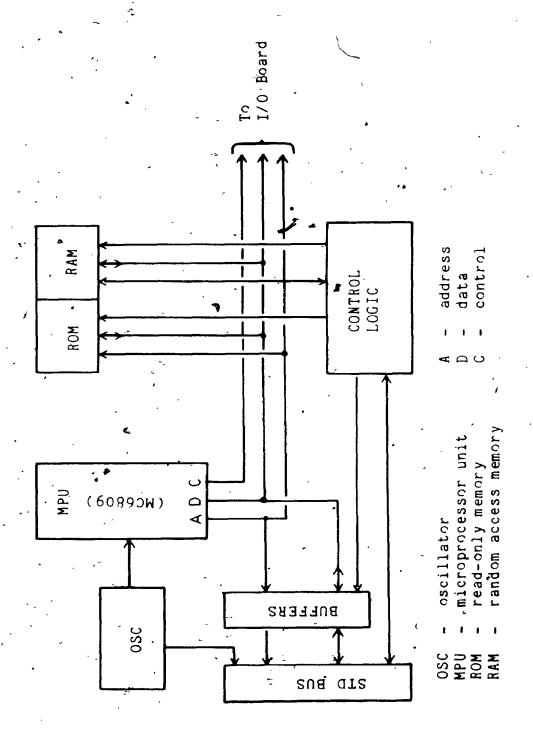

|      | 3.16  | Block diagram of CPU board.                                         | 8 7         |

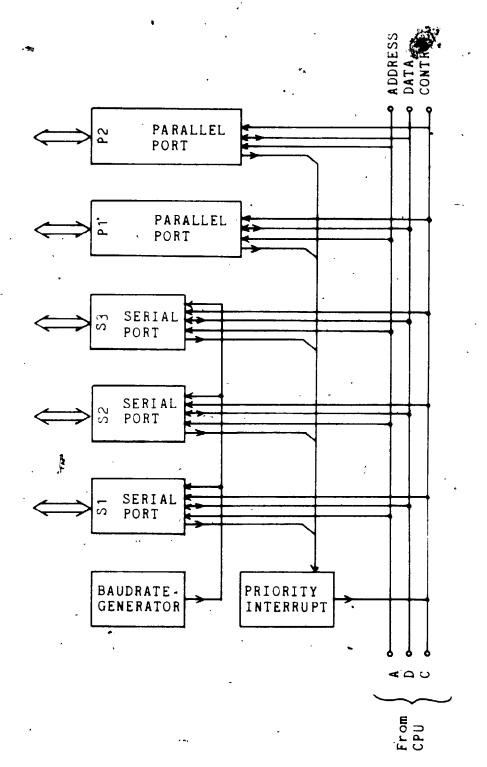

|      | 3.17  | Block diagram of I/O board.                                         | 89          |

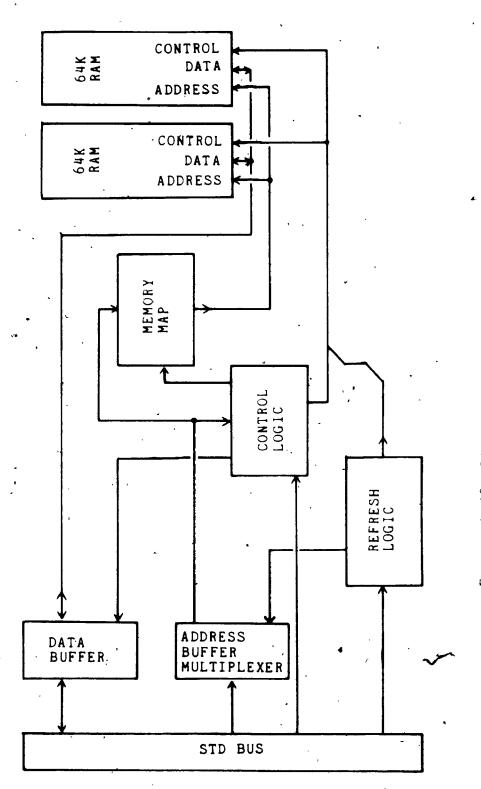

|      | 3.18  | Block diagram of RAM board.                                         | 91          |

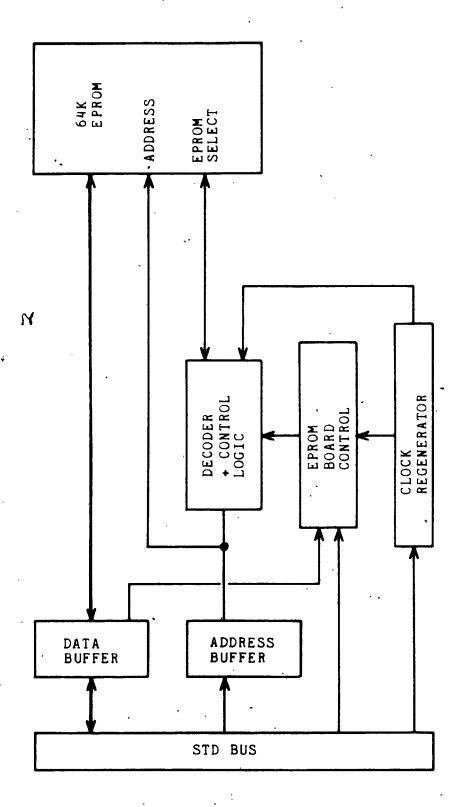

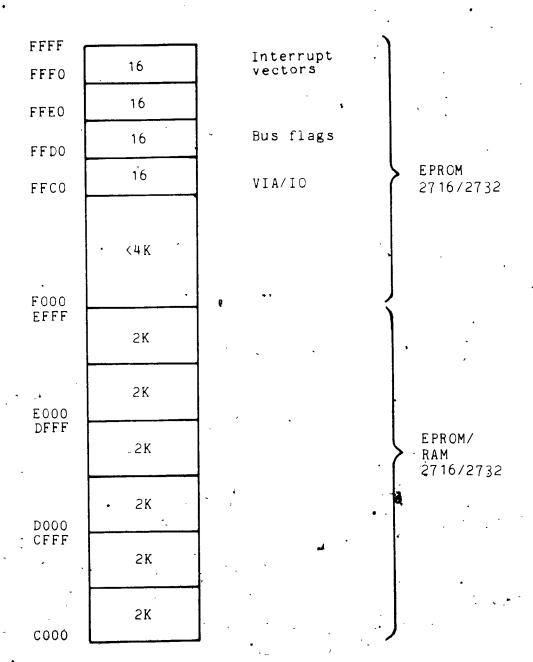

|      | 3.19  | Block diagram of EPROM board.                                       | 9'3         |

Ÿ

| 3.20  | Block diagram of controller board.                                             | 95          |

|-------|--------------------------------------------------------------------------------|-------------|

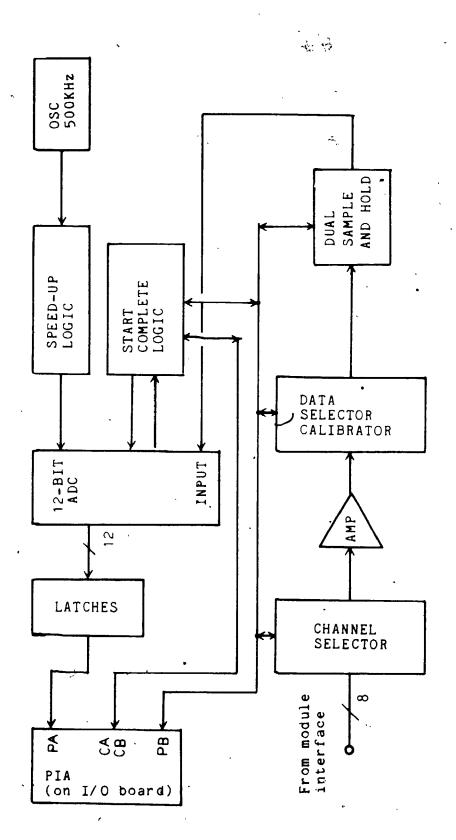

| 3.21  | Block diagram of ABC board.                                                    | 97          |

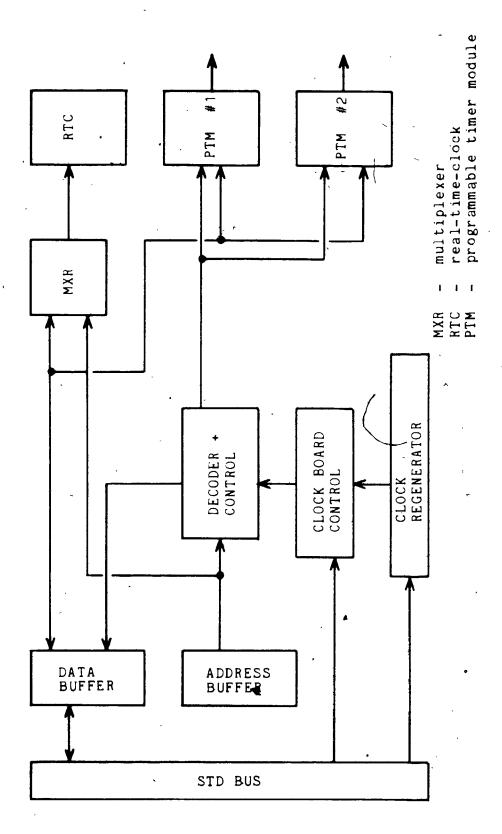

| 3.22  | Block diagram of RTC/PTM board.                                                | 99          |

| 4,1   | Hardware layout of the first section of front-end module.                      | 109         |

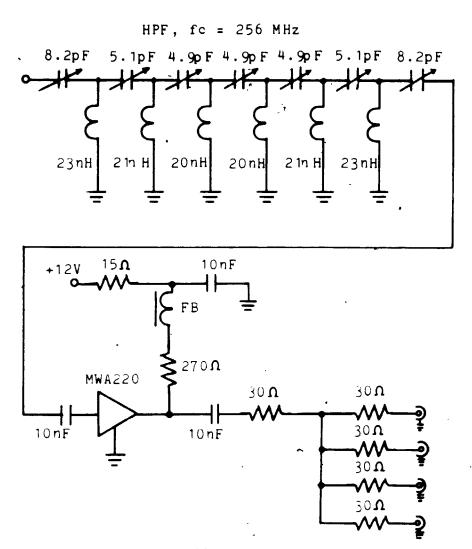

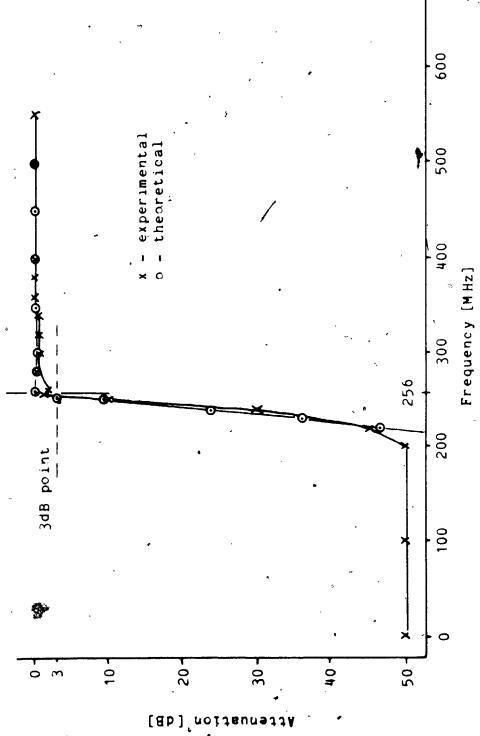

| 4.2   | Low-pass filter schematic (fc = 256 MHz).                                      | <b>i</b> 11 |

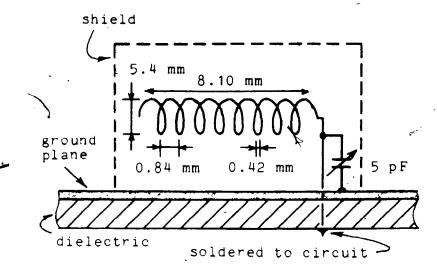

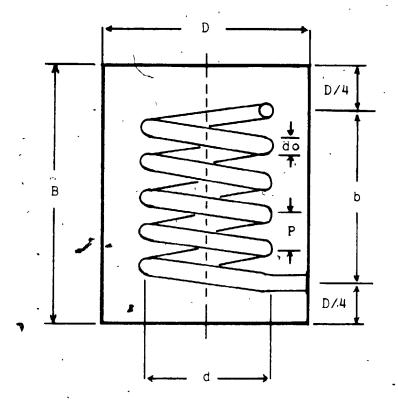

| 4.3a  | Helical resonator structure.                                                   | -113        |

| 4:3b  | Frequency response of the helical resonator.                                   | 113         |

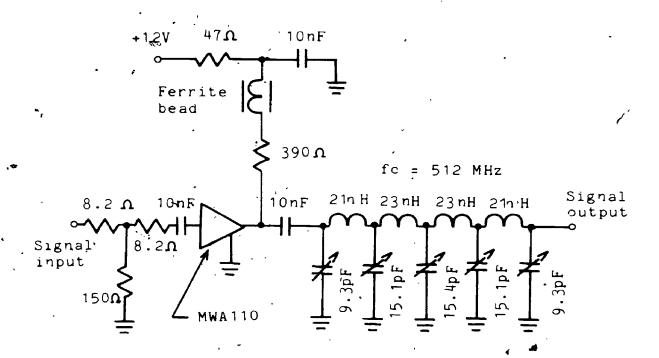

| 4.4   | Buffer amplifier and low-pass filter for a lower half of signal spectrum.      | 115         |

| 4.5   | Schematic of second section of front-end module.                               | *117        |

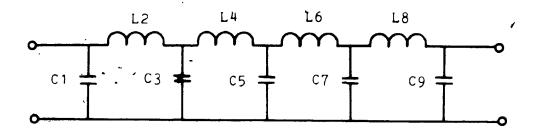

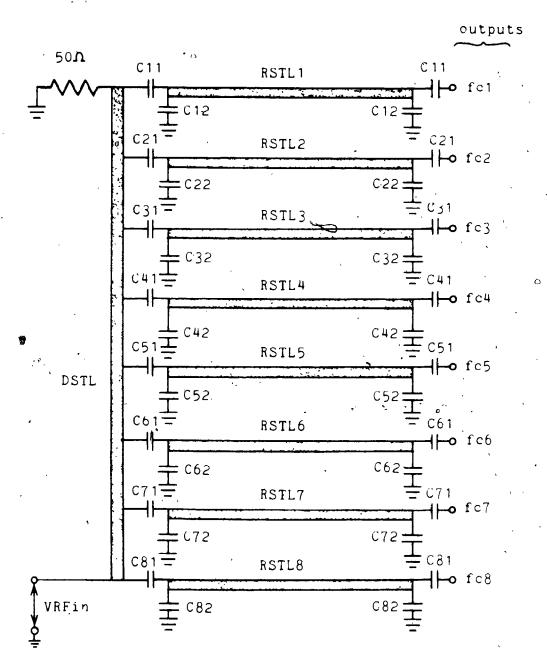

| 4.6   | Filter bank structure.                                                         | 119         |

| 4.7   | Hardware layout of receiver module.                                            | 123         |

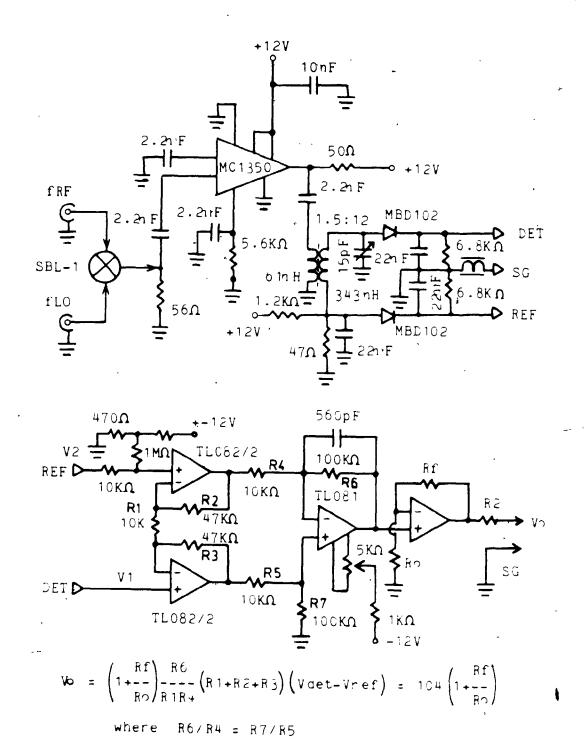

| 4.8   | Schematic of channel receiver.                                                 | 126         |

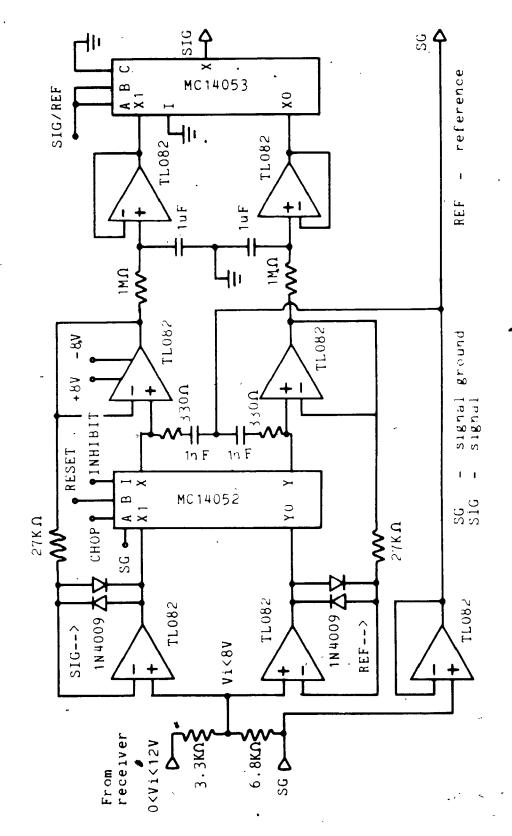

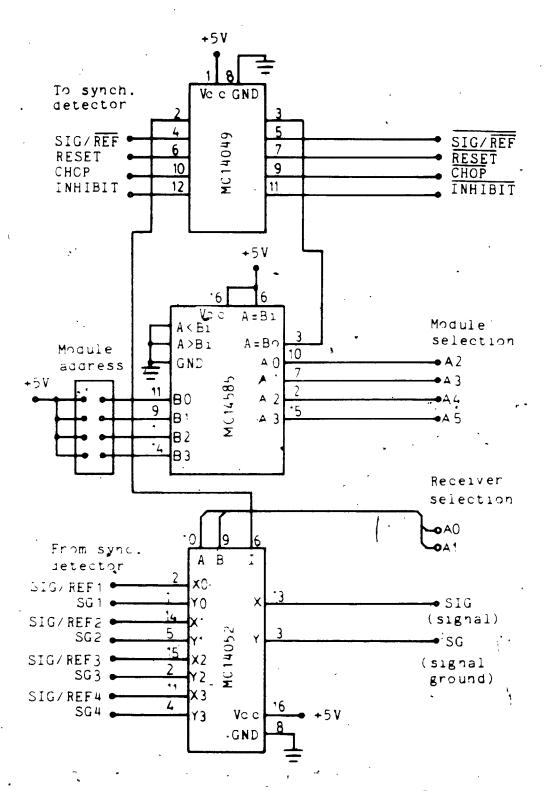

| 4.9   | Synchronous detector schematic.                                                | 131         |

| 4.10  | Receiver module interface.                                                     | 135         |

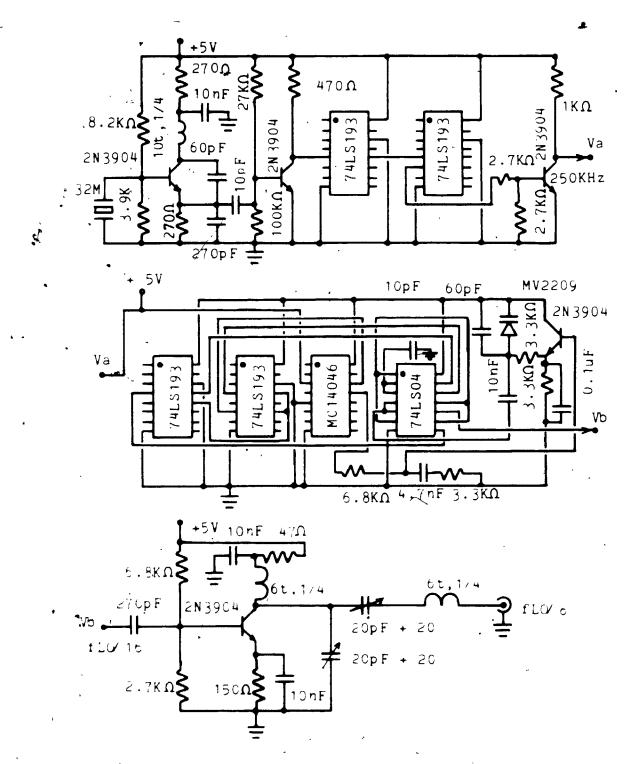

| 4.11  | Frequency synthesizer schematic.                                               | 137         |

| 4.12a | Theoretical frequency synthesizer.                                             | . 139       |

| 4.12b | Frequency synthesizer implementation.                                          | 139         |

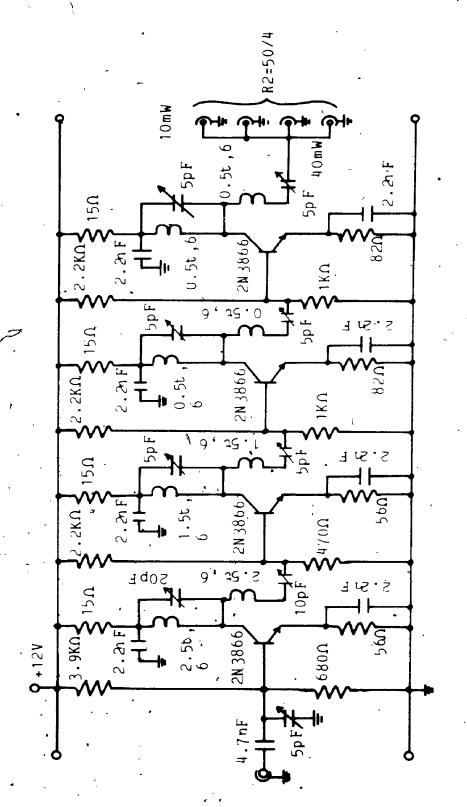

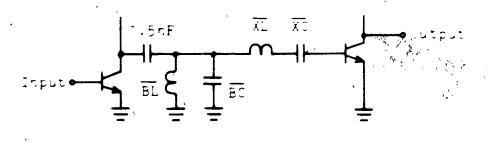

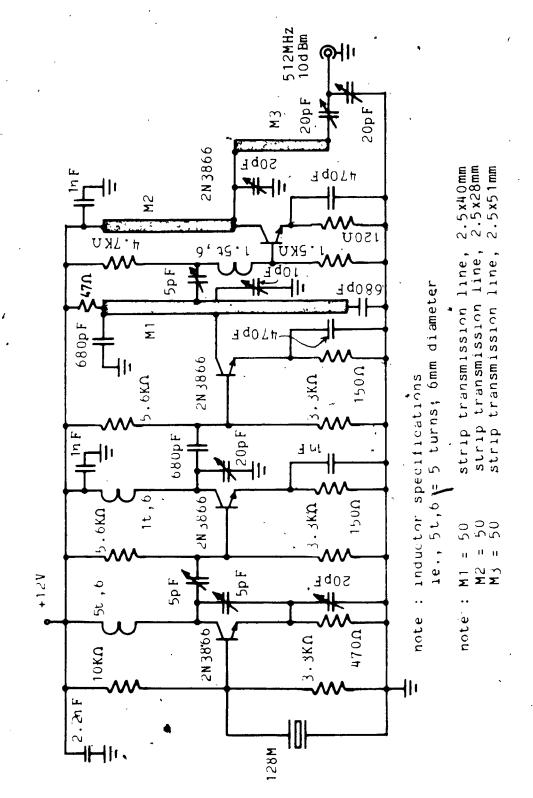

| 4.13  | Frequency multiplier schematic.                                                | 143         |

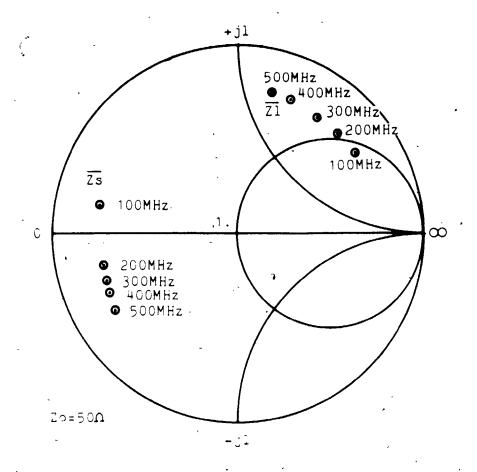

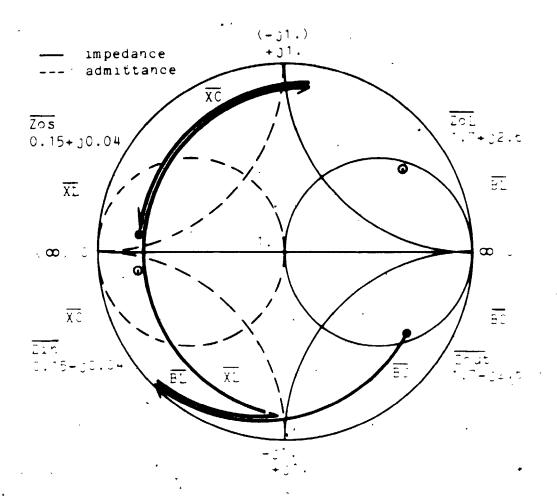

| 4.14  | Optimum load and source impedances for 2N3866.                                 | 145         |

| 4.15  | Impedance matching of a 2N3866 on a combined impedance-admittance Smith-chart. | 146         |

| 4.16  | Front-end local oscillator schematic.                                          | 148         |

| 4.17  | CPU board memory map.                                                          | 166         |

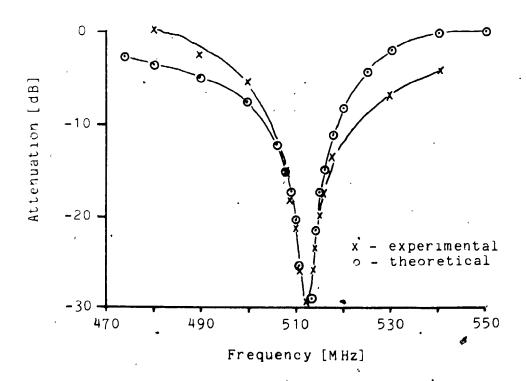

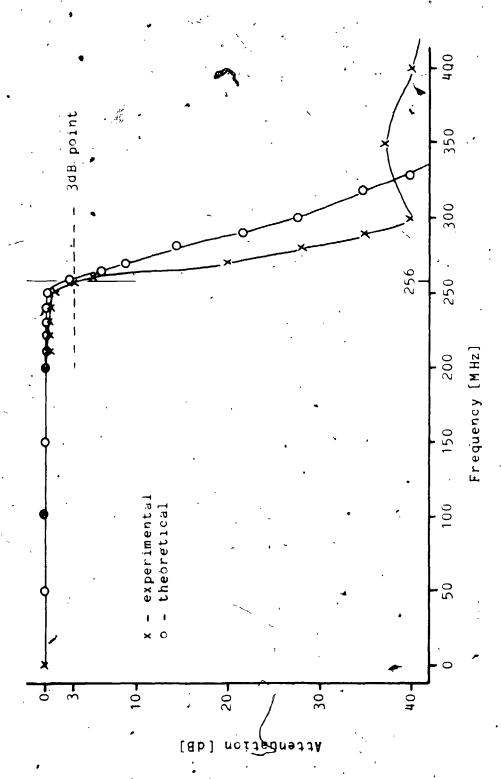

| 5.1   | Low-pass filter response ( $f_c = 256 \text{ MHz}$ ).                          | . 171       |

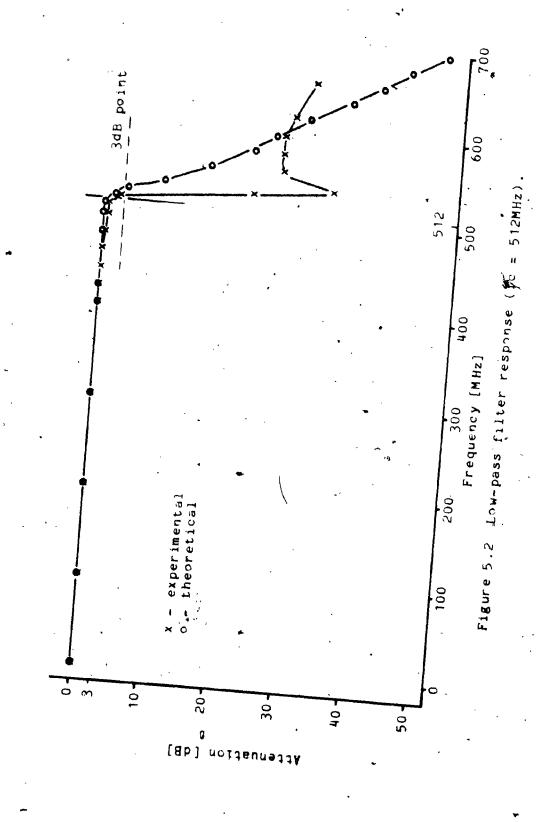

| 5 2   | Now-nace filter response (f = 512 MHz)                                         | 176         |

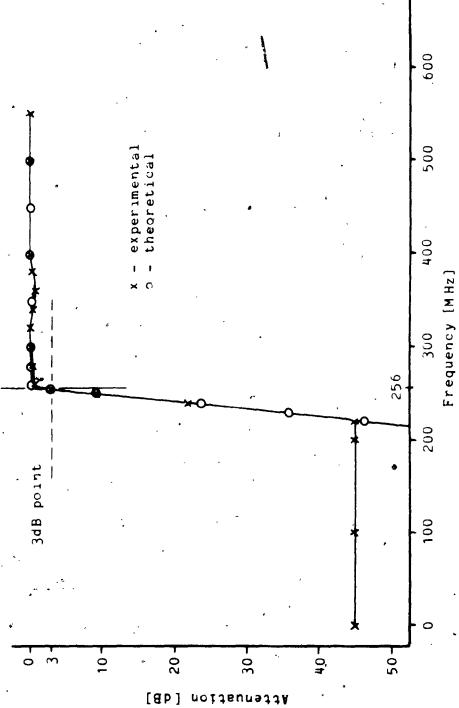

| 5.3      | High-pass filter response for lower half of signal spectrum ( $f_c = 256 \text{ MHz}$ ).                             | 178  |

|----------|----------------------------------------------------------------------------------------------------------------------|------|

| 5.4      | High-pass filter response for upper half of signal spectrum ( $f_c = 256 \text{ MHz}$ ).                             | 179  |

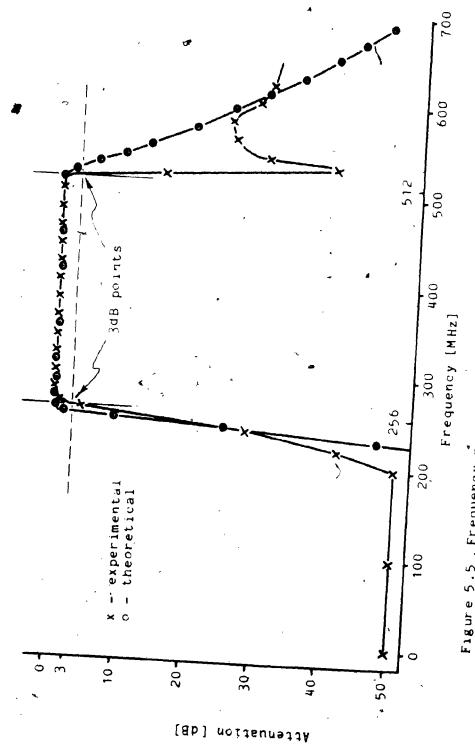

| 5.5      | Frequency response of combined low-pass and high-pass filter (f <sub>cl</sub> = 512 MHz, f <sub>ch</sub> = 256 MHz). | 180  |

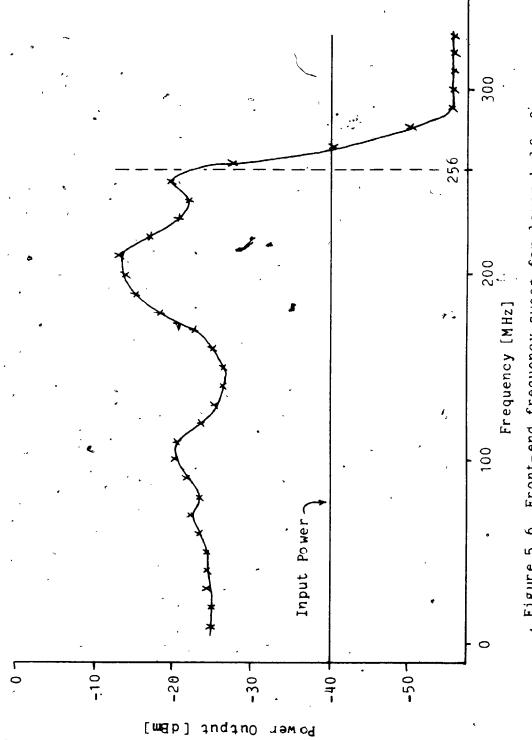

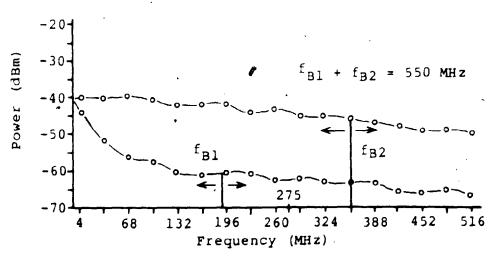

| 5.6      | Front-end frequency sweep for lower half of signal spectrum.                                                         | 184  |

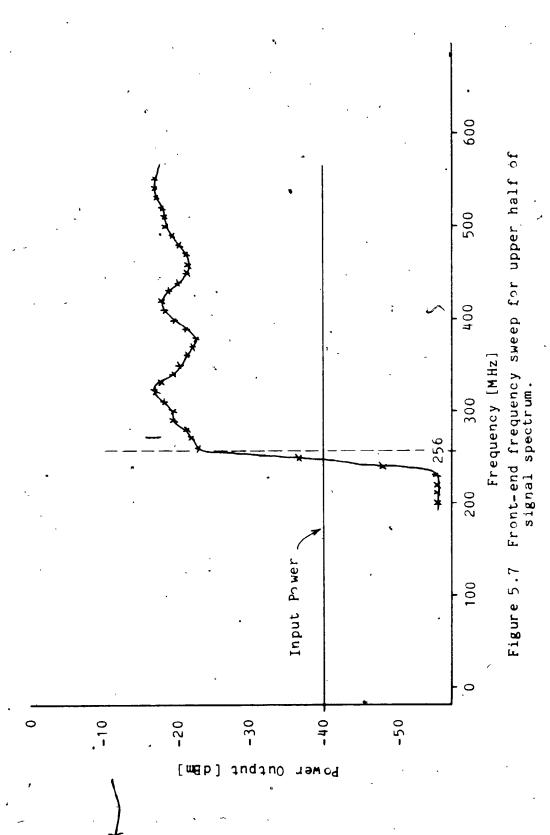

| 5.7      | Front-end frequency sweep for upper half of signal spectrum.                                                         | 185  |

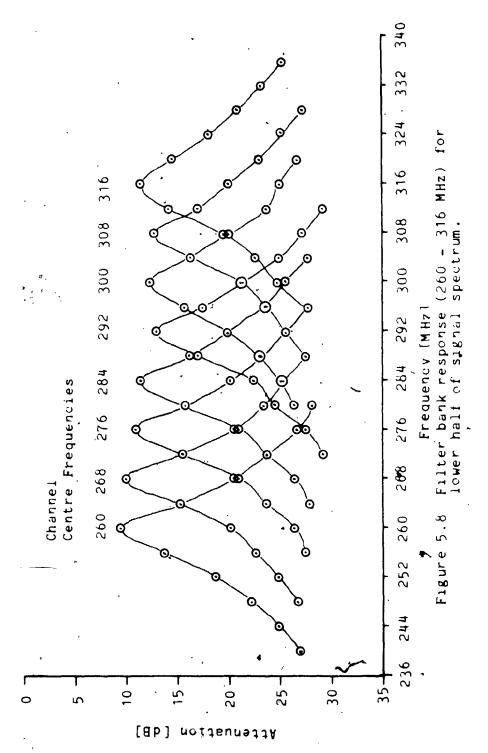

| 5.8      | Filter bank response (260 - 316 MHz) for lower half of signal spectrum.                                              | 188  |

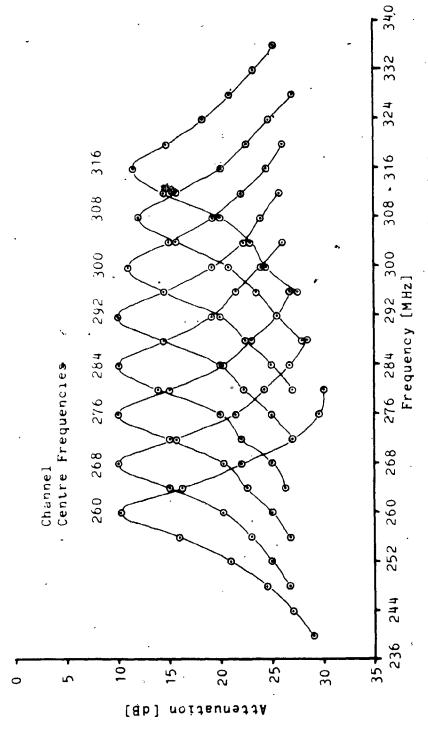

| 5.9      | Filter bank response (260 - 316 MHz) for upper half of signal spectrum.                                              | 189  |

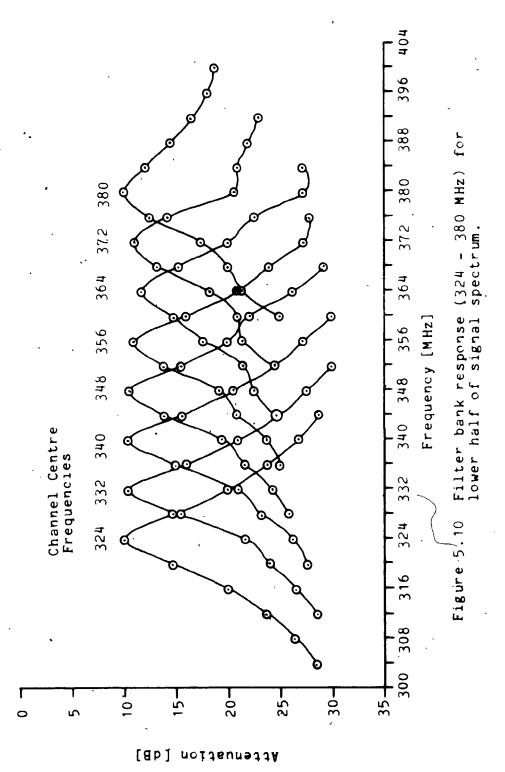

| 5.10     | Filter bank response (324 - 380 MHz) for lower half of signal spectrum.                                              | 190  |

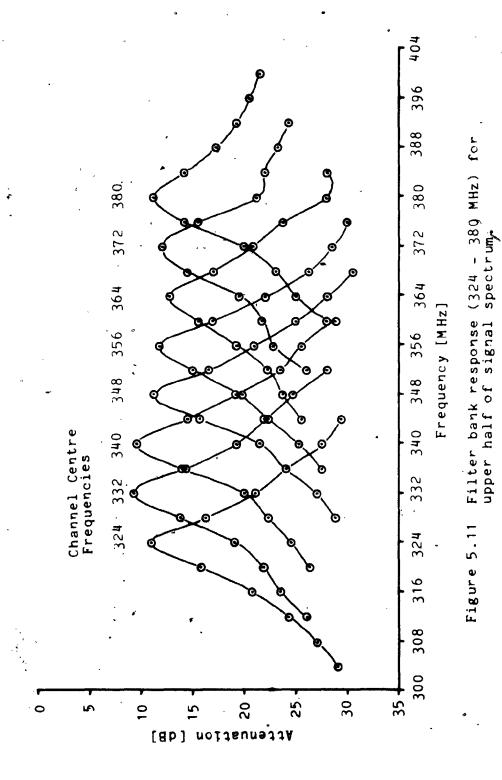

| 5.11     | Filter bank response (324 - 380 MHz) for upper half of signal spectrum,                                              | 191  |

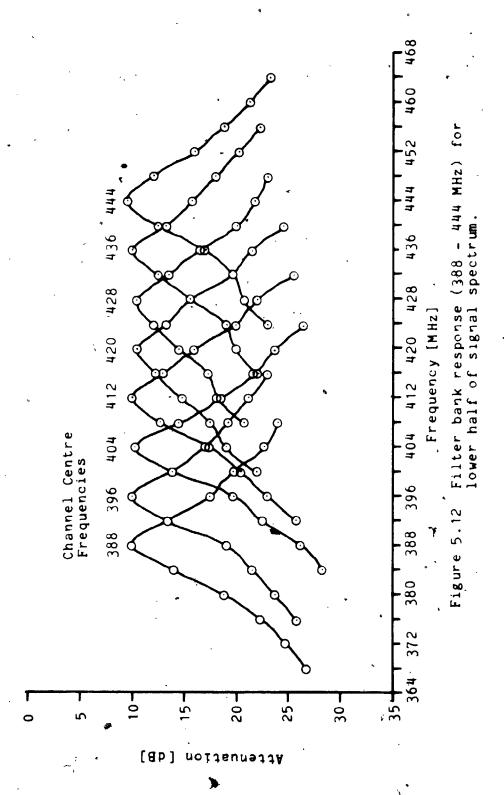

| 5.12     | Filter bank response (388 - 444 MHz) for lower half of signal spectrum.                                              | ĺ92  |

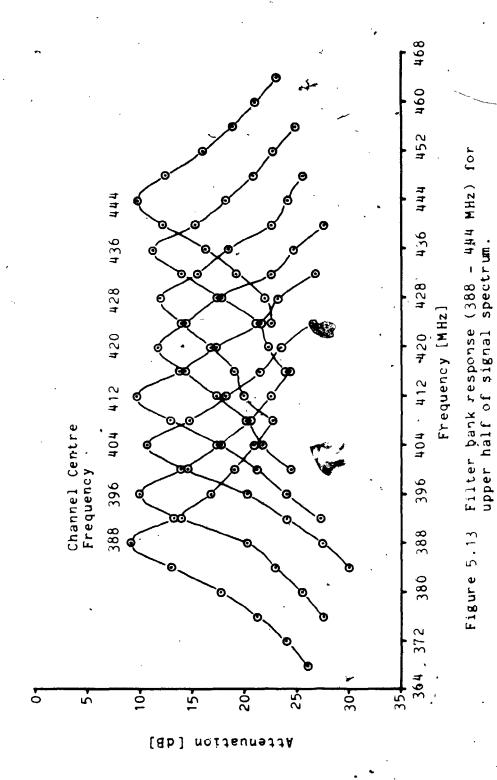

| 5.13     | Filter bank response (388 - 444 MHz) for upper half of signal spectrum.                                              | 193  |

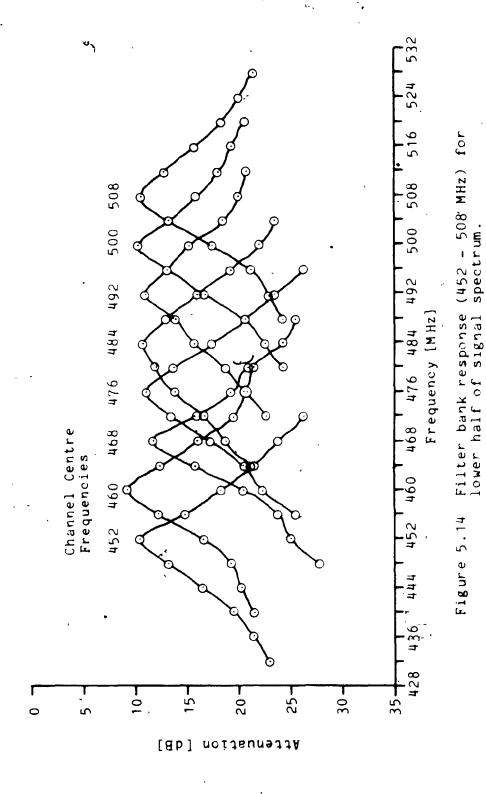

| 5.14     | Filter bank response (452 - 508 MHz) for lower half of signal spectrum.                                              | 194  |

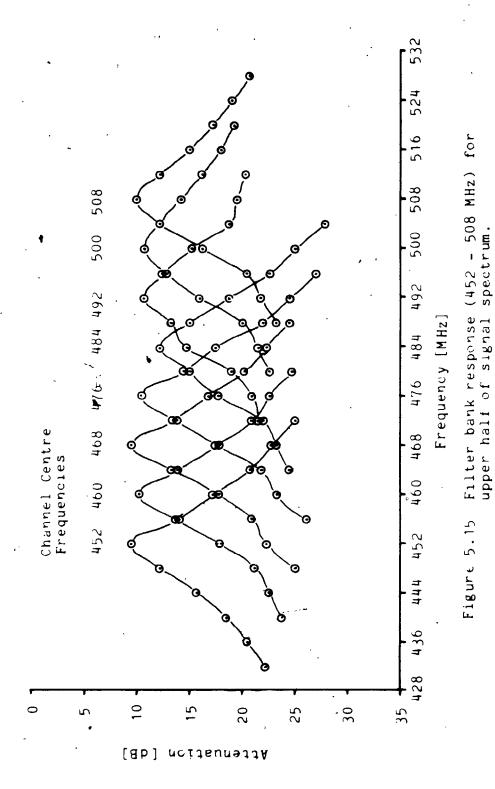

| 5.15     | Filter bank response (452 - 508 MHz) for upper half of signal spectrum.                                              | 195  |

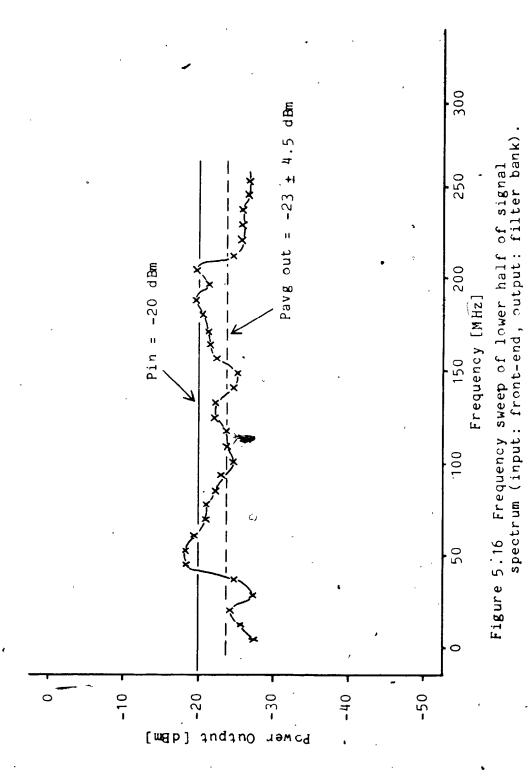

| 5.16     | Frequency sweep of the lower half of signal spectrum (output: filter bank).                                          | 197  |

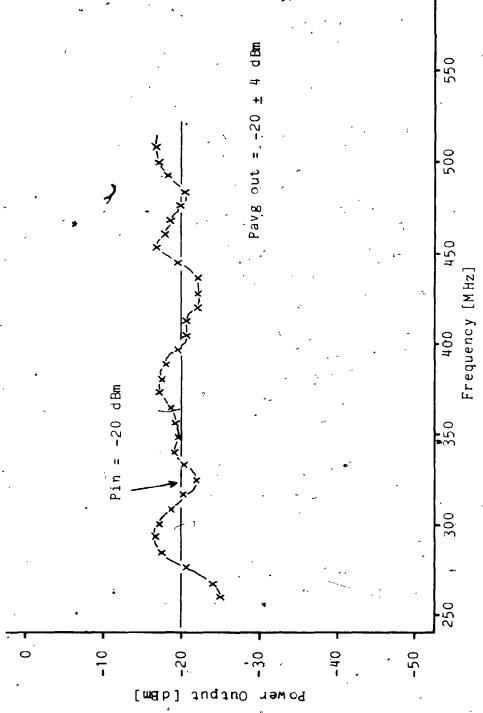

| 5.17     | Frequency sweep of the upper half of signal spectrum (output: filter bank).                                          | 198  |

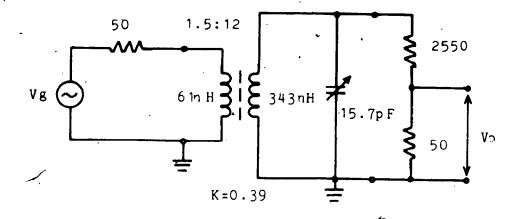

| 5.18     | Ideal transformer response.                                                                                          | 202  |

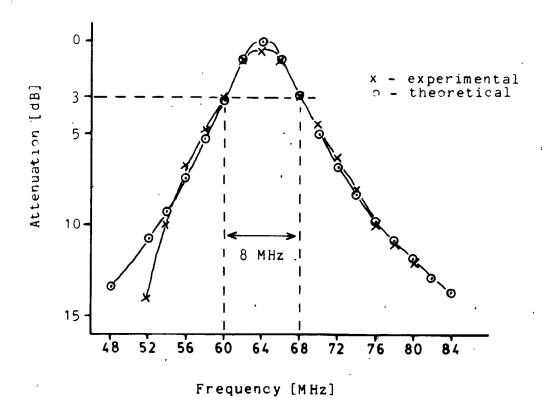

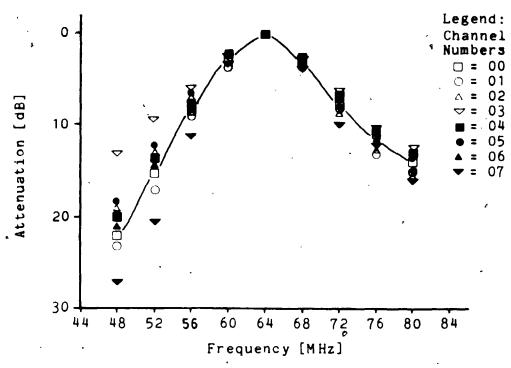

| 5.19a    | Receiver response, channel nos. \$00-\$07                                                                            | 205  |

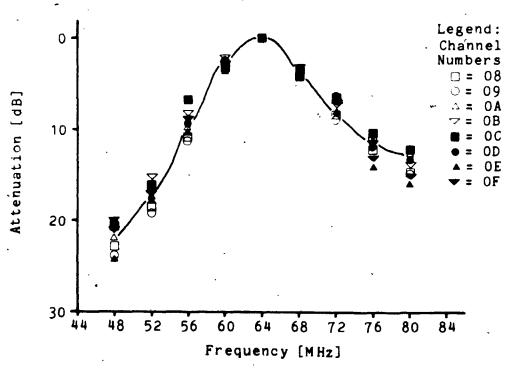

| 5.19b    | Receiver response, channel nos. \$08-\$0F                                                                            | 20,5 |

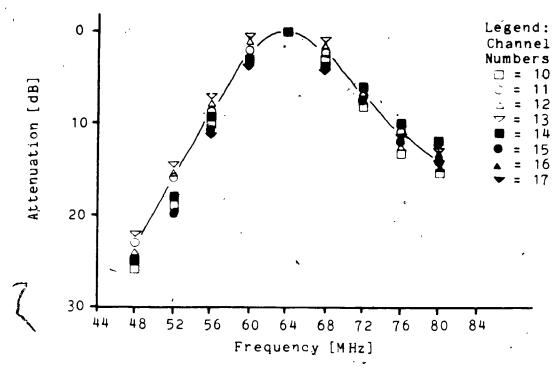

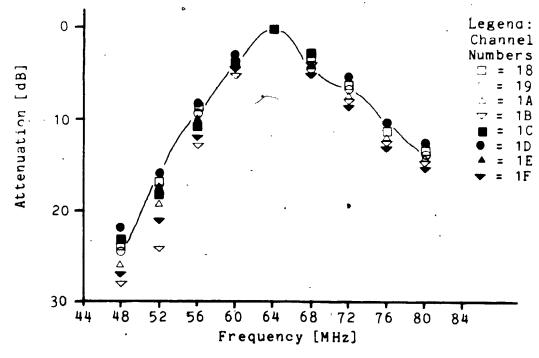

| 5.20a    | Receiver response, channel nos. \$10-\$17                                                                            | 206  |

|          | xii                                                                                                                  |      |

| <b>7</b> |                                                                                                                      |      |

| 5.20b | Receiver response, channel nos. \$18-\$1F                         | 206  |

|-------|-------------------------------------------------------------------|------|

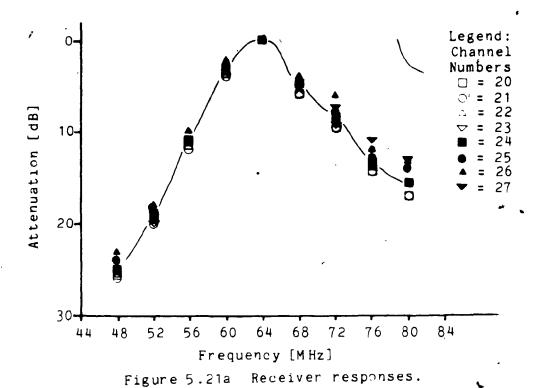

| 5.21a | Receiver response, channel nos. \$20-\$27                         | 207  |

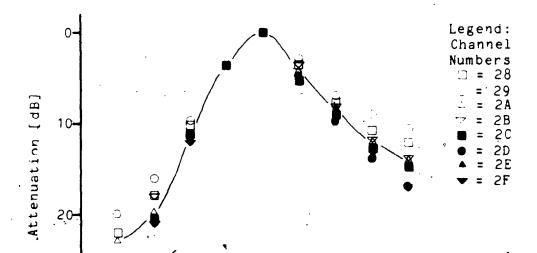

| 5.21b | Receiver response, channel nos. \$28-\$2F                         | 207  |

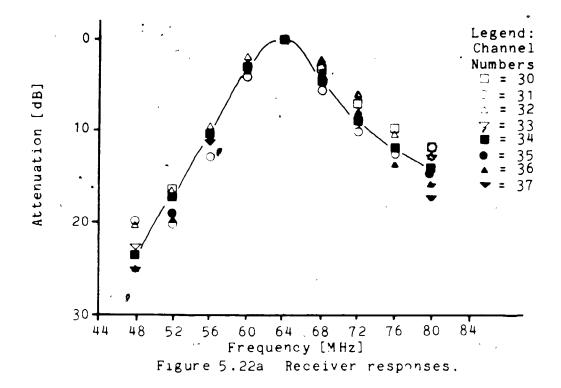

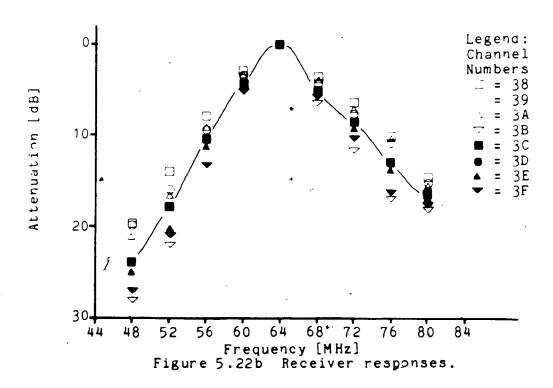

| 5.22a | Receiver response, channel nos. \$30-\$37                         | 208  |

| 5.22b | Receiver response, channel nos. \$38-\$3F                         | 208  |

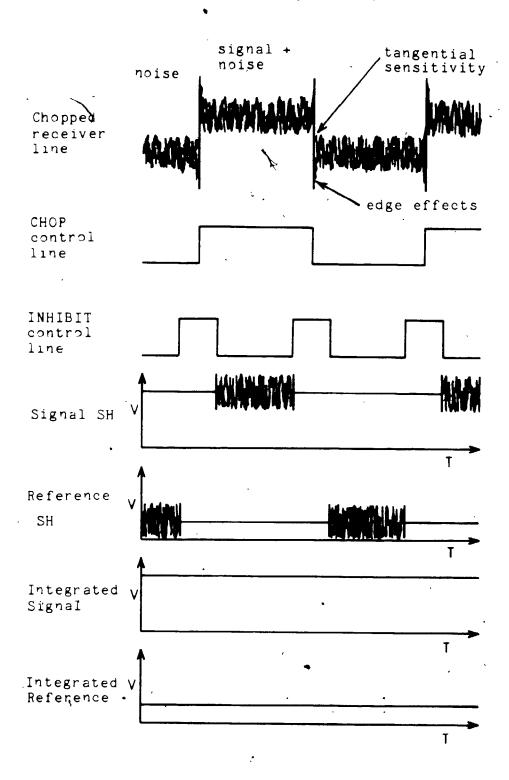

| 5.23  | Synchronous detector timing diagram.                              | 210  |

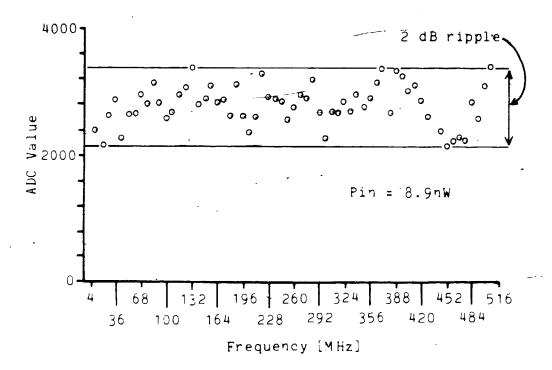

| 5.24  | Linear response to frequency sweep.                               | 223  |

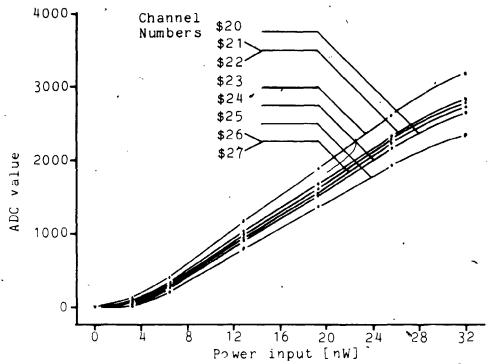

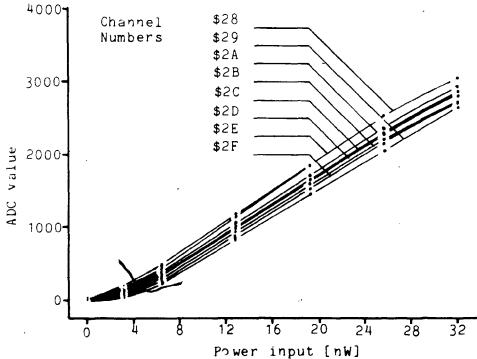

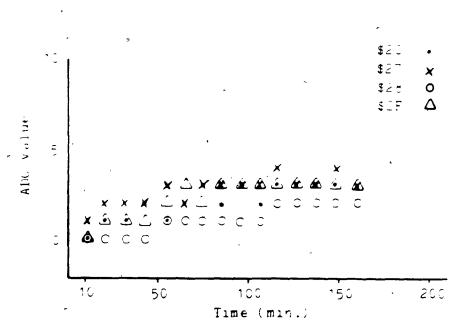

| 5.25a | Dynamic response of selected signal channels (nos. \$20-\$27).    | 224  |

| 5.25b | Dynamic response of selected signal channels (nos. \$28-\$2F).    | 22,4 |

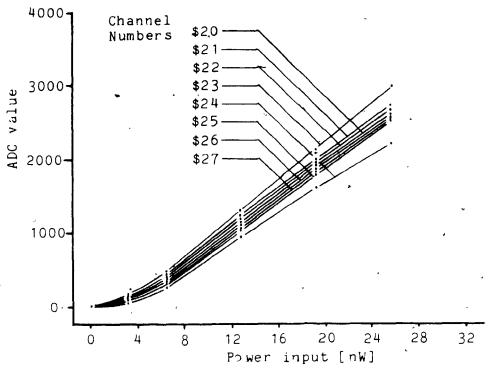

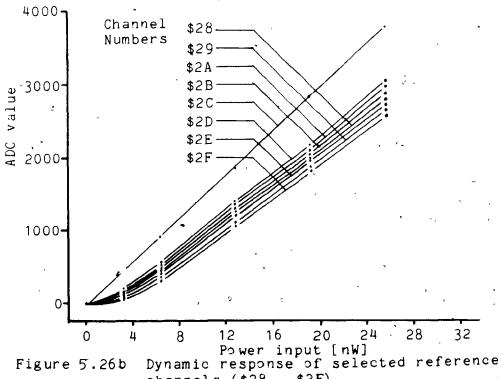

| 5.26a | Dynamic response of selected reference channels (nos. \$20-\$27). | 225  |

| 5.26b | Dynamic response of selected reference channels (nos. \$28-\$2F). | 225  |

| 5.27a | Thermal gain drift response.                                      | 228  |

| 5.27b | Thermal offset drift response.                                    | 228  |

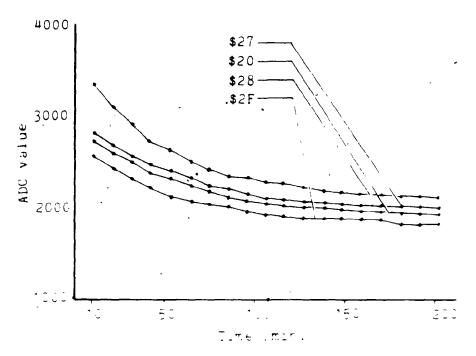

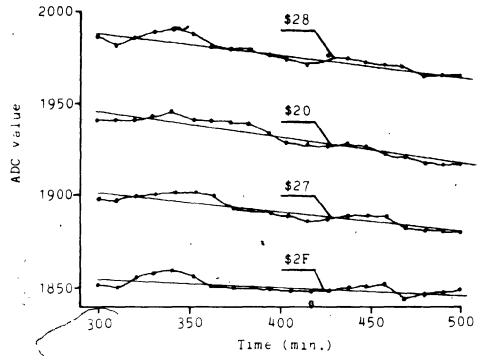

| 5.28  | Long term thermal drift response.                                 | 231  |

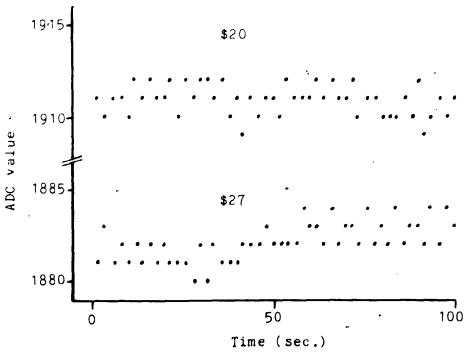

| 5.29  | Short term thermal drift response.                                | 231  |

| 5.30a | Adjacent channel interaction.                                     | 232  |

| 5:30b | Adjacent channel interaction.                                     | 232  |

| 5.30c | Adjacent channel interaction.                                     | ·233 |

| 5.30d | Adjacent channel interaction.                                     | 233  |

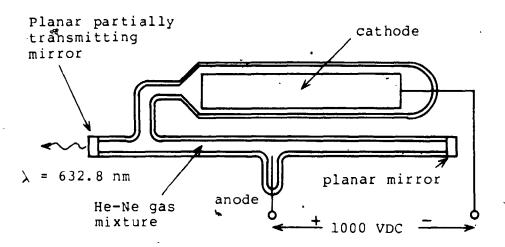

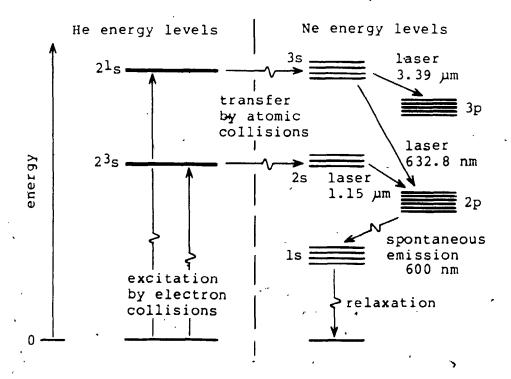

| 6.la  | He-Ne laser tube structure.                                       | 241  |

| 6.1b  | He-Ne laser operation.                                            | 241  |

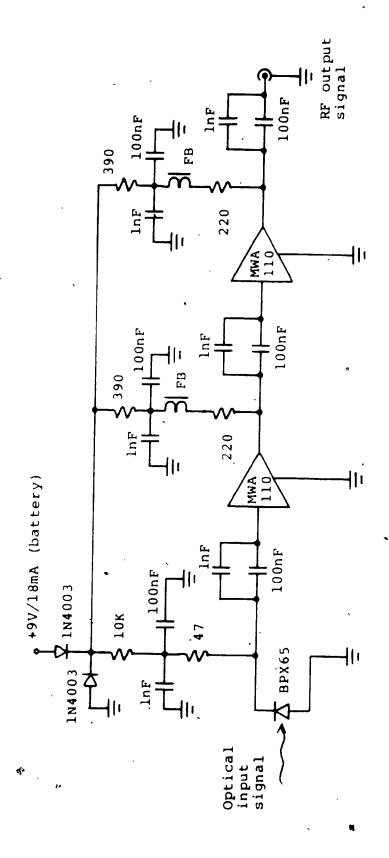

| 6.2   | Optical detector/preamplifier design.                             | 244  |

| 6.3   | Optical heterodyne spectrometer.                                  | 246  |

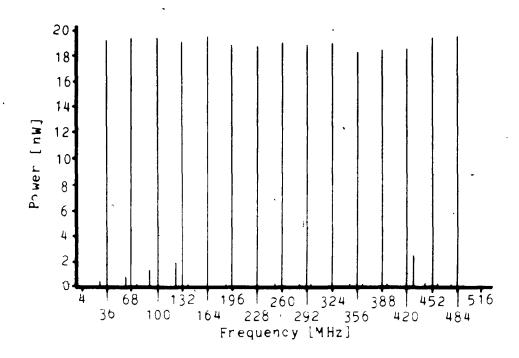

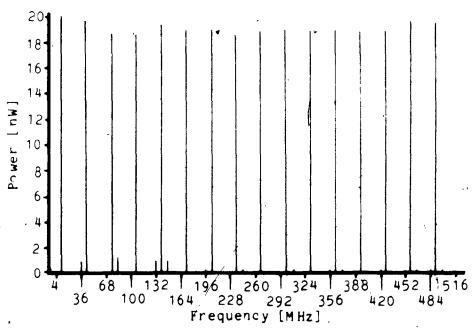

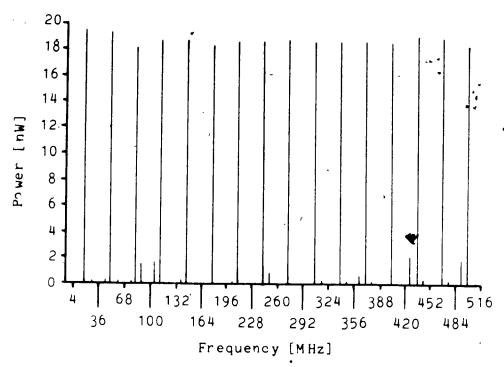

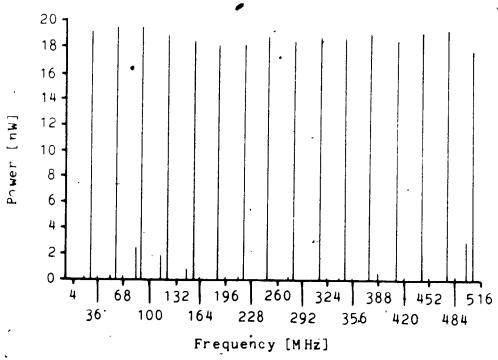

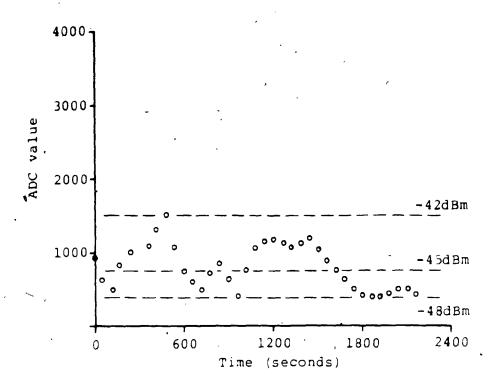

| 6.4a  | Time response of intermodal beat frequency.                       | 250  |

| 6.4b  | Heterodyne beat frequencies.                                  | 250          |

|-------|---------------------------------------------------------------|--------------|

| D.1   | Helical resonator structure and design.                       | 281          |

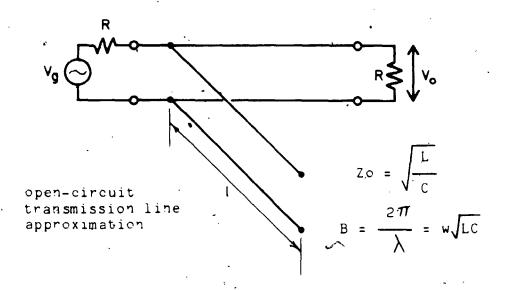

| D.2   | Equivalent circuit and approximation for a helical resonator. | 282          |

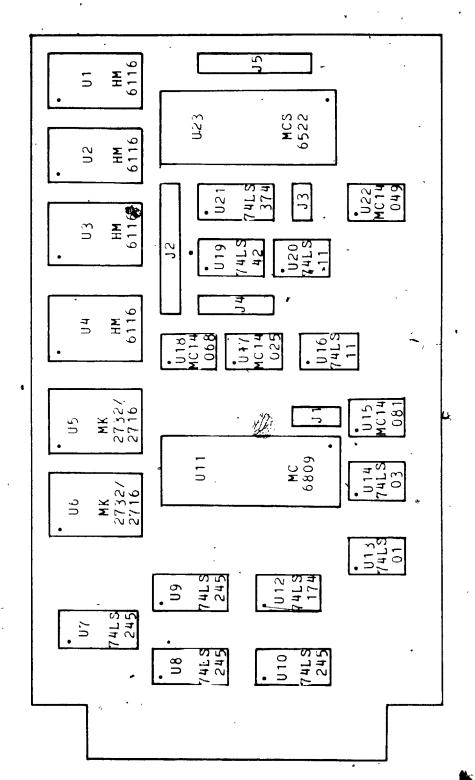

| E.la  | CPU board layout.                                             | 286          |

| E.1b  | CPU board layout.                                             | 287          |

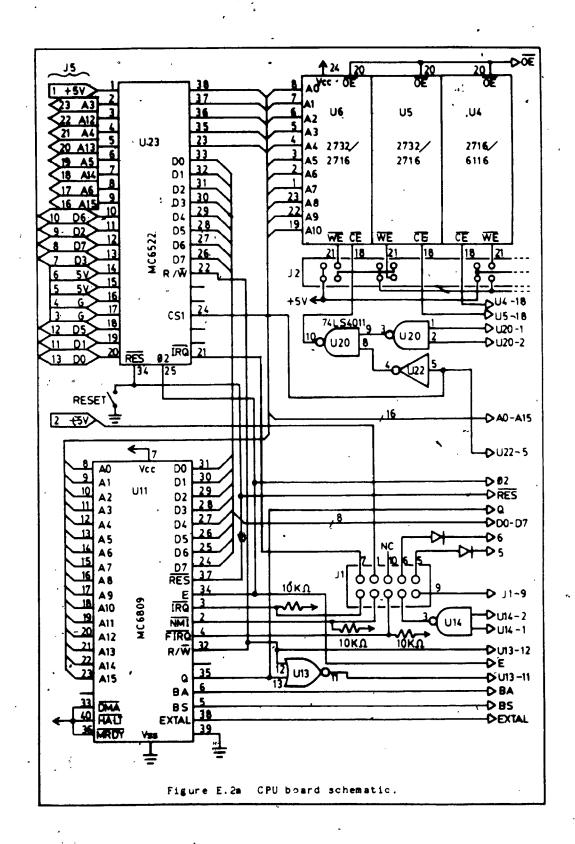

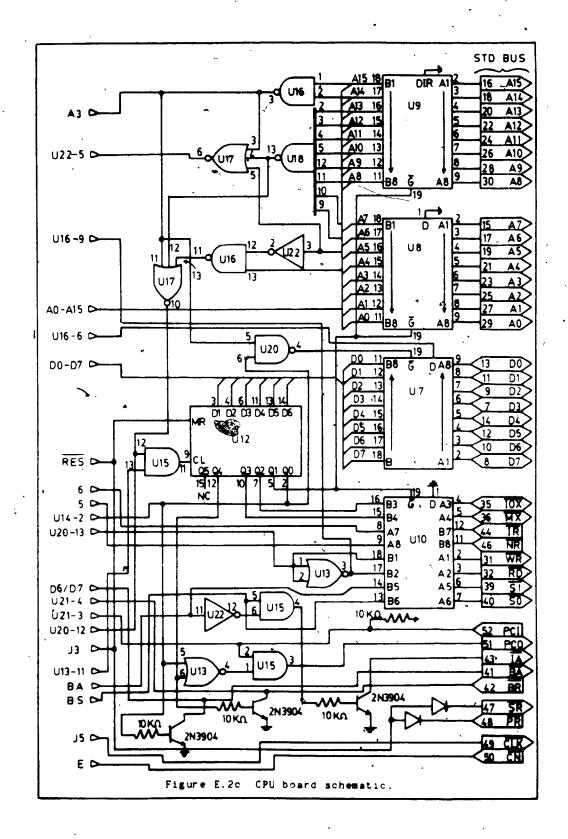

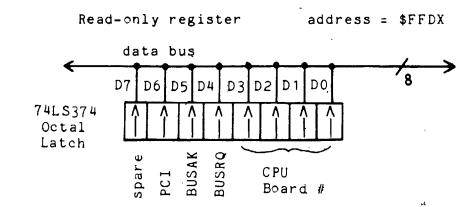

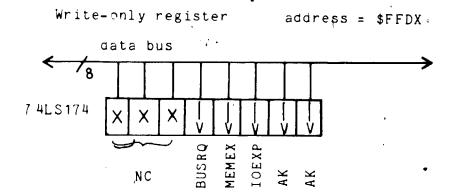

| E.2a  | CPU board schematic.                                          | 288          |

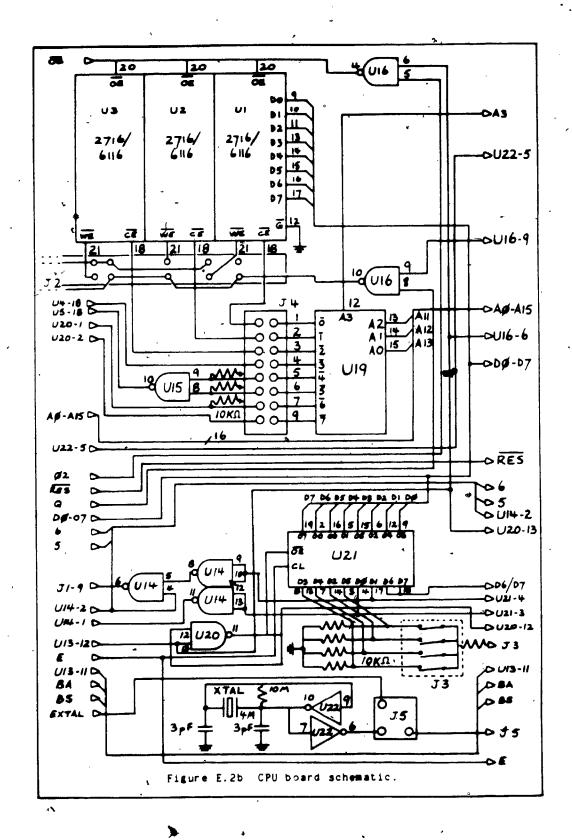

| E.2b  | CPU board schematic.                                          | 289          |

| E.2c  | CPU board schematic.                                          | 290          |

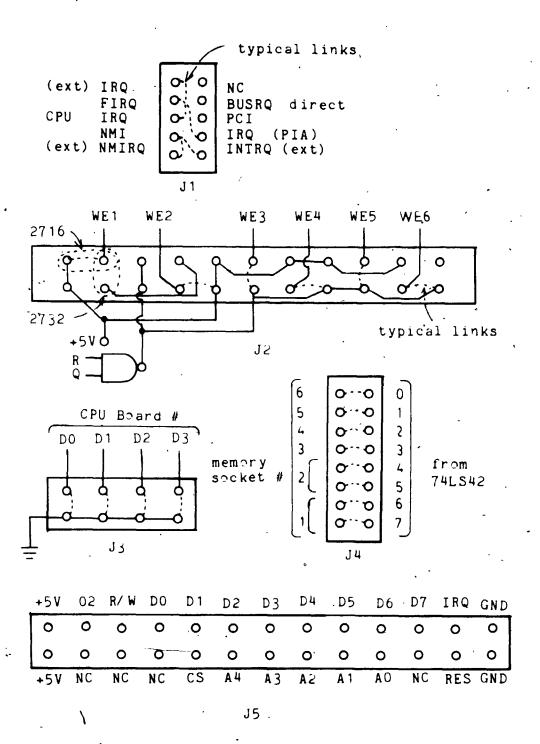

| E.3   | CPU board bus flags and VIA jumpers.                          | 291          |

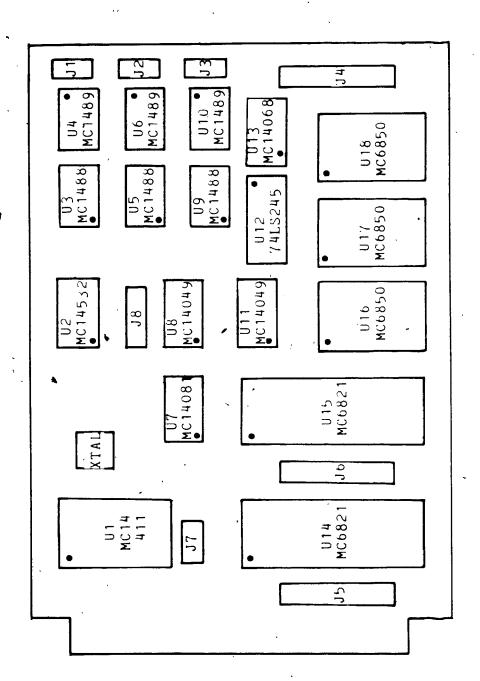

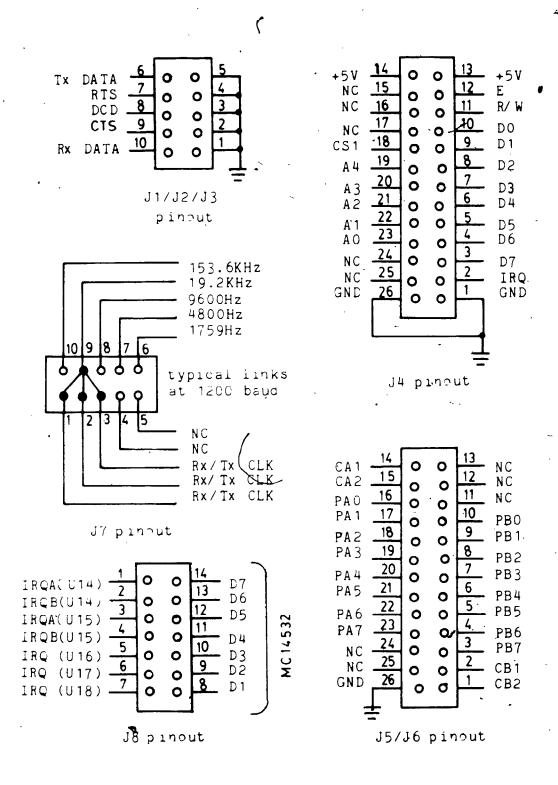

| E.4a  | I/O board layout                                              | 292          |

| E.4b  | I/O board layout                                              | 293          |

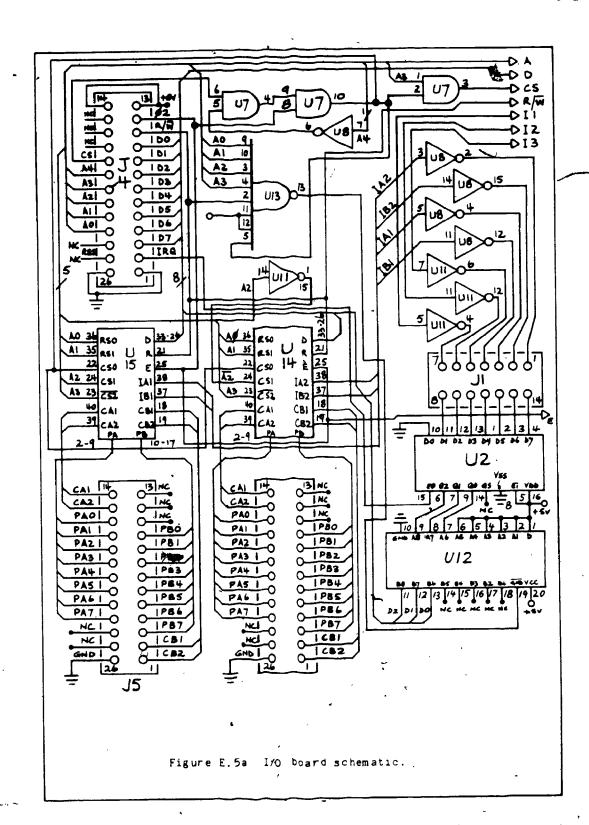

| E.5a  | I/O board schematic.                                          | 294          |

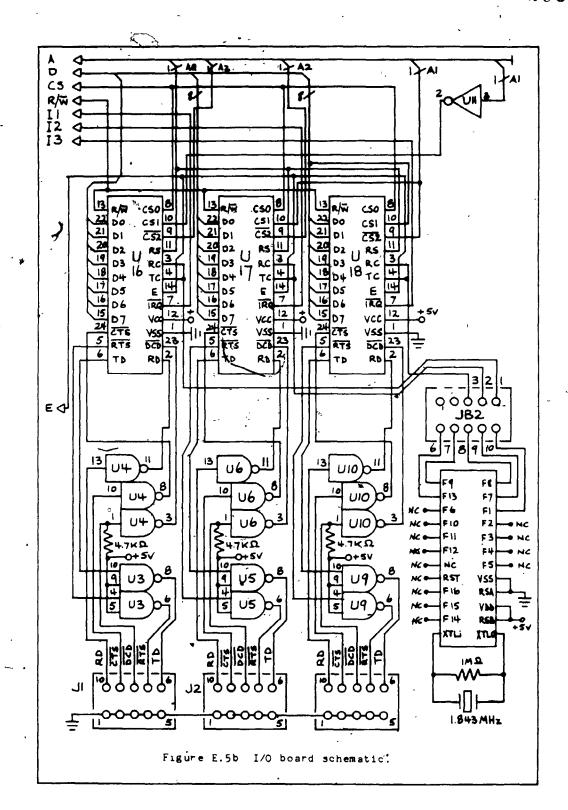

| E.5b  | I/O board schematic.                                          | 2 <b>9</b> 5 |

| E.6   | RAM board layout.                                             | 296          |

| E.7a  | RAM board schematic.                                          | 297          |

| E.7b  | RAM board schematic.                                          | 298          |

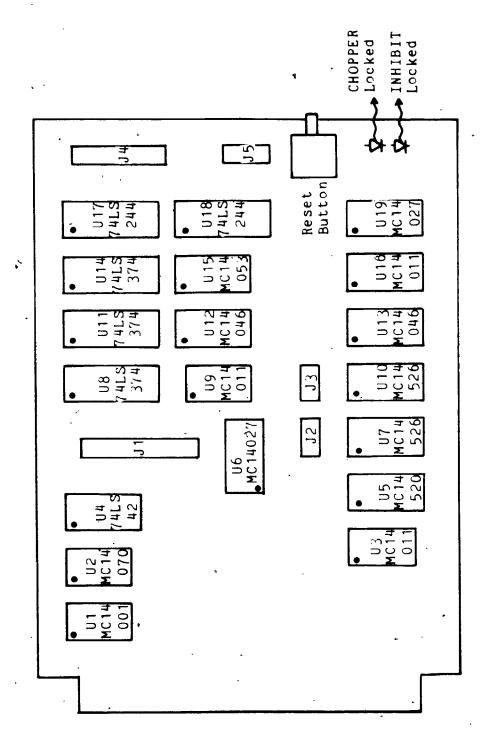

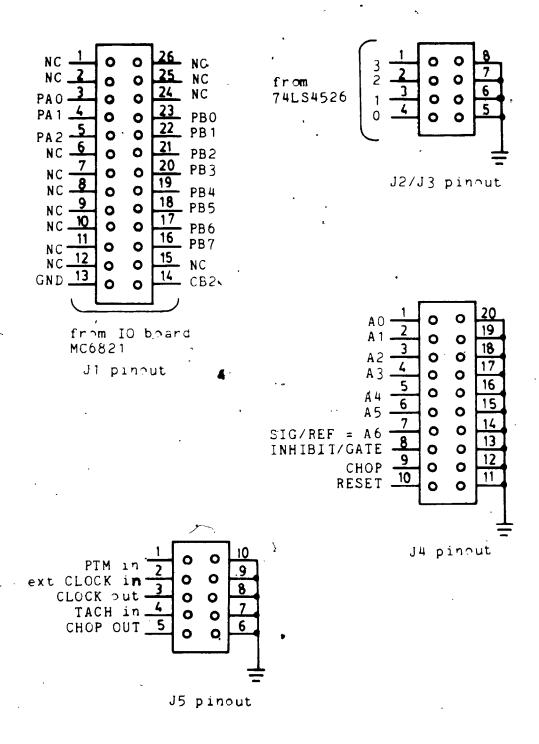

| E.8   | EPROM board layout.                                           | 299          |

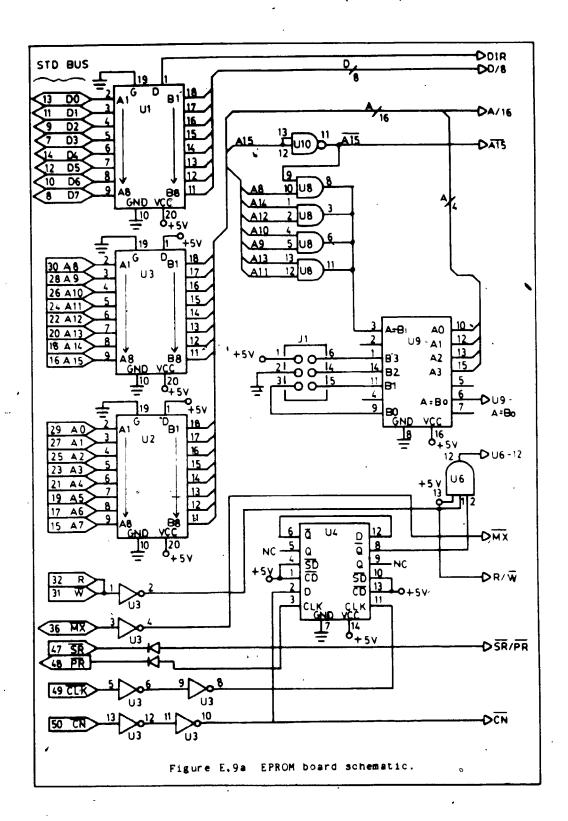

| E.9a  | EPROM board schematic.                                        | 300          |

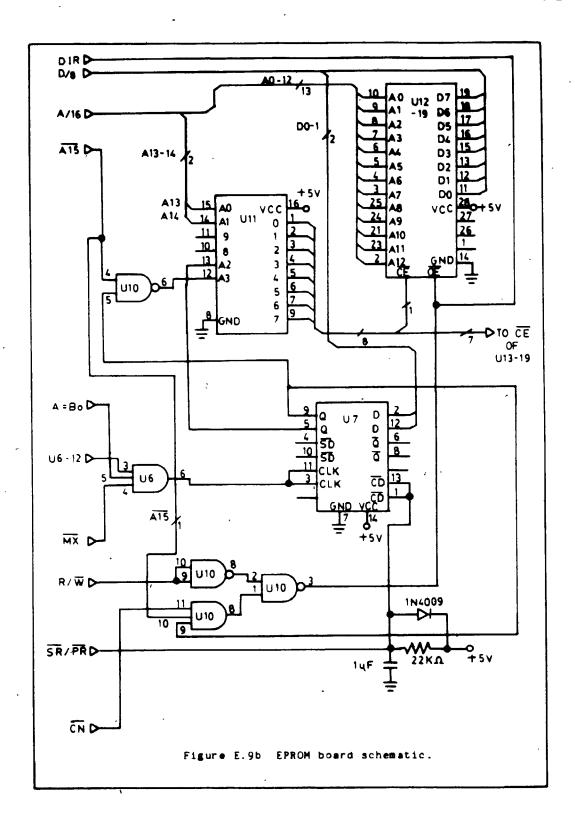

| E.96  | EPROM board schematic.                                        | 301          |

| E.10a | Controller board layout.                                      | 302          |

| Ę.10b | Controller board layout.                                      | 303          |

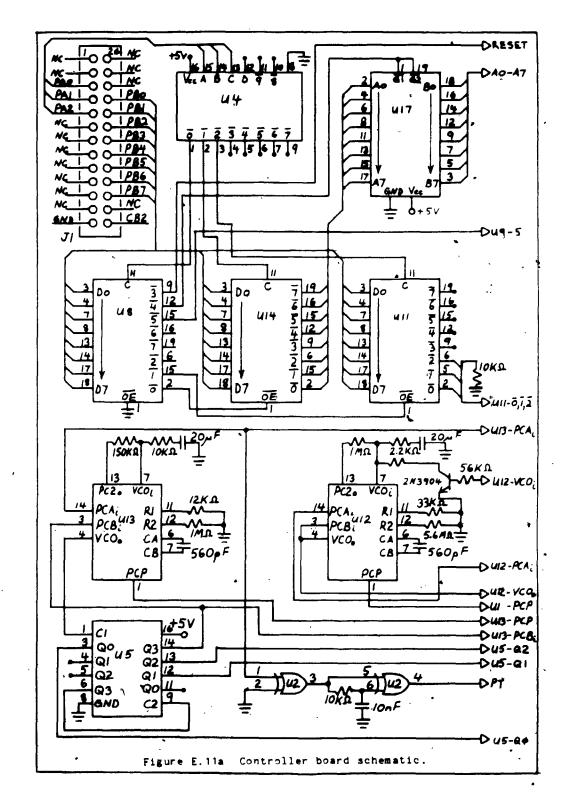

| E.11a | Controller board schematic.                                   | 304          |

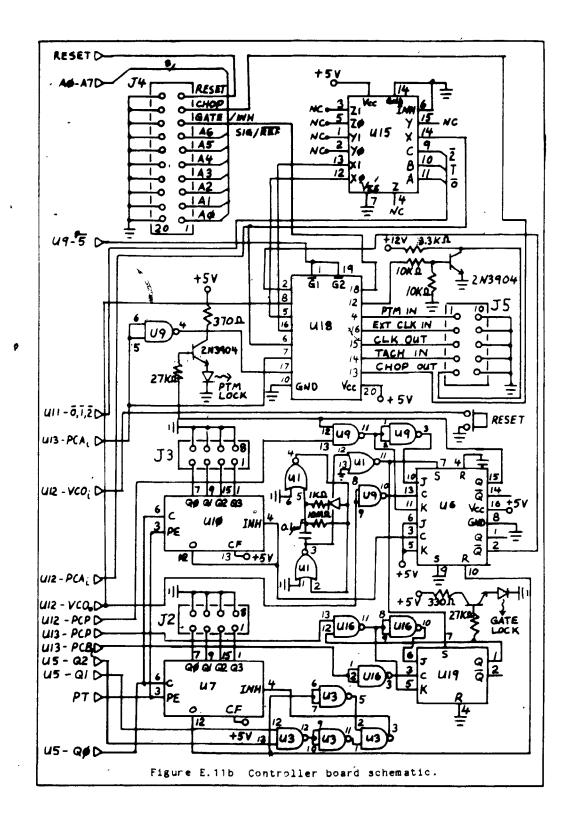

| E.11b | Controller board schematic.                                   | . 305        |

| E.12a | ADC board layout.                                             | 306          |

| E.12b | ADC board layout.                                             | 307          |

| E.13a | ADC board schematic.                                          | 308          |

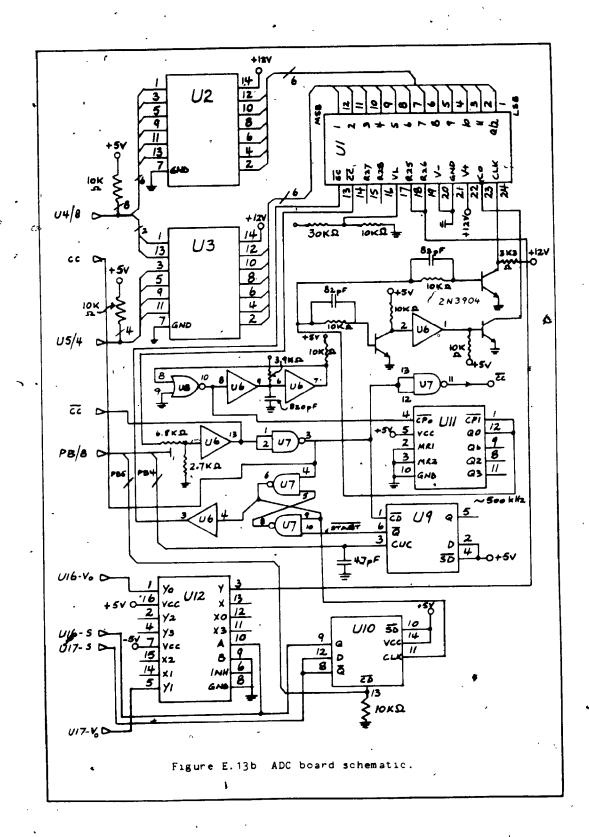

| E.13b | ADC board schematic.     | 309 |

|-------|--------------------------|-----|

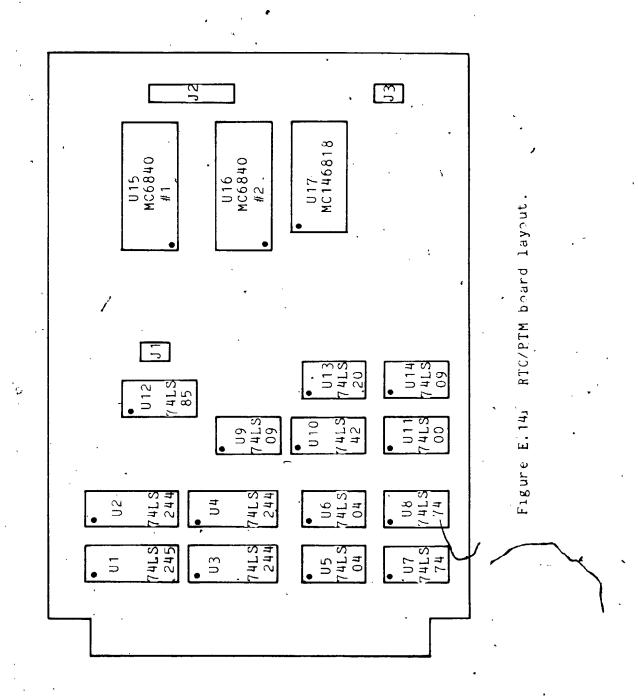

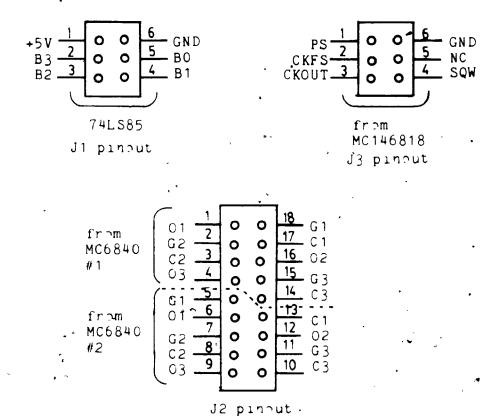

| E.14a | RTC/PTM board layout.    | 310 |

| E.14b | RTC/PTM board layout.    | 311 |

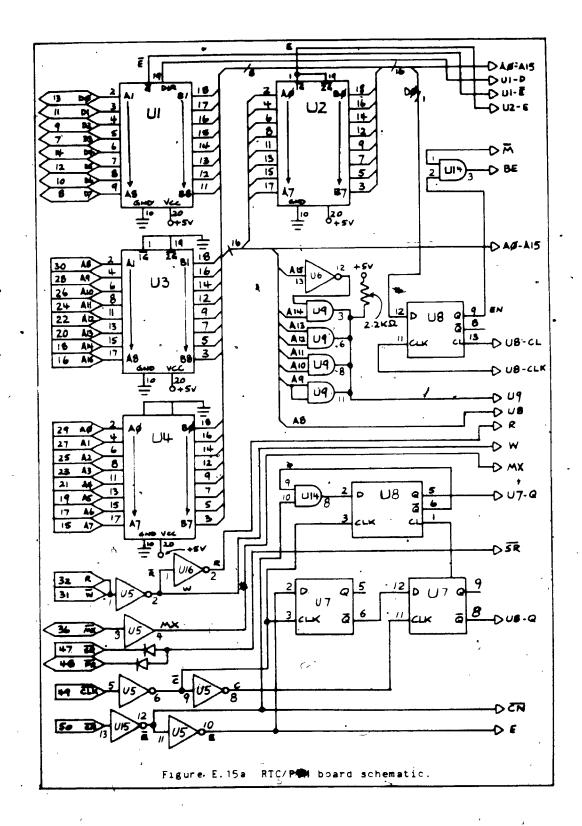

| E.15a | RTC/PTM board schematic. | 312 |

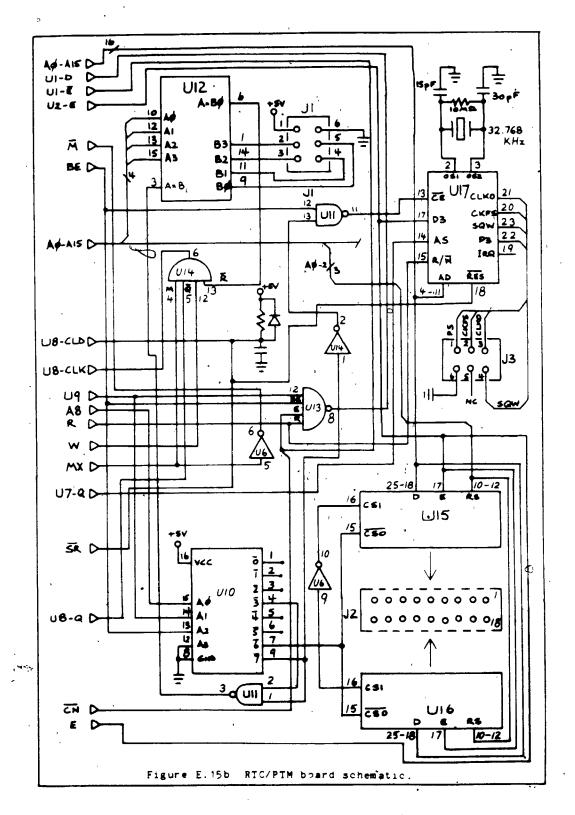

| E.15b | RTC/PTM board schematic. | 313 |

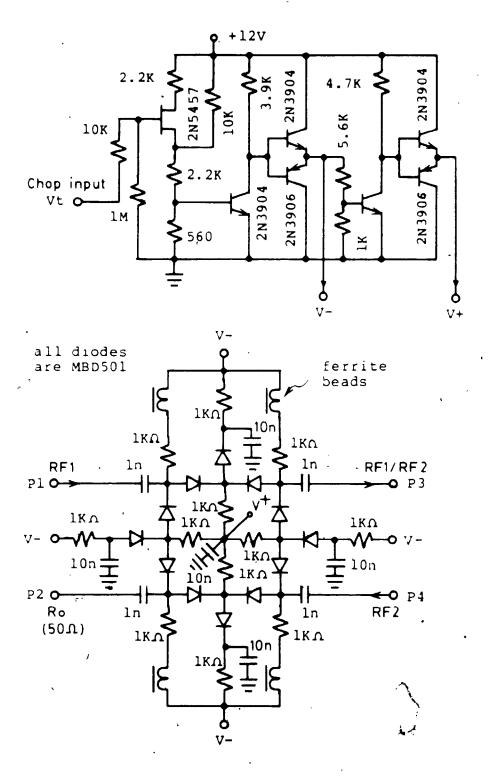

| G.1   | Electronic RF chopper.   | 326 |

## List of Appendices

| Appendix | •                                                  |   | Page |

|----------|----------------------------------------------------|---|------|

| A        | Calculation of loop filter for a phase-locked loop |   | 272  |

| В        | Y-Parameter amplifier analysis                     |   | 274  |

| С        | Device specifications                              |   | 277  |

| D        | Helical resonator design                           | • | 280  |

| E        | Microcomputer diagrams and schematics              |   | 283  |

| F        | FORTH routines for the MCSA                        | • | 314  |

| G        | RF electronic diode chopper                        |   | 324  |

## Glossary of Symbols and Abbreviations

Term Description

ACIA asynchronous communications interface adapter

ADC analog-to-digital convertor (conversion)

AM amplitude modulation

ASCII ' American Standard Code for Information Interchange

B bandwidth

B; input bandwidth

B output bandwidth

B<sub>HF</sub> predetection bandwidth

BIFET bipolar and FET technology

BPF band-pass filter

BW bandwidth

BWO backward-wave oscillator

C capacitor,

Linvill stability factor

C; diode junction capacitance

CMOS complementary MOS

CPU central processing unit

dBm logarithmic power units referenced to 1 mW

DAS data acquisition system

DC direct current

e<sub>r</sub> relative permittivity

EMI electromagnetic interference

EPROM electrically programmable ROM

f centre frequency, cutoff frequency

f unit gain-bandwidth product

F noise figure

F nth amplifier noise figure

F(S) transfer function of PLE filter

FB filter bank

FM frequency modulation

Gn nth amplifier gain

GPIB general purpose instrument bus

H(S) transfer function of PLL

HP Hewlett-Packard ·

HPF high-pass filter

In diode RMS noise current

induced shield current,

diode reverse saturation current

IEEE Institute of Electrical and Electronic Engineers

IF intermediate frequency

I/O input/output

k transformer coupling coefficient

K Boltzmann's constant

K' phase detector gain

K VCO gain factor

L inductance

L transformer primary inductance

$L_s$  transformer secondary inductance

LNA low noise amplifier

LO local oscillator

LPF low-pass filter

m modulation index

M mutual inductance

MCSA multichannel spectrum analyzer

MI module · interface

MOS metal oxide semiconductor

MPU microprocessor unit

n<sub>q</sub> generator noise power

n; diode noise power

n receiver noise power

OHR optical heterodyne receiver

OHS optical heterodyne spectrometer

P<sub>min</sub> minimum detectable power

PA port A of PIA

PB port B of PIA

PCB printed circuit board

PIA peripheral interface adapter

PIN p-iatrinsic-n semiconductor

PLL phase-locked loop

PS power splitter

PTM programmable timer module

PWM pulse width modulation

q electron charge

Q quality factor

R diode junction resistance

R<sub>p</sub> transformer primary resistance

R<sub>s</sub> shield resistance, transformer secondary

resistance

RAM random access memory

RC resistor-capacitor

RF radio frequency

RMS root-mean-square

ROM read-only memory

RTC real-time-clock

SAW surface acoustic wave

SETI Search for Extra-Terrestrial Intelligence

SH sample-and-hold

SNR signal-to-noise ratio

SNR; input SNR

SNR output SNR

STD microcomputer bus type

STL strip transmission line

SYN DET synchronous detector

$\mathbf{t}_{\text{T.F}} \qquad \text{postdetection integration time}$

T absolute temperature (Kelvin)

T<sub>a</sub> antenna temperature

T<sub>C</sub> , comparison load noise temperature

T<sub>g</sub> generator noise temperature

T<sub>min</sub> minimum detectable temperature

$T_{O}$  ambient temperature

T<sub>r</sub> receiver noise temperature

${\tt T}_{\tt SYS}$  system noise temperature

TSS tangential sensitivity

TTL transistor-transistor logic

$\mu_{r}$  relative permeability

UHF ultra high frequency

diode voltage  $v_{d}$  $v_n$ noise voltage v<sub>p</sub> carrier amplitude V<sub>pp</sub> voltage measured peak-to-peak Ý<sub>s</sub> induced shield voltage voltage controlled oscillator VCO versatile interface adapter VIA voltage standing wave ratio VSWR carrier frequency natural frequency wn modulation frequency w<sub>s</sub> θ<sub>i</sub> PLL input phase θ ο PLL output phase ۲ damping factor

#### Chapter 1

### Reception of Spectrally Resolved Signals

## 1.1 Introduction

The radio frequency multichannel spectrum analyzer (MCSA) has many applications where signal reception is limited by noise. The more notable fields of application are spectroscopy, astronomy, and remote sensing.

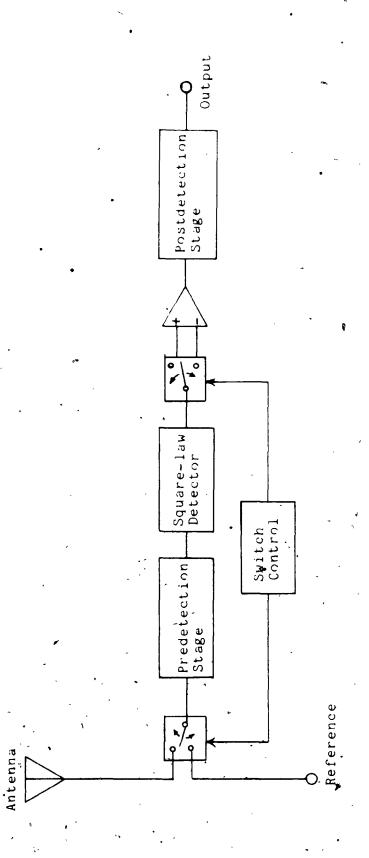

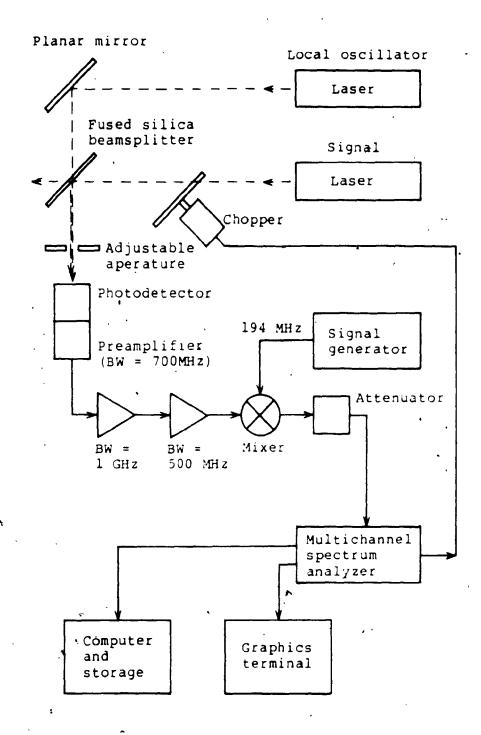

The MCSA has an important role in the spectral resolution of optical signals in the field sensitivity laser spectroscopy. The laser is a coherent source that makes it ideal as an optical local oscillator for the heterodyning of optical signals. In its simplest form, an optical heterodyne receiver (OHR) consists of a laser local oscillator, a beamsplitter to mix the measured optical signal and local oscillator laser beams, and a fast photodetector. An optical heterodyne spéctrometer (OHS) consists of an optical heterodyne receiver followed processing by radio frequency (RF) multichannel spectrum analyzer (see figure 1.1).

Laser heterodyne spectroscopy is well suited for the study of absorption and emission lines because of its high resolution. This high resolution is limited by the uncertainty in laser frequency which, for a high quality stable gas laser, can be confined to a bandwidth of 10 kHz (Siegman, 1971). The first optical laser heterodyne

Figure 1.1 An optical heterodyne spectrometer.

detection experiments were performed by Nieuwenhuijzen (1970) on a number of bright stars and the planet Jupiter. The spectrometer consisted of a He-Ne laser, photodiode detector, wideband RF amplifier (200 MHz), and a lock-in amplifier.

Infrared heterodyne spectroscopy of carbon dioxide on Mars has been performed with a multichannel spectrometer at Kitt Peak National Observatory (Betz, 1975). The results proved the practicality and usefulness of infrared heterodyne techniques in astronomy. A spectral resolution of several orders of magnitude better than conventional methods was obtained.

The spectrometer employed a carbon dioxide laser as a local oscillator and a cooled (77 K) HgCdTe detector to produce an IF band from 0 to 1500 MHz. The IF band was spectrally resolved by a multichannel spectrum analyzer consisting of 40 x 5 MHz bandpass filters with a reception range of 50 - 250 MHz. Direct RF detection, synchronous detection, and multiplexing was performed on each of the channels.

The first tunable 8.5 µm infrared heterodyne spectrometer was constructed using tunable diode lasers (PbSe) for the study of black body emission from the Moon and Mars. The spectrometer had a reception range of 200 MHz covered by a bank of 8 x 25 MHz filters (Mumma, 1975). The RF signal from each channel was directly detected, synchronously detected, and then multiplexed for

data acquisition.

Infrared heterodyne spectroscopy is well suited to atmospheric studies because of its high detection sensitivity and high spectral resolution. The carbon dioxide laser heterodyne spectrometer at the Goddard Space Flight Centre and a tunable diode laser heterodyne spectrometer were utilized to make atmospheric absorption measurements based on solar observations of absorption lines of  ${\rm CO}_2$  and  ${\rm O}_3$  in the 10  $\mu{\rm m}$  band (Abbas, 1979).

The spectrometer consisted of  $40 \times 5 \text{ MHz}$ ,  $23 \times 50 \text{ MHz}$ , and  $1 \times 1000 \text{ MHz}$  bandpass filters. The outputs of the filters were processed by direct RF detection, synchronous detection, and multiplexing.

Infrared heterodyne spectroscopy of ammonia and ethylene in stars has been carried out with a multichannel analyzer consisting of 128 x 20 MHz filter banks (Betz, 1981). Initial observations were successful and present work is directed toward synthesizing laser local oscillator frequencies to higher accuracy.

A multichannel spectrum analyzer consisting of 2<sup>20</sup> channels is presently being built by the NASA-Ames Research Centre for the SETI project (Search for Extra-Terrestrial Intelligence). Its high sensitivity is achieved through the use of large existing antennas, integrating for long periods of time, and using low temperature systems. High resolution is achieved by the examination of the channels with narrow bandwidths of 4 Hz

or less (Billingham et al, 1978).

An optical heterodyne receiver provides greater sensitivity than conventional direct detection schemes. The regions where these receivers are most useful are in the 3-5  $\mu$ m and 8-14  $\mu$ m regions where atmospheric windows exist.

In many cases, the output signal from a photodiode, produced by the detection of an optical signal, is very noisy. This noisy signal has a signal-to-noise ratio (SNR) much less than the capability of a direct detection scheme. The SNR can be greatly improved by periodically interrupting the optical signal, producing a modulated or chopped optical signal for coherent processing (Meade, 1983).

The high sensitivity processing of optical signals is made possible by the use of coherent detectors. These are phase-sensitive detectors that measure difference voltages by using a synchronous reference voltage derived from the input modulator or chopper. Phase-sensitive detection provides amplitude as well as phase information in the presence of noise and interference. Phase-sensitive detectors that are phase-locked to the modulation or chopper frequency with no phase offset are synchronous detectors (Meade, 1983).

The preservation of amplitude and phase information makes heterodyne detection systems suitable for interferometry. Long baseline interferometers have been

used to study fringe signals from the planet Mercury in the 10  $\mu m$  region (Johnson, 1974).

Coherent processing systems operating on the phase-sensitive detector principle are known as lock-in detection systems and the equipment is known as lock-in amplifiers (Meade, 1983).

Previously mentioned heterodyne spectrometers are limited in their RF processing capabilities by the characteristic behaviour of each of the RF bandpass filters. Since all filters are different, the process of alignment and balancing, with respect to other filters, places a practical limit to the number of filters in the multichannel spectrum analyzers.

The electronic techniques of superheterodyne receiving were not employed in these spectrometers. This is an important technique that is widely used in common radio receivers. Superheterodyne reception is the process of multiplying two frequencies together (RF signal and RF local oscillator) and making use of the resulting difference frequency as the intermediate frequency (IF) band.

The benefits of superheterodyne reception are that most of the amplification and filtering takes place in the IF band rather than in the RF band. Amplification at a fixed narrow frequency band is much easier to accomplish than at a variable, wider frequency band. In addition, the local oscillator may be changed to receive a different

RF band without altering the superheterodyne receiver. IF filtering for a given bandpass response is easier to obtain and keep consistent across many receivers.

thesis describes a multichannel This lock-in detection system developed for the coherent processing of optical signals. A radio frequency multichannel spectrum analyzer has been designed, built and tested for detection of weak signals buried in predominantly white noise. Sixty-four channel filters and receivers covering a range of 0 - 512 MHz are employed to extract the signal from noise. The signal is alternately switched or chopped with a noise reference and synchronously detected by receivers.

The system consists of four parts: a radio frequency (RF) section, a detector section, a digital electronic section, and a microcomputer section.

The RF section consists of wideband low noise amplifiers, high-pass filters and dow-pass filters in the front-end module. Following this, there are filter banks containing a total of 64 channel filters of equal bandwidth (8 MHz) uniformly spaced across the reception range of 0 - 512 MHz. Each of the 64 channels has a superheterodyne receiver incorporating square-law detection for optimum sensitivity.

The detector section consists of 64 synchronous detection or coherent detection circuits following the

superheterodyne receivers. These maximize the sensitivity of the multichannel spectrum analyzer (MCSA) by significantly reducing all noise, including system noise, that is asynchronous with the chopped input signal.

The digital electronics supplies all the necessary control signals for synchronous detection, analog-to-digital conversion, and data collection.

The microcomputer with its operating system provides user and external computer interfacing with the analyzer. In addition, some data processing and manipulation is possible, such as extended integration times and graphic displays of system spectral response. The data, once collected by the microcomputer, is transferred to a minicomputer for further analysis and storage.

The radio frequency multichannel spectrum analyzer was designed and built with state-of-the-art (MCSA) technology. Very low noise, wideband, gallium arsenide (GaAs) preamplifiers were used as the first stage of amplification on the front-end module of the MCSA for improved noise figure characteristics. Wideband, linear, double-balanced mixers were employed in the front-end system to module and throughout the intermodulation distortion. Tapped strip transmission line structures were used as high quality (Q) channel The concepts of lock-in filters and power splitters. detection were applied to detection at radio frequencies. stages of detection, square-law detection and

synchronous detection, were employed for optimum sensitivity. A dual square-law detection scheme was used to maximize the sensitivity of the RF superheterodyne receivers. Each receiver output is synchronously detected to improve the signal-to-noise ratio. It also includes Dicke chopper edge cancellation to eliminate spurious responses due to edge effects.

The data acquisition system containing a high speed, 12-bit analog-to-digital converter can perform a system sweep and conversion of all the receiver outputs (128 for both signal and reference outputs) in 3.1 ms. As with all of the system, the scanning is under control of a microcomputer which also handles data transfer to a graphics terminal and to a minicomputer. The entire system was designed to be controlled by a microcomputer. In this way, the system can be easily reconfigured and optimized for a given application by changing the controlling software.

The multichannel spectrum analyzer is essentially a multichannel lock-in amplifier system. Sixty-four channels divide the reception range uniformly and perform coherent detection in each channel. The channel receivers are lock-in amplifiers that coherently or synchronously detect the chopped RF input signal.

The multichannel spectrum analyzer differs markedly from other spectrum receiver designs. The MCSA uses multiple channels of a fixed bandwidth and at a fixed

frequency spaced uniformly across the frequency range of interest. Most other spectrum receiver designs employ a single channel that is swept through the desired frequency range.

The MCSA system is essentially a parallel processing system in the time domain, since each of the multiple channels is continuously receiving signals. The swept spectrum receiver systems are essentially serial processing systems since an event that occurs on the input will only be recorded when it is synchronous in time with the sweeping channel.

This thesis is organized into eight chapters which are briefly described below.

Chapter two describes the multichannel spectrum analyzer and its environment. A comparison is made with more common swept spectrum analyzers. The lock-in amplifier technique and design are discussed.

Chapter three gives an overview of the entire MCSA, emphasizing the functional operation of the system. Theory supporting design decisions and characteristics of the system is presented.

Chapter four provides details of the structure of the multichannel spectrum analyzer. Each electronic component of the analyzer is described in detail with supporting diagrams and schematics.

Chapter five describes the tests and calibrations performed on the system. Tests and calibrations are shown for individual components and sections of the system. A complete system test and calibration are described and evaluated.

Chapter six describes an optical heterodyne experiment for validation and calibration of the multichannel spectrum analyzer.

Chapter seven discusses the foregoing tests, and results. In addition, recommendations regarding the project are made.

Chapter eight briefly summarizes the project and presents the conclusions.

## Chapter 2

The Multichannel Spectrum Analyzer System.

### 2.1 The Multichannel Spectrum Analyzer

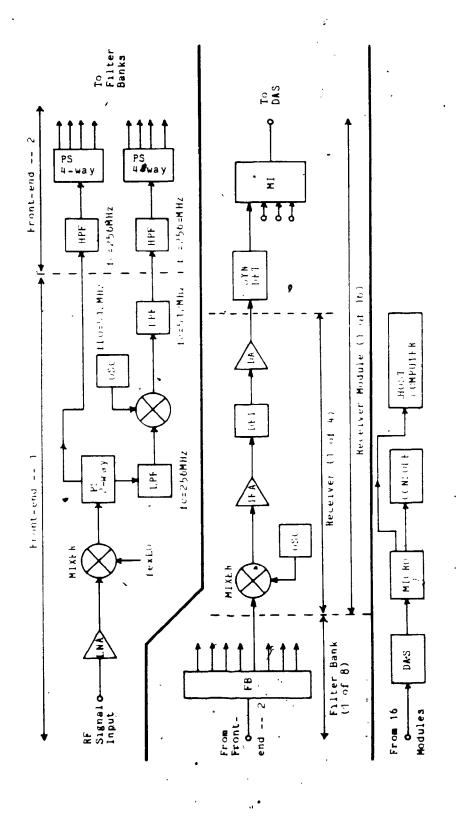

The following is a brief functional description of the multichannel spectrum analyzer (MCSA), followed by a more detailed functional description of the system with reference to figure 2.1. The application of the concepts of modularity, symmetry, and parallelism to the MCSA are described.

The multichannel spectrum analyzer system was developed for the acquisition of signals buried in noise. To optimize the recovery of the signal, synchronous detection is employed. To accommodate this detection scheme, the RF input is switched or chopped alternately with a reference source (4e. noise source). This scheme was derived from a receiver originally developed by Dicke (1946).

The RF input reception range of 0 - 512 MHz is covered by 64 channel filters and receivers. Each channel filter consists of a transmission line filter with a bandwidth of 8 MHz. These channel filters are uniformly spaced across the 512 MHz reception range. Sixty-four channel receivers are connected to the 64 channel filters and use square-law detection to recover the signal.

LNA - low noise amplifier

fexto - external local oscillator frequency

PS - power splitter

LPF - low-pass filter

HPF - high-pass filter '

OSC - oscillator

FB - filter bank

IFA - intermediate frequency amplifier

.DET - detetor

DA - differential amplifier

SYN DET - synchronous detector

MI - module interface

DAS - data acquisition system

f - centre frequency

RF - radio frequency

$f_{LO}$  - local oscillator frequency

Legend for figure 2.1

Figure ... The modifications of From An exercise

The output of each channel receiver is synchronously detected to remove any noise that is asynchronous with the chopped RF input. The output of each synchronous detector is integrated for 6 s by an analog integrator and collected by the data acquisition system. A microcomputer performs some preprocessing on the digitized data and either displays it on the console terminal or sends it to the host computer for further analysis. Details of the operation of the analyzer are shown in figure 2.1.

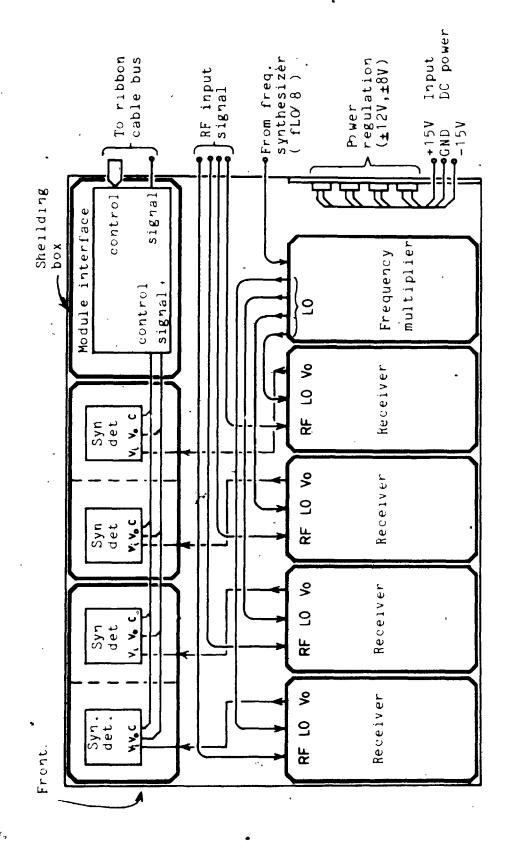

The multichannel spectrum analyzer (MCSA) can be divided into seven parts: first section of the front-end module, second section of the front-end module, filter banks, receiver modules, data acquisition system, microcomputer, and host computer. This partitioning is based mainly on the physical construction of the MCSA, but is also a convenient logical partitioning of the system.

The first section of the front-end module receives the RF input signal using a low-noise amplifier (LNA). The output of the LNA may be frequency shifted by a mixer and external oscillator to a convenient frequency band in the 512 MHz reception range. The signal power is split (PS) two ways with one output going to one side of the second section of the front-end module and the other output going on for further processing. The upper half of the signal spectrum (LPF, f<sub>C</sub> = 256 MHz) is suppressed and the lower half passed. The lower half of the original spectrum is frequency shifted to the upper half by mixing

(512 MHz) and directed to the second side of the second section of the front-end module.

Section two of the front-end module consists of two identical) sets of circuitry; one for the upper half and one for the lower half of the signal spectrum. Here, the signal is high-pass filtered (HPF,  $f_{\rm C}$  = 256 MHz) and power split (PS) four ways. There is a total of eight outputs for each of the eight filter banks (FB).

The filter banks (FB) consist of eight channel filters. These filters are tapped transmission line structures and isolate the required frequency band for the receivers. There is a total of 64 outputs from all of the filter banks.

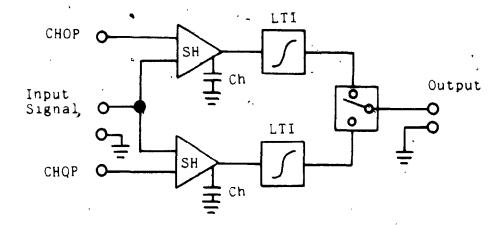

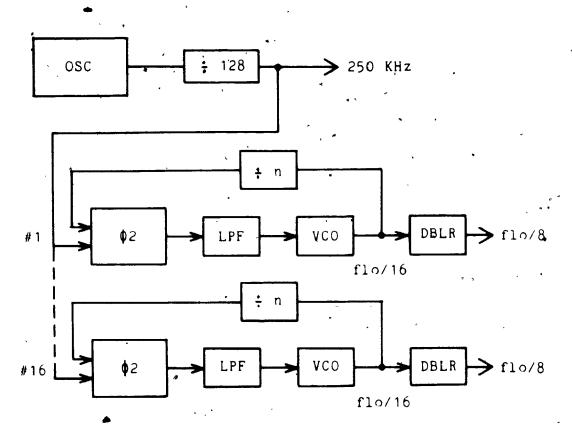

Four outputs from four different filter banks go to a The receiver module consists of four receiver module. receivers, four synchronous detectors, a local oscillator, and a module interface. Each receiver in a module and between modules is identical. They have an intermediate (IF) of 64 MHz with a bandwidth of 8 MHz and square-law detection. The synchronous detector (SYN phase with the chopped RF input and recovers switches in the signal from the multiplexed signal and reference The module interface (MI) links the receiver waveform. module with the data acquisition system and with the system controller of the microcomputer. There is a total of 16 receiver modules in the MCSA system.

The data acquisition system (DAS) collects and digitizes the 64 detected signals from all of the modules. This is done under direct control of the microcomputer.

The microcomputer (MICRO) controls the entire MCSA system by providing control signals for the synchronous detector and controlling the data acquisition system. It also performs some preprocessing for graphic displays at the console terminal. In addition, it also handles data transfer to a host computer (PDP-11/23, PDP-10).

The host computer is required for further data analysis and storage; it also facilitates software development for the microcomputer.

In the development of the MCSA, the principles of multiplicity and symmetry were employed. The channel filters are organized into filter banks, and receivers into multiples of an identical receiver module. This multiplicity allows subsystem symmetry to be employed, better alignment of modules, and negligible pick-up of spurious signals.

This multiplicity of design has a number of benefits. Subsystem design and implementation are much less time consuming and tedious, since the circuits are simply reproductions. Design problems and their solutions, encountered during development, are similar throughout all of the subsystems.

The 8 filter banks are all basically of the same construction with only minor differences to accommodate

the different resonant frequencies. All 64 receivers are identical, having the same intermediate frequency (IF), IF. bandwidth, and detection scheme. The receivers only differ in the local oscillator frequency and the RF input frequency. All 64 synchronous detectors are identical. All module interfaces are identical except for wire-wrapped pins that uniquely define an address for the a receiver module and receiver.

Parallel processing as it is employed in the MCSA has number of advantages. Continuous reception at all frequencies in the reception range of 0 -512 MHz significant improvement over that of a swept spectrum analyzer since an event occurring at any time will received and recorded. This is an important characteristic as many phenomena of scientific. interest are transient in behaviour.

Parallel processing systems may, in general, involve more circuitry than a serial processing system, but there is a trade off between numerous, redundant, simple circuits and a few highly complex individual circuits. Redundancy is an important factor in improving system reliability. Failure of a channel or even a group of channels will not necessarily bring the entire system to a halt. More elaborate parallel systems may have provision to replace, a failed subsystem, with one on standby, resulting in no noticeable degradation of performance. This is a cularily important in aircraft, or military

systems where a system failure can be catastrophic (Hobb, 1970).

In general, parallel systems are more expensive than serial ones due mainly to the quantity of circuitry in a parallel system. In addition, some data acquisition system is usually required to record and collect the data generated continuously by all the channels.

parallel processing systems are typically used in areas of phased array radar, sonar processing, radar processing, pattern recognition, and computer hardware and software.

The highly parallel MCSA for the SETI project, under development at the NASA-Ames Research Centre, is a system for very high spectral resolution of astronomical radio signals. A typical application of this system would be the spectral search of the 'water-hole' spectrum (1.420 - 1.667 GHz) which is bounded by the hydrogen and hydroxyl lines. The effectiveness of such a MCSA is given by the time-bandwidth product of the system, which is the ratio of the reception range to the channel bandwidth ('frequency bin'). This is simply equal to the number of bins or channels that the system is capable of analyzing simultaneously (Machol, 1979).

The resolution capability is the ability to distinguish between two signals that are close together. The sampling theorem as applied to the frequency domain requires uniform sampling by the channels at greater than

twice the frequency interval of interest (Stremler, 1979). Consequently, for the presented MCSA which has 64 channels of 8 MHz each, the spectral resolution is 16 MHz which a minimum separation of 16 MHz to resolve two closely placed signals. Resolution can be improved channels increasing the number of samples or Sampling, in practice, must frequency interval. greater than the theoretical minimum of twice the interval (Nyquist rate). Filters are not perfectly rectangular but have sloping transition bands which produce distortion known as aliasing (Ziemer, 1976).

Since the noise power in a channel is directly proportional to bandwidth (n = KTB), it is desirable to reduce the channel width as much as possible. However, for a filter bandwidth, B, it takes at least 1/B seconds for the filter to settle. In addition, increasing analogintegration time over 10 seconds produces marginal improvement in SNR due to the problem of 1/f noise (Leger, 1976). However, digital integration is immune to this problem and can perform integration on a channel for extended periods of time.

The upper limit on the reception bandwidth is set by the computational speed of the computer and its memory size. The lower limit on the width of the bin is set by the stability of the system's components such as: local oscillators, amplifiers, power supplies, and filters.

### 2.2 Swept Spectrum Analyzers

apalyzer is basically swept spectrum superheterodyne receiver where the local oscillator is swept across the frequency band of interest. The local oscillator and RF input signal are applied to a mixer and the output intermediate frequency (IF) is bandpass filtered and detected. The swept spectrum analyzer is a common laboratory instrument. In the following, operation is described and compared to the MCSA.

Spectrum analyzers of this type are capable of very wide frequency sweeps (spectrum range), limited mostly by the the sweeping capability of the local oscillator (Adam, 1969). Using multiple frequency conversion techniques, improves the total reception bandwidth, but not the spectrum width. The spectrum width can be increased by increasing the sweep range of the local oscillator. A device that has this property is the backward-wave oscillator (BWO).

A BWO differs from conventional microwave oscillators in that the output frequency of oscillation is not determined by resonant circuits, but by a frequency-selective feedback and amplification process. This device is capable of voltage-tuned bandwidths of up to 5:1. A typical BWO has a range of 2 - 4 GHz. Thus, the spectrum width for a spectrum analyzer employing this device would be 2 GHz.

Serious problems with the swept spectrum analyzer are stability the BWO and linearity in the Phase-locked loop techniques have been employed stabilize the sweeping system for the BWO with the result that inherent FM can be reduced to less than +1 KHz (Adam, The linearity of mixers with respect to bandwidth 1969). and dynamics is difficult to improve. Optimal can be achieved by using small bandwidths and ensuring the input RF signal is small compared to the local oscillator for minimal intermodulation distortion.

Resolution is an important characteristic of a spectrum analyzer. It is affected by the width and shape of the IF passband and by the frequency sweep rate of the local oscillator. If two frequencies are spaced closer than the passband of the IF passband filter, then only a single response will occur. If the local oscillator is swept too fast past a signal, the detector will not have time to respond completely. Resolution is also affected by linearity of the swept local oscillator. Any inherent FM in the local oscillator will be displayed since the detector cannot differentiate between the input signal and the undesired FM signal from the local oscillator.

Simplicity of the MCSA makes it more advantageous than the swept spectrum analyzer. Local oscillators are stationary and phase-locked to a single reference. This eliminates the need for complicated circuitry required to control the linearity of sweep, maintain constant

amplitude, and control FM noise.

The mixers in the MCSA are used only in the relatively narrow frequency range of the channel filters and with a stationary oscillator. Consequently, the mixer has a linear response across that range. In addition, virtually all intermodulation products are produced well away from the IF band and are heavily suppressed by the IF bandpass filter.

The resolution of the MCSA cannot be directly compared to that of a swept system since the MCSA is optimized for detection of signals buried in noise. Signals that are spaced closer than the channel bandwidth of 8 MHz will not be resolved separately. However, the detector bandwidth, after synchronous detection and integration, is the inverse of the integration time of 6 seconds or 0.17 Hz. A typical swept system has a minimum detection bandwidth of 1 kHz.

# 2.3 Lock-in Amplification

As mentioned in the Introduction, lock-in used in phase-sensitive detection systems for the measurement of amplitude and phase of periodic signals noise and interference. The typical lock-in phase-sensitive detector, amplifier consists of preamplifiers, post-detection amplifiers, and extensive (Meade, reference processing 1983). functional description of lock-in amplification follows with emphasis placed on its application to the design of the MCSA.

Lock-in amplification is used in two main areas of experimental activity. The first area of use is in signal acquisition or recovery of modulated signals from noise. The second area of use is in precision measurement of signals where noise is not a problem. The first case is of direct interest for this thesis.

Conventional lock-in amplifiers have been optimized for use in the range of 1 kHz to 1 MHz. This is due to a large majority of applications requiring such a frequency range and electronics is readily available for this range. The techniques of lock-in amplification can be applied frequency, but compromises are necessary accommodate technical problems. Αt radio frequencies, there are problems with amplifiers, since operational amplifiers with their characteristic high gains, high input impedance, and low output impedance, do not function much beyond a few megahertz. In general, at high frequencies, all components of an electronic system start to deviate significantly from the ideal, thus making the required compensations more complicated.

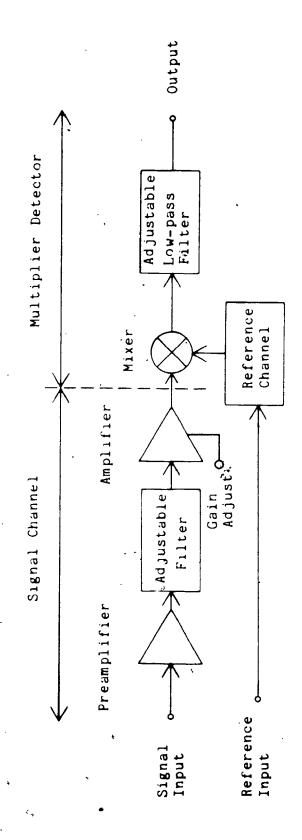

The phase-sensitive detector, which is at the heart of the lock-in amplifier, was originally developed by Dicke (1946). This detector was developed for a receiver system known as the Dicke receiver (see section 3.5 for details). The basic lock-in amplifier consisting of a preamplifier, adjustable filter, variable gain amplifier, mixer, reference channel, and adjustable low-pass filter, is shown in figure 2.2 (Meade, 1983).

The preamplifier on the input of the lock-in amplifier is a low-noise amplifier. The first stage of amplification must have good noise characteristics rather than gain, so that noise produced in this amplifier does not bury the signal further into noise.

The adjustable filter in the signal channel limits the noise bandwidth to the vicinity of the signal frequency. This is important mainly to keep the front stage amplifiers out of saturation. This is possible in wideband situations where random noise pulses may add up and drive the amplifier into saturation, resulting in distortion and intermodulation.

In the detector section, it is essential to have an ideal multiplier. It must have a linear performance under all applied levels of signal and noise. Departure from

Figure 2.2 Block diagram of a lock-in amplifier.

linearity will give rise to distortion. The switching multiplier or phase-sensitive detector provides the widest linear dynamic range for signal-recovery systems (Meade, 1983). In this case, the multiplier is driven by a square-wave switching waveform that is synchronized to the applied reference waveform.

The switching waveform is derived from the reference channel and is triggered by the positive-going edge of the reference channel. A calibrated phase control can phase shift the switching waveform with respect to the reference, independent of frequency.

The adjustable low-pass filter usually has a relatively long time constant or narrow bandwidth to reduce high frequency noise. However, there must be a compromise on the bandwidth since, as it decreases, there will be greater tracking error of the output to follow a changing signal. Most low-pass filters are simple one-stage or two-stage RC filters.

Commercial lock-in amplifiers are often specified by the word 'capability'. Systems that are described as 'capable' are those that can withstand very low levels of input SNR· (ie., -20 dB) while maintaining a linear response to a synchronous signal (Meade, 1983). SNR improvement in a lock-in amplifier is limited only by the minimum bandwidth of the output filter of the synchronous detector. This improvement is only realized provided that the desired signal is fixed in amplitude and phase for the

duration of the experiment and the settling time of the output filter.

The improvement factor supplied by synchronous detection is  $B_i/B_0$  where  $B_i$  is the input bandwidth and  $B_0$  is the output bandwidth. The output signal-to-noise ratio (SNR $_0$ ) is given by:

$$SNR_{o} = \frac{B_{i}}{B_{o}} SNR_{i}$$

2.1

The multichannel spectrum analyzer is essentially a multichannel lock-in system with each channel designed as a simple lock-in amplifier. The front-end, wideband, low-noise amplifiers on the MCSA are equivalent to the preamplifiers of the basic lock-in amplifier (see The front-end filters and filter banks of the MCSA are equivalent to the signal channel filter of the lock-in The synchronous detector of the MCSA amplifier. equivalent to the multiplier detector section of lock-in amplifier. The MCSA has, in addition, a number of mixers and local oscillators, but these only provide frequency translation and do not affect the amplifier.

The MCSA, as mentioned in the previous section, has a minimum output bandwidth of 0.17 Hz. For an input signal buried in white noise within the reception bandwidth of 512 MHz, the improvement factor by equation 2.1 is 94.8 dB. For a band limited input signal of 8 MHz, the

improvement factor is 76.7 dB.

## Chapter 3

### Overview of the Multichannel Spectrum Analyzer

3.1 Noise, Shielding, and Ground considerations

To realize the full potential of parallel processing in spectrum analysis, the problems of electromagnetic interference (EMI) must be considered. At frequencies above a few megahertz, electromagnetic interference (EMI) becomes a significant problem. At a few hundred megahertz, EMI problems are severe and require the same attention as the circuits being developed.

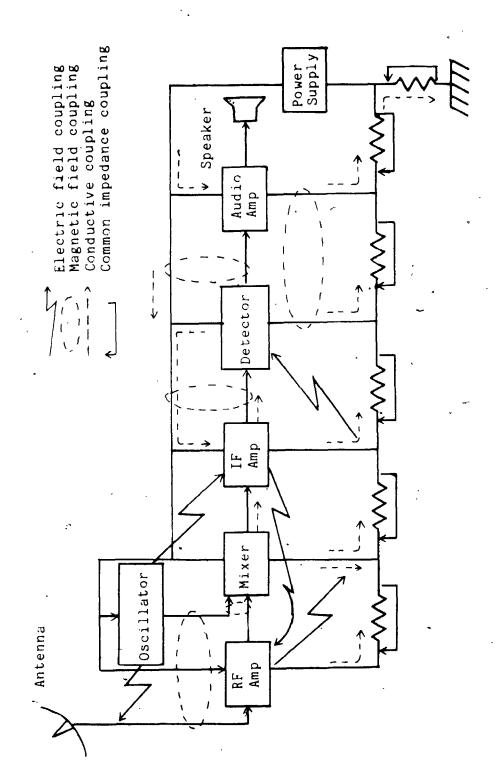

Figure 3.1 shows a simple block diagram of heterodyne radio receiver with all the possible problems associated with improper shielding and grounding (Ott, 1976). The interface generated within a system can be divided into four parts: electric field coupling, magnetic field coupling, conductive coupling, and common impedance coupling. The wiring between various stages of a system are conductors of noise and some stages are The ground currents flowing from sources of noise. various stages flow through common impedances and produce a noise voltage on the ground bus.

Noise "can be broadly defined as any undesired electrical signal present in a circuit. Nonlinearities that produce unwanted signals in a circuit are not noise but distortion products resulting from imperfectly built

Figure 3.1 Electromagnetic interference in a common heterodyne radio receiver (Ott, 1976).

circuits. There are basically three categories of noise: intrinsic noise due to the nature of physical systems (ie.; thermal noise, shot noise); man-made noise due to motors, switches, etc.; and natural disturbances such as lightning and the signals generated by sun spots.

Electric field coupling of noise between two circuits is analogous to capacitive coupling between the circuits under consideration. Likewise, if a time varying magnetic field couples two conductors from two circuits, then this can be represented by a mutual inductance between the two.

Conductive coupling of noise into a circuit is a serious problem and can best be realized by considering the power leads of a circuit that may run through a noisy environment, pick up the noise, and conduct it into the circuit.

Noise coupling through common impedance occurs when currents from two different sources flow through a common impedance. The typical situation is when two circuits have a common ground and the two ground currents flow through the common ground impedance. The result is that one circuit sees the ground potential modulated by the ground current of the second circuit as it flows through the common ground impedance (Ott, 1979).

Noise can result from the galvanic action between dissimilar metals. Water vapour or moisture between the two metals produces a chemical wet cell. The galvanic action causes positive ions from one metal (anode) to be

transferred to the other metal (cathode) which leads to corrosion of the anode. The rate of corrosion depends on the ambient moisture content and the relative separation of the metals in the galvanic series. For example, a poor combination of metals is copper and aluminum with the result that aluminum is corroded away from the copper. Plating the copper with lead-tin solder reduces this corrosion considerably since the solder is closer to aluminum in the galvanic series (Ott, 1979).

Noise due to electrolytic action occurs when any two metals with an electrolyte (moisture) have a direct current flowing through them.

An effective way to reduce the problems of capacitive coupling is through the use of shielding to break the capacitive link between two circuits. This can best be illustrated by considering capacitive coupling between two conductors, one of which is shielded (ie., coaxial cable).

Figure 3.2 shows the equivalent circuit for a conductor capacitively coupled to a coaxial cable. The equivalent circuit accounts for extension of the centre conductor beyond the shield and termination in a finite resistance to ground. The noise voltage coupled to the centre conductor with a grounded shield is given by:

$$v_n = \frac{SRC_{12}v_1}{1+SR(C_{12}+C_{2g}+C_{2s})}$$

3.1

Minimizing  $C_{12}$  by reducing the extension beyond the shield

Figure 3.2 Capacitive coupling between a conductor and a shielded conductor.

and providing a good RF ground on the shield will minimize the capacitively coupled noise voltage. Multiple ground points on the shield should not be spaced further than 1/20th of a wavelength of the highest significant frequency (Ott, 1976).

Generally, some of the impedances in figure 3.2 are much smaller than others.

$$R << \frac{1}{S(C_{12} + C_{2g} + C_{2s})}$$

3.2a

then from equation 3.1

$$V_{n} = SRC_{12}V_{1}$$

3.2b

This is the noise voltage due to the capacitance  $(C_{12})$  between the external conductor and the exposed centre conductor of the coaxial cable. If the coaxial cable is braided, then  $C_{12}$  will also include capacitive coupling through the holes in the shield.

The problems associated with magnetic field coupling can be understood by considering a similar circuit to that considered for the capacitive coupling case. Figure 3.3 illustrates the magnetic coupling case between a conductor and a shielded coaxial cable. The basic equations for inductive coupling into a closed loop are:

Figure 3.3 Magnetic coupling between a conductor and a shielded conductor.

$$V_{n} = \frac{-d}{dt} \int_{A} \overline{B} \cdot \overline{A} dA$$

3.3a

$$V_s = SBACos\theta = SMI_s$$

3.3b

where B = magnetic flux density

A = area of closed loop

$V_n = induced noise voltage$

V<sub>c</sub> = induced shield noise

M = mutual inductance

I = induced shield current

R<sub>e</sub> = shield resistance

Consider now the case of magnetic coupling between the shield and the inner conductor. If one assumes that the shield is a a very thin tubular conductor, then for a uniform axial current flowing in it, all of the magnetic field is external to the tube and none is internal. (Ott, 1976). Since the magnetic flux produced by the shield also links the inner conductor, the inductance of the shield equals the mutual inductance between the shield and the inner conductor (Ott, 1976).

The voltage,  $V_n$ , induced in the centre conductor by a shield current of  $I_s$  is given by:

$$V_n = SMI_s$$

3.4a

$$V_{s} = I_{s}(SL_{s}+R_{s})$$

3.4b

$$\therefore V_n = \frac{SMV_s}{SL_s + R_s}$$

3.4c

$$\therefore V_n = \frac{SV_S}{S + R_S / L_S}$$

3.4d

The last equation implies a cutoff frequency of  $f_c = R_s/(2\pi L_s)$  which is in the audio frequency band for most coaxial cables (eg., for RG-58C,  $f_c = 2$  kHz).

The external magnetic field can be eliminated if there is a shield current equal and opposite to that flowing in the centre conductor. The fields produced by the centre conductor and the shield will cancel. Therefore, in order to successfully reduce radiation of magnetic fields from a conductor, the shield should be grounded at both ends. It should be noted that magnetic shielding at high frequencies above cutoff is not due to the magnetic shielding properties of the shield but is due to the return current on the shield generating a field that cancels the centre conductor's field (Ott, 1976).

At frequencies below cutoff, a ground plane will provide a better return path than the shield because it will have lower effective inductance than the mutual inductance between the shield and centre conductor. Below cutoff, the shield is one of the circuits conductors where any noise current in it will produce an IR drop and hence a noise voltage. For maximum noise protection at low

frequencies, the shield should not be one of the signal conductors. One end of the circuit must be isolated from ground to eliminate a ground plane return path.

Double-shielded or triaxial cables can eliminate noise problem altogether since the noise current flows on the outer shield and the return signal current inner shield. The two currents, therefore, do not Triaxial cables flow through a common impedance. However, ordinary coaxial cables behave like expensive. triaxial cables at frequencies above 1 MHz due to a phenomena known as skin effect. In this situation noise current flows on the outside surface of the shield and the signal current flows on the inside surface.

The proper use of grounding is one of the primary ways of reducing noise in any electronics system. The two basic objectives involved in the design of good grounding systems are: elimination of common ground impedances which will generate noise voltages if currents from other circuits pass through it; and elimination of ground loops which are susceptible to magnetic fields. Most electronic systems require three types of grounds: one for equipment enclosures (eg., chassis, racks), one for noisy high power circuits (eg., motors), and one for the signal grounds of low-level circuits.

Shields for amplifiers should always be connected to the common point of the amplifier even if it is at a different potential than ground. If it is connected to another convenient ground then capacitive coupling (between: shield-input, shield-output, shield-common) could setup feedback conditions for oscillation. When the shield is connected to the amplifier's common point, one capacitive coupling is shorted and the feedback eliminated. Shielded cables for differential amplifiers at low frequencies should be grounded at one end only. Grounding should be at the common point of the source or the common point of the amplifier, never both.

At high frequencies where cables are more than 1/20th of a wavelength, capacitive coupling tends to complete ground loops at several points, thus making it impossible to isolate the unterminated end. For long cables, grounding may be required at least every 1/10th of a wavelength.

The shielding effectiveness of metallic sheets consists of absorption loss, reflection loss, and a correction factor to account for multiple reflections (Manassewitsch, 1976). In practice, a solid shield enclosing a circuit can provide more than 90 dB of shielding effectiveness (Ott, 1976). However, this shielding is often degraded by leakage through seams, joints, and holes.

Leakage from a seam or hole depends on the maximum linear dimension of the opening, the wave impedance, and the frequency of the source. For best shielding, the noise induced currents in the shield should be allowed to

flow undisturbed in the manner in which they were induced by the incident field. These currents will generate additional fields that will tend to cancel the original field. Thus a series of small circular holes will be much better at shielding than a large hole of the same area in the shield.

Seams may be required in some cases (eg., lids for boxes) and here, effective shielding can be maintained with the use of EMI gaskets. The gaskets ensure uniformity of current flow around the box. Lids with flanges reduce EMI as well by increasing the surface area around the lid's perimeter for better electrical contact and for capacitive coupling to the walls of the box.

Passive components located in the low-level electronic portions of a circuit can be major contributors of noise. Components such as: resistors, capacitors, diodes. and transformers have different noise characteristics and must be treated differently.

Resistors, theoretically, produce a noise power equal to KTB. However, this ignores the effect of 1/f noise or excess noise which is dependant on the construction of the resistor. Generally, the more uneven the DC current flows through the resistor, the more excess noise is generated (Motchenbacher, 1973). Composition carbon resistors usually generate the greatest noise, whereas tin oxide, metal film, and wire-wound are all lower noise devices. All resistors used in the construction of the MCSA were

low-noise carbon film resistors (Philips, CR carbon film).