#### Western Graduate & Postdoctoral Studies

# Western University Scholarship@Western

Electronic Thesis and Dissertation Repository

5-21-2013 12:00 AM

### Design and Evaluation of FPGA-based Hybrid Physically Unclonable Functions

Sasan Khoshroo The University of Western Ontario

Supervisor Arash Reyhani-Masoleh *The University of Western Ontario*

Graduate Program in Electrical and Computer Engineering A thesis submitted in partial fulfillment of the requirements for the degree in Master of Engineering Science © Sasan Khoshroo 2013

Follow this and additional works at: https://ir.lib.uwo.ca/etd

Part of the Electrical and Electronics Commons, Electronic Devices and Semiconductor Manufacturing Commons, and the VLSI and Circuits, Embedded and Hardware Systems Commons

#### **Recommended Citation**

Khoshroo, Sasan, "Design and Evaluation of FPGA-based Hybrid Physically Unclonable Functions" (2013). *Electronic Thesis and Dissertation Repository*. 1281. https://ir.lib.uwo.ca/etd/1281

This Dissertation/Thesis is brought to you for free and open access by Scholarship@Western. It has been accepted for inclusion in Electronic Thesis and Dissertation Repository by an authorized administrator of Scholarship@Western. For more information, please contact wlswadmin@uwo.ca.

### DESIGN AND EVALUATION OF FPGA-BASED HYBRID PHYSICALLY UNCLONABLE FUNCTIONS

by

Sasan Khoshroo

#### Graduate Program in Electrical and Computer Engineering

A thesis submitted in partial fulfillment of the requirements for the degree of

Master of Engineering Science

The School of Graduate and Postdoctoral Studies Western University

London, Ontario, Canada

© Sasan Khoshroo 2013

#### Abstract

A Physically Unclonable Function (PUF) is a new and promising approach to provide security for physical systems and to address the problems associated with traditional approaches. One of the most important performance metrics of a PUF is the randomness of its generated response, which is presented via uniqueness, uniformity, and bit-aliasing. In this study, we implement three known PUF schemes on an FPGA platform, namely SR Latch PUF, Basic RO PUF, and Anderson PUF. We then perform a thorough statistical analysis on their performance. In addition, we propose the idea of the Hybrid PUF structure in which two (or more) sources of randomness are combined in a way to improve randomness. We investigate two methods in combining the sources of randomness and we show that the second one improves the randomness of the response, significantly. For example, in the case of combining the Basic RO PUF and the Anderson PUF, the Hybrid PUF uniqueness is increased nearly 8%, without any pre-processing or post-processing tasks required.

Two main categories of applications for PUFs have been introduced and analyzed: authentication and secret key generation. In this study, we introduce another important application for PUFs. In fact, we develop a secret sharing scheme using a PUF to increase the information rate and provide cheater detection capability for the system. We show that, using the proposed method, the information rate of the secret sharing scheme will improve significantly.

**Keywords:** FPGA, Hardware Security, Information Rate, Message Authentication Code, Physically Unclonable Functions, Robust Secret Sharing, VHDL

## Acknowlegement

The author would like to thank Dr. Arash Reyhani-Masoleh and Dr. Shahriar B. Shokouhi for their valuable support and help.

## Contents

| A  | bstrac  | et            |                                    | ii  |

|----|---------|---------------|------------------------------------|-----|

| A  | eknov   | vlegeme       | ent                                | iii |

| Li | st of ] | Figures       |                                    | vii |

| Li | st of ' | <b>Fables</b> |                                    | ix  |

| Li | st of . | Abbrevi       | ations                             | X   |

| Li | st of ] | Notatio       | ns                                 | xi  |

| 1  | Intr    | oductio       | n                                  | 1   |

|    | 1.1     | PUF C         | Constructions                      | 2   |

|    | 1.2     | PUF P         | Performance Metrics and Properties | 3   |

|    | 1.3     | PUF A         | Applications                       | 4   |

|    | 1.4     | Thesis        | Outline and Contributions          | 5   |

| 2  | Lite    | rature ]      | Review                             | 7   |

|    | 2.1     | PUF A         | applications                       | 7   |

|    |         | 2.1.1         | Authentication                     | 7   |

|    |         | 2.1.2         | Secret Key Generation              | 8   |

|    | 2.2     | Memo          | ry-based PUFs                      | 8   |

|    | 2.3     | Delay-        | based PUFs                         | 11  |

|    |         | 2.3.1         | Arbiter PUF                        | 11  |

|    |         | 2.3.2         | RO PUF                             | 14  |

|    |         | 2.3.3         | Glitch PUF                         | 21  |

| 3 | Imp  | lementa | ation Results                                     | 25                                             |

|---|------|---------|---------------------------------------------------|------------------------------------------------|

|   | 3.1  | PUF P   | Performance Metrics                               | 25         26         26         26         27 |

|   |      | 3.1.1   | Reliability                                       | 26                                             |

|   |      | 3.1.2   | Uniqueness                                        | 26                                             |

|   |      | 3.1.3   | Uniformity                                        | 27                                             |

|   |      | 3.1.4   | Bit-aliasing                                      | 27                                             |

|   | 3.2  | Design  | n concepts: Basic PUFs                            | 27                                             |

|   |      | 3.2.1   | SR Latch PUF                                      | 28                                             |

|   |      | 3.2.2   | Basic RO PUF                                      | 29                                             |

|   |      | 3.2.3   | Anderson PUF                                      | 30                                             |

|   | 3.3  | Design  | n Concepts: The Proposed Hybrid PUF               | 31                                             |

|   |      | 3.3.1   | RO/Anderson Hybrid PUF, Method 1                  | 32                                             |

|   |      | 3.3.2   | RO/Anderson Hybrid PUF, Method 2                  | 33                                             |

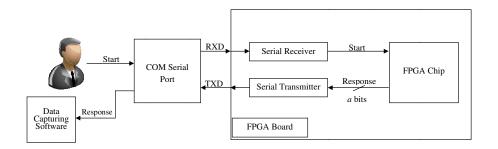

|   | 3.4  | Implei  | mentation Details and the Measurement System      | 36                                             |

|   |      | 3.4.1   | Design Parameters                                 | 36                                             |

|   |      | 3.4.2   | Measurement System                                | 39                                             |

|   | 3.5  | Result  | s and Discussion                                  | 41                                             |

| 4 | Secr | et Shar | ring Based on Physically Unclonable Functions     | 53                                             |

|   | 4.1  | Introd  | uction                                            | 53                                             |

|   | 4.2  | Relate  | d Work                                            | 55                                             |

|   | 4.3  |         | inaries                                           | 56                                             |

|   |      | 4.3.1   | Ito, Saito, and Nishizeki's Constructions         | 57                                             |

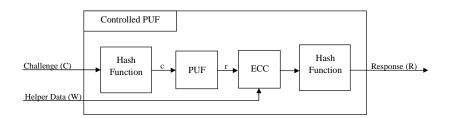

|   |      | 4.3.2   | Controlled PUFs                                   | 57                                             |

|   | 4.4  | Our Pr  | roposed Model                                     | 58                                             |

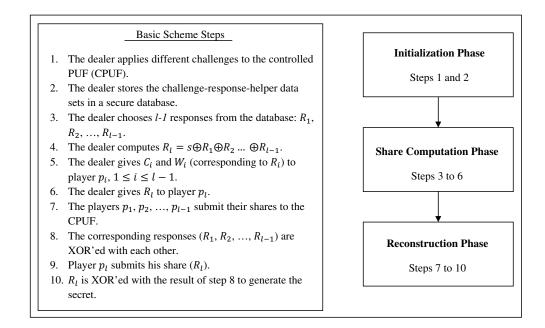

|   |      | 4.4.1   | Basic Scheme                                      | 58                                             |

|   |      |         | Information Rate                                  | 60                                             |

|   |      |         | Security Analysis                                 | 62                                             |

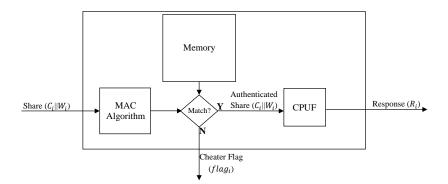

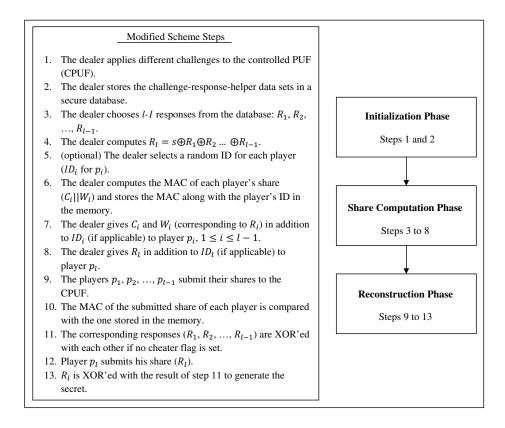

|   |      | 4.4.2   | Modified Scheme With Cheater Detection Capability | 63                                             |

|   |      |         | Security Analysis                                 | 68                                             |

|   |      |         |                                                   |                                                |

|                  | 4.4.3      | PUF requirements | 69 |

|------------------|------------|------------------|----|

| 5                | Conclusion | and Future Work  | 70 |

| Bi               | bliography |                  | 72 |

| A                | Response S | amples           | 80 |

| B                | Hybrid PU  | F VHDL Code      | 82 |

| Curriculum Vitae |            | 93               |    |

## **List of Figures**

| 1.1  | A general PUF-based authentication scheme [1]              | 4  |

|------|------------------------------------------------------------|----|

| 1.2  | A secret key generation scheme using PUF [1]               | 6  |

| 2.1  | SRAM cell logic circuit                                    | 9  |

| 2.2  | Different memory-based PUF structures                      | 10 |

| 2.3  | A basic Arbiter PUF design [2]                             | 12 |

| 2.4  | The feed-forward Arbiter PUF design [2]                    | 13 |

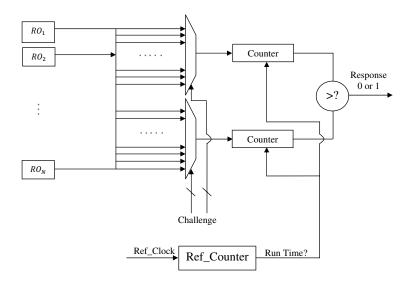

| 2.5  | An architecture of an RO PUF [1]                           | 14 |

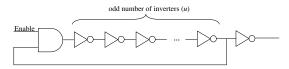

| 2.6  | A basic ring oscillator circuit                            | 14 |

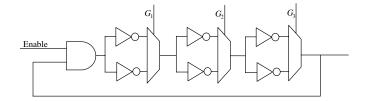

| 2.7  | Maiti's Configurable RO [3]                                | 15 |

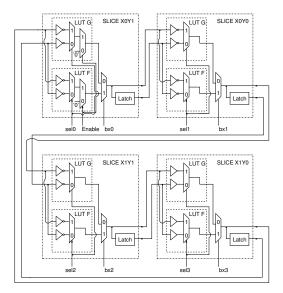

| 2.8  | Xin's Configurable RO in One CLB [4]                       | 17 |

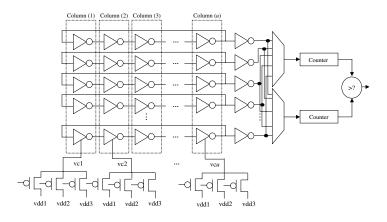

| 2.9  | Multi-voltage RO PUF [5]                                   | 18 |

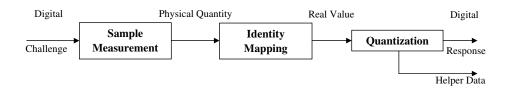

| 2.10 | The RO PUF with identity-mapping [6]                       | 18 |

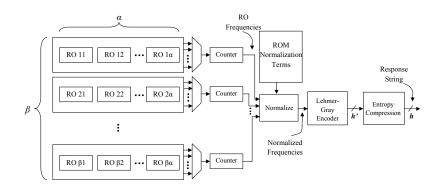

| 2.11 | The RO PUF structure proposed in [7]                       | 20 |

| 2.12 | The proposed Anderson PUF circuit [8]                      | 22 |

| 2.13 | PUF response bit generation [8]                            | 22 |

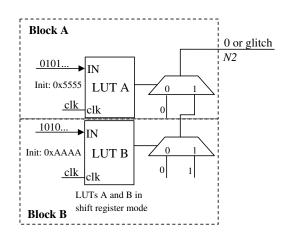

| 2.14 | The Glitch PUF [9]                                         | 23 |

| 3.1  | The NAND-based SR Latch [10]                               | 28 |

| 3.2  | Tuning the glitch width in the Anderson PUF                | 31 |

| 3.3  | The proposed RO/Anderson Hybrid PUF structure, method $1$  | 32 |

| 3.4  | The proposed RO/Anderson Hybrid PUF structure, method 2    | 34 |

| 3.5  | The proposed RO/SR Latch Hybrid PUF structure              | 36 |

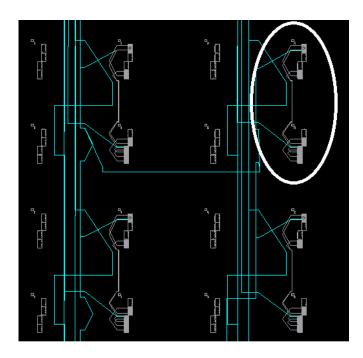

| 3.6  | Four identical ring oscillators implemented as hard macros | 38 |

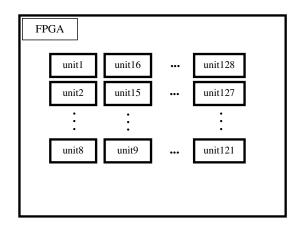

| 3.7  | 2-Dimensional placement of PUF units                       | 39 |

| 3.8  | Separating the RO/SR Latch PUF units                             | 40 |

|------|------------------------------------------------------------------|----|

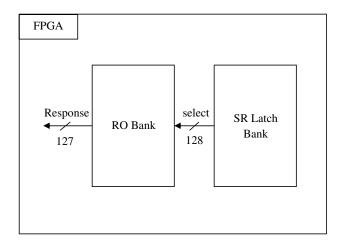

| 3.9  | The measurement system block diagram                             | 40 |

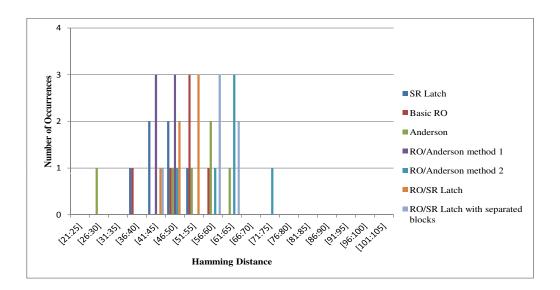

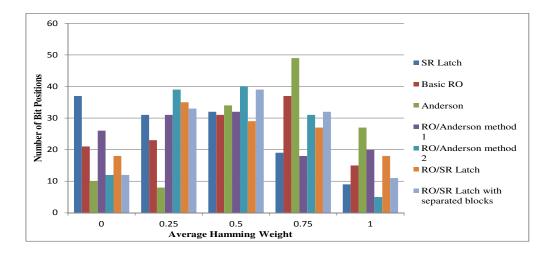

| 3.10 | Comparison between different schemes in terms of Uniqueness .    | 43 |

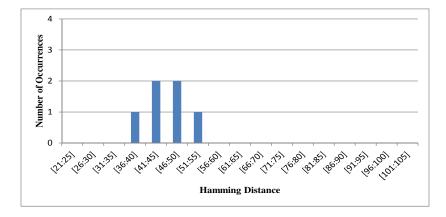

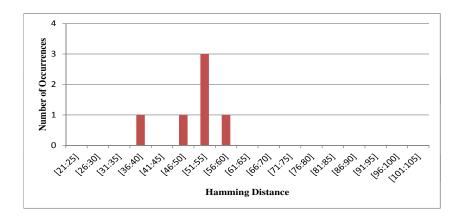

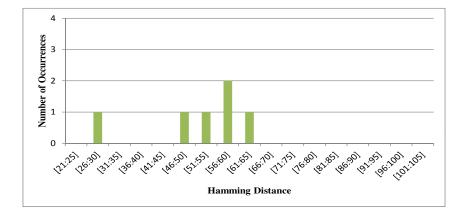

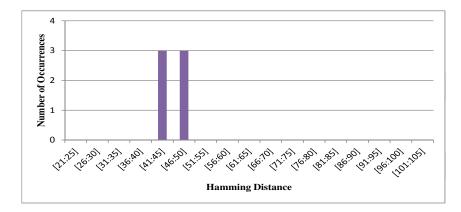

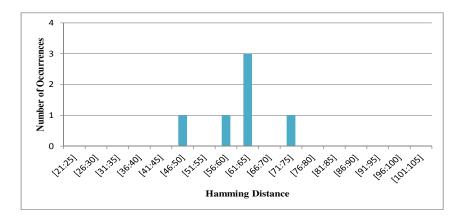

| 3.11 | Uniqueness of the SR Latch PUF structure                         | 44 |

| 3.12 | Uniqueness of the Basic RO PUF structure                         | 44 |

| 3.13 | Uniqueness of the Anderson PUF structure                         | 44 |

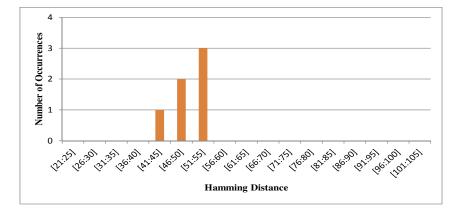

| 3.14 | Uniqueness of the RO/Anderson Hybrid PUF structure, method 1     | 45 |

| 3.15 | Uniqueness of the RO/Anderson Hybrid PUF structure, method 2     | 45 |

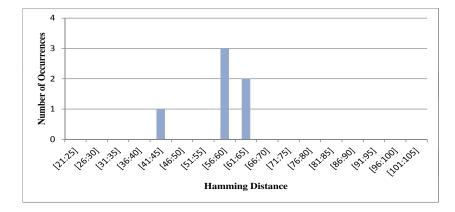

| 3.16 | Uniqueness of the RO/SR Latch Hybrid PUF structure               | 45 |

| 3.17 | Uniqueness of the RO/SR Latch Hybrid PUF structure 2             | 46 |

| 3.18 | Comparison between different schemes in terms of bit-aliasing .  | 46 |

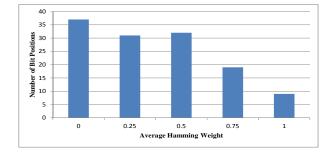

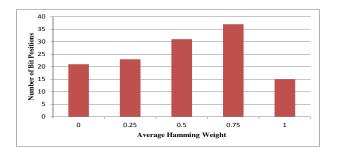

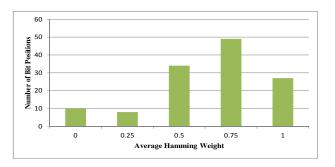

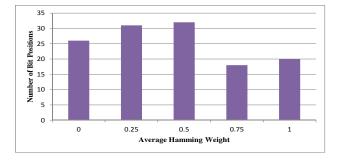

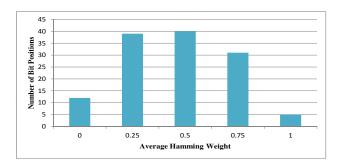

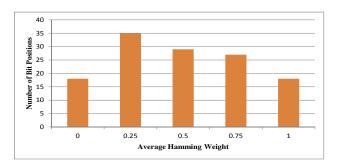

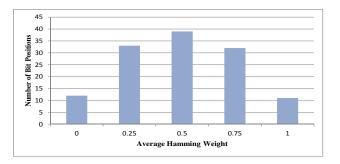

| 3.19 | Bit-aliasing of the SR Latch PUF structure                       | 47 |

| 3.20 | Bit-aliasing of the Basic RO PUF structure                       | 47 |

| 3.21 | Bit-aliasing of the Anderson PUF structure                       | 47 |

| 3.22 | Bit-aliasing of the RO/Anderson Hybrid PUF structure, method 1   | 48 |

| 3.23 | Bit-aliasing of the RO/Anderson Hybrid PUF structure, method 2   | 48 |

| 3.24 | Bit-aliasing of the RO/SR Latch Hybrid PUF structure             | 48 |

| 3.25 | Bit-aliasing of the RO/SR Latch Hybrid PUF structure 2           | 48 |

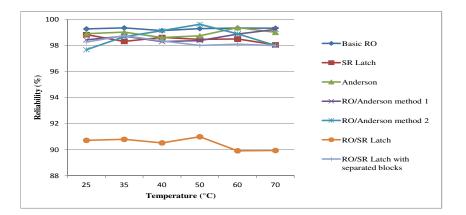

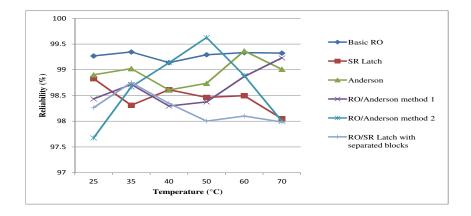

| 3.26 | The effect of the ambient temperature on all PUF structures      | 49 |

| 3.27 | The effect of the ambient temperature on all PUF structures 2    | 50 |

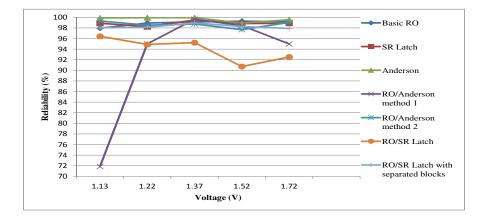

| 3.28 | The effect of the FPGA chip supply voltage on all PUF structures | 51 |

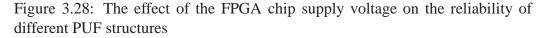

| 4.1  | The basic idea of a controlled PUF [11, 12]                      | 58 |

| 4.2  | The Basic Scheme design steps                                    | 60 |

| 4.3  | The proposed modified scheme with cheater detection capability   | 64 |

| 4.4  | The Modified Scheme design steps                                 | 66 |

|      |                                                                  |    |

## **List of Tables**

| 2.1 | Comparing the performance of different PUF schemes  | 24 |

|-----|-----------------------------------------------------|----|

| 3.1 | RO/Anderson Hybrid PUF method 1 different scenarios | 33 |

| 3.2 | RO/Anderson Hybrid PUF method 2 different scenarios | 34 |

| 3.3 | PUF implementation parameters                       | 37 |

| 3.4 | PUF Implementation results                          | 42 |

| 3.5 | Comparison between different structures             | 51 |

## **List of Abbreviations**

| BCH    | Bose-Chaudhuri-Hochquenghen                         |

|--------|-----------------------------------------------------|

| CLB    | Configurable Logic Block                            |

| CPUF   | Controlled Physically Unclonable Function           |

| CRP    | Challenge-Response Pair                             |

| ECC    | Error Correcting Code                               |

| EEPROM | Electrically Erasable Programmable Read-Only Memory |

| FPGA   | Field Programmable Gate Array                       |

| HD     | Hamming Distance                                    |

| HW     | Hamming Weight                                      |

| LUT    | Lookup Table                                        |

| MAC    | Message Authentication Code                         |

| PAR    | Place And Route                                     |

| PUF    | Physically Unclonable Function                      |

| RO     | Ring Oscillator                                     |

| ROM    | Read-Only Memory                                    |

| RTL    | Register-Transfer Level                             |

| SRAM   | Static Random-Access Memory                         |

## **List of Notations**

| b                  | The ECC syndrome bit-size                                             |

|--------------------|-----------------------------------------------------------------------|

| q                  | The secret key bit-size                                               |

| r                  | The PUF response                                                      |

| С                  | The PUF challenge                                                     |

| R                  | The controlled PUF output (response)                                  |

| C                  | The controlled PUF input (challenge)                                  |

| $A^*$              | The additional arbiter in the feed-forward Arbiter PUF                |

| N                  | Number of PUF units in the challenge-response system                  |

| u                  | Number of inverters in the RO feedback loop                           |

| <i>Ref_Counter</i> | The reference counter in the RO PUF design                            |

| Ref_Clock          | The reference clock of the RO PUF design                              |

| $\gamma$           | Number of ring oscillators in each RO block in the 1-out-of- $\gamma$ |

|                    | masking scheme                                                        |

| $G_i$              | The <i>i</i> -th select bit in Maiti's configurable RO                |

| $bx_i$             | The <i>i</i> -th select bit in Xin's configurable RO                  |

| $sel_i$            | The <i>i</i> -th select bit in Xin's configurable RO                  |

| d                  | Number of different supply voltage values in the multi-voltage        |

|                    | RO PUF design                                                         |

| $\alpha$           | Number of ROs in each RO batch in Maes's RO PUF                       |

| eta                | Number of RO batches in Maes's RO PUF                                 |

| h                  | Number of response bits generated in Maes's RO PUF after each         |

|                    | $\beta$ simultaneous frequency measurements                           |

| h'                 | The Lehmer-Gray Encoder output bit-size in Maes's RO PUF              |

| N2                 | The top carry chain multiplexer output in the Anderson PUF            |

| n                  | Number of players in the secret sharing scheme                        |

| $p_i$              | The <i>i</i> -th player in the secret sharing scheme                  |

| P                  | The set of all players in the secret sharing system                   |

| s ,                | The secret to be shared using the secret sharing scheme               |

| s'                 | The reconstructed secret using the secret sharing scheme              |

| k                  | The threshold value in Shamir's secret sharing scheme                 |

| $\rho_{\alpha}$    | Information rate of a secret sharing scheme                           |

| $S \\ G$           | The set of secrets to be shared using the secret sharing scheme       |

| $S_p$              | The set of the shares given to the player $p$                         |

| t                  | Number of fake shares submitted by dishonest players                  |

| $key_j$      | The authentication key received by the player $p_j$ in the Rabin |

|--------------|------------------------------------------------------------------|

| -            | and Ben-Or scheme                                                |

| $\lambda$    | Robustness measure of a robust secret sharing scheme             |

| Ω            | Lower bound function                                             |

| $\mathbb{F}$ | Finite field                                                     |

| y            | A random element chosen from the finite field $\mathbb{F}$       |

| z            | An element of the finite field $\mathbb{F}$                      |

| Γ            | An authorized set                                                |

| ${\cal H}$   | A monotone access structure                                      |

| $\oplus$     | Bit-wise XOR                                                     |

| W            | Helper data                                                      |

| x            | The bit-size of $x$                                              |

| max          | Maximum function                                                 |

| log          | Logarithm function                                               |

| avg          | Average function                                                 |

| l            | Number of players in an authorized set                           |

|              | Concatenation                                                    |

| $flag_i$     | The cheater flag corresponding to the player $p_i$               |

| m            | Number of response samples                                       |

| a            | Number of response bits                                          |

| g            | Number of PUF instances                                          |

|              |                                                                  |

### Chapter 1

### Introduction

The traditional approach to prevent passive physical attacks such as counterfeiting, cloning, reverse engineering and the insertion of malicious components include cryptographic primitives such as encryption/decryption algorithms, digital signature schemes, and authentication codes. The problem with these types of security measures is that, they rely on the protection of the secret keys which are stored in non-volatile memory such as EEPROMs or fuses. The sensitive data stored in such memory can be read out directly through invasive attacks [1]. To counter this issue, expensive protective coatings are applied but still, the devices are vulnerable to sophisticated physical attacks.

Therefore, physically unclonable functions (PUFs) are introduced to address such problems. A PUF is a *challenge-response* primitive which is used in a physical system to provide the required security measures [1,13]. Instead of storing the secret key in a memory, it can be intrinsically generated by the PUF. In fact, a PUF generates a *response* to a given *challenge*. The idea behind the PUF is that, the output response is totally random and unpredictable. It is also unique for different instances, even if the two instances are exactly the same and use the exact same components. This is because the PUF response depends solely on the unique and random characteristics of physical devices, such as gate delays. In fact, the very important feature of a PUF is its unclonability, i.e., even if an attacker has access to the circuit and builds an exact same copy of it using the same components, the response of the new device to a given challenge would be different from that of the original device to the same challenge.

#### **1.1 PUF Constructions**

A variety of PUF constructions have been introduced during the past ten years [14]. Non-electrical PUFs include Optical PUFs [15, 16], Acoustical PUFs [17], and Coating PUFs [18]. Optical PUFs use an optical micro-structure which is built by mixing microscopic refractive glass spheres on a tiny transparent epoxy plate [15]. This micro-structure is called a token. When a laser beam is applied to the token, it will generate a random pattern that can be further processed to produce the PUF response. The pattern generated by the token will substantially change even with a slight change in the laser beam, in terms of its wavelength, angle, or focal distance. Acoustical PUFs are built upon the acoustical delay lines. An alternating electrical signal is transformed to a mechanical vibration using a transducer. This vibration propagates through a solid medium (acoustical line) which includes random scatterers. At the other end of the line, the wave is transformed back to an electrical signal. The produced electrical signal has unique properties which depend on the random physical characteristics of the acoustical line. Therefore, this electrical signal can be used as the unique PUF response. In Coating PUFs, a protective coating material is inserted onto the device using random dielectric particles which have random properties in size, shape and location. In fact, in Coating PUFs, a random element is purposely inserted into the device in order to provide more strength against physical attacks. Therefore, Coating PUFs are different from other *intrinsic* PUFs in which the random element is intrinsic to the device.

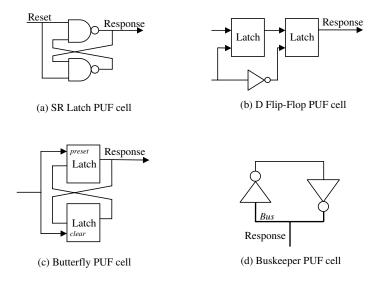

In addition, Electrical PUFs are categorized as Memory-based PUFs and Delaybased PUFs. Memory-based PUFs include SRAM, SR Latch, Flip-Flop, Butterfly, and Buskeeper PUFs [19–24]. The idea behind memory-based PUFs is to bring a bistable memory element (which can contain only 1 bit of information) into its metastable state where it is not clear to which stable state it will fall back. This settling state is totally random and unpredictable for different memory elements due to random physical variations.

Moreover, delay-based PUFs consist of Arbiter PUFs [2, 25], Ring-Oscillator PUFs (RO PUFs) [3,8,13,26–28], and Glitch PUFs [8,9,29]. The random element used in delay-based PUFs to produce response bits is the gate delay. For example, in Ring Oscillator PUFs, two identical ring oscillators produce two clocks with different frequencies. The frequency of each RO depends on the delay of the inverters used in the feedback loop of the ring oscillator. Therefore, the frequencies can be compared to each other to produce one response bit, based on which ring oscillator is faster. In this study, we focus on electrical PUFs and discuss their characteristics in more details in Chapter 2.

#### **1.2 PUF Performance Metrics and Properties**

Some of the important performance metrics of PUFs include reliability, uniqueness, uniformity, and bit-aliasing [6, 30]. Reliability of a PUF is a measure of its reproducibility. The reliability of an ideal PUF is 100%, i.e., the PUF generates the same response to a given challenge at different instances of time and under different environmental conditions. Uniqueness is a measure of *inter-distance* variations of the response bits among different PUF instances. In other words, if a specific challenge is applied at the same time and under the same conditions to two identical PUF instances, the response of the two PUFs should be different. Ideally, this value should be 50%. Uniqueness is one of the most important features of PUFs and represents the randomness of the PUF response bits [30]. Also, uniformity of a PUF measures the ratio between the number of 1's and the total number of response bits are 1 and 50% are 0, and therefore, the PUF response does not have a biased behavior towards a specific bit value. Another important factor of a PUF which also represents the randomness of the PUF response is bit-aliasing. Bit-aliasing of a given bit position in the PUF response is its percentage Hamming Weight (HW) across several PUF instances. Again, this value should be ideally 50% for all response bit positions. The definition of these properties along with their formulations are provided in details in Chapter 3.

#### **1.3 PUF Applications**

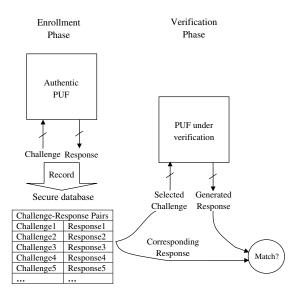

Two main applications have been introduced for PUFs: device authentication and secret key generation [1]. Authentication is performed in two steps. First, in the enrollment phase, a trusted party (authentication authority) records a number of challenge-response pairs (CRPs) in a database. Then, in the verification phase, a random challenge chosen from the database is applied to the PUF under verification and if the generated response is "close enough" to the recorded response, the PUF is verified to be authentic. Figure 1.1 shows a general PUF-based authentication scheme [1].

Figure 1.1: A general PUF-based authentication scheme [1]

One of the most important requirements of a practical PUF which is utilized in a device authentication process is a large set of challenge-response pairs (CRPs).

#### CHAPTER 1. INTRODUCTION

Because the CRP which is chosen by the authentication authority is transferred over an insecure channel, an attacker can capture and reuse this information to attack the authentication system. In order to prevent such replay attacks, each challenge-response pair should be used only once during the authentication process. Therefore, the utilized PUF should provide a large number of challengeresponse pairs so that a device can be authenticated a significant number of times before the CRP set is exhausted.

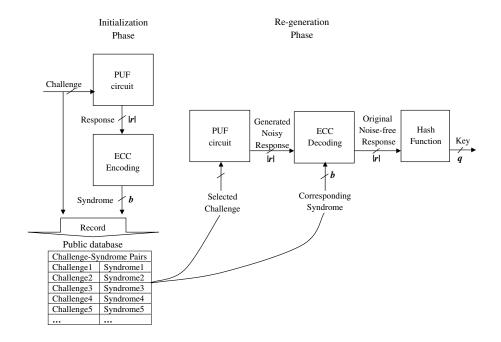

In secret key generation, on the other hand, a specific key should be regenerated for unlimited number of times. In other words, because the secret key is not stored in the system, and the PUF circuit produces it whenever it is needed, the regenerated response (key) should be 100% noise-free. As proposed by Suh et al., the secret key generator based on PUF works as follows [1]: in the initialization phase, a specific challenge is applied to the PUF and a response is generated, as shown in Fig. 1.2. Then, using an error correcting code such as BCH, the error correcting syndrome (called Helper Data) for that response is computed. The applied challenge and the syndrome are then stored publicly on a chip or a server. In the reconstruction phase, the same challenge is applied to the PUF and the noisy output will be corrected using the computed syndrome to produce the same response as the secret key. Note that, the publicly stored syndrome reveals information about the PUF response and thus the secret key. Therefore, if a *q*-bit secret key is needed and the syndrome bit-size is *b*, the number of PUF response bits should be at least |r| = b + q [1].

#### **1.4 Thesis Outline and Contributions**

In Chapter 2, we discuss different memory-based and delay-based PUFs in more details. More specifically, the construction and properties of SRAM, SR Latch, Flip-Flop, Butterfly, Buskeeper, Arbiter, Ring Oscillator, and Glitch PUFs are discussed. Additionally, more details about the PUF applications are provided. The first contribution of this thesis is introduced in Chapter 3. It includes proposing a novel Hybrid PUF structure to improve the randomness of the generated response.

Figure 1.2: A secret key generation scheme using PUF [1]

In fact, two known PUF schemes are combined in a way to take advantage of both of them. We analyze the performance of the proposed scheme in terms of reliability, uniqueness, uniformity, and bit-aliasing and compare it with other implemented schemes. The second contribution is discussed in Chapter 4. We propose an efficient secret sharing scheme based on PUF properties. The information rate which is the main factor in assessing the efficiency of a secret sharing scheme is increased using our method. Our proposed scheme also provides cheater detection capability for the system. Finally, conclusion and future work are briefly discussed in Chapter 5.

### Chapter 2

### **Literature Review**

In this chapter, we briefly review the proposed schemes in the literature related to both PUF applications and PUF design. As mentioned in the previous chapter, both memory-based and delay-based PUFs are chosen, which include SRAM, SR Latch, Flip-Flop, Butterfly, Buskeeper, Arbiter, Ring Oscillator, and Glitch PUFs. We describe the PUF structures and explain how the response bits are generated. Also, each structure's advantages and disadvantages are mentioned.

#### 2.1 **PUF Applications**

In this section, we briefly review the proposed works published in the open literature regarding the applications of PUFs.

#### 2.1.1 Authentication

As discussed before, in device authentication, there is no need to generate 100% noise-free response bits. In fact, if the generated response is "close enough" to the one stored in the database, the PUF under verification is authenticated. Therefore, the failure rate of the authentication system which is defined as the device misidentification probability [30], depends on the reliability and uniqueness properties of the utilized PUF. It also depends on the number of PUF response bits. In other words, a longer PUF response can authenticate a bigger population of devices with less failure rate [6]. In addition, the resilience of the authentication system against the replay attacks depends on the number of challenge-response pairs provided by the PUF. Thus, all the works which are proposed to either improve the reliability, uniqueness, number of response bits, and/or number of CRPs, can be considered as works related to the authentication application.

#### 2.1.2 Secret Key Generation

The main building block in a secret key generator scheme using PUF is the error correcting code (ECC) which is used to produce a 100% noise-free response. The use of 2D Hamming codes for error correction is suggested in [12]. Also, using a more realistic model of PUFs noisy properties, Suh et al. suggested the use of BCH codes as the ECC [31]. In addition, a new syndrome coding scheme that restricts the amount of leaked information by the PUF error-correcting codes is proposed in [32].

A fuzzy extractor implementation on FPGAs is proposed in [33] to generate uniformly distributed and noise-free cryptographic keys. The proposed fuzzy extractor has two stages; the first stage generates a noise-free key using an ECC, and the second stage transforms the response using a universal hash function to achieve a uniform or any other required distribution of keys. A 128-bit secret key using an RO-PUF is proposed in [13] using a fuzzy extractor which includes a BCH(255,37,45) error correcting code. In addition, Maes et al. proposed a practical low overhead secret key generation called PUFKY, which can generate a 128-bit secret key with a failure rate of  $10^{-9}$ , in 5.62 ms, and with low area overhead [7].

#### 2.2 Memory-based PUFs

As discussed before, a bistable memory cell which has 2 stable states (0 and 1), goes to the metastable state for a short period of time and then settles in one of

the 2 states. This settling state is random and unpredictable for each memory cell. Therefore, this random behavior is used to build a PUF which produces random response bits. For example, as shown in Fig. 2.1, an SRAM memory cell consists of 2 cross-coupled inverters at its core. The transient behavior of an SRAM cell when it is powered up is what an SRAM PUF is built upon [19]. Typical SRAM cells are designed to have perfectly matched inverters. However, due to uncontrol-lable process variations, the *strength* of the inverters will not match in an SRAM cell. Based on which inverter is stronger, the memory cell will settle in one of the stable states. If the difference between the strength of the inverters is significant, the produced response bit (which is the settling state of the cell) will be stable. On the other hand, if the inverters are somehow equally strong, the settling state on each *power-up* will be different due to noise effects, resulting in an unstable bit.

Figure 2.1: SRAM cell logic circuit

The power-up state of 8190 bytes of SRAM from different memory blocks on different FPGA boards are collected in [19]. The uniqueness is reported to be 49.97% and the reliability is shown to be 96.43% at normal conditions and 88% for higher temperature conditions. The main drawback of this PUF scheme is that, the response bit is generated only on the power-up state of the circuit. In other words, the response bit cannot be re-generated while the circuit is operational. This drawback makes the SRAM PUF an impractical PUF because for each sample of the response bit, one has to turn the circuit off and on again.

Other memory-based PUFs are depicted in Fig. 2.2. The basic principle of these PUFs is the same as that of the SRAM PUF: random mismatch between

nominally matched cross-coupled devices. For example, in the SR Latch PUF, 2 cross-coupled NAND (or NOR) gates constitute a simple SR Latch.

Figure 2.2: Different memory-based PUF structures

In the NAND-based SR Latch, when the *Reset* signal is 0, the output bit is 1. When the reset is released, the output bit will converge to either 0 or 1 depending on the internal mismatch between the 2 gates. 128 NOR-based SR Latches are instantiated on 19 ASICs manufactured in 130 nm CMOS technology [20]. The uniqueness and reliability at nominal conditions are reported as 50.55% and 96.96%, respectively. The main advantage of the SR Latch PUF is that the PUF response bits can be re-generated at any time when the circuit is powered and operational. In fact, we can take many samples from the response bit to analyze the PUF performance by connecting a *clock* to the Reset signal. In addition, a majority voting technique can be applied on the samples to generate more reliable bits. Flip-Flop, Butterfly, and Buskeeper PUFs behavior and principle are basically similar to those of the SRAM PUF. Like the SRAM PUF, the response bits generated by these PUFs are obtained only on the device power-up state. The power up states of 4096 Flip-Flops on 3 different FPGA boards are measured in [21]. After applying simple majority voting techniques on the output bits, the uniqueness and reliability are estimated as 50% and 95%, respectively. Also, implementation of 64 Butterfly cells on 36 FPGA boards yields a uniqueness of approximately 50% and a reliability of 95% [22]. Finally, a 8192-bit Buskeeper PUF has been implemented on an ASIC platform in [34]. The uniqueness is estimated as 48.88%. At normal conditions, the reliability is reported as 95.84% and under higher temperature conditions, it is shown to be approximately 83%.

#### 2.3 Delay-based PUFs

#### 2.3.1 Arbiter PUF

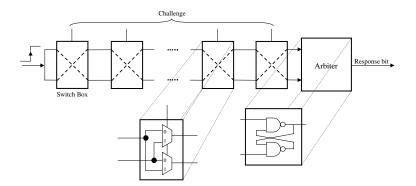

Figure 2.3 depicts a basic Arbiter PUF design proposed in [2]. The basic idea of this scheme is to let a rising-edge signal travel through two different delay paths. At the end of the delay paths, an arbiter circuit decides which path is the winner of the race. The arbiter circuit has 2 inputs and 1 output. If the rising edge arrives at the first input before it arrives at the second input, the output will be 1, and 0 otherwise. The delay paths are implemented as a chain of *switch boxes*. Each switch box has a *select* signal which determines the connection between the 2 inputs and the 2 outputs. If the *select* is 0 the connection is straight and if it is 1, the connection is crossed. As shown in the figure, the switch box can be implemented using two 2 - to - 1 multiplexers. Since there are a number of switch boxes in the chain, the set of *select* signals can be considered as the PUF challenge bits, and the outputs for each configuration can be considered as the PUF response bits. The structure of the utilized switch boxes, and thus the delay lines must be nominally perfectly symmetrical so that the output bits depend only on the random physical and manufacturing variations. Also, the arbiter circuit must be completely fair, i.e., it must not have a biased behavior towards a specific bit. As suggested by Lin et al. in [35], a basic SR latch is the best option for a fair arbiter because of its symmetric construction.

There is a non-trivial chance that, both delay lines are almost identical. In this case, the rising edge arrives at the 2 inputs of the arbiter at nearly the same time.

Therefore, the arbiter goes into its metastable state and after a short period of time, it will settle down in one of its 2 stable states. Although the output in this case is totally random, it is not static for each device and therefore, it is the main cause of unreliability in an Arbiter PUF.

Figure 2.3: A basic Arbiter PUF design [2]

Gassend et al. [36] implemented the basic Arbiter PUF design on a set of FPGA chips. This implementation lacks low-level control over the placement and routing of the delay lines. The reliability is reported to be 99.9% under normal conditions, which is a high value. However, the uniqueness of this scheme has an extremely low value: 1.05%. Hence, this Arbiter PUF implementation is very biased which is a result of non-symmetric delay line design. Another implementation is performed by the same group on ASIC platform which controls the placement and routing of the switch boxes. The uniqueness is shown to improve significantly: 23%. But, it is still far from the ideal 50%. The reliability is also shown to be very high: 99.3% under normal conditions and 95.18% under high temperature conditions.

The most important issue with the basic Arbiter PUF is its weak resilience against modeling attacks. The digital delay line is additive by nature, meaning that, the total delay of the delay line paths is the sum of the delay of the switch boxes in the chain. Therefore, an attacker will be able to predict unknown responses as accurately as possible after monitoring a specific number of challenge response pairs. It is shown in [25] that the basic Arbiter PUF scheme is 96.45% predictable after observing 5000 CRPs. Hence, it is easily broken through modeling attacks. *Feed-forward* Arbiter PUF is thus proposed in [2] to increase the resilience of Arbiter PUFs against modeling attacks. The idea of feed-forward Arbiter is shown in Fig. 2.4. As we can observe, the *select* signal of a switch box in the main delay path is determined by the inserted arbiter  $A^*$ . The implementation results on ASIC platform indicate that the uniqueness of the new Arbiter PUF is increased to 38%, while its reliability is decreased to 90.16% under high temperature conditions. The reliability is decreased because the number of arbiters are increased in the design and as discussed before, each arbiter can go to a metastable state which results in noisy outputs. This scheme is also shown to be vulnerable against modeling attacks [37, 38]. In fact, the feed-forward Arbiter PUF is shown to be 97.5% predictable after observing 50000 CRPs.

Figure 2.4: The feed-forward Arbiter PUF design [2]

Majzoobi et al. proposed a more advanced technique to make Arbiter PUFs resilient against modeling attacks in [39]. In this technique, multiple arbiter PUFs are used in parallel and their outputs are XOR'ed to generate the response bits. Although this technique makes modeling attacks much harder, it is still shown that modeling attack against such scheme is feasible. Rührmair et al. show that the new scheme with 64 switching boxes and 3 parallel arbiters is 99% predictable with 60000 challenge-response pairs being observed [38].

#### 2.3.2 RO PUF

Figure 2.5 shows a basic RO PUF structure proposed in [1]. It includes N identical u-stage ring oscillators shown in Fig. 2.6. Note that, the number of stages in a ring oscillator is the number of inverters in the feedback loop. The ring oscillator generates a clock signal, the frequency of which is directly related to the delay of the inverters.

Figure 2.5: An architecture of an RO PUF [1]

The outputs of the ring oscillators are connected to the inputs of two N-to-1 multiplexers. A  $2 \log_2 N$ -bit challenge selects a pair of ring oscillators, the outputs of which will be connected to the clock inputs of the two counters.

Figure 2.6: A basic ring oscillator circuit

The two counters will start counting at the same time and after a specific period of time (determined by the *Ref\_Counter* as *Run Time*), the counter outputs are compared. If the upper counter has a greater value, the response bit will be 1, otherwise 0. Theoretically, the oscillation frequency of all the ring oscillators should be the same because they are exactly identical. However, due to the inherent inter-chip and intra-chip process variations, as well as the environmental conditions, the delays of the inverters will vary across different ring oscillators, thus affecting the oscillation frequency of the ROs [28]. Note that, the pair of ring oscillators that generate two oscillation frequencies which differ more, will produce a more reliable response bit, because the environmental changes will less likely reverse the relation between their frequencies. In other words, the reliability of a PUF depends greatly on the difference between the oscillation frequencies of any RO pair. Additionally, one of the advantages of the RO PUF is that, the ring oscillator can be implemented as a hard macro and instantiated as many times as needed in the top-level design. Using this technique, all the ROs will be identical in terms of placement and routing. A large scale characterization of RO PUF is provided in [26]. The uniqueness is shown to be 47.31% and the reliability is measured to be 99.14% under normal conditions.

In order to improve the reliability of an RO PUF, a 1-out-of- $\gamma$  masking was introduced in [1]. In this scheme, the RO pair that has the maximum frequency distance among other pairs are selected and their frequencies are compared to produce the response bit. The reliability of this PUF scheme implemented on 15 FPGA chips shows a uniqueness of 46.15% and a reliability of 99.52% under normal conditions [1]. The main drawback of this scheme is the huge area overhead. In fact,  $\gamma$  times more area is used to produce the same number of response bits. Maiti et al. addressed this drawback by proposing and constructing a *configurable RO* [3]. Figure 2.7 depicts their proposed 3-stage configurable RO, each stage of which can fit into 1 SLICE.

Figure 2.7: Maiti's Configurable RO [3]

Despite the basic RO (Fig. 2.6) that has only one path in the feedback loop, in this configurable RO the three signals,  $G_1, G_2$ , and  $G_3$  can select the inverters to be included in the loop. This provides us with 8 different ring oscillators (because of the delay variations of different LUTs and wires within the FPGA), while it occupies the same amount of area (1 CLB) compared to a basic RO. Similar to the 1-out-of- $\gamma$  masking scheme, a configuration for the one pair of configurable ROs which has the maximum frequency distance among the 8 configurations can be selected in order to improve the PUF reliability. In summary, the configurable ROs can be used in a 1-out-of- $\gamma$  manner (where  $\gamma = 8$ ), while occupying the same amount of area. Another important advantage of the Maiti's configurable RO is its ability to create 8 response bits instead of a single response bit. Implementation results for 64-, 128-, and 256-RO PUFs under varying voltage and temperature shows that, using the 1-out-of-8 scheme with the configurable RO improves the PUF reliability while maintaining a high value of uniqueness.

In addition, Xin et. al improve Maiti's configurable RO by increasing the number of possible configurations to 256 [4]. Figure 2.8 shows their proposed configurable 3-stage RO which can also fit into 1 CLB. As we can see, similar to Maiti's design, each stage is implemented in 1 SLICE. However, a latch is inserted in all SLICES and the signal *sel* determines whether or not a latch should be included in the path coming from the preceding stage. Because the delay associated with each latch is random and unpredictable due to manufacturing variations, it can be considered as another random factor in the PUF design that helps enhance the PUF unclonability. Note that, the other select signals,  $bx_i$ , have the same functionality as select signals,  $G_i$ , in Maiti's RO.

Because there are 8 configuration signals in the ring oscillator, namely sel[3..0]and bx[3..0], 256 different RO configurations are available, each of which can generate different oscillation frequencies. Thus, this scheme is able to generate even more response bits for a given challenge while occupying the same amount of area. It is shown that the reliability of this RO PUF design with 128 ROs is

Figure 2.8: Xin's Configurable RO in One CLB [4]

98.98% and the uniqueness is reported to be 40% for the same number of ROs.

In addition, a multi-voltage RO PUF is proposed in [5] as depicted in Fig. 2.9. The idea behind this scheme is the dependency of the combinational path of digital cells delay on the supply voltage. As we can see in Fig. 2.9, the supply voltage of each column of inverters is different and can be selected among d different values. Because the oscillation frequency of each RO depends on the delay of the inverters included in its feedback loop, and the delay of the inverters depends on process variations as well as the supply voltage, different ROs generate clock signals with different frequencies. The authors claim that this new RO PUF can produce a higher number of response bits, consumes less amount of area, and is more reliable in case of temperature variations. It can generate a higher number of response bits because the supply voltage of the different columns is considered as another random factor that can directly influence on the oscillation frequencies of the ROs. Therefore, by changing the supply voltages of the inverter columns, each pair of ROs can generate a set of different response bits. However, one of the important drawbacks of this scheme is that, the inverters used in different columns are not identical any more. Thus, if an attacker gains access to the supply voltage configuration of a chip through an invasive attack, they would most likely estimate the most probable response bits.

Figure 2.9: Multi-voltage RO PUF [5]

The 1-out-of- $\gamma$  masking scheme proposed in [1] is a good example of PUF *post-processing*. In fact, an additional processing is performed on the ring oscillator frequencies to provide more reliable response bits. In addition, the previous schemes suffer from the fact that, the number of PUF response bits and the number of challenge-response pairs provided by the PUF are limited to the area. The idea of RO frequencies post-processing is further investigated in [6]. In this study, an *identity-mapping function* along with a quantization process are applied on the RO frequencies in order to increase the number of challenge-response pairs. The proposed scheme is shown in Fig. 2.10.

Figure 2.10: The RO PUF with identity-mapping [6]

In the sample measurement phase, the challenge, c, selects each ring oscillator one at a time and the selected RO frequency is measured and recorded. Therefore, the "Physical Quantity" in the figure refers to the RO frequencies. In the identitymapping phase, any subset of RO frequencies whose cardinality is greater than 2 is selected and a corresponding Q-value is computed for each subset. The "Real Value" in the figure refers to this Q-value because it is not a digital value and it can have more than 2 values. Therefore, a quantization process is required to transform these real values to digital strings which are used as the PUF response bits. It is shown that, the proposed scheme can provide upto  $2^N - N - 1$  response bits, where N is the number of ring oscillators. Therefore, it is observed that, with a small number of ring oscillators (and thus, a small area cost), a large number of response bits and a large set of CRPs can be produced. The only expense that is paid is the additional post-processing applied on the RO outputs. Experimental data obtained from an implementation on 125 FPGAs shows a uniqueness of 49.99% which is nearly ideal. Also, the reliability is demonstrated to be 90% under high temperature conditions (70 °C).

Another good example of post-processing on the generated RO frequencies is the one proposed by Maes et al. in [7] and shown in Fig. 2.11. There are  $\beta$ batches of ring oscillators where each batch contains  $\alpha$  ring oscillators. In total, there are  $\beta \times \alpha$  number of ROs. The design of each batch is similar to the basic RO structure shown in Fig. 2.5, i.e., all  $\alpha$  ring oscillators are fed into an  $\alpha - to - 1$ multiplexer and the output of the multiplexer is connected to the clock input of a counter. The counter counts for a specific period of time which is determined by a reference counter. The count value after this run time represents the frequency of the selected RO. The frequencies of  $\beta$  ROs selected from each batch are measured simultaneously and an *h*-bit response is generated based on the ordering of the measured frequencies. Therefore, the total number of generated response bits is equal to  $h \times \alpha$ . The process of encoding the  $\beta$  frequency measurements and transforming them into an h-bit response is performed in 3 steps. First, the measured frequencies are normalized by removing the oscillator-dependent structural bias. The bias value is shown to be the mean value of the RO frequency which is estimated by averaging the frequency over many measurements on many devices. The estimated mean value for different ROs are called the normalization terms which need to be computed only once and can be stored in a ROM for later use. Subtracting this mean value from the measured frequency results in the normalized frequency. The normalized frequencies are then transformed into an h'-bit vector based on the order of the frequencies using the proposed Lehmer-Gray Encoder. It is shown that, some bits among the generated h' bits are biased and/or dependent to each other. Therefore, in order to increase the entropy and thus, the randomness of the response bits, a simple compression is performed on the h' bits. In fact, the bits which suffer the most from the bias and/or dependencies are XOR'ed with each other to produce an h-bit response, where  $h' \leq h$ .

Figure 2.11: The RO PUF structure proposed in [7]

Possible modeling attacks that can be applied on the Basic RO PUF are discussed in [38]. It is mentioned that, if an attacker can select the challenge-response pairs adaptively, they can sort the RO frequencies in a specified order without knowing the exact frequency of each RO. Then, the attacker will be able to predict the responses with a correctness rate of 100% because the absolute value of the RO frequency does not have any effect on the generated response. In fact, the response is produced based on the ranking of the RO frequencies. Maiti et al. investigate the security of their proposed RO PUF with identity-mapping ([6]) against this modeling attack. Since the produced response of this scheme does not solely depend on the frequency ranking of the ROs, it is shown to be resilient against this attack. In other words, because the RO frequencies are first transformed into *Q*-values, and then the *Q*-values are transformed into binary strings using the quantization function, the sorting technique proposed in [38] will not work against this scheme. Additionally, five other cases are considered to analyze the security of the RO PUF with identity-mapping in [6]: uniformity of response, response conditioned by challenge, inter-response dependency test, differential attack, and reverse engineering attack. The proposed scheme is shown to be resilient in all cases [6].

Finally, the effect of the FPGA chip *aging* on the Basic RO PUF is investigated in [40]. Aging is considered to be an *irreversible* temporal change that has the potential of affecting the reliability and randomness of the PUF response and thus, making the PUF unsuitable for authentication and secret key generation applications. It is shown that, the reliability of the RO PUF is reduced by 6% with aging. However, the uniqueness and entropy of the RO PUF do not seem to be affected by this parameter. Therefore, the security of the RO PUF is not compromised with aging.

#### 2.3.3 Glitch PUF

Any combinatorial logic has a glitch behavior. The occurrence, the number and the shape of the glitches on the output of the combinatorial logic is partially random and device-specific depending on the random process variations. The glitch behavior of such circuit can thus be converted into random response bits. In other words, Glitch PUFs produce response bits from the unwanted glitches in the circuit.

Anderson PUF proposed in [8] is an example of Glitch PUFs. As discussed before, in order to have a set of identical ring oscillators in terms of placement and routing, one should create a ring oscillator as a hard macro and instantiate it as many times as needed in the top level PUF design. The drawback of this approach is that, the design flow becomes too complicated with the use of hard macros. In fact, the designer must work at a lower level of abstraction than Register-Transfer Level (RTL). Also, routed hard macros tend to cause longer run times in the Place and Route (PAR), and might even cause PAR to crash. The Anderson PUF addresses these issues. It does not need the use of hard macros and can be easily

embedded in a design's HDL. Figure 2.12 depicts the proposed PUF circuit.

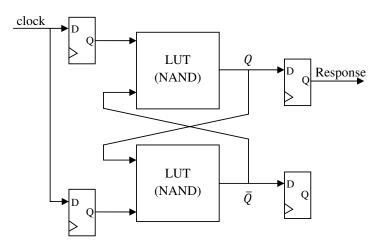

Figure 2.12: The proposed Anderson PUF circuit [8]

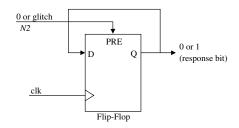

Two LUTs within a slice are used as 16-bit shift registers. LUT A is initialized with 0x5555 and LUT B is initialized with 0xAAAA. Therefore, shift register A generates a bit stream of 0101... and shift register B generates a bit stream of 1010....Note that, these two bit streams are complement of each other. Because the delays associated with the shift registers and the multiplexers they drive are different due to process variations, the output N2 can be either a constant 0 or a short positive spike. The presence or absence of a positive spike on N2 is utilized to decide the response bit. This process is shown in Fig. 2.13. The response bit is 1 if a spike is applied to the asynchronous preset input of the flip-flop, and 0 otherwise. The PUF circuit shown in Fig. 2.12 generates only 1 response bit. This circuit can be instantiated as many times as needed to create a multi-bit response.

Figure 2.13: PUF response bit generation [8]

The aforementioned design along with a pulse width tuning approach are implemented on a Virtex-5 65 nm FPGA and the performance is analyzed under temperature variation. It is shown that, on average, 3.6% of signature bits are unstable under high temperature conditions, which is in line with other published PUF circuits. Also the uniqueness is reported 48.28%. Another implementation of a 64-bit Anderson PUF on 5 Spartan-6 FPGAs in [41] shows a uniqueness of 45.62%.

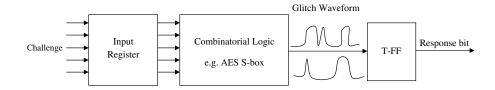

Another example of Glitch PUFs is the one proposed in [29] and later improved in [9]. Figure 2.14 depicts the Glitch PUF proposed in [9]. The generated response bit is the parity of the number of glitches that occur during a specific period of time. In fact, the output of the combinatorial logic, which is chosen to be the AES S-Box as an example, is connected to a toggle flip-flop. If the number of glitches is odd, the response will be 1 and if it is even, the response will be 0. To improve the reliability of the proposed scheme, the unstable bits are identified in a pre-processing stage and the information about them is stored in the system. These unstable bits are ignored when the PUF is actually used in practice. This technique is called *bit-masking* and adds extra overhead to the system but it is shown to improve the reliability, significantly. The proposed scheme along with the bit-masking technique is implemented on 16 FPGA chips and the reliability is reported to be 98.7% under normal conditions. However, it is shown that the applied bit-masking technique ignores almost 38% of the response bits. This demonstrates that, the proposed Glitch PUF without the bit-masking technique suffers from a substantial instability. Since the bit-masking technique is a general technique and not specific to Glitch PUFs, it is concluded that the proposed Glitch PUF does not show a suitable practical behavior. In addition, the uniqueness is reported to be 35%.

Figure 2.14: The Glitch PUF [9]

|                                   | Reliability     |                           |                 |                  | Number | Any        |

|-----------------------------------|-----------------|---------------------------|-----------------|------------------|--------|------------|

| PUF Scheme                        | Uniqueness      | Normal Higher Temperature |                 | Platform         | of     | Processing |

|                                   |                 | Conditions                | Conditions      |                  | Boards | Applied?   |

| Basic RO [26]                     | 47.31           | 99.14                     | 96              | Xilinx Spartan   | 125    | No         |

| Dasic KO [20]                     |                 |                           | 70              | 3E FPGA          | 125    |            |

| <b>RO</b> with 1-out-of- $\gamma$ | 46.15 99.52 N/A |                           | Xilinx Virtex 4 | 15               | Yes    |            |

| masking [1]                       | 40.15           | <i>)).32</i>              | 11/74           | LX25 FPGA        | 15     | 105        |

| Configurable RO [4]               | 40              | 98.98                     | N/A             | Xilinx Spartan   | 4      | Yes        |

| 0 11                              |                 |                           | 11/74           | 3E FPGA          | +      |            |

| RO with identity-                 | 49,99           | 99 90                     |                 | Xilinx Spartan   | 125    | Yes        |

| mapping [6]                       | 47.77           |                           | 90              | 3E FPGA          | 125    | 105        |

| RO with Lehmer-                   | 48.4            | 98 91                     |                 | Xilinx Spartan 6 | 10     | Yes        |

| Gray Encoder [7]                  | 40.4            | 20                        | 71              | XC6SLX45 FPGA    | 10     | 105        |

| Anderson [8]                      | 8] 48.28        | N/A                       | 96.4            | Xilinx Virtex    | 36     | No         |

| Anderson [0]                      |                 |                           |                 | 5 FPGA           | 50     |            |

| Anderson [41]                     | 45.62           | N/A                       | N/A             | Xilinx Spartan 6 | 5      | No         |

|                                   |                 |                           |                 | XC6SLX45 FPGA    | 5      |            |

| SR Latch [20]                     | 50.55           | 96.96                     | N/A             | 130 nm CMOS ASIC | 19     | No         |

| SR Latch [34]                     | 37.01           | 96.6                      | 87.29           | 65 nm CMOS ASIC  | 192    | No         |

Table 2.1: Comparing the performance of different PUF schemes in the literature in terms of uniqueness and reliability (%)

Table 2.1 summarizes the performance of the PUFs discussed in this chapter in terms of uniqueness and reliability. Note that, a fair comparison between different PUFs performance can be done only when they are all implemented on the same platform, under the same conditions, and even designed by the same developer.

# **Chapter 3**

# **Implementation Results**

In this chapter, we provide the implementation results of different PUF schemes in terms of reliability, uniqueness, uniformity, and bit-aliasing. First, the formal definitions and formulations of these PUF performance metrics are presented. Then more details on the implemented schemes, design parameters, and measurement system are provided. Finally, the implementation results are presented and discussed.

# 3.1 **PUF Performance Metrics**

In this section, four important PUF characteristics including reliability, uniqueness, uniformity, and bit-aliasing are discussed. The *randomness* of a PUF response is determined by its *entropy*. However, it is very difficult to estimate and calculate the entropy of a PUF response because one cannot learn the complete details about the statistical distribution of the PUF responses which is generally determined by very complex and even chaotic physical processes [34]. So, the randomness of the PUF responses is truly indicated by uniqueness, uniformity, and bit-aliasing [6].

### 3.1.1 Reliability

Reliability of a given PUF instance is a measure of stability of the PUF response bits to a given challenge at different times and under different conditions [3]. Ideally, the value of reliability is 100%, meaning that the PUF under study generates the exact same response to a given challenge at different times and under different conditions, such as different temperatures or different supply voltage values. It is defined as [3]:

$$Reliability = (1 - \frac{2}{m \times (m-1)} \sum_{i=1}^{m-1} \sum_{j=i+1}^{m} \frac{HD(r_i, r_j)}{a}) \times 100\%$$

(3.1)

where *m* is the number of response samples, *a* is the number of response bits, and *HD* is the Hamming distance between two response samples  $r_i$  and  $r_j$ . So, we basically take *m* number of samples of the response of a given PUF instance to a specific challenge, calculate the Hamming distance between any two responses (where the total number of unique comparisons between *m* responses is  $\frac{m \times (m-1)}{2}$ ), and calculate the average number of unstable bits among *a* response bits. This value represents the average instability or intra-distance of the given PUF instance. Finally, reliability is derived by reducing this value from 100%.

### 3.1.2 Uniqueness

Another important feature of a PUF is its uniqueness. Uniqueness is a measure of inter-distance variations of the response bits of different PUF instances. In other words, if a specific challenge is applied at the same time and under the same conditions to two identical PUF instances, the response of the two PUFs should be different. Ideally, this value should be 50%. It is calculated as [3]:

$$Uniqueness = \frac{2}{g \times (g-1)} \sum_{i=1}^{g-1} \sum_{j=i+1}^{g} \frac{HD(r_i, r_j)}{a} \times 100\%$$

(3.2)

where g is the number of PUF instances under study, a is the number of response bits, and HD is the Hamming distance between two response samples  $r_i$  and  $r_j$ . The same challenge is applied to g identical PUF instances and the average Hamming distance between the response bits of any two PUF circuits is calculated (where the total number of unique comparisons between g different PUF circuits is  $\frac{g \times (g-1)}{2}$ ).

### 3.1.3 Uniformity

Uniformity is the measure of uniform distribution of 0's and 1's in the response of a single PUF instance. It is defined as [14,42]:

$$Uniformity = \frac{1}{m \times a} \sum_{i=1}^{m} \sum_{j=1}^{a} r_{i,j} \times 100\%$$

(3.3)

where m is the number of response samples, a is the number of response bits, and  $r_{i,j}$  is the *j*-th bit of the *i*-th response sample. Ideally, uniformity should be 50% meaning that 50% of the response bits are 1 and 50% are 0.

### 3.1.4 Bit-aliasing

Another important indicator of a PUF randomness and unclonability is bit-aliasing. The bit-aliasing of the j-th response bit is the average Hamming weight of that bit position across several PUF instances. Ideally, this value should be 0.5 for all bit positions in the PUF response. It is defined as [26]

$$Bit - aliasing_j = \frac{1}{g} \sum_{i=1}^{g} r_{i,j}$$

(3.4)

for all j,  $0 \le j \le a$ , where g is the number of PUF instances and  $r_{i,j}$  is the j-th bit of the *i*-th PUF instance response.

### **3.2 Design concepts: Basic PUFs**

Among the memory-based PUF schemes, the SR Latch PUF is chosen because of its ability to re-generate the response bits when the circuit is powered and operational. We also implement the Basic RO and Anderson PUFs and we evaluate and compare their performance through statistical analysis.

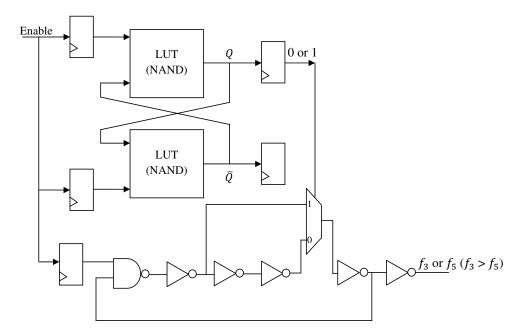

### 3.2.1 SR Latch PUF

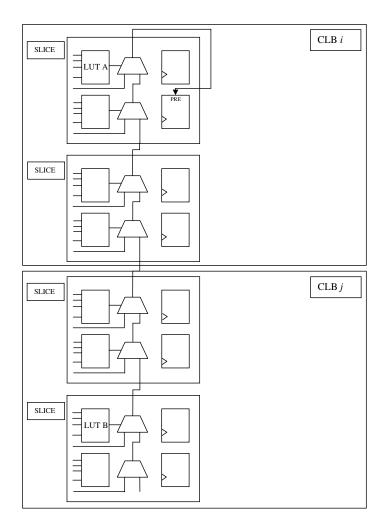

A NAND-based SR Latch PUF is implemented as shown in Fig. 3.1. A *clock* is connected to the reset signal and whenever the level of the clock is 1, the output bit is read and recorded. Note that, if we need to obtain an N-bit response, we have to instantiate the SR Latch unit N times and obtain 1 bit from each unit.

Figure 3.1: The NAND-based SR Latch [10]

In order to achieve the best results for the SR Latch PUF in terms of randomness of the response bits, some details related to the implementation of the SR Latch have to be considered [10]. First of all, the flip-flops used on the input side of the latch are necessary to reduce the skew of the clock signal. The flip-flop used on the output bit (Q signal) is used to balance the capacitive load of the Qsignal with the capacitive load of the  $\overline{Q}$  signal [10]. Note that, our platform in this study is a Virtex II Pro FPGA evaluation board. Each CLB of a Virtex II Pro FPGA has four SLICEs, and each SLICE contains two lookup tables and two flipflops. Therefore, each lookup table (NAND gate) along with its input and output flip-flops are implemented in a single SLICE. So, the SR Latch shown in Fig. 3.1 requires only two SLICEs which can be placed in a single CLB. However, in order to guarantee the symmetrical implementation of the Q and  $\overline{Q}$  signals, the two SLICEs have to be placed in two separate CLBs. Even the distance between the two CLBs is important and has direct effect on the PUF performance. A thorough analysis is performed on the effect of the placement of the CLBs on the randomness of the generated response bits in [10]. Based on our initial implementations and experiments, we obtained the best results when the distance between the two CLBs is 1 CLB. In other words, if one of the lookup tables along with the corresponding flip-flops is fitted in the SLICE X0Y0, the other lookup table and its flip-flops are implemented in the SLICE X0Y4.

#### **3.2.2 Basic RO PUF**

As discussed before, an RO PUF generates the response bits by comparing the frequencies of two different ring oscillators (Fig. 2.5). Note that, the counter size and run time should be carefully selected because, as we can observe, the response of the PUF relies on the difference between the oscillation frequency of different ring oscillators. Thus, the run time should be long enough to differentiate between the oscillation frequency of different ring oscillators. On the other hand, it should not be too long to cause a counter overflow. Also, the counter size should be big enough to prevent a counter overflow. A more detailed discussion on how to select the counter size and run time is provided in [13]. Also note that, in order to generate an *M*-bit response, *M* different challenges (where each challenge is  $2 \log_2 N$  bits wide) have to be applied to make *M* comparisons between different ROs. So, one of the disadvantages of this design is the low ratio of the number of response bits to the number of challenge bits  $(\frac{1}{2\log_2 N})$ .

The maximum number of possible comparisons between N different ROs is equal to:  $\frac{N \times (N-1)}{2}$ . However, not every comparison will result in an uncorrelated response bit. For example, if A is greater than B and B is greater than C, then A will be greater than C. Therefore, the comparison between A and C is correlated to the comparisons between A and B, and B and C. It is shown in [3] that, selecting and comparing the adjacent RO pairs (i.e., comparing  $RO_1$  with  $RO_2$ ,  $RO_2$  with  $RO_3$ ,  $RO_3$  with  $RO_4$ , etc.) eliminates the effect of this correlation. Thus, we perform only N-1 comparisons out of the total number of comparisons, resulting in a response which is N-1 bits wide.

### 3.2.3 Anderson PUF

As mentioned in Chapter 2, Anderson PUF design is an example of the Glitch PUFs which produce response bits from unwanted glitches in the circuit (Fig. 2.12 and 2.13). The response bit is decided based on the presence or absence of a glitch signal on the output of the top carry-chain multiplexer (N2). The most important factor that determines the quality of this design in terms of randomness is the width of the produced glitch. If the glitch is too narrow, it will be damped while it propagates through a wire which acts like a low pass filter. Thus, even if a glitch is produced, the response will be 0 because the glitch is not seen by the flip-flop. If the 2 shift register-multiplexer blocks, A and B, are located very close to each other, the produced glitch will be too narrow and the response bits will always be 0. In fact, 100% of the response bits will be 0 in this case. On the other hand, if the 2 blocks, A and B, are located in a way that they are too far from each other, a glitch will always be present on N2 and therefore, the response bit will always be 1. The concept of *tuning the glitch width* is utilized in the proposed PUF design to address this issue [8]. The idea is to widen the produced glitch so that it is seen by the flip-flop. This is accomplished by inserting some *intermediate blocks* between the blocks A and B, as shown in Fig. 3.2.

Note that, the shift registers in the intermediate blocks are initialized with all 1's. So, they act like a simple wire. They only cause the transitions from B's output to take a little longer and therefore, the glitch will be widened. Now, if too many intermediate blocks are inserted between A and B, the response bits will be 1 with higher probability. So, all the possible number of intermediate blocks should be tested in order to achieve the best result in terms of uniformity and randomness. The best tuning was shown to be 5 intermediate blocks (shown in Fig. 3.2) in [8]. Based on our tests, the tuning which resulted the best uniformity

Figure 3.2: Tuning the glitch width in the Anderson PUF on a Virtex II platform [8]

was also 5 intermediate blocks.

# 3.3 Design Concepts: The Proposed Hybrid PUF

In this section, we propose the idea of the Hybrid PUF structure. The idea is to combine two (or more) available sources of randomness in a way to improve the uniqueness while maintaining other important performance metrics. This structure is based on the Basic RO PUF which can be combined with any other PUF unit that produces a random bit. The RO PUF and the Anderson PUF are combined using two methods and it is shown that the second method results in better performance. Therefore, we combine the RO PUF with the SR Latch PUF as another example using the second method only. Finally, the implementation results are presented and discussed in Section 3.5.

#### **3.3.1 RO/Anderson Hybrid PUF, Method 1**

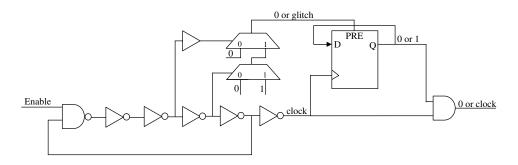

As previously discussed, the RO PUF uses the randomly generated RO frequencies to produce the response bits, and the Anderson PUF uses the shift registermultiplexer delay as its random parameter to generate the response bits. We try to combine these two ideas to increase the PUF randomness. As shown in Fig. 2.12, the Anderson PUF works in a clocked manner and the clock is the same for all instances. Also note that, the inverters in the RO circuit are implemented using lookup tables in the FPGA. Thus, an inverter in the RO circuit and a 1-bit buffer can be used as LUT A and LUT B in the Anderson PUF design. Figure 3.3 shows the proposed scheme.

Figure 3.3: The proposed RO/Anderson Hybrid PUF structure, method 1

Note that, the output of the inverter and the buffer are complement of each other which is a requirement of the Anderson PUF. In fact, the proposed scheme is similar to the Anderson PUF except the fact that, the clock of the system is generated using a ring oscillator which can be different across different instances. So, there are two sources of randomness in the scheme, one is the random clock frequency generated by the RO and the other one is the lookup table-multiplexer delay. The output of the flip-flop is AND'ed with the RO clock. Therefore, the output of this scheme is either a 0 or a clock. Similar to the RO PUF structure (Fig. 2.5), this block is instantiated as many times as needed and the counter values are compared after a specific run time to produce the required number of response bits. Note that, if we have N number of blocks and if we compare only the adjacent pairs, as discussed earlier, the number of response bits will be N-1. Let us consider two instances of this scheme, *instance i* and *instance j*. Because each instance can have 2 different outputs, 0 or a random clock, there are 4 different scenarios shown in Table 3.1. As we can see, the response bit produced in scenario 1 is 1, scenarios 2 and 3 will produce 0, and the response bit of the scenario 4 will be either 0 or 1 (with probability of 0.5 for each of them). Note that, the response bit is the comparison result of the two instances outputs after a specific run time, similar to the Basic RO PUF scheme. Because the occurrence probability of all scenarios are theoretically equal to 0.25, it is expected to have 37.5% (=  $(0.25 \times 1 + 0.25 \times 0.5) \times 100\%$ ) of the response bits to be 1 and 62.5%  $(= (0.25 \times 1 + 0.25 \times 1 + 0.25 \times 0.5) \times 100\%)$  to be 0. This means that the proposed method has a biased behavior toward the bit 0 and does not improve the randomness of the response bits. The implementation results presented in Section 3.5 verify this fact.

|                          | Scenario 1 | Scenario 2 | Scenario 3 | Scenario 4 |

|--------------------------|------------|------------|------------|------------|

| Instance <i>i</i> output | Clock      | 0          | 0          | Clock      |

| Instance <i>j</i> output | 0          | 0          | Clock      | Clock      |

| Response bit             | 1          | 0          | 0          | 0 or 1     |

Table 3.1: RO/Anderson Hybrid PUF method 1 different scenarios

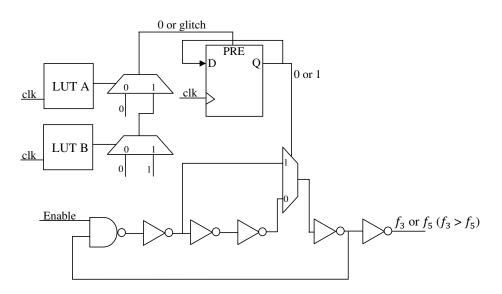

### 3.3.2 RO/Anderson Hybrid PUF, Method 2

Figure 3.4 shows method 2 for combining the RO PUF and the Anderson PUF. The Anderson PUF implementation is exactly the same as the original Anderson in terms of tuning and in the sense that the input clock to all instances are the same. The Anderson output bit which is 0 or 1 (with theoretical probability of 0.5 for each of them), is connected to the *select* signal of the 2 - to - 1 multiplexer in the ring oscillator circuit. If the *select* signal is 0, the ring oscillator will have 5