# Western University Scholarship@Western

Electronic Thesis and Dissertation Repository

3-14-2012 12:00 AM

# Investigation on the Benefits of Safety Margin Improvement in CANDU Nuclear Power Plant Using an FPGA-based Shutdown System

Jingke She The University of Western Ontario

Supervisor Dr. Jin Jiang *The University of Western Ontario*

Graduate Program in Electrical and Computer Engineering A thesis submitted in partial fulfillment of the requirements for the degree in Doctor of Philosophy © Jingke She 2012

Follow this and additional works at: https://ir.lib.uwo.ca/etd

Part of the Electrical and Electronics Commons, Nuclear Engineering Commons, and the Power and Energy Commons

### **Recommended Citation**

She, Jingke, "Investigation on the Benefits of Safety Margin Improvement in CANDU Nuclear Power Plant Using an FPGA-based Shutdown System" (2012). *Electronic Thesis and Dissertation Repository*. 474. https://ir.lib.uwo.ca/etd/474

This Dissertation/Thesis is brought to you for free and open access by Scholarship@Western. It has been accepted for inclusion in Electronic Thesis and Dissertation Repository by an authorized administrator of Scholarship@Western. For more information, please contact wlswadmin@uwo.ca.

# Investigation on the Benefits of Safety Margin Improvement in CANDU Nuclear Power Plant Using an FPGA-based Shutdown System

(Thesis format: Monograph)

By

Jingke She

Graduate Program in Electrical and Computer Engineering

A thesis submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

School of Graduate and Postdoctoral Studies The University of Western Ontario London, Ontario

© Jingke She, 2012

## THE UNIVERSITY OF WESTERN ONTARIO SCHOOL OF GRADUATE AND POSTDOCTORAL STUDIES

## **CERTIFICATE OF EXAMINATION**

Chief Advisor

Examining Board

Dr. Jin Jiang

Advisory Committee

Dr. Arash Reyhani-Masoleh

Dr. Robert Sobot

Dr. Mark Lawford

Dr. Robert E. Webber

Dr. Xianbin Wang

Dr. Robert Sobot

The thesis by Jingke She Entitled Investigation on the Benefits of Safety Margin Improvement in CANDU Nuclear Power Plant

## Using an FPGA-based Shutdown System

is accepted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Date: \_\_\_\_\_

Chair of Examining Board

## ABSTRACT

The relationship between response time and safety margin of CANadian Deuterium Uranium (CANDU) nuclear power plant (NPP) is investigated in this thesis. Implementation of safety shutdown system using Field Programmable Gate Array (FPGA) is explored. The fast data processing capability of FPGAs shortens the response time of CANDU shutdown systems (SDS) such that the impact of accident transient can be reduced. The safety margin, which is closely related to the reactor behavior in the event of an accident, is improved as a result of such a faster shutdown process.

Theoretical analysis based on neutron dynamic theory is carried out to establish the fact that a faster shutdown process can mitigate accidental consequences. To provide more realistic test cases from a thermalhydraulic perspective, an industry grade simulation tool known as CATHENA is used to generate comparable accident-shutdown transients for different SDS response times. Results from both verification methods explicitly prove the feasibility of improving the safety margin via faster shutdown process.

To demonstrate this concept, a prototype of the proposed faster SDS is constructed. The trip logic of CANDU shutdown system No.1 (SDS1) is converted into a digital hardware design and implemented within chosen FPGA platform. The functionality of the FPGA-based SDS1 is implemented, and the response times are tested and compared to those of the existing CANDU SDS1. The achieved 10.5 *ms* response time of the FPGA-based SDS1 is again applied to the CATHENA simulation process to quantitatively present the 26.98% improvement in the safety margin.

To investigate potential improvement in safety margin by using FPGA technology, hardware-in-the-loop (HIL) simulation is performed by connecting the FPGA-based SDS1 to an NPP training simulator. The 6.26% improvement in safety margin has been verified, based on which a 10% potential power upgrade is discussed as another benefit of applying FPGA technology to CANDU NPPs.

**Keywords:** FPGA, safety margin, CANDU, response time, SDS1, HIL, power upgrade.

Learning is like rowing upstream, not to advance is to drop back.

学如逆水行舟,

不进则退。

# ACKNOWLEDGMENTS

This thesis would not have been successful without Dr. Jin Jiang who not only served as my supervisor but also encouraged and challenged me throughout my academic program. His creative instructions and everlasting support helped me greatly during the entire research process.

I wish to express my sincere thanks to my colleagues in the Control, Instrumentation and Electrical System group at the University of Western Ontario, such as Mr. Drew James Rankin, Mr. Peiwei Sun, and Dr. Xinhong Huang, for their invaluable support during my Ph. D research work.

I would like to pass my gratitude to my committee members for their guidance through my academic program.

I own my deepest gratitude to my parents, Guoyun She and Lijun Wu, as well as my parents-in-law, Wenke Tang and Kuangyun Li. They never stop loving me and teaching me the way a man should be. This thesis is dedicated to them as my sincerest acknowledgement.

My special appreciation goes to my beloved wife Jing Tang and daughter Jingyan She, who give me the strongest spiritual support in the world.

Finally, I would like to highly acknowledge both the financial and technical supports from the following organizations (listed alphabetically, including but not limited to): Atomic Energy Canada Limited (AECL), Natural Science and Engineering Research Council of Canada (NSERC), Ontario Power Generation (OPG), University Network of Excellence in Nuclear Engineering (UNENE), and the University of Western Ontario (UWO).

# TABLE OF CONTENTS

| CERTIFICATE OF EXAMINATIONii |            |                                                                                                                                                                                          |                |

|------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| ABSTRACTiii                  |            |                                                                                                                                                                                          |                |

| ACKN                         | OWLE       | DGMENTS                                                                                                                                                                                  | . v            |

| TABLE                        | E OF C     | ONTENTS                                                                                                                                                                                  | vi             |

| LIST O                       | F TAB      | LES                                                                                                                                                                                      | ix             |

| LIST O                       | F FIGU     | JRES                                                                                                                                                                                     | . x            |

| ABBRI                        | EVIAT      | IONS AND NOMENCLATURE                                                                                                                                                                    | iii            |

| 1                            | INTRO      | DUCTION                                                                                                                                                                                  | . 1            |

|                              | 1.1        | <ul> <li>Safety issues in NPPs</li> <li>1.1.1 Safety objectives and requirements in NPPs</li> <li>1.1.2 Operation limits and safety margins</li> <li>1.1.2 NPD safety systems</li> </ul> | . 2            |

|                              | 1.2        | <ul> <li>1.1.3 NPP safety systems</li> <li>Safety systems in CANDU NPPs</li> <li>1.2.1 General information</li> <li>1.2.2 SDS1</li> </ul>                                                | . 7<br>. 7     |

|                              | 1.3        | Research motivations         1.3.1       Safety margin improvement         1.3.2       SDS1 performance         1.3.3       Advantages of using FPGAs                                    | 11<br>12<br>13 |

|                              | 1.4        | Objectives, methodologies, and scope of research1.4.1Research objectives1.4.2Research approaches1.4.3Research scope                                                                      | 16<br>16<br>18 |

|                              | 1.5<br>1.6 | Main contributions<br>Organization of the thesis                                                                                                                                         | 22             |

|                              |            | EAR SAFETY AND FPGA APPLICATIONS IN NPPS                                                                                                                                                 |                |

|                              | 2.1        | Nuclear safety2.1.1Regulations and standards                                                                                                                                             | 25<br>26       |

|                              | 2.2        | Safety margins                                                                                                                                                                           | 32<br>32       |

|                              | 2.3        | <ul> <li>2.2.2 Safety margin improvement through faster shutdown process</li> <li>CANDU SDS1</li> <li>2.3.1 Evolutions</li> <li>2.3.2 Issues in software-based SDS1</li> </ul>           | 50<br>50       |

|   |       | 2.3.3 Speed of response of CANDU SDS1                           | 52  |

|---|-------|-----------------------------------------------------------------|-----|

|   | 2.4   | FPGA applications for NPP I&C systems                           |     |

|   |       | 2.4.1 Why FPGA                                                  | 55  |

|   |       | 2.4.2 Performance enhancement through FPGA applications         | 57  |

|   | 2.5   | Previous work review                                            |     |

|   |       | 2.5.1 Work on safety margin                                     |     |

|   |       | 2.5.2 Discussions on existing NPP safety systems                |     |

|   |       | 2.5.3 FPGA applications in NPPs                                 |     |

|   | 2.6   | Summary                                                         |     |

| 3 | INVES | STIGATIONS ON ACCIDENTS IN CANDU NPPS                           | 69  |

|   | 3.1   | CANDU thermalhydraulic basics                                   | 69  |

|   |       | 3.1.1 Chosen thermalhydraulic loop                              |     |

|   |       | 3.1.2 CATHENA basics in accident simulations                    |     |

|   |       | 3.1.3 Description and justification of the postulated accidents |     |

|   | 3.2   | CATHENA simulation for the postulated accidents                 |     |

|   | 0.2   | 3.2.1 Construction of simulation models                         |     |

|   |       | 3.2.2 The simulation cases                                      |     |

|   |       | 3.2.3 Simulation for steady-state conditions                    |     |

|   | 3.3   | Simulation results                                              |     |

|   | 5.5   | 3.3.1 Results for the LOFA case                                 |     |

|   |       | 3.3.2 Results for the Large LOCA case                           |     |

|   | 3.4   | Summary                                                         |     |

| 4 | SDS1  | TRIP LOGIC AND ITS FPGA IMPLEMENTATION                          |     |

|   | 4.1   | SDS1 trip logic                                                 |     |

|   | т.1   | 4.1.1 PDCs in a CANDU 6 unit                                    |     |

|   |       | 4.1.2 Trip logics                                               |     |

|   | 4.2   | Implementation of SDS1 trip logic on an FPGA platform           |     |

|   | 4.2   | 4.2.1 System design                                             |     |

|   |       | 4.2.1 System design                                             |     |

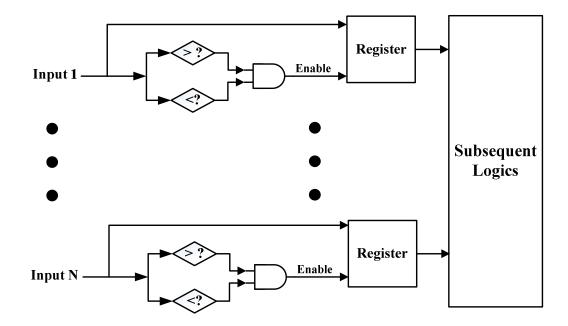

|   |       | 4.2.3 Setpoint register                                         |     |

|   |       | 1 0                                                             |     |

|   |       | 4.2.4 Extensive conditions                                      |     |

|   |       | 4.2.5 Processing logic                                          |     |

|   |       | 4.2.6 Output circuit                                            |     |

|   |       | 4.2.7 Implementation details                                    |     |

|   | 4.2   | 4.2.8 Discussions for the implemented FPGA platform             |     |

|   | 4.3   | Summary                                                         | 128 |

| 5 | PERFO | ORMANCE EVALUATION OF THE FPGA-BASED SDS1                       | 130 |

|   | 5.1   | Methodology, experimental setup, and test cases                 | 130 |

|   |       | 5.1.1 Methodologies for performance evaluation                  | 130 |

|   |       | 5.1.2 Experimental setups                                       | 130 |

|   |       | 5.1.3 Simulation approaches and test cases                      | 132 |

|   | 5.2   | Experimental results and analysis                               |     |

|   |       | 5.2.1 Functionality simulation                                  |     |

|   |       | 5.2.2 Response time evaluation                                  |     |

|   |       | -                                                               |     |

|                  |                                                      | 5.2.3 Analysis of the test results               | 136 |

|------------------|------------------------------------------------------|--------------------------------------------------|-----|

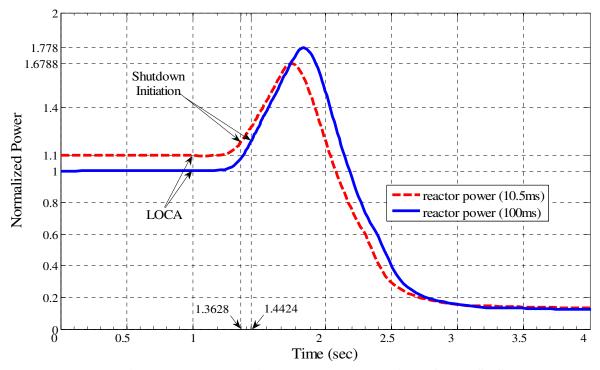

|                  | 5.3                                                  | CATHENA simulation using evaluated response time | 139 |

|                  |                                                      | 5.3.1 Simulation results                         | 139 |

|                  |                                                      | 5.3.2 Analysis of simulation results             | 142 |

|                  | 5.4                                                  | Summary                                          |     |

| 6                | 6 VALIDATION OF FPGA-BASED SDS1 IN AN HIL SIMULATION |                                                  |     |

|                  | 6.1                                                  | Advantages of HIL simulations                    | 146 |

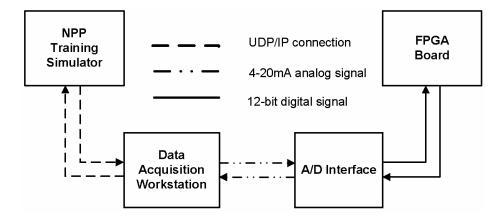

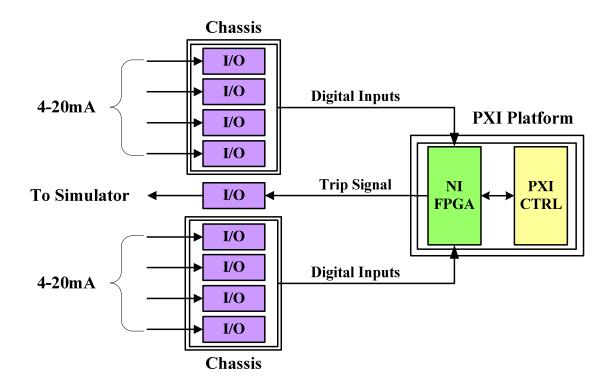

|                  | 6.2                                                  | HIL simulation setup                             | 147 |

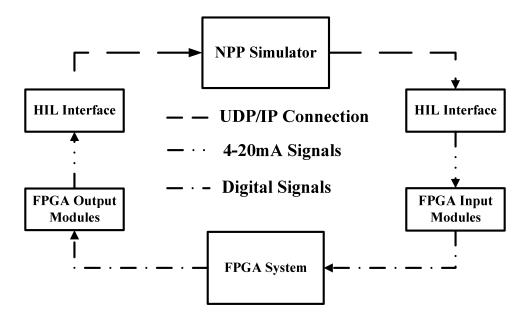

|                  |                                                      | 6.2.1 HIL simulation platform                    | 147 |

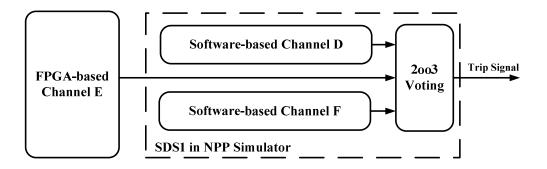

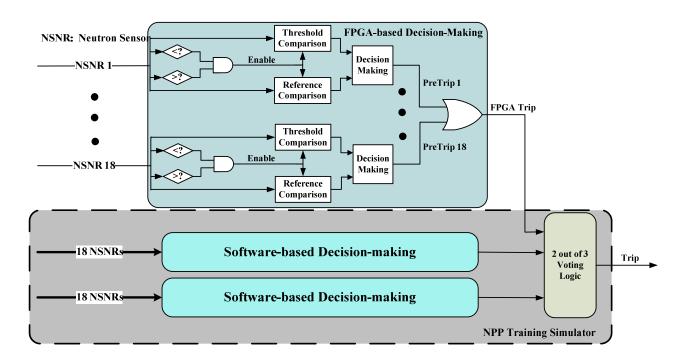

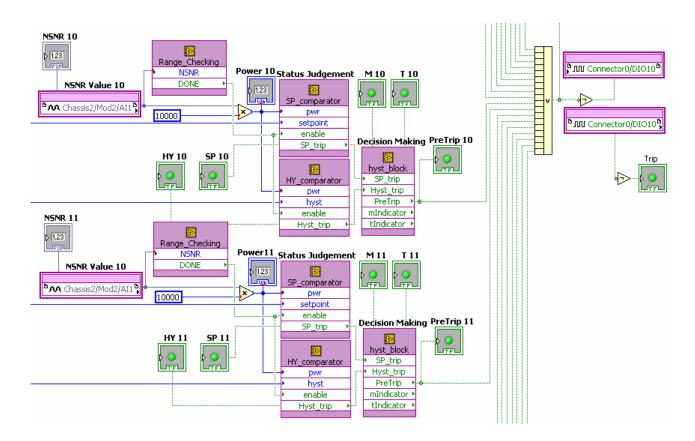

|                  |                                                      | 6.2.2 Implementation of the trip logic           | 151 |

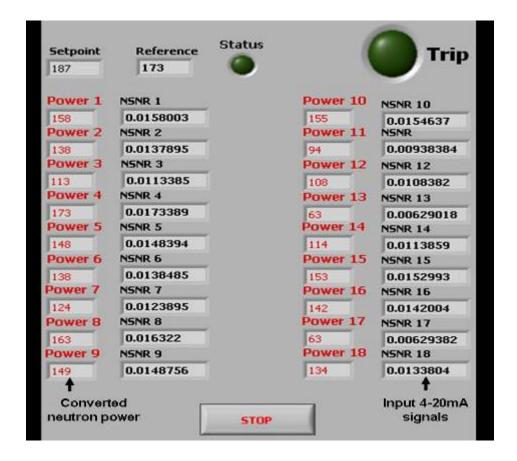

|                  |                                                      | 6.2.3 Setup of experiments                       | 154 |

|                  |                                                      | 6.2.4 Selection of simulation case               | 156 |

|                  | 6.3                                                  | HIL simulation results                           | 157 |

|                  | 6.4                                                  | Discussions                                      | 158 |

|                  | 6.5                                                  | Summary                                          | 160 |

| 7                | CON                                                  | CLUSIONS AND FUTURE WORK                         | 162 |

|                  | 7.1                                                  | Conclusions of this research                     | 162 |

|                  | 7.2                                                  | Limitations and suggestions for future work      | 165 |

|                  |                                                      | 7.2.1 Limitations of the current work            |     |

|                  |                                                      | 7.2.2 Suggestions for future work                | 167 |

| 8                | REFE                                                 | ERENCES                                          | 168 |

| APPENDIX A       |                                                      |                                                  |     |

| APPENDIX B       |                                                      |                                                  |     |

| APPENDIX C       |                                                      |                                                  |     |

|                  |                                                      |                                                  |     |

| CURRICULUM VITAE |                                                      |                                                  |     |

# LIST OF TABLES

| Table 2.1 Relevant parameter values based on a                                      | 48  |

|-------------------------------------------------------------------------------------|-----|

| Table 3.1 Fuel channel attributes for CATHENA simulation                            | 77  |

| Table 3.2 Region characteristics                                                    | 80  |

| Table 3.3 Coefficients of reactivity change caused by void fraction and temperature | 82  |

| Table 3.4 Pipe attributes in RIH and ROH                                            | 84  |

| Table 3.5 Steady-state conditions for LOFA                                          | 90  |

| Table 3.6 Steady-state conditions for large LOCA                                    | 91  |

| Table 4.1 SDS1 Trip Parameters and Setpoints                                        | 101 |

| Table 5.1 Statistical measures of the response time tests                           | 136 |

| Table 5.2 Comparison of key parameters under two shutdown cases                     | 143 |

| Table B.1 Stratix FPGA features                                                     | 213 |

| Table B.2 NI 7811R FPGA features                                                    | 222 |

| Table B.3 NI 9151 expansion chassis features                                        | 223 |

| Table B.4 NI 9203 analog current input module features                              | 223 |

# LIST OF FIGURES

| Figure 1.1 –Limits and margins of CANDU NPPs                                  | 4   |

|-------------------------------------------------------------------------------|-----|

| Figure 1.2 – CANDU SDS1 and SDS2                                              | 8   |

| Figure 1.3 – Schematic view of an FPGA chip                                   | 14  |

| Figure 2.1 –Concept of safety margins and uncertainties                       | 33  |

| Figure 2.2 – Reactivity insertion in accident-shutdown process                | 38  |

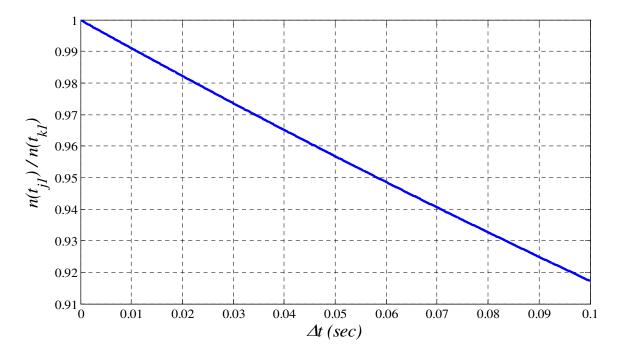

| Figure 2.3 – Surge peak ratio of LOCA transients (PJA)                        | 47  |

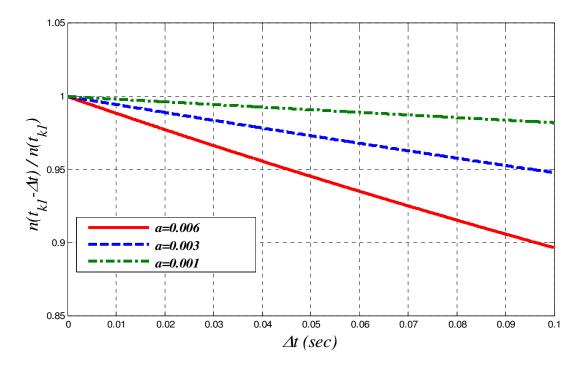

| Figure 2.4 – Surge peak ratios on different <i>a</i>                          | 49  |

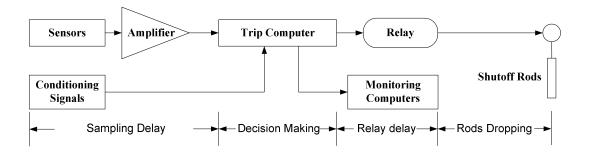

| Figure 2.5 – Signal path of SDS1                                              | 53  |

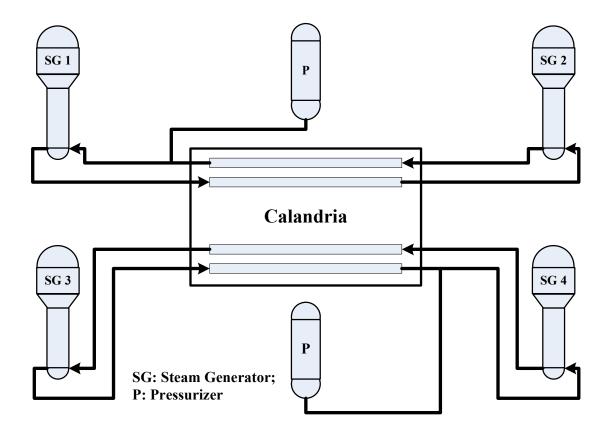

| Figure 3.1 – CANDU PHT loops                                                  | 71  |

| Figure 3.2 – CANDU 6 face view with SDS1 shutoff rods                         | 77  |

| Figure 3.3 – Fuel channel model                                               | 78  |

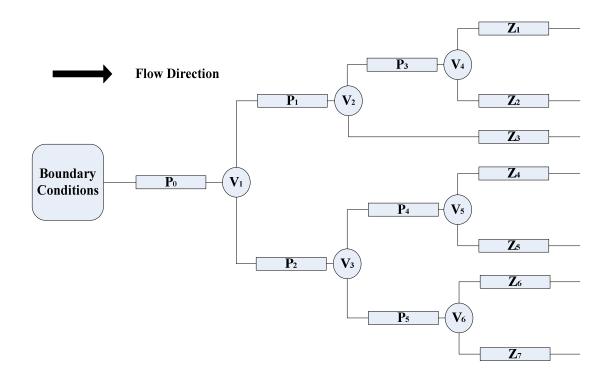

| Figure 3.4 – Postulated region assembly                                       | 79  |

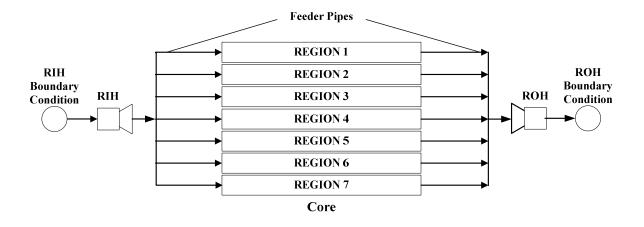

| Figure 3.5 – Core partitioning for simulation studies                         | 80  |

| Figure 3.6 – Layout of the RIH model                                          | 82  |

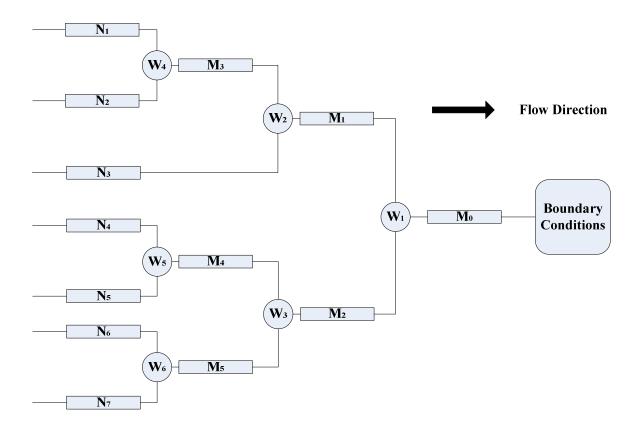

| Figure 3.7 – Layout of the ROH model                                          | 83  |

| Figure 3.8 – CATHENA simulation model for large LOCA studies                  | 85  |

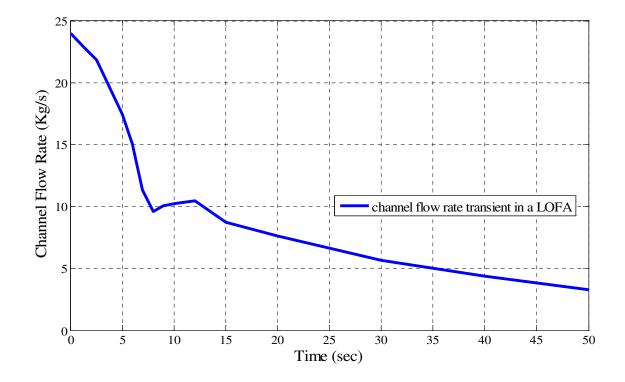

| Figure 3.9 – Flow rate transient in a LOFA                                    | 86  |

| Figure 3.10 – RIH flow rate at different break sizes [143]                    | 89  |

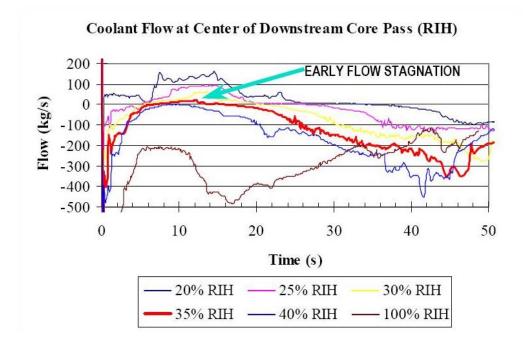

| Figure 3.11 – Sheath temperature at central channel during RIH breaks [143]   | 90  |

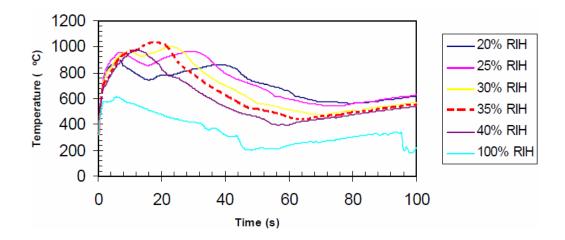

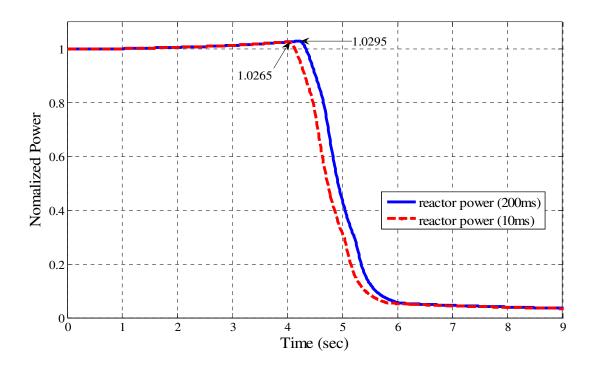

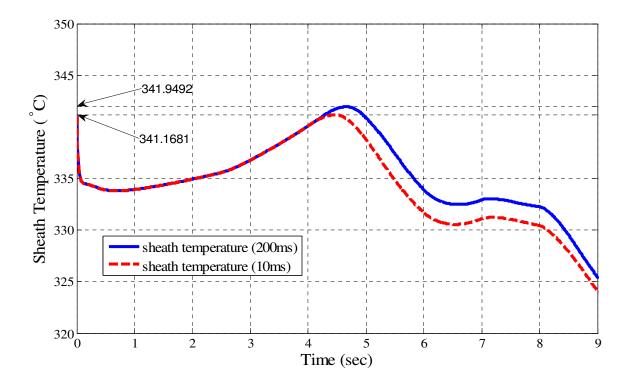

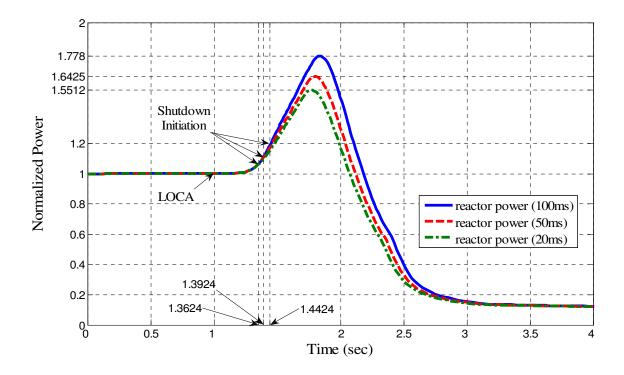

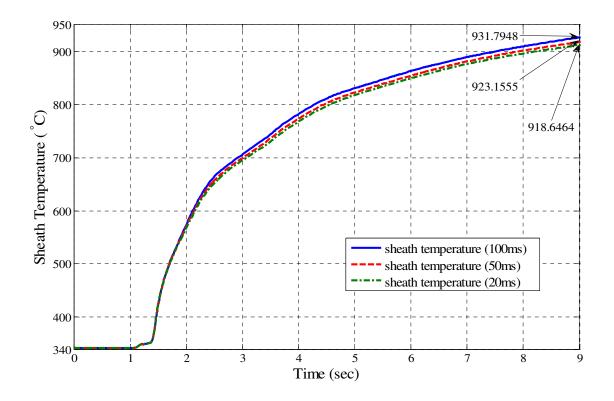

| Figure 3.12 – Comparison of power transients in LOFA                          | 92  |

| Figure 3.13 – Comparison of sheath temperature transients in LOFA             | 93  |

| Figure 3.14 – Comparison of power transients in large LOCA                    | 94  |

| Figure 3.15 – Comparison of sheath temperature transients in large LOCA       | 95  |

| Figure 4.1 – Overview of SDS1 trip channel                                    | 99  |

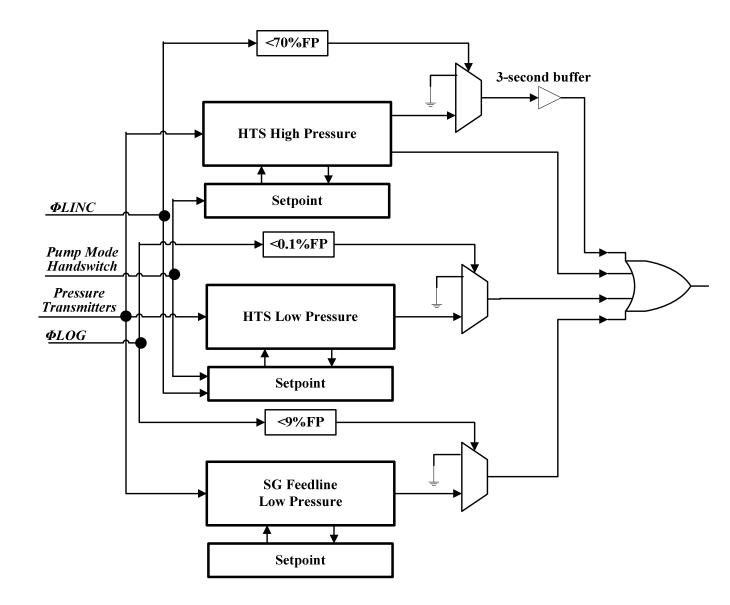

| Figure 4.2 – Trip logic structure in PDC1                                     | 103 |

| Figure 4.3 – Trip logic structure in PDC2                                     | 104 |

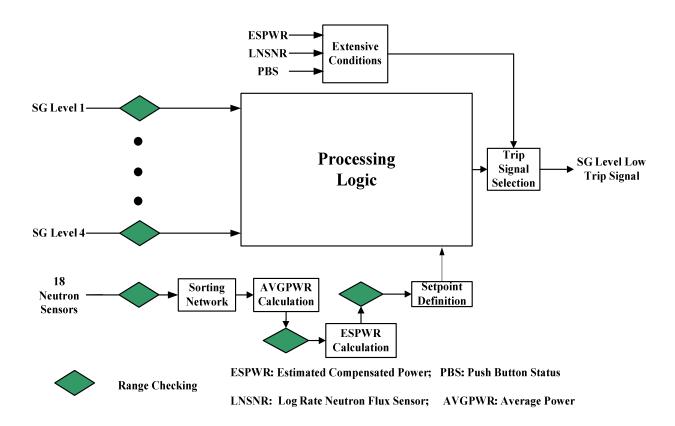

| Figure 4.4 – SG low level trip logic                                          | 106 |

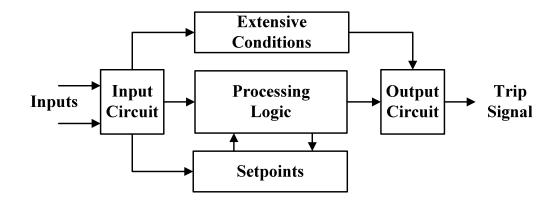

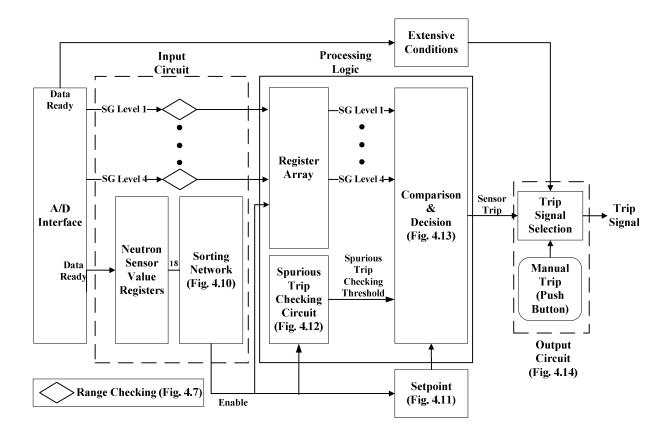

| Figure 4.5 – System architecture of the FPGA-based SDS1                       | 109 |

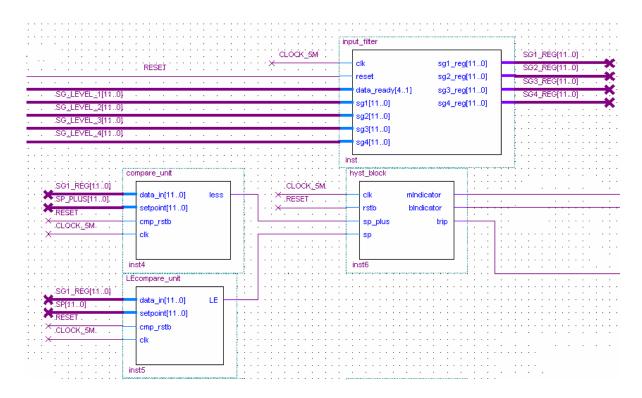

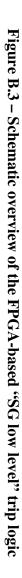

| Figure 4.6 – System description of the FPGA-based "SG low level" trip channel | 111 |

| Figure 4.7 – Parallel range checking circuit                                       | 13 |

|------------------------------------------------------------------------------------|----|

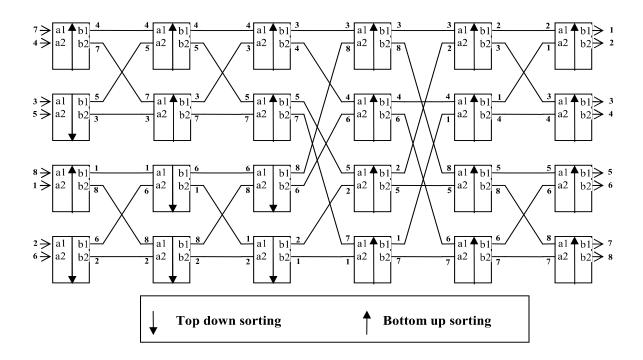

| Figure 4.8 – An illustrative diagram for Batcher-Merge sorting network             | 15 |

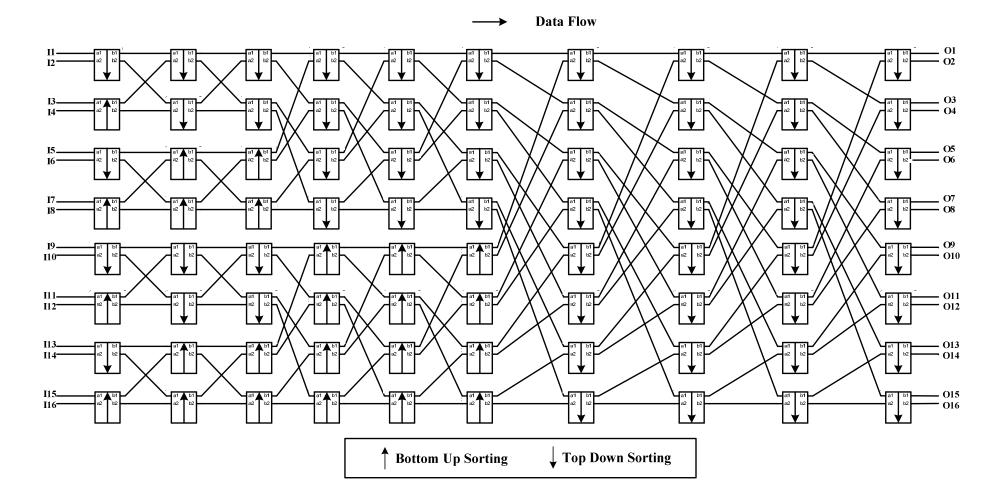

| Figure 4.9 – 16-element sorting network 11                                         | 17 |

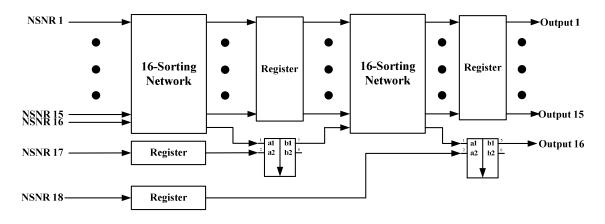

| Figure 4.10 – The "16 out of 18" method 11                                         | 18 |

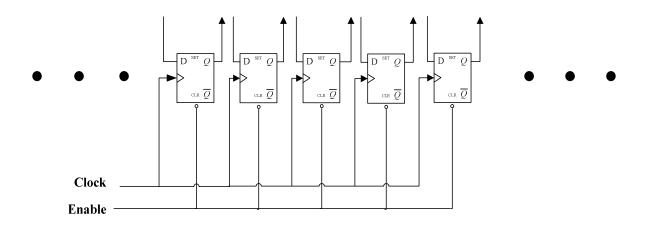

| Figure 4.11 – Register array for setpoint storage                                  | 19 |

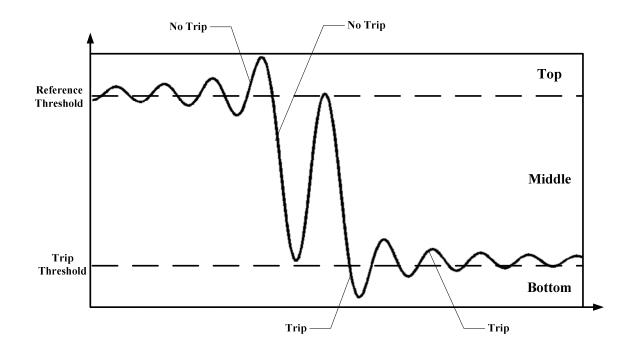

| Figure 4.12 – The two-threshold design                                             | 22 |

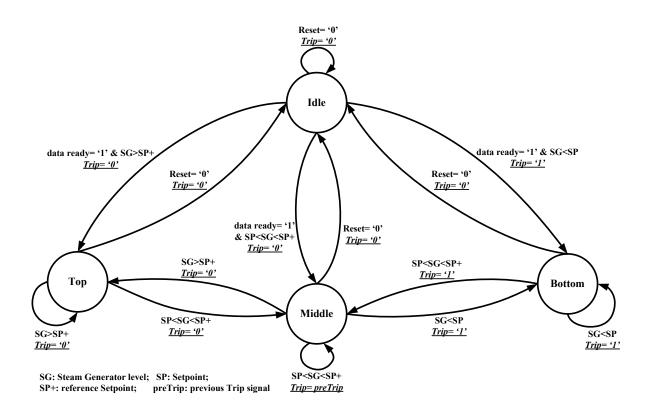

| Figure 4.13 – State diagram of the processing logic                                | 23 |

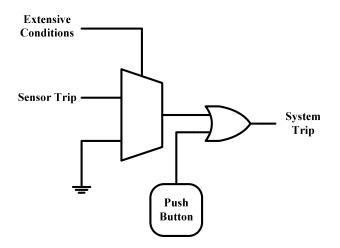

| Figure 4.14 – The structure of the output circuit                                  | 24 |

| Figure 4.15 – Snapshot of the EDA development environment                          | 25 |

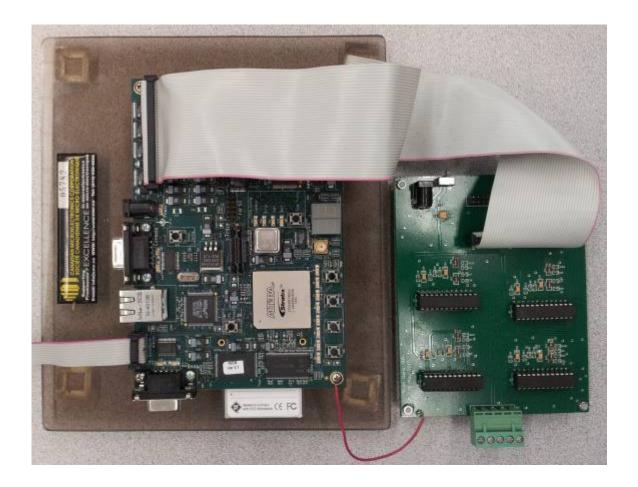

| Figure 4.16 – FPGA platform and the A/D interface                                  | 26 |

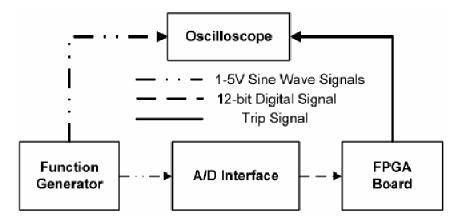

| Figure 5.1 – HIL simulation environment for functionality evaluation               | 31 |

| Figure 5.2 – Channels representation of the HIL simulation                         | 31 |

| Figure 5.3 – Setup for evaluation response time of the FPGA implementation         | 32 |

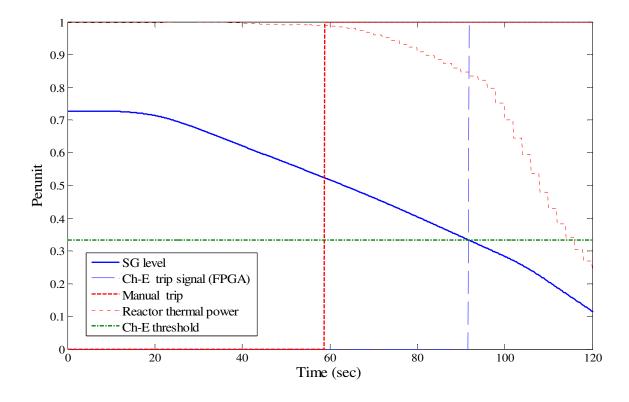

| Figure 5.4 – Functionality evaluation of FPGA-based SDS1                           | 34 |

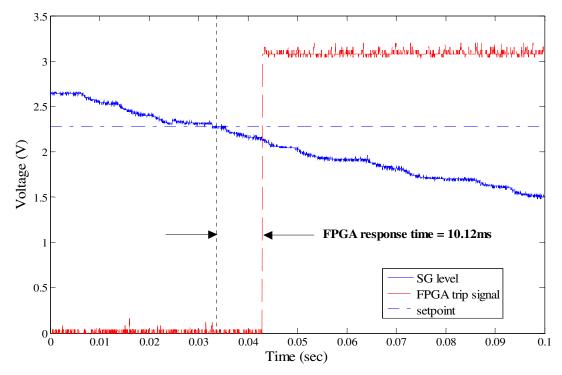

| Figure 5.5 – Result of a response time test of the FPGA-based SDS1                 | 35 |

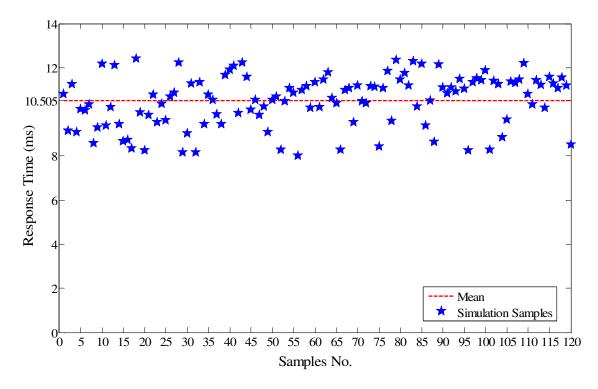

| Figure 5.6 – Distribution of the timing simulation samples                         | 35 |

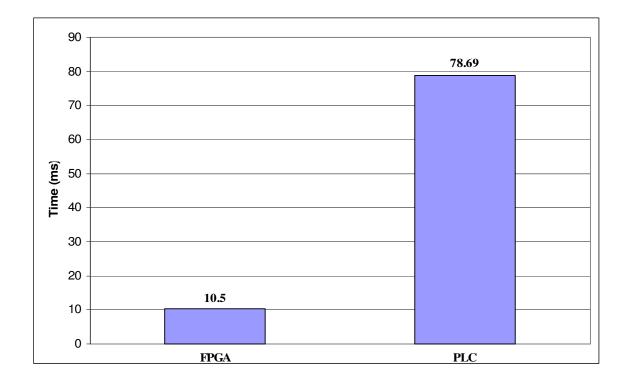

| Figure 5.7 – Comparison of response time between FPGA and PLC                      | 37 |

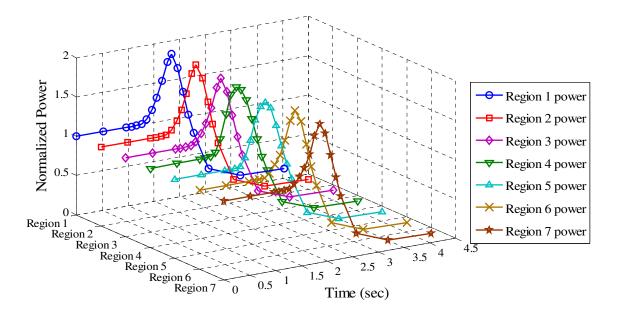

| Figure 5.8 – Region power transients with 100.0 ms response time                   | 40 |

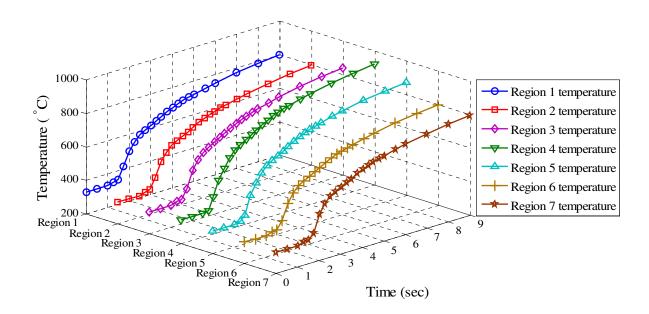

| Figure 5.9 – Region temperature transients with 100.0 ms response time             | 40 |

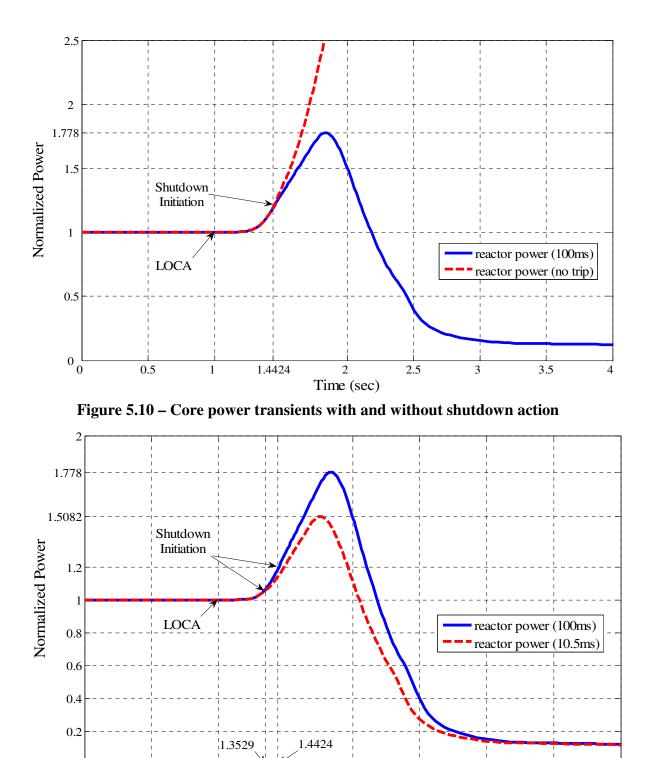

| Figure 5.10 – Core power transients with and without shutdown action               | 41 |

| Figure 5.11 – Comparison of power transients under two different response times 14 | 41 |

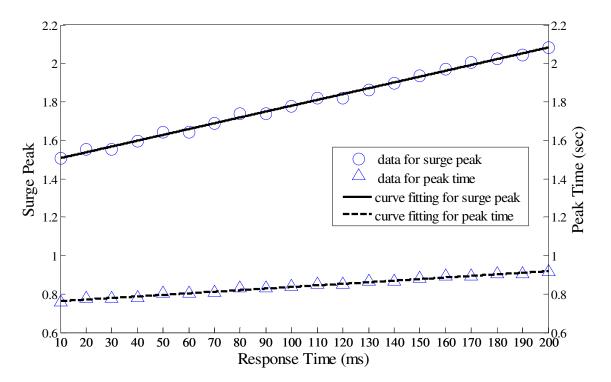

| Figure 5.12 – Power surge (peak and time) vs. the response time                    | 44 |

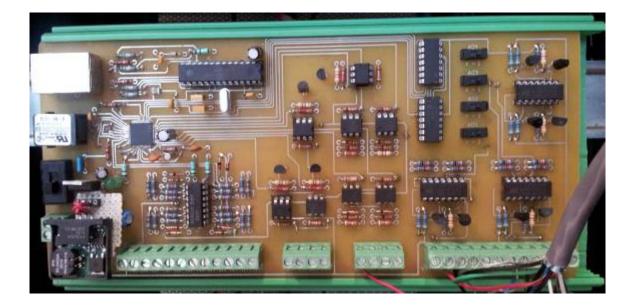

| Figure 6.1 – Microprocessor-based HIL interface board                              | 48 |

| Figure 6.2 – National Instruments PXI-7811R FPGA platform 14                       | 49 |

| Figure 6.3 – National Instruments expansion chassis and I/O modules 15             | 50 |

| Figure 6.4 – Assembly of the PXI FPGA system 15                                    | 50 |

| Figure 6.5 – Logic process of neutron overpower trip process                       | 51 |

| Figure 6.6 – Programmed neutron overpower trip logic                               | 52 |

| Figure 6.7 – Real-time monitoring interface                                        | 53 |

| Figure 6.8 – HIL simulation setup with FPGA-based shutdown channel 15              | 54 |

| Figure 6.9 – Experimental setup with FPGA-based shutdown channel                   | 55 |

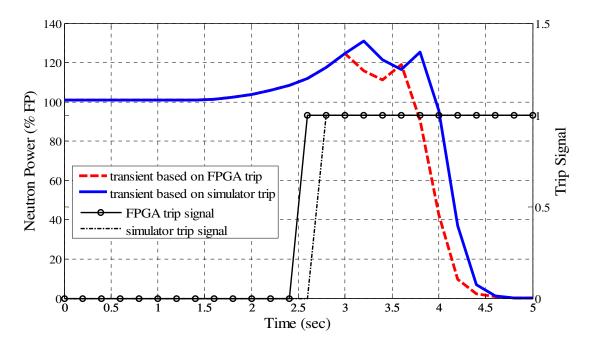

| Figure 6.10 – Power comparison between FPGA trip and simulator trip channels | 158 |

|------------------------------------------------------------------------------|-----|

| Figure 6.11 – Potential power upgrade with a faster SDS1                     | 159 |

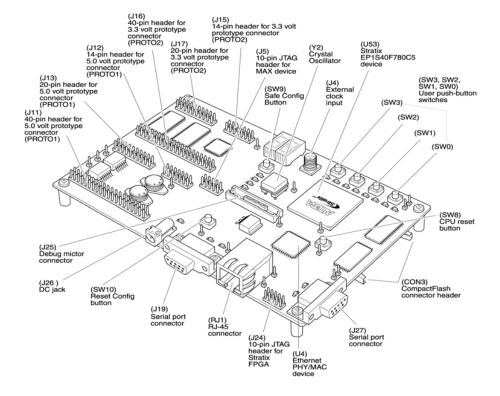

| Figure B.1 – Component layout of the Stratix FPGA development board          | 213 |

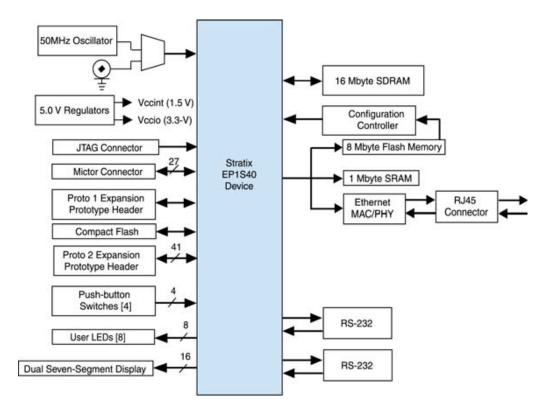

| Figure B.2 – Block diagram of Stratix FPGA development board                 | 214 |

| Figure B.3 – Schematic overview of the FPGA-based "SG low level" trip logic  | 215 |

# ABBREVIATIONS AND NOMENCLATURE

# Abbreviations

| 2003    | Two-out-of-three voting                                     |

|---------|-------------------------------------------------------------|

| A/D     | Analog to Digital                                           |

| AECB    | Atomic Energy Control Board                                 |

| AECL    | Atomic Energy Canada Ltd.                                   |

| ALARA   | As Low As Reasonable Achievable                             |

| AOO     | Anticipated Operational Occurrence                          |

| ASIC    | Application Specific Integrated Circuit                     |

| BWR     | Boiling Water Reactor                                       |

| CANDU   | CANadian Deuterium Uranium                                  |

| CATHENA | Canadian Algorithm for THEermalyhraulic Network Analysis    |

| CNSC    | Canadian Nuclear Safety Commission                          |

| CSA     | Conservative Safety Analysis                                |

| DBA     | Design Based Accident                                       |

| DCC     | Digital Control Computer                                    |

| DSP     | Digital Signal Processing                                   |

| EDA     | Electronic Design Automation                                |

| EdF     | Electricite de France                                       |

| E/E/PE  | Electrical, Electronic, and Programmable Electronic systems |

| EMI     | Electromagnetic Interference                                |

| EPZ     | Elektriciteits Produktiemaatschappij Zuid-Nederland         |

| FPGA    | Field Programmable Gate Array                               |

| HIL     | Hardware-In-the-Loop                                        |

| HTS     | Heat Transport System                                       |

| I&C     | Instrumentation and Control                                 |

| 1/0     | Input and Output                                            |

I/O Input and Output

| IAEA     | International Atomic Energy Agency          |

|----------|---------------------------------------------|

| IEC      | International Electrotechnical Commission   |

| LOCA     | Loss of Coolant Accident                    |

| LOFA     | Loss of Flow Accident                       |

| NI       | National Instruments                        |

| NPP      | Nuclear Power Plant                         |

| РСВ      | Printed Circuit Board                       |

| PDC      | Programmable Digital Comparator             |

| РНТ      | Primary Heat Transport                      |

| PJA      | Prompt Jump Approximation                   |

| PLD      | Programmable Logic Device                   |

| PROM     | Programmable Read-Only Memory               |

| PWR      | Pressurized Water Reactor                   |

| R/D      | Research and Development                    |

| RIH      | Reactor Inlet Header                        |

| ROH      | Reactor Outlet Header                       |

| ROPT     | Reactor Overpower Trip                      |

| RRS      | Reactor Regulating System                   |

| SDS      | Shutdown System                             |

| SDS1     | Shutdown System No. 1                       |

| SDS2     | Shutdown System No. 2                       |

| SG       | Steam Generator                             |

| SIL      | Safety Integrity Level                      |

| SUT      | System Under Test                           |

| U.S. NRC | United States Nuclear Regulatory Commission |

| V&V      | Verification and Validation                 |

| VHDL     | VHSIC Hardware Description Language         |

| VHSIC    | Very High Speed Integrated Circuit          |

# Nomenclature

| a                               | reactivity insertion rate                                        |

|---------------------------------|------------------------------------------------------------------|

| A                               | reactivity feedback coefficient                                  |

| В                               | reactivity feedback coefficient                                  |

| β                               | faction of the single group delay neutrons in the total neutrons |

| $eta_i$                         | fractions of one of the six delay neutron groups                 |

| C <sub>i</sub>                  | concentration of one of the six delay neutron groups             |

| $e_E$                           | relative error of the mean                                       |

| Ε                               | mean of measured response time samples                           |

| γ                               | a / β                                                            |

| $\Delta k$                      | added reactivity by the change of the density or the temperature |

| $K_{e\!f\!f}$                   | effective reactor multiplication constant                        |

| l                               | lifetime of the single group delay neutrons                      |

| $l_i$                           | lifetime of one of the six delay neutron groups                  |

| L                               | $\gamma - t_{k1}$                                                |

| λ                               | decay constant of the single group delay neutrons                |

| $\lambda_{i}$                   | decay constant of one of the six delay neutron groups            |

| ρ                               | reactivity                                                       |

| $\sigma$                        | standard deviation of the measured response time samples         |

| $\sigma_{\scriptscriptstyle E}$ | standard deviation of the mean                                   |

| $n_0$                           | initial neutron flux density                                     |

| $n_j$                           | maximum of neutron flux density in process $j$                   |

| $n_k$                           | maximum of neutron flux density in process $k$                   |

| n(t)                            | neutron flux density                                             |

| $n(t)_{\rm max}$                | maximum of the neutron flux density                              |

| $n_1(t)$                        | neutron flux density in time range $(0 \le t \le t_1)$           |

| $n_2(t)$                        | neutron flux density in time range $(t_1 \le t \le 2t_1)$        |

| $P_{peak}$                    | peak of the power surge                                   |

|-------------------------------|-----------------------------------------------------------|

| $SP_V$                        | voltage value of the setpoint                             |

| $SP_b$                        | binary value of the setpoint                              |

| $\Delta t$                    | $t_{k1} - t_{j1}$                                         |

| <i>t</i> <sub>1</sub>         | shutdown initiation time                                  |

| t <sub>d</sub>                | decision-making time of SDS1                              |

| <i>t</i> <sub>j1</sub>        | shutdown initiation time of process j                     |

| t <sub>jd</sub>               | decision-making time of SDS1in process j                  |

| <i>t</i> <sub><i>k</i>1</sub> | shutdown initiation time of process $k$                   |

| t <sub>kd</sub>               | decision-making time of SDS1in process k                  |

| t <sub>r</sub>                | time for an accident transient to reach the setpoint      |

| x                             | the appropriate variable (coolant density or temperature) |

## **1 INTRODUCTION**

A nuclear power plant (NPP) is a complicated system which utilizes nuclear fission energy to generate electricity. It has been proved to be an effective and clean way to provide energy to human society. However, both the fuel and the fission products are radioactive and could harm human health, if handled inappropriately. Thus, safety is always the top priority during the design, construction, and operation of an NPP. Nowadays, more and more technologies have the potential of improving NPP safety. This thesis focuses on improving the safety margins of NPPs using Field Programmable Gate Arrays (FPGAs). A brief introduction is given in this chapter to illustrate NPP safety issues, CANadian Deuterium Uranium (CANDU) NPPs, safety systems in CANDU NPPs, FPGA technology, and the motivations, objectives, as well as the research approaches taken in this thesis.

### 1.1 Safety issues in NPPs

Nuclear safety refers to managing the operational risk such that the probability of releasing radioactive materials or other hazards is kept at an acceptable level. It is always the top priority of NPPs since the results of nuclear accidents can cause severe public hazards and massive economic loss. More specifically, operational limits and safety requirements have to be established with the objective of keeping the risk associated with plant operation within the limits prescribed by government appointed independent nuclear safety regulators. Satisfaction of these limits and requirements demands reliable

and effective safety systems that are capable of ensuring safe operation, preventing severe accidents, and alleviating the accident consequences. Technical specifications are also declared for NPP systems and operation status such that the plant operation does comply with all the necessary limits and requirements.

#### 1.1.1 Safety objectives and requirements in NPPs

According to the documentations released by the International Atomic Energy Agency (IAEA), all the requirements for minimizing the risks associated with NPPs are derived based upon three fundamental safety objectives [1]:

- (1) **General nuclear safety objective:** To protect individuals, society and the environment from harm by establishing and maintaining in nuclear installations effective defences against radiological hazards;

- (2) **Radiation protection objective**: To ensure that in all operational states radiation exposure within the installation or due to any planned release of radioactive material from the installation is kept below prescribed limits and as low as reasonably achievable, and to ensure mitigation of the radiological consequences of any accidents; and

- (3) **Technical safety objective**: To take all reasonably practicable measures to prevent accidents in nuclear installations and to mitigate their consequences should they occur; to ensure with a high level of confidence that, for all possible accidents taken into account in the design of the installation, including those of very low probability, any radiological consequences would

be minor and below prescribed limits; and to ensure that the likelihood of accidents with serious radiological consequences is extremely low.

The latter two objectives are indeed complementary support to the general one, which indicate specific goals from two different aspects. Measures, like reactor regulating system (RRS) and digital control computers (DCCs), are taken to guarantee that these objectives are achievable at any of the plant's operational states. Although the NPP design is required to cut down the likelihood of plant states that could lead to radioactive releases, it has to be clearly indicated that the probability of an accident does exist. In the case of an accident, further measures, such as deployment of safety systems and post-accident systems, are necessary to keep the level of radioactive exposure as low as possible and mitigate subsequent radiological consequences.

To achieve the above three fundamental objectives, safety requirements are issued and applied to every lifecycle stage and every operational state of an NPP. These safety requirements cover design, operation, and decommission of an NPP. They are specified for each lifecycle stage from risk management, safety defence, principle technology, to human factors. These requirements are mandatory and documented as regulations for the nuclear industry.

At the design stage of a new NPP, comprehensive safety analysis is required to identify all the possible sources and evaluate the effects that radiation doses could bring to on-site workers, the public, and the environment. The design organization is required to ensure that the NPP is designed to comply with all the necessary safety regulations. The accomplished design should also pass an independent safety assessment before it can be delivered for fabrication/construction. During the design process, a requirement so called "defence in depth" [2] shall be incorporated such that the NPP can maintain the integrity of physical barriers of radioactive materials. The defence in depth concept includes a series of levels of protection with a consideration of both accident and failure of certain barrier. It offers NPPs graded safety protection against various possibilities of transients, anticipated operational occurrences (AOOs), and accidents. Following such a concept, the design is required to be carried out through safety classification, general plant design, plant system design, equipment qualification, human factor evaluation, etc. Safety systems of NPPs, due to their importance to plant safety, are highly considered with more specific requirements. The operating organization, on the other hand, is also required to prescribe proper operating procedures and assure their execution.

### 1.1.2 Operation limits and safety margins

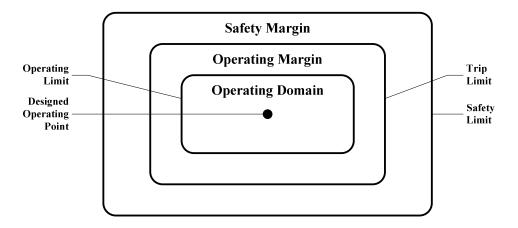

With the purpose of meeting the safety requirements, a comprehensive description of NPP operating status is provided by defining operational limits. These operational limits categorize the plant behavior into several domains and margins. As an example, the limits and margins used in CANDU NPPs are illustrated in Figure 1.1 [3]:

Figure 1.1 – Limits and margins of CANDU NPPs

As can be seen, the normal operation of a CANDU NPP is restricted within the "operating domain" by the trip limit (trip setpoint). While safety limit indicates the regulatory acceptance criteria. Violation of the safety limit can lead to severe accident such as fuel channel dryout, which may cause catastrophic consequences, say, core meltdown. In case of an accident, parameters representing reactor behavior, such as reactor power and temperature, will drift out of the operating domain and violate the trip limit. NPP safety systems then step in to execute reactor trip functions, preventing the safety limit of the reactor from being exceeded. With the consideration that it takes time to accomplish the trip process, the trip limit is defined lower than the safety limit. Two quantities, margin to trip and margin to dryout, are discussed in [4], giving a clear illustration of their relationship.

According to the official IAEA definition, safety margin is "the difference or ratio in physical units between the limiting value of an assigned parameter the surpassing of which leads to the failure of a system or component, and the actual value of that parameter in the plant" [5]. It plays an important role of transient buffer between the operating value and the regulatory acceptance criteria. Because it takes time for the accidental transients of operating parameters to overcome this buffer, the existence of safety margin allows safety systems to detect accidents, stop the dangerous progress, and mitigate major threatening consequences.

Variables within the reactor can change dramatically in the event of an accident. For example, in a large loss of coolant accident (LOCA) in CANDU, the positive reactivity, as a result of quick voiding of the primary heat transport (PHT) system, can be as high as  $+4.3 \ mk$  at 0.9 second into the accident [6]. As a consequence, the temperature and the

reactor power can elevate at an expeditious rate, which poses a serious threat to the reactor safety. Various accident analyses have been done to show how CANDU reactors mitigate severe accidents within the safety limits [7-11]. Safety margins buffer these accident transients and keep the plant safety under such undesired accident conditions. Due to its importance to the plant safety, safety margin is often utilized in NPPs for modifications and performance improvement [12].

#### 1.1.3 NPP safety systems

It is strictly required that NPPs must be equipped with safety systems such that the plant safety is preserved even when an accident happens. Major functionality of the safety systems is to prevent the damage of physical barriers and the releasing of radioactive substances. Moreover, NPP safety systems have to mitigate the post-accident consequences such that the damage or harm caused by the accident is reduced to a level as low as possible.

No matter which reactor type is adopted in an NPP, its safety systems are normally categorized into reactor protection system, emergency core cooling system, and containment system with respect to their functions. The reactor protection system has the responsibility of shutting down the reactor once the reactor is threatened by abnormal transients, e.g. rapid increase of reactor power. Methods of shutting down the reactor include insertion of control/shutoff rods and injection of neutron poison. Either of them introduces rapid neutron absorption that leads to reactor shutdown. The emergency core cooling system provides extra coolant supply for both the core and the containment in case of undesired loss of coolant. The temperature is then kept at an acceptable level to prevent damage such as core melt. Failure of such safety systems can lead to severe

consequences, such as what happened in Fukushima NPP, Japan [13]. The containment system, including the fuel cladding, reactor vessel, and primary containment, is a group of physical barriers that prevent radioactive materials from being released to the environment. The containment system also possesses depressurization and exhausting equipments to strengthen the seal function.

## 1.2 Safety systems in CANDU NPPs

CANDU is a unique reactor type that were designed and developed by Atomic Energy Canada Limited (AECL) and Ontario Hydro since the early 1950s [14]. Its unique features, such as heavy water moderator, horizontal calandria, and on-line refueling, make it one of the most successful reactor types for commercial production of electricity [15]. Safety systems of CANDU are capable of detecting accident situations and mitigating the relevant consequences.

### 1.2.1 General information

Safety systems are deployed in CANDU NPPs to prevent catastrophic consequences resulting from accidents. Accident scenarios are detected and the reactor is shut down in a timely fashion. They are also in charge of dealing with the post-accident situation such as removing residual heat, refilling the fuel channel with coolant, preventing release of hazardous radioactive particles, etc.

Four fundamental safety functions are considered in CANDU NPP safety systems, which are consistent with international reactor safety design principles and Canadian safety requirements [16]. They are:

- (1) To shutdown the reactor and maintain it in a safe shutdown condition;

- (2) To remove decay heat from the fuel effectively;

- (3) To maintain a barrier to limit radioactive release to the public and plant personnel; and

- (4) To supply information necessary for the operator to monitor the status of the plant.

In order to achieve the above functions effectively, CANDU safety systems are categorized as shutdown systems, post-shutdown safety systems, and safety support systems.

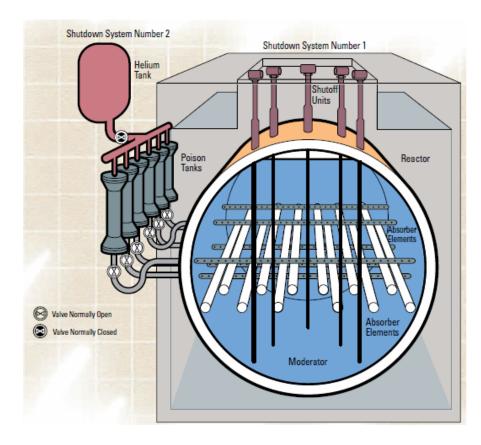

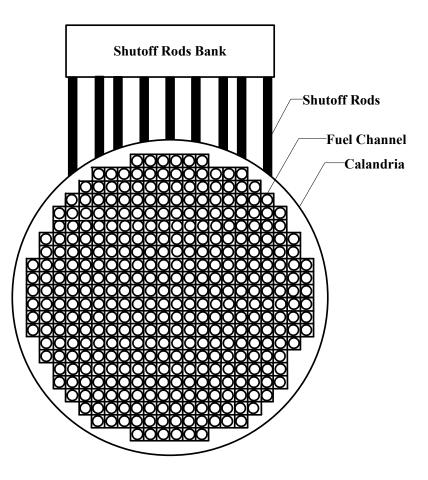

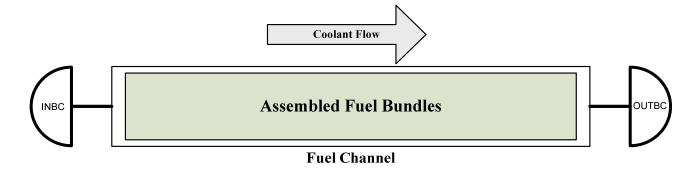

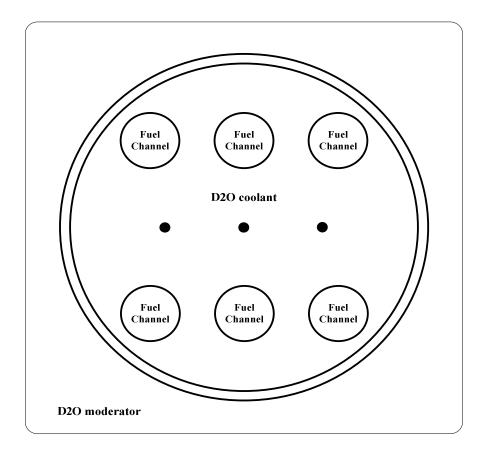

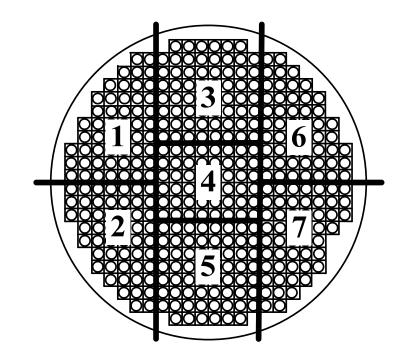

Figure 1.2 – CANDU SDS1 and SDS2

Shutdown systems are used to, as indicated by their names, shutdown the reactor before an accident causes serious damage to the plant. Figure 1.2 [17], describes the CANDU shutdown system No. 1 (SDS1) and shutdown system No. 2 (SDS2), respectively. SDS1 shuts the reactor down by inserting 28 shutoff rods from the top of the calandria, while SDS2 performs the shutdown action in a manner of rapid poison injection. When the reactor is shutdown, it is the responsibility of the post-shutdown systems to alleviate the consequences that has been caused by the accident, such as decay heat removal. The safety support system, which provides power and monitoring information for shutdown and post-shutdown purposes, works together with the above mentioned safety systems to assure a successful shut down process.

#### 1.2.2 SDS1

All CANDU NPPs are required to be equipped with two independent and diverse shutdown systems, SDS1 and SDS2. Each shall be able to shutdown the reactor and keep the reactor subcritical such that any fuel failure mechanism shall not result in a loss of primary heat transport system integrity.

In CANDU 6 SDS1, there are totally 28 shutoff rods arranged in two banks with 14 rods each. They are located right above the top of the reactor so that gravity can be the driving force when a drop-down action is required.

As one of the safety systems in CANDU NPP, SDS1 has to meet strict requirements that are stipulated for these safety systems [18]:

(1) shutdown the reactor and keep it subcritical whenever necessary;

(2) have high availability;

- (3) have online testing ability;

- (4) have enough redundancy and independency; and

- (5) perform its function on time whenever necessary.

According to the requirements documented by regulators, the unavailability of CANDU SDS1 is required to be less than  $10^{-3}$  years per year, which means the fraction of time for which SDS1 is not available per year shall be demonstrated to be less than  $10^{-3}$  years. The online testing ability is required to ensure the availability of SDS1 such that the testing of SDS1 can be carried out without a reduction in the effectiveness of the system. Sufficient redundancy and independency allow the SDS1 to remain functional when a failure of any single component in the SDS1 happens. On-time actuation of SDS1 is critical to plant safety since the consequence could be much worse with a delayed shutdown in an accident with rapid transient. The response time of SDS1 is the key factor that affects the shutdown speed. The shorter the response time is, the faster the SDS1 can shutdown the reactor, resulting in a lower power surge. Thus shortening the response time could help improve the safety features in the plant.

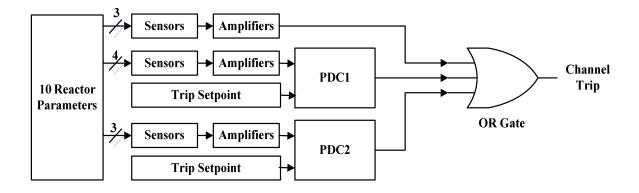

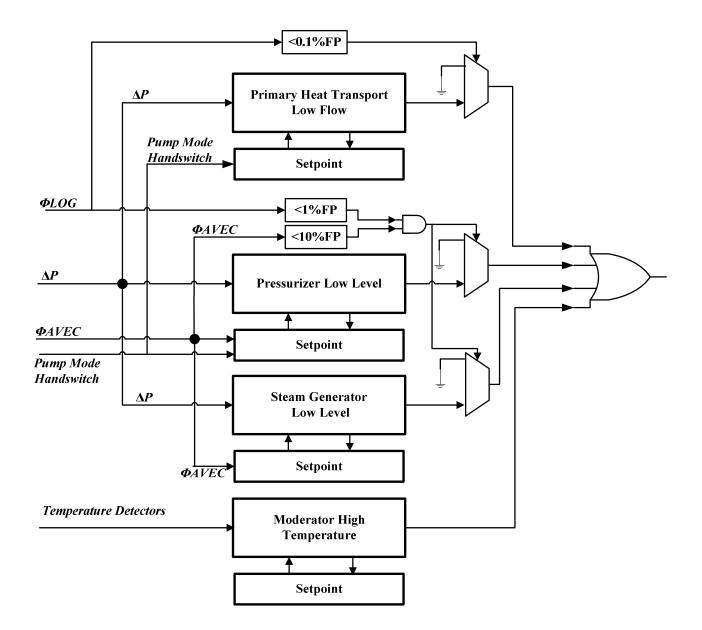

To obtain the mentioned qualifications, the SDS1 control is designed to be a triplicate, relay logic applied system [19]. There are a total of three trip channels (D, E, and F) with completely independent and physically separated power supplies, trip parameter sensors, instrumentation trip logic and annunciation. Each trip channel has exactly the same functionality. The reliability and availability criteria are met with the triple redundancy

while the online testing ability is allowed by the independence between each channel. Meanwhile spurious trips are also effectively prevented through a two out of three (2003) vote of the three outputs of the triple redundant trip channels. This majority voting logic permits the reactor trip signal to be released only when at least two trip channels are on trip status, which reduces the probability of a false trip decision.

SDS1 is one of the most important safety systems in CANDU NPPs since it provides an effective and reversible shutdown process. Due to its importance to the plant safety, there have been many efforts for SDS1 improvement, which leads to three evolutions [20]. With a purpose of enhancing plant safety, the current thesis work also focuses on improving SDS1 using digital hardware technology.

### 1.3 Research motivations

The motivations of using FPGA technology to improve CANDU SDS1 and further the NPP safety margin lie in several technical aspects: potential benefits of an improved safety margin, the problems that an existing CANDU SDS1 is facing, and FPGA advantages for SDS1 improvement. This thesis work is stimulated when FPGA has shown its superiority in some non-safety applications of nuclear industry [21]. At the same time, conventional safety system in existing CANDU NPPs are facing problems ranging from obsolescence resistance to regulatory approval difficulties. Preliminary investigations show that applying FPGA technology to CANDU SDS1 not only solve current technical problems, but also can lead to safer operation and even performance enhancement of the plant.

#### 1.3.1 Safety margin improvement

Safety margin is a buffer between the normal operation and unacceptable system failure caused by an accident. A more conservative safety margin ensures higher tolerance to accident consequences. If SDS1 reacts to the accident with a shorter response time, the trip process will be initiated earlier and the transient surge of reactor parameters will be lower. Moreover, process variables such as temperature and pressure progress rapidly during accidents. Hence, the earlier the reactor is shutdown, the lighter the impact of the accident would be. For example, less heat is generated when the chain reaction is stopped earlier, which alleviates the post-accident recovery. Considering the fact that FPGA systems have the potential of faster processing speed than software-based ones for a given algorithm/logic, the safety margin improvement can be realized by a faster shutdown process via an FPGA-based shutdown system. Detailed validation of such a concept will be discussed in detail in Chapter 2 based on neutron dynamics analysis.

A further idea regarding to a faster shutdown is that the operating power of the plant can be upgraded without endangering the plant safety. Since the surge peak of an accident transient with a faster shutdown process is lower, power upgrade is allowed as long as the accidental surge peak remains within acceptable criteria. If the safety margin improvement with faster shutdown is validated, then there is a possible chance for the power upgrade. However, power upgrade not only depends on the realization of faster shutdown process, but also regulatory approval and other engineering considerations on related systems.

#### 1.3.2 SDS1 performance

As one of the most important safety systems in CANDU NPPs, SDS1 takes critical responsibility of protecting the reactor. Since it is the first safety system that reacts to an NPP accident, there is a direct relationship between SDS1 performance and the NPP safety margin. Regulators require SDS1 to have the highest safety integrity level (SIL). Its performance is hence one of the key issues of NPP safety.

SDS1 is a standby system waiting to be called upon to shutdown the reactor. Therefore, 1) it should have high reliability when waiting for the call of duty; 2) it should react to the upset condition quickly and properly to mitigate the post-accident consequences; and 3) it should have firm obsolescence resistance since an NPP is built to be in service for decades. The software-based SDS1, however, is facing problems at meeting these requirements because of its inherent failure modes, serial processing pattern, and unavoidable reprogramming process for alternative platforms.

Inherent failure modes and difficulties of algorithm validation have burdened the regulatory approval process for software reliability and availability. In a microprocessorbased platform, task-distribution process and the serial processing pattern limit the overall processing speed. The obsolescence problem becomes more and more serious with microprocessor-based systems under rapid technology progress. These problems are offering a margin for SDS1 performance improvement. For this reason, SDS1 is chosen as the research topic of this thesis work to investigate how its performance can be improved and how the plant safety margins can be improved with a faster speed of response of the SDS1.

### 1.3.3 Advantages of using FPGAs

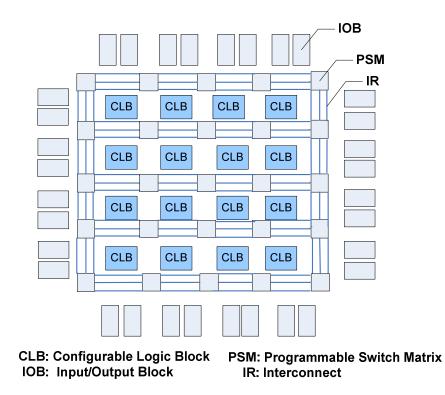

FPGAs have been widely utilized in applications where flexible and low cost digital hardware implementations are needed. This programmable semiconductor device contains a matrix of high density configurable logic blocks connected via programmable interconnects. Resorting to computer-based design tools, the logic design for FPGAs is essentially circuit-independent [22]. This unique feature enables a design to be transferred from one FPGA platform to another without going through redesign [23], which leads to potential enhancement of the obsolescence resistance of a system. A schematic view of an FPGA chip structure is shown in Figure 1.3.

Figure 1.3 – Schematic view of an FPGA chip

It is important to point out that, in the design and implementation phase of any FPGA systems, Electronic Design Automation (EDA) tool kits which are operating system driven are involved. However, once the design and implementation phase is complete, the

final implemented product is a pure hardware system. It does not include software failure modes so that the regulatory approval process becomes less complex.

With the help of parallel processing and pure hardware implementation, FPGAs have the potential to achieve faster processing speed than software-based systems. Development of modern semiconductor technology has allowed the amount of logic elements in one FPGA chip to reach a million-gate level. This feature offers abundant resource for realizing parallel processing for all the similar logic steps, say, thousands of value range checking. Propagation delay and queuing time consumed in a serial processing system are eliminated and, hence a faster processing speed can be obtained. In a pure hardware implementation, no operating system exists. Even the memory access is not necessary if there are no complicated calculations. Logics that are to be processed then can be distributed to corresponding elements directly through pre-configured routes. Therefore, the results can be obtained at the output quickly. In previous applications of FPGAs, it was found the processing speed of FPGAs can be two to three orders of magnitude faster than pure software implementation for the same problem [24].

Having the capability of higher obsolescence resistance, easier regulatory approval, and faster processing speed, FPGAs have shown great potential for improving current NPP safety systems that are computer-based. How to realize an FPGA-based safety system and how the NPP safety features can be improved by this method are the main motivations for this thesis.

FPGA itself is not a brand new technology but has become more and more powerful for implementation of customized systems. Its logic elements capacity and processing speed

have been improved by several magnitude orders since it was invented in 1985, which now makes it possible for the replacement of software-based systems such as the existing SDS1.

As what have been introduced, FPGA has obvious advantages over software-based systems such as improved obsolescence resistance, easier approval procedure, and faster processing speed. Replacing those existing software-based systems, even safety-related systems in NPPs, with FPGA-based platform, can have these advantages fully utilized. As a consequence, the whole plant can benefit from these advantages to achieve a safer NPP.

### 1.4 Objectives, methodologies, and scope of research

Current thesis work focuses on: 1) exploring the speed of the shutdown systems and its impact on plant safety; 2) validating the concept of improving safety margin with faster shutdown process; 3) realizing the SDS1 trip logic that is currently implemented within a software-based system; 4) verifying and validating its performance; and 5) evaluating the improvement that can be realized. To accomplish the listed objectives, research methodologies are defined as well as the research scope.

#### 1.4.1 Research objectives

Objectives of the work are defined for three major stages of the research procedure: 1) analysis for the plant accident behavior and the impact of faster shutdown process; 2) implementation of an FPGA-based SDS1; and 3) evaluation of the FPGA-based SDS1 and the safety margin improvement.

The analysis work concentrates on the accident scenarios and the related plant response. Analytical attempts are used to explore in detail the accidental transients within different shutdown processes. The objectives for the analysis work are defined below:

- (1) Accident scenarios are to be set up as analysis objects; and

- (2) The concept that the safety feature can be improved via a faster SDS1 is to be validated and verified based on the predefined accident scenarios;

For the FPGA implementation work, the focus is on: 1) the feasibility of a pure hardware implementation of the SDS1 trip logic; and 2) the effective utilization of FPGA advantages for the SDS1 implementation. Then the objectives are defined as follows:

- An FPGA-based SDS1 trip channel is to be implemented. The related Input/Output (I/O) ports are defined and connected to a simulation environment for performance evaluation;

- (2) The functionalities of the designed FPGA-based SDS1 trip channel are validated under normal and accident conditions;

- (3) A methodology for comparison of the speed of responses is established; and

- (4) Comparisons are carried out under different NPP operating conditions.

For the evaluation of the safety margin improvement, expected outputs are an illustration of the benefits that a faster SDS1 can offer to the plant and a practical implementation that can show the proved improvement under certain accident scenarios. More specifically, the following issues are to be addressed:

- (1) The benefits of shortening response time of the shutdown systems is to be validated quantitatively in terms of the safety margins of a CANDU NPP;

- (2) A diverse FPGA implementation to achieve shortened response time and to validate the safety margin improvements in a simulation environment is to be demonstrated; and

- (3) Other benefits as a result of shorten response time, more specifically, the potential power upgrade, while maintaining the improved safety margins is to be explored quantitatively.

#### 1.4.2 Research approaches

To obtain the above objectives, suitable research approaches are determined through literature survey, assessment, and selection. Specific techniques are targeted to certain procedures for cost-effective results.

To validate the concept of safety margin improvement, thermalhydraulic analysis for accident transients is necessary. The analysis of transients based on distinct response time is capable of showing the improvement in a faster shutdown process against the slower one. With selected accident scenarios, an industry standard code, CATHENA [25], is used for such kind of analysis. A simplified reactor model and the accident scenarios are created for the thermalhydraulic simulation.

A standard FPGA development procedure is applied for the SDS1 implementation. A systematic design is drafted based on current SDS1 trip logic. Hardware coding,

simulation, synthesis, and configuration are performed by using industry standard development kit [26].

Hardware-in-the-loop (HIL) simulation [27] is chosen for the functionality and performance validation of the FGPA-based SDS1. With an industry grade NPP simulator available, the FPGA-based SDS1 can be tested by being connected to the simulator and acting as a trip channel that reacts to the simulated accidents. Real-time monitoring of variables and trip signals is then enabled. The functionality evaluation is then straightforward when the captured responses from the FPGA system are analyzed.

To statistically estimate the response speed of such an FPGA-based SDS1, Monte Carlo simulation [28] is selected. This is because the timing is not a fixed value due to measurement noise and equipment uncertainties. Applying this simulation method allows a more comprehensive description of the timing performance of the FPGA system, which is of importance to the safety margin improvement objective.

The thermalhydraulic simulations are utilized further to analyze the improvement based on evaluated timing performance of the FPGA-based SDS1. Transients of a worst-case accident are simulated using different response time of SDS1 to generate comparable results.

With the purpose of further verifying the effectiveness of the shortened response time and validating the safety margin improvement in a real-time environment, HIL simulation is again applied. Unlike the off-line CATHENA simulation, HIL simulation performs online performance evaluation and the performance of the tested system can be monitored in real time. In summary, the research approaches adopted in this work are listed as following:

- (1) Establish thermalhydraulic models for CATHENA simulations with specified accident scenarios that represent a typical worst case accident;

- (2) Analyze the simulated transients to verify the "faster shutdown" concept and validate the performance improvement;

- (3) Analyze the CANDU SDS1 trip logics and translate them into a suitable form for FPGA implementation;

- (4) Use a simulator to validate the results of the implemented FPGA system;

- (5) Use both deterministic and statistical methods to evaluate the performance of the FPGA-based implementation of SDS1 against its software-based implementations in PLCs;

- (6) Perform the thermalhydraulic simulation for the worst case scenario again using the evaluated FPGA response time;

- (7) Analyze transients of critical system variables based on the results of the thermalhydraulic simulation as a function of different shutdown response time to establish the baseline for evaluating the FPGA implementation;

- (8) Compare the simulation results with different response times so that the characteristics of transients are identified as a function of response time;

- (9) Describe how the safety margins can be improved with a faster decisionmaking process, as well as how this can be utilized for potential power upgrade; and

- (10) Demonstrate the feasibility of this approach using an HIL simulation with an industry grade CANDU NPP simulator and to provide further verification and validation.

## 1.4.3 Research scope

Although safety margin improvement covers a wide range of considerations, the current thesis mainly focuses on the CANDU safety margin improvement via improved SDS1 resorting to FPGA technology. Necessary bounds are defined such that the research is under explicit direction and the accomplished work is oriented to specific results.

First of all, the research objectives are defined within CANDU NPPs. Both the safety margin and the SDS1 trip logic are analyzed based on existing CANDU technical information. Although other NPPs or even non-nuclear industry share the safety margin concept as well, such kinds of safety margins are not considered in this work.

Secondly, the improvement of SDS1 is focused on the shortening of its response time using digital hardware implementation. After being in service for decades, SDS1 can be potentially improved in many ways. However, this work exams only the shortening of response time as an objective, to which research effort is mainly paid.

Choosing an FPGA as the implementation platform is based on its verified advantages, especially the fast processing that can potentially increase the SDS1 response speed.

Focus of this part is only to evaluate the response time of an FPGA-based SDS1prototype. There is no plan to qualify such a prototype work for regulatory approval, including the software design tools used for FPGA design and implementation.

Some of the FPGA advantages indicated in this work are derived from comparison against current software-based system. The comparison is based on a survey of previously accomplished work. There is no intention to evaluate software-based system here to provide a performance comparison.

Current study does not have all the SDS1 trip parameters implemented since one process trip parameter is enough for functionality validation and response time comparison against software-based system. Proper responses of other parameter implementation are only redundant supports and do not account more for the research objectives. However, data cross verifications between multiple channels will not be considered.

Finally, the accident scenarios applied for safety margin analysis are obtained from previous CANDU safety analysis work. The CATHENA simulation is mainly based on a selected worst case scenario which is enough to show the safety margin improvement. It has to be pointed out that the overall evaluation of the plant safety margin needs thorough study for different accident scenarios. However, this will be beyond the scope.

## 1.5 Main contributions

Within the prescribed research scope, this thesis uses SDS1 as an example to show how FPGA-based safety-critical system can improve the safety margin of CANDU NPPs as

well as the feasibility for potential power upgrade. The main contributions of this thesis can be summarized as:

- (1) A valuable reference for FPGA applications in NPP safety systems has been presented in the "Top-Down" design flow with special design techniques involved;

- (2) Performance illustration of FPGA-based SDS1 has been given by the timing evaluation, which proves the advantages of applying FPGAs to NPP safety systems;

- (3) Quantitative description of the safety margin improvement with faster shutdown process has been obtained through thermalhydraulic simulations;

- (4) Analytical relationships between the response time and the critical transient parameters are derived as an evaluation of the response time effects;

- (5) Potential power upgrade has been validated with thermalhydraulic simulations; and

- (6) The safety margin improvement has been validated by on-line HIL simulations using an NPP simulator.

# 1.6 Organization of the thesis

The remainder of this thesis is structured as follows: Chapter 2 presents analytical discussion for safety margin improvement, FPGA applications in NPPs, and relevant literature reviews. Chapter 3 covers the thermalhydraulic analysis for the validation of

safety margin improvement. The SDS1 trip logic and its FPGA implementation process are discussed in Chapter 4. The main content of Chapter 5 is the evaluation of both the FPGA-based SDS1 and the potential safety margin improvement. The HIL simulation work is introduced in Chapter 6 to demonstrate the safety margin improvement within a realistic NPP environment, followed by Chapter 7 where the conclusions are drawn and future research directions are suggested.

# 2 NUCLEAR SAFETY AND FPGA APPLICATIONS IN NPPS

The objective of the current research work deals with safety issues in NPPs due to their significance to both the plants and public safety. This chapter covers the essentials of nuclear safety and relevant FPGA applications, including safety regulations and standards, safety margins, safety systems, why and how FPGA-based system can be and has been applied to NPPs, etc. Detailed literature review is also presented on these aspects.

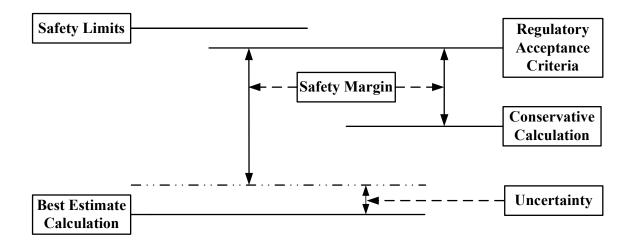

## 2.1 Nuclear safety

The safety assurance of an NPP is to protect the on-site operating staff, the public, and the environment from the hazards of the radioactive substances. To achieve such a goal, both natural and engineered radiation barriers are deployed. The design, operation, and analysis of an NPP have to comply with strictly prescribed safety regulations and standards issued by regulators such that the nuclear safety objectives are achieved. Safety margin is defined for a plant parameter as a buffer between the operating value and the tolerance of the barriers. These crucial barriers can then survive in accidents to prevent release of radiological hazards. Safety analysis methods are developed and utilized to evaluate the plant behavior and safety margins. Safety systems are designed and installed in order to detect the initiating conditions of undesired abnormal situations and mitigate the consequences.

#### 2.1.1 Regulations and standards

Significant efforts have been invested in designing reliable NPP safety systems to achieve the goal of safe and effective energy production. To satisfy the NPP safety demands, regulators and other national/international organizations, such as International Electrotechnical Commission (IEC) and IAEA, have developed guidelines and standards for the entire procedure of design, installation, and operation according to experiences and knowledge accumulated in decades.

#### (1) IEC standards

Among these organizations, IEC is well known for their meticulously developed IEC standards. For safety systems such as SDS1, where computer systems are involved, the standard named IEC-61508 provides corresponding requirements for their functional safety.

IEC-61508 is specifically developed to provide requirements and guidance for electrical, electronic, and programmable electronic (E/E/PE) systems that are used to carry out safety-related functions [29, 30]. It provides detailed lifecycle requirements for the system itself and its software along with the precise definitions, safety integrity requirement, and technique overview. In its general requirements, an overall framework of the lifecycle of safety-related systems is described using a flow chart. Each step of the lifecycle, such as risk analysis and system realization, is depicted with objective, scope, requirements, inputs, and desired outputs. Following the general requirements are the requirements for E/E/PE systems and software, respectively. Definitions and abbreviations are also indicated for the whole standard to obtain consistency.

Conformance to this standard is now an essential requirement by the regulators to the NPP research and development (R/D) procedure.

In addition to the IEC-61508 standard, there are two standards that are documented specially for NPPs: IEC-61513 and IEC-62138. IEC-61513 provides general requirements for NPP instrumentation and control (I&C) system important to safety [31], where both conventional hard-wired equipment and computer-based systems are considered. Requirements and recommendations for safety-related I&C systems are listed from overall architecture to each component. IEC-62138 focuses on the software aspects of computer-based systems that perform functional safety in NPPs [32].

Because of the popularity and effectiveness of IEC standards in NPP safety system R/D processes, they are considered as the minimum requirement for safety systems in NPPs. Each country develops its own regulations and guidance for nuclear safety based on related IEC standards.

### (2) IAEA safety series

IAEA takes the responsibility of guiding the peaceful nuclear power utilization, including the NPPs and medical isotopes. To explicitly define, describe, and enforce the appropriate use of nuclear energy, IAEA publishes its safety series covering all the aspects of nuclear safety. For instance, safety standards for NPPs are developed and published for the reference of all the countries that have nuclear energy utilization purposes [33]. As for I&C systems in NPPs, including the shutdown systems, IAEA publishes relevant standards and guidance. Especially with the rapid development of digital systems, IAEA issues its specifications of requirements for NPP I&C systems [34] as well as the requirements for safety related NPP systems [35]. The development work for NPP safety systems follows a strict life-cycle process such that the proper functionality and acceptable quality are ensured. FPGA-based systems, as one of the digital systems that are being utilized for NPP I&C applications, have to follow these standards as well.

#### (3) Canadian classification of NPP safety requirements

Starting from 1946, Canada established its own nuclear safety regulator at the outset of its nuclear development plan. This regulator, Atomic Energy Control Board (AECB), had been working for decades to provide surveillance and administration for Canada's nuclear industry until it was replaced by a new government-organized one, Canadian Nuclear Safety Commission (CNSC). With the evolution of CANDU reactors, safety requirements are developed to provide clearly defined safety objectives and the approaches. Presently, there are complete and mature safety guidelines and requirements for entire CANDU lifecycle, such as the "General Nuclear Safety and Control Regulations" and "Requirements for Shutdown Systems for CANDU NPPs". These regulations set the standards how CANDU reactors should be designed, operated, maintained, and protected. For example, requirements for SDS1 define what criteria an SDS1 should meet to achieve the safety [36]:

### (1) Seismic qualification;

(2) Environmental qualification including against jets crash and other dynamic loads;

- (3) Unavailability of less than  $10^{-3}$  years per reactor year;

- (4) Fail-safe operation;

- (5) On-line testing without impairing the normal operation;

- (6) Manual initiation from the control room;

- (7) Separation and independence of safety system channels from each other and from process systems; and

- (8) Requirements applicable to safety support equipment.

Safety analysis criteria are also available to guide licensees in a proper manner of performing the required safety analysis of a nuclear facility [37]. Only with the satisfaction of such criteria can CNSC accept the analysis results when considering a licensing process. One thing that needs to be clarified is that CNSC evaluates the compliance of safety criteria also in association with other international standards, such as those from IAEA and IEC. Safety analysis in this thesis work takes these requirements into priority consideration.

#### 2.1.2 Defence in depth

In fact, all the CANDU NPPs have extensive conventional safety programs which are much more stringent than that in other industrial facilities. The philosophy against hazards in NPP is to reduce the hazard levels to As Low As Reasonably Achievable (ALARA). Achievement in this aspect so far in Canada is that the radiation dose received by CANDU NPP onsite workers has been reduced by about a factor of 10 over the 40-50 years of plant operation [38]. With the rules listed as power control, fuel cooling, and

radioactivity containment, CANDU established its "Defence in Depth" safety concept. This concept assumes possible design flaws, equipment failures, as well as human errors. It then sets up a safety model to protect the plant from these threats using multiple barriers, reliable process systems, reliable safety systems, competent operating and maintenance staff, and failure detection/correction techniques.

To achieve the "Defence in Depth" goal and ensure safe and normal operation, NPPs require high reliability and availability of both process systems and safety systems. Several principles are followed during design and operation to meet the high reliability and availability requirements.

The first one is redundancy. Additional components are installed to the system to avoid whole system failure when one of the components is down. The redundant components increase the reliability and availability by providing a backup at possible single component failure. For example, both SDS1 and SDS2 have three redundant trip channels. By this means, the shutdown system maintains its function even when one or two of its trip channels are out of operation.