| Title                   | Secure architectures for pairing based public key cryptography                                                     |

|-------------------------|--------------------------------------------------------------------------------------------------------------------|

| Author(s)               | Pan, Weibo                                                                                                         |

| Publication date        | 2013                                                                                                               |

| Original citation       | Pan, W. 2013. Secure architectures for pairing based public key cryptography. PhD Thesis, University College Cork. |

| Type of publication     | Doctoral thesis                                                                                                    |

| Rights                  | © 2013. Weibo Pan<br>http://creativecommons.org/licenses/by-nc-nd/3.0/                                             |

| Embargo information     | No embargo required                                                                                                |

| Item downloaded<br>from | http://hdl.handle.net/10468/1336                                                                                   |

Downloaded on 2017-02-12T08:14:46Z

University College Cork, Ireland Coláiste na hOllscoile Corcaigh

# Secure Architectures for Pairing Based Public Key Cryptography

Weibo Pan September 2013

A Thesis Submitted to the National University of Ireland in Fulfillment of the Requirements for the Degree of Doctor of Philosophy

Supervisor: Dr. Liam Marnane Head of Department: Prof. Nabeel A. Riza

Department of Electrical and Electronic Engineering, University College, Cork

## ABSTRACT

Along with the growing demand for cryptosystems in systems ranging from large servers to mobile devices, suitable cryptogrophic protocols for use under certain constraints are becoming more and more important. Constraints such as calculation time, area, efficiency and security, must be considered by the designer.

Elliptic curves, since their introduction to public key cryptography in 1985 have challenged established public key and signature generation schemes such as RSA, offering more security per bit. Amongst Elliptic curve based systems, pairing based cryptographies are thoroughly researched and can be used in many public key protocols such as identity based schemes. For hardware implementions of pairing based protocols, all components which calculate operations over Elliptic curves can be considered. Designers of the pairing algorithms must choose calculation blocks and arrange the basic operations carefully so that the implementation can meet the constraints of time and hardware resource area. This thesis deals with different hardware architectures to accelerate the pairing based cryptosystems in the field of characteristic two. Using different top-level architectures the hardware efficiency of operations that run at different times is first considered in this thesis.

Security is another important aspect of pairing based cryptography to be considered in practically Side Channel Analysis (SCA) attacks. The naively implemented hardware accelerators for pairing based cryptographies can be vulnerable when taking the physical analysis attacks into consideration. This thesis considered the weaknesses in pairing based public key cryptography and addresses the particular calculations in the systems that are insecure.

In this case, countermeasures should be applied to protect the weak link of the implementation to improve and perfect the pairing based algorithms. Some important rules that the designers must obey to improve the security of the cryptosystems are proposed. According to these rules, three countermeasures that protect the pairing based cryptosystems against SCA attacks are applied. The implementations of the countermeasures are presented and their performances are investigated.

## CONTENTS

| 1. | Intro             | oductio        | n                                                                                                  | 7  |

|----|-------------------|----------------|----------------------------------------------------------------------------------------------------|----|

|    | 1.1               | Motiva         | ation                                                                                              | 7  |

|    | 1.2               | Aim o          | f thesis $\ldots$ | 8  |

|    | 1.3               | Thesis         | soutline                                                                                           | 10 |

| 2. | Background Theory |                |                                                                                                    |    |

|    | 2.1               | Introd         | uction                                                                                             | 13 |

|    | 2.2               | 2 Cryptography |                                                                                                    |    |

|    | 2.3               | Privat         | e and Public Key Cryptography                                                                      | 15 |

|    |                   | 2.3.1          | Private Key Cryptography                                                                           | 15 |

|    |                   | 2.3.2          | Public Key Cryptography                                                                            | 16 |

|    |                   | 2.3.3          | Identity Based Encryption                                                                          | 17 |

|    |                   | 2.3.4          | Attribute Based Encryption                                                                         | 19 |

|    |                   | 2.3.5          | ABE structure                                                                                      | 19 |

|    | 2.4               | Mathe          | ematical Background                                                                                | 21 |

|    |                   | 2.4.1          | Groups                                                                                             | 21 |

|    |                   | 2.4.2          | Finite Fields                                                                                      | 22 |

|    |                   | 2.4.3          | Elliptic Curves over Finite Fields                                                                 | 23 |

|    |                   | 2.4.4          | Point Operations over Elliptic Curves                                                              | 24 |

|    |                   | 2.4.5          | Elliptic Curve Discrete Logarithm Problem                                                          | 26 |

|    | 2.5               | Pairin         | g Based cryptography                                                                               | 27 |

|    |                   | 2.5.1          | Tate pairing over supersingular curves                                                             | 29 |

|    |                   | 2.5.2          | Implementing the Pairings                                                                          | 31 |

|    |                   | 2.5.3          | Bilinear Pairings applied in IBE                                                                   | 31 |

|    |                   | 2.5.4          | Bilinear Pairings applied in ABE                                                                   | 34 |

|    |                   | 2.5.5          | Security of Pairing based cryptosystem                                                             | 36 |

|    | 2.6               | Crypta         | analysis                                                                                           | 38 |

|    |                   | 2.6.1          | Side Channel Analysis Attacks                                                                      | 38 |

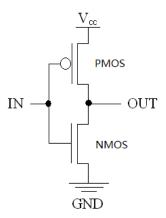

|    |                   | 2.6.2          | Hardware Power consumption                                                                         | 39 |

|                                                              |                                                                      | 2.6.3                                                          | Weakness in pairing based protocols to side channel attacks. $% \left( {{{\bf{x}}_{{\rm{s}}}}} \right)$ . | 41 |

|--------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----|

|                                                              |                                                                      | 2.6.4                                                          | Countermeasures against power analysis attacks                                                            | 42 |

|                                                              | 2.7                                                                  | .7 Hardware Accelerators                                       |                                                                                                           | 42 |

|                                                              |                                                                      | 2.7.1                                                          | Field Programmable Gate Arrays                                                                            | 43 |

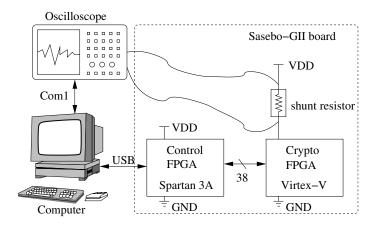

|                                                              |                                                                      | 2.7.2                                                          | SASEBO-GII board                                                                                          | 44 |

|                                                              |                                                                      | 2.7.3                                                          | Efficiency Evaluation of Hardware Designs                                                                 | 45 |

|                                                              | 2.8                                                                  | Conclu                                                         | usions                                                                                                    | 47 |

| 3.                                                           | Arit                                                                 | hmetic                                                         | Architectures over the Field $GF(2^m)$                                                                    | 49 |

|                                                              | 3.1                                                                  | Introd                                                         | luction                                                                                                   | 49 |

|                                                              | 3.2                                                                  | Choice                                                         | e of Finite Fields                                                                                        | 49 |

|                                                              | 3.3                                                                  | Choice                                                         | e of Basis                                                                                                | 50 |

|                                                              | 3.4                                                                  | Addit                                                          | ion over $GF(2^m)$                                                                                        | 51 |

|                                                              | 3.5                                                                  | Multip                                                         | plication over $GF(2^m)$                                                                                  | 52 |

|                                                              |                                                                      | 3.5.1                                                          | Bit parallel multiplier and Bit serial multiplier                                                         | 54 |

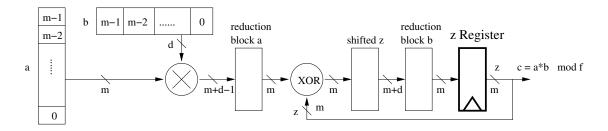

|                                                              |                                                                      | 3.5.2                                                          | Digit serial multiplier                                                                                   | 55 |

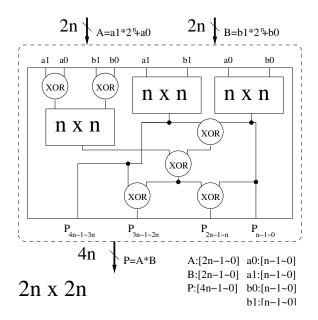

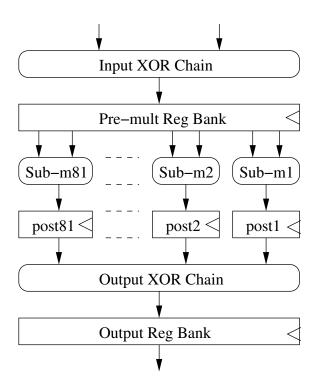

|                                                              |                                                                      | 3.5.3                                                          | Karatsuba Multiplier                                                                                      | 59 |

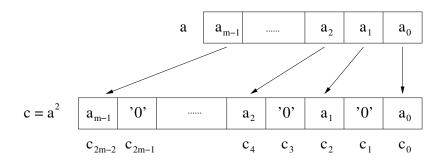

|                                                              | 3.6                                                                  | Squar                                                          | ing over $GF(2^m)$                                                                                        | 64 |

|                                                              | 3.7                                                                  | Invers                                                         | ion/Division over $GF(2^m)$                                                                               | 65 |

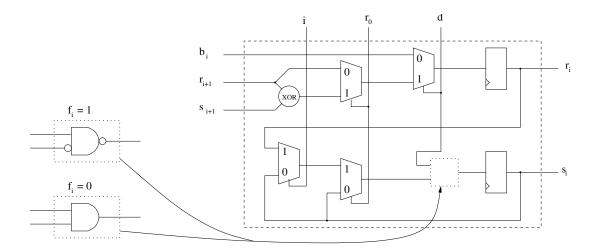

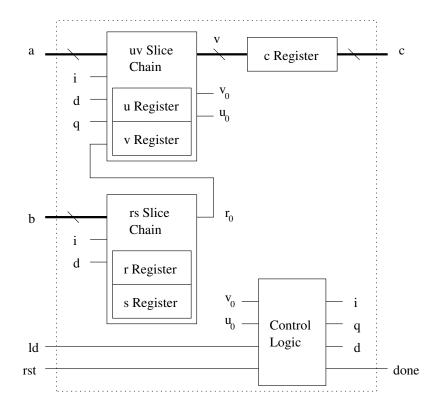

|                                                              | 3.8                                                                  | 8 Dedicated Inversion and Division architecture over $GF(2^m)$ |                                                                                                           | 67 |

|                                                              | 3.9                                                                  | Conclu                                                         | usions                                                                                                    | 71 |

| 4. Implementation of the Tate Pairing over extension field G |                                                                      |                                                                | ation of the Tate Pairing over extension field $GF(2^{4m})$                                               | 73 |

|                                                              | 4.1                                                                  | Introd                                                         | luction                                                                                                   | 73 |

|                                                              | 4.2                                                                  | Archit                                                         | tecture for computations over $GF(2^{4m})$                                                                | 73 |

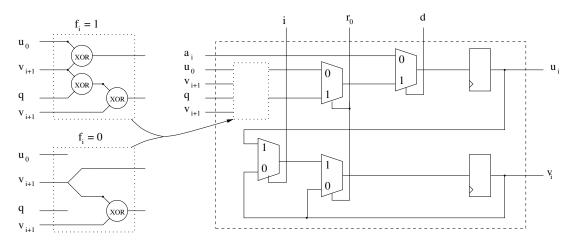

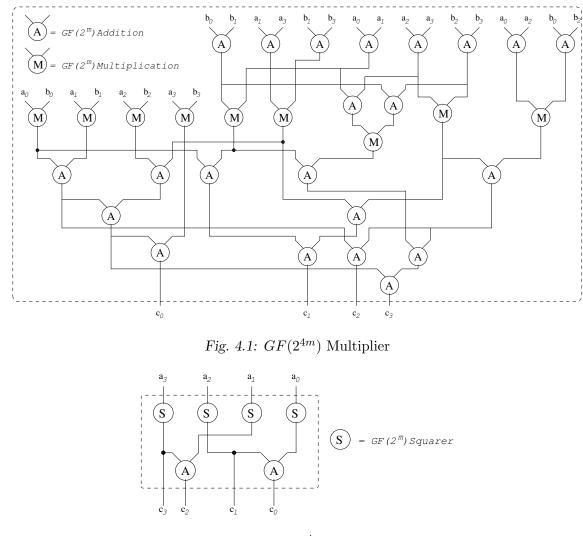

|                                                              |                                                                      | 4.2.1                                                          | $GF(2^{4m})$ Multiplication                                                                               | 75 |

|                                                              |                                                                      | 4.2.2                                                          | $GF(2^{4m})$ Squaring                                                                                     | 76 |

|                                                              |                                                                      | 4.2.3                                                          | $GF(2^{4m})$ Inversion                                                                                    | 78 |

|                                                              |                                                                      | 4.2.4                                                          | $GF(2^{4m})$ Frobenius Map                                                                                | 81 |

|                                                              | 4.3 Implementing the $\eta_T$ algorithm for calculating Tate pairing |                                                                | menting the $\eta_T$ algorithm for calculating Tate pairing                                               | 82 |

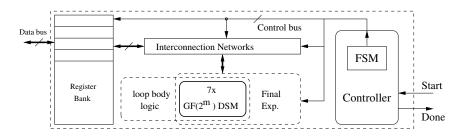

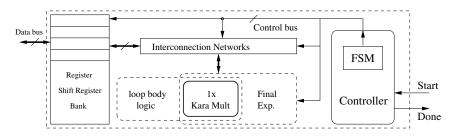

|                                                              |                                                                      | 4.3.1                                                          | Top level architecture design of $\eta_T$ algorithm                                                       | 82 |

|                                                              |                                                                      | 4.3.2                                                          | Reconfiguration of the multiplications in Bus type design $\ . \ .$                                       | 86 |

|                                                              |                                                                      | 4.3.3                                                          | Implementation results of Bus type top-level architecture                                                 | 89 |

|                                                              |                                                                      | 4.3.4                                                          | Implementation results of mixed type top-level architecture                                               | 91 |

|                                                              | 4.4                                                                  | Analy                                                          | sis of implementation result                                                                              | 93 |

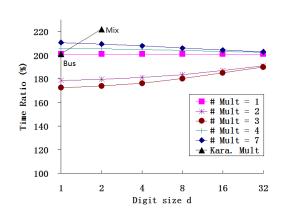

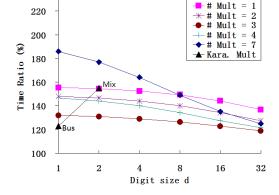

|                                                              |                                                                      | 4.4.1                                                          | Time analysis                                                                                             | 93 |

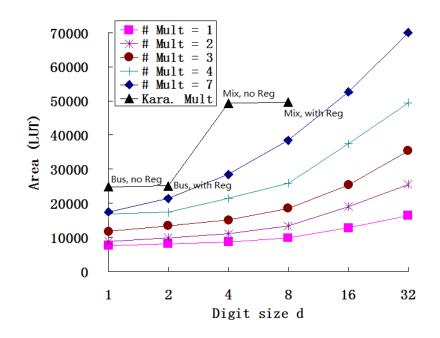

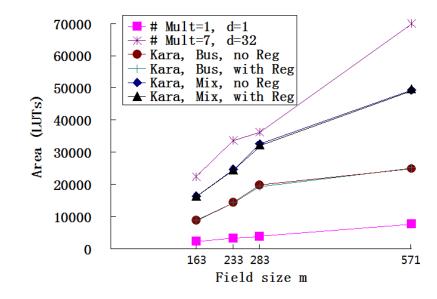

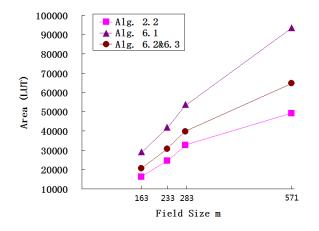

|                                                              |                                                                      | 4.4.2                                                          | Area analysis                                                                                             | 95 |

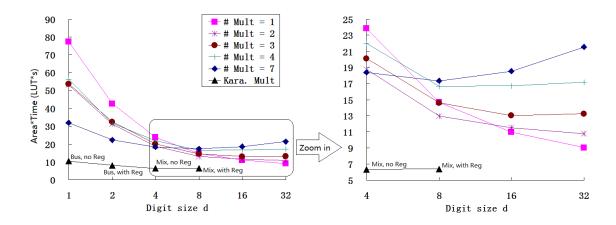

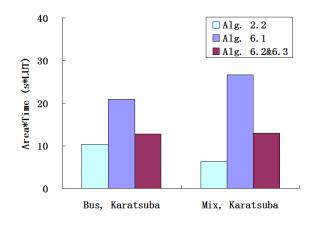

|                                                                                                            |                                     | 4.4.3                            | $A^*T$ product analysis                                                                | 97  |

|------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------|----------------------------------------------------------------------------------------|-----|

|                                                                                                            |                                     | 4.4.4                            | Comparison with earlier work                                                           | 98  |

|                                                                                                            | 4.5                                 | Conclu                           | usions                                                                                 | 100 |

| 5.                                                                                                         | Side                                | Chann                            | el Attacks against Implementations of Tate Pairing algorithms .                        | 102 |

|                                                                                                            | 5.1                                 | Introd                           | uction                                                                                 | 102 |

|                                                                                                            | 5.2                                 | Side C                           | Channel Analysis Attacks                                                               | 102 |

|                                                                                                            |                                     | 5.2.1                            | Correlation Power Analysis Attacks                                                     | 103 |

|                                                                                                            |                                     | 5.2.2                            | Relationship between intermediate variables and power con-                             |     |

|                                                                                                            |                                     |                                  | sumption                                                                               | 104 |

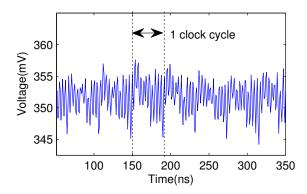

|                                                                                                            |                                     | 5.2.3                            | CPA attack setup                                                                       | 105 |

|                                                                                                            | 5.3                                 | Side-cl                          | hannel security analysis of the $\eta_T$ Pairings                                      | 107 |

|                                                                                                            |                                     | 5.3.1                            | Weakness of $\eta_T$ pairing based IBE scheme $\ldots \ldots \ldots \ldots$            | 107 |

|                                                                                                            |                                     | 5.3.2                            | Weakness in addition                                                                   | 109 |

|                                                                                                            |                                     | 5.3.3                            | Weakness in multiplication                                                             | 110 |

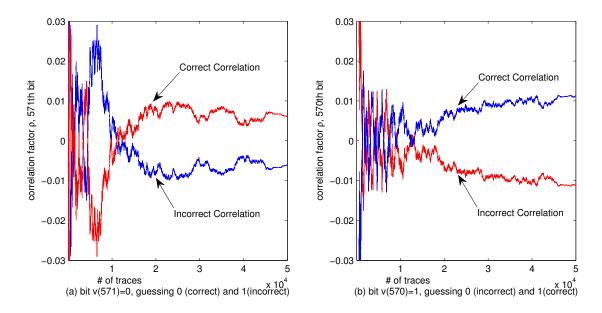

|                                                                                                            | 5.4                                 | CPA a                            | attack against the $GF(2^m)$ operations                                                | 111 |

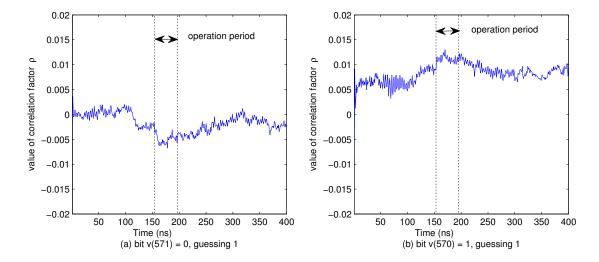

|                                                                                                            |                                     | 5.4.1                            | CPA against addition: Condition 1) $P(\alpha, \beta)$ public, attacking                |     |

|                                                                                                            |                                     |                                  | Q(x,y)                                                                                 | 111 |

|                                                                                                            |                                     | 5.4.2                            | CPA against addition: Condition 2) $Q(x, y)$ public, attacking                         |     |

|                                                                                                            |                                     |                                  | $P(\alpha,\beta)$                                                                      | 115 |

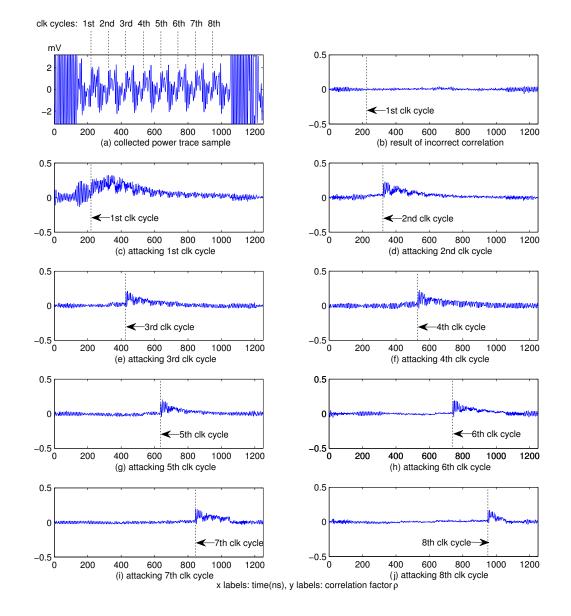

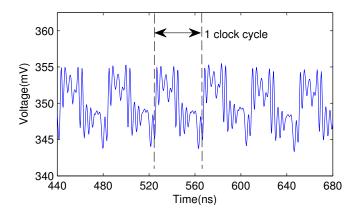

|                                                                                                            |                                     | 5.4.3                            | CPA against digit-serial multiplier (DSM): Condition 1) $P(\alpha, \beta)$             |     |

|                                                                                                            |                                     |                                  | public, attacking $Q(x, y)$                                                            | 115 |

|                                                                                                            |                                     | 5.4.4                            | CPA against digit-serial multiplier (DSM): Condition 2) $Q(x, y)$                      |     |

|                                                                                                            |                                     |                                  | public, attacking $P(\alpha, \beta)$                                                   | 122 |

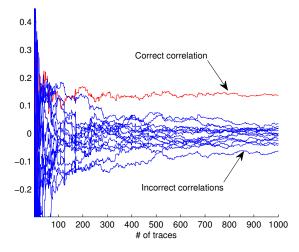

|                                                                                                            |                                     | 5.4.5                            | CPA against Karatsuba multiplier                                                       | 125 |

|                                                                                                            |                                     | 5.4.6                            | CPA against register inserted Karatsuba multiplier: Condition                          |     |

|                                                                                                            |                                     |                                  | 1) $P(\alpha, \beta)$ public, attacking $Q(x, y)$                                      | 125 |

|                                                                                                            |                                     | 5.4.7                            | CPA against register inserted Karatsuba multiplier: Condition                          |     |

|                                                                                                            |                                     |                                  | 2) $Q(x,y)$ public, attacking $P(\alpha,\beta)$                                        | 128 |

|                                                                                                            | 5.5                                 | Conclu                           | usions                                                                                 |     |

| 6.                                                                                                         | Countermeasures against CPA attacks |                                  |                                                                                        | 130 |

| 6.1 Introduction $\ldots$ |                                     | uction                           | 130                                                                                    |     |

|                                                                                                            | 6.2                                 | Weakness in the $\eta_T$ pairing |                                                                                        | 130 |

|                                                                                                            | 6.3                                 | Count                            | ermeasures to protect the $\eta_T$ pairing $\ldots \ldots \ldots \ldots \ldots \ldots$ | 131 |

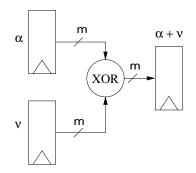

|                                                                                                            |                                     | 6.3.1                            | Exploiting bilinearity to protect the $GF(2^m)$ Adder                                  | 132 |

|                                                                                                            |                                     | 6.3.2                            | Randomized Miller variable to protect the $GF(2^m)$ Adder                              | 134 |

|    |                                                            | 6.3.3               | Using projective coordinates to protect the $GF(2^m)$ Adder                                             | 135 |  |

|----|------------------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------|-----|--|

|    |                                                            | 6.3.4               | Cost comparison between countermeasures                                                                 |     |  |

|    | 6.4                                                        | Security discussion |                                                                                                         |     |  |

|    |                                                            | 6.4.1               | Security of exploiting bilinearity method                                                               |     |  |

|    |                                                            | 6.4.2               | Security of randomized Miller variable method                                                           | 139 |  |

|    |                                                            | 6.4.3               | Security of using projective coordinates method                                                         | 140 |  |

|    |                                                            | 6.4.4               | Security operations in common                                                                           | 140 |  |

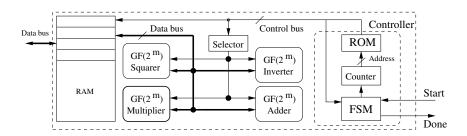

|    | 6.5                                                        | Bus ty              | pe top-level architecture implementation result of the counter-                                         |     |  |

|    |                                                            | measu               | res                                                                                                     | 141 |  |

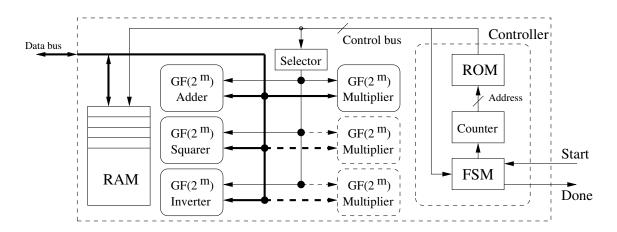

|    | 6.6                                                        | Mixed               | Type Implementation results of the countermeasures                                                      | 144 |  |

|    | 6.7                                                        | Analys              | is of implementation result of the proposed countermeasures .                                           | 145 |  |

|    |                                                            | 6.7.1               | Time analysis $\ldots$ | 146 |  |

|    |                                                            | 6.7.2               | Time ratio analysis $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$    | 147 |  |

|    |                                                            | 6.7.3               | A*T product analysis                                                                                    | 149 |  |

|    | 6.8                                                        | Conclu              | sions                                                                                                   | 150 |  |

| 7  | a                                                          | 1 .                 |                                                                                                         | 150 |  |

| 7. |                                                            |                     | ·                                                                                                       |     |  |

|    | 7.1                                                        |                     | butions to the Field                                                                                    |     |  |

|    | 7.2                                                        |                     | work                                                                                                    |     |  |

|    | 7.3                                                        | Public              | ations                                                                                                  | 150 |  |

|    |                                                            |                     |                                                                                                         |     |  |

| Ap | opend                                                      | ix                  |                                                                                                         | 157 |  |

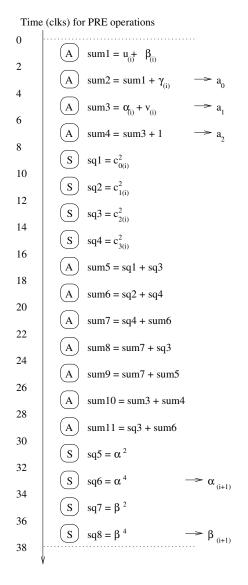

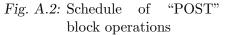

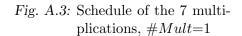

| Α. | Sche                                                       | dule of             | "for" loop operations                                                                                   | 159 |  |

| В. | Impi                                                       | lementa             | tion Results of Tate pairing                                                                            | 162 |  |

|    |                                                            |                     |                                                                                                         |     |  |

| С. | C. Features of Virtex Families                             |                     |                                                                                                         |     |  |

| D. | D. Countermeasures Algorithms Using Projective Coordinates |                     |                                                                                                         |     |  |

| E. | E. Calculation Time of Countermeasures Against CPA Attack  |                     |                                                                                                         |     |  |

| Re | feren                                                      | ces                 |                                                                                                         | 173 |  |

|    |                                                            |                     |                                                                                                         |     |  |

## 1. INTRODUCTION

### 1.1 Motivation

Throughout the development of human civilization, people all over the world have developed their own methods to protect their information in communications. In modern society, cryptosystems use secret keys to transform plaintext into ciphertext [1]. Both the encryptor and the decryptor need these secret key system to communicate. However, once the key is exposed, this system can be solved easily. The study of trying to break an encryption system without previously knowing the secret key is called cryptanalysis. The idea of cryptanalysis has existed since cryptography was first developed. Throughout history, cryptanalysis and cryptography have spurred on the development of the other. It always happens that in a war or a commercial war, breaking encrypted information of an opponent can lead to decisive events or even victory. Advanced cryptanalysis technology forces people to develop newer and stronger methods for securely encrypting and transmitting information.

Cryptography was initially used to protect secret information by governments and the military. With the development of the modern society, the demand for information security comes from many fields, such as commerces, client information protection, or personal e-mails. Since secure cryptographic systems are required in many applications, this thesis analyses and implements a highly effecient and secure public-key cryptographic scheme.

In the 1970s, cryptography became a widespread tool for securing communications. The security of modern public key cryptography relies on some mathematical problems. These problems include integer factorization [2] and the discrete logarithm problem (DLP) [3]. Among modern cryptosystems, Identity Based Encryption (IBE) [4, 5] and Attribute Based Encryption (ABE) [6] based on pairings [4] are popular public key schemes.

Pairing based IBE and ABE systems can be implemented on hardware accelerators on FPGAs. Different implementations of the cryptosystem can meet the demand for information security in many devices ranging from large servers, to mobile devices, to smart cards. Flexible platforms provide a variety of solutions for different constraints for certain demands. For example, a large server will use more hardware in exchange for a faster operation speed, while a smart card can use less hardware and a restricted operation speed. In most previous pairing based algorithm implementations, timing efficiency were considered as the first priority [7, 8, 9, 10, 11]. However, such designs do not satisfy the various demands of different applications. Thus, this work not only focuses on the the calculation speed, but also considers the hardware efficiency of the designs. In this work, different schedules of arranging the calculation modules are used, similar to those investigated in [12]. In addition, examing the calculation loop in the pairing based algorithm allows the differences between operations that happen only once and those that iterate many times to be considered for the first time. Thus in this work, different top-level architectures are implemented and their effeciency is investigated.

However, people who take such cryptosystem as a method to protect their information would always ask: "Are these schemes secure?" Thus in this work the security aspect of the chosen cryptographic algorithm implementation will be examined and perfected.

"The greatest enemy is the greatest teacher." The improvement and perfection of a cryptogarphic algorithm will not happen without the input of cryptanalysis. To examine the security aspect from point of view of an attacker helps a designer overcome the defects existing in the original cryptosystem. Side channel information leaked from the operating hardware is often related to the secret information [13, 14, 15]. A cryptosystem designer should consider all the assumptions under which the attackers may find weaknesses in the proposed cryptosystem.

If there is any weakness identified in the cryptosystem, a designer should try to overcome such defects by applying countermeasures accordingly. Countermeasures must be carefully applied so that the including hard mathematical problem still exists while the weakness is perfectly masked. Although introducing countermeasures to the original algorithm can lead to the lowering of the efficiency of the design by increasing the operation time and hardware used, it still is necessary.

## 1.2 Aim of thesis

The primary aim of this work is to investigate and improve the secure implementation of a public key cryptographic processor. Elliptic curve cryptography (ECC) [3, 19] was introduced by Miller and Koblitz in 1985 [20, 21]. It is based on a mathematical entity known as an elliptic curve [22] and provides a good security level making use of only small hardware resources [23]. Pairing based cryptography (PBC) is used in new forms of public key cryptography known as IBE and ABE. Among PBCs, the Tate Pairings is proved to be the most efficient one [24, 25]. In this work, the performance and security aspects of the Tate pairing, more specifically the  $\eta_T$  algorithm [26] for calculating the Tate pairing, will be investigated.

There are two main options for implementing the Tate pairing: software on a general purpose processor and dedicated hardware. The general purpose processors are in general electronic devices whose functions are based on the software programmes implemented, such as computers, PDAs and cell phones. However, as these processors are not optimized for implementing cryptography, a software implementation on a general purpose processor may lead to low performance [27, 28, 29, 30], and moreover, security aspects of the secret information in the general purpose processors is not guaranteed. A dedicated hardware processor for the cryptosystems can provide much better performance, not only accelerating the operation time, but also promising better security and can be tamper proof to prevent attackers compromising the cryptosystem. Thus, dedicated hardware accelerators are widely used in implementing practical cryptosystems. In this work, the algorithms are implemented on Field Programmable Gate Arrays.

There are several parameters to show the efficiency of a hardware processor. Since dedicated hardware processors are initially developed to accelerate the operation speed of the cryptography, operation time is considered as an important parameter. Area efficiency is another factor that has been considered. This is because in hardware implementations, taking more silicon resource leads to more cost. Thus, in this thesis, both time and area are taken as performance parameters.

By scheduling the architecture and the operations of the cryptographic algorithms, the flexibility of the algorithms is also considered in this thesis. In the architecture for the Tate pairing, there are arithmetic units over  $GF(2^{4m})$  such as additions, squarings, multiplications and divisions. These units can be implemented as operations over  $GF(2^m)$ . In practical implementation of the Tate pairing algorithm, the architectures can be reconfigured for different design constraints, such as the number of multipliers used in the design and the size of multipliers. This results in trade-offs between calculation time and area. In this thesis, the architectures for the Tate pairing algorithm are described using VHDL, and then synthesized for a particular FPGA technology. A software program is used to automatically generate the VHDL implementation of the architectures for different constraints. This software along with the use of FPGAs, allows the implementation of different designs to be quickly analyzed.

Apart from cost and efficiency, security is another important aspect of a cryptosystem. A new class of attack on cryptography known as side channel analysis (SCA) attacks [14], which monitors the side channel information (electromagnetic radiation, timing, power [13, 14, 15]) of a cryptosystem, has been developed to reveal the knowledge of the secret key. In this thesis, the security of the Tate pairing is considered. Several different attacks are applied on the Tate pairing designs to test their resistance against SCA attacks. For different kinds of protocols, the security is discussed. Against SCA attacks, several countermeasures are studied, including utilizing the bilinear property of the Tate pairing [16, 17], randomizing Miller variables in the algorithm [17], and using projective coordinates to mask the operations [18]. The proposed countermeasures are implemented in this work and the operation time and area costs of their implementations are evaluated, along with the consideration of the security aspects of the countermeasures.

## 1.3 Thesis outline

In this thesis,  $\eta_T$  algorithm, a fast approach to calculate the Tate pairing is studied. Considering the constraints of time and area, the scheduling methods of implementing the  $\eta_T$  pairing algorithm will be discussed. For security aspect of the  $\eta_T$  pairing algorithm, the important applications, the pairing based IBE system [5, 4] and ABE system [6] will be considered in this work. In the IBE or ABE cryptosystem, how the  $\eta_T$  pairing algorithm can be attacked under certain conditions is discussed. With all these possible attacks available to an opponent, countermeasures must be considered by the cryptosystem designer. Three countermeasures are studied and applied to protect the  $\eta_T$  pairing algorithm.

Chapter 2 introduces the theoretical material behind private and public key cryptography. In particular, the pairing based cryptosystems and the elliptic curve on which pairings are based and their underlying fields arithmetic are covered. The details of some applications of the pairing based cryptography, for example the IBE and ABE schemes are introduced. Cryptanalysis is the ever present force finding weaknesses and spurring the development of cryptography. To improve and perfect the cryptosystem, this thesis applies correlation power analysis (CPA) attacks on the hardware implemented pairing based cryptosystems. Introduction of the mathematical theory of CPA and the FPGA platform on which the proposed cryptosystem is implemented is also given in this chapter.

In Chapter 3, the size of the Galois Field where the Elliptic curve lies on is determined. All calculations in the pairing based algorithms are operated over the chosen Elliptic curve. The basic operation blocks of Addition and Squaring are introduced. Two popular methods of implementing field Multiplication, the digit-serial multiplication and the Karatsuba Multiplier are discussed. For the implementation of field Division/Inversion, an Itoh-Tsujii algorithm which makes use of the squaring and the multiplication to implement an inversion operation over  $GF(2^m)$ , and a dedicated algorithm for Division over  $GF(2^m)$ , the Extended Euclidean Algorithm (EEA) are introduced. These operations form the basic calculation units of a pairing based algorithm.

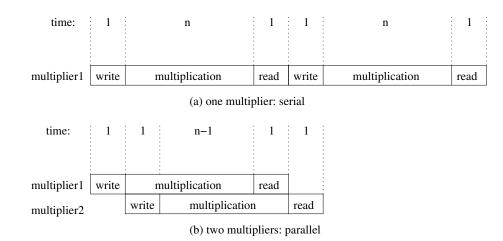

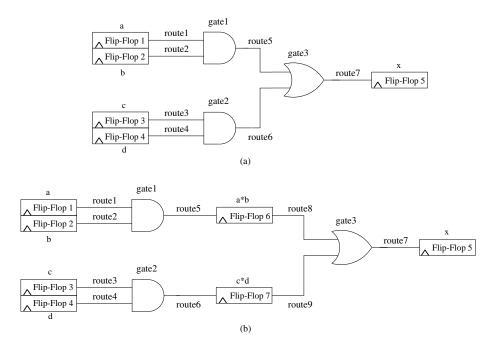

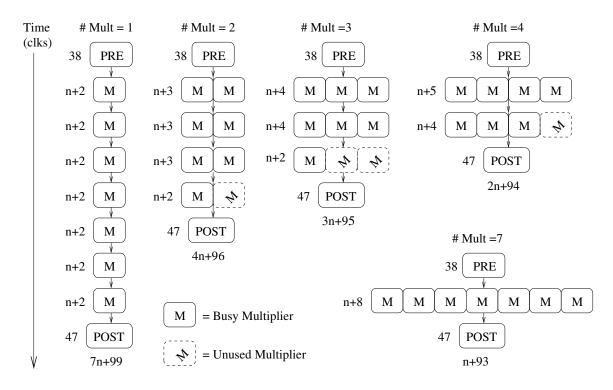

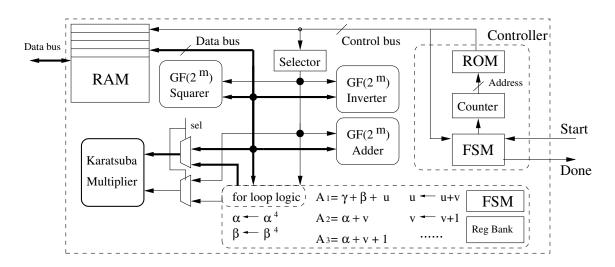

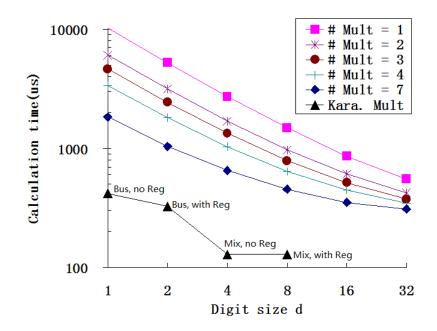

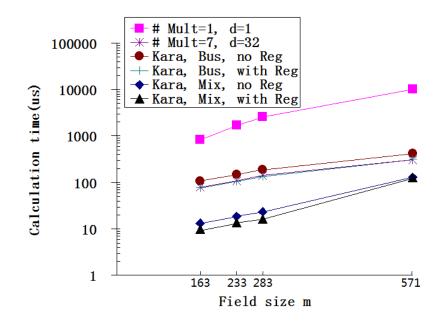

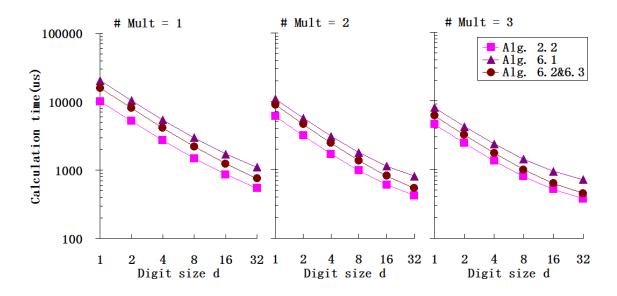

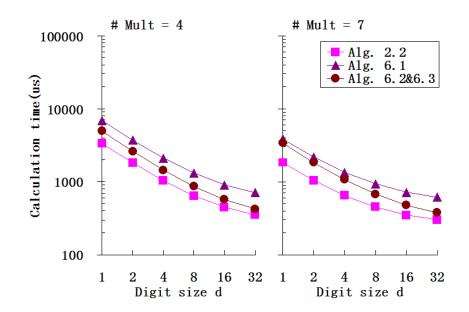

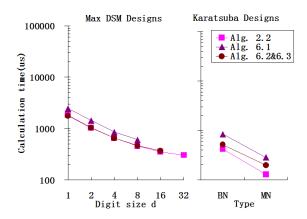

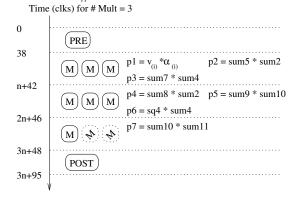

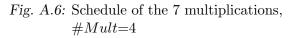

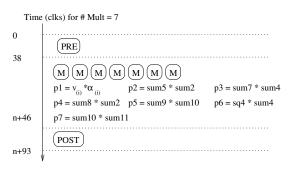

Chapter 4 introduces the structure and design flow of the  $\eta_T$  pairing over select Elliptic curve. As the operation field of the  $\eta_T$  pairing is raised to an extended field  $GF(2^{4m})$ , the operations for addition, squaring, multiplication and division are introduced. The top level architectures of the implementation of the  $\eta_T$  pairing are presented. Since there are 7 multiplications in the main loop in the  $\eta_T$  pairing calculation, when using the digit-serial multiplier, these multiplications dominate the calculation time. Different schedules for arranging these 7 multiplications are applied. The implementation results of  $\eta_T$  pairing using both the digit-serial multiplier and the Karatsuba multiplier are shown in this chapter.

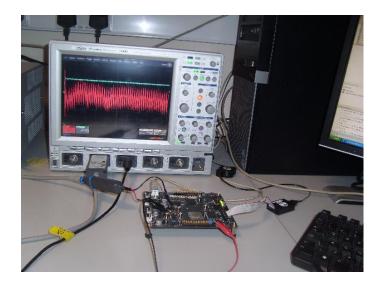

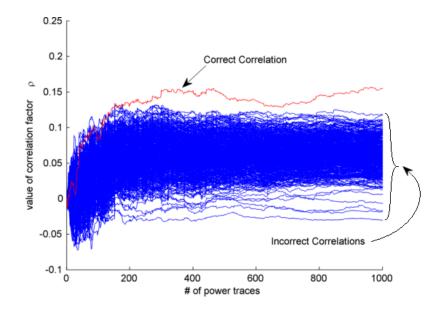

In Chapter 5 the detailed calculation steps of CPA attacks are introduced. To examine the security aspect of the  $\eta_T$  pairing algorithm in a more practical and more general way, the important applications, the pairing based IBE scheme and ABE scheme, are chosen as the targets of the CPA attack. The weaknesses of the  $\eta_T$ pairing algorithm in the IBE system are discussed in this chapter. The CPA attacks are applied against every weakness of the algorithm, including the adder and the two multipliers. With the power traces of these operations collected using an oscilloscope, this chapter presents how an attacker tries to attack such components making use of the side channel information leaked during the operations. The target components of each proposed attack, the operation steps, and the mathematical calculation results of the attacks applied are described.

Chapter 6 introduces the precautions that must be used to implement a pairing based IBE system according to the weaknesses exposed by the attacks proposed in chapter 5. These precautions can be applied through carefully arranging the intermediate variables and the operation blocks by the hardware designers. However, applying such precautions does not provide perfect security to the Tate pairing algorithm. Some defects of the pairing based IBE and ABE cryptosystems must be fixed through additional operations. For this reason, several countermeasures to protect the pairing algorithm from CPA attacks are introduced and applied to the original  $\eta_T$  pairing. The implementation results of such countermeasures using the same top-level architectures are shown.

## 2. BACKGROUND THEORY

## 2.1 Introduction

This chapter presents the mathematical background and some of the theories related to the topics covered in this thesis. Section 2.2 briefly introduces cryptography. Section 2.3 explains the difference between private and public key cryptography. Some popular public key schemes, the IBE scheme and the ABE scheme, are introduced in this section.

In section 2.4, the basic mathematical concepts of groups, finite fields, elliptic curves and point operations over elliptic curves are introduced. In section 2.5, the basic theory of Tate pairing and an example of pairing based IBE and ABE schemes, are presented. Discrete logarithm problems (DLPs), serving as the main security challenge in each case, are discussed.

Section 2.6 introduces some popular cryptanalysis measures of attacking public key cryptography. Mathematical analysis methods and their complexity are considered in this section. As a popular method to attack hardware implemented cryptosystems, side channel analysis attacks are introduced. The security of pairing based IBE and ABE schemes, as examples of pairing based public key schemes, is discussed in this section.

Section 2.7 introduces some dedicated hardware accelerators used to implement the pairing based cryptographic algorithms and the reason why they are used. Two different types of FPGA platforms used in the thesis are introduced in this section. The method of evaluating the power consumption of a hardware accelerator is also explained.

## 2.2 Cryptography

Cryptography protects information and information systems from unauthorized access or from being modified [1]. Thousands of years ago people realized that it was necessary to protect the confidentiality of important information. Secrets should

always be kept secure from being accessed and tampered with by unintended recipients. Julius Caesar, the Roman Emperor [34] was credited with the invention of the Caesar cipher in approximately 50 B.C., which was created for the protection of the secret and important messages being transmitted between Caesar and his military. This Caeser Cipher encrypts a message by substituting letters in the message with letters a fixed number of positions down the alphabet. The number of places the letters were shifted along the alphabet is called the secret key. Over the years, novel ciphers were invented and used in cryptography to make cryptosystems more and more secure. World War II resulted in significant improvements in information security and marked the beginning of the professional field of modern cryptography.

As modern electronics develops, the development of the internet and personal computers calls for cryptographic protocols that are suitable for daily communications. In many applications, keeping the information transferred between public communication platforms secret can be critical to politics, business and personal interests. Digital cryptography has developed in order to meet these security needs [35].

Cryptography, as a system of protecting information, is of course not just about keeping private information from being read by an unintended recipient. As a safeguard of the modern communication via electronic media, modern cryptography encompasses Confidentiality, Integrity and Availability. Other principles, such as Authenticity and Non-Repudiation, are also considered to be very important [36].

- Confidentiality: A message should not be disclosed to unauthorized individuals or systems.

- Integrity: It is always possible to check the message has not been altered while in transit.

- Availability: A cryptosystem must remain available at all times.

- Authenticity: The identities of the sender and recipient, and the data being transmitted, are genuine.

- Non-Repudiation: The sender cannot deny having sent a particular message. The recipient cannot deny having received a particular message.

## 2.3 Private and Public Key Cryptography

To provide the properties mentioned above in section 2.2, different protocols have been developed. There are two different types of cryptography nowadays: private key cryptography and public key cryptography.

Private key cryptography, also called symmetric key cryptography, uses a single secret key k which is shared by both the sender and the receiver. This key is used both to encrypt and decrypt the information. Both sender and receiver need the key and the key must be kept secret from anyone else. The security of the transmission depends on how well the key is protected.

Public key cryptography uses two different keys to encrypt and decrypt: a public and a private key, respectively. Each user has its own key set and while the private key must be kept secret the public key is publicly available to everyone. Both keys are mathematically related.

#### 2.3.1 Private Key Cryptography

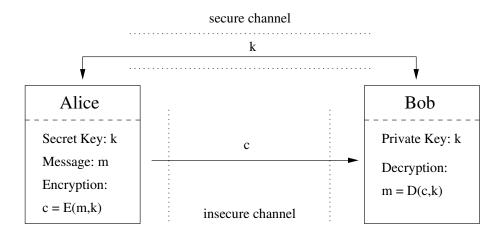

A communication between Alice and Bob using the private key cryptosystem is illustrated in Fig. 2.1. In the transmission, Alice first encrypts the plaintext musing the encryption function E and the secret key k. The encrypted text is called the ciphertext c. Then Alice sends c to Bob through the insecure channel. The cipher text c is of no use to anyone except Bob because Bob holds the same shared secret key k and can recover the message from ciphertext c to plaintext m using a decryption function D. For security reasons, the primary requirement of this cryptosystem is that it must be constructed so as to prevent an eavesdropper from simply trying every possible key (known as brute force attack [37]).

Private key cryptosystems are considered very fast and, thus, are suitable for the transmissions of a large throughput of data. However, there are two problems to consider: the key distribution problem and the key management problem. The key distribution problem is how Alice and Bob agree the value of their shared secret key. A third party key generator over some secure channel is necessary to distribute the key. The key management problem is that for each pair of users in the communication network, there must be a unique key. Therefore, for a network of n users, at least  $\frac{n(n-1)}{2}$  unique keys are required [38]. For a large network, the number of unique keys becomes difficult to manage.

Fig. 2.1: Private key scheme communication

Fig. 2.2: Public key scheme communication

#### 2.3.2 Public Key Cryptography

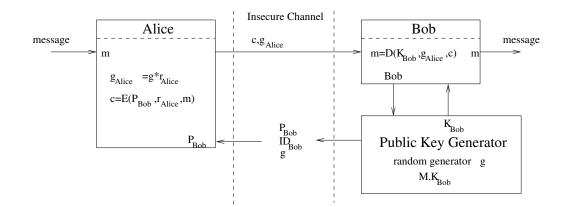

Consider the communication between Alice and Bob again, as shown in Fig. 2.2. In a Public key cryptosystem, Alice has a public and private key pair:  $(P_{Alice}, K_{Alice})$ , respectively. Similarly, Bob has  $(P_{Bob}, K_{Bob})$ . If Alice wants to send Bob a message m, she firstly encrypts the message with Bob's public key,  $P_{Bob}$ . The encrypted message is then sent to Bob and can only be decrypted using Bob's private key,  $K_{Bob}$ . Similarly, anyone who knows Alice's public key can send her a message by encrypting it with her public key  $P_{Alice}$ . Alice will then decrypt the message with her private key  $K_{Alice}$ .

In this scheme, the key distribution problem is solved because the public key is available to everyone. Alice and Bob do not need to agree a shared secret key. Similarly, anyone who wants to communicate with Bob can encrypt their message with the same public key  $P_{Bob}$ . Thus, key management is no longer a problem. The British government claimed that James H. Ellis, Clifford Cocks and Malcolm Williamson, members of the British Government Communicationis Headquarters (GCHQ), first developed the public key algorithms in 1973. The reader may refer to [39] for the story. However, the most famous public key scheme is RSA which was developed in 1977 by Rivest, Shamir and Adleman in the US [40].

The disadvantage of public key cryptography is that it is much more computationally complex than private key cryptography. Although public key cryptography eliminates the key distribution and key management problems, it brings some problems of its own. The main problem is the confirmation of the authenticity of the public key. In the communication model, Alice has to consider whether the public key of Bob, received from an insecure channel, is the real one or a value sent by an attacker.

In a public key cryptosystem, since Alice cannot confirm whether the public key is authentic or not, a Public Key Infrastructure (PKI) can be introduced [41]. The PKI includes a trusted third party that provides the service of a Certificate Authority (CA) [42]. CA certifies Bob's public key as belonging to him. Before Alice sends Bob a message, she has to validate the public key of Bob by contacting the CA. This adds an additional step in the communication between Alice and Bob. It is very important that the CA is trustworthy, otherwise Alice may receive false keys disguised by some attackers and any message Alice encrypted using the false keys may be easily decrypted by the attacker.

#### 2.3.3 Identity Based Encryption

In 1984 Shamir [5] proposed a public key scheme in which the public key can be an arbitrary string. This scheme is called IBE. The first practical IBE implementation was applied by Boneh and Franklin in 2001 [4]. IBE was originally developed to simplify the certification process. It eliminates the need for the CA. Thus, a PKI is no longer necessary in the scheme. Instead, a trusted third party Public Key Generator (PKG) is introduced which is used to distribute the private key of a receiver.

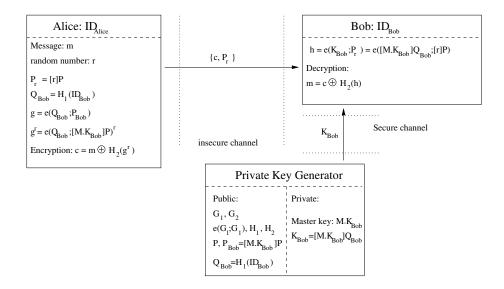

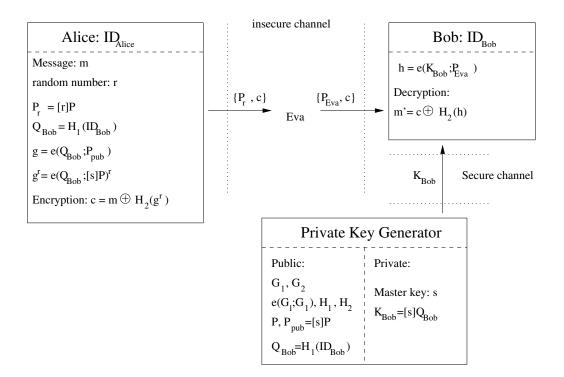

The structure of an IBE scheme is shown in Fig. 2.3. In the figure,  $P_{Bob}$  and  $K_{Bob}$  represent the keys to encrypt and to decrypt respectively. An encrypted message 'm' can be readily decrypted by the intended receptient Bob only.

In an IBE system, each user is identified by a unique identity string, for example a user name or an e-mail address. The identity of Bob in Fig. 2.3 is  $ID_{Bob}$ . The IBE system can be described in 4 steps: setup, key generation, encryption and decryption.

**Setup** A trusted third party, the PKG, publishes the algorithm E for encryption and D for decryption, a random generator g and some related rules such as how the user's public key can be generated. All elements used in this cryptosystem are a

Fig. 2.3: Identity-Based Encryption scheme structure

multiple of the generator g.

**Key generation** The PKG randomly picks a master key  $M.K_{Bob}$  for Bob. With this master key, the PKG generates a pair of keys, a public key  $P_{Bob}$  and a private key  $K_{Bob}$ , for user Bob and publishes the public key  $P_{Bob}$  of  $ID_{Bob}$  to the insecure channel.

**Encryption** Sender Alice in this IBE scheme can get the public key  $P_{Bob}$  according to the information published by the PKG (without certificates). Alice then picks a random number  $r_{Alice}$  and generates an identity number  $g_{Alice}$  using generator g:  $g_{Alice} = g * r_{Alice}$ . This  $g_{Alice}$  helps Bob recognize the sender of the received message. The rules published by the PKG must ensure that the decryptor can remove  $r_{Alice}$  using  $g_{Alice}$ . With the elements above, Alice can encrypt a message 'm' by calculation  $c = E(m, P_{Bob}, r_{Alice})$ . Alice sends Bob the message pair  $\{c, g_{Alice}\}$ .

**Decryption** The PKG is responsible for delivering the private key  $K_{Bob}$  to the authorised recipient Bob according to his ID. When Bob wants to decrypt the message, he has to contact the PKG and ask for his corresponding private key. On confirmation of  $ID_{Bob}$ , the PKG sends Bob his private key  $K_{Bob}$  through some secure channel. With the received message pair  $\{c, g_{Alice}\}$  and the private key  $K_{Bob}$ , Bob is able to decrypt the message by calculation:  $m = D(c, K_{Bob}, g_{Alice})$ .

In this scheme, it is no longer necessary that the message sender contact a third party to validate the public key of a receiver. It is easier to send a message as the onus is on the receiver to contact the PKG and verify his identity to obtain the private key. This scheme also allows the PKG to control the validity of a customer's identity. If the PKG finds that the identity of Bob is no longer valid, it can change the master key and thus, the private key that Bob received before no longer works.

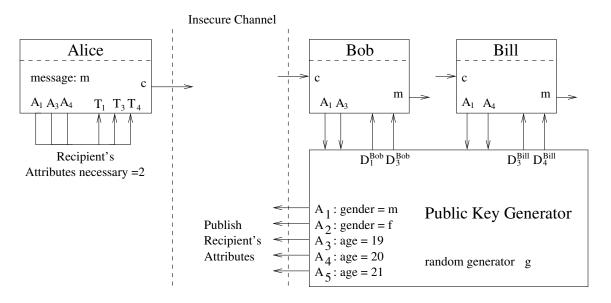

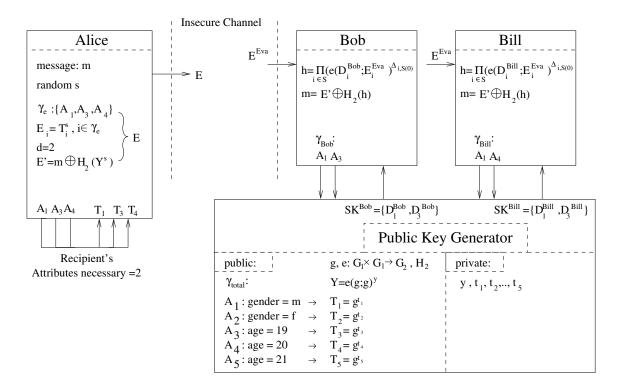

Fig. 2.4: Attribute-Based Encryption scheme structure

#### 2.3.4 Attribute Based Encryption

ABE [6] is a new kind of public key encryption which is based on IBE [5]. In contrast to the IBE schemes, ABE is a scheme in which each user is identified by a set of attributes, for example age, gender, college, etc. Some function of those attributes is used to determine decryption ability for each ciphertext.

Sahai and Waters introduced a single authority attribute encryption scheme in [6] and named this scheme a 'Fuzzy identity-based encryption'. In this scheme, a trusted third party is needed to monitor all the attributes of the users. This authority is in charge of delivering the secret keys corresponding to each of the attributes to the intended recepients.

There are two kinds of ABE systems, Key-Policy ABE (KP-ABE) and Ciphertext-Policy ABE (CP-ABE). In KP-ABE [6, 43], every ciphertext is associated with a set of attributes and the secret key of every user is associated with a threshold access structure based on attributes. Decryption is enabled if and only if the ciphertext attribute set satisfies the access structure of the user secret key. In CP-ABE, [44, 45, 46, 47, 48], the situation is reversed: each ciphertext is associated with an access structure.

#### 2.3.5 ABE structure

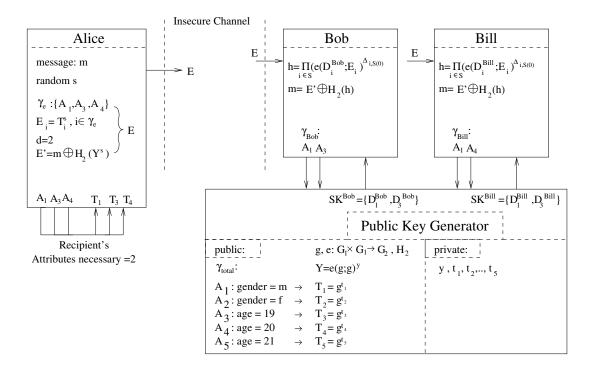

The structure of a basic ABE scheme is shown in Fig. 2.4. In the figure,  $A_i$  represents different attribute parameters. In this scheme, a sender can designate the recepient to

be a set of elements holding the same specific attributes. For example, a boys' soccer team recruiting e-mail may be sent to all boys between 19 - 20 years old. In an ABE system, all members with attributes age = 19 or 20 and attribute gender = male will be qualified to decrypt such an e-mail. In this case, Bob and Bill, respectively 19 and 20 years of age, are able to read such an e-mail whilst the girl Eva does not get access to such information.

Similar to IBE systems, an ABE system can be described using the following steps: setup, encryption, key generation and decryption [43]. Suppose there are 5 attributes in the ABE system shown in Fig. 2.4, i.e.  $A_i$ , where  $i \in \mathbb{Z}_5$ . Taking Bob as an example, the operations in the ABE scheme are described as follows:

Setup This is a randomized algorithm that takes no input other than the implicit security parameter. In the ABE scheme shown in Fig. 2.4, the Key Generator publishes the attribute set  $\gamma_{total} = \{A_i\}$  and a public key set  $PK = \{T_i\}$ . It keeps the master key MK which was used to generate the public key and will be used to generate the secret key SK.

**Encryption** This is a randomized algorithm that takes as input a message m, a set of attributes  $\gamma_e$  with  $n_e$  attributes and the public parameters PK. It outputs the ciphertext c and a number d. In Fig. 2.4, Sender Alice picks 3 attributes  $\gamma_e = \{A_1, A_3, A_4\}$  out of the 5 attributes and uses the corresponding public key  $\{T_1, T_3, T_4\}$  to encrypt the message m, into ciphertext c and defines a number d = 2 which means that any decryptor should hold at least 2 of the attributes in  $\gamma_e$  to decrypt the message.

Key Generation This is a randomized algorithm that takes as input an access structure  $\gamma_1$ , the master key MK and the public parameters PK. It outputs a decryption key SK={ $D_i$ }. In Fig. 2.4, this step shows the communications between Bob and the Key Generation algorithm. On trying to get the access to the message, Bob has to contact the Key Generator with the attributes,  $\gamma_{Bob}={A_1, A_3}$ , he holds and ask for the corresponding secret key. The Key Generator generates a secret key set  $SK^{Bob} = {D_1^{Bob}, D_3^{Bob}}$  according to the master key and the attribute set input by Bob and sends  $SK^{Bob}$  back to the decryptor. In  $SK^{Bob} = {D_1^{Bob}, D_3^{Bob}}$ the superscript 'Bob' implies that the secret key set is randomly generated for Bob. **Decryption** This algorithm takes as input the ciphertext *c* that was encrypted under the set  $\gamma_e$  of attributes, the decryption key SK={ $D_i$ } for access control structure  $\gamma_{Bob}$ and the public parameters PK. It outputs the correct message *m* if  $|\gamma_e \cap \gamma_{Bob}| \ge d$ , where '||' represents the number of elements. In Fig. 2.4, on receiving the secret key set  $SK^{Bob} = {D_1^{Bob}, D_3^{Bob}}$ , Bob is able to compute the plain text of the message. No matter how many attributes Bob holds, provided at least 2 of the attributes in  $\gamma_{Bob}$  match with those in  $\gamma_e$ , the message will be correctly decrypted. Otherwise, Bob will not have the access to the plain text.

For Bill, the same steps are performed and Bill will get a secret key set  $SK^{Bill} = \{D_1^{Bill}, D_4^{Bill}\}$  for decryption. Thus, this system enables an encryptor to send a message to a group of recepients who match the requirements he sets up. Note that the secret key sets,  $SK^{Bob}$  and  $SK^{Bill}$ , are randomly generated for specific decryptors. Although Decryptor1 and Decryptor2 hold 3 attributes in total  $(\{A_1, A_3, A_4\})$ , merging the information from Decryptor1 and Decryptor2 generates the secret key set  $\{D_1^{Bob}, D_3^{Bob}, D_1^{Bill}, D_4^{Bill}\}$  rather than  $\{D_1^{Bob}, D_3^{Bob}, D_4^{Bol}\}$  or  $\{D_1^{Bill}, D_3^{Bill}, D_4^{Bill}\}$ . This means that unqualified decryptors cannot forge secret keys, even by colluding.

## 2.4 Mathematical Background

In this section the necessary mathematical background is introduced. The concepts of groups, fields and elliptic curves are necessary for building the cryptosystem presented in this thesis.

#### 2.4.1 Groups

In mathematics, a group is an algebraic structure which consists of a set of elements and an operation [49]. Such an operation is called the group operation. The group operation operates on any two of its elements to form a third element. For example, the set of integers is a group and addition and multiplications are both group operations of the integer group. A group must satisfy the following properties under the '+' operation:

- Closure: the result of the operation is still in the group, c = a + b, if  $a, b \in G$ , then  $c \in G$ ,

- Associativity: the group operation order does not affect the operation result, (a+b)+c = a + (b+c) for any  $a, b, c \in G$ .

- Identity element: There exists an identity element  $e \in G$ , such that for every element  $a \in G$ , the equation e + a = a + e = a holds.

- Inverse element: For each  $a \in G$ , there exists an element  $b \in G$  such that a + b = b + a = e.

A group G is said to be Abelian or commutative if a + b = b + a,  $a, b \in G$ . A group G is said to be finite if there is a finite number of elements in the group. The order of this group is defined as the number of elements in the group, denoted #G. For example, the integer Z with addition as its group operation, is an infinite group, its order is infinity. A group made up of integers modulo p is a finite group, denoted  $Z_p$ , where p is the order of this group.

A group G is said to be cyclic if there exists an element g such that for any element  $a \in G$ , there exists integer k such that [k]g = a. Here the operation [k]g = a is the k times addition chain of g, as shown in equation 2.1.

$$a = [k]g = \underbrace{g + g + \ldots + g}_{`+' k - 1 \ times}$$

$$(2.1)$$

Here the element g is called the generator of this cyclic group G. The cyclic group generated by g is denoted  $\langle g \rangle$ . The smallest integer n that satisfies [n]g = e is the order of this group.

#### 2.4.2 Finite Fields

Mathematically, a field is a cyclic group of elements in which nonzero elements form a group under multiplication [50]. In a field, notions of addition, subtraction, multiplication and division satisfy certain axioms. A field F must satisfy the following properties:

- Closure: c = a + b, d = a \* b, if  $a, b \in G$ , then  $c, d \in F$ .

- Associativity: (a+b)+c = a+(b+c) and (a\*b)\*c = a\*(b\*c) for all  $a, b, c \in F$ .

- Commutative: a + b = b + a and a \* b = b \* a for all a and  $b \in F$ .

- Distributive: a \* (b + c) = a \* b + a \* c for all  $a, b, c \in G$ .

- Inverse: for all  $a \in F$ , there always exists an element  $a^{-1} \in F$  such that  $a * a^{-1} = 1$ .

The most commonly used fields are the field of real numbers and the field of complex numbers which are infinite.

The Galois Field is a finite field named after  $\dot{E}$  variate Galois. The order of a Galois Field must be equal to the positive integer power of a prime p.  $\dot{E}$  variate Galois showed that for any prime p and positive integer m, there exists a finite field

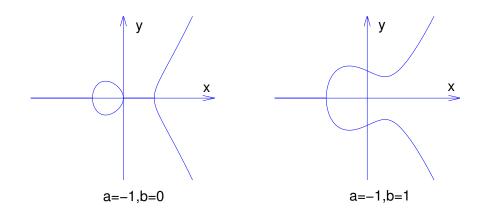

Fig. 2.5: Example of Elliptic Curve  $y^2 = x^3 + ax + b$

with  $q = p^m$  elements [52]. The prime p is known as the characteristic of the field  $GF(p^m) = GF(q)$ . In cryptographic applications the characteristics of p = 2, p = 3 and p some large prime are often used. Fields with characteristic two show better performance in area, runtime, power and energy than prime fields [53]. Page showed that finite fields of characteristic two and three result in similar performance [54]. In this work, fields of characteristic 2 with power  $m \ge 163$  are used, denoted  $GF(2^m)$ .

#### 2.4.3 Elliptic Curves over Finite Fields

An elliptic curve E(GF(q)) over GF(q) can be represented in equation 2.2 [51].

$$E(GF(q)): y^{2} + a_{1}xy + a_{3}y = x^{3} + a_{2}x^{2} + a_{4}x + a_{6}, \qquad (2.2)$$

where  $a_1, a_2, a_3, a_4, a_6 \in GF(q)$ . Any point P over this curve consists of two coordinates x and y, which satisfy equation 2.2 as a pair, i.e.  $P(x, y) \in E(GF(q))$ ,  $x, y \in GF(q)$ . An example of an elliptic curve over the field of real numbers is shown in Fig. 2.5. The two curves in Fig. 2.5 are described by equation 2.3. For simplicity, let a and b represent  $a_4$  and  $a_6$  in equation 2.2, respectively.

$$E(GF(q)): y^{2} = x^{3} + ax + b, \qquad (2.3)$$

Restricting the elliptic curve over some special finite fields, for example  $GF(2^m)$ , simplifies the curve equation 2.2. Equation 2.4 describes an elliptic curve over  $GF(2^m)$ .

$$E(GF(2^m)): y^2 + xy = x^3 + ax + b, (2.4)$$

The number of points on the curve, denoted  $\#E(GF(2^m))$ , is the order of the curve. In Hasse's Theorem [52], the number of points can be calculated as  $\#E(GF(2^m)) = 2^m + 1 - T_r$  where  $T_r$  is called the Trace of Frobenius. Hasse pointed out that  $T_r \leq 2\sqrt{2^m}$ . The calculation of  $T_r$  is introduced in [55]. For elliptic curves used in cryptographic schemes,  $2^m$  is usually very large. Thus,  $2\sqrt{2^m}$  is relatively small compare to  $2^m$  and the order of the curve can be represented by  $\#E(GF(2^m)) \approx 2^m$ . In Elliptic Curve Cryptography (ECC), the order of the curve represents the number of possible values that can be used in the cryptosystem. If  $2^m$  is divisible by  $T_r$ , the curve is supersingular. Otherwise, it is non-supersingular or ordinary. Supersingular and non-supersingular elliptic curves behave fundamentally differently in many aspects. For some certain supersingular elliptic curves, the operations can be optimized. Consequently, the calculation time of the cryptographic algorithms based on such curves can be reduced.

#### 2.4.4 Point Operations over Elliptic Curves

There is a specified point O which represents the point at infinite. This point is also the identity element of this elliptic curve. The point at infinity, O, together with the curve itself, form a group which provides some useful properties for cryptography.

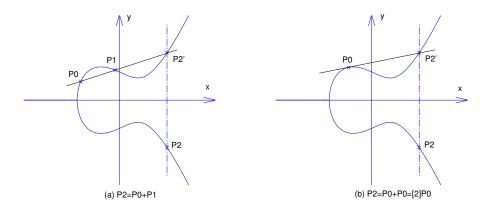

The group operation of Elliptic Curve is point addition, given by P2 = P0 + P1for  $Pi \in GF(2^m)$ . It operates on two input points P0 and P1 and forms a third point P2. For the point at infinity O there exists P + O = O + P = P, where  $P \in GF(2^m)$ . The geometrical explanation of this point addition operation is given by Ian Blake in [51]. Let P0 and P1 be two distinct rational points on curve  $E(GF(2^m))$ . The  $E(GF(2^m))$  is a cubic curve, thus, the straight line d(x, y) joining P0 and P1 must intersect the curve at a third point, called P2' which is a rational point on  $E(GF(2^m))$ . Reflecting P2' with the x-axis, one obtains another rational point P2 = P0 + P1. Fig. 2.6(a) shows a visualization of the point addition over elliptic curve  $E(GF(2^m)): y^2 = x^3 - x + 1$ .

In point addition, the special case P0 = P1, i.e. P2 = P0 + P0 = [2]P0, is called point doubling. In this case, the tangent to the curve at point P0, d(x, y), must intersect the curve at exactly one other point P2', as  $E(GF(2^m))$  is a cubic curve. Again, reflecting P2' about the x-axis, one obtains another rational point P2 = P0 + P0 = [2]P0. Fig. 2.6(b) shows a visualization of point doubling over the reals.

For an elliptic curve  $E(GF(2^m))$  defined by equation 2.4, let  $P0(x_0, y_0)$  and  $P1(x_1, y_1)$  be the points on the curve given in affine coordinates. Assume  $P0, P1 \neq O$

Fig. 2.6: Point Addition and Point Doubling over Elliptic curves

and  $P0 \neq -P1$ . The arithmetic operations for point addition P2 = P0 + P1 and point doubling P2 = P0 + P0 over the field GF(2m) are given as follows.

$$P2 = P0 + P1 \qquad P2 = P0 + P0 = [2]P0$$

$$\lambda = \frac{y_0 + y_1}{x_0 + x_1} \qquad \lambda = \frac{y_0}{x_0} + x_0$$

$$x_2 = \lambda^2 + \lambda + x_0 + x_1 + a \qquad (2.5) \qquad x_2 = \lambda^2 + \lambda + a \qquad (2.6)$$

$$y_2 = (x_0 + x_2)\lambda + x_2 + y_0 \qquad y_2 = (x_0 + x_2)\lambda + x_2 + y_0$$

$$Cost = 2M + 1I + 1S + 8A \qquad Cost = 2M + 1I + 1S + 6A$$

In equations 2.5 and 2.6,  $\lambda$  represents the slope of the straight line d(x, y) used in the chord and tangent illustrated in Fig. 2.6(a) and 2.6(b), respectively. **M**, **I**, **S** and **A** represent the operations of multiplication, inversion, squaring and addition over field  $GF(2^m)$ , respectively. For an elliptic curve over a finite field  $GF(2^m)$ , the group of points  $E(GF(2^m))$  is always either a cyclic group or the product of two cyclic groups [56]. Based on point addition and point doubling, and recalling the successive additions for cyclic groups in equation 2.1, a Point Scalar Multiplication is defined as per equation 2.7:

$$Q = [k]P = \underbrace{P + P + \dots + P}_{`+' k-1 \ times}$$

$$(2.7)$$

where P and Q are points on curve  $E(GF(2^m))$  and k is an integer. Let  $\ell$  be the order of point P and k can be an arbitrary integer in the range  $1 \le k \le \ell$ . Equation 2.7 can be simply carried out by repeated point additions. But, for large k, this can be slow in practice. A simple method to speed up Point Scalar Multiplication

Algorithm 2.1 Binary Method for Point Scalar Multiplication

Input:  $P \in E(GF(2^m))$ , *n*-bit integer  $k = \sum_{j=0}^{n-1} k_j 2^j$ ,  $k_j \in \{0, 1\}$ Output:  $Q = [k]P \in E(GF(2^m)))$ 1:  $Q \leftarrow O$ 2: for j = n - 1 downto 0 3:  $Q \leftarrow [2]Q$ 4: if  $k_j = 1$ 5:  $Q \leftarrow Q + P$ 6: end if 7: end for 8: return Q

is to make use of both point addition and point doubling operations. The binary method used to calculate equation 2.7 relies on the binary expansion of k, as given in Algorithm 2.1.

This algorithm takes point P over the elliptic curve and an arbitrary integer k, consisting of n bits, as inputs. It iterates through the n bits of k. For each bit of k, a point doubling operation is performed. If the present bit of k equals '1', a point addition operation is also performed. Let W represent the number of bits that equal to '1' in the binary expansion of k, i.e.  $W = \sum_{j=0}^{n-1} k_j, k_j \in \{0, 1\}$ . The Point Scalar Multiplication requires n-1 point doublings and W-1 point additions.

#### 2.4.5 Elliptic Curve Discrete Logarithm Problem

In a cyclic group G with a generator g and a multiplicative group operation ' $\times$ ', exponentiation is defined as

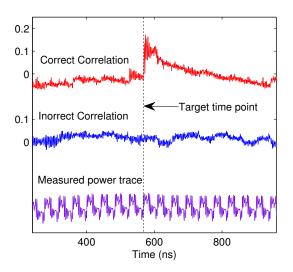

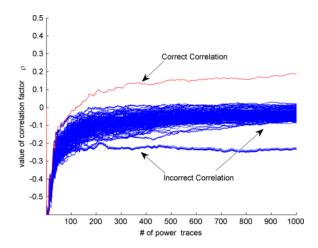

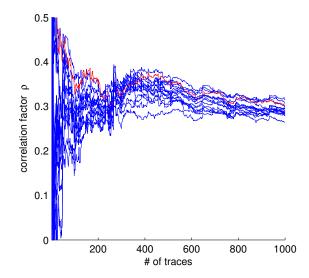

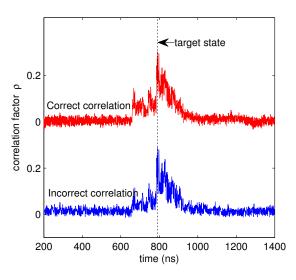

$$h = g^x \mod n \tag{2.8}$$