| Title                   | Development of germanium/silicon integration for near infrared detection                                                      |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Author(s)               | Gity, Farzan                                                                                                                  |

| Publication date        | 2013                                                                                                                          |

| Original citation       | Gity, F. 2013. Development of germanium/silicon integration for near infrared detection. PhD Thesis, University College Cork. |

| Type of publication     | Doctoral thesis                                                                                                               |

| Rights                  | © 2013. Farzan Gity<br>http://creativecommons.org/licenses/by-nc-nd/3.0/                                                      |

| Embargo information     | No embargo required                                                                                                           |

| Item downloaded<br>from | http://hdl.handle.net/10468/1250                                                                                              |

Downloaded on 2017-02-12T04:30:54Z

University College Cork, Ireland Coláiste na hOllscoile Corcaigh

# Development of Germanium/Silicon Integration for Near Infrared Detection

Farzan Gity

A thesis submitted in partial fulfilment of the requirements for the degree of Doctor of Philosophy

August 2013

Supervisors: Mr. Brian Corbett Dr. Alan Morrison Advisor: Dr. John Hayes Head of Department: Prof. Nabeel A. Riza

NATIONAL UNIVERSITY OF IRELAND, CORK

DEPARTMENT OF ELECTRICAL AND ELECTRONIC ENGINEERING

Research supported by Science Foundation Ireland (SFI) under grant number 07/SRC/I1173: Photonics Integration from Atoms to Systems (PIFAS)

# Declaration

This thesis is the candidate's own work and has not been submitted for another degree, either at the University College Cork or elsewhere.

Farzan Gity

# Abstract

Silicon (Si) is the base material for electronic technologies and is emerging as a very attractive platform for photonic integrated circuits (PICs). PICs allow optical systems to be made more compact with higher performance than discrete optical components. Applications for PICs are in the area of fibre-optic communication, biomedical devices, photovoltaics and imaging. Germanium (Ge), due to its suitable bandgap for telecommunications and its compatibility with Si technology is preferred over III-V compounds as an integrated on-chip detector at near infrared wavelengths. There are two main approaches for Ge/Si integration: through epitaxial growth and through direct wafer bonding. The lattice mismatch of  $\sim 4.2\%$  between Ge and Si is the main problem of the former technique which leads to a high density of dislocations while the bond strength and conductivity of the interface are the main challenges of the latter. Both result in trap states which are expected to play a critical role. Understanding the physics of the interface is a key contribution of this thesis.

This thesis investigates Ge/Si diodes using these two methods. The effects of interface traps on the static and dynamic performance of Ge/Si avalanche photodetectors have been modelled for the first time. The thesis outlines the original process development and characterization of mesa diodes which were fabricated by transferring a ~700 nm thick layer of p-type Ge onto n-type Si using direct wafer bonding and layer exfoliation. The effects of low temperature annealing on the device performance and on the conductivity of the interface have been investigated. It is shown that the diode ideality factor and the series resistance of the device are reduced after annealing. The carrier transport mechanism is shown to be dominated by generation–recombination before annealing and by direct tunnelling in forward bias and band-to-band tunnelling in reverse bias after annealing.

The thesis presents a novel technique to realise photodetectors where one of the substrates is thinned by chemical mechanical polishing (CMP) after bonding the Si-Ge wafers. Based on this technique, Ge/Si detectors with remarkably high responsivities, in excess of 3.5 A/W at 1.55  $\mu$ m at -2 V, under surface normal illumination have been measured. By performing electrical and optical measurements at various temperatures, the carrier transport through the hetero-interface is analysed by monitoring the Ge band bending from which a detailed band structure of the Ge/Si interface is proposed for the first time. The above unity responsivity of the detectors was explained by light induced potential barrier lowering at the interface. To our knowledge this is the first report of light-gated responsivity for vertically illuminated Ge/Si photodiodes.

The wafer bonding approach followed by layer exfoliation or by CMP is a low temperature wafer scale process. In principle, the technique could be extended to other materials such as Ge on GaAs, or Ge on SOI. The unique results reported here are compatible with surface normal illumination and are capable of being integrated with CMOS electronics and readout units in the form of 2D arrays of detectors. One potential future application is a low-cost Si process-compatible near infrared camera.

# **Acknowledgements**

First and foremost I would like to extend my sincerest thanks to my PhD supervisor Mr. Brian Corbett for giving me the opportunity to carry out my PhD in his group at Tyndall National Institute. I am very grateful for his professional guidance, support and understanding. I did not have any experimental background in semiconductor device fabrication when I first jointed this research group in 2009. Without Brian's constant guidance, encouragement and support during my three and half year study, I would not be able to reach to this point.

I am deeply grateful to my co-supervisor Dr. Alan Morrison. His support and valuable advices made my efforts possible. I have also learned a lot from my advisor Dr. John Hayes from whom I am really grateful. I would also like to thank Prof. Paul Townsend as a member of my dissertation committee for his encouragements and suggestions at my PhD review meetings. I would like to express my appreciation to Prof. Cindy Colinge, Mr. Joe O'Brien and Dr. Ki Yeol Byun for their great advices on wafer bonding. I would also like to thank Dr. Giovanni Isella, from Polytechnic University of Milan - Italy, for the germanium heteroepitaxy.

Many thanks go to my group members who were always ready to help me whenever I met difficulties in fabrication or characterization, especially Dr. James O'Callaghan, Dr. Mahbub Akhter, John Justice, Aidan Daly, Brad Snyder, Dr. Brendan Roycroft, and Dr. Liam Lewis.

I would like to thank Dr. Paul Hurley and Dr. Karim Cherkaoui for their helpful discussions and comments on my work. I am also grateful to members of the CFF group who helped me one way or another during my PhD program, especially Dan O'Connell, Vladimir Djara, Carmel Murphy, Brendan O'Neill, Alan Blake, Mary White, Paul Tassie, and also Michael Schmidt (for taking TEM images). All of them have given me a lot of help and provided me very useful suggestions in my research.

Huge thanks go to my parents and sister for their love, support and encouragements during this period and finally to my best friend and my wife, Lida.

# **Related patent / publications**

Patent: European Patent Application - Number: 1221079.5 Title: Amplified Ge/Si detectors formed by low temperature direct wafer bonding

Inventors: Farzan Gity, Brian Corbett, Alan Morrison, and John Hayes

- F. Gity, A. Daly, B. Snyder, F. H. Peters, J. M. Hayes, C. Colinge, A. P. Morrison and B. Corbett, "Ge/Si Heterojunction Photodiodes Fabricated by Low Temperature Wafer Bonding," *Optics Express*, vol. 21, no. 14, pp. 17309–17314, July 2013.

- F. Gity, K. Y. Byun, K. -H. Lee, K. Cherkaoui, J. M. Hayes, A. P. Morrison, C. Colinge, and B. Corbett, "Characterization of Germanium/Silicon *p*-*n* Junction Fabricated by Low Temperature Direct Wafer Bonding and Layer Exfoliation," *Applied Physics Letters*, vol. 100, Article number: 092102, 2012.

- J. M. Hayes, F. Gity, B. Corbett, and A. P. Morrison, "Modeling the Effects of Interface Traps on Passive Quenching of a Ge/Si Geiger Mode Avalanche Photodiode," *Journal of Optical and Quantum Electronics*, vol. 44, pp. 119– 124, January 2012.

- F. Gity, J. M. Hayes, B. Corbett, and A. P. Morrison, "Modeling the Effects of Interface Traps on the Static and Dynamic Characteristics of Ge/Si Avalanche Photodiodes," *IEEE Journal of Quantum Electronics*, vol. 47, no. 6, pp. 849– 857, June 2011.

- K. Y. Byun, P. Fleming, N. Bennet, F. Gity, P. McNally, M. Morris, I. Ferain, and C. Colinge, "Comprehensive Investigation of Ge–Si Bonded Interfaces using Oxygen Radical Activation," *Journal of Applied Physics*, vol. 109, Article number: 123529, 2011.

- A. P. Morrison, J. M. Hayes, F. Gity, and B. Corbett, "Progress towards Photon Counting between 1μm and 1.6μm using Silicon with Infra–Red Absorbers," *Proc. of SPIE*, vol. 7681, Article Number: 76810N, 2010.

- K. Y. Byun, I. Ferain, J. M. Hayes, R. Yu, F. Gity, and C. Colinge, "Surface Activation using Oxygen and Nitrogen Radical for Ge–Si Avalanche Photodiode Integration," *Elsevier Journal of Microelectronic Engineering*, vol. 88, pp. 522–525, September 2010.

- 8. **F. Gity**, K. Y. Byun, K. -H. Lee, K. Cherkaoui, J. M. Hayes, A. P. Morrison, C. Colinge, and B. Corbett, "Ge/Si p–n Diode Fabricated by Direct Wafer Bonding

and Layer Exfoliation," *Transaction of the 221st Electro-Chemical Society Conf. (ECS)*, vol. 45 (6), pp. 131–139, USA, May **2012**.

- J. M. Hayes, F. Gity, B. Corbett, and A. P. Morrison, "Modeling the Effects of Interface Traps on Passive Quenching of a Ge/Si Geiger Mode Avalanche Photodiode," 11<sup>th</sup> International Conference on Numerical Simulation of Optoelectronic Devices (NUSOD), Rome, Italy, Sept. 2011.

- K. Y. Byun, J. M. Hayes, F. Gity, B. Corbett, and C. Colinge, "Wafer Bonded Ge–Si Heterostructure for Avalanche Photodiode Application," *Materials Research Society (MRS)*, San Fransisco, USA, Apr. 2011.

- I. Ferain, J. Hayes, R. Yu, K. Y. Byun, F. Gity, B. Long, and C. Colinge, "Electrical Conductivity of Directly Bonded Silicon/Germanium Hetero-Structures", 52<sup>nd</sup> TMS Electronic Materials Conference (EMC), p. 117, California, USA, Jun. 2011.

- F. Gity, J. M. Hayes, B. Corbett, and A. P. Morrison, "Modeling Ge/Si Avalanche Photodiodes," *IEEE European Conference on Integrated Optics (ECIO)*, Cambridge, UK, Apr. 2010.

- R. Yu, K. Y. Byun, F. Gity, J. M. Hayes, I. Ferain, C. Colinge, and B. Corbett, "Structural and Electrical Properties of Low Temperature Direct Bonded Germanium to Silicon Wafer for Photodetector Applications," *Transaction of the* 218<sup>th</sup> Electro–Chemical Society (ECS) Meeting, pp. 161–168, Las Vegas, USA, Oct. 2010.

# Non-related publications

- H. Yang, C. L. L. M. Daunt, F. Gity, K. –H. Lee, W. Han, B. Corbett, and F. H. Peters, "Zero–Bias High–Speed Edge–Coupled Unitraveling–Carrier InGaAs Photodiode," *IEEE Photonics Technology Letters*, vol. 22, no. 23, pp. 1747– 1749, December 2010.

- H. Yang, C. L. L. M. Daunt, F. Gity, K. –H. Lee, W. Han, K. Thomas, B. Corbett, and

F. H. Peters, "Design and Fabrication of Uni–Traveling–Carrier InGaAs Photodiodes," *Proc. of SPIE*, vol. 7847, Article Number: 784705, 2010.

- H. Yang, C. L. L. M. Daunt, K. –H. Lee, W. Han, F. Gity, B. Corbett, and F. H. Peters, "High–Speed and High–Power InGaAs/InP Photodiode," 23<sup>rd</sup> International Conference on Indium Phosphide and Related Materials (IPRM), Berlin, Germany, May 2011.

# Table of contents

| Declaration       | 2  |

|-------------------|----|

| Abstract          | 3  |

| Acknowledgements  | 4  |

| Publications      | 5  |

| Table of contents | 7  |

| List of acronyms  | 11 |

| List of figures   | 13 |

| List of tables    | 21 |

# Chapter 1: Introduction and literature review

| 1.1. | Introduction.  |                                                                           | 22 |

|------|----------------|---------------------------------------------------------------------------|----|

|      | 1.1.1. Germa   | anium for long wavelength detection                                       | 22 |

|      | 1.1.2. Chara   | cteristics of optical receiver                                            | 24 |

| 1.2. | Ge/Si photoni  | c and electronic integrated circuits                                      | 25 |

| 1.3. | Ge/Si integrat | ion techniques                                                            | 28 |

|      | 1.3.1. Ge/Si   | integration by epitaxy                                                    | 29 |

|      | 1.3.1.1.       | Molecular Beam Epitaxy (MBE)                                              | 30 |

|      | 1.3.1.2.       | Ultrahigh Vacuum Chemical Vapour Deposition<br>(UHV-CVD)                  | 31 |

|      | 1.3.1.3.       | Reduced Pressure Chemical Vapour Deposition (RP-CVD)                      | 32 |

|      | 1.3.1.4.       | Low Energy Plasma Enhanced Chemical Vapour<br>Deposition (LEPE-CVD)       | 33 |

|      | 1.3.1.5.       | Multiple Hydrogen Annealing for Heteroepitaxy<br>(MHAH) CVD               | 33 |

|      | 1.3.1.6.       | Rapid Melting Growth (RMG) – Ge on insulator<br>and wavegui de structures | 33 |

|      | 1.3.2. Ge/Si   | photodetector by hetero-epitaxy                                           | 35 |

|      | 1.3.2.1.       | Ge/Si photodetector – vertical structure                                  | 35 |

|      | 1.3.2.2.       | Ge/Si photodetector – waveguide structure                                 | 38 |

|      | 1.3.2.3.       | Ge/Si avalanche photodiode                                                | 43 |

|      | 1.3.3. Ge/Si integration by wafer bonding           | 47 |

|------|-----------------------------------------------------|----|

|      | 1.3.3.1. Fabrication challenges using wafer bonding | 48 |

|      | 1.3.4. Ge/Si photodetector by wafer bonding         | 49 |

| 1.4. | Organization of the thesis                          | 51 |

| 1.5. | Conclusions                                         | 52 |

| 1.6. | References                                          | 53 |

## Chapter 2: Design and simulation of Ge/Si APDs

| 2.1. | Introduction |                                                  | 59 |

|------|--------------|--------------------------------------------------|----|

| 2.2. | Design       | of Ge/Si APD structure                           | 59 |

|      | 2.2.1.       | Gain profile and breakdown voltage               | 61 |

|      | 2.2.2.       | Gain-bandwidth product                           | 64 |

| 2.3. | Effects      | of interface traps                               | 66 |

|      | 2.3.1.       | Physics of the model                             | 67 |

|      | 2.3.2.       | Electrical characteristics                       | 71 |

|      | 2.3.3.       | Electric field profile and carrier concentration | 75 |

|      | 2.3.4.       | APD gain                                         | 77 |

|      | 2.3.5.       | Frequency response and gain-bandwidth product    | 80 |

| 2.4. | Conclu       | isions                                           | 86 |

| 2.5. | References   |                                                  | 86 |

# Chapter 3: Investigation of photodetectors based on epitaxial Ge on structured Si substrate

| 3.1. | Introduction                     |                                        | 88 |

|------|----------------------------------|----------------------------------------|----|

| 3.2. | Layer structure of Ge/Si devices |                                        | 90 |

| 3.3. | Materi                           | al analysis                            | 93 |

|      | 3.3.1.                           | Ge film characterization               | 93 |

|      | 3.3.2.                           | Quantifying dislocation density        | 93 |

| 3.4. | Dopin                            | gprofile of different layers           | 95 |

|      | 3.4.1.                           | Spreading resistance profile           | 95 |

|      | 3.4.2.                           | Secondary-ion mass spectrometry result | 95 |

| 3.5. | Mask o                           | design                                 | 99 |

| 3.6.  | Device fabrication                                      | 99  |

|-------|---------------------------------------------------------|-----|

| 3.7.  | Electrical characterization                             | 100 |

| 3.8.  | Low temperature electrical and optical characterization | 105 |

| 3.9.  | Si epilayers characterization                           | 107 |

| 3.10. | Effects of low/high temperature annealing               | 109 |

| 3.11. | Conclusions                                             | 110 |

| 3.12. | References                                              | 111 |

# Chapter 4: Ge/Si diodes fabricated by layer exfoliation

| 4.1. | Introduction |                                          | 113 |

|------|--------------|------------------------------------------|-----|

| 4.2. | p-Ge/        | n+-Si diode fabrication                  | 114 |

| 4.3. | Result       | s and discussion                         | 116 |

|      | 4.3.1.       | Current-voltage characteristics          | 116 |

|      | 4.3.2.       | Proposed band diagram at Ge/Si interface | 120 |

|      | 4.3.3.       | Capacitance-voltage characteristics      | 121 |

| 4.4. | Conclu       | usions                                   | 123 |

| 4.5. | Refere       | nces                                     | 123 |

# Chapter 5: Ge/Si photodetectors fabricated by direct wafer bonding

| 5.1. | Introduction       |                                                  | 127 |

|------|--------------------|--------------------------------------------------|-----|

| 5.2. | Device fabrication |                                                  | 128 |

| 5.3. | Result             | s and discussion - Ge on Si devices              | 128 |

|      | 5.3.1.             | TEM and SEM images of the Ge/Si devices          | 128 |

|      | 5.3.2.             | Electrical characteristics of the Ge/Si diodes   | 130 |

|      | 5.3.3.             | Proposed band diagram at the Ge/Si interface     | 136 |

|      | 5.3.4.             | Optical characteristics of the Ge/Si photodiodes | 136 |

| 5.4. | Result             | s and discussion - Si on Ge devices              | 142 |

| 5.5. | Conclu             | isions                                           | 146 |

| 5.6. | References         |                                                  | 148 |

# Chapter 6: Conclusions and future work

| 6.1. | Summary and conclusions         | 150 |

|------|---------------------------------|-----|

| 6.2. | Novel contributions of the work | 152 |

| 6.3. | Recommendations for future work | 152 |

# Appendices

| A1. | Details of wafer bonding                                                  | 155 |

|-----|---------------------------------------------------------------------------|-----|

| A2. | Spreading resistance profiling (SRP)                                      | 158 |

| A3. | Defective regions of the UPSW and the <i>I</i> - <i>V</i> characteristics | 160 |

| A4. | Germanium and silicon processing parameters                               | 162 |

| A5. | Layer structure of the APD wafers and the device mask layout              | 165 |

| A6. | References                                                                | 167 |

# List of acronyms

| Acronym  | Definition                                            |

|----------|-------------------------------------------------------|

| AML      | Applied Microengineering Limited                      |

| APD      | Avalanche Photodiode                                  |

| ARC      | Anti-Reflection Coating                               |

| BCB      | Bisbenzocyclobutane                                   |

| BEOL     | Back-End-Of-Line                                      |

| BER      | Bit Error Rate                                        |

| BOX      | Buried Oxide                                          |

| BW       | Bandwidth                                             |

| CMOS     | Complementary Metal Oxide Semiconductor               |

| СМР      | Chemical Mechanical Polishing                         |

| EPD      | Etch Pit Density                                      |

| GBP      | Gain Bandwidth Product                                |

| GOI      | Germanium-On-Insulator                                |

| GR       | Guard Ring                                            |

| LEPE-CVD | Low Energy Plasma Enhanced Chemical Vapour Deposition |

| MBE      | Molecular Beam Epitaxy                                |

| МНАН     | Multiple Hydrogen Annealing for Heteroepitaxy         |

| MSM      | Metal Semiconductor Metal                             |

| M/NEMS   | Micro/Nano-Electro-Mechanical Systems                 |

| NEP      | Noise Equivalent Power                                |

| NI       | Normal Incident                                       |

| PECVD    | Plasma Enhanced Chemical Vapour Deposition            |

| PIC      | Photonics Integrated Circuits                         |

| RMG      | Rapid Melting Growth                                  |

| RP-CVD   | Reduced Pressure Chemical Vapour Deposition           |

| SACM     | Separate Absorption Charge Multiplication             |

| SAT      | Spray Acid Tool                                       |

| SC1(2)   | Standard Cleaning 1 (2) solution                      |

| SEG     | Selective Epitaxial Growth                  |  |  |  |

|---------|---------------------------------------------|--|--|--|

| SEM     | Scanning Electron Microscopy                |  |  |  |

| SIMS    | Secondary Ion Mass Spectrometry             |  |  |  |

| SOI     | Silicon-On-Insulator                        |  |  |  |

| SRP     | Spreading Resistance Profile                |  |  |  |

| TDD     | Threading Dislocation Density               |  |  |  |

| TEM     | Transmission Electron Microscopy            |  |  |  |

| TLM     | Transfer Length Method                      |  |  |  |

| UHV-CVD | Ultrahigh Vacuum Chemical Vapour Deposition |  |  |  |

| UID     | Un-Intentionally Doped                      |  |  |  |

| UPSW    | Un-Processed Silicon Wafer                  |  |  |  |

| WG      | Waveguide                                   |  |  |  |

| XRD     | X-Ray Diffraction                           |  |  |  |

# List of figures

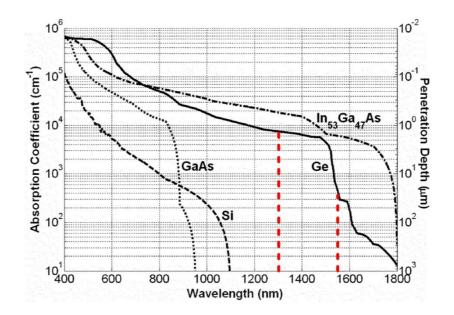

| Fig. 1-1. Absorption coefficients of various semiconductors - taken from Dosunmu [4].                                                                                                                                                                                                                                                                      | 23 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

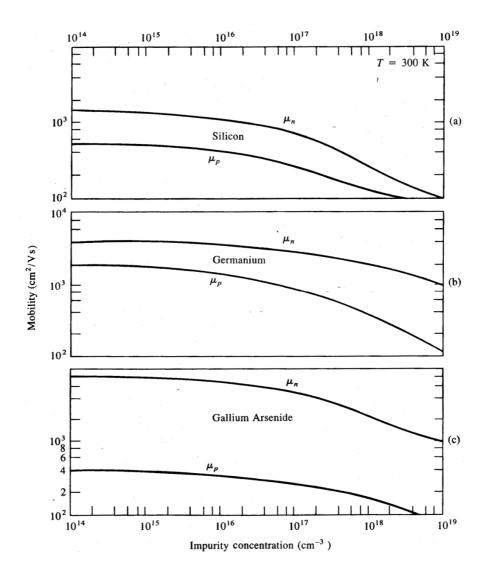

| Fig. 1-2. Drift mobility of (a) Si, (b) Ge, and (c) GaAs at 300 K versus impurity concentration - taken from Sze [5].                                                                                                                                                                                                                                      | 23 |

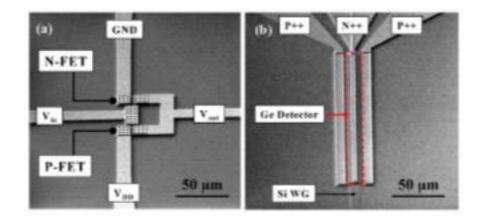

| Fig. 1-3. (a) SEM micrograph of a Si CMOS inverter circuit on SOI platform. (b) SEM micrograph of a monolithically integrated Ge p-i-n photodetector with a Si photonic waveguide [8].                                                                                                                                                                     | 26 |

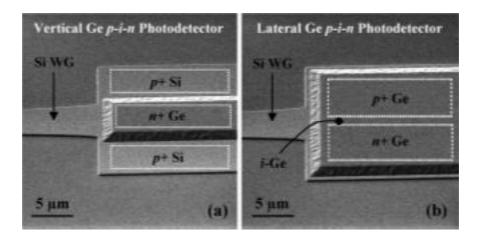

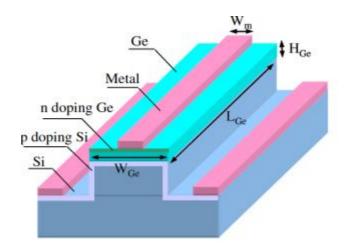

| Fig. 1-4. (a) SEM micrograph showing an evanescent coupled Ge photodetector<br>featuring vertical p-i-n configuration. The width $W$ and length $L$ of the detector is 8 and<br>100 µm, respectively. (b) Ge photodetector design with a lateral p-i-n configuration.<br>The width $W$ and length $L$ of this detector is 20 and 100 µm, respectively [8]. | 26 |

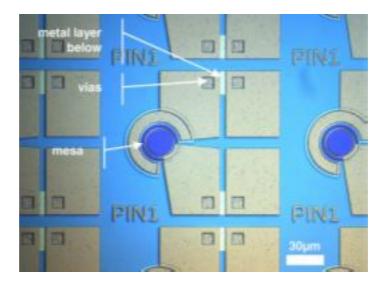

| Fig. 1-5. Fabricated 30- $\mu$ m mesa diameter photodiode array. Vias connect the photodiode pads to the embedded metal layer below from the CMOS-based silicon wafer [10].                                                                                                                                                                                | 27 |

| Fig. 1-6. Cross-sectional SEM view of a 90 nm CMOS-Integrated Nano-Photonics (CINP) metal stack with Ge PD embedded into the front-end. Zoomed-in image of a PD is shown on top left. Optical microscope top-down image is shown on the low left [11].                                                                                                     | 28 |

| Fig. 1-7. Various techniques that have been used for the integration of germanium with silicon. MBE: Molecular Beam Epitaxy; CVD: Chemical Vapour Deposition; RMG: Rapid Melting Growth; RP-CVD: Reduced Pressure CVD; UHV-CVD: Ultra High Vacuum CVD; LEPE-CVD: Low Energy Plasma Enhanced CVD.                                                           | 29 |

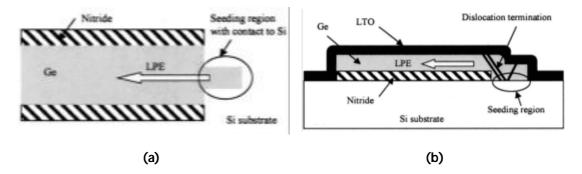

| Fig. 1-8. (a) Top view and (b) cross-sectional schematics of the structure used for Ge RMG growth [32]. LTO: Low Temperature Oxide.                                                                                                                                                                                                                        | 34 |

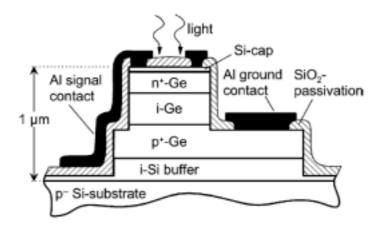

| Fig. 1-9. Schematic cross section of the p-i-n photodetector (not to scale) [18].                                                                                                                                                                                                                                                                          | 36 |

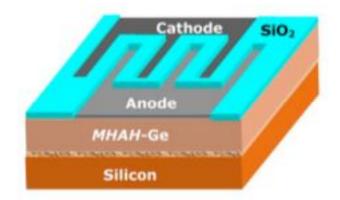

| Fig. 1-10. Cross-section of MSM PD fabricated on MHAH-Ge layer grown on Si substrate. SiO <sub>2</sub> layer was patterned before the evaporation of the metal electrodes. Defects are concentrated near the Si/Ge interface [33].                                                                                                                         | 37 |

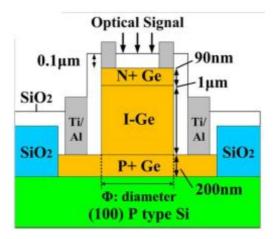

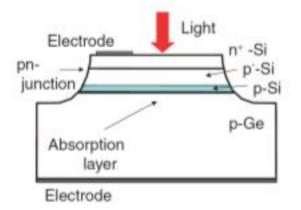

| Fig. 1-11. Schematic diagram of the cross section of normal incidence Ge/Si p-i-n photodiode [36].                                                                                                                                                                                                                                                         | 38 |

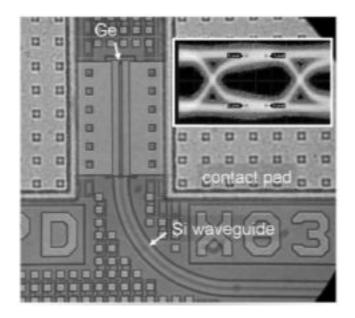

| Fig. 1-12. Ge photodetector integrated in CMOS, shown with 10-Gbps eye (inset) [39].                                                                                                                                                                                                                                                                       | 39 |

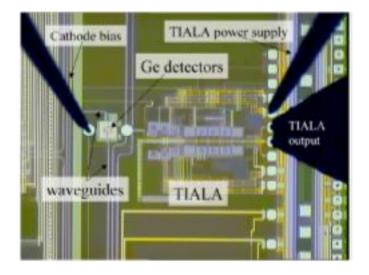

| Fig. 1-13. Picture of the optical receiver including germanium waveguide photodetector monolithically integrated in CMOS process by Luxtera [40].                                                                                                                                                                                                          | 40 |

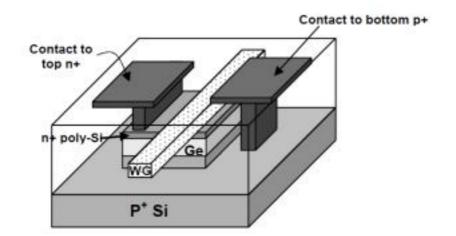

| Fig. 1-14. Schematic structure of a waveguide-integrated Ge p-i-n photodetector [41].                                                                                                                                                                                             | 40 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

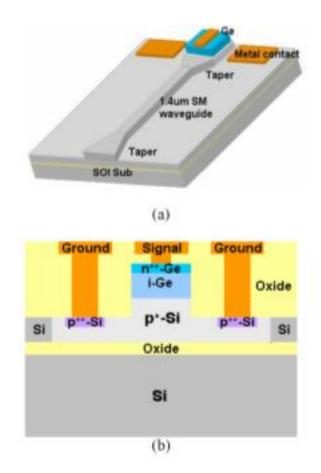

| Fig. 1-15. (a) Schematic layout for the Ge detector integrated with a passive waveguide.<br>(b) Cross-section schematic of the Ge n-i-p waveguide photodetector [42].                                                                                                             | 41 |

| Fig. 1-16. Schematic view of a vertical pin Ge waveguide photodetector integrated on top of an SOI waveguide [43].                                                                                                                                                                | 42 |

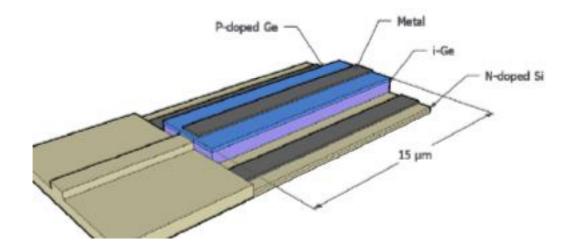

| Fig. 1-17. Schematic view of pin germanium photodetector integrated in SOI waveguide. The photodetector length and width are 15 µm and 3 µm, respectively [44].                                                                                                                   | 43 |

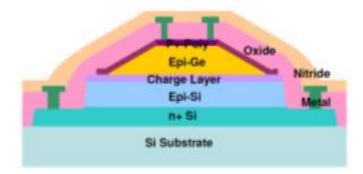

| Fig. 1-18. Schematic cross-section of Ge/Si SACM structure [45].                                                                                                                                                                                                                  | 44 |

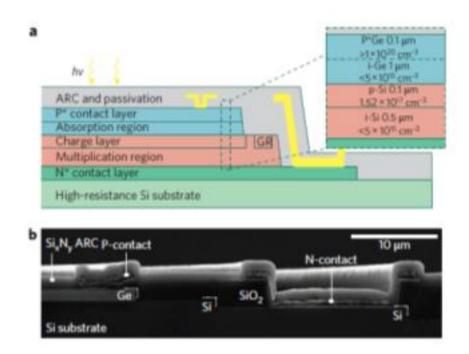

| Fig. 1-19. (a) Schematic and (b) SEM cross-sections of a germanium/silicon APD. The floating guard ring (GR in 'a') design was used to prevent premature breakdown along the device perimeter. ARC: anti-reflection coating [3].                                                  | 44 |

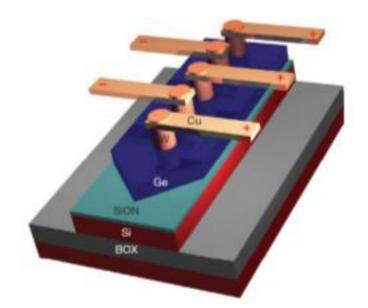

| Fig. 1-20. Schematic of the nanophotonics Ge waveguide-integrated APD. The Ge layer<br>is deposited on top of a SiON insulating layer which overlays a Si waveguide. The<br>detector is biased though metallic interdigitated contacts consisting of W plugs and Cu<br>wires [2]. | 45 |

| Fig. 1-21. Ge/Si heterojunction photodiode structure fabricated by low temperature wet wafer bonding [74].                                                                                                                                                                        | 50 |

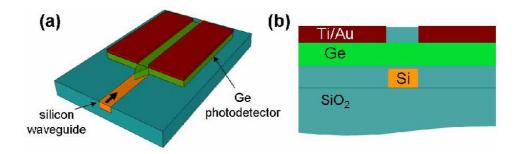

| Fig. 1-22. Schematics of (a) the integrated Ge photodetector on a silicon waveguide, and (b) the device cross section [58].                                                                                                                                                       | 51 |

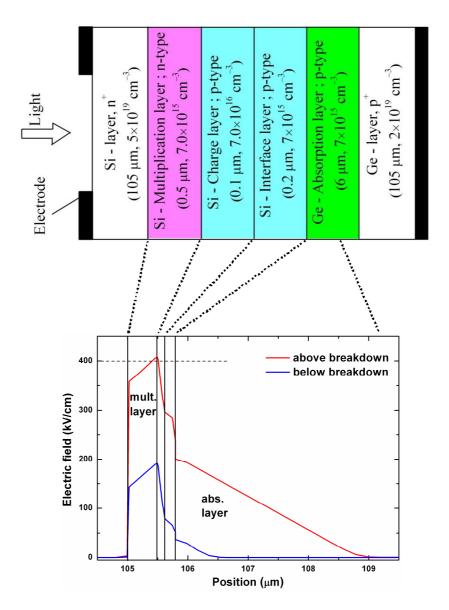

| Fig. 2-1. Schematic of the Ge/Si SACM-APD base structure along with the static electric field distribution across the selected regions for two bias vol tages.                                                                                                                    | 60 |

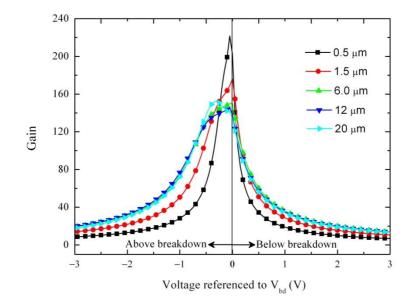

| Fig. 2-2. Dependence of the Ge/Si APD gain on the absorption layer thickness.                                                                                                                                                                                                     | 61 |

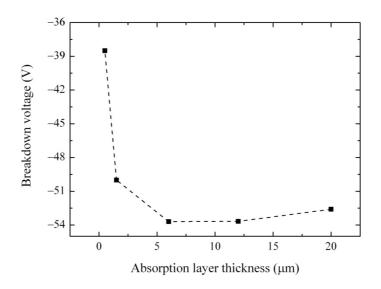

| Fig. 2-3. Si/Ge APD breakdown voltage as a function of absorption layer thickness.                                                                                                                                                                                                | 62 |

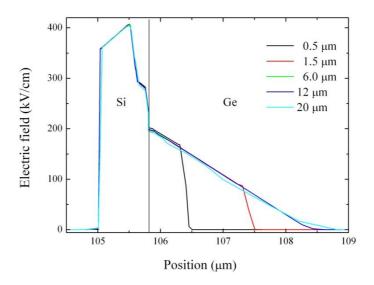

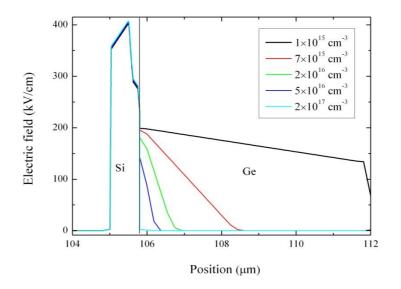

| Fig. 2-4. Effects of absorption layer thickness on the electric field across different layers of the Ge/Si APD.                                                                                                                                                                   | 62 |

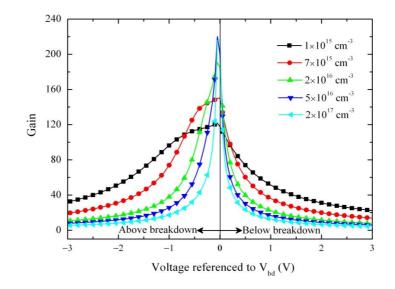

| Fig. 2-5. Ge/Si APD gain-voltage profile for different absorption layer doping concentrations. Other structural parameters are the same as Fig. 2-1.                                                                                                                              | 63 |

| Fig. 2-6. Effects of absorption layer doping concentration on the electric field across different layers of the Ge/Si APD. Other structural parameters are the same as Fig. 2-1.                                                                                                  | 63 |

| Fig. 2-7. Si/Ge APD breakdown voltage as a function of absorption layer doping concentration. Other structural parameters are the same as Fig. 2-1.                                                                                                                               | 64 |

|                                                                                                                                                                                                                                                                                   |    |

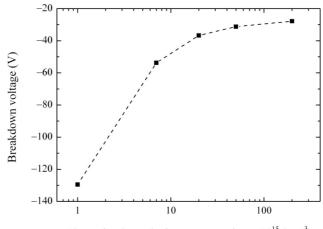

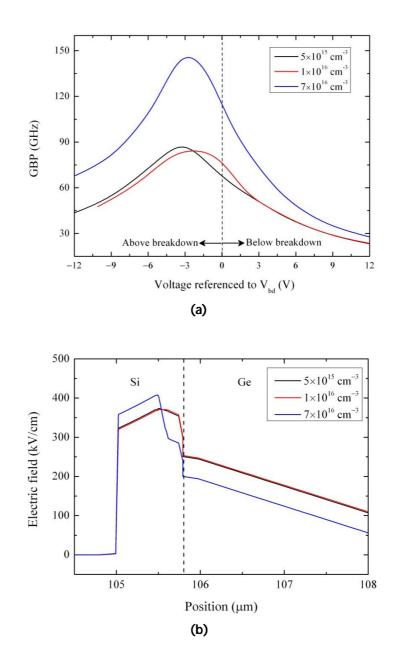

| Fig. 2-8. Dependence of the (a) GBP, and (b) electric field profile of the Si/Ge APD for65different multiplication layer doping concentrations.                                                                                                                                                                                                | 5 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

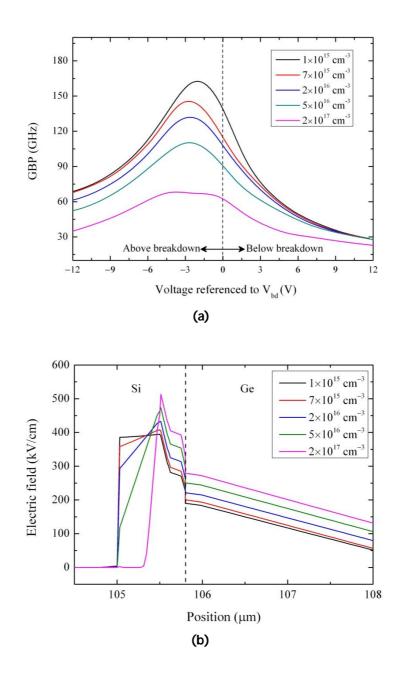

| Fig. 2-9. Dependence of the (a) GBP, and (b) electric field profile of the Si/Ge APD for66different charge layer doping concentrations.                                                                                                                                                                                                        | 6 |

| Fig. 2-10. Schematic of the Ge/Si SACM-APD structure modelled in this work. 68                                                                                                                                                                                                                                                                 | 8 |

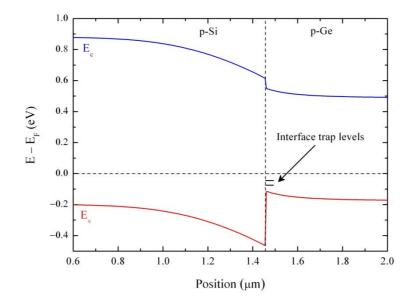

| Fig. 2-11. Band diagram and defect levels at p-Si/p-Ge interface at equilibrium (doping concentration is $5 \times 10^{15}$ cm <sup>-3</sup> for Si and Ge).                                                                                                                                                                                   | 8 |

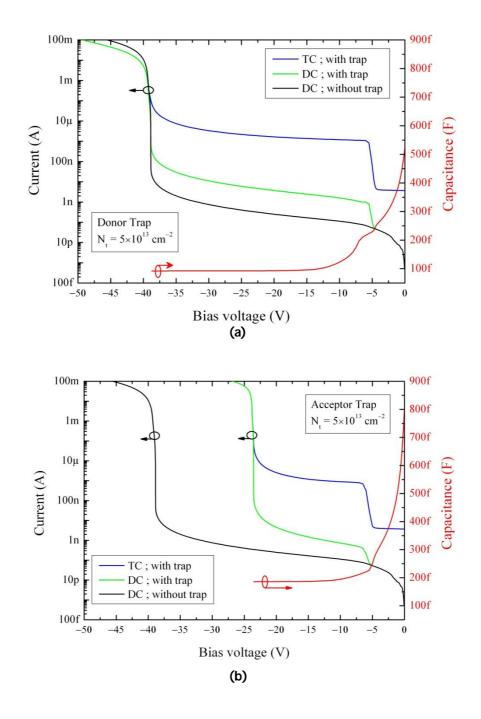

| Fig. 2-12. <i>I</i> – <i>V</i> and <i>C</i> – <i>V</i> characteristics of Ge/Si APD with (a) donor traps ( $N_t = 5 \times 10^{13}$ cm <sup>-2</sup> ), and (b) acceptor traps ( $N_t = 5 \times 10^{13}$ cm <sup>-2</sup> ). Dark current of an ideal APD is also shown.                                                                      | 1 |

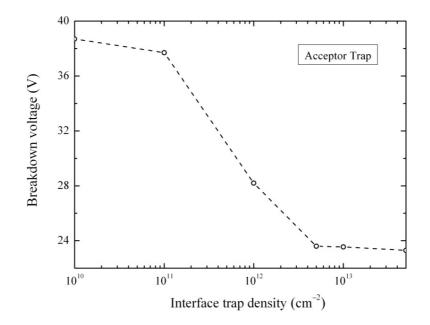

| Fig. 2-13. Effects of acceptor trap density on the Ge/Si APD breakdown voltage.72                                                                                                                                                                                                                                                              | 2 |

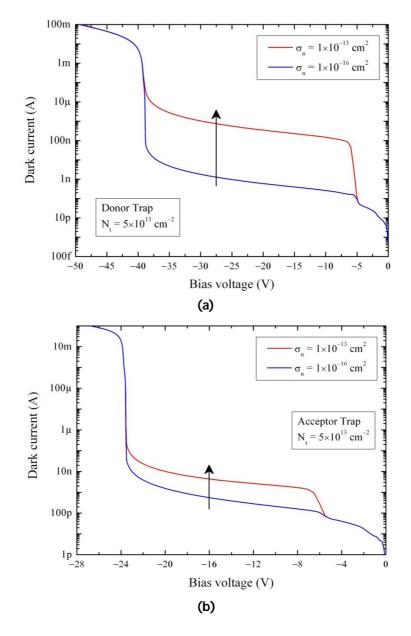

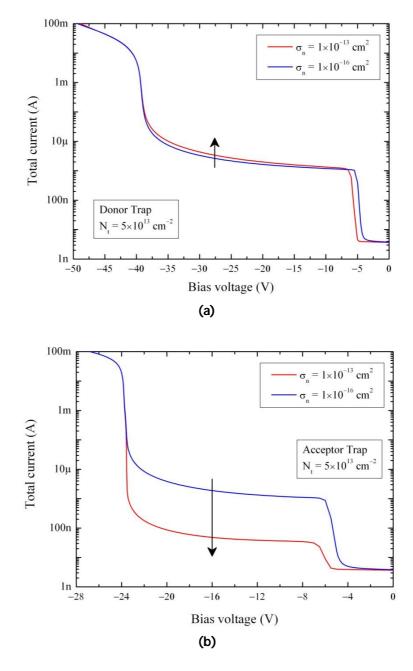

| Fig. 2-14. Effects of electron capture cross sections on the dark current for (a) donor 73 type and (b) acceptor type traps. $N_t = 5 \times 10^{13} \text{ cm}^{-2}$ for all cases.                                                                                                                                                           | 3 |

| Fig. 2-15. Effects of electron capture cross sections on the total current for (a) donor 74 type and (b) acceptor type traps. $N_t = 5 \times 10^{13} \text{ cm}^{-2}$ for all cases.                                                                                                                                                          | 4 |

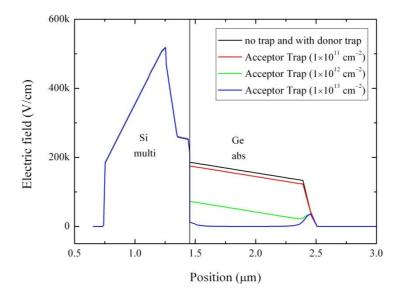

| Fig. 2-16. Electric field distribution across the Ge/Si APD at breakdown voltage for no<br>traps and donor traps ( $N_t = 5 \times 10^{13}$ cm <sup>-2</sup> ), and for acceptor traps at the interface with<br>different densities. The electric field in the silicon multiplication region is high enough<br>for impact ionization to occur. | 5 |

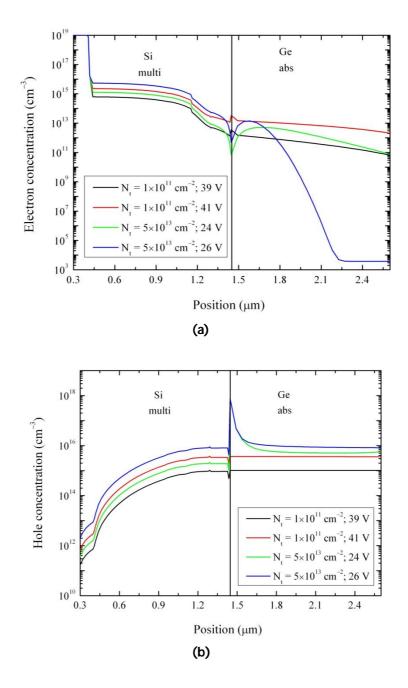

| Fig. 2-17. Effects of acceptor trap densities on the (a) electron concentration, and (b)76hole concentration across the Ge/Si APD at different bias voltages.                                                                                                                                                                                  | 6 |

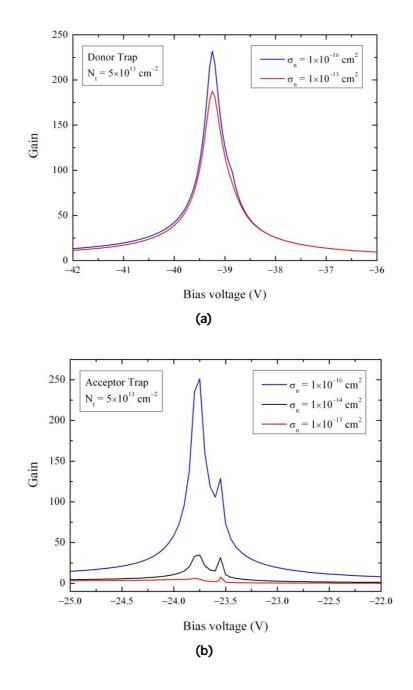

| Fig. 2-18. Gain of Ge/Si APD – comparison between the effects of interface trap types78and electron capture cross sections for (a) donor and (b) acceptor traps.                                                                                                                                                                               | 8 |

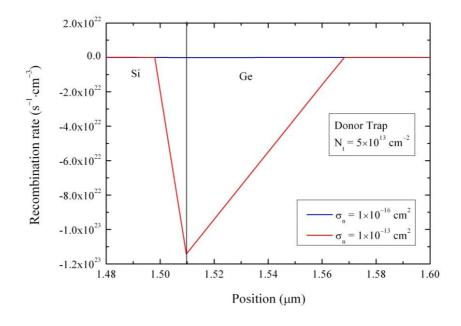

| Fig. 2-19. Recombination rate profile at the material interface at the bias79corresponding to the gain peak for two different trap types: (a) donor traps, and (b)acceptor traps.                                                                                                                                                              | 9 |

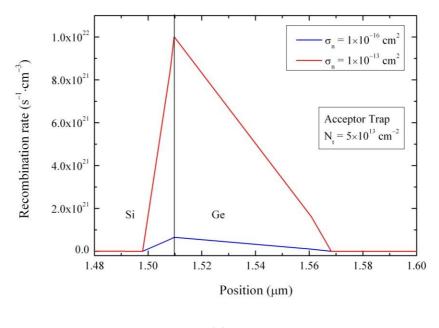

| Fig. 2-20. (a) Electron and (b) hole velocities at different bias voltages considering81different acceptor trap densities.                                                                                                                                                                                                                     | 1 |

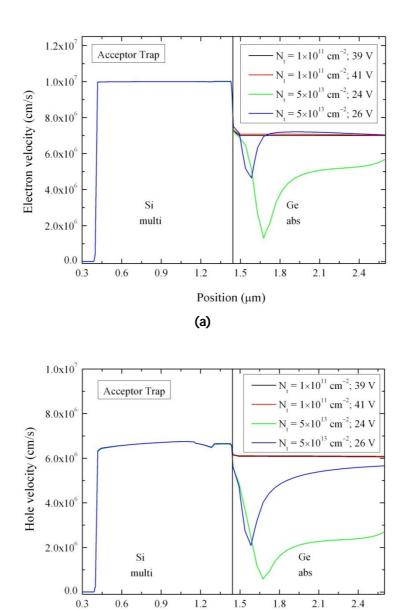

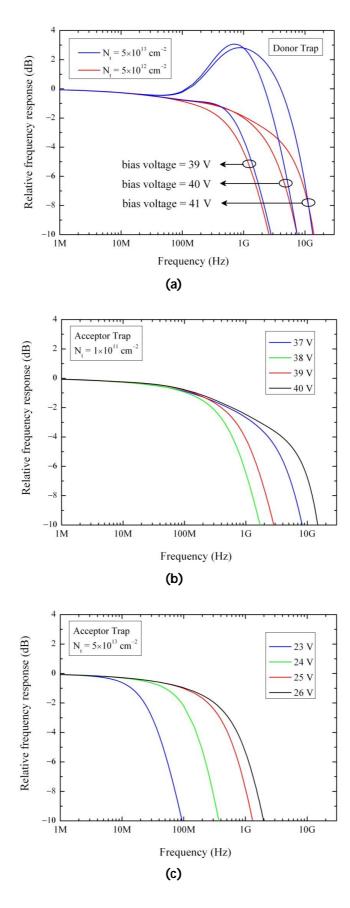

| Fig. 2-21. Frequency response at different bias voltages for (a) donor traps, (b)       82                                                                                                                                                                                                                                                     | 2 |

| acceptor traps with $N_t = 1 \times 10^{11}$ cm <sup>-2</sup> , and (c) acceptor traps with $N_t = 5 \times 10^{13}$ cm <sup>-2</sup> . $\sigma_n = 1 \times 10^{-13}$ cm <sup>2</sup> in all cases.                                                                                                                                           |   |

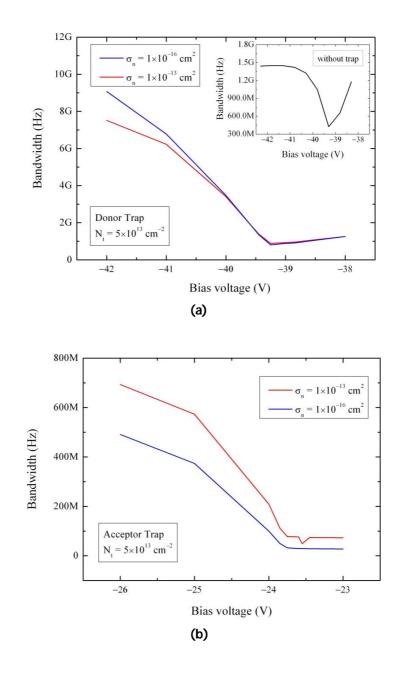

capture cross sections for (a) donor traps, and (b) acceptor traps, both with  $N_t = 5 \times 10^{13}$  cm<sup>-2</sup>. The inset in (a) shows the bandwidth of an ideal APD.

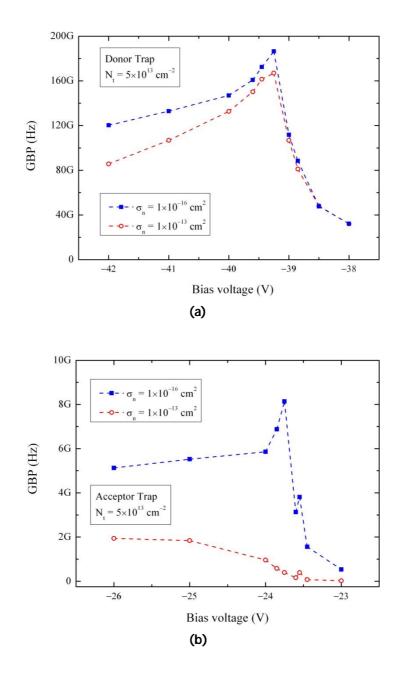

Fig. 2-23. GBP of Ge/Si APD versus bias voltage for different electron capture cross85sections for (a) donor, and (b) acceptor traps.

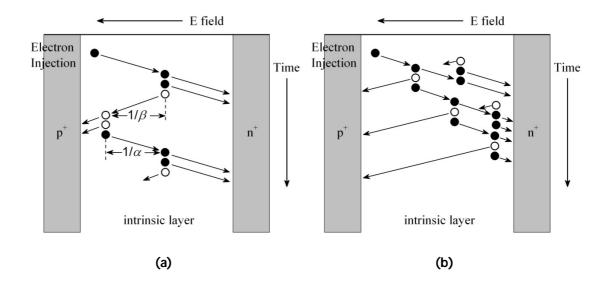

| Fig. 3-1: Avalanche multiplication process for (a) $\alpha \approx \beta$ , and (b) $\alpha >> \beta$ . | 89 |

|---------------------------------------------------------------------------------------------------------|----|

|---------------------------------------------------------------------------------------------------------|----|

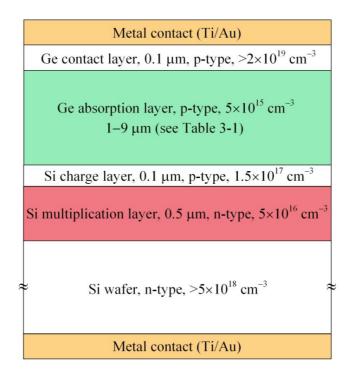

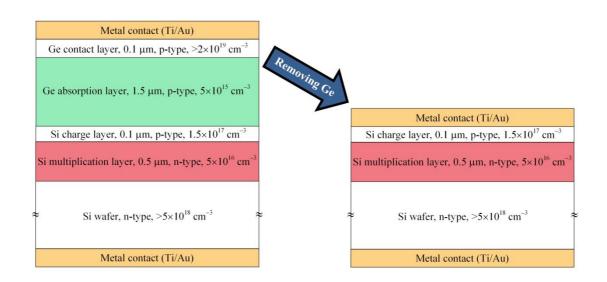

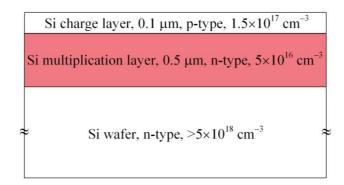

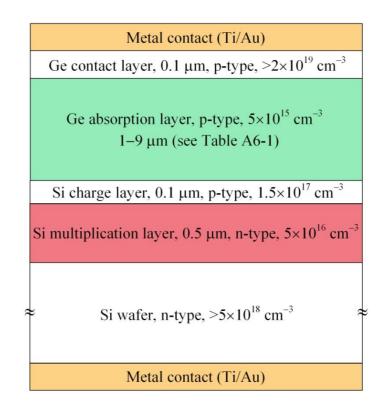

Fig. 3-2. Schematic cross-sectional view of different layers of the epitaxial Ge/Si APDs. 92

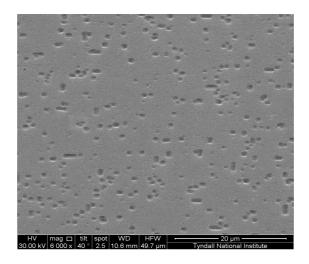

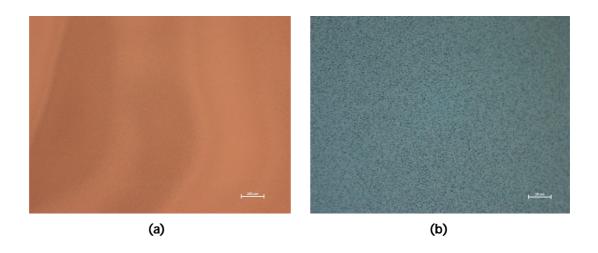

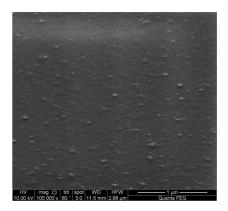

Fig. 3-3. An SEM image of sample number 8511 (Ge thickness: 1  $\mu$ m) from wafers 94 grown by LEPE-CVD after shallow etch (10 s) for the purpose of EPD counting. The TDD is ~1-2×10<sup>7</sup> cm<sup>-2</sup>. The scale bar is 20  $\mu$ m.

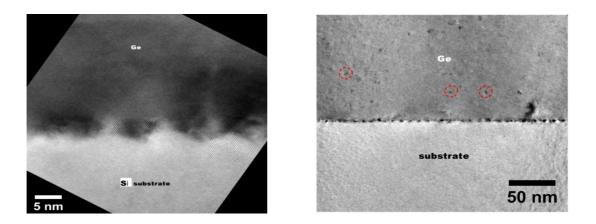

Fig. 3-4. Cross-sectional TEM images of the Ge epitaxial layer directly grown on Si95substrate and the Ge/Si interface at different magnifications. Red circles show thedislocations generated at the Ge/Si interface and terminated at the sidewall.

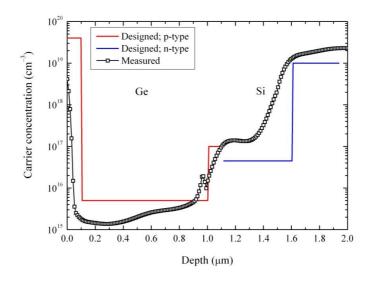

Fig. 3-5. SRP result of wafer number 8511 (Ge thickness: 1 μm). Black dots are the96measured data; Red line shows the designed doping level in the p-type layers; Blue lineshows the designed doping level in the n-type layers.

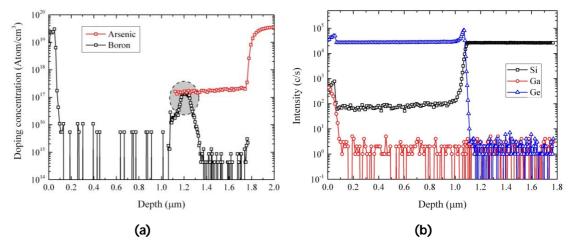

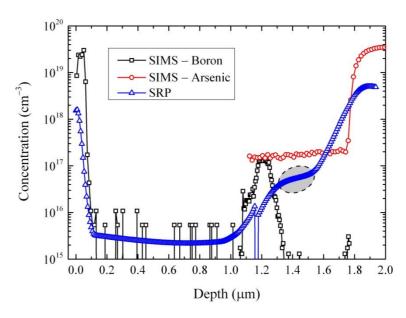

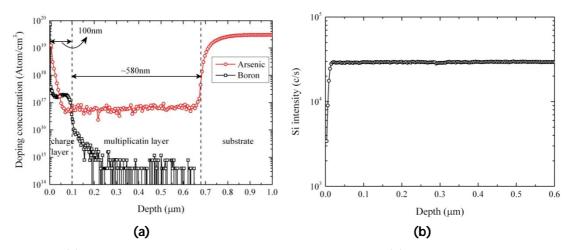

Fig. 3-6. (a) As and B doping concentrations, and (b) Si, Ge and Ga intensity at different

96 layers of wafer number 8515 (Ge thickness: 1.5 μm). These results are obtained by

SIMS measurement. The difference in doping concentration (shaded region in part (a))

with reference to the designed level (Fig. 3-5) is crucial since it greatly affects the

electric field profile across the device and therefore changes the device characteristics.

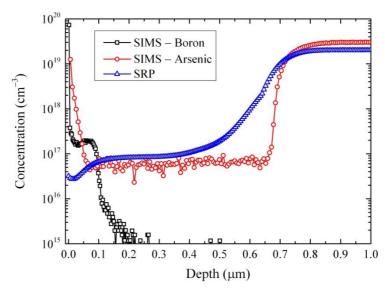

Fig. 3-7. Comparison between the SRP profile (blue triangular symbols) and the SIMS

97 result (black square and red circular symbols for arsenic and boron concentrations) of

wafer number 8515 (Ge thickness: 1.5 μm).

Fig. 3-8. (a) Arsenic and boron doping concentrations, and (b) Si intensity of different98layers of UPSW. These results are obtained by SIMS measurement.

Fig. 3-9. Comparison between the SRP profile (blue triangular symbols) and the SIMS 98 result (black square and red circular symbols for B and As concentrations) of UPSW.

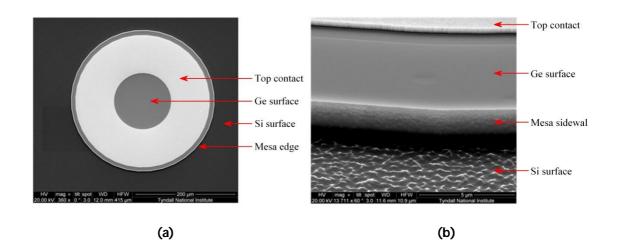

Fig. 3-10. (a) Top view, and (b) side view SEM images of the fabricated Ge/Si devices 99 showing the top contact, mesa edge and sidewall, and Si and Ge surfaces.

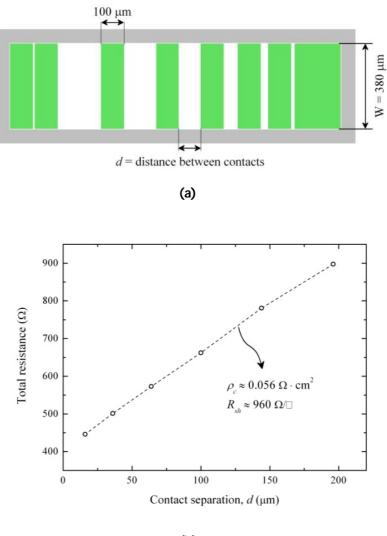

Fig. 3-11. (a) A transfer length method test structure showing the definitions of contact 101 metal bar width (W), contact separation distance (d) and the contact stripe length. (b) Plot of total resistance as a function of contact spacing, d, of wafer number 8511 (Ge thickness: 1 µm). The calculated values of sheet resistance and the specific contact

resistivity obtained by fitting the curve are also shown in part (b).

Fig. 3-12. Band diagram of the top Ge and Si layers showing the possible current flow 101 paths.

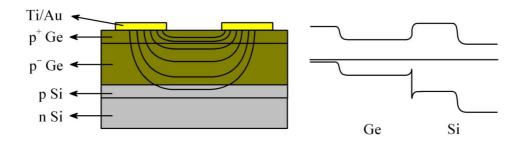

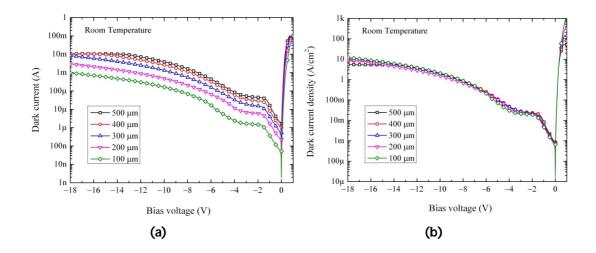

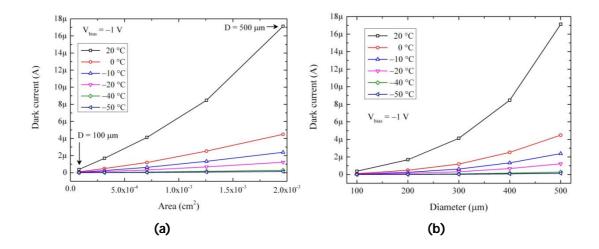

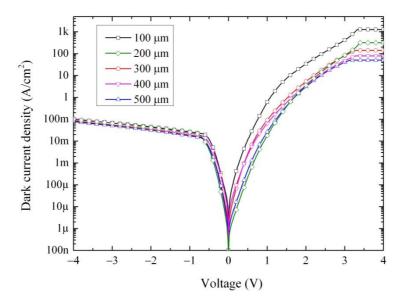

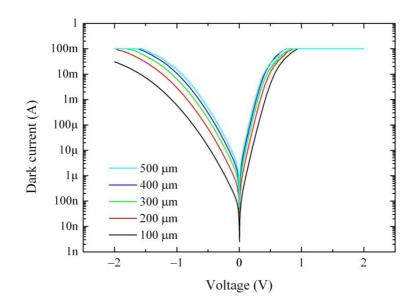

Fig. 3-13. (a) Dark current, and (b) dark current density versus bias vol tage of Ge/Si102devices from wafer number 8515 (Ge thickness: 1.5 μm) with different diameters atroom temperature. Bulk component of the current is dominant in the leakage current.

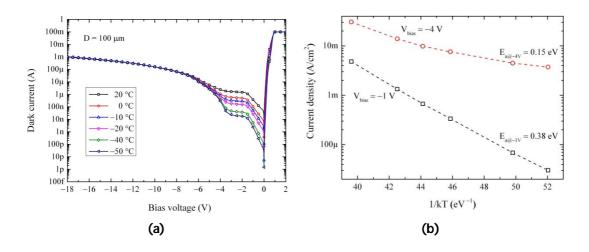

Fig. 3-14. (a) *I–V* characteristics of a 100  $\mu$ m-diameter Ge/Si device from wafer number 103 8515 (Ge thickness: 1.5  $\mu$ m) at different temperatures in dark. (b) Current density versus 1/kT at –1 V and –4 V. The value of *E*<sub>a</sub> at each bias voltage is also shown.

Fig. 3-15. Dark current of the Ge/Si devices versus (a) device area, and (b) device103diameter at different temperatures. The Ge/Si devices were made using wafer number8515 (Ge thickness: 1.5 μm).

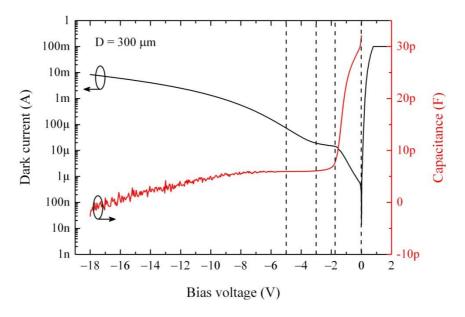

Fig. 3-16. Dark current (left axis) and capacitance (right axis) vs bias voltage of a 300 105 μm-diameter device at room temperature from wafer number 8515 (Ge thickness: 1.5 μm).

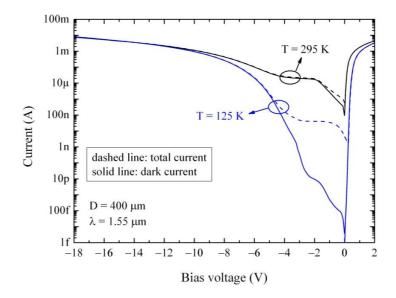

Fig. 3-17. Dark current and total current (under 1.55 μm laser illumination) of a Ge/Si 106 device with the diameter of 400 μm at two different temperatures: 125 K and 295 K.

The devices are made using wafer number 8515 (Ge thickness: 15 μm).

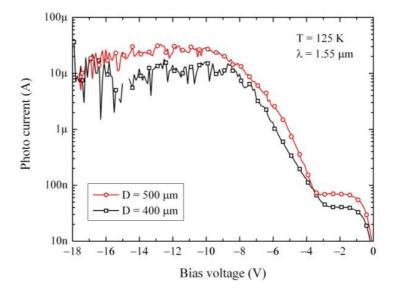

Fig. 3-18. Photo-current ( $I_{TC} - I_{DC}$ ) of a 400 µm- and a 500 µm-diameter device at 125 K. 106 The devices are made using wafer number 8515 (Ge thickness: 1.5 µm).

Fig. 3-19. Si devices were made from wafer number 8515 (Ge thickness: 1.5 μm) by107removing the germanium layer using wet etching.

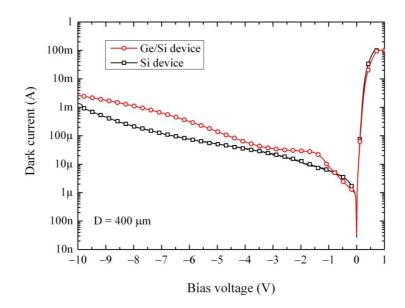

Fig. 3-20. Dark current of the Si device compared to Ge/Si device made from the same108wafer (number 8515, Ge thickness: 1.5 μm). It can be concluded that the high reversecurrent is related to Si epilayers quality.

Fig. 3-21. SEM image of (a) Si sample designed for Ge/Si detector (wafer number 8515, 108 Ge thickness: 1.5 μm), and (b) Si sample (bulk, p-type), both after being etched using KOH.

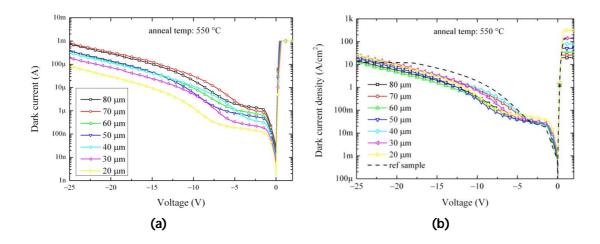

Fig. 3-22. (a) Dark current and (b) dark current density versus voltage of the annealed 110 sample at 550 °C (wafer number: 8515, Ge thickness: 1.5 μm). In part (b), the dark current density of the reference sample (not annealed) is shown for comparison.

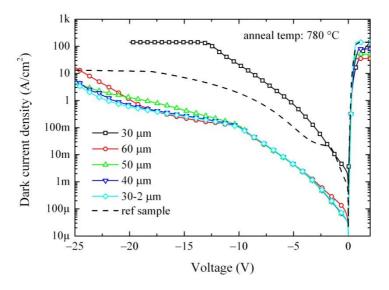

Fig. 3-23. Dark current density of the annealed sample at 780 °C for devices with110different diameters (wafer number: 8515, Ge thickness: 1.5 μm). Comparing the resultsof the two 30 μm-diameter devices shows the non-uniform effect of high temperature

anneal. The characteristic of a reference sample (not annealed) is shown by dashed line.

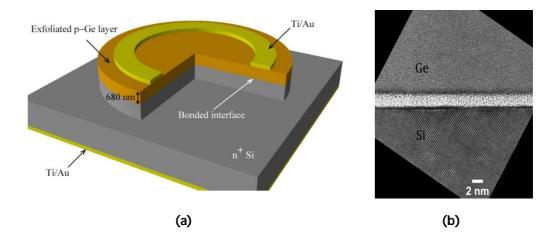

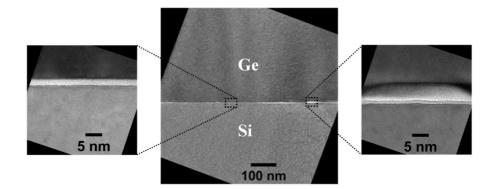

Fig. 4-1. (a) Schematic illustration of the Ge/Si diode made by hydrogen implantation 116 and layer transfer technique. (b) High resolution TEM image of the Ge/Si interface. The amorphous interfacial layer is ~2 nm thick and is uniform along the interface.

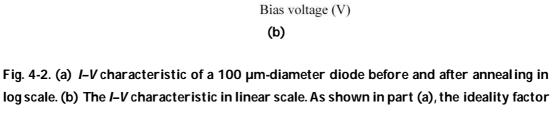

Fig. 4-2. (a) *I–V* characteristic of a 100 µm-diameter diode before and after annealing in 117 log scale. (b) The *I–V* characteristic in linear scale. As shown in part (b), the ideality factor of the diode is 5.48 before annealing and 2.28 after annealing.

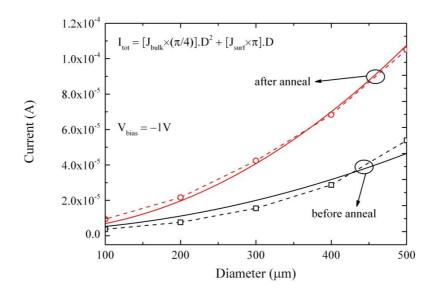

Fig. 4-3. Current versus device diameter at -1 V before and after annealing; Dashed118lines: measured data; Solid lines: fit from bulk leakage (per unit area) and surfaceleakage (per unit diameter).

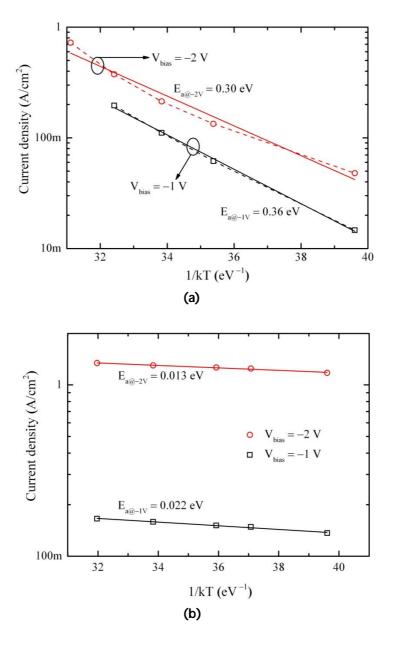

Fig. 4-4. (a) Current density versus 1/kT at –1 V and –2 V before annealing. (b) Current 119 density versus 1/kT at –1 V and –2 V after annealing. The circular and square symbols are the measured data and the solid lines are the Arrhenius-fit plots. The value of the activation energy at each bias voltage is also shown.

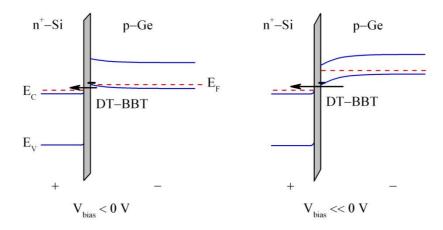

Fig. 4-5. Schematic representation of the Ge/Si band diagram illustrating the carrier120transport mechanism in reverse bias.

Fig. 4-6. Schematic representation of the Ge/Si band diagram illustrating the carrier121transport mechanism in forward bias.

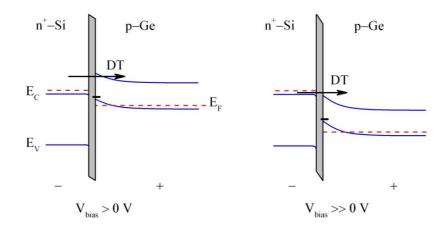

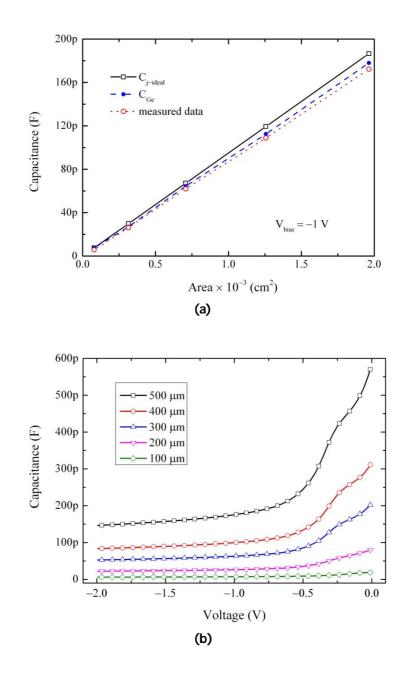

Fig. 4-7. (a) Capacitance versus device area at -1 V. Solid line: junction capacitance122calculated using the analytical formula (4-2); Dashed line: capacitance due to the120depletion region inside Ge; Dotted line: measured data. (b) C-V characteristic of diodeswith various diameters.

Fig. 5-1. High resolution TEM image of the Ge/Si interface. The two zoomed-in images 129 show the thin (~2 nm thick) interfacial layer (on the left) and the thick region (on the right).

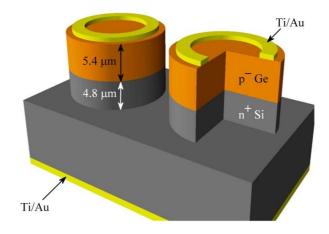

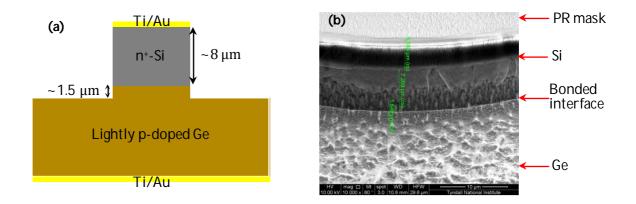

Fig. 5-2. Schematic illustration of the Ge/Si photodetectors made by the wafer bonding 129 technique followed by CMP.

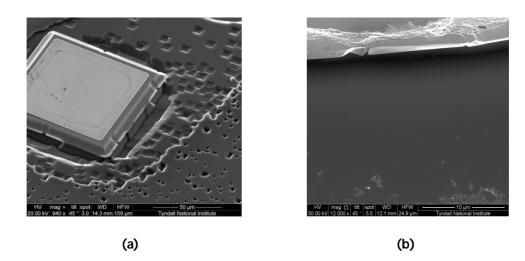

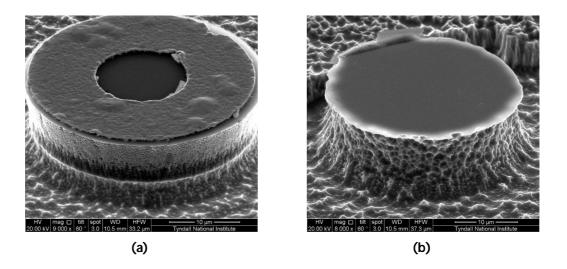

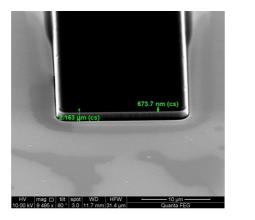

Fig. 5-3. SEM image of (a) a fabricated photodiode by direct wafer bonding, and (b) a 130 delaminated bonded pair after CMP.

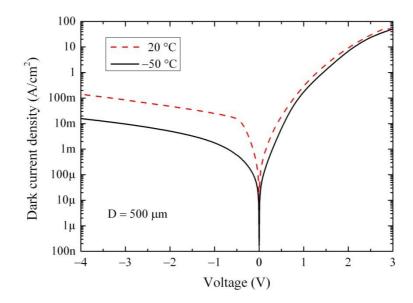

Fig. 5-4. *J–V* characteristics of a 500  $\mu$ m-diameter device at two different temperatures 131 in the dark. The dashed line is at 20 °C and the solid line is at –50 °C.

| Fig. 5-5. Dark current density of devices with different diameters which shows that the main component of the reverse current is due to the bulk (area).                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 131 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

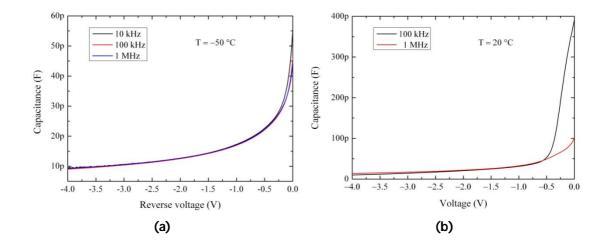

| Fig. 5-6. <i>C</i> – <i>V</i> characteristics of a Ge/Si photodetector at different frequencies at (a) $-50$ °C, and (b) 20 °C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 132 |

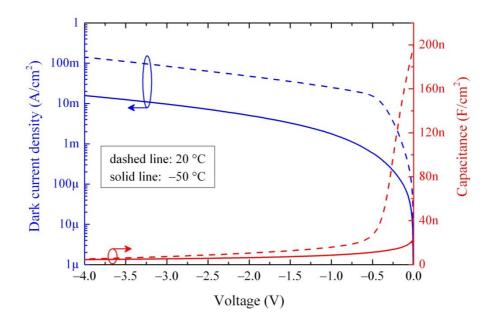

| Fig. 5-7. Dark current density versus reverse bias voltage (left axis) and $C-V$ characteristic at 100 kHz (right axis) of the Ge/Si diode. Dashed lines are at 20 °C and solid lines are at $-50$ °C.                                                                                                                                                                                                                                                                                                                                                                                                                        | 133 |

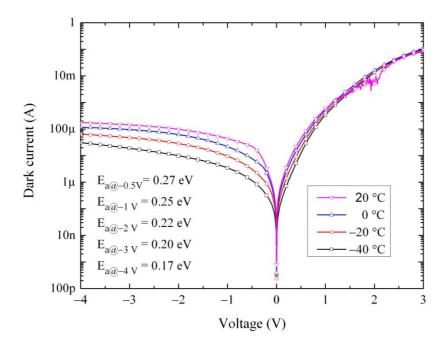

| Fig. 5-8. <i>I–V</i> characteristic of a Ge/Si diode at different temperatures. The values of activation energy ( $E_a$ ) at different reverse bias voltages are indicated in the inset.                                                                                                                                                                                                                                                                                                                                                                                                                                      | 133 |

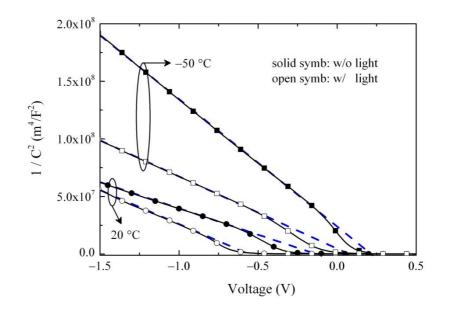

| Fig. 5-9. $1/C^2$ versus reverse bias voltage at 20 °C and -50 °C. Solid symbols: in dark;<br>Open symbols: under illumination ( $\lambda$ = 1.62 µm, P <sub>opt</sub> = 10 µW).                                                                                                                                                                                                                                                                                                                                                                                                                                              | 135 |

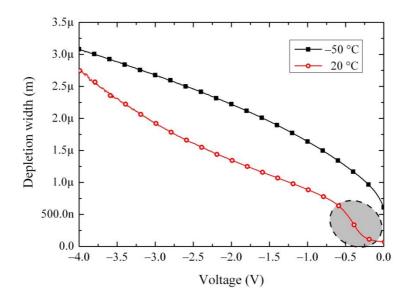

| Fig. 5-10. Depletion width as a function of reverse bias voltage at 20 °C and $-50$ °C. The shaded region illustrates the effect of charges captured by the interface traps at 20 °C.                                                                                                                                                                                                                                                                                                                                                                                                                                         | 135 |

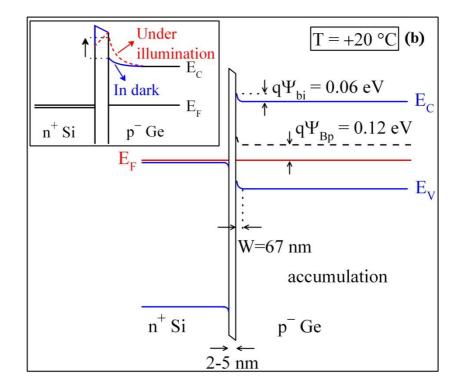

| Fig. 5-11. Schematic representation of the Ge/Si band diagram at equilibrium at (a) $-50$ °C, and (b) 20 °C. $\Psi_{bi}$ and $\Psi_{Bp}$ are the built-in potential and the Fermi potential with respect to the midgap in the bulk of p-Ge, respectively. In part (a), the Ge surface at the interface is in the "weak inversion" mode while in part (b) it is in the "accumulation" mode due to trap filling. The dashed lines in (a) and (b) are the intrinsic Fermi level. The inset of part (b) schematically illustrates the potential barrier lowering due to filling of acceptor traps by either temperature or light. | 137 |

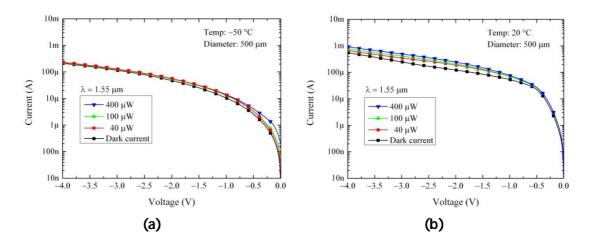

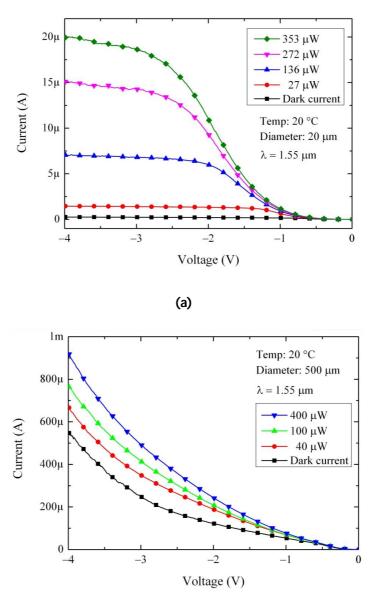

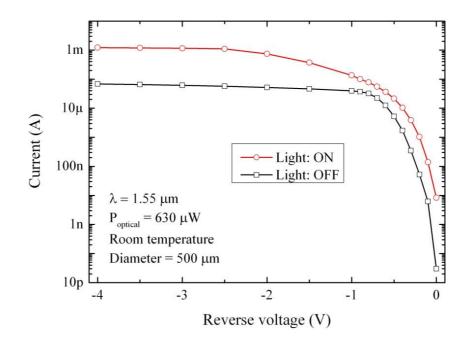

| Fig. 5-12. <i>I–V</i> characteristics of the 500 $\mu$ m-diameter Ge/Si photodetector in dark and under illumination ( $\lambda$ = 1.55 $\mu$ m) at (a) –50 °C, and (b) 20 °C.                                                                                                                                                                                                                                                                                                                                                                                                                                                | 138 |

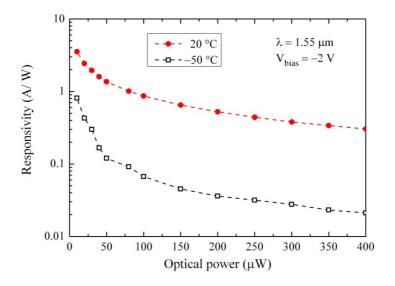

| Fig. 5-13. Responsivity of the Ge/Si photodiode versus input optical power at a wavelength of 1.55 $\mu$ m and V = -2 V at two temperatures.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 138 |

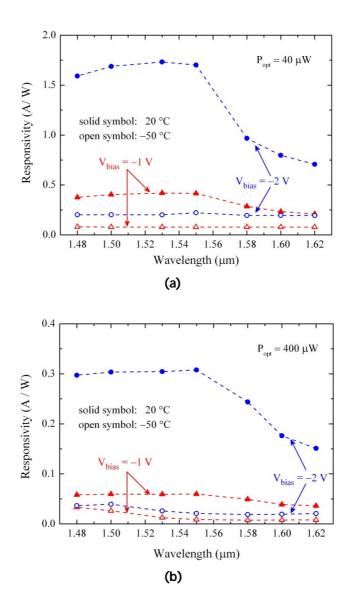

| Fig. 5-14. Responsivity as a function of wavelength at different reverse bias voltages and temperatures and at a constant optical power of (a) 40 $\mu$ W, and (b) 400 $\mu$ W.                                                                                                                                                                                                                                                                                                                                                                                                                                               | 140 |

| Fig. 5-15. <i>I–V</i> characteristics of the (a) 20 $\mu$ m-diameter, and (b) 500 $\mu$ m-diameter Ge on Si photodiodes. I <sub>TC</sub> /I <sub>DC</sub> ratio of the smaller device is larger than the large device.                                                                                                                                                                                                                                                                                                                                                                                                        | 141 |

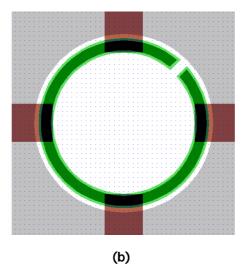

| Fig. 5-16. (a) Schematic and (b) SEM image of the <i>pn</i> junction fabricated by wafer bonding followed by CMP. The structure is circular mesa.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 142 |

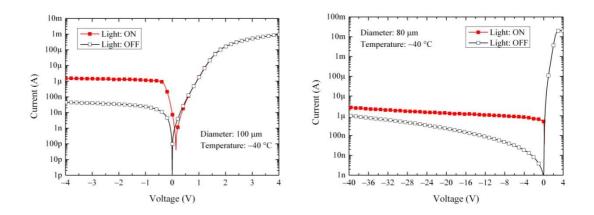

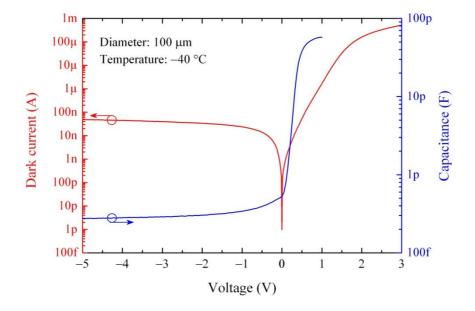

| Fig. 5-17. Dark current and total current (under microscope white light illumination) of a 100 $\mu$ m-diameter device (left) and an 80 $\mu$ m-diameter device (right) for different bias voltage ranges.                                                                                                                                                                                                                                                                                                                                                                                                                    | 143 |

| Fig. 5-18. <i>I–V</i> (left axis) and <i>C–V</i> (right axis) characteristics of the 100 $\mu$ m-diameter device at –40 °C.                                                                              | 143 |

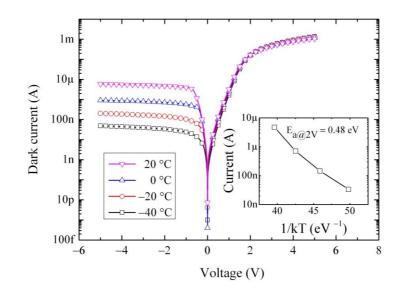

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 5-19. Dark current of the 100 $\mu$ m-diameter device at different temperatures. The inset shows the considerable dependence of current on temperature and also shows the activation energy at 2 V. | 144 |

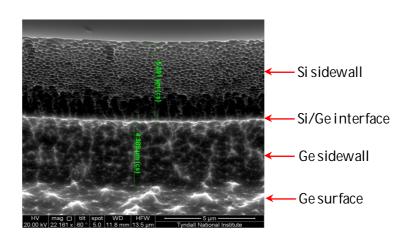

| Fig. 5-20. SEM image of the Si-on-Ge cross section (circular mesa) made by wafer bonding.                                                                                                                | 144 |

| Fig. 5-21. <i>I–V</i> characteristics of the 500 $\mu$ m-diameter Si on Ge photodiode.                                                                                                                   | 145 |

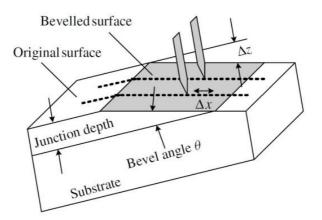

| Fig. A2-1. Spreading resistance bevelled sample with probes - the probe path is shown by the dashed line.                                                                                                | 158 |

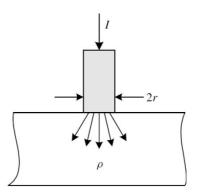

| Fig. A2-2. A cylindrical contact of diameter 2 <i>r</i> to a semiconductor. The arrows represent the current flow.                                                                                       | 158 |

| Fig. A3-1. Optical image of the structured Si wafer designed for Ge/Si detector at two different magnifications. The scale bar in (a) is 200 $\mu$ m and in (b) is 20 $\mu$ m.                           | 160 |

| Fig. A3-2. Schematic of the UPSW structure designed for Ge/Si detector.                                                                                                                                  | 160 |

| Fig. A3-3. <i>I–V</i> characteristics of the devices made using the UPSW.                                                                                                                                | 161 |

| Fig. A4-1. SEM images of the etched Ge sample using $NH_4OH:H_2O_2:H_2O$ after 45 minutes.                                                                                                               | 162 |

| Fig. A4-2. SEM images of germanium sample after 1 min of Run 6. The image on the right shows the surface of Ge after etching.                                                                            | 163 |

| Fig. A4-3. SEM images of germanium sample after 2 min of Run 7. The image on the right shows the surface of Ge after etching.                                                                            | 164 |

| Fig. A5-1. Schematic cross-sectional view of different layers of the epitaxial Ge/Si APDs.                                                                                                               | 165 |

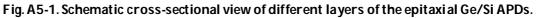

| Fig. A5-2. Mask layout of Ge/Si devices at (a) lower magnification, and (b) higher magnification (one device).                                                                                           | 166 |

# List of tables

| Table 1-1. Summary of germanium growth techniques. TDD: Threading Dislocation Density.                                                                                                                                                                                                                                                                                                                                               | 35  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 1-2. Summary of the performance of germanium photodetectors. R:<br>Responsivity; $\lambda$ : wavelength; $\eta$ : quantum efficiency; BW: Bandwidth; NI: Normal<br>Incident; WG: Waveguide; MSM: Metal Semiconductor Metal; GBP: Gain Bandwidth<br>Product; SACM APD: Separate Absorption, Charge, and Multiplication Avalanche Photo<br>Diode.                                                                                | 46  |

| Table 2-1: Parameters used to model interface traps in Ge/Si APD.                                                                                                                                                                                                                                                                                                                                                                    | 70  |

| Table 2-2: Effects of donor trap density on the APD bandwidth.                                                                                                                                                                                                                                                                                                                                                                       | 83  |

| Table 2-3: Effects of acceptor trap density on the APD bandwidth.                                                                                                                                                                                                                                                                                                                                                                    | 83  |

| Table 3-1: Wafer number and the corresponding Ge layer thickness.                                                                                                                                                                                                                                                                                                                                                                    | 92  |

| Table 4-1. Summary of different ion implantation conditions and heat treatments.<br>Abbreviation definitions are as follows – H <sub>2</sub> : Hydrogen; He: Helium; SOI: SiOn<br>Insulator; GOI: Ge On Insulator; SGOI: SiGe On Insulator; sSOI: strained Si On Insulator;<br>RT: Room Temperature; h: hour; min: minute.                                                                                                           | 114 |

| Table 5-1. Performance comparison of different vertical illuminated Ge/Si<br>photodetectors. Abbreviation definitions are as follows – CVD: Chemical Vapour<br>Deposition; RP: Reduced Pressure; UHV: Ultra High Vacuum; LP: Low Pressure; MBE:<br>Molecular Beam Epitaxy; LEPE: Low Energy Plasma Enhanced; MHAH: Multiple<br>Hydrogen Anneal Heteroepitaxy; QD: Quantum Dot; ARC: Anti Reflection Coating; RC:<br>Resonant Cavity. | 146 |

| Table A4-1. Effects of experimental setup parameters and plasma gases on Ge etch rate.<br>ER: Etch Rate; S: Selectivity.                                                                                                                                                                                                                                                                                                             | 163 |

| Table A4-2: Si and Ge dry etch results using SF <sub>6</sub> and C <sub>4</sub> F <sub>8</sub> . ER: Etch Rate; S: Selectivity; PR: Photoresist.                                                                                                                                                                                                                                                                                     | 164 |

| Table A5-1: Wafer number and the corresponding Ge layer thickness.                                                                                                                                                                                                                                                                                                                                                                   | 165 |

## Chapter 1: Introduction and literature review

### 1.1. Introduction

In order to achieve high performance and low-cost optical links, it is desirable to integrate optical components such as photodetectors, light sources and modulators with the silicon technology. Silicon is the base material for electronic technologies and is emerging as a very attractive platform for photonic integrated circuits (PICs). As PICs and other optical networks are moving toward the consumer market, developing low-cost and manufacturable optical components integrated on a chip with other electrical components is crucial. Many of these components have been demonstrated by integrating the discrete optical devices in existing silicon integrated circuits. Considerable research has been directed towards this challenge for highly integrated modulators [1], silicon-on-insulator (SOI) waveguide technology [2], and silicon-germanium based photodetectors [3]. One major application of such photodetectors is in optical communication systems. Another application is in infra-red wavelength cameras.

The basic advantages of a silicon-based approach to fabricate photonic devices are the potential to lower cost and easier manufacturing process for mass-production. Most silicon-based optical receivers in the past operated at  $\lambda < 1 \,\mu\text{m}$  (band gap of silicon). In order to extend the operating wavelength to longer wavelengths, i.e., 1.3  $\mu\text{m}$  and 1.55  $\mu\text{m}$ , absorbing materials with smaller band gap, such as germanium, is required to be integrated with silicon.

#### 1.1.1. Germanium for long wavelength detection

Both InGaAs and Ge have high absorption at  $1.3 \,\mu$ m which makes them suitable for long wavelength photodiodes. Fig. 1-1 shows the optical absorption coefficient of germanium and silicon as a function of wavelength. The high optical absorption coefficient at 1.3  $\mu$ m and 1.55  $\mu$ m makes germanium suitable for photodetection.

Fig. 1-1. Absorption coefficients of various semiconductors - taken from Dosunmu [4].

Fig. 1-2. Drift mobility of (a) Si, (b) Ge, and (c) GaAs at 300 K versus impurity concentration - taken from Sze [5].

Although high performance photodetectors are widely available using III-V semiconductors, the use of germanium is advantageous in terms of lower cost of fabrication and compatibility with silicon complementary metal oxide semiconductor (CMOS) process using the existing mature silicon manufacturing infrastructure. Another attractive feature of Ge is its low temperature processing capability. In addition, germanium is promising for other applications such as microwave photonic systems that require high photocurrent [6]. Germanium has also higher carrier mobility than silicon for both electrons ( $\sim$  3x) and holes ( $\sim$  4x). As shown in Fig. 1-2, the hole mobility of germanium is even higher than that of GaAs.

#### 1.1.2. Characteristics of optical receiver

Two of the most important characteristics of optical receivers are their sensitivity and speed; both depend upon the performance of the integrated detectors. A high performance photodiode must provide high quantum efficiency, low leakage current and high speed. The quantum efficiency,  $\eta$ , for a photodetector is a measure of how many electron-hole pairs are collected per incident photon. The quantum efficiency can be expressed as:

$$\eta = (1 - R) (1 - e^{-\alpha d}), \tag{1-1}$$

where *R* is the reflectivity of the material,  $\alpha$  is the absorption coefficient of the absorption region, and *d* is the absorption layer thickness.

The dark current of a photodetector is the current which is generated in the absence of light and depends mostly on the device structure and the material quality. Usually, this current is high for materials with narrow bandgap, and therefore, high intrinsic carrier concentration. For lattice-mismatched materials, the large density of dislocations may be the dominant component of the dark current. In an optical receiver system, the dark current of the photodiode contributes to the noise of the receiver and hence the signal-to-noise ratio of the system.

The speed of a photodetector defines how fast the photodetector responds to a modulated optical input. The speed is determined by both the RC and the transit-time components. For normal-incidence photodiodes there is a trade off between the speed and the quantum efficiency. In order to achieve high quantum efficiency, a thick absorption region is required, which on the other hand, increases the distance that the

photo-generated carriers must travel and hence limits the device speed. This issue can be greatly alleviated if a waveguide configuration is used. In this configuration, light absorption occurs along the propagation axis of an optical mode parallel to the wafer surface, therefore converting the thickness requirement into a waveguide length requirement.

#### 1.2. Ge/Si photonic and electronic integrated circuits

Over the past decades, conventional optical components were typically made of III–V compound materials such as gallium arsenide (GaAs) and indium phosphide (InP) due to their excellent light emission and absorption properties. Unfortunately, compound-semiconductor devices are generally too complicated to process and costly to implement in optical interconnects. In search for a cost-effective solution, Si photonics emerges to hold great promise for its inexpensive material and its compatibility with current CMOS fabrication technology. Recent advancements have also shown that silicon is a viable optical material suitable for high-bandwidth data communication applications. In addition, the feasibility of converging photonic and electronic integrated circuits all on a single chip makes it an extremely attractive option to extend the performance roadmap as driven by Moore's Law.

There is a considerable research work in the field of silicon photonics in particular in the integration of long wavelength germanium photodetectors with silicon. For example, a low-power, short-wavelength eight-channel monolithically integrated photoreceiver array, based on SiGe/Si heterojunction bipolar transistors was demonstrated by Qasaimeh *et al.* from University of Michigan, Ann Arbor in 2000 [7]. The photodiode and transistors are grown by molecular beam epitaxy in a single step. The p-i-n photodiode exhibits a responsivity of 0.3 A/W and a bandwidth of 0.8 GHz at  $\lambda = 0.88 \ \mu m$ .

Design and fabrication of a monolithically integrated evanescent-coupled germaniumon-silicon-on-insulator (SOI) photodetector and CMOS circuits on common SOI platform using an "electronic-first and photonic-last" integration approach are reported in 2010 by Prof. Kwong's group in A\*STAR, Singapore [8, 9]. A highperformance detector with an integrated Si waveguide was demonstrated on ~500 nm thick epitaxial germanium absorbing layer which was selectively grown by ultrahigh vacuum chemical vapour deposition (UHV-CVD) technique on an ultrathin SOI

25

substrate (Fig. 1-3). Performance metrics of photodetector designs featuring vertical and lateral PIN configurations were investigated (Fig. 1-4). High responsivity of ~0.92 A/W was obtained in both detector designs for a wavelength of 1550 nm, which corresponds to a quantum efficiency of ~73%. Eye patterns measurement confirms the achievement of high-speed and low-noise photodetection at a bit rate of 8.5 Gb/s.

Fig. 1-3. (a) SEM micrograph of a Si CMOS inverter circuit on SOI platform. (b) SEM micrograph of a monolithically integrated Ge p-i-n photodetector with a Si photonic waveguide [8].

Fig. 1-4. (a) SEM micrograph showing an evanescent coupled Ge photodetector featuring vertical p-i-n configuration. The width W and length L of the detector is 8 and 100  $\mu$ m, respectively. (b) Ge photodetector design with a lateral p-i-n configuration. The width W and length L of this detector is 20 and 100  $\mu$ m, respectively [8].

Kopp *et al.* from LETI, France in 2011 demonstrated high-density germanium photodiode arrays integrated on top of a dummy CMOS 200-mm silicon wafer by depositing germanium using RP-CVD at temperatures > 700 °C (Fig. 1-5) [10]. Using a conventional available semiconductor fabrication line, the target specifications are reached with a yield exceeding 99% for several thousands of tested photodiodes with respect to bandwidth, responsivity, and dark current. A very low dark current density in the range of 7 mA/cm<sup>2</sup> is obtained. A bandwidth above 9 GHz is reached with a 30- $\mu$ m diameter photodiode. At a wavelength of 850 nm a responsivity of 0.48 A/W for 350-nm thick Ge layer and 0.56 A/W for 650-nm thick Ge layer is measured.

Fig. 1-5. Fabricated 30-µm mesa diameter photodiode array. Vias connect the photodiode pads to the embedded metal layer below from the CMOS-based silicon wafer [10].

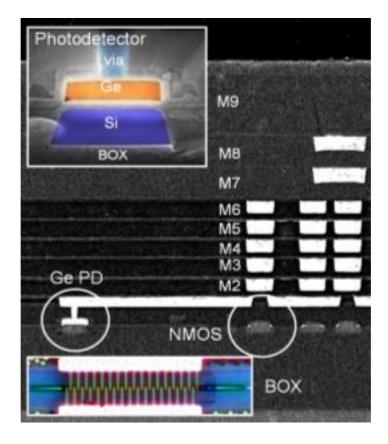

Very recently in Dec. 2012, Assefa *et al.* from IBM demonstrated the first sub-100 nm technology that allows the monolithic integration of optical modulators and germanium photodetectors as features into a current 90 nm-base high performance logic technology node [11]. The electrical eye diagram of the receiver, measured with 1.54  $\mu$ m light modulated at 25 Gbps, shows good performance. To yield deeply scaled nanophotonics features, a high resistivity SOI substrate with 2  $\mu$ m BOX is utilized as a base for 90 nm CMOS-Integrated Nano-Photonics (CINP) technology (see Fig. 1-6).

Fig. 1-6. Cross-sectional SEM view of a 90 nm CMOS-Integrated Nano-Photonics (CINP) metal stack with Ge PD embedded into the front-end. Zoomed-in image of a PD is shown on top left. Optical microscope top-down image is shown on the low left [11].

## 1.3. Ge/Si integration techniques

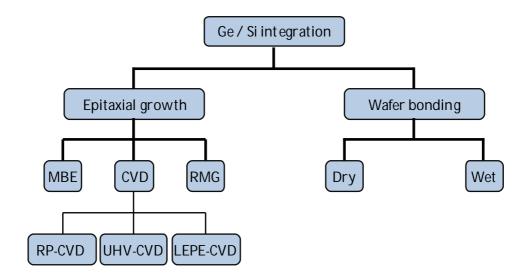

There are two major techniques to integrate crystalline germanium with silicon. As shown in Fig. 1-7, these methods are epitaxial growth and wafer bonding. Sections 1.3.1 and 1.3.3 review the progress that has been made with regard to each technique. A combination of hetero-epitaxy and wafer bonding has also been investigated for this purpose [10, 12].

Fig. 1-7. Various techniques that have been used for the integration of germanium with silicon. MBE: Molecular Beam Epitaxy; CVD: Chemical Vapour Deposition; RMG: Rapid Melting Growth; RP-CVD: Reduced Pressure CVD; UHV-CVD: Ultra High Vacuum CVD; LEPE-CVD: Low Energy Plasma Enhanced CVD.

#### 1.3.1. Ge/Si integration by epitaxy

Despite the potential advantages of Ge, the growth techniques and material quality of Ge on Si have limited the device performance and the potential for integration with Si ICs. The greatest challenge for high quality germanium epitaxy on silicon is the 4.2% lattice mismatch between the two materials. The misfit-related strain of the Ge film is relaxed by formation of a micro-rough surface up to a critical thickness of a few monolayers. For thicker Ge films the misfit is relieved by forming dislocation network in the germanium epitaxial layer originated from the Ge/Si interface. The difference between the Si and Ge thermal expansion coefficients ( $\alpha_{Si} = 3.55 \times 10^{-6} \text{ K}^{-1}$  and  $\alpha_{Ge} = 7.66 \times 10^{-6} \text{ K}^{-1}$  [13]) also leads to tensile strain during cooling down from the growth temperature which results in microcracks or residual tensile strain and dislocations which could be an advantage in terms of narrowing the band gap [14].

High density of threading dislocations affects the performance of normal incident germanium devices because of the recombination centres that are introduced along these dislocations. For the purpose of fabricating surface normal Ge photodetectors integrated with Si, the thickness of the Ge absorption layer has to be much larger than the critical thickness. Various techniques have been utilized to achieve low defect density in the Ge film on Si; such as: (i) graded buffer layers, (ii) selective growth, (iii) two-step Ge growth (low/high temperature), (iv) post-growth cyclic thermal annealing, or combination of some of them.

## 1.3.1.1. Molecular Beam Epitaxy (MBE)

The first approach to overcome the lattice mismatch and to achieve high-quality Ge epilayer on Si is to use compositionally graded SiGe buffer layer(s). The first successful approach was reported by Luryi *et al.* from AT&T Bell Laboratories in 1984 where a graded SiGe buffer layer grown in a *MBE* chamber was used to reduce the threading dislocation density in the Ge layer [15]. The graded buffer layers consist of 10% Ge per 1  $\mu$ m, which results in a very thick (10  $\mu$ m) buffer layer for Ge content varying from 0% to 100%. This approach has led to the Ge film with low threading dislocations of < 2 × 10<sup>6</sup> cm<sup>-2</sup>. In view of the integration with Si CMOS circuits, the thick SiGe buffer layer makes integration difficult.

Compositionally graded  $Ge_xSi_{1-x}$  layers on Si at 900 °C with both *MBE* and rapid thermal chemical vapour deposition techniques are grown in 1991 by Fitzgerald *et al.* from AT&T Bell Laboratories [16].  $Ge_xSi_{1-x}$  cap layers grown on these graded layers showed low threading-dislocation densities (4 × 10<sup>5</sup> cm<sup>-2</sup> and 3 × 10<sup>6</sup> cm<sup>-2</sup> for x = 0.23 and x = 0.50, respectively).

Malta *et al.* from North Carolina State University in 1991 reported on a heteroepitaxial Ge on Si grown using *MBE* at a temperature of 900 °C [17]. Their results reveal a highly faceted interface, indicating localized Ge melting and subsequent local alloying with Si which leads to extensive threading dislocation confinement near the Ge/Si interface. Etch pit density measurements obtained on Ge heteroepitaxial films showed the density of dislocations to be as low as 10<sup>5</sup> cm<sup>-2</sup>.

In 2001, Liu *et al.* from UCLA reported high-quality Ge-on-Si using solid-source *MBE* [18]. They used a SiGe graded buffer. A relaxed Ge film on a  $4-\mu$ m-thick graded buffer was grown and shown to have a threading dislocation density of  $5.4 \times 10^5$  cm<sup>-2</sup>.

Jutzi *et al.* in 2005 have utilized an ultrathin virtual substrate for the purpose of matching the 4% larger lattice constant of Ge to Si. Matching is obtained by misfit dislocations. A rather high density of threading dislocations in the order of 10<sup>8</sup> cm<sup>-2</sup> is

generated by the thin ungraded buffer by *MBE*. In the next growth step at 300 °C, a fully strain relaxed 300 nm intrinsic region is deposited [19].

### 1.3.1.2. Ultrahigh Vacuum Chemical Vapour Deposition (UHV-CVD)