| Title                       | Metacomputing on clusters augmented with reconfigurable hardware                                                          |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Author(s)                   | Healy, Philip D.                                                                                                          |

| Publication date            | 2006-05                                                                                                                   |

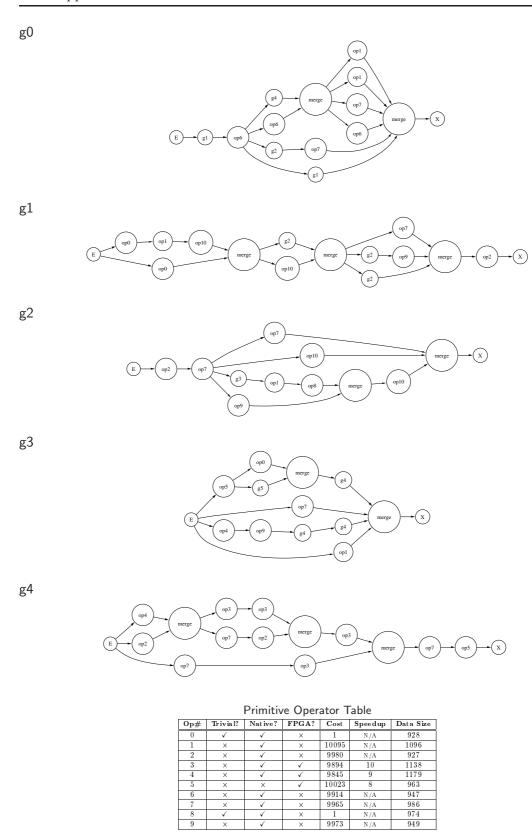

| Original citation           | Healy, P. D. 2006. Metacomputing on clusters augmented with reconfigurable hardware. PhD Thesis, University College Cork. |

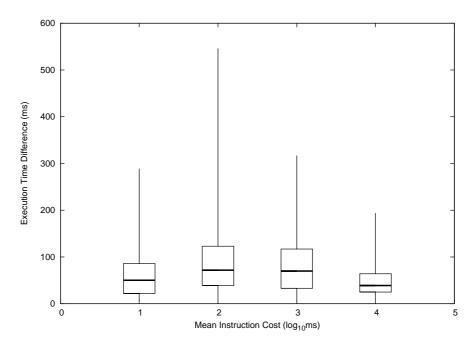

| Type of publication         | Doctoral thesis                                                                                                           |

| Link to publisher's version | http://library.ucc.ie/record=b1551998~S0 Access to the full text of the published version may require a subscription.     |

| Rights                      | © 2006, Philip Healy http://creativecommons.org/licenses/by-nc-nd/3.0/                                                    |

| Item downloaded from        | http://hdl.handle.net/10468/803                                                                                           |

Downloaded on 2017-02-12T10:54:23Z

# Metacomputing on Clusters Augmented with Reconfigurable Hardware

by

Philip D. Healy, B.Sc.

#### **THESIS**

Presented to the Faculty of Science National University of Ireland, Cork

for the Degree of

Doctor of Philosophy

May 2006

# Acknowledgements

First and foremost, I would like to thank my family and friends for their ongoing support and encouragement. In particular, my parents have helped me in countless ways through many years of education; I couldn't have done it without them. Special thanks are also due to my supervisor, Prof. John Morrison, for his tireless assistance and endless patience during all stages of my postgraduate studies, from suggesting the idea of a Ph.D. through to preparation for the thesis defence. Thank you John.

Although all of my colleagues at the CUC, past and present, deserve credit for creating a work environment that is both enjoyable and interesting, several deserve special mention for being of particular assistance. Padraig O'Dowd collaborated directly on a number of the projects described in this thesis as well as several publications that subsequently arose. Brian Clayton patiently answered countless technical questions and also found time to administer the FPGA cluster despite having almost endless work commitments of his own. Thomas Quillinan was the first to propose a Condensed Graphs implementation of RC5 key search, and answered many questions over the years on a variety of topics. The friendly race to the finish between Tom and I provided a spur whenever it seemed like the end would never come; I hope that our arrangement was of similar benefit to him. A debt of gratitude is owed to Daithí Ó Crualaoich for his assistance with mathematical notation as well as many helpful corrections and suggestions. Finally, I would like to thank Dave Power, James Kennedy and Keith Power for our many lunchtime chats. Apart from providing lively conversation, their collective wisdom and experience was of enormous benefit while preparing this thesis.

# Contents

| A        | Acknowledgements       |         |                                                      | 1  |

|----------|------------------------|---------|------------------------------------------------------|----|

| 1        | Inti                   | oducti  | ion                                                  | 5  |

|          | 1.1                    | Cluste  | er Computing                                         | 6  |

|          |                        | 1.1.1   | Programming Models for Cluster Computing             | 7  |

|          | 1.2                    | Reconf  | figurable Computing                                  | 11 |

|          |                        | 1.2.1   | Programmable Logic                                   | 12 |

|          |                        | 1.2.2   | Benefits and Limitations of Reconfigurable Computing | 14 |

|          |                        | 1.2.3   | Reconfigurable Computing Topologies                  | 16 |

|          |                        | 1.2.4   | Creating FPGA Configurations                         | 18 |

|          | 1.3                    | Augme   | enting Clusters with Reconfigurable Hardware         | 21 |

|          | 1.4                    | Paralle | el Computing Metrics                                 | 23 |

|          | 1.5                    | Resear  | rch Motivation and Objectives                        | 25 |

|          |                        | 1.5.1   | Shortcomings of Current Techniques                   | 25 |

|          |                        | 1.5.2   | Research Question and Thesis Overview                | 27 |

| <b>2</b> | $\mathbf{A}\mathbf{R}$ | C: A D  | Distributed Reconfigurable Metacomputing System      | 29 |

|          | 2.1                    | Design  | Philosophy                                           | 29 |

|          | 2.2                    | System  | n Overview                                           | 32 |

|          |                        | 2.2.1   | Compile-time Environment                             | 32 |

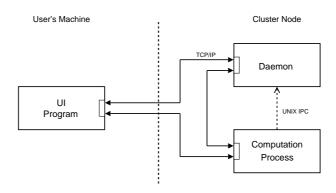

|          |                        | 2.2.2   | Runtime Environment                                  | 34 |

|          | 2.3                    | The C   | ondensed Graphs Model of Computation                 | 36 |

|          | 2.4                    | XML I   | Definition Files                                     | 36 |

|          | 2.5                    | The C   | ondensed Graphs Compiler                             | 44 |

|          | 2.6                    | The A   | RC User Interface Program                            | 46 |

|          |                        | 2.6.1   | Executing Applications                               | 47 |

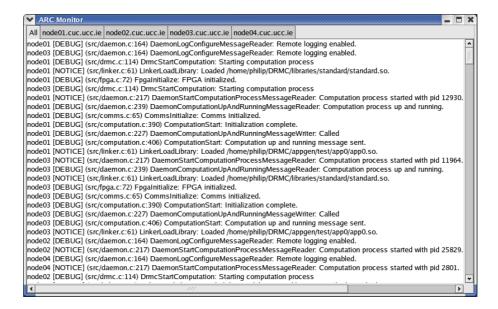

|          |                        | 2.6.2   | Monitoring Applications                              | 50 |

|          | 2.7                    | The A   | RC Daemon                                            | 50 |

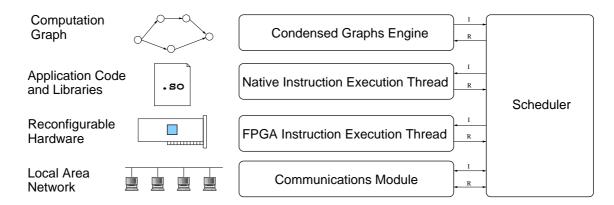

|          | 2.8                    | Compi   | utation Process Architecture                         | 51 |

0.0 CONTENTS 3

|   |     | 2.8.1                                             | Condensed Graphs Engine                                        | 54  |  |

|---|-----|---------------------------------------------------|----------------------------------------------------------------|-----|--|

|   |     | 2.8.2                                             | Scheduler                                                      | 55  |  |

|   |     | 2.8.3                                             | Native and FPGA Instruction Execution Threads                  | 56  |  |

|   |     | 2.8.4                                             | Communications Module                                          | 57  |  |

|   | 2.9 | Applie                                            | cation Development                                             | 59  |  |

| 3 | An  | Exam                                              | ple ARC Application                                            | 61  |  |

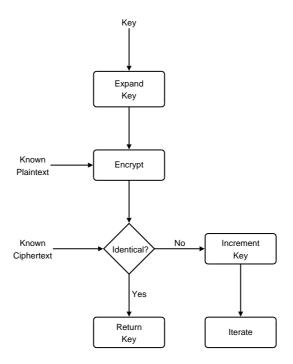

|   | 3.1 | Crypt                                             | ographic Key Search                                            | 61  |  |

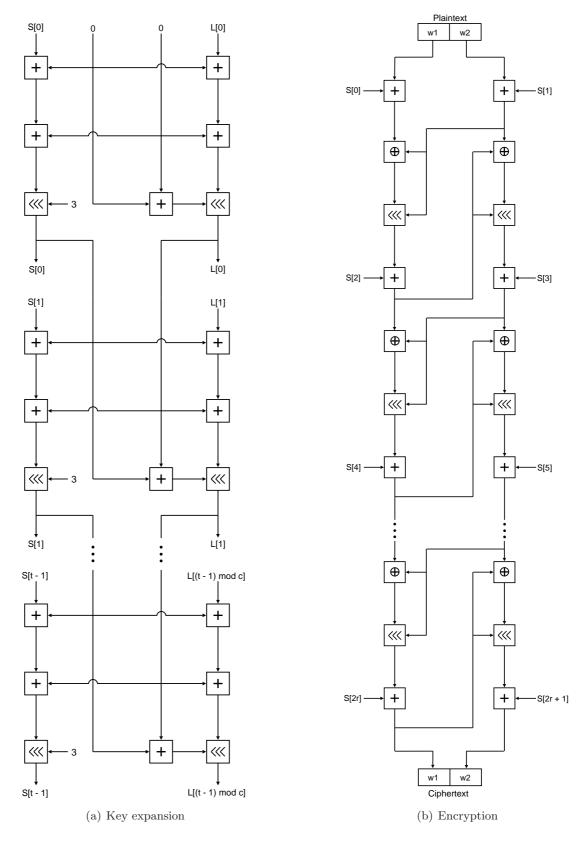

|   | 3.2 | The R                                             | RC5 Encryption Algorithm                                       | 63  |  |

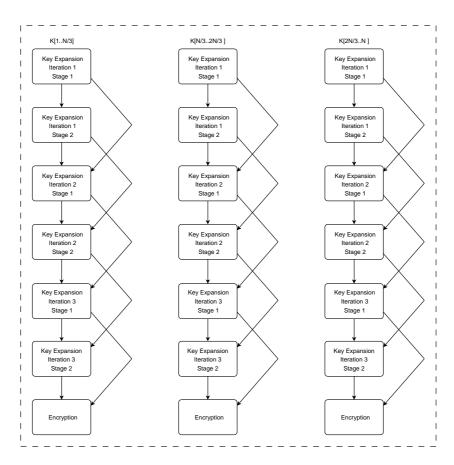

|   | 3.3 | Develo                                            | opment of the Hardware Implementation                          | 65  |  |

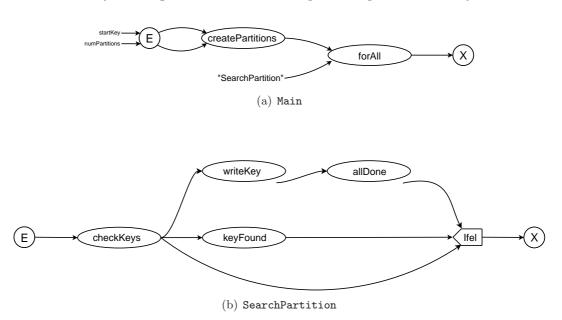

|   | 3.4 | Develo                                            | opment of the ARC Application                                  | 67  |  |

| 4 | Per | forma                                             | nce Model of the ARC Runtime Environment                       | 71  |  |

|   | 4.1 | Applie                                            | cation Generation                                              | 71  |  |

|   |     | 4.1.1                                             | Generation of Primitive Operators                              | 72  |  |

|   |     | 4.1.2                                             | Generation of Graph Definitions                                | 75  |  |

|   |     | 4.1.3                                             | Application Output                                             | 77  |  |

|   | 4.2 | Modif                                             | fications to ARC to Support Performance Model Development      | 80  |  |

|   | 4.3 | Develo                                            | opment of the Performance Model                                | 81  |  |

|   |     | 4.3.1                                             | Approximating Native Instruction Completion Cost               | 82  |  |

|   |     | 4.3.2                                             | Approximating FPGA Instruction Completion Cost                 | 88  |  |

|   |     | 4.3.3                                             | Approximating Instruction Delegation Overhead                  | 91  |  |

|   | 4.4 | Estim                                             | ating Minimum Instruction Completion Cost                      | 95  |  |

|   | 4.5 | Benefits and Limitations of the Performance Model |                                                                |     |  |

| 5 | Dev | velopm                                            | ent of the ARC Load Balancing Framework                        | 98  |  |

|   | 5.1 | Identi                                            | fication of ARC Load Balancing Requirements                    | 99  |  |

|   |     | 5.1.1                                             | Taxonomy of Dynamic Load Balancing Algorithms                  | 100 |  |

|   |     | 5.1.2                                             | Classification of Required Load Balancing Behaviour            | 101 |  |

|   | 5.2 | Develo                                            | opment of Basic Load Balancing Framework                       | 102 |  |

|   |     | 5.2.1                                             | Candidate Load Categorization Algorithms                       | 105 |  |

|   |     | 5.2.2                                             | Candidate Remote Processor Selection Algorithms                | 106 |  |

|   |     | 5.2.3                                             | ARC Modifications to Support Load Balancing Experimentation $$ | 107 |  |

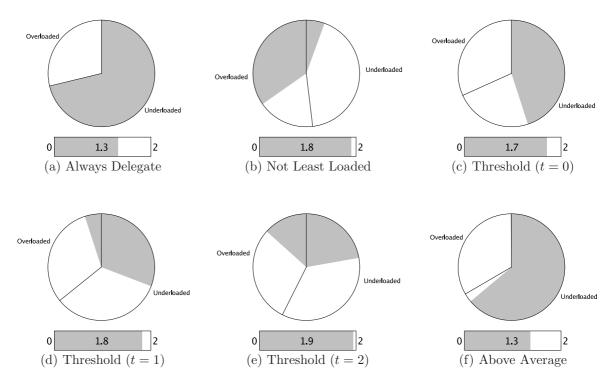

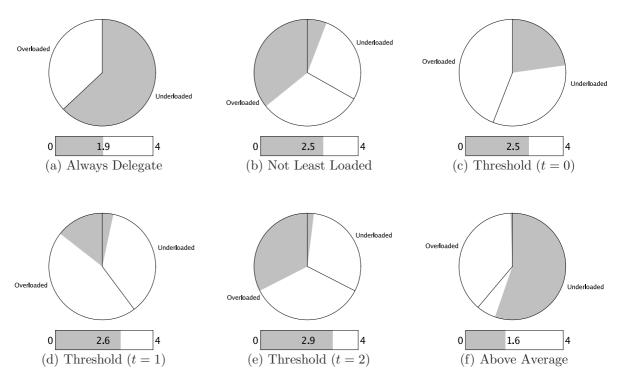

|   |     | 5.2.4                                             | Evaluation of Load Categorization Algorithms                   | 110 |  |

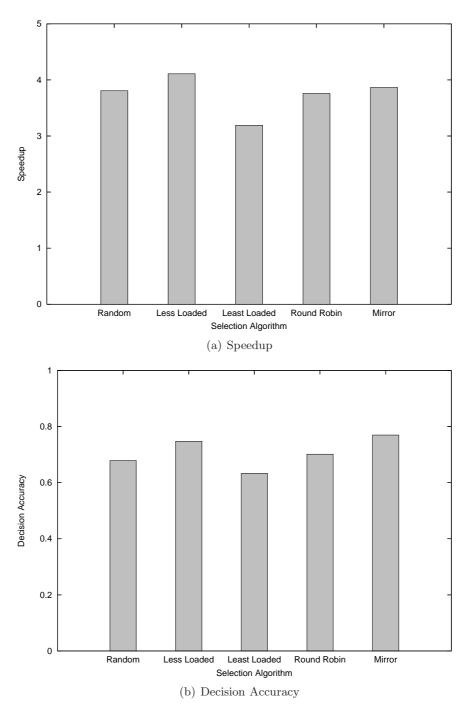

|   |     | 5.2.5                                             | Evaluation of Remote Processor Selection Algorithms            | 119 |  |

|   | 5.3 | Frame                                             | ework Optimizations                                            | 121 |  |

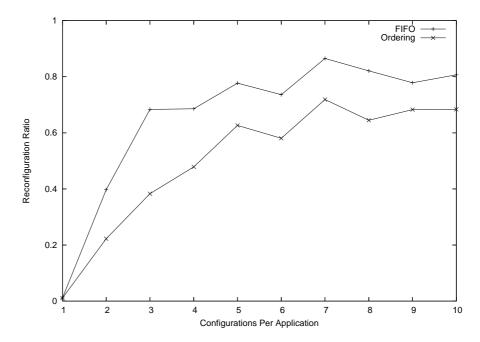

|   |     | 5.3.1                                             | FPGA Instruction Queue Ordering                                | 122 |  |

|   |     | 5.3.2                                             | Incorporation of Triviality Information                        | 124 |  |

| 0.0 CONTENTS | 4 |

|--------------|---|

|--------------|---|

|    | _    | 5.3.3 Reassignment of Instructions with Dual Implementations |     |

|----|------|--------------------------------------------------------------|-----|

| 6  | Con  | clusions and Future Work                                     | 133 |

|    | 6.1  | Conclusions                                                  | 133 |

|    |      | 6.1.1 Future Prospects for the Field                         | 134 |

|    | 6.2  | Future Work                                                  | 135 |

|    | 6.3  | Afterword                                                    | 136 |

| ъ. | 1 1. | raphy                                                        | 138 |

## Chapter 1

## Introduction

Despite the low price and ever increasing capability of commodity desktop computing hardware, a strong demand still exists in many quarters for computing power beyond that which can be delivered by the desktop PC. Examples of performance-hungry computer applications include 3D image rendering, large-scale simulations and computational biology. Users wishing to execute applications such as these could wait for Moore's Law [1] to deliver better-performing commodity hardware sometime in the future, but this approach is unsatisfactory in many situations, particularly when execution times run to days or even weeks.

An alternative approach is to turn to the field of *High Performance Computing*, i.e., the use of specialized architectures or an aggregation of commodity computing resources to improve application performance. The most common method of achieving higher performance is known as *Parallel Computing* or *Parallel Processing*, and involves the use of multiple processing units working together to solve the problem at hand. Parallel computing was traditionally performed using purpose-built supercomputers developed by companies such as Cray, IBM, Sun Microsystems and Silicon Graphics. These systems, although enormously powerful in comparison to contemporary desktop machines, are highly expensive to purchase and maintain. Furthermore, the ongoing exponential increase in commodity computer performance soon negates the performance advantage of supercomputers. As a result of these factors, High Performance Computing has traditionally been a worthwhile activity only for organizations with acute need and deep pockets.

In recent years, supercomputers have increasingly been replaced by clusters composed of commodity hardware (see Section 1.1 below). The rise in prominence of clusters has led to a drastic reduction in the cost associated with High Performance Computing, and hence increased popularity. Another recent trend is the increasing interest in the use of reconfigurable hardware (FPGAs) to create application-specific coprocessors that improve

application performance (see Section 1.2). Although still regarded as a niche area, it is likely that interest will continue to grow as the capability of reconfigurable hardware increases over time. The focus of this thesis will be on how both techniques (Cluster Computing and Reconfigurable Computing) can be combined in a manner so as to yield portability, reuse and separation of concerns and hence better and faster engineered code. In addition, attention is paid to computational efficiency; all design decisions are cognisant of the resulting effect on application performance.

#### 1.1 Cluster Computing

The notion of creating *compute clusters*, i.e., collections of interconnected computers working together as a single parallel system, is not a new one; IBM created compute clusters from mainframes during the 1960s [2]. However, it was not until the 1990s that the popularity of clusters gathered momentum due to the falling price and improving capability of commercial-off-the-shelf (COTS) components such as microprocessors and networking equipment. Efforts to create *commodity clusters* such as Beowulf [3] and Berkeley NOW (Networks of Workstations) [4] demonstrated that many large-scale and grand-challenge applications that were previously in the realm of supercomputers could be tackled using inexpensive hardware manufactured for the desktop computing market.

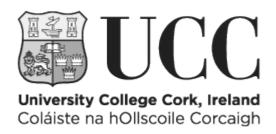

Commodity clusters are typically composed of a number of *compute nodes* connected by an Ethernet network. The compute nodes are usually homogeneous desktop machines configured without monitors, keyboards and other peripherals in order to save money and reduce space requirements (see Figure 1.1). Some clusters also contain a dedicated *head node*, which can perform a number of roles: running a firewall to separate the cluster

Figure 1.1: A typical commodity compute cluster, composed of 16 compute nodes, an Ethernet network and a head node.

from the outside world, hosting home directories that the compute nodes can access using NFS, running job management systems or even acting as a master in master/slave type computations. Clusters designed for applications that deal with large amounts of data may also contain *network attached storage* (NAS) units capable of storing Terabytes of data.

Although the majority of clusters are composed of dedicated machines, they may also be constructed in an *ad hoc* fashion by exploiting the idle cycles of underused workstations. The most simple method of constructing such clusters is by rebooting a collection of machines into dedicated disk partitions during periods when they are out of use [5]. More sophisticated schemes involve the use of daemons that allow machines to perform work during periods of inactivity (see Section 1.1.1).

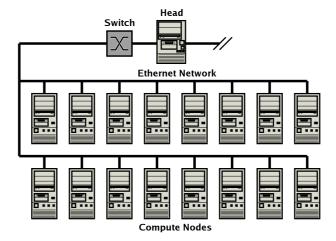

Despite the relatively poor performance characteristics (i.e., processor performance, network latency and network bandwidth) of commodity clusters when compared with dedicated parallel processing machines, they offer much higher price/performance ratios due to the economies of scale achieved during the manufacture of their constituent components. Notwithstanding their shortcomings, clusters have been shown to be capable of executing a wide variety of High Performance Computing problems [6]. The increasing popularity of clusters is illustrated by the rapid rise in recent years of the number of clusters on the list of the world's top 500 supercomputers (see Figure 1.2). In any case, the performance gap between clusters and dedicated parallel machines has narrowed significantly over time. Specialized minicomputers and workstations are almost a thing of the past; modern desktop microprocessors are up to all but the most demanding tasks. The advent of Gigabit Ethernet has made cheap, high performance networking a reality. Higher performance cluster interconnects that offer improved latency and scalability, such as Myrinet [7], are available if even Gigabit Ethernet does not suffice for the task at hand. However, many tightly-coupled, latency-sensitive applications (such as some real-time visualization applications [8]) still lie outside the realm of commodity hardware, and will require the use of dedicated parallel machines for some time to come.

#### 1.1.1 Programming Models for Cluster Computing

A variety of APIs, dedicated programming languages and middlewares are available for developing applications on clusters. The most suitable choice for any given project may depend on a number of factors, such as a desire for maximal performance, dependence on existing libraries, or ease of development. The wide range of choice available can be explained by the fact that no method has emerged that is best for all possible situations; each has associated advantages and disadvantages, and it falls to the programmer to choose the most appropriate model for the task at hand.

The most widely used technique is the use of traditional low-level programming languages such as ANSI C and Fortran in conjunction with message passing libraries such as PVM [9] and MPI [10]. The use of these libraries involves the explicit scheduling of networking communications through the sending and receiving of messages. Although this method is somewhat cumbersome and error-prone, the efficiency of a well-written message passing application is difficult to match using higher-level techniques. The continuing popularity of message passing libraries can also be explained by their high performance, relatively long history (and subsequent buildup of expertise), portability and popularity on non-cluster architectures (e.g., multiprocessors).

Another approach is to use distributed shared memory; each machine has access to the memory of all the others participating in the computation, creating a global virtual memory. Network communications are performed implicitly and are triggered by reads and writes to the shared memory space. Some shared memory systems, such as Treadmarks [11] and OpenMP [12], use APIs for existing programming languages. Others, such as Linda [13] and Unified Parallel C (UPC) [14], are utilized through programming language extensions. Shared memory systems require a mechanism for keeping data consistent. That is, a method of determining how local updates to the shared memory space are reflected on the other machines in the system. The simplest approach is to maintain sequential consistency by immediately transmitting any changes to the memory of a machine to the memories of all the other machines in the cluster. Unfortunately, the relatively poor performance characteristics of commodity networking equipment makes this approach impractical. As a result, most implementations use relaxed memory models. Reading the contents of a virtual shared memory location in these models does not necessarily return the last value written to that location. Knowledge of the message sequencing in the application will allow the programmer

Figure 1.2: The growth of cluster market share as a percentage of the world's top 500 supercomputers [Source: top500.org].

to extract performance when it is clear that consistency is not an issue. On the other hand, the onus is on the application programmer to maintain global consistency by explicitly using synchronization barrier and lock constructs.

Dedicated parallel programming languages offer a more appealing environment for the application developer to work with compared to the traditional approach of using a sequential language in combination with a parallel processing library. Parallel languages fall into two broad categories: extensions to existing sequential languages, and new languages designed specifically with the goal of facilitating parallel processing. Extensions to existing languages, such as High Performance Fortran (HPF) [15] and Charm++ [16], are comprised of parallel programming constructs such as forall loops and new keywords or directives (such as DISTRIBUTE and ALIGN) to facilitate the exploitation of distributed shared memory. Languages designed specifically for parallelism such as Occam [17] and Sisal [18] can express parallel programming functionality in a more elegant manner since they can be designed without the constraints of maintaining backward compatibility. Occam, for instance, features seq and par statements that specify sequential and parallel sections, as well as channels that allow processes to communicate easily in a fashion that minimizes deadlocks. Although these languages certainly simplify the job of the application developer to some extent, they are essentially syntactic sugar for underlying message passing or shared memory environments. As such, responsibility for parallelizing the program remains with the application developer.

Compilers for sequential programming languages often take advantage of chip-level parallel architectural features such as multiple ALUs and vector processing. Compilers such as SUIF [19] have extended this idea further through the development of compilers that attempt to extract the intrinsic parallelism of the application during compile-time and produce executables that can make use of multiple processors with no intervention on the part of the programmer. This approach carries obvious appeal; the burden of parallelizing the application is lifted from the developer and, even more importantly, preexisting code and libraries can be utilized in a parallel fashion with little effort. Unfortunately, code written in traditional sequential languages tends to be difficult to parallelize automatically due to the proliferation of side-effects caused by destructive assignment and limited inherent parallelism. Functional languages such as Haskell [20] tend to be more amenable to parallel compilation [21] since, due to the nature of these languages, side-effects are typically used only when necessary. However, the use of functional languages has not found wide acceptance within the HPC community because appropriate compilers have not been developed and because the necessary library codebase does not exist. All in all, parallelizing compilers are more suited to tightly-coupled architectures than clusters, due to the very fine-grain

nature of the parallelism they are able to exploit. Programs that express parallelism, either explicitly or through implicit parallel constructs, can result in a more efficient HPC implementation than a sequential equivalent that relies on extensive compiler support to find and exploit any inherent parallelism.

All of the parallel programming schemes mentioned above present the cluster of individual machines, to some extent, as a single system image (SSI) to the end user. Message passing libraries, for example, allow the cluster to be programmed as a loosely coupled parallel machine. Some projects have taken this idea to its logical extreme by allowing the cluster to be utilized as a single virtual machine. Examples of this approach are MOSIX [22] and Kerrighed [23]. These systems provide modified kernels allowing the user to see the cluster as a single UNIX workstation. No recompilation of existing applications is necessary; processes, and in the case of Kerrighed, threads, are migrated automatically across the cluster. Memory can be shared between nodes as needed, allowing virtual memory to page to the physical memory of the other nodes as well as to disk. Although undoubtedly the easiest method of using a cluster, the limitations inherent in this approach impose severe restrictions on the types of applications that can be parallelized. Mosix is only suited to applications that can execute as a set of independent processes. Even though Kerrighed allows for threads to be migrated across the cluster, the need to maintain global memory consistency and the performance overheads imposed by commodity networking hardware are likely to negate many of the advantages gained through thread migration. The lack of any method of discovering and taking advantage of the fine-grain parallelism found in many scientific applications (e.g., matrix multiplication) means that those wishing to execute such applications efficiently must turn to other techniques.

In contrast to dedicated clusters, Networks of Workstations can be used for distributed computing using a technique known as *cycle stealing* [24]. With this technique, any idle CPU time can be exploited in an opportunistic fashion without impacting on the individual machine users, taking advantage of an abundant resource that would otherwise be wasted. Examples of cycle-stealing systems, in addition to the SSI systems mentioned above, include Condor [25], Cyclone [26], and LinuxNOW (see Section 2.8.4).

The term metacomputing has recently come into vogue. In [27] it is defined as "the use of powerful computing resources transparently available to the user via a networked environment". However, this definition does not distinguish metacomputing from the SSI systems mentioned above. In practice, metacomputing has come to mean the use of middlewares to present a collection of potentially diverse and geographically distributed computing resources transparently to the user as a single virtual computer. Perhaps the most well-known metacomputing environment is the Globus Metacomputing Toolkit [28], which provides a

middleware for constructing computational grids from distributed, heterogeneous computing resources. The term *grid* is most often used to mean an infrastructure for the sharing of resources across administrative domains. Therefore, a *computational grid* is a hardware and software infrastructure that provides dependable, consistent and pervasive access to high-end computational capabilities, despite the geographical distribution of both resources and users [29]. A computational grid may be composed of a number of clusters, or parallel processing machines, or both. Globus is designed to be as flexible as possible, and as such does not enforce the use of any particular programming model. Programming languages and APIs supported include MPI, Java, Compositional C++, RPC and Perl.

Besides Globus, other metacomputing projects of interest include Legion [30] and WebCom [31]. Legion is an object-oriented metacomputing system that implements computations as collections of distributed objects. Programming languages supported include MPL (a parallel version of C++ that was also used as the implementation language), Fortran and Java. Emulation libraries are also provided for PVM and MPI, allowing legacy applications to be supported. WebCom is a metacomputing environment that allows computations expressed as Condensed Graphs (see Section 2.3) to be executed on a variety of platforms in a secure, fault-tolerant manner. Load-balancing is also performed over the computing resources available without requiring any intervention on the part of the programmer. Originally designed as a means of creating ad hoc metacomputers from Java applets embedded in web pages, WebCom has since been developed into a general-purpose distributed computing environment suitable for the creation of grids. An extended version of WebCom, entitled WebCom-G [32], allows for interoperability with other Grid Computing platforms and includes support for legacy applications.

#### 1.2 Reconfigurable Computing

Reconfigurable Computing is defined as "the use of systems that can alter their hardware configuration in response to changing context or data content" [33]. In effect, this requires the utilization of reconfigurable hardware, i.e., logic devices that can be reprogrammed with different hardware designs. Although different types of reconfigurable hardware are available (see Section 1.2.1), field programmable gate arrays (FPGAs) are of most interest, since they allow complex, register-heavy and pipelined designs to be executed at comparatively high clock speeds. These interesting properties have led to FPGAs finding applications in a number of areas, such as ASIC design prototyping, Embedded Computing and, most notably, High Performance Computing.

The notion of creating application-specific coprocessors using reconfigurable hardware has gained popularity in recent years as FPGAs have increased in speed and density. Using

this technique, applications may be accelerated by delegating some of their most commonly used functionality (usually an innermost loop) to an FPGA coprocessor configured with a suitable hardware implementation. Not all applications are amenable to acceleration with reconfigurable hardware; the part of the application to be accelerated must typically exhibit a high degree of intrinsic parallelism and data locality in order to make the conversion to hardware worthwhile. For some classes of applications, however, the benefits are impressive, with orders-of-magnitude increases in performance common in fields such as cryptography [34], image processing [35], data compression [36] and neural networks [37].

#### 1.2.1 Programmable Logic

Unlike application-specific integrated circuits (ASICs) which are fixed-function, i.e., the gates implementing the hardware design are physically etched into the silicon die, reconfigurable hardware is characterized by its ability to be reprogrammed with different configurations. A variety of devices fitting this description are available, but all fall into three broad categories: SPLDs, CPLDs and FPGAs [38].

The term programmable logic device (PLD) is often used to describe all types of programmable and reconfigurable hardware, but was initially used to refer to simple reconfigurable devices capable of replacing a small collection of combinatorial logic (i.e., AND, OR and NOT) chips on a circuit board. More recently, these devices have been referred to as simple programmable logic devices (SPLDs) in order to avoid confusion with the other classes of programmable devices described below. The advantage of using SPLDs when designing circuits is that they require less board area, power and wiring than a collection of simpler chips. SPLDs are typically implemented as a collection of fully-connected macrocells, each containing the logic necessary to implement a simple Boolean equation and a flip-flop to store the result until the next clock transition [39]. Other terms for SPLDs include programmable logic array (PLA) and programmable array logic (PAL). Most SPLDs cannot be reprogrammed; although they are capable of implementing a variety of logic functions, the function is typically fixed by the manufacturer and cannot be changed thereafter. The advent of SPLDs capable of being reprogrammed, referred to as generic array logic (GAL), marked the beginning of the field of Reconfigurable Computing.

Complex programmable logic devices (CPLDs) can be thought of as a number of SPLDs integrated on the same silicon die, along with a programmable switch matrix that connects them. This configuration allows more complex designs to be implemented, and allows dozens of individual logic chips to be replaced by a single device. Unlike the interconnects within the individual PLDs, the switch matrix in a CPLD is often not fully connected, making some designs impossible to implement even when there are sufficient logic gates available.

Although an overlap exists between the capabilities of CPLDS and low-end FPGAs, the simpler structure of CPLDs allows for shorter delays and hence higher clock speeds. As a result, CPLDs are often chosen for circuits where high performance is a priority.

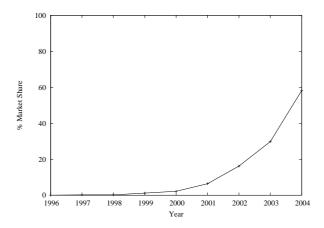

The most complex type of reconfigurable hardware devices are field programmable gate arrays<sup>1</sup> (FPGAs). FPGAs are composed of a two-dimensional array of logic blocks surrounded by routing resources, with I/O resources at the periphery. The principle application of FPGAs has traditionally been the prototyping of ASIC designs. In recent years they have also made inroads into the embedded computing market, where their reconfigurable nature offers the advantage of allowing hardware designs to be upgraded over time. The cost savings achieved by mass producing low-end FPGAs have also led to them increasingly being used in place of low-volume runs of ASICs. As the complexity of high-end FPGAs has increased over time, they have become capable of executing many applications faster than even top-of-the-range microprocessors, creating an interest in the use of FPGAs for High Performance Computing purposes [40].

Figure 1.3: Simplified diagram of the internal structure of a typical FPGA, composed of I/O blocks (IOBs), configurable logic blocks (CLBs), connection blocks (CBs) and switch boxes (SBs).

FPGAs are composed of a collection of configurable logic blocks (CLBs) sitting in a "sea" of routing resources. The routing resources are surrounded by a collection of I/O blocks (IOBs) which are connected to I/O pins. Other resources, such as memory banks and ALUs, may also be embedded in the FPGA fabric. CLBs are capable of implementing simple logic functions and are typically implemented using lookup tables (LUTs). The routing resources are composed of wires, connection blocks and switch boxes. Wires carry signals between the various components. Connection blocks contain multiplexers that select which signals are to

<sup>&</sup>lt;sup>1</sup>The *field programmable* part of the title refers to the fact that the devices can be programmed "in the field" rather than any electromagnetic properties they possess.

be connected to the terminals of nearby CLBs, and also connect short local wires to longer routing resources. Switchboxes are used to change the direction of signals from horizontal to vertical routing resources or *vice versa*. Although the architecture described here is by far the most common, a number of alternative approaches have been developed [41].

Of the three distinct types of reconfigurable hardware described here, FPGAs are by far the most commonly used by those wishing to create application-specific coprocessors. In light of this, the term *reconfigurable hardware* will hereafter be used to refer only to a collection of one or more FPGAs.

#### 1.2.2 Benefits and Limitations of Reconfigurable Computing

Performance increases attained through the use of reconfigurable hardware result from the massive levels of parallelism that exist within FPGAs. While CPUs are limited to sequential operation by the fetch/decode/execute cycle, FPGAs can carry out many operations in parallel. Even though modern CPUs are parallel to an extent through the use of pipelining and multiple ALUs, FPGAs offer much greater parallelism due to their ability to have many data paths, each of which can carry out operations of much more complexity than a CPU instruction. Unfortunately, the performance characteristics of FPGAs are in many respects far inferior to those of CPUs, particularly in terms of clock speed and floating-point performance (see below). The relatively low bandwidth and latency of many FPGA connection topologies (see Section 1.2.3) further degrades performance. Application developers wishing to improve performance by using reconfigurable hardware must be sure that the application in question plays to the strengths of FPGAs if any improvement is to be seen.

Suitable applications for FPGA acceleration must be CPU-intensive and exhibit a high degree of intrinsic parallelism and data locality. Applications that work with large, complex memory structures involving many non-local memory accesses are unlikely to benefit [42]. FPGAs are also at a signicant disadvantage for applications that make heavy use of floating-point arithmetic. The complexity associated with performing floating-point operations leads to long delays within resulting FPGA configurations and hence poor performance. Modern CPUs improve floating-point performance through the use of floating point units (FPUs); FPGAs under development that contain embedded FPUs are likely to ameliorate this situation in the future. Another factor that application developers must take into account is the sequential bottleneck imposed by the limited number of I/O pins that connect FPGAs to the outside world. Applications may be unable to take advantage of parallelism if they are starved of data due to the limited amount of data they can read per clock cycle. The highest-performing applications are those that can unroll loops and execute them in parallel inside the FPGA, with little communication occurring with the outside world. Research

by Sun Microsystems into the development of microchip architectures that use capacitive coupling rather than pins [43] to increase bandwidth may improve this situation in future generations of FPGAs.

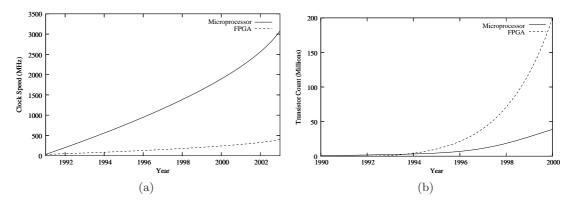

The most significant factor mitigating against the use of FPGAs is the significant difference between the clock speeds of even the highest-performing FPGA and contemporary CPU (see Figure 1.4(a)). The problem of low FPGA clock speeds is further exacerbated by the fact that maximum clock speeds are rarely attained in practice due to longest path delays in hardware designs. At the time of writing, the most advanced FPGA available is the Xilinx Virtex-4 family, which has a maximum clock speed of 500 MHz /Source: xilinx.com. This figure stands in stark contrast to the clock speed of the highest-performing Intel Pentium 4 desktop CPU, which is clocked at 3.6 GHz [Source: intel.com] – over seven times faster. This divergence in clock speeds is likely to increase over time as the rate of increase of CPU clock speeds is greater than that of FPGAs. Although the exact date for the expiration of Moore's Law is the subject of ongoing speculation (the International Technology Roadmap for Semiconductors currently extends to 2016 [44]), the laws of Physics dictate that a limit on microprocessor clock speed must be reached at some point in the future. Once this limit has been reached, FPGA clock speeds could begin to converge with those of CPUs, but the degree to which this convergence can occur is, again, the subject of speculation.

Given the increasingly large divergence between FPGA and CPU clock speeds, pessimism about the future of Reconfigurable Computing for high performance purposes is understandable. However, such pessimism ignores another important performance characteristic: transistor count. The number of transistors embedded in FPGAs (and hence the complexity of the hardware designs they can accommodate) has increased exponentially (see Figure 1.4(b)), a trend that looks likely to continue into the future as smaller-scale

Figure 1.4: The divergence between (a) the clock speeds and (b) the densities of the Intel Pentium family of microprocessors compared with the Xilinx Virtex family of FPGAs during the 1990s.

manufacturing processes are used. An increasing divergence, similar to that between clock speeds, exists between the transistor counts of CPUs and FPGAs. It is therefore likely that Reconfigurable Computing will deliver even greater speedups relative to CPUs in the future, but only for those fine-grained, compute-intensive parallel applications to which they are already suited [45].

#### 1.2.3 Reconfigurable Computing Topologies

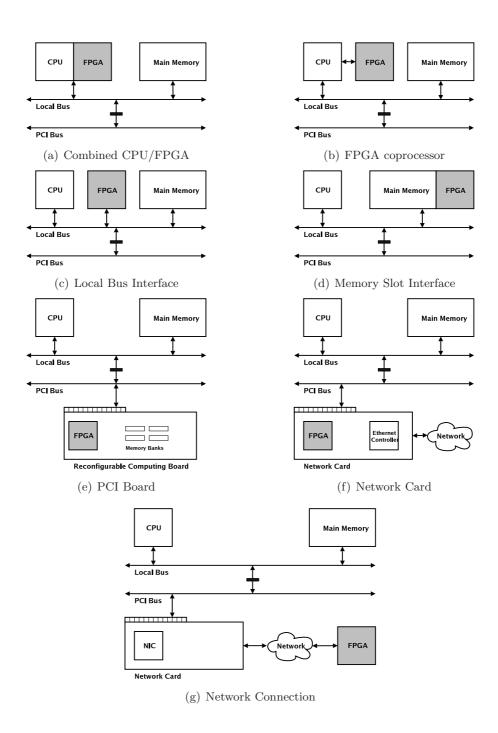

A variety of methods for attaching reconfigurable hardware to host processors have been proposed. The most tightly-coupled arrangement is the integration of microprocessors and reconfigurable hardware on the same silicon die (see Figure 1.5(a)). This approach can involve augmenting an existing microprocessor architecture with a reconfigurable functional unit (RFU) that has direct access to the CPU's registers, and is utilized through extensions to the microprocessor's instruction set. The Chimaera RFU [46] is an example of this approach. A similar approach is the integration of reconfigurable hardware in the form of a tightly-coupled coprocessor, for example the REMARC [47] architecture (see Figure 1.5(b)).

Other methods involve the attachment of reconfigurable computing boards to the local bus of the motherboard, allowing the FPGA to communicate with the same latency and bandwidth as main memory (see Figure 1.5(c)). FPGA boards are available that can plug into unused processor slots on AMD Opteron motherboards [48]. Unfortunately, most motherboards, especially the commodity models typically found in clusters, are not capable of supporting such devices. An ingenious workaround for this limitation is the creation of reconfigurable computing boards that can be fitted to the memory slots of commodity motherboards, for example Pilchard [49] and SmartDIMM [50] (see Figure 1.5(d)). Such boards have only ever been manufactured in limited quantities, however, and are not commercially available at the time of writing<sup>2</sup>.

The most common means of attaching reconfigurable hardware to the host processor is to use dedicated parallel processing boards that are fitted to the PCI bus of standard motherboards (see Figure 1.5(e)). This approach is less than ideal due to the performance penalty incurred by sending data back and forth over the PCI bus. The largest market for high-end FPGAs is currently the prototyping of ASIC designs, an application much less sensitive to the limitations imposed by the PCI bus than the creation of application-specific coprocessors. As a result, PCI-based reconfigurable computing boards are manufactured in large quantities and are hence widely available at relatively low cost. Manufacturers of reconfigurable computing boards include Celoxica, Nallatech, Xilinx and Annapolis Microsystems.

<sup>&</sup>lt;sup>2</sup>One company (Nuron) did briefly manufacture such devices during the late 1990s, but has since ceased trading.

Figure 1.5: Reconfigurable Computing Topologies

Alternative methods of attaching FPGAs to desktop PCs include using the serial or USB buses, but the poor performance of these buses makes this approach unsuitable in situations where high performance is a consideration.

Another PCI-based approach is the integration of reconfigurable hardware with network interface cards (NICs), for example the custom cards created in the construction of the Tower of Power [51], a cluster created from commodity machines fitted with FPGA/NIC hybrids (see Figure 1.5(f)). These cards are designed for Digital Signal Processing (DSP) applications, where data arriving over the network is piped through the FPGA on the network card before being passed to the host CPU for further processing.

The most loosely-coupled connection topology is direct communication with reconfigurable hardware over a network (see Figure 1.5(g)). For example, QinetiQ market a system composed of a desktop workstation as well as a heterogeneous collection of FPGAs and individual CPUs, all of which communicate directly with a Myrinet packet-switched network [52]. Although very modular and adaptable, the performance limitations of even the best-performing networking equipment limits the range of applications that can be tackled on systems such as this. This is due to the fact that without the supervision of a locally-attached CPU, every communication with the FPGAs must be performed over the network, degrading the performance of many applications. As such, network-attached FPGAs are suited only to the most coarse-grained of applications that are amenable to FPGA acceleration.

Although the majority of work relating to reconfigurable computing involves the integration of FPGAs with host processors, as described above, other work has focused on the creation of custom computing machines. These are specialized computing architectures integrating many discrete programmable logic components into a single computing board [53] [54]. Despite being expensive to design and construct, architectures such as these are useful in situations where throughput requirements would limit the usefulness of a single, complex, FPGA. For example, matrix multiplication, although not normally amenable to acceleration using a single FPGA (see Section 1.2.2 above), could be accelerated using a number of relatively simple devices with shared memory operating in parallel.

#### 1.2.4 Creating FPGA Configurations

The creation of FPGA configurations (or *bitstreams*) is typically a two-step process. The first step is to create a description of the logic gates and their interconnections that comprise the hardware design, using a standard format such as Electronic Design Interchange Format (EDIF) [55]. The hardware description is then passed through a *place-and-route* tool specific to the target model of FPGA. The place-and-route tool uses a floorplanning algorithm to

map the logic blocks contained in the hardware description to a bitstream that can be sent to an FPGA using a suitable software driver or API. Although little choice usually exists in the selection of place-and-route tool and support software (these are typically vendor-specific), numerous techniques are available for the creation of hardware descriptions.

The most widely used means of creating hardware descriptions is the use of traditional hardware description languages such as VHDL [56], Verilog [57] and ABEL [58]. When using these languages the designer must explicitly specify the logic elements (such as gates, flip-flops and latches) and interconnections that comprise the design. This approach is comparable to assembly language programming for microprocessors in that it has the advantage of allowing for the creation of extremely efficient designs but at the cost of increased development time and reduced design maintainability.

Rather than using a dedicated language, low-level hardware designs may also be created programatically using *circuit generators*, i.e., APIs for existing software programming languages. Perhaps the most popular of these is JBits [59], an API for the Java language. Other APIs include PAM-Blox (C++) [60], PyHDL (Python) [61] and Lava (Haskell) [62]. These APIs can be used either for the creation of parameterized low-level hardware designs, such as variable-width adders, or can be used at a higher level to create designs by linking together predefined logic blocks.

Graphical hardware design tools, such as Simulink [63] and Viva [64], aim to reduce the complexity associated with specifying low-level hardware designs by providing a more user-friendly environment than text-based interfaces to hardware design languages or APIs. When using these tools, circuits are specified by dragging and dropping predefined logic blocks from a palette and "drawing" the connections between them. This technique is particularly powerful when a large selection of high-level predefined components such as adders, multipliers and counters are available. The drawbacks of these systems are that they emphasise structural rather than behavioural development, and the fact that large designs with many non-local interconnections can become extremely complex to develop and maintain in a graphical fashion.

High-level general purpose hardware design languages such Handel-C [65], SystemC [66] and Transmogrifier C [67] have also become available. All are based upon the ANSI C language, but with some features (such as pointers) removed and others (such as parallel programming constructs) added. By starting with a simple, poorly-performing design, analysis with place and route tools reveals the longest paths in the resulting hardware design. Through a process of iterative refinement, various optimizations can be performed until an acceptable level of speed/efficiency is reached. Small changes in the high-level source code can result in major changes in the resulting logic, allowing different design strategies

to be evaluated quickly. Although these languages offer the advantage of reduced development time and increased agility in comparison with their lower-level counterparts, the resulting designs cannot match the efficiency of implementation attainable using traditional languages.

The creation of FPGA configurations directly from existing sequential languages is a field under active investigation. Some systems map complete programs directly to FPGA configurations. This approach has been attempted for a variety of languages, such as Occam [68] and Smalltalk [69]. Other systems allow the developer to identify the part of an existing sequential program most amenable to hardware acceleration (perhaps using a profiler) and then delegate the necessary hardware/software co-design to the compiler. The Galadriel [70] compiler, one example of such a system, converts Java byte code to FPGA configurations (via VHDL) and modifies the byte code to transmit data to and from the attached reconfigurable hardware. Similarly, the NAPA C compiler [71] allows parts of an ANSI C program to be automatically delegated to reconfigurable hardware through the use of #pragma directives. Although sequential compilers such as these allow reconfigurable hardware to be exploited with very little effort on the part of the application designer, the resulting designs are usually far less efficient than those created using more traditional methods. In particular, dedicated hardware design languages and APIs allow the width of data paths to be specified explicitly to avoid wasting logic resources, a feature that sequential languages lack. NAPA C provides directives for specifying the bit-width of variables, although doing so significantly increases development time and erodes the advantage associated with automatic compilation.

A more unusual approach is the evolution of hardware designs using genetic algorithms [72]. Starting with a random configuration, the effect of small perturbations are measured against a fitness function to determine how close they come to meeting the desired behaviour. Through this evolutionary process, those designs that perform well are more likely to be chosen for the next iteration until eventually a configuration emerges that meets all of the design requirements. The resulting designs are often very efficient and can take advantage of characteristics of FPGAs unavailable to conventional design tools. For example, some evolved configurations contain areas of logic completely cut off from the main circuit, causing them at first to appear redundant. However, if these areas of logic are removed the main circuit may cease to function. Possible explanations for this behaviour include electromagnetic coupling or subtle interactions through the power supply or silicon substrate. Although unorthodox circuit behaviour such as this may be advantageous in terms of performance and efficiency, care must be taken to ensure that the design does not rely on the exact conditions in which it was evolved (e.g., the precise voltage used, the individual FPGA used for evaluation and the presence of electromagnetic interference) by including

tests for robustness in the fitness function.

#### 1.3 Augmenting Clusters with Reconfigurable Hardware

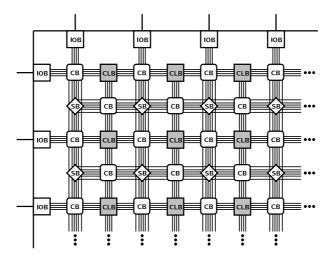

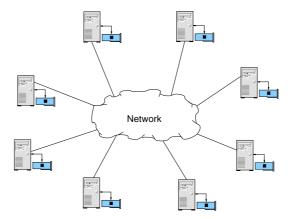

Given the large performance increases attainable using Cluster Computing and Reconfigurable Computing, it is not surprising that interest has developed in using a combination of both techniques, i.e., the creation of clusters where the compute nodes are augmented with reconfigurable hardware in order to improve performance [73][74][75] (see Figure 1.6 below). This field is still in its infancy, and referred to by a number of synonymous terms in the literature, including Distributed Reconfigurable Computing, Distributed Adaptive Computing and High Performance Reconfigurable Computing. In order to avoid confusion, it should also be noted that the term FPGA cluster is generally used to refer to groups of logic blocks within FPGAs [76] rather than compute clusters augmented with reconfigurable hardware.

Figure 1.6: A cluster augmented with reconfigurable hardware in the form of PCI FPGA boards.

The most common methodology for developing applications for clusters augmented with reconfigurable hardware is to use MPI in conjunction with high-level hardware design languages, with communications to and from the reconfigurable hardware performed using vendor-supplied drivers. The FPGAs are typically connected to the cluster nodes using either PCI cards or combined FPGA/NICs. A number of applications have successfully been implemented using this technique, such as Parallel Brutus [77] (a chess playing application), fast Fourier transforms [78], data processing for physics applications [79], and an application for solving the n queens problem [80].

Libraries have been developed to simplify the task of developing applications for clusters augmented with reconfigurable hardware. The Adaptable Computing API [81] is a connection-oriented library that allows stream-based applications to be created that utilize distributed reconfigurable computing boards in a portable fashion. When using this library,

all reconfigurations and communications must be specified explicitly, and as such this approach can be regarded as a reconfigurable computing analogue of message passing libraries for clusters. Similarly, an extension has been added to the low-level GRIM (General-purpose Reliable In-order Messages) protocol in order to exploit clusters augmented with various resources, such as network attached storage and FPGAs, through the creation of logical channels [82]. Another approach is the use of existing job management systems (JMSs), such as LSF and CODINE, to target reconfigurable hardware embedded in distributed machines at the process level [83].

Considerable effort has been expended in developing tools for compiling and scheduling applications both for individual custom computing machines containing multiple FPGAs and clusters augmented with reconfigurable hardware. MATCH [84] is a Matlab compiler that can target a collection of distributed heterogeneous FPGAs. An automated mapping and scheduling tool has been developed [85] that statically partitions a graph description of an application based on the distributed computational resources available and produces an execution schedule. A similar approach is the notion of resource pools [86], which are abstract representations of the computing resources available, allowing a high-level description of an application to be mapped to both hardware and software as necessary.

CARMA (Comprehensive Approach to Reconfigurable Management Architecture) [87] is a management framework designed to facilitate the development of applications, system services, programming models and middlewares that utilize distributed reconfigurable hardware. The services provided include board-independent application mapping, dynamic job scheduling, distributed configuration management [88], performance monitoring [89] and board-independent modules for interfacing with FPGAs.

On the theoretical side, a *performance model* has also been developed for clusters augmented with reconfigurable hardware [90]. The performance model allows the behaviour of various cluster configurations to be accurately simulated, and as such can be of significant benefit when designing clusters before purchase. Related work includes an analysis of the cost effectiveness of clusters augmented with reconfigurable hardware [91].

Despite the advances planned and supplied by many of the systems above, it can be noted that these applications and systems are relatively simple to construct and do not consider issues such as task heterogeneity and the management of multiple FPGA configurations. Active consideration for these important characteristics was a prime motivator for the ARC system.

Although the majority of work related to the use of reconfigurable hardware within clusters is concerned with executing portions of applications on the reconfigurable hardware, as described above, other roles for reconfigurable hardware have also been examined. A significant body of research has been conducted on the use of FPGAs to improve the performance

of networks for HPC purposes [92][93]. Higher networking performance is typically achieved through the implementation of custom protocols designed specifically for that purpose. An implementation of the Condensed Graphs (see Section 2.3) model of computation has been developed [94] with the aim of reducing the performance overhead associated with identifying subtasks. Unfortunately, the latencies associated with communicating over the PCI bus and the sequential bottleneck imposed by access to the development board's memory banks resulted in poor performance. Nevertheless, this concept may become viable if adapted to more advanced FPGA architectures and connection methods. A similar approach is the automatic delegation of grid services to reconfigurable hardware in a platform-independent fashion [95].

#### 1.4 Parallel Computing Metrics

A number of useful metrics can be applied to parallel processing systems, either before development in order to evaluate potential benefits, or afterwards so that the performance of the system can be measured. Since the goal of parallel processing is typically to minimize execution time, perhaps the most useful metric is the ratio of the times taken to execute the application sequentially and in parallel. This ratio, called the *speedup factor* (S), is given by

$$S = \frac{t_s}{t_p}$$

where  $t_s$  is the sequential execution time and  $t_p$  is the parallel execution time. In multiprocessor systems the speedup factor is typically limited by the number of processors (n). Superlinear speedup, where S > n, is sometimes observed in multiprocessor systems, often due to the extra memory available in systems with distributed shared memory. However, in the case of clusters augmented with reconfigurable hardware, when utilized effectively, superlinear speedup should be the norm rather than the exception if the FPGAs are not included in the processor count.

Calculating the maximum speedup attainable for an application is an important aspect of parallel application design; there is little point in attempting to parallelize an application unless a significant speedup will result. Any parallel application not composed of completely independent processes is composed of some parts that, by their nature, must execute sequentially. Amdahl observed in 1967 that the sequential fraction of a computation limits the maximum speedup that can be achieved, even if all parallel processing resources are fully utilized during the parallel parts. As Amdahl put it: "the effort expended on achieving

high parallel processing rates is wasted unless it is accompanied by achievement in sequential processing rates of very nearly the same magnitude" [96]. This observation has become known as Amdahl's Law, and although Amdahl's original paper did not contain an equation form of the law, it is usually formulated in terms of multiprocessor systems and expressed as follows:

$$S(n) = \frac{1}{f + \frac{1-f}{n}}$$

where S(n) is the maximum speedup attainable for n processors and f is the fraction of the computation that must be executed sequentially. Even with an infinite number of processors, the maximum speedup is limited to  $\frac{1}{f}$ :

$$\lim_{n \to \infty} S(n) = \frac{1}{f}$$

It should be noted that this limitation applies equally to Reconfigurable Computing; the fact that the parallel processing resources available are logic gates rather than processors makes no difference. Despite the fact that the law was originally published as an attack on the viability of parallel systems, proponents of parallel processing have argued that any significant speedup is of benefit, particularly in long-running computations.

Others have questioned the reasoning behind Amdahl's Law, in particular the assumption that the amount of computation to be performed is fixed and not dependent on the number of processors available. Gustafson observed in 1988 [97] that in practice users tend to scale the amount of computation performed to the resources available. For example, the grid resolution of a weather prediction application may be increased to improve accuracy. In many cases, it is therefore execution time that is held constant rather than the amount of computation to be performed. Furthermore, it is frequently the case that the sequential fraction of such applications is constant rather than scaling with the amount of computation to be performed. In this case, the *scaled speedup* is given by

$$S_S(n) = n(1-f) + f$$

where  $S_S(n)$  is the scaled speedup for n processors and f is the fixed sequential fraction of the program. Note that the scaled speedup increases linearly with the number of processors. This observation has become known as Gustafson's Law.

When deciding on the number and complexity of subtasks in a parallel application, it is essential that inter-task communication does not dominate the overall computation time. The application designer must therefore strike the right balance between maximizing parallelism in the application and minimizing time spent communicating. A useful metric in this case is the granularity(G) or "work/talk" ratio

$$G = \frac{t_{comp}}{t_{comms}}$$

where  $t_{comp}$  is the computation time and  $t_{comms}$  is the communication time.

Computational Efficiency (E) is a measure of how effectively an application takes advantage of the parallel computing resources available to it, and is given by

$$E = \frac{t_s}{t_p n}$$

where  $t_s$  is the sequential execution time,  $t_p$  is the parallel execution time and n is the number of processors in the system. Note that if efficiency of utilization of FPGAs as well as CPUs in the system is being considered, then the number of FPGAs present should be included in the processor count. This definition of efficiency does not take into account the limitations imposed by Amdahl's Law; in most situations full efficiency (according to definition above) is unattainable due to the presence of sequential sections in the application. As a result, the following alternative definition of computational efficiency is sometimes given:

$$E = \frac{S_a}{S_i}$$

where  $S_a$  is the actual speedup and  $S_i$  is the ideal speedup.

#### 1.5 Research Motivation and Objectives

#### 1.5.1 Shortcomings of Current Techniques

The current standard practice when targeting commodity clusters is to leave the task of extracting parallelism from the application and performing network communications to the programmer. Existing sequential languages coupled with message passing libraries are used to reduce the learning curve associated with parallel programming. This approach, although somewhat primitive and labour intensive in comparison with some of the more advanced programming models outlined in Section 1.1.1, is the methodology of choice for the majority of cluster applications. Reasons for the continuing popularity of the message passing approach over alternative methods include better performance, portability and resistance to change due to the large body of existing code and expertise accumulated through many

years of use. However, the resulting applications are large and intricate where the implementation of the desired algorithm is scattered amongst frequent calls to the message passing library.

The complexity imposed by the message passing approach is manageable in simple scatter/gather type applications where the parallelism can be divided evenly over the available resources and all parallel subtasks take the same amount of time to execute. Unfortunately, not every application can be decomposed into identical parallel subtasks, and there may be many more tasks to execute than processors available. In this case, *load balancing* must be performed in order to efficiently utilize the computational resources, whereby unassigned tasks are sent to the most *lightly loaded* nodes, i.e., the nodes with the least amount of work left to perform. Message passing libraries by their nature offer no support to the programmer in situations such as this – load balancing must be performed explicitly.

The lack of load balancing support in message passing libraries is particularly disadvantageous to those wishing to exploit reconfigurable hardware efficiently within cluster nodes. If the resources available (CPUs and FPGAs) are to be exploited most effectively, then they must be utilized as much as possible during the lifetime of the computation. In order to achieve this, the application must partition the computation and balance the load between the CPUs and FPGAs available both on each node and over the cluster as a whole. This situation is further exacerbated by computations where multiple FPGA configurations are in use throughout the cluster, in effect requiring load balancing across heterogeneous resources. Furthermore, this heterogeneity is dynamic in that FPGA reconfigurations take place and need to be planned with a view to minimizing execution time.

Given the difficulties associated with scheduling tasks across clusters augmented with reconfigurable hardware on an application-by-application basis, prudent programmers will trade off this cost with the potential speedups that could be achieved. Complex applications may require a disproportionate effort to load balance effectively. The load balancing effort dominates the application development costs when the number of processors exceeds a particular threshold and/or when the application processes are heterogeneous in size or function. These limitations stem from the lack of expressiveness of the message passing libraries, making it difficult to succinctly express complex policies; the purpose of message passing libraries is to move data from one node to another, they do not assist in deciding where to send it. Furthermore, message passing libraries do not address the sending of data to and from reconfigurable hardware – this task is beyond the scope of their design.

#### 1.5.2 Research Question and Thesis Overview

The prospect of developing complex applications for clusters augmented with reconfigurable hardware can be a challenging one, as evidenced by the previous section. A reasonable question to ask is the following: Would the average programmer, aware of the potentially large speedups attainable using reconfigurable hardware embedded in clusters, attempt to develop for such a system using the techniques currently available?

The answer would appear to be largely in the negative because of the lack of uptake of the technique despite its availability for a number of years. It follows that a more developer-friendly environment may be beneficial if Reconfigurable Computing is to find wider acceptance within the field of Cluster Computing. However, any system attempting to provide a higher-level view by abstracting details will invariably incur a performance overhead. There is a lesson to be learned here from the continued popularity of the message passing paradigm in Cluster Computing – any system that exhibits what is deemed to be an unacceptably high degradation in performance is unlikely to find favour among parallel programmers since the ultimate goal in the field is, after all, high performance. As a result, it can be concluded that any system designed to simplify the task of developing applications for clusters augmented with reconfigurable hardware should make efficient use of the computational resources available as well as the programmer's time.

The Accessible Reconfigurable Computing (ARC) system, which is the subject of this thesis, is a collection of software tools created with the aim of providing the application developer with an efficient high-level abstraction of a cluster augmented with reconfigurable hardware. The overriding design goal during the development of the ARC system was to create an environment where the implementation of applications for clusters augmented with reconfigurable hardware is cleanly separated, insofar as possible, from the details of the hardware upon which they are to be executed. Using this approach, application logic is not cluttered with calls to message passing APIs or to FPGA drivers. Instead, the distinct tasks of implementing the application logic, specifying high-level parallelism and accelerating parts of the application using reconfigurable hardware are treated separately. The most appropriate tools and methodologies can then be used for each of these tasks in isolation, instead of specifying all of these activities as a large and intricate program written in a sequential language, as is the current practice.

The remainder of this thesis is organized as follows: Chapter 2 describes in detail the design, implementation and operation of the ARC system. An example application (cryptographic key search) is presented in Chapter 3. The development of a performance model of the ARC runtime environment is described in Chapter 4, along with a program that automatically generates ARC applications. The ARC load balancing framework is presented

in Chapter 5, and various load balancing algorithms and optimizations are evaluated with the aid of the performance model. Finally, conclusions and future work are presented in Chapter 6.

# Chapter 2

# ARC: A Distributed Reconfigurable Metacomputing System

The Accessible Reconfigurable Computing (ARC) system [98] is a collection of software tools created with the aim of providing the application developer with an efficient high-level abstraction of a cluster augmented with reconfigurable hardware. The following sections present the motivation behind the project as well as a detailed description of the architecture and operation of the system itself, both at compile-time and at runtime. The process of developing applications for the system is also described through the development of a sample application. A more detailed example of application development will be presented in Chapter 3.

#### 2.1 Design Philosophy

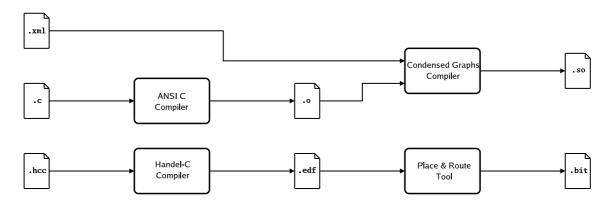

ARC's overriding design goal was to create an environment where the implementation of applications for clusters augmented with reconfigurable hardware is cleanly separated, insofar as possible, from the details of the hardware upon which they are to be executed. Using this approach, application logic is not cluttered with calls to message passing APIs or FPGA drivers. Instead, the distinct tasks of implementing the application logic, specifying high-level parallelism and accelerating parts of the application using reconfigurable hardware are treated separately. The most appropriate tools and methodologies can then be used for each of these three tasks in isolation, in contrast to specifying all of these activities as a single large and intricate program.

1. ANSI C was chosen as the most appropriate language for implementing the application

logic. Despite the increasing popularity of higher-level languages such as C++ and Java, ANSI C is still considered the best choice for high performance applications due to the existence of very efficient compilers and a large body of existing code and libraries that can be leveraged when implementing applications. Performance considerations aside, and despite the fact that ANSI C lacks many of the features (such as exception handling and object-oriented constructs) found in many modern languages, it is still regarded as a very capable procedural language, much more so than its predecessor, Fortran, in the field of High Performance Computing. Although the language has its detractors [99], the continuing popularity of ANSI C is illustrated by the fact that it has consistently ranked highly in the TIOBE Programming Community Index<sup>1</sup>, a monthly independent survey of programming language popularity. In the period from January 2001 to the time of writing it has never dropped below second place in the survey.

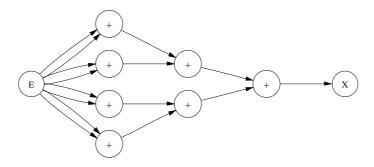

- 2. The Condensed Graphs model of computation (see Section 2.3) was chosen as the means of specifying the high-level parallelism within applications. Unlike message passing libraries, the Condensed Graphs model does not require network communications to be explicitly specified within application code; communications can be performed implicitly by the runtime environment based on the high-level relationships contained in the application's definition graphs. Other graph-based means of expressing parallelism and data dependency, such as control-flow and data-flow graphs [100], lack the flexibility of the Condensed Graphs model, especially its ability to allow large, complex graphs to be modularized using condensation and its ability to express multiple sequencing constraints such as demand-driven, data-driven and control-driven modes within the same application. XML was chosen as the file format for specifying graph definitions (see Section 2.4). This format was chosen for its flexibility; XML specifications can be easily created manually using a text editor or high-level GUI. Furthermore, XML documents are simple to generate automatically using a variety of XML APIs on many different platforms.

- 3. In keeping with the theme of providing the application developer with as much flexibility as possible in terms of implementing the various application components, no particular method of creating FPGA configurations was mandated. Developers are free to use any of the hardware design methodologies outlined in Section 1.2.4, and as such may choose to maximize performance at the cost of increased development time using low-level hardware design languages such as VHDL. Alternatively, they may decide to use a more agile development system such as Handel-C.

<sup>&</sup>lt;sup>1</sup>See http://www.tiobe.com/tpci.htm

Unfortunately, the goal of abstracting the application from the underlying execution environment breaks down somewhat when FPGA configurations are considered. Although well-written ANSI C code and the XML Condensed Graphs file format are completely portable across cluster installations, in most cases FPGA configurations are targeted towards a specific model of FPGA. This drawback is not caused by any defect in the hardware tools; indeed, EDIF files are completely cross-platform and in theory could be compiled for any logic device containing enough gates to implement the logic specified therein. When trying to maximize performance, the parallelism within a hardware design is tuned so as to take advantage of as much of the available resources on a particular FPGA model as possible. One can only hope that in the future this lack of available abstraction can be remedied through the availability of FPGAs containing more logic gates than most applications can leverage.

Linux was chosen as the sole target operating system due to its position as the cluster operating system of choice in the majority of high performance computing centres. Other UNIX variants were not considered; the extra effort involved in writing portable code and performing comprehensive testing across multiple platforms was deemed to be too great when compared with the questionable benefits. One particular obstacle to portability is the limited availability of drivers for reconfigurable boards on more niche platforms such as FreeBSD. In fact, very little Linux-specific functionality is used in the implementation of ARC, so a portable version could certainly be developed without undue effort in the future. A Microsoft Windows port would represent a more formidable undertaking, but this task could be simplified through the use of the Linux-emulating Cygwin tools and libraries.

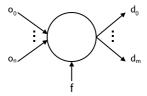

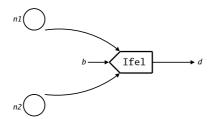

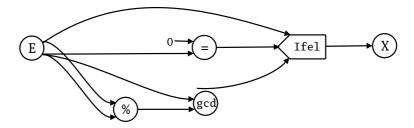

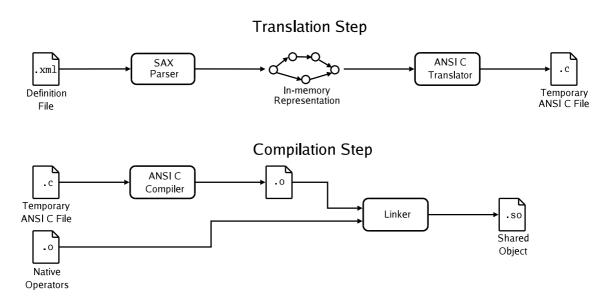

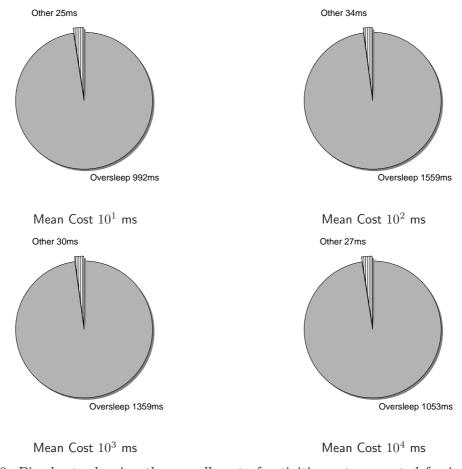

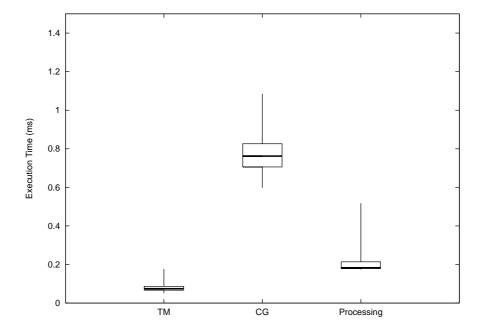

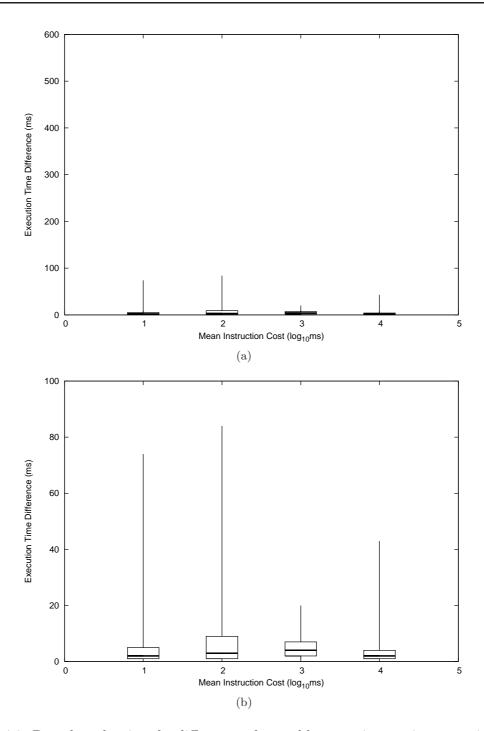

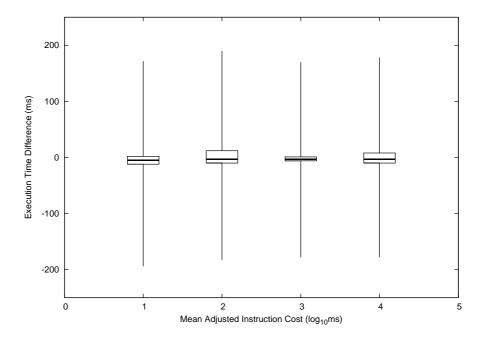

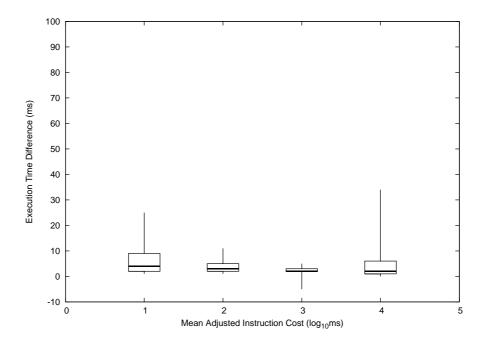

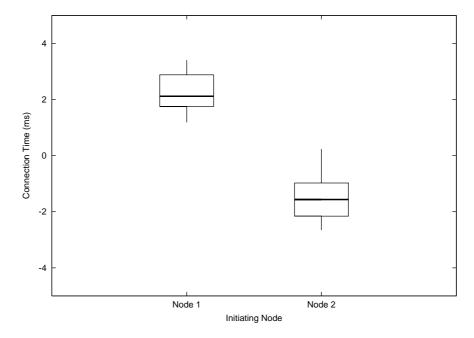

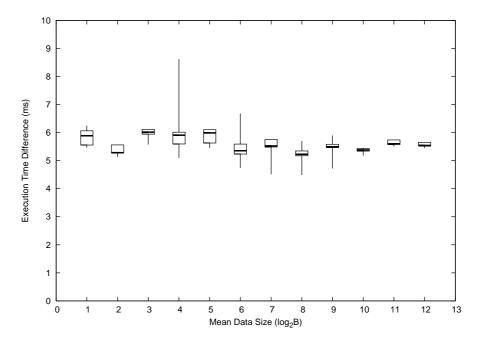

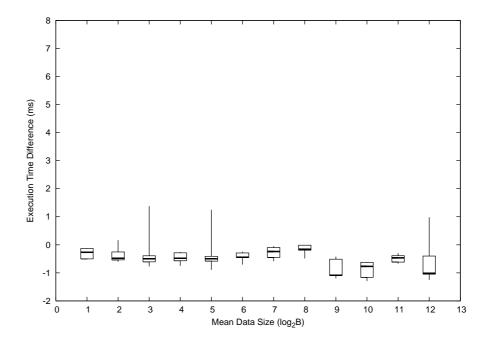

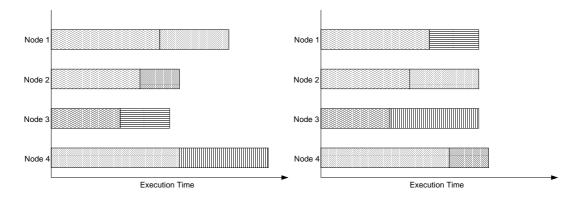

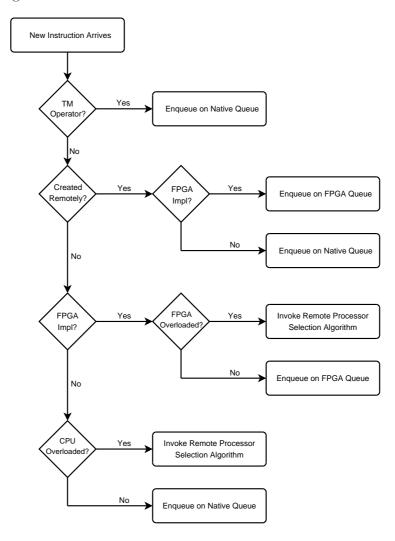

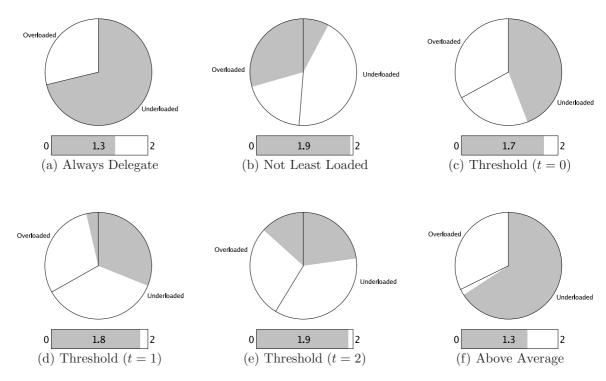

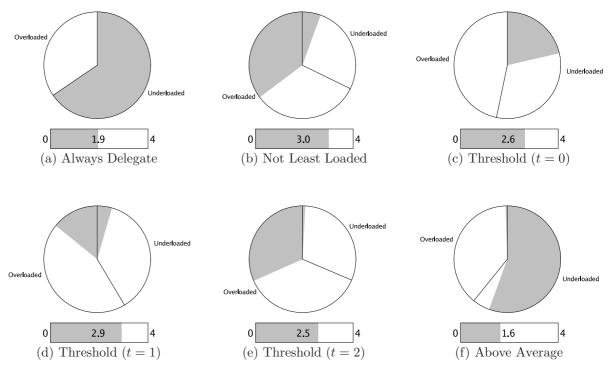

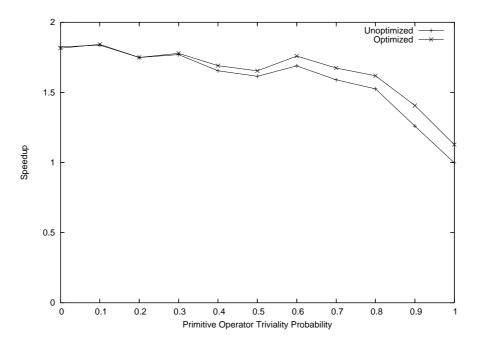

Once an (albeit imperfect) abstraction of clusters augmented with reconfigurable hardware is available, any such cluster can be regarded from the developer's perspective as a single virtual machine rather than a collection of discrete entities. The task of maintaining the illusion of a single system falls to the compile-time and runtime environments that comprise the ARC system (subsequent sections will describe the operation of these in some detail). If the illusion proves successful, developing for the ARC system can be regarded as a form of declarative programming, where the developer specifies what is to be computed rather how it is to be computed.