| Title                          | 42.6 Gbit/s fully integrated all-optical XOR gate                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Author(s)                      | Dailey, James M.; Ibrahim, Selwan K.; Manning, Robert J.; Webb, Rod<br>P.; Lardenois, Sébastien; Maxwell, Graeme D.; Poustie, Alistair J.                                                                                                                                                                                                                                                  |

| Publication date               | 2009-09                                                                                                                                                                                                                                                                                                                                                                                    |

| Original citation              | Dailey, J.M., Ibrahim, S.K., Manning, R.J., Webb, R.P., Lardenois, S.,<br>Maxwell, G.D., Poustie, A.J. (2009) '42.6 Gbit/s Fully Integrated All-<br>Optical XOR Gate'. Electronics Letters, 45(20), 1047 - 1049. doi:<br>10.1049/el.2009.2036                                                                                                                                              |

| Type of publication            | Article (peer-reviewed)                                                                                                                                                                                                                                                                                                                                                                    |

| Link to publisher's<br>version | http://dx.doi.org/10.1049/el.2009.2036<br>Access to the full text of the published version may require a<br>subscription.                                                                                                                                                                                                                                                                  |

| Rights                         | © The Institution of Engineering and Technology 2009. This paper<br>is a postprint of a paper submitted to and accepted for publication<br>in Electronics Letters and is subject to Institution of Engineering<br>and Technology Copyright. The copy of record is available at IET<br>Digital Library<br><u>http://www.ietdl.org/journals/doc/IEEDRL-</u><br>home/info/support/copyinf.jsp |

| Item downloaded<br>from        | http://hdl.handle.net/10468/412                                                                                                                                                                                                                                                                                                                                                            |

Downloaded on 2018-08-23T17:49:57Z

University College Cork, Ireland Coláiste na hOllscoile Corcaigh

This paper is a postprint of a paper submitted to and accepted for publication in *Electronics Letters* and is subject to Institution of Engineering and Technology Copyright. The copy of record is available at IET Digital Library

# 42.6 Gb/s Fully Integrated All-Optical XOR Gate

J.M. Dailey, S.K. Ibrahim, R.J. Manning, R.P. Webb, S. Lardenois, G.D. Maxwell, and A.J. Poustie

## Abstract

We demonstrate an SOA-based all-optical high-speed Mach-Zehnder interferometer exclusive- OR (XOR) gate fabricated in a silica III-V hybrid-integration technology platform. The device includes integrated time delays for rapid differential operation as well as integrated phase shifters for fine tuning of power splitters and interferometer bias enabling highly optimized XOR gate operation. XOR functionality is verified through inspection of the output pulse sequence and the carrier-suppressed output spectrum. A 2.3 dB penalty for a 42.6 Gb/s RZ-OOK signal at a 10<sup>-9</sup> bit error rate is observed.

#### Introduction

Demand for higher signal processing bandwidths in the core and metro networks continues unabated as data traffic continues to grow rapidly worldwide. Aggregate transmission rates in the hundreds and thousands of Gb/s are being actively pursued, and debate continues on whether or not the electronics needed to operate in these regimes will be too costly [1, 2]. A well championed solution is the development of all-optical processing techniques, which promise ample bandwidth through the exploitation of ultrafast (~fs-ps) processes. All-optical exclusive-OR (XOR) logical gates are of special interest due to their use in constructing a number of higher level logic functions including e.g. parity checkers, pseudorandom pulse generators, firewalls, and packet header processors [3].

Semiconductor optical amplifiers (SOAs) have garnered particular interest as all-optical processors due to their high level of integrability and relatively large nonlinearities in tiny volumes, leading to smaller switching energies and packages more suited for telecoms-type applications [4]. Furthermore, bandwidth limitations arising from slow interband carrier dynamics have been greatly ameliorated through differential switching techniques in SOA-based interferometer structures relying on cross-phase modulation (XPM).

In this letter we report on a novel highly integrated XOR gate based on differentially switched SOAs in a Mach-Zehnder interferometer (MZI) operating at 42.6 Gb/s, and its bit-error rate (BER) penalties. This device has a higher level of integration than previously reported [5]: differential signal delays are included on-chip along with variable power splitters for both data channels. Together with the variable phase shifters in the MZI arms, these enable highly optimized gate operation [6]. We are the first, to our knowledge, to demonstrate this high level of photonic integration for an all-optical XOR gate and to report such low BER penalties at 40 Gb/s [7].

## XOR Operation Principle

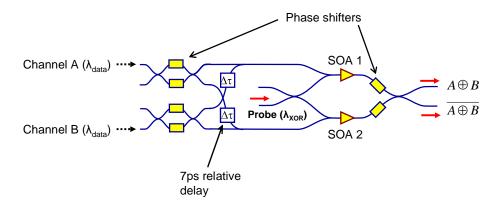

The XOR gate was fabricated by CIP Technologies using a hybrid-integration platform [5] incorporating nonlinear InP-based SOAs with low-loss planar silica waveguides, and is shown in Fig. 1. The SOAs are strained multiple-quantum-well devices with an effective length of 2 mm and 10% to 90% gain recovery times of ~ 33ps. A Peltier cooler is included for temperature stability. The continuous-wave (cw) probe at  $\lambda_{XOR}$  is injected into the gate and is made to destructively interfere at the MZI output through appropriate SOA and phase shifter bias settings. When a return-to-zero (RZ) pulse is injected into the channel A power splitter, the non-delayed pulse saturates SOA1 and through XPM opens a switching window, carving the rising edge of the probe output pulse.

Fig. 1 The hybrid-integrated XOR gate, with all components shown integrated on-chip.

At a time  $\Delta \tau$  (~7 ps) later the delayed pulse enters SOA2 and closes the switching window, forming the falling edge of the output pulse. The pulse delay was chosen specifically for the 42.6 Gb/s data rate, and the ultimate operational speed of the gate is limited by the choice of this delay and the SOA recovery times. This is an AND operation between channel A and the probe. Fig. 1 also shows an AND gate for channel B placed symmetrically inside the device, and when an input pulse enters the channel B power splitter a pulse also emerges from the output. However, if there is a pulse at channel A as well as channel B, the two SOAs are identically saturated resulting in zero relative phase shift and no output pulse. This switching behaviour describes XOR operation. Note that the phase shifters at the channel A and B inputs enable continuously variable power splitters which together with the probe phase shifters are essential for open output eyes with high extinction [6]. The SOAs' amplified spontaneous emission (ASE) 3-dB bandwidth was measured to be greater than 40 nm indicating a large operational bandwidth. The SOAs have been designed to minimize polarization sensitivity, though because of the birefringence of the passive waveguides the device displays a polarization dependence on both the probe and data inputs.

#### Experimental Setup

The data channels were implemented using the 2 ps output pulses ( $\lambda_{data} = 1560$ nm) from a commercial mode-locked laser synchronized to a 10.65 GHz RF clock. The pulse stream was modulated with a pseudorandom binary sequence (PRBS) of length 2<sup>7</sup>-1, using a lithium niobate optical modulator, and was then passively multiplexed up to a 42.6 Gb/s stream. The data was divided into two channels (A and B) with the introduction of some relative optical delay. The use of erbium doped fibre amplifiers (EDFAs) and optical attenuators enabled control over the data input power to the gate. A performance optimum corresponded with data input powers around 5 dBm, or pulse energies of approximately 150 fJ. The cw probe input ( $\lambda_{XOR} \sim = 1552.5$ nm) power was 1 dBm and polarization controllers for both the data and probe signals enabled optimization of the output eyes. The SOA bias currents were 548 and 488 mA. Ideally the bias currents would be identical, and the disparity here is attributed to a small excess loss asymmetry in the gate. The SOAs and Peltier element comprise the largest current sinks in the package and the total electrical power consumption was ~ 3 W with no optical inputs.

## Results

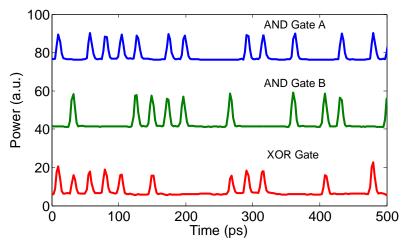

XOR operation is verified in Fig 2 where we show the traces from a high-speed optical sampling oscilloscope when the device is operated in both AND as well as XOR modes. The upper trace (AND Gate A) is the output when channel B is turned off, and similarly the middle trace (AND Gate B) is the output when channel A is turned off. When both channels are input to the device, the result is shown in the bottom trace (XOR Gate) and by comparing all three traces the appropriate XOR logical operations are verified. The extinction ratio for the output XOR signal measured from the scope trace is 11 dB.

Fig 2. Time domain probe output from gate operating in AND (upper and middle traces) and XOR modes (bottom trace). Power offsets between traces are arbitrary.

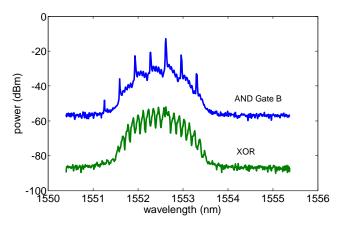

We also verify correct device operation by examining the probe output spectra shown in Fig 3. The upper spectrum shows the output when channel A is turned off, and the device acts as an AND gate for channel B. The 42.6 GHz sideband harmonics can be clearly seen in relation to the carrier frequency at  $\lambda_{XOR} \sim 1552.5$ nm. The bottom spectrum shows the output when both channels are input to the device, and we note that this spectrum is derived from the output pulses corresponding to AND operations on channels A and B, i.e. if both channels input zero or one then there is no pulse output. Channels A and B trigger the two SOAs in opposite order, and the resultant "A" and "B" output pulses have opposing phase shifts. The PRBS sequence ensures that an "A" or "B" pulse is equally likely in the output, and so on average, the carrier is suppressed and the output spectrum resembles that of a differential phase-shift keyed (DPSK) signal.

Fig 3. The probe output spectra for both AND and XOR modes. Power offset between traces is arbitrary.

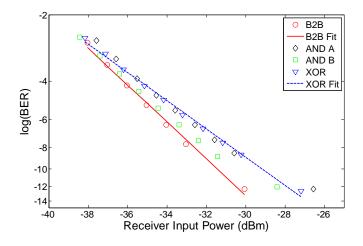

Finally, we filter the data signal from the device output and send the XOR signal to an optically preamplified receiver. In Fig 4 we show the results from measuring the bit error rate (BER) as a function of receiver input power. The back-to-back (B2B) channel is plotted with circles, and shows the BER when a data channel is directly input to the receiver. The two AND gate results are also shown as the data with squares and diamonds. Linear fits to the data indicate that the penalties for gates A and B at a BER of  $10^{-9}$  are 2.3 and 1.2 dB, respectively. We believe that the discrepancy in penalties may be due to a residual asymmetry in the fabrication leading to a better extinction ratio for channel B than for channel A. The XOR data are shown with triangle markers and indicate a measured penalty of 2.3 dB, though we believe that penalties approaching the B gate penalty may be possible by addressing the fabrication asymmetries

discussed earlier. However, we do not expect XOR performance to equal that of an individual AND gate due to the increased operational bandwidth needed for XOR operation: when a binary "one" is input to both data channels each SOA receives two pulses separated by  $\Delta \tau = 7$ ps, i.e. a temporal separation less than a bit slot.

Fig 4. BER vs input power for XOR gate. XOR operates with 2.3 dB penalty at a BER of 10<sup>-9</sup>.

# Conclusions

We have demonstrated a high-speed all-optical XOR gate fabricated in a hybrid-integration technology platform. The fully integrated device includes phase shifters and power splitters that can be adjusted for highly optimized gate operation. The output signal experiences only a 2.3 dB penalty at 42.6 Gb/s and we believe smaller penalties, closer to the 1.2 dB AND gate penalty, are within reach of this technology.

# Acknowledgement

This work was supported by the Science Foundation Ireland under grant number 06/IN/I969.

## Authors' Affiliations

J.M. Dailey, S.K. Ibrahim, R.J. Manning, and R.P. Webb are with the Photonic Systems Group, Tyndall National Institute and Physics Department, University College Cork, Ireland.S. Lardenois, G.D. Maxwell and A.J. Poustie are with CIP Technologies, Phoenix House, Adastral Park, Martlesham Heath, Ipswich, IP5 3RE, UK

## Corresponding author: James Dailey at james.dailey@tyndall.ie

## References

- [1] J. Gripp, D. Stiliadis, J. E. Simsarian, P. Bernasconi, J. D. Le Grange, L. Zhang, L. Buhl, and D. T. Neilson, "IRIS optical packet router [Invited]," *J. Opt. Netw.*, vol. 5, pp. 589-597, 2006.

- [2] R. S. Tucker, "The Role of Optics and Electronics in High-Capacity Routers," *J. Lightwave Technol.*, vol. 24, pp. 4655-4673, 2006.

- [3] J. M. Martinez, F. Ramos, and J. Marti, "All-optical packet header processor based on cascaded SOA-MZIs," *Electronics Letters*, vol. 40, pp. 894-895, 2004.

- [4] T. Fjelde, D. Wolfson, A. Kloch, B. Dagens, A. Coquelin, I. Guillemot, F. Gaborit, F. Poingt, and M. Renaud, "Demonstration of 20 Gbit/s all-optical logic XOR in integrated SOA-based interferometric wavelength converter," *Electronics Letters*, vol. 36, pp. 1863-1864, 2000.

- [5] R. P. Webb, R. J. Manning, G. D. Maxwell, and A. J. Poustie, "40 Gbit/s all-optical XOR gate based on hybrid-integrated Mach-Zehnder interferometer," *Electronics Letters*, vol. 39, pp. 79-81, 2003.

- [6] J. M. Dailey and T. L. Koch, "Simple Rules for Optimizing Asymmetries in SOA-Based Mach-Zehnder Wavelength Converters," *Lightwave Technology, Journal of*, vol. 27, pp. 1480-1488, 2009.

- [7] X. Yang, A. K. Mishra, R. J. Manning, R. P. Webb, G. Maxwell, A. Poustie, and R. Harmon, "Comparison of All-Optical XOR Gates at 42.6 Gbit/s," in *European Conference on Optical Communications*, Berlin, Germany, 2007, p. Paper P070.