# UNIVERSIDADE DO ALGARVE INSTITUTO SUPERIOR DE ENGENHARIA

# METODOLOGIA PARA PREVER O ENVELHECIMENTO DE CIRCUITOS DIGITAIS

## AGING PREDICTION METHODOLOGY FOR DIGITAL CIRCUITS

Jakson dos Santos Pachito

Dissertação para obtenção do Grau de Mestre em

Engenharia Eléctrica e Electrónica

Área de Especialização em Tecnologias de Informação e Telecomunicações

# UNIVERSIDADE DO ALGARVE INSTITUTO SUPERIOR DE ENGENHARIA

# METODOLOGIA PARA PREVER O ENVELHECIMENTO DE CIRCUITOS DIGITAIS

## AGING PREDICTION METHODOLOGY FOR DIGITAL CIRCUITS

Jakson dos Santos Pachito

Dissertação para obtenção do Grau de Mestre em

Engenharia Eléctrica e Electrónica

Área de Especialização em Tecnologias de Informação e Telecomunicações

Orientador: Professor Doutor Jorge Filipe Leal Costa Semião

**Presidente de Júri:** Professor Doutor Isménio Lourenço Eusébio Martins

**Vogais:** Professor Doutor José Manuel Aguiar Tavares Bastos

Professor Doutor António João Freitas Gomes da Silva

Professor Doutor Jorge Filipe Leal Costa Semião

### **AGRADECIMENTOS**

Em primeiro lugar quero agradecer a uma pessoa fundamental para que este trabalho chegasse até aqui. O meu Professor e orientador Jorge Semião. Agradeço-lhe pela sua dedicação pessoal e profissional, pela paciência, pelos ensinamentos que foram para além dos académicos, e por muitas vezes me ter concedido tempo para estudar e apreender. Agradeço-lhe pelo dom que tem em ensinar e fazer as coisas parecerem simples, quando na verdade em muitas ocasiões não o eram. Embora sem saber, nos momentos em que sentia que não era capaz de continuar, a sua motivação e talento foi sempre uma inspiração para mim. Enfim, palavras não chegam para tamanha gratidão. Obrigado Professor!

Durante a realização deste trabalho muitas foram as pessoas que, de uma maneira ou de outra, contribuíram para o seu sucesso. Quero agradecer aos professores da UAlg que me acompanharam, em especial ao Professor Carlos Marinho. Agradeço aos meus colegas Edmar, Balakov, Naiss, Mats, Ivan e Ary. Agradeço à Dona Joana, pelo afecto e cuidado incondicional que sempre demonstrou, e à CASA, na pessoa do Sr. Pedro Cebola. Agradeço também ao Wilson e ao Aricson pelo companheirismo.

Aos meus pais deixo uma palavra especial de gratidão, pela educação que tive, e agradeço também aos meus irmãos Vânia e Wando.

A todos os que disponibilizaram documentação e informações diversas, nomeadamente M. A. Alam – Purdue University, Y. Cao e E. Wang - Arizona State University, Júlio Vazquez – INAOE/INESQ ID, quero também deixar uma palavra de agradecimento.

Por fim, e não menos importante, um muito obrigado à pessoa que me estendeu a mão no momento mais crítico, o Sr. Aristides.

Jakson dos Santos Pachito, Faro, 19 de Janeiro de 2012

### **RESUMO**

Com a constante miniaturização da tecnologia de circuitos integrados CMOS, diversos problemas de fiabilidade e performance estão a tornar-se críticos à medida que a escala continua a ser reduzida. Efeitos a longo prazo, como o NBTI, TDDB, HCI, MS, etc, degradam os parâmetros físicos dos transístores CMOS e com consequências nas propriedades eléctricas dos semicondutores. O fenómeno NBTI é considerado o efeito dominante no processo de degradação por envelhecimento dos CMOS e influencia a operação dos transístores PMOS. Os efeitos degradantes do NBTI são manifestados na degradação da corrente de dreno, nas capacidades, na transcondutância e na tensão limiar de condução (*Vth*) dos transístores PMOS, mas pode ser representada simplesmente como um incremento no |*Vth*| ao longo do tempo. Esta degradação é chamada de envelhecimento e estes efeitos cumulativos têm um grande impacto na performance do circuito, especialmente se ocorrerem outras variações paramétricas, como as variações de processo, tensão de alimentação e temperatura.

O trabalho apresentado nesta dissertação tem por objectivo desenvolver uma metodologia para prever a degradação na performance dos circuitos digitais CMOS na presença de efeitos de envelhecimento por NBTI. Uma biblioteca genérica SPICE de CMOS foi também definida de forma a usar vários modelos preditivos de tecnologias (PTM). A previsão do envelhecimento é baseada em cálculos das probabilidades dos transístores PMOS terem uma polarização negativa em V<sub>GS</sub>, na modelação das correspondentes variações em *Vth* para cada transístor e nas simulações SPICE para medir a degradação na performance. A automatização da metodologia é materializada numa nova ferramenta de *software* chamada AgingCalc, desenvolvida no âmbito desta tese de mestrado.

A metodologia de previsão de envelhecimento proposta é demonstrada através de simulações em circuitos de referência em tecnologias de 130nm a 16nm, usando modelos PTM.

**PALAVRAS-CHAVE:** Previsão do envelhecimento, NBTI, Degradação dos atrasos nos caminhos, Modulação de *Vth*, Probabilidade de operação, Simulações SPICE automáticas.

### ABSTRACT

With the constant miniaturization of CMOS IC (*Integrated Circuits*') technology, various issues of reliability and performance are becoming critical as the scale continues to be reduced. Long term effects, such as NBTI, TDDB, HCI, MS, etc., degrade the physical CMOS transistors' parameters and with consequences on the electrical properties of semiconductors. The NBTI phenomenon is considered the dominant effect in the CMOS aging degradation process and influences PMOS transistors' operation. The degrading effects of NBTI are manifested in the degradation of drain current, capacitance, transconductance and threshold voltage (*Vth*) of PMOS transistors, but it can be represented simply as an increment in |*Vth*| over time. The set of this degradation is called aging and these cumulative effects have high impact on circuit performance, especially if other parametric variations occur, such as Process, Voltage or Temperature variations.

The work presented in this thesis aims to develop a methodology to predict CMOS digital circuits' performance degradation in the presence of NBTI aging effects. A generic SPICE CMOS library was defined in order use various transistor's Predictive Technology Models (PTM). The aging prediction is based on probability calculations for the PMOS transistors to have a negative  $V_{GS}$  polarization, on modeling the corresponding Vth variations of each transistor and on SPICE simulations to measure the performance degradation. Methodology automation is materialized in a new software tool called AgingCalc, developed in the context of this thesis.

The proposed aging prediction methodology is demonstrated by extensive simulation on benchmark circuits designed in IC technologies ranging from 130nm to 16nm, using PTM models.

**KEYWORDS:** Aging prediction, NBTI, Path-delay degradation, Operation probability, *Vth* Modulation, Automatic SPICE simulations.

## INDÍCE

| 1. | Int | rodu  | ção                                                             | 1        |

|----|-----|-------|-----------------------------------------------------------------|----------|

|    | 1.1 | Env   | velhecimento em Circuitos Integrados                            | 1        |

|    | 1.2 | Enc   | quadramento do Trabalho                                         | 3        |

|    | 1.3 | Obj   | ectivos do Trabalho                                             | 4        |

|    | 1.4 | Cor   | ntexto do Trabalho                                              | <i>6</i> |

|    | 1.5 | Org   | ganização do Documento                                          | 7        |

| 2. | En  | velhe | ecimento em Nano tecnologias CMOS                               | 9        |

|    | 2.1 | Fen   | ómeno NBTI                                                      | 11       |

|    | 2.1 | .1    | O Modelo Reaction-Diffusion                                     | 14       |

|    | 2.1 | .2    | Geração dos Obstáculos à Passagem de Corrente (Interface Traps) | 15       |

|    | 2.1 | .3    | Dependência do NBTI com a Temperatura                           | 20       |

|    | 2.1 | .4    | Dependência do NBTI com o Campo Eléctrico                       | 21       |

|    | 2.1 | .5    | Modelação do efeito NBTI                                        | 21       |

|    | 2.1 | .6    | Redução de Efeitos Provocados pelo NBTI                         | 25       |

|    | 2.2 | Out   | tros Efeitos que Causam o Envelhecimento dos Circuitos          | 26       |

|    | 2.2 | .1    | Time Dependent Dielectric Breakdown                             | 27       |

|    | 2.2 | 2     | Hot Carrier Injection                                           | 27       |

|    | 2.2 | .3    | Electro-Migration                                               | 28       |

|    | 2.2 | .4    | Stress Induced Voids                                            | 30       |

|    | 2.2 | .5    | Total Ionizing Dose                                             | 30       |

| 3. | Me  | etodo | ologia para Previsão do Envelhecimento                          | 33       |

|    | 3.1 | Mo    | delação do Envelhecimento dos Transístores CMOS                 | 33       |

|    | 3.2 | Cál   | culo de Probabilidades em Circuitos Digitais                    | 35       |

|    | 3.2 | .1    | Cálculo das Probabilidades nos Nós de Saída dos Componentes     | 36       |

|    | 3.2 | .2    | Cálculo das Probabilidades de Operação dos Transístores PMOS    | 38       |

|    | 3.3 | Deg   | gradação de Circuitos Digitais                                  | 43       |

|    | 3.3 | .1    | Modelo do Transístor para Modelação do Parâmetro Vth            | 44       |

|    | 3.3 | .2    | Biblioteca CMOS para Modelação do Envelhecimento                | 46       |

X ÍNDICE

|      | 3.3.3  | Simulação HSPICE com Modelação do Envelhecimento               | 48               |

|------|--------|----------------------------------------------------------------|------------------|

|      | 3.3.4  | Simulação de Monte Carlo com Modelação do Envelhecin           | nento 52         |

| 3.   | .4 E   | Enquadramento com Metodologia de Inserção de                   | Sensores de      |

| E    | nvelhe | ecimento                                                       | 55               |

| 4.   | Progr  | rama AgingCalc                                                 | 59               |

| 4.   | .1 (   | Características Gerais                                         | 59               |

|      | 4.1.1  | Entrada de Dados                                               | 60               |

|      | 4.1.2  | 2 Organização e Estrutura de Dados                             | 60               |

|      | 4.1.3  | Saída de Dados                                                 | 65               |

| 4.   | .2 [   | Descrição das Principais Funcionalidades                       | 71               |

|      | 4.2.1  | Cálculo de Probabilidades                                      | 74               |

|      | 4.2.2  | 2 Cálculo de Atrasos em Portas Lógicas e Caminhos              | 78               |

| 5.   | Resu   | ıltados Experimentais                                          | 85               |

| 5.   | .1 F   | Resultados do Envelhecimento de um Transístor                  | 85               |

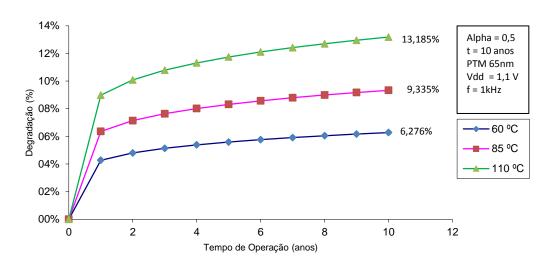

|      | 5.1.1  | Variação da Degradação com a Temperatura                       | 85               |

|      | 5.1.2  | 2 Variação da Degradação com a Frequência de Operação          | 87               |

|      | 5.1.3  | Variação da Degradação com a Tensão de Alimentação $V_{\rm I}$ | <sub>DD</sub> 88 |

|      | 5.1.4  | Variação da Degradação com a Tecnologia de Fabricação.         | 89               |

| 5.   | .2 F   | Resultados do Envelhecimento em Circuitos de Referência        | 92               |

|      | 5.2.1  | Caracterização dos Circuitos de Referência                     | 93               |

|      | 5.2.2  | Resultados de Cálculo de Probabilidades                        | 94               |

|      | 5.2.3  | Resultados de Análise de Atrasos em Condições Nominais         | 95               |

|      | 5.2.4  | Resultados de Análise de Envelhecimento                        | 95               |

|      | 5.2.5  | Comparação entre Atrasos Calculados por Simulação de C         | Componentes e    |

|      | por S  | Simulação do Circuito                                          | 99               |

| 6.   | Conc   | clusões e Trabalho Futuro                                      | 103              |

| 6.   | .1 (   | Conclusões                                                     | 103              |

| 6.   | .2 Т   | Trabalhos Futuros                                              | 106              |

| Bibl | iograf | fia                                                            | 109              |

# ÍNDICE DE FIGURAS

| Figura 1: Representação física da estrutura do transístor PMOS onde se dão              | as |

|-----------------------------------------------------------------------------------------|----|

| reacções químicas (esquerda) e representação química da estrutura                       | da |

| interface Si-SiO <sub>2</sub> (direita) [50]                                            | 12 |

| Figura 2: Distribuição do hidrogénio pelo óxido fino: (a) quebra das ligaçõ             | es |

| químicas; (b) relação da concentração de ao longo do óxido fino do PMO                  | S  |

| [33]                                                                                    | 14 |

| Figura 3: Geração de IT, difusão do H e H <sub>2</sub> em direcção à porta e combinação | de |

| átomos de H para formar H <sub>2</sub> [55]                                             | 16 |

| Figura 4: Quantidade de NIT junto à gate do PMOS durante as fases de stresse            | e  |

| recuperação [7].                                                                        | 18 |

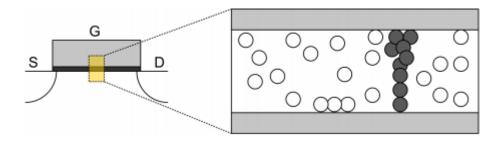

| Figura 5: Corte transversal de um transístor apresentando um caminho condutivo a        | no |

| óxido da gate devido ao TDDB.                                                           | 27 |

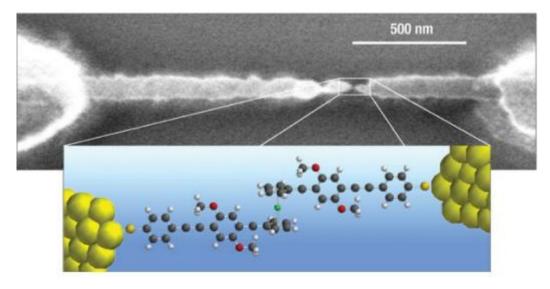

| Figura 6: Radiografia de um fio condutor rompido devido a degradação devido             | à  |

| migração eléctrica dos átomos [93].                                                     | 29 |

| Figura 7: Corte transversal de um transístor sob efeito de radiação por partícul        | as |

| carregadas positiva e negativamente                                                     | 31 |

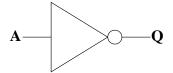

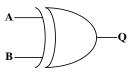

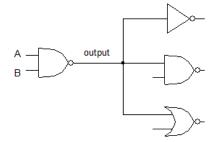

| Figura 8: Inversor                                                                      | 37 |

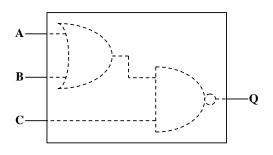

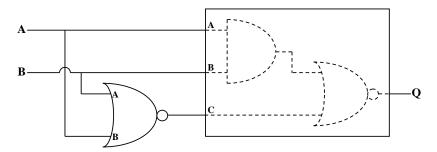

| Figura 9: Porta lógica OAI210                                                           | 37 |

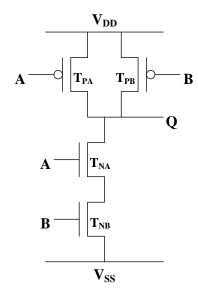

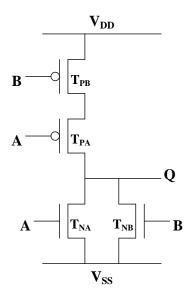

| Figura 10: Esquemático da porta lógica NAND20.                                          | 39 |

| Figura 11: Esquemático da porta lógica NOR20.                                           | 40 |

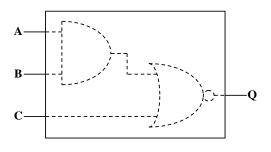

| Figura 12: Porta lógica AOI210                                                          | 41 |

| Figura 13: Esquemático da porta lógica AOI210.                                          | 41 |

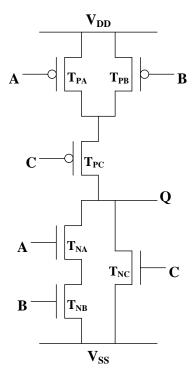

| Figura 14: Porta lógica XOR20.                                                          | 42 |

| Figura 15: Composição da porta lógica XOR20.                                            | 42 |

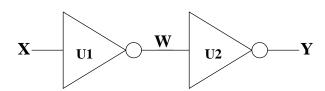

| Figura 16: Cadeia de 2 Inversores.                                                      | 49 |

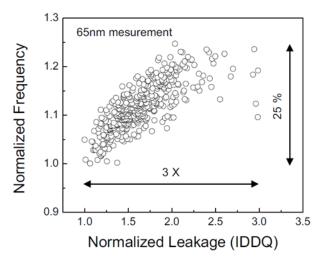

| Figura 17: Variações na frequência e em I <sub>DDQ</sub> , num CI de 65nm, considerand  | do |

| variações do processo de fabricação                                                     | 56 |

XII ÍNDICE DE FIGURAS

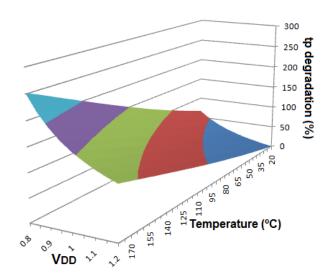

| Figura 18: Variações no tempo de propagação de uma cadeia de 20 inversores,           |

|---------------------------------------------------------------------------------------|

| provocada por variações VT, numa tecnologia de 65nm57                                 |

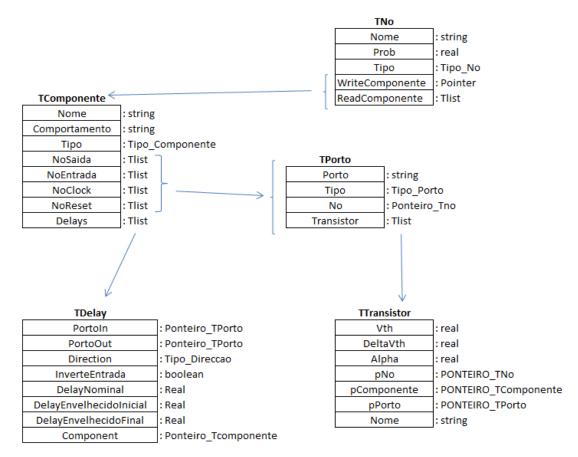

| Figura 19: Resumo da estrutura de dados do programa AgingCalc                         |

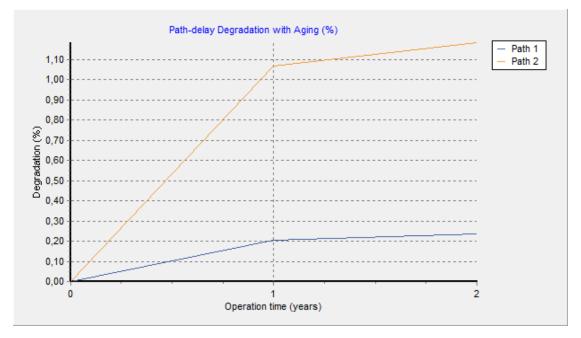

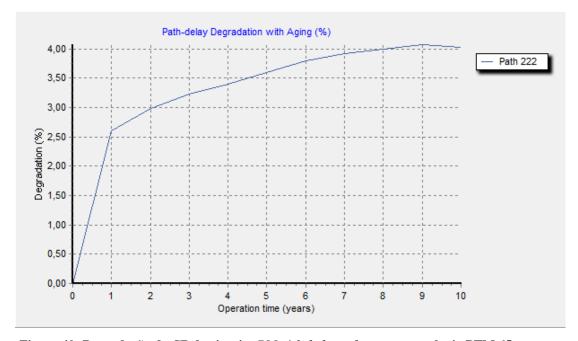

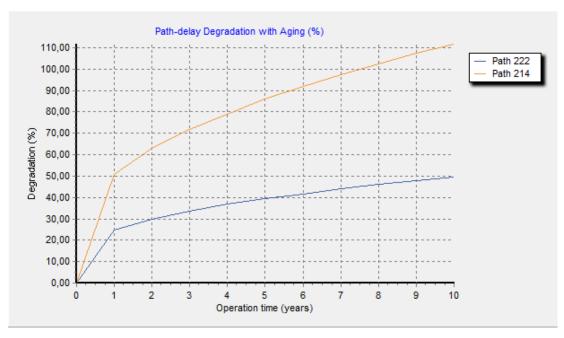

| Figura 20: Gráfico da evolução da degradação dos atrasos dos caminhos em [%] 70       |

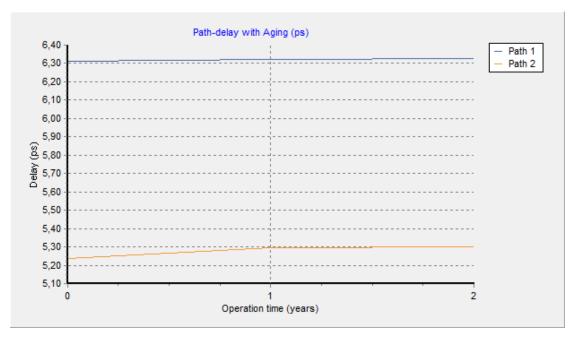

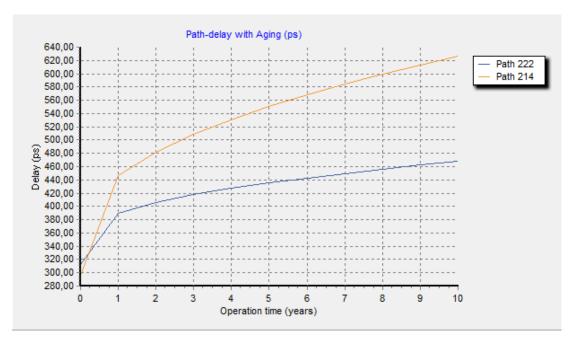

| Figura 21: Gráfico da evolução da degradação dos atrasos dos caminhos em [ps] 71      |

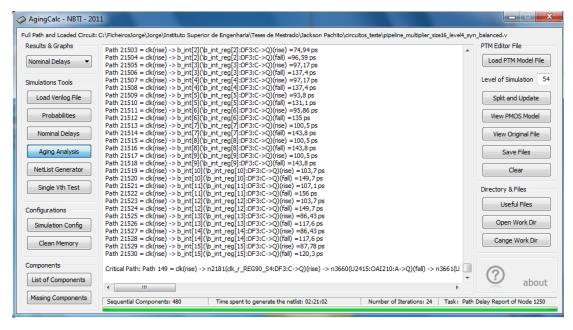

| Figura 22: Aspecto gráfico e janela principal do programa AgingCalc72                 |

| Figura 23: Pormenor da janela do programa AgingCalc, com as principais                |

| funcionalidades agrupadas no menu Simulation Tools                                    |

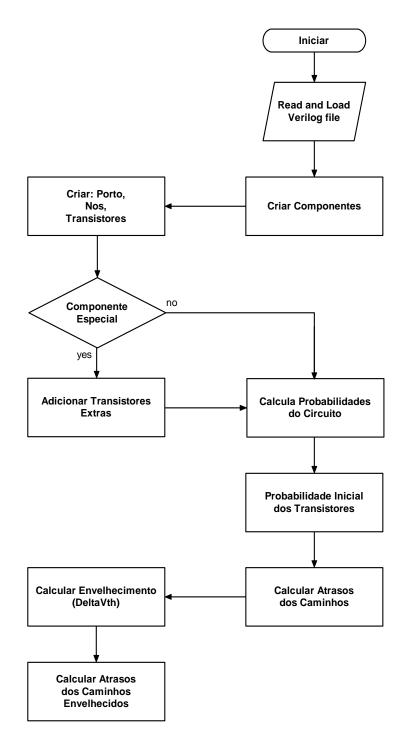

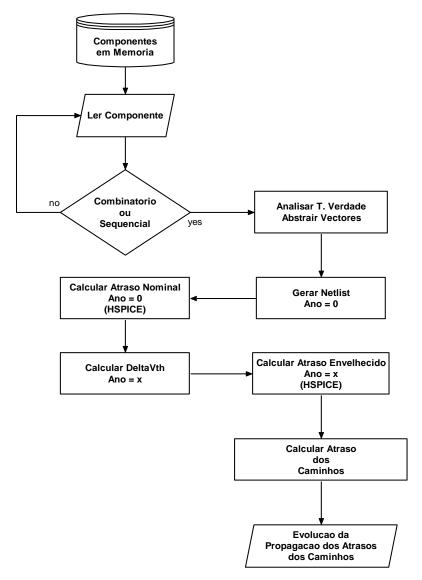

| Figura 24: Fluxograma geral da aplicação AgingCalc                                    |

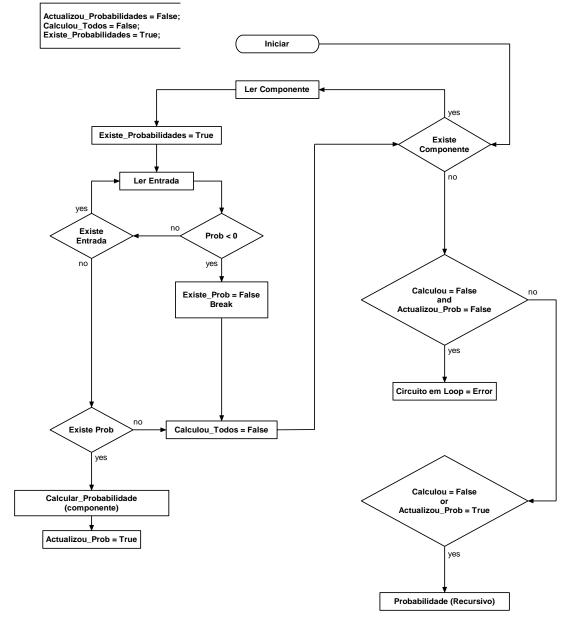

| Figura 25: Fluxograma do procedimento <i>Probabilidades</i>                           |

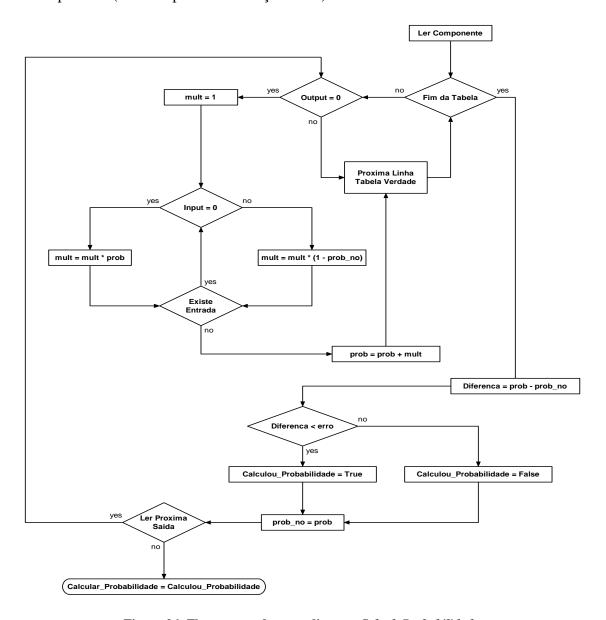

| Figura 26: Fluxograma do procedimento CalculaProbabilidades                           |

| Figura 27: Circuito sequencial genérico                                               |

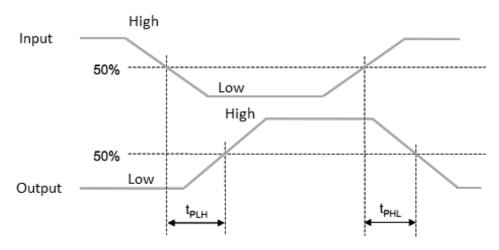

| Figura 28: Tempos de propagação de subida t <sub>PLH</sub> e descida t <sub>PHL</sub> |

| Figura 29: Fluxograma para obter a propagação dos atrasos das portas e dos            |

| caminhos81                                                                            |

| Figura 30: Sub-circuito de exemplo para cálculo dos tempos de propagação na porta     |

| lógica NAND2082                                                                       |

| Figura 31: Evolução da degradação do Vth do transístor PMOS com variação da           |

| temperatura86                                                                         |

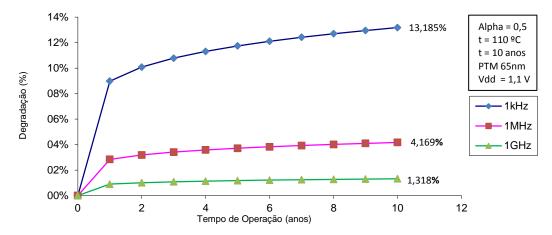

| Figura 32: Evolução da degradação do transístor PMOS com variação da frequência.      |

| 87                                                                                    |

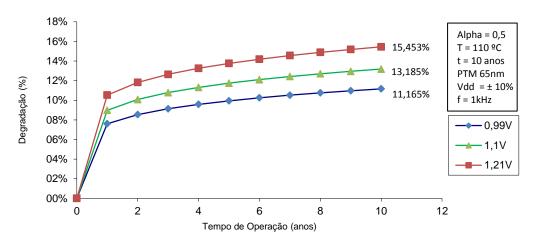

| Figura 33: Evolução da degradação do transístor PMOS com variação da tensão de        |

| alimentação V <sub>DD</sub> 88                                                        |

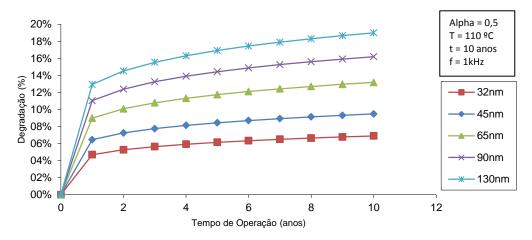

| Figura 34: Evolução da degradação do transístor PMOS com variação da tecnologia       |

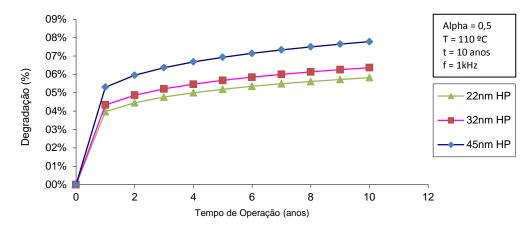

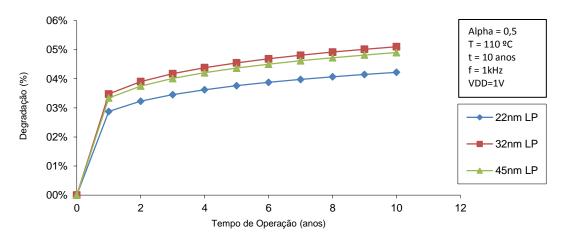

| de fabricação para tecnologias de dieléctrico normal e $V_{DD}$ nominal 89            |

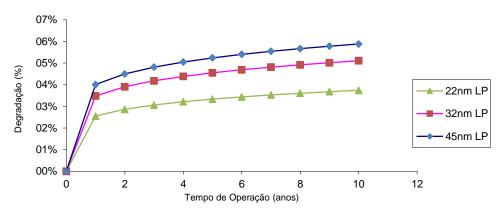

| Figura 35: Evolução da degradação do transístor PMOS Low Power (LP) com               |

| variação da tecnologia de fabricação utilizando material dieléctrico high-K           |

| e V <sub>DD</sub> nominal90                                                           |

| Figura 36: Evolução da degradação do transístor PMOS High Performance (HP) com        |

| variação da tecnologia de fabricação utilizando material dieléctrico high-K           |

| e V <sub>DD</sub> nominal90                                                           |

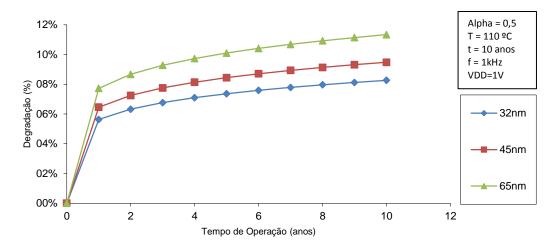

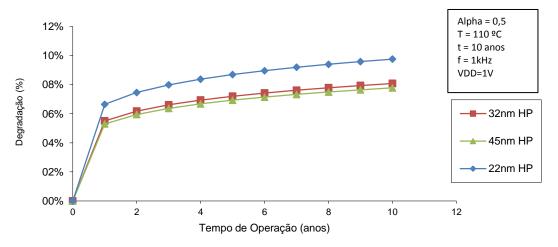

| Figura 37: Evolução da degradação do transístor PMOS com variação da tecnologia       |

| de fabricação para tecnologias de dieléctrico normal e V <sub>DD</sub> constante 91   |

ÍNDICE DE FIGURAS xiii

| Figura 38: Evolução da degradação do transístor PMOS Low Power (LP) com                |

|----------------------------------------------------------------------------------------|

| variação da tecnologia de fabricação utilizando material dieléctrico high-K            |

| e V <sub>DD</sub> constante                                                            |

| Figura 39: Evolução da degradação do transístor PMOS High Performance (HP) com         |

| variação da tecnologia de fabricação utilizando material dieléctrico high-K            |

| e V <sub>DD</sub> constante                                                            |

| Figura 40: Degradação do CP do circuito $PM\_4-2\_balanced$ , para a tecnologia PTM    |

| 65nm, com V <sub>DD</sub> = 1,1V, T=110°C e f=500Hz97                                  |

| Figura 41: Degradação do CP do circuito <i>PM_4-2_balanced</i> , para a tecnologia PTM |

| 65nm, com V <sub>DD</sub> = 1,1V, T=110°C e f=10Hz                                     |

| Figura 42: Evolução dos tempos de propagação dos 2 CP do circuito $PM\_4$ -            |

| $2\_balanced$ , para a tecnologia PTM 65nm, com $V_{DD}=1.1V$ , T=110°C e              |

| f=10Hz98                                                                               |

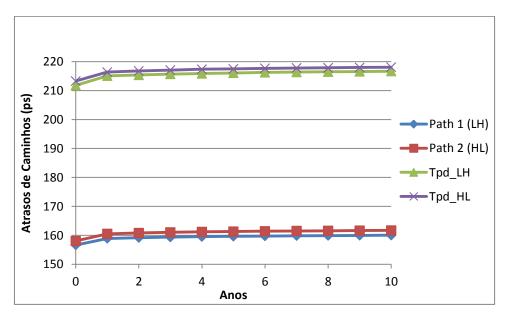

| Figura 43: Comparação dos resultados para cálculos de atrasos para o circuito          |

| $20$ _invs, para a tecnologia PTM 65nm, com $V_{DD} = 1.1V$ , T=110°C e                |

| f=500kHz                                                                               |

# ÍNDICE DE TABELAS

| Tabela 1: Parâmetros das tecnologias PTM                                               |

|----------------------------------------------------------------------------------------|

| Tabela 2: Tabela de verdade do Inversor                                                |

| Tabela 3: Tabela de verdade da porta OAI210                                            |

| Tabela 4: Tabela de verdade da porta AOI210                                            |

| Tabela 5: Tabela de verdade da porta XOR20                                             |

| Tabela 6: Tabela resumo da Classe TComponente. 62                                      |

| Tabela 7: Tabela resumo da Classe TPorto. 63                                           |

| Tabela 8: Tabela resumo da Classe TTransistor                                          |

| Tabela 9: Tabela resumo da Classe TNo. 63                                              |

| Tabela 10: Tabela resumo da Classe TDelay                                              |

| Tabela 11: Tabela de verdade da porta NAND20.                                          |

| Tabela 12: Descrição dos circuitos de referência utilizados                            |

| Tabela 13: Caracterização da estrutura dos circuitos de referência utilizados 93       |

| Tabela 14: Resultados do cálculo das probabilidades nos nós nos circuitos de teste. 94 |

| Tabela 15: Resultados da análise de atrasos sem envelhecimento, para a tecnologia      |

| PTM 65nm, com V <sub>DD</sub> = 1,1V, T=110°C e f=500kHz95                             |

| Tabela 16: Resultados da análise de atrasos com envelhecimento a 10 anos, para a       |

| tecnologia PTM 65nm, com V <sub>DD</sub> = 1,1V, T=110°C e f=500kHz96                  |

## **ACRÓNIMOS**

ASIC Application Specific Integrated Circuit, ou circuito integrado

de aplicação específica

ATPG Automatic Test Pattern Generator, ou gerador automático para

padrões de teste

CI Circuito Integrado

CMOS Complementary Metal-Oxide Semiconductor, ou

semiconductor de metal e óxido de lógica complementar

(família lógica)

CP Critical Path, ou caminho crítico (o caminho com maior

tempo de propagação)

**EM** Electro-Migration, ou migração eléctrica

**FF** Flip-flop

**FPGA** Field Programmable Gate Array, ou matriz de portas

programáveis

H Hidrogénio (símbolo químico)

**HCA** Hot Carrier Aging, ou envelhecimento por portadores quentes

**HCI** Hot Carrier Injection, ou inserção de portadores quentes

IT Interface Traps, ou obstáculos à passagem da corrente

eléctrica, formados no interface Si-SiO<sub>2</sub>

LTD Long Term Degradation, ou degradação em períodos de

tempo longos (referente a modelo de degradação)

**NBTI** Negative Bias Temperature Instability, ou instabilidade na

temperatura em polarização negativa

NMOS N-type Metal-Oxide Semiconductor, ou semicondutor de metal

e óxido do tipo N (transístor ou família lógica)

**NMOSFET** *N-type Metal Oxide Semiconductor Field-Effect Transistors*,

ou transístor semicondutor de metal e óxido de efeito de

campo do tipo N

XVIII ACRÓNIMOS

**PBTI** Positive Bias Temperature Instability, ou instabilidade na

temperatura em polarização positiva

**PDF** Path Delay Faults, ou faltas de atrasos em caminhos

PI Primary Input, ou entrada primária

**PHOS** P-type Metal-Oxide Semiconductor, ou semicondutor de metal

e óxido do tipo P (transístor ou família lógica)

**PMOSFET** P-type Metal Oxide Semiconductor Field-Effect Transistors,

ou transístor semicondutor de metal e óxido de efeito de

campo do tipo P

PO Primary Output, ou saída primária

PTM Predictive Technology Model, ou modelo preditivo da

tecnologia (referente a modelos SPICE de transistores)

**PVT** Process, power-supply Voltage and Temperature, ou processo

(V), tensão de alimentação (V) e temperatura (T) (variações)

**PVTA** Process, power-supply Voltage, Temperature and Aging, ou

processo (V), tensão de alimentação (V), temperatura (T) e

envelhecimento (A) (variações)

**R-D** Reaction – Diffusion, ou reacção – difusão (modelo)

SI Secondary Input, ou entrada secundária

**Si** Silício (símbolo químico)

SiO2 Dióxido de Silício

SIV Stress Induced Voids, lacunas induzidas por stresse

SM Stress Migration, ou migração devida ao stresse

SO Secondary Output, ou saída secundária

T Temperatura

TC Thermal Cycling, ou fase termal

TV Tabela de Verdade

TDDB Time Dependent Dielectric Breakdown, ou quebra no

dieléctrico dependente do tempo

TID Total Ionizing Dose, ou dose de ionização total (efeito

cumulativo da ionização de um circuito ou semicondutor)

V Power-supply Voltage, ou tensão de alimentação (variações)

VT Power-supply Voltage and Temperature, ou tensão de

alimentação (V) e temperatura (T) (variações)

ACRÓNIMOS xix

Vth

*Threshold Voltage*, ou tensão limiar de condução dos transístores MOSFET (valor que pode variar)

O envelhecimento, de uma forma geral, pode ser entendido como a consequência da passagem do tempo ou como o processo cronológico pelo qual um indivíduo se torna mais velho. Em biologia, o processo natural de envelhecimento, ou o conjunto de fenómenos associados a este processo, denomina-se por "senescência" e caracteriza-se pelo envelhecimento do organismo como um todo, ligado, entre outros fenómenos, ao envelhecimento celular [60]. Este envelhecimento é geralmente caracterizado pela diminuição da capacidade de responder a desafios da função orgânica, desafios esses que, em geral, oneram a capacidade funcional dos órgãos e sistemas (que diminui com o passar dos anos).

De forma interessante, em indivíduos jovens e saudáveis, esta capacidade funcional encontra-se muito além do necessário para o quotidiano, de forma que existe uma denominada reserva funcional [60]; o envelhecimento fisiológico, ou normal, pode também ser entendido como uma diminuição lenta e progressiva desta reserva funcional, de forma a diminuir a capacidade de resposta a desafios. Por esta razão, a morte é a consequência final do envelhecimento.

## 1.1 ENVELHECIMENTO EM CIRCUITOS INTEGRADOS

É interessante verificar que, tal como os organismos vivos, os circuitos integrados apresentam, durante a sua vida útil, um processo de degradação das suas características iniciais muito semelhante ao envelhecimento fisiológico. Também os circuitos vão perdendo as suas características iniciais, ou vão modificando lentamente o seu comportamento. Assim, a esse processo de degradação também chamamos de envelhecimento. É um processo lento e cumulativo, em que ocorre um desgaste dos circuitos provocado pelo tempo de operação e condições de funcionamento, com origem em diversos factores, como temperatura, tensão de alimentação, humidade,

frequência de operação, radiação exterior presente, etc [2][10][30]. No fundo, o envelhecimento é provocado por todos os mecanismos que acabam por alterar os parâmetros físicos e eléctricos dos circuitos, diminuindo o seu tempo de vida útil [5].

Para além disso, o envelhecimento fisiológico provoca normalmente a diminuição da capacidade de responder aos estímulos, que nos circuitos digitais pode ser representada pelo tempo de resposta das células, ou pelo tempo de propagação dos caminhos combinatórios, associado à menor condutividade média dos transístores. Enquanto o aumento dos tempos estiver garantido pelo tempo de segurança (definido normalmente por time slack, ou seja a margem de tempo que resta num período, depois de subtraído o tempo de propagação do caminho) existente dentro do período de operação dos circuitos, não ocorrerá nenhum erro de sincronismo [68]. No entanto, se o tempo de propagação aumentar, potenciado por variações do processo de fabrico (Process variations), ou por variações na tensão de alimentação (power-supply Voltage variations), ou por variações na temperatura de operação (Temperature variations), ou pelo envelhecimento (Aging variations), ou por um somatório de todos os efeitos (PVTA variations), ocorre um erro de sincronismo [72]. As células de memória (normalmente os flip-flops) não capturam o valor correcto, mas um valor atrasado, devido ao aumento do tempo de propagação dos caminhos combinatórios que terminam na entrada da célula de memória [8]. Assim, embora as variações PVT possam provocar os mesmos erros de sincronismo que as variações provocadas pelo envelhecimento, como estas últimas são variações cumulativas, fazem com que o tempo de vida útil diminua, porque os circuitos integrados (CI) digitais começam a ter cada vez mais propensão para falhar, por ficarem mais lentos [6][7][30].

Pelo exposto atrás, mais uma vez é interessante verificar a extraordinária semelhança com os organismos vivos, onde podemos comparar a reserva funcional com o tempo de segurança ou *time slack*. Gradualmente a degradação provocada pelo envelhecimento altera os parâmetros eléctricos dos transístores e, consequentemente, do circuito [1], até ao ponto em que o equipamento, no seu todo, deixa de funcionar devido a falhas críticas (a morte, nos organismos vivos).

O envelhecimento dos circuitos integrados tem sido alvo de extensa pesquisa na comunidade científica [2][3][4][9]. Diversos factores contribuem para degradar a longo prazo a estrutura do transístor, como o *Negative Bias Temperature Instability* (NBTI) [28][31], *Hot Carrier Injection* (HCI) [14][20], *Electro-Migration* (EM)

[16][17], Time Dependent Dielectric Breakdown (TDDB) [15][19] e Stress Induced Voids (SIV) [23], Thermal Cycling (TC) [15], Stress Migration (SM) [24], ou Total Ionizing Dose (TID) [94]. No entanto, o efeito considerado dominante no processo de envelhecimento é o NBTI, que é caracterizado por afectar a condução dos transístores PMOS, traduzindo-se esse efeito num aumento da sua tensão limiar de condução, Vth [25]. Estas alterações de Vth irão modificar os tempos de propagação dos caminhos, alterando em última análise a performance dos circuitos integrados e podendo causar uma falha de atraso (delay-fault). Se pensarmos em aplicações onde a segurança é crítica (por exemplo, para aplicações da indústria automóvel), estas falhas não podem ocorrer [69].

## 1.2 ENQUADRAMENTO DO TRABALHO

Já existem diversos trabalhos publicados que estudam o impacto do efeito NBTI no desempenho dos circuitos integrados [39][41]. Soluções para tornar os circuitos integrados mais tolerantes a variações e degradações de *Vthp* foram já apresentados em [61][62], e em [3] é mostrado como a optimização do projecto do circuito integrado pode minimizar a degradação de performance provocada pelo efeito NBTI. Para além disso, foram apresentadas em [27][63][64][65] várias topologias de sensores de envelhecimento para, globalmente, detectar a degradação do desempenho do circuito.

Porém, o desempenho temporal de um circuito é afectado por muitos factores para além do envelhecimento (como por exemplo o *crosstalk* [66], ou o *IR-drop* [67], e muitos outros), dos quais se destacam as variações de processo, da tensão de alimentação ou da temperatura (*Process, power-supply Voltage and Temperature* – PVT – *variations*) [68]. Aliás, o efeito cumulativo de muitos destes factores pode provocar uma situação de aumento extraordinário nos tempos de propagação de um circuito, conduzindo à ocorrência das falhas de atraso.

Por outro lado, pequenos defeitos que não se manifestaram em falhas durante a produção, podem vir a tornar-se críticos durante a vida útil do circuito ao serem potenciados por variações de PVT e de envelhecimento (PVTA, *PVT and Aging*). Assim, é importante estudar quais os caminhos onde é mais provável a ocorrência de

erros de desempenho, para podermos actuar sobre os componentes onde as falhas críticas realmente ocorrem.

Um tipo diferente de sensores de envelhecimento foi apresentado por M. Agarwal et al. em [58], realizando uma previsão de falha sobre as células de memória que capturam os erros de desempenho. A ideia subjacente é antecipar os erros no sistema, antes de eles ocorrerem. Este conceito foi posteriormente melhorado e utilizado com o objectivo de monitorizar os erros de desempenho durante toda a vida útil de um circuito em [69][70][71]. O objectivo é observar o envelhecimento numa situação real, perante a existência de variações heterogéneas da tensão de alimentação e da temperatura (VT, *power-supply Voltage and Temperature*), para antecipar a falha crítica. Mais recentemente, este sensor foi ainda aperfeiçoado, surgindo um sensor inovador para monitorização local do envelhecimento e previsão das falhas de desempenho que ainda está em desenvolvimento [72].

#### 1.3 OBJECTIVOS DO TRABALHO

Ao consideramos a operação dos sensores de envelhecimento atrás referidos, que monitorizam a performance do circuito localmente, existem dois aspectos que são críticos para que os sensores sejam eficazes: monitorizar as células de memória correctas, e garantir que os caminhos críticos são efectivamente activados e testados. Assim, os sensores são inseridos no final dos caminhos críticos e dos caminhos quase críticos (caminhos com os maiores tempos de propagação). Contudo, a questão fundamental é: "Quantos caminhos quase críticos devem ser monitorizados?" Como é referido em [3], os caminhos pequenos têm margens de segurança (time slacks) muito grandes que conseguem acomodar as degradações provocadas pelas variações PVTA, os caminhos críticos são conhecidos e podem ser monitorizados, mas os caminhos quase críticos podem envelhecer de forma diferente dos restantes caminhos do circuito e poderão tornar-se críticos com os efeitos do envelhecimento. Como os caminhos quase críticos são muitos e estão a crescer exponencialmente à medida que a tecnologia decresce em tamanho, torna-se importante prever como estes caminhos envelhecem. Torna-se portanto imperativo a existência de uma metodologia completa para prever o envelhecimento em circuitos integrados digitais, de forma a identificar INTRODUÇÃO 5

quais dos caminhos quase críticos têm mais probabilidades de se tornarem críticos quando os efeitos do envelhecimento influenciarem o comportamento e desempenho do circuito. Este é o objectivo primordial do trabalho documentado na presente dissertação de mestrado.

A modelação dos efeitos de NBTI nos transístores, tanto na operação estática (constant stress), como na operação dinâmica (alternância entre o stress e o recovery), por períodos curtos, ou até a longo prazo (long term), já foram propostos em [46][49]. Estes trabalhos mostram como calcular qual o desvio em Vth, de um transístor PMOS, provocado pelo efeito NBTI. Estes resultados, aliados aos resultados de uma análise temporal estática com dados estatísticos (Statistical Static Timing Analysys, SSTA), ou ao estudo das probabilidades de operação dos componentes do circuito apresentados em [81], poderão permitir prever e extrapolar os desvios em Vth, provocados pelo envelhecimento, para todos os transístores presentes num circuito.

Assim, o primeiro objectivo do trabalho é definir uma biblioteca de células ao nível de transístor, através de descrições SPICE de cada porta lógica e utilizando como modelos de transístores os modelos de Berkeley *Predictive Tecnology Models*, PTM [74]. Essa biblioteca deve ser genérica o suficiente para permitir a utilização de diferentes tamanhos de transístor e de tecnologia, para poder serem analisadas várias tecnologias nano métricas: 130nm, 90nm, 65nm, 45nm, 32nm e 22nm [74].

O segundo objectivo é analisar um circuito ao nível de porta lógica e, com base em probabilidades iniciais definidas para as suas entradas primárias (probabilidade de ocorrência de '0' lógico em cada entrada) e analisando o comportamento lógico de cada porta que compõe o circuito, pretende-se calcular as probabilidades de ocorrência do nível baixo (valor lógico '0') em todos os nós que compõem o circuito. Esta informação é fundamental para definir qual a probabilidade de operação de cada transístor dentro das portas lógicas, mais propriamente a probabilidade de condução de cada transístor. É de notar que apenas irão ser calculadas as probabilidades de operação dos transístores PMOS, uma vez que é sobre estes que incide maioritariamente o efeito NBTI, o efeito dominante no envelhecimento, como já foi referido.

O terceiro objectivo é, utilizando os modelos de envelhecimento a longo prazo por NBTI definidos em [46][59], automatizar o cálculo de todas as variações do parâmetro *Vth* nos transístores PMOS para um circuito, ao longo do suposto tempo de utilização do circuito. O resultado será uma descrição SPICE em que o parâmetro *Vth*

é diferente entre transístores, de acordo com a probabilidade de operação de cada transístor e com o tempo de envelhecimento pretendido. É de notar que, para a obtenção da descrição SPICE com todas as modelações de *Vth*, é necessário que a biblioteca de células seja genérica o suficiente de forma a permitir essas modelações nas portas lógicas.

O quarto objectivo é automatizar a simulação SPICE para todos os componentes lógicos do circuito. Cada simulação permitirá determinar os tempos de propagação de uma porta lógica, de acordo com o tempo de utilização e envelhecimento modelado nos parâmetros *Vth* dos seus transístores.

O quinto objectivo é, com base nos tempos de propagação das portas lógicas, obter todos os caminhos combinatórios e calcular os seus tempos de propagação. Esta análise permite obter, para cada caminho, qual a sua degradação ao longo do tempo de envelhecimento do circuito, e prever como o circuito se irá comportar quando os efeitos do envelhecimento são considerados. Esta análise permite obter aquele que foi definido como o objectivo principal, já referido, que é analisar quais os caminhos que poderão se tornar críticos na vida útil de um circuito.

O último objectivo, e de forma mais genérica, é definir uma metodologia completa para prever o envelhecimento dos circuitos integrados digitais, reunindo todos os objectivos anteriormente definidos, e elaborar uma ferramenta de *software* que automatize este método para prever o comportamento dos circuitos digitais com um determinado tempo de vida e nível de envelhecimento.

#### 1.4 CONTEXTO DO TRABALHO

O presente trabalho de investigação foi realizado no Instituto Superior de Engenharia da Universidade do Algarve, em estreita colaboração com o INESC-ID Lisboa. O grupo de trabalho constituído nos 2 institutos portugueses, e com parcerias desenvolvidas com outros institutos e universidades estrangeiras, como a Universidade de Vigo em Espanha, o INAOE no México e a PUCRS no Brasil, tem vindo nos últimos anos a realizar trabalho de investigação na área dos sensores de envelhecimento, tanto para circuitos integrados de aplicação específica (ASIC, Application Specific Integrated Circuit) como para circuitos emulados em FPGA

(*Field-Programable Gate Array*). Para além disso, em paralelo com o presente trabalho de mestrado, está a ser desenvolvido um novo sensor de envelhecimento em outra tese de mestrado desenvolvida no ISE (já publicado em [72]).

O presente estudo é, portanto, de fulcral importância na correcta utilização dos sensores de envelhecimento. A análise e previsão do comportamento dos circuitos envelhecidos permitirá reduzir a complexidade do *hardware* necessário num circuito de monitorização do envelhecimento, pela redução do número de sensores necessários, mesmo garantindo uma boa fiabilidade do circuito sujeito a variações PVTA [73].

O trabalho foi ainda aceite para publicação numa conferência internacional da especialidade, em [73] (ainda não apresentado, à data de escrita desta tese).

## 1.5 ORGANIZAÇÃO DO DOCUMENTO

O presente documento está organizado como se descreve em seguida.

No capítulo 2 são apresentados os principais fenómenos e efeitos que contribuem para o envelhecimento dos circuitos integrados digitais CMOS, com especial destaque para o fenómeno NBTI. São apresentados os modelos que permitem calcular a variação do parâmetro *Vth* dos transístores PMOS, na presença de efeitos a longo prazo provocados pela instabilidade NBTI, bem como uma breve referência a trabalhos que propõe técnicas para minimizar os efeitos degradantes do NBTI.

No capítulo 3 é apresentada a metodologia para prever o envelhecimento dos circuitos digitais CMOS. A metodologia consiste na modelação do envelhecimento dos transístores CMOS, utilizando o cálculo da probabilidade de operação de cada transístor PMOS presente no circuito, a definição de uma biblioteca CMOS genérica, para ser utilizada em simulações SPICE, e a previsão final do impacto que a degradação do circuito pelo fenómeno NBTI terá, previsivelmente, na sua performance (ou desempenho).

No capítulo 4 é feito a descrição da ferramenta de *software* desenvolvida para automatizar todo o processo de modelação da degradação do efeito NBTI, no qual é apresentado as suas características gerais e funcionalidades. Para além disso, faz-se

uma breve descrição sobre o seu enquadramento com a metodologia de inserção de sensores de envelhecimento.

Os resultados do estudo realizado são apresentados no capítulo 5. Este capítulo tem por objectivo perceber como se comporta a evolução da degradação do tempo de atraso de um transístor sob os efeitos do NBTI, bem como em circuitos digitais CMOS de referência. Também apresenta resultados de simulação sobre a relação existente entre o NBTI e factores tais como a temperatura, o campo eléctrico e tecnologias de fabricação dos CMOS.

Por último, no capítulo 6 as conclusões do trabalho realizado, bem como futuras investigações, são apresentadas e discutidas.

### 2. ENVELHECIMENTO EM NANO TECNOLOGIAS CMOS

Como tudo na vida, os circuitos também vão perdendo as suas características iniciais, ou vão modificando lentamente o seu comportamento. Diz-se, portanto, que envelhecem. Mas, é de notar que este envelhecimento não é a deterioração ocasional e aleatória que pode danificar um componente (muitas vezes potenciada por variações extremas no processo de fabrico), nem a deterioração provocada por operações em situações muito particulares de *stress* que danificam irremediavelmente um componente (como por exemplo, a entrada em disrupção de um condensador, ou a quebra das ligações eléctricas num componente). O envelhecimento aqui reportado trata-se de uma modificação generalizada no comportamento de todos os transístores que compõem um circuito integrado [40], modificação essa que é lenta, progressiva e diferente de transístor para transístor, e que se traduz normalmente numa diminuição da sua capacidade de condução da corrente eléctrica (que no caso do NBTI, corresponde ao aumento do valor absoluto do *Vth* dos transístores do tipo P).

Por outro lado, a constante redução do tamanho da tecnologia, necessária para manter actual a Lei de Moore<sup>1</sup>, também potencia o envelhecimento dos circuitos integrados CMOS. A existência de transístores mais pequenos, em que a condução é feita por um menor número de iões e electrões, torna os circuitos e componentes mais vulneráveis a influências externas. O aumento da variação de qualquer parâmetro existente, em nano tecnologias conduz a maiores incertezas no comportamento eléctrico dos circuitos e a menores níveis de energia necessários para modificar esse comportamento, ficando os circuitos mais susceptíveis a modificações da sua estrutura e do seu comportamento. O envelhecimento é, portanto, mais acelerado em nano tecnologias [30][43].

<sup>&</sup>lt;sup>1</sup> Gordon Moore vaticinou que o número de transístores usados num único circuito integrado duplica, aproximadamente, a cada dois anos. Esta lei foi descrita num artigo publicado em 1965 [75], referindose aos resultados obtidos desde a invenção do CI em 1958 até 1965, e prevendo que a mesma relação se manteria pelo menos por mais 10 anos. Na realidade, a relação manteve-se até hoje, mais de 50 anos depois, e espera-se que continue pelo menos até 2015 ou 2020.

Em tecnologias anteriores às nano métricas, este envelhecimento também ocorria, mas como os efeitos sobre os circuitos eram menores, eles não se faziam notar durante a vida útil dos circuitos, estando garantidos pelos generosos tempos de segurança (time slacks) normalmente utilizados. Então, dizia-se que os circuitos, praticamente, não envelheciam. Porém, em nano tecnologias, e mais concretamente no caso dos circuitos integrados digitais, o envelhecimento causa normalmente o aumento dos tempos de propagação das portas lógicas e, consequentemente, dos tempos de propagação dos caminhos. Se o tempo de propagação aumentar, causado nomeadamente por variações PVTA, pode ocorrer um erro de sincronismo nos circuitos digitais síncronos, quando o tempo de segurança existente no período não conseguir acomodar este aumento dos tempos de propagação. Neste caso, os flip-flops (e as células de memória síncronas) não conseguem capturar o valor correcto, pois ele chega atrasado em relação ao sinal de relógio (que marca o sincronismo) [68]. A existência de variações PVT em conjunto com a degradação cumulativa provocada pelo envelhecimento (ou seja, no geral variações PVTA), faz reduzir o tempo de vida útil dos circuitos. Na verdade, como referido em [69], se considerarmos aplicações em nano tecnologias onde a segurança é crítica e onde os circuitos têm tempos médios de utilização relativamente elevados, como é o caso da electrónica para a indústria automóvel onde os camiões têm tempos médios de vida útil de 15 a 20 anos (e onde a electrónica utilizada já é maioritariamente em tecnologias nano métricas [70]), então a degradação cumulativa provocada pelo envelhecimento começa a tornar-se crítica para o correcto desempenho dos circuitos. É imperativo que o envelhecimento seja considerado na fase de projecto, de forma a prever a sua existência e garantir que os circuitos se mantêm a funcionar durante o tempo de vida útil esperado, sem erros, sobretudo nas novas tecnologias nano métricas [73].

Os principais fenómenos e mecanismos que provocam a degradação nos CI digitais são: Negative Bias Temperature Instability (NBTI) [36][38], Hot Carrier Injection (HCI) [14][20] (também conhecido como Hot Carrier Aging, HCA [12]), Electro-Migration (EM) [16][17], Time Dependent Dielectric Breakdown (TDDB) [15][19], Stress Induced Voids (SIV) [23], Thermal Cycling (TC) [15], Stress Migration (SM) [24] e Total Ionizing Dose (TID) [94]. De todos estes os fenómenos, o NBTI destaca-se como sendo aquele que provoca maior degradação nos CIs,

afectando os transístores tipo p, ou seja, os PMOSFET (P-type Metal Oxide Semiconductor Field-Effect Transistors).

O presente capítulo apresenta um breve estudo sobre os principais fenómenos descritos atrás que provocam o envelhecimento nos circuitos integrados. Destaca-se uma descrição mais detalhada do fenómeno NBTI, uma vez que é o efeito considerado dominante de entre todos e o utilizado neste trabalho de investigação para prever o impacto do envelhecimento nos circuitos integrados digitais.

#### 2.1 FENÓMENO NBTI

Embora, recentemente esteja sendo dado muito interesse ao seu estudo, o fenómeno NBTI foi dado a conhecer pela primeira vez em 1967 por Deal e seus colegas (como referido em [30][31]), mas o seu efeito só se tornou significativo para tecnologias abaixo dos 130nm de comprimento de canal [47]. Pode ser simplesmente caracterizado pelo aumento do valor absoluto da tensão limiar de condução (*threshold voltage*, ou *Vth*), ocorrendo nos transístores PMOSFET. O seu nome vem da analogia com a *Na+ induced negative bias temperature instability*, que também causa o aumento do *Vth* [25].

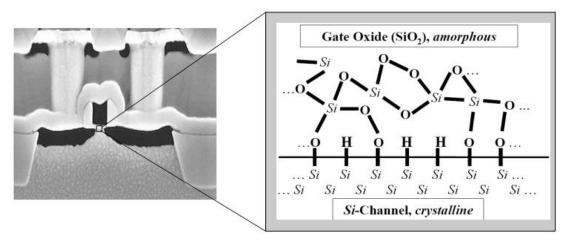

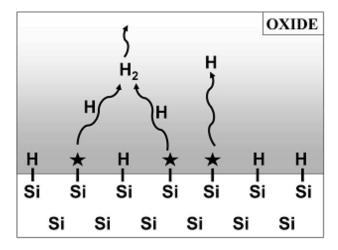

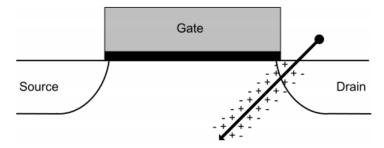

Analisando com mais detalhe o fenómeno NBTI, este ocorre nos transístores PMOSFET negativamente polarizados (com V<sub>GS</sub> < 0V) e com temperaturas elevadas, e é uma consequência do aparecimento de novos dadores de electrões (conhecidos por *Interface Traps*, IT) no canal, que são no fundo obstáculos à condução no semicondutor que se formam na interface entre o Silício e o Dióxido de Silício (Si - SiO<sub>2</sub>). Durante a formação desta interface, criam-se ligações entre as moléculas de Si do canal (Silício cristalino) e as moléculas de Oxigénio do dieléctrico SiO<sub>2</sub>. Porém, devido às diferenças nas estruturas entre os 2 materiais (desfasamentos), ficam algumas moléculas de Silício cristalino do canal sem ligação a moléculas de Oxigénio (ligações químicas pendentes, de Si), enfraquecendo as ligações entre os materiais, criando instabilidades e dando origem a possíveis dadores de electrões (pois ficam alguns electrões sem ligação). Por essa razão, no processo de fabricação tradicional de MOSFETs em Silício, os transístores são formados em ambiente hidrogenado (ambiente com hidrogénio (H)), de forma a tornar passivas as ligações de Silício que

Figura 1: Representação física da estrutura do transístor PMOS onde se dão as reacções químicas (esquerda) e representação química da estrutura da interface Si-SiO<sub>2</sub> (direita) [50].

ficam livres, pela criação de ligações ao H (ver Figura 1) [26][28][29]. Este método tradicional de fabricação provou ser, durante décadas, uma boa solução para a existência de instabilidades nas interfaces com o semicondutor, fazendo diminuir a existência deste tipo de obstáculos à condução. Contudo, os constantes esforços para miniaturizar os MOSFET, (isto é, a diminuição da espessura do óxido, que conduz a elevados campos eléctricos no óxido e a outras modificações do processo, como a nitridação dos óxidos para prevenir a difusão de átomos de Boro da área dopada p+, reduzindo correntes de fuga [25]) e a operação a altas temperaturas (derivada da dissipação de potência dos circuitos ou das condições ambiente) aceleram, com o tempo, a quebra de ligações na interface Si-SiO<sub>2</sub> durante a operação do dispositivo. A existência de novos dadores de electrões no canal do transístor PMOS faz aumentar a tensão limiar de condução, reduzindo a mobilidade [78]. De uma forma geral, com o passar do tempo aumenta a degradação da tensão limiar (Vth), da corrente de dreno, das capacidades, da transcondutância, e a confiança no transístor começa a merecer uma importante preocupação [25]. De salientar ainda que a degradação destes parâmetros é fortemente afectado pela temperatura, ou seja, quanto maior for a temperatura, maior é a degradação [33][34].

Pelo exposto, é fácil perceber que o fenómeno NBTI, como o próprio nome indica, é uma instabilidade que é provocada nos transístores PMOS quando estes são polarizados negativamente [32] e operando a altas temperaturas [35].

Num circuito digital, a operação de um transístor PMOS corresponde normalmente à ligação da porta (gate) ao nivelo lógico '0', o que equivale a ter  $V_{GS}$  =

–V<sub>DD</sub>. Nesta condição, também conhecida como a fase de *stress* do transístor, o campo eléctrico exercido entre a porta e o canal do transístor tem uma intensidade máxima. Para além disso, se existir uma energia térmica maior (temperatura elevada), estão reunidas as condições que favorecem a quebra das ligações químicas (as ligações de Si e H na interface Si-SiO<sub>2</sub>), aumentando a instabilidade [36][37] e criando obstáculos à condução (que fazem diminuir a mobilidade dos buracos, fazendo diminuir a corrente de condução, I<sub>D</sub> [3]).

Na condição em que o nível lógico da porta é alto ( $V_{GS}=0V$ , ou  $V_{G}=V_{DD}$ ), algumas das ligações Si-H são restabelecidas, sendo por isso esta fase também chamada de fase de recuperação (recovery) [9][37]. No entanto, nem todas as ligações são restabelecidas, o que conduz a uma degradação lenta e cumulativa do transístor. Isto é, considerando o transístor como uma chave (como acontece nos circuitos digitais), o tempo entre o corte e a condução, e vice-versa, será maior [10]. Por esse facto, o NBTI é o mecanismo de envelhecimento que mais danos causa nos CI digitais, sendo actualmente o que mais preocupa a comunidade científica na área das nano tecnologias e, portanto, o mais investigado [2]. O aumento do Vth dos transístores, faz com que o tempo de vida útil dos PMOS seja drasticamente reduzido, aumentando os tempos de atraso das portas lógicas digitais e os tempos de respostas dos caminhos, levando a que os circuitos possam começar a falhar [9][42] e, consequentemente, todo o equipamento onde estão inseridos. De salientar ainda que em [30] é defendido que a NBTI, é um factor limitador na redução do tamanho para as próximas tecnologias.

É de notar que, de forma similar aos efeitos de NBTI nos transístores PMOS, os transístores NMOS são afectados pelo PBTI (*Positive Bias Temperature Instability*) [77], sendo que este afecta a mobilidade dos electrões quando ocorre uma polarização positiva  $V_{GS} > 0$  (e tendo como efeito a diminuição do Vth) e sendo igualmente afectado pela temperatura. Porém, os seus efeitos são diminutos quando comparados com os efeitos de NBTI nos transístores PMOS [5][7].

A explicação teórica do efeito NBTI sustenta-se, principalmente, no modelo *Reaction-Diffusion* (R-D) [9], que se apresentará na próxima secção 2.1.1.

## 2.1.1 O Modelo Reaction-Diffusion

Como referido, o modelo teórico que melhor explica a física por detrás do fenómeno de envelhecimento dos transístores PMOS devido ao NBTI é o modelo *Reaction-Diffusion* (R-D), explicado em [25] e publicado pela primeira vez em 1970 por Jeppson e Svensson [49]. O modelo é constituído por dois processos, a reacção e a difusão [9][26], que explicam que a degradação do transístor tem origem nas ligações químicas Si-H que são quebradas na interface Silício – Dióxido de Silício (Si-SiO<sub>2</sub>), ou seja, a região entre o substrato e a porta (gate), durante a polarização negativa da porta ( $V_{GS} = -V_{DD}$ ), sob forte campo eléctrico ( $E_{ox}$ ) e a altas temperaturas (T), pela geração de obstáculos à passagem da corrente no canal [48][51][52][53][54].

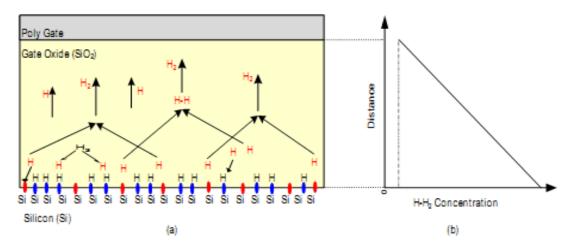

Na Figura 1 podemos observar a estrutura das ligações químicas na interface Si-SiO<sub>2</sub>, a interface entre o canal e o dieléctrico da porta do transístor. Das ligações Si-H que se vão quebrando, como resultado das vibrações térmicas das ligações químicas, vão sendo libertadas átomos de H (Figura 2 (a)). As ligações de Si livres irão actuar como possíveis dadores de electrões para o canal, criando obstáculos à condução da corrente eléctrica. Este processo é designado de Reacção (*Reaction*) no modelo R-D.

Por outro lado, os átomos de H que se libertam podem-se difundir pelo óxido fino até à gate [8][33][35], permanecendo livres ou combinando-se entre si para formar H<sub>2</sub> (Figura 2 (a)), ou até se podem voltar a recombinar com o Si de novo. Com o passar do tempo, e devido ao processo de difusão do H pelo óxido, estas moléculas vão-se afastando do canal e vão-se aproximando da porta (*gate*, tradicionalmente em

Figura 2: Distribuição do hidrogénio pelo óxido fino: (a) quebra das ligações químicas; (b) relação da concentração de ao longo do óxido fino do PMOS [33]

polisilício). Este processo designa-se por Difusão (*Diffusion*) no modelo R-D. Deste modo, o hidrogénio vai-se distribuindo ao longo do dieléctrico SiO<sub>2</sub> da porta (também chamado de óxido fino) sob a forma de H ou de H<sub>2</sub>, sendo que a sua concentração é maior junto ao canal e vai diminuindo à medida que nos aproximamos do terminal da porta (como se pode ver na Figura 2 (b)). É de notar que embora possa haver o restabelecimento das ligações Si-H originais, o processo de difusão do H pelo óxido, e o seu afastamento do canal em direcção à porta, torna mais difícil o seu processo de recombinação com o Si. Por essa razão o efeito NBTI provoca degradações lentas e cumulativas na estrutura do transístor, envelhecendo-o.

É de notar que as fases de *Stress* e Recuperação referem-se ao estado do transístor (com tensão negativa entre a porta e o canal, ou tensão de 0V), enquanto Reacção e Difusão referem-se aos processos que ocorrem no transístor. A fase de *stress* favorece a reacção de quebra das ligações Si-H; e a fase de recuperação favorece a reacção de restabelecimento das ligações Si-H. A difusão, pode ocorrer em ambas as fases [35].

# 2.1.2 Geração dos Obstáculos à Passagem de Corrente (Interface Traps)

Como mostrado atrás, o modelo R-D [44][82] assume que o NBTI resulta da dissociação das ligações químicas entre o Silício e o Hidrogénio, gerando na interface Si-SiO<sub>2</sub> novos dadores de electrões para o canal (os Si que ficam sem a ligação aos H). A existência de um campo eléctrico e a presença de temperaturas elevadas favorece a quebra das ligações Si-H e, consequentemente, a ionização do Si pela perda do electrão que ficou sem ligação ao H. A existência de cargas positivas Si<sup>+</sup> prejudica a livre circulação dos electrões pelo canal, pois cria obstáculos à passagem da corrente. Os átomos de H que se libertam, irão difundir-se pelo dieléctrico. A longo prazo, os átomos de H tendem a associar-se entre si formando moléculas de Hidrogénio (H<sub>2</sub>) [47].

A equação (1) (apresentada em [82]) resume a reacção química que resulta na geração dos obstáculos à passagem da corrente, as *Interface Traps* (IT). Em (1), Si-H refere-se a uma ligação passiva entre o Si e o H; h<sup>+</sup> refere-se a um buraco; e Si<sup>+</sup> refere-se ao Si que perdeu a ligação com o H e que perdeu um electrão para o buraco, tornando-se numa IT no canal.

$$Si-H + h^+ \leftrightarrow Si^+ + H \tag{1}$$

De acordo com [33][35][48], a taxa de geração de obstáculos à passagem a corrente na interface ( $N_{IT}$ , *number of interface traps*) depende: (i) da taxa de ligações químicas quebradas ( $k_f$ ) entre Si-H na interface Si-SiO<sub>2</sub>; e (ii) da taxa de recuperação das ligações ( $k_r$ ) antes desfeitas. Este número  $N_{IT}$  é exponencialmente dependente do campo eléctrico, bem como da temperatura e densidade de reacção das espécies. O  $N_{IT}$  pode ser quantificado através da seguinte expressão:

$$\frac{dN_{IT}}{dt} = k_f (N_o - N_{IT}) - k_r N_{IT} N_H^0$$

(2)

Na equação (2), N<sub>o</sub> e N<sup>o</sup><sub>H</sub> representam, respectivamente, a densidade inicial de ligações existentes e a densidade atómica de H na interface Si-SiO2.

Os átomos de Hidrogénio resultantes da quebra das ligações Si-H, contribuem para três sub-processos, que são: (a) a difusão em direcção à *gate*; (b) a combinação entre átomos produzindo moléculas de Hidrogénio (H<sub>2</sub>) (estas difundem em direcção à *gate* tanto na forma de H<sub>2</sub> como de H, pois as moléculas podem dissociar-se formando novamente átomos de Hidrogénio); e por último (c) a recuperação das ligações quebradas, ou seja, o Hidrogénio recombina-se novamente com o Silício (fase de recuperação), sendo que esta recombinação depende da distância a que se encontram

Figura 3: Geração de IT, difusão do H e H<sub>2</sub> em direcção à porta e combinação de átomos de H para formar H<sub>2</sub> [55].

esses átomos de H (ou seja, quanto mais perto estes átomos se encontrarem da interface maior é a probabilidade da recombinação) [7]. Na Figura 3, ilustram-se os sub-processos (a) e (b), pelo que o sub-processo (c) nada mais seria do que o sentido inverso representado pela direcção das setas. Todos estes sub-processos determinam o número de obstáculos presentes na interface substrato/porta.

A quantificação das espécies de Hidrogénio presentes junto à interface SiO<sub>2</sub>, podem ser calculadas pelas expressões (3) e (4), que exprimem, respectivamente, as quantidades de átomos e moléculas de Hidrogénio.

$$\frac{dN_{H}}{dt} = D_{H} \frac{d^{2}N_{H}}{dx^{2}} - k_{H}N_{H}^{2} + k_{H_{2}}N_{H_{2}}$$

(3)

$$\frac{dN_{H_2}}{dt} = D_{H_2} \frac{d^2N_{H_2}}{dx^2} - \frac{1}{2} k_H N_H^2 + k_{H_2} N_{H_2}$$

(4)

$N_H$  e  $N_{H_2}$  representam as densidades dos átomos e moléculas de H e  $H_2$ .  $D_H$  e  $D_{H_2}$  representam a taxa de difusão atómica e molecular de Hidrogénio e, por último,  $k_H$  e  $k_{H_2}$  representam as taxas de geração e conversão de átomos e de moléculas de Hidrogénio.

Inicialmente, os sub-processos dominantes são a quebra e a recuperação das ligações químicas na interface Si-SiO<sub>2</sub>, e a espécie de difusão dominante na camada SiO<sub>2</sub> é o de H. No entanto, se o transístor for mantido a uma polarização negativa durante um longo período de tempo, a maioria dos átomos de H convertem-se em moléculas de Hidrogénio, tornando o H<sub>2</sub> a espécie de difusão dominante junto à camada SiO<sub>2</sub>. Combinando as equações (2) e (4), obtêm-se a quantidade de IT (N<sub>IT</sub>) presentes na interface substrato/gate [33][35][56], dada pela equação (5).

$$N_{IT}(t) = \left(\frac{k_f N_o}{k_r}\right)^{2/3} \left(\frac{k_H}{k_{H_2}}\right)^{1/3} (6D_{H_2}t)^{1/6}$$

(5)

A equação (5) mostra que a quantidade de IT presente depende de diferentes subprocessos, sendo que estes, por último, dependem do campo eléctrico e/ou da temperatura, provando assim o papel relevante que a temperatura e o campo eléctrico desempenham no processo da degradação devido ao NBTI [33][35]. Segundo [7] e

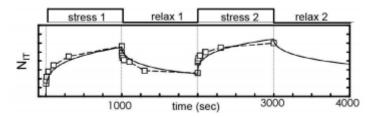

Figura 4: Quantidade de NIT junto à gate do PMOS durante as fases de stresse e recuperação [7].

como ilustrado na Figura 4, a velocidade com que ocorre a degradação (aumento do Vth) diminui com a diminuição da quantidade de ligações Si-H, por isso  $N_{IT}$  aumenta. Por outro lado, na fase de recuperação ocorre exactamente o contrário, ou seja, quanto maior a quantidade  $N_{IT}$  presente mais rápido se dá a recuperação. Contudo uma total recuperação teoricamente, só ocorre para um tempo infinitamente grande.

De acordo com os sub-processos atrás mencionados, (a), (b) e (c) (respectivamente, a difusão em direcção a gate, a combinação entre átomos produzindo moléculas de Hidrogénio ( $H_2$ ) e a recuperação das ligações quebradas), a sua análise foi melhorada em [35][55] e, por conseguinte, foi revisto e melhorado o modelo R-D, na qual, em vez dos três sub-processos, foram distinguidos quatro estágios diferentes, dependentes da geração de IT. No primeiro estágio (i), no instante inicial da fase de *stress* em que o número de IT e de Hidrogénio presentes na interface é zero ( $N_{IT} = N_H \sim 0$ ), os sub-processos de recuperação, conversão e difusão podem ser desprezadas. Nesta fase inicial, o número de IT gerados é maioritariamente dominado pela taxa das ligações químicas quebradas entre Si-H, ou seja,  $N_{IT}(t) = k_f N_0 t$ .

Durante o segundo estágio (ii), a predominância da quebra de ligações continua a produzir átomos de Hidrogénio, podendo estes participar no processo de recuperação ou na interacção com outros átomos para formar as moléculas  $H_2$ , mas sendo as densidades de H e  $H_2$  na interface muito baixas, o sub-processo de difusão (a) também pode ser desprezado. Rearranjando as equações (2) e (3), a quantidade de "armadilhas" presentes na interface,  $N_{IT}$ , é dado por:

$$N_{IT}(t) = \left(\frac{k_f N_o}{k_r}\right)^{2/3} (k_H t)^{1/3}$$

(6)

No terceiro estágio (iii), que é considerado muito curto, os sub-processos dominantes na geração de IT são: a quebra e a recuperação das ligações e a difusão de átomos de Hidrogénio. Contudo, a difusão e a dissociação molecular do  $H_2$  continuam desprezáveis. Este terceiro estágio pode ser quantificado resolvendo as equações (2) e (3), resultando em um  $N_{IT}$  dado por,

$$N_{IT}(t) = \left(\frac{k_f N_o}{k_r}\right)^{1/2} (D_H t)^{1/4}$$

(7)

E por último, no estágio (iv), a maioria dos átomos de Hidrogénio convertem-se em  $H_2$ , tornando estes na espécie dominante na geração do número de IT e dado pela equação (5) [35]. Por esta razão, a versão do modelo R-D mais utilizado na modelação do NBTI seja o  $H_2$  R-D, por considerar o processo da degradação devido ao NBTI a longo prazo (long-term) (ou seja, utiliza-se o parâmetro n com o valor aproximado de 1/6 para indicar este tipo de modelo,  $H_2$  R-D) [44][47]. Para além da conversão  $H \rightarrow H_2$ , neste estágio também acontece o processo inverso, ou seja, a dissociação do  $H_2$  em H, que por seu lado, contribui para a recuperação das ligações pendentes do Silício.

Porém, como o modelo R-D prevê a fase de recuperação quando a condição de polarização  $V_{GS} = V_{DD}$  é satisfeita, alguns átomos de H difundem em direcção ao Silício, refazendo as ligações de Si pendentes. A recuperação destas ligações pode então ser traduzida através da equação (8) [25][35],

$$N_{IT}^* = \frac{1}{2} N_H^* (\xi. D_H. t)^{1/n}$$

(8)

em que,  $N_H^*$  representa o número de átomos de Hidrogénio que recuperam as ligações pendentes do Silício e  $\xi$  é a constante de difusão na camada do óxido durante o processo de recuperação. Como se referiu anteriormente, uma total recuperação teoricamente só acontece para um tempo infinitamente grande [7], isto porque o número de IT que conseguem resistir à fase de recuperação depende das quantidades restantes das fases anteriores. Assim, o número de obstáculos resistentes é dado por:

$$N_{IT}(t) = N_{IT}(t_0) - N_{IT}^*(t)$$

(9)

em que,  $N_{IT}(t_0)$  diz respeito aos obstáculos das fases anteriores e  $N_{IT}^*$  representa os que foram recuperados.

## 2.1.3 Dependência do NBTI com a Temperatura

Nas secções anteriores falou-se na dependência do NBTI em relação à temperatura, mas, segundo os autores em [25], [33] e [35], o modelo R-D assume que a degradação por NBTI depende da temperatura, mas não apresenta nenhuma explicação física para essa dependência. Por outro lado, em [47] defende-se que esta dependência ainda não estava extensivamente explorada.

Embora exista uma aparente contradição entre a comunidade científica sobre esta matéria, alguns autores como [33], [35] e [82], defendem que a dependência do NBTI em relação à temperatura pode ser explicada pela relação de Arrhenius<sup>2</sup>, ou seja, a velocidade da maioria das reacções químicas aumenta à medida que a temperatura aumenta. Isto porque, como o sub-processo de difusão de H e H<sub>2</sub> no óxido segue a lei de Fick<sup>3</sup>, a densidade de difusão das espécies H e H<sub>2</sub> no óxido (D<sub>H</sub> e D<sub>H2</sub> respectivamente) são fortemente afectadas pela variação da temperatura segundo a relação de Arrhenius, dada por:

$$D_{H} = D_{H_{o}} \exp\left(-\frac{E_{a}}{kT}\right) \tag{10}$$

Em que  $D_{H_o}$ é a taxa de difusão a uma temperatura de referência  $T_{ref}$ ,  $E_a$  é a energia de activação, k é a constante de Boltzman e T é a temperatura em Kelvin. Pela equação verifica-se que aumentando a temperatura T, a taxa de difusão  $D_H$  também aumenta. Além disso, a dependência do NBTI em relação à temperatura pode ser modelada por

<sup>3</sup> A lei de Fick é uma lei que quantifica na forma de equação diferencial diversos casos de difusão da matéria ou energia em um meio no qual inicialmente não existe equilíbrio químico ou térmico.

<sup>&</sup>lt;sup>2</sup> A relação de Arrhenius é uma fórmula simples, mas extremamente precisa, que permite determinar a dependência da constante de velocidade com a temperatura numa reacção química

uma onda sinusoidal, como se apresenta na equação (11) [33][35], em que t representa qualquer instante das fases de stress,  $T_{max}$  é a temperatura de stress máximo em relação à temperatura de referência  $T_{ref}$  e f é frequência térmica.

$$T(t) = \left[\frac{1}{2}(T_{max} + T_{ref})\right] + \left[\frac{1}{2}(T_{max} - T_{ref})\sin(2\pi ft)\right]$$

(11)

Contudo, alguns autores tais como [83] e [84], defendem que esta dependência não pode ser descrita simplesmente pela relação de Arrhenius. Por esta razão, em [85] defende-se que a explicação desta dependência recorrendo à relação de Arrhenius é controversa, pelo que é muito importante resolver esta inconsistência na comunidade científica, para que a estimação do tempo de vida útil dos PMOS seja a mais correcta possível. Para além disso, em [35] conclui-se que, o impacto da temperatura durante a fase de recuperação é um fenómeno que ainda levanta muitas dúvidas na comunidade científica, sendo importante a sua clarificação.

## 2.1.4 Dependência do NBTI com o Campo Eléctrico

Por várias vezes foi referida a dependência do fenómeno NBTI em relação ao campo eléctrico, mas o modelo inicial R-D não apresenta claramente a quantificação desta dependência, como também acontece em relação à temperatura.

Segundo [47], esta dependência só foi demonstrada pela primeira vez em [25]. A demonstração consistiu na generalização do modelo R-D, pelo que o estudo mais pormenorizado pode ser analisado em [25] e [87].

## 2.1.5 Modelação do efeito NBTI

De acordo com a formulação do modelo R-D, a degradação devido ao NBTI resulta das ligações químicas entre Si-H que são desfeitas na interface Si/SiO2, favorecendo a ionização do Si, que ficou sem ligação ao H, pela perda do seu electrão livre (resultando em Si<sup>+</sup> [82], [47]), ou seja, cargas carregadas que impedem a livre

circulação dos electrões que atravessam o canal. Como consequência, o PMOS acaba por se tornar lento, o que naturalmente pode ser mais ou menos visível, dependente do número de obstáculos presentes na interface (interface traps). Por outro lado, como se sabe, estes obstáculos podem ser criados pela libertação e difusão de H na forma atómica, ou então na forma de moléculas de Hidrogénio (H<sub>2</sub>). A presença predominante de uma destas duas espécies (H e/ou H<sub>2</sub>) é quantificada pelas equações (5) e (7) mais precisamente pelo  $(D_H t)^n$  e  $(6D_{H2} t)^n$ , em que o expoente n = 1/4 e 1/6, respectivamente, reflecte esta predominância. Ao fim de muito tempo, a espécie H<sub>2</sub> é a mais predominante porque os átomos de H acabam por se associarem, pois embora haja períodos em que a condição de stress seja retirada, os H nunca fazem o percurso inverso por completo. Assim, a modelação do efeito NBTI normalmente faz-se utilizando o modelo de degradação a longo prazo (Long Term Degradation) [44][55] que será explicado mais a frente. Não obstante, a degradação devido ao NBTI pode ser modelada considerando: (a) NBTI estático (Static NBTI); e o (b) NBTI dinâmico (Dynamic NBTI). O NBTI estático corresponde ao caso em que o PMOS se encontra constantemente na condição de stress, enquanto o NBTI dinâmico existe pelo facto de haver uma alternância entre as condições de stress e recovery (que, por sua vez, pode ser analisado a curto ou a longo prazo).

A degradação do *Vth* sofrida nestes casos pode ser calculado como a seguir se descreve.

#### **NBTI** estático

$$\Delta V_{\text{th}} = A \left( (1+\delta)t_{\text{ox}} + \sqrt{C(t-t_0)} \right)^{2n}$$

(12)

Em que  $t_{ox}$  é a espessura do óxido,  $(t - t_0)$  é o intervalo de tempo no qual o PMOS esteve submetido à condição de *stress* e  $\delta = 0,5$ . Por seu lado n e C representam respectivamente a predominância da espécie de *interface traps* (1/4 ou 1/6) e a dependência do NBTI em relação a temperatura [59], em que,

$$C = T_o^{-1} exp\left(\frac{-E_a}{kT}\right) \tag{13}$$

Em (13): Ea é a energia de activação ( $\approx$  0,49 [eV]) quando a difusão é dominada pelo H<sub>2</sub>;  $To = 10^{-8} \text{ s.nm}^{-2}$ ; T é a temperatura Kelvin; e k é a constante de Boltzmann.

$$A = \left(\frac{qt_{ox}}{\epsilon_{ox}}\right)^{3} \sqrt{K^{2}C_{ox}(V_{gs} - V_{th})\left(exp\left(\frac{E_{ox}}{E_{0}}\right)\right)^{2}}$$

(14)

Em (14), A é linearmente proporcional à densidade dos buracos e têm uma dependência exponencial da temperatura T e do campo eléctrico  $E_{ox}$  no óxido. Para além disso, q é a carga do electrão,  $\epsilon_{ox}$  refere-se à constante dieléctrica do terminal gate em relação ao vácuo,  $C_{ox} = \left(\frac{\epsilon_{ox}}{t_{ox}}\right)$  é a capacidade do óxido (depende da tecnologia) por unidade de área  $[F/nm^2]$ , e  $K = 3 \times 10^4 \ [C^{-0.5}nm^{-2}]$ . A fórmula do campo eléctrico vertical em [V/nm] entre o terminal gate e o canal do PMOS,  $E_{ox}$ , é dada pela expressão (15) e a constante de aceleração do campo eléctrico, Eo, apresenta o valor de 0,335 [V/nm] para os modelos PTM de Berkeley.

$$E_{ox} = \frac{V_{gs} - V_{th}}{t_{ox}} \tag{15}$$

#### NBTI dinâmico (para períodos curtos de tempo)

Stress:

$$\Delta V_{th} = \left[ K_{v} (t - t_0)^{1/2} + \sqrt[2n]{\Delta V_{th0}} \right]^{2n}$$

(16)

Recovery:

$$\Delta V_{th} = \Delta V_{th0} \left[ 1 - \frac{2\xi_1 t_e + \sqrt[2n]{\xi_2 C(t - t_0)}}{2t_{ox} + \sqrt{Ct}} \right]$$

(17)

Em que,

$$K_{v} = \left(\frac{qt_{ox}}{\epsilon_{ox}}\right)^{3} K^{2} C_{ox} (V_{gs} - V_{th}) \sqrt{C} exp\left(\frac{2E_{ox}}{E_{o}}\right)$$

(18)

$\Delta V_{th0}$  é a variação da tensão de *treshold* e  $\xi_1$  e  $\xi_2$  são constantes adimencionais, cujos valores são respectivamente 0,9 e 0,5.

$$t_e = t_{ox} \sqrt{\frac{t - t_o}{t_1}} - \frac{\sqrt{\xi_2 C (t - t_o)}}{2\xi_1}$$

(19)

É de notar que, normalmente, os modelos referidos para NBTI estático e dinâmico são utilizados para períodos de tempo muito curtos em que se consegue conhecer o intervalo de tempo  $(t-t_0)$  em que ocorre o *stress* ou então o *recovery*. Porém, é mais usual querer-se conhecer os efeitos degradantes do NBTI a longo prazo. Assim, é comum utilizar-se o modelo de cálculo do  $\Delta V_{th}$  pela expressão da degradação a longo prazo, descrita em [25][46][59].

## NBTI dinâmico (para períodos longos de tempo)

A análise a longo prazo prevê períodos de *stress* ( $\alpha$ ) e *recovery* ( $\beta_t$ ) de acordo com um tempo de funcionamento t, pelo que torna impraticável conhecer os intervalos ( $t-t_0$ ) em que estes ocorrem. A modelação à longo prazo do efeito degradante do  $V_{th0}$  do PMOS pode então ser calculado recorrendo ao modelo *Long Term Degradation* (LTD), como se segue:

$$\Delta V_{th} = \left(\frac{\sqrt{K_v^2 \alpha T_{clk}}}{1 - \beta_t^{1/2n}}\right)^{2n} \tag{20}$$

Onde  $\alpha$  representa a probabilidade do PMOS se encontrar sob a condição de *stress*;  $\beta_t$  é o parâmetro que traduz as fases de recuperação durante o processo de envelhecimento e é dado por:

$$\beta_t = 1 - \frac{2\xi_1 t_e + \sqrt{\xi_2 C (1 - \alpha) T_{clk}}}{2t_{ox} + \sqrt{Ct}}$$

(21)

$T_{clk}$  é o período do relógio e corresponde a um ciclo de *stress-recovery*; e  $K_v$  é calculado através da equação (18), e é dependente do campo eléctrico e da temperatura [59].

O facto de se utilizar o LTD, o cálculo de  $t_e$  pode ser simplificado ao desprezar os tempos  $t_o$  e  $t_l$ , em que estes representam tempos em que o PMOS se encontra em períodos de *stress* e *recovery*. Como referido em [46][59], para LTD podemos considerar:

$$t_e = t_{ox} (22)$$

# 2.1.6 Redução de Efeitos Provocados pelo NBTI

Uma vez conhecido o fenómeno NBTI, desde logo a comunidade científica começou a estudar formas de minimizar os seus efeitos nas tecnologias mais pequenas. Nesta secção serão abordados, numa breve descrição, alguns trabalhos que propõem técnicas com o objectivo de atenuar o efeito do NBTI nos CI digitais. O objectivo não é ser um estudo exaustivo dos trabalhos existentes sobre minimização dos efeitos de NBTI, mas apenas ilustrar que é possível diminuir a sua influência na degradação dos CIs.

Os autores em [3], demonstraram como um simples aumento da banda de guarda dos tempos de atrasos dos caminhos em circuitos de lógica aleatória (*random logic*), pode ser eficiente para mitigar os efeitos destrutivos do NBTI.

Por outro lado, existem técnicas mais sofisticadas e agressivas, tais como (*Adaptive Body Biasing* - ABB) e a redução da tensão V<sub>DD</sub> em períodos de *stand-by*. A primeira (ABB), traduz-se em adaptar a polarização do poço dos transístores PMOS para modificar a sua tensão limiar de condução (e atenuar os efeitos de NBTI) [11]. A redução da tensão V<sub>DD</sub> consiste em aproveitar os períodos de *stand-by*, que normalmente são períodos prolongados, para reduzir a tensão de alimentação para níveis abaixo do valor nominal. Com isto, atinge-se o objectivo de reduzir a dissipação de potência (*leakage power consumption*), bem como a degradação provocada pelo NBTI, sabendo que este é fortemente dependente do campo eléctrico

vertical do óxido (*vertical oxide field*). Esta técnica tem a vantagem de ser facilmente incorporada em estruturas de memória sem custos adicional [57].

Em [10], é utilizando o algoritmo de relaxamento de Lagrange<sup>4</sup> (*Lagrangian Relaxation - LR*) modificado para optimizar o tamanho das portas lógicas. Utilizando a tecnologia dos 70nm, conseguiram evitar os efeitos degradantes devido ao NBTI aumentando a área média em 8,7% (*worst case scenario*). Em alternativa, e utilizando ainda o algoritmo LR modificado, em [96], para aumentarem a área, aplicaram diferentes escalas em relação aos NMOS e PMOS, conseguindo assim uma redução da área em cerca de 40% em relação ao proposto em [86].

Por último, em [7] é apresentada uma solução para reduzir os efeitos devido ao NBTI, através da redução do tempo em que o PMOS está sujeito ao sinal lógico '0'. Considerando os instantes em que um determinado bloco não está a ser executado, são utilizados vectores específicos para activar esse bloco de forma a reduzir o tempo que determinados transístores PMOS estão a conduzir. Segundo os autores, este método tem a vantagem de não ter custos adicionais devido a adição de *hardware* extra, nem a perda de performance e o TDP (*Thermal Design Power*) pode ser desprezado.

# 2.2 OUTROS EFEITOS QUE CAUSAM O ENVELHECIMENTO DOS CIRCUITOS