# Virtual Inertia for Suppressing Voltage Oscillations and Stability Mechanisms in DC Microgrids

von der

Fakultät für Elektrotechnik und Informationstechnik der

Technischen Universität Dortmund

genehmigte

#### **DISSERTATION**

zur Erlangung des akademischen Grades Doktor der Ingenieurwissenschaften

vorgelegt von

Gang Lin, M.Sc. aus ShanDong, P.R. China

Referent: Univ.-Prof. Dr.-Ing. Christian Rehtanz, Technische Universität Dortmund Korreferent: Univ.-Prof. Dr.-Ing. Marco Liserre, Christian-Albrechts-Universität zu Kiel

Tag der mündlichen Prüfung: 08.12.2022

# **Abstract**

Renewable energy sources (RES) are gradually penetrating power systems through power electronic converters (PECs), which greatly change the structure and operation characteristics of traditional power systems. The maturation of PECs has also laid a technical foundation for the development of DC microgrids (DC-MGs). The advantages of DC-MGs over AC systems make them an important access target for RES. Due to the multi-timescale characteristics and fast response of power electronics, the dynamic coupling of PEC control systems and the transient interaction between the PEC and the passive network are inevitable, which threatens the stable operation of DC-MGs. Therefore, this dissertation focuses on the study of stabilization control methods, the low-frequency oscillation (LFO) mechanism analysis of DC-MGs and the state-of-charge (SoC) imbalance problem of multi-parallel energy storage systems (ESS).

Firstly, a virtual inertia and damping control (VIDC) strategy is proposed to enable bidirectional DC converters (BiCs) to damp voltage oscillations by using the energy stored in ESS to emulate inertia without modifications to system hardware. Both the inertia part and the damping part are modeled in the VIDC controller by analogy with DC machines. Simulation results verify that the proposed VIDC can improve the dynamic characteristics and stability in islanded DC-MG. Then, inertia droop control (IDC) strategies are proposed for BiC of ESS based on the comparison between conventional droop control and VIDC. A feedback analytical method is presented to comprehend stability mechanisms from multi-viewpoints and observe the interaction between variables intuitively. A hardware in the loop (HIL) experiment verifies that IDC can simplify the control structure of VIDC in the promise of ensuring similar control performances. Subsequently, a multi-timescale impedance model is established to clarify the control principle of VIDC and the LFO mechanisms of VIDC-controlled DC-MG. Control loops of different timescales are visualized as independent loop virtual impedances (LVIs) to form an impedance circuit. The instability factors are revealed and a dynamic stability enhancement method is proposed to compensate for the negative damping caused by VIDC and CPL. Experimental results have validated the LFO mechanism analysis and stability enhancement method. Finally, an inertia-emulation-based cooperative control strategy for multi-parallel ESS is proposed to address the SoC imbalance and voltage deviation problem in steady-state operation and the voltage stability problem. The contradiction between SoC balancing speed and maintaining system stability is solved by a redefined SoC-based droop resistance function. HIL experiments prove that the proposed control performs better dynamics and static characteristics without modifying the hardware and can balance the SoC in both charge and discharge modes.

# Acknowledgements

Sincerely thank the people all over the world for their efforts in the fight against the COVID-19 pandemic.

I would like to express the deepest gratitude to my supervisor, Prof. Dr.-Ing. Christian Rehtanz, the head of the ie3 institute, for the attentive care, invaluable guidance and the research environment provided to me. His great technical and editorial advice on my research work is essential for the completion of this dissertation. It is my great honor to have the opportunity to obtain his guidance.

Finally, I would like to acknowledge the financial support from the Chinese Scholarship Council (No. 201906130196) for providing the opportunity to perform the research in Germany.

Gang Lin

Dortmun, Germany, 16 December, 2022

# **Nomenclature and Abbreviations**

#### **Abbreviations**

bi-DC Bidirectional DC

BiC Bidirectional DC converter

CCL Constant current load

CCS Current coordinate system

CPL Constant power load

DC-BVF DC bus voltage fluctuation

DC-MG Direct current microgrid

DFIG Doubly fed induction generator

DG Distributed generations

DLC Dual loop control

DVI Dynamic virtual impedance

ESS Energy storage system

ESU Energy storage unit

EU European Union

EV Electric vehicle

HESS Hybrid energy storage system

HIL Hardware in the loop

H-MG Hybrid AC/DC microgrid

HVDC High voltage direct current

HPF High pass filter

IDC Inertia droop control

IDA-PBC Interconnection and damping assignment-passivity-based control

IEL Inertia emulation loop

IM Impedance model

LFO Low-frequency oscillation

LPF Low pass filter

LVI Loop virtual impedance

MIMO Multi-input multi-output

MMC Modular multilevel converter

MSD Mass-spring-damper

MTDC Multi-terminal DC

ND Negative damping

NF Negative feedback

PBC Passivity-based control

PBSC Passivity-based stability criterion

PCH Port-controlled Hamiltonian

PD Positive damping

PDRL Positive-damping reshaping loop

PEC Power electronic converter

PFB Positive feedback

PV Photovoltaics

RES Renewable energy source

RHP Right half plane

RoCoV Rate of change of voltage

SC Super-capacitor

SG Synchronous generator

SISO Single-input single-output

SM Switch model

SMES Superconducting magnetic energy storage

SoC State-of-charge

SSO Sub-synchronous oscillation

SST Solid-state transformer

SVR Secondary voltage regulation

TVN Transient voltage nadir

VCS Voltage coordinate system

VDCM Virtual DC machine

VIC Virtual inertia control

VIDC Virtual inertia and damping control

VSC Voltage source converter

VSG Virtual synchronous generator

VSM Virtual synchronous machine

#### Parameters and Variables

$C_{\text{bus}}$  DC bus capacitance

$C_{\rm f}$  Output capacitance of buck converter

$C_{\rm in}$  Input capacitance of buck converter

$C_{\text{out}}$  Output filter capacitor of bidirectional DC converter

d Duty ratio

$i_{\rm m}/i_{\rm s}$  Input current of bidirectional DC converter

$i_{

m out}/v_{

m out}$  Output current and voltage of bidirectional DC converter  $J_{

m vir}/k_{

m vd}/k_{

m svr}$  Virtual inertia, damping and stiffness coefficient of VIDC  $k_{

m ip}/k_{

m ii}$  Proportional and integral gain of current-loop controller  $k_{

m vp}/k_{

m vi}$  Proportional and integral gain of voltage-loop controller

$L_{\rm f}/R_{\rm f}$  Filter inductor and its parasitic resistance of buck converter

$L_s/R_s$  Input filter inductor and its parasitic resistance of bidirectional DC converter

$P_{\text{const}}/P_{\text{cpl}}$  Power of CPL

$R_{\rm cpl}$  Small-signal impedance of CPL

$R_{\rm d}$  Droop coefficient  $R_{\rm line}/L_{\rm line}$  Line impedance

v<sub>bus</sub> Rated value of DC bus voltagev<sub>out\_buck</sub> Load voltage of buck converter

$v_s/v_{in}$  Input voltage of bidirectional DC converter

# **Contents**

| N  | omenclature and Abbreviations                                                   | I    |

|----|---------------------------------------------------------------------------------|------|

| C  | ontents                                                                         | V    |

| Li | st of Figures                                                                   | IX   |

| Li | st of Tables                                                                    | XV   |

| 1  | Introduction                                                                    | 1    |

|    | 1.1 Background and Motivation                                                   | 1    |

|    | 1.2 Research Questions and Corresponding Sulutions                              | 4    |

|    | 1.3 Outlines of the Dissertation                                                | 7    |

| 2  | Analysis of the State of the Art                                                | 11   |

|    | 2.1 Review of DC-MG Topologies and Bus Voltage Fluctuation Classification       | 11   |

|    | 2.1.1 Topologies of DC-MG and its applications                                  | 11   |

|    | 2.1.2 Leading causes and classification of voltage fluctuation                  | 16   |

|    | 2.2 Review of Stabilization Control Methods in DC-MG                            | 18   |

|    | 2.2.1 Passivity-based control method                                            | 18   |

|    | 2.2.2 Virtual inertia and damping control                                       | 20   |

|    | 2.2.3 Impedance-reshaping-based control method                                  | 22   |

|    | 2.3 Review of Modelling and Stability Analysis Method                           | 23   |

|    | 2.3.1 Impedance-model-based stability analysis methods                          | 23   |

|    | 2.3.2 State-space-model-based stability analysis method                         | 25   |

|    | 2.3.3 Transfer-function-based stability analysis method                         | 26   |

|    | 2.4 Review of SoC Balance Method                                                | 27   |

|    | 2.5 Summary                                                                     | 28   |

| 3  | A Virtual Inertia and Damping Control to Suppress Voltage Oscillation in Isla   | nded |

|    | DC Microgrid                                                                    | 31   |

|    | 3.1 Topology of the Studied DC-MG and its Simplification                        | 32   |

|    | 3.2 Inertia Source in DC-MG and VIDC Strategy                                   | 34   |

|    | 3.2.1 Inertia source analysis in DC-MG                                          | 34   |

|    | 3.2.2 VIDC concept model and its implementation                                 | 35   |

|    | 3.2.3 Droop control for multi-parallel operation                                | 38   |

|    | 3.3 Small Signal Model and Dynamic Characteristic Analysis of the VIDC Strategy | 39   |

|    | 3.4 Parameter Design                                                            | 41   |

|   | 3.4.1 Design of voltage outer loop and current inner loop                   | 41    |

|---|-----------------------------------------------------------------------------|-------|

|   | 3.4.2 Parameters design of VIDC                                             | 42    |

|   | 3.4.3 Inertia matching method                                               | 46    |

|   | 3.5 Simulation Verification                                                 | 46    |

|   | 3.5.1 Comparison between different control methods                          | 47    |

|   | 3.5.2 Stand-alone operation mode of bi-DC converter                         | 48    |

|   | 3.5.3 Multi-parallel operation of bi-DC converters                          | 49    |

|   | 3.6 Summary                                                                 | 49    |

| 4 | Inertia Droop Control and its Stability Mechanism Analysis for Energy Sto   | orage |

|   | System in Islanded DC-MG                                                    | 51    |

|   | 4.1 DC-MG Structure and Discussion about VIDC                               | 51    |

|   | 4.1.1 System configuration                                                  | 51    |

|   | 4.1.2 Discussion about virtual inertia and damping control                  | 52    |

|   | 4.2 Inertia Droop Control                                                   | 54    |

|   | 4.2.1 Design of voltage-mode inertia droop control                          | 54    |

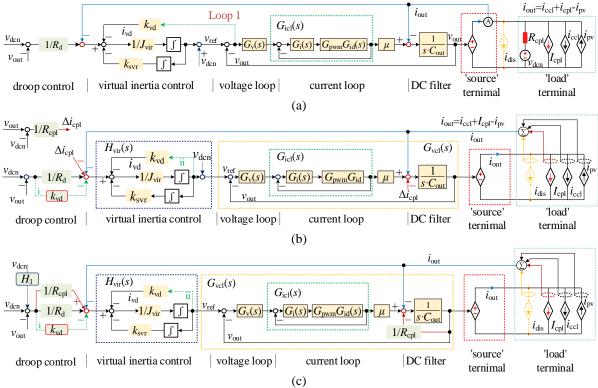

|   | 4.2.2 Design of current-mode inertia droop control                          | 56    |

|   | 4.3 Stability Mechanism Analysis                                            | 59    |

|   | 4.3.1 Introduction of feedback analysis method                              | 59    |

|   | 4.3.2 Unified model and stability mechanism analysis                        | 60    |

|   | 4.4 Dynamic Performance and Stability Analysis                              | 64    |

|   | 4.4.1 Dynamic performance analysis of IDC                                   | 64    |

|   | 4.4.2 Small-signal stability analysis of voltage-mode IDC                   | 65    |

|   | 4.4.3 Small-signal stability analysis of current-mode IDC                   | 67    |

|   | 4.5 Hardware in the Loop Experiment Verification                            | 68    |

|   | 4.6 Summary                                                                 | 75    |

| 5 | Low-Frequency Oscillation Analysis of Virtual-Inertia-Controlled DC-MG base | ed on |

|   | Multi-timescale Impedance Model                                             | 77    |

|   | 5.1 DC-MG Description and Discussion about VIDC                             | 78    |

|   | 5.1.1 System configuration                                                  | 78    |

|   | 5.1.2 Virtual inertia and damping control                                   | 79    |

|   | 5.1.3 Equivalent two-terminal model of islanded DC-MG                       | 81    |

|   | 5.2 Multi-timescale Impedance Modelling                                     | 83    |

|   | 5.2.1 Methodology: mapping between virtual impedance and controlled-source  | 83    |

|   | 5.2.2 Derivation and analysis of multi-timescale impedance                  | 84    |

|    | 5.2.3 Positive-feedback-based instability factor analysis and verification of | multi- |

|----|-------------------------------------------------------------------------------|--------|

|    | timescale impedance model                                                     | 93     |

|    | 5.3 Transient Stability Enhancement Method and its Verification               | 96     |

|    | 5.3.1 Transient stability enhancement method                                  | 96     |

|    | 5.3.2 Time-domain validation of stability enhancement method                  | 99     |

|    | 5.4 Passivity-Based Voltage Stability Assessment                              | 100    |

|    | 5.5 Experiment Verification                                                   | 102    |

|    | 5.5.1 Hardware in the loop experiment                                         | 102    |

|    | 5.5.2 Physical experiment verification                                        | 104    |

|    | 5.6 Conclusion and Discussion                                                 | 107    |

| 6  | An Inertia-Emulation based Cooperative Control Strategy and Parameter Design  | gn for |

|    | Multi-parallel Energy Storage Systems in Islanded DC Microgrids               | 109    |

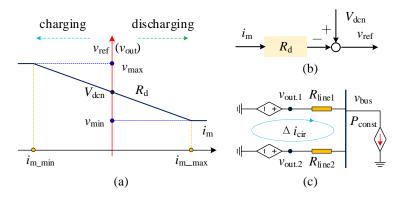

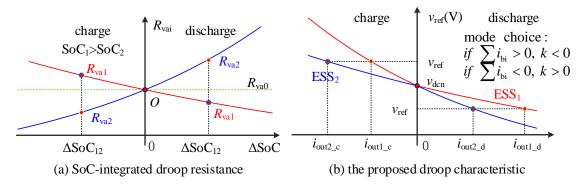

|    | 6.1 Principle of SoC Self-balance Algorithm and IEL                           | 110    |

|    | 6.1.1 Principle of SoC self-balance algorithm                                 | 110    |

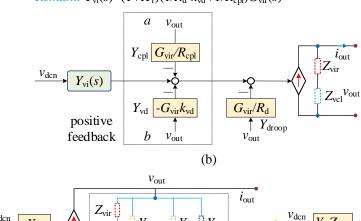

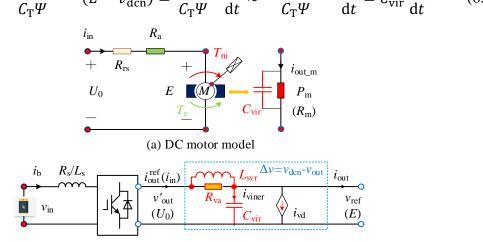

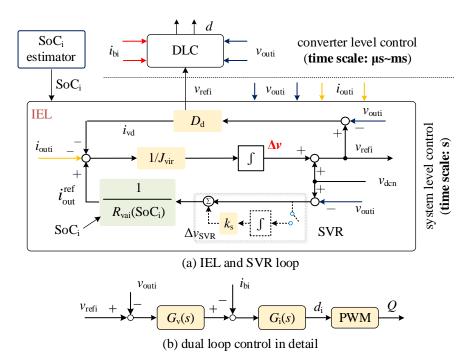

|    | 6.1.2 The design of IEL and SVR loop                                          | 112    |

|    | 6.1.3 The illustration of the proposed cooperative control strategy           | 114    |

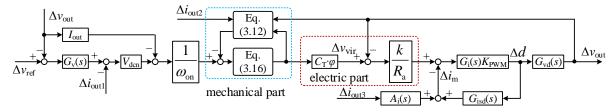

|    | 6.2 Dynamic Performance and Stability Analysis                                | 115    |

|    | 6.2.1 SoC balance speed adjustment                                            | 116    |

|    | 6.2.2 Stability analysis of the SoC self-balance algorithm                    | 116    |

|    | 6.2.3 Small signal stability analysis of inertia emulation loop               | 118    |

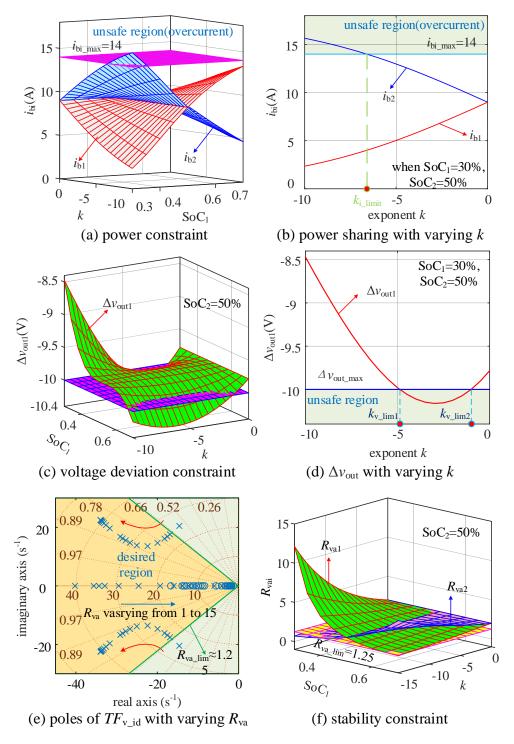

|    | 6.3 Parameters Optimal Design                                                 | 120    |

|    | 6.3.1 Power constraint                                                        | 120    |

|    | 6.3.2 Voltage deviation constraint                                            | 122    |

|    | 6.3.3 Dynamic stability constraint                                            | 122    |

|    | 6.4 Simulation and Experiment Verification                                    | 124    |

|    | 6.4.1 Simulation results                                                      | 124    |

|    | 6.4.2 Hardware in the loop experiment results                                 | 126    |

|    | 6.5 Summary                                                                   | 129    |

| 7  | Conclusions and Future Works                                                  | 131    |

|    | 7.1 Conclusions                                                               | 131    |

|    | 7.2 Future Works                                                              | 134    |

| Re | eferences                                                                     | 137    |

| Δ1 | uthor Curriculum Vitae                                                        | 145    |

# **List of Figures**

| Figure 1.1: A typical layout of RES-integrated single-bus DC-MG.                                                    |

|---------------------------------------------------------------------------------------------------------------------|

| Figure 1.2: Structure of the dissertation.                                                                          |

| Figure 2.1: Typical topology of multi-bus DC-MG.                                                                    |

| Figure 2.2: Typical reconfigurable topology of DC-MG. (a) Zonal DC-MG architecture. (b)                             |

| Ring-bus based DC-MG15                                                                                              |

| Figure 2.3: Typical applications of DC-MG.                                                                          |

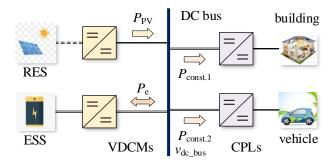

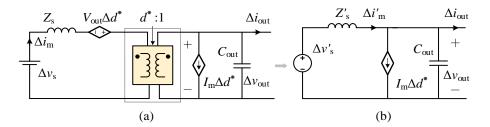

| Figure 3.1: Topology of the studied DC-MG in islanded mode                                                          |

| Figure 3.2: Circuit of DC converter. (a) bi-DC converter. (b) Buck converter                                        |

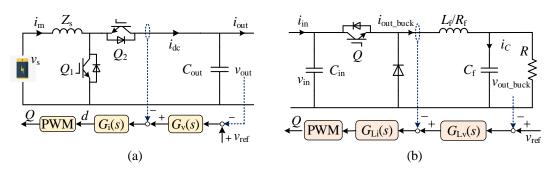

| Figure 3.3: The simplified model of bi-DC converter (a) Switching cycle average model. (b)                          |

| Simplified circuit of bi-DC converter                                                                               |

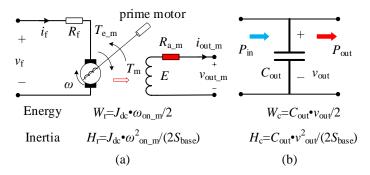

| Figure 3.4: Inertia mapping between the DC machine and capacitor. (a) DC machine model. (b)                         |

| DC capacitor34                                                                                                      |

| Figure 3.5: Concept model and block diagram of VIDC strategy. (a) Concept model. (b) Contro                         |

| block diagram. (c) Virtual inertia and damping emulation part                                                       |

| Figure 3.6: Droop control and circulating current analysis. (a) Concept model. (b) Control block                    |

| diagram (c) Equivalent circuit                                                                                      |

| Figure 3.7: Small signal model of the bi-DC converter control system                                                |

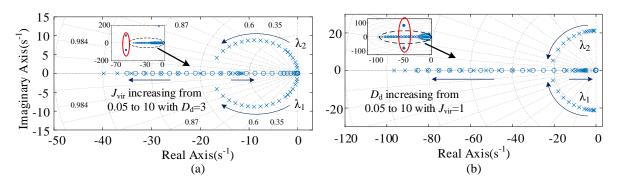

| Figure 3.8: Zero and dominant poles distribution of $TF(s)$ . (a) Arrow direction: $J_{vir}$ changing               |

| from 0.05 to 10. (b) Arrow direction: $D_d$ changing from 0.05 to 10                                                |

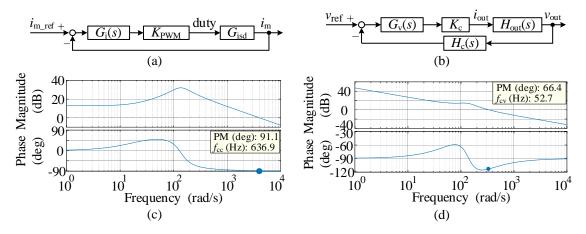

| Figure 3.9: Small signal model and Bode diagram. (a) Small signal model of current loop. (b)                        |

| Small signal model of voltage loop. (c) Bode diagram of current loop. (d) Bode diagram o                            |

| voltage loop                                                                                                        |

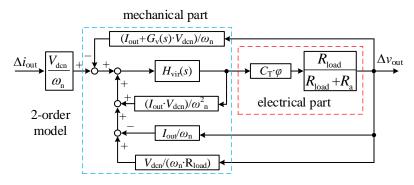

| Figure 3.10: Simplified 2nd-order model of the bi-DC converter control system43                                     |

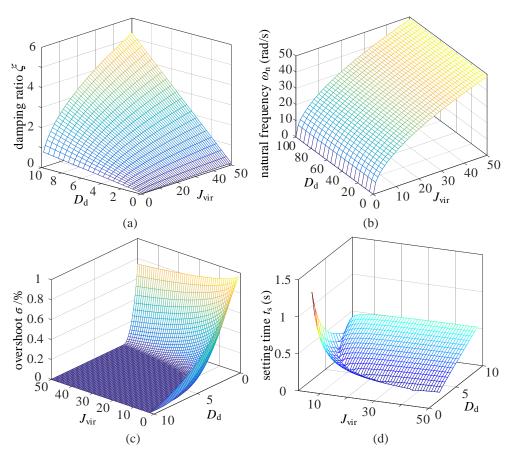

| Figure 3.11: Variation range of different performance indices. (a) Damping ratio $\xi$ . (b) Natura                 |

| oscillation frequency. (c) Overshoot. (d) Setting time                                                              |

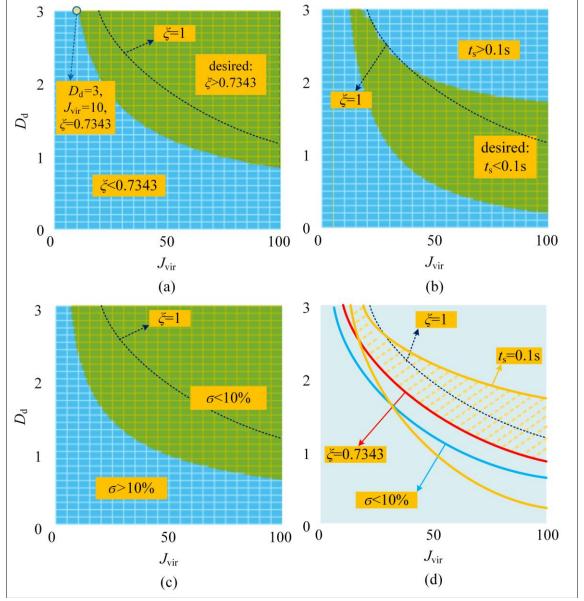

| Figure 3.12: Parameters design when performance indices with different requirements. (a)                            |

| Damping ratio $\xi$ . (b) Setting time $t_s$ . (c) Overshoot $\sigma$ . (d) Intersection of solutions with differen |

| requirements45                                                                                                      |

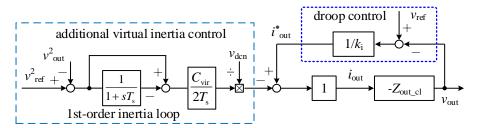

| Figure 3.13: Block diagram of $V^2$ - $P$ -based VIC                                                                |

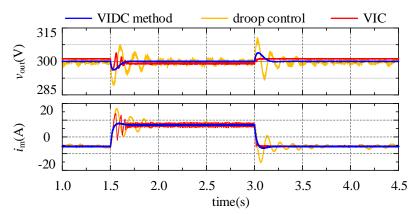

| Figure 3.14: Comparison of different control strategies                                                             |

| Figure 3.15: The simulation results during sudden power change. (a) RES. (b) CPL48                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.16: The simulation results of parallel operation. (a) Converters with equal capacity. (b)                                                                                                           |

| Converters with unequal capacity                                                                                                                                                                             |

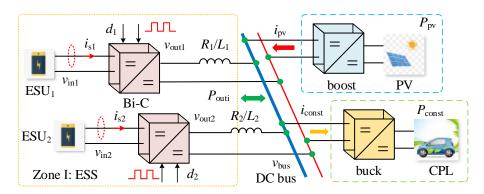

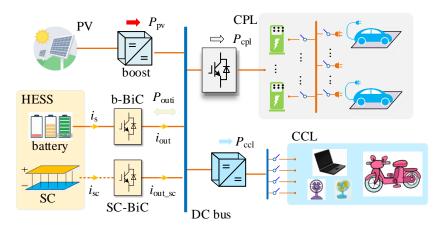

| Figure 4.1: The general layout of the studied PV-integrated DC-MG                                                                                                                                            |

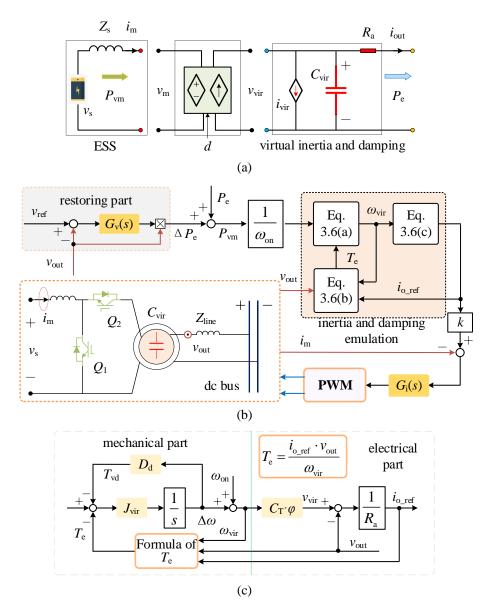

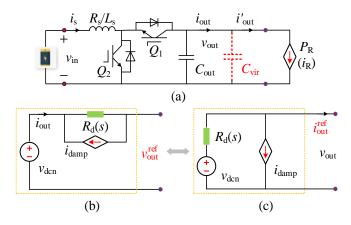

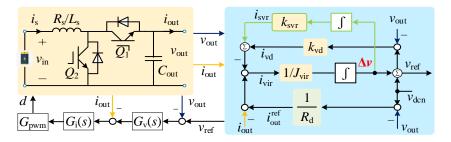

| Figure 4.2: Diagram of BiC circuit and the simplified model of VIDC. (a) Circuit of BiC. (b)                                                                                                                 |

| Voltage source model (c) Current source model                                                                                                                                                                |

| Figure 4.3: Inertia explanation of vm-IDC. (a) Frequency domain. (b) Time domain 55                                                                                                                          |

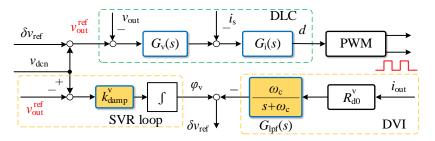

| Figure 4.4: Control diagram of voltage-mode inertia droop control                                                                                                                                            |

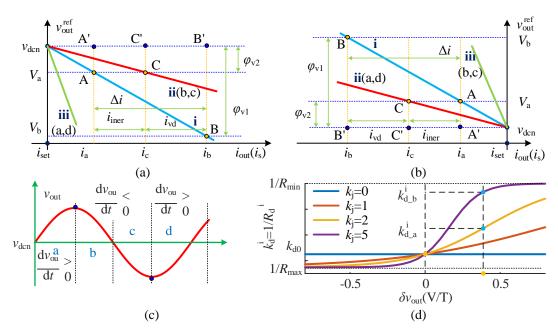

| Figure 4.5: Explanation of inertia from cm-IDC. (a) Discharging mode. (b) Charging mode. (c)                                                                                                                 |

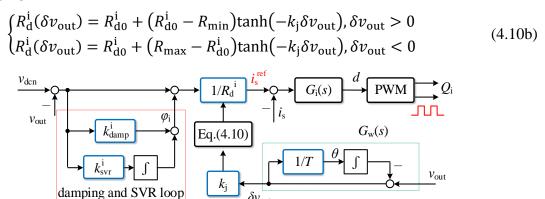

| Transient voltage (d) Variable droop resistance                                                                                                                                                              |

| Figure 4.6: Control diagram of current-mode inertia droop control                                                                                                                                            |

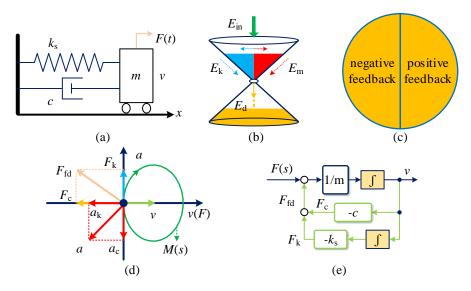

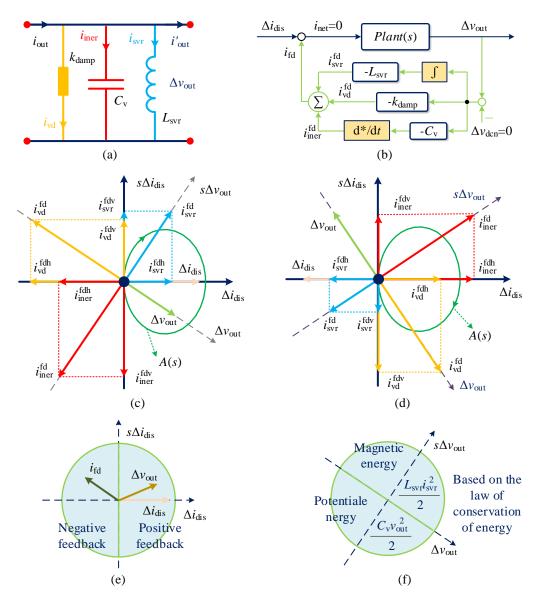

| Figure 4.7: Feedback analysis. (a) MSD model. (b) Energy conversion. (c) Illustration of                                                                                                                     |

| feedback. (d) Phasor analysis. (e) Sketch of feedback control                                                                                                                                                |

| Figure 4.8: Physical interpretation of IDC. (a) <i>RLC</i> equivalent model. (b) The equivalent model                                                                                                        |

| of BiC with IDC. (c) Phasor diagram when $\Delta i_{\rm dis} > 0$ . (d) Phasor diagram when $\Delta i_{\rm dis} < 0$ . (e)                                                                                   |

| Illustrate of feedback control. (f) Sketch of energy                                                                                                                                                         |

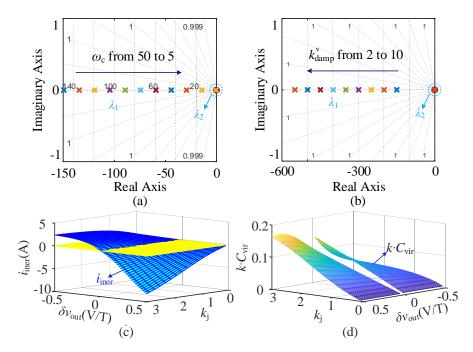

| Figure 4.9: Dynamic analysis of inertia droop control. (a) vm-IDC with varying $\omega_c$ . (b) vm-IDC                                                                                                       |

| with varying $k_{\text{damp}}^{\text{v}}$ . (c) Inertia power from cm-IDC. (d) Virtual inertia from cm-IDC65                                                                                                 |

| Figure 4.10: Small-signal model of vm-IDC.                                                                                                                                                                   |

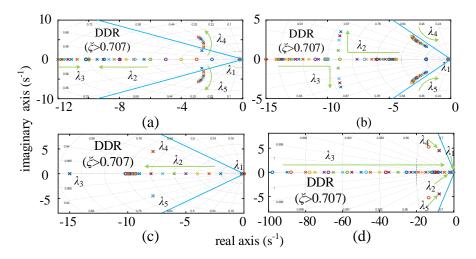

| Figure 4.11: The pole distribution of $T_{vv}(s)$ and $T_{vi}(s)$ . (a) $T_{vv}(s)$ when $k_{damp}^{v}$ varying from 2 to 10                                                                                 |

| with $\omega_c$ =15. (b) $T_{vv}(s)$ when $\omega_c$ varying from 90 to 5, with $k_{damp}^v$ =2. (c) $T_{vi}(s)$ when $k_{damp}^v$ varying                                                                   |

| from 2 to 10 with $\omega_c$ =15. (d) $T_{vi}^v$ when $\omega_c$ varying from 90 to 5, with $k_{damp}^v$ =267                                                                                                |

| Figure 4.12: The pole distribution of $T_{vv}(s)$ and $T_{vi}(s)$ .                                                                                                                                          |

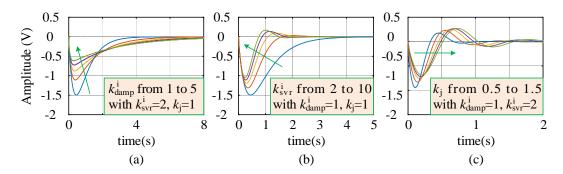

| Figure 4.13: The pole distribution of $T_{vv}(s)$ and $T_{vi}(s)$ . (a) $k_{damp}^i$ varying from 1 to 5 with $k_{svr}^i=2$                                                                                  |

| and $k_j=1$ . (b) $k_{svr}^i$ varying from 2 to 10 with $k_{damp}^i=1$ and $k_j=1$ . (c) $k_j$ varying from 0.5 to 1.5 with                                                                                  |

| $k_{\text{damp}}^{\text{i}}=1 \text{ and } k_{\text{svr}}^{\text{i}}=2.$                                                                                                                                     |

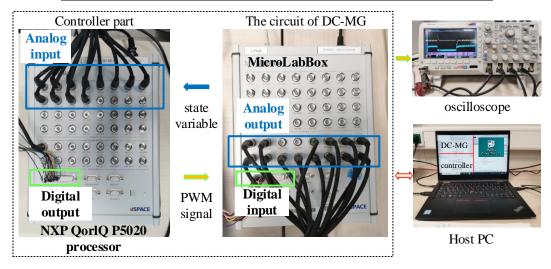

| Figure 4.14: The dSPACE-based HIL experiment setup                                                                                                                                                           |

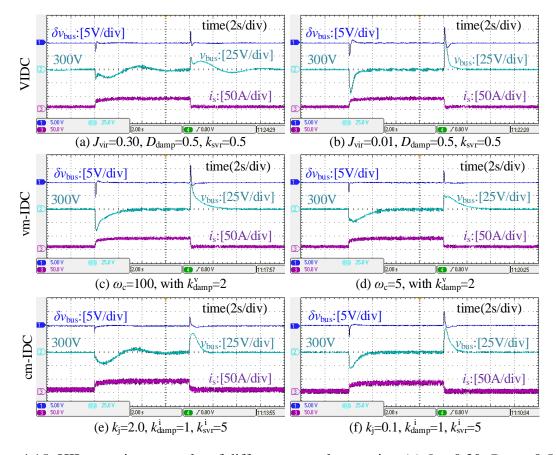

| Figure 4.15: HIL experiment results of different control strategies. (a) $J_{\text{vir}}$ =0.30, $D_{\text{damp}}$ =0.5 and                                                                                  |

| $k_{\rm svr}$ =0.5. (b) $J_{\rm vir}$ =0.01, $D_{\rm damp}$ =0.5 and $k_{\rm svr}$ =0.5. (c) $\omega_{\rm c}$ =100 and $k_{\rm damp}^{\rm v}$ =2. (d) $\omega_{\rm c}$ =5 and $k_{\rm damp}^{\rm v}$ =2. (e) |

| $k_j=2.0, k_{\text{damp}}^i=1 \text{ and } k_{\text{svr}}^i=5. \text{ (f) } k_j=0.1, k_{\text{damp}}^i=1 \text{ and } k_{\text{svr}}^i=5. $                                                                  |

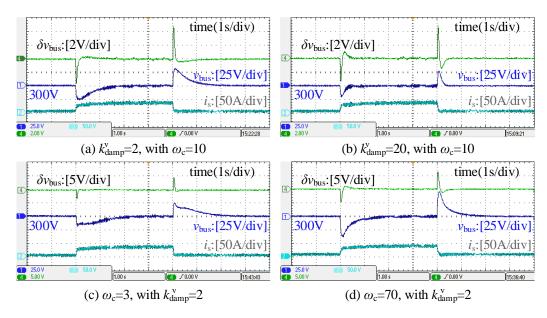

| Figure 4.16: Experiment results of vm-IDC when EV charging load fluctuating. (a) $k_{\text{damp}}^{\text{v}}$ =2 and                                                                                         |

| $\omega_{\rm c}$ =10. (b) $k_{\rm damp}^{\rm v}$ =20 and $\omega_{\rm c}$ =10. (c) $\omega_{\rm c}$ =3 and $k_{\rm damp}^{\rm v}$ =2. (d) $\omega_{\rm c}$ =70 and $k_{\rm damp}^{\rm v}$ =271               |

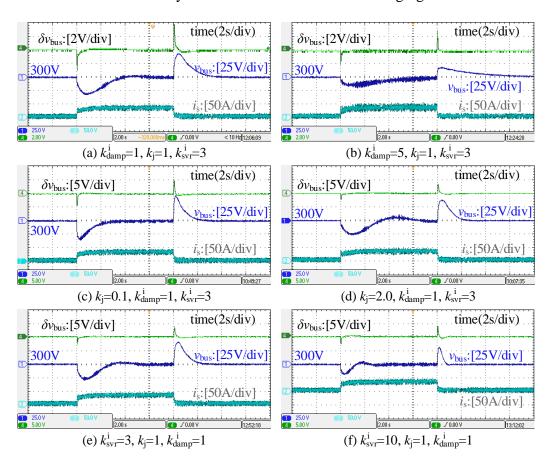

| Figure 4.17: Experiment results of cm-IDC when EV charging load fluctuating. (a) $k_{\text{damp}}^{i}=1$ , $k_{j}=1$                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| and $k_{\text{svr}}^{\text{i}}=3$ . (b) $k_{\text{damp}}^{\text{i}}=5$ , $k_{\text{j}}=1$ and $k_{\text{svr}}^{\text{i}}=3$ . (c) $k_{\text{j}}=0.1$ , $k_{\text{damp}}^{\text{i}}=1$ and $k_{\text{svr}}^{\text{i}}=3$ . (d) $k_{\text{j}}=2.0$ , $k_{\text{damp}}^{\text{i}}=1$ and $k_{\text{svr}}^{\text{i}}=3$ . |

| (e) $k_{\text{svr}}^{\text{i}}=3$ , $k_{\text{j}}=1$ and $k_{\text{damp}}^{\text{i}}=1$ . (f) $k_{\text{svr}}^{\text{i}}=10$ , $k_{\text{j}}=1$ and $k_{\text{damp}}^{\text{i}}=1$                                                                                                                                    |

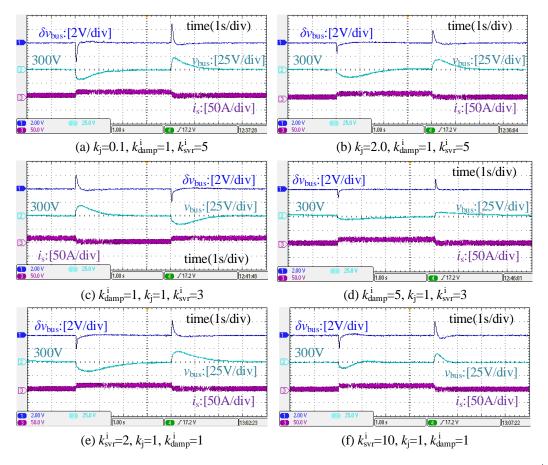

| Figure 4.18: Experiment results of cm-IDC when PV generation fluctuating. (a) $k_j$ =0.1, $k_{damp}^i$ =1                                                                                                                                                                                                             |

| and $k_{\text{svr}}^{\text{i}}=5$ . (b) $k_{\text{j}}=2.0$ , $k_{\text{damp}}^{\text{i}}=1$ and $k_{\text{svr}}^{\text{i}}=5$ . (c) $k_{\text{damp}}^{\text{i}}=1$ , $k_{\text{j}}=1$ and $k_{\text{svr}}^{\text{i}}=3$ . (d) $k_{\text{damp}}^{\text{i}}=5$ , $k_{\text{j}}=1$ and $k_{\text{svr}}^{\text{i}}=3$ .   |

| (e) $k_{\text{svr}}^{i}=2$ , $k_{j}=1$ and $k_{\text{damp}}^{i}=1$ . (f) $k_{\text{svr}}^{i}=10$ , $k_{j}=1$ and $k_{\text{damp}}^{i}=1$                                                                                                                                                                              |

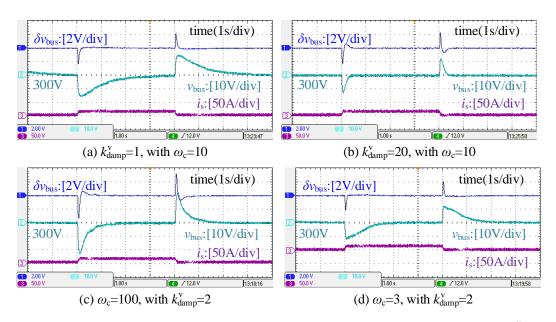

| Figure 4.19: Experiment results of vm-IDC when PV generation fluctuating. (a) $k_{\text{damp}}^{\text{v}}$ =1 and                                                                                                                                                                                                     |

| $\omega_{c}$ =10. (b) $k_{damp}^{v}$ =20 and $\omega_{c}$ =10. (c) $\omega_{c}$ =100 and $k_{damp}^{v}$ =2. (d) $\omega_{c}$ =3 and $k_{damp}^{v}$ =274                                                                                                                                                               |

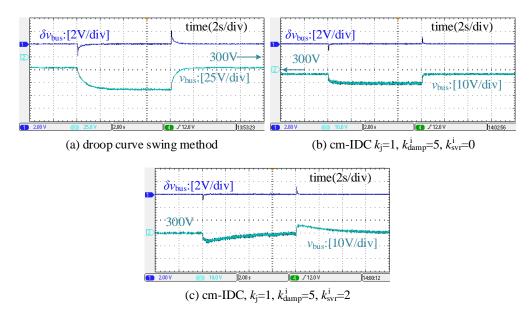

| Figure 4.20: HIL experiment results of comparison with droop curve swing method. (a) Droop                                                                                                                                                                                                                            |

| curve swing method. (b) cm-IDC: $k_j=1$ , $k_{damp}^i=5$ and $k_{svr}^i=0$ . (c) cm-IDC: $k_j=1$ , $k_{damp}^i=5$ and $k_{svr}^i=2$ .                                                                                                                                                                                 |

| Figure 5.1: The layout of the studied islanded DC-MG                                                                                                                                                                                                                                                                  |

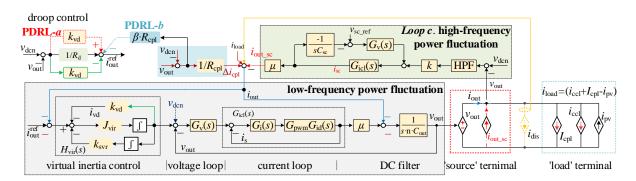

| Figure 5.2: The circuit of b-BiC and its VIDC strategy                                                                                                                                                                                                                                                                |

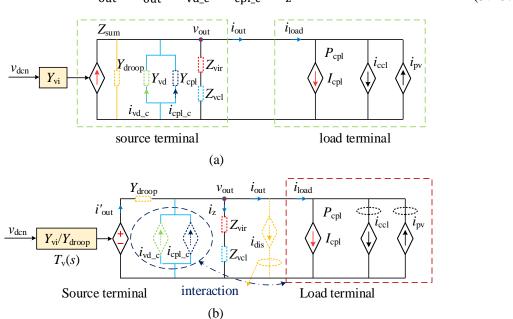

| Figure 5.3: Equivalent two-terminal model of DC-MG considering CPL. (a) Original model.                                                                                                                                                                                                                               |

| (b) Assigning CPL to 'source' terminal. (c) Simplified model                                                                                                                                                                                                                                                          |

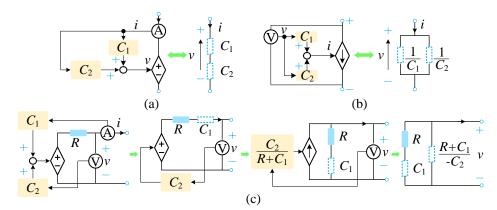

| Figure 5.4: Equivalent virtual impedance of controlled source. (a) Self-controlled voltage                                                                                                                                                                                                                            |

| source. (b) Self-controlled current source. (c) General example                                                                                                                                                                                                                                                       |

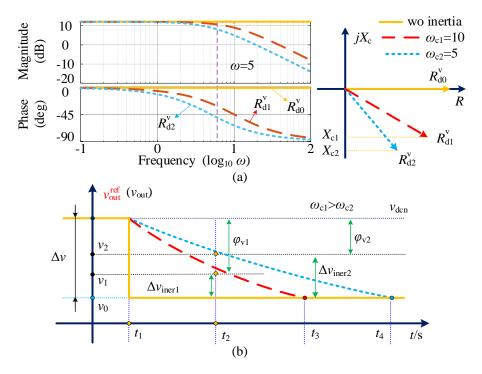

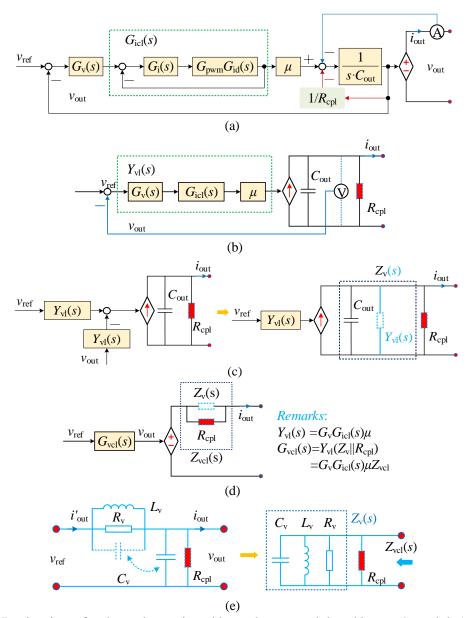

| Figure 5.5: Derivation of voltage-loop virtual impedance model and its <i>RLC</i> model. (a) Voltage-                                                                                                                                                                                                                 |

| loop mathematical model. (b) Norton equivalent model. (c) Virtual impedance derivation. (d)                                                                                                                                                                                                                           |

| Thevenin equivalent model. (e) <i>RLC</i> circuit                                                                                                                                                                                                                                                                     |

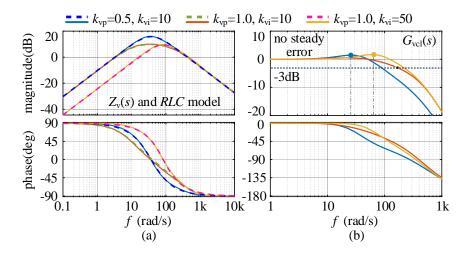

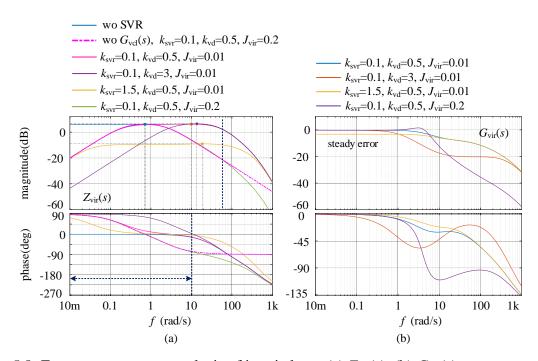

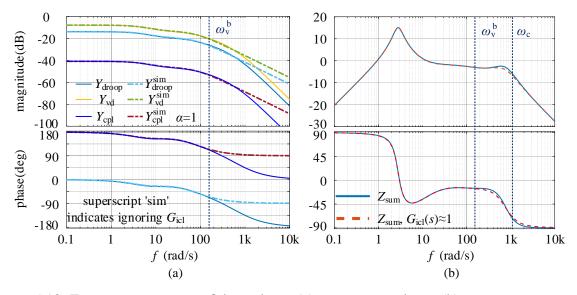

| Figure 5.6: Frequency response analysis of voltage loop. (a) $Z_v(s)$ and $RLC$ model. (b) $G_{vcl}(s)$ .                                                                                                                                                                                                             |

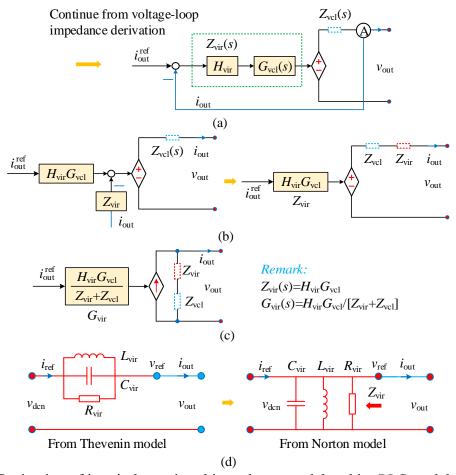

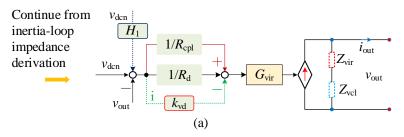

| Figure 5.7: Derivation of inertia-loop virtual impedance model and its <i>RLC</i> model. (a) Inertia-                                                                                                                                                                                                                 |

| loop mathematical model. (b) Inertia-loop virtual impedance derivation. (c) Norton equivalent                                                                                                                                                                                                                         |

| circuit. (d) RLC model                                                                                                                                                                                                                                                                                                |

| Figure 5.8: Frequency response analysis of inertia loop. (a) $Z_{vir}(s)$ . (b) $G_{vir}(s)$                                                                                                                                                                                                                          |

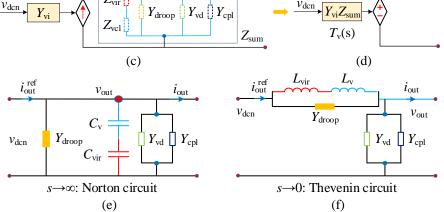

| Figure 5.9: Derivation of droop-control virtual impedance model and the RLC model of the                                                                                                                                                                                                                              |

| total system impedance. (a) Droop-loop mathematical model. (b) Droop-loop virtual impedance                                                                                                                                                                                                                           |

| derivation. (c) Norton equivalent circuit. (d) Thevenin equivalent circuit. (e) RLC model in                                                                                                                                                                                                                          |

| Norton circuit form. (f) <i>RLC</i> model in Thevenin circuit form                                                                                                                                                                                                                                                    |

| Figure 5.10: Frequency response of droop loop. (a) $Y_{droop}$ , $Y_{vd}$ and $Y_{cpl}$ . (b) $Z_{sum}$                                                                                                                                                                                                               |

| Figure 5.11: Feedback-based instability factor analysis. (a) Current-source. (b) Voltage-source.                                                                                                                                                                                                                      |

| 93                                                                                                                                                                                                                                                                                                                    |

| Figure 5.12: Switch model verification of multi-timescale virtual impedance model with                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| different parameters. (a) $k_{vp}$ . (b) $k_{vi}$ . (c) $J_{vir}$ . (d) $k_{vd}$ . (e) $k_{svr}$                                                                                                                             |

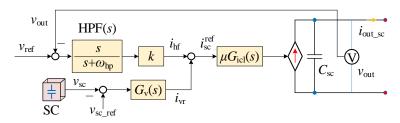

| Figure 5.13: The control diagram of SC                                                                                                                                                                                       |

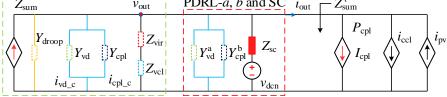

| Figure 5.14: Source-load two-terminal model of islanded DC-MG considering the transient                                                                                                                                      |

| stability enhancement method                                                                                                                                                                                                 |

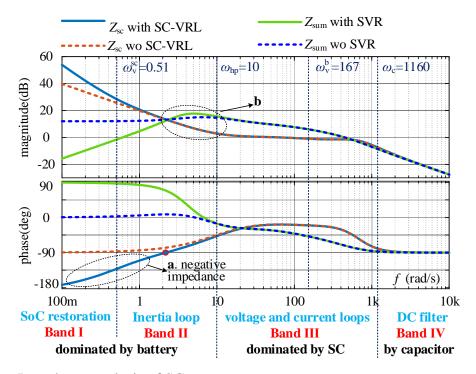

| Figure 5.15: Impedance reshaping effect of stability enhancement loops                                                                                                                                                       |

| Figure 5.16: Impedance analysis of SC                                                                                                                                                                                        |

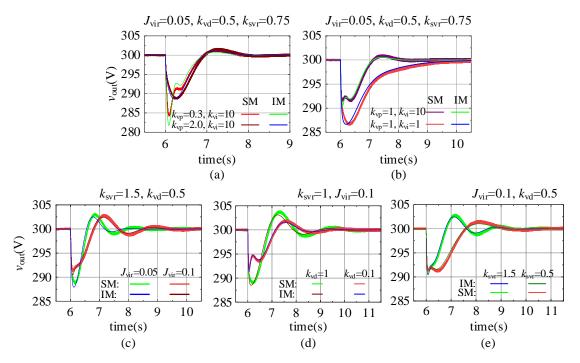

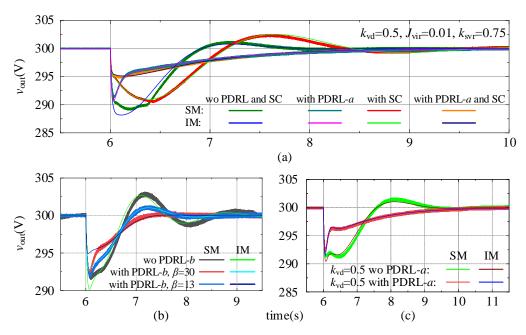

| Figure 5.17: SM verification of stability enhancement method. (a) Comparison of different                                                                                                                                    |

| stability enhancement loops. (b) Varying $\beta$ . (c) Effect of PDRL- $a$                                                                                                                                                   |

| Figure 5.18: Nyquist plot of impedance model $Z_{\text{sum}}^{\text{t}}$ with various parameters. (a) Varying $J_{\text{vir}}$ . (b)                                                                                         |

| Varying $k_{\text{vd}}$ . (c) Varying $k_{\text{svr}}$ . (d) Varying $\beta$                                                                                                                                                 |

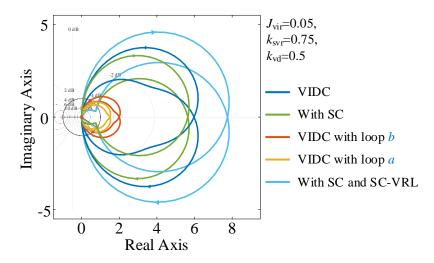

| Figure 5.19: Nyquist plot of $Z_{\text{sum}}$ with different stability enhancement loops                                                                                                                                     |

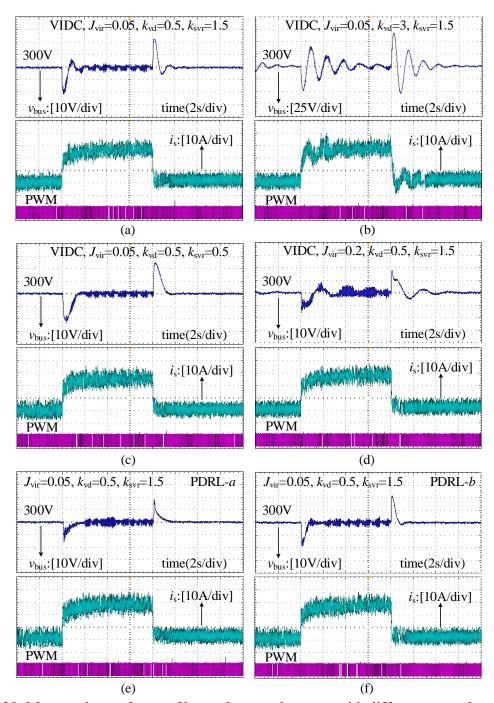

| Figure 5.20: Measured waveforms of bus voltage and current with different control method. (a)                                                                                                                                |

| Effect of VIDC. (b) Varying $k_{vd}$ . (c) Varying $k_{svr}$ . (d) Varying $J_{vir}$ . (e) Effect of PDRL-a. (f)                                                                                                             |

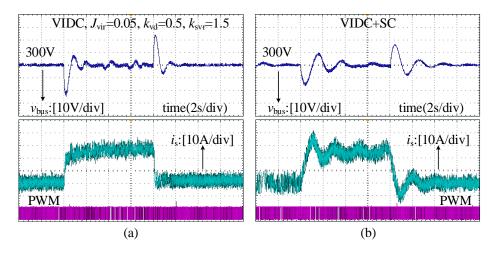

| Effect of PDRL- $b$ with $\beta$ =11                                                                                                                                                                                         |

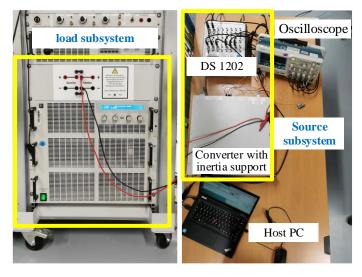

| Figure 5.21: Waveforms of bus voltage and current. (a) VIDC. (b) VIDC+SC 104                                                                                                                                                 |

| Figure 5.22: Configuration of the experimental setup                                                                                                                                                                         |

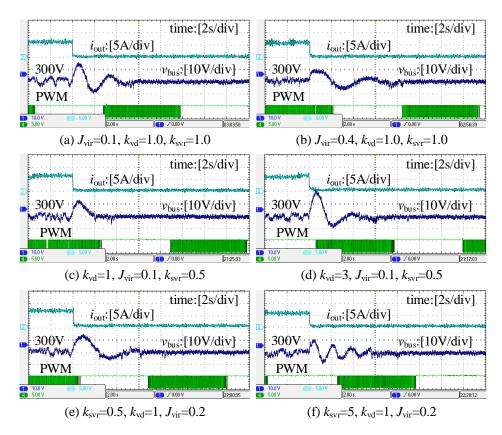

| Figure 5.23: Experiment results with different control parameters. (a) $J_{\text{vir}}$ =0.1, $k_{\text{vd}}$ =1.0 and                                                                                                       |

| $k_{\text{svr}}$ =1.0. (b) $J_{\text{vir}}$ =0.4, $k_{\text{vd}}$ =1.0 and $k_{\text{svr}}$ =1.0. (c) $k_{\text{vd}}$ =1, $J_{\text{vir}}$ =0.1 and $k_{\text{svr}}$ =0.5. (d) $k_{\text{vd}}$ =3, $J_{\text{vir}}$ =0.1 and |

| $k_{\text{svr}}$ =0.5. (e) $k_{\text{svr}}$ =0.5, $k_{\text{vd}}$ =1 and $J_{\text{vir}}$ =0.2. (f) $k_{\text{svr}}$ =5, $k_{\text{vd}}$ =1 and $J_{\text{vir}}$ =0.2                                                        |

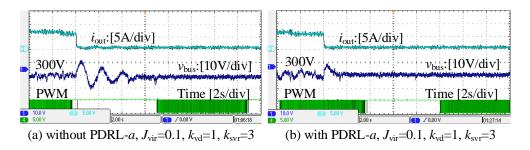

| Figure 5.24: Experiment results with PDRL-a. (a) Without PDRL-a, $J_{vir}$ =0.1, $k_{vd}$ =1 and $k_{svr}$ =3.                                                                                                               |

| (b) With PDRL- $a$ , $J_{\text{vir}}$ =0.1, $k_{\text{vd}}$ =1.0 and $k_{\text{svr}}$ =3                                                                                                                                     |

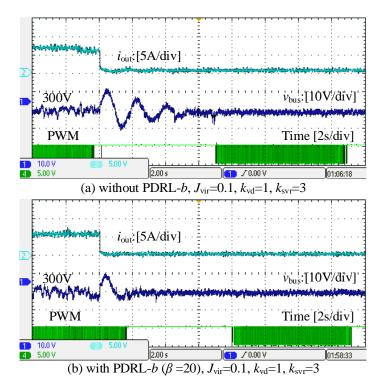

| Figure 5.25: Experiment results with PDRL- $b$ ( $\beta$ =20). (a) Without PDRL- $b$ , $J_{\text{vir}}$ =0.1, $k_{\text{vd}}$ =1 and                                                                                         |

| $k_{\text{svr}}$ =3. (b) With PDRL- $b$ ( $\beta$ =20), $J_{\text{vir}}$ =0.1, $k_{\text{vd}}$ =1.0 and $k_{\text{svr}}$ =3106                                                                                               |

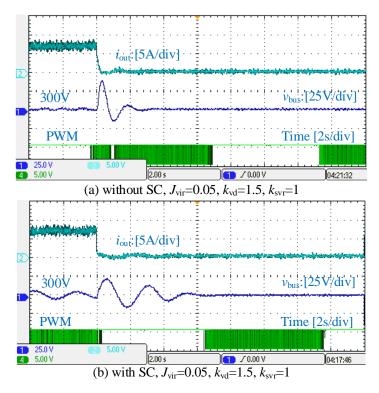

| Figure 5.26: Experiment results with SC. (a) Without SC, $J_{vir}=0.05$ , $k_{vd}=1.5$ and $k_{svr}=1$ . (b) With                                                                                                            |

| SC, $J_{\text{vir}}=0.05$ , $k_{\text{vd}}=1.5$ and $k_{\text{svr}}=1$ .                                                                                                                                                     |

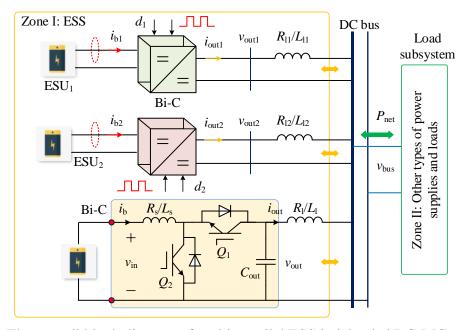

| Figure 6.1: The overall block diagram of multi-parallel ESS in islanded DC-MG 110                                                                                                                                            |

| Figure 6.2: The illustration of droop characteristics with SoC self-balance algorithm. (a) SoC-                                                                                                                              |

| integrated droop resistance. (b) The proposed droop characteristic                                                                                                                                                           |

| Figure 6.3: Mapping between BiC and DC motor, and equivalent model for IEL. (a) DC motor                                                                                                                                     |

| model. (b) The equivalent model of the IEL with SVR                                                                                                                                                                          |

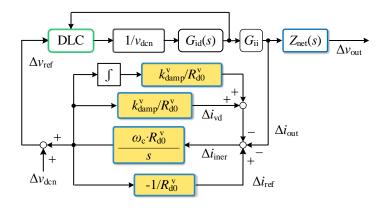

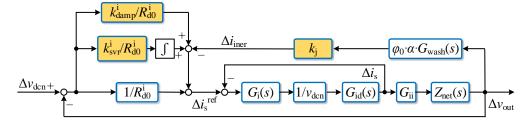

| Figure 6.4: The block diagram of inertia-emulation based cooperative control strategy. (a) IEL                                                                                                                               |

| and SVR loop. (b) Dual loop control in detail                                                                                                                                                                                |

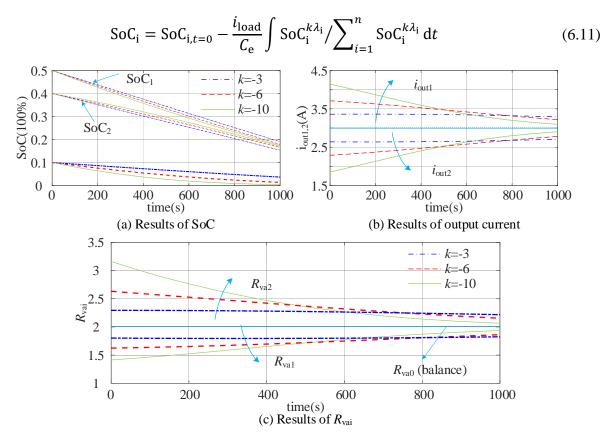

| Figure 6.5: SoC balance speed regulation with different k. (a) Result of SoC. (b) Result of output                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| current. (c) Result of $R_{\text{vai}}$                                                                                                                                 |

| Figure 6.6: The dominant pole distribution of SoC self-balance algorithm. (a) Discharge process                                                                         |

| with varying $SoC_1$ . (b) Discharge process with varying $k$ . (c) Charge process with varying $SoC_1$ .                                                               |

| (d) Charge process with varying k                                                                                                                                       |

| Figure 6.7: Small signal model of BiC with the proposed IEL                                                                                                             |

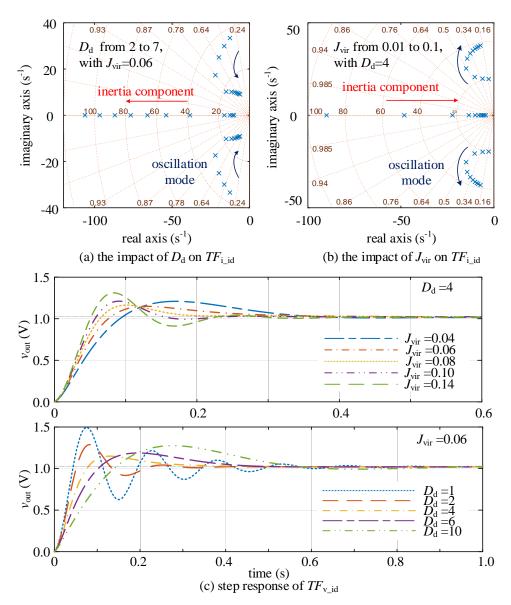

| Figure 6.8: Dynamic stability analysis of BiC with the proposed IEL. (a) The impact of $D_{\rm d}$ on                                                                   |

| $TF_{i\_id}(s)$ . (b) The impact of $J_{vir}$ on $TF_{i\_id}(s)$ . (c) Step response of $TF_{v\_id}(s)$                                                                 |

| Figure 6.9: Different constraints for exponent $k$ . (a) Power constraint. (b) Power sharing with                                                                       |

| varying k. (c) Voltage deviation constraint. (d) $\Delta v_{\text{out}}$ with varying k. (e) Poles of $TF_{v_{\text{id}}}(s)$ with                                      |

| varying $R_{\text{va}}$ . (f) Stability constraint. 121                                                                                                                 |

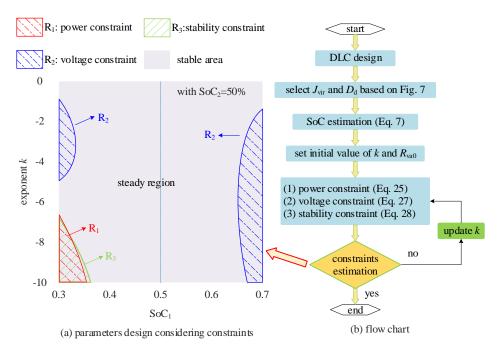

| Figure 6.10: Constraint estimation and parameter optimization flow chart. (a) Parameters design                                                                         |

| considering coonstraints. (b) Flow chart. 123                                                                                                                           |

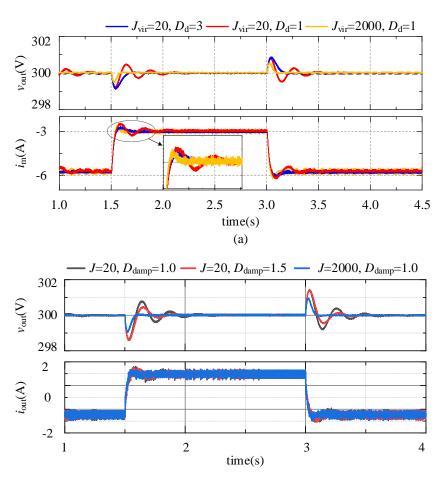

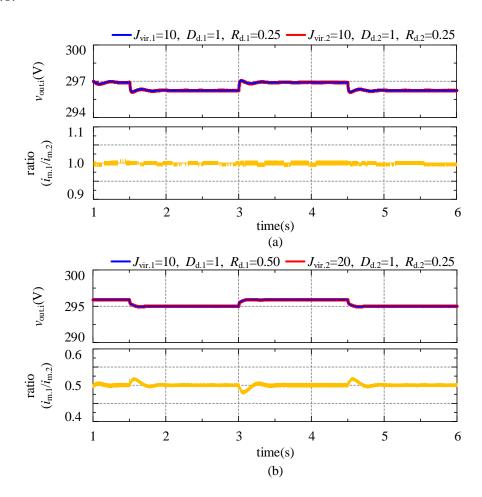

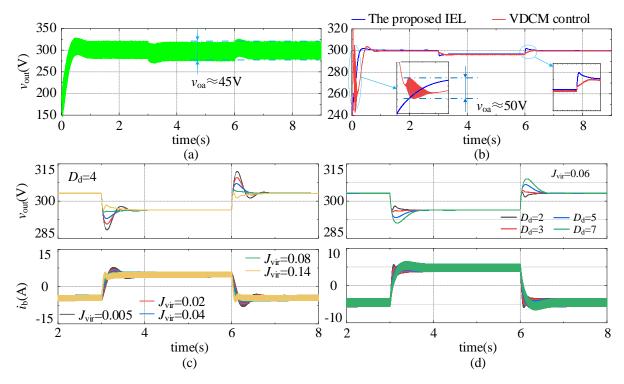

| Figure 6.11: Comparison of different control strategies. (a) The $v_{\text{out}}$ of droop control. (b) The                                                             |

| comparison between the proposed IEL and VIDC. (c) The impact of $J_{\rm vir}$ . (d) The impact of $D_{\rm d}$                                                           |

|                                                                                                                                                                         |

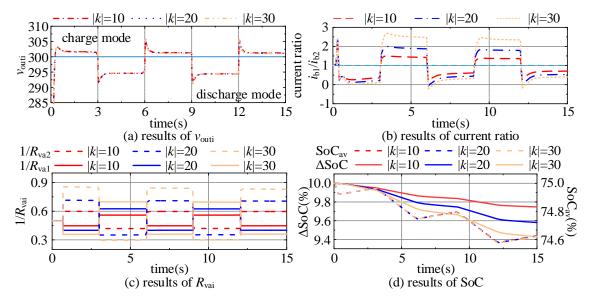

| Figure 6.12: The influence of $k$ on SoC balance speed. (a) The result of $v_{\text{outi}}$ . (b) The result of                                                         |

| current ratio. (c) The result of $R_{\text{vai}}$ . (d) The result of SoC                                                                                               |

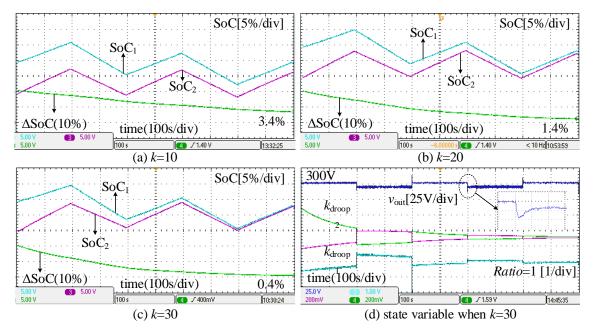

| Figure 6.13: The effect of $k$ on the SoC balance when $SoC_{1, t=0}=80\%$ and $SoC_{2, t=0}=70\%$ . (a)                                                                |

| k=10. (b) $k=20$ . (c) $k=30$ . (d) State variable when $k=30$                                                                                                          |

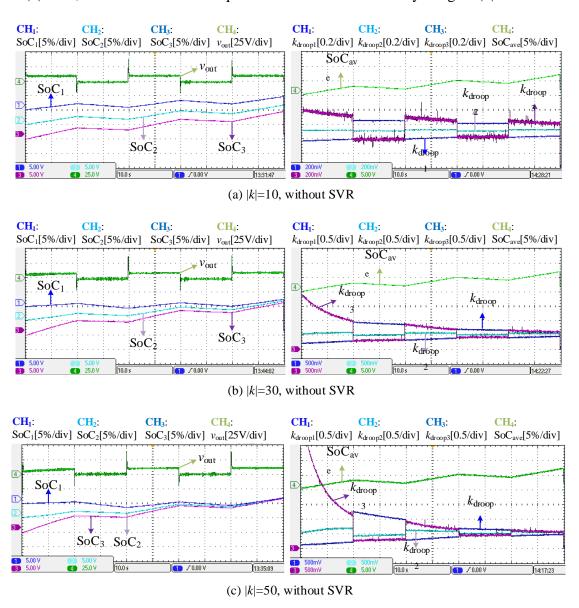

| Figure 6.14: The effect of $k$ on the SoC balance when SoC <sub>1, t=0</sub> =80% and SoC <sub>2, t=0</sub> =70%. (a)                                                   |

| k=10. (b) $k=20$ . (c) $k=30$ . (d) State variable when $k=30$ .                                                                                                        |

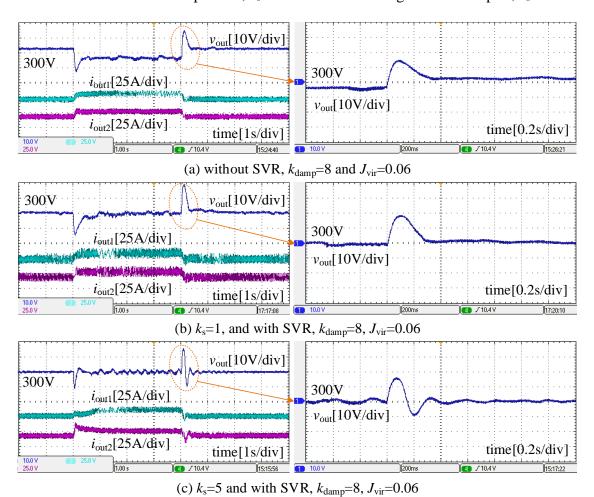

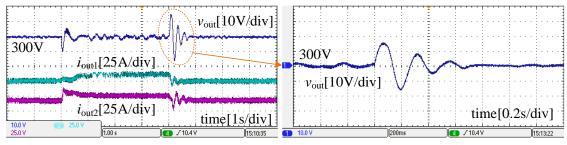

| Figure 6.15: The influence of SVR loop. (a) Without SVR, $k_{damp}$ =8 and $J_{vir}$ =0.06. (b) $k_s$ =1 with                                                           |

| SVR, $k_{\text{damp}}$ =8 and $J_{\text{vir}}$ =0.06. (c) $k_{\text{s}}$ =5 with SVR, $k_{\text{damp}}$ =8 and $J_{\text{vir}}$ =0.06. (d) $k_{\text{s}}$ =10 with SVR, |

| $k_{\text{damp}} = 8 \text{ and } J_{\text{vir}} = 0.06.$ 129                                                                                                           |

# **List of Tables**

| Table 2.1 Overview of DC bus configuration and applications                        | 16  |

|------------------------------------------------------------------------------------|-----|

| Table 2.2 Overview of DC-BVF classification                                        | 18  |

| Table 3.1 System parameters of the studied DC-MG                                   | 33  |

| Table 3.2 Analogy between DC machine and VIDC                                      | 37  |

| Table 3.3 Control parameters of VIDC strategy                                      | 45  |

| Table 3.4 Control parameters of dual loopcontrol and $V^2$ - $P$ -based VIC        | 47  |

| Table 4.1 Analogy between the mass-spring-damper model and virtual inertia control | 61  |

| Table 4.2 Control parameters of different control strategies                       | 69  |

| Table 4.3 Circuit parameters of the studied DC-MG                                  | 70  |

| Table 5.1 Control parameters of VIDC strategies                                    | 80  |

| Table 5.2 System parameters of the studied islanded DC-MG                          | 80  |

| Table 5.3 Summary of multi-timescale impedance model                               | 94  |

| Table 6.1 Analogy between DC motor and IEL with SVR                                | 113 |

| Table 6.2 Numeric solution of SoC balance regulation when <i>t</i> =800 <i>s</i>   | 117 |

| Table 6.3 System parameters of the studied multi-parallel ESS                      | 118 |

| Table 6.4 Control parameters of different control                                  | 124 |

# 1 Introduction

### 1.1 Background and Motivation

As an important measure to deal with the energy crisis and climate change, carbon neutrality has become the focus of current and future global energy policies to promote the development of renewable energy sources (RES). A number of legislations and proposals have been passed to ensure that the European Union (EU) meets its climate and energy targets, including the Emissions Trading System, the Effort Sharing Regulation, and the transport and land use legislation [1]. New ambitious targets for RES and energy efficiency have been set: the intermediate target of a net reduction in greenhouse gas emissions is raised from 40% to at least 55% by 2030, as well as at least 32% share for renewable energy and at least 32.5% improvement in energy efficiency [1-2]. By 2050, the EU aims to achieve climate neutrality and strive to become the first climate-neutral continent [3]. As the world's largest emitter of carbon dioxide, China promised to peak CO<sub>2</sub> emissions before 2030 and achieve carbon neutrality before 2060, which will require significant changes to transform China's energy system [4-5].

Obviously, the fossil fuels dominated energy structure has difficulties in meeting the requirements of sustainable development. It is urgent to improve the energy consumption mode and reduce the dependence on fossil energy. Therefore, the development and utilization of RES, such as wind and solar energy, have gradually gained attention and shown a strong growth trend. On average, RES accounted for 19.7% of gross final energy consumption in the EU in 2019, up from 13.9% in 2009. Sweden ranked first in the EU, with RES accounting for 56.4% of its gross final energy consumption in 2019, and Germany ranked 16 across the EU with 17.4% while the EU average was 19.7%. Newly installed RES capacity in Asia accounted for 54% of the global total installed capacity in 2019. Among them, solar and wind energy accounted for 90% of the newly installed RES in 2019 [6]. The vigorous development and increasing penetration of RES force the global energy market and power system to undergo an unprecedented revolution.

Influenced by geographical differences, climate changes, and other factors, RES presents the characteristics of volatility, intermittency and randomness which threaten the secure and stable operation of power system and severely restrict the development of RES and related technologies. On the other hand, the wide and diverse access of DC sources and DC loads has become

a trend in electric energy applications. Driven by power electronics technology, the DC microgrid (DC-MG) thus emerges as an effective form for the local consumption of RES. Compared with the AC system, DC-MG has promising advantages of its high power-conversion efficiency, natural interface with RES, electronic loads and energy storage systems (EES), and no concern for power angle stability [7].

Considering the advantages of DC-MG, its usage covers various residential and industrial applications, such as rail transportations, aircrafts, and ship power systems, data centers, fast electric vehicle (EV) charging stations, high-efficiency households and renewable energy parks [8]. Nowadays, the electric traction DC power supply technology has matured. In terms of residential DC power supply, the EU, Japan and the United States have carried out relevant research and demonstration projects, which have laid a good theoretical and practical foundation for the promotion of DC-MG [8, 18, 34-35]. At present, there is no clear standard voltage class for the DC bus voltage. Usually, DC power supplies and DC loads convert and adjust their voltages according to their own requirements and industry standards. For instance, integrated circuits or chips usually operate at 5V and 12V, electronic devices such as computers and tablets operate at 12V, the DC voltages of EV batteries and on-board supplies are 12V, 24V, or 48V, the power supply system of telecom operates at 48V, the DC voltages of data centers and high-power appliances are 280V-400V, and charging piles operate at 250V-700V.

As an emerging technology, standardization is another obstacle to the proliferation of DC-MG in industrial and commercial applications. Several organizations and institutions have therefore developed practical standards. The European standard ETSI EN 300 132-3-1 is mainly designed for low-voltage DC (LVDC) systems, such as data/telecom equipments with voltage levels of up to 400V [9]. As an open industry association, the EMerge Alliance deploys advanced architectures and control systems based on DC-MGs in occupied spaces, data/telecom centers, building exteriors, and building services [10]. IEC SG4 delivers standards for LVDC distribution systems of up to 1500V [11] and coordinates the standardization of different utilizations of LVDC distribution systems. IEEE DC@Home concerns with developing the standards and defining the roadmap for research and commercialization of DC-MGs [12]. In addition, IEEE 946, Rebus and MIL-STD-1399 are proposed for standardizing the operation of DC-MG [8]. IEEE 946 is designed for the DC auxiliary power system, Rebus normalized the operation of DC-MG in residential and commercial applications, and MIL-STD-1399 provided the military standard for shipboard power systems.

Power electronic converters (PECs) are the key to integrating RES units, ESS, and various DC

loads into DC-MG, replacing traditional synchronous generators (SGs) that provide rotational inertia. In conventional power systems, SGs autonomously slow down or speed up in accordance with the grid frequency. In this way, SGs release/absorb the energy to/from the power grid so that the power mismatch can be partially compensated. This effect is quantitatively evaluated by the per unit kinetic energy, which is defined as the inertia of power systems [75]. As the penetration level of RES increases, more SGs are phased out and replaced by PEC, since RES is usually coupled to power systems through power electronic devices without rotational inertia. As a result, the entire power system becomes less inertial [81].

The PEC increases system bandwidth and its fast response capability brings flexibility to power systems. It also makes DC-MGs a typical power electronics dominated power system and exhibits low-inertia characteristics. In DC-MG, its inertia manifests the ability to prevent sudden changes in the DC bus voltage [73]. More specifically, due to the fast-response interface converters, the DC bus voltage may easily fluctuate beyond the acceptable range, resulting in undesirable load shedding and system collapses [54]. This means that DC-MG does not have sufficient inertia to stabilize the DC bus voltage. Therefore, it is necessary to develop measures to improve the dynamic behavior.

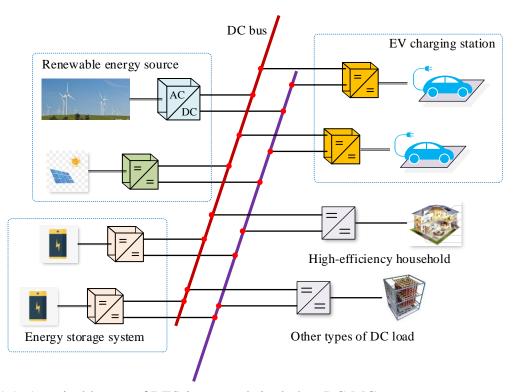

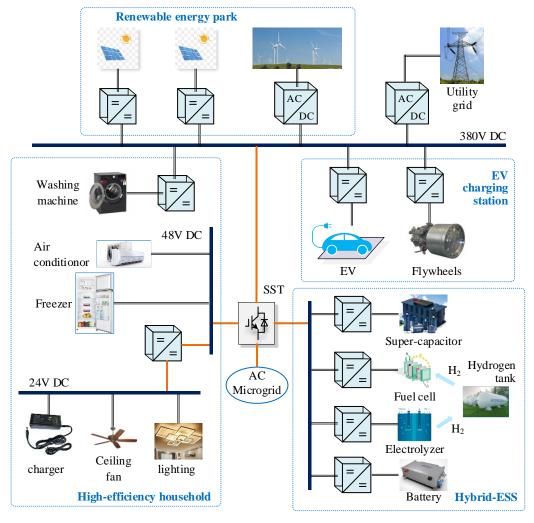

Figure 1.1: A typical layout of RES-integrated single-bus DC-MG.

Besides, most loads are connected to the DC bus via PECs, which makes the loads behave as constant power loads (CPLs). Further, the negative impedance characteristics of CPLs would

reduce the system damping, make DC-MG poor damping, and destabilize the DC-MG after being disturbed. In addition, RES would bring the problem of power quality degradation and difficult energy management. ESS, as a supporting source, can provide better conditions for integrating RES into DC-MG because ESS can balance the output power of RES and load demand to solve the voltage fluctuation/oscillation problem caused by power fluctuations of RES.

DC-MG would become the main access target of RES and an important component of the future smart grid. The typical structure of a single-bus RES-integrated DC-MG is shown in Figure 1.1. It mainly includes photovoltaic plants, wind farms, ESS, EV charging stations, high-efficiency buildings and other DC loads. The studies in Chapters 3-6 of this dissertation are mainly based on Figure 1.1 or its simplified version.

It can be seen from Figure 1.1 that most RES, ESS and loads have DC properties and can be connected to DC-MG directly or via interface converters. Thus DC-MG would become one of the main forms or an important element in the future power systems to cope with the large-scale RES integration into the grid. Therefore, ensuring the secure and stable operation of DC-MG is conducive to overcoming the bottleneck of connecting RES to the grid and solving the problem of efficient consumption of RES, which is of great theoretical and practical significance for the development of the future power system.

As the only indicator of the security and stable operation of the DC-MG, the instability of the DC-bus voltage would jeopardize the stable operation of the whole DC-MG. The main motivation of this research is to improve the stability of DC-MG and power quality for users by providing sufficient virtual inertia and damping. Increasing inertia can slow down the dynamic response of DC-MG and thus reduce RoCoV, while increasing damping can suppress the amplitude of voltage oscillations. Taking full advantage of ESS's ability to suppress DC bus voltage fluctuations provides a theoretical basis for accessing RES into DC-MG with high penetration. Further, it is of great significance to study the stabilization technology and low-frequency oscillation (LFO) mechanism of DC-MG to ensure its stable operation.

## 1.2 Research Questions and Corresponding Sulutions

This research focuses on how to improve voltage stability without additional hardware and intuitively reveal the LFO mechanism in islanded DC-MG. Especially, the following problems are worthy of more in-depth investigations:

(1) Problem of how to enhance the inertia and damping of suppressing voltage oscillations.

An appropriate stabilization control method is a good solution to improve the dynamic

response of DC-MG. Without modifications to the system hardware, the inertia can be synthesized by the energy stored in ESS to mitigate voltage oscillations caused by power disturbances. By properly regulating ESS to release or absorb energy as the rotors of DC machines and capacitors do and connecting a virtual resistance in series with the output port, DC bus voltage oscillations can be alleviated. Compared with connecting capacitors which will bring additional power losses and are limited by certain application scenarios with limited space, such as ship electrical systems, stabilization control methods basically would not increase system costs, because the virtual inertia power and damping power are provided for ESS which is always required in islanded DC-MG for voltage stabilization. Moreover, control parameters should be carefully determined to ensure better control performance and excellent dynamic response.

- (2) Problem of how to simplify the structure and complexity of virtual inertia and damping control to reduce the difficulty of its realization.

- The existing virtual inertia and damping control (VIDC) strategy for DC-MG is derived from the external characteristic of a capacitor or the operation principle of a rotating machine. An additional loop is requested to imitate the inertial response, complicating the overall control system and its implementation. How to streamline the control structure of VIDC for easier utilization in engineering applications becomes an important issue. Besides, a unified analytical method and related analysis tool are necessary to illustrate the stability mechanism of various inertia controls and intuitively observe the interaction between feedback variables. Therefore, the physical significance and control function of the parameters can be explained from multiple perspectives.

- (3) Problem of establishing an impedance modelling framework for analyzing LFO mechanisms in an intuitive view.

- The stability mechanism of VIDC, the influence of CPL on VIDC, and the LFO mechanism of VIDC controlled DC-MG (VIDC-DC-MG) with a clear physical significance are less investigated. Besides, there is a lack of appropriate analysis tools to identify the potential instability factors of VIDC-DC-MG.

At present, three mainstream modelling approaches are used for the stability analysis of power electronics systems: the transfer-function-based method, the state-space-model-based method, and the impedance-model-based method. The transfer-function-based method focuses on the relationship between key variables and is therefore incomprehensive compared with the state-space model. The state-space model describes each variable of the system and thus can gain insight into the leading causes of underdamped

or unstable modes. However, the state-space model is a white-box model in nature and requires complete system information, and its abstract form makes it difficult to intuitively clarify the mapping between the oscillation modes and the corresponding factors. The all-in-one impedance model that can be directly measured and verified has less requirements for design details. Hence, it is more suitable for stability evaluation with clear physical meanings. However, the existing impedance model lacks systematic and intuitive insight into the internal roots of underdamped or instability factors, and is essentially a black-box model.

Therefore, an appropriate modeling framework as the bridge between white-box and black-box modeling by combining the advantages of the impedance model and the state-space model is necessary and worth investigating for the LFO mechanism analysis.

(4) Problem of how to address the state-of-charge imbalance in multi-parallel ESS.

Multi-parallel ESS is indispensable as the supporting energy source of DC-MG. The parameter mismatches of energy storage units (ESU), such as various series resistances, different self-discharge rates, and uneven operation temperatures across ESU, result in significant divergence of state of charge (SoC) among ESUs. Thus the unbalanced SoC leads to over-charge/-discharge and even explosion, degrades the utilization of some ESUs and decreases the operation lifespan of batteries. Therefore, how to achieve SoC balance under the premise of improved system dynamic stability becomes particularly important. Besides, the optimal design of key parameters should also be considered to address the contradiction between the speed of SoC balancing and system stability.

Aiming at the above problems (1)-(4), this dissertation proposes corresponding solutions, mainly including the following aspects:

- (1) Propose a VIDC to suppress voltage oscillations in islanded DC-MGs. Without modifying system hardware and increasing system cost and complexity, the proposed VIDC can regulate ESS to release or absorb energy as rotors of DC machines and capacitors do. Thus, inertia can be synthesized by the energy stored in ESS to mitigate the voltage oscillations caused by power disturbances.

- (2) Develop inertia droop controls to simplify the complexity of VIDC. In order to stream-line the control structure of VIDC for easier implementation in engineering applications, inertia droop controls are designed based on the equivalent droop-control-form models of VIDC. Besides, a unified analytical method and related analysis tool should be provided to illustrate the stability mechanism of various inertia controls from multi-views.

- (3) Establish a modeling framework for the LFO mechanism analysis. The proposed multi-timescale impedance modeling framework can be converted into a white-box or black-box model depending on the need for analysis. Control loops of different timescales are visualized as independent loop virtual impedances, and the impedance properties of control loops/parameters and their impedance-shaping effects can be illustrated at various timescales to explain the LFO in different bandwidths.

- (4) Achieve SoC self-balance of multi-parallel ESS by the inertia-emulation based cooperative control. Under the premise of ensuring the increased inertia to improve the system stability, the SoC imbalance problem should be solved by the SoC self-balance algorithm and the SoC self-balance rate can be adjusted. Besides, the contradiction between the SoC balancing speed and maintaining system stability should be considered.

To sum up, the overall objective of this dissertation is to propose a stabilization control method for bidirectional DC converters to improve the voltage stability and quality of DC-MG, to establish a suitable modeling framework to explore the LFO mechanism, and to address the hazards of SoC divergence by the proposed inertia-emulation based cooperative control.

#### 1.3 Outlines of the Dissertation

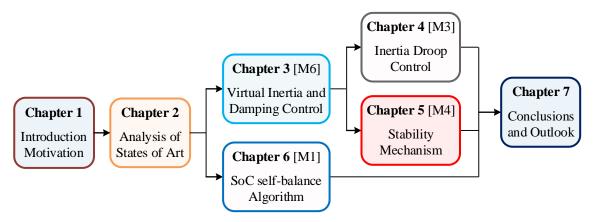

The structure of this dissertation is demonstrated in Figure 1.2 and organized as follows:

In Chapter 2, the state of art about investigations on DC-MG is summarized from four aspects. Firstly, the topologies of DC-MG and their applications are presented, and the main causes of DC voltage fluctuations and their manifestations are reviewed. Then, the basic principle of commonly used stabilization control methods is introduced. Subsequently, the mainstream modeling and stability analysis methods are reviewed. Moreover, the SoC balance methods for multi-parallel ESS are also introduced.

In Chapter 3 [M6], a VIDC strategy is proposed to enable bidirectional DC (bi-DC) converter to dampen voltage oscillations by using the energy stored in ESS to emulate the inertia of DC-MG without modifications of system hardware. Both the inertia part and the damping part are modeled in the VIDC controller, by analogy with DC machines. Droop control is introduced to achieve the multi-parallel operation of ESS. Furthermore, the small-signal model is established and the dynamic characteristics of DC bus voltage under power fluctuations are analyzed. A 2nd-order equivalent model is introduced to simplify the parameter design. By analyzing the control performance indices, the VIDC parameters are optimized. At last, based on the principle

of equivalent machine, an inertia matching method for multi-parallel bi-DC converters is proposed. The simulation results verify that ESS by acting as synthetic inertia can improve the voltage dynamic characteristics and stability in islanded DC-MGs. Compared with other control methods, it has better control effects.

Figure 1.2: Structure of the dissertation.

In Chapter 4 [M3], inertia droop control (IDC) strategies are proposed for a bidirectional DC converter (BiC) to improve dynamic stability and provide high-quality power supply in islanded DC-MG. Compared with VIDC, the proposed IDC can be implemented by easily modifying conventional droop control, which avoids a complex control structure. First, the virtual inertia in the proposed IDC strategies can be achieved in two ways: 1) dynamic virtual impedance, and 2) adaptive droop algorithm. The damping support comes from the redesigned damping term which features secondary voltage regulation to eliminate the voltage deviation. Then, a feedback analytic method is proposed to comprehend the stability mechanism from multiple perspectives, and a double-coordinate-based phasor diagram is developed as its analytical tool to intuitively observe the interaction between variables. Accordingly, the IDC's negative feedback property is revealed, and the impactors of system inertia, stiffness and dissipation properties are explored. Dynamic performance and small-signal stability analysis are also presented to guide parameter selection and optimize transient response. Hardware in the loop (HIL) experiment results verify that IDC strategies have similar effects to VIDC while simplifying the control structure.

In Chapter 5 [M4], the multi-timescale impedance modeling framework is established to clarify the stability mechanism of VIDC and the LFO of VIDC controlled islanded DC-MG. Control loops of different timescales are visualized as independent loop virtual impedance elements to form an impedance circuit considering the CPL, rather than an all-in-one impedance as the

external dynamic representation of power converters. Concrete impedance analysis is performed on loop virtual impedances to reveal the impedance-shaping effect of control loops intuitively, the physical impedance nature of control parameters and the interaction between different timescale, which illustrates the stability mechanism of VIDC. The LFOs (*LC* impedance interaction) in voltage and inertia loops are elaborated by *RLC* circuits of loop virtual impedances. The potential instability factors resulting in poor damping against voltage oscillations are also revealed. Thus, a dynamic stability enhancement method is proposed to compensate for the negative damping caused by the positive feedbacks of VIDC and CPL, and a supercapacitor is added to alleviate rapid voltage changes. Accordingly, the passivity property of the system impedance is strengthened and the stability can be evaluated by Nyquist plot. Finally, the simulation and experiment results have validated the LFO analysis and stability enhancement methods.

In Chapter 6 [M1], an inertia-emulation-based cooperative control strategy for multi-parallel ESS in islanded DC-MG is proposed to address the state-of-charge (SoC) imbalance and voltage deviation problem in steady-state operation and the voltage stability problem caused by inertia-less in transient process, as well as an optimal parameter design is carried out. A SoC self-balance algorithm is developed to dynamically equalize SoC of energy storage units (ESUs). The defined SoC mismatch degree and the balance speed adjustment factor k are introduced into the droop resistance to adjust the SoC self-balance rate and eliminate the SoC deviation among ESUs. And the contradiction between SoC balancing speed and maintaining system stability is addressed by this redefined SoC-based droop resistance function. In addition, the inertia emulation loop is constructed by analogy with DC motors to dampen voltage oscillations, while the secondary voltage recovery loop is derived from the circuit equivalence of an inductor to indicate system stiffness and achieve zero-steady-state voltage deviation. The dynamic performance of the SoC self-balance algorithm is analyzed and the small-signal model of the multi-parallel ESS with the proposed strategy is established. Based on the eigenvalue analysis and step response, the system stability is assessed, and the influences of the control parameters on the transient response and stability margin are investigated. Considering the power constraint, the voltage deviation constraint and the stability constraint, the optimal design method of k is given. Finally, simulations and HIL experiments prove that the proposed control has better dynamic and static performances without modifying hardware and can equalize SoC in charge and discharge mode.

Finally, Chapter 7 summarizes all the research in the dissertation, points out the remaining

problems in the research process, and gives an outlook for the next research content.

# 2 Analysis of the State of the Art

Extensive research has been conducted on the stability analysis and stabilization control methods of power electronics systems, such as DC microgrids (DC-MG). This chapter presentes an overview of challenges and problems in the development of DC-MGs, including main topologies of DC-MG and the classification of DC bus voltage fluctuations (DC-BVF), stabilization control methods, low-frequency oscillation (LFO) mechanism analysis methods, and energy management systems. This chapter closes with concluding the reason for the stabilization technique and stability analysis approach pursued in this thesis.

## 2.1 Review of DC-MG Topologies and Bus Voltage Fluctuation Classification

Driven by practical requirements of certain DC-MG applications, various topologies and their applications have been reported in literatures [8], which are reviewed. Besides, since DC bus voltage stability is the key to the stable operation of DC-MG and needs in-depth study, the leading causes and classification of DC-BVF are analyzed and summarized.

## 2.1.1 Topologies of DC-MG and its applications

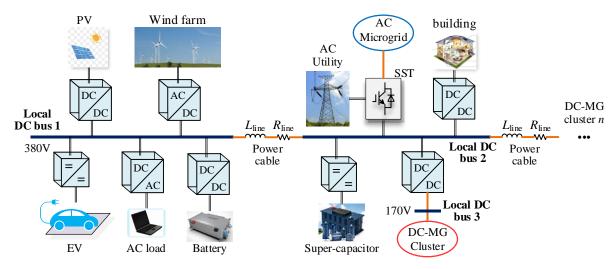

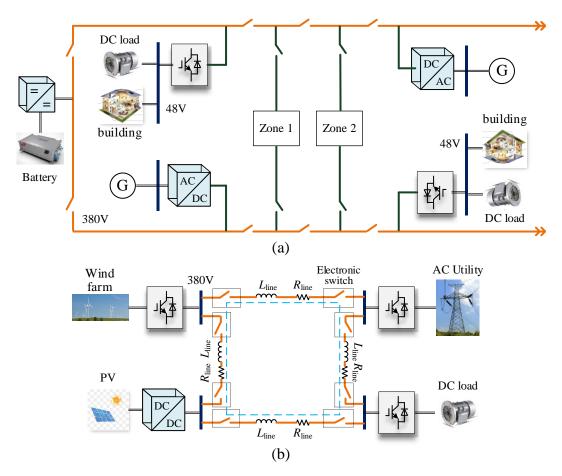

Typical DC-MG topologies and their applications are reviewed here. A number of topologies have been reported in the existing literatures and this section assess of the most prominent representatives. Generally, the DC-MG topologies can be classified into three categories, that is, single-bus topologies, multi-bus topologies, and reconfigurable topologies. Besides, this section also gives an overview of corresponding industrial scenarios.

#### (a) single-bus topology:

First of all, the single-bus topology is reviewed. As the basis of DC power systems, the single bus DC-MG topology is commonly deployed in industrial applications and a typical topology of single-bus DC-MG integrating RES has been presented in Figure 1.1. An energy storage system (ESS, usually an electrochemical battery pack) can be directly connected to the DC bus to maintain the DC bus voltage [13]. The number of series battery cells depends on the voltage required for the loads. This configuration operating at 48V has been used in telecommunications [14]. However, this configuration has the following drawbacks: (a) uncontrollable voltages, depending on the state of charge (SoC) and current of the battery, and (b) unregulated

battery charging [15]. As well as, ESS can be connected to the DC bus via a converter interface, which provides more flexible control and the possibility of connecting multiple buses to enhance system reliability or supply loads over a wider area [16], while paralleled converters exist circulating current problem which leads to uneven loading and accelerates the wear of the stationary battery [17]. The only one DC bus compels consumers to adapt to this voltage level, thus lacking flexibility. To solve this problem, a bipolar single regulated bus structure is proposed in [18]. This configuration provides load-side DC–DC converters with the option to select source voltages of 340, +170, and -170V. The system reliability is thus increased, since power can be supplied by the other two lines and an auxiliary converter in the event of failures of one line.