Copyright

by

Kai Wang

2020

# The Dissertation Committee for Kai Wang certifies that this is the approved version of the following dissertation:

# **Improving Efficiency for GPUs with Decoupled Delegate**

Committee:

Calvin Lin, Supervisor

Donald Fussell, Co-Supervisor

Chris Rossbach

Steve Keckler

# **Improving Efficiency for GPUs with Decoupled Delegate**

by

# Kai Wang

#### **DISSERTATION**

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

#### DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN

December 2020

### **Acknowledgments**

I'd like to thank the many people who helped me during my PhD studies. First, I'd like to thank my advisors, Calvin Lin and Don Fussell. They provided excellent mentorship and helped me grow intellectually. I am fortunate to have them as my advisors. Dr. Lin helped me to see the bigger picture behind specific research questions and helped me to understand the importance of a strong research methodology. I'm especially grateful for his guidance on how to write clear documents. Dr. Fussell helped me to look beyond the immediate research questions and helped me to connect dots between my own research and that of broader fields. I'm especially grateful for his guidance on how to present ideas clearly. The skills I acquired from my advisors will be immensely beneficial to my future career.

Next, I'd like to thank my committee members, Chris Rossbach and Steve Keckler. Dr. Rossbach pointed me to important related work for comparative study. Dr. Keckler raised interesting questions on work. Their value feedback helped me greatly during the process of improving my dissertation.

I'd like to thank my group members, Akanksha, Hao, Zhan, Chirag, Curtis, and Molly for their valuable feedback, and I also broadened my knowledge by learning from their research.

Finally, I'd like to thank my mother, Rong. I wouldn't be able to finish my degree without her support along the way.

**Improving Efficiency for GPUs with Decoupled Delegate**

Kai Wang, Ph.D.

The University of Texas at Austin, 2020

Supervisors:

Calvin Lin

Co-Supervisor: Donald Fussell

GPUs are increasingly used for general-purpose computation. For many ap-

plications, GPUs achieve significant performance advantages over CPUs, largely

due to GPUs' ability to exploit massive parallelism. However, massive parallelism

can cause inefficiency for many operations, such as concurrent data structures.

Symptoms include synchronization bottleneck and redundant overheads.

To make such operations efficient, our key strategy is to *decouple* them from

the rest of GPU program. Then, we use a few threads acting as a *delegate* to perform

the decoupled operations on behalf of all other threads. This reduces the synchro-

nization for decoupled operations because fewer threads are used. In addition, the

delegate amortizes overheads for other threads, similar to the way in which vector

execution amortizes instruction overheads. The cost of our approach is the need

for communication between the delegate and other threads. We develop innovative

ways to reduce the communication so that the benefit strongly outweighs the cost.

Based on the strategy, we propose three solutions for both regular and irregular

workloads.

vi

For regular GPU workloads, our solution reduces repetitive ALU OPs and instruction execution, while reducing memory latency with non-speculative prefetching. This approach enabled our solution to achieve 40.7% speedup and 20.2% energy reduction on average for 29 benchmarks. For lock-based workloads, our solution avoids destructive lock contention in global memory and thus achieves an average speedup of 3.6×, implemented entirely in software. Finally, we introduce a new GPU single source shortest path (SSSP) algorithm with a complex worklist; it offers many benefits compared to a simpler worklist but incurs significant overheads. However, our decoupled delegate approach reduces the overheads and makes the complex worklist design efficient for GPUs. Hence, our solution, implemented in software, achieved an average speedup of 2.8× over 226 graphs compared with state-of-the-art approaches.

# **Table of Contents**

| Acknowledgments                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |  |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|

| Abstra                                                      | ct                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | vi   |  |

| List of                                                     | Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | xii  |  |

| List of                                                     | Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | xiii |  |

| Chapte                                                      | er 1. Introduction <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1    |  |

| 1.1                                                         | Goal of this Thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3    |  |

| 1.2                                                         | Worklist-Based Algorithms—problem and strategy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3    |  |

| 1.3                                                         | Generalization of the Problem and Strategy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6    |  |

| 1.4                                                         | Cost of Decoupled Delegate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9    |  |

| 1.5                                                         | Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9    |  |

| Chapte                                                      | er 2. Related Work <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11   |  |

| 2.1                                                         | Repetitive Computation Reduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11   |  |

| 2.2                                                         | Memory Latency Reduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 12   |  |

| 2.3                                                         | Fine-Grained Synchronization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 13   |  |

| 2.4                                                         | Sinlge Source Shortest Path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 15   |  |

| 2.5                                                         | Delegation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 16   |  |

| Asi<br>Fa<br>A<br>M<br><sup>2</sup> Porti<br>Asi<br>Fa<br>A | tons of this chapter are based on the following publications:  ffine Computation for SIMT GPUs, ISCA 2017[134]  ast Fine-Grained Global Synchronization on GPUs, ASPLOS 2019[133]  Fast Work-Efficient SSSP Algorithm for GPUs, to be appear in PPOPP 2021  by contributions: I'm the first author for all three papers  ions of this chapter are based on the following publications:  ffine Computation for SIMT GPUs, ISCA 2017[134]  ast Fine-Grained Global Synchronization on GPUs, ASPLOS 2019[133]  Fast Work-Efficient SSSP Algorithm for GPUs, to be appear in PPOPP 2021  for contributions: I'm the first author for all three papers |      |  |

| Chapter | r 3. Decoupled Affine Computation <sup>3</sup>           | 20         |

|---------|----------------------------------------------------------|------------|

| 3.1     | Background and Motivation                                | 24         |

| 3.2     | Our Solution                                             | 27         |

| 3.3     | Implementation                                           | 30         |

|         | 3.3.1 <b>Expansion Units</b>                             | 32         |

|         | 3.3.2 <b>Prefetching</b>                                 | 33         |

|         | 3.3.3 Control Flow Handling                              | 35         |

|         | 3.3.4 Divergent Affine Tuples                            | 36         |

| 3.4     | Methodology                                              | 4(         |

|         | 3.4.1 Baseline Techniques                                | 41         |

|         | 3.4.2 <b>Benchmarks</b>                                  | 43         |

| 3.5     | Evaluation                                               | 43         |

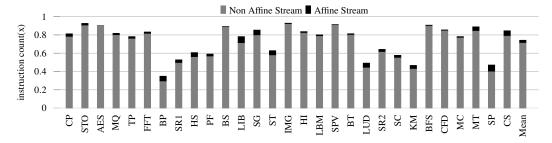

|         | 3.5.1 <b>Instruction Execution Reduction</b>             | 44         |

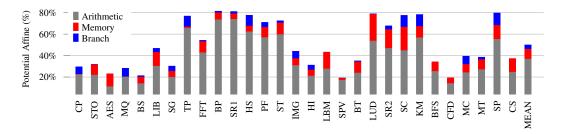

|         | 3.5.2 Affine Instruction Coverage                        | 45         |

|         | 3.5.3 Memory Latency Hiding                              | 46         |

|         | 3.5.4 Energy Efficiency                                  | 47         |

|         | 3.5.5 <b>Area Estimation</b>                             | 48         |

| 3.6     | Summary                                                  | 49         |

| Chapte  | r 4. Decoupled Fine-Grained Synchronization <sup>4</sup> | <b>5</b> 1 |

| 4.1     | Motivation                                               | 52         |

| 4.2     | Our Solution                                             | 53         |

|         | 4.2.1 Decoupled Program                                  | 55         |

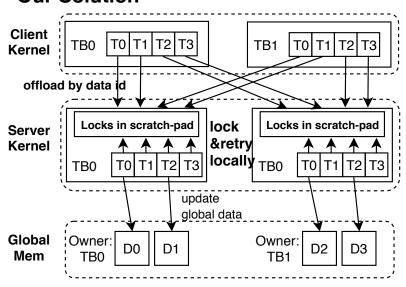

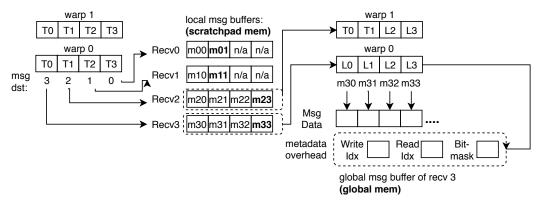

| 4.3     | Our Software Message Passing System                      | 59         |

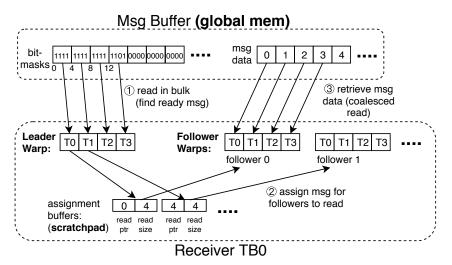

|         | 4.3.1 Our Basic Algorithm                                | 59         |

|         | 4.3.2 Our Optimized Algorithm                            | 61         |

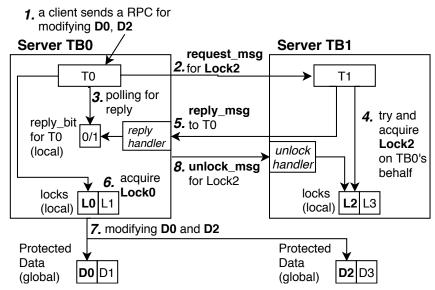

| 4.4     | Handling Nested Locks                                    | 63         |

Fast Fine-Grained Global Synchronization on GPUs, ASPLOS 2019[133]

My contributions: I'm the first author for the paper

$<sup>^3</sup>$ Portions of this chapter are based on the following publication:

Affine Computation for SIMT GPUs, ISCA 2017[134]

My contributions: I'm the first author for the paper

<sup>&</sup>lt;sup>4</sup>Portions of this chapter are based on the following publication:

| 4.5                  | Metho                  | odology                                                     |  |  |

|----------------------|------------------------|-------------------------------------------------------------|--|--|

| 4.6                  | Evalua                 | ation                                                       |  |  |

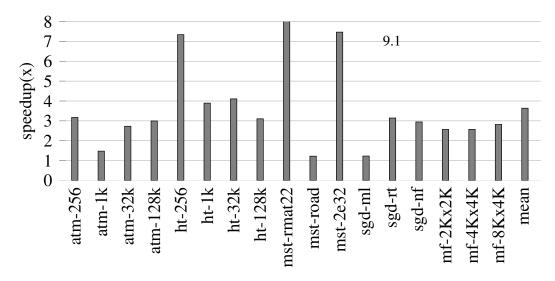

|                      | 4.6.1                  | <b>Performance</b>                                          |  |  |

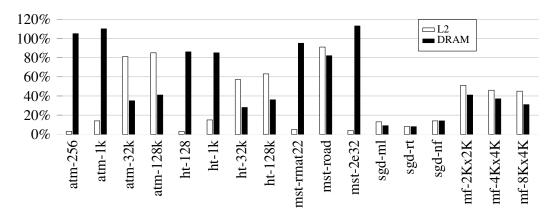

|                      | 4.6.2                  | <b>Bandwidth Benefits</b>                                   |  |  |

|                      | 4.6.3                  | Latency Benefits                                            |  |  |

|                      | 4.6.4                  | <b>Comparison Against Hardware Solutions</b>                |  |  |

| 4.7                  | Summ                   | nary                                                        |  |  |

|                      |                        | _                                                           |  |  |

| -                    |                        | A GPU SSSP Solution with Decoupled Worklist <sup>5</sup> 75 |  |  |

| 5.1                  | _                      | ground                                                      |  |  |

|                      | 5.1.1                  | Work Scheduling                                             |  |  |

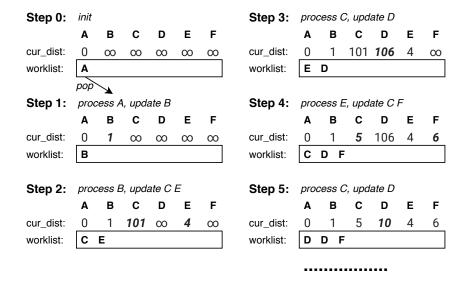

|                      | 5.1.2                  | $\Delta$ -Stepping                                          |  |  |

| 5.2                  | Motiv                  | ation                                                       |  |  |

|                      | 5.2.1                  | <b>Design Consideration 1</b>                               |  |  |

|                      | 5.2.2                  | <b>Design Consideration 2</b>                               |  |  |

|                      | 5.2.3                  | <b>Design Consideration 3</b>                               |  |  |

| 5.3                  | The O                  | verview of Our Solution                                     |  |  |

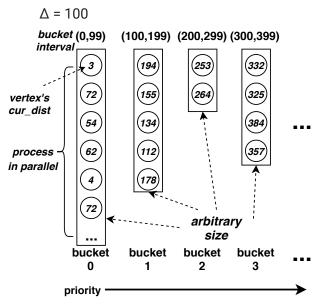

| 5.4                  | A Single Bucket        |                                                             |  |  |

| 5.5                  | Multiple Buckets       |                                                             |  |  |

| 5.6                  | Dynamic Data Structure |                                                             |  |  |

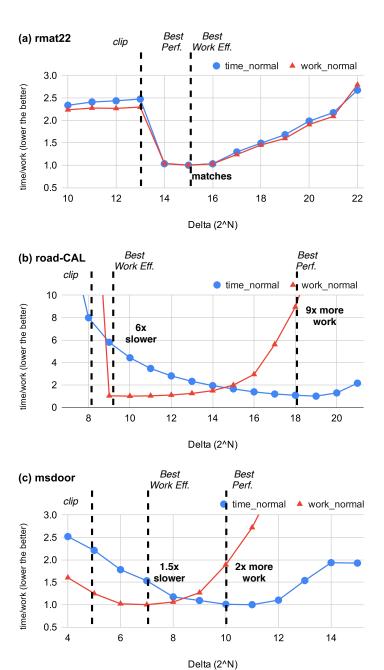

| 5.7 Setting $\Delta$ |                        | g $\Delta$ dynamically                                      |  |  |

|                      | 5.7.1                  | Finding the <i>Clip-Point</i>                               |  |  |

|                      | 5.7.2                  | Changing $\Delta$ Based on Utilization                      |  |  |

| 5.8                  | Metho                  | odology                                                     |  |  |

|                      | 5.8.1                  | Graph Inputs                                                |  |  |

|                      | 5.8.2                  | Evaluated Prior Implementations                             |  |  |

| 5.9                  | Evalua                 | ation                                                       |  |  |

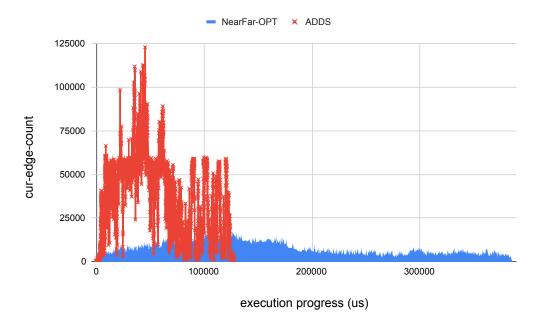

|                      | 5.9.1                  | Timing Results                                              |  |  |

|                      | 5.9.2                  | Work Efficiency                                             |  |  |

A Fast Work-Efficient SSSP Algorithm for GPUs, to be appear in PPOPP 2021

<sup>&</sup>lt;sup>5</sup>Portions of this chapter are based on the following publication:

|         | 5.9.3 Performance Analysis                                                                                           | 118 |

|---------|----------------------------------------------------------------------------------------------------------------------|-----|

| 5.10    | Summary                                                                                                              | 125 |

| Chapte  | r 6. Conclusion <sup>6</sup>                                                                                         | 126 |

| 6.1     | Why does the decoupled delegate approach work well on GPUs, and what other platforms may benefit from this approach? | 127 |

| 6.2     | Should we make irregular algorithms architectural efficient or algorithmic efficient? Or could we have both?         |     |

| Bibliog | raphy                                                                                                                | 131 |

<sup>&</sup>lt;sup>6</sup>Portions of this chapter are based on the following publications:

Affine Computation for SIMT GPUs, ISCA 2017[134]

Fast Fine-Grained Global Synchronization on GPUs, ASPLOS 2019[133]

A Fast Work-Efficient SSSP Algorithm for GPUs, to be appear in PPOPP 2021

My contributions: I'm the first author for all three papers

# **List of Tables**

| 3.1 | Simulation Parameters                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.2 | List of Benchmarks – G: GPGPU-sim distribution [10], R: Rodinia benchmark suite [22], C: CUDA SDK, P: Parboil benchmark                                                                                                                                                                                                                                                                                                                 |

|     | suite [128]                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4.1 | GTX 1080 ti Specifications                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4.2 | Latency and Total Execution Time                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4.3 | <b>Speedup over respective baselines</b> —For HQL, the results are from Figure 12 of the paper [146]; the baseline is a simulated Radeon HD 5870 GPU. For BOWS, the results are from Figure 15 of the paper [40]; the baseline is a simulated GTX 1080ti. The HQL paper only provides results for the HT microbenchmark, and the BOWS paper only provides results for HT-1K and ATM-1K; unavailable results are left blank in the table |

| 5.1 | RTX 2080 ti GPU                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5.2 | The Distribution of Graph Characteristics—count(% of 226 graphs) 111                                                                                                                                                                                                                                                                                                                                                                    |

| 5.3 | Speedup of ADDS over prior implementations—the distribution of 226 graphs over speedup intervals                                                                                                                                                                                                                                                                                                                                        |

| 5.4 | The execution time of ADDS, NearFar-OPT ( <b>NF</b> ), Gunrock-Bellman-Ford (BF), and nvGRAPH (NV). The speedup column is ADDS over NF                                                                                                                                                                                                                                                                                                  |

| 5.5 | Normalized vertex processing count of ADDS (lower the better) 117                                                                                                                                                                                                                                                                                                                                                                       |

# **List of Figures**

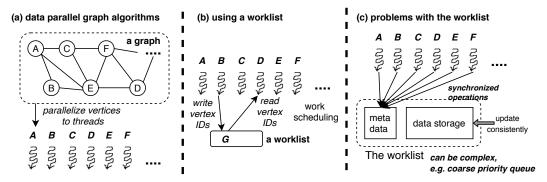

| 1.1  | (a) data parallelism for graph processing. (b) adding a worklist to the graph algorithm. (c) problems caused by using a worklist                                             | 2  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

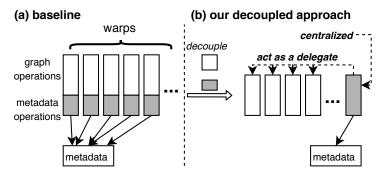

| 1.2  | Our Decoupled Delegate Strategy                                                                                                                                              | 4  |

| 1.3  | Code sample: each thread increments an array element—instr0 and instr1 calculate the memory access address, and instr2 and instr3 load the data and perform the computation. | 7  |

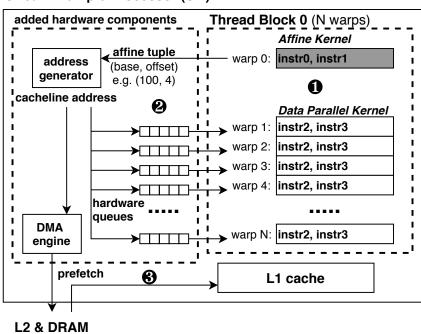

| 3.1  | <b>Decoupling Repetitive Computations</b> : the figure illustrates our solution                                                                                              | 21 |

| 3.2  | Operand Values–Baseline GPU and Affine Computation                                                                                                                           | 24 |

| 3.3  | Example Kernel                                                                                                                                                               | 26 |

| 3.4  | Affine Values and Affine Tuples for 3 Threads                                                                                                                                | 26 |

| 3.5  | Percentage of Instructions Computing on Scalar Data and Thread IDs                                                                                                           | 27 |

| 3.6  | Decoupled Kernels                                                                                                                                                            | 29 |

| 3.7  | Interaction Between the Affine Warp and the Non-Affine Warps                                                                                                                 | 30 |

| 3.8  | DAC Hardware Organization                                                                                                                                                    | 31 |

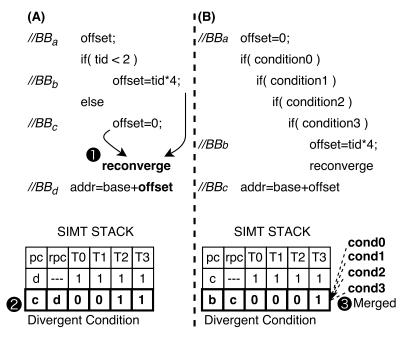

| 3.9  | Re-Convergence Stack for the Affine Warp                                                                                                                                     | 35 |

| 3.10 | Divergent Base-Offset Pairs on SIMT Lanes                                                                                                                                    | 37 |

| 3.11 | Using SIMT Entry as Divergent Condition                                                                                                                                      | 39 |

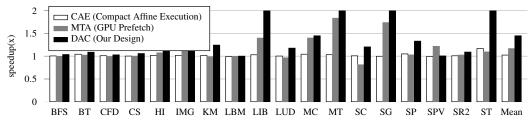

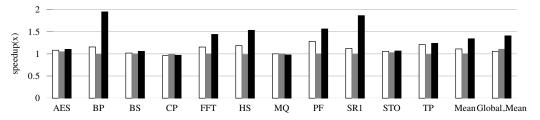

| 3.12 | Speedup of CAE, MTA, and DAC over the Baseline GTX 480 GPU                                                                                                                   | 42 |

| 3.13 | Number of Warp Instructions Executed by DAC Normalized to the Baseline GPU                                                                                                   | 44 |

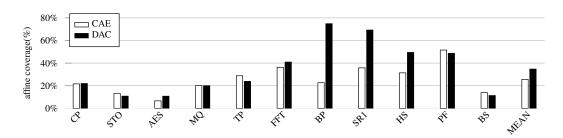

| 3.14 | Affine Instruction Coverage of DAC and CAE                                                                                                                                   | 45 |

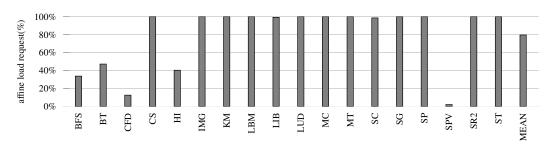

| 3.15 | Percentage of Affine Global and Local Load Requests on DAC                                                                                                                   | 46 |

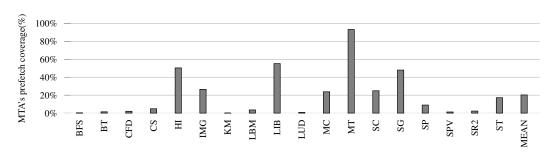

| 3.16 | MTA Prefetcher Coverage                                                                                                                                                      | 47 |

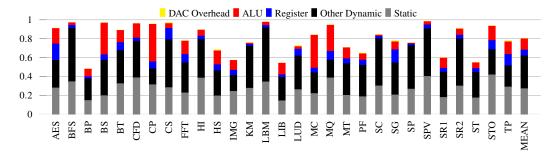

| 3.17 | Energy Consumption of DAC Normalized to the Baseline GPU                                                                                                                     | 48 |

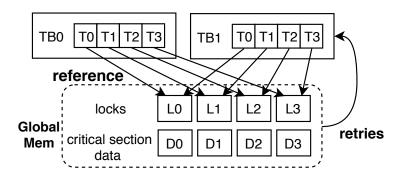

| 4.1  | Fine-grained mutual exclusion with (a) global locks (baseline) and (b) our solution                                                                                          | 54 |

| 4.2  | The basic data structure of a single message buffer and the basic algorithm for reading and writing                                                                                                                                                                                                                                       | 60  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.3  | Sender Design—using local buffers for aggregated message write .                                                                                                                                                                                                                                                                          | 61  |

| 4.4  | Receiver Design—using a single warp (the leader warp) for metadata accesses                                                                                                                                                                                                                                                               | 62  |

| 4.5  | <b>Synchronization Server for Two Nested Lock</b> —operations for handling an offloaded request from client that involves two server TBs                                                                                                                                                                                                  | 65  |

| 4.6  | Speedup of our solution over the state-of-the-art                                                                                                                                                                                                                                                                                         | 69  |

| 4.7  | L2 and DRAM traffic of our solution as a percentage (%) of the baseline—The L2 traffic is the total cache-line accesses of global loads and stores and atomics, including misses to DRAM. The DRAM traffic includes both reads and writes. The traffic includes overhead due to non-coalesced accesses (i.e. unused words in cache lines) | 70  |

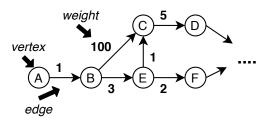

| 5.1  | An Example Graph—edges are directed with weight                                                                                                                                                                                                                                                                                           | 79  |

| 5.2  | Illustrate SSSP step-by-step                                                                                                                                                                                                                                                                                                              | 79  |

| 5.3  | $\Delta$ -Stepping's Work Scheduling Data Structure                                                                                                                                                                                                                                                                                       | 82  |

| 5.4  | Implementing a List as Double Buffers                                                                                                                                                                                                                                                                                                     | 85  |

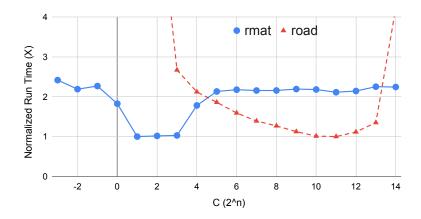

| 5.5  | Execution Time against $C$ for Two Graphs—the execution time is normalize to the minimum in the series; labels of the x-axis are power of $2 \dots \dots \dots \dots \dots \dots \dots \dots$ .                                                                                                                                           | 88  |

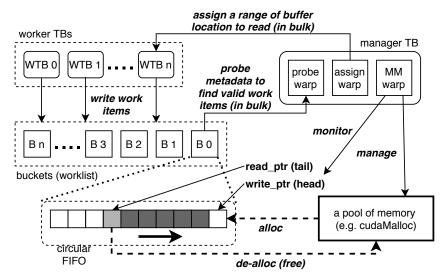

| 5.6  | The Overview of Components' Functionalities                                                                                                                                                                                                                                                                                               | 91  |

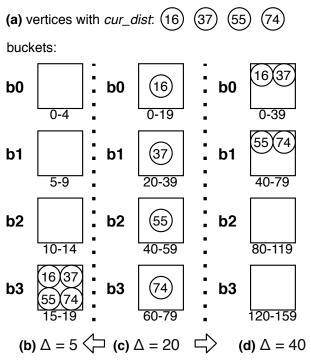

| 5.7  | How $\Delta$ Affects Work Efficiency and Concurrency—pushing 4 vertices (a) to 4 buckets under 3 scenarios: when $\Delta$ =20 (c), it has best work efficiency; when increased to 40 (d), it improves concurrency; but when decreased to 5 (b), all vertices are clipped to the last                                                      | 101 |

| 5.8  | This Experiment Plots Execution Time and Work Performed Against $\Delta$ —the choices of $\Delta$ are predetermined and fixed during execution; both <i>time</i> and <i>work</i> are normalized to the lowest point (lower the better); finally, the experiments are done using 32 buckets                                                | 103 |

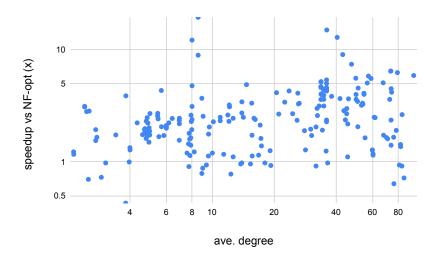

| 5.9  | The distribution of ADDS' speedup over NF-OPT correlating to graph degree                                                                                                                                                                                                                                                                 | 114 |

| 5.10 | graph diameter                                                                                                                                                                                                                                                                                                                            | 116 |

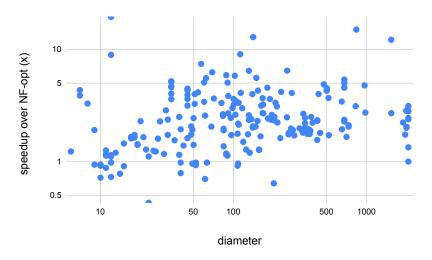

| 5.11 | The correlation between speedup and work-efficiency (inverse of vertex count); both higher the better.                                                                                                                                                                                                                                    | 118 |

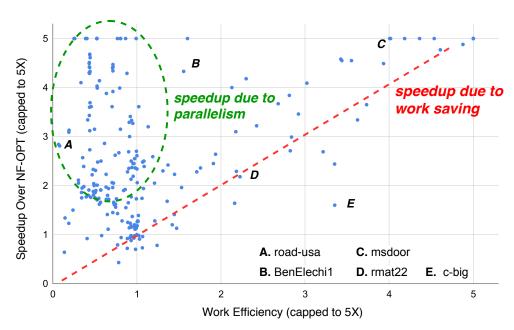

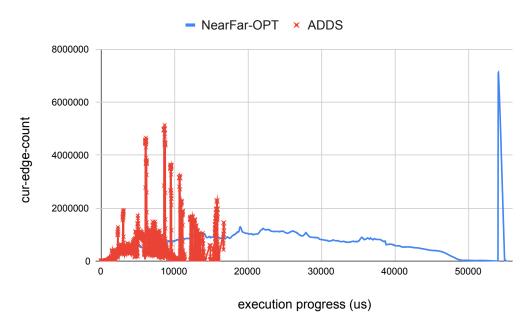

| 5.12 | A.road-USA: s:3.09x, w:0.19x (s:speedup, w:work-efficiency), the                          |

|------|-------------------------------------------------------------------------------------------|

|      | figure plots the amount of parallelism (edge count) during the progress of execution (us) |

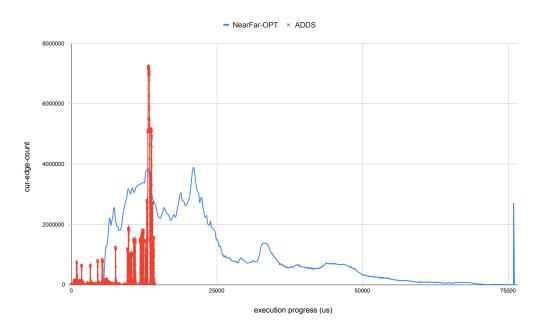

| 5.13 | B.BenElechi1: s:4x, w:2.12x                                                               |

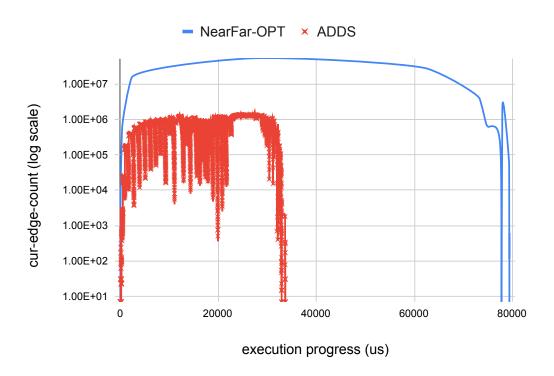

| 5.14 | C.msdoor: s:5.57x, w:4x                                                                   |

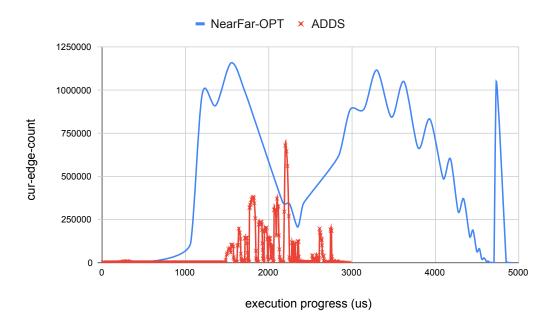

| 5.15 | D.rmat22: s:2.29x, w:2.18x                                                                |

| 5.16 | E.c-big: s:1.6x, w:3.35x                                                                  |

# **Chapter 1**

#### Introduction<sup>1</sup>

Historically, single thread performance (or ILP) has been the main focus of microprocessor design Although ILP is still at a premium even today for desktop and mobile CPUs, circa mid-2000s, the diminishing returns of complex superscalar CPU designs and the demise of Dennard scaling incentivized the industry to explore ways to the transistors on a chip. Evolved from dedicated 3D graphics accelerators, GPUs have emerged as attractive alternatives to CPUs for general–purpose applications.

GPUs deliver throughput by executing many lightweight scalar threads. The threads are organized hierarchically, first into thread blocks (*TBs*) and then into warps. At hardware level, threads within each warp are executed in lock-steps using a vector data path to amortize the instruction handling overhead. Warps within each TB are executed concurrently using fine-grained multi-threading to hide memory latency. This execution model is known as *single instruction multiple thread* (*SIMT*).

Affine Computation for SIMT GPUs, ISCA 2017[134]

Fast Fine-Grained Global Synchronization on GPUs, ASPLOS 2019[133]

A Fast Work-Efficient SSSP Algorithm for GPUs, to be appear in PPOPP 2021

My contributions: I'm the first author for all three papers

<sup>&</sup>lt;sup>1</sup>Portions of this chapter are based on the following publications:

The key to GPU hardware efficiency is to focus on throughput instead of latency. This means the workloads running on GPUs must have massive parallelism. In general, GPU workloads achieve parallelism by assigning different data elements, such as array elements, to different threads for processing; this is known as *data parallelism*. For regular data structures such as simple arrays and matrices, GPUs are highly efficient due to convergent control flow and coalesced memory access.

The principle of data parallelism also applies to irregular data structures such as graphs. As Figure 1.1 (a) shows, vertices of a graph can be parallelized in a similar way as array elements. These irregular workloads are less efficient for GPUs due to divergent control flow and memory access. However, prior work has shown that GPUs have performance advantages over CPUs for many irregular workloads, and various hardware and software optimizations have been proposed to reduce divergence [85, 114, 64, 68, 115, 23, 119, 86, 105]. Therefore, it is still beneficial to use GPUs for irregular workloads.

**Figure 1.1:** (a) data parallelism for graph processing. (b) adding a worklist to the graph algorithm. (c) problems caused by using a worklist

2

#### 1.1 Goal of this Thesis

For both regular and irregular workloads, there are two fundamental requirements for data parallelism to work efficiently. First, there exist many data elements that can be assigned to many threads. Second, threads could process these data elements independently from each other.

However, many GPU workloads contain routines that violate the two requirements. Simply executing such routines with many data parallel threads would introduce inefficiency or even bottlenecks. This problematic approach is still adopted by existing GPU hardware and algorithm designs. The aim of this thesis is to find better ways to handle those routines. In particular, our three projects address three different manifestations of similar problems. All of our projects share the same strategy, namely the **decoupled delegate**.

In the rest of this introduction, we first discuss one of our projects in detail as an example to illustrate the common problem and our strategy. Then we extend the discussion to our other two projects.

### 1.2 Worklist-Based Algorithms—problem and strategy

**The Problem** As Figure 1.1 (b) shows, suppose a *worklist* is used for work scheduling and work distribution, where threads write vertex IDs to the worklist and read them out later in a certain order. It is evident that, unlike many vertices of the graph, only one worklist is globally accessed by all threads and threads' operations on the worklist are not independent from each other. Therefore, the worklist violates the

two requirements mentioned earlier and does not work well under massive data parallelism.

To be specific, Figure 1.1 (c) shows that the worklist consists of data storage (e.g. for vertex IDs) and metadata. To update the globally shared data storage consistently, all threads must synchronize on metadata operations to avoid race conditions. The massive number of threads in GPUs leads to massive synchronization contention. Moreover, a worklist can be a complex data structure, such as a coarse priority queue, which would mean the metadata operations are complicated. Therefore, massive synchronization on complex metadata operations turns the worklist into a bottleneck, which hinders the graph processing operations.

Figure 1.2: Our Decoupled Delegate Strategy

\_

**Our Strategy** Figure 1.2 illustrates our strategy for solving the problem. In the baseline (a), all warps must perform both graph operations and worklist metadata operations, which leads to the problem identified earlier. In our solution (b), we decouple or separate the two types of operations and execute them on two set of warps. We use most of the warps to execute graph operations because they are

suitable for massive data parallelism. To simplify discussion, assume we use only one warp to execute worklist metadata operations. The single warp would act as a *delegate* to handle metadata operations on behalf of all other warps.

he main rationale of our approach is to centralize metadata operations to fewer threads, namely the delegate warp. This approach has two benefits. First, metadata operations are centralized, which avoids synchronization across many threads. Second, in the baseline, each thread must pay metadata overheads for individual worklist reads/writes. By contrast, in our solution, the single delegate would amortize metadata overheads over many reads/writes, similar to the manner in which vector execution amortizes the instruction overheads. The reduced synchronization and overheads mean that most of the warps can focus on data parallel graph operations, without being hindered by bottlenecks.

Based on this approach, we develop a new *single source shortest path* (*SSSP*) algorithm for GPUs, implemented entirely in software. We chose the SSSP because work scheduling has a strong impact on its performance; in addition, SSSP is an extensively studied graph problem on GPUs. Without decoupling, existing algorithms adopt simple worklist designs to mitigate the problems mentioned earlier, but they suffer from poor *work scheduling quality*. This problem increases the total amount of work performed or causes hardware under-utilization (see Section 5.2). Our algorithm uses a more complex worklist design to achieve high-quality work scheduling, while making the complex design efficient for GPUs with the decoupled delegate.

We evaluated our algorithm along with seven prior GPU SSSP algorithms

(e.g. nvGRAPH [101], Gunrock [135, 138]). Our algorithm achieved an average speedup of  $2.8 \times$  on a set of 226 graphs, compared with the state-of-art (from Lonestar 4.0 [15, 105]). We discuss this project in more detail in Chapter 5.

#### 1.3 Generalization of the Problem and Strategy

We discussed our first project in the section above. To generalize, the problem is that certain operations are problematic for massive data parallelism. Our strategy is to decouple such operations, which are then centralized to a delegate so that fewer threads can be used to execute them. We now discuss how the problem and the strategy relate to our two other projects.

**Fine-Grained Synchronization** Our second project is a software solution that makes fine-grained locks more efficient on GPUs. Fine-grained locks are used to maintain mutual exclusion for updating globally shared data (items). Similar to the worklist problem, synchronization bottlenecks arise when too many threads attempt to update the same data item and thus contend on the same lock. Massive contention causes polling of lock variables in global memory and serialized critical-section execution.

Similar to our worklist delegate idea, our solution for this problem is to confine the scope of synchronization to fewer threads. In particular, we decouple the critical section and use delegates to execute it on behalf of others, where each delegate is a thread block (TB). Because synchronization is confined within each TB, we can use much faster local scratchpad memory to implement locks, which

significantly eases the lock-polling and serialization problems. Non-delegate TBs now must offload their critical- section tasks to the appropriate delegate TB for execution, which is a form of communication. We implement an efficient inter-TB communication mechanism in software, to render such communication efficient. As a result, our solution achieves an average speedup of  $3.6\times$  for five benchmarks. We discuss this project in detail in Chapter 4.

The two projects we have discussed are for highly irregular workloads with synchronization bottlenecks. Perhaps surprisingly, our decoupled delegate approach also benefits typical regular workloads.

| threads:                 | t0  | t1     | t2      | t3  |                |

|--------------------------|-----|--------|---------|-----|----------------|

| instructions:            | dst | operan | d value |     | -              |

| 0. MUL r0, 4, <i>TID</i> | 0   | 4      | 8       | 12  | addr.<br>calc. |

| 1. ADD r1, r0, base      | 100 | 104    | 108     | 112 | repetitive     |

| 2. LOAD r2, [r1]         | 389 | 153    | 207     | 60  |                |

| 3. ADD r3, r2, 1         | 390 | 154    | 208     | 61  |                |

**Figure 1.3:** Code sample: each thread increments an array element—instr0 and instr1 calculate the memory access address, and instr2 and instr3 load the data and perform the computation.

**Repetitive Computation** Figure 1.3 illustrates a common GPU computation pat-

highly repetitive in terms of operand values, where adjacent threads are simply offset by 4. In practice, regular workloads have a substantial amount of such repetitive

tern: processing consecutive elements of an array. Notice that *instr0* and *instr1* are

computation used for address calculation and control-flow condition evaluation. In

a sense, the repetitive address calculations are overheads of actual computation on array data (*instr2* and *instr3*). On SIMT GPUs, each thread must pay the overheads for computing individual data elements, similar to the worklist metadata overhead problem. In this case, the overheads translate to ALU OPs at the scalar thread level and to instruction execution at the warp level.

Also similar to the worklist problem, we use the decoupled delegate strategy to amortize the overheads. Specifically, for each TB, we use a single warp as the delegate to perform repetitive computation on behalf of other warps in the TB. For example, the delegate executes the address calculation instructions once (see Section 3.1) and then generates cache-line addresses. These are then passed to other warps to be used for memory accesses. The benefit is that non-delegate warps do not have to execute instructions or perform ALU OPs for the repetitive computation. Therefore, our strategy improves performance and energy efficiency by reducing instruction count and ALU OPs.

In addition, our decoupled approach allows non-speculative prefetch to reduce memory latency. The delegate already produces cache-line addresses and can run ahead of other warps independently. Hence, it can retrieve data early from L2 or DRAM to the L1 cache. This principle is similar to *decoupled access/execution* [126]. As a result, our solution (implemented in hardware) achieved 40.7% speedup and 20.2% energy reduction on average for 29 benchmarks.

#### 1.4 Cost of Decoupled Delegate

In general, the decoupled operations are integral parts of the original workloads, so the decoupled delegate must interact with others to work together cooperatively. This situation incurs a communication cost.

We employ two general measures to reduce the cost. First, we decouple the operations appropriately to reduce the required communication. For example, for *repetitive computation*, the delegate passes only cache-line address to other warps, instead of word addresses for individual threads, to reduce the interactions. Second, we maximize the efficiency of the communication. For *fine-grained synchronization*, we implement an optimized software solution for inter-TB communication. For *repetitive computation*, we add specialized hardware in each GPU core to facilitate passing results from the delegate to other warps.

#### 1.5 Contributions

This thesis makes the following high-level contribution:

Many GPU workloads have abundant parallelism but also contain operations

that cause bottlenecks or inefficiency under massive parallelism. We develop

a strategy to address the problem by decoupling such operations. They are

then centralized to a delegate so that fewer threads can be used to execute

them.

At the tactical level, the contributions of this thesis are three solutions that employ the decoupling strategy:

- For regular workloads, we introduce a hardware solution that decouples scalar-like computations so that they can be performed by a single warp for each TB.

This approach reduces redundancy and allows non-speculative prefetching.

Hence, our solution improves performance and energy efficiency. Specifically, our solution achieves 40.7% speedup and 20.2% energy reduction on average for 29 benchmarks.

- 2. For workloads using global memory locks, we introduce a software solution that decouples the critical section so that it can be executed by a single TB instead of all threads. By doing this, our solution can use high-bandwidth and low-latency scratchpad memory for handling lock operations, which improves performance. Specifically, our solution achieves an average speedup of 3.6× over global memory locks.

- 3. We introduce a new GPU SSSP algorithm that uses a complex worklist to achieve high-quality work scheduling. To deal with the complexity, the principle is to decouple worklist management so that it can be handled by a few warps instead of all threads. For a set of 226 graphs, our algorithm achieves an average speedup of 2.8× compared with the state-of-art.

# Chapter 2

### Related Work<sup>1</sup>

This chapter summarizes related prior solutions. Section 2.1 discusses prior solutions that reduce repetitive computations on GPUs. Alternative prior solutions have exploited the repetitive behavior for prefetching; these are discussed in Section 2.2. By contrast, our solution achieves both goals with a unified mechanism, which yields wider benefits. Section 2.3 discusses prior solutions related to fine-grained synchronization. Section 2.4 discusses prior graph algorithm designs that solve the SSSP problem. Finally, Section 2.5 discusses how our solutions relate to prior work on delegation

### 2.1 Repetitive Computation Reduction

Previous work [48, 139, 143] has proposed a dedicated data path for scalar computation to eliminate redundancy and to improve performance and energy efficiency on SIMT GPUs. Collange, et al [27] introduce the notion of affine computation as a generalization of scalar computation. Kim, et al [65] extend this idea by

Affine Computation for SIMT GPUs, ISCA 2017[134]

Fast Fine-Grained Global Synchronization on GPUs, ASPLOS 2019[133]

A Fast Work-Efficient SSSP Algorithm for GPUs, to be appear in PPOPP 2021

My contributions: I'm the first author for all three papers

<sup>&</sup>lt;sup>1</sup>Portions of this chapter are based on the following publications:

adding a functional unit that can perform affine branch and memory operations.

Our solution extends the special support for affine computation by decoupling its execution onto a separate warp. This approach (1) further reduces computational redundancy, (2) reduces the dynamic warp instruction count, and (3) hides memory latency through a form of non-speculative data prefetching.

Lee, et al [8] present a compiler-based technique to identify opportunities for scalar code to execute under divergent constraints in GPU workloads. Collange, et al [27] present a scalarizing compiler technique for mapping CUDA kernel to SIMD architectures. We build on their insights and present a compiler technique for identifying control-flow divergent conditions.

#### 2.2 Memory Latency Reduction

For scalable speculative prefetching on GPUs, previous work [72, 120, 60, 59, 144] has built on the regularity of memory accesses across different GPU threads to infer prefetches, based on the observed behavior of a few threads. However, GPU prefetchers can sometimes be vexed by useless prefetches for inactive threads. This situation can cause cache pollution and other contention [72]. By contrast, our solution issues early memory requests non-speculatively as a part of the program execution. It does not suffer from mispredictions or early evictions.

Decoupled Access Execution (DAE) [126, 74, 41, 28] is a lightweight memory latency hiding mechanism for in-order processors. The main idea is to decouple memory instructions (the access stream) from other instructions (the execute

stream), so that the access stream can bypass memory stalls and issue memory requests early. Arnau, et al. [7] decouple memory accesses from a fragment processor's tile queue, allowing a tile's memory requests to be issued before dispatch. Our solution employs decoupling to affine computations, both to reduce memory latency and to improve computational efficiency.

#### 2.3 Fine-Grained Synchronization

Previous work propose designating one or more threads as servers (or delegates) to handle critical sections for multi-core CPUs with a cache-coherent shared memory interface [20, 83, 111, 129, 54, 104, 43] and for many-core CPUs with both cache coherence and hardware message-passing capability [109] (e.g. Tilera TILE serie [136]). While their designs differ, the principle of transforming synchronization into communication remains the same. The aim is to let clients offload the updates for the same data to the same server so that critical-section updates can be serialized at the servers.

Our work is the first to apply similar principles for GPUs. Since GPU architecture differs significantly from that of CPUs, our solution differs from previous work in several ways.

First, CPUs have fewer hardware threads than do GPUs. Hence, previous work has used individual threads as servers. Since conflicts are serialized to a single thread, no further synchronization is needed for processing requests. Because of the large thread/warp count of GPUs, our solution uses TBs as servers. Hence, when requests are processed, threads in the TB synchronize via their fast local scratchpad.

Second, CPUs have cache coherence and often also sophisticated on-chip interconnect as implicit hardware inter-core communication mechanisms. Previous work has employed software message-passing systems on top of these mechanisms for a relatively small number of threads. By contrast, our solution must be scalable for the much larger number of threads on GPUs, which lack such hardware support for inter-SM (inter-TB) communication.

On the other hand, several issues such as a large number of threads, no coherent L1 cache, and lower memory bandwidth per thread, render fine-grain locks a more severe problem on GPUs than CPUs [146, 40]. Therefore, our solution has greater performance improvement potential.

Yilmazer, et al. [146] propose a hardware-accelerated fine-grained lock scheme for GPUs, which adds support for queuing locks in L1 and L2 caches and uses a customized communication protocol to enable faster lock transfer and to reduce lock retries for non-coherent caches. ElTantawy et al. [40] propose a hardware warp scheduling policy that reduces lock retries by de-prioritizing warps whose threads are spin waiting. Hardware-accelerated locks have also been proposed for CPUs [131, 79, 147, 4].

By contrast, our solution does not require hardware modification. Moreover, a rough comparison with published results (see Section 4.6.4) suggests that our solution performs as well as, if not better than, previous hardware solutions. This is likely the result of our solution addressing the problem at higher level by using scratchpad memories for global synchronization.

#### 2.4 Sinlge Source Shortest Path

Dijkstra's algorithm[38] uses a priority queue to process (i.e. relax) vertices according their tentative distance. This feature makes it the most work-efficient algorithm. By contrast, Bellman-Ford's algorithm [11] processes vertices without order. Originally, the advantage of Bellman-Ford is to allow negative edge weights.

There are parallel versions of both algorithms. Dijkstra's algorithm can be parallelized while persevering the exact ordering semantic. Crauser, et al. [29] propose an algorithm that discovers suitable vertices in the priority queue that can be processed in parallel; for example, if the first N vertices in the priority queue have the same distance, they can be removed in parallel. GPU-based parallel algorithms [84, 103] have also been proposed. Generally, these parallel algorithms are practical only for graphs with highly structured edge weights and connectivity.

Bellman-Ford's algorithm is much more straight-forward to parallelize, since it does not require a priority queue. Many GPU implementations have been proposed [51, 16, 130, 18, 117, 19, 124, 71, 101]. However, the disadvantage of Bellman-Ford is redundant work caused by processing vertices in an arbitrary order. Meyer, et al. [88] propose  $\Delta$  -Stepping as a midway between Bellman-Ford and Dijkstra'. The algorithm processes vertices in approximate order, so it improves work efficiency when compared to Bellman-Ford; however, it does not use a priority queue, which makes parallelism possible.

Many GPU adoptions of  $\Delta$  -Stepping have been proposed [135, 132, 12, 31, 9]. Ingeneral, these previous solutions render the work-scheduling data structure

scalable for GPUs by simplifying the design. However, by doing so, they sacrifice the quality of work scheduling; in particular, they achieve sub-optimal work efficiency and concurrency, which limits their performance.

Our algorithm is a GPU adoption of  $\Delta$ -Stepping. Compared with previous solutions, ours uses a more sophisticated work-scheduling mechanism that achieves better work efficiency and concurrency. At the same time, we implement a sophisticated mechanism to be efficient for GPUs. As a result, our solution performs far better than previous ones.

#### 2.5 Delegation

Delegation is proposed by previous work [37, 42, 107, 121, 145, 54, 104, 109, 43, 108, 20, 83, 111, 116] as a way to avoid the inefficiency caused by locking for multi-core or multi-socket CPU systems. In this regard, our fine-grain lock project is closely related to prior work, and we have demonstrated that the notion of delegates can be adapted so that they work on GPUs. Our other two project uses delegation in a broader sense, and we have demonstrate that the idea can used beyond locking problems.

The main idea of delegation is that one or several threads act as servers that execute the critical section on behalf of other threads. Prior delegation proposals can be categorized into two main approaches—combiner and dedicated delegate.

As to the combiner approach [37, 42, 107, 121, 145, 54, 104, 109, 43], one thread is dynamically selected to act as the temporary delegate, i.e. combining;

the rationale is to avoid wasting a thread for handling critical section execution exclusively, especially for multi-core CPUs with a small hardware thread count.

As to the dedicated delegate approach [108, 20, 83, 111, 116], as the name suggests, delegates are dedicated server threads, which avoids the overhead of dynamical combining; this approach achieves better performance for systems with a moderate thread count. Lozi, et al. propose RCL [83, 108] with a drop-in replacement for locks but has additional complexities and overheads due to the need for supporting legacy programs. Roghanchi, et al. propose ffwd [116], which offers somewhat restricted functionalities, i.e. no support for certain legacy programming patterns, but achieves better performance when compared to RCL.

We now discuss how our projects are related to prior work.

Our fine-grain lock project is the first to adopt a dedicated delegate approach on GPUs. Due to the significant difference between GPU and CPU architectures, our solution differs from prior solution in two ways. First, each delegate is a thread block instead of a thread in our solution, and we take advantage of GPUs' fast local scratch-pad memories for locking within each delegate thread block. Second, most of the complexities of a delegate design lies in handling the interaction between the client and the delegate threads, where our solution uses an entirely different approach for GPU architecture.

To be specific, in both RCL [83, 108] and ffwd [116], each client CPU core owns a cache line for writing its request to the delegate (i.e. request buffer), and delegate polls those cache lines in round-robin to find and to retrieve clients' re-

quests. Clearly, we could modify this approach for GPUs, e.g. each warp instead of a thread owns a request buffer (layout in memory as multiple cache lines), etc. but fundamentally, the idea of letting a client write a fixed location is not suitable for GPUs. First, GPUs have a large number of concurrent threads with sparsity in terms of requests to the delegate; therefore, polling through the request fields of threads/warps one by one is not efficient. Second, also due to sparisty, those requests would not be in consecutive memory locations, which is detrimental to coalesced memory accesses and L2 cache footprint. Therefore, in our solution, each delegate owns a concurrent read-write-able FIFO queue so that clients only write valid requests in consecutive locations. Furthermore, we apply various optimizations to promote coalesced memory accesses and to amortize overheads when writing and reading the FIFO queue. Therefore, our approach is more suitable for the highly parallel nature of GPU-like architecture.

As to the worklist manager in our SSSP project, although the manager can be considered as a delegate in a broader sense, the key difference is that the manager interacts with the clients at a much coarser granularity. To be specific, in both CPU and our own GPU lock-replacement delegate designs, the delegate handles individual threads' requests; clearly, this is unnecessary for the purpose of maintaining a coarse-grain priority queue (i.e. the buckets), since the manager does not care about the individual work items written by client threads. Instead, the manager only needs to determine when and which work-items (in a range) can be read out for maintaining consistency and ordering and to determine which client thread blocks are available for accepting work; in addition, features, such as dynamic delta

adjustment, also only require coarse-grain information. Therefore, for our worklist solution, the manager acts as a controller for the clients that accesses various metadata only instead of a true delegate in the traditional sense.

# **Chapter 3**

# **Decoupled Affine Computation**<sup>1</sup>

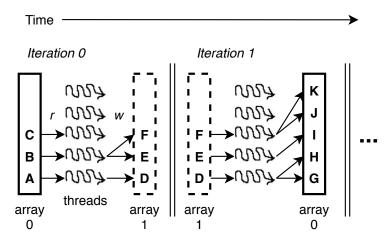

GPUs are optimized for regular data parallel workloads. Data parallelism is commonly expressed with single instruction multiple threads (SIMT), where data elements are parallelized to lightweight scalar threads, which are then grouped into vector warps at the hardware level (e.g. Nvidia GPUs) or at the assembly or compiler level (e.g. AMD GPUs). However, regular workloads often exhibit a high degree of repetitiveness in terms of address calculation and control flow. The repetitive computations must be duplicated to all threads or warps; in particular, it causes unnecessary instruction executions and ALU OPs.

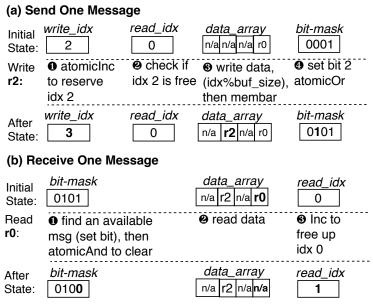

Our main idea is simply to **de-duplicate** such computations. This is done by decoupling the original kernel into the *affine kernel* containing the repetitive portion (e.g. instr0, instr1 in Figure 1.3) and the *data parallel* (DP) kernel containing the true data parallel portion (e.g. instr2, instr3). As Figure 3.1 ① shows, for each thread block (TB), we launch N warps for the DP kernel, which is the same as for the original kernel, but only one warp for the affine kernel. The repetitive instructions are thus executed by a single warp instead of decoupling to N warps. Therefore,

<sup>&</sup>lt;sup>1</sup>Portions of this chapter are based on the following publication: Affine Computation for SIMT GPUs, ISCA 2017[134] My contributions: I'm the first author for the paper

#### **Stream Multiple Processor (SM)**

**Figure 3.1: Decoupling Repetitive Computations**: the figure illustrates our solution

our solution reduces the instruction execution count by a factor of N.

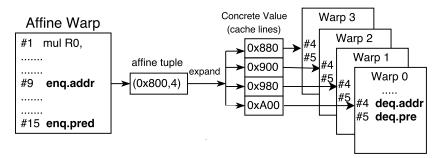

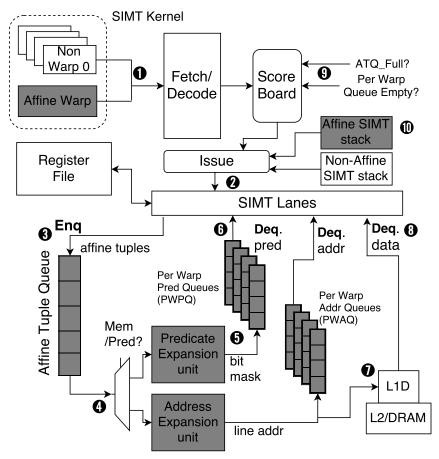

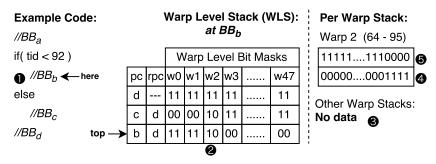

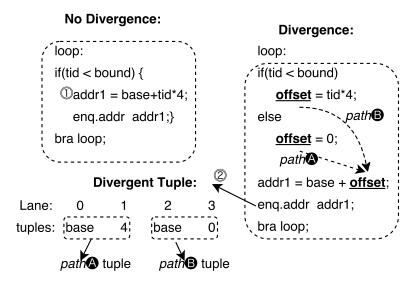

The two decoupled kernels work cooperatively as a single kernel, so the results produced by the affine warp must be passed efficiently to the DP warps. To facilitate such communication, we use a compact encoding format and add specialized hardware to each GPU core (SM), as shown in Figure 1.3 ②. For example, instr0 and instr1 calculate the memory addresses for array access. Because of the repetitiveness, the addresses can be encoded as a base-offset pair, such as (100, 4), known as the *affine tuple*. The affine warp produces the affine tuple and pass it to the *address generator*, which generates cache-line addresses and then buffers them in a set of *hardware queues*, one for each DP warp. In contrast to a baseline SIMT GPU, which calculates addresses thread-by-thread and then coalesces them into cache-line addresses, our solution generates cache-line addresses directly from the affine tuple. This approach improves the efficiency. In addition to address calculation, a similar mechanism is used for repetitive control flow condition evaluations (not shown). In this case, our solution generates predicate bit-masks directly.

In addition to de-duplication, our solution allows non-speculative prefetch of memory data. As Figure 3.1 ③ shows, the affine warp already produces cacheline addresses and it can be run ahead of DP warps due to decoupling. Therefore, we add a *DMA engine* that retrieves data early from L2 or DRAM to the L1 cache, which be accessed by DP warps later. The principle is similar to *decoupled access/execution* [126].

Some previous solutions have reduced repetition without decoupling. For example, AMD GPUs [6] use explicit scalar and vector instructions and a dedicated

scalar data path so that repetitive instructions are handled with scalar ALU OPs instead of vector OPs. Kim, et al[65] propose a solution that achieves a similar effect for Nvida-like SIMT GPUs by detecting scalar executable instructions in run-time. The main drawback of previous solutions is that they de-duplicate only repetitive computation within each warp by transforming vector ALU OPs into scalar ones; repetitive instructions are still duplicated to all warps because they are not decoupled, and are executed redundantly. By contrast, our solution de-duplicates them at TB scope and thus reduces instruction executions.

In summary, our solution improves performance and energy efficiency by reducing dynamic instruction count, ALU OPs, and memory latency. For evaluation, we implement our solution on GPGPU-Sim simulating a GTX 480 GPU. For comparison, we also implement *CAE* [65], a previous repetition-reduction solution, and *MTA* [72], a previous speculative prefetching solution. We use a set of 29 GPGPU benchmarks, of which 18 are memory-bound and 11 are compute-bound. For all 29 benchmarks, our solution achieves 40.7% speedup and 20.2% energy reduction on average. For the 18 memory-bound benchmarks, our solution achieves a 44.7% mean speedup compared to the 16.7% achieved by MTA. For the 11 compute-bound benchmarks, our solution achieves a 34.0% mean speedup, compared to CAE's 11.0%.

The rest of this chapter is organized as follows. Section 3.1 formalizes the notion of repetitive computations with a previously proposed concept known as *affine computation*. Section 3.2 discusses our idea of decoupling affine computation. Section 3.3 shows how our solution can be implemented at the hardware and

compiler levels. In Sections 3.4 and 3.5, we present the experimental evaluation of our solution.

# 3.1 Background and Motivation

Collange, et al [27] introduces *affine computation* to represent repetitive computations. The idea is based on the observation that GPU workloads often use scalar data, such as kernel parameters, and the thread ID to map memory accesses and control flow to threads. Therefore, the operand values of many ALU instructions often exhibit a high degree of regularity across threads. This characteristic can be exploited to reduce ALU operation.

|          | Baseline GPU |     |              |  |     | Affine<br>Computation |  |

|----------|--------------|-----|--------------|--|-----|-----------------------|--|

| Operands |              | SI  | Affine Tuple |  |     |                       |  |

|          | О            | 1   | 2            |  | 31  | (base, offset)        |  |

| Α        | 100          | 101 | 102          |  | 131 | (100, 1)              |  |

| В        | 200          | 201 | 202          |  | 231 | (200, 1)              |  |

| C=A+B    | 300          | 302 | 304          |  | 362 | (300, 2)              |  |

| D        | 2            | 2   | 2            |  | 2   | (2 , 0)               |  |

| E=CxD    | 600          | 604 | 608          |  | 724 | (600, 4)              |  |

Figure 3.2: Operand Values–Baseline GPU and Affine Computation

Figure 3.2 shows the per-thread operand values of an ADD OP and an MUL OP as examples of the regularity. First, it is evident that the value of A starts at 100 in lane 0 and then increases by 1 with each successive thread. Hence, the entire vector value of A can be represented as an affine tuple (100, 1), where 100 is a base and 1 is the offset. Algebraically, an affine tuple represents values as a function of

thread ID:

$$operand\_value = base + thread\_ID \times offset$$

(3.1)

Similarly, the scalar B can be represented as the tuple (200, 1). Next, the value of C (as the result of ADD OP) can be represented as the tuple (300, 2). Instead of performing one ALU per lane in vector computation, the C tuple can be derived with A and B affine tuples using just two additions. The first adds A's base to B's base; the second adds A's offset to B's offset, producing (300, 2). The C affine tuple can then be used as a source operand for subsequent affine computations.

The value of D can be represented as (2, 0), where the offset is 0. Such an operand is called a scalar operand. The MUL OP between C and D can also be calculated using affine arithmetic with two multiplications, one to multiply C's base with D's base and the other to multiply C's offset with D's base; the result is (600, 4). However, for affine MUL OP, one of the operands must be scalar; alternatively, vector computations must be used, because the result cannot be represented as an affine tuple.

Figure 3.3 shows a sample CUDA kernel in a relatively concrete example. Figure 3.4 shows how address addrA is derived entirely from affine arithmetic. The same applies to address addrB and predicate p0 (not shown).

A sequence of affine computations can continue as long as both source and destination operands can be represented as affine tuples. Otherwise, affine tuples must be expanded into concrete values. For memory instructions with affine addresses (e.g. *addrA*) and for predicate computation instructions with affine operands

```

mul r0, blockIdx.x, blockDim.x;

2

add tid, threadIdx.x, r0;

mul r1, tid, 4;

void example_kernel(int A[],int B[],5

add addrA, A[], r1;

add addrB, B[], r1;

int dim, int num)

mov i, 0;

int tid=blockIdx.x*blockDim.x+

LOOP:

threadIdx.x;

for(int i=0;i<dim;i++)

ld.global tmp, [addrA];

add r2, tmp, 1;

10

st.global [addrB], r2;

int tmp=A[i*num+tid];

B[i*num+tid]=tmp+1;

add i, i, 1;

12

mul r3, num, 4;

13

add addrA, r3, addrA;

add addrB, r3, addrB;

15

setp.ne p0, dim, i;

(a) CUDA Code

@p0 bra L00P;

```

(b) Pseudo Assembly Code

Figure 3.3: Example Kernel

|              | O        | Affine Tuple |          |                |

|--------------|----------|--------------|----------|----------------|

| operand name | Thread 0 | Thread 1     | Thread 2 | (Base, Offset) |