Copyright by Wei Shi 2022 The Dissertation Committee for Wei Shi certifies that this is the approved version of the following dissertation:

## Design and Automation Techniques for High-Performance Mixed-Signal Circuits

Committee:

David Z. Pan, Supervisor

Nan Sun, Supervisor

Michael Orshansky

Jaydeep Kulkarni

Song Han

## Design and Automation Techniques for High-Performance Mixed-Signal Circuits

by

Wei Shi

#### DISSERTATION

Presented to the Faculty of the Graduate School of The University of Texas at Austin in Partial Fulfillment of the Requirements for the Degree of

#### DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN May 2022 Dedicated to my parents.

## Acknowledgments

I want to express my sincerest gratitude to my advisor, Dr. Nan Sun, who I met at the start of my academic journey. He has been an academic role model and a supportive mentor. His persistence, concentration, and confidence in tackling technical problems guide me to encounter research challenges. He bestowed me all the presentation and writing skills, and the passion to contribute to frontier research. I hope to follow in his footsteps to be the kind of person he is.

I want to say my deepest appreciation to my advisor, Dr. David Z. Pan. As I stepped into the area of machine learning for circuit optimization, I received tremendous help from Dr. Pan and UTDA group members. I also appreciate his leadership, involving me in multi-disciplinary projects. Visions of people from different domains including optimization, machine learning, and science are eye-opening and inspiring, setting the future course I want to pursue.

I would also like to thank my committee members, Prof. Song Han, Prof. Michael Orchansky, and Prof. Jaydeep Kulkarni, for their valuable advice and discussions.

It has been a great honor to meet and work with all the Sun-lab members: Miguel Gandara, Shaolan Li, Abhishek Mukherjee, Jiaxin Liu, Linxiao Shen, Xiyuan Tang, Sungjin Hong, Chen-Kai Hsu, Wenda Zhao, Xiangxing Yang, Xing Wang, Zijie Gao, and Yi Shen. Working with them is truly inspiring and fun. Also, I would like to thank UTDA members: Keren Zhu, Jiaqi Gu, Zixuan Jiang, Hao Chen, Hanqing Zhu, etc. I would like to thank Dr. Linxiao Shen and Dr. Xiyuan Tang for numerous technical discussions and suggestions about my research. I would like to thank Dr. Ahbishek Mukherjee for sharing his expertise in CTDSM with me. Also, I would like to thank Dr. Yi Shen and Dr. Jiaxin Liu for teaching me simulation and measurement skills in my early years of data converter research. I would like to thank Keren Zhu for his help in my CAD research. I would like to thank Jiaqi Gu for his generous help in writing ML papers. I would also thank Andrew Kieschnick for the technical supports on server environments.

Besides, I would like to thank my good friend, Dr. Zhaowen Wang from Columbia University. His encouragements and help are precious.

I would like to thank my beautiful girlfriend, Xuejun. She has been with me through lots of critical moments in my Ph.D life. During the years, my life and career has been through three huge changes. She has witnessed my emotional and physical up and downs and always stood by my side.

My beloved family is the one I am truly indebted to. While I am on the other end of the Earth, my parents continuously support me unconditionally. Without their support and love, I never could have reached where I am today. This dissertation is dedicated to them.

## Design and Automation Techniques for High-Performance Mixed-Signal Circuits

Wei Shi, Ph.D. The University of Texas at Austin, 2022

> Supervisors: David Z. Pan Nan Sun

In the era of ubiquitous sensing environment, the modern electronic system expands our perception of the outside world. Analog/mixed-signal circuit has played a critical role to bridge the physical and digital worlds. The boom of Internet-of-Things (IoT), bio-sensing, and digital camera calls for versatile high-performance mixed-signal circuits and the corresponding automated design methodology. However, high-performance analog circuits are area or power hungry. Moreover, the design cost is prohibitively expensive. To address these challenges, this dissertation explores solutions from both the design and automation techniques.

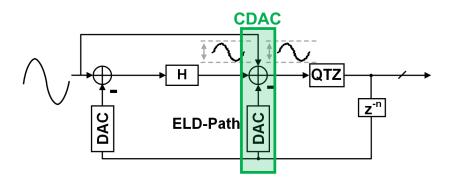

Analog-to-digital converter (ADC) is an important subset of analog/mixedsignal circuits. Continuous time Delta-Sigma modulator (CTDSM) is a popular design choice for high-speed and high-resolution designs. CTDSMs feature a higher power efficiency than their discrete-time (DT) counterpart. The first work presents a high-speed  $4^{th}$ -order DSM featuring the CT-DT hybridization and an efficient excess-loop-delay (ELD) compensation technique in the charge domain. Compared to prior high-order CTDSMs, the proposed hybrid DSM achieves 4<sup>th</sup>-order noise shaping with single operational trans-conductance amplifier (OTA). Minimized number of OTAs reduces power and enhances stability. On top of that, an efficient ELD compensation technique is implemented by utilizing the inherent capacitor digital-to-analog converter (CDAC) of SAR. Fabricated in 40 nm CMOS, the prototype ADC achieved a peak Schreier Figure-of-Merits (FoM) of 176.1 dB, marking 4 dB improvement over prior arts.

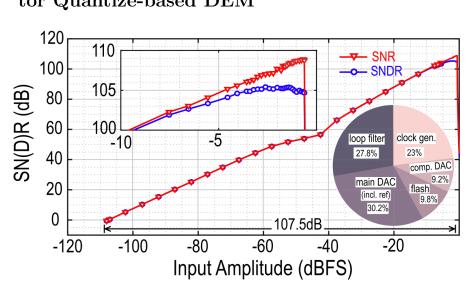

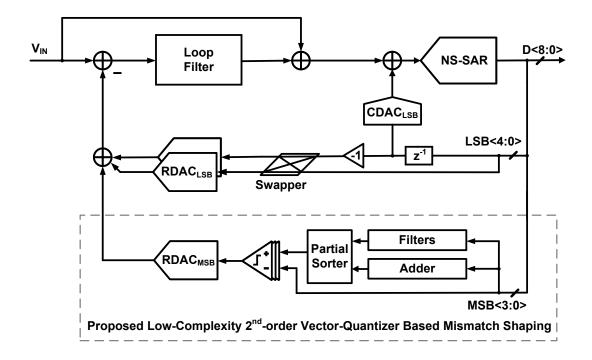

The second project explores the techniques to reduce the area consumption of high-resolution CTDSMs. The performance of existing high-resolution CTDSMs is limited by the feedback DAC. The stringent non-linearity requirement leads to the large area of DAC. To address this limitation, a lowcomplexity hardware-based  $2^{nd}$ -order dynamic-element-matching (DEM) is proposed. The partial sorter applied to the DEM minimizes the hardware cost. Moreover, feedforward path assisted loop filter adapts the highly-linear integrator design to the low power supply voltage. With these techniques combined, the prototype shows a feasible design pattern to achieve compact-area, high-resolution design at advanced technology nodes. A prototype fabricated in 40 nm CMOS measured 95dB SNDR, occupying only 0.37 mm<sup>2</sup> area.

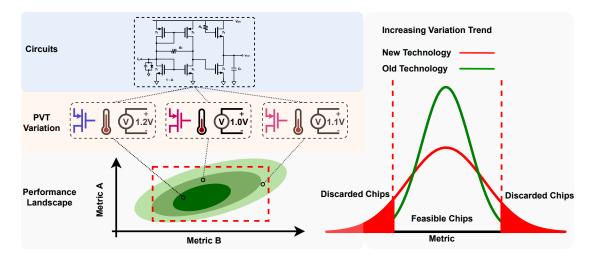

After the exploration of pushing the ADC performance boundary, this dissertation also demonstrates the automated design methodology. The design cost of high-performance mixed-signal circuit grows exponentially with the technology scaling. Existing analog automation techniques cannot handle practical circuit design constraints (e.g. robustness against variations). The third work presents RobustAnalog, a variation-aware analog circuit optimization via multi-task reinforcement learning (RL) and task-space pruning. RobustAnalog is mainly designed to tackle the process-voltage-temperature (PVT) robustness in the analog design. Correlations between similar variations are modeled and conflicts between distinct variations are mitigated. With task pruning, a small-sized proxy training task set is formed. The pruning reduces the queries to the full task set. Compared with the popular blackbox optimization methods, RobustAnalog significantly reduces the simulation cost. Therefore, RobustAnalog shows the staggering progress towards analog automation techniques that can be applied to real silicon conditions.

# Table of Contents

| Acknowledgments                                                |       |                                                     | $\mathbf{v}$ |

|----------------------------------------------------------------|-------|-----------------------------------------------------|--------------|

| Abstra                                                         | ict   |                                                     | vii          |

| List of                                                        | Table | 25                                                  | xiii         |

| List of                                                        | Figur | es                                                  | xiv          |

| Chapter 1.                                                     |       | Introduction                                        | 1            |

| 1.1                                                            | High- | Performance Mixed-Signal Circuit                    | 1            |

|                                                                | 1.1.1 | ADC Background and Applications                     | 1            |

|                                                                | 1.1.2 | High-Speed and High-Resolution CTDSMs               | 2            |

| 1.2                                                            | Analo | g Design Automation                                 | 6            |

|                                                                | 1.2.1 | Automation Problem Formulation                      | 10           |

|                                                                | 1.2.2 | Optimization Methods                                | 11           |

|                                                                |       | 1.2.2.1 Evolutionary Strategy                       | 12           |

|                                                                |       | 1.2.2.2 Bayesian Optimization                       | 14           |

|                                                                |       | 1.2.2.3 RL-Guided Optimization                      | 16           |

|                                                                |       | 1.2.2.4 Challenges in Practical Analog Optimization | 18           |

| Chapter 2. High Speed Hybrid CT-DT DSM with Charge-don<br>ELDC |       | ain<br>20                                           |              |

| 2.1                                                            | Intro | luction                                             | 21           |

| 2.2                                                            | Prope | osed $4^{th}$ -Order Hybrid CT-DT DSM               | 23           |

|                                                                | 2.2.1 | Prior High-Order CT DSMs                            | 23           |

|                                                                | 2.2.2 | Hybrid DSM Architecture                             | 25           |

|                                                                | 2.2.3 | Coefficient Sensitivity                             | 26           |

|                                                                | 2.2.4 | Finite UGB Effects                                  | 27           |

| 2.3                                                            | Prope | sed ELD Compensation Scheme                         | 30           |

|        | 2.3.1          | Brief Review of ELD Compensation                                | 30 |

|--------|----------------|-----------------------------------------------------------------|----|

|        | 2.3.2          | Proposed Charge-domain ELD Compensation                         | 32 |

|        | 2.3.3          | Feedforward Path and STF                                        | 36 |

| 2.4    | Circu          | it Implementations                                              | 38 |

|        | 2.4.1          | System Architecture                                             | 38 |

|        | 2.4.2          | SAB Design                                                      | 40 |

|        | 2.4.3          | $2^{nd}$ -order NS-SAR Design                                   | 43 |

| 2.5    | Measu          | urement Results                                                 | 46 |

| 2.6    | Concl          | lusion                                                          | 49 |

| Chapte | er 3.          | High Resolution CTDSM with 2 <sup>nd</sup> -order MES           | 50 |

| 3.1    | Intro          | duction $\ldots$                                                | 51 |

| 3.2    |                | osed CTDSM with Low-Cost 2nd-Order Vector Quantize-             |    |

|        | 10 010 0 0 0   | DEM                                                             | 54 |

|        |                | Prior Mismatch Error Shaping Techniques                         | 54 |

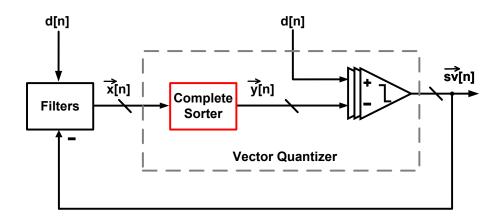

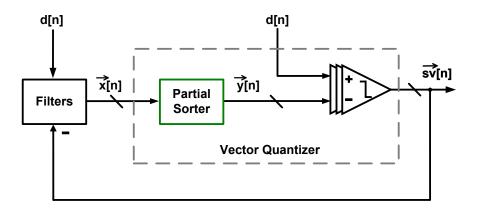

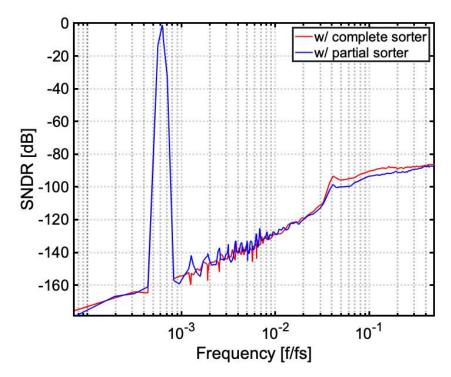

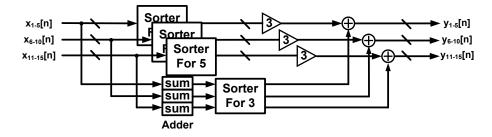

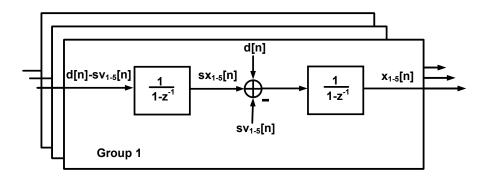

|        | 3.2.2          | $2^{nd}$ -Order DEM with Partial Sorter                         | 56 |

| 3.3    | Loop           | Filter Design                                                   | 62 |

| 3.4    | CTDS           | SM Architecture                                                 | 65 |

|        | 3.4.1          | OTA Schematic                                                   | 66 |

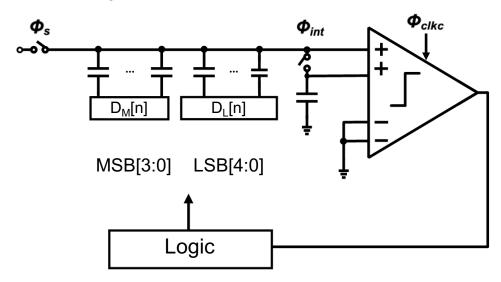

|        | 3.4.2          | NS-SAR Schematic                                                | 67 |

| 3.5    | Measu          | urement Results                                                 | 68 |

| 3.6    | Concl          | lusion                                                          | 73 |

| Chapte | er 4.          | Robust Analog Design Automation Via Reinforce-<br>ment Learning | 77 |

| 4.1    | Intro          | duction                                                         | 78 |

| 4.2    | 2 Related Work |                                                                 | 81 |

| 4.3    | Propo          | osed PVT Variation-Aware Circuit Sizing                         | 84 |

|        | 4.3.1          | Problem Definition                                              | 84 |

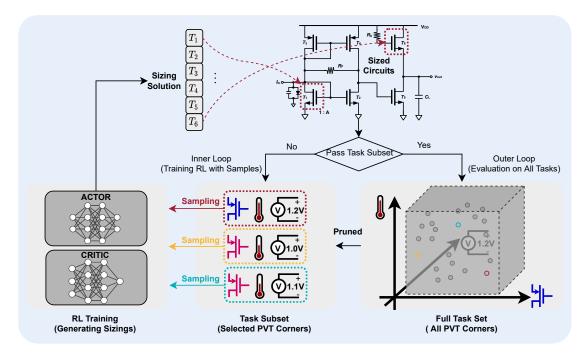

|        | 4.3.2          | Framework Overview                                              | 85 |

|        | 4.3.3          | Multi-Task RL training                                          | 86 |

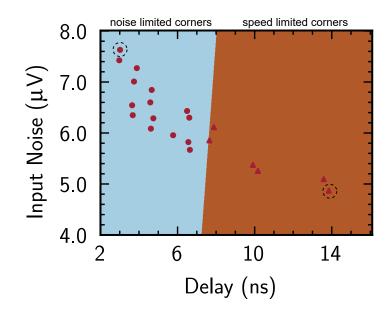

|        | 4.3.4          | Task Space Pruning                                              | 89 |

| 4.4    | Expe           | riments                                                         | 92 |

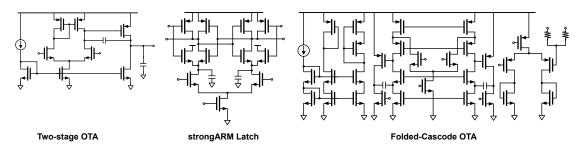

|                       | 4.4.1 | Analog/Mixed-Signal Circuits           | 92  |

|-----------------------|-------|----------------------------------------|-----|

|                       | 4.4.2 | Training Settings                      | 95  |

|                       | 4.4.3 | Evaluation of the Circuit Optimization | 96  |

|                       | 4.4.4 | Analysis                               | 97  |

| 4.5                   | Concl | usion                                  | 100 |

| Chapter 5. Conclusion |       |                                        | 102 |

| Bibliography          |       |                                        | 104 |

| Vita                  |       |                                        | 121 |

# List of Tables

| 2.1 | Comparison with the state-of-the-art single-loop CT DSMs                            | 44 |

|-----|-------------------------------------------------------------------------------------|----|

| 3.1 | Pros and cons of different $2^{nd}$ -order DEMs                                     | 61 |

| 3.2 | Performance summary and comparison with state-of-<br>the-art high-resolution CTDSMs | 75 |

| 4.1 | Comparison between RobustAnalog's solution and expert's so-<br>lution               | 99 |

# List of Figures

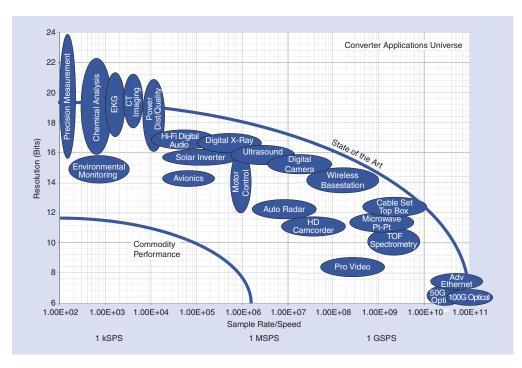

| 1.1  | ADC application universe [Robertson [2015]]                                                                                                            | 2  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

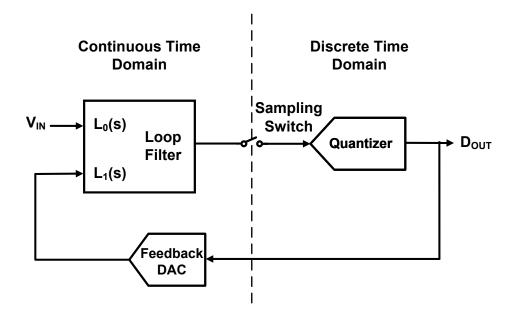

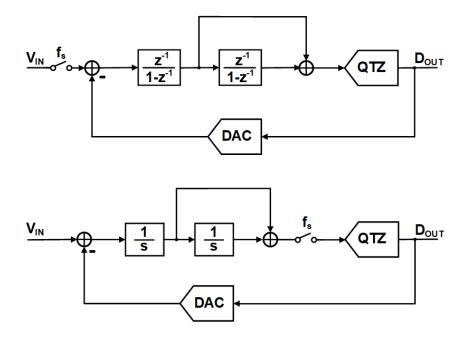

| 1.2  | Generic model of CTDSM                                                                                                                                 | 3  |

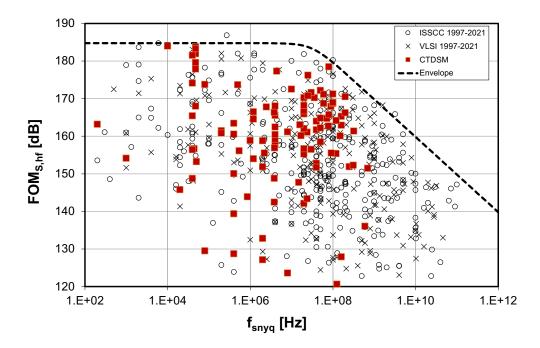

| 1.3  | CTDSM in ADC FoM surveys                                                                                                                               | 4  |

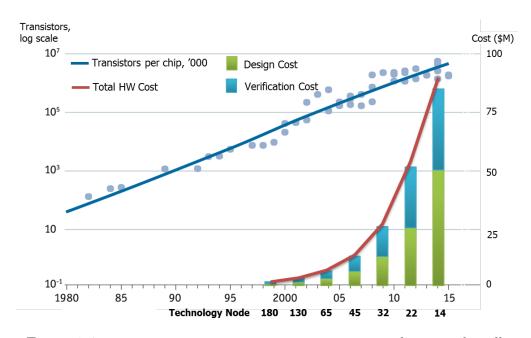

| 1.4  | Increasing design cost in today's technologies [Olofsson [2018]]                                                                                       | 7  |

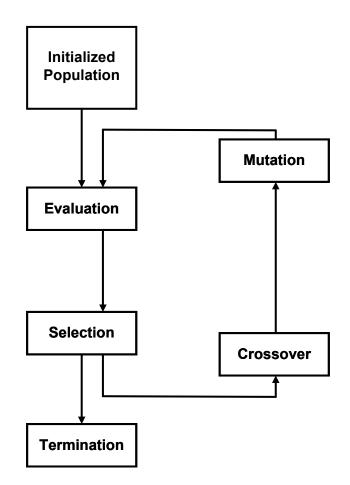

| 1.5  | Evolutionary Computation Flow                                                                                                                          | 13 |

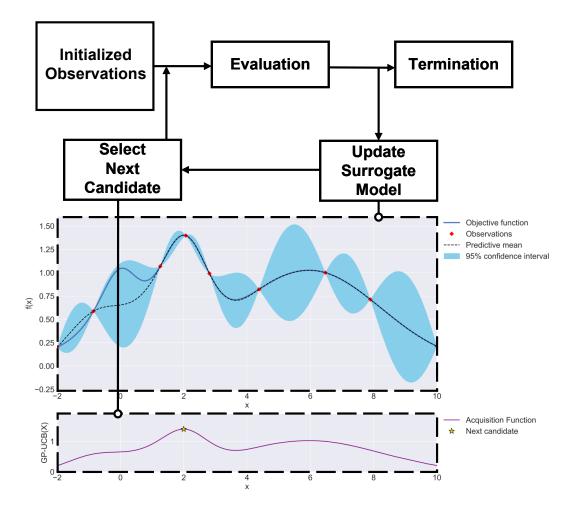

| 1.6  | Bayesian Optimization Flow                                                                                                                             | 15 |

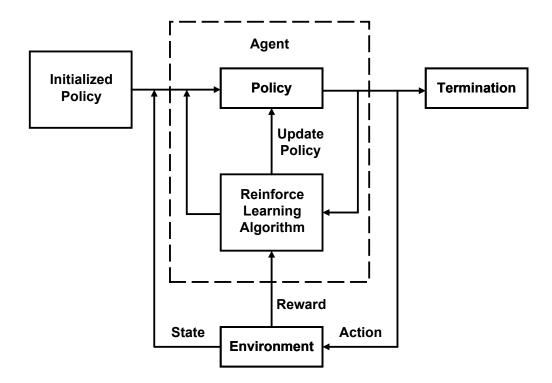

| 1.7  | Reinforcement Learning Flow.                                                                                                                           | 17 |

| 2.1  | Typical discrete-time and continuous-time structures                                                                                                   | 22 |

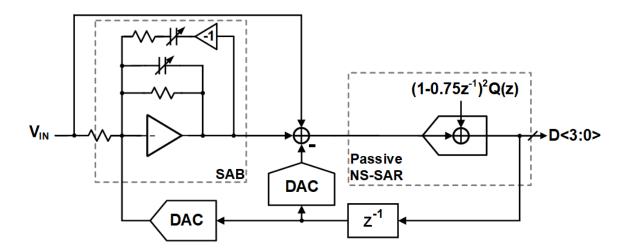

| 2.2  | Proposed hybrid DSM with SAB filter and passive NS-SAR quantizer                                                                                       | 26 |

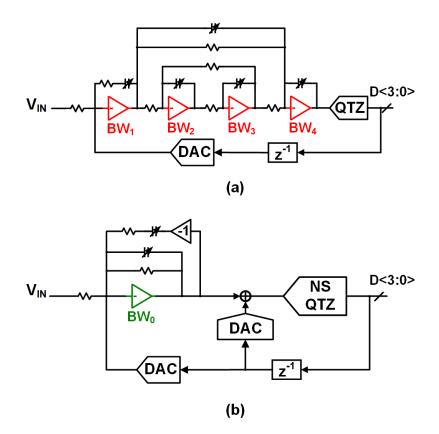

| 2.3  | (a) Conventional $4^{th}$ -order CT DSM, (b) Proposed $4^{th}$ -order hybrid CT-DT DSM                                                                 | 27 |

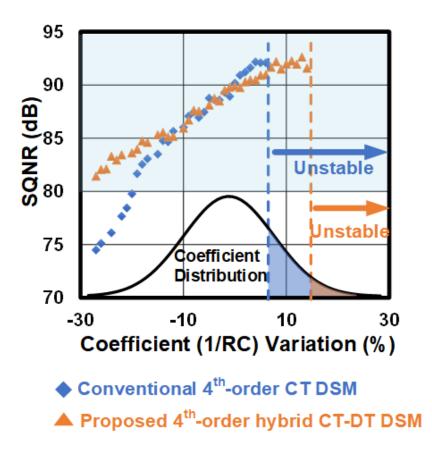

| 2.4  | Coefficient sensitivity comparison between a conventional and the proposed $4^{th}$ -order hybrid CT-DT DSM                                            | 28 |

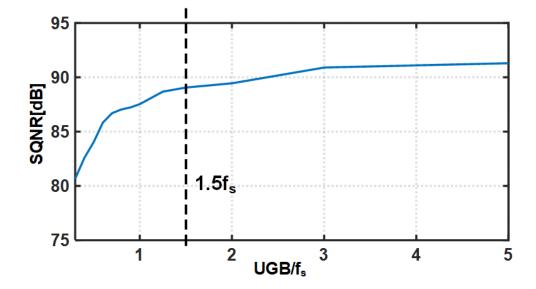

| 2.5  | Proposed hybrid CT-DT DSM SQNR with different OTA UGBs                                                                                                 | 29 |

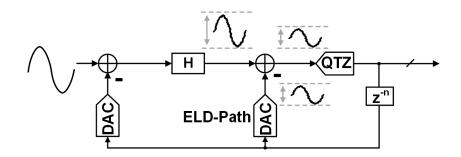

| 2.6  | ELDC implemented by the direct feedback path                                                                                                           | 30 |

| 2.7  | ELDC implemented by the residual feedforward path                                                                                                      | 30 |

| 2.8  | (a) Residual ELDC signal flow (b) ELDC path implementation<br>in the current domain                                                                    | 32 |

| 2.9  | Residual ELDC implementation in the charge domain                                                                                                      | 33 |

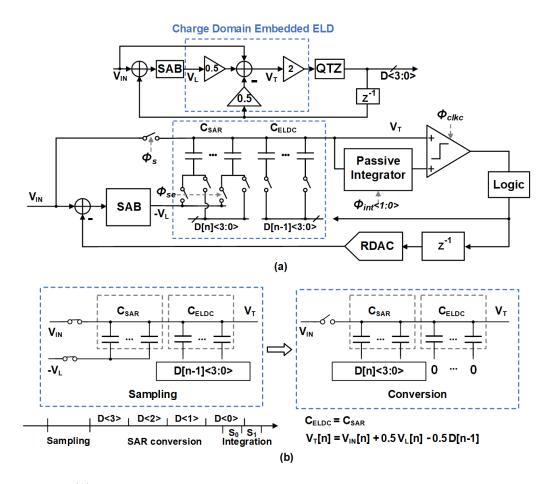

| 2.10 | (a) Signal flow and schematic of proposed charge domain em-<br>bedded ELD compensation, (b) Timing diagram of ELD com-<br>pensation operations on CDAC | 34 |

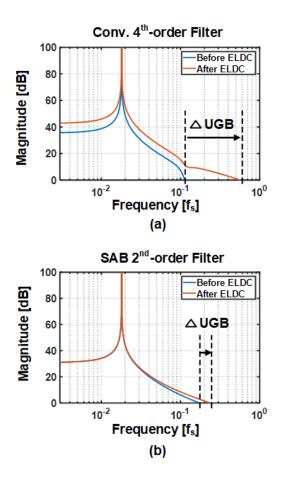

| 2.11 | (a) The UGB increase of the conventional $4^{th}$ -order filter after ELDC, (b) The UGB increase of the SAB $2^{nd}$ -order filter after ELDC.         | 35 |

| 2.12 | (a) Original CT DSM model, (b) Equivalent residual ELD compensation model.                                                                             | 37 |

| 2.13 | (a) Rearranged model to separate CT and DT domain, (b) STF<br>Bode plot                                  |

|------|----------------------------------------------------------------------------------------------------------|

| 2.14 | Schematic and timing diagram of proposed hybrid DSM                                                      |

| 2.15 | The two-stage feedforward-compensated OTA design                                                         |

| 2.16 | Comparator design                                                                                        |

|      | Die micrograph                                                                                           |

| 2.18 | Measured single-tone spectrum                                                                            |

|      | Measured two-tone spectrum                                                                               |

| 2.20 | Measured SNDR/DNR vs. different input amplitudes                                                         |

| 3.1  | Selection pattern of DWA                                                                                 |

| 3.2  | SNDR measurements at different input amplitudes in [Theertham et al. [2020]]                             |

| 3.3  | Conventional VQ-based DEM structure                                                                      |

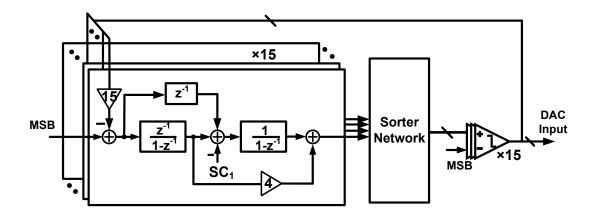

| 3.4  | VQ-based DEM structure with partial sorter.                                                              |

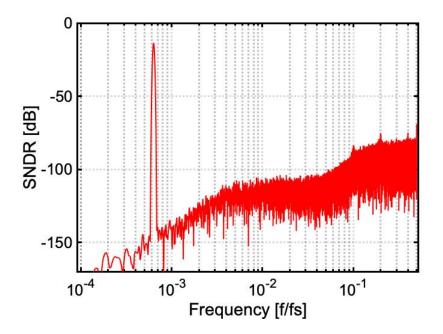

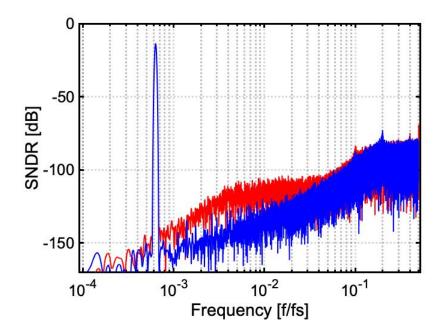

| 3.5  | Mismatch error shaping spectrum of VQ-based DEM with complete sorter and partial sorter.                 |

| 3.6  | Partial sorter structure for 15 elements.                                                                |

| 3.7  | Spectrum at input of 14 dBFS                                                                             |

| 3.8  | Filter structure of VQ-based DEM.                                                                        |

| 3.9  | Spectrum comparison before and after compensation.                                                       |

| 3.10 | VQ-based DEM logic.                                                                                      |

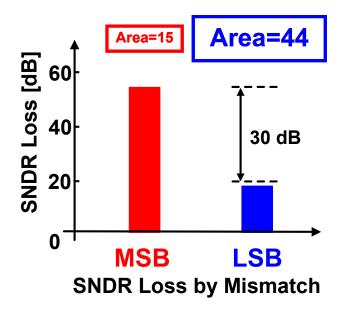

| 3.11 | SNDR loss by mismatch.                                                                                   |

| 3.12 | Architecture of the proposed low-complexity $2^{nd}$ -order VQ-based mismatch error shaping.             |

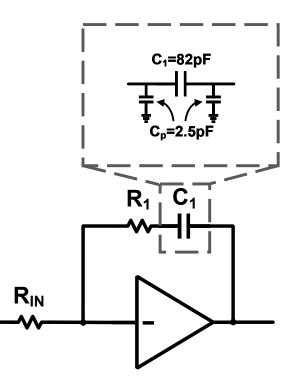

| 3.13 | Large integration capacitor due to a small $R_{IN}$                                                      |

| 3.14 | Integration capacitor area and OTA output swing are reduced with<br>the resistive feedforward path added |

| 3.15 | The schematic of proposed CTDSM                                                                          |

|      | Chopped OTA schematic: $1^{st}$ stage                                                                    |

|      | Chopped OTA schematic: $2^{nd}$ stage                                                                    |

|      | Simplified NS-SAR schematic.                                                                             |

|      | NS-SAR timing.                                                                                           |

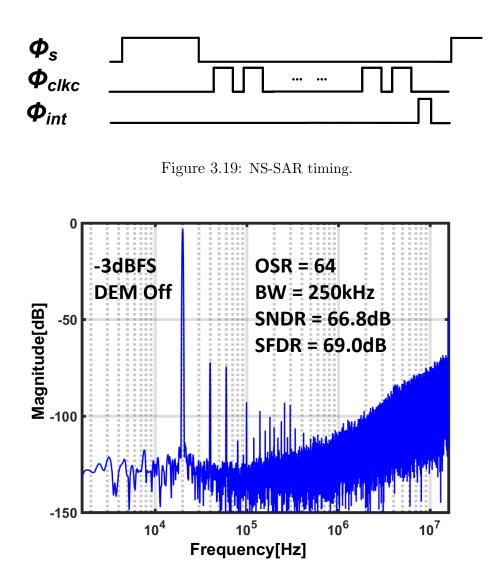

| 3.20 | Measured output spectra at large-amplitude input with DEM off .                                          |

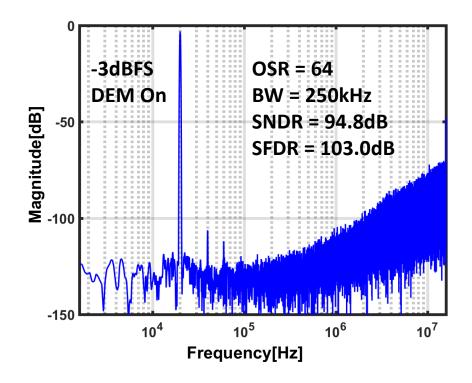

| 3.21 | Measured output spectra at large-amplitude input with DEM on $\ .$                                                                                                                                                                                                                                                                        | 70        |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

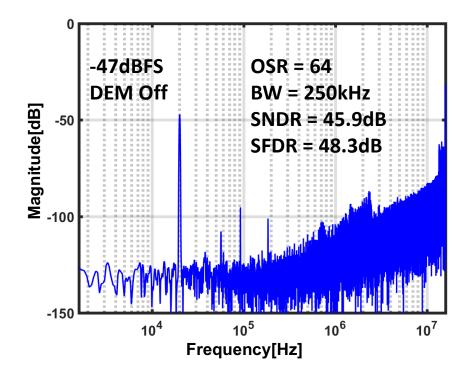

| 3.22 | Measured output spectra at small-amplitude input with DEM off $% \mathcal{A}$ .                                                                                                                                                                                                                                                           | 71        |

| 3.23 | Measured output spectra at small-amplitude input with DEM on $% \mathcal{A}$ .                                                                                                                                                                                                                                                            | 72        |

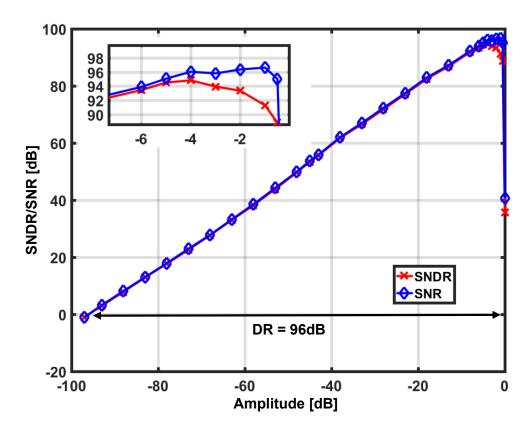

| 3.24 | Measured SNDR/SNR vs. different input amplitudes                                                                                                                                                                                                                                                                                          | 73        |

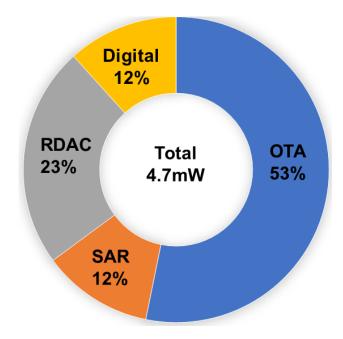

| 3.25 | Power breakdown.                                                                                                                                                                                                                                                                                                                          | 74        |

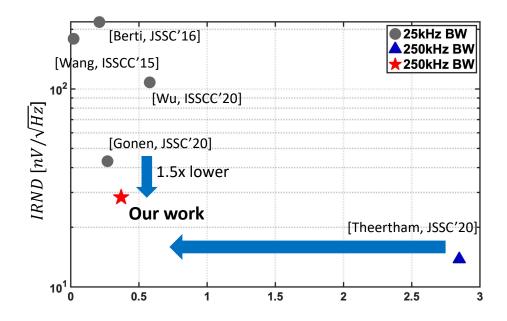

| 3.26 | IRND and area plot of high-resolution CTDSMs                                                                                                                                                                                                                                                                                              | 76        |

| 4.1  | <i>Left:</i> Performances under variations form a distribution. <i>Right:</i> New technologies have larger process variations, vulnerability to environmental variations, hence higher discarded rate                                                                                                                                     | 78        |

| 4.2  | RobustAnalog Overview. (1) A pruned task subset is generated<br>from the full task set (2) Multi-task RL agent is trained on<br>task subset (3) Training continues until the produced sizing can<br>achieve training tasks. Then the sizing is evaluated on the full<br>set. If it passes all the tasks, RobustAnalog returns the result. | 86        |

| 4.3  | Visualization of corner task clustering and selection for stron-<br>gARM Latch. k-means decision boundary is shown, dividing<br>corners into two kinds: noise-limited corners (blue) and speed-<br>limited corners (brown). The corner with the worst performance<br>in each cluster is chosen as one of the training tasks               | 90        |

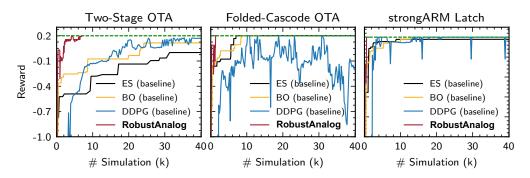

| 4.4  | Three analog/mixed-signal benchmarks.                                                                                                                                                                                                                                                                                                     | 96        |

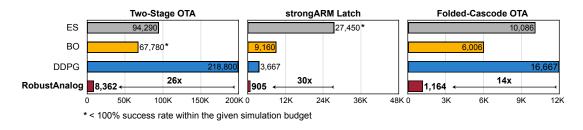

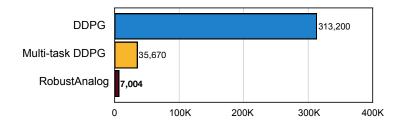

| 4.5  | Simulation times for each method to take to first hit reward= $0.2$                                                                                                                                                                                                                                                                       | 96        |

| 4.6  | Compare learning curves (average reward vs. $\#$ simulation)<br>among baselines and our proposed RobustAnalog. Reward=0.2<br>indicates all tasks are passed. RobustAnalog hits the reward of<br>0.2 significantly faster than the baseline methods on all bench-                                                                          |           |

|      | marks.                                                                                                                                                                                                                                                                                                                                    | 97        |

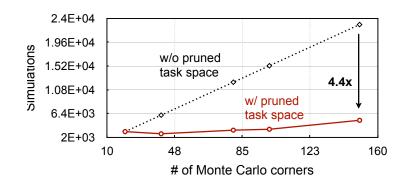

| 4.7  | Ablation of applying multi-task and task space pruning. Using two together brings the least simulation cost.                                                                                                                                                                                                                              | 98        |

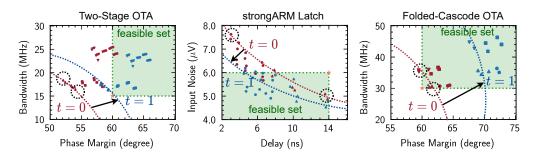

| 4.8  | Performance distributions of two intermediate sizings during the RobustAnalog optimization. Red and blue markers are performances on different corners at time $t_0$ and $t_1$ . Selected training corners are indicated by black circles.                                                                                                | 99        |

| 4.9  |                                                                                                                                                                                                                                                                                                                                           | 99<br>100 |

| т.Ј  |                                                                                                                                                                                                                                                                                                                                           | 100       |

## Chapter 1

### Introduction

# 1.1 High-Performance Mixed-Signal Circuit1.1.1 ADC Background and Applications

Nowadays, we have witnessed an increasing demand for high-performance mixed-signal circuits. Analog-to-digital converter (ADC), as a typical mixedsignal circuit, plays an essential role in many applications, as shown in Fig. 1.1. Today's world has become a ubiquitous sensing environment. ADC serves as the portal connecting the physical world to computational intelligence. For example, trillions of photos are captured by digital cameras in the world each year. A digital cameras usually demand many ADCs of around 80 dB signal-tonoise-and-distortion-ratio (SNDR) and a bandwidth of tens of MHz. Moreover, Internet of Things (IoT), mobile sensing, and bio-sensing have further reduced the boundaries of sensor data granularity. The way we perceive the world is no longer restricted to our visual or auditory sense. The boom of received information is reshaping our understanding of the world. Such minuscular sensing devices requires ADCs of 60-100 dB SNDR and tens to hundreds of kHz bandwidth. Unfortunately, high-speed, high-resolution ADCs are costly in area and power. The gap between such demand and supply motivates us to develop energy and area-efficient designs.

Figure 1.1: ADC application universe [Robertson [2015]]

#### 1.1.2 High-Speed and High-Resolution CTDSMs

Oversampling and noise-shaping ADCs are proposed to achieve high resolution. Their sampling frequency is much higher than the Nyquist rate. With proper signal processing, noise shaping, in-band quantization noise can be largely suppressed. Noise shaping is usually achieved by Delta-Sigma modulation(DSM). Continuous-time Delta-Sigma modulator (CTDSM) features a higher efficiency than its discrete-time (DT) counterpart. A generic block diagram of CTDSM is shown in Fig. 1.2. They generally consist of a quantizer, feedback digital-to-analog converter (DAC), and, importantly, a loop filter that determines the noise transfer function (NTF). The continuous pro-

Figure 1.2: Generic model of CTDSM

cessing of signals yields lower dynamic requirements on the loop filters. Also, CTDSM has easier drivability, and probably most importantly, their implicit signal filtering. The CTDSM gained its popularity in high-resolution design with sub-MHz bandwidth, as shown in Fig 1.3. High oversampling ratio (OSR) and moderate order loop-filters are usually used for high-resolution designs. CTDSM has also paved its way to the wideband domain. As evidenced by Fig. 1.3, CTDSM showed its great power efficiency at the bandwidth of hundreds of MHz. Low OSR and high loop-filter order are usually the design choices for high-speed designs. Nevertheless, there are several bottlenecks preventing the power/area efficiency of CTDSM from being further improved. For high-speed designs, the obstacles to achieve low power come two-fold. First, as

Figure 1.3: CTDSM in ADC FoM surveys.

mentioned above, the high loop filter order dictates a large number of OTAs. The OTAs need to consume a considerable amount of static current to guarantee the loop filters' performance. Second, the high loop filter order demands excess-loop-delay (ELD) compensation, which is expensive. Therefore, an efficient high-speed design should minimize the involvement of OTAs and the price for ELD compensation. For high-resolution CTDSMs, there are two obstacles to compact area designs. First, the distortion target poses stringent mismatch requirements for the feedback DAC. The feedback DAC has to occupy a large area to suppress the mismatch error. Second, large capacitors are required due to the thermal noise requirement. To attain the area reduction, it imminently calls for new design patterns for high-resolution CTDSMs. The new pattern should leverage the advancement of CMOS scaling instead of being limited by them.

A substantial part of this dissertation is to research and propose new techniques for power-efficient high-speed CTDSMs and area-efficient highresolution CTDSMs. In the discussion of power-efficient high-speed CTDSMs, the focus is placed on hybridizing CTDSM with passive DTDSM. The sheer number of power-hungry OTAs is reduced by using a nested noise-shaping (NS) quantizer. The lower CT NS order also eases the ELD compensation. Such a combination decouples the trade-off between stability and aggressive NS of CTDSMs. In the discussion of area-efficient high-resolution CTDSMs, a high-order mismatch error shaping (MES) is applied to save the resistor DAC (RDAC) area. The prototype design essentially adapts the high-resolution DSM to a more digital-intensive fashion, thus unveiling many new possibilities for area reduction. The research of high-speed and high-resolution CTDSMs in this dissertation is carried out in two stages, with a prototype ADC taped out in each stage as proof of concept.

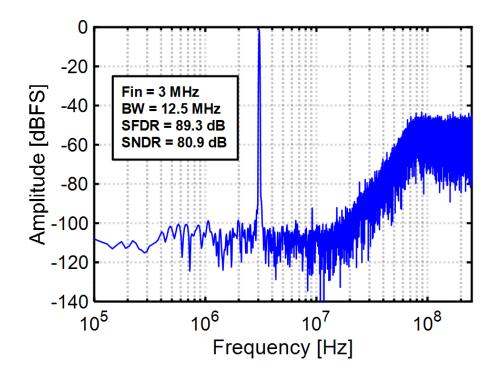

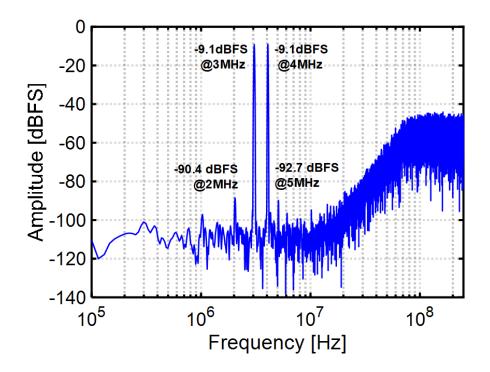

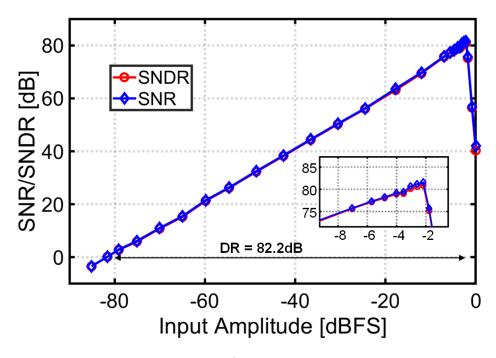

The first prototype demonstrates a hybridized high-order CT-DT DSM. It presents a design that combines a CT single-amplifier biquad (SAB)-based  $2^{nd}$ -order loop filter with a DT passive  $2^{nd}$ -order NS Successive approximation registers (SAR). As a result, the prototype ADC uses only one OTA but achieves  $4^{th}$ -order shaping. The power and area of the NS-SAR can be made very small owing to the high gain from the SAB filter. Process-VoltageTemperature (PVT) robustness is improved as NS-SAR is immune from PVT variations. On top of the hybridization, this work implements both ELD compensation and the direct feedforward path in the charge domain, further reducing the circuit complexity and the OTA power. The techniques enable the proposed ADC to achieve 81dB SNDR over 12.5MHz BW with 3.7mW power, leading to a Schreier FoM of 176dB.

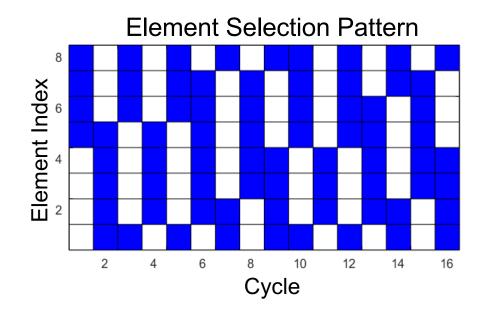

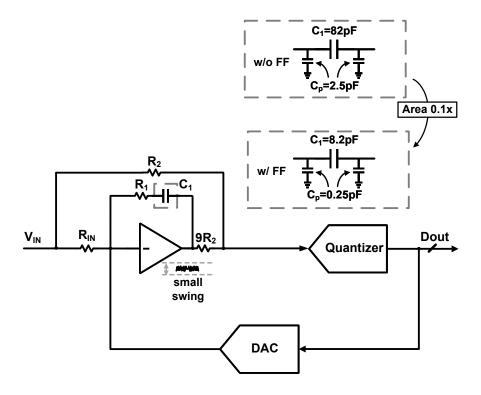

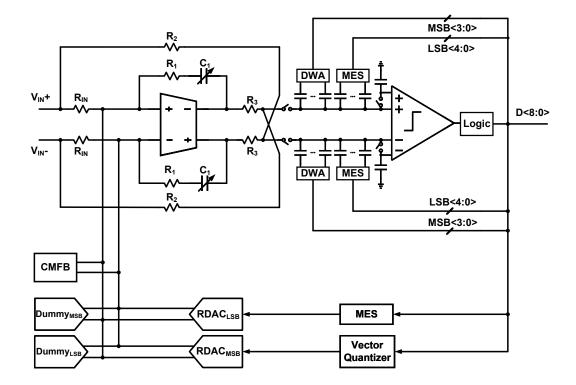

The second prototype explores the area reduction techniques in the high-resolution CTDSM. This work significantly reduces the total DAC area by applying a hardware-efficient  $2^{nd}$ -order vector-quantizer (VQ) based dynamic element matching (DEM) to the MSB DAC. The  $2^{nd}$ -order DSM not only suppresses the dominiant MSB DAC mismatch error, but also alleviates the SNDR kink issue of the  $1^{st}$ -order dynamic weighted averaging (DWA). Moreover, a direct feedforward-assisted loop filter reduces the integrating capacitor's area by 10 times. Overall, this work achieves 95 dB SNDR and 250 kHz BW while consuming 4.7 mW from a 1.1 V supply and having a compact area of 0.37 mm<sup>2</sup>.

In the subsequent chapters, the details of these prototypes and their corresponding techniques will be presented and analyzed. Measurement results will also be discussed and compared to state-of-the-art statistics.

#### **1.2** Analog Design Automation

Thanks to technology scaling and circuit innovations, analog/mixedsignal circuits have achieved great advancement in the past twenty years.

Figure 1.4: Increasing design cost in today's technologies [Olofsson [2018]].

However, the design complexity grows exponentially with technology scaling, as shown in Fig. 1.4. Nowadays, circuit design is a paramount and extremely challenging task. The explosive growth of engineering cost in circuit design calls for a highly automated workflow. Analog, mixed-signal, and RF circuits are indispensable in modern electronics systems. Implementing analog circuits is mainly a manual, time-consuming, and error-prone task. In a modern application-specific integrated circuit (ASIC), analog circuits occupy 30% of the total area but consumes 70% of engineers' efforts. Analog design requires a huge amount of human effort and lacks effective automation. A short turnaround time of analog, mixed-signal, radio-frequency (RF) IC design is highly desired.

Typical analog design procedure includes the following steps. First, designers must determine circuit topology according to the requirements. Second, devices are appropriately sized for the targeted performance. Devices include dimensions of different transistors, resistors/capacitors, and so on. After device sizing, a corresponding layout is carefully designed to avoid performance degradation. At last, a comprehensive verification including process-voltagetemperature(PVT) and Monte-Carlo simulations are performed. There has been plenty of work on automating analog sizing and layout. For sizing problems, many simulation-based optimization methods have been explored recently [Liu et al. [2009]; Lyu et al. [2018a]; Wang et al. [2020a]; Settaluri et al. [2020]]. For the automatic analog/mixed-signal layout synthesis, current popular methods can be categorized into two kinds: procedural-based methods and optimization-based methods. Recent works on procedural-based methods have shown the potential of producing tape-out quality designs [Wulff and Ytterdal [2017]; Chang et al. [2018]]. For optimization-based methods, there are several open-source layout generators [Kunal et al. [2019]; Xu et al. [2019]].

In this dissertation, we focus on the analog circuit sizing which is an important stage in the procedure. Analog sizing, as an engineering optimization problem, is hard due to the following reasons: 1) The relationship between the circuit performances and the design variables is extremely complex and highly non-linear. In fact, designers spent the most time on the derivation of circuit performance metrics. For example, noise analysis is non-trivial even for highly-skilled designers. Designers dive into noise sources and transfer functions, attempting to obtain insights to design optimal sizings. Tremendous efforts of such derivation can be avoided by relying on the simulator to provide the mapping. However, A large number of slow simulations are needed, which makes this optimization problem computationally expensive. 2) The solution space is sparse and multi-objective optimization is not easy. Unlike digital circuits, analog design usually requires transistors to operate in a narrow region. For example, transistors in OTAs must be in saturation to provide proper trans-conductance and output resistance. Moreover, very few combinations of design variables can produce desired circuit performance. The list of things that can go wrong is long. This problem becomes worse in a more complicated design that has 20 or more design variables. 3) There are many constraints that are difficult to be quantified. Designers develop their common sense from their past experiences. The width to length ratio should not be either too large or small to save area. Critical transistors should not be biased into the deep sub-threshold region to ensure PVT robustness. However, in analog automation, such common sense is blind to the machine unless one explicitly set a quantized constraint. Machine sometimes presents solutions that are numerically satisfying but violate some hidden constraints. Debugging with the machine-generated results and implementing the ad-hoc constraints is also a laborious and frustrating process.

#### **1.2.1** Automation Problem Formulation

Circuit sizing can be formulated as a constrained optimization problem. Given a fixed circuit topology, we search for a circuit sizing that has the optimal performance.

minimize

$$F_0(X)$$

subject to  $F_i(X) < C_i, \quad i = 1, \dots, k$  (1.1)

where

$$X = X_1, X_2, ..., X_n$$

$D = D_1, D_2, ..., D_n$

$C = C_1, C_2, ..., C_m$

X, the sizing vector, is an n-dimensional variable which corresponding to n circuit sizing parameters. D is the domain for X. For example,  $D_1$  is [0, 1] which means the design space of  $X_1$  is [0, 1]. C is the constraint set for all circuit metrics. Because we have m metrics, the number of constraints is also m.  $F_i(X)$  is the  $i^{th}$  performance metric of circuit.  $F_i$  is a non-linear mapping between X and the  $i^{th}$  metric in the performance. X is the input. We rely on the circuit simulator to provide this mapping. Circuit design is a multi-objective design. Thus,  $F_0(X)$  is a vector. In most existing automation methods,  $F_0(X)$  is scalarized. Therefore, our goal is to find an optimal X that can satisfy any constraints in C. A common variant is to make  $F_0(X)$  a constant and put all objectives into constraints. Thus, the constrained optimization problem degenerates to a constraint satisfaction problem (CSP). The CSP formulation implies that sometimes our target is to satisfy design requirements rather than maximize the performance.

#### 1.2.2 Optimization Methods

Various research works attempted to tackle the analog automation challenges with different levels of human involvement. Human designers can help to narrow down the initial sizing range, which makes the problem easier. Such simplification requires designers' expertise in circuit behavior, device technology, and past design experiences. The more prior human knowledge we utilize, the easier the sizing will be. Therefore, existing automation techniques can be categorized into equation-based and simulation-based methods. Equations are derived by human experts, characterizing the relationship between sizing and circuit metrics. Equation-based methods are computationally efficient as they lump the complex circuit system into multiple equations. However, solutions are not satisfying because equations are inaccurate, which becomes a more severe problem in the advanced technologies. Simulation-based methods search the design space for optimal solutions according to the circuit simulation results. The automatic design space exploration can provide solutions with superior performance to that of human designs. Nevertheless, the expensive simulations prevent such methods from solving large-scale circuits or many constraints. This dissertation will talk about improving the efficiency and scalibility through various optimization techniques.

As simulation-based methods solely rely on the simulator to provide sizing-to-performance mapping close-form expression of objective function and constraints can be hardly obtained. In the meanwhile, the simulations are computationally expensive and time-consuming. Thus, it resembles a blackbox optimization problem. With multiple sizing variables as inputs, the simulator provides multi-dimensional metrics as outputs. Several black-box optimization methods are applied to the analog sizing, achieving different optimalities and sample efficiency. They are Evolutionary Strategy (ES), Bayesian Optimization (BO), and Reinforcement Learning (RL)-guided optimization.

#### 1.2.2.1 Evolutionary Strategy

Evolutionary computation is a global heuristic search method that mimics the natural evolution process to find approximate solutions for optimization problems. ES is a subset of Evolutionary computation. ES works with vectors of real numbers as representation of solutions. ES solves the trialand-error problems based on survival of the fittest. Fitness is usually defined by our objective function. The evolutionary concepts are inheritance, selection, mutation, and crossover. A typical ES methodology is shown in Fig. 1.5. Initially, a set of individual solutions, called population, is randomly generated to cover the entire range of search space extensively. Then the fitness of each individual in the population is evaluated. The next step consists of the selection stage, where the fitness of the individuals is utilized for determining

Figure 1.5: Evolutionary Computation Flow.

the individuals that will be selected for breeding to generate solutions of the future generation. A few individuals of low fitness can also be selected to ensure solution diversity. Diversity can prevent premature convergence and strike a balance between local versus global search. Next, the reproduction stage occurs where the selected solutions from the previous step are mated through crossover and/or mutation. The algorithm is continued until fitness

values satisfy our requirements.

The advantages of ES are that they are not affected by discontinuous optimization landscape and are suitable for high-dimensional problems. ES achieved progress in solving medium-scale problems (20-40 dimensions). In the context of analog sizing, the scale is corresponding to a circuit building block that has around 20 devices. ES was applied to analog synthesis as early as 1997 in [Koza et al. [1997]]. In the work of [Liu et al. [2009]], augmented Lagrangians are incorporated to solve the constrained sizing optimization. Surrogate modeling has also been introduced to improve sampling efficiency [Liu et al. [2013, 2014, 2016]]. Recently, Deep neural network (DNN) has been put into the loop of ES to model the circuit behavior [Hakhamaneshi et al. [2019]].

#### 1.2.2.2 Bayesian Optimization

Bayesian optimization is another sequential design strategy for global optimization of black-box functions that does not assume any functional forms. The basic flow is shown in Fig. 1.6. The objective function is evaluated by the simulator, which is an unknown and expensive process. Bayesian optimization treats it as a random function and place a prior over it. In each iteration, a set of function evaluations are collected and used as training data to update the prior. Then a posterior distribution over the objective function is obtained from prior. At last, an acquisition function is constructed to determine the next query point. There are several methods used to define the prior/posterior distribution over the objective function. Models that describe such distribu-

Figure 1.6: Bayesian Optimization Flow.

tions are called surrogate model. They not only provides predictive means but also the corresponding uncertainty estimations. The most common surrogate model is Gaussian Processes. Bayesian optimization is particularly advantageous in terms of sample efficiency. However, it has high computation complexity with the number of samples. Considering its computation cost, it is a good fit in problems of fewer than 20 dimensions.

BO was introduced to analog sizing problem later than ES. In the work of [Lyu et al. [2018b,a]], authors view sizing as a multi-objective sizing and applied BO framework to solve it. Sizing optimization can also benefit from simulations of different accuracy and speeds [Zhang et al. [2019b, 2020]].

#### 1.2.2.3 RL-Guided Optimization

RL originates from ideas from dynamic system theory, specifically, as the optimal control of incompletely-known Markov decision problem. We train a learning agent to achieve a goal by making it interacting with its environment over time. The learning agent sense the states of the environment and take actions that affect the state. These three aspects, sensation, action, and goal echo the sequential decision process in the optimization problem. Beyond the agent and the environment, there are four main elements of a reinforcement learning system: a policy, a reward, a value function, and, optionally, a model of the environment. A policy defines the agent's behavior at a given state. The policy can be loosely described as a mapping from perceived states of the environment to actions. Generally, policies may be stochastic and specify probabilities for each action. A reward defines the goal of a RL problem. On each iteration, environment sends a reward, a number, to the agent. The agent's objective is to maximize the long-term cumulative reward. Models refer to the environment modeling, which is similar to the surrogate model. They mimic the environment outputs given the same inputs. Recently, RL methods

Figure 1.7: Reinforcement Learning Flow.

become attractive as they achieved great success in domains including gaming, autoML, and robotics. Applied to the circuit design automation, RL methods show the potential to achieve higher circuit performances given enough explorations [Wang et al. [2018a, 2020a]; Settaluri et al. [2020]]. Moreover, RL enables transfer- learning across different design conditions, including different technologies and pre/post-layout design stage. Moreover, DNNs are being extensively studied and turn out to be a powerful model of the environment. They can approximate the complex relation between circuit parameters and performances. DNNs are tailored to circuit optimizations in the works of [Budak et al. [2021]; Yang et al. [2021]]. Graph neural network (GNN) leverages the circuit connectivity information to improve the model performance [Wang et al. [2020a]; Zhang et al. [2019a]].

#### 1.2.2.4 Challenges in Practical Analog Optimization

We still have many challenges though there has been great progress in circuit sizing optimization. There are three directions we can explore. 1) scal*abity.* All existing works have focused on small-sized circuit blocks. To extend the current methods to larger-scale circuits, we have two potential directions. First, the single thread of sequential trial-and-error process limits the exploration at each time step. Asynchronous parallelism is a way to best leverage modern compute power nowadays. Second, hierarchy in large circuit systems has not been studied. Human designers often start designing in a top-down fashion. Similarly, how to automate divide and conquer, how to communicate between high-level and low-level abstractions are essential questions we have to answer to achieve large-scale optimization. 2) robustness. There are very few works about optimization under uncertainty. However, the real challenge of designing the analog circuit is to overcome numerous unpredictable uncertainties in the fabrication and end-user environment. Incorporating uncertainty into automation flow in a brute force way leads to the explosive simulation cost increase. 3) *generalization*. Unlike digital circuits, analog circuits are usually highly customized. However, there are still many properties analog circuits share in common (e.g. noise-bandwidth trade-off). Existing methods are applied to a small cluster of circuits and can hardly be adapted into a different kind. To overcome this challenge, a promising way is to discover a better circuit representation. GNN, as used in [Mirhoseini et al. [2021]], has a data structure better aligning with the circuit connectivity. With such circuit representation, offline data could be exploited to achieve few-shot learning.

A substantial part of dissertation is to address the robustness problem of analog design automation. The challenges of variation-aware automation come twofold. First, the simulation cost is prohibitively expensive in order to get accurate variation effects. Second, optimizing circuits under one condition may conflict with the other, making the optimization landscape more complex. a multi-task RL framework with task-space pruning is presented to address the above challenges. Variations are viewed as different tasks. Their correlations are modeled and conflicts are mitigated, leading to an increased sampling efficiency. A proxy training task set is selected by pruning, reducing the simulations of the full set. In the subsequent chapter, the corresponding methodology and analysis will be shown. Comparisons between existing optimization methods and the proposed method will be discussed.

## Chapter 2

# High Speed Hybrid CT-DT DSM with Charge-domain ELDC

This chapter <sup>1</sup> presents a hybrid  $4^{th}$ -order delta-sigma modulator (DSM). It combines a continuous-time (CT) loop filter and a discrete-time (DT) passive  $2^{nd}$ -order noise-shaping SAR (NS-SAR). Since the  $2^{nd}$ -order NS-SAR is robust against PVT, the stability of this  $4^{th}$ -order DSM is similar to that of a  $2^{nd}$ -order CT-DSM. The CT loop filter is based on single-amplifier bi-quad (SAB) structure. As a result, only one OTA is used to achieve  $4^{th}$ -order noise shaping, leading to a high power efficiency. Moreover, this work implements both ELD compensation and an input feedforward path inside the NS-SAR in the charge domain, further reducing the circuit complexity and the OTA power. Overall, this work achieves 81 dB SNDR over 12.5 MHz with 3.7 mW

<sup>&</sup>lt;sup>1</sup>This chapter is a partial reprint of the publication: Wei Shi, Jiaxin Liu, Abhishek Mukherjee, Xiangxing Yang, Xiyuan Tang, Linxiao Shen, Wenda Zhao and Nan Sun, "A 3.7mW 12.5MHz 81dB-SNDR 4th-Order CTDSM with Single-OTA and 2nd-Order NS-SAR," in *IEEE International Solid-State Circuits Conference (ISSCC)*, pp. C170-C172, February 2021. I am the main contributor in charge of circuit design, layout, and chip validations.

power, leading to a Schreier FoM of 176 dB.

### 2.1 Introduction

The continuous time (CT) delta-sigma modulator (DSM) is a popular choice in wide-band analog-to-digital converters (ADCs), especially for wireless transceivers. Typical DT and CT DSMs are shown in Fig. 2.1. The loop filter of CT DSM processes the signal before sampling, achieving both noise shaping and anti-alias filtering. The settling requirement is obviated owing to the CT-domain operation. Therefore, lower dynamic requirements for the loop-filter, the inherent anti-aliasing filtering, and an easy-to-drive front-end are the major advantages that CTDSM has over its DT counterpart. A low oversampling ratio (OSR) is needed if an energy-efficient CT DSM with high bandwidth and high resolution is desired. A high-order noise transfer function (NTF) is usually applied to achieve the target resolution. However, several challenges are posed to the high-order CT DSMs due to the non-idealities of practical implementations. First, the CT loop-filter is sensitive to the process variation [Schreier and Zhang [1996]]. The loop-filter coefficients primarily depend on the resistors and capacitors whose values vary across PVT variations. Consequently, extra tuning circuitry is needed. Second, conventional high-order loop-filters have a large number of OTAs. Multiple cascaded OTAs cause phase shifts, leading to instability. Third, excess-loop-delay (ELD) in the CT DSM alters the NTF. The price paid to compensate the ELD is high in high-order designs. Extra circuit complexity and power consumption dete-

Figure 2.1: Typical discrete-time and continuous-time structures.

riorate the power efficiency.

In this work, we present a  $4^{th}$ -order hybrid CT-DT DSM that combines a  $2^{nd}$ -order single-amplifier-biquad (SAB)-based CT filter with a  $2^{nd}$ -order passive noise-shaping SAR (NS-SAR). With the DT noise shaping immune from the PVT variation, the hybrid DSM obtains a better robustness. Compared to the conventional design, the combination of SAB and passive NS-SAR reduces the number of OTAs from many to one. The power is saved because of removing many power-hungry OTAs and the relaxed bandwidth requirement. Moreover, the ELD compensation (ELDC) is embedded into the charge domain. There is minimal extra power and circuitry cost for the ELD compensation since it is implemented with the small CDAC of the NS-SAR.

This chapter is organized as follows. Section 2.2 reviews the prior highorder CTDSM designs and introduces the proposed hybrid  $4^{th}$ -order DSM. Section 2.3 discusses the ELD compensation techniques and introduces the proposed charge-domain ELD compensation with both feedforward and feedback paths. Section 2.4 describes the design of the prototype ADC and discusses implementation details. Section 2.5 presents measurement results. Section 2.6 concludes this chapter.

# 2.2 Proposed 4<sup>th</sup>-Order Hybrid CT-DT DSM 2.2.1 Prior High-Order CT DSMs

There is extensive research on tackling the challenges in high-order CTDSM designs. The NTF sensitivity to the RC time constant variation causes the performance degradation and instability. Leaving design margin for variation is a feasible solution, which essentially trades noise-shaping performance for better robustness [De Vuyst et al. [2011]; Ho et al. [2015]; Berti et al. [2016]]. An alternative solution is a corner-adaptive tuning circuit or off-chip calibration [Pavan et al. [2017]]. The loop-filter implementation is a determinant for the power efficiency. Gm-C and VCO integrators are proposed as a low-power alternative for the power-hungry feedback integrators [Mukherjee et al. [2020]; Li et al. [2017]]. However, their linearity is limited. To reduce the total delay of the multiple cascaded OTAs, higher power budget has to be assigned to meet the stringent OTA bandwidth requirement. OTA bandwidth

requirements can be relaxed by the ELD over-compensation [Shu et al. [2013]], but there are still four OTAs for a  $4^{th}$ -order DSM. One way to improve the power efficiency is to reduce the sheer number of OTAs. SAB has been studied and used in the CT DSM [Zanbaghi et al. [2013]; Wang et al. [2018b]; Berti et al. [2016]]. However, unsatisfying loop-filter robustness still remains as an issue.

Lowering the CT noise shaping order by adding the DT order can be a strategy to improve both the robustness and power efficiency. A CT front-end is applied to the DSM, followed by switched-capacitor based filters in [Signore et al. [1990]]. The large sampling capacitor is avoided by using a first-order RC integrator. The precise positioning of poles and zeros in the NTF are guaranteed by the following third-order DT filter. However, the DT filter still needs OTA. Thus, the total number of OTAs in the DSM is unchanged. An effective way to incorporate the DT shaping order is to embed a noise-shaping quantizer into the DSM loop. Emerging passive NS-SARs are attractive because they are OTA-free, PVT robust, and energy-efficient [Guo and Sun [2016]; Lo et al. [2019]]. An RC integrator and a  $2^{nd}$ -order passive NS-SAR is proposed in [Liu et al. [2019]]. Third-order shaping is achieved by a single OTA. However, the passive NS-SAR input-referred noise cannot be sufficiently suppressed by the  $1^{st}$ -order CT filter. Even worse, the NS-SAR noise is amplified by four times because of the direct feedback ELD compensation, which will be discussed in Section 2.3. Therefore, the resolution is limited to 70 dB SNDR. The work of [Xing et al. [2020]] adopts a SAB-based filter as front-end and  $1^{st}$ -order NS-SAR as the backend quantizer. However, the NS-SAR NTF is mild, and the current domain ELD compensation is costly. A  $1^{st}$ -order NS-SAR is used with a  $1^{st}$ -order RC integrator in [Lo et al. [2019]]. The high resolution relies on the 12-cycle NS-SAR. Nevertheless, the 12-cycle NS-SAR requires a larger timing budget and area consumption.

#### 2.2.2 Hybrid DSM Architecture

To address the high-order CT DSM design challenges mentioned above, we propose a  $4^{th}$ -order hybrid CT-DT DSM. Fig. 2.2 shows the architecture of the proposed hybrid DSM with a  $2^{nd}$ -order CT SAB filter and a passive  $2^{nd}$ order DT NS-SAR. The NS-SAR NTF coefficients are set by capacitor and transistor device ratios [Liu et al. [2019]]. Therefore, the  $2^{nd}$ -order shaping from the passive NS-SAR is immune from PVT variations, which improves the robustness of the proposed  $4^{th}$ -order DSM.

The extra thermal noise from the passive NS-SAR prevents it from achieving a high resolution as a standalone quantizer. In the proposed DSM, the high gain provided by the SAB filter suppresses the noise of the passive NS-SAR. Consequently, the power and area of the NS-SAR can be made very small. In the meantime, the  $4^{th}$ -order shaping is achieved by only one OTA. The power is saved from the elimination of multiple power-hungry OTAs and the bandwidth relaxation. Moreover, the ELD compensation is implemented in the charge domain with minimal circuitry and power overhead.

Figure 2.2: Proposed hybrid DSM with SAB filter and passive NS-SAR quantizer

#### 2.2.3 Coefficient Sensitivity

Fig. 2.3 compares a conventional  $4^{th}$ -order CTDSM with the proposed hybrid architecture. In the conventional design, tunable capacitor banks are added to deal with the variation. Four OTAs are cascaded in the loop-filter with the corresponding bandwidths  $BW_{1-4}$ . The proposed DSM has a single OTA with bandwidth  $BW_0$  and a noise-shaped quantizer. The sensitivity of the conventional and proposed DSM to the RC time constant variation is shown in Fig. 2.4. Both DSMs have an NTF with two optimized zeros.

It can be clearly seen that the conventional  $4^{th}$ -order CTDSMs are highly sensitive to RC time constant variations. It becomes unstable when the variation in the coefficients (1/RC) goes beyond +8%. In the meantime, its SQNR drops significantly as the coefficients decreases. By contrast, the proposed DSM remains stable as long as the coefficients variation is less than

Figure 2.3: (a) Conventional  $4^{th}\text{-}\mathrm{order}$  CT DSM, (b) Proposed  $4^{th}\text{-}\mathrm{order}$  hybrid CT-DT DSM

+15%, and the slope of the SQNR variation is also milder (e.g., SQNR >80 dB with -30% coefficient variation). The improved robustness leads to the area and complexity reduction of the tuning circuits.

#### 2.2.4 Finite UGB Effects

The finite UGB of the OTA degrades the stability of the feedback loop. To investigate how the proposed DSM performs under different  $BW_0$ , we in-

Figure 2.4: Coefficient sensitivity comparison between a conventional and the proposed  $4^{th}$ -order hybrid CT-DT DSM

corporate the OTA UGB into our DSM modeling. The SAB transfer function is:

$$H(s) = \frac{k_1 s + k_2}{s^2 + k_3 s + w_p^2} \tag{2.1}$$

We model the OTA as a single-pole system with a finite DC gain  $A_{DC}$ and a pole frequency  $\omega_0$ . Correspondingly, the UGB is  $A_{DC}\omega_0$ . In order to achieve an ideal SAB filter response,  $k_3$  is set to zero by choosing proper

Figure 2.5: Proposed hybrid CT-DT DSM SQNR with different OTA UGBs RC values. Therefore, the SAB transfer function with the finite OTA UGB becomes

$$H'(s) = \frac{k_1 s + k_2}{s^2 + w_p^2 + (\frac{s}{UGB} + \frac{1}{A_{DC}})(s^2 + k_1 s + k_2 + w_p^2)}$$

(2.2)

Fig. 2.5 shows the SQNR over different UGB of the single OTA. From  $0.5f_s$  to  $1.5f_s$ , the SQNR improvement is around 10 dB while there is only 2~3 dB improvement from  $1.5f_s$  to  $5f_s$ . Thus,  $1.5f_s$  is chosen as our OTA bandwidth. By contrast, conventional  $4^{th}$ -order CTDSMs requires  $3\sim 4 f_s$  OTA bandwidth to make the loop stable [Wang et al. [2020c]]. The relaxation of OTA bandwidth and the decreased number of OTAs result in significantly reduced power.

Figure 2.6: ELDC implemented by the direct feedback path

Figure 2.7: ELDC implemented by the residual feedforward path

# 2.3 Proposed ELD Compensation Scheme

#### 2.3.1 Brief Review of ELD Compensation

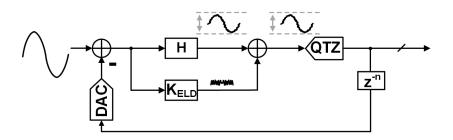

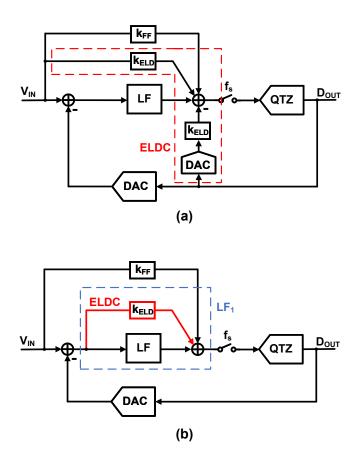

ELD is a key problem in the CT DSM design. Such delay is bound to degrade modulator stability and change NTF. ELD compensation techniques can be used to restore the loop stability and the desired NTF. However, the price for ELD compensation is high in high-order and high-speed CT DSM designs. The high cost consists of two parts. First, it adds the extra circuitry into the DSM. In the conventional designs, a direct feedback path around the quantizer dictates an extra DAC [Pavan et al. [2017]]. Second, the tuning of the filter coefficients is needed. To compensate for the delay, we have to increase the coefficients of lower-order paths in the loop filter. The required filter UGB is then increased. The OTA bandwidths have to be increased proportionally to maintain the desired filter response. Therefore, the ELD compensation incurs a significant increase in both circuitry complexity and power consumption. Prior works have dedicated significant efforts to address the high cost of ELD compensation. The direct feedback path can be embedded into the flash quantizer [Shu et al. [2013]]. However, the feedback path complicates the flash quantizer design. If the quantizer is SAR, the feedback path implementation can be simplified because of the inherent CDAC [Wei et al. [2015]; Wu et al. [2016]; Liu et al. [2019]]. However, the direct feedback path around the quantizer increases the loop-filter swing, as shown in Fig. 2.6. The larger swing degrades the OTA linearity or even exceeds the power supply range. A dynamic range scaling has to be performed by changing the loop-filter and quantizer gain. With a reduced filter gain, the noise is amplified. A residual ELD compensation can avoid the large filter output swing by not feeding the signal component to the filter output [Ho et al. [2015]; Wang et al. [2020c]]. Fig. 2.7 shows that only noise part is sent to the sum node before the quantizer. However, they are implemented in the current domain. A feedforward resistor is inserted into the RC integrator, which is shown in Fig. 2.8. The ELD compensation is affected by the finite UGB of the OTA. Alternatively, the compensation can also be implemented in the phase domain in a VCObased design [Huang et al. [2017]]. Nevertheless, it consumes almost a 1.5-fold power of the whole loop filter.

Figure 2.8: (a) Residual ELDC signal flow (b) ELDC path implementation in the current domain

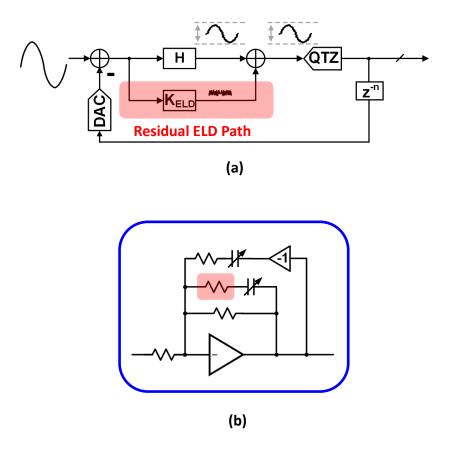

#### 2.3.2 Proposed Charge-domain ELD Compensation

Thanks to the inherent CDAC of SAR quantizer, we can implement the residual ELDC in the charge domain easily, as shown in Fig. 2.9. We propose an efficient charge-domain ELD compensation shown in Fig. 2.10(a). The high efficiency stems from two reasons. First, the compensation is implemented by the small CDAC of NS-SAR. The passive capacitor based ELD compensation

Figure 2.9: Residual ELDC implementation in the charge domain

adds no extra burden on the OTA. In the meantime, the additional circuitry on the CDAC is minimal. An extra feedback DAC is not needed. Second, it implements the residual ELD compensation by combining a feedforward and a feedback path. Therefore, no dynamic range scaling is needed. The noise performance degradation is avoided. Fig. 2.10(b) shows the timing and charge domain operations. The feedback path and feedforward path are implemented by a sub-DAC,  $C_{ELDC}$ . The feedback path output is fed into the bottom plate of  $C_{ELDC}$ . The feedforward path output is sampled onto the top plate of  $C_{ELDC}$ . Note the feedforward signal is also sampled onto the  $C_{SAR}$ . This helps to reduce the SAB output swing further, leading to the linearity enhancement. The timing of the ELD compensation is the following. During the sampling phase, the bottom plates of  $C_{ELDC}$  and  $C_{SAR}$  are connected to D[n-1] and the inverse of the SAB output  $-V_L$ , respectively. Their top plates are both connected to the DSM input,  $V_{IN}$ . At the sampling frequency of 500 MHz, all sampling operations need to finish within 200 ps under 40-nm LP technology. Fortunately, they do not need to be absolutely accurate, as any sampling error

Figure 2.10: (a) Signal flow and schematic of proposed charge domain embedded ELD compensation, (b) Timing diagram of ELD compensation operations on CDAC

is  $2^{nd}$ -order shaped by the front-end SAB. As the SAR conversion phase begins, their top plates are disconnected from  $V_{IN}$ . Shortly after that, the bottom plates of  $C_{ELDC}$  and  $C_{SAR}$  are reset to  $V_{cm}$ . Consequently, both feedback and feedforward functions are implemented. Then the SAR conversion is performed on  $C_{SAR}$ .

Figure 2.11: (a) The UGB increase of the conventional  $4^{th}$ -order filter after ELDC, (b) The UGB increase of the SAB  $2^{nd}$ -order filter after ELDC.

It is worth noting that lowering the number of CT noise-shaping order can significantly save the power of ELD compensation. Compared with a  $4^{th}$ order loop filter, a  $2^{nd}$ -order filter is easier to stabilize. To compensate for the same ELD, the UGB increase of the conventional  $4^{th}$ -order filter is significantly larger that of the  $2^{nd}$ -order SAB filter, as shown in Fig. 2.11. Assuming the loop-filters are active RC filters, the filter transfer functions with higher UGBs need OTAs with higher bandwidths, leading to more power consumption. Note the frequency response plots in Fig. 2.11 are normalized to  $f_s$ . It is more challenging to push UGB even further at a higher  $f_s$ . Consequently, DSMs of a higher  $f_s$  benefits more from lower-order CT shaping because of the reduced ELD cost.

#### 2.3.3 Feedforward Path and STF

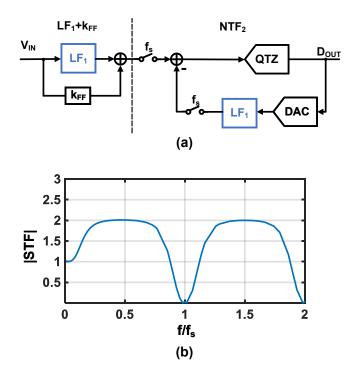

In the high-order CTDSM with multiple OTAs, the full output swing is handled by the last integrator. The resulting distortion due to the large output swing is suppressed by the prior stage gain. However, SAB has an inferior linearity because the single OTA has to handle the full swing and provides less loop gain to suppress the distortion. The non-linearity becomes an issue when the target resolution is high (SNDR >80 dB). In this work, the feedforward path with a gain of  $k_{ELD}$  and direct feedback DAC is shown in Fig. 2.12(a). Such organization forms a residual ELDC in Fig. 2.12(b). Besides the feedforward signal for ELD compensation purpose, the extra signal is feedforwarded to enhance the filter linearity. This feedforward component, with a gain of  $k_{FF}$ , will modify the STF of the CT DSM. Since STF of the NS-SAR is unity, we only need to study the STF of second-order CT outer loop. We can rearrange the signal flow model to separate the CT and DT transfer functions [Pavan et al. [2017]]. Fig. 2.13(a) shows the signal models.

After the rearrangement, it can be easily shown that the STF is

$$STF(s) = (LF_1(s) + k_{FF}) \cdot NTF_2(e^{sT_s})$$

(2.3)

Figure 2.12: (a) Original CT DSM model, (b) Equivalent residual ELD compensation model.

where  $LF_1(s)$  is the loop-filter transfer function with ELDC and  $NTF_2$  is the corresponding  $2^{nd}$ -order NTF created by the outer CT loop. STF(s) is shown in Fig. 2.13(b).  $LF_1(s)$  is low-pass. Since  $NTF_2$  creates notches at multiples of sampling frequency, STF(s) maintains the anti-aliasing feature. The cost is a peaking of 6 dB due to the direct feedforward path.

Figure 2.13: (a) Rearranged model to separate CT and DT domain, (b) STF Bode plot.

## 2.4 Circuit Implementations

#### 2.4.1 System Architecture

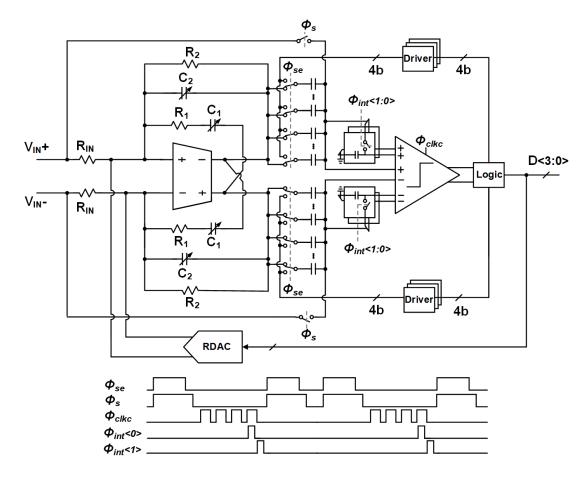

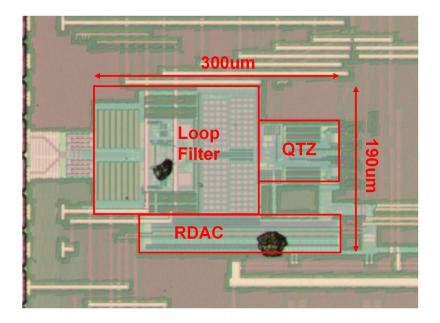

Fig. 2.14 shows the schematic of the entire DSM. The  $2^{nd}$ -order CT front-end is implemented by a SAB. To realize the desired biquad response, the OTA outputs are cross-coupled to its inputs via  $R_1$  and  $C_1$ . Negative feedback paths are formed by  $R_2$  and  $C_2$ .  $C_1$  and  $C_2$  are made by adjustable capacitor banks to further enhance DSM stability against process variations. The passive NS-SAR achieves  $2^{nd}$ -order NTF by capacitor merging and the multi-input comparator ratio. The OTA output and one-cycle delayed quantizer output

Figure 2.14: Schematic and timing diagram of proposed hybrid DSM.

are sampled onto the CDAC bottom plates. ADC input is sampled onto the CDAC top plates. kT/C noise and capacitor mismatch errors in the NS-SAR CDAC are significantly attenuated by the  $2^{nd}$ -order shaping provided by the SAB. Thus, capacitors in the CDAC can be made very small. The differential CDAC is used for both sampling and conversion. Each half is only 30 fF. The small CDAC facilitates the high-speed operations in the NS-SAR, including signal sampling, SAR conversion, and capacitor-merging based

residue integration. The power that CDAC draws from the reference is only 0.04 mW, which is 1% of the total ADC power.

#### 2.4.2 SAB Design

In the conventional CT DSM design, the number of OTAs is at least the number of orders. A number of prior works aim to reduce the number of OTAs in the loop filter because the OTAs are the main contributors to the power dissipation. The work of [Zeller et al. [2011]] introduces a cross-coupled SAB which can achieve arbitrary second-order polynomial in the numerator of its transfer function. A cross-coupled structure with a simplified RC network is used in the CT DSM [Ho et al. [2015]]. It only contains one resistor and two capacitors. Reference [Chae et al. [2013]] uses a structure with only one more resistor than that of [Ho et al. [2015]] to make a single amplifier resonator. The work of [Berti et al. [2016]] uses the same structure as that of [Chae et al. [2013]] but changes the output node to achieve complex poles in the filter transfer. Therefore, NTF with optimized zeros can be achieved. Because of the low OSR in our design, we use the same SAB as that of [Berti et al. [2016]]. In our work, the coefficients in (2.1) are:

$$\begin{cases} k_{1} = \frac{1}{R_{IN}C_{2}} \\ k_{2} = \frac{1}{R_{IN}R_{1}C_{1}C_{2}} \\ k_{3} = \frac{1}{R_{1}C_{1}} + \frac{1}{R_{2}C_{2}} - \frac{1}{R_{1}C_{2}} \\ w_{p}^{2} = \frac{1}{R_{1}R_{2}C_{1}C_{2}} \end{cases}$$

$$(2.4)$$

Assuming  $R_{IN}$  is bounded by thermal noise constraints, the resulting component values are

$$\begin{cases}

R_{2} = \frac{k_{2}}{\omega_{p}^{2}}R_{IN} \\

R_{1} = \frac{R_{2}}{1 + \left(\frac{k_{2}}{k_{1}}\right)^{2}\frac{1}{\omega_{0}^{2}}} \\

C_{1} = \frac{k_{1}}{k_{2}R_{1}} \\

C_{2} = \frac{\left(\frac{k_{2}}{k_{1}}\right)^{2}}{\left(\frac{k_{2}}{k_{1}}\right)^{2} + \omega_{p}^{2}}C_{1}

\end{cases}$$

(2.5)

$C_1$  is derived from the condition  $k_3 = 0$ . Arbitrary combinations of a second-order and a first-order path can be achieved. However, there is a lack of a zero-order path in the SAB filter transfer function. The zero-order path has to be implemented by other circuitry in the CT DSM.

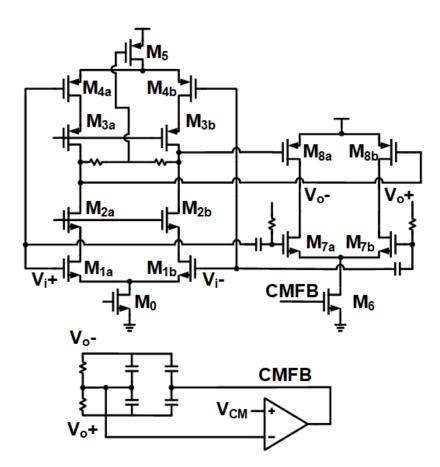

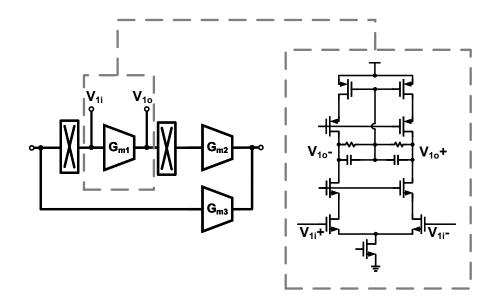

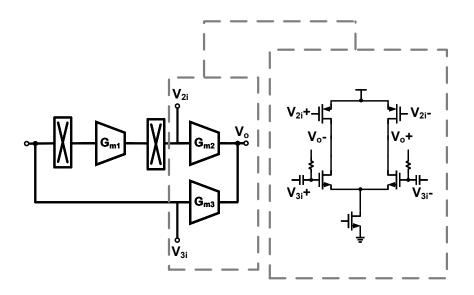

The single OTA is a key circuit block in our DSM design. Thanks to the system design of the proposed DSM, the tight BW requirement is significantly

Figure 2.15: The two-stage feedforward-compensated OTA design

relaxed to only  $1.5f_s$ . Therefore, a simple two-stage feedforward compensated OTA is adopted in the SAB filter. Fig. 2.15 shows the OTA schematic. The cascade of  $M_{1-4}$  and  $M_7$  provides a slow but high dc gain path.  $M_8$  creates a fast feedforward path between the input and the output to stabilize the OTA. The input common-mode voltage of second stage is determined by the output common-mode voltage of the first stage. Therefore, the current of the second stage tracks that of the first stage under PVT variations. The constant current

Figure 2.16: Comparator design

ratio leads to a constant  $g_m$  ratio between the first and second stage, hence a high stability. The first stage adopts the current reuse technique in [Song et al. [2013]], which nearly doubles the  $g_m/I_d$ . The first stage CMFB loop is implemented by an output resistor divider. The second stage CMFB includes an extra error amplifier. Overall, this OTA consumes 2 mW under the 1.2-V power supply, which takes 54% of the total power.

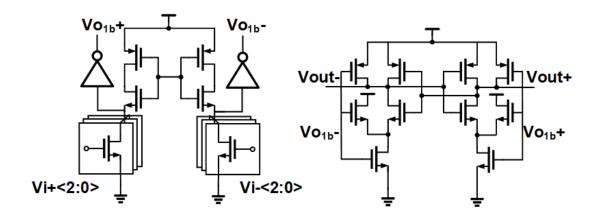

## 2.4.3 2<sup>nd</sup>-order NS-SAR Design

The passive NS-SAR is an emerging quantizer architecture. It can achieve a high resolution by the noise shaping capability while inheriting the high power efficiency from the SAR architecture. They leverage the charge sharing between capacitors to implement the integration. The passive NS-SAR variants have different ways to implement the gain block. Two methods are capacitor stacking [Lin et al. [2019]; Liu et al. [2020]] and multi-input comparator [Guo and Sun [2016]; Liu et al. [2019]]. Capacitor-stacking helps

|                         | ISSCC-13<br>Shu | ISSCC-17<br>Kim | ISSCC-19<br>Lo                   | VLSI-18<br>Liu                   | VLSI-19<br>Weng                  | VLSI-20<br>Xing                  | This<br>work                     |

|-------------------------|-----------------|-----------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|

| Order                   | 4               | 4               | 2                                | 3                                | 3                                | 3                                | 4                                |

| # OTA                   | 4               | 2               | 1                                | 1                                | 3                                | 1                                | 1                                |

| Quantizer               | Flash           | DNSQ            | 1 <sup>st</sup> -order<br>NS-SAR | 2 <sup>nd</sup> -order<br>NS-SAR | 1 <sup>st</sup> -order<br>NS-SAR | 1 <sup>st</sup> -order<br>NS-SAR | 2 <sup>nd</sup> -order<br>NS-SAR |

| Process [nm]            | 28              | 130             | 7                                | 40                               | 12                               | 28                               | 40                               |

| Fs [MHz]                | 640             | 640             | 400                              | 500                              | 832                              | 1500                             | 500                              |

| BW [MHz]                | 18              | 15              | 25                               | 12.5                             | 30                               | 50                               | 12.5                             |

| Area [mm <sup>2</sup> ] | 0.08            | 0.17            | 0.056                            | 0.029                            | 0.058                            | 0.024                            | 0.057                            |

| Power [mW]              | 3.9             | 11.4            | 3.8                              | 1.16                             | 3.2                              | 10.4                             | 3.7                              |

| DR [dB]                 | 78.1            | 82.9            | 79.4                             | 73                               | 74.5                             | 80.6                             | 82.2                             |

| SNDR [dB]               | 73.6            | 80.4            | 74                               | 70.4                             | 71.4                             | 74.4                             | 80.9                             |

| FoMs* [dB]              | 170.2           | 171.6           | 172.2                            | 170.7                            | 171                              | 171.2                            | 176.1                            |