# Impact of V th Instability of Schottkytype p-GaN Gate HEMTs on Switching Behaviors

Lu, X., Videt, A., Faramehr, S., Li, K., Marsic, V., Igic, P. & Idir, N. Author post-print (accepted) deposited by Coventry University's Repository

# Original citation & hyperlink:

Lu, X, Videt, A, Faramehr, S, Li, K, Marsic, V, Igic, P & Idir, N 2024, 'Impact of V th Instability of Schottky-type p-GaN Gate HEMTs on Switching Behaviors', IEEE Transactions on Power Electronics, vol. (In-Press), pp. (In-Press). <u>https://doi.org/10.1109/tpel.2024.3405320</u>

DOI 10.1109/tpel.2024.3405320 ISSN 0885-8993 ESSN 1941-0107

Publisher: Institute of Electrical and Electronics Engineers

© 2024 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

Copyright © and Moral Rights are retained by the author(s) and/ or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This item cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder(s). The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

This document is the author's post-print version, incorporating any revisions agreed during the peer-review process. Some differences between the published version and this version may remain and you are advised to consult the published version if you wish to cite from it.

# Impact of $V_{\text{th}}$ Instability of Schottky-type p-GaN Gate HEMTs on Switching Behaviors

Xuyang Lu, Arnaud Videt, Member, IEEE, Soroush Faramehr, Ke Li, Member, IEEE, Vlad Marsic, Petar Igic, Senior Member, IEEE, Nadir Idir, Member, IEEE,

Abstract—Schottky-type p-GaN gate Gallium Nitride High Electron Mobility Transistors (GaN-HEMTs) suffer from threshold voltage ( $V_{\rm th}$ ) instability phenomenon. Both positive and negative  $V_{\rm th}$  shifts are reported when device undertakes the voltage bias, but the impact of this  $V_{\rm th}$  instability phenomenon on device switching behaviors is less investigated. In this study, the drain-source voltage ( $V_{\rm ds}$ ) induced bidirectional  $V_{\rm th}$  shift in hard-switching condition is characterized and decoupled by an Hbridge based double-pulse test (DPT). Subsequently, the influence of  $V_{\rm th}$  shift on switching behaviors is theoretically analyzed and demonstrated through SPICE simulation and experiment, showing how a positive shifted  $V_{\rm th}$  can reduce the device turn-on commutation speed and increase the switching losses, and vice versa. The results suggest that the  $V_{\rm th}$  instability phenomenon should be considered in accurate switching modeling.

Index Terms—Power semiconductor devices, threshold voltage, switching loss, semiconductor device modeling, neural networks

### I. INTRODUCTION

**G** AN high electron mobility transistors (GaN-HEMTs) have been playing an increasing significant role in electrical energy conversion due to the low power losses and fast switching speed that is beneficial to high-efficiency and high power density converter design [1]. However, the GaN-HEMTs suffer from instability phenomena when undertaking drain to source voltage ( $V_{ds}$ ) or gate to source voltage ( $V_{gs}$ ) biases, mainly expressed as dynamic on-state resistance ( $R_{ds}^{on}$ ), current collapse and threshold voltage ( $V_{th}$ ) instability [2]–[4].

Among different gate technologies to achieving enhancement mode devices, p-GaN gate technology provides a good trade-off between cost and reliability [5]. Ohmic- and Schottky-type p-GaN gate HEMTs are two kinds of commercialized power transistors. The stabilities of Ohmic-type devices are widely reported for both  $R_{ds}^{on}$  [6]–[8] and  $V_{th}$ [9], [10]. However, their stabilities come at the cost of current driving and high gate leakage current in mA level,

Manuscript created 25 January 2024; This work was supported by the University of Lille, France and Coventry University, U.K.

Xuyang Lu is with Univ. Lille, Arts et Metiers Institute of Technology, Centrale Lille, Junia, L2EP, F-59000 Lille, France and the Centre for Clean Growth and Future Mobility (CGFM), Coventry University, CV1 2TL, Coventry, U.K. (email:xuyang.lu.etu@univ-lille.fr; lux26@coventry.ac.uk)

Arnaud Videt and Nadir Idir are with Univ. Lille, Arts et Metiers Institute of Technology, Centrale Lille, Junia, L2EP, F-59000 Lille, France. (email:arnaud.videt@univ-lille.fr; nadir.idir@univ-lille.fr)

Soroush Faramehr, Vlad Marsic and Petar Igic are with the Centre for Clean Growth and Future Mobility (CGFM), Coventry University, CV1 2TL, Coventry, U.K. (email:soroush.faramehr@coventry.ac.uk; vlad.marsic@coventry.ac.uk; petar.igic@coventry.ac.uk)

Ke Li is with the Power Electronics, Machines and Control (PEMC) group, University of Nottingham, NG7 2RD, Nottingham, U.K. (email:ke.li2@nottingham.ac.uk)

1

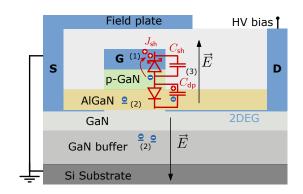

Fig. 1. Structure of Schottky-type p-GaN gate HEMTs under off-state high  $V_{\rm ds}$  voltage bias and main mechanisms of  $V_{\rm th}$  instability: (1) Holes emitted from p-GaN layer. (2) Trapped electrons in AlGaN or GaN buffer layer. (3) p-GaN potential is elevated by  $V_{\rm ds}$  due to the in series  $C_{\rm sh}$  and  $C_{\rm dp}.$

which requires relative complicated gate circuit design and causes higher driving losses [6], [8], [11]. On the other hand, Schottky-type devices exhibit voltage driving characteristics and significantly suppressed gate leakage current, resulting in convenient application and low driving losses [8]–[10]. Therefore, Schottky-type GaN-HEMTs show considerable potential in high-efficiency power converter applications.

However, the Schottky-type devices suffer from  $V_{\rm th}$  instability phenomenon that is mainly attributed to its "backto-back" diode structure in gate stack, composed by the Schottky junction (gate metal/p-GaN) and PIN junction (p-GaN/AlGaN/GaN), as shown in Fig. 1. Here, three main mechanisms could be responsible for the  $V_{\rm th}$  instability under high  $V_{\rm ds}$  bias:

- (1) The PIN junction is in reverse bias, electrons in p-GaN are accumulated at the interface of p-GaN/AlGaN. Simultaneously, holes in p-GaN are emitted to gate electrode, but these holes cannot be recovered immediately after removing the  $V_{ds}$  bias, as the Schottky junction (J<sub>sh</sub>) is in reverse bias. These unrestored holes cause hole-deficiency of p-GaN layer, leading to positive  $V_{th}$  shift [12]–[14].

- (2) Material growth defect or doping introduced acceptor-like traps in AlGaN and GaN buffer can capture electrons under high  $V_{ds}$  bias, leaving negative charged states. And these states can lead to positive  $V_{th}$  shift [15], [16].

- (3) The equivalent capacitors of the Schottky junction  $(C_{sh})$  and PIN junction  $(C_{dp})$  are in series. Here, the p-GaN potential can be elevated by a  $V_{ds}$  bias, reducing the energy barrier of the channel under the gate and resulting in a negative  $V_{th}$  shift [17], [18].

| TABLE I                   |              |                          |  |

|---------------------------|--------------|--------------------------|--|

| Two types of $V_{\sf ds}$ | BIAS RELATED | $V_{\sf th}$ instability |  |

| $V_{\sf ds}$ bias      | I-type $V_{\sf ds}$ bias                                                                                                                      | II-type $V_{ds}$ bias                                  |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| $V_{th}$ shift         | positive [13]-[16], [19]-[21]                                                                                                                 | negative [17], [18], [22], [23]                        |

| Mechanisms             | <ol> <li>Hole-deficiency in<br/>p-GaN layer [12]–[14];</li> <li>Electron trapping in<br/>AlGaN layer and GaN<br/>buffer [15], [16]</li> </ol> | (3) p-GaN potential is elevated by $V_{ds}$ [17], [18] |

| Device state           | off-state                                                                                                                                     | switching commutation                                  |

| Switching<br>waveforms | Vds I-type Id                                                                                                                                 | off on                                                 |

| +<br>E<br>Vgs<br>(a)   | $I_{L}$ $V_{ds}$ $V_{ds}$ $V_{ds}$ $V_{ds}$ $V_{gs}$ $V_{gs}$ $V_{gs}$                                                                        | switching transient<br>(II-type 1 <sub>a</sub> , bias) |

Fig. 2. Conventional double-pulse test (DPT) (a) schematic and (b) corresponding switching waveforms including the two types of  $V_{\rm ds}$  bias.

When using the device, it is crucial to consider when these mechanisms will occur, and whether the shifted  $V_{\rm th}$  can impact device turn-on and turn-off switching behaviors. The  $V_{ds}$  bias induced positive shift are reported when device is in offstate [13]-[16], [19]-[21], and they could be explained by the aforementioned mechanisms (1) and (2). However, the device also undertakes high  $V_{ds}$  bias during the switching commutation transient in hard-switching, as depicted in the waveform diagram in Table I. During the turn-on transient, the current rising stage is under high  $V_{ds}$ , and this voltage bias could cause negative  $V_{\text{th}}$  shift based on mechanism (3). This negative  $V_{\rm th}$  shift is observed during the resistance load hardswitching transient in [22], and the negative  $V_{\rm th}$  induced false turn-on phenomenon is discussed in [23]. For conciseness, the off-state  $V_{ds}$  bias is defined as I-type  $V_{ds}$  bias, and the  $V_{ds}$  bias during switching commutation is defined as II-type  $V_{ds}$  bias in this study, as summarized in Table I. Consequently, the hard switching commutation transient could be influenced by these two types of  $V_{ds}$  bias induced reverse directional  $V_{th}$  shift.

In [14], [19]–[21], the decreased  $dV_{ds}/dt$  and  $dI_d/dt$  in turnon switching transient are reported and attributed to the Itype  $V_{ds}$  bias induced positive  $V_{th}$  shift, but lacking of theoretical explanation. Moreover, the influence of II-type  $V_{ds}$ bias induced negative  $V_{th}$  shift on switching behavior are not sufficiently discussed in literature. Neglecting the  $V_{th}$  shift may lead to inaccurate evaluation of device switching losses and electromagnetic interference (EMI).

This study aims to investigate the influence of these two types of  $V_{ds}$  bias induced bidirectional  $V_{th}$  shift on device switching behaviors. The commercial GS66502B GaN-HEMTs are adopted as the research object [24]. The method-

ologies are given bellow:

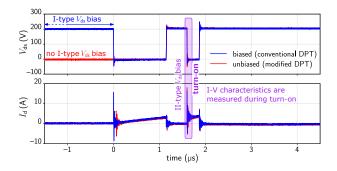

- 1) To characterize the bidirectional  $V_{\rm th}$  shift in hardswitching, the double-pulse test (DPT) is adopted. The schematics and switching waveforms of device under test (DUT) in conventional DPT are shown in Fig. 2. Both types of  $V_{\rm ds}$  bias can be observed in the typical switching waveforms of DPT in Fig. 2(b). Furthermore, an H-bridge based DPT is implemented to control the I-type  $V_{\rm ds}$  bias induced positive  $V_{\rm th}$  shift by eliminating the initial offstate  $V_{\rm ds}$  bias (before  $t_0$ ). In this way, the switching waveforms and the corresponding I-V characteristics with and without the influence of I-type  $V_{\rm ds}$  bias induced positive  $V_{\rm th}$  shift can be obtained. Moreover, both of the extracted I-V characteristics include the II-type  $V_{\rm ds}$  bias induced negative  $V_{\rm th}$  shift, since they are extracted from the hard-switching transient under high  $V_{\rm ds}$ .

- 2) To demonstrate the impact of  $V_{\rm th}$  instability on switching behaviors, the relationship between  $dV_{\rm ds}/dt$ ,  $dI_{\rm d}/dt$ , and  $V_{\rm th}$ is deducted. Afterward, the obtained I-V characteristics including  $V_{\rm th}$  instability are modelled and imported to SPICE device models. By comparing the simulation results and experiments with and without initial I-type  $V_{\rm ds}$ bias, the influence of positive  $V_{\rm th}$  shift can be verified. The impact of II-type  $V_{\rm ds}$  bias induced negative  $V_{\rm th}$  shift can be observed by comparing the simulation results under different  $V_{\rm ds}$ .

It should be clarified that a  $1 k\Omega$  turn-on gate resistor  $(R_g^{on})$  is used to slow down the turn-on switching transient for extracting the *I*-*V* characteristics, which is not a typical application case for GaN-HEMTs. The device  $V_{th}$  in this slowed hard-switching transient might be different with fast switching, due to the higher possibility of hot electrons trapping [25] and impact ionization [26]. Moreover, the dynamic  $R_{ds}^{on}$  phenomenon of the device might become serious due to this slowed down switching transient [25], [27], which could increase the conduction losses of the device. However, the objective of this work is purely to demonstrate the impact of  $V_{th}$  instability on switching behaviors. In fast switching, circuit parasitic inductance [28] and probe impedance [29] will all make it impossible to draw the conclusion if any difference observed, which will be investigated in future work.

This paper is structured as follows: Section II theoretically analyses the influence of  $V_{\text{th}}$  shift on switching behaviors. In section III, the *I-V* characteristics are constructed, where two types of  $V_{\text{ds}}$  bias induced  $V_{\text{th}}$  instability are considered. Afterward, SPICE models considering the obtained *I-V* characteristics are proposed to verify the impact of  $V_{\text{th}}$  instability on switching behaviors. The conclusion is given in section IV.

# II. IMPACT OF $V_{\rm th}$ instability on the turn-on and turn-off switching behaviors of transistors

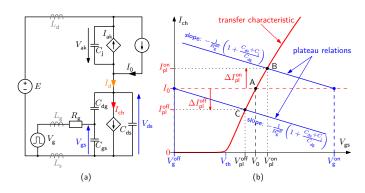

A simple model of the switching cell is depicted in Fig. 3(a) for analysing the typical hard switching transition, where the switched voltage and current are E and  $I_0$ , respectively. The diode is modelled as a voltage-controlled current source  $I_{ak}$  and a junction capacitance  $C_j$ , and the transistor is modelled as a channel current source  $I_{ch}$  and three inter-electrode

Fig. 3. Simplified analysis based on (a) switching cell model and (b) plateau voltage determination.

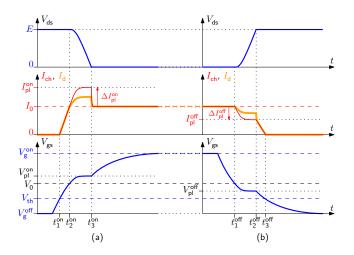

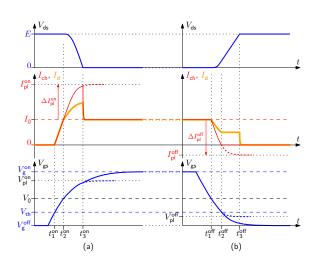

Fig. 4. Simplified commutation waveforms with Miller plateau (a) turn-on (b) turn-off.

capacitances  $C_{gs}$ ,  $C_{ds}$ , and  $C_{dg}$ . It is driven by a control voltage  $V_g$  and a gate resistance  $R_g$ . The on/off gate control voltages are named  $V_g^{off}$  and  $V_g^{on}$ , respectively.

To simplify the analysis, parasitic drain, gate, and common source inductances are neglected and the inter-electrode capacitances are assumed linear. Two situations depending on the existence of Miller plateau are analysed at first in section II-A and section II-B, which respectively corresponds to the slow and fast switching commutation cases. The expected impact of  $V_{\rm th}$  instability on switching commutations is then analysed in a more general case in section II-C. The analysis in this section notably aims at highlighting the different impact of  $V_{\rm th}$  instability between turn-on and turn-off transitions.

# A. Case I: with Miller plateau voltage

With the aforementioned hypotheses, Fig. 4 presents typical power transistor switching waveforms with Miller plateau (gate voltage  $V_{\rm pl}^{\rm on}$  and  $V_{\rm pl}^{\rm off}$  at turn-on and turn-off, respectively) occurring during the  $V_{\rm ds}$  transition. Since the commutation mostly occurs in the current saturation region of the output characteristics, it can be conveniently analysed in the  $I_{\rm ch}-V_{\rm gs}$  plane of transfer characteristics under high  $V_{\rm ds}$  shown in Fig. 3(b), where the operating point moves along the device characteristics during the commutation process:

- at turn-on, current transition starts with  $V_{\rm gs}$  rising until the  $(V_{\rm gs}, I_{\rm ch})$  operating point reaches point A  $(V_0, I_0)$ , corresponding to time  $t_2^{\rm on}$  in Fig. 4(a). Then the diode gets blocked (zero  $I_{\rm ak}$ ) and the plateau voltage is reached between  $t_2^{\rm on}$  and  $t_3^{\rm on}$ , corresponding to point B in Fig. 3(b), where  $V_{\rm ds}$  drops due to  $I_{\rm ch} > I_0$  discharging of the DUT output capacitance  $(C_{\rm ds} + C_{\rm dg})$  and charging of the diode junction capacitance  $C_{\rm j}$ . Finally the device conducts with low  $V_{\rm ds}$  and the transfer characteristic is no longer relevant.

- at turn-off, voltage transition starts around point A when the channel current gets smaller than  $I_0$ , so that the DUT output capacitance gets charged. The corresponding plateau voltage is reached at point C between  $t_1^{\text{off}}$  and  $t_2^{\text{off}}$ in Fig. 4(b). Once the diode becomes conducting at  $t_2^{\text{off}}$ , transistor current drops to zero with decreasing  $V_{\text{gs}}$ .

The current transition is obviously linked to the transfer characteristics according to the basic model:

$$I_{\rm ch} = g_{\rm m} (V_{\rm gs} - V_{\rm th}) \quad , \quad V_{\rm gs} > V_{\rm th} \tag{1} \label{eq:lambda}$$

The voltage transition however, requires more analysis focusing on the plateau voltage. At the plateau, constant  $V_{\rm gs}$  implies that  $V_{\rm dg}$  and  $V_{\rm ds}$  have the same time derivatives, such that:

$$\frac{V_{\rm g} - V_{\rm gs}}{R_{\rm g}} = -C_{\rm dg} \frac{dV_{\rm ds}}{dt} \tag{2}$$

In addition, voltage variations are linked to the charge or discharge of the output  $C_{dg}$  and  $C_{ds}$  capacitances by  $I_{ch} - I_{d}$ , where  $I_{d}$  is the drain current:

$$\frac{dV_{ds}}{dt} = \frac{I_d - I_{ch}}{C_{dg} + C_{ds}}$$

(3)

Since parasitic inductances to the DC source E are omitted,  $V_{ds}$  and  $V_{ak}$  also have the same time derivatives, which yields:

$$I_{\mathsf{d}} = I_0 - C_{\mathsf{j}} \frac{dV_{\mathsf{ak}}}{dt} = I_0 - C_{\mathsf{j}} \frac{dV_{\mathsf{ds}}}{dt} \tag{4}$$

Combining eqs. (2) to (4),  $I_{ch}$  and  $V_{gs}$  are linked by:

$$I_{\rm ch} = I_0 - \frac{V_{\rm gs} - V_{\rm g}}{R_{\rm g}} \left( 1 + \frac{C_{\rm ds} + C_{\rm j}}{C_{\rm dg}} \right)$$

(5)

This "plateau relation" is plotted as straight lines in Fig. 3(b), passing through points  $(V_{\rm g}^{\rm on}, I_0)$  at turn-on (respectively,  $(V_{\rm g}^{\rm off}, I_0)$  at turn-off) with a negative slope that depends on the gate resistance  $(R_{\rm g}^{\rm on} \text{ or } R_{\rm g}^{\rm off} \text{ respectively}$ , if different) and power devices inter-electrode capacitances. Note that  $C_{\rm j}$  equals  $C_{\rm ds} + C_{\rm dg}$ , if an identical reverse-conducting GaN-HEMT is used as the diode. Thus, the operating point at the plateau (point B  $(V_{\rm pl}^{\rm on}, I_{\rm pl}^{\rm on})$  at turn-on and C  $(V_{\rm pl}^{\rm off}, I_{\rm pl}^{\rm off})$  at turn-off) is obtained at the intersection of the the plateau relation with the DUT transfer characteristics.

Furthermore, the difference  $\Delta I_{ch}$  between channel and load currents is a key parameter for voltage transition speed since (3) and (4) yield:

$$\frac{dV_{\rm ds}}{dt} = \frac{I_0 - I_{\rm ch}}{C_{\rm dg} + C_{\rm ds} + C_{\rm j}} = \frac{-\Delta I_{\rm ch}}{C_{\rm dg} + C_{\rm ds} + C_{\rm j}} \tag{6}$$

Fig. 5.  $I_{ch}-V_{gs}$  significant points for device commutation.

Its value at points B and C is represented in Fig. 3(b) as  $\Delta I_{\rm pl}^{\rm on}$  and  $\Delta I_{\rm pl}^{\rm off}$ , respectively. Calculating the intersection of the plateau relation line with the transfer characteristic using eq. (1), the voltage transition at the plateau can then be expressed as a function of  $V_{\rm th}$ :

$$-\frac{dV_{\rm ds}}{dt} = \frac{g_{\rm m}(V_{\rm g} - V_{\rm th}) - I_{\rm 0}}{g_{\rm m}R_{\rm g}C_{\rm dg} + C_{\rm ds} + C_{\rm dg} + C_{\rm j}} = f(V_{\rm th}) \qquad (7)$$

This equation shows how the  $V_{\rm th}$  instability influences the voltage transition. Interestingly, it is easily verified that turn-on transition gets slower due to negative  $\frac{df}{dV_{\rm th}}$ .

Finally, drain current is related to channel current from eqs. (4) and (6) by:

$$\frac{I_{\rm d} - I_{\rm 0}}{\Delta I_{\rm ch}} = \frac{C_{\rm j}}{C_{\rm dg} + C_{\rm ds} + C_{\rm j}} \tag{8}$$

which equals 1/2 if the diode is actually an identical GaN-HEMT (still considering linear capacitances). For this reason, the  $I_d$  curve in Fig. 4 has half the deviation of  $I_{ch}$  to  $I_0$  during the voltage transitions.

### B. Case II: without Miller plateau voltage

The preceding analysis should be completed by considering that plateau voltages may actually not have time to be attained, due to the fast switching speed of GaN-HEMTs [30]. Indeed, with high  $C_{ds}/C_{dg}$  ratio and small  $R_g$  values, the slopes of the plateau relation lines in Fig. 3(b) increase so that the resulting crossing points move away as shown in Fig. 5.

At turn-on, both current and voltage transitions are similar to the previous section, except that the "target"  $\Delta I_{pl}^{on}$  is now much larger at point B. Consequently, as  $I_{ch}$  keeps increasing a lot beyond point A,  $V_{ds}$  voltage falls more and more rapidly and eventually reaches its final on-state value before the pseudo steady state is reached. Thus, point B is not fully attained and the waveforms in Fig. 6(a) do not have time to stabilize in the  $[t_2^{an}, t_3^{on}]$  interval (dotted lines after  $t_3^{on}$  show how they would have stabilized otherwise).

The turn-off transition is more impacted by the new slopes in Fig. 5, because the crossing point with the transfer characteristics is now at point D with zero channel current. Should

Fig. 6. Commutation waveforms without Miller plateau (a) turn-on (b) turn-off.

the transconductance curve remain straight below  $V_{\rm th}$  gate voltage, extending to negative  $I_{ch}$ , then the "target" pseudo steady state for the voltage transition would be at point C with a large negative  $\Delta I_{pl}^{off}$ . Consequently, when voltage transition starts, the channel current rapidly drops to zero in Fig. 6(b). Thus, current transition is already finished in the channel at time  $t_2^{\text{off}}$  in Fig. 6(b) (dotted lines after  $t_2^{\text{off}}$  show how  $V_{gs}$  and  $I_{ch}$  would stabilize if current could become negative at point C). However,  $t_2^{\text{off}}$  is only the beginning of the voltage transition: afterwards drain voltage rises up to Ein the  $[t_2^{\text{off}}, t_3^{\text{off}}]$  interval, under  $\Delta I_{ch} = -I_0$  in eq. (6). Thus, the drain current alone is merely charging the DUT output capacitance, resulting in a turn-off voltage rising speed that only depends on the load current  $I_0$ . Similar behavior has been reported for various transistor technologies [31], [32], usually associated with low current switching. It suggests that  $V_{\rm th}$  instability would not influence the turn-off commutation once the channel stops conducting.

# C. Influence of $V_{th}$ instability on switching behaviors

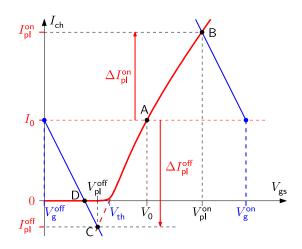

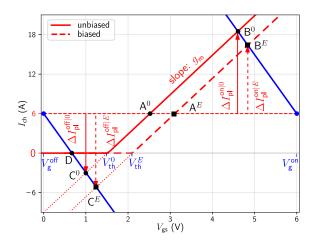

The analysis from Figs. 5 and 6 can be combined with the Itype  $V_{ds}$  bias induced positive  $V_{th}$  shift to illustrate its effect on switching waveforms. Fig. 7 presents simple piecewise linear transfer characteristics defined by device  $V_{th}$  and  $g_m$  according to eq. (1). Two curves are considered:

- **unbiased** means that the DUT is not affected by the initial I-type  $V_{ds}$  bias. The corresponding curve (solid line) would be obtained when the device has zero initial  $V_{ds}$  bias. Thus, the corresponding threshold voltage are identified with a "0" superscript:  $V_{th}^0$ .

- **biased** means that the DUT incurred initial I-type  $V_{ds}$  bias induced positive  $V_{th}$  shift, by voltage E before  $t_0$  in the conventional DPT in Fig. 2. The corresponding curve (dashed line in Fig. 7) is determined by  $V_{th}^E$ , including the E bias superscript indication.

In addition, the plateau relation lines are also plotted, similar to Fig. 5, and the crossing points  $A^0$ ,  $B^0$ ,  $C^0$  for the unbiased curve and  $A^E$ ,  $B^E$ ,  $C^E$  for the biased case are defined.

Fig. 7. Transfer characteristics in unbiased and biased modes

TABLE IIParameter values for Fig. 7

| $V_{\rm th}^0=1.5{\rm V}$ | $V_{\rm g}^{\rm on}=6{\rm V}$  | $I_0=6\mathrm{A}$   | $R_{\rm g}=15\Omega$      | $C_{\rm j}=20.3{\rm pF}$ |

|---------------------------|--------------------------------|---------------------|---------------------------|--------------------------|

| $V^E_{\rm th}=2.1{\rm V}$ | $V_{\rm g}^{\rm off}=0{\rm V}$ | $g_{m}=6\mathrm{S}$ | $C_{dg} = 0.3\mathrm{pF}$ | $C_{ds} = 20\mathrm{pF}$ |

The parameters used for Fig. 7 are based on the GaN Systems device GS66502B, where the unbiased  $V_{\text{th}}^0$  is approximated from the datasheet transfer characteristics, while the biased  $V_{\text{th}}^{\text{E}}$  is set in Table II. And the positive shifted value is consistent with orders of magnitude to our measurement and literature [13]–[16], [20], [21]. For plotting the plateau relation lines, Table II also indicates the on/off gate voltages, switched current, gate resistance (same for on and off) and device capacitance values that are approximated from the datasheet at 200 V drain voltage.

At turn-on, Fig. 7 shows that current transition should be slower in biased conditions because the  $V_{\rm gs}$  rising span from  $(V_{\rm th}^E, 0)$  to point  $A^E$  is closer to its final value  $V_{\rm g}^{\rm on}$ , compared with the unbiased case from  $(V_{\rm th}^0, 0)$  to  $A^0$ . This means the current rising stage in biased condition is longer due to the RC charging characteristics of  $V_{\rm gs}$ . Afterwards, the voltage transition is linked to  $\Delta I_{\rm ch}$  as mentioned in eq. (6). Fig. 7 reveals that its "target" values in biased  $(\Delta I_{\rm pl}^{\rm on|E})$  and unbiased  $(\Delta I_{\rm pl}^{\rm on|0})$  conditions are different, as  $V_{\rm th}$  instability shifting the transfer characteristics. Thus,  $\Delta I_{\rm ch}$  rises slower in biased state (from  $A^E$  towards  $B^E$ ) than in unbiased one (from  $A^0$ towards  $B^0$ ), resulting in slower voltage transition as well. Importantly, it can be expected that slower transitions in biased case increase switching power losses.

At turn-off, the previous section shows that voltage rise is first associated with a fast current transition in  $I_{\rm ch}$  that quickly reaches zero when the operating point moves from point A towards point C in Fig. 5, bifurcating at  $(V_{\rm th}, 0)$  towards point D. Consequently, this transition is much less impacted by  $V_{\rm th}$  shift as it was at turn-on. Afterwards, drain voltage keeps rising under the effect of drain current charging the DUT output capacitance, as discussed in Fig. 6(b). Since this transition is then independent on the transfer characteristics, it might be concluded that the  $V_{\rm th}$  shift does not influence turn-off

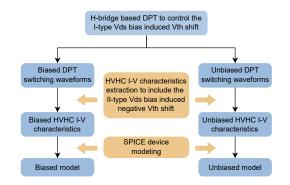

Fig. 8. The process of HVHC I-V characterization and modeling to decouple the two types of  $V_{ds}$  bias induced  $V_{th}$  instability.

Fig. 9. Schematic of the H-bridge based DPT.

switching, which is subjected to low power losses anyway.

Overall, the I-type  $V_{\rm ds}$  bias induced positive  $V_{\rm th}$  shift can slow down the turn-on switching commutation by decreasing the  $dV_{\rm ds}/dt$  and  $dI_{\rm d}/dt$ , while the turn-off switching transition is not influenced. Moreover, the device  $V_{\rm th}$  is also depend on the II-type  $V_{\rm ds}$  bias in hard-switching. And only the transfer characteristics under high  $V_{\rm ds}$  can be used to predict the hardswitching transition, as the switching commutation mainly occurs in high  $V_{\rm ds}$  saturation region.

To verify the two types of  $V_{ds}$  bias induced  $V_{th}$  instability on device switching behaviors, a method to obtain and modeling the transfer characteristics under different high  $V_{ds}$  is required.

# III. HVHC *I*–*V* CHARACTERIZATION AND MODELING USING THE H-BRIDGE BASED DOUBLE PULSE TEST

The conventional DPT based high-voltage and high-current (HVHC) I-V (equivalent to the transfer characteristics under different high  $V_{\rm ds}$ ) characterization methods are reported for SiC-MOSFETs in [28], [33]. The HVHC I-V characteristics can include the II-type  $V_{\rm ds}$  bias related negative  $V_{\rm th}$ , because they are extracted from hard-switching transition in different high  $V_{\rm ds}$ . However, the HVHC I-V characterization method in [28], [33] is undesirable for GaN-HEMTs, since the initial I-type  $V_{\rm ds}$  bias in conventional DPT cannot be eliminated as shown in Fig. 2(b), and its impact on the I-V characteristics will be coupled with II-type  $V_{\rm ds}$  bias. To reveal the bidirectional  $V_{\rm th}$  shift and their impact on switching behaviors, theses two types of  $V_{\rm ds}$  bias in conventional DPT should be decoupled. The whole HVHC I-V characterization and modeling process of this section is shown in Fig. 8.

Fig. 10. Biased and unbiased switching waveforms from H-bridge based DPT.

Fig. 11. The HVHC output characteristics can be obtained by interpolating (a) a set of slowed down turn-on switching waveforms with different load current (b) extracted HVHC output characteristics when  $V_{\rm gs} = 1.8$  V.

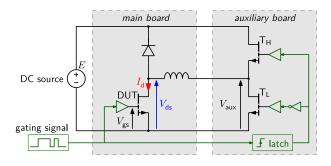

# A. H-bridge based I-V characterization

To decouple these two types of  $V_{ds}$  bias induced  $V_{th}$  instability, the existence of I-type  $V_{ds}$  bias should be controlled. Hence, an H-bridge based DPT circuit is adopted, which is proposed in our previous research [34]. The schematic is shown in Fig. 9. The modified H-bridge DPT consists of two parts. The main board is a normal half-bridge for conventional DPT. The auxiliary board is used to control the I-type  $V_{ds}$ bias of DUT, where  $T_{\rm H}$  and  $T_{\rm L}$  operate complementarily. Two modes of DPT can be realized in this H-bridge. In unbiased mode, initially, the  $T_{\rm H}$  is off and the  $V_{\rm ds}$  of DUT is zero as  $V_{\text{aux}}$ . In this way, the initial  $V_{\text{ds}}$  bias before starting the DPT can be removed. After  $T_{\rm H}$  is turned on, the state of  $T_{\rm H}$ and  $T_1$  will be latched, afterward the H-bridge behaves as the conventional DPT. In the biased mode, the conventional DPT can be directly achieved by tuning on and locking the  $T_{\rm H}$ in advance. This H-bridge enables to control the DC source E caused I-type  $V_{ds}$  bias in conventional DPT. Therefore, the DPT with and without the influence of I-type  $V_{ds}$  bias can be implemented, labeled as biased and unbiased DPT, respectively, in this paper. The switching waveforms of biased and unbiased DPT are displayed in Fig. 10.

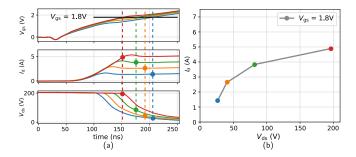

The HVHC output characteristics can be obtained by interpolating a set of turn-on switching waveforms from the H-bridge based DPT with various  $V_{\rm gs}$  values, where the  $V_{\rm ds}$ drops from 200 V to 0 V and  $I_{\rm d}$  increases from 0 A to various values, as shown in Fig. 11(a). For example, when  $V_{\rm gs}$  is 1.8 V, the corresponding  $I_{\rm d}$  and  $V_{\rm ds}$  can be plotted as one curve of HVHC output characteristics, as shown in Fig. 11(b). By repeating this interpolation over a range of  $V_{\rm gs}$ , the full HVHC output characteristics can be obtained. More delicate

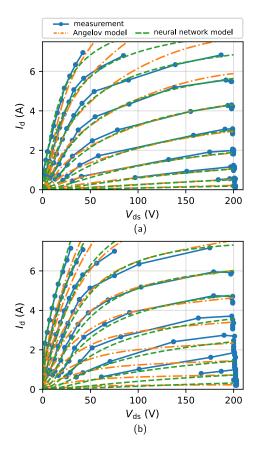

Fig. 12. The HVHC *I*–*V* characteristics with (biased) and without (unbiased) the influence of I-type  $V_{\rm ds}$  bias (a) output characteristics and (b) transfer characteristics under different  $V_{\rm ds}$ . Here, the transfer characteristics are obtained by interpolating at different  $V_{\rm ds}$  on the output characteristics. The I-type  $V_{\rm ds}$  bias induced positive  $V_{\rm th}$  shift can be obtained by comparing the dashed and solid curves. The II-type  $V_{\rm ds}$  bias induced negative  $V_{\rm th}$  shift are shown with  $V_{\rm ds}$  increasing from 50 V to 200 V in both types of curves.

curves can be obtained if the numbers of the waveform at various currents are increased in Fig. 11(a). In the HVHC output characteristics, the complete relationship between  $V_{\rm gs}$ ,  $V_{\rm ds}$  and  $I_{\rm d}$  in device switching commutation can be obtained. And this method is reported in our previous work [35]. Though the turn-on switching waveforms are slowed down by a large  $R_{\rm g}^{\rm on}$ , the voltage drop on device internal resistance and the displacement current through inter-electrode capacitance of device are still compensated to get the channel current  $I_{\rm ch}$  and voltage drop on  $C_{\rm gs}$ . And the propagation delay between voltage and current probes are de-skewed based on the power-resistor based method in [36]. One minute of initial I-type  $V_{\rm ds}$  bias is applied in biased mode DPT to produce a saturated positive  $V_{\rm th}$  shift [15], [22], [37], as the  $V_{\rm ds}$  induced  $V_{\rm th}$  instability is time dependent.

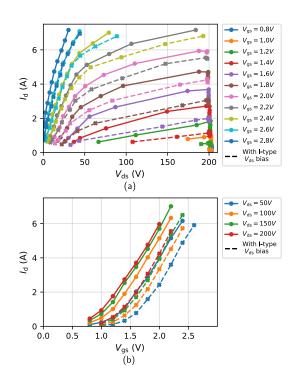

The HVHC output characteristics of GS66502B are shown in Fig. 12(a). These characteristics are depicted as biased and unbiased HVHC output characteristics, represented by dashed and solid lines, respectively. This differentiation depends on whether the HVHC output characteristics are extracted from the biased mode DPT switching waveforms. Moreover, the transfer characteristics at different high  $V_{ds}$  can be obtained by interpolating at different  $V_{ds}$  values on the HVHC output characteristics as shown in Fig. 12(b). In this way, these two types of  $V_{ds}$  bias induced bidirectionally  $V_{th}$  shift can be clearly observed.

By comparing the solid and dashed curves in transfer characteristics, the I-type  $V_{ds}$  bias induced positive  $V_{th}$  shift

Fig. 13. Measured (a) turn-on switching waveforms under different II-type  $V_{\sf ds}$  bias from unbiased mode DPT and (b) negative  $V_{\sf th}$  shift with the increase of II-type  $V_{\sf ds}$  bias.

can be observed, where the 0.5 V of  $\Delta V_{\text{th}}$  is in the same order of magnitude as the literature [15], [37]. Moreover, all the transfer characteristics shift negatively with  $V_{\text{ds}}$  increasing from 50 V to 200 V, which could be related to the II-type  $V_{\text{ds}}$  bias during turn-on transient. And the mechanism may be attributed to the elevated potential of p-GaN layer under high  $V_{\text{ds}}$  bias as discussed in [17], [18]. Note that this negative transfer characteristics shift are also reported for power SiC-MOSFETs [28], [38], but they are referred to the drain induced barrier lowering (DIBL) effect of vertical power MOSFETs.

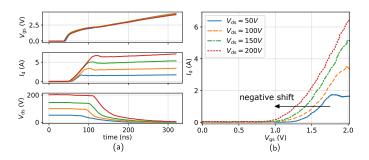

To further investigate this negative  $V_{\rm th}$  shift, the unbiased mode DPT is implemented under different DC voltage, where the initial I-type  $V_{\rm ds}$  bias is eliminated. And the turn-on time of DUT is set to 1 us to exclude the influence of varying  $V_{\rm gs}$  bias time. The turn-on switching waveforms are shown in Fig. 13(a). It is clear that  $I_{\rm d}$  starts to rise earlier and faster under higher II-type  $V_{\rm ds}$  bias. Furthermore, the transfer characteristics under different  $V_{\rm ds}$  are plotted using the  $I_{\rm d}$ and  $V_{\rm gs}$  switching waveforms in Fig. 13(a), as shown in Fig. 13(b). Noted that the influence of parasitic parameters are compensated, same as the HVHC I-V characteristics, to ensure that the  $I_{\rm d}$  and  $V_{\rm gs}$  can represent the channel current and voltage potential on the  $C_{\rm gs}$ . Around -0.4 V of  $\Delta V_{\rm th}$  can be observed with  $V_{\rm ds}$  increase from 50 V to 200 V, which is agree with the negative  $\Delta V_{\rm th}$  in Fig. 12(b).

In this way, the  $V_{\rm th}$  instability induced by the two types of  $V_{\rm ds}$  bias are characterised. Note that both the biased and unbiased HVHC output characteristics in Fig. 12(a) include IItype  $V_{\rm ds}$  bias induced negative  $V_{\rm th}$ , since they both considers the complete relation between  $V_{\rm ds}$ ,  $V_{\rm gs}$  and  $I_{\rm d}$  during high voltage hard-switching. While only the biased HVHC output characteristics include the I-type  $V_{\rm ds}$  bias induced positive  $V_{\rm th}$ shift. Theses biased and unbiased HVHC output characteristics can be further modeled to validate the impact of  $V_{\rm th}$  instability on switching behaviors.

# B. I-V characteristics modeling for SPICE behavior models

Behavior models considering the obtained HVHC I-V characteristics are constructed in this part. In conventional behavior modeling, empirical equations are adopted to fit measured I-V characteristics [28], [39], [40]. However, proposing appropriate equations and searching global solution for tens of optimized parameters are time-consuming and complicated

Fig. 14. Comparison of HVHC I-V characteristics between experiment measurement and constructed models (neural network and Angelov models) (a) with and (b) without the influence of I-type  $V_{ds}$  bias.

in non-linear regression. More importantly, most of the I-V characteristics models are proposed for HEMTs and MOS-FETs, assuming  $I_d$  becoming saturated after  $V_{ds}$  above 5 V or 10 V [24], [41], like manufacturer model [24], which means they do not include II-type  $V_{ds}$  bias induced  $V_{th}$  instability. But the power transistor mainly operates under hundred voltage of  $V_{ds}$  and the switching commutation happen in high  $V_{ds}$  region, such models may not be enough to accurately predict device switching behavior. Therefore, a neural network-based HVHC I-V characteristics model is proposed in this paper, where the dedicated equations are not required and the training process is faster and more convenient compared to the conventional non-linear regression [33], [42].

The multilayer perceptron (MLP) neural network is adopted to model the HVHC I-V characteristics due to the compatibility of SPICE environment. A 3-layer neural network with 2 neurons in the input layer, 6 neurons in the hidden layer, and 1 neuron output layer (for  $I_d$ ) is employed, as expressed:

$$I_{d} = \tanh(\mathbf{I} \times \mathbf{W}_{1}^{\mathsf{T}} + \mathbf{B}_{1}^{\mathsf{T}}) \times \mathbf{W}_{2} + \mathsf{b}$$

(9)

Where the  $I = (V_{gs} V_{ds})$  is the input vector, b is a bias

TABLE III

$dV_{ds}/dt$ ,  $dI_{d}/dt$  and switching losses during turn-on transition

FROM MEASUREMENT AND MODEL SIMULATION RESULTS IN FIG. 15

| Turn-on switching waveforms   | ${dV_{\sf ds}/dt} \ ({ m V/ns})$ | ${dI_{\sf d}/dt} \ ({ m A/us})$ | $egin{array}{c} E_{on}\ (\mathrm{uJ}) \end{array}$ |

|-------------------------------|----------------------------------|---------------------------------|----------------------------------------------------|

| Measurement result biased     | -1.40                            | 63.64                           | 142.88                                             |

| Measurement result unbiased   | -1.75                            | 70.45                           | 126.86                                             |

| Neural network model biased   | -1.24                            | 65.02                           | 159.71                                             |

| Neural network model unbiased | -1.34                            | 71.20                           | 141.15                                             |

| Angelov model biased          | -1.15                            | 73.54                           | 139.36                                             |

| Angelov model unbiased        | -1.12                            | 74.53                           | 145.74                                             |

| Manufacture model             | -2.38                            | 78.65                           | 114.49                                             |

|                               |                                  |                                 |                                                    |

parameter, and other parameter matrices are display as follows:

$$\mathbf{W_1} = \begin{pmatrix} w_{11} & w_{21} \\ w_{12} & w_{22} \\ \vdots & \vdots \\ w_{16} & w_{26} \end{pmatrix}, \mathbf{B_1} = \begin{pmatrix} b_1 \\ b_2 \\ \vdots \\ b_6 \end{pmatrix}, \mathbf{W_2} = \begin{pmatrix} w_{31} \\ w_{32} \\ \vdots \\ w_{36} \end{pmatrix}$$

(10)

As the above naming rules, the biased and unbiased neural network-based HVHC I-V characteristics models are created by feeding the data of measured turn-on switching waveforms from biased and unbiased DPT. For cross reference, the I-V characteristics equations from high voltage adapted Angelov model in [43] are used to fit the measured HVHC I-V characteristics to get the corresponding Angelov models.

The HVHC I-V characteristics models constructed by neural network and Angelov equations are compared to the measurement results in Fig. 14. All models show good agreement with measured output characteristics. However, the Angelov model exhibits undesirable fitting result in high current region in biased conditions and this might be attributed to the limitation of model itself.

The device SPICE behavior models can be achieved by modifying the manufacturer model of GS66502B [24], in which the original I-V characteristics equations are replaced by our constructed HVHC I-V characteristics models in Fig. 14. As for other parts, such as, C-V characteristics, parasitics inductance inside the package remain unchanged, and the target is to exclude the influence of these parameters. This is why the SPICE model is adopted to demonstrate the influence of  $V_{\rm th}$  instability on device switching behavior, as it is challenging to decouple the influence of I-V and C-Vcharacteristics in experiments. Since the switching transition is also dependent on the device C-V characteristics, and the C-V characteristics may be also impacted by the  $V_{\rm ds}$  biasinduced trapping effect in GaN buffer layer [44].

# C. Model validation and switching behavior prediction

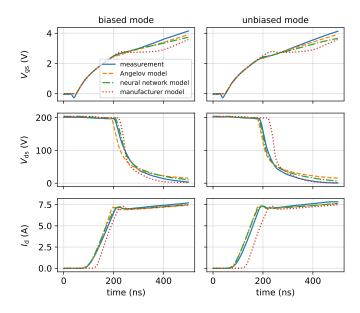

All SPICE behavior models are applied to the DPT simulation, with same schematic in Fig. 2(a), to replace the freewheeling diode and DUT. Their turn-on simulation waveforms are compared to the biased and unbiased DPT measurement result at  $I_d = 7$  A, which are depicted in Fig. 15. The result

Fig. 15. Comparison of turn-on switching waveforms (with  $1 k\Omega R_g^{on}$ ) from biased and unbiased DPT with simulation results of biased and unbiased SPICE models.

TABLE IV Comparison of the Absolute difference of  $dV_{ds}/dt$ ,  $dI_d/dt$  and  $E_{on}$ between models and measurement results in Table III

| Model-Measurement             | ${dV_{\sf ds}/dt} \ ({ m V/ns})$ | ${dI_{\sf d}/dt} \ ({ m A/us})$ | $egin{array}{c} E_{on} \ (\mathrm{uJ}) \end{array}$ |

|-------------------------------|----------------------------------|---------------------------------|-----------------------------------------------------|

| Neural network model biased   | 0.16                             | 1.38                            | 16.83                                               |

| Neural network model unbiased | 0.41                             | 0.75                            | 14.29                                               |

| Angelov model biased          | 0.25                             | 9.90                            | 3.52                                                |

| Angelov model unbiased        | 0.63                             | 4.08                            | 18.88                                               |

| Manufacture model biased      | 0.98                             | 15.01                           | 28.39                                               |

| Manufacture model unbiased    | 0.63                             | 8.20                            | 12.37                                               |

|                               |                                  |                                 |                                                     |

of manufacturer model is compared as a reference. Note that when using the split output gate driver (like LM5114) to drive GaN devices, the influence of output capacitance from gate driver MOSFETs should be considered to accurately model the switching waveform, especially in slow switching condition, the details are shown in our previous work [45]. As shown in Fig. 15, Miller plateau appears in  $V_{gs}$  waveforms as the large  $R_{g}^{on}$  is used, and it is tilted from the results of measurement and simulation models that the HVHC I-V is considered. This tilted Miller plateau could be attributed to the II-type  $V_{ds}$ bias induced negative  $V_{\rm th}$  shift. Because transfer characteristics shift positively with  $V_{ds}^{ii}$  decreasing as shown in Fig 12(b), thus, a higher  $V_{gs}$  is required to maintain the same  $I_d$  in  $V_{ds}$ dropping stage. This can also be observed from Fig 3(b), where shifted transfer characteristic would pull point B farther to the right, increasing plateau voltage. By contrast, flat Miller plateau is exhibited by the manufacturer model, as the transfer characteristics keep constant under different  $V_{\rm ds}$  bias, meaning the II-type  $V_{ds}$  bias induced  $V_{th}$  instability is overlooked. This tilted Miller plateau is also observed in [38] for SiC-MOSFETs and in [14] for GaN-HEMTs. However, in Fig 15,

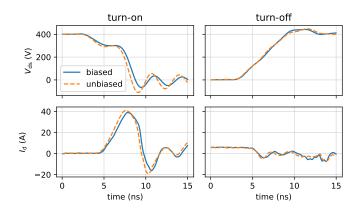

Fig. 16. Comparison of turn-on and turn-off simulation switching waveforms of biased and unbiased neural network models. In turn-on transient, the  $dV_{ds}/dt$ ,  $dI_d/dt$  and current overshoot of biased model are decreased.

both neural network and Angelov model show slow voltage dropping speed when  $V_{ds}$  is under aroud 30 V, especially in unbiased models, which may be attributed to the undesirable fitting in low  $V_{ds}$  Ohmic region in HVHC I-V characteristics.

In addition, the  $dV_{ds}/dt$ ,  $dI_d/dt$  and turn-on switching losses  $(E_{on})$  of simulation and experiment waveforms in Fig. 15 are calculated in Table III. By comparing experimental results, the absolutely value of  $dV_{ds}/dt$  and  $dI_d/dt$  in biased mode are reduced, leading to 12.6 % higher switching losses, which is attributed to the I-type  $V_{\rm ds}$  induced positive  $V_{\rm th}$  shift and in accordance with the analysis in section II-C. In simulation results, the neural network models can reproduce this trend, and the switching losses are increased 13.2% from unbiased to biased model. However, the Angelov models could not show this phenomenon effectively, which could be ascribed to the undesirable fitting results in the high  $I_d$  and high  $V_{ds}$  region of HVHC I-V characteristics in Fig 14(a). To further evaluate the performance of proposed models, the absolute difference of  $dV_{ds}/dt$ ,  $dI_d/dt$  and  $E_{on}$  between simulation and experiment results in Table III are compared in Table IV. The neural network models show the best agreement with measurement results in terms of  $dV_{ds}/dt$  and  $dI_d/dt$ . This also shows the potential advantage of neural network in non-linear fitting.

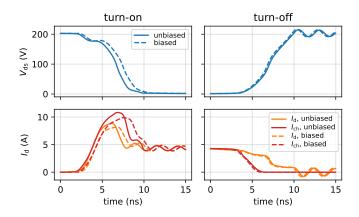

The neural network models are employed to further verify the impact of  $V_{\rm th}$  shift on device switching waveforms in fast switching conditions. In the simulation,  $20 \Omega$  of  $R_{g}^{on}$  and  $2\,\Omega$  of  $R_{\rm g}^{\rm off}$  are adopted, and the  $10\,{\rm nH}$  of  $L_{\rm g}$  and  $6\,{\rm nH}$  of  $L_{\rm d}$  are included. The simulation waveforms of  $V_{\rm ds},~I_{\rm d}$  and  $I_{ch}$  are shown in Fig 16. At turn-on, the absolute value of  $dV_{ds}/dt$ ,  $dI_{d}/dt$ , and current overshoot towards  $\Delta I_{pl}^{on}$  are larger in unbiased mode, as analysed in Fig 7. At turn-off, the commutation waveforms are almost identical in these two models. This is because  $I_{ch}$  drops to zero when  $V_{ds}$  starts to increase, meaning the current transition is finished in the channel, afterward, the  $V_{ds}$  increasing process is independent of transfer characteristics. These results verify the hypothesis proposed in section II-C that I-type of  $V_{ds}$  induced positive  $V_{th}$ shift can slow down the turn-on commutation speed, while the turn-off process is not affected.

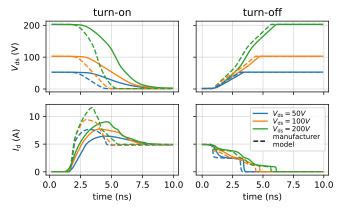

Fig. 17. Turn-on and turn-off simulation waveforms at different  $V_{\rm ds}$  from unbiased neural network models. In turn-on transient,  $dI_{\rm d}/dt$  and current overshoot of neural-network model are increased with  $V_{\rm ds}$  voltage increasing.

waveforms, the unbiased neural network model is utilized for DPT simulation at different DC voltage, and the manufacture model is used as a reference. To clearly show the impact, the parasitic inductances are neglected. The simulation results are depicted in Fig 17. At turn-on, the  $I_d$  rises earlier and faster under higher  $V_{ds}$  bias, due to the negatively shifted transfer characteristics induced by the higher II-type  $V_{ds}$  bias. This trend is also observed in the measured turn-on switching waveforms in Fig 13(a). By contrast, the waveform of  $I_d$  from manufacturer model remains unchanged at different  $V_{ds}$  bias, due to its constant transfer characteristics. At turn-off, the  $I_d$  commutation speed is not affected by the shifted transfer characteristics, because  $I_{ch}$  drops to zero quickly as mentioned above. Both of the specific switching behaviors in turn-on and turn-off agree with the analysis in section II-C.

### D. Experimental verification in fast switching commutation

The impact of  $V_{th}$  instability on device hard switching commutation is demonstrated by modeling and simulation above. And the decreased  $dV_{ds}/dt$  and  $dI_d/dt$  from slow experimental waveforms are quantified in Table III. However, the existence of this impact in a more practical switching condition deserve to be verified. Hence, the H-bridge DPT is implemented under 400 V DC bus voltage with  $20 \Omega$  of  $R_{g}^{on}$  and  $2 \Omega$  of  $R_{g}^{off}$ that is a typical application condition for the  $650 \,\mathrm{V}$  power transistors. The turn-on and turn-off switching transition in biased and unbiased DPT are shown in Fig 18. The  $V_{ds}$ and  $I_{\rm d}$  in biased mode show the decreased  $dV_{\rm ds}/dt$  (10.8%) and  ${}^{dI_{d}/dt}$  (13.2%), leading to a 13.4% increased  $E_{on}$ . And the switching waveforms show less peak overshoot compared to the unbiased mode in turn-on transition. While, the turnoff commutation does not show this variation. All of these experimental results show the consistency with the theoretical analysis and simulation. Similar effect in turn-on switching waveforms is also reported in [20].

# IV. CONCLUSION

In this work, we investigated two types of  $V_{ds}$  bias induced  $V_{th}$  instability in Schottky-type p-GaN gate HEMTs using

9

To evaluate the impact of II-type  $V_{\rm ds}$  bias on switching  $~V_{\rm th}$

Fig. 18. Experimental turn-on and turn-off switching waveforms from the H-bridge based DPT in fast switching condition with 400 V of  $V_{\rm DC}$ .

the switching waveforms from the H-bridge based DPT. The results indicated that the off-state  $V_{ds}$  bias before turn-on commutation (I-type  $V_{ds}$  bias) can cause positive  $V_{th}$  shift, while the  $V_{ds}$  bias during turn-on transient (II-type  $V_{ds}$  bias) can lead to negative  $V_{\rm th}$  shift. Based on the switching transient analysis, the positive  $V_{\rm th}$  shift could reduce the turn-on  $dV_{\rm ds}/dt$ ,  $dI_{\rm d}/dt$ , increasing the switching losses. The reason is that the  $V_{\rm gs}$  rising span from  $V_{\rm th}$  to the plateau voltage is closer to  $V_{\rm g}^{\rm on}$ after positive  $V_{\rm th}$  shift. As a result, the current commutation becomes longer due to the RC charging characteristics of  $V_{\rm gs}$ . Moreover, the change in channel current  $\Delta I_{\rm ch}$  becomes smaller, which is positively related to  $dV_{ds}/dt$  based on our deduction in section II. Meanwhile, the turn-off transition remains essentially unchanged because the channel current drops to zero rapidly before the above mechanisms occur. The influence of negative  $V_{\rm th}$  follows the same principle. Moreover, the tilted Miller plateau of GaN-HEMTs in slow switching condition can be attributed to the II-type  $V_{ds}$  bias induced negative  $V_{\rm th}$  shift. The results suggest that the HVHC I-V characteristics that include the  $V_{\rm th}$  instability phenomenon are indispensable for accurate turn-on switching behavior modeling and losses estimation.

The actual I-V characteristics are influenced by various factors, including voltage biases, hot electrons, temperatures and etc., when the device operates in real power converters. Consequently, the characterization method to obtain the multiparameter coupled I-V characteristics is essential, which would improve the accuracy for switching behaviors modeling for GaN-HEMTs.

#### REFERENCES

- T. Liu, C. Chen, K. Xu, Y. Zhang, and Y. Kang, "GaN-Based Megahertz Single-Phase Inverter With a Hybrid TCM Control Method for High Efficiency and High-Power Density," *IEEE Transactions on Power Electronics*, vol. 36, no. 6, pp. 6797–6813, 2021.

- [2] J. P. Kozak, R. Zhang, M. Porter, Q. Song, J. Liu, B. Wang, R. Wang, W. Saito, and Y. Zhang, "Stability, Reliability, and Robustness of GaN Power Devices: A Review," *IEEE Transactions on Power Electronics*, vol. 38, no. 7, pp. 8442–8471, 2023.

- [3] S. Faramehr, K. Kalna, and P. Igić, "Drift-diffusion and hydrodynamic modeling of current collapse in GaN HEMTs for RF power application," *Semiconductor Science and Technology*, vol. 29, no. 2, p. 025007, jan 2014.

- [4] M. Meneghini, C. De Santi, I. Abid, M. Buffolo, M. Cioni, R. A. Khadar, L. Nela, N. Zagni, A. Chini, F. Medjdoub, G. Meneghesso, G. Verzellesi, E. Zanoni, and E. Matioli, "GaN-based power devices: Physics, reliability, and perspectives," *Journal of Applied Physics*, vol. 130, no. 18, p. 181101, 2021. [Online]. Available: https://doi.org/10.1063/5.0061354

- [5] G. Greco, F. Iucolano, and F. Roccaforte, "Review of technology for normally-off HEMTs with p-GaN gate," *Materials Science in Semiconductor Processing*, vol. 78, pp. 96–106, 2018.

- [6] S. Kaneko, M. Kuroda, M. Yanagihara, A. Ikoshi, H. Okita, T. Morita, K. Tanaka, M. Hikita, Y. Uemoto, S. Takahashi, and T. Ueda, "Currentcollapse-free operations up to 850 V by GaN-GIT utilizing hole injection from drain," in 2015 IEEE 27th International Symposium on Power Semiconductor Devices IC's (ISPSD), 2015, pp. 41–44.

- [7] S. Yang, S. Han, K. Sheng, and K. J. Chen, "Dynamic On-Resistance in GaN Power Devices: Mechanisms, Characterizations, and Modeling," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 7, no. 3, pp. 1425–1439, 2019.

- [8] K. Zhong, J. Wei, J. He, S. Feng, Y. Wang, S. Yang, and K. J. Chen, "IG- and VGS-Dependent Dynamic RON Characterization of Commercial High-Voltage p-GaN Gate Power HEMTs," *IEEE Transactions on Industrial Electronics*, vol. 69, no. 8, pp. 8387–8395, 2022.

- [9] J. O. Gonzalez, B. Etoz, and O. Alatise, "Characterizing Threshold Voltage Shifts and Recovery in Schottky Gate and Ohmic Gate GaN HEMTs," in 2020 IEEE Energy Conversion Congress and Exposition (ECCE), 2020, pp. 217–224.

- [10] T. Oeder and M. Pfost, "Gate-Induced Threshold Voltage Instabilities in p-Gate GaN HEMTs," *IEEE Transactions on Electron Devices*, vol. 68, no. 9, pp. 4322–4328, 2021.

- [11] Y. Uemoto, M. Hikita, H. Ueno, H. Matsuo, H. Ishida, M. Yanagihara, T. Ueda, T. Tanaka, and D. Ueda, "Gate Injection Transistor (GIT)—A Normally-Off AlGaN/GaN Power Transistor Using Conductivity Modulation," *IEEE Transactions on Electron Devices*, vol. 54, no. 12, pp. 3393–3399, 2007.

- [12] L. Sayadi, G. Iannaccone, S. Sicre, O. H\u00e4berlen, and G. Curatola, "Threshold Voltage Instability in p-GaN Gate AlGaN/GaN HFETs," *IEEE Transactions on Electron Devices*, vol. 65, no. 6, pp. 2454–2460, 2018.

- [13] J. Wei, R. Xie, H. Xu, H. Wang, Y. Wang, M. Hua, K. Zhong, G. Tang, J. He, M. Zhang, and K. J. Chen, "Charge Storage Mechanism of Drain Induced Dynamic Threshold Voltage Shift in *p* -GaN Gate HEMTs," *IEEE Electron Device Letters*, vol. 40, no. 4, pp. 526–529, 2019.

- [14] H. Xu, J. Wei, R. Xie, Z. Zheng, J. He, and K. J. Chen, "Incorporating the Dynamic Threshold Voltage Into the SPICE Model of Schottky-Type p-GaN Gate Power HEMTs," *IEEE Transactions on Power Electronics*, vol. 36, no. 5, pp. 5904–5914, 2021.

- [15] J. Chen, M. Hua, J. Wei, J. He, C. Wang, Z. Zheng, and K. J. Chen, "OFF-State Drain-Voltage-Stress-Induced VTH Instability in Schottky-Type p-GaN Gate HEMTs," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 9, no. 3, pp. 3686–3694, 2021.

- [16] L. Efthymiou, K. Murukesan, G. Longobardi, F. Udrea, A. Shibib, and K. Terrill, "Understanding the Threshold Voltage Instability During OFF-State Stress in p-GaN HEMTs," *IEEE Electron Device Letters*, vol. 40, no. 8, pp. 1253–1256, 2019.

- [17] M. Nuo, J. Wei, M. Wang, J. Yang, Y. Wu, Y. Hao, and B. Shen, "Gate/Drain Coupled Barrier Lowering Effect and Negative Threshold Voltage Shift in Schottky-Type p-GaN Gate HEMT," *IEEE Transactions* on *Electron Devices*, vol. 69, no. 7, pp. 3630–3635, 2022.

- [18] M. Nuo, Y. Wu, J. Yang, Y. Hao, M. Wang, and J. Wei, "Time-Resolved Extraction of Negatively Shifted Threshold Voltage in Schottky-Type p-GaN Gate HEMT Biased at High VDS," *IEEE Transactions on Electron Devices*, vol. 70, no. 7, pp. 3462–3467, 2023.

- [19] K. Li, A. Videt, N. Idir, P. Evans, and M. Johnson, "Experimental Investigation of GaN Transistor Current Collapse on Power Converter Efficiency for Electrical Vehicles," in 2019 IEEE Vehicle Power and Propulsion Conference (VPPC), 2019, pp. 1–6.

- [20] F. Yang, C. Xu, and B. Akin, "Characterization of Threshold Voltage Instability Under Off-State Drain Stress and Its Impact on p-GaN HEMT Performance," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 9, no. 4, pp. 4026–4035, 2021.

- [21] R. Xie, X. Yang, G. Xu, J. Wei, Y. Wang, H. Wang, M. Tian, F. Zhang, W. Chen, L. Wang, and K. J. Chen, "Switching Transient Analysis for Normally-off GaN Transistor With p-GaN Gate in a Phase-Leg Circuit," *IEEE Transactions on Power Electronics*, vol. 34, no. 4, pp. 3711–3728, 2019.

- [22] I. Hwang, J. Oh, S.-K. Hwang, B. Kim, J. H. Park, J. Kim, and J. Kim, "Extraction of Dynamic Threshold Voltage in Resistive Load

Hard Switching Operation of Schottky-Type p-GaN Gate HEMT," *IEEE Electron Device Letters*, vol. 43, no. 10, pp. 1720–1723, 2022.

- [23] Z. Fan, M. Wang, J. Wei, M. Nuo, J. Zhou, J. Zhang, Y. Hao, and B. Shen, "Analysis of Drain-Dependent Threshold Voltage and False Turn-On of Schottky-Type p-GaN Gate HEMT in Bridge-Leg Circuit," *IEEE Transactions on Power Electronics*, vol. 39, no. 2, pp. 2351–2359, 2024.

- [24] GS66502B Datasheet REV180420, GaNsystems, 2018, rev. 2018. [Online]. Available: https://gansystems.com/wp-content/uploads/2018/ 04/GS66502B-DS-Rev-180420.pdf

- [25] N. Modolo, C. De Santi, A. Minetto, A. Minetto, L. Sayadi, S. Sicre, G. Prechtl, G. Meneghesso, E. Zanoni, and M. Meneghini, "Cumulative Hot-Electron Trapping in GaN-Based Power HEMTs Observed by an Ultra-Fast (10V/ns) on-Wafer Methodology," *IEEE Journal of Emerging* and Selected Topics in Power Electronics, pp. 1–1, 2021.

- [26] H. Onodera, T. Kabemura, and K. Horio, "Numerical Analysis of Impact Ionization Effects on Hard Switching in AlGaN/GaN HEMTs," *IEEE Transactions on Electron Devices*, vol. 70, no. 12, pp. 6217–6224, 2023.

- [27] F. Yang, C. Xu, and B. Akin, "Experimental Evaluation and Analysis of Switching Transient's Effect on Dynamic on-Resistance in GaN HEMTs," *IEEE Transactions on Power Electronics*, vol. 34, no. 10, pp. 10121–10135, 2019.

- [28] H. Sakairi, T. Yanagi, H. Otake, N. Kuroda, and H. Tanigawa, "Measurement Methodology for Accurate Modeling of SiC MOSFET Switching Behavior Over Wide Voltage and Current Ranges," *IEEE Transactions* on Power Electronics, vol. 33, no. 9, pp. 7314–7325, 2018.

- [29] Z. Zeng, J. Wang, L. Wang, Y. Yu, and K. Ou, "Inaccurate Switching Loss Measurement of SiC MOSFET Caused by Probes: Modelization, Characterization, and Validation," *IEEE Transactions on Instrumentation and Measurement*, vol. 70, pp. 1–14, 2021.

[30] E. A. Jones, Z. Zhang, and F. Wang, "Analysis of the dv/dt transient of

- [30] E. A. Jones, Z. Zhang, and F. Wang, "Analysis of the dv/dt transient of enhancement-mode GaN FETs," in 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), 2017, pp. 2692–2699.

- [31] X. Huang, Q. Li, Z. Liu, and F. C. Lee, "Analytical loss model of high voltage GaN HEMT in cascode configuration," in 2013 IEEE Energy Conversion Congress and Exposition, 2013, pp. 3587–3594.

[32] K. Li, P. Evans, and M. Johnson, "SiC/GaN power semiconductor

- [32] K. Li, P. Evans, and M. Johnson, "SiC/GaN power semiconductor devices: a theoretical comparison and experimental evaluation under different switching conditions," *IET Electrical Systems in Transportation*, vol. 8, no. 1, pp. 3–11, 2018.

- [33] P. Yang, W. Ming, J. Liang, I. Lüdtke, S. Berry, and K. Floros, "Hybrid Data-Driven Modeling Methodology for Fast and Accurate Transient Simulation of SiC MOSFETs," *IEEE Transactions on Power Electronics*, vol. 37, no. 1, pp. 440–451, 2022.

- [34] A. Videt, K. Li, N. Idir, P. Evans, and M. Johnson, "Analysis of GaN Converter Circuit Stability Influenced by Current Collapse Effect," in 2020 IEEE Applied Power Electronics Conference and Exposition (APEC), 2020, pp. 2570–2576.

- [35] X. Lu, A. Videt, K. Li, S. Faramehr, P. Igic, and N. Idir, "Influence of Current Collapse due to  $V_{ds}$  Bias Effect on GaN-HEMTs  $I_d - V_{ds}$ Characteristics in Saturation Region," in 2022 24th European Conference on Power Electronics and Applications (EPE'22 ECCE Europe), 2022, pp. P.1–P.9.

- [36] H. Li, Z. Gao, R. Chen, and F. Wang, "Improved Double Pulse Test for Accurate Dynamic Characterization of Medium Voltage SiC Devices," *IEEE Transactions on Power Electronics*, vol. 38, no. 2, pp. 1779–1790, 2023.

- [37] K. Zhong, H. Xu, Z. Zheng, J. Chen, and K. J. Chen, "Characterization of Dynamic Threshold Voltage in Schottky-Type p-GaN Gate HEMT Under High-Frequency Switching," *IEEE Electron Device Letters*, vol. 42, no. 4, pp. 501–504, 2021.

- [38] N. Wang, J. Zhang, and F. Deng, "Improved SiC MOSFET Model Considering Channel Dynamics of Transfer Characteristics," *IEEE Transactions on Power Electronics*, vol. 38, no. 1, pp. 460–471, 2023.

- [39] A. U. Rashid, M. M. Hossain, A. I. Emon, and H. A. Mantooth, "Datasheet-Driven Compact Model of Silicon Carbide Power MOSFET Including Third-Quadrant Behavior," *IEEE Transactions on Power Electronics*, vol. 36, no. 10, pp. 11748–11762, 2021.

- [40] S. Faramehr and P. Igić, "Analysis of GaN HEMTs Switching Transients Using Compact Model," *IEEE Transactions on Electron Devices*, vol. 64, no. 7, pp. 2900–2905, 2017.

- [41] H. Li, X. Zhao, W. Su, K. Sun, X. You, and T. Q. Zheng, "Nonsegmented PSpice Circuit Model of GaN HEMT With Simulation Convergence Consideration," *IEEE Transactions on Industrial Electronics*, vol. 64, no. 11, pp. 8992–9000, 2017.

- [42] D. Chiozzi, M. Bernardoni, N. Delmonte, and P. Cova, "A Neural Network Based Approach to Simulate Electrothermal Device Interaction

in SPICE Environment," *IEEE Transactions on Power Electronics*, vol. 34, no. 5, pp. 4703–4710, 2019.

- [43] K. Li and S. Sen, "A Fast and Accurate GaN Power Transistor Model and Its Application for Electric Vehicle," *IEEE Transactions on Vehicular Technology*, pp. 1–13, 2023.

- [44] Q. Song, R. Zhang, Q. Li, and Y. Zhang, "Output Capacitance Loss of GaN HEMTs in Steady-State Switching," *IEEE Transactions on Power Electronics*, pp. 1–10, 2023.

- [45] X. Lu, A. Videt, N. Idir, V. Marsic, P. Igic, and S. Faramehr, "Investigation on Single and Split Output Gate Configurations Influence on the GaN-HEMTs Switching Behaviours," in 2023 25th European Conference on Power Electronics and Applications (EPE'23 ECCE Europe), 2023, pp. 1–9.