ACS APPLIED

ELECTRONIC MATERIALS

## Thermal Compact Modeling and Resistive Switching Analysis in **Titanium Oxide-Based Memristors**

Juan B. Roldán,\* Antonio Cantudo, David Maldonado, Cristina Aguilera-Pedregosa, Enrique Moreno, Timm Swoboda, Francisco Jiménez-Molinos, Yue Yuan, Kaichen Zhu, Mario Lanza, and Miguel Muñoz Rojo

Cite This: ACS Appl. Electron. Mater. 2024, 6, 1424-1433

**ACCESS**

III Metrics & More

Article Recommendations

s Supporting Information

ABSTRACT: Resistive switching devices based on the Au/Ti/TiO<sub>2</sub>/Au stack were developed. In addition to standard electrical characterization by means of I-V curves, scanning thermal microscopy was employed to localize the hot spots on the top device surface (linked to conductive nanofilaments, CNFs) and perform in-operando tracking of temperature in such spots. In this way, electrical and thermal responses can be simultaneously recorded and related to each other. In a complementary way, a model for device simulation (based on COMSOL Multiphysics) was implemented in order to link the measured temperature to simulated device temperature maps. The data obtained were employed to calculate the thermal resistance to be used in compact models, such as the Stanford model, for circuit simulation. The thermal resistance extraction technique presented in this work is based on electrical and thermal measurements instead of being indirectly supported by a single fitting of the electrical response (using just I-V curves), as usual. Besides, the set and reset voltages were calculated from the complete I-V curve resistive switching series through different automatic numerical

methods to assess the device variability. The series resistance was also obtained from experimental measurements, whose value is also incorporated into a compact model enhanced version.

KEYWORDS: memristor, resistive switching, thermal analysis, device simulation, modeling, variability analysis

#### 1. INTRODUCTION

Memristors based on resistive switching (RS) are being scrutinized at academic and industrial research centers. The potential of these electron devices is outstanding at the commercial level, and different niche applications have already been put in the market. Some of these memristors change their internal resistance by means of the creation and destruction of a conductive nanofilament across an insulator layer (this layer is sandwiched between two metals, i.e., a metal-insulator-metal, MIM, structure) that shorts the metallic electrodes. These types of devices are known as resistive memories, and they are included by several companies in their technologies as nonvolatile memories (TSMC for its 40,<sup>2</sup> 28,<sup>3</sup> and 22 nm<sup>4</sup> nodes, as well as INTEL for its 22 nm<sup>5</sup> node).

When the CNF is formed, the device is in the low-resistance state (LRS); conversely, when the CNF is broken (after switching from the LRS), it is said to be in the high-resistance state (HRS). This digital operational viewpoint allows their use in memory circuits; however, if the analog perspective is considered in terms of the device conductance variation, new applications come up such as neuromorphic engineering, where these memristive devices offer in-memory computing capabilities, that lead to new architectures that can overcome the limitations of von Newmann's bottleneck.<sup>6</sup> The role of memristors within this new paradigm  $^{7-16}$  is essential to reduce energy consumption in artificial intelligence computation, since circuits based on conventional MOS transistors to implement artificial neurons and synapses are more power-inefficient. In addition, resistive memories can also be used for hardware cryptography as entropy sources to build physical unclonable functions and true random number generators. 17-19

It is known that RS is controlled by the application of an electric field and also by the device internal temperature that is increased by Joule heating. <sup>20–24</sup> In fact, the physical mechanisms behind RS are thermally activated; hence, thermal effects are key to understanding and controlling the device operation. Consequently, an accurate description of these effects is essential to build compact models for circuit simulations. 21,22,25-27

Here, we study the RS features of devices based on Au/Ti/  $TiO_2/Au$  stacks. We fabricate them and measure I-V curves

Received: December 7, 2023 Revised: February 1, 2024 Accepted: February 1, 2024 Published: February 15, 2024

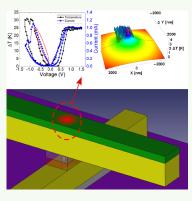

Figure 1. (a) Device cross-sectional schematic. (b) Experimental current vs voltage curves for 261 consecutive RS cycles (for a  $2 \times 2 \mu m$  device) measured for  $I_{CC} = 500 \mu A$  (the voltage ramp was 0.57 V/s). The mean of the curves measured is colored red, with arrows showing the typical hysteresis of a memristive device. (c) Set voltages vs cycle number including three different numerical techniques (MS1, MS2, and MS3) used for the set voltage extraction (see Supporting Information note 1 for the detailed explanation of the numerical procedures). (d) Set current vs cycle number corresponding to the voltages extracted in (c). (e) Reset voltages vs cycle number including four numerical techniques (MR1, MR2, MR3, and MR4) employed for the reset voltage extraction (see Supporting Information note 1). (f) Reset current vs cycle number corresponding to the voltages extracted in (e).

under the ramped voltage stress (RVS) operation regime. An in-depth analysis of the experimental data is performed making use of different numerical methods to extract RS parameters. In addition, a study of the cycle-to-cycle variability<sup>22,28,29</sup> is performed to understand the experimental data structure. The information on heat dissipation produced by the filament for these devices is provided in ref 30. An operando scanning thermal microscope (SThM) was used to characterize the device surface, localize the device CNFs, and extract the temperature in the hot spots. The results are contrasted with physical simulations by means of the COMSOL Multiphysics simulation tool, and the device charge conduction and temperature distributions are analyzed. Both experimental current and temperature distributions are used to tune the simulator. Finally, we go through a compact modeling stage where the Stanford model<sup>31-34</sup> is adapted to fit experimental and simulation data, and essential parameters such as thermal resistance are extracted.

## 2. DEVICE CHARACTERIZATION, AND ELECTRICAL MEASUREMENT SETUP

The cross-sectional scheme of the devices we fabricated is shown in Figure 1a. The fabrication process is explained in the Methods and Materials section. The devices were measured by means of a Keysight B1500A semiconductor parameter analyzer and a probe station (Karl Suss PSM6). A B1511B medium power source measurement unit (MPSMU) was used for the quasi-static ramped voltage stress measurements. The bottom electrode was grounded, and the input voltage signal was applied to the top electrode. A ramped voltage stress (RVS) operation regime was employed for the device characterization. The I-V curves measured are shown in Figure 1b, including more than 250 cycles. An average curve is highlighted in red to let the reader see the I-V curve shape,

which looks similar to that of valence change memories based on  $HfO_2$ . <sup>21,28</sup>

The set and reset voltages and currents (current levels at the I-V point determined by the corresponding set and reset voltages) have been obtained by making use of different techniques (the numerical details of each procedure are described in the Supporting Information note 1). The set (reset) voltages and currents extracted from the experiments are plotted in Figure 1c,d (e and f). For the reset voltage, a higher variability is shown for the MR1 and MR2 techniques.

# 3. DEVICE THERMAL CHARACTERIZATION (SCANNING THERMAL MICROSCOPY)

The thermal characterization of the devices was carried out with a scanning thermal microscope (SThM), as described in ref 30 and in the Supporting Information note 2. For that purpose, we used an Asylum MFP-3D atomic force microscope with a SThM add-on from Bruker. For sensing the devices, we used thermoresistive GLA-1 probes from Bruker. The electrical resistance of these probes varies with temperature, and it is connected electrically to a Wheatstone bridge to sense these variations during surface scans. We operated the SThM in sensing mode using a probe power of 19  $\mu$ W, which, as determined in a prior study, is optimum for measuring under sensing conditions.<sup>35</sup>

In that mode, we kept the probe at a low self-heating temperature while achieving a high temperature sensitivity. For the conversion of the SThM Wheatstone bridge voltage signal (mV) into temperature, we calibrated the system as described in ref 35.

A Keithley 4200 A-SCS parameter analyzer was used in combination with the SThM to study the heat dissipation in the memristor devices when applying I-V curves in between the two contact pads. <sup>30</sup> In these measurements, we studied the TiO<sub>2</sub>-based RRAM devices with a cross-point area size of 2 × 2

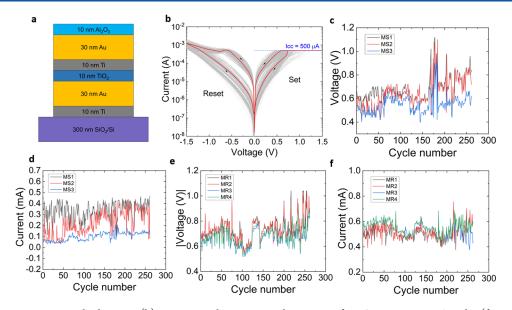

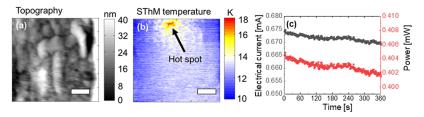

Figure 2. (a) Steady-state topography map of the cross-point of a  $TiO_2$ -based RRAM device with an area size of  $2 \times 2 \mu m^2$  in its LRS. (b) SThM temperature map corresponding to the scan in (a). The map shows a hot spot with an elevated temperature induced by the electrical current flowing through the CNF (scale bar corresponds to 200 nm). (c) Electrical current and power are applied to the device as functions of the scan time.

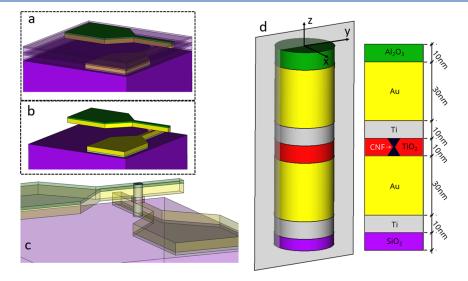

Figure 3. (a) Device fabrication scheme: titanium oxide is employed as a dielectric and bilayers of Au/Ti as electrodes. (b) Device view in the crossbar structure. (c) Cylindrical simulation domain containing the main device layers (zoomed-in view from b). (d) 3D longitudinal device cross section where the revolution geometry that constitutes the COMSOL simulation domain is shown.

$\mu m^2$  and a cross-section structure, as described in the previous section. In order to verify the cyclability of our devices, we performed more than 10 RS cycles before doing the SThM scans. During the cycling, we limited the current using a compliance of 1 mA for the set process.

Once we verified the cyclability, we carried out SThM steady-state measurements at the cross-point area while applying a constant current to identify the heat dissipation at the surface. Figure 2a,b shows the topography and the temperature map of the cross-point area of a biased  $2\times 2$   $\mu\text{m}^2$  device in its low resistive state (LRS). The applied current and electrical power during the steady-state scan are plotted in Figure 2c. In the LRS, the device is set, and the electrical current flows through the formed and confined CNF. The heat dissipation of the generated filament Joule heating is then localized as a hot spot at the surface, as illustrated in Figure 2b. At this point it is worth noting that the heat dissipation between CNF and the surface varies depending on the device material selection and thickness, and hence, it must be carefully analyzed. <sup>36</sup>

Afterward, we kept the SThM probe static at the initial hot spot position, as localized by the steady-state measurements. Then, in order to correlate the electrical signal with temperature, in-operando, we ran I-V cycles while tracking the SThM signal at the hot spot position. The results of these measurements are presented in the Results and Discussion.

## 4. DEVICE SIMULATION

For device simulation, we employed the COMSOL Multiphysics simulation tool. The physical model developed is in line with the one reported in ref 30 although we have included improvements to correctly describe the internal device thermal behavior. In this respect, we considered the simulation structure shown in Figure 3.

It consists of a revolution geometry that forms the simulation domain (Figure 3c,d). The layer structure is given in Figure 3d, in line with previous approaches.<sup>30</sup> We assume a CNF with an hourglass shape, with the maximum and minimum radius of 6 and 2.9 nm, respectively.

Some of the material properties are given in Table 1, while others are extracted from ref 30. The CNF electrical conductivity is assumed to be  $2.85 \times 10^5 \ (\Omega \text{m})^{-1}$  at T=300 K. Since the conductive filament is fully formed and shorts

Table 1. Thermal Conductivities of the Materials Employed in the Simulation

| material                | k [W/(m K)] | ref   |

|-------------------------|-------------|-------|

| Ti                      | 8.2         | 37    |

| Au                      | 317.15      |       |

| $TiO_2$                 | 0.8         | 38    |

| SiO <sub>2</sub>        | 1.4         |       |

| $Al_2O_3$               | 3.45        | 24    |

| conductive nanofilament | 18          | 20,27 |

Table 2. Statistical Study of the Extracted Set of RS Parameters for the Different Extraction Methodologies

| parameter    | mean $(\mu)$                       | standard deviation $(\sigma)$      | coefficient of variation $(\sigma/\mu)$ |

|--------------|------------------------------------|------------------------------------|-----------------------------------------|

| $V_{ m MS1}$ | 0.68789 V                          | 0.10654 V                          | 0.15488                                 |

| $V_{ m MS2}$ | 0.64782 V                          | 0.11663 V                          | 0.18004                                 |

| $V_{ m MS3}$ | 0.55103 V                          | 0.08048 V                          | 0.14606                                 |

| $I_{ m MS1}$ | $3.32701 \times 10^{-4} \text{ A}$ | $7.83586 \times 10^{-5} \text{ A}$ | 0.23552                                 |

| $I_{ m MS2}$ | $2.2049 \times 10^{-4} \text{ A}$  | $1.0575 \times 10^{-4} \text{ A}$  | 0.47961                                 |

| $I_{ m MS3}$ | $9.95904 \times 10^{-5} \text{ A}$ | $3.76061 \times 10^{-5} \text{ A}$ | 0.37761                                 |

<sup>a</sup>The minimum CV values are highlighted.

the electrodes (the filament is in contact with both the bottom and top electrodes), heat transport is more efficient through the filament than through the surrounding oxide; in this respect, interfacial oxides formed between Ti and the dielectric are not expected to influence much when the device operates in the low-resistance state.

In the reset process experimental data (the CNF is fully formed at the beginning of the reset process), the current versus voltage relationship is not completely linear. Therefore, in order to implement this nonlinearity, we include a constriction (described with the quantum point contact, QPC, model<sup>39–41</sup>) in series with the ohmic CNF, as it has been implemented for the modeling of other devices. <sup>20,42</sup> In this manner, the external applied voltage ( $V_{\rm RRAM}$ ) is the sum of the voltage in the CNF ( $V_{\rm CNF}$ ) and the voltage at the constriction ( $V_{\rm CTR}$ ), so that  $V_{\rm RRAM} = V_{\rm CNF} + V_{\rm CTR}$ . The QPC physics has been described previously, <sup>39–41</sup> and the current in the constriction that quantizes the electron energy in the CNF transverse direction is given in eq 1.

$$I = \frac{2eN}{h} \left\{ eV_{\text{CTR}} + \frac{1}{\alpha} \ln \left[ \frac{1 + \exp\{\alpha[\Phi - \beta eV_{\text{CTR}}]\}}{1 + \exp\{\alpha[\Phi + (1 - \beta)eV_{\text{CTR}}]\}} \right] \right\}$$

(1)

Landauer's formalism for 1D quantum conductors and the zero-temperature limit were employed  $^{39,40}$  to obtain eq 1, where  $\Phi$  is the potential barrier height measured with respect to the Fermi level,  $\alpha$  is a parameter linked to the potential barrier thickness at the Fermi level,  $V_{\rm CTR}$  is the voltage which is assumed to drop at both ends of the CF constriction (in a fraction of  $\beta$  and  $(1-\beta)$  at each extreme, as suggested in ref 43) and N is the number of channels. The QPC parameters employed in the fitting of the experimental data of our devices are the following:  $\beta = 0.99$ ,  $\alpha = 14 \, {\rm eV}^{-1}$ , N = 242, and  $\Phi = 0.134 \, {\rm eV}$ .

### 5. RESULTS AND DISCUSSION

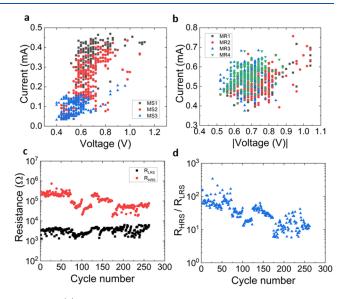

**5.1. Parameter Extraction.** As highlighted above, the set and reset voltage extraction procedures are explained in the Supporting Information 1 and Figure S1. If the set and reset currents are plotted versus the corresponding voltages (Figure 4a,b), we see that the reset parameters present less variability, which is easily seen in the cumulative distribution functions plotted in Figure S2a-d.

It is observed that  $R_{\rm HRS}/R_{\rm LRS}$  is high enough to let the use of these devices feasible for nonvolatile memory applications, and the values found for  $R_{\rm HRS}$  and  $R_{\rm LRS}$  are coherent in comparison to other memristive devices.

**5.2. RS Parameter Statistics.** We performed a statistical analysis to untangle the structure of the data obtained in

**Figure 4.** (a) Experimental  $I_{\rm set}$  vs  $V_{\rm set}$  extracted, employing methods MS1, MS2, and MS3. (b) Experimental  $I_{\rm reset}$  vs  $V_{\rm reset}$  extracted, switching voltage parameters, employing methods MR1, MR2, MR3, and MR4. (c) LRS and HRS resistances (read at 0.2 V) vs cycle number for all the measured RS series. (d) HRS/LRS resistance ratio vs cycle number calculated with data from (c).

previous sections. To do so, we obtained the mean values, standard deviations, and coefficients of variation (CV, calculated as  $\sigma/\mu$ , where  $\sigma$  stands for the standard deviation and  $\mu$  for the mean) for each RS parameter; see Tables 2 and 3 for the set (reset) parameters. In general, if the cycle-to-cycle variability is low (i.e., CV of  $V_{\rm set}$  < 2%), the devices could be used for information storage, 4 computation, 6 or transmission; 45 if the variability is high (CV of  $V_{\rm set}$  > 20%), the devices could rather be employed for data encryption as entropy source for true random number generators or physical unclonable functions. 46

As known, a lower CV indicates lower variability. The results demonstrate, as expected, that the CV depends on the extraction methodology. This is a key result that makes it clear that the extraction numerical procedure should be clarified in the literature. In particular, MS3 presents the lowest value for  $V_{\rm set}$ , whereas MS1 is for  $I_{\rm set}$ . MR3 marks the minimum variability for  $V_{\rm reset}$ , while MR4 is for  $I_{\rm reset}$ .

In filamentary-based memristive devices, the reset process normally exhibits higher variability than the set;  $^{1,47,48}$  however, in our devices, the behavior is different. Therefore, a different role of thermal and electric field effects is expected to lead to the homogenization of the  $V_{\rm reset}$  distribution.

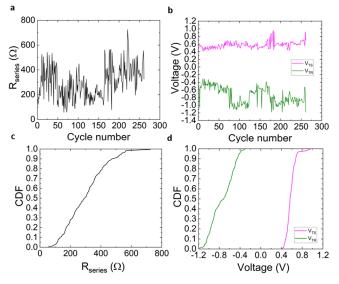

We have also extracted the series resistance of our devices following a previously published extraction technique; <sup>49,50</sup> see Figure 5a. In addition, the reset and set transition voltages

Table 3. Statistical Study of the Reset RS Parameters for the Different Extraction Methodologies<sup>a</sup>

| parameter    | mean $(\mu)$                       | standard deviation $(\sigma)$      | coefficient of variation $(\sigma/\mu)$ |

|--------------|------------------------------------|------------------------------------|-----------------------------------------|

| $V_{ m MR1}$ | 0.73267 V                          | 0.08869 V                          | 0.12105                                 |

| $V_{ m MR2}$ | 0.73084 V                          | 0.08786 V                          | 0.12022                                 |

| $V_{ m MR3}$ | 0.6658 V                           | 0.06492 V                          | 0.09751                                 |

| $V_{ m MR4}$ | 0.68092 V                          | 0.07063 V                          | 0.10373                                 |

| $I_{ m MR1}$ | $5.08099 \times 10^{-4} \text{ A}$ | $5.09536 \times 10^{-5} \text{ A}$ | 0.10028                                 |

| $I_{ m MR2}$ | $5.17962 \times 10^{-4} \text{ A}$ | $5.46663 \times 10^{-5} \text{ A}$ | 0.10554                                 |

| $I_{ m MR3}$ | $5.47164 \times 10^{-4} \text{ A}$ | $5.32173 \times 10^{-5} \text{ A}$ | 0.09726                                 |

| $I_{ m MR4}$ | $5.53214 \times 10^{-4} \text{ A}$ | $5.09291 \times 10^{-5} \text{ A}$ | 0.09206                                 |

<sup>&</sup>lt;sup>a</sup>The minimum CV values are highlighted.

Figure 5. (a) Series resistance computed for the complete RS series as a function of the cycle number for the data analyzed. (b) Set transition voltage  $(V_{\rm TS})$  and reset transition voltage  $(V_{\rm TR})$  plotted against the cycle number for the complete RS series of the data under study. Cumulative distribution functions for the studied parameters in the whole RS series: (c) series resistance, (d) transition voltages for the set  $(V_{\rm TS})$  and for the reset processes  $(V_{\rm TR})$ .

were extracted<sup>50</sup> (they stand for the reset and set voltages, once the effects of the series resistance have been extracted from the original current vs voltage curve, what is known as the normalized I-V curve); see Figure 5b. The CDFs for these parameters are listed in Figure 5c,d. It is observed, as also reported in ref 50 for the HfO<sub>2</sub> technology, that the absolute values of the reset and set transition voltages are much more

similar than the original set and reset voltages. However, the series resistances extracted are higher than that in the  $HfO_2$  devices analyzed in ref 50.

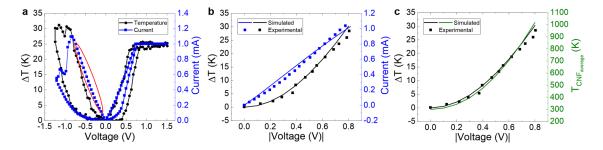

**5.3. Device Physical Simulation.** We have made use of the simulation approach described in Section 4. The reset process was simulated by assuming that the CNF is fully formed at the beginning of the simulation. We employ the first part of the reset I-V curve (see Figure 6a), prior to the reset event, in order to fit the experimental current and also the temperature in certain parts of the device. In Figure 6a, we show the current versus voltage (blue data) and temperature increment (black data) on top of the Al2O3 layer measured with the SThM technique (in an in-operando manner). In particular, we simulated the reset curve (highlighted with a red ellipse); in this case, we use a fully formed hourglass-shaped CNF, as shown in Figure 3. Simulation and in-operando experimental data for the reset process highlighted in Figure 6a are shown in Figure 6b showing a reasonably good fit, taking into account the complexity of simultaneously reproducing temperature and current data.

Once the COMSOL simulation model was tuned, we calculated the average CNF temperature. This temperature is employed in compact models since just one temperature is usually assumed in the device for each bias point. In this respect, simplified thermal models can be built to describe the devices in the circuit simulation approach.<sup>25</sup>

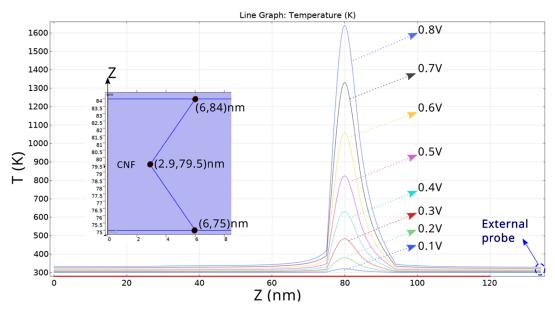

A closer look at the CNF temperature allows us to detail the thermal distribution along its length (Figure 7). See the temperature peaks at the CNF narrowing, as it should be since Joule heating increases at this point because of the current line concentration. Notice also the fast temperature decrease outside the filament region, mostly at the Au side.

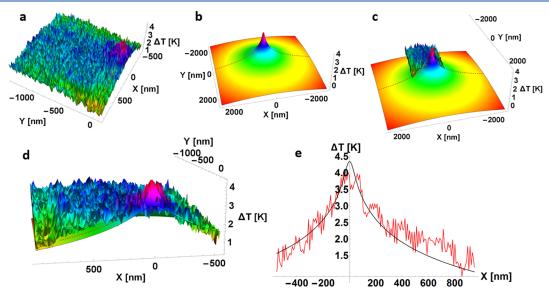

It is worth also mentioning the good fit obtained by comparing the simulated and measured distributions of

**Figure 6.** (a) Experimental current vs voltage (in blue) and temperature increment (in black, obtained with SThM) on top of the device outer  $Al_2O_3$  layer vs voltage (the current curve corresponds to the temperature increment curve; i.e., in-operando measurements), (b) simulated (straight lines) and experimental data (in dots) for the reset process (the experimental data correspond to the curve highlighted in the red ellipse in (a). (c) Simulated (straight lines) and experimental (black dots) temperature increment on top of the  $Al_2O_3$  layer and simulated CNF average temperature along the reset process I-V curve (this latter curve is needed for the compact modeling process).

**Figure 7.** Temperature at the center of the conductive filament vs *z* coordinate (vertical device coordinate) in our simulation domain for different external voltages. CNF position and the *z*-axis orientation are seen in the inset. The higher temperature is obtained at the CNF narrowing (at the center of the hourglass structure).

Figure 8. (a) Three-dimensional experimental plot (temperature increase with respect to room temperature) on top of the  $Al_2O_3$  layer for V = 0.3 V. (b) Corresponding COMSOL simulation (after tuning) for the device scheme in Figure 3 and V = 0.3 V. (c) Comparison between the simulated and measured distributions; (d) panel; (c) zoomed-in view. (e) Good fit is obtained for the different cuts in the experimental/simulated distributions at different simulation domain orientations; this one is taken along the *x*-axis.

temperature increase at the device surface (Figure 8). A good result is obtained throughout the simulation domain top surface. These results suggest the correctness of the model proposed.

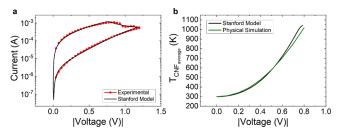

**5.4. Compact Modeling.** For the compact modeling approach, the Stanford model<sup>31–34</sup> is employed. This widely known model uses an equivalent single RC electrical network, driven by a current source, for representing the thermal behavior (thermal resistance and capacitance) and the Joule heating, respectively. We were able to fit the experimental reset curve highlighted in Figure 6, as shown in Figure 9.

We employed the model parameters described in Table 4. In particular, for the determination of the thermal resistance, we used the COMSOL simulated data of Figure 9b (average CNF

**Figure 9.** (a) Current vs voltage for a reset process. Experimental data are shown in red symbols, and those obtained with the Stanford model are shown in lines. (b) Average temperature in the CNF obtained with the COMSOL simulation tool (green line) and device temperature obtained with the Stanford model (black line).

Table 4. Stanford Model Parameters Used in Figure 9<sup>a</sup>

| symbol      | value                       | symbol           | value                         |

|-------------|-----------------------------|------------------|-------------------------------|

| $t_{ m ox}$ | 10 nm                       | $E_{\mathrm{a}}$ | 1.05 eV                       |

| $I_0$       | 50 mA                       | $E_{ m m}$       | 3.25 eV                       |

| $V_0$       | 0.2 V                       | $g_{ m max}$     | 6.3 nm                        |

| $g_0$       | 0.7 nm                      | $g_{ m ini}$     | 5.2 nm                        |

| β           | 10.5 (reset)                | $T_0$            | 300 K                         |

| $\nu_0$     | $5 \times 10^6 \text{ m/s}$ | $T_{ m crit}$    | 450 K                         |

| $\gamma_0$  | 20                          | $R_{ m series}$  | 220 Ω                         |

| $\alpha$    | 1.1 (reset)                 | $R_{ m th}$      | $1.2 \times 10^6 \text{ K/W}$ |

$<sup>^{</sup>a}R_{\text{series}}$  is a series resistance added to the nonlinear current source of the Stanford model.  $^{50}$

temperature). At this point, we highlight the fact that, when fitting I-V curves in developing memristor models, we usually do not have the information given in Figure 9b, which is connected to the SThM measurements, and therefore, the thermal resistance ( $R_{\rm th}$ ) cannot be accurately determined. In our case (see Table 4), the value is  $1.2 \times 10^6$  K/W, which is in line with those reported in refs 25, 31.

The analytical expression to determine the thermal resistance is given in eq 2. In our case, accounting for the low-frequency RVS operation measurements performed (this implies steady-state operation), the transient part of the modified heat equation can be excluded for the usual thermal capacitance values found for resistive memories.<sup>25</sup>

$$R_{\rm th} = \frac{T - T_0}{VI} \tag{2}$$

We also used a series resistance in the compact modeling approach, following a previous work, 50 where the inclusion of this parameter and the effects on the simulation are described.

#### 6. CONCLUSIONS

An experimental characterization of resistive switching in Au/ Ti/TiO<sub>2</sub>/Au devices has been presented, including data obtained with surface scanning thermal microscopy. Macroscopic simulations with COMSOL Multiphysics are performed in order to link the electrical and thermal measurements. Quantum effects are considered in the simulations performed. The experimental and simulated data are used together to calibrate a compact model (an enhanced version of the widely used Stanford model). In this way, temperature in-operando measurements of hot spots on the top device surface, linked to the position of CNFs, and simulations allow us to describe the CNF internal temperature for modeling. A good agreement between simulated and experimental data is achieved, for both the current and CNF temperature. The average CNF temperature is employed to extract the device thermal resistance. This parameter is indirectly determined in compact modeling by fitting the electrical characteristics (I-V curves). On the contrary, the procedure presented in this work permits a direct estimation, linked to thermal measurements. The device characterization is completed by the extraction of set/ reset voltages and series resistance from the experimental I-Vcurves. The latter parameter is also incorporated in the compact model.

## 7. METHODS AND MATERIALS

**7.1. Device Fabrication.** The devices were built on a 300 nm  $SiO_2/Si$  substrate. A 30 nm gold layer was deposited as the bottom electrode on top of a Ti adhesion layer with a thickness of 10 nm

grown by e-beam evaporation. For the dielectric, a 10 nm thick TiO $_2$  layer was grown by means of atomic layer deposition (ALD). The top electrode was deposited in a similar way to the bottom electrode, including the Ti layer. For electrical isolation, an Al $_2$ O $_3$  capping layer of 10 nm was grown by ALD. The device structure consists of a crosspoint structure with contact pad sizes of 100  $\times$  100  $\mu m^2$ . The devices were built making use of two different cross-point area sizes (2  $\times$  2 and 5  $\times$  5  $\mu m^2$ ). The use of Au as an electrode material is not unusual; it has been employed in different academic studies  $^{51-54}$  and also in the context of the industry.  $^{55,56}$

#### ASSOCIATED CONTENT

### **Data Availability Statement**

The data sets generated and/or analyzed during the current study are available from the corresponding author on reasonable request.

### Supporting Information

The Supporting Information is available free of charge at https://pubs.acs.org/doi/10.1021/acsaelm.3c01727.

Numerical techniques employed in the extraction of the set and reset voltages; cumulative distribution functions of the set and reset voltages and currents; and thermal measurement techniques, features, resolution, and limitations (PDF)

#### AUTHOR INFORMATION

#### **Corresponding Author**

Juan B. Roldán — Departamento de Electrónica y Tecnología de Computadores, Universidad de Granada, 18071 Granada, Spain; o orcid.org/0000-0003-1662-6457; Email: jroldan@ugr.es

## Authors

Antonio Cantudo — Departamento de Electrónica y Tecnología de Computadores, Universidad de Granada, 18071 Granada, Spain

David Maldonado – Departamento de Electrónica y Tecnología de Computadores, Universidad de Granada, 18071 Granada, Spain; IHP-Leibniz-Institut für innovative Mikroelektronik, 15236 Frankfurt (Oder), Germany

Cristina Aguilera-Pedregosa — Departamento de Electrónica y Tecnología de Computadores, Universidad de Granada, 18071 Granada, Spain

Enrique Moreno – CEMDATIC—E.T.S.I Telecomunicación, Universidad Politécnica de Madrid (UPM), 28040 Madrid, Spain

Timm Swoboda – Department of Thermal and Fluid Engineering, Faculty of Engineering Technology, University of Twente, 7500 AE Enschede, The Netherlands

Francisco Jiménez-Molinos — Departamento de Electrónica y Tecnología de Computadores, Universidad de Granada, 18071 Granada, Spain; orcid.org/0000-0002-8866-7568

Yue Yuan — Materials Science and Engineering Program, Physical Sciences and Engineering Division, King Abdullah University of Science and Technology (KAUST), Thuwal 23955-6900, Saudi Arabia

Kaichen Zhu – MIND, Department of Electronic and Biomedical Engineering, Universitat de Barcelona, E-08028 Barcelona, Spain

Mario Lanza – Materials Science and Engineering Program, Physical Sciences and Engineering Division, King Abdullah University of Science and Technology (KAUST), Thuwal 23955-6900, Saudi Arabia; o orcid.org/0000-0003-4756-8632.

Miguel Muñoz Rojo − 2D Foundry, Instituto de Ciencia de Materiales de Madrid (ICMM), CSIC, Madrid 28049, Spain; Department of Thermal and Fluid Engineering, Faculty of Engineering Technology, University of Twente, 7500 AE Enschede, The Netherlands; orcid.org/0000-0001-9237-4584

Complete contact information is available at: https://pubs.acs.org/10.1021/acsaelm.3c01727

#### **Author Contributions**

Conceptualization was by J.B.R., M.L., and M.M.R.; electrical measurements and data curation were by D.M., A.C., F.J.-M., and K.Z.; Y.Y. fabricated the memristors; C. A.-P. and E. M. performed the simulations; T.S. and M.M.R. performed the scanning thermal microscopy measurements. The original draft preparation, review, and editing were done by J.B.R., M.L., D.M., and M.M.R. All coauthors have checked and validated the final version of the manuscript.

#### Notes

The authors declare no competing financial interest.

#### ACKNOWLEDGMENTS

We acknowledge grant PID2022-139586NB-44 funded by MCIN/AEI/10.13039/501100011033 and by ERDF, a way of making Europe. M.L. acknowledges the generous support from the Baseline funding scheme of the King Abdullah University of Science and Technology.

## REFERENCES

- (1) Lanza, M.; Sebastian, A.; Lü, W.; Gallo, M. L.; Chang, M.; Akinwande, D.; Puglisi, F. M.; Alshareef, H. N.; Liu, M.; Roldán, J. B. Memristive technologies for data storage, computation, encryption, and radio-frequency communication. *Science* **2022**, *376* (6597), No. eabj9979, DOI: 10.1126/science.abj9979.

- (2) Chou, C.; Lin, Z.; Tseng, P.; Li, C.; Chang, C.; Chen, W.; Chih, Y.; Chang, T. J.An N40 256K × 44 embedded RRAM macro with SL-precharge SA and low-voltage current limiter to improve read and write performance; *IEEE International Solid-State Circuits Conference* (ISSCC); 2018, IEEE, DOI: 10.1109/isscc.2018.8310392.

- (3) Yang, C.; Wu, C.; Yang, M.; Wang, W.; Yang, M.; Chien, T.; Fan, V. S.; Tsai, S.; Lee, Y.; Chu, W. T.; Hung, A.Industrially Applicable Read Disturb Model and Performance on Mega-Bit 28nm Embedded RRAM; *Proceedings of the IEEE Symposium on VLSI Technology*; IEEE, 2020, DOI: 10.1109/vlsitechnology18217.2020.9265060.

- (4) Chou, C.; Lin, Z.; Lai, C.; Su, C. J.; Tseng, P.; Chen, W.; Tsai, W.; Chu, W.; Ong, T.; Chuang, H.; Chih, Y.; Chang, T. J.A 22nm 96KX144 RRAM Macro with a Self-Tracking Reference and a Low Ripple Charge Pump to Achieve a Configurable Read Window and a Wide Operating Voltage Range; Proceedings of the IEEE Symposium on VLSI Circuits; IEEE, 2020, DOI: 10.1109/vlsicircuits18222.2020.9163014.

- (5) Jain, P.; Arslan, Ü.; Sekhar, M.; Lin, B.; Wei, L.; Sahu, T.; Alzate-Vinasco, J.; Vangapaty, A.; Meterelliyoz, M.; Strutt, N.; Chen, A. B.; Hentges, P.; Quintero, P. A.; Connor, C.; Golonzka, O.; Fischer, K.; Hamzaoglu, F.13.2 A 3.6Mb 10.1Mb/mm2 Embedded Non-Volatile ReRAM Macro in 22nm FinFET Technology with Adaptive Forming/Set/Reset Schemes Yielding Down to 0.5V with Sensing Time of 5ns at 0.7V; Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC); IEEE, 2019, DOI: 10.1109/isscc.2019.8662393.

- (6) Sebastian, A.; Gallo, M. L.; Khaddam-Aljameh, R.; Eleftheriou, E. Memory devices and applications for in-memory computing. *Nat. Nanotechnol.* **2020**, *15* (7), 529–544.

- (7) Yu, S.; Wu, Y.; Jeyasingh, R. G. D.; Kuzum, D.; Wong, H. An electronic synapse device based on metal oxide resistive switching memory for neuromorphic computation. *IEEE Trans. Electron Devices* **2011**, *58* (8), 2729–2737.

- (8) Quesada, E. P.; Romero-Záliz, R.; Pérez, E.; Mahadevaiah, M. K.; Reuben, J.; Schubert, M. A.; Jiménez-Molinos, F.; Roldán, J.; Wenger, C. Toward reliable compact modeling of multilevel 1T-1R RRAM devices for neuromorphic systems. *Electronics* **2021**, *10* (6), 645.

- (9) Ambrogio, S.; Narayanan, P.; Tsai, H.; Shelby, R. M.; Boybat, I.; Di Nolfo, C.; Sidler, S.; Giordano, M.; Bodini, M.; Farinha, N. C. P.; Killeen, B. D.; Cheng, C.; Jaoudi, Y.; Burr, G. W. Equivalent-accuracy Accelerated neural-network training using analogue memory. *Nature* **2018**, *558* (7708), 60–67.

- (10) Merolla, P.; Arthur, J. V.; Alvarez-Icaza, R.; Cassidy, A.; Sawada, J.; Akopyan, F.; Jackson, B. L.; Imam, N.; Chen, G.; Nakamura, Y.; Brezzo, B.; Vo, I.; Esser, S. K.; Appuswamy, R.; Taba, B.; Amir, A.; Flickner, M.; Risk, W. P.; Manohar, R.; Modha, D. S. A million spiking-neuron integrated circuit with a scalable communication network and interface. *Science* **2014**, *345* (6197), 668–673.

- (11) Hui, F.; Liu, P.; Hodge, S.; Carey, T.; Wen, C.; Torrisi, F.; Galhena, D. T. L.; Tomarchio, F.; Lin, Y.; Moreno, E. M. O.; Roldán, J.; Koren, E.; Ferrari, A. C.; Lanza, M. In situ observation of Low-Power Nano-Synaptic response in graphene oxide using conductive atomic force microscopy. *Small* **2021**, *17* (26), No. 2101100, DOI: 10.1002/smll.202101100.

- (12) Alibart, F.; Zamanidoost, E.; Strukov, D. B. Pattern classification by memristive crossbar circuits using ex situ and in situ training. *Nat. Commun.* **2013**, *4* (1), 2072 DOI: 10.1038/ncomms3072.

- (13) Prezioso, M.; Merrikh-Bayat, F.; Hoskins, B. D.; Adam, G. C.; Likharev, K. K.; Strukov, D. B. Training and operation of an integrated neuromorphic network based on metal-oxide memristors. *Nature* **2015**, *521* (7550), *61*–*64*.

- (14) Zidan, M. A.; Strachan, J. P.; Lü, W. The future of electronics based on memristive systems. *Nature Electronics* **2018**, *1* (1), 22–29.

- (15) Roldán, J. B.; Maldonado, D.; Aguilera-Pedregosa, C.; Moreno, E. M. O.; Aguirre, F.; Romero-Záliz, R.; García-Vico, Á. M.; Shen, Y.; Lanza, M. Spiking neural networks based on two-dimensional materials. *npj* 2D Mater. Appl. **2022**, 6 (1), 63 DOI: 10.1038/s41699-022-00341-5.

- (16) Yu, S.; Jiang, H.; Huang, S.; Peng, X.; Lu, A. Compute-in-Memory Chips for Deep Learning: Recent trends and prospects. *IEEE Circuits and Systems Magazine* **2021**, *21* (3), 31–56.

- (17) Wei, Z.; Katoh, Y.; Ogasahara, S.; Yoshimoto, Y.; Kawai, K.; Ikeda, Y.; Eriguchi, K.; Ohmori, K.; Yoneda, S., True random number generator using current difference based on a fractional stochastic model in 40-nm embedded ReRAM; 2016 IEEE International Electron Devices Meeting (IEDM); IEEE, 2016, DOI: 10.1109/iedm.2016.7838349.

- (18) Wen, C.; Li, X.; Zanotti, T.; Puglisi, F. M.; Shi, Y.; Saiz, F.; Antidormi, A.; Roche, S.; Zheng, W.; Liang, X.; Hu, J.; Duhm, S.; Roldán, J.; Wu, T.; Chen, V.; Pop, E.; Garrido, B.; Zhu, K.; Hui, F.; Lanza, M. Advanced data encryption using 2D materials. *Adv. Mater.* 2021, 33 (27), No. 2100185, DOI: 10.1002/adma.202100185.

- (19) Carboni, R.; Ielmini, D. Stochastic memory devices for security and computing. *Adv. Electron. Mater.* **2019**, *5* (9), No. 201900198, DOI: 10.1002/aelm.201900198.

- (20) Aldana, S.; García-Fernández, P.; Rodríguez-Fernández, A.; Romero-Zaliz, R.; González, M.; Jiménez-Molinos, F.; Campabadal, F.; Gómez-Campos, F. M.; Roldán, J. A 3D Kinetic Monte Carlo simulation study of resistive switching processes in NI/HFO2/SI-N +-based RRAMs. J. Phys. D: Appl. Phys. 2017, 50 (33), 335103.

- (21) Funck, C.; Menzel, S. Comprehensive model of electron conduction in Oxide-Based Memristive Devices. ACS Applied Electronic Materials 2021, 3 (9), 3674–3692.

- (22) Ielmini, D., Waser, R., Resistive Switching: From Fundamentals of Nanoionic Redox Processes to Memristive Device Applications. Wiley-VCH, 2015. ISBN: 978-3-527-33417-9.

- (23) Aldana, S.; García-Fernández, P.; Romero-Záliz, R.; González, M.; Jiménez-Molinos, F.; Gómez-Campos, F. M.; Campabadal, F.; Roldán, J. Resistive switching in HFO2 based valence change memories, a comprehensive 3D kinetic Monte Carlo approach. *J. Phys. D: Appl. Phys.* **2020**, 53 (22), 225106.

- (24) Kim, S.; Du, C.; Sheridan, P.; Ma, W.; Choi, S. H.; Lü, W. Experimental demonstration of a Second-Order memristor and its ability to biorealistically implement synaptic plasticity. *Nano Lett.* **2015**, *15* (3), 2203–2211.

- (25) Roldán, J.; González-Cordero, G.; Picos, R.; Miranda, E.; Palumbo, F.; Jiménez-Molinos, F.; Moreno, E. M. O.; Maldonado, D.; Baldomá, S. B.; Chawa, M. M. A.; De Benito, C.; Stavrinides, S. G.; Suñé, J.; Chua, L. O. On the thermal models for resistive random access memory circuit simulation. *Nanomaterials* **2021**, *11* (5), 1261.

- (26) Von Witzleben, M.; Fleck, K.; Funck, C.; Baumkötter, B.; Zuric, M.; Idt, A.; Breuer, T.; Waser, R.; Böttger, U.; Menzel, S. Investigation of the impact of high temperatures on the switching kinetics of Redox-Based resistive switching cells using a High-Speed Nanoheater. *Adv. Electron. Mater.* **2017**, 3 (12), No. 201700294, DOI: 10.1002/aelm.201700294.

- (27) Ielmini, D. Modeling the universal Set/Reset characteristics of bipolar RRAM by field- and Temperature-Driven filament growth. *IEEE Trans. Electron Devices* **2011**, 58 (12), 4309–4317.

- (28) Roldán, J. B.; Miranda, E.; Maldonado, D.; Mikhaylov, A. N.; Agudov, N. V.; Dubkov, A. A.; Koryazhkina, M. N.; González, M.; Villena, M. A.; Poblador, S.; Saludes-Tapia, M.; Picos, R.; Jiménez-Molinos, F.; Stavrinides, S. G.; Salvador, E.; Alonso, F.; Campabadal, F.; Spagnolo, B.; Lanza, M.; Chua, L. O. Variability in resistive memories. *Adv. Intell. Syst.* **2023**, *5* (6), No. 2200338, DOI: 10.1002/aisy.202200338.

- (29) Acal, C.; Maldonado, D.; Aguilera, A. M.; Zhu, K.; Lanza, M.; Roldán, J. Holistic variability analysis in resistive switching memories using a Two-Dimensional Variability Coefficient. ACS Appl. Mater. Interfaces 2023, 15 (15), 19102–19110.

- (30) Swoboda, T.; Gao, X.; Rosário, C. M. M.; Hui, F.; Zhu, K.; Yuan, Y.; Deshmukh, S.; Köroğlu, Ç.; Pop, E.; Lanza, M.; Hilgenkamp, H.; Rojo, M. M. Spatially-Resolved thermometry of filamentary nanoscale hot spots in TIO2 resistive random access memories to address device variability. ACS Applied Electronic Materials 2023, 5 (9), 5025–5031.

- (31) Guan, X.; Yu, S.; Wong, H. A SPICE compact model of metal oxide resistive switching memory with variations. *IEEE Electron Device Lett.* **2012**, 33 (10), 1405–1407.

- (32) Jiang, Z.; Yu, S.; Wu, Y.; Engel, J.; Guan, X.; Wong, H. P., Verilog-A compact model for oxide-based resistive random access memory (RRAM); International Conference on Simulation of Semiconductor Processes and Devices (SISPAD); IEEE, 2014, DOI: 10.1109/sispad.2014.6931558.

- (33) Jiang, Z.; Wu, Y.; Yu, S.; Yang, L.; Song, K.; Karim, Z.; Wong, H. P. A compact model for Metal—Oxide resistive random access memory with experiment verification. *IEEE Trans. Electron Devices* **2016**, 63 (5), 1884–1892.

- (34) Chen, P.; Yu, S. Compact modeling of RRAM devices and its applications in 1T1R and 1S1R array design. *IEEE Trans. Electron Devices* **2015**, 62 (12), 4022–4028.

- (35) Swoboda, T.; Wainstein, N.; Deshmukh, S.; Köroğlu, Ç.; Gao, X.; Lanza, M.; Hilgenkamp, H.; Pop, E.; Yalon, E.; Rojo, M. M. Nanoscale temperature sensing of electronic devices with calibrated scanning thermal microscopy. *Nanoscale* **2023**, *15* (15), 7139–7146.

- (36) Deshmukh, S.; Rojo, M. M.; Yalon, E.; Vaziri, S.; Köroğlu, Ç.; Islam, R.; Iglesias, R. A.; Saraswat, K. C.; Pop, E. Direct measurement of nanoscale filamentary hot spots in resistive memory devices. *Sci. Adv.* 2022, 8 (13), No. eabk1514, DOI: 10.1126/sciadv.abk1514.

- (37) Sandell, S.; Maire, J.; Chávez-Ángel, E.; Torres, C. M. S.; He, J.; Zhang, Z.; He, J. Enhancement of thermal boundary conductance of Metal—Polymer system. *Nanomaterials* **2020**, *10* (4), 670.

- (38) Scott, E. A.; Gaskins, J. T.; King, S. W.; Hopkins, P. E. Thermal conductivity and thermal boundary resistance of atomic layer deposited high-K dielectric aluminum oxide, hafnium oxide, and titanium oxide thin films on silicon. *APL Mater.* **2018**, *6* (5), No. 058302, DOI: 10.1063/1.5021044.

- (39) Miranda, E.; Walczyk, C.; Wenger, C.; Schroeder, T. Model for the resistive switching effect in HFO2MIM structures based on the transmission properties of narrow constrictions. *IEEE Electron Device Lett.* **2010**, *31* (6), 609–611.

- (40) Prócel, L. M.; Trojman, L.; Moreno, J.; Crupi, F.; Maccaronio, V.; Degraeve, R.; Goux, L.; Simoen, E. Experimental evidence of the quantum point contact theory in the conduction mechanism of bipolar HFO2-based resistive random access memories. *J. Appl. Phys.* **2013**, *114* (7), No. 074509, DOI: 10.1063/1.4818499.

- (41) Roldán, J.; Miranda, E.; González-Cordero, G.; García-Fernández, P.; Romero-Záliz, R.; González-Rodelas, P.; Aguilera, A. M.; González, M.; Jiménez-Molinos, F. Multivariate analysis and extraction of parameters in resistive RAMs using the Quantum Point Contact model. *J. Appl. Phys.* **2018**, *123* (1), No. 014501, DOI: 10.1063/1.5006995.

- (42) Villena, M. A.; González, M.; Jiménez-Molinos, F.; Campabadal, F.; Roldán, J.; Suñé, J.; Romera, E.; Miranda, E. Simulation of thermal reset transitions in resistive switching memories including quantum effects. *J. Appl. Phys.* **2014**, *115* (21), 214504 DOI: 10.1063/1.4881500.

- (43) Lian, X.; Cartoixà, X.; Miranda, E.; Perniola, L.; Rurali, R.; Long, S.; Liu, M.; Suñé, J., Quantum Point Contact model for filamentary conduction in resistive switching devices; 2012 13th International Conference on Ultimate Integration on Silicon (ULIS), Grenoble, France, 2012, pp. 101–104, DOI: 10.1109/ULIS.2012.6193367.

- (44) Chiu, Y.-C.; Hu, H.-W.; Lai, L.-Y.; Huang, T.-Y.; Kao, H.-Y.; Chang, K.-T.; Ho, M.-S.; Chou, C.-C.; Chih, Y.-D.; Chang, T.-Y.; Chang, M.-F., A 40nm 2MB ReRAM macro with 85% reduction in formin time and 99% reduction in Page-Write time using Autoforming and Auto-Write schemes; *IEEE Conference Publication* | *IEEE Xplore*, 2019. https://ieeexplore.ieee.org/document/8776540.

- (45) Kim, M.; Pallecchi, E.; Ge, R.; Wu, X.; Ducournau, G.; Lee, J. C.; Happy, H.; Akinwande, D. Analogue switches made from boron nitride monolayers for application in 5G and terahertz communication systems. *Nature Electronics* **2020**, 3 (8), 479–485.

- (46) Nili, H.; Adam, G. C.; Hoskins, B. D.; Prezioso, M.; Kim, J.; Mahmoodi, M. R.; Bayat, F. M.; Kavehei, O.; Strukov, D. B. Hardware-intrinsic security primitives enabled by analogue state and nonlinear conductance variations in integrated memristors. *Nature Electronics* **2018**, *1* (3), 197–202.

- (47) Chen, S.; Mahmoodi, M. R.; Shi, Y.; Mahata, C.; Yuan, B.; Liang, X.; Wen, C.; Hui, F.; Akinwande, D.; Strukov, D. B.; Lanza, M. Wafer-scale integration of two-dimensional materials in high-density memristive crossbar arrays for artificial neural networks. *Nature Electronics* **2020**, 3 (10), 638–645.

- (48) Zhu, K.; Pazos, S.; Aguirre, F.; Shen, Y.; Yuan, Y.; Zheng, W.; Alharbi, O.; Villena, M. A.; Fang, B.; Li, X.; Milozzi, A.; Farronato, M.; Rojo, M. M.; Wang, T.; Li, R.; Fariborzi, H.; Roldán, J. B.; Benstetter, G.; Zhang, X.; Lanza, M. Hybrid 2D—CMOS microchips for memristive applications. *Nature* 2023, 618 (7963), 57–62.

- (49) Ibáñez, M., Barrera, D., Maldonado, D., Yáñez, R. J.; Roldán, J. (2021). Non-Uniform Spline Quasi-Interpolation to extract the series resistance in resistive switching memristors for compact modeling purposes. Mathematics, 9(17), 2159.

- (50) Maldonado, D.; Aguirre, F.; González-Cordero, G.; Roldán, A.; González, M.; Jiménez-Molinos, F.; Campabadal, F.; Miranda, E.; Roldán, J. Experimental study of the series resistance effect and its impact on the compact modeling of the conduction characteristics of HFO2-based resistive switching memories. *J. Appl. Phys.* **2021**, *130* (5), No. 054503, DOI: 10.1063/5.0055982.

- (51) Sangwan, V.; Lee, H. S.; Bergeron, H.; Balla, I.; Beck, M. E.; Chen, K. S.; Hersam, M. C. Multi-terminal memtransistors from

- polycrystalline monolayer molybdenum disulfide. *Nature* **2018**, *554*, 500–504.

- (52) Lin, Z.; Liu, Y.; Halim, U.; Ding, M.; Liu, Y.; Wang, Y.; Jia, C.; Chen, P.; Duan, X.; Wang, C.; Song, F.; Li, M.; Wan, C.; Huang, Y.; Duan, X. Solution-processable 2D semiconductors for high-performance large-area electronics. *Nature* **2018**, *562*, 254–258.

- (53) Marega, G.; Zhao, Y.; Avsar, A.; Wang, Z.; Tripathi, M.; Radenovic, A.; Kis, A. Logic-in-memory based on an atomically thin semiconductor. *Nature* **2020**, *587*, 72–77.

- (54) Mennel, L.; Symonowicz, J.; Wachter, S.; Polyushkin, D. K.; Molina-Mendoza, A. J.; Mueller, T. Ultrafast machine vision with 2D material neural network image sensors. *Nature* **2020**, *579*, 62–66.

- (55) O'Brien, K. P.; Dorow, C. J.; Penumatcha, A.; Maxey, K.; Lee, S.; Naylor, C. H.; Hsiao, A.; Holybee, B.; Rogan, C.; Adams, D.; Tronic, T.; Ma, S.; Oni, A.; Sen Gupta, A.; Bristol, R.; Clendenning, S.; Metz, M., Advancing 2D Monolayer CMOS Through Contact, Channel and Interface Engineering. *IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA*, 2021, pp. 7.1.1–7.1.4, DOI: 10.1109/IEDM19574.2021.9720651.

- (56) Dorow, C. J.; O'Brien, K. P.; Naylor, C. H.; Lee, S.; Penumatcha, A.; Hsiao, A.; Tronic, T.; Christenson, M.; Maxey, K.; Zhu, H.; Oni, A.; Alaan, U. S.; Gosavi, T. A.; Gupta, A. S.; Bristol, R.; Clendenning, S.; Metz, M.; Avci, U. E., Advancing Monolayer 2D NMOS and PMOS Transistor Integration From Growth to Van Der Waals Interface Engineering for Ultimate CMOS Scaling; 2021 Symposium on VLSI Technology, IEEE, 2021, pp. 1–2.