PhD dissertation

# A Flexible System-on-Chip FPGA Architecture for Prototyping Experimental GNSS Receivers

Author

Marc Majoral Ramoneda

PhD Advisors

Dr. Carles Fernández Prades and Dr. Javier Arribas Lázaro Centre Tecnològic de Telecomunicacions de Catalunya Parc Mediterrani de la Tecnologia Av. Carl Friedrich Gauss 7, Building B4 08860 Castelldefels

PhD Tutor

Prof. Ana Isabel Pérez Neira Universitat Politècnica de Catalunya (UPC) Campus Nord UPC, Edifici D5 Jordi Girona, 1-3 08034 Barcelona

Universitat Politècnica de Catalunya

A la meva família i amics.

iv

# Abstract

Global Navigation Satellite System (GNSS) technology is evolving at a rapid pace, necessitating the use of advanced prototyping tools for researching new and innovative signals and systems. Prototyping plays a crucial role in the design and development process as it allows researchers to test and validate their ideas before large-scale deployment. It facilitates the exploration of concepts, enabling researchers to identify drawbacks and areas for improvement early in the development process. Moreover, it aids in demonstrating the feasibility and potential of a concept, making it easier to attract funding and support for further research.

Prototyping with readily available GNSS receivers presents challenges. Presently, GNSS receivers are mainly built-up in Application-Specific Integrated Circuits (ASICs), providing low power consumption with small size and low cost, but offering limited flexibility. While some commercial devices utilize Software-Defined Radio (SDR) techniques, they often incorporate proprietary code, restricting reconfigurability through a predefined Application Programming Interface (API).

Free and Open Source Software (FOSS) GNSS receivers have emerged as valuable resources in the realm of research and development, particularly for those in the field of satellite navigation. These software-based receivers are highly appreciated for their customization and flexibility, allowing researchers to tailor the software to suit specific experimental requirements or to innovate new signal processing algorithms. However, compared to their hardware-based counterparts, these receivers are generally less power-efficient and offer lower performance. This is because they usually operate on general-purpose processors, like those in regular computers, which are not designed for low-power usage.

This thesis focuses on designing and developing a low-cost System on Chip (SoC) Field Programmable Gate Array (FPGA) architecture for prototyping experimental GNSS receivers. This architecture addresses the limitations of commercial GNSS receivers by emphasizing customization, flexibility, and reprogrammability, and it achieves improved power efficiency over conventional designs reliant on general-purpose processors. The core idea is to combine the versatility and adaptability of SDR concepts with the massive parallelism and improved power consumption of reprogrammable hardware, offering the best of both worlds. This combination enables the development of compact, portable, multi-band, and multiconstellation GNSS receivers, facilitating the development of embedded devices suitable for field testing. Additionally, the core GNSS processing engine is based on a free and opensource software receiver, enabling detailed access to the signal processing path and thorough cross-examination of the underlying mechanisms.

This thesis also introduces a comprehensive design methodology for developing novel GNSS signal processing algorithms and concept demonstrators, utilizing the newly proposed SoC FPGA architecture. This methodology places significant emphasis on code reuse, which is relevant for reducing developmental costs and time. Reusing code increases the added value of the proposed architecture by enabling the progressive incorporation of new features into the architecture, further enhancing its adaptability and efficiency. This facilitates the adaptation of GNSS receivers across various research applications, thereby streamlining and economizing the development process.

The practical applications of this architecture have been demonstrated through three develop-

ments: a spaceborne GNSS receiver, a GNSS rebroadcaster, and a High Sensitivity (HS) GNSS receiver.

The spaceborne receiver is a low-power, multi-frequency, multi-constellation concept demonstrator designed for space applications, featuring a form factor suitable for CubeSats. It has been tested using live signals, assessing the quality of the navigation solutions, and demonstrating its capability to process GNSS signals in Low Earth Orbit (LEO) scenarios.

The GNSS rebroadcaster is a low-power, Small Form Factor (SFF) signal generator and regenerator capable of transmitting and retransmitting GNSS signals with minimal delay. It can modify the retransmitted navigation solutions in real-time, potentially enabling the replication of movement dynamics in multiple scenarios. The rebroadcaster has undergone testing to assess the quality and the latency of the regenerated signals. This design integrates advanced capabilities for GNSS signal generation and regeneration within the proposed SoC FPGA architecture.

The HS GNSS receiver is a portable device designed for processing weak signals. It is capable of acquiring and tracking severely attenuated GNSS signals with a Carrier-to-Noise Density Ratio  $(C/N_0)$  down to 20 dB-Hz in real time. The HS GNSS receiver is ideal for developing and testing experimental GNSS algorithms, particularly those related to positioning in weak signal conditions. It has been evaluated for its ability to acquire and track weak signals and obtain navigation solutions.

The novel approach presented in this thesis facilitates the development of flexible and portable GNSS receiver and signal generator prototypes with non-standard capabilities. These prototypes are designed for operation in battery-powered devices, making them suitable for both laboratory experiments and field testing.

## Resum

La ràpida evolució en la tecnologia de navegació per satèl·lit (GNSS) requereix eines de prototipatge avançades per a l'exploració de nous senyals i el desenvolupament de sistemes innovadors. El prototipatge és essencial en el procés de disseny i desenvolupament, ja que permet als investigadors provar i perfeccionar les seves idees abans de dur a terme una implementació a gran escala. Els models preliminars faciliten l'exploració de conceptes i ajuden a identificar limitacions i oportunitats de millora des de les primeres fases de desenvolupament d'un producte. A més, contribueixen a demostrar la viabilitat i el potencial dels dissenys, la qual cosa facilita l'obtenció de finançament i suport per a futures investigacions.

El prototipatge utilitzant receptors GNSS comercials planteja diversos reptes. En l'actualitat, aquests receptors es basen majoritàriament en circuits integrats d'aplicació específica (ASICs), els quals es caracteritzen per un consum energètic reduït, dimensions compactes i un cost baix, però ofereixen una flexibilitat limitada. Tot i que alguns dispositius comercials incorporen tècniques de ràdio definida per programari (SDR), aquests freqüentment contenen codi propietari que en restringeix la reconfiguració mitjançant una interfície de programació d'aplicacions (API) establerta pel fabricant.

Els receptors GNSS basats en programari lliure i codi obert han esdevingut recursos molt valuosos en el camp de la recerca i desenvolupament, especialment en el camp de la navegació per satèl·lit. Aquests receptors són molt valorats per la seva adaptabilitat i flexibilitat, permetent als investigadors adaptar el programari a necessitats experimentals específiques o desenvolupar nous algoritmes de processament de senyal. Tanmateix, els receptors definits per programari solen ser menys eficients energèticament en comparació amb els receptors basats en maquinari, ja que operen en processadors de propòsit general, que no estan optimitzats per a un baix consum energètic.

Aquesta tesi se centra en el disseny i desenvolupament d'una arquitectura de baix cost per al prototipatge de receptors GNSS experimentals, basada en sistemes en un xip amb matrius de portes lògiques programables in situ (SoC FPGA). Aquesta arquitectura supera les limitacions dels receptors GNSS comercials en termes d'adaptabilitat, flexibilitat i capacitat de reprogramació, i ofereix una eficiència energètica millorada en comparació amb els receptors basats en programari que depenen de processadors de propòsit general. L'estratègia consisteix a combinar la versatilitat de la ràdio definida per programari amb el paral·lelisme intensiu i el consum energètic optimitzat del maquinari reprogramable, proporcionant el millor de tots dos mons. Aquesta fusió permet el desenvolupament de receptors GNSS compactes, portàtils i capaços de treballar simultàniament en diverses bandes de freqüència i amb diferents sistemes GNSS, facilitant així el prototipatge de dispositius encastats adequats per a proves de camp. A més, el nucli de processament GNSS es basa en una implementació de programari lliure i obert, que proporciona un accés detallat a la cadena de processament de senyal i permet una exploració i modificació sense restriccions dels algoritmes utilitzats.

Aquesta tesi també presenta una metodologia de disseny per al desenvolupament de nous prototips i nous algoritmes de processament de senyal GNSS basats en l'arquitectura SoC FPGA que es proposa. Aquesta metodologia posa especial èmfasi en la reutilització de codi, aspecte clau per a reduir els costos i temps de desenvolupament. La reutilització de codi

augmenta el valor afegit de l'arquitectura, permetent la incorporació progressiva de noves funcionalitats i millorant-ne la adaptabilitat i eficiència. Això facilita l'adaptació dels receptors GNSS a una àmplia gamma d'aplicacions de recerca, optimitzant i economitzant el procés de desenvolupament.

Les aplicacions pràctiques d'aquesta arquitectura s'han demostrat a través de tres prototips: un receptor GNSS per a l'espai, un retransmissor de senyals GNSS, i un receptor GNSS d'alta sensibilitat.

El receptor per a l'espai és un receptor GNSS multifreqüència i multi-constel·lació, dissenyat per a aplicacions espacials, de baix consum d'energia i amb un tamany adaptable per a CubeSats. Ha estat provat amb senyals a temps real, evaluant-ne la qualitat de les solucions de navegació, i demostrant la seva capacitat per processar senyals GNSS en escenaris d'òrbita baixa terrestre (LEO).

El retransmissor de senyals GNSS és un generador i regenerador de senyals de baix consum i tamany reduït, capaç de transmetre i retransmetre senyals GNSS amb un retard mínim. Aquest regenerador pot modificar les solucions de navegació retransmeses en temps real, permetent la simulació de dinàmiques de moviment en multiples escenaris. El retransmissor ha estat provat per verificar-ne la qualitat dels senyals regenerats i per avaluar-ne la latència. Aquest disseny integra funcionalitats avançades per a la generació i la regeneració eficient de senyals GNSS, adaptades específicament a l'arquitectura SoC FPGA que es proposa en aquesta tesi.

El receptor GNSS d'alta sensibilitat és un dispositiu portàtil dissenyat per processar senyals febles. És capaç d'adquirir i fer seguiment en temps real de senyals GNSS extremadament atenuats amb una relació entre la potència de la portadora i la densitat espectral de soroll  $(C/N_0)$  tant baixa com 20 dB-Hz. Aquest receptor és ideal per al desenvolupament i prova d'algoritmes GNSS experimentals, especialment en condicions de senyal feble. Ha estat provat per demostrar la seva capacitat per adquirir i fer seguiment de senyals febles, i per evaluar-ne la qualitat de les solucions de navegació.

L'enfocament innovador presentat en aquesta tesi facilita al desenvolupament de prototips experimentals de receptors i generadors de senyals GNSS flexibles i portàtils, aptes tant per a experiments de laboratori com per a proves de camp.

# Acknowledgements

This thesis was conducted within the Signal Theory and Communications Department (TSC) of the Universitat Politècnica de Catalunya (UPC), concurrently with full-time employment at Centre Tecnològic de Telecomunicacions de Catalunya (CTTC). The research presented in this thesis was supported by a diverse array of funding sources and collaborations, highlighting the multi-institutional efforts involved.

The European Commission provided support under grant agreement H2020-687367-AUDITOR. The European Space Agency supported this research through contract AO/2-1647/17/NL/CRS. Additionally, part of the work was carried out in the framework of the European Space Agency contract 4000133576/20/NL/CRS with SENER Aeroespacial S.A., with the CTTC serving as the subcontractor, highlighting the project's industry collaboration.

Additional financial support for this research was provided by grant RTI2018-099722-B-I00, funded by the Spanish Ministry of Science and Innovation, and grant PID2021-128373OB-I00, funded by the Spanish Ministry of Science and Innovation through MCIN/AEI/10.13039/501100011033, and by the European Regional Development Fund (ERDF) "A way of making Europe". Additional support, also from the Spanish Ministry of Science and Innovation, was received through project CPP2021-008648, titled "Receptor Abierto y Flexible de Investigación por Satélite".

I would like to thank my thesis advisors, Dr. Carles Fernández-Prades, Dr. Javier Arribas, and Prof. Ana Isabel Pérez-Neira for their invaluable guidance and support throughout the journey of my thesis. Their expertise and encouragement have been pivotal in shaping both the direction and substance of my research. Carles and Javi's rigorous approach to scientific inquiry, alongside their keen insights, has not only enriched my work but also fostered my growth as a researcher. Their dedication and commitment to excellence have inspired me at every step, making this endeavor both enlightening and rewarding. I am profoundly thankful for their mentorship in my academic development. Finally, I would like to express my gratitude to all the individuals at CTTC who encouraged and supported me during this research endeavor.

## Contents

| Ab | ostrac  | t             |                                               | v    |

|----|---------|---------------|-----------------------------------------------|------|

| Re | sum     |               |                                               | vii  |

| Ac | know    | ledgem        | ents                                          | ix   |

| Li | st of I | Figures       | 2                                             | xvii |

| Li | st of ] | <b>Fables</b> |                                               | xxi  |

| Ac | rony    | ms            | :                                             | XXV  |

| 1  | Intro   | oductio       | n                                             | 1    |

|    | 1.1     | Motiva        | ntion                                         | 2    |

|    | 1.2     | Object        | ives                                          | 5    |

|    | 1.3     | Outline       | e of the dissertation                         | 7    |

|    | 1.4     | Resear        | ch contributions                              | 9    |

|    |         | 1.4.1         | Journal papers                                | 9    |

|    |         | 1.4.2         | Peer-Reviewed International Conferences       | 9    |

|    |         | 1.4.3         | International Conferences (Non-Peer Reviewed) | 9    |

|    |         | 1.4.4         | Open-Source GNSS Receiver Contributions       | 10   |

| 2  | Bacl    | kground       | and State of the Art                          | 11   |

|    | 2.1     | Basics        | of GNSS Positioning                           | 12   |

|    | 2.2     | GNSS          | Satellite Signals                             | 14   |

|    |         | 2.2.1         | Frequency Bands                               | 14   |

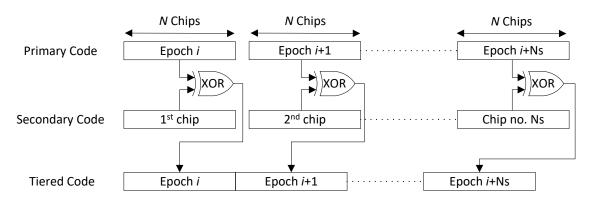

|     | 2.2.2   | Spreading Codes                                | 16 |

|-----|---------|------------------------------------------------|----|

|     | 2.2.3   | Signal Structure                               | 16 |

|     | 2.2.4   | Doppler frequency                              | 20 |

|     | 2.2.5   | Navigation Data                                | 20 |

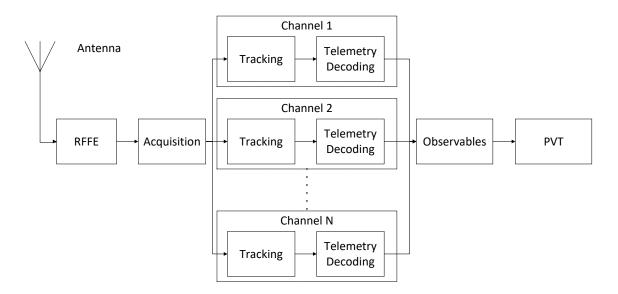

| 2.3 | Funda   | mentals of GNSS Receivers                      | 21 |

|     | 2.3.1   | GNSS Antennas                                  | 22 |

|     | 2.3.2   | Radio Frequency Front-End (RFFE)               | 23 |

|     | 2.3.3   | Analog to Digital Converter (ADC)              | 24 |

|     | 2.3.4   | Signal Acquisition                             | 25 |

|     | 2.3.5   | Signal Tracking                                | 27 |

|     | 2.3.6   | Telemetry Decoder                              | 29 |

|     | 2.3.7   | Observables                                    | 29 |

|     | 2.3.8   | Position, Velocity, and Time (PVT) computation | 29 |

| 2.4 | GNSS    | -SDR Software Receiver                         | 30 |

|     | 2.4.1   | Receiver Configuration                         | 30 |

|     | 2.4.2   | Receiver Architecture                          | 31 |

|     | 2.4.3   | Supported Output Formats                       | 33 |

|     | 2.4.4   | Cross-compiling GNSS-SDR                       | 33 |

| 2.5 | Introdu | action to FPGAs                                | 34 |

|     | 2.5.1   | Basic Building Blocks of an FPGA               | 35 |

|     | 2.5.2   | FPGA Intellectual Property (IP) Cores          | 37 |

|     | 2.5.3   | FPGA Design Flows                              | 39 |

|     | 2.5.4   | FPGA Design Tools                              | 40 |

| 2.6 | SoC F   | PGAs                                           | 41 |

|     | 2.6.1   | SoC FPGA Design Flows                          | 42 |

| 2.7 | Desigr  | Forces and Key Performance Indicators (KPIs)   | 44 |

|     | 2.7.1   | Design Forces                                  | 44 |

|     | 2.7.2   | Key Performance Indicators (KPIs)              | 45 |

|     | 2.7.3   | Time to First Fix (TTFF)                       | 46 |

|     | 2.7.4   | Precision of the Navigation Solutions          | 47 |

|   |      | 2.7.5   | Accuracy of the Navigation Solutions                    | 48 |

|---|------|---------|---------------------------------------------------------|----|

|   | 2.8  | Review  | v of Software-Defined GNSS Receivers                    | 49 |

|   | 2.9  | Summa   | ary                                                     | 52 |

| 3 | Syst | em Desi | gn and Methodology                                      | 53 |

|   | 3.1  | Propos  | ed GNSS receiver architecture                           | 54 |

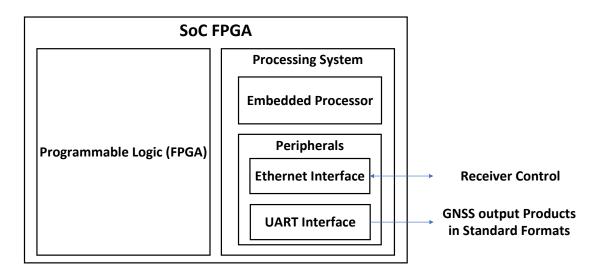

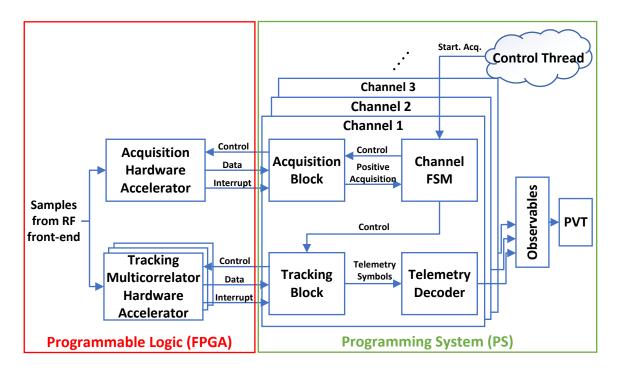

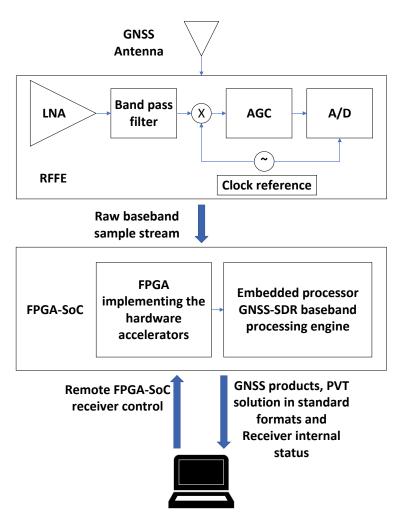

|   |      | 3.1.1   | SoC FPGA Architecture                                   | 55 |

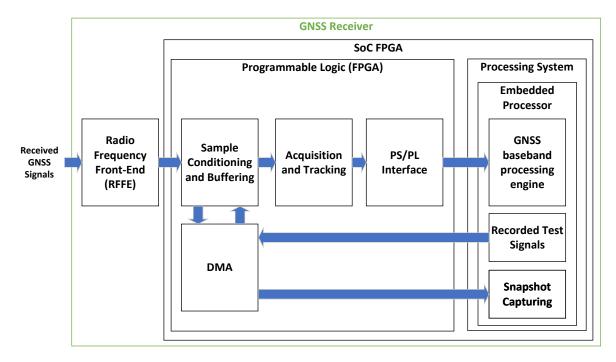

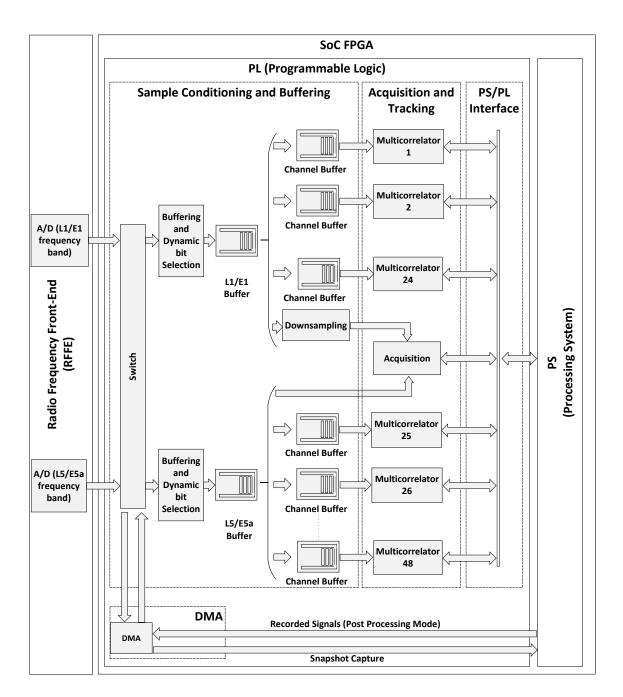

|   |      | 3.1.2   | FPGA Architecture                                       | 58 |

|   |      | 3.1.3   | Dynamic Bit Selection                                   | 61 |

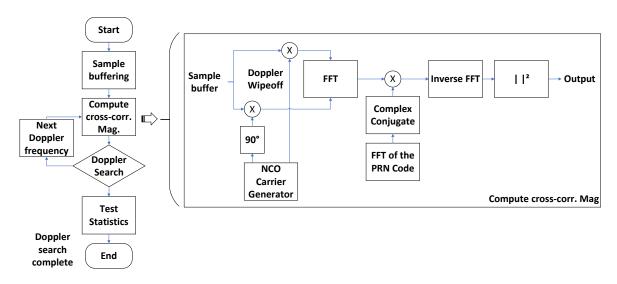

|   |      | 3.1.4   | Acquisition Hardware Accelerator                        | 61 |

|   |      | 3.1.5   | Tracking Multicorrelator Hardware Accelerators          | 63 |

|   |      | 3.1.6   | Software Architecture                                   | 66 |

|   | 3.2  | Propos  | ed Design Methodology                                   | 67 |

|   |      | 3.2.1   | Stage 1: Software Design Process                        | 69 |

|   |      | 3.2.2   | Stage 2: SoC-FPGA Design Process                        | 70 |

|   | 3.3  | Analyz  | ting Design Force and KPIs in the Proposed Architecture | 75 |

|   |      | 3.3.1   | Scalability                                             | 75 |

|   |      | 3.3.2   | Testability                                             | 76 |

|   |      | 3.3.3   | Portability                                             | 78 |

|   |      | 3.3.4   | Maintainability                                         | 78 |

|   |      | 3.3.5   | Reproducibility                                         | 79 |

|   |      | 3.3.6   | Openness                                                | 80 |

|   | 3.4  | Summa   | ary                                                     | 80 |

| 4 | Spac | ceborne | GNSS Receiver                                           | 83 |

|   | 4.1  | Introdu | iction                                                  | 84 |

|   | 4.2  | Object  | ives                                                    | 85 |

|   | 4.3  | System  | Design                                                  | 86 |

|   |      | 4.3.1   | Implementation on the ADRV9361-Z7035 Board              | 86 |

|   |      | 4.3.2   | Implementation on the ZCU102 Board                      | 92 |

|   |      | 4.3.3   | Tracking GNSS Signals in High-Dynamic Environments      | 93 |

|   |     | 4.3.4   | Telemetry and Telecontrol Interfaces                      |

|---|-----|---------|-----------------------------------------------------------|

|   | 4.4 | Test Re | esults                                                    |

|   |     | 4.4.1   | Test Results using the ADRV9361-Z7035 platform            |

|   |     | 4.4.2   | Test Results using the ZCU102 platform                    |

|   | 4.5 | Conclu  | usions                                                    |

|   | 4.A | Receiv  | er Configuration for Static Scenarios                     |

|   | 4.B | Receiv  | er Configuration for Low Earth Orbit (LEO) scenarios      |

| 5 | GNS | SS Rebr | oadcaster 121                                             |

|   | 5.1 | Introdu | action                                                    |

|   | 5.2 | Object  | ives                                                      |

|   | 5.3 | System  | n Design                                                  |

|   |     | 5.3.1   | Hardware Implementation                                   |

|   |     | 5.3.2   | Signal Model                                              |

|   |     | 5.3.3   | Rebroadcaster Architecture                                |

|   |     | 5.3.4   | Receiver Internal Status                                  |

|   | 5.4 | Transn  | nitter Design                                             |

|   |     | 5.4.1   | Software Transmitter                                      |

|   |     | 5.4.2   | Timed Commands                                            |

|   |     | 5.4.3   | FPGA Transmitter                                          |

|   |     | 5.4.4   | Telemetry Symbol Link                                     |

|   | 5.5 | Results | 5                                                         |

|   |     | 5.5.1   | GNSS Signal Raw Sample Generator Validation               |

|   |     | 5.5.2   | GNSS Signal Rebroadcasting                                |

|   |     | 5.5.3   | Latency                                                   |

|   |     | 5.5.4   | Correctness of the Rebrodcasted Navigation Message        |

|   |     | 5.5.5   | FPGA Resource Utilization                                 |

|   |     | 5.5.6   | Power Consumption                                         |

|   | 5.6 | Conclu  | usions                                                    |

|   | 5.A | Receiv  | er Configuration for Rebroadcasting Galileo E1b/c Signals |

| 6 | Higl | n-Sensit | ivity GNSS Receiver                                                    | 149   |

|---|------|----------|------------------------------------------------------------------------|-------|

|   | 6.1  | Introdu  | action                                                                 | . 150 |

|   | 6.2  | Backgr   | round                                                                  | . 152 |

|   | 6.3  | Object   | ives                                                                   | . 154 |

|   | 6.4  | System   | n Design                                                               | . 155 |

|   |      | 6.4.1    | High Sensitivity GNSS Receiver Architecture                            | . 155 |

|   |      | 6.4.2    | Receiver Operating Modes                                               | . 158 |

|   |      | 6.4.3    | Assistance Data                                                        | . 159 |

|   |      | 6.4.4    | Acquisition in High-Sensitivity Mode                                   | . 160 |

|   |      | 6.4.5    | Doppler Prediction                                                     | . 171 |

|   |      | 6.4.6    | Acquisition in Normal-Sensitivity Mode                                 | . 173 |

|   |      | 6.4.7    | Tracking                                                               | . 174 |

|   |      | 6.4.8    | Telemetry Decoding                                                     | . 175 |

|   |      | 6.4.9    | Computation of the Navigation Solutions                                | . 177 |

|   |      | 6.4.10   | GNSS Output Products                                                   | . 177 |

|   | 6.5  | Results  | S                                                                      | . 177 |

|   |      | 6.5.1    | Test Setup                                                             | . 178 |

|   |      | 6.5.2    | High-Sensitivity Acquisition Latency                                   | . 179 |

|   |      | 6.5.3    | Acquisition and Tracking of GNSS Signals in Real Time                  | . 184 |

|   |      | 6.5.4    | Precision of the Navigation Solutions                                  | . 186 |

|   |      | 6.5.5    | FPGA Resource Utilization                                              | . 188 |

|   |      | 6.5.6    | Estimated Power Consumption                                            | . 189 |

|   | 6.6  | Conclu   | isions                                                                 | . 190 |

|   | 6.A  | Receiv   | er configuration for Galileo E1 b/c signals in high-sensitivity mode   | . 192 |

|   | 6.B  |          | er configuration for Galileo E5a and GPS signals in normal-sensitivity | . 194 |

|   | 6.C  | Receiv   | er configuration for PVT                                               | . 196 |

| 7 | Con  | clusions | s and Directions for Future Work                                       | 197   |

|   | Bibl | iograph  | y                                                                      | 203   |

xvi

## **List of Figures**

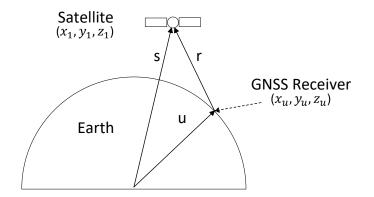

| 2.1  | Vector representation of the receiver position                                                          | 13 |

|------|---------------------------------------------------------------------------------------------------------|----|

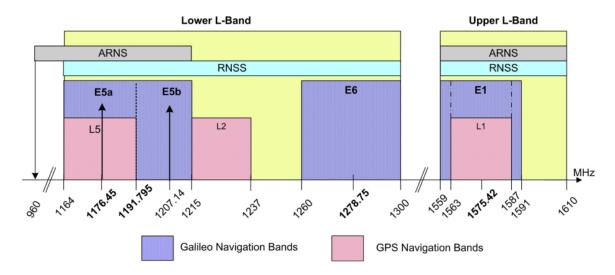

| 2.2  | GPS and Galileo frequency bands                                                                         | 15 |

| 2.3  | Tiered codes generation.                                                                                | 16 |

| 2.4  | GNSS receiver block diagram.                                                                            | 21 |

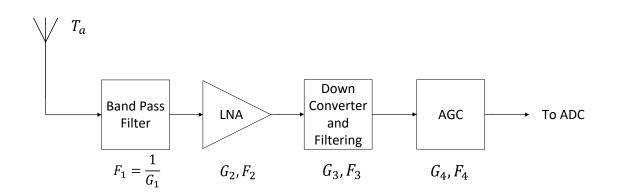

| 2.5  | Example Block Diagram of a GNSS receiver's RFFE.                                                        | 24 |

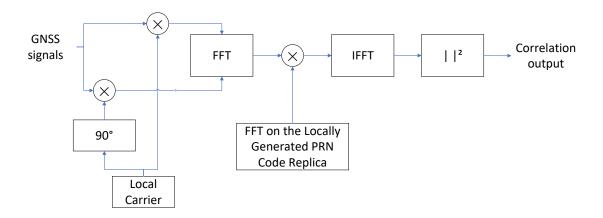

| 2.6  | Parallel Code Phase Search (PCPS) algorithm                                                             | 27 |

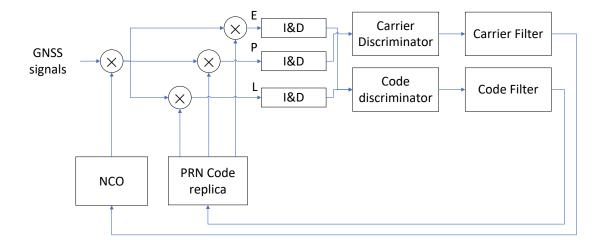

| 2.7  | Tracking Loop.                                                                                          | 28 |

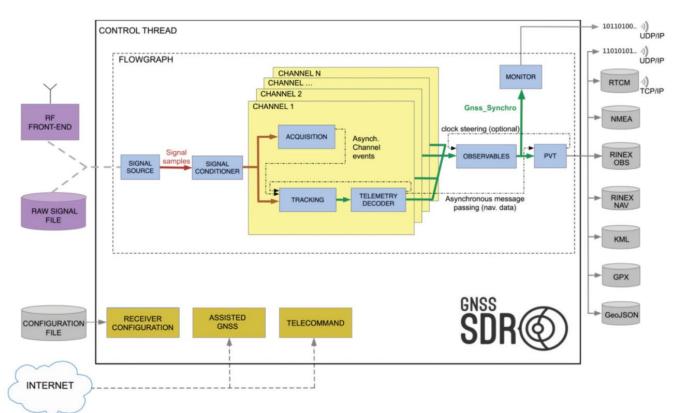

| 2.8  | Software architecture of the GNSS-SDR software receiver                                                 | 32 |

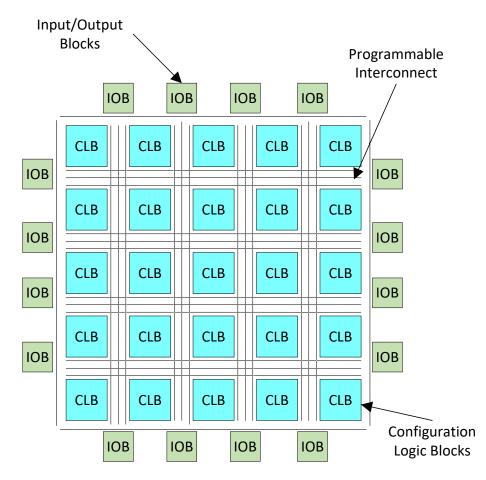

| 2.9  | Simplified FPGA block diagram (DSP blocks, RAM blocks and other specialized hardware blocks not shown). | 36 |

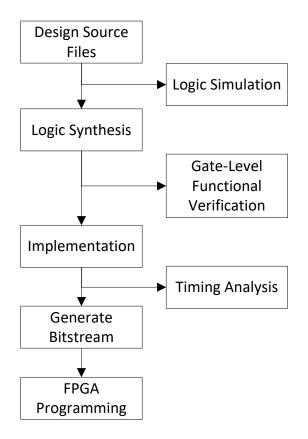

| 2.10 | Simplified FPGA design flow.                                                                            | 40 |

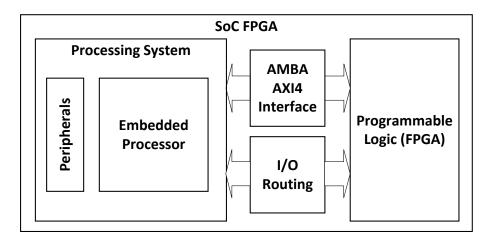

| 2.11 | Simplified SoC FPGA block diagram.                                                                      | 41 |

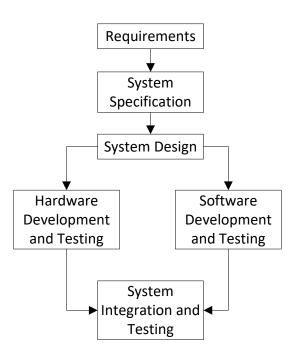

| 2.12 | A simple hardware/software design methodology                                                           | 43 |

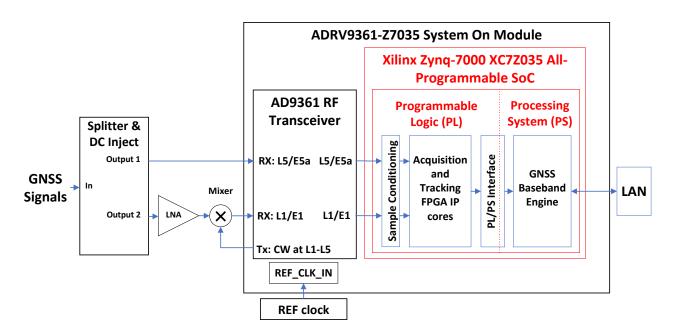

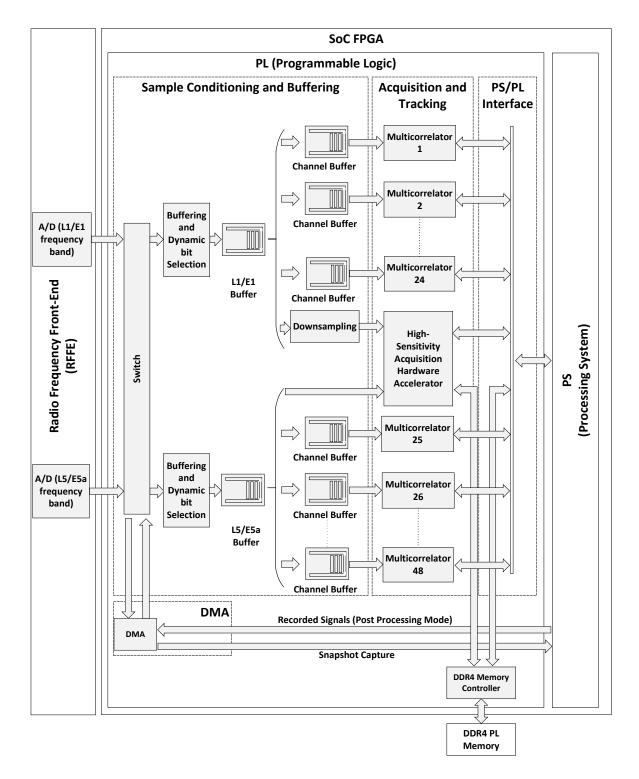

| 3.1  | SoC-FPGA Receiver block diagram.                                                                        | 55 |

| 3.2  | Receiver architecture.                                                                                  | 56 |

| 3.3  | Detailed FPGA design.                                                                                   | 59 |

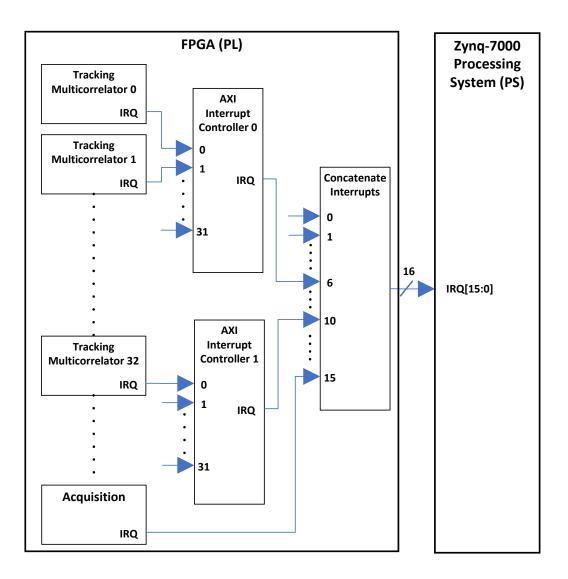

| 3.4  | FPGA acquisition hardware accelerator.                                                                  | 63 |

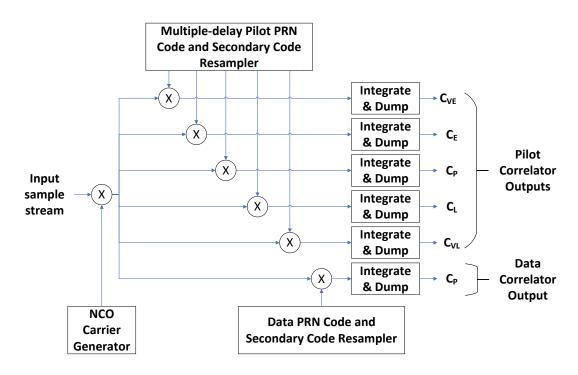

| 3.5  | FPGA tracking multicorrelator hardware accelerator.                                                     | 65 |

| 3.6  | Interface between the FPGA IPs and the GNSS-SDR software receiver                                       | 67 |

| 3.7  | Host-based GNSS-SDR receiver.                                                                           | 69 |

| 3.8  | SoC-FPGA GNSS receiver.                                                                                 | 70 |

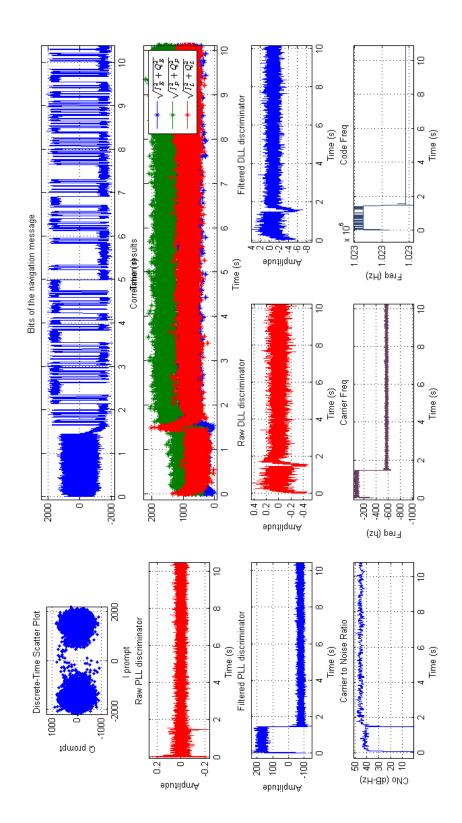

| 3.9  | Status of the GPS L1 C/A tracking loops                                                                 | 77 |

| 4.1  | Spaceborne GNSS receiver block diagram using the ADRV9361-Z7035 development board                                                                      | 37      |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 4.2  |                                                                                                                                                        | 39      |

| 4.3  |                                                                                                                                                        | 90      |

| 4.4  |                                                                                                                                                        | )<br>)1 |

|      |                                                                                                                                                        | '1      |

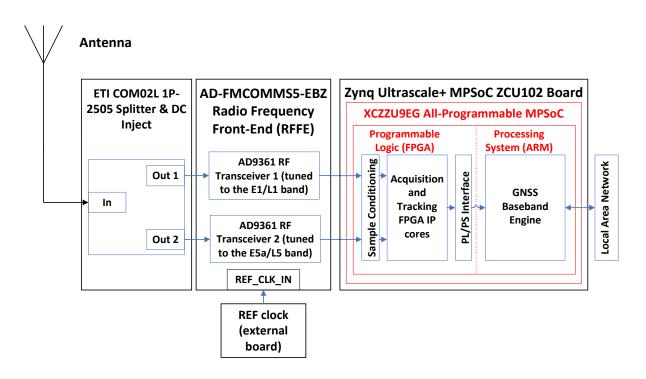

| 4.5  | Spaceborne GNSS receiver block diagram using the ZCU102 development board and the AD-FMCOMMS5-EBZ Radio Frequency Front-End (RFFE).                    |         |

|      | · · · · · · · · · · · · · · · · · · ·                                                                                                                  | 92      |

| 4.6  | Sample capture                                                                                                                                         | 98      |

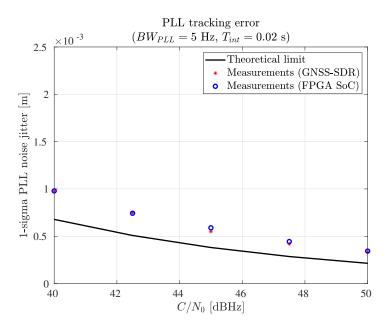

| 4.7  | Receiver carrier phase RMSE (1-sigma) when using the FPGA-SoC (stars) and when using GNSS-SDR in software mode (circles).                              | )6      |

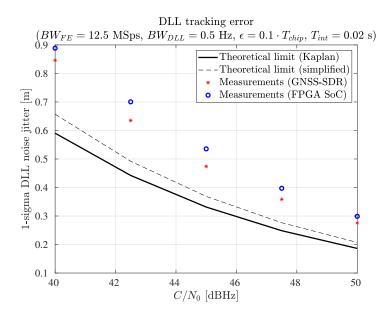

| 4.8  | Receiver code phase RMSE (1-sigma) when using the FPGA-SoC (stars) and when using GNSS-SDR in software mode (circles)                                  | )7      |

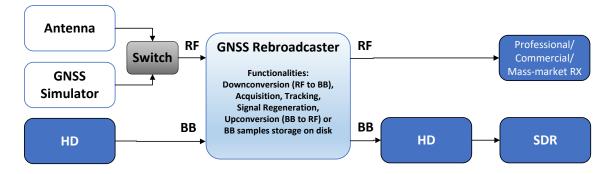

| 5.1  | GNSS Signal Rebroadcaster                                                                                                                              | 23      |

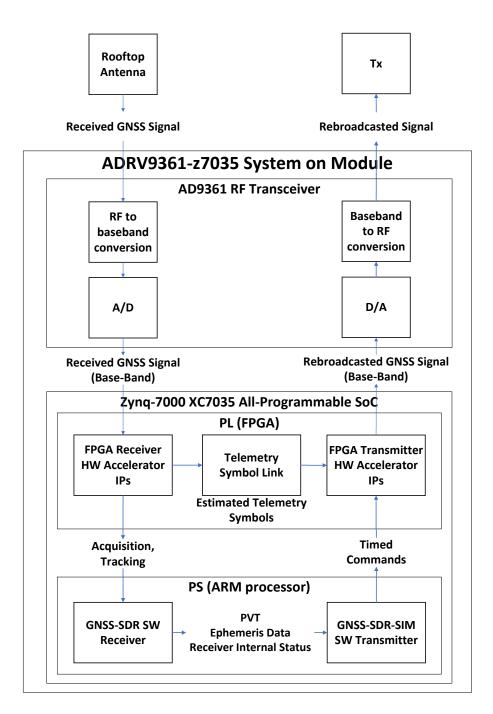

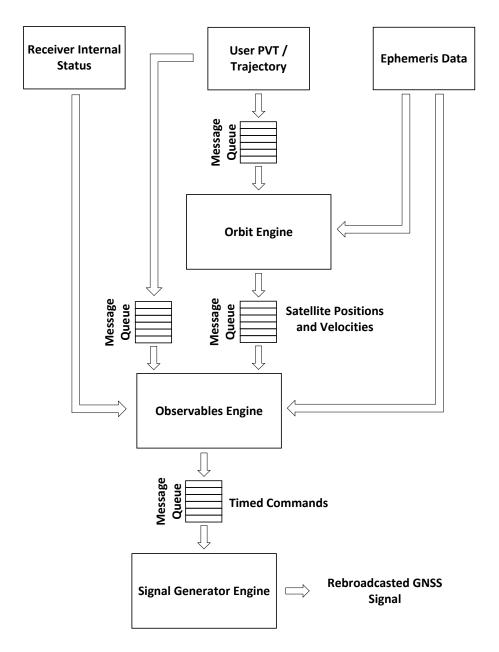

| 5.2  | GNSS Signal Regenerator block diagram                                                                                                                  | 28      |

| 5.3  | Software transmitter block diagram                                                                                                                     | 32      |

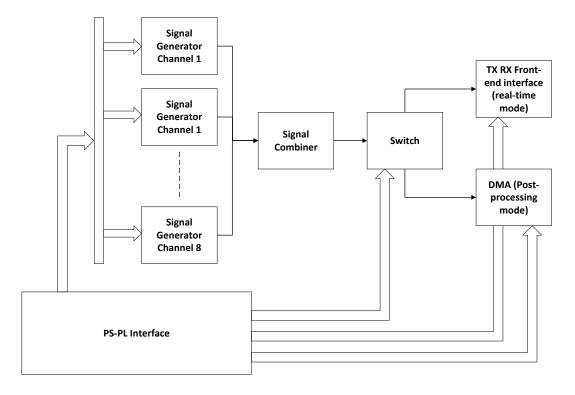

| 5.4  | FPGA Transmitter block diagram                                                                                                                         | 35      |

| 5.5  | FPGA Telemetry Symbol Link block diagram                                                                                                               | 36      |

| 5.6  | GNSS signal raw sample generator validation                                                                                                            | 38      |

| 5.7  | GNSS signal raw sample generator validation using the FPGA                                                                                             | 38      |

| 5.8  | Galileo E1 b/c signal rebroadcasting: Deviation Map Test                                                                                               | 39      |

| 5.9  | Deviation map of the received signal at the rooftop antenna                                                                                            | 10      |

| 5.10 | Deviation map of the rebroadcasted signal, centered on the average position derived from the received signal at the rooftop antenna, for comparison 14 | 40      |

| 5.11 | Telemetry Symbol Link latency                                                                                                                          | 1       |

| 6.1  | High-sensitivity GNSS receiver block diagram                                                                                                           | 55      |

| 6.2  | Detailed FPGA design                                                                                                                                   | 56      |

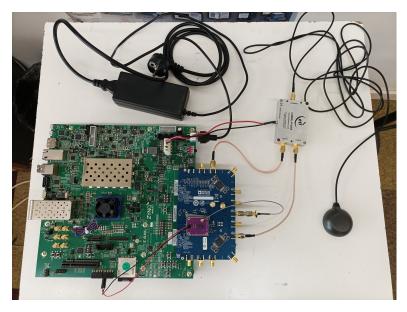

| 6.3  | Picture of the high-sensitivity GNSS receiver prototype                                                                                                | 58      |

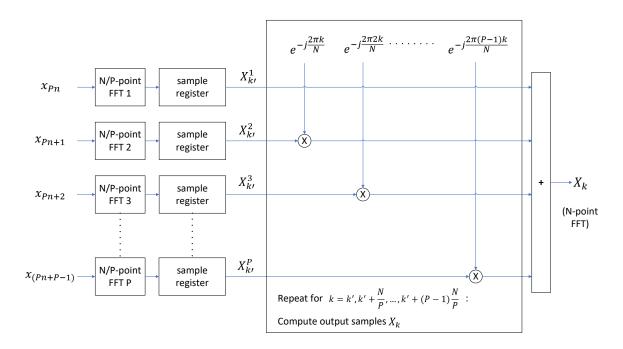

| 6.4  | Computation of an N-point FFT as a combination of P FFTs, each of $N/P$ points.16                                                                      | 53      |

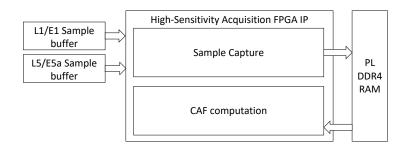

| 6.5  | High-sensitivity acquisition FPGA hardware accelerator block diagram 16                                                                                | 57      |

| 6.6  | Acquisition timing diagram.                                                                                                                            | 58      |

| 6.7 | CAF computation module.                                               | 170 |

|-----|-----------------------------------------------------------------------|-----|

| 6.8 | Large FFT/IFFT module implemented in the high-sensitivity acquisition | 171 |

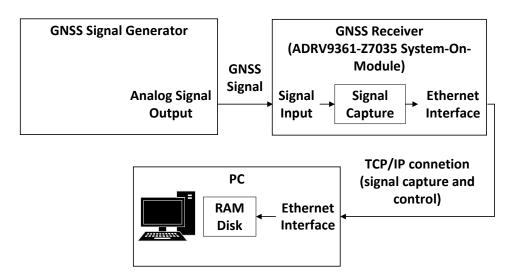

| 6.9 | Test setup for the high-sensitivity GNSS receiver.                    | 178 |

### **List of Tables**

| 2.1  | GNSS signal characteristics.                                                           | 15 |

|------|----------------------------------------------------------------------------------------|----|

| 2.2  | GPS L1 C/A signal characteristics.                                                     | 17 |

| 2.3  | GPS L5 signal characteristics.                                                         | 18 |

| 2.4  | Galileo E5a signal characteristics.                                                    | 18 |

| 2.5  | E1 Composite Binary Offset Carrier (CBOC) sub-carrier rates.                           | 19 |

| 2.6  | Galileo E1 signal characteristics.                                                     | 19 |

| 2.7  | Support of output formats                                                              | 33 |

| 2.8  | Key Performance Indicators (KPIs) for architectural and design methodology evaluation  | 45 |

| 2.9  | KPIs for concept demonstrator evaluation                                               | 46 |

| 2.10 | Most common 2D precision measures.                                                     | 47 |

| 2.11 | Most common 3D precision measures.                                                     | 47 |

| 2.12 | Most common 2D accuracy measures.                                                      | 48 |

| 2.13 | Most common 3D accuracy measures.                                                      | 49 |

| 2.14 | Table comparing related work based on publication date and underlying processing units | 51 |

| 3.1  | Notation table for the acquisition algorithm description                               | 62 |

| 3.2  | Notation table for the tracking multicorrelator algorithm description                  | 64 |

| 3.3  | Tracking multicorrelator configuration.                                                | 66 |

| 3.4  | SoC FPGA-based GNSS receiver design flow.                                              | 68 |

| 4.1  | Telecommand (ground station to satellite)                                              | 96 |

| 4.2  | Telemetry (satellite to ground station)                                                | 96 |

| 4.3  | Embedded Data logger)                                                                  | 97 |

| 4.4  | GNSS signal combinations tested in real-time using the ADRV9361-Z7035 platform         |

|------|----------------------------------------------------------------------------------------|

| 4.5  | Acquisition sensitivity                                                                |

| 4.6  | Tracking sensitivity                                                                   |

| 4.7  | FPGA resource utilization in the spaceborne receiver implemented on the XC7Z035 device |

| 4.8  | GNSS signal combinations tested using the ZCU102 platform                              |

| 4.9  | 2D precision results                                                                   |

| 4.10 | 3D precision results                                                                   |

| 4.11 | PVT accuracy using a LEO scenario                                                      |

| 4.12 | FPGA resource utilization in the spaceborne receiver implemented on the XCZU9EG device |

| 4.13 | Spaceborne receiver acquisition configuration for static scenarios                     |

| 4.14 | Spaceborne receiver GPS tracking configuration for static scenarios                    |

| 4.15 | Spaceborne receiver Galileo tracking configuration for static scenarios 116            |

| 4.16 | Spaceborne receiver PVT configuration for static scenarios                             |

| 4.17 | Spaceborne receiver acquisition configuration for LEO scenarios                        |

| 4.18 | Spaceborne receiver GPS tracking configuration for LEO scenarios                       |

| 4.19 | Spaceborne receiver Galileo tracking configuration for LEO scenarios 120               |

| 4.20 | Spaceborne receiver PVT configuration for LEO scenarios                                |

| 5.1  | Timed command parameters                                                               |

| 5.2  | Measured RMSE of position fixes                                                        |

| 5.3  | CRC Statistics of the Rooftop Antenna Signal                                           |

| 5.4  | CRC Statistics of the Rebroadcasted Signal                                             |

| 5.5  | FPGA resource utilization in the rebroadcaster implemented on the XC7Z035device        |

| 5.6  | Rebroadcaster acquisition configuration                                                |

| 5.7  | Rebroadcaster tracking configuration                                                   |

| 5.8  | Rebroadcaster PVT configuration                                                        |

| 6.1  | Default receiver operating modes                                                       |

| 6.2  | Assistance data                                                                        |

| 6.3  | Purpose of the assistance data.                                                                    | 160 |

|------|----------------------------------------------------------------------------------------------------|-----|

| 6.4  | Input parameters of the high-sensitivity acquisition.                                              | 164 |

| 6.5  | Output parameters of the high-sensitivity acquisition.                                             | 165 |

| 6.6  | Variables introduced in the description of the high-sensitivity algorithm                          | 165 |

| 6.7  | Acquisition process in two steps.                                                                  | 173 |

| 6.8  | Acquisition latency: test procedure.                                                               | 180 |

| 6.9  | CFO in the E1 frequency band when using a TXCO.                                                    | 180 |

| 6.10 | Acquisition latency using a TCXO                                                                   | 181 |

| 6.11 | List of signals acquired and tracked when utilizing a TCXO                                         | 182 |

| 6.12 | Acquisition latency using an OCXO                                                                  | 183 |

| 6.13 | Test procedure.                                                                                    | 184 |

| 6.14 | Processing GNSS signals at nominal power levels                                                    | 185 |

| 6.15 | Processing weak Galileo E1b/c signals.                                                             | 186 |

| 6.16 | The 2D precision results.                                                                          | 187 |

| 6.17 | The 3D precision results.                                                                          | 187 |

| 6.18 | Galileo satellites tracked and $C/N_0$                                                             | 188 |

| 6.19 | The 2D precision results using weak Galileo E1b/c signals                                          | 188 |

| 6.20 | The 3D precision results using weak Galileo E1b/c signals                                          | 188 |

| 6.21 | FPGA resource utilization in the high-sensitivity GNSS receiver implemented on the XCZU9EG device. | 189 |

| 6.22 | High-sensitivity receiver Galileo E1b/c acquisition configuration                                  | 192 |

| 6.23 | High-sensitivity receiver Galileo E1 b/c tracking configuration                                    | 193 |

| 6.24 | High-sensitivity receiver GPS and Galileo E5a acquisition configuration (normal-sensitivity mode). | 194 |

| 6.25 | High-sensitivity receiver GPS tracking configuration (normal-sensitivity mode).                    | 195 |

| 6.26 | High-sensitivity receiver Galileo E5a tracking configuration (normal-sensitivity mode)             | 195 |

| 6.27 | High-sensitivity receiver PVT configuration.                                                       | 196 |

## Acronyms

| $C/N_0$ | Carrier-to-Noise Density Ratio                      |

|---------|-----------------------------------------------------|

| 5G      | 5th Generation                                      |

| A-GNSS  | Assisted Global Navigation Satellite System         |

| ADC     | Analog to Digital Converter                         |

| AGC     | Automatic Gain Control                              |

| AI      | Artificial Intelligence                             |

| AltBOC  | Alternative Binary Offset Carrier                   |

| AMBA    | Advanced Microcontroller Bus Architecture           |

| AMD     | Advanced Micro Devices                              |

| API     | Application Programming Interface                   |

| ARNS    | Aeronautical Radio Navigation Service               |

| ASIC    | Application-Specific Integrated Circuit             |

| AXI     | Advanced eXtensible Interface                       |

| AXI4    | Advanced eXtensible Interface 4th generation        |

| BDT     | Beidou Time                                         |

| BPSK    | Binary Phase Shift Keying                           |

| BRAM    | Block Random Access Memory                          |

| C/A     | Coarse Acquisition                                  |

| CAF     | Cross-ambiguity function                            |

| CBOC    | Composite Binary Offset Carrier                     |

| CEP     | Circular Error Probability                          |

| CFAR    | Constant False Alarm Rate                           |

| CFO     | Carrier Frequency Offset                            |

| CI      | Coherent Integration                                |

| CLB     | Configurable Logic Block                            |

| CMOS    | Complementary Metal-Oxide-Semiconductor             |

| CMT     | Clock Management Tile                               |

| COTS    | Commercial Off-The-Shelf                            |

| CPU     | Central Processing Unit                             |

| CRC     | Cyclic Redundancy Check                             |

| CSAC    | Chip Scale Atomic Clock                             |

| CSV     | Comma-Separated Values                              |

| CTTC    | Centre Tecnològic de Telecomunicacions de Catalunya |

| CW      | Continuous Wave                                     |

| DAC     | Digital-to-Analog Converter                         |

| DDR     | Double Data Rate                                    |

| DDR3     | Double Data Rate 3                                          |

|----------|-------------------------------------------------------------|

| DDR4     | Double Data Rate 4                                          |

| DFT      | Discrete Fourier Transform                                  |

| DLL      | Delay-Locked Loop                                           |

| DMA      | Direct Memory Access                                        |

| DOP      | Dilution of Precision                                       |

| DPDI     | Differential Post-Detection Integration                     |

| DRMS     | Distance Root Mean Square                                   |

| DSP      | Digital Signal Processor                                    |

| DSSS     | Direct Sequence Spread Spectrum                             |

| E        | Early                                                       |

| ECEF     | Earth-Centered, Earth-Fixed                                 |

| ENU      | East-North–Up                                               |

| eSDK     | Extensible Software Development Kit                         |

| FDE      | Fault Detection and Exclusion                               |

| FF       | Flip-Flop                                                   |

| FFT      | Fast Fourier Transform                                      |

| FIFO     | First In, First Out                                         |

| FLL      | Frequency-Locked Loop                                       |

| FOSS     | Free and Open Source Software                               |

| FPGA     | Field Programmable Gate Array                               |

| FSM      | Finite State Machine                                        |

| GEO      | Geosynchronous Earth Orbit                                  |

| GIC      | Generic Interrupt Controller                                |

| GIS      | Geographic Information Systems                              |

| GLONASS  | GLObalnaya NAvigatsionnaya Sputnikovaya Sistema             |

| GLONASST | Glonass Time                                                |

| GNSS     | Global Navigation Satellite System                          |

| GPDIT    | Post-Detection Integration Truncated                        |

| GPDITSD  | Post-Detection Integration Truncated with Squaring Detector |

| GPIO     | General Purpose Input/Output                                |

| GPL      | General Public License                                      |

| GPS      | Global Positioning System                                   |

| GPST     | GPS System Time                                             |

| GPU      | Graphics Processing Unit                                    |

| GPX      | GPS Exchange Format                                         |

| GST      | Galileo System Time                                         |

| HD       | Hard Disk                                                   |

| HDL      | Hardware Description Language                               |

| HLS      | High-Level Synthesis                                        |

| HS       | High Sensitivity                                            |

| Ι        | In-Phase                                                    |

| I/O      | Input/Output                                                |

| I&D      | Integrate and Dump                                          |

| IC       | Integrated Circuit                                          |

| IF       | Intermediate Frequency                                      |

|          | · ·                                                         |

| IFFT   | Inverse Fast Fourier Transform                  |

|--------|-------------------------------------------------|

| IMU    | Inertial Measurement Unit                       |

| INS    | Inertial Navigation System                      |

| ΙΟ     | Input/Output                                    |

| ION    | Institute of Navigation                         |

| IoT    | Internet of Things                              |

| IP     | Intellectual Property                           |

| IRQ    | Interrupt Request                               |

| JTAG   | Joint Test Action Group                         |

| KML    | Keyhole Markup Language                         |

| KPI    | Key Performance Indicator                       |

| L      | Late                                            |

| LAN    | Local Area Network                              |

| LEO    | Low Earth Orbit                                 |

| LHCP   | Left-Handed Circular Polarization               |

| LNA    | Low-Noise Amplifier                             |

| LS     | Least Squares                                   |

| LUT    | Lookup Table                                    |

| LUTRAM | Lookup Table Random-Access Memory               |

| LVDS   | Low Voltage Differential Signaling              |

| MEO    | Medium Earth Orbit                              |

| ML     | Machine Learning                                |

| MMU    | Memory Management Unit                          |

| MPSoC  | Multi Processor System-on-Chip                  |

| MRSE   | Mean Radial Spherical Error                     |

| Msps   | Mega samples per second                         |

| NCI    | Non-Coherent Integration                        |

| NCO    | Numerically Controlled Oscillator               |

| NMEA   | National Marine Electronics Association         |

| NPDI   | Non-Coherent Post Detection Integration         |

| NTP    | Network Time Protocol                           |

| NTRIP  | Network Transport of RTCM via Internet Protocol |

| OCXO   | Oven-Controlled Crystal Oscillator              |

| OpenCL | Open Computing Language                         |

| OS     | Operating System                                |

| OTG    | On-The-Go                                       |

| Р      | Prompt                                          |

| PC     | Personal Computer                               |

| PCB    | Printed Circuit Board                           |

| PCPS   | Parallel Code Phase Search                      |

| PDI    | Post-Detection Integration                      |

| PFA    | Probability of False Alarm                      |

| PL     | Programmable Logic                              |

| PLL    | Phase-Locked Loop                               |

| POD    | Precise Orbit Determination                     |

| PPA    | Power, Performance and Area                     |

|        |                                                 |

| ppb         | parts per billion                                |

|-------------|--------------------------------------------------|

| ppo         | parts per million                                |

| PPS         | Pulse Per Second                                 |

| PRN         | Pseudo Random Noise                              |

| PS          | Processing System                                |

| PS<br>PVT   |                                                  |

|             | Position, Velocity and Time                      |

| Q           | In-Quadrature                                    |

| QSPI        | Quad Serial Peripheral Interface                 |

| RAIM<br>RAM | Receiver Autonomous Integrity Monitoring         |

|             | Random-Access Memory                             |

| RF<br>RFFE  | Radio Frequency                                  |

|             | Radio Frequency Front-End                        |

| RHCP        | Right-Handed Circular Polarization               |

| RINEX       | i e                                              |

| RMSE        | Root Mean Square Error                           |

| RNSS<br>ROM | Radio Navigation Satellite Service               |

| -           | Read Only Memory                                 |

| RTCM        | Radio Technical Commission for Maritime Services |

| RTL         | Register Transfer Level                          |

| SAS         | Spherical Accuracy Standard                      |

| SD<br>SDV   | Secure Digital                                   |

| SDK<br>SDR  | Software Development Kit                         |

| SDR         | Software-Defined Radio                           |

| SEP         | Spherical Error Probable                         |

| SFF         | Small Form Factor                                |

| SFTP        | Secure File Transfer Protocol                    |

| SMP         | Symmetric Multi-Processing                       |

| SNR         | Signal-to-Noise Ratio                            |

| SoC         | System on Chip                                   |

| SoM         | System on Module                                 |

| SPI         | Serial Peripheral Interface                      |

| SRAM        | Static Random Access Memory                      |

| SSH         | Secure Shell                                     |

| TC          | Telecommand                                      |

| TCP         | Transmission Control Protocol                    |

| TCP/IP      |                                                  |

| TCXO        | Temperature-Compensated Crystal Oscillator       |

| ТоА         | Time of Arrival                                  |

| ToF         | Time of Flight                                   |

| ToT         | Time of Transmission                             |

| TOW         | Time of Week                                     |

| TTFF        | Time to First Fix                                |

| UART        | Universal Asynchronous Receiver / Transmitter    |

| UIO         | User Input/Output                                |

| USB         | Universal Serial Bus                             |

| UTC         | Coordinated Universal Time                       |

|             |                                                  |

- VE Very Early

- VHDL Very High Speed Integrated Circuit Hardware Description Language

- VL Very Late

- WGS World Geodetic System

- XML Extensible Markup Language

### Chapter 1

#### Introduction

Over recent years, Global Navigation Satellite System (GNSS) technology has significantly grown in importance, exerting a profound influence across a diverse array of global sectors. GNSS is a system of satellites and ground-based stations that provide signals used for precise positioning and navigation anywhere on Earth's surface. It consists of multiple satellites in orbit around the Earth, which transmit signals that are received and used by GNSS receivers and other GNSS devices to determine their precise location, velocity, and time information. Examples of GNSS include Europe's Galileo, the United State's Global Positioning System (GPS), Russia's GLONASS and China's BeiDou. It is widely used in applications that require precise positioning, navigation, and timing synchronization across various domains, including disaggregated advanced 5th Generation (5G) radio access networks. GNSS technology is essential in transportation, enhancing safety and efficiency in vehicle, aircraft, and maritime navigation. In agriculture, it enables precision farming, leading to more effective resource use and improved crop management. Additionally, GNSS is essential in emergency services for providing precise and timely responses during disasters. Its significance also extends to scientific research, aiding in environmental monitoring and space exploration, thus demonstrating its broad impact on various aspects of modern life and industrial operations [1, 2].

GNSS systems are rapidly evolving due to a confluence of technological advancements, increasing demands for precision, and global geopolitical factors. The need for more precise and reliable positioning, navigation, and timing services grows as industries and technologies advance. This demand drives continuous improvements in satellite technology, including more sophisticated payloads and extended satellite lifespans, enhancing the accuracy and reliability of GNSS services. New generations of satellites, such as those from the United States'

GPS, Russia's GLObalnaya NAvigatsionnaya Sputnikovaya Sistema (GLONASS), Europe's Galileo, and China's BeiDou, offer improved capabilities including better signal quality, increased accuracy, and expanded coverage areas. Enhancements often feature new capabilities like multi-frequency signals for civilian use, providing greater accuracy and resistance to interference. Furthermore, the addition of more satellites enhances the redundancy and reliability of GNSS signals.

In addition, GNSS technology is increasingly being integrated with emerging technologies, including augmented reality [3], intelligent transportation and robotics [4], Inertial Navigation System (INS) [5], cellular networks [6], and Internet of Things (IoT) devices [7]. This integration not only expands the capabilities and applications of GNSS but also fosters innovation within the technology itself, leading to new and improved functionalities [1,2].

#### 1.1 Motivation

The swift progress in GNSS technologies necessitates prototyping tools for the exploration of new signals and systems. Prototyping is crucial in research, serving as a bridge between abstract theories and practical applications, and offering a hands-on approach to experimentation and analysis. A key advantage of prototyping is its ability to speed up the research and development process, enabling researchers to quickly transition from concept to application. This contrasts with traditional research methods that often involve extensive theoretical study before any practical testing. Prototyping allows for faster testing, refining, and iteration of ideas, leading to a deeper, intuitive understanding of a product's potential and functionality. Furthermore, prototyping plays a vital role in risk mitigation by allowing the early identification and resolution of potential issues, thus avoiding the pursuit of unfeasible or ineffective ideas. It also enhances communication, as a physical model provides a tangible representation of a concept, making it easier to understand and facilitating the exchange of ideas, feedback, and collaborative problem-solving.

Prototyping with commercial GNSS receivers in research environments often presents challenges. These difficulties stem from the inherent limitations of commercial receivers, which are typically designed for general mass-market use rather than specialized research applications. Commercial GNSS receivers usually come with fixed, proprietary firmware and software, which restricts the ability to modify or customize their functionality to meet specific research needs. They often operate as black boxes, with their internal processing methods not disclosed to the researcher. This lack of transparency can be particularly problematic in advanced GNSS research, where specialized algorithms and processing techniques are often required, and a deep understanding of the receiver's signal processing chain is crucial for tasks such as error analysis or the development of new positioning methods. Research activities involving GNSS technology, usually require non-standard features from the receivers and detailed knowledge of the signal processing tasks that are invovled in the computation of the GNSS products. If the commercial receiver supplies the required measurements, researchers can employ statistical characterization and fitting models in their analysis. Nevertheless, researchers encounter the obstacle of constructing their own receiver in the absence of available measurements. This can be problematic, as receiver prototyping typically falls outside their area of expertise or field of focus [8].

Software-Defined Radio (SDR) techniques offer a solution to the constrained adaptability of commercial receivers. With its programmable and adaptable nature, SDR technology can be customized precisely to fulfill the user's specific needs. Moreover, access to inspection and modification of the full SDR receiver's signal processing chain can be addressed using Free and Open Source Software (FOSS). FOSS allows users and programmers to edit, inspect, and modify the software's source code. The open philosophy of FOSS is well suited for education and research, since the source code of the software is available for examination and derivative software can be written without any copyright issues [8]. With FOSS, researchers can freely share and reuse their work, optimizing the development process of applications and increasing productivity in software teams. This collaborative approach is not only beneficial for advancing the technology but also provides an educational resource for students and new researchers, helping them to understand practical applications and gain hands-on experience. Code reuse allows developers to focus on the implementation of new features instead of reinventing the wheel for each project. Moreover, it encourages clean, modular, and efficient software, which decreases the likelihood of introducing bugs or inconsistencies. The flexibility, adaptability, and collaborative potential of FOSS GNSS software receivers, combined with their costeffectiveness and educational value, make them particularly suited for research environments where deep technological understanding, innovation, and customization are key.

However, GNSS software-defined receivers have a notable drawback in terms of power consumption. They typically do not match the power efficiency of hardware-based receivers, mainly because they run on general-purpose processors found in computers. These processors are not optimized for low-power operation, leading to excessive power consumption, particularly when executing complex algorithms. The intensive computational demands of real-time GNSS signal processing result in significant power consumption, making these systems less suitable for scenarios that require prolonged battery operation. This aspect is relevant for fieldbased GNSS applications, where power efficiency is needed. Such applications involve the practical use of GNSS technology in outdoor or real-world environments, rather than in controlled settings like laboratories.

It is thus interesting to investigate SDR architectures that can improve the trade-off between efficiency and flexibility. The semiconductor industry historically relied on Central Processing Unit (CPU) scaling to increase performance and reduce power consumption. This practice was largely governed by Moore's Law and Dennard Scaling, which together provided a predictable roadmap for performance improvements in semiconductor devices. Moore's Law predicted that the number of transistors on a chip would double approximately every two years, leading to increased performance, reduced costs, and greater energy efficiency [9]. Dennard Scaling complemented Moore's Law by outlining how, as transistors were made smaller, they would consume less power, produce less heat, and operate faster, allowing for more transistors to be packed into the same chip size without increasing overall power consumption [10].

Through these principles, the semiconductor industry was able to consistently deliver significant performance improvements from generation to generation of integrated circuits. However, as transistor sizes approached the atomic scale, the industry began encountering physical and technical limitations that made continued scaling as per Moore's Law and Dennard Scaling more challenging [11]. Issues such as heat dissipation, quantum tunneling, and variability increased, diminishing the returns on traditional scaling efforts.

As a result, the industry has shifted towards new strategies for performance improvement. This

shift includes adopting increasingly parallel architectures and creating hardware that better matches the applications, exploring heterogeneous computing and advanced chip architectures previously limited to extreme performance segments [12, 13]. In this sense, there is a growing focus on specialized processors designed for specific tasks, such as vector-based processing with Digital Signal Processors (DSPs) and Graphics Processing Units (GPUs), as well as fully parallel programmable hardware like Field Programmable Gate Arrays (FPGAs).

An FPGA is a type of digital Integrated Circuit (IC) that can be reprogrammed by the user after manufacturing to perform a wide variety of digital functions. FPGAs are made up of an array of programmable logic blocks, interconnects, and Input/Output (IO) blocks that can be configured to execute complex combinational functions, implement state machines, or even mimic the architectures of entire CPUs. FPGAs offer precise customization for distinct computational tasks, rendering them ideal for latency-critical real-time applications. They outperform processors in terms of computing power and energy consumption for tasks that are highly parallelizable and require low latency and high throughput. FPGAs achieve this due to the nature of their architecture and design. Their reconfigurable matrix of logic blocks enables the execution of a diverse array of digital functions, including SDR algorithms. Designed for parallel processing, FPGAs can concurrently manage multiple tasks, enhancing their overall efficiency. This parallelism reduces the overall processing time and decreases the power consumption compared to sequential processing by CPUs. On top of that, FPGAs do not carry the overhead associated with managing complex instruction sets and control logic, which is typical in CPUs. As a result, they can perform specific tasks efficiently with minimal unnecessary operations, leading to lower power consumption.

GNSS receivers exploit parallelism to efficiently process signals from multiple satellites at once, thereby enhancing the speed and precision of Position, Velocity and Time (PVT) solutions. By utilizing multiple channels that operate in parallel, these receivers can simultaneously process signals from various satellites. This approach to parallel processing is essential for achieving accurate positioning, as data from at least four satellites are needed for a precise three-dimensional location. The integration of FPGA technology further enhances GNSS signal processing efficiency. FPGAs, with their intrinsic parallel architecture and adaptability, are suitable for GNSS applications, offering an effective method for signal management. The adaptability of FPGAs is also a key feature. As GNSS technology advances or as processing needs change, the hardware can be adjusted to meet these new demands. This flexibility ensures the system remains relevant and efficient, offering both cost-effectiveness and energy efficiency.

Integrating FPGAs with embedded general-purpose processors enhances the flexibility and power efficiency of software-defined GNSS receivers. This configuration allows for the optimal allocation of signal processing tasks to the most appropriate processing units, ensuring the system's adaptability to evolving requirements. System on Chip (SoC) FPGAs and Radio Frequency (RF) SoC FPGAs are particularly suited for developing architectures that merge software-defined systems with specialized hardware. At the heart of an SoC FPGA is the integration of a general-purpose processor with a reconfigurable FPGA fabric. Typically, SoC FPGAs include high-speed interconnects, such as buses or dedicated interfaces, to ensure efficient communication between the FPGAs and the embedded processor. These interconnects facilitate rapid data transfer, enhancing the interaction between hardware and software components. The integration of both an embedded processor and an FPGA into a single chip reduces power consumption, as internal chip connections consume less power compared to the

external links of separate processor and FPGA systems. Moreover, RF SoC FPGAs further integrate RF Analog to Digital Converters (ADCs) and Digital-to-Analog Converters (DACs), further improving flexibility and reducing board space and power consumption [14, 15].

Still, adopting FPGAs presents challenges. Their performance can lag behind general-purpose processors for tasks that are inherently sequential or involve complex branching and decision-making processes. Furthermore, FPGA development is generally more time-consuming than traditional software development, encompassing stages like simulation, synthesis, and place-and-route, and debugging. This process not only extends development timelines but also demands a high level of specialized knowledge and expertise in hardware design, making FPGA programming less accessible to those without a background in this area.

Despite these challenges, strategically partitioning software between the FPGA and CPU can leverage their combined strengths, enhancing both power efficiency and performance. This approach involves dividing computational tasks, with certain tasks designated for the CPU and others offloaded to the FPGA, to achieve an optimal power-performance tradeoff in SoC FPGAs. Meticulous design and analysis are essential for this process. Typically, tasks suited for FPGAs require high throughput, parallel processing, and real-time execution. In contrast, the CPU is better equipped for handling complex control logic, decision branching, and sequential processing. Such optimal hardware-software partitioning not only improves the power consumption-performance balance but also enables efficient GNSS signal processing. The software-defined portion, managed by the processor, provides fast adaptability, whereas the FPGA offers hardware-accelerated functions. This dual capability is essential for GNSS receiver functionalities that require both adaptability and precise processing.

#### 1.2 Objectives

The main objective of this thesis is to design and implement a scalable SoC-FPGA architecture for prototyping experimental, portable multi-constellation and multi-frequency GNSS receivers using Commercial Off-The-Shelf (COTS) products. The proposed architecture overcomes the flexibility limitations of commercial receivers by enabling the implementation of GNSS processing engines on SoC-FPGA platforms. It capitalizes on the embedded processors' flexibility and the FPGAs' massive parallelism and energy efficiency, facilitating the creation of real-time, portable receivers. These receivers can be adapted to a wide range of SoC-FPGA devices with varying FPGA and embedded processor sizes, with a focus on optimizing for low power consumption, price-performance ratio, or catering to high-capacity and high-performance needs based on the application.

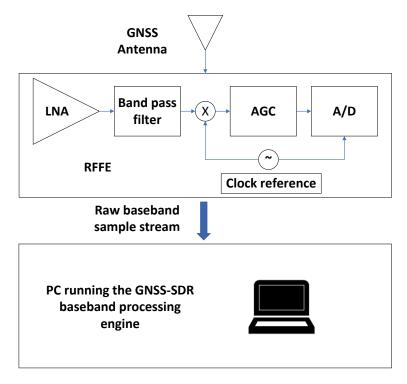

In the proposed architecture, the SoC-FPGA embedded processor runs GNSS-SDR, a popular and well-regarded FOSS GNSS SDR receiver that is readily available online [16, 17]. The adoption of open-source software enables thorough inspection and modification of the receiver's chain, fostering freedom, collaboration, and innovation, while also reducing implementation costs. Conventionally, GNSS-SDR operates as a host-based GNSS receiver: an Radio Frequency Front-End (RFFE) tuned to GNSS frequency bands receives satellite signals, performs RF-to-baseband down-conversion and sampling, and then streams the samples to a Personal Computer (PC) running GNSS-SDR. This thesis introduces a significant enhancement by adding the capability to cross-compile GNSS-SDR for its execution on SoC-FPGA

embedded devices. With this enhancement, GNSS-SDR can offload the most computationally intensive tasks to the FPGA, thus realizing an SoC-FPGA-based embedded receiver. In this configuration, the FPGA processes the incoming sample stream from the RFFE, utilizing hardware accelerators for the most demanding algorithms, notably acquisition and tracking. These FPGA hardware accelerators are designed as reusable Intellectual Property (IP) cores, making them adaptable to a wide range of FPGAs.

This thesis also proposes a design methodology for implementing GNSS signal processing algorithms and concept demonstrators based on the SoC FPGA architecture. This methodology is based on a hardware/software design flow where FPGA and software development can largely proceed independently. In this way, software can be implemented using a complete FOSS toolchain, independently of the FPGA development tools. Researchers have the option to release FPGA IP cores under either FOSS or proprietary licenses. This flexibility allows for the monetization of research outcomes while simultaneously enhancing research impact and reputation. The FPGA IP cores developed within the framework of this thesis are available under proprietary terms, which restrict access to their source code. However, access to the internal aspects of the signal processing algorithms is possible by inspecting the software version of the FPGA hardware accelerators in GNSS-SDR, along with the documentation provided by the developers of the FPGA IP cores. This approach facilitates code reusability, which is essential for minimizing development time and costs.

Finally, this thesis validates the practicality of the proposed architecture and design methodology by implementing various real-time concept demonstrators. These include a spaceborne receiver for processing GNSS signals in LEO scenarios, a GNSS rebroadcaster for regenerating live signals, and a High Sensitivity (HS)-GNSS receiver designed for weak signal conditions. The prototypes are evaluated based on hardware resources, size, and power consumption, highlighting the scalability of the proposed architecture. They are tested with live signals to demonstrate their capability to fulfill the requirements.

The software-defined spaceborne GNSS Receiver offers a fully customizable platform capable of processing GPS L1 C/A, GPS L5, Galileo E1b/c, and Galileo E5a signals. It can produce navigation solutions and deliver GNSS products in standard formats in real time, even in high-dynamic scenarios such as Low Earth Orbit (LEO). Designed for space applications, this receiver features a form factor suitable for CubeSats.

The rebroadcaster integrates a closely coupled receiver and transmitter within a single device, capable of generating, receiving, and regenerating GPS L1 C/A and Galileo E1b/c signals with very low latency. It can regenerate the received satellite signals in real time while simultaneously rebroadcasting a PVT solution that differs from the PVT fixes obtained by the receiver. This device can be used to test the addition of new features in GNSS signals, and to simulate the channel dynamics in various scenarios. The GNSS rebroadcaster features a specialized component within the FPGA, known as the telemetry symbol link. This link directly forwards telemetry data, estimated by the receiver's tracking multicorrelator hardware accelerators, to the signal generators in the FPGA, bypassing any need for processor intervention. The telemetry symbol link can be enabled for Galileo E1b/c signals. When enabled, the telemetry data is rebroadcasted with a latency that can be set below 30 ms. This facilitates maintaining the consistency with other sensors, e.g., an Inertial Measurement Unit (IMU), where available.

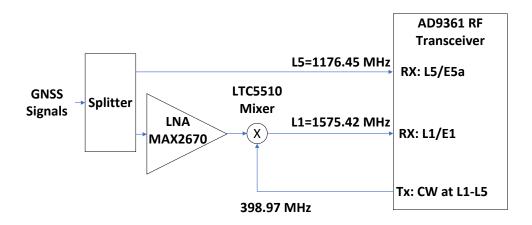

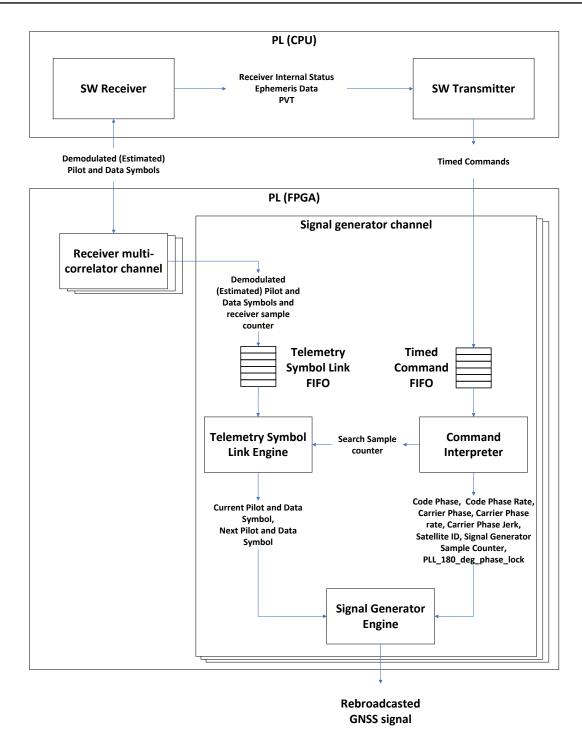

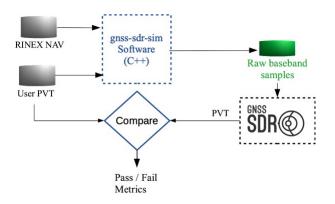

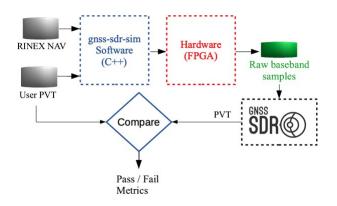

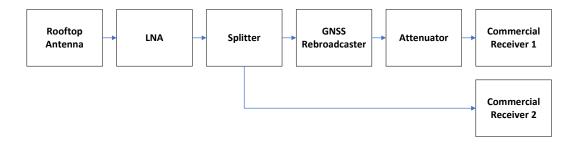

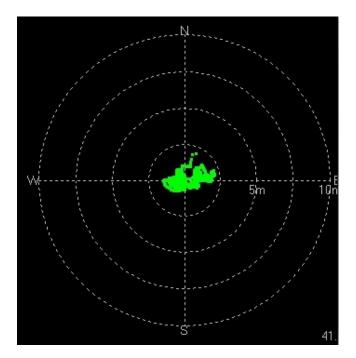

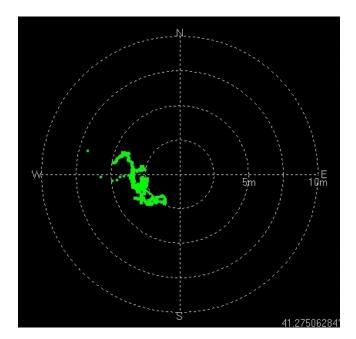

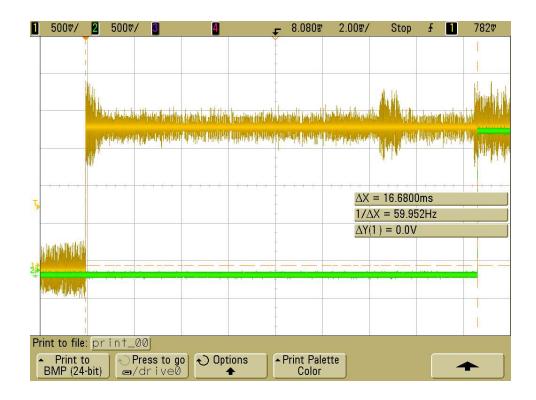

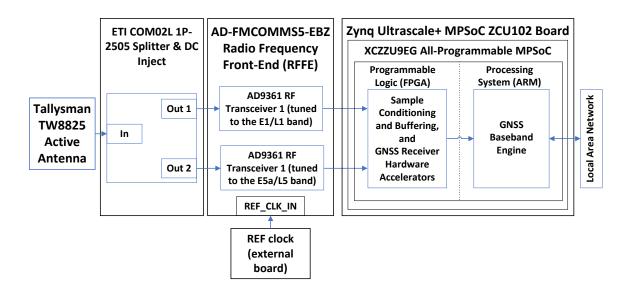

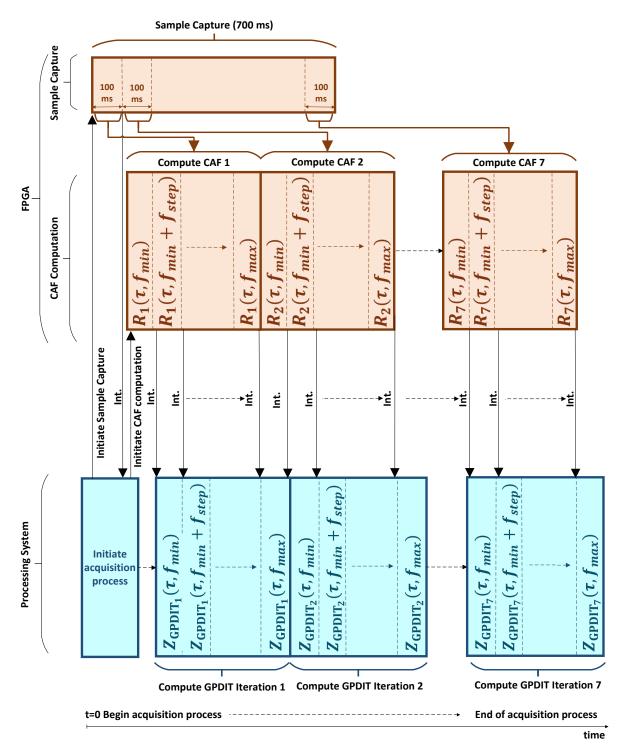

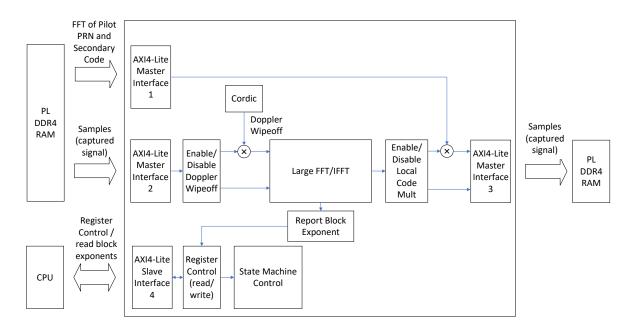

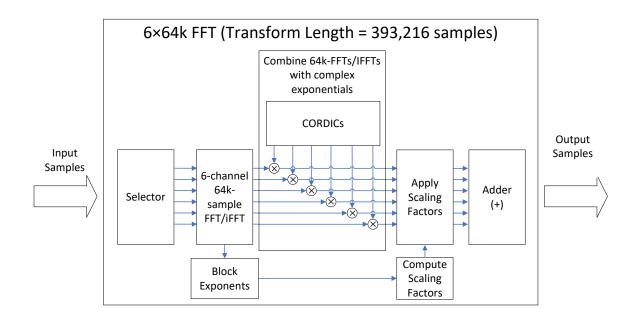

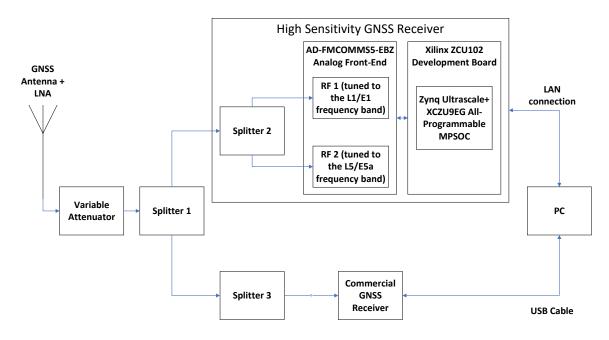

The HS GNSS receiver is designed for processing weak signals. It implements two operating modes: high-sensitivity mode, and normal-sensitivity mode. When operating in high-sensitivity mode, the receiver is capable of acquiring and tracking Galileo E1b/c signals with a Carrier-to-Noise Density Ratio ( $C/N_0$ ) as low as 20 dB-Hz (equivalent  $C/N_0$  observed at the post-correlation level), enabling the derivation of navigation solutions. On the other side, when operating in normal-sensitivity mode, the receiver processes GPS L1 C/A, Galileo E1b/c, GPS L5 and Galileo E5a signals with an acquisition sensitivity of approximately 37 dB-Hz. To enhance the availability of satellite signals, the receiver is capable of processing Galileo E1b/c signals in high-sensitivity mode, while simultaneously processing GPS L1 C/A, GPS L5 and Galileo E5a signals and has the potential to test novel algorithms that address common indoor GNSS challenges, such as multipath interference [18]. However, it currently does not incorporate these algorithms.