Wang, Liquan (2012) *Reliable design of tunnel diode and resonant tunnelling diode based microwave sources.* PhD thesis.

http://theses.gla.ac.uk/3423/

Copyright and moral rights for this thesis are retained by the author

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge

This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the Author

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the Author

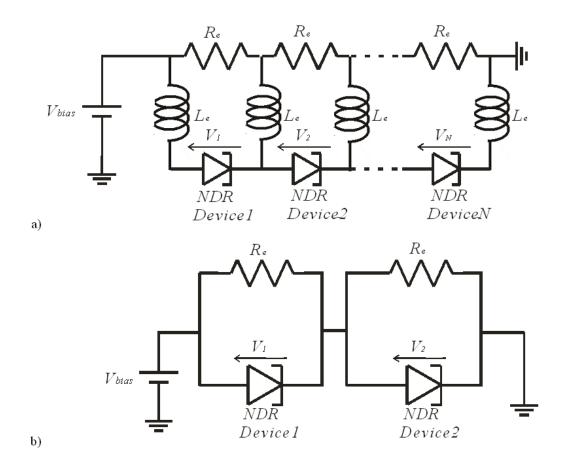

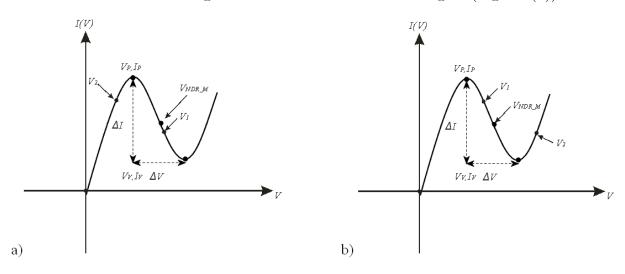

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given

Glasgow Theses Service http://theses.gla.ac.uk/ theses@gla.ac.uk

# RELIABLE DESIGN OF TUNNEL DIODE AND RESONANT TUNNELLING DIODE BASED MICROWAVE SOURCES

BY

#### LIQUAN WANG

A Dissertation submitted to The School of Engineering University of Glasgow in fulfillment of the requirements for the Degree of

Doctor of Philosophy

**Glasgow** University

2011

Copyright 2011 by Liquan Wang

## DEDICATION

This thesis is dedicated to my parents Xinxiang Wang & Dongmei Yan and my sister Liwei Wang

### ACKNOWLEDGMENTS

Sincere thanks go to my first supervisor, Dr. Edward Wasige, for his guidance, discussions and advice on my work throughout the course of this PhD. I would also like to thank him for his support with corrections of my papers and reports. Extra special thanks are also due to my co-supervisor, Professor Charles N Ironside, for giving me a precious opportunity to work on the resonant tunnelling diode - laser diode (RTD-LD) project which led to many fruitful results.

Special thanks to Ian McGregor for his help in general and in particular for his excellent suggestions and advice on tunnel diode oscillators design. Also, I would like to thank Bruno Romeira and Prof. José Figueiredo of the University of Algarve, Portugal, and Thomas Slight for the many excellent discussions and conversations on both tunnel diode/RTD oscillators and RTD-LD.

Many thanks to Lianping Hou, Richard Oxland, Haiping Zhou, Steven Mcmaster, Gabor Mezosi and Xu Li, for their many useful discussions and suggestions on monolithic RTD oscillator fabrication process.

I am deeply grateful to Stewart Fairbairn and Chong Li. Stewart, for the huge number of hybrid printed circuit boards (PCB) he fabricated for me and Chong, for his great help with RF measurements.

I wish to express my gratitude to Alex Ross, Eve Aitkenhead, Douglas Lang,

Mark Dragsness, Linda Pollock, Robert Harkins, Mary Robertson, Helen McLelland, Susan Ferguson, Fiona McEwan, Donald Nicolson and Lesley Donaldson their technical support. They made my life in the clean room a lot easier.

I am grateful for the help and support from my colleagues in the High Frequency Electronics Research Group: Sanna Taking, Abishek Banerjee, Giangiacomo Cramarossa, Salah Sharabi, Daniel Pillow and Douglas Macfarlane. Last but not least, I would like to thank my examiners Professor Iain Thayne and Dr Heribert Eisele for their patience in having to read through several revisions of this thesis.

#### ABSTRACT

This thesis describes the reliable design of tunnel diode and resonant tunnelling diode (RTD) oscillator circuits. The challenges of designing with tunnel diodes and RTDs are explained and new design approaches discussed. The challenges include eliminating DC instability, which often manifests itself as low frequency parasitic oscillations, and increasing the low output power of the oscillator circuits.

To stabilise tunnelling devices, a common but sometimes ineffective approach is the use of a resistor of suitable value connected across the device. It is shown in this thesis that this resistor tunnel diode circuit can be described by the Van der Pol model. Based on this model, design equations have been derived which enable the design of current-voltage (I-V) measurement circuits that are free from both low frequency bias oscillations and high frequency parasitic oscillations. In the conventional setup, the I-V characteristic of the tunnelling device is extracted from the measurement by subtracting from the measured current the current through the stabilising resistance at each bias voltage. In this thesis, also using the Van der Pol model, a circuit for the direct measurement of I-V characteristics is proposed. This circuit utilises a series resistor-capacitor combination in parallel with the tunnelling device for stabilisation. Experimental results show that I-V characterisation of tunnel diodes in the negative differential resistance (NDR) region free from oscillations can be made. A new test set-up suitable for radio frequency (RF) characterisation of tunnel diodes over the entire NDR region was also developed. Initial measurement results on a packaged tunnel diode indicate that accurate characterisation and subsequent small-signal equivalent circuit model extraction for the NDR region can be done.

To address the limitations of low output power of tunnel diode or RTD oscillators, a new multiple device circuit topology, incorporating a novel design methodology for the DC bias decoupling circuit, has been developed. It is based on designing the oscillator specifically for sinusoidal oscillations, and not relaxation oscillations which are also possible in tunnel diode oscillators. The oscillator circuit can also be described by the Van der Pol model which provides theoretical predictions of the maximum inductance, in terms of the tunnel diode device parameters, that is required to resonate with the device capacitance for sinusoidal oscillations. Each of the tunnel diodes in the multiple device oscillator circuit is decoupled from the others at DC and so can be stabilised independently. The oscillator topology uses parallel resonance but with each tunnel diode individually biased and DC decoupled making it possible to employ several tunnel diodes for higher output power. This approach is expected to eliminate parasitic bias oscillations in tunnel diode oscillators whilst increasing the output power of a single oscillator. Simulation and experimental oscillator results were in good agreement, with a two-tunnel diode oscillator exhibiting approximately double the output power as compared to that of a single tunnel diode oscillator, i.e. 3 dB higher.

Another method considered for the realisation of higher output power tunnel diode or RTD oscillators was series integration of the NDR devices. A new method to suppress DC instability of the NDR devices connected in series with all the devices biased in their NDR regions was investigated. It was successfully employed for DC characterisation with integrations of 2 and 5 tunnel diodes. Even though no suitable oscillator circuit topology and/or methodology with series-connected NDR devices could be established for single frequency oscillation, the achieved results indicated that this approach may be worthy of further investigation.

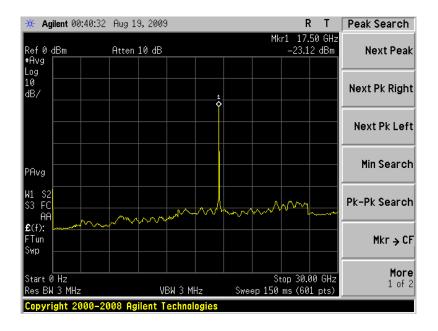

The final aspect of this project focussed on the monolithic realisation of RTD oscillators. Monolithic oscillators in coplanar waveguide (CPW) technology were successfully fabricated and worked at a fundamental frequency of 17.5 GHz with -21.83 dBm output power. Finally, to assess the potential of RTD oscillators for high frequency signal generation, a theoretical analysis of output power of stabilised RTD oscillators was undertaken. This analysis suggests that it may be possible to realise RTD oscillators with high output power ( $\sim 0$  dBm) at millimetre-wave and low terahertz (up to 1 THz) frequencies.

#### PUBLICATIONS

- [1] L. Wang and E. Wasige, "A design procedure for tunnel diode microwave oscillators," in *Proceedings IEEE International Conference on Microwave and Millimeter-Wave Technology*, vol. 2, pp.832-834, Apr. 2008.

- [2] L. Wang and E. Wasige, "Tunnel diode microwave oscillators employing a novel power combining circuit topology," in *European Microwave Conference* (*EuMC*), pp.1154-1157, Sep. 2010.

- [3] L. Wang, J. M. L. Figueiredo, C. N. Ironside and E. Wasige, "DC characterisation of tunnel diodes under stable non-oscillatory circuit conditions," *IEEE Transactions on Electron Devices*, vol. 58, no. 2, pp.343-347, Feb. 2011.

- [4] T. J. Slight, B. Romeira, L. Wang, J. M. L. Figueiredo, E. Wasige and C. N. Ironside, "A Lienard oscillator resonant tunnelling diode - laser diode hybrid integrated circuit: model and experiment," *IEEE Journal of Quantum Electronics*, vol. 44, no. 12, pp.1158-1163, Dec. 2008.

- [5] B. Romeira, J. M. L. Figueiredo, T. J. Slight, L. Wang, E. Wasige, C. N. Ironside, J. M. Quintana and M. J. Avedillo, "Observation of frequency division and route to chaos in a laser diode modulated by a resonant tunneling diode," *Conference on Quantum Electronics and Laser Science, Lasers and Electro-Optics (CLEO)*, 2008.

- [6] B. Romeira, J. M. L. Figueiredo, T. J. Slight, L. Wang, E. Wasige, C. N. Ironside, J. M. Quintana and M. J. Avedillo, "Synchronization and chaos in a laser diode driven by a resonant tunneling diode," *IET Optoelectronics Journal*, vol. 2, no. 6, pp.211-215, 2008.

- [7] J. M. L. Figueiredo, B. Romeira, T. J. Slight, L. Wang, E. Wasige and C. N. Ironside, "Self-oscillation and period adding from resonant tunnelling diode-laser diode circuit," *Electronics Letters*, vol. 44, no. 14, pp.876-877, 2008.

- [8] B. Romeira, J. M. L. Figueiredo, T. J. Slight, L. Wang, E. Wasige and C. N. Ironside, "Synchronizing optical to wireless signals using a resonant tunneling diode laser diode circuit," 21st Annual Meeting of IEEE Laser of Electro-Optics Society, 2008.

- [9] B. Romeira, J. M. L. Figueiredo, T. J. Slight, L. Wang, E. Wasige and C. N. Ironside, "Wireless injection locking and phase noise reduction in a semiconductor laser driven by a resonant tunnelling diode nonlinear oscillator," *European Conference on Lasers and Electro-Optics (CLEO)*, 2009.

- [10] B. Romeira, J. M. L. Figueiredo, T. J. Slight, L. Wang, E. Wasige and C. N. Ironside, "Wireless/Photonics interfaces based on resonant tunneling diode optoelectronic oscillators," *Conference on Quantum Electronics and Laser Science, Lasers and Electro-Optics (CLEO)*, 2009.

- [11] B. Romeira, J. M. L. Figueiredo, T. J. Slight, L. Wang, E. Wasige, C. N. Ironside A. E. Kelly and R. Green, "Nonlinear dynamics of resonant tunnelling optoelectronic circuits for wireless/optical interfaces," *IEEE Journal of Quantum Electronics*, vol. 45, no. 11, pp.1436-1445, Nov. 2009.

- [12] B. Romeira, J. M. L. Figueiredo, T. J. Slight, L. Wang, E. Wasige and C. N. Ironside, "Wireless to optical frequency locking and chaos using a resonant tunnelling - laser diode circuit," *IEEE/LEOS Winter Topics Meeting Series*, 2009.

- [13] C. N. Ironside, J. M. L. Figueiredo, B. Romeira ,T. J. Slight, L. Wang and E. Wasige, "The resonant tunnelling diode - laser diode optoelectronic integrated circuit operating as a voltage controlled oscillator," invited paper, *Proceeding of SPIE*, vol. 7366, 736614, May 2009.

### CONTENTS

| LIST OF TABLES    |                                           |        | xvi        |                                                              |    |

|-------------------|-------------------------------------------|--------|------------|--------------------------------------------------------------|----|

| LIST OF FIGURES x |                                           |        |            | XXXV                                                         |    |

| 1                 | INTRODUCTION                              |        |            | 1                                                            |    |

|                   | 1.1 Review of tunnel diode and RTD theory |        |            | 6                                                            |    |

|                   |                                           | 1.1.1  | Esaki Tu   | mnel diodes [43], [46] - [49]                                | 6  |

|                   |                                           | 1.1.2  | Resonan    | t tunnelling diodes [46], [52] $\ldots \ldots \ldots \ldots$ | 10 |

|                   | 1.2                                       | NDR o  | device cha | aracterisation and NDR oscillator circuits                   | 13 |

|                   |                                           | 1.2.1  | DC (in)s   | stability and equivalent circuit modelling                   | 13 |

|                   |                                           | 1.2.2  | Parasitio  | e bias oscillations and low oscillator output power .        | 15 |

|                   |                                           |        | 1.2.2.1    | Waveguide RTD oscillators                                    | 16 |

|                   |                                           |        | 1.2.2.2    | Planar RTD oscillators                                       | 17 |

|                   |                                           |        | 1.2.2.3    | Quasi-optical power combining                                | 21 |

|                   |                                           |        | 1.2.2.4    | Series or parallel device integration                        | 21 |

|                   |                                           |        | 1.2.2.5    | Power combining for other two terminal devices .             | 23 |

|                   | 1.3                                       | Projec | t aims an  | d thesis layout                                              | 24 |

| 2                 | VAN                                       | DER    | POL OS(    | CILLATOR ANALYSIS                                            | 27 |

|                   | 2.1                                       | Introd | uction .   |                                                              | 27 |

|                   | 2.2                                       | Van de | er Pol osc | illator theory                                               | 27 |

|   | 2.3                 | Negative differential resistance based Van der Pol oscillator                     | 29 |

|---|---------------------|-----------------------------------------------------------------------------------|----|

|   | 2.4                 | Small-signal analysis                                                             | 37 |

|   | 2.5                 | Summary                                                                           | 40 |

| 3 | DC                  | CHARACTERISATION OF TUNNEL DIODES                                                 | 41 |

|   | 3.1                 | Introduction                                                                      | 41 |

|   | 3.2                 | Simulation results of un-stabilised and stabilised tunnel diodes $\ .$ .          | 42 |

|   |                     | 3.2.1 Unstable circuit at low frequency                                           | 43 |

|   |                     | 3.2.2 Stable circuit at low frequency                                             | 44 |

|   |                     | 3.2.3 Stable circuit at low and high frequencies                                  | 47 |

|   | 3.3                 | Direct characterisation of $I$ - $V$ characteristics                              | 48 |

|   | 3.4                 | Experiment Results                                                                | 50 |

|   | 3.5                 | Discussion                                                                        | 52 |

|   | 3.6                 | Summary                                                                           | 56 |

| 4 | $\operatorname{RF}$ | CHARACTERISATION OF TUNNEL DIODES                                                 | 59 |

|   | 4.1                 | Introduction                                                                      | 59 |

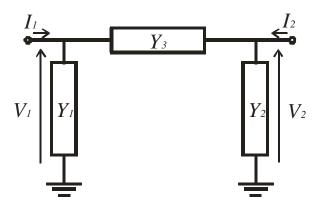

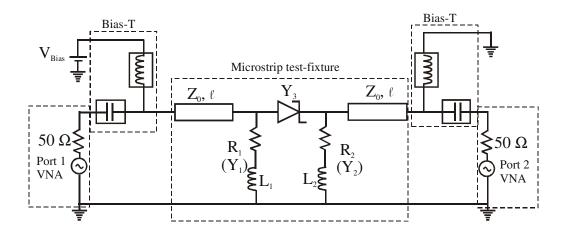

|   | 4.2                 | RF test fixture: theory and experiment                                            | 60 |

|   | 4.3                 | Experimental results                                                              | 63 |

|   | 4.4                 | Extracted RF model for the NDR region                                             | 64 |

|   |                     | 4.4.1 Variation of $G_n$ and $C_n$ with bias $\ldots \ldots \ldots \ldots \ldots$ | 68 |

|   | 4.5                 | Summary                                                                           | 69 |

| 5 | OSC | CILLAT  | OR DESIGN WITH TUNNEL DIODES                                                                                                    | 70  |

|---|-----|---------|---------------------------------------------------------------------------------------------------------------------------------|-----|

|   | 5.1 | Introd  | $uction \ldots \ldots$ | 70  |

|   | 5.2 | Requir  | ements for tunnel diode sinusoidal oscillator design                                                                            | 70  |

|   | 5.3 | Simula  | ation results of oscillator circuits                                                                                            | 74  |

|   |     | 5.3.1   | Oscillators with bias stabilisation                                                                                             | 74  |

|   |     | 5.3.2   | Oscillators without bias stabilisation                                                                                          | 77  |

|   | 5.4 | Oscilla | tor topology and design                                                                                                         | 78  |

|   | 5.5 | Experi  | mental results                                                                                                                  | 82  |

|   |     | 5.5.1   | Oscillator efficiency                                                                                                           | 87  |

|   | 5.6 | Discus  | $\operatorname{sion}$                                                                                                           | 88  |

|   |     | 5.6.1   | Comparison to other planar RTD oscillator circuits $\ldots$                                                                     | 91  |

|   | 5.7 | Summ    | ary                                                                                                                             | 95  |

| 6 | SER | IES IN  | TEGRATION OF TUNNEL DIODES                                                                                                      | 96  |

|   | 6.1 | Introd  | uction                                                                                                                          | 96  |

|   | 6.2 | DC sta  | ability of series connected tunnel diodes                                                                                       | 97  |

|   |     | 6.2.1   | Analytical model for the tunnel diode                                                                                           | 101 |

|   |     | 6.2.2   | Analysis of DC stability of series connected tunnel diodes .                                                                    | 104 |

|   |     |         | 6.2.2.1 Theoretical analysis                                                                                                    | 104 |

|   |     |         | 6.2.2.2 Experimental results                                                                                                    | 110 |

|   | 6.3 | Oscilla | tor design with series connected tunnel diodes $\ldots$                                                                         | 112 |

|   |     | 6.3.1   | Experimental results                                                                                                            | 114 |

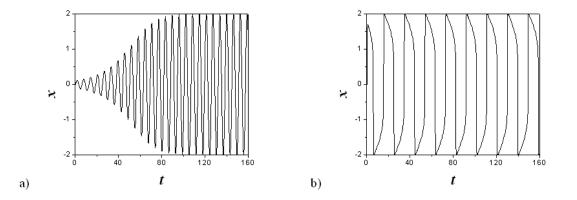

|     | 6.3.2 Time domain simulations                       | 116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.4 | Summary                                             | 119                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| MO  | NOLITHIC RTD OSCILLATORS                            | 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7.1 | Introduction                                        | 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7.2 | Components of RTD MMIC oscillators                  | 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     | 7.2.1 Resonant tunnelling diode                     | 122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     | 7.2.2 Coplanar waveguide                            | 126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     | 7.2.3 Nickel chromium resistor                      | 128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7.3 | Monolithic RTD oscillator topology                  | 129                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7.4 | Basic fabrication processes                         | 133                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     | 7.4.1 Sample preparation                            | 133                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     | 7.4.2 Photolithography                              | 134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     | 7.4.3 Lift-off metallisation                        | 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     | 7.4.4 Metallisation                                 | 137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     | 7.4.5 Etching                                       | 139                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     | 7.4.6 Passivation                                   | 142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7.5 | RTD oscillator fabrication                          | 142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7.6 | Experimental results                                | 147                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7.7 | Discussion                                          | 149                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7.8 | Summary                                             | 151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     | MO<br>7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7 | 6.4       Summary         MONOLITHIC RTD OSCILLATORS         7.1       Introduction         7.2       Components of RTD MMIC oscillators         7.2       Components of RTD MMIC oscillators         7.2.1       Resonant tunnelling diode         7.2.2       Coplanar waveguide         7.2.3       Nickel chromium resistor         7.3       Monolithic RTD oscillator topology         7.4       Basic fabrication processes         7.4.1       Sample preparation         7.4.2       Photolithography         7.4.3       Lift-off metallisation         7.4.4       Metallisation         7.4.5       Etching         7.4.6       Passivation         7.5       RTD oscillator fabrication         7.6       Experimental results         7.7       Discussion |

| 8          | OU  | FPUT POWER ANALYSIS OF RTD OSCILLATORS                              | 152 |  |

|------------|-----|---------------------------------------------------------------------|-----|--|

|            | 8.1 | Introduction                                                        | 152 |  |

|            | 8.2 | Output power analysis for parallel RTD oscillators                  | 153 |  |

|            | 8.3 | Power limitation of the Chahal RTD oscillator topology              | 157 |  |

|            | 8.4 | Comparison between the Chahal and the parallel RTD oscillator       |     |  |

|            |     | topology                                                            | 159 |  |

|            | 8.5 | Limitations of the RTD waveguide oscillator                         | 162 |  |

|            | 8.6 | Power limitation of a single RTD oscillator                         | 164 |  |

|            |     | 8.6.1 RTD devices for waveguide oscillators                         | 164 |  |

|            |     | 8.6.2 RTD devices for planar oscillators                            | 167 |  |

|            |     | 8.6.3 Estimation of RTD oscillator power from device sizes $\ldots$ | 168 |  |

|            |     | 8.6.4 Output power and frequency                                    | 172 |  |

|            |     | 8.6.4.1 $$ Simulated output power for some NDR devices $$ .         | 176 |  |

|            | 8.7 | Summary                                                             | 182 |  |

| 9          | COI | NCLUSIONS AND FUTURE WORK                                           | 184 |  |

|            | 9.1 | Conclusions                                                         | 184 |  |

|            | 9.2 | Future work                                                         | 186 |  |

| APPENDICES |     |                                                                     |     |  |

|            | А.  | List of Abbreviations and Acronyms                                  | 190 |  |

|            | В.  | List of Symbols                                                     | 193 |  |

|            | С.  | RTD Oscillator Fabrication Process                                  | 195 |  |

|    | Sample cleaning                                       | 195 |

|----|-------------------------------------------------------|-----|

|    | Alignment makers and collector contacts               | 195 |

|    | Etch to emitter layer                                 | 196 |

|    | Emitter contacts                                      | 197 |

|    | Etch to substrate                                     | 198 |

|    | Passivation                                           | 199 |

|    | Shunt resistor                                        | 200 |

|    | Bond pad and CPW                                      | 200 |

| D. | Fundamental constants                                 | 201 |

| E. | Datasheet of tunnel diodes 1N3717 and 1N3714 $\ldots$ | 201 |

#### LIST OF TABLES

- 5.1 Simulation results of the power delivered to a 50- $\Omega$  load for various values of  $\varepsilon$ .  $f_0$  is the fundamental frequency,  $P(f_0)$  is the power at fundamental, and  $P(2f_0)$  is the power at the first harmonic. . . . 74

- Calculated maximum device areas for some published RTD InP-8.1 based AlAs/InGaAs/AlAs double barrier quantum-well RTD structures. The resistance  $R_e$  is set to 10  $\Omega$  and L is set to 100 pH.  $V_p$ and  $V_v$  are the peak and valley voltages,  $\Delta J$  is the current density difference,  $C_d$  is the capacitance per unit area of the device and  $f_{cut-off}$  is the cut-off frequency [36],[37], [40], [83].  $A_{max1}$  and  $A_{max2}$  are the maximum device areas for the waveguide RTD oscillators from the models of Kidner et al [63] and Eisele et al [72], respectively.  $A_{max3}$  is the maximum device area of planar RTD oscillators derived here. 171Typical specifications of tunnel diode 1N3717 ..... 2029.1

- 9.2 Typical specifications of tunnel diode 1N3714 ..... 203

#### LIST OF FIGURES

- 1.2 Cross-section of a tunnel diode and the corresponding band diagram.  $E_{cp}$ ,  $E_{vp}$  and  $E_{Fp}$  are the conduction band, valence band and Fermi-level of the p-type semiconductor, respectively, and  $E_{cn}$ ,  $E_{vn}$  and  $E_{Fn}$  are the conduction band, valence band and Fermi-level of the n-type semiconductor, respectively, and  $V_{bias}$  is the forward bias voltage. a) The cross-section of a tunnel diode, b) band diagram without forward bias  $V_{bias} = 0$ , c) band diagram with forward bias at peak voltage  $V_{bias} = V_p$ , d) band diagram with forward bias at valley voltage  $V_{bias} = V_v$ . [46], [48]. . . . . . . . . . . . . . . . .

7

3

1.3 Typical current-voltage characteristic of a tunnel diode [46]. . . . 9

- 1.4 A cross-section of a resonant tunnelling diode and the corresponding conduction band diagram under forward bias, and the corresponding *I-V* curve.  $E_{cE}$  and  $E_{FE}$  are the conduction band and Fermi-level of the emitter, respectively, and  $E_{cC}$  and  $E_{FC}$  are the conduction band and Fermi-level of the collector, respectively, and  $V_{bias}$  is the forward bias voltage. a) The cross-section of a resonant tunnelling diode, b) conduction band diagram without forward bias  $V_{bias} = 0, c$  conduction band diagram with forward bias at peak voltage  $V_{bias} = V_p$ , d) conduction band diagram with forward bias at valley voltage  $V_{bias} = V_v$ . e) Typical current-voltage characteristic of a tunnel diode [46], [52].

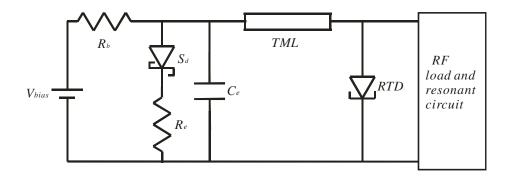

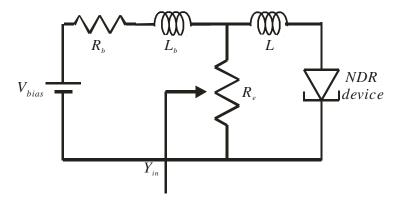

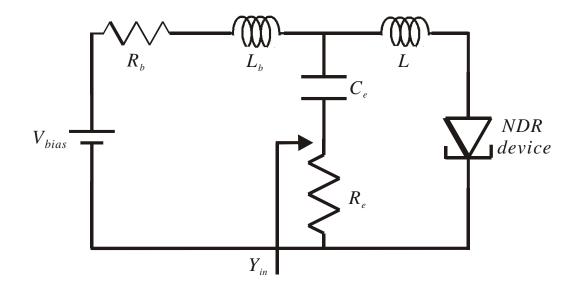

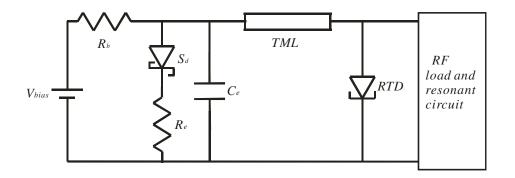

- 1.6 Reddy's bias stabilization scheme for sub-mm-wave RTD oscillators.  $R_b$  is the resistance of the bias line.  $S_d$ ,  $R_e$  and  $C_e$  are the Schottky diode, external resistor and external capacitor, respectively, which form the stabilising circuit. TML is the quarter-wave length transmission line at the oscillation frequency [83]. . . . . . 19

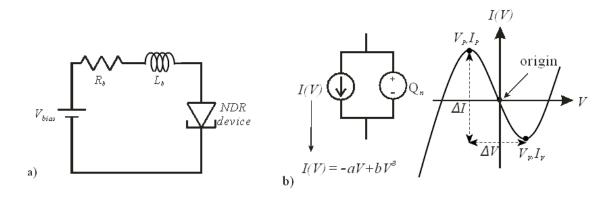

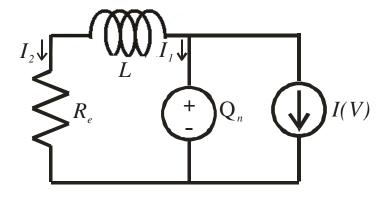

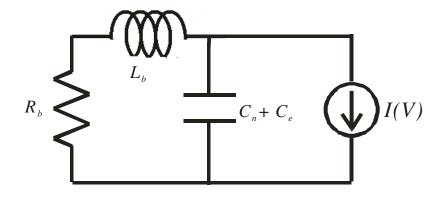

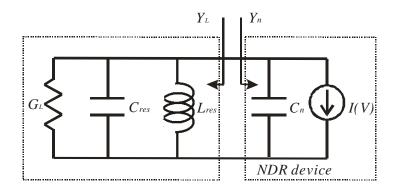

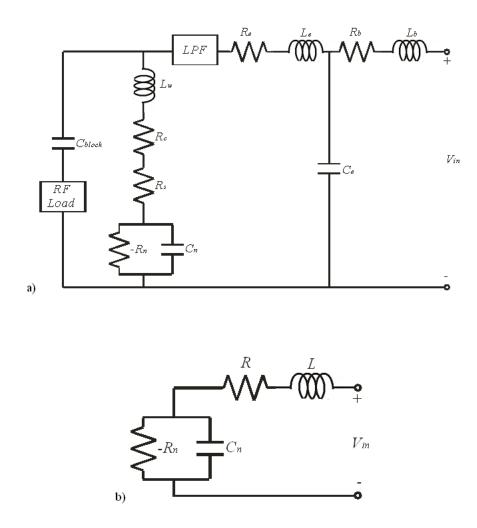

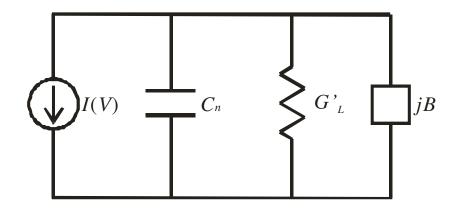

- 2.3 (a) A NDR device with DC bias, (b) A large-signal model for the NDR device biased in the NDR region. The voltage controlled current source I(V) is modelled by a cubic polynomial. The charge an the pn junction is modelled by a charge source  $Q_n(V)$ . . . . . 31

- 2.4 (a) A small-signal equivalent circuit of Fig.2.3(a).  $R_b$ ,  $R_s$  and  $L_s$ are typically small therefore they are ignored in the RF equivalent circuit, (b) A large-signal RF equivalent circuit of Fig. 2.3(a). . . 32

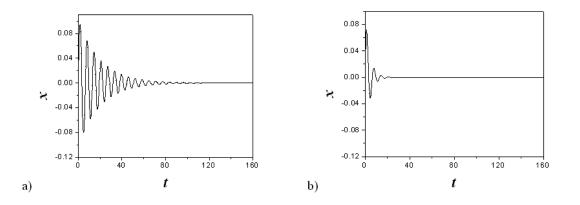

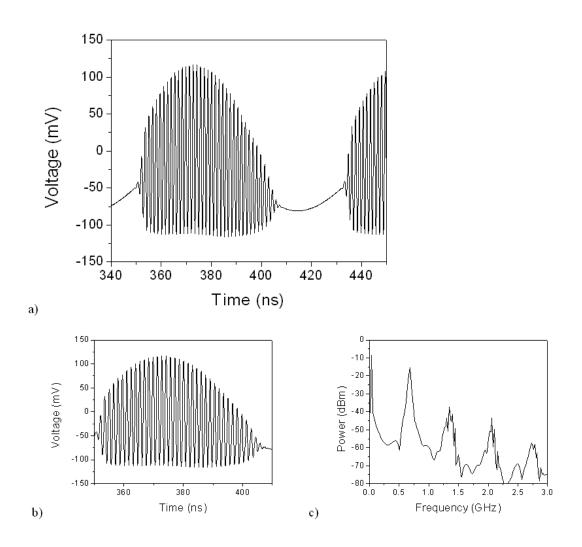

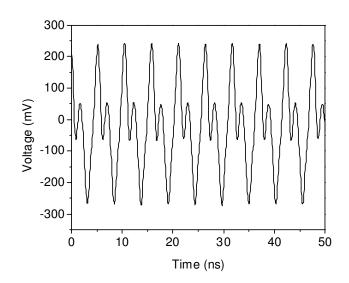

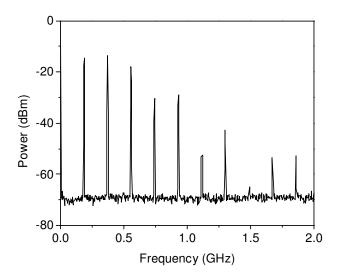

- 3.1 Simulation results of the tunnel diode bias circuit with  $R_e > 1/G_n$ .  $R_b = 1 \ \Omega, \ L_b = 56 \ \text{nH}, \ L = 2 \ \text{nH}, \ R_e = 50 \ \Omega, \ \text{and} \ V_{bias} = 145$ mV (the DC voltage across the tunnel diode is 140 mV). (a) Time domain signal of the voltage across the NDR device (b) The spectrum of the voltage across the diode. The circuit oscillates at a low frequency (137 MHz) as determined by the bias line ( $L_b = 56 \ \text{nH}$ ) and the tunnel diode capacitance characteristics ( $C_n = 13 \ \text{pF}$ ). 45

- 3.2 Simulation results of the tunnel diode bias circuit with R<sub>e</sub> < 1/G<sub>n</sub>.

R<sub>b</sub> = 1 Ω, L<sub>b</sub> = 56 nH, L = 2 nH, R<sub>e</sub> = 5 Ω and V<sub>bias</sub> = 170 mV (the DC voltage across the tunnel diode is 140 mV). (a) Time domain signals of the voltage across the load R<sub>L</sub> over a 100 ns time span,

(b) Time domain signals of the voltage across the load R<sub>L</sub> over a 25 ns time span, (c) The spectrum of the diode voltage. . . . . . 46

- 3.3 Time domain simulation results of the tunnel diode bias circuit with  $aL/C_n < R_e < 1/a$ .  $R_b = 1 \ \Omega$ ,  $L_b = 56 \ \text{nH}$ ,  $L = 2 \ \text{nH}$ ,  $R_e = 15 \ \Omega$ , and  $V_{bias} = 155 \ mV$  (the DC voltage across the tunnel diode is 140 mV). It shows that neither low-frequency bias oscillations nor high frequency oscillations are present.

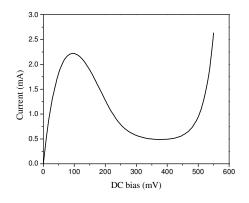

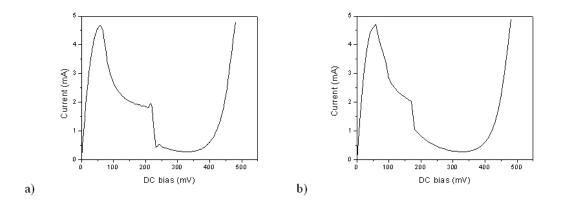

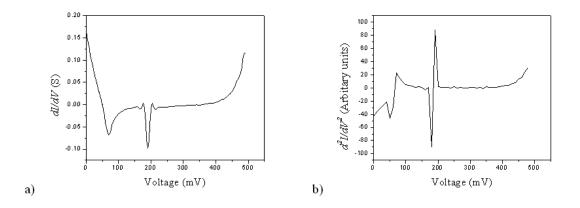

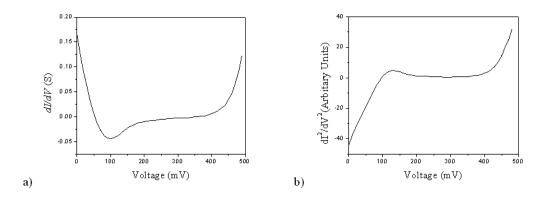

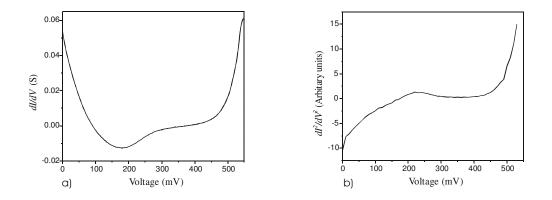

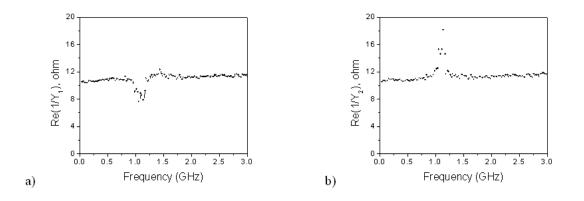

- 3.11 First (a) and second (b) derivatives of the *I-V* curve of the stabilised 1N3717 tunnel diode (Fig. 3.7(b)). Here  $R_e = 15 \ \Omega$ . There are no sharp valleys followed immediately by sharp peaks in the second derivative showing no oscillations are present during measurement. 57

- 3.12 First (a) and second (b) derivatives of the *I-V* curve of the stabilised

1N3714 tunnel diode (Fig. 2.14(c)). There are no valleys/peaks in

the second derivative showing no oscillations present during measurement.

58

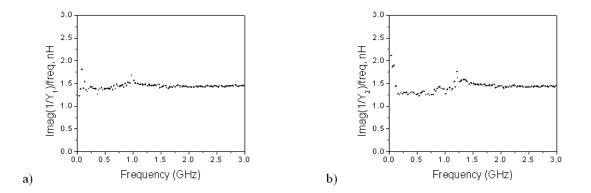

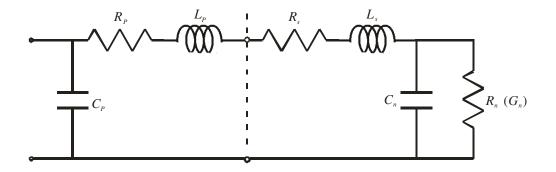

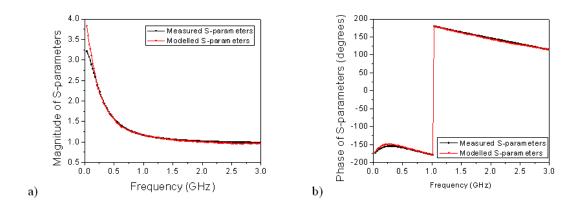

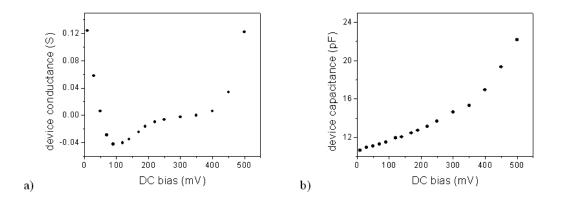

- 4.7 Extracted device conductance and capacitance of a tunnel diode

(1N3717) with different DC bias voltages: a) The extracted device

conductance, b) the extracted device capacitance.

68

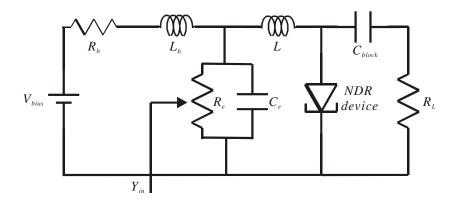

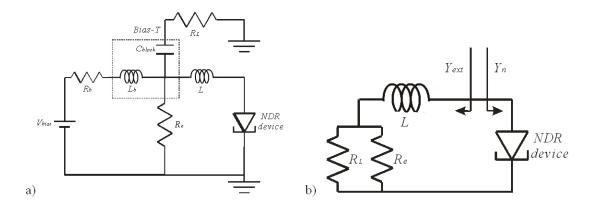

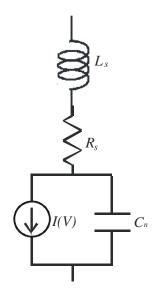

- 5.1 A NDR device oscillator topology with the DC decoupling circuit  $(R_e, C_e)$ .  $R_b$  and  $L_b$  model the resistance and inductance of the bias line.  $C_{block}$  and  $R_L$  are DC block and load, respectively. The total inductance L and capacitance of the NDR device determine the frequency of oscillation.

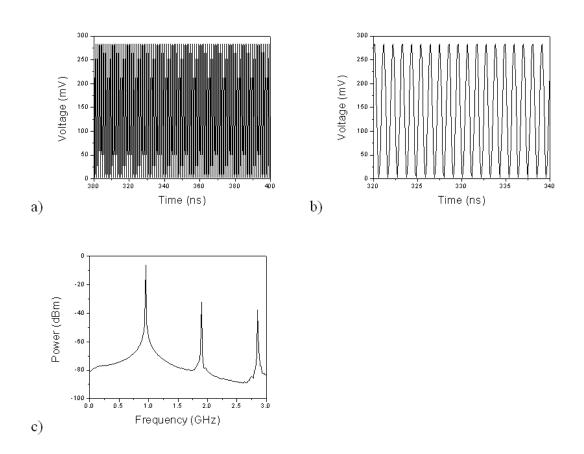

76

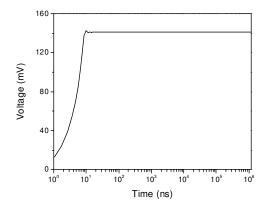

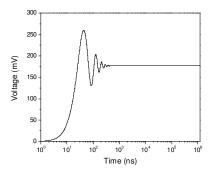

- 5.2 Simulation result of the tunnel diode oscillator with  $R_e < 1/G_n$ .  $R_b = 1 \Omega$ ,  $L_b = 56 \text{ nH}$ , L = 4 nH,  $R_e = 15 \Omega$ ,  $C_e = 2.5 \text{ nF}$ ,  $R_L = 50$   $\Omega$ ,  $C_{block} = 2.5 \text{ nF}$  and  $V_{bias} = 180 \text{ mV}$ . It shows the time domain signal of the voltage across the shunt resistor  $R_e$ . The voltage across  $R_e$ , which is the same as across the bias line, is constant with time indicating that no bias oscillations are present.

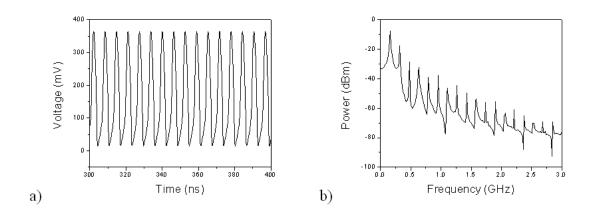

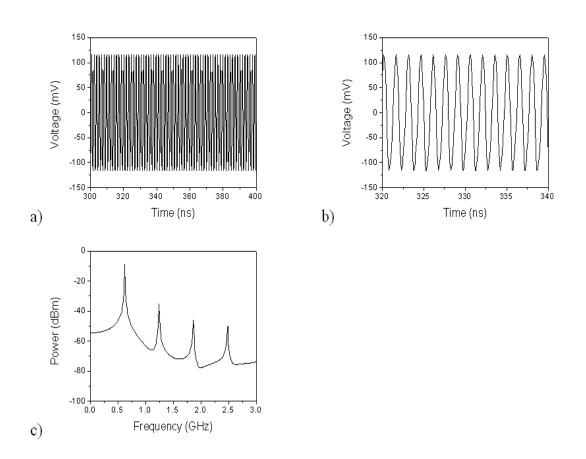

- 5.3 Simulation results of the tunnel diode bias circuit with the same conditions as shown in Fig. 5.2. (a) Time domain signal of the voltage across the load  $R_L$ . (b) The voltage across the load  $R_L$ between 320 ns and 340 ns. (c) The spectrum of the voltage across the  $R_L$ . The circuit oscillates at high frequency (625 MHz) determined by series inductor (L = 4 nH) and tunnel diode capacitance  $C_n$ .....

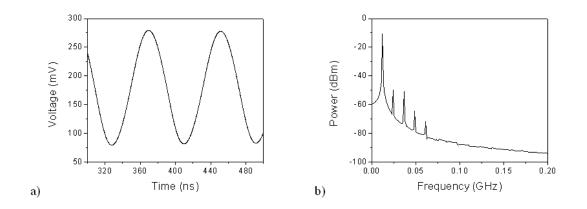

5.4 Simulation results of the tunnel diode oscillator with  $R_e > 1/G_n$ .  $R_b = 1 \ \Omega, \ L_b = 56 \ \text{nH}, \ L = 0 \ \text{nH}, \ R_e = 50 \ \Omega, \ C_e = 2.5 \ \text{nF}, \ R_L =$   $50 \ \Omega, \ C_{block} = 2.5 \ \text{nF}$  and  $V_{bias} = 180 \ \text{mV}$ . (a) Time domain signal of the voltage across the shunt resistor  $R_e$ . (b) The spectrum of the voltage across  $R_e$ .

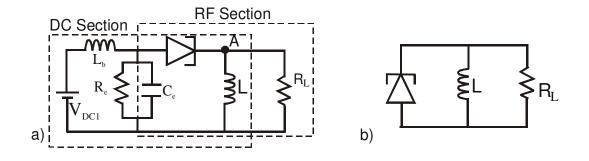

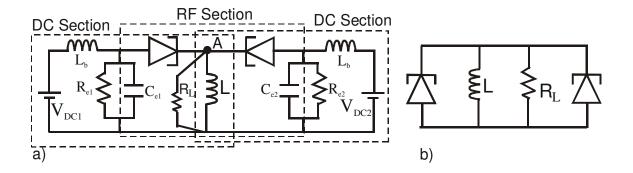

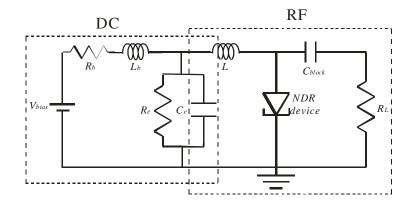

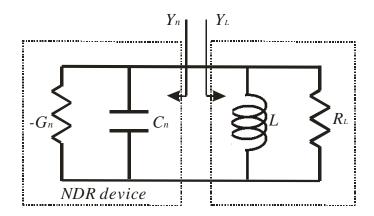

- 5.6 a) A single NDR device oscillator topology with DC stabilisers  $C_e$ and  $R_e$  ( $R_e < 1/G_n$ ), oscillation frequency determining inductance L, and load resistance  $R_L$ . b) RF equivalent circuit  $\ldots \ldots \ldots 82$

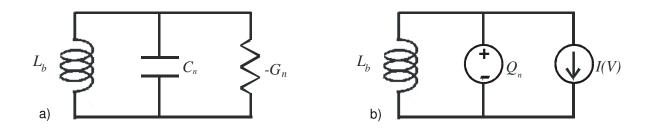

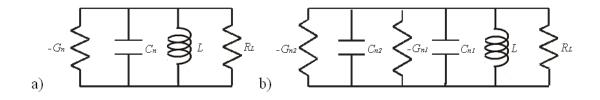

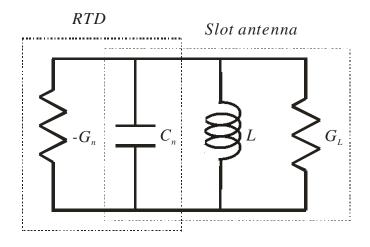

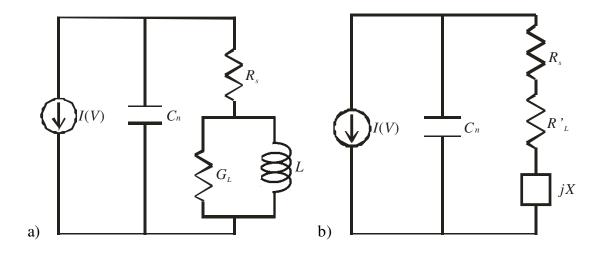

| 5.8  | (a) RF equivalent circuit of a single NDR device oscillator (Fig.             |    |

|------|-------------------------------------------------------------------------------|----|

|      | 5.6): $-G_n$ and $C_n$ are the negative differential conductance and          |    |

|      | the capacitance of the NDR device based in the NDR region, (b)                |    |

|      | RF equivalent circuit of a two NDR device parallel-connected os-              |    |

|      | cillator (Fig. 5.11): $-G_{n1}$ , and $-G_{n2}$ are the negative differential |    |

|      | conductance, and $C_{n1}$ and $C_{n2}$ are the capacitances of the NDR        |    |

|      | device 1 and NDR device 2 biased in the NDR region, respectively.             | 83 |

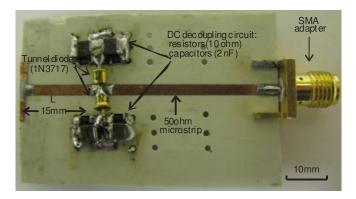

| 5.9  | A picture of a two tunnel diodes (1N3717) parallel-connected oscil-           |    |

|      | lator realized in hybrid microstrip technology.                               | 85 |

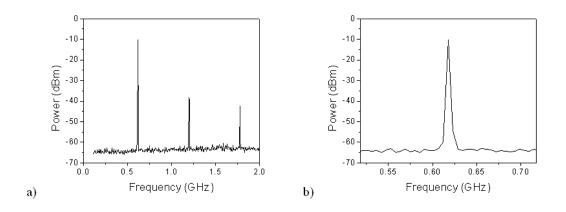

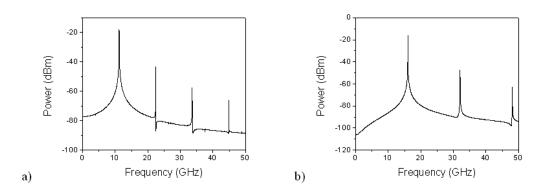

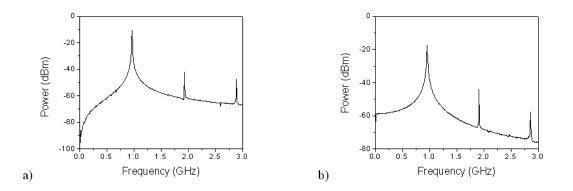

| 5.10 | a) The measured spectrum of a single tunnel diode oscillator with             |    |

|      | fundamental oscillations at $618$ MHz with -10.17 dBm output power.           |    |

|      | b)An expanded spectrum of Fig. 5.10(a) around the fundamental                 |    |

|      | oscillations frequency.                                                       | 88 |

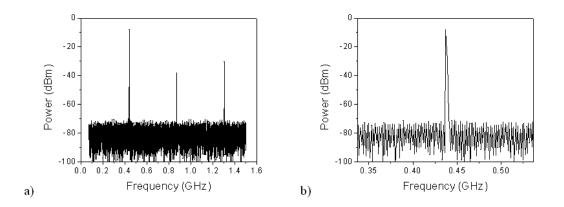

| 5.11 | a) The measured spectrum of a two tunnel diode parallel-connected             |    |

|      | oscillator with -7.83 dBm fundamental oscillations at 437 MHz. b) $$          |    |

|      | An expanded spectrum of Fig. 5.11(a) around the fundamental                   |    |

|      | oscillations frequency.                                                       | 89 |

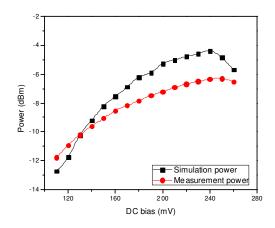

| 5.12 | The measured and simulated output power of the two tunnel diode               |    |

|      | parallel-connected oscillator as a function of bias voltage                   | 89 |

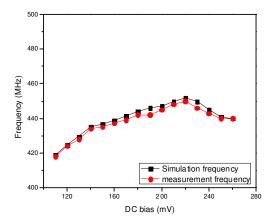

| 5.13 | The measured and simulated oscillation frequencies of the two tun-            |    |

|      | nel diode parallel-connected oscillator as a function of bias voltage.        | 90 |

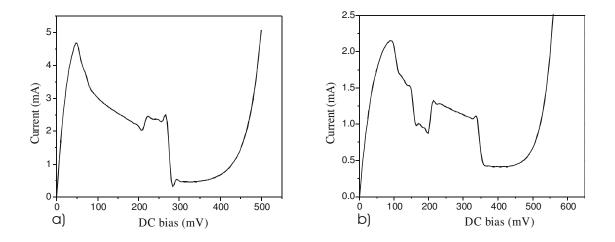

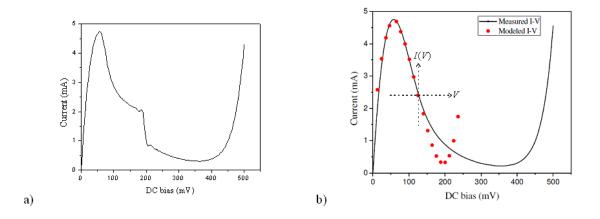

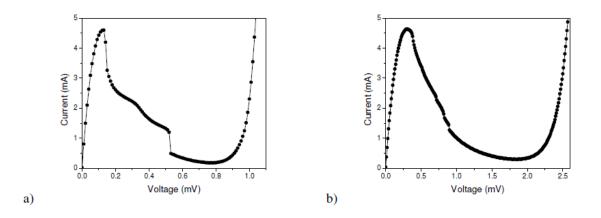

- 6.3 Measured *I-V* characteristics of two NDR devices (1N3717) connected in series. The *I-V* characteristic is not stretched along the voltage axis as expected due to DC instability. . . . . . . . . . 100

| 6.8  | Measured voltages across two individual tunnel diodes (1N3717) in             |     |

|------|-------------------------------------------------------------------------------|-----|

|      | the series integration as shown in Fig. $6.6(b)$ . The measurements           |     |

|      | show that the bias voltage is almost evenly split between the two             |     |

|      | devices.                                                                      | 111 |

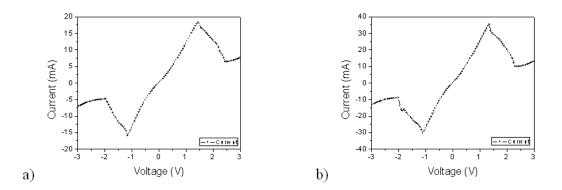

| 6.9  | Extracted $I-V$ characteristics of a) 2 and b) 5 tunnel diodes (1N3717)       |     |

|      | connected in series. Compared to the $I\text{-}V$ characteristics of a single |     |

|      | device as shown in Fig. 3.7(b), the voltage axis is expanded 2 and            |     |

|      | 5 times, respectively                                                         | 112 |

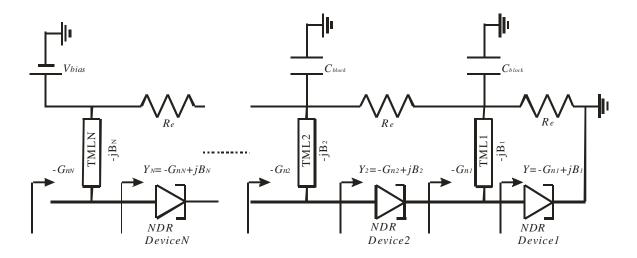

| 6.10 | An extended resonance power combining circuit topology with N                 |     |

|      | NDR devices connected in series. TML are transmission lines                   | 113 |

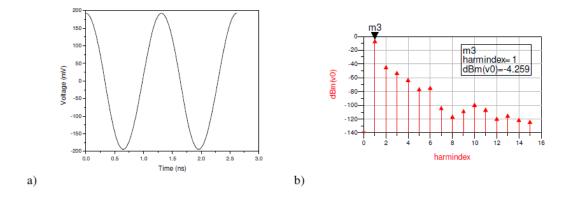

| 6.11 | Harmonic Balance simulation results for an oscillator with 3 tunnel           |     |

|      | diodes connected in series using the extended resonance technique.            |     |

|      | (a) Time domain signal of the voltage across the 50- $\Omega$ load. (b)       |     |

|      | The spectrum of the voltage obtained using a in-built function "fs"           |     |

|      | in ADS shows an output power of -4.259 dBm at the fundamental                 |     |

|      | frequency                                                                     | 115 |

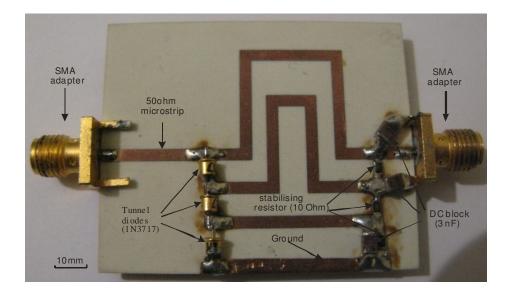

| 6.12 | A picture of the three series-connected tunnel diodes $(1N3717)$ os-          |     |

|      | cillator realised in hybrid microstrip technology.                            | 116 |

| 6.13 | Measured waveform of the three series-connected tunnel diodes                 |     |

|      | (1N3717) oscillator.                                                          | 117 |

| 6.14 | Measured spectrum of the three series-connected tunnel diodes (1N37             | 17) |

|------|---------------------------------------------------------------------------------|-----|

|      | oscillator.                                                                     | 117 |

| 6.15 | Transient/time domain simulation results for oscillator with three              |     |

|      | tunnel diodes connected in series using the extended resonance tech-            |     |

|      | nique. (a) Time domain signal of the voltage across the 50- $\Omega$ load.      |     |

|      | (b) The spectrum of the voltage across the 50 $\Omega$ load obtained using      |     |

|      | a in-built "fs" function in ADS                                                 | 119 |

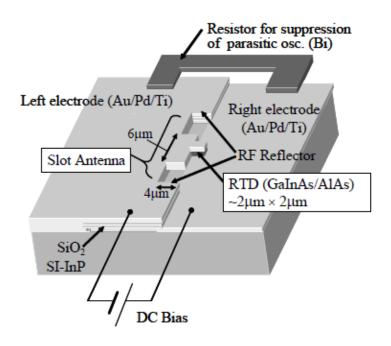

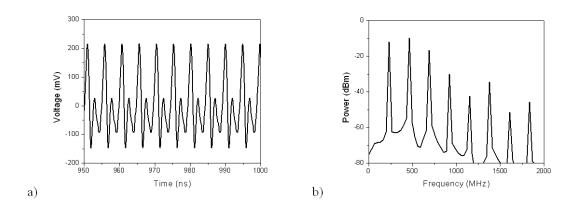

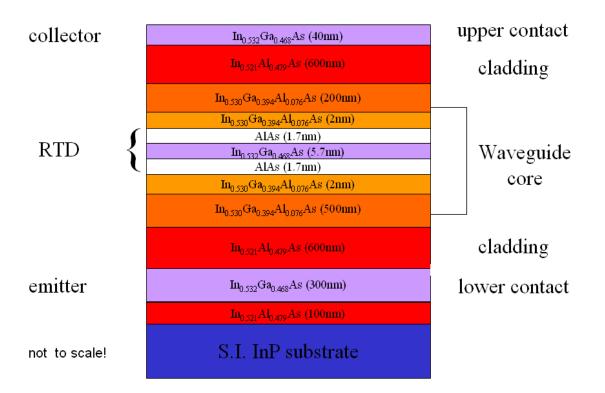

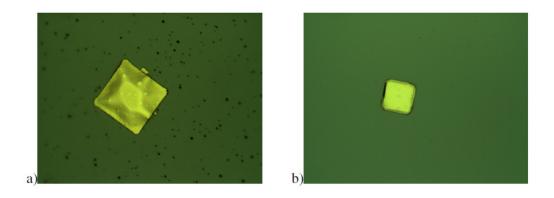

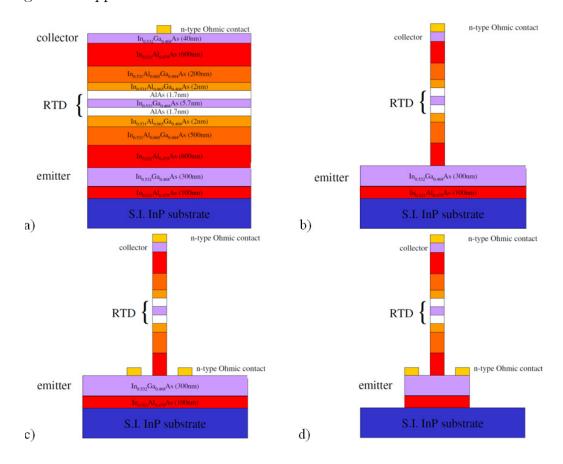

| 7.1  | The heterolayer structure specification for the RTD-OW wafer. It                |     |

|      | was grown by Molecular Beam Expitaxy in a Varian Gen II system                  |     |

|      | on a semi-insulating InP substrate by IQE, Ltd                                  | 123 |

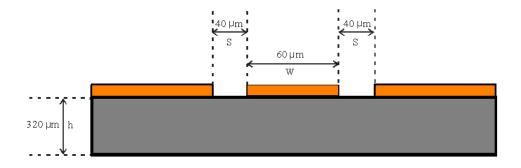

| 7.2  | Cross-section of a CPW on an InP substrate with a dielectric con-               |     |

|      | stant of 12.56 and a thickness of 320 $\mu \mathrm{m}.$ The signal line width W |     |

|      | = 60 $\mu$ m, and the gap space S = 40 $\mu$ m                                  | 128 |

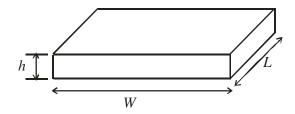

| 7.3  | The layout of the NiCr resistor. $L, W$ and $h$ are the length, width           |     |

|      | and thickness of the resistor, respectively.                                    | 129 |

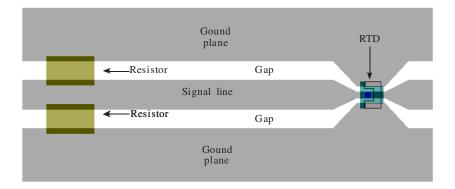

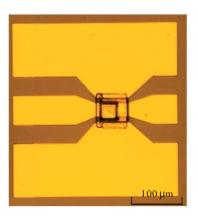

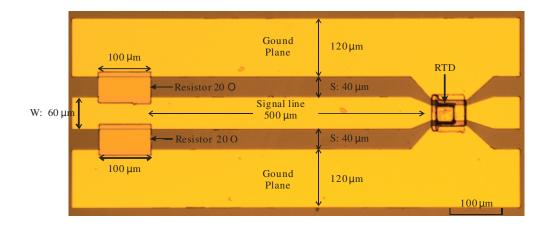

| 7.4  | Layout of MMIC RTD oscillator comprising an RTD and a DC                        |     |

|      | decoupling circuit (two resistors in parallel) embedded in a coplanar           |     |

|      | waveguide (CPW) line. The characteristic impedance of the CPW                   |     |

|      | is 50 $\Omega$ and its series inductance per unit length is 90 pH/mm. The       |     |

|      | output power can be measured from the right hand side using a                   |     |

|      | 50- $\Omega$ CPW probe.                                                         | 131 |

- 7.6 Simulated spectrum of a single RTD oscillator (400 μm<sup>2</sup>, device size) using a fitted *I-V* characteristic: a) Fundamental oscillations are at 11.26 GHz with -18.27 dBm output power with a 500 μm long CPW and 3.6 pF capacitor. b) Fundamental oscillations are at 16.07 GHz with -14.32 dBm output power with a 500 μm long CPW and 2 pF capacitor.

- 7.8 Cross-sectional views of the main fabrication steps for the RTD. . 145

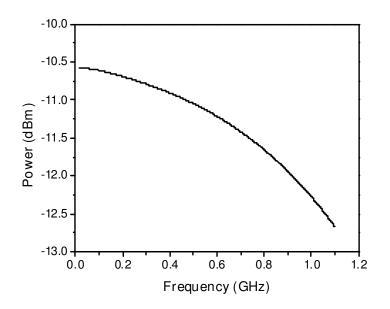

| 8.5  | Simulation results of the tunnel diode oscillator with $R_e < 1/G_n$ .                                                                                                  |     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | $R_b = 1 \Omega, L_b = 56 \text{ nH}, L = 2 \text{ nH}, R_e = 10 \Omega, C_e = 2.5 \text{ nF}, R_L =$                                                                   |     |

|      | 50 $\Omega,C_{block}=2.5~\mathrm{nF}$ and $V_{bias}=180$ mV. a) The power delivered                                                                                     |     |

|      | to the load $(R_L)$ at 935 MHz is -10.8 dBm with an RF short circuit                                                                                                    |     |

|      | via $C_e = 2.5$ nF. b) The power delivered to the load $(R_L)$ at 935                                                                                                   |     |

|      | MHz is -17.6 dBm without $C_e$ .                                                                                                                                        | 162 |

| 8.6  | a) The equivalent circuit for a resonant tunnelling diode waveguide                                                                                                     |     |

|      | oscillator including the bias circuit. b) The equivalent circuit where                                                                                                  |     |

|      | series elements have been combined without an external capacitor                                                                                                        |     |

|      | [63]                                                                                                                                                                    | 165 |

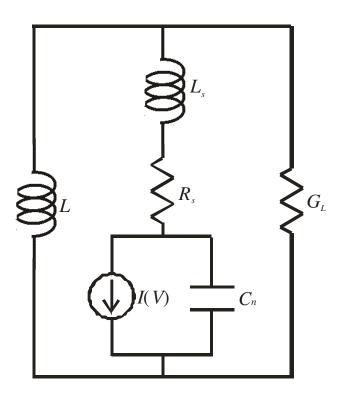

| 8.7  | RTD model with series resistance $R_s$ . $C_n$ is the device capacitance                                                                                                |     |

|      | and $I(V)$ is the voltage controlled current source                                                                                                                     | 173 |

| 8.8  | RF equivalent circuit of Fig. 8.3                                                                                                                                       | 177 |

| 8.9  | Re-drawn RF equivalent circuit of the circuit of Fig.8.8                                                                                                                | 177 |

| 8.10 | Parallel RTD oscillator with equivalent load conductance $G^\prime_L$ and                                                                                               |     |

|      | equivalent parallel susceptance $B$                                                                                                                                     | 178 |

| 8.11 | Simulated output power versus frequency for the 1N3717 tunnel                                                                                                           |     |

|      | diode                                                                                                                                                                   | 179 |

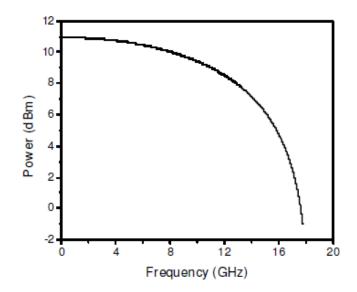

| 8.12 | Simulated output power versus frequency for RTD layer structure                                                                                                         |     |

|      | used in the MMIC oscillators described in Chapter 7, Table 7.1. $% \left( {{\left( {{{\left( {{{\left( {{{\left( {{{}}} \right)}} \right)}}}} \right)}_{0.2}}} \right)$ | 180 |

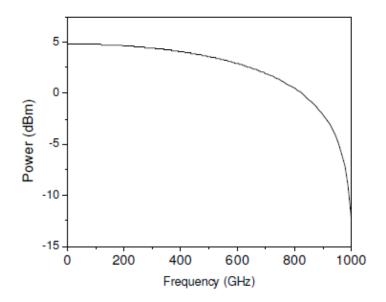

| 8.13 | Simulated output power versus frequency for RTD layer structure     |     |

|------|---------------------------------------------------------------------|-----|

|      | in Ref. <i>[36].</i>                                                | 181 |

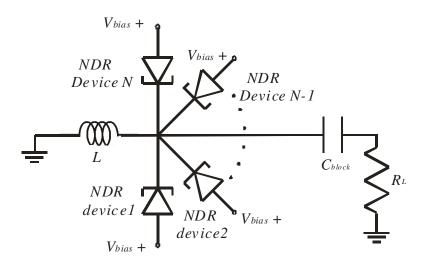

| 9.1  | A N tunnel diodes/RTDs parallel-connected oscillator topology with  |     |

|      | individual DC decoupling circuit for each device                    | 188 |

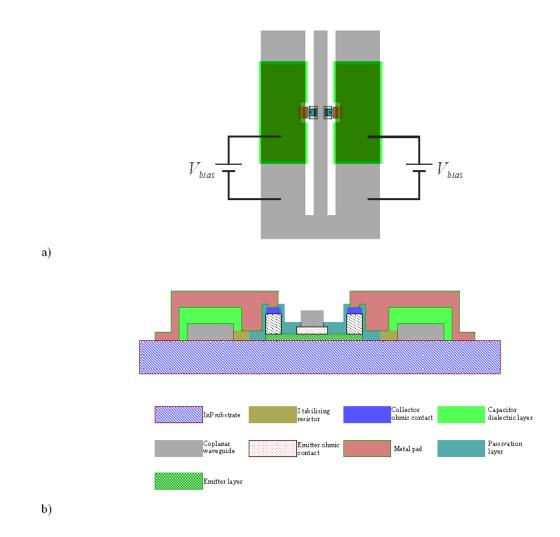

| 9.2  | Top view (a) and the cross-section (b) of an illustration of a MMIC |     |

|      | oscillator employing two RTDs.                                      | 189 |

# CHAPTER 1

## INTRODUCTION

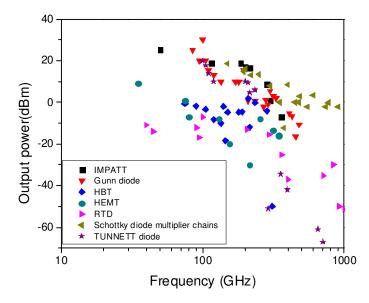

Millimetre-wave and submillimetre-wave signal sources are widely required for a variety of applications, such as medical imaging and radio astronomy [1], upper atmosphere study [2], [3], plasma diagnostics [4], security and surveillance [5], adaptive cruise control systems [6], biological imaging [7], and pollution monitoring and disease detection [8]. Several electronic devices may be used to build millimetrewave and submillimetre-wave sources. These include impact avalanche transittime (IMPATT) diodes [9], [10], Gunn diodes [10], [11], tunnel injection transittime (TUNNETT) diodes [12], [13], heterojunction bipolar transistors (HBT) [14], [15], high electron mobility transistors (HEMT) [16], [17], Schottky diode multiplier chains [18], [19] and resonant tunnelling diodes (RTD) [20], [21]. Fig. 1.1 summarises published RF power levels from the devices mentioned above. As can be seen, besides TUNNETT diodes, Schottky multiplier diode chains and RTDs are two of the sources that can provide RF signals above 500 GHz. The RF signals that can be achieved by Schottky diode multiplier chains range from 14.8-15.4 dBm<sup>1</sup> at 200 GHz [19], -2 dBm at 920 GHz [22] to -30 dBm - -25.2 dBm

<sup>&</sup>lt;sup>1</sup>To express an arbitrary power P as x dBm, or vice versa, the following equations may be used:  $x = 10 \log_{10} P$  or  $P = 10^{(x/10)}$  where P is the power in mW and x is the power ratio in dBm.

at 1.8-1.9 THz [23] and -40 dBm at 2.55 THz [24]. The multiplier chains have been broadly used in the last two decades. However, they require input signals that largely depend upon the development of solid-state sources, some of which are shown in Fig. 1.1, and power amplifiers [18]. Moreover, to date the power conversion efficiency of the input signal to the output signal is below 10% above 600 GHz [18].

Three-terminal devices, whose performance is also shown in Fig. 1.1, have higher DC-to-RF conversion efficiency compared to two-terminal devices. For example, the DC-to-RF conversion efficiency for HEMT and HBT devices was reported to be up to 36% in the Ka-band [25], [26]. However, three-terminal devices have higher phase noise values compared to two-terminal devices [27], including RTDs [28]. IMPATT diodes, Gunn diodes and TUNNETT diode based millimetre-wave sources can provide higher RF output power levels compared to three-terminal devices. IMPATT-diode based sources were reported to achieve 18.9 dBm and 8.8 dBm at 115 GHz and 285 GHz, respectively [9]. Gunn diode based sources were also reported to achieve 24.9 dBm and 5.4 dBm at 82.4 GHz and 315 GHz, respectively [29]-[31]. TUNNETT-diode based sources, on the other hand, were reported to achieve 20 dBm and 10 dBm at 100 GHz and 200 GHz, respectively [13]. According to published results on Gunn diodes, IMPATT diodes and TUNNETT diode based sources, the DC-to-RF conversion efficiency is normally below 3% [13], [32]. To date, the highest operating frequencies for the HBT,

HEMT, IMPATT diode, TUNNETT diode and Gunn diodes based sources are 311 GHz, 480 GHz, 394 GHz, 706 GHz and 480 GHz, respectively [15], [16], [33]-[35].

Figure 1.1: Published state-of-the-art RF power levels for IMPATT diodes, Gunn diodes, HBTs, HEMTs, RTDs, Schottky diode multiplier chains and TUNNETT diodes in the frequency range of 10 – 1000 GHz [9]-[38].

RTD based sources can also provide RF power above 500 GHz. Fundamental oscillations at 712 GHz from an RTD oscillator were demonstrated by Brown and co-workers in 1991 [21]. Recently, fundamental frequency oscillations of an RTD oscillator close to (831 GHz, 915 GHz) and above a terahertz (1.04 THz) at room temperature were reported by Asada and co-workers [36], [37]-[39]. Compared to Schottky diode multiplier chains which require RF input signals, RTDs only require a DC source to produce an RF output signal. The DC power consump-

tion of RTDs is extremely low ( $\sim 1.2 \text{ mW}$  [40]) compared, for instance, to that of Gunn diodes ( $\sim 5 \text{ W}$  [6] but is considerably less for submillimetre-wave operation), IMPATT diodes or TUNNETT diodes. The DC-to-RF conversion efficiency for Gunn diode oscillators is approximately 1-3% [32]. Planar Gunn diodes [41] have lower DC consumption of about 70 mW but with still very poor DC-to-RF conversion efficiency ( $\sim 0.3\%$ ) and are therefore limited by Joule heating. An excellent review by Eisele of the state of the art and future of electronic sources at terahertz frequencies is provided in Ref. [42].

RTD oscillators are the only solid state oscillators to have demonstrated room temperature oscillations above 500 GHz. The theoretical DC-to-RF device conversion efficiencies of RTDs, which can be estimated from the *I-V* characteristic  $(P_{max} = 3\Delta I\Delta V/16 \text{ and } P_{DC} = I_{DC}V_{DC})^2$ , can reach as high as 20% [40]. However, DC-to-RF conversion efficiency of published millimetre-wave or terahertz RTD oscillators is less than 1% [32]. The low efficiency is attributed to parasitic bias oscillations and inefficient oscillator circuit topologies (as will be explained later in this thesis). RTDs may therefore be used to realise millimetre-wave and submillimetre-wave sources if the known problems of parasitic oscillations and low output power (which is also related to inefficient oscillator topologies) can be solved.

A two-terminal device with terminal DC electrical characteristics similar to an

$<sup>^{2}\</sup>Delta V$  and  $\Delta I$  are the peak-to-valley voltage and current differences, respectively.  $P_{max}$  is the theoretical maximum RF output power for a single RTD oscillator [100] and will be derived and discussed in chapter 8 on output power analysis.  $I_{DC}$  and  $V_{DC}$  are the RTD bias current and voltage, while  $P_{DC}$  is the DC power consumption.

RTD is the Esaki tunnel diode [43]. Both the tunnel diode and the RTD exhibit a negative differential resistance (NDR) region in their *I-V* characteristics, but RTDs are faster devices because of the faster tunnelling process that causes the NDR region and so have a much larger bandwidth. The NDR region in both device types is the reason they are well-suited to oscillator realisation. The electrical circuit design challenges such as parasitic oscillations and low oscillator output power limitations are common to both device types [44], [45], [46]. Therefore circuit concepts developed for tunnel diodes are applicable to RTDs so long as suitable circuit implementation technologies are used (suitable for the frequency of operation). Unlike RTDs, packaged tunnel diodes are commercially available and so can be used for prototyping oscillator circuits in hybrid form at low frequency to demonstrate new circuit concepts that could be applicable to RTDs.

The approach of using tunnel diodes to assess the potential of RTD circuits has been used by previous researchers [45], [46]. It is best suited only for prototyping planar RTD integrated oscillators, but clearly not for (rectangular) waveguide RTD oscillators due to the similar and dissimilar circuit implementations, respectively. Also, at high frequencies accurate modelling of the RTD to account especially for parasitic effects would be required. As will be described in subsequent chapters, many of the circuit concepts developed on this project were implemented using tunnel diodes. A brief description of the principle of operation of the tunnel diode and the resonant tunnelling diode is provided in the next sub-section.

## 1.1 Review of tunnel diode and RTD theory

## 1.1.1 Esaki Tunnel diodes [43], [46] - [49]

Tsu and Esaki [43] first proposed the resonant tunnelling structure. Heavily doped p-type and n-type semiconductors are used to build tunnel diodes. A p-type semiconductor is doped with acceptor impurities and an n-type semiconductor is doped with donor impurities. The Fermi-level (energy level where the probability of an available state being occupied by an electron is equal to 50 percent) of the intrinsic semiconductor is at the centre of the band gap [46]. However, for the doped semiconductors, the Fermi-level moves towards the valence band edge with increasing acceptor concentration or moves towards to the conduction band edge with increasing donor concentration [46]-[48].

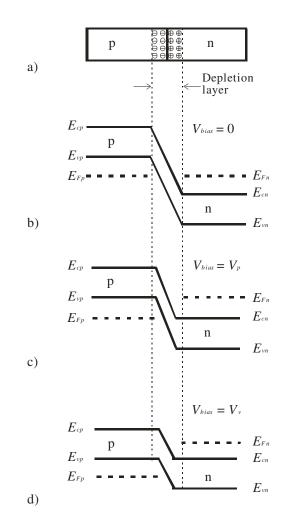

A cross section of a tunnel diode is shown in Fig. 1.2(a), which is a p-n junction structure made of heavily doped semiconductors (carrier concentrations of  $10^{19}$ per cm<sup>3</sup> to  $10^{20}$  per cm<sup>3</sup>) [47], [49]. The n-type semiconductor contains so many donor impurities that all of the states near the bottom of the conduction band are occupied by electrons so that the Fermi-level moves up into the conduction band instead of being located in the band gap (right side of Fig. 1.2). On the other hand, the p-type semiconductor contains so many acceptor impurities that all of the states near the top of the valence band are emptied of electrons so that the Fermi-level moves into the valence band instead of being located in the band gap (left side of Fig. 1.2).

Figure 1.2: Cross-section of a tunnel diode and the corresponding band diagram.  $E_{cp}$ ,  $E_{vp}$  and  $E_{Fp}$  are the conduction band, valence band and Fermi-level of the p-type semiconductor, respectively, and  $E_{cn}$ ,  $E_{vn}$  and  $E_{Fn}$  are the conduction band, valence band and Fermi-level of the n-type semiconductor, respectively, and  $V_{bias}$  is the forward bias voltage. a) The cross-section of a tunnel diode, b) band diagram without forward bias  $V_{bias} = 0$ , c) band diagram with forward bias at peak voltage  $V_{bias} = V_p$ , d) band diagram with forward bias at valley voltage  $V_{bias} = V_v$ . [46], [48].

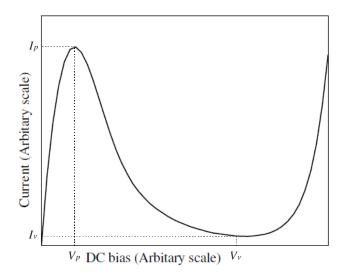

With no applied forward bias, no current flows through the junction (Fig. 1.2(b)). Then if a small forward (positive on the p-type semiconductor) bias is applied, it causes a large number of the electrons at the bottom of the conduction band of the n-type semiconductor to tunnel through to the top of the valence band of the p-type semiconductor. With increasing forward bias, a larger forward current flows through the junction because the overlap between the region between the Fermi-level and valence band of p-type semiconductor  $(E_{Fp} \text{ and } E_{vp})$  and the region between the Fermi-level and conduction band of n-type semiconductor  $(E_{Fn})$ and  $E_{cn}$  increase. When the forward bias reaches the peak voltage  $(V_p)$  which means the overlap reaches maximum, the tunnelling current reaches its peak current  $I_p$  (Fig. 1.2(c)). When the forward voltage is further increased, there are fewer available unoccupied states in the p-type semiconductor. Therefore the current decreases with the increasing forward bias and negative differential resistance (NDR) region is produced. When the forward bias reaches the valley voltage  $(V_v)$ , the bands are almost "uncrossed" and there are almost no unoccupied states in the p-type semiconductor available for tunnelling. Therefore, the tunnelling current reaches its valley current  $I_v$  (Fig. 1.2(d)). With still further increase of the voltage the normal thermal current will flow [46], [48]. Fig. 1.3 shows a typical current-voltage (I-V) characteristic of tunnel diode with forward bias. The depletion layer introduces a junction depletion capacitance, which is bias dependent

and it is given by [49]

$$\frac{1}{C_n^2} = \frac{2(V_{bi} - V_j - 2V_T)}{A^2 q \varepsilon_r n^*} \tag{1.1}$$

where  $C_n$  is the junction capacitance of tunnel diode,  $V_{bi}$  is the built-in potential voltage,  $V_j$  is the voltage across the p-n junction,  $V_T$  is the thermal voltage, Ais junction area, q is the elementary charge and  $\varepsilon_r$  is the relative permittivity of the material used to form the tunnel diode. The  $n^*$  is the effective carrier concentration [50], [51].

Figure 1.3: Typical current-voltage characteristic of a tunnel diode [46].

## 1.1.2 Resonant tunnelling diodes [46], [52]

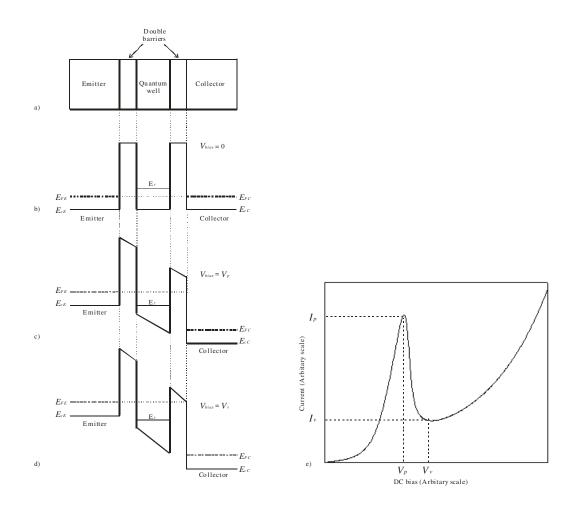

A resonant tunnelling diode (RTD) consists of three parts: 1) an emitter region, which is the source of electrons, 2) a double-barrier quantum-well (DBQW) structure which consists of a low band-gap quantum-well material sandwiched between two barriers of high band-gap material, 3) a collector region to collect the electrons tunnelling through the double-barrier structure. The emitter and collector regions are made of heavily doped n-type semiconductors. The crosssection and the corresponding conduction band diagram of an RTD are given in Fig. 1.4. The double-barrier structure is designed such that resonant energy levels are present in the quantum-well. Electrons from the emitter can tunnel through the barriers if their longitudinal energy is equal to one of the resonant energy levels in the quantum-well.

As shown in the band diagram of Fig. 1.4, if the forward bias (positive on the collector) is zero, there is no current because the electrons from the emitter cannot quantum mechanically tunnel through the double-barriers structure (Fig. 1.4(b)). When the forward applied bias is small, electrons from the emitter form an accumulation layer near the barrier and a small fraction of electrons reach the first resonant energy level and then can tunnel through the double-barriers structure, leading to a small current. As the voltage increases, the first resonant energy level ( $E_1$ ) of the quantum-well is moved downwards to the Fermi level of the emitter ( $E_{FE}$ ). A great number of electrons from the emitter can tunnel through the double-barriers structure into the collector, which leads to an increasing current with the forward bias. This continues until the maximum current  $I_p$  is reached when the first resonant energy level reaches  $(E_1)$  the bottom of the conduction band of emitter  $(E_{cE})$  which means that the overlap between the region of incident electrons from the emitter and the first resonant level region reaches a maximum (Fig. 1.4(c)). When a larger voltage is applied, fewer electrons from the emitter can go across the double barriers and the diode current rapidly drops and a negative differential resistance (NDR) region is produced. For even larger applied voltages, thermal emission over the barrier and tunnelling through the non-resonant energy levels of the well become important and the diode current rises rapidly (Figure 1.4(d)).

Since the double barrier structure is an undoped region sandwiched between two heavily doped regions, the device capacitance can be given approximately by

$$C_n = \frac{A\varepsilon_0\varepsilon_r}{d} \tag{1.2}$$

where,  $\varepsilon_0$  is the permittivity of free space,  $\varepsilon_r$  is the relative permittivity of the barrier and well materials, A is the area of the device and d is the width of the double barriers quantum well structure, i.e. consists of the width of the barrier layers, the quantum well and any spacer layers [53]. Unlike the tunnel diode junction capacitance which varies with bias, the RTD capacitance is largely bias independent.

Figure 1.4: A cross-section of a resonant tunnelling diode and the corresponding conduction band diagram under forward bias, and the corresponding I-V curve.  $E_{cE}$  and  $E_{FE}$  are the conduction band and Fermi-level of the emitter, respectively, and  $E_{cC}$  and  $E_{FC}$  are the conduction band and Fermi-level of the collector, respectively, and  $V_{bias}$  is the forward bias voltage. a) The cross-section of a resonant tunnelling diode, b) conduction band diagram without forward bias  $V_{bias} = 0$ , c) conduction band diagram with forward bias at peak voltage  $V_{bias} = V_p$ , d) conduction band diagram with forward bias at valley voltage  $V_{bias} = V_v$ . e) Typical current-voltage characteristic of a tunnel diode [46], [52].

## 1.2 NDR device characterisation and NDR oscillator circuits

## 1.2.1 DC (in)stability and equivalent circuit modelling

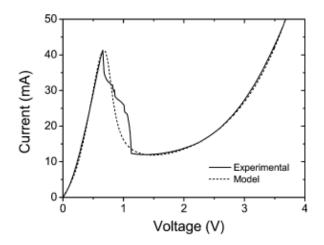

Accurate DC characterisation of the negative differential resistance (NDR) region of tunnel diodes or RTDs is often hindered by parasitic oscillations in the bias circuit making it difficult to determine the static characteristics of these devices in this very critical region [54]-[57] correctly. A common method to solve the bias instability problem is to employ a stabilising resistor connected directly across the tunnelling diode [46], [58]-[60]. The stabilising resistor is chosen such that the combined resistance (at DC and low frequencies) is positive when the tunnelling diode is biased in the NDR region. The diode characteristic is then determined indirectly. Another previously proposed method uses a large capacitor connected across the device [61], but the inductance of the interconnect between the capacitor and the tunnel diode must be kept very low for this to work [63]. The former method yields accurate results so long as the stabilising resistance value suppresses all oscillations in the circuit. This shunt resistor stabilisation method is to date the most accurate and robust method for DC characterisation of tunnel diodes. It is, however, known that either too large or too small a shunt resistor cannot suppress oscillations effectively [58], [60], [64], [65] and the oscillations present in the bias circuit modify the measured characteristics of the NDR region. Therefore as method to resolve this uncertainty and enable robust characterisation of the entire NDR region is desirable.

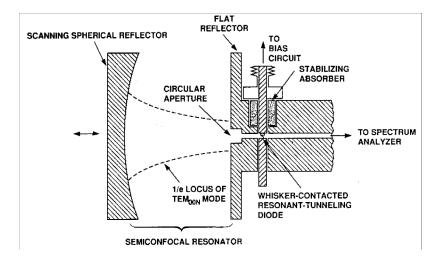

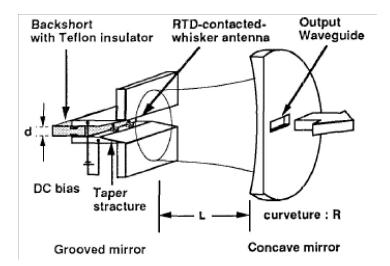

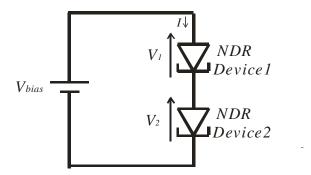

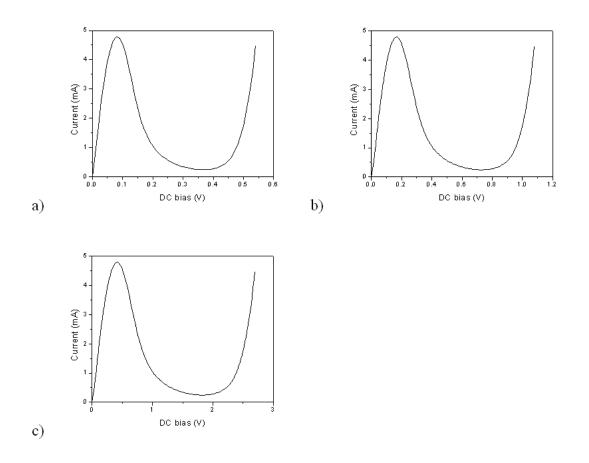

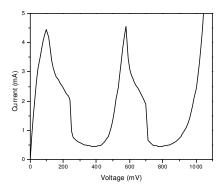

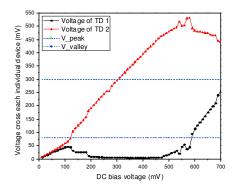

An RF model for RTDs is also required for circuit design, especially for high frequency analogue circuits such as submillimetre-wave oscillators. A few direct RF measurements have been reported from which the device equivalent circuit elements can be extracted, but these have been performed under very restricted bias conditions [66], [67], [68] or for small size devices for which the circuit was stable under measurement conditions. This is possible for some parts of the NDR region [70], [71] or the entire NDR region when the magnitude of the effective diode negative differential conductance is smaller than the conductance of the measurement set-up (which is usually 0.02 S) [62], [69]. Note that small area RTDs (corresponding to a negative differential resistance of say -100  $\Omega$ ) exhibit DC stability and so have no problem of low-frequency bias oscillations. DC stability is easily achieved here because of the sufficiently small negative conductance in small area devices (approx.  $1 \mu m^2$ ) [62]. However, because of the small size of the RTDs the output power of oscillators employing these is limited [63], [72].