# **Durham E-Theses**

# Design of a reliability methodology: Modelling the influence of temperature on gate Oxide reliability

Owens, Gethin Lloyd

#### How to cite:

Owens, Gethin Lloyd (2007) Design of a reliability methodology: Modelling the influence of temperature on gate Oxide reliability, Durham theses, Durham University. Available at Durham E-Theses Online: <a href="http://etheses.dur.ac.uk/2695/">http://etheses.dur.ac.uk/2695/</a>

#### Use policy

The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-profit purposes provided that:

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

# Design of a Reliability Methodology: Modelling the Influence of Temperature on Gate Oxide Reliability

# Gethin Lloyd Owens

The copyright of this thesis rests with the author or the university to which it was submitted. No quotation from it, or information derived from it may be published without the prior written consent of the author or university, and any information derived from it should be acknowledged.

A Thesis presented for the degree of Doctor of Philosophy

School of Engineering

University of Durham

Durham

UK

Design of a Reliability Methodology:

Modelling the Influence of Temperature

on Gate Oxide Reliability

Gethin Lloyd Owens

### **Abstract**

In any product design process there is a fundamental endeavour to design reliable products. This is to ensure that the product will have the capability to perform as designed for a required period of time. However in a world that demands faster and greater functionality of products, ensuring long-term reliability is ever becoming an increased concern. Advances in technology have provided huge performance benefits, but have also accelerated the onset of reliability problems. Compounding the problem is a growing demand for devices applicable to a wide range of operating environments such as elevated temperatures.

Traditionally reliability assurance has relied on failure analysis at the latter stages of the product development process. This involves a time consuming and costly cycle of re-design and testing that is simply no longer practical for today's time-to-market requirements. What is required is a quick and effective way of evaluating product reliability at the earliest stages of conceptual design and to allow the designer to repeatably examine and improve the product. In this thesis we address this problem with the design of a new reliability tool. This tool uses a novel methodology to integrate for the first time several failure mechanism models, thus providing a method of reliability analysis that can be used throughout the design process.

An Integrated Reliability Methodology (IRM) is presented that encompasses the changes that technology growth has brought with it and includes several new device degradation models. Each model is based on a physics of failure approach and includes on the effects of temperature. At all stages the models are verified experimentally on modern deep sub-micron devices. The research provides the foundations of a tool which gives the user the opportunity to make appropriate trade-offs between performance and reliability, and that can be implemented in the early stages of product development.

# **Declaration**

The work in this thesis is based on research carried out in the School of Engineering, University of Durham, UK. No part of this thesis has been submitted elsewhere for any other degree or qualification and it all my own work unless referenced to the contrary in the text.

#### Copyright © 2006 by Gethin Lloyd Owens.

"The copyright of this thesis rests with the author. No quotations from it should be published without the author's prior written consent and information derived from it should be acknowledged".

### Acknowledgements

Firstly I would like to thank my supervisor, Dr Simon Johnson, for his academic supervision and encouragement throughout my Ph.D. I remain grateful to Simon for giving me the opportunity to undertake a Ph.D. Discussions, guidance and feedback from Simon have provided invaluable for the development of the thesis and it has been a pleasure knowing and working with him. Additionally I would like to thank those at Goodrich, Bob Newman, Peter Shrimpling and Robert Edward's for their support and helpful suggestions throughout.

Thanks go to Andrew Maiden, a friend, colleague and housemate. Thanks not only for all his help and knowledge but also for sharing the experience. The long walks and life at Aden cottage (especially during the cold winter nights) will always be remembered. For her continued belief in me and the joy she has brought to me, I would like to thank my girlfriend, Joelle Davies. Your smile, and food parcels kept me going in those long days.

Finally a special thanks go to my family for their patience and for standing by me during the more difficult times. I would particularly like to thank my Dad for his love, and always being there for me, and my Mother who has given me the confidence to follow my ambitions in life. My love and gratitude is forever with you.

# Contents

| Abstract                                  | 11                                                                                                                                                                                                                                       |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Acknowledgements                          | v                                                                                                                                                                                                                                        |

| List of Figures                           | xii                                                                                                                                                                                                                                      |

| List of Tables                            | xvii                                                                                                                                                                                                                                     |

| Glossary                                  | 1                                                                                                                                                                                                                                        |

| Introduction                              | 3                                                                                                                                                                                                                                        |

| 1.1 Objectives and Focus of the Research  | . 5                                                                                                                                                                                                                                      |

| 1.2 Organisation of Thesis                | . 6                                                                                                                                                                                                                                      |

| Reliability in CMOS Technology : A Review | 7                                                                                                                                                                                                                                        |

| 2.1 Introduction                          | . 7                                                                                                                                                                                                                                      |

| 2.2 CMOS Reliability Review               | . 8                                                                                                                                                                                                                                      |

| 2.3 Physics of Failure                    | . 16                                                                                                                                                                                                                                     |

|                                           | Acknowledgements  List of Figures  List of Tables  Glossary  Introduction  1.1 Objectives and Focus of the Research  1.2 Organisation of Thesis  Reliability in CMOS Technology: A Review  2.1 Introduction  2.2 CMOS Reliability Review |

|   | 2.4 | ranure Methodologies                            |

|---|-----|-------------------------------------------------|

|   | 2.5 | Failure Mechanisms                              |

|   |     | 2.5.1 Electromigration                          |

|   |     | 2.5.2 Gate Oxide Failures                       |

|   |     | 2.5.2.1 Gate Induced Drain Leakage 2            |

|   |     | 2.5.2.2 Negative Bias Temperature Instability 2 |

|   |     | 2.5.3 Hot-Carrier Effects                       |

|   | 2.6 | High Temperature Effects                        |

|   | 2.7 | Alternative Materials                           |

|   | 2.8 | Silicon-On-Insulator Technology                 |

|   | 2.9 | Conclusion                                      |

| 3 | Hig | Temperature Device Model 40                     |

|   | 3.1 | Introduction                                    |

|   | 3.2 | Devices and Measurement                         |

|   | 3.3 | I-V Model                                       |

|   |     | 3.3.1 Threshold Voltage                         |

|   |     | 3.3.2 Linear Region                             |

|   |     | 3.3.3 Saturation Region                         |

|   |     | 3.3.4 Mobility Model                            |

|   |     | 3.3.5 Parasitic Drain/Source Resistance 5 | 12 |

|---|-----|-------------------------------------------|----|

|   |     | 3.3.6 Subthreshold Region                 | 2  |

|   |     | 3.3.7 Transition Region                   | 5  |

|   |     | 3.3.8 I-V Model Test Results              | 6  |

|   | 3.4 | Temperature Effects                       | 3  |

|   |     | 3.4.1 Carrier Mobility                    | 3  |

|   |     | 3.4.2 Velocity Saturation                 | 4  |

|   |     | 3.4.3 Threshold Voltage                   | 6  |

|   |     | 3.4.4 Subthreshold Swing Factor           | 8  |

|   |     | 3.4.5 Drain Source Resistance             | 9  |

|   |     | 3.4.6 Temperature Results                 | 0  |

|   | 3.5 | Conclusion                                | 2  |

| 4 | NB' | TI 74                                     | 1  |

|   | 4.1 | Introduction                              | 4  |

|   | 4.2 | Mechanism Overview                        | 5  |

|   | 4.3 | Experimental Method                       | 3  |

|   | 4.4 | NBTI Model                                | •  |

|   | 4.5 | Recovery Effect                           | 2  |

|   | 4.6 | Lock-in                                   | 7  |

|   | 4.7                                                                   | Dynamic Degradation                                               |

|---|-----------------------------------------------------------------------|-------------------------------------------------------------------|

|   | 4.8                                                                   | Conclusion                                                        |

| 5 | GII                                                                   | 94<br>94                                                          |

|   | 5.1                                                                   | Introduction                                                      |

|   | 5.2                                                                   | Mechanism Overview                                                |

|   | 5.3                                                                   | Experimental Method                                               |

|   | 5.4                                                                   | GIDL Model                                                        |

|   | 5.5                                                                   | Integration into I-V Model                                        |

|   | 5.6                                                                   | Conclusion                                                        |

|   |                                                                       |                                                                   |

| 6 | Hot                                                                   | -Carrier Effects 114                                              |

| 6 | Hot<br>6.1                                                            | -Carrier Effects 114 Introduction                                 |

| 6 |                                                                       |                                                                   |

| 6 | 6.1                                                                   | Introduction                                                      |

| 6 | 6.1<br>6.2                                                            | Introduction         114           Mechanism Overview         115 |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul>                         | Introduction                                                      |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li><li>6.4</li></ul>             | Introduction                                                      |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li><li>6.4</li><li>6.5</li></ul> | Introduction                                                      |

| 7 | An  | Integrated Reliability Methodology | 135 |

|---|-----|------------------------------------|-----|

|   | 7.1 | Introduction                       | 135 |

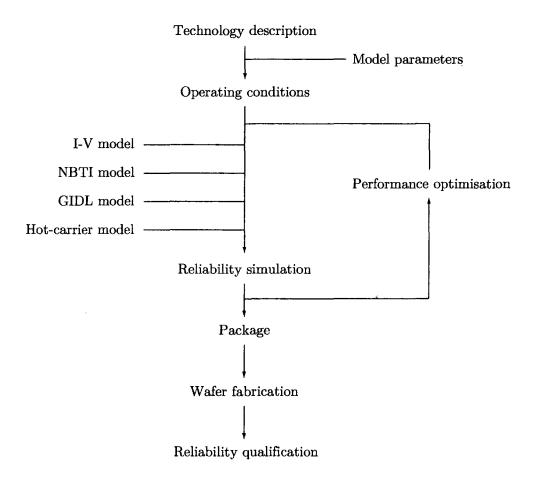

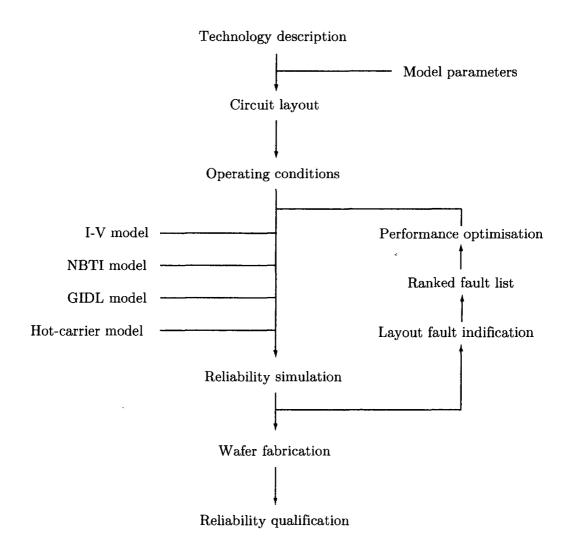

|   | 7.2 | Methodology                        | 136 |

|   | 7.3 | Tool Design                        | 138 |

|   | 7.4 | Simulation Results                 | 141 |

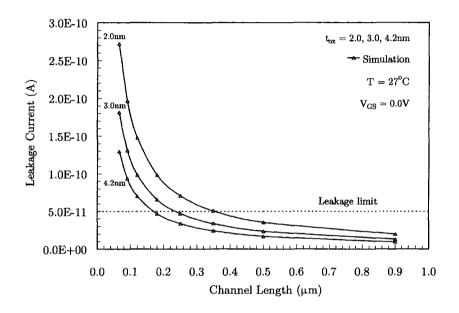

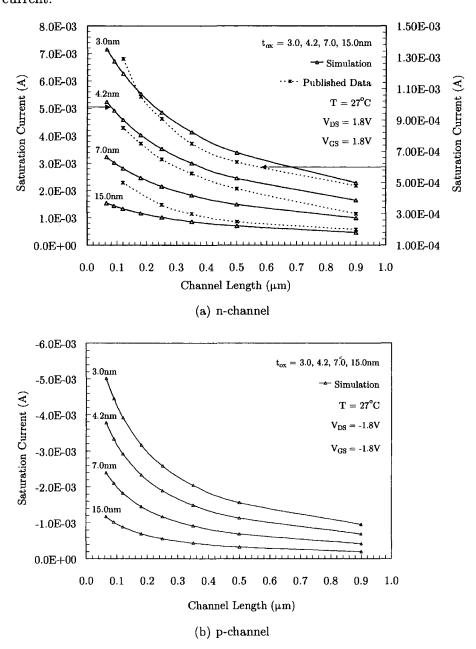

|   |     | 7.4.1 Scaling                      | 141 |

|   |     | 7.4.2 Failure Mechanisms           | 146 |

|   |     | 7.4.2.1 NBTI                       | 147 |

|   |     | 7.4.2.2 GIDL                       | 151 |

|   |     | 7.4.2.3 Hot-Carrier Effects        | 153 |

|   | 7.5 | Conclusion                         | 157 |

| 8 | Fut | ure Work and Conclusions           | 160 |

|   | 8.1 | Future Work                        | 160 |

|   |     | 8.1.1 Layout Diagnostics           | 161 |

|   |     | 8.1.2 Competing Failures           | 162 |

|   |     | 8.1.3 Tool Implementation          | 163 |

|   | 8.2 | Conclusions                        | 164 |

|   | Bib | liography                          | 167 |

| A Experimental Setup     | 181 |

|--------------------------|-----|

|                          |     |

| B Parameter Optimization | 183 |

# List of Figures

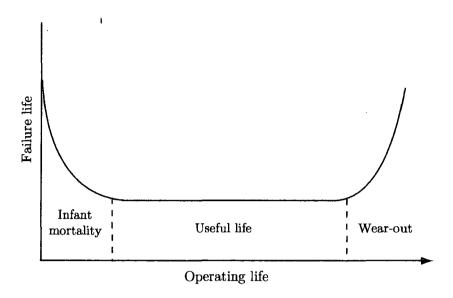

| 2.1 | Bathtub curve                                      | 9  |

|-----|----------------------------------------------------|----|

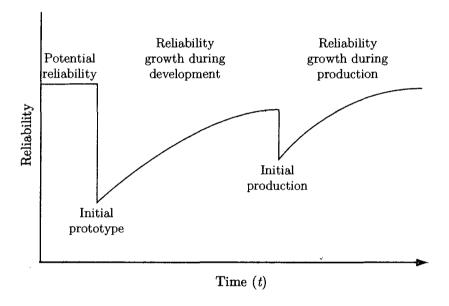

| 2.2 | Product development cycle                          | 10 |

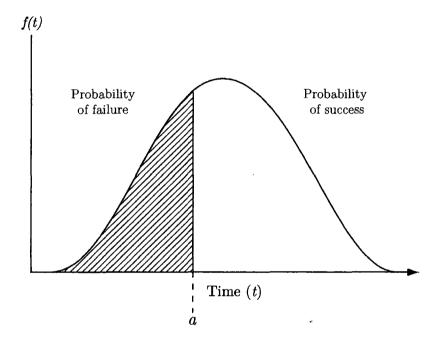

| 2.3 | Reliability distribution                           | 11 |

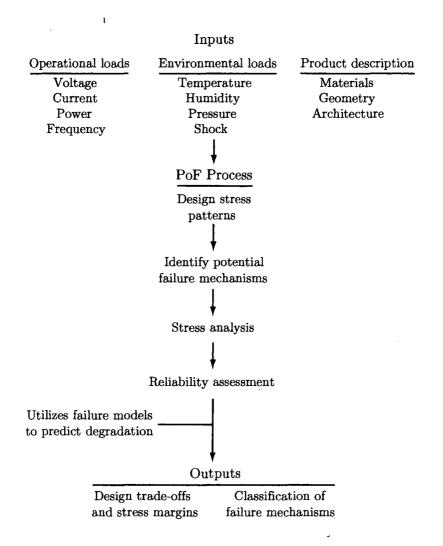

| 2.4 | Physics of failure process                         | 17 |

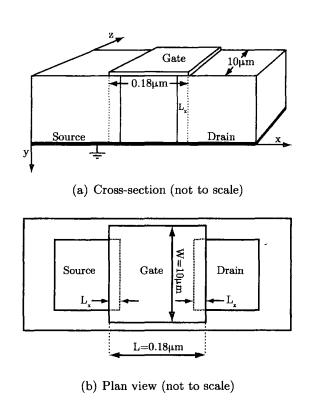

| 3.1 | An image of $0.18\mu\mathrm{m}$ n-channel device   | 41 |

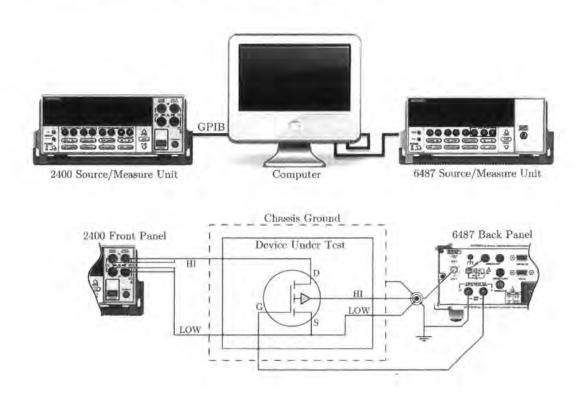

| 3.2 | Schematic diagram of experimental setup            | 42 |

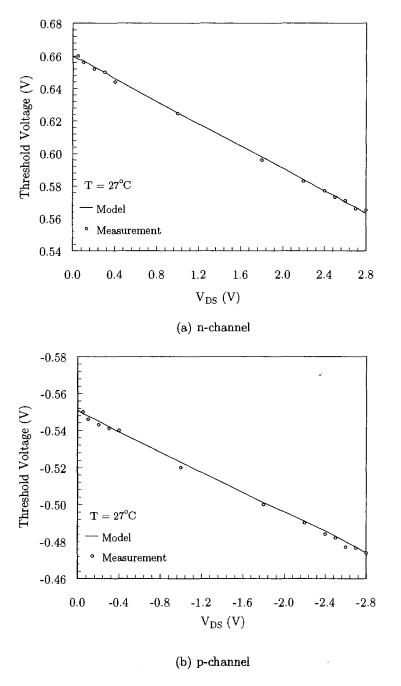

| 3.3 | Threshold voltage as a function of drain voltage   | 44 |

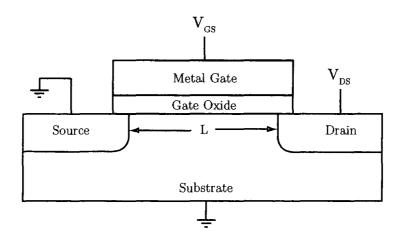

| 3.4 | MOSFET gate construction                           | 46 |

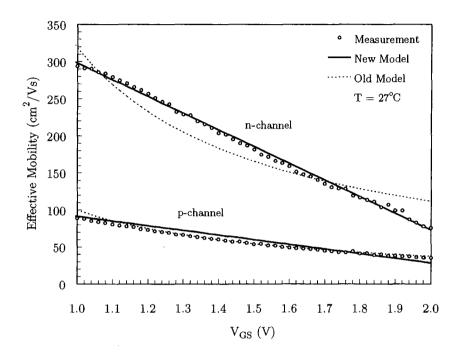

| 3.5 | Mobility as a function of gate voltage             | 51 |

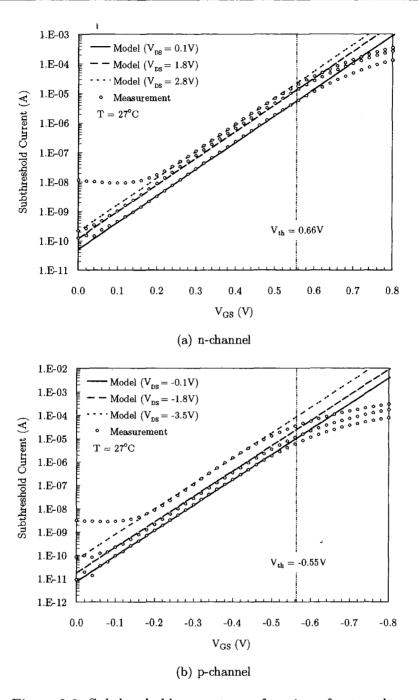

| 3.6 | Subthreshold current as a function of gate voltage | 54 |

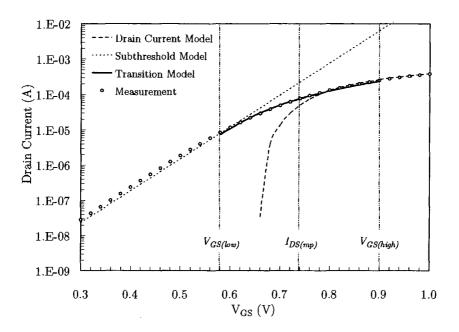

| 3.7 | Illustration of the transition region              | 56 |

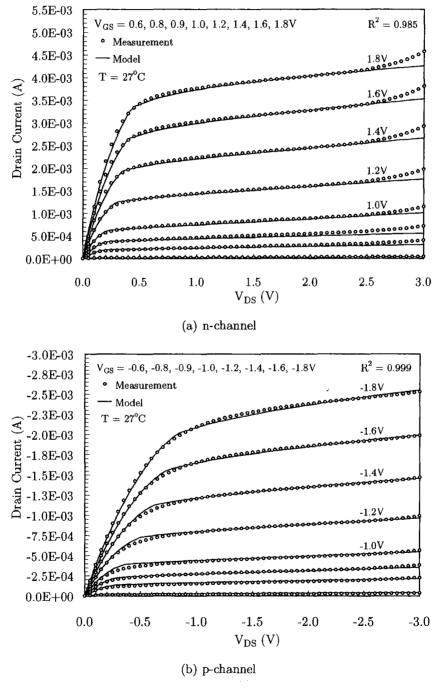

| 3.8 | $V_{DS}$ - $I_{DS}$ characteristic                 | 58 |

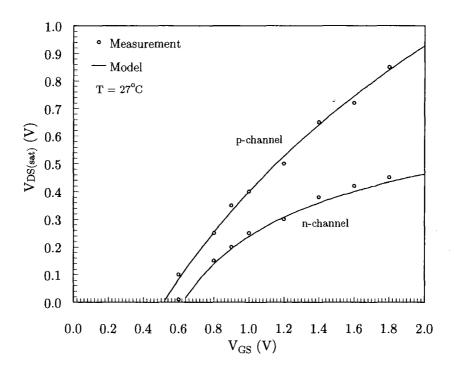

| 3.9 | Saturation voltage as a function of gate voltage   | 59 |

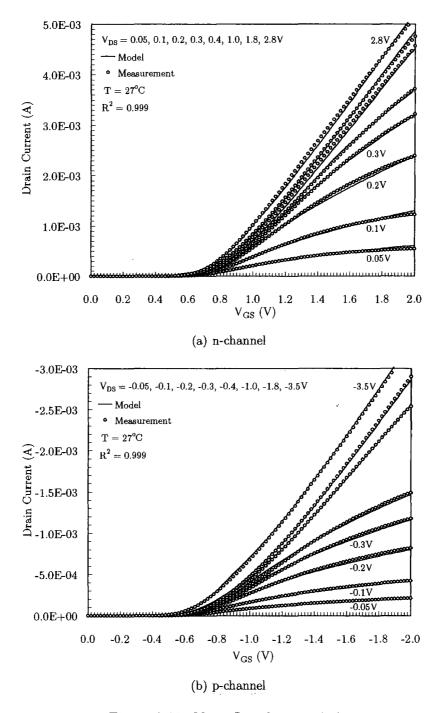

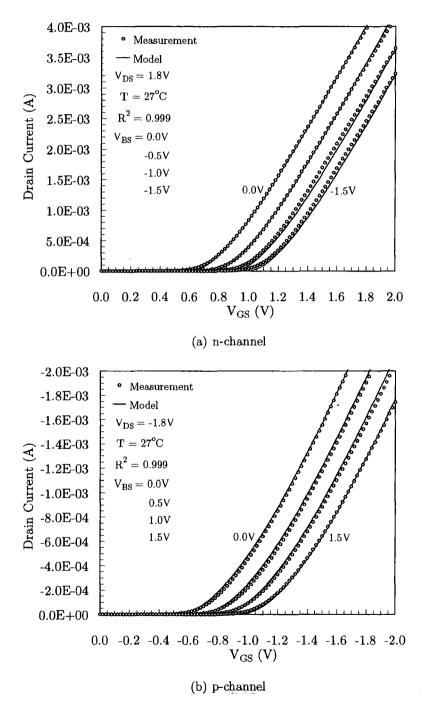

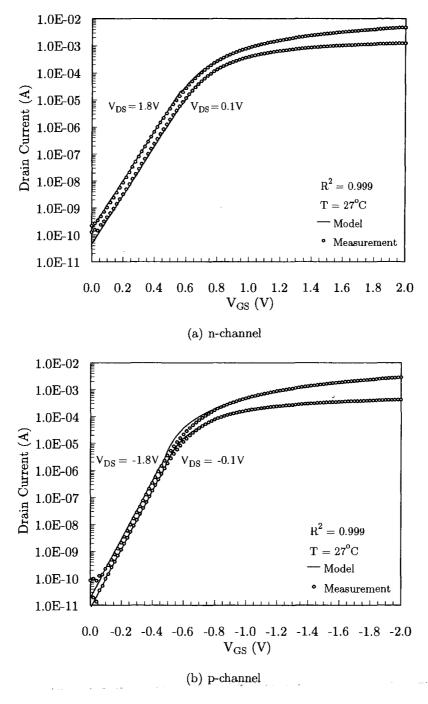

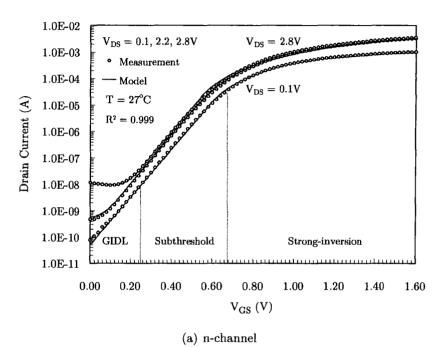

| 3.10 | $V_{GS}$ - $I_{DS}$ characteristic                                               | 60 |

|------|----------------------------------------------------------------------------------|----|

| 3.11 | $V_{GS}$ - $I_{DS}$ characteristic as a function of substrate bias $\dots \dots$ | 61 |

| 3.12 | Logarithmic $V_{GS}$ - $I_{DS}$ characteristic                                   | 62 |

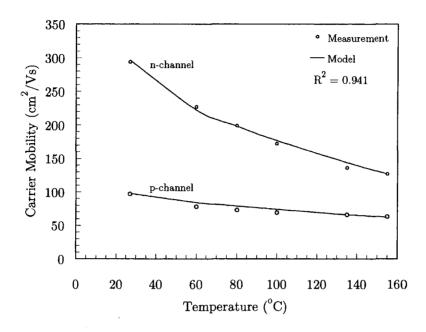

| 3.13 | Carrier mobility as function of temperature                                      | 64 |

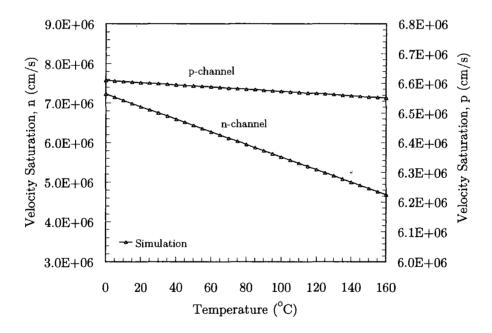

| 3.14 | Velocity saturation as function of temperature                                   | 65 |

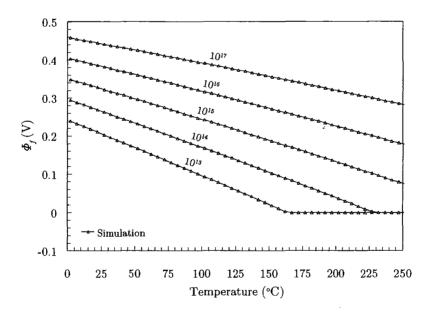

| 3.15 | Fermi potential as a function of temperature                                     | 66 |

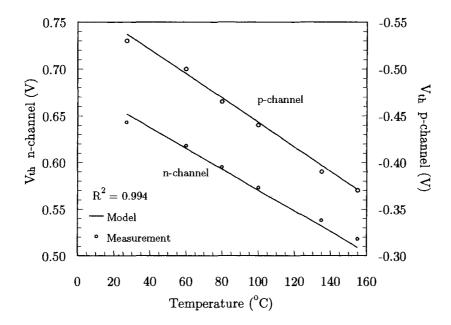

| 3.16 | Threshold voltage as a function of temperature                                   | 67 |

| 3.17 | Temperature dependence of the subthreshold region (p-channel)                    | 68 |

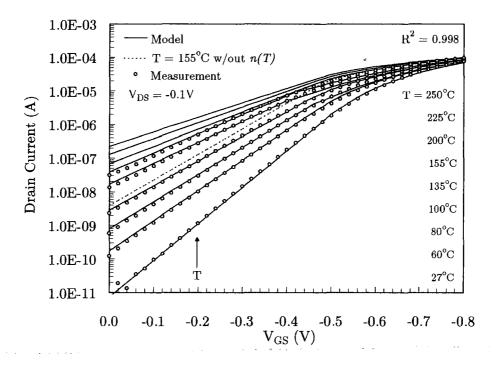

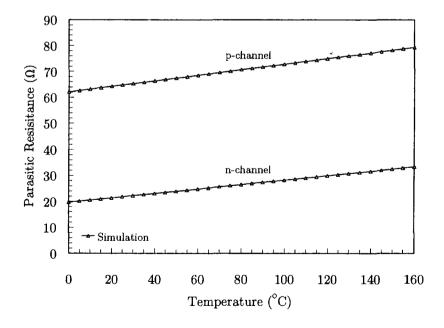

| 3.18 | Temperature dependence of parasitic resistance                                   | 69 |

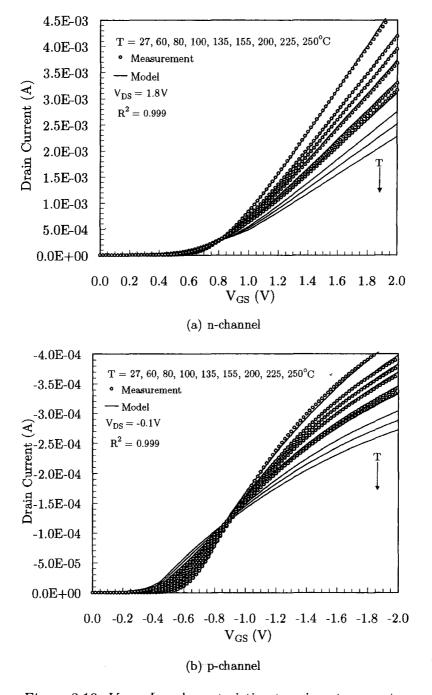

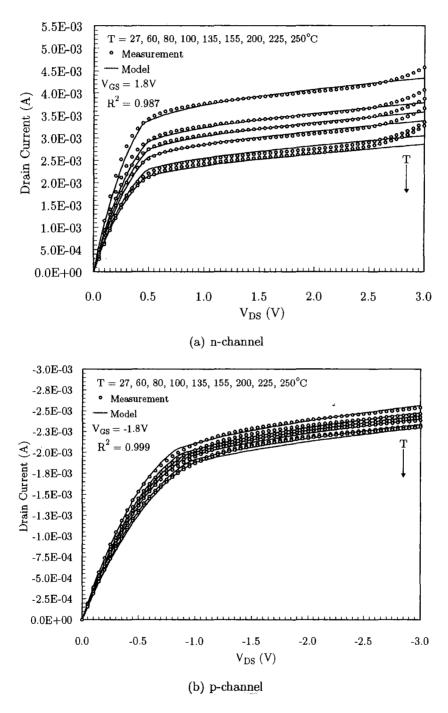

| 3.19 | $V_{GS}$ - $I_{DS}$ characteristic at various temperatures                       | 70 |

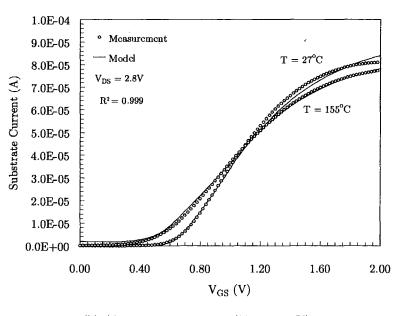

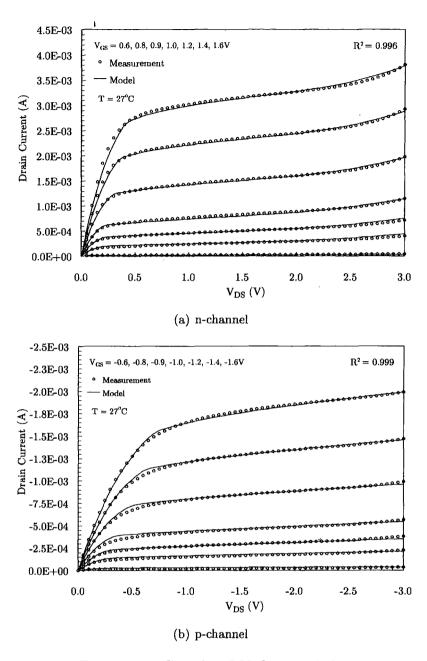

| 3.20 | $V_{DS}$ - $I_{DS}$ characteristic at various temperatures                       | 71 |

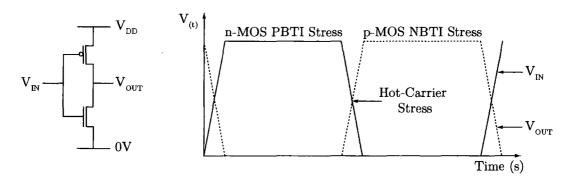

| 4.1  | Stress time window                                                               | 75 |

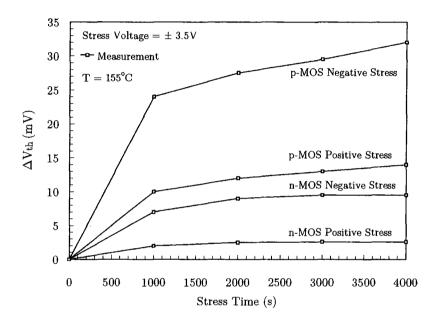

| 4.2  | NBTI n-channel and p-channel degradation comparison                              | 76 |

| 4.3  | Interface trap creation                                                          | 77 |

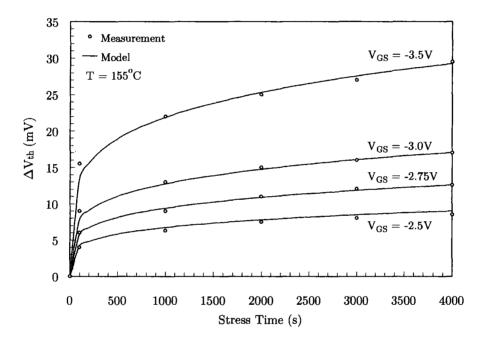

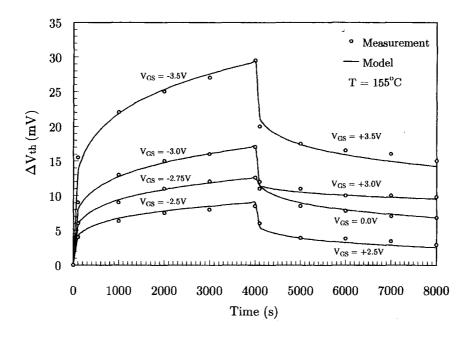

| 4.4  | Threshold voltage shift under DC stress                                          | 80 |

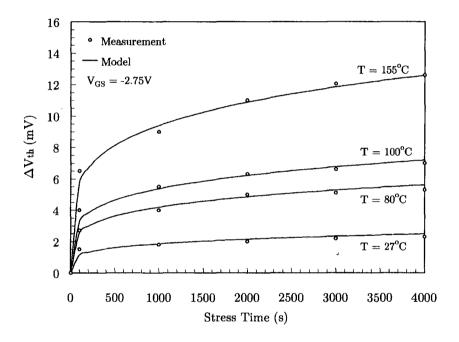

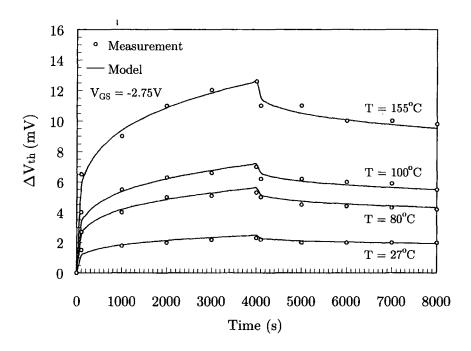

| 4.5  | NBTI stress as a function of temperature                                         | 81 |

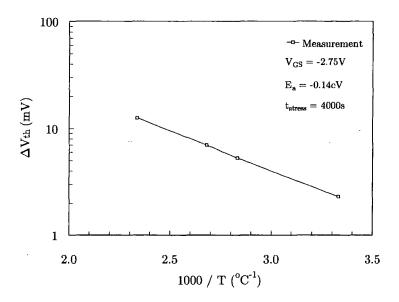

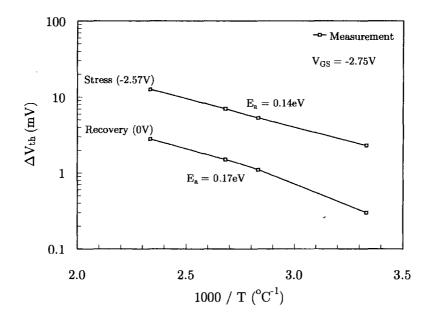

| 4.6  | Arrhenius plot showing temperature dependence of $\triangle V_{th}$              | 82 |

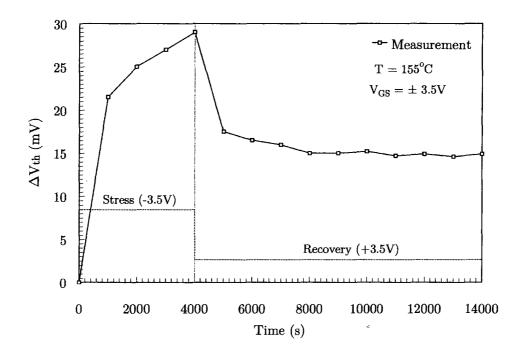

| 4.7  | Threshold voltage recovery after NBTI stress                                     | 83 |

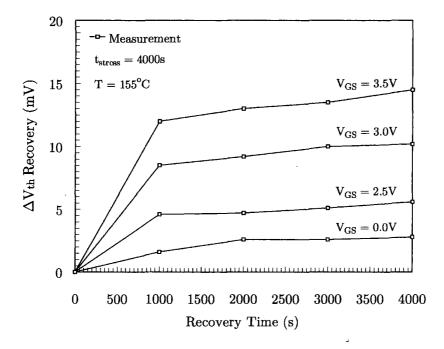

| 4.8  | Threshold voltage recovery as a function of gate voltage                         | 84 |

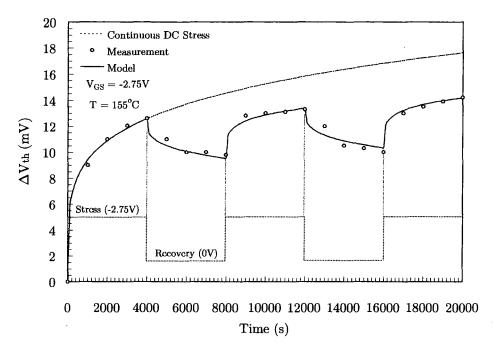

| 4.9  | Comparison between NBTI model and experimental results 8      |

|------|---------------------------------------------------------------|

| 4.10 | Comparison between stress and recovery activation energies 80 |

| 4.11 | Temperature dependence of NBTI stress and recovery 8          |

| 4.12 | NBTI lock-in illustration                                     |

| 4.13 | NBTI lock-in temperature dependence                           |

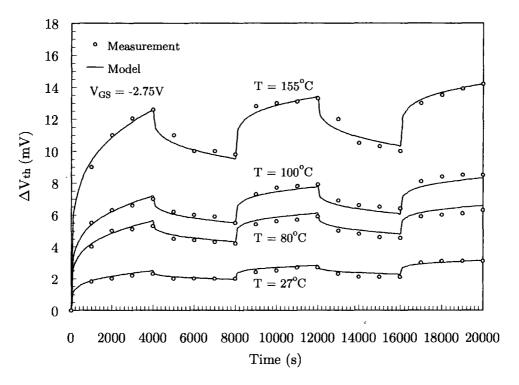

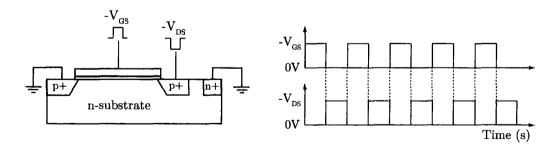

| 4.14 | Dynamic stress configuration                                  |

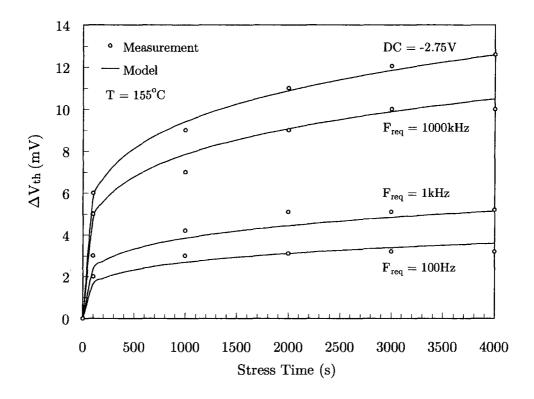

| 4.15 | NBTI frequency dependence                                     |

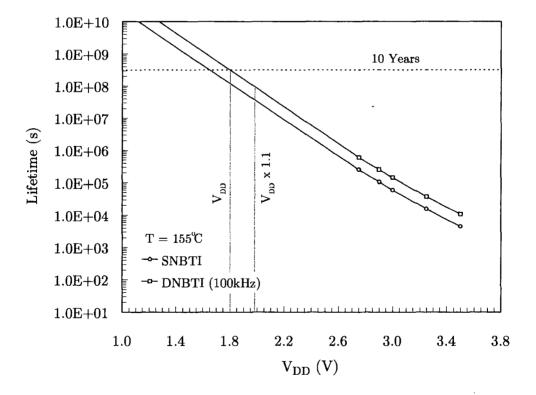

| 4.16 | NBTI lifetime comparison                                      |

| 5.1  | Illustration of gate-to-drain overlap region                  |

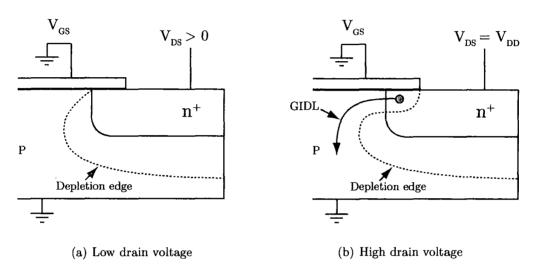

| 5.2  | GIDL mechanism (n-channel)                                    |

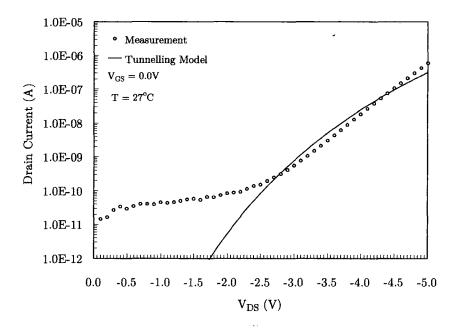

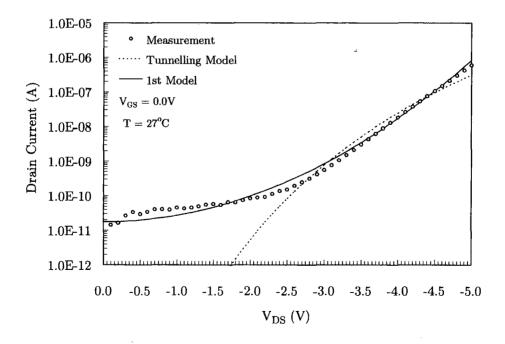

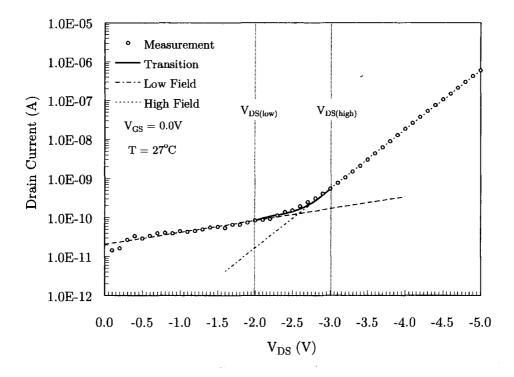

| 5.3  | GIDL characteristic (p-channel)                               |

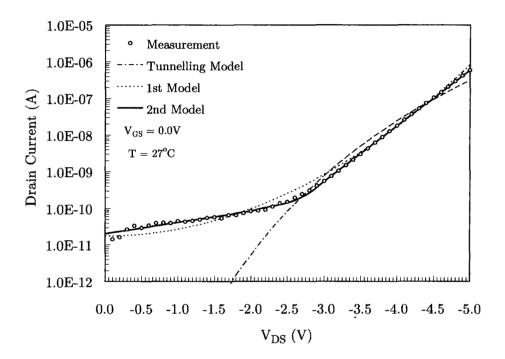

| 5.4  | Comparison of first GIDL model with measured data             |

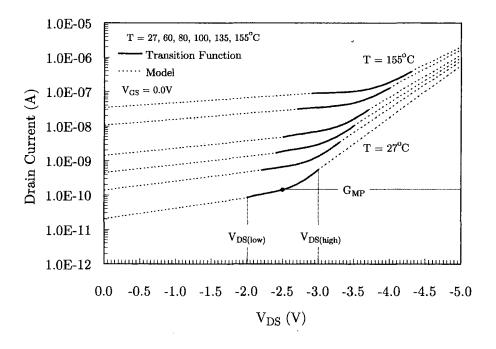

| 5.5  | Illustration of GIDL transition function                      |

| 5.6  | Comparison of GIDL model with 1st design                      |

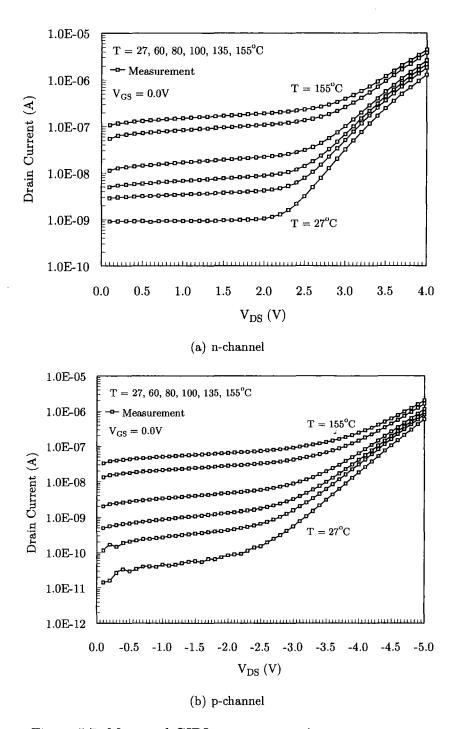

| 5.7  | Measured GIDL current at various temperatures                 |

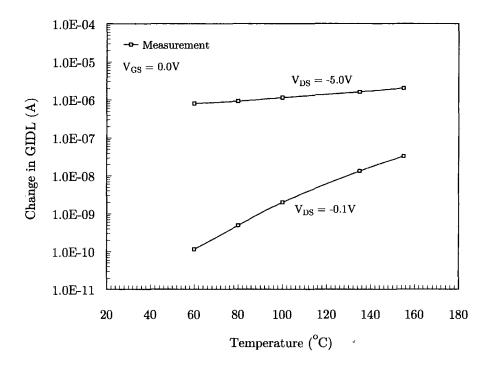

| 5.8  | Change in GIDL in different operating regions (p-channel) 104 |

| 5.9  | Change transition points with temperature (p-channel) 106     |

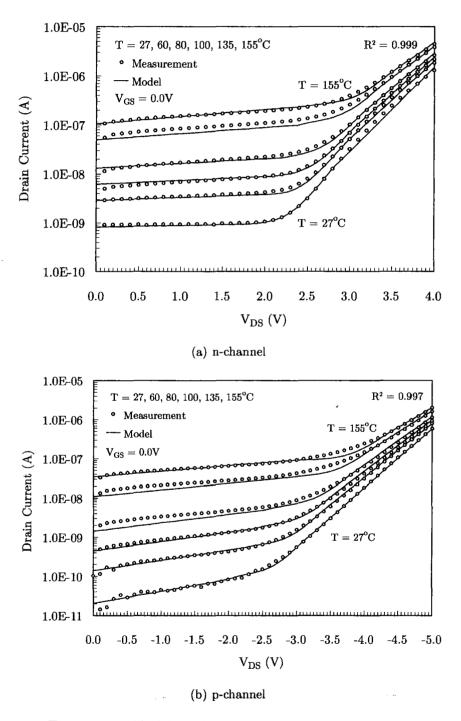

| 5.10 | Model predictions at various temperatures                     |

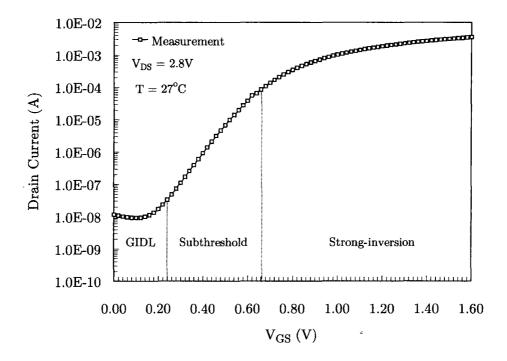

| 5.11 | Illustration of device operating regions (n-channel)          |

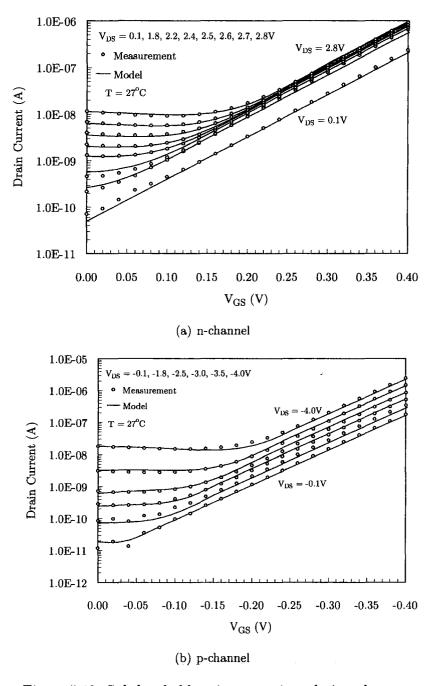

| 5.12 | Subthreshold region at various drain voltages                   |

|------|-----------------------------------------------------------------|

| 5.13 | Complete I-V characteristic                                     |

| 6.1  | Illustration of hot-carrier mechanism (n-channel)               |

| 6.2  | Illustration of silicon-oxide interface energy bands            |

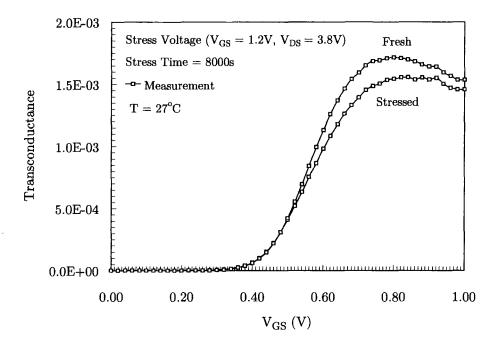

| 6.3  | Transconductance degradation after hot-carrier stress           |

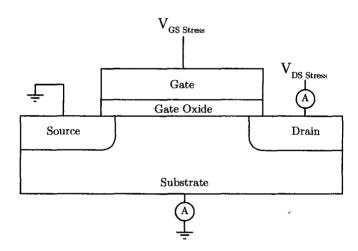

| 6.4  | Hot-carrier stress configuration                                |

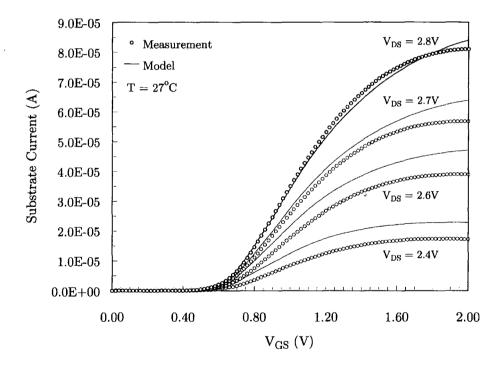

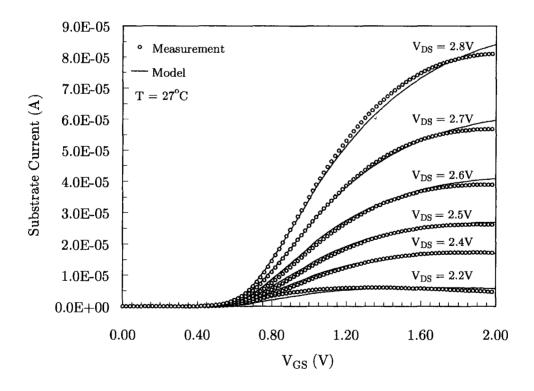

| 6.5  | Inaccuracy in substrate current prediction (n-channel)          |

| 6.6  | Substrate current versus gate voltage (n-channel)               |

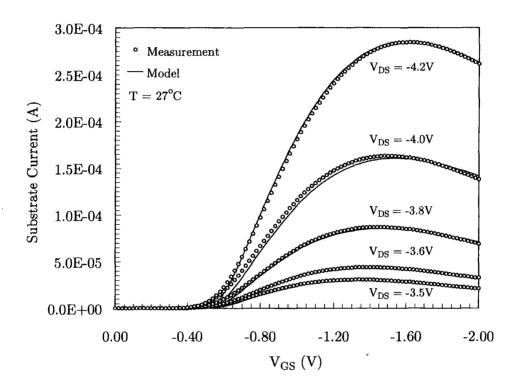

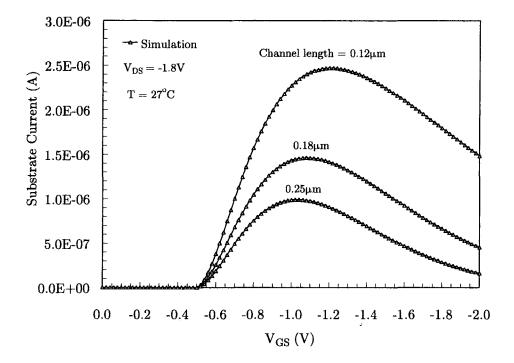

| 6.7  | Substrate current versus gate voltage (p-channel)               |

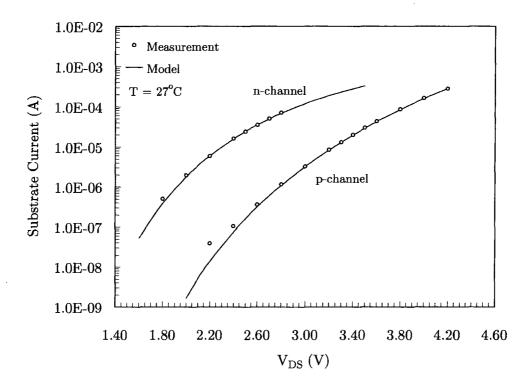

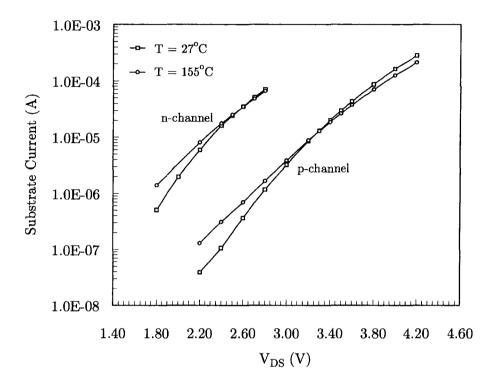

| 6.8  | Comparison between n- and p-channel substrate currents          |

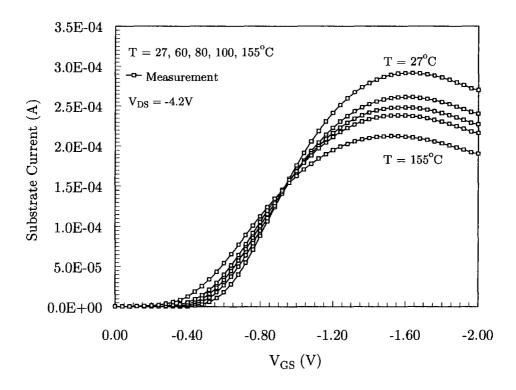

| 6.9  | Substrate current at various temperatures (high $V_{DS}$ )      |

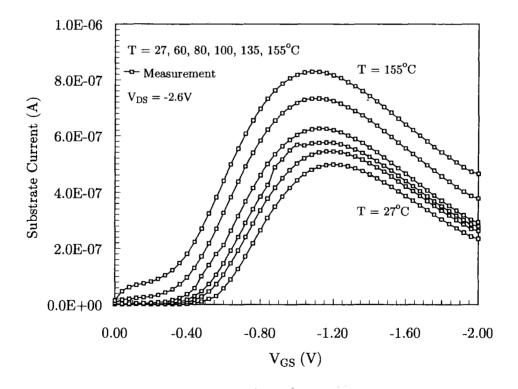

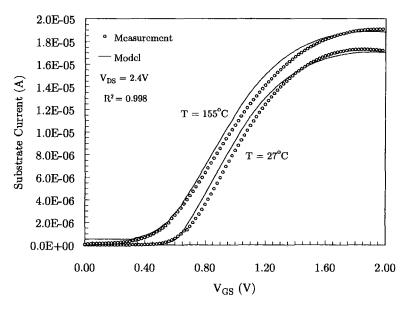

| 6.10 | Substrate current at various temperatures (low $V_{DS}$ ) 125   |

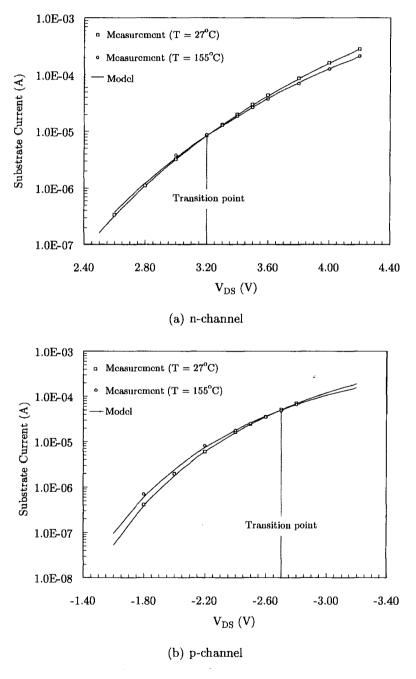

| 6.11 | Substrate current crossover point                               |

| 6.12 | Model predictions for substrate current transition              |

| 6.13 | Substrate current characteristic above and below transition 129 |

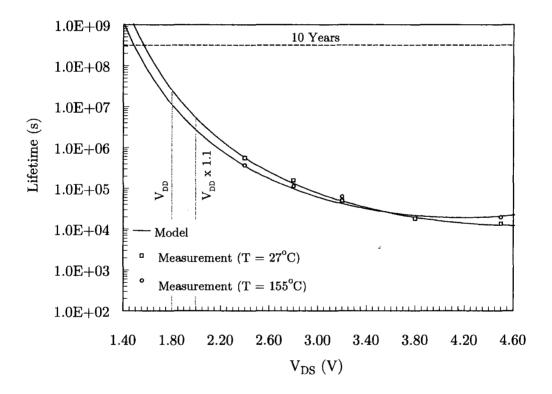

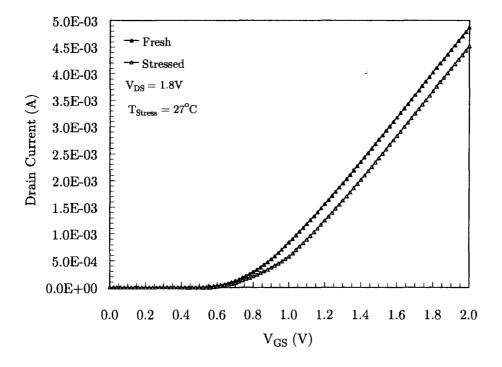

| 3.14 | Hot-carrier lifetime (n-channel)                                |

| 6.15 | Complete I-V characteristic                                     |

| 7.1  | Integrated reliability methodology                              |

| 7.2  | Layers of MathCAD development                                   |

| 7.3         | Embedded MathCAD file                                              |

|-------------|--------------------------------------------------------------------|

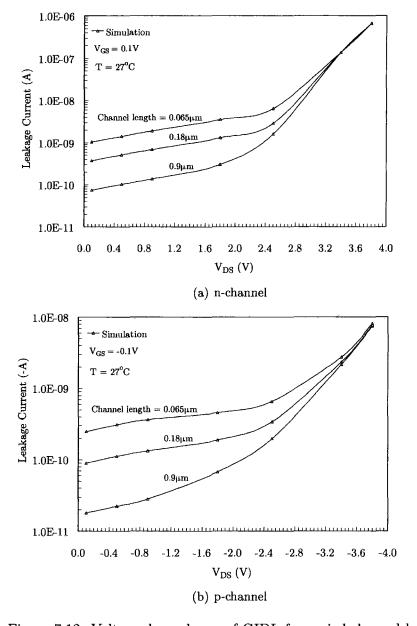

| 7.4         | Leakage current as a function of channel length (n-channel) 142    |

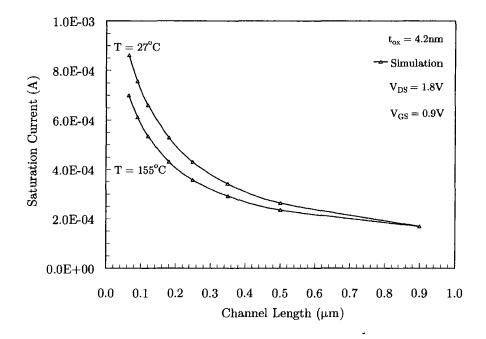

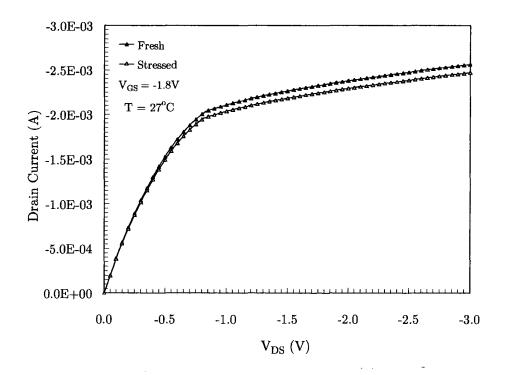

| 7.5         | Saturation current as a function of channel length                 |

| 7.6         | Influence of temperature on scaling channel length (n-channel) 144 |

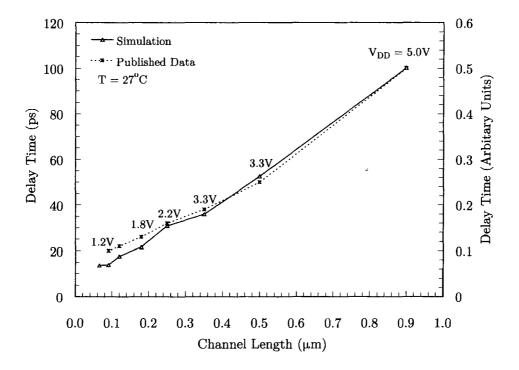

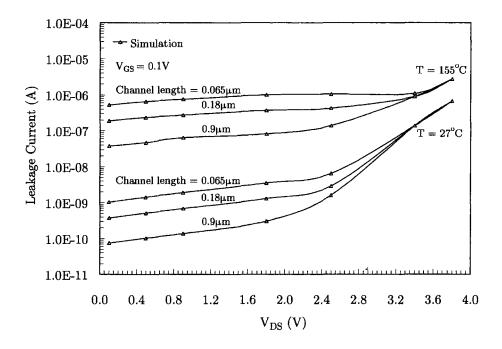

| 7.7         | Delay time as a function of channel length                         |

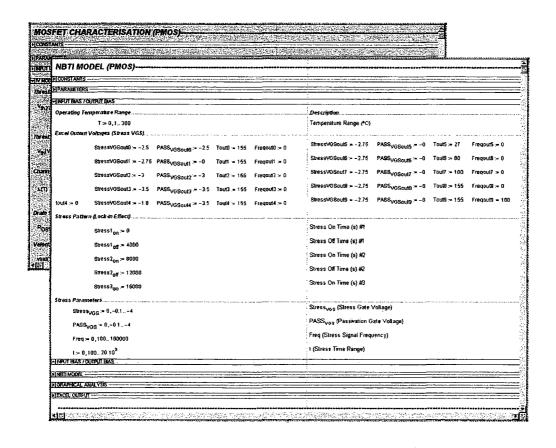

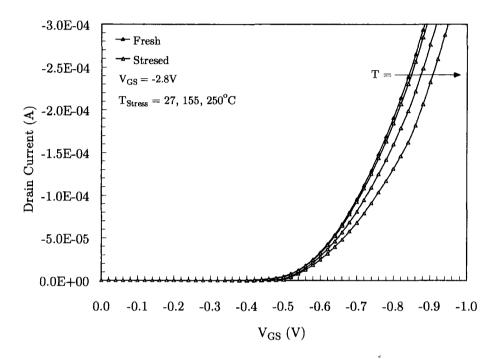

| 7.8         | Snapshot of NBTI model in simulation tool                          |

| 7.9         | NBTI stress simulation                                             |

| 7.10        | NBTI stress simulation at varied temperatures                      |

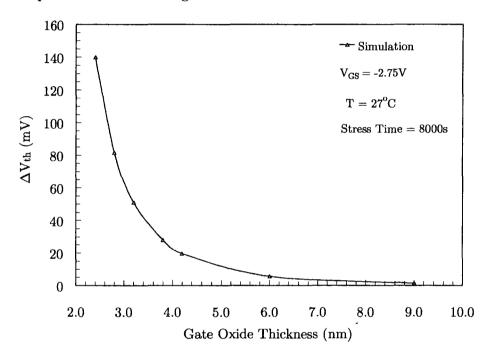

| 7.11        | NBTI stress simulation as a function of oxide thickness            |

| 7.12        | Voltage dependency of GIDL for varied channel lengths              |

| 7.13        | Temperature dependency of GIDL at varied channel lengths 152       |

| 7.14        | Snapshot of HCE model in simulation tool                           |

| 7.15        | Hot-carrier stress simulation                                      |

| 7.16        | Substrate current as a function of channel length (p-channel) 155  |

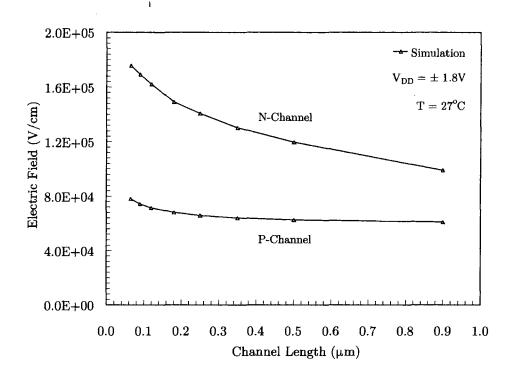

| 7.17        | Maximum electric field as a function of channel length             |

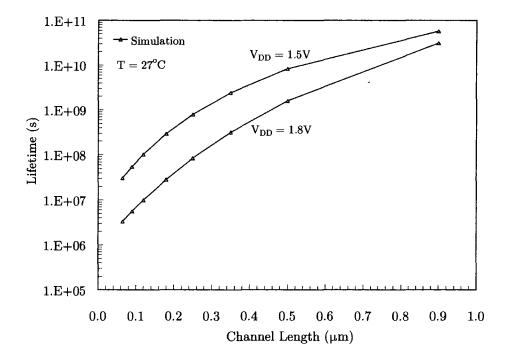

| 7.18        | Device lifetime as a function of channel length (n-channel) 156    |

| 8.1         | Development of methodology for layout diagnostics                  |

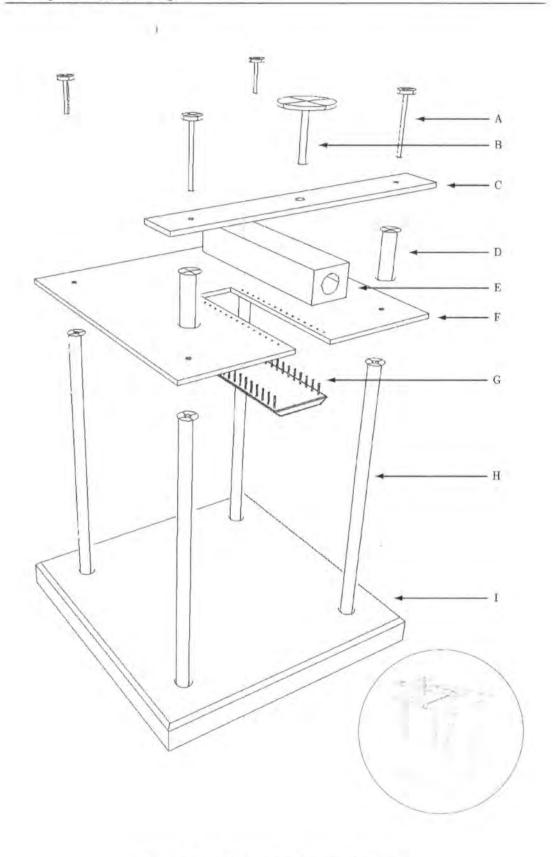

| <b>A</b> .1 | Schematic diagram of test rig                                      |

# List of Tables

| 2.1 | MOSFET road map                                       | 25  |

|-----|-------------------------------------------------------|-----|

| 2.2 | Comparison table of different semiconductor materials | 34  |

| 3.1 | Extracted model parameters                            | 57  |

| 5.1 | Extracted GIDL model parameters                       | 108 |

| 7.1 | Scaling parameters                                    | 146 |

# Glossary

AGREE Advisory Group on the Reliability of Electronic Equipment

AlN Aluminium Nitride

**BSIM** Berkeley Short-channel IGFET Model

CAD Computer Aided Design

CALCE Computer Aided Life Cycle Engineering Centre

CLM Channel Length Modulation

Complimentary Metal-Oxide Semiconductor **CMOS**

COTS Commercial Off The Shelf

DIBL Drain Induced Barrier Lowering

DRAM Dynamic Random Access Memory

**EEPROM** Erasable Programmable Read Only Memory

GaAs Gallium Arsenide

GaN Gallium Nitride

GIDL Gate Induced Leakage Currents

**GPIB** General Purpose Interface Bus

HCE **Hot-Carrier Effects**

IC Integrated Circuit

IRM Integrated Reliability Methodology

I-V Current-Voltage

JEDEC Joint Electron Device Engineering Council

LDD Lightly Doped Drain

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MTTF Mean Time To Failure

NBTI Negative Bias Temperature Instability

PBTI Positive Bias Temperature Instability

PoF Physics of Failure

R-D Reaction-Diffusion

SiC Silicon Carbide

SOI Silicon-on-insulator

SOS Silicon on Sapphire

TSMC<sup>™</sup> Taiwan Semiconductor Manufacturing Company

ULSI Ultra Large Scale Integration

ZTC Zero-Temperature Coefficient

# Chapter 1

# Introduction

THE DESIGN OF accurate reliability methodologies must be seen as a vital element for the future evolution of Complimentary Metal-Oxide Semiconductor (CMOS) technologies. The ever continued scaling of CMOS technologies, has made it increasingly difficult to ensure device reliability. Added to this the influence of an external factor such as temperature, the process of predicting the lifetime of a product is made even more complex. Hence, development of a novel reliability methodology is needed to encompass external conditions such as temperature but to also prevent device modelling falling behind the fast changes in technology.

As we enter the age of the nanometer scale, it is essential any reliability or performance issues brought about by reduced dimensions are addressed. Deep sub-micron dimensions have introduced a set of new reliability challenges which are forcing a dramatic change in the approaches used to assure integrated circuit reliability in the product design flow. High speed and low power are not the only targets that designers have to aim for. The designer has to able to simulate how several factors may change the behaviour of known failure mechanisms or even bring about the introduction of a new failure mechanism.

#### 1. Introduction

Determining the lifetime of a particular device is dependent on numerous considerations. Device geometry, architecture, materials, and environmental and operational stresses are all factors which play a key role in reliability assessment. The environmental stresses include temperature, relative humidity, pressure, static charge, and their cycles, gradients, and transients. Accelerating operational stresses include voltage and current. While high levels of these stresses will overstress the device to catastrophic failure, smaller values of the same stresses may result in a performance degradation and not necessarily hard breakdown. Hence device modelling is not strictly confined to predicting when a device will fail, but also analysing the effects of any performance degradation over time.

In this thesis we consider how deep sub-micron devices degrade for a varied set of operating and environmental conditions and then develop new models to simulate such behaviour. Using a physics of failure approach, novel models are designed for well known failure mechanisms and also for mechanisms only very recently emerging. This provides the foundation for the development of a new integrated reliability tool. Combining each failure model into a single tool will allow analysis of how any technology changes and/or elevated temperatures affect the performance and lifetime of devices. The author believes the provision of this information is vital to recognise trends in the failure mode distributions for both present day and future technologies. At present we are entering a time when physical limitations may prevent any further scaling. Variations in channel dimensions and oxide thickness to take two examples are undoubtedly going to cause variance to the physical operation of associated failure mechanisms. Hence, the development of a integrated reliability tool would provide invaluable information to how certain failure mechanisms vary after such changes. Furthermore, the tool will provide the capability to predict if the present rate of scaling can continue.

### 1.1 Objectives and Focus of the Research

The aim of the research is to address the actual impact of temperature and device technology on the failure mechanisms utilising a physics of failure approach. This is to be achieved through the development of an integrated reliability tool and failure models. To accomplish this goal, the following tasks were set.

- To understand how temperature affects the operation of a CMOS device and the development of a new temperature dependent MOSFET model. This will provide current-voltage characteristics and individual parameter data.

- Determine the prominent failure mechanisms that occur in deep sub-micron devices. In particular knowledge about each physical mechanism and its temperature dependence.

- Concentrated research on gate oxide failure mechanisms: how has the reduction in gate oxide thickness affected device performance and reliability.

- Identify any new failure mechanisms such as Negative Bias Temperature Instability (NBTI): Investigate the physical mechanism behind this new failure and develop novel models.

- Studies into how leakage degradation such as Gate Induced Leakage Currents

(GIDL) are effected by temperature in modern devices.

- Hot-Carrier Stress: In particular investigate the temperature dependence of hot-carrier damage in deep sub-micron devices.

- Development and design of failure/degradation models using a Physics of Failure (PoF) approach.

- Integrated Reliability Methodology (IRM): how best to integrate the PoF models in a novel way to provide accurate and efficient device analysis.

### 1.2 Organisation of Thesis

A critical review of reliability in CMOS technology given in chapter 2. This covers the relevant background to the subject from reliability fundamentals such as the bathtub curve through to a review of alternative technologies. In addition the prominent failure mechanisms and the main effects of temperature are discussed in this chapter. Following this, chapter 3 describes the development of a new temperature dependent MOSFET model. The mathematical foundation behind the model is presented along with a set of benchmark simulation and experimental test results. This chapter serves to update present MOSFET current-voltage modelling but also as a foundation for later chapters.

Chapters 4-6 describe the research into the three failure mechanisms covered in this thesis. Chapter 4 investigates a recent degradation phenomenon, Negative Bias Temperature Instability. In chapter 5 a new Gate Induced Drain Leakage model is presented. Finally chapter 6 covers the present understanding of hot-carrier effects including some new results on its temperature dependence. In each of these chapters a new failure model is developed based on experimental data.

Chapter 7 combines the research and model developments in the previous chapters. The current-voltage model and each failure model are integrated into a novel reliability tool and simulation findings presented.

Future work and possible tool developments such as layout diagnostics are included in chapter 8 along with conclusions of what has been accomplished. The appendices include further details of the experimental setup in Appendix A, and an example of parameter optimisation in Appendix B.

# Chapter 2

# Reliability in CMOS Technology:

# A Review

### 2.1 Introduction

A CRITICAL REVIEW of reliability in CMOS technology and the impact of higher temperatures on devices is given in this chapter. The reliability of a product is defined as its ability to fulfill its intended function, under stated conditions for a stated period of time. Reliability associated failures in this case are caused by a failure mechanism, that is induced generally by internal and external stresses. How these mechanisms are monitored, understood and modeled has seen considerable research in the past. The following provides a review of this work looking at different reliability techniques that have previously aimed to predict device lifetimes. A critical review of past and present failure mechanisms is presented. Furthermore the influence of temperature and the growing demand for devices applicable for higher temperatures is reviewed.

### 2.2 CMOS Reliability Review

As early as the 1940s product and system reliability was identified as a major engineering discipline. However engineers have always worked towards reliable design. For example, in 1860, A. Wohler [1] presented some of the earliest fatigue failure information, which occurred on stagecoach and railroad axles. The applied load versus cycles to failure diagrams, which resulted from Wohler's work, were used to identify the load condition (called a fatigue limit) below which 'no failures' should be expected.

Although both technology and reliability have moved on significantly, the fundamental endeavour to design products to not fail still remains. The establishment of the Ad Hoc group on Reliability of Electronic Equipment in 1950 and subsequent Advisory Group on the Reliability of Electronic Equipment (AGREE) began reliability engineering in the electronics field. It was not until 1956 though that the first reliability methodology was conceived with the publication of the RCA release TR-1100, titled "Reliability Stress Analysis for Electronic Equipment," which presented models for computing rates of component failures [2]. It was this document that first applied the term reliability to integrated circuit manufacturing. It defined reliability as the lifetime during which a component is expected to perform its desired function. This definition can be represented graphically with the now well known mortality (bathtub) curve shown on the next page in figure 2.1. The first stage shows a high failure rate. This period is called the "early period," "burn-in period," "break-in period," or "infant mortality period." During this period, failures occur which are due to design or manufacturing weaknesses [3]. In other words, failure is due to weak or substandard components in which the probability of failure depends on how long the component has been operating. The next region is known as its useful life since the components can be used to the greatest advantage. Failures in this stage are mainly

Figure 2.1: Bathtub curve

due to a low level of residual defects or electrical overstress/electrostatic discharge events. The failures are known as "chance," "random", "catastrophic failures" since they occur randomly and unpredictably. Failures are inevitably going to rise though as time goes on and this is what we see from figure 2.1. The final stage is the wear-out period where degradation failures begin to appear as a consequence of ageing or wear when the components are nearing their "rated life." In general, reliability is concerned with all three periods. In a lot of cases though, early life can be made as short as desired (even eliminated) by proper design, fabrication, and assembly, or by deliberate burn-in periods. Also if design and application are correct, the wear-out period should never be reached within operating life. This is because components are replaced as they fail during useful life, and each component is replaced (even if it has not failed) no later than at the end of its useful life.

The bathtub curve is ideal in illustrating reliability over the operating lifetime of a component. It is important also to consider how reliability changes throughout the whole product development cycle. Figure 2.2 illustrates this process from initial concept to production. Low reliability of the initial prototype could be a flaw in de-

sign, an unknown manufacturing process problem, or the cumulative effect of several environmental stresses. As these factors are determined and overcome throughout the development process, the reliability starts to improve. With the transition to the manufacturing production line though there is usually a fall in reliability. In many cases this is because the manufacturing production line environment can be very different from the environments of the research and development line. Additionally, at this point in the product life cycle the human involvement factor is usually at its most drastic transition, causing variances in the fabrication process.

Figure 2.2: Product development cycle

From the manufacturing perspective it is very important to shorten this development time as much as possible. Traditionally, reliability assurance has relied mainly on failure detection at the end of the product development process. Due to the reliability analysis taking place towards the end of the development cycle any re-design work adds significantly to design time and cost. Ideally a manufacturer can use methods to allow reliability growth to occur in conjunction with product development. This would allow the manufacturer to gain a quicker time-to-market time of a reliable product that will not require costly warranty repair or replacement.

To quantify reliability we must take the concept of reliability as a probability distribution. One of the most common and simplest ways is to use the cumulative failure function F(t). It is defined as the cumulative probability that a component fails at time t, or a fraction of the total number of components that have failed. It originates from the probability density function f(t). This is a plot of the frequency at which components fail as a function of time divided by the whole population.

Figure 2.3: Reliability distribution

The probability density function can take many forms but one of the most common and simplest is the normal (Gaussian) curve. Figure 2.3 shows the normal distribution probability density function f(t). This describes the probability of a failure occurring between two different points in time. However, in terms of quantifying component reliability, determining the probability of failure occurring before or after a certain time would be of greater use. This is where the cumulative failure function comes in. It measures the area under the failure probability curve, up to a given time, in this case, point a. This returns the probability of a failure occurring before

point a. Given that the area under the probability density function is always equal to 1, subtracting the cumulative density function from 1 would result in the probability of a failure occurring after a given time. This is the widely used reliability function R(t) and is defined as the fraction of the surviving good parts at any time.

$$R(t) = 1 - F(t) (2.1)$$

The cumulative failure function F(t) is then found by taking the integral of the probability density function f(t) between zero and time a.

$$F(t) = \int_0^a f(t)dt \tag{2.2}$$

Therefore the reliability function R(t) can be expressed as:

$$R(t) = 1 - \int_0^a f(t)dt$$

(2.3)

$$R(t) = \int_{a}^{\infty} f(t)dt \tag{2.4}$$

From this follows the failure rate which is also known as the hazard rate function. The failure rate is the rate of change of the cumulative failure probability divided by the probability that the unit will not already be failed at time t. Thus it gives us the instantaneous failure frequency based on accumulated age and is defined as:

$$\lambda(t) = \frac{f(t)}{R(t)} \tag{2.5}$$

It is simply the probability density failure function divided by the reliability function, and has the units of failure per unit time among surviving parts, e.g. two failures per month. There is a clear and important distinction though to be made between this and the probability failure function. The probability failure function f(t) is the unconditional probability that the component will fail between to time a and time b.

The instantaneous failule rate  $\lambda(t)$  is the conditional probability that the component will fail in the same time interval, given it has reached age T without failure. By analogy, the probability that a brand new component will fail in its fifteenth and sixteenth year of use is very small. However the probability of the same component failing in that same period, provided the component has lasted fifteen years is much greater. Another function that is very useful when trying to quantify component reliability is the Mean Time To Failure (MTTF). This can again be derived from the probability density function f(t) and is the weighted average of all time values from zero to infinity, weighted according to the density. Hence the mean time to first failure  $\mu$  is expressed as:

$$MTTF = \mu = \frac{\int_0^\infty t \ f(t)dt}{\int_0^\infty f(t)dt}$$

(2.6)

Given that the denominator will normally be 1, because the component has a cumulative probability of 1 of failing some time from zero to infinity, the mean time to fail is usually be expressed as

$$MTTF = \mu = \int_0^\infty t \ f(t)dt \tag{2.7}$$

For simplicity up to now I have only dealt with the normal probability distribution. The probability distribution curve can take many forms though that can resolve the above functions such as the MTTF. The common distributions including the normal distribution are the lognormal distribution, the Weibull distribution, and the exponential distribution. From figure 2.3 we can see how the normal distributions are appropriate when there is a strong tendency for the variable to take a central value, and positive or negative deviations from this central value are equally likely. Alternatively where components have a constant failure rate, it has been very common to use the exponential distribution.

The exponential distribution is described mathematically as:

$$f(t) = \lambda \ e^{-\lambda t} \tag{2.8}$$

where  $\lambda$  is the failure rate. The mean time to failure  $\mu$ , and the reliability R(t) of this distribution is expressed as:

$$MTTF = \mu = \frac{1}{\lambda} \tag{2.9}$$

$$R(t) = e^{-\lambda t} \tag{2.10}$$

As an example consider a batch of 1000 devices, with each functioning device having a probability of 0.1 of failing on any given day, regardless of how many days it has already been functioning (constant failure rate). We would expect 100 devices to fail on the first day leaving 900 functioning devices. On the second day we would expect to lose 0.1 of our remaining devices, thus leaving us with 810 functioning devices. Given a constant failure rate the decrease in functioning components with respect to time is exponential. It is however important to evaluate whether the devices really do have a constant failure rate. This is because this form of distribution assumes the probability of failure for a functioning device at any given time is independent of how long it has already been functioning. Therefore it does not consider the 'wear-out' stage. However in general, components are replaced as they fail during useful life, and each component is replaced no later than at the end of its useful life.

In this section I have only briefly covered what I feel are two of the most frequently used distributions in reliability engineering. There is scope for much more detailed analysis and comparisons. Kapur and Lamberson [4] have written a book titled "Reliability in Engineering Design" which has an excellent review and detailed comparisons of all the distributions.

A vital and common element to all failure distributions and failure analysis is the collation of reliability data from real-life measurements. The most direct way to obtain the data would involve testing a large number of samples in normal use conditions and monitor their performance against the failure criteria over time. Given that most applications have lifetimes of several years this approach is clearly not practical. One method which has been widely used in the electronic industry has been accelerated life testing. This employs a variety of high stress test methods that shorten the life of a product or accelerate the degradation of the products performance. Thereafter the accelerated lifetime values for different stress levels can be used to extrapolate the lifetime to normal operating conditions. Using this method efficiently obtains performance data that yields reasonable estimates of the life of a product or performance under normal conditions. Common stresses used to accelerate the failure include temperature, voltage, humidity and vibration.

For a long time, mathematically determining how different stresses affect the lifetime has been fulfilled by the use of the Arrhenius equation. This relates how increased temperature accelerates the age of a product as compared to its normal operating temperature and is given by:

$$A_f = A e^{E_a/k_b(1/T_u - 1/T_s)} (2.11)$$

where  $A_f$  is the acceleration factor, A a proportional multiplier,  $E_a$  is the activation energy of the chemical reaction or physical process (eV),  $k_b$  is Boltzmann's constant<sup>1</sup>,  $T_u$  is the steady state use temperature (Kelvin) and  $T_s$  is the stress temperature. The activation energy is derived from empirical data gathered during accelerated testing and it represents the effect that the applied stress has on the product under test.

$<sup>^{1}</sup>$ Boltzmann's constant = 8.617 x  $^{10^{-5}}$  eV/K

The concept of using the century old Arrhenius relationship to model electronic component failure rates was first formally introduced in the RADC <sup>2</sup> release TR-1100, titled "Reliability Stress Analysis for Electronic Equipment," [2]. From this the first reliability prediction handbook for electronics, MIL-HDBK-217A presented data to confirm that the Arrhenius relationship can be applied to the thermal ageing processes of semiconductor components. An important point to highlight is that the use of Arrhenius is only valid under the assumption that the dominant component failure mechanisms depend on steady state temperature. This assumption eliminates any failure mechanism that may have a temperature threshold below which the mechanism is not active, plus those which have a negative temperature dependence. Despite this, reliability requirements based on constant failure rates lead developers to continue to use this approach as a basis. It is the authors belief that reliability could be quantified much more accurately with not only the use of mathematical approaches such as Arrhenius, but also with a realisation of the physical cause of a failure. This is why this work follows an approach to fundamentally understand the physical mechanism behind the failure before any models and predictions are made.

### 2.3 Physics of Failure

Even with the MIL standard being updated by a number of companies and Universities such as Boeing and the Computer Aided Life Cycle Engineering Centre (CALCE) at the University of Maryland, rapid improvements and increased complexity of microelectronic devices pushed the application of MIL-HDBK-217B beyond reason. The last version of the document was published in 1991. At this time many companies had discarded traditional methods of reliability prediction that were included in this publication. In its place, they started to use a new reliability assessment technique, based on the root cause of a failure, called physics of failure.

<sup>&</sup>lt;sup>2</sup>Rome Air Development Centre

Figure 2.4: Physics of failure process

The underlying process behind the physics of failure approach is shown in figure 2.4. Physics of failure provides a method to understand the interaction, or physics, between a product's materials within specific use environments by identifying the underlying physical causes. This allows predictions to be made on how the failure mode will be affected by specific change to a device or technology. It is based on the fact that failure mechanisms are governed by fundamental mechanical, electrical, thermal, and chemical processes. Hence to exploit its potential, a firm understanding of the physical failure mechanisms present in the device is necessary.

The process begins with the preliminary design, looking at the device geometry, architecture and materials. Failure mainly results from the application of an overstress, or by a lower stress level over a period of time. The next step is to define the applied life-cycle loads. Once the inputs have been established the process then moves to the main element of the physics of failure process: to determine the sources of reliability risks under life-cycle loads by identifying the potential weak-links and dominant failure mechanisms. This step is best described in two stages.

- Stress Analysis to decide how the stress factors affect the device. This is to identify which failures may occur, where they occur, their cause (failure mode) and the consequences of such a failure.

- Lifetime Prediction after identifying the likely failure mechanisms, the analysis involves the reliability prediction. Implementation of device models allows device degradation and lifetimes to be predicted. This allows not only the most dominant failure mechanism to be identified, but also to plot trends of the less likely failures. This will allow prediction of changes in failure distributions that would not be noticed in an approach that only identifies the most dominant failure mechanism.

In addition to establishing the failure modes of a device and the dominant mechanisms, a physics of failure approach can be used to ensure the device has adequate stress margins and that it meets the reliability targets. By understanding the root causes of the failure it also allows potential problems in technology changes, i.e. technology change to be identified and solved before they occur. However, the use of physics of failure is only one part of the complete process for predicting reliability. For complete reliability analysis the physics of failure or any other approach must fit into a reliability methodology or simulation tool.

# 2.4 Failure Methodologies

The traditional reliability prediction methods such as the MIL standards were based on analysis almost at the end of the design process. This meant that at this point in the product development cycle only minor design changes could be made. Also the tests often did not address the actual failure mechanisms occurring in the application environment. The stuck at fault test is one such example. Classically designers assumed they could model a circuit dependent on each node being stuck at one or zero. Banerjee et al [5] proposed that in a real life environment an MOS circuit can produce logic levels that cannot be classified as either a zero or one. Today this hypothesis has clearly been proven with the emergence of soft failures such as stress induced leakage currents that in some cases lead to a degradation but not necessarily complete circuit failure. Furthermore, some manufactures have previously used the same models for both temperature and voltage acceleration. It is unlikely that we can accept that in case of failure one activation energy can be used for all failures in acceleration factor calculations, knowing that different failure modes have different dependencies on temperature and voltage.

Shoucair [6] previously called for the development of new CAD tools to include a number of features that would be desirable for purposes of rendering high-temperature IC design more accurate, flexible, and realistic. It is the authors belief that the same call is now needed to advance the understanding again and provide a novel tool to include the most recently discovered failure mechanisms. This is something Fergerson and Shen [7] highlighted in their analysis of reliability methodologies during the last decade. Some good developments have been made, such as that of Li et al [8]. Li and his co-workers proposed the Failure Rate-Based SPICE (FaRBS) reliability simulation methodology. It combined modules of SPICE simulation with wear-out models and acceleration factor models to identify critical or failure prone

circuit block in a system. Both McClusky et al [9] in the form of Computer Aided Design of Microelectronic Packages II (CADMP-II) and Charpenal et al [10] in the form of FIDES developed similar tools. FIDES arose from a consortium of industry groups and was particularly interesting from the aspect it was designed to incorporate Commercial Off The Shelf (COTS) components into the reliability assessment. A number of simulation tools have been developed that concentrate on hot-carrier effects. Texas instruments developed HOTRON [11] as a proprietary simulator of hot-electron effects. The University of Southern California developed RELY [12] to simulate hot-electron effects and electromigration. Also hot-carrier simulation tools BERT<sup>3</sup> [13] and CAS<sup>4</sup> [14] were developed by the University of California, Berkeley.

Many of these tools have been developed for relatively large devices in comparison to today's technologies. Additionally at present there is not an accurate simulation tool that can take into account a range of temperatures and includes the most recently discovered failures mechanisms for deep sub-micron devices. In 2006 Li et al [15] stated that the advancement of device failure modelling had fallen behind the development of CMOS technology which has raised many new issues related to both circuit performance and reliability. Success in today's globally competitive environment requires the ability to repeatably examine and constantly improve manufacturing processing. Thus a time, and hence cost effective reliability test tool is required. For the future generation of devices, it is no longer practical to design the product and then measure and improve the reliability at the latter stages of development. A physical understanding of the failures to allow identification and prioritisation in the early stages of development is the key. The development of this idea continues in chapter 7, but it is clear to see that something new is needed to cope with the combination of elevated temperatures and any new failure mechanisms the dramatic changes in technology growth may have brought with it.

<sup>&</sup>lt;sup>3</sup>Berkeley Reliability Tool

<sup>&</sup>lt;sup>4</sup>Circuit Ageing Simulator

## 2.5 Failure Mechanisms

As well as providing the methodology for predicting reliability, if a physics of failure approach is to be harnessed it is critical that there is a fundamental understanding of the failure mechanisms themselves. The history of CMOS development has been dogged by three major causes of IC failures. These have been electromigration, gate oxide wear-out and hot-carrier effects.

## 2.5.1 Electromigration

Electromigration is the dominant mechanism in terms of interconnect failure and has been a major failure mechanism in discrete solid state devices since 1970. The first ICs were constructed with pure aluminium (Al) metal lines that were  $10\mu m$  in width or more. At the same time they were very thin, in the order of 3000A. This meant a high current density was being passed along a material with a low melting temperature, which implies fast diffusion at low temperature. This combination was a recipe for disaster and failed parts were soon returned from the field. Under inspection many failures were caused by very fine cracks in the metal resulting in open circuits. This structural damage was due to ion transport in metal lines. If the current density is high enough, the momentum exchange between conducting electrons and diffusing metal atoms can be significant, resulting in noticeable mass transport generating electromigration damage. The damage manifests itself in the movement of vacancies and interstitials. The vacancies coalesce into voids and interstitial become hillocks. The voids in turn, decrease the cross sectional area of the circuit metallisation and increase local resistance and current density at that point in the track. Conversely, hillocks can cause a short to the adjacent or overhead metallisation.

Modeling of electromigration was first significantly contributed to by a landmark paper by Black [16]. He proposed an empirical model for prediction of electromigration lifetime as a function of current density J, and metal line temperature in the following form:

$$t_{50} = \frac{A}{J^n} e^{\frac{E_a}{k_b T}} \tag{2.12}$$

Where  $t_{50}$  is the median time to failure, A is a material and process dependent constant,  $k_b$  Boltzmann's constant, T the absolute temperature, and  $E_a$  is the activation energy for failure. Traditionally, according to Blacks original work it was observed that electromigration failure followed a  $1/J^2$  inverse square law. After 1967 most subsequent experiments indicated a current exponent ranging from 2 to 3, usually 2 and although the mechanism was not clear, most experiments were consistent with Black's relationship [17]. There is an assumption though in Black's model, that the mechanism leading to electromigration induced failures under the accelerated lifetime test conditions are the same as those under device operating conditions.

At the time that Black developed his model, the physical solution to the electromigration problem was simple: make the tracks thicker. However as device miniaturisation demanded smaller and smaller interconnects, this became no longer a solution. Today tracks are often in the order of  $0.5\mu m$  thick, carrying a current of 1mA which can result in a current density of  $10^6 A/cm^2$ . The continued increase in current density over the past 40 years has meant new methods to counter the electromigration problems have needed to be devised. The first idea to make the metallisation more resistant to electromigration was to add a small amount (up to 4%) of copper to the aluminium. This solution bought some time but in the past five years there has again been the need to develop a better interconnect for two main reasons. Firstly, there is a resistance-capacitance delay in fine tracks. The use of narrower lines, not only increases the resistance, increasing the likelihood of electro-

migration but also the dapacitance between the lines increases, bringing down signal propagation. The second problem is the high cost of building a multilayer interconnect structure. The solution adopted by industry has been to turn to pure copper as the on-chip conductor material. Since copper has a much higher melting point (1083°C) than aluminium (660°C), diffusion should be much lower in copper than aluminium at the same device operation temperature [18]. Experiments by Tu [18], Lloyd [19], and Tao et al [20] on copper tracks found the electromigration lifetime increased. Tao et al [20] found that in both DC and pulsed-DC tests, the lifetimes of the pure copper interconnects were about one and two orders of magnitude longer than those of aluminium alloyed with copper. His work was also interesting in that it aimed to make the interlayer as thin as possible. Because there had been issues with adhesion of copper to the Si<sub>02</sub> dielectric layer [18], previous test structures had employed a interlayer metal with significant thickness (compared to the copper thickness) to improve adhesion. Tao's and his colleagues work cleverly used a seeding layer of 15nm Cobalt. Firstly, this solved the adhesion problem as cobalt adheres well to SiO<sub>2</sub>. Secondly with a reduction in interlayer thickness, its effect on the electromigration properties of copper interconnects was kept to a minimum.

Developments in the use of copper has helped to make its introduction easier. Some authors [19, 21] still see the processing problems of using copper to be an issue. Further downscaling and also technological advancements continue to require more reliable interconnects under conditions where metallisation is inherently less reliable. One example is the introduction of flip chip solder joints, which tend to become weak links in the system. Due to the unique geometry of the joints, current crowding at the contact interface causes increased current density and electromigration damage. This and a number of other reasons documented by Tu [18] mean electromigration in flip chip solder joints is now competing with on-chip metallisation as the major electromigration reliability problem in microelectronic devices.

Although this is a very brief history of its origins, problems and solutions, it is clear electromigration is always going to be an important reliability issue. The promise of developing future metallisation schemes that will eliminate the problem has so far not been solved [21]. Recent advances have shown that with careful design electromigration can at least be controlled such that advanced microcircuits can be designed with the required reliability. As a result it was felt it would be more beneficial for the time spent on this project to be aimed towards other more prominent failure mechanisms. Although electromigration for a long time has been seen as the major failure mechanism is CMOS devices, continued device scaling has brought about more pressing issues needing study including gate oxide failures and hot-carrier effects. This can also be seen as a reflection of the amount of current research and publications work in this area. The following section goes on to highlight such failures and why it is the authors belief they pose the greatest reliability problems for future technologies.

### 2.5.2 Gate Oxide Failures

In today's technology, transistor dimensions have been scaled dramatically and one of the most critical issues of this scaling has been the reduction of the gate oxide thickness [22]. Table 2.1 on the following page shows the road map of MOS-FET minimum feature size as predicted by the semiconductor industry, showing the prospect of less than 2nm dielectrics by the year 2014 for standard CMOS fabrication. As a result of the reduction in oxide thickness, oxide related failures have increased and many see these to be the limiting failure modes for future technologies [22, 23, 24, 25, 26]. With oxide thickness now being measured in atomic units, there is cause to be concerned and subsequently a major element of this research aims to investigate the failure modes that are currently a problem and which pose a limiting factor for further scaling.

| Parameters     | ı         | 1991 | 1994 | 1997 | 2001 | 2005 | 2007 | 2009  |

|----------------|-----------|------|------|------|------|------|------|-------|

| Channel length | $(\mu m)$ | 0.5  | 0.35 | 0.25 | 0.18 | 0.13 | 0.09 | 0.065 |

| $t_{ox}$       | (nm)      | 13.5 | 9.0  | 8.0  | 7.0  | 4.5  | 3.5  | 2.7   |

Table 2.1: MOSFET road map

For many years gate-oxide was more of a production problem than an intrinsic reliability problem. Most of the research conducted was concerned with extrinsic failures as the intrinsic quality of the oxide never posed a serious reliability threat under typical operating conditions [22]. However, over the past ten years as oxide thickness  $(t_{ox})$  has decreased, the intrinsic reliability limits have been approached and the study of gate-oxide breakdown has become no longer limited by extrinsic failures. The dominating factor to account for this was the change in feature size without proportional scaling of the power supply voltage. This resulted in a significant increase of the horizontal and vertical electrical fields in the channel of the device [27]. As a result new problems that posed an additional constraint on the acceptable supply voltage and or oxide thickness became evident for deep sub-micron devices [28, 29, 30].

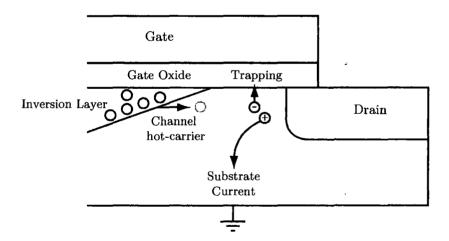

#### 2.5.2.1 Gate Induced Drain Leakage

Gate-induced leakage current is the name given to a tunnelling effect that occurs in the gate-to-drain overlap region of MOS devices in the OFF-state. It is caused by high transverse and lateral electric fields close to the drain region, generated by gate-source  $(V_{GS})$  and drain-source  $(V_{DS})$  voltages [31]. Huang et al [32] presented a paper in 1998 that recognised GIDL current as the major drain leakage current phenomenon in OFF-state MOSFET's. Before this Chan et al [28] reported GIDL as a new mechanism in 1987, showing the presence of leakage in the sub-half micron regime. A significant drain leakage was detected in thin gate oxide (15.5nm) MOSFET's at drain voltages much lower than the junction breakdown voltage.

Chan et al discussed device design considerations for minimising the GIDL current. In order to limit the leakage current to  $0.1 \text{pA}/\mu\text{m}$  of the channel width, it was proposed that the oxide field in the gate-to-drain overlap region should be limited to 1.9MV/cm. An important proposal by Chan et al was also to attribute the gate-induced leakage to the band-to-band tunnelling process. The belief that bandto-band tunnelling is the root cause of GIDL has continued to the present time. Endoh et al in 1990 [33], Guo et al in 1998 [34], Chen et al in 2001 [35], Touhami et al in 2002 [31], and Lopez et al in 2004 [36], all published notable papers stating that they saw band-to-band tunnelling as the major leakage mechanism responsible for GIDL. Endoh et al [33] was one of the first to propose a model to describe the band-to-band tunnelling effect and the leakage current assessment. It built upon Chan's et al [28] model that neglected the dependence of the transverse electric field on the drain doping profile and used a fixed value of band bending. Both Chen et al [35] and Touhami et al [31] developed models that considered doping concentration, vertical field, and lateral field with results showing good agreement with measurement data over a range of gate and drain biases. None of the above authors mentioned above have considered the influence of temperature on GIDL. It has not been until very recently that researchers have started to investigate this [37].

Limited data is available on how temperature affects GIDL current. It was proposed in a report by Slisher et al [38] that GIDL is independent of temperature whereas both Lopez et al [36] and Bouhdada et al [39] presented results showing an increase in GIDL at elevated temperatures. Lopez et al [36] hypothesised that the variation in leakage was due to the variation of the energy band gap of silicon with temperature. Bouhdada et al [39] had an alternative outlook. Again, results showed an increase in GIDL current with temperature but it was believed to be due to increased carrier generation. Several authors have studied how changes in device dimensions and process parameters have effected GIDL. Chung et al [40] found that GIDL is

enhanced by either decreasing oxide thickness, or by increasing drain voltage. In the same study GIDL was seen to be virtually independent of channel length because the tunnelling depends only on conditions in the immediate gate-to-drain overlap region. Bouhdada et al [41] found that at higher doping densities, the electric field increases in the overlap region, encouraging carrier generation, and hence causing an increase in GIDL current.

The review of published data has provided a valuable background to GIDL. I believe there is still a requirement for the development of a computationally efficient expression for GIDL ideal for use within a complete reliability tool. Currently there is only one GIDL model for use in a SPICE like simulator, which is a complicated expression in the BSIM4 model [42]. Our aim is to develop a simple, easy to use model, that would ideally have the capability to predict the effect of high temperatures on deep sub-micron devices. Chapter 5 details the development of one such model along with further detailed analysis of the physical mechanism behind GIDL.

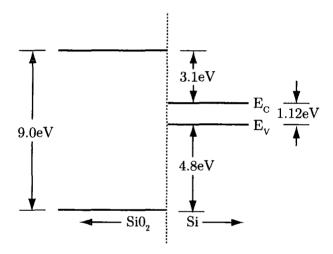

#### 2.5.2.2 Negative Bias Temperature Instability

The degradation phenomenon of Negative Bias Temperature Instability (NBTI) is characterised by an increase of threshold voltage and decrease of drive current, as a result of elevated temperatures and a high negative gate bias stress. Typical stress temperatures lie in the 100-250°C range with oxide electric fields typically below 6 MV/cm i.e fields below those that lead to hot-carrier degredation. Potentially parameter variations caused by NBTI can lead to transistor mismatch, timing issues and reduced switching speed. Given that the number of digital transistors approach millions of devices in modern products, such NBTI degradation characteristics have today become a critical issue for circuit designers.

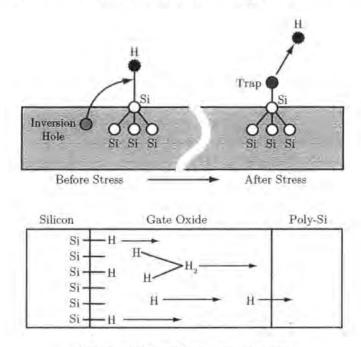

NBTI has been known since the very early days of MOS device development, having been observed as early as 1967 [43]. Deal [44] named it Instability Number VI. Goetzberger [45] and his co-workers at Bell laboratories were one of the first groups to investigate NBTI degradation. They stressed 100 nm oxides at 300°C and found an increased interface trap creation for negative gate voltage stress compared to positive stress. The generation of interface traps under negative gate voltage stress was discovered to have a time dependence of  $t^{0.25}$ . Their investigations also found a higher trap density for p-channel devices compared to n-channel devices. Nevertheless, NBTI effects remained marginal for many years, especially when compared to mechanisms like hot-carrier effects [46].

NBTI effects have become a critical reliability issue for modern deep sub-micron devices in recent times for three main reasons. Firstly slower scaling of operating voltages for both digital and analog circuits compared to more aggressive oxide thickness scaling has gradually increased the effective field across the oxide. Secondly thinner oxides have brought the poly-silicon gate closer to the Si/SiO<sub>2</sub> interface increasing the chances of hydrogen diffusion, trap creation and NBTI susceptibility. Thirdly the introduction of nitrogen atoms into the oxide has enhanced NBTI degradation. To increase the dielectric constant nitrogen was added, intended to improve hot-carrier resistance and gate current leakage. However, nitrogen tends to increased NBTI problems. Tan et al [47] presented some excellent results showing the enhancement of NBTI with incorporation of nitrogen into the oxide. Comparisons between pure SiO<sub>2</sub> and various interfacial nitrogen concentrations showed an increase in NBTI degradation, sometimes by a factor of 10 as in the case when comparing pure SiO<sub>2</sub> to 15.5% nitrogen concentrate. These results were complimented by Huard and his co-workers [46] who further investigated the effect of nitrogen, showing an accelerated NBTI degradation for increased nitrogen concentrations.

As well as highlighting the influence of nitrogen on NBTI, Huard et al [46] also presented some results on oxide field and temperature dependence of NBTI. A range of gate oxide thickness (1.6 to 6.5nm), were stressed for ten thousand seconds at varying gate voltages and temperatures. The investigation found that both trap creation and charge trapping were increased for higher gate voltage stress levels. Results also showed an increase in threshold voltage shift at higher temperatures, which was proposed to be due to increased interface trap creation. Similar characteristics were observed by Aono et al [48] and Mahapatra et al [49] who pointed out that  $\Delta V_{th}$  has a tendency to saturate with increasing stress time. This is a characteristic noted by Goetzberger et al [45] over thirty years ago. Since then many groups have reported the time-dependent shift to follow a power law dependence with an exponent around 0.25. This value was what early studies by Jeppson and Svensson [50] proposed but there after the value has been widely debated. As Ershov et al [51] stated, one of the reasons for this debate is that the exponent is not a universal parameter, and may depend on stress and measurement conditions. This was proven by Aono et al [48] who showed that the coefficient decreases with increasing stress time and can vary from 0.3 down to 0.16. Further deviations from the single exponent power law were presented by Alam et al [52].

A key characteristic of NBTI first noted by Schlünder et al [53] in 1999 was a recovery effect. He noticed that the combination of high temperature and high positive gate voltage resulted in strong relaxation of the NBTI effects. Ershov et al [51] performed experiments with measurements taken during and after sequences of stresses revealing the the recovery contains a fast initial transient followed by a very slow non-exponential transient, which appears to saturate with time. This would suggest that NBTI degradation contains a level of permanent damage, possibly related to fixed positive charge in the gate oxide. The obvious question that springs to mind when considering the recovery effect, is how NBTI degradation would be

effected by dynamic stressing. The majority of published research has focused on static stressing. Tan et~al~[54] presented some insight into the effects of pulsed stress finding an increased lifetime enhancement for dynamic signals compared to constant voltage stressing. Chen et~al~[55] presented results showing dynamic NBTI (DNBTI) degradation was less than that of equivalent static NBTI (SNBTI) stress and DNBTI effects were frequency independent. In contrast Mahapatra et~al~[49] proposed that interface trap creation and thus  $\triangle V_{th}$  decreased at higher frequencies.

Exact modelling of NBTI has been made difficult because the physics and root cause of the degradation is still not fully understood [46]. It is believed that NBTI is a result of a build up of positive charge either at the Si/SiO<sub>2</sub> interface or in the oxide layer, which in-turn leads to an increase in threshold voltage. A number of authors [43, 49, 51, 56] have attributed the formation of this positive charge to the diffusion of hydrogen away from the Si/SiO<sub>2</sub> interface. Mahapatra et al [49] explained this process using the Reaction-Diffusion (R-D) model. The model states that under NBTI stress the interface trap is due to the dissociation of Si-H bonds at the Si/SiO<sub>2</sub> interface (reaction) and the subsequent movement of released H species away from the interface (diffusion) leaving behind a positively charged interface state. According to the R-D model, the movement of hydrogen species back to the interface when the stress is removed would also give an explanation to the the recovery effect. This is what Mahapatra et al [49] proposed but Huard et al [46] argued against this. His results compared the reduction of the threshold voltage with interface trap density after stress removal. The results showed a strong decrease (more than 50%) of the threshold voltage whereas the interface trap density remained almost unchanged. He therefore proposed that the recovery effect should not be accounted for by the re-passivation of hydrogen, but failed to detail any alternative reason.

It is acknowledged that at present exact determination of the the process that leads to NBTI degradation and its recovery is not fully understood. It is clear also just from this review that there are a number of issues still be resolved, including the effects of dynamic stressing. The use of models such as the reaction-diffusion type has helped put together a more complete understanding of NBTI physics, but it could be said that the NBTI signatures noticed by Goetzberger [45] and his coworkers over thirty years ago are still valid today.

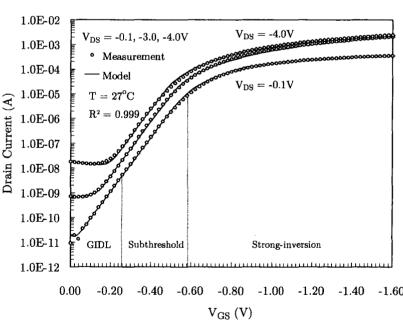

## 2.5.3 Hot-Carrier Effects

Hot-carrier damage leads to degradation of the threshold voltage, transconductance (on-resistance), and drain current driving capabilities. The driving force behind the degradation is the channel electric field. This has always posed an important consideration to the development of CMOS transistor technology and there has been substantial research into hot-carriers effects and the cause of the degradation [57, 58, 59]. However the repeating problems brought about by aggressive scaling has resulted in its effects being enhanced in recent years. Ning et al [60] was one of the first to recognise the problem hot-carriers posed to device scaling. Chen et al [61] continued Ning's early work to apply the lucky electron model in the study of substrate hot electron injection. The lucky electron model developed by Shockley hinges on there being a supply of 'lucky' hot electrons. Two factors that constitute the electron being 'lucky' are firstly if it has enough kinetic energy from the channel to become 'hot'. Within the literature several analytical models for substrate current behaviour have been reported [57, 62, 63]. Hu et al [57] used the lucky electron model as a basis for a landmark paper that explored the use of the substrate current as a measure of hot-carrier effects. Using the substrate current as a link to hot-carrier degradation he proposed a method for predicting device lifetime that has been used extensively since by numerous researchers.