## **Durham E-Theses**

# An embedded adaptive optics real time controller

Saunter, Christopher D.

#### How to cite:

Saunter, Christopher D. (2007) An embedded adaptive optics real time controller, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/2423/

#### Use policy

The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-profit purposes provided that:

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

# An Embedded Adaptive Optics Real Time Controller

## Christopher D. Saunter

The copyright of this thesis rests with the author or the university to which it was submitted. No quotation from it, or information derived from it may be published without the prior written consent of the author or university, and any information derived from it should be acknowledged.

A Thesis presented for the degree of Doctor of Philosophy

Centre for Advanced Instrumentation

Department of Physics

University of Durham

England

April 17<sup>th</sup>, 2007

- 2 JAN 2008

### An Embedded Adaptive Optics Real Time Controller

#### Christopher D. Saunter

Submitted for the degree of Doctor of Philosophy April  $17^{th}$  2007

#### Abstract

The design and realisation of a low cost, high speed control system for adaptive optics (AO) is presented. This control system is built around a field programmable gate array (FPGA). FPGA devices represent a fundamentally different approach to implementing control systems than conventional central processing units.

The performance of the FPGA control system is demonstrated in a specifically constructed laboratory AO experiment where closed loop AO correction is shown. An alternative application of the control system is demonstrated in the field of optical tweezing, where it is used to study the motion dynamics of particles trapped within laser foci.

## Declaration

The work in this thesis is based on research carried out at the Centre for Advanced Instrumentation, the Department of Physics, University of Durham, England. Some of the data present in the results chapter has formerly been published in FPGA technology for high speed, low cost adaptive optics Saunter C.D., Love G.D., Johns, M., Holmes, J. from proc. 5th International Workshop on Adaptive Optics in Industry and Medicine (2005). No part of this thesis has been submitted elsewhere for any other degree or qualification and it is all the sole work of the author with the exception of those areas listed below.

Assistance is acknowledged with PCB design - the detailed layout and fabrication of the custom DAC PCB used in the laboratory demonstrator was undertaken by the workshop services in the Physics Department at Durham. This work was carried out to the authors specification. The detailed layout and fabrication of the custom PCBs forming the enhanced prototype controller was undertaken by Sira Technologies Ltd. This work was carried out to a specification arrived at jointly by the author and Sira. The work on optical tweezing presented in chapter 7 was conducted at the Optics Group at the University of Glasgow using an experiment created and maintained by Glasgow. The results obtained and presented here are a joint result of their experimental setup and the authors control system being used as a high speed data processing camera.

#### Copyright © 2007 by Christopher D. Saunter.

"The copyright of this thesis rests with the author. No quotations from it should be published without the author's prior written consent and information derived from it should be acknowledged".

# Acknowledgements

Undertaking a PhD has been a fantastic experience and one I could not have started without the faith of my supervisor, Gordon Love.

During the three year period (give or take a little...) between starting and finishing my work I have had many useful discussions with members of the CfAI here in Durham, with thanks going to every member of the group, and have enjoyed the hospitality of the adaptive optics community in the UK and abroad, with special notes of thanks to Enrico, Rob and Christian at ESO in Garching, David and John-Mark (scourge of the coke machines) at Strathclyde and Sarah from London.

I am grateful to Miles Padgett from the University of Glasgow for the opportunity to work with their group, thanks to all this group for their hospitality and also to a fellow visitor there, Roberto di Leonardo, for a crash course in the behaviour of optically trapped particles and for ploughing through half a gigabyte of data.

I would like to thank the members of Sira Technology Ltd. with whom I worked for their hospitality, wonderful canteen and technical assistance. I would especially like to thank Kate for saving parts of my work during the demise of Sira.

Finally no instrumentation thesis would be complete without acknowledging the impact (!) and assistance of my contemporary travellers from Room 4, including Harold D, Tom O, Tim M, Tim B, Paul B, Jason C, Mark H and James O.

# Contents

|   | Abs  | tract   |               |             |          |        |     |      |      |      |  |  | ii  |

|---|------|---------|---------------|-------------|----------|--------|-----|------|------|------|--|--|-----|

|   | Dec  | laratio | n             |             |          |        |     |      |      |      |  |  | iii |

|   | Ack  | nowled  | gements       |             |          |        |     |      |      |      |  |  | iv  |

| 1 | Intr | oducti  | on            |             |          |        |     |      |      |      |  |  | 1   |

|   | 1.1  | Synop   | is            |             |          |        |     | <br> | <br> |      |  |  | 1   |

|   |      | 1.1.1   | Chapter 2     |             |          |        |     | <br> | <br> |      |  |  | 2   |

|   |      | 1.1.2   | Chapter 3     |             |          |        |     | <br> | <br> |      |  |  | 2   |

|   |      | 1.1.3   | Chapter 4     |             |          |        |     | <br> | <br> |      |  |  | 2   |

|   |      | 1.1.4   | Chapter 5     |             |          |        |     | <br> | <br> |      |  |  | 2   |

|   |      | 1.1.5   | Chapter 6     |             |          |        |     | <br> | <br> |      |  |  | 2   |

|   |      | 1.1.6   | Chapter 7     |             |          |        |     | <br> | <br> |      |  |  | 2   |

|   |      | 1.1.7   | Chapter 8     |             |          |        |     | <br> | <br> |      |  |  | 2   |

| 2 | Ada  | ptive   | Optics Theory | y           |          |        |     |      |      |      |  |  | 3   |

|   | 2.1  | Introd  | action        |             |          |        |     | <br> | <br> |      |  |  | 3   |

|   | 2.2  | Spatia  | control       |             |          |        |     | <br> | <br> |      |  |  | 3   |

|   |      | 2.2.1   | Open and clos | ed loop cor | ntrol .  |        |     | <br> | <br> |      |  |  | 3   |

|   |      | 2.2.2   | Wavefront Sen | sing        |          |        |     | <br> | <br> |      |  |  | 5   |

|   |      |         | 2.2.2.1 Gene  | ric Wavefro | ont Sen  | sor.   |     | <br> | <br> |      |  |  | 6   |

|   |      |         | 2.2.2.2 Geom  | netric wave | front se | ensors |     | <br> | <br> |      |  |  | 8   |

|   |      |         | 2.2.2.3 The   | Shack-Hart  | mann S   | Sensor | · . | <br> | <br> |      |  |  | 9   |

|   |      |         | 2.2.2.4 The l | Pyramid Se  | ensor.   |        |     | <br> | <br> |      |  |  | 11  |

|   |      |         | 2.2.2.5 The   | Curvature : | Sensor   |        |     | <br> | <br> |      |  |  | 12  |

|   |      | 2.2.3   | Wavefront Cor | rection .   |          |        |     | <br> | <br> | <br> |  |  | 13  |

|          | · · |  |

|----------|-----|--|

| Contents |     |  |

|   |   |     |         | 2.2.3.1     | Generic wavefront corrector | 15 | 3 |

|---|---|-----|---------|-------------|-----------------------------|----|---|

|   |   |     |         | 2.2.3.2     | Reflective devices          | 14 | 4 |

|   |   |     |         | 2.2.3.3     | Transmissive devices        | 16 | 6 |

|   |   |     | 2.2.4   | Figure R    | teconstruction              | 17 | 7 |

|   |   |     |         | 2.2.4.1     | Control Matrix Generation   | 17 | 7 |

| • |   |     | 2.2.5   | Wavefron    | nt Reconstruction           | 19 | 9 |

|   |   |     | 2.2.6   | Modal C     | Control                     | 19 | 9 |

|   |   | 2.3 | Tempo   | oral contro | ol                          | 20 | ) |

|   |   | 2.4 | System  | n operatio  | on                          | 20 | ) |

|   |   |     | 2.4.1   | System c    | calibration                 | 20 | ) |

|   |   |     | 2.4.2   | Closed lo   | oop operation               | 2  | 1 |

|   |   | 2.5 | Static  | correction  | a                           | 2  | 1 |

|   | 3 | FPC | GA/AC   | O Theory    | y                           | 25 | 5 |

|   |   | 3.1 | Introd  | uction      | ·                           | 25 | 5 |

|   |   | 3.2 | Archit  | ecture of   | Modern Devices              | 26 | 6 |

|   |   | 3.3 | Progra  | amming m    | nodel and tool flow         | 29 | 9 |

|   |   | 3.4 | Existin | ng Applica  | ations to AO                | 31 | 1 |

|   | 4 | FPG | GA/A(   | ) Frame     | work                        | 33 | 3 |

|   |   | 4.1 | Introd  | uction      |                             | 35 | 3 |

|   |   |     | 4.1.1   | Overview    | v                           | 33 | 3 |

|   |   |     | 4.1.2   | Target sy   | ${f ystem}$                 | 34 | 4 |

|   |   | 4.2 | Frame   | work Over   | rview                       | 34 | 4 |

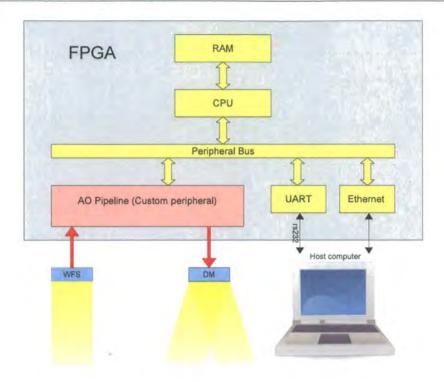

|   |   | 4.3 | Systen  | n on a Ch   | ip Design                   | 3  | 5 |

|   |   |     | 4.3.1   | Design C    | Choices                     | 36 | 6 |

|   |   |     |         | 4.3.1.1     | Choice of CPU               | 36 | 6 |

|   |   |     |         | 4.3.1.2     | External interfacing        | 3' | 7 |

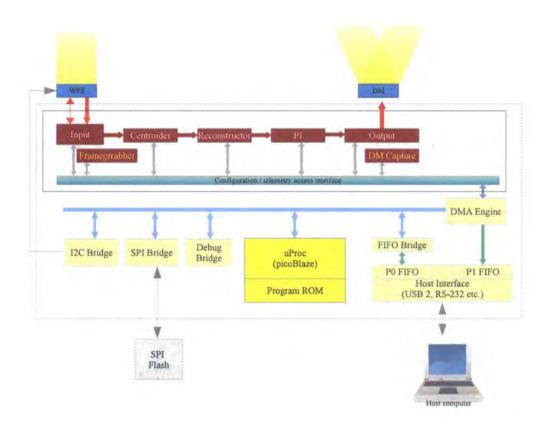

|   |   |     | 4.3.2   | AO Fran     | nework and SOC Architecture | 39 | 9 |

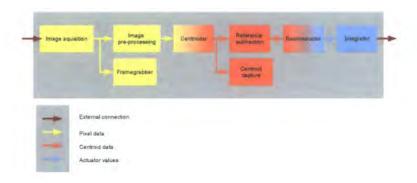

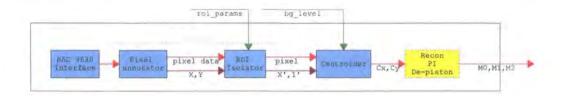

|   |   | 4.4 | The A   | daptive O   | Optics Pipeline             | 4: | 2 |

|   |   |     | 4.4.1   | Image ac    | equisition                  | 45 | 2 |

|   |   |     |         | 0           | 1                           |    |   |

|   |   |     | 4.4.2   | _           | rabber                      | 43 | 3 |

|   |   |     | 4.4.2   | _           |                             |    |   |

|   |   |     | 4.4.2   | Frame gr    | rabber                      | 44 | 4 |

| Contents |      | vii |

|----------|------|-----|

| ··       | <br> |     |

|   |     | 4.4.3  | Image pr   | re-processing                                                                                                                    | 45 |

|---|-----|--------|------------|----------------------------------------------------------------------------------------------------------------------------------|----|

|   |     | 4.4.4  | Centroid   | 46                                                                                                                               |    |

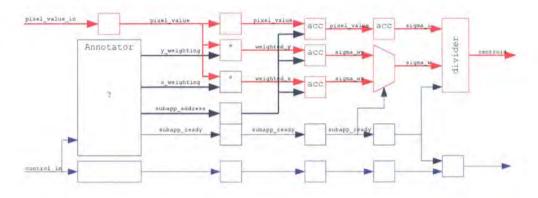

|   |     |        | 4.4.4.1    | Generic FPGA Centroider                                                                                                          | 46 |

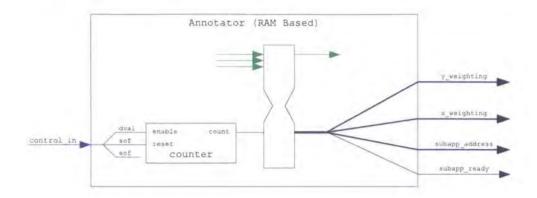

|   |     |        | 4.4.4.2    | Arbitrary Geometry Centroider                                                                                                    | 47 |

|   |     |        | 4.4.4.3    | Partially Confined Geometry Centroider                                                                                           | 50 |

|   |     | 4.4.5  | Reference  | e subtraction and centroid capture                                                                                               | 53 |

|   |     | 4.4.6  | Reconstr   | uctor Design and Implementation                                                                                                  | 53 |

|   |     |        | 4.4.6.1    | Design of an efficient reconstructor for the Xilinx Virtex-II                                                                    |    |

|   |     |        |            | $architecture \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                    | 54 |

|   |     | 4.4.7  | Gain and   | l Integrator                                                                                                                     | 55 |

|   |     | 4.4.8  | Code imp   | plementation                                                                                                                     | 57 |

|   |     | 4.4.9  | Software   | $architecture \dots \dots$ | 57 |

|   | 4.5 | Design | performa   | ance and summary                                                                                                                 | 58 |

| 5 | Lab | orator | y Demon    | strator 1 - Design and construction                                                                                              | 59 |

|   | 5.1 | Introd | 59         |                                                                                                                                  |    |

|   | 5.2 |        |            | 60                                                                                                                               |    |

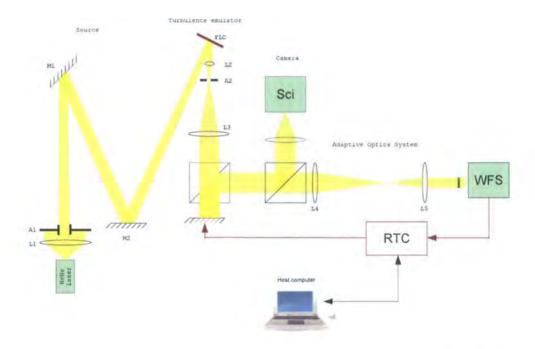

|   |     | 5.2.1  | The Sour   | rce Module                                                                                                                       | 60 |

|   |     | 5.2.2  | Turbulen   | ce emulation                                                                                                                     | 60 |

|   |     | 5.2.3  | Adaptive   | e Optics System                                                                                                                  | 62 |

|   |     |        | 5.2.3.1    | $DM \ \dots $              | 62 |

|   |     |        | 5.2.3.2    | WFS                                                                                                                              | 62 |

|   |     | 5.2.4  | Imaging    | Camera                                                                                                                           | 66 |

|   | 5.3 | Real t | ime contro | oller                                                                                                                            | 66 |

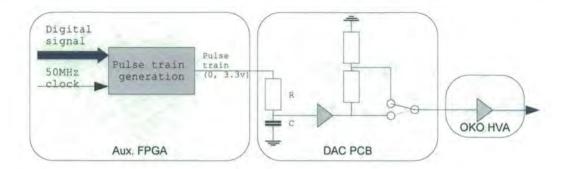

|   |     | 5.3.1  | DM Driv    | re electornics                                                                                                                   | 69 |

|   |     | 5.3.2  | FPGA/A     | O framework implementation                                                                                                       | 70 |

| 6 | Lab | orator | y Demon    | nstrator 2 - Results                                                                                                             | 72 |

|   | 6.1 | Open : | Loop Mea   | surements                                                                                                                        | 72 |

|   | 6.2 | System | n Calibrat | ion                                                                                                                              | 73 |

|   |     | 6.2.1  | Reconstr   | uctor performance                                                                                                                | 74 |

|   |     | 6.2.2  | Self corre | ection tests                                                                                                                     | 76 |

|   |     | 6.2.3  | Static ab  | perration optimization                                                                                                           | 78 |

|   | 6.3 | Closed | l Loop     |                                                                                                                                  | 79 |

| viii |

|------|

|      |

| 7 | Fur | ther A | pplications                     | 81 |

|---|-----|--------|---------------------------------|----|

|   | 7.1 | Introd | uction                          | 81 |

|   | 7.2 | Enhan  | ced Prototype                   | 81 |

|   | 7.3 | Dedica | ted tip/tilt controller         | 84 |

|   | 7.4 | A Sma  | rt Camera for particle tracking | 86 |

|   |     | 7.4.1  | Background                      | 87 |

|   |     | 7.4.2  | Smart Camera Implementation     | 88 |

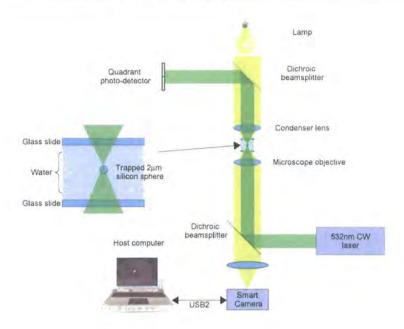

|   |     | 7.4.3  | Experimental setup              | 89 |

|   |     |        | 7.4.3.1 Single particle         | 89 |

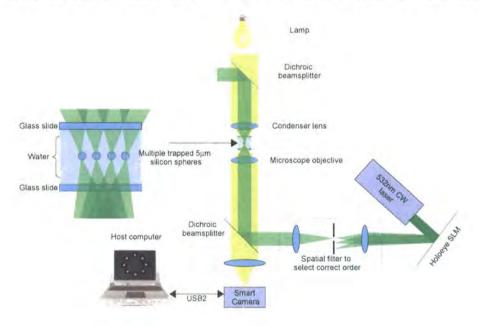

|   |     |        | 7.4.3.2 Multi-particle setup    | 90 |

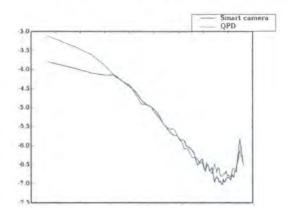

|   |     | 7.4.4  | Results                         | 90 |

|   |     |        | 7.4.4.1 Single particle         | 90 |

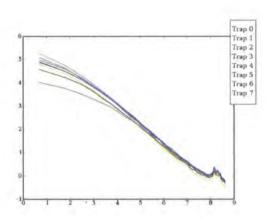

|   |     |        | 7.4.4.2 Multiple particles      | 92 |

| 8 | Con | cludin | g Remarks                       | 94 |

|   | 8.1 | On Wo  | ork Undertaken                  | 94 |

|   |     | 8.1.1  | Adaptive Optics                 | 94 |

|   |     | 8.1.2  | Smart Camera                    | 95 |

|   | 8.2 | Future | Directions                      | 95 |

|   |     | 8.2.1  | Future AO control systems       | 95 |

|   |     | 8.2.2  | High Order AO Control           |    |

|   |     | 823    | Smart Camera                    | 96 |

# List of Figures

| 2.1  | Model AO Systems                                                       | 4  |

|------|------------------------------------------------------------------------|----|

| 2.2  | Generic wavefront sensor                                               | 6  |

| 2.3  | Geometric wavefront sensing                                            | 9  |

| 2.4  | The Shack-Hartmann Sensor                                              | 10 |

| 2.5  | The Curvature Sensor                                                   | 12 |

| 2.6  | Types of push/pull actuated mirror                                     | 14 |

| 2.7  | Types of force controlled mirror                                       | 15 |

| 2.8  | Detailed breakdown of operations in an AO system                       | 22 |

| 2.9  | Static aberrations in an AO system                                     | 23 |

| 3.1  | Basic structure of Xilinx devices                                      | 27 |

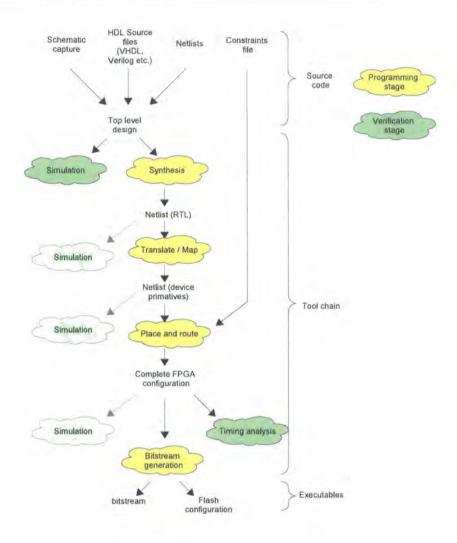

| 3.2  | Tool flow for programming Xilinx FPGA devices                          | 31 |

| 4.1  | Example System on a Chip system for AO                                 | 35 |

| 4.2  | Detailed view of the AO SOC                                            | 40 |

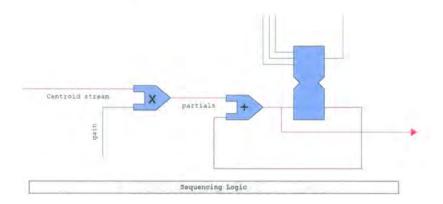

| 4.3  | AO Pipeline configuration                                              | 43 |

| 4.4  | Images captured with the successive partial system                     | 45 |

| 4.5  | Generic hardware based centroider :                                    | 46 |

| 4.6  | RAM annotation for an arbitrary geometry                               | 48 |

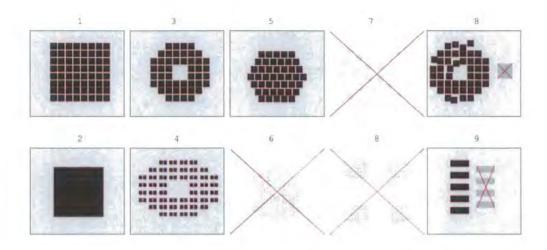

| 4.7  | Some possible subaperture geometries for the AGC                       | 50 |

| 4.8  | Limitations imposed by restricted centroider                           | 51 |

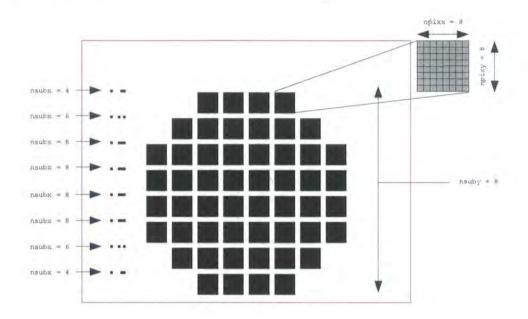

| 4.9  | Compressed annotation RAM for horizontally confined geometries $\dots$ | 52 |

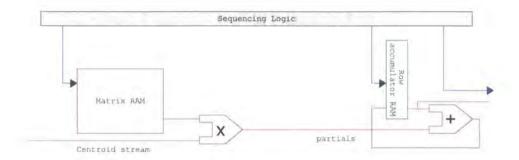

| 4.10 | Generic FPGA based reconstructor                                       | 54 |

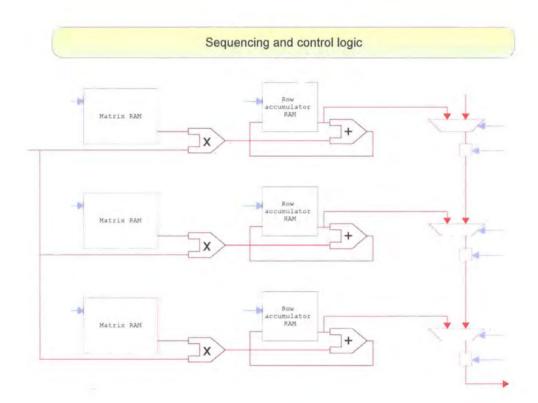

| 4.11 | Reconstructor designed for all-internal operation                      | 56 |

| 4.12 | Gain and integration                                                   | 57 |

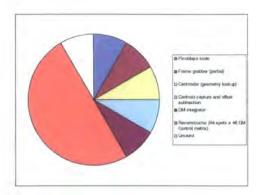

| 4.13 | Breakdown of BlockRAM usage within the FPGA/AO Framework               | 58 |

List of Figures x

| F 1  | Days and the A.O. South and                                              | cc |

|------|--------------------------------------------------------------------------|----|

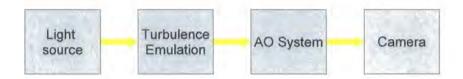

| 5.1  | Demonstrator AO System                                                   |    |

| 5.2  | Optical bench configuration for the AO demonstrator                      | 61 |

| 5.3  | The 37 Channel OKO Deformable Mirror                                     | 63 |

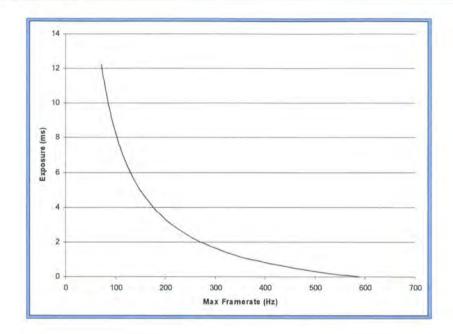

| 5.4  | Maximum framerate vs Exposure for the KAC-9630 image sensor              | 64 |

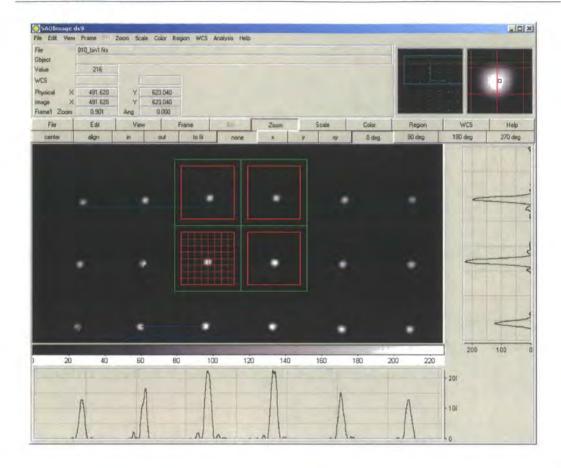

| 5.5  | Shack-Hartmann spot pattern                                              | 65 |

| 5.6  | Wavefront sensor assembly                                                | 66 |

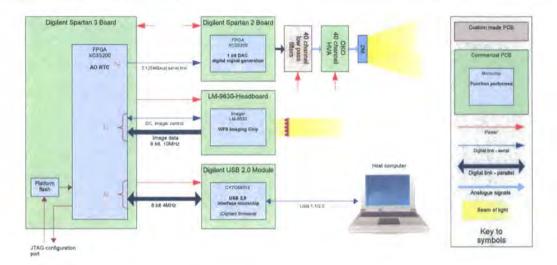

| 5.7  | Electronics configuration                                                | 67 |

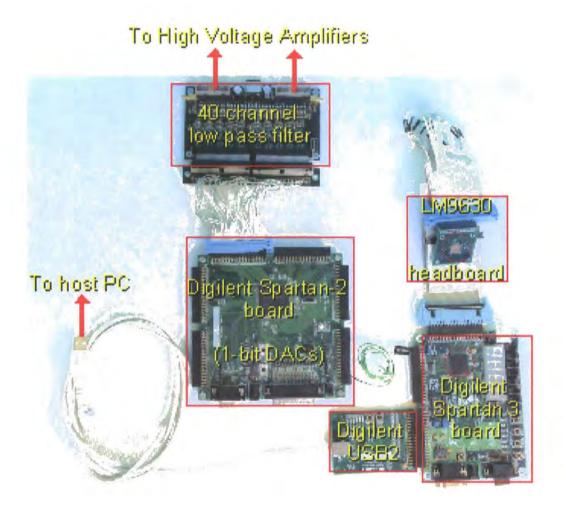

| 5.8  | Photograph of PCBs used in the demonstrator                              | 68 |

| 5.9  | DM Drive electronics                                                     | 69 |

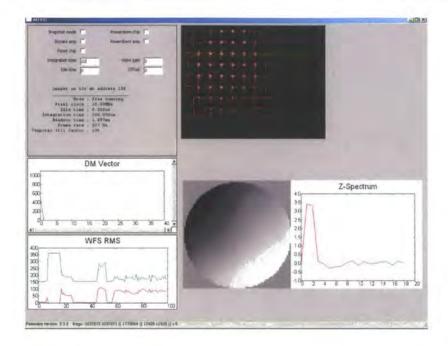

| 5.10 | Screenshot of the AO GUI created for monitoring the AO RTC               | 70 |

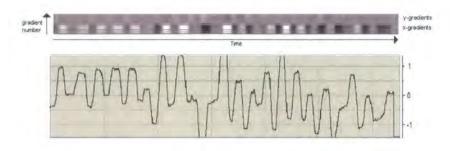

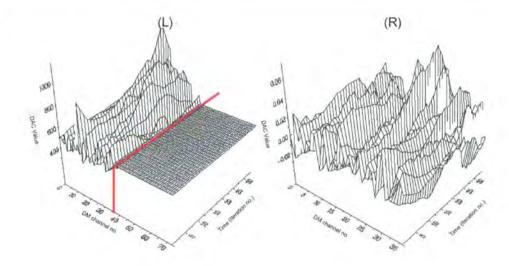

| 6.1  | high speed open loop sensing of global tilt                              | 73 |

| 6.2  | high speed open loop turbulence sensing                                  | 74 |

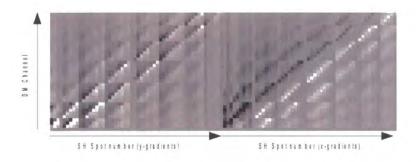

| 6.3  | Interaction Matrix (top) and the derived Control Matrix (bottom) for the |    |

|      | AO Laboratory Demonstrator                                               | 75 |

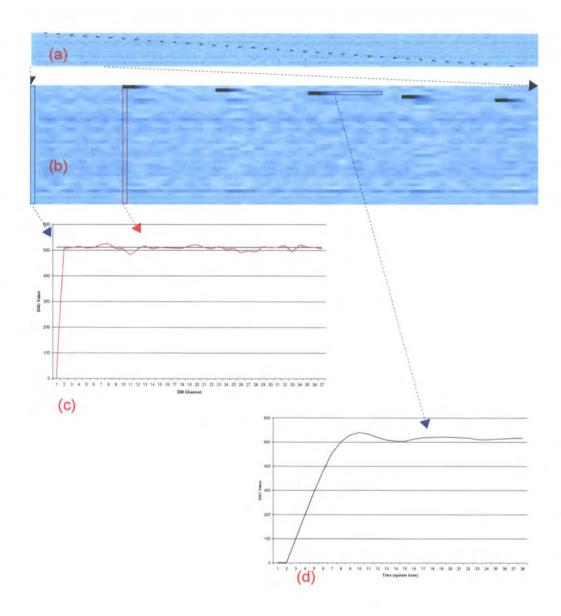

| 6.4  | FPGA based reconstructor test                                            | 76 |

| 6.5  | Closed loop step response testing of the AO system                       | 77 |

| 6.6  | Static aberration correction                                             | 78 |

| 6.7  | Closed loop AO correction                                                | 80 |

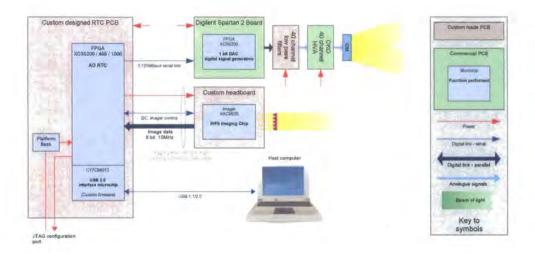

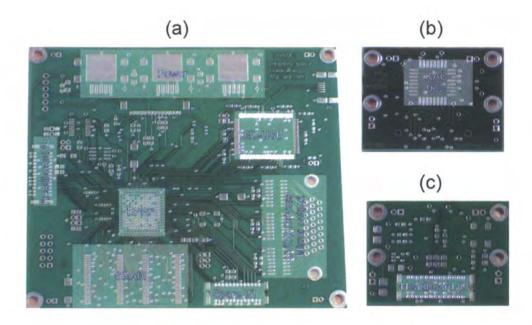

| 7.1  | Custom PCBs developed for AO control                                     | 82 |

| 7.2  | Photographs of the custom PCBs for AO control                            | 83 |

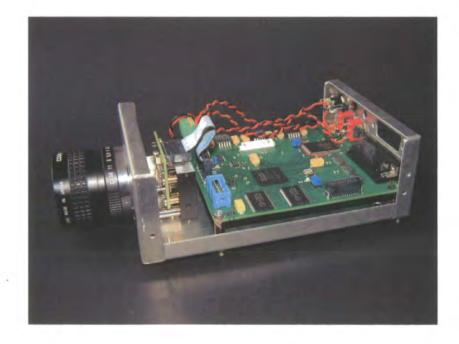

| 7.3  | Photograph of the enhanced prototype AO controller                       | 83 |

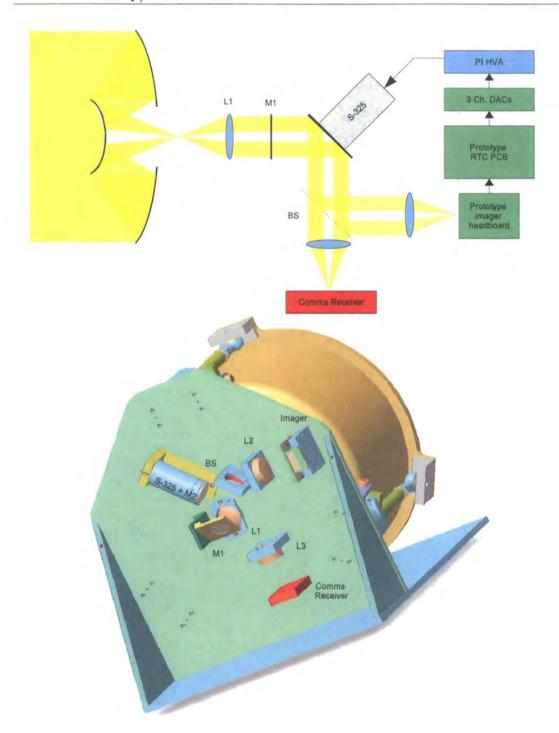

| 7.4  | FSO receiver with tip/tilt system                                        | 85 |

| 7.5  | Tip/tilt data path                                                       | 87 |

| 7.6  | Screenshot of the Smart Camera GUI tracking 8 particles                  | 90 |

| 7.7  | Experimental setup used for the single particle experiment               | 91 |

| 7.8  | Experimental setup used for the hydrodynamic coupling experiments        | 91 |

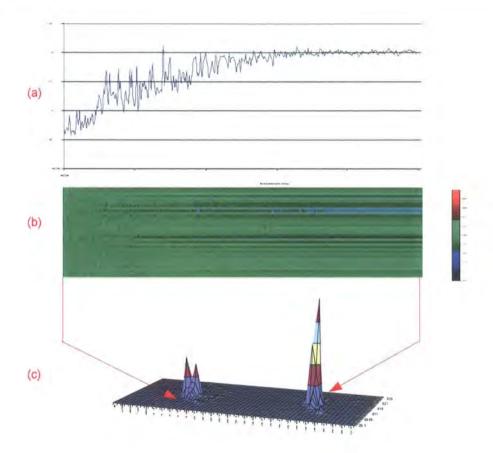

| 7.9  | Power spectra of 1 optically trapped bead                                | 92 |

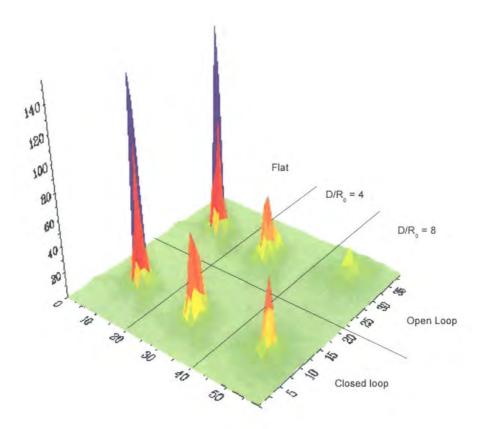

| 7.10 | Power spectrum of 8 beads in optical traps                               | 93 |

# Chapter 1

# Introduction

### 1.1 Synopsis

The first proposal of a method for reducing the effects of atmospheric seeing was from Horace Babcock [1] in 1953. The development of practical adaptive optics (AO) systems for such purposes required significant advances in detector technology and signals processing technology - particularly the development of the integrated circuit and central processing unit concepts necessary to provide the large real-time processing requirements.

During the last decade AO has become a de-facto technology installed on most ground based astronomical telescopes in the 4-10M diameter range and is integral to the design of future large telescopes in the 10-50M range. Recently AO has found applications to other fields such as ophthalmology, improving the resolution of retinal images[2] enabling the [3] mapping of waveband specific cones in the human eye, high power laser beam shaping to improve performance for inertial confinement fusion research [4, 5], and increasing the performance of free space optical communications links[6].

As the use of adaptive optics increases in these fields the possibility is raised of AO being used in commercial instruments and devices as well as a tool for scientific research. This thesis presents the development of a low cost, high speed control system intended for use in such commercial AO systems, offering lower cost and smaller sizes than existing AO control technologies. The control system presented here is based around field programmable gate array technology (FPGA), a relatively new class of microchip device radically different from traditional the central processing units (CPUs) and digital signals processors (DSPs) employed by existing AO control systems.

1.1. Synopsis 2

#### 1.1.1 Chapter 2

This chapter presents a theoretical overview of adaptive optics systems intended for high bandwidth correction with an onus on exploring the devices and algorithms used to implement such a system.

#### 1.1.2 Chapter 3

In this chapter the various options for implementing a real time control system, such as microprocessors and FPGA devices are examined, and a rationala given for the choice of FPGAs for this work. The operation and programming of FPGA devices is also examined in this chapter. Finally a review of other work on using FPGA devices for AO is presented.

#### 1.1.3 Chapter 4

Chapter 4 presents a framework for real time image processing and control that was developed and the AO control system built on this. A broad view of the developed architecture is given, along with detailed examination of key components for AO control.

#### 1.1.4 Chapter 5

Chapter 5 examines the design and construction of a laboratory AO system, including a turbulence source and an imaging system, for testing and developing the control system.

#### 1.1.5 Chapter 6

Chapter 6 presents the operation and results gained from the laboratory demonstrator.

#### 1.1.6 Chapter 7

This chapter examines further development of the control system, presenting an enhanced prototype that is a more compact system of packaged electronics providing a compact AO control system. Also examined are alternate uses of this control system including a tip/tilt beam steering control loop for free space optical communications and an open loop camera with in-built data processing and reduction, a 'smart camera'.

#### 1.1.7 Chapter 8

Finally in chapter 8 concluding remarks are drawn.

## Chapter 2

# **Adaptive Optics Theory**

### 2.1 Introduction

This chapter introduces the theory underlying an adaptive optics system, paying particular attention to the algorithms used as a precursor to their implementation in chapter 4.

An adaptive optics system controls the phase of a light beam, both spatially and temporally, to modify the wavefront to be some normally flat shape. Whilst the temporal bandwidth of many sources of turbulence requires an adaptive optics system to run at high update rates the majority of the calculation involved in performing these updates are concerned with processing the spatial qualities of the wavefront. As such the spatial and temporal aspects of wavefront control are often presented and implemented separately, and are examined in sections 2.2 (Spatial control) and 2.3 (Temporal control) below. Section 2.4 draws these areas together to show how a complete system is calibrated and operated. Finally section 2.5 looks at methods used to reduce static errors.

## 2.2 Spatial control

#### 2.2.1 Open and closed loop control

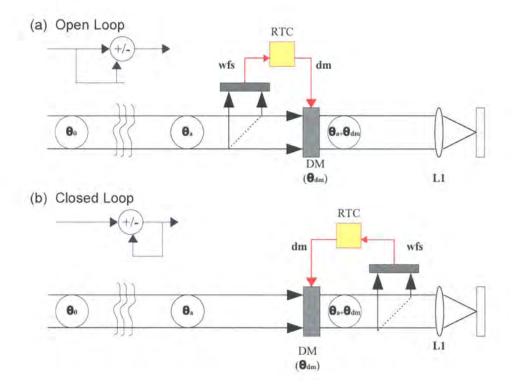

The two principle forms that may be taken by an AO system are open loop and closed loop, as shown in figures 2.1 (a) and (b). These figures represent a simple imaging system in which a distant point source is imaged by the lens L1. In the absence of any distortions the point source produces a flat wavefront,  $\theta_0$ , leading to a diffraction limited image.

Distortions to the incoming wavefront caused by perturbations, for example atmospheric turbulence, aberrate the beam, leading to a distorted wavefront  $\theta_a$  and subse-

Figure 2.1: Model AO Systems - simple open loop (a) and closed loop (b) AO systems in which a flat wavefront  $\theta_0$  is distorted with a wavefront of  $\theta_a$  before being corrected by a deformable mirror (DM). The DM is driven by a command vector  $\mathbf{dm}$  derived from the wavefront sensor (WFS). The positioning of the WFS determines the open- or closed-loop nature of the system.

quently a distorted focal plane image. The system is examined during a time period shorter than the coherence time of the perturbations, such that they may be considered static.

In both systems an optical element with a configurable phase, the deformable mirror (DM) in the figure, responds to the control signal  $\mathbf{dm}$  by adding a phase of  $\theta_{dm} = DM(\mathbf{dm})$  to the beam, where the function  $DM(\mathbf{x})$  represents the mirror's optical response to its electronic control vector  $\mathbf{x}$ . The aim of this is to counteract the aberrations in the beam.

In the open loop case a wavefront sensor (WFS) measures the phase of the aberrated beam, quantifying it in the form of a series of measurements, collectively referred to as the wavefront sensor vector, wfs. This is processed by the real time controller (RTC) into the DM vector suitable for driving the DM with an equal and opposite phase thus removing the aberrations.

In the closed loop case the WFS is placed after the corrector, causing the WFS to measure a phase of  $\theta_{\mathbf{w}} = \theta_{\mathbf{a}} + \theta_{\mathbf{dm}}$ . This is processed by the RTC into commands for the DM that should cause the DM to reduce the measured phase to 0, i.e.  $\theta_{\mathbf{dm}} = -\theta_{\mathbf{w}}$ . In the close loop system the wavefront sensor is operating in a nulling mode in which the system acts to reduce the signal on the sensor to 0, reducing the dynamic range requirements on the WFS, which in practice simplifies design and allows for greater precision over this reduced range.

The majority of AO systems follow the open- or closed- loop models thus described with some form of RTC algebraically manipulating the WFS signal into DM commands by use of digital signals processing (DSP), although there have been examples of systems where the transformation is performed by a trained neural network instead such as early work with the MMT [7] or where the transform is omitted entirely and a high speed optimisation loop in employed instead [8] in a similar, but significantly faster, method to the static aberration correction outlined at the close of this chapter.

#### 2.2.2 Wavefront Sensing

The WFS is a device that measures the wavefront or more usually some quantity related to the wavefront, presenting these measurements as an electronics signal suitable for further processing. Below a generic overview of wavefront sensing is presented followed by a brief examination of common WFS types used in AO.

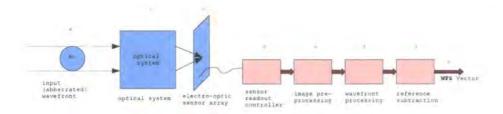

Figure 2.2: Generic wavefront sensor - most wavefront sensors can be represented by the series of optical end electronic signals processing shown in the figure

#### 2.2.2.1 Generic Wavefront Sensor

A generic wavefront sensor is illustrated in 2.2, used to examine an incoming wavefront illustrated by (a) in the figure, with a wavefront of  $\theta_{\mathbf{a}}$  and ultimately produce a vector wfs describing some quantities of this wavefront, (h) in the figure.

The sensor is examined in stages with a system consisting of optics (b) to convert the phase information into an intensity pattern, a sensor array (c) sampling this pattern into an electrical signal, typically analogue at this stage. The readout of this sensor array is performed by a controller (d) which emits the intensity of the sensor elements as a digital data-steam that may be regarded as an image. Image pre-processing (e) is then carried out related to the sensor array - this is independent of the type of WFS system, and is intended to compensate for non-uniformity in the sensor array and to reduce the effect of background light etc. The image is now ready for wavefront processing (f) which is specific to the type of WFS involved and extracts the measurements encoded by (a) from the image. Finally to compensate for imperfect alignment of the system, and in a closed-loop system to convert the sensor to a nulling mode a reference wavefront vector may be subtracted (g), with the system emitting the 'wavefront sensor' vector, WFS.

Most wavefront sensors can be constructed by taking this generic system and customising just the optical processing (a) and the wavefront processing (e) stages. With this in mind the AO framework developed and explored in chapter 4 seeks to be as generic and modular as possible enabling new modes of operation to be created by only changing these two components.

#### (b) - Optical processing

This initial stage of the system uses some physical optical system to convert the aberrated phase of the beam into an intensity pattern. Typical approaches rely on either specialised forms of interferometry such as point diffraction interferometry, [9] or lateral shearing interferometry or dedicated AO sensing technologies such as the Shack-Hartmann, Pyramid and Curvature sensors outlined below.

#### (c) - Sensor array

The sensor array converts the optical intensity signals produced by (a) into electrical signals for further processing. A typical sensor array in an astronomical environment must make highly efficient use of the available light levels leading to the use of discrete avalanche photo-diode elements, as in the Subaru AO system [10] for example, or a charge coupled device (CCD).

An array of discrete sensors, such as those used by the Subaru AO system, often require fibre coupling of the sensors to the focal plane output of the optics, and a large quantity of supporting electronics making such a configuration both expensive to manufacture and physically bulky - neither trait suitable for the goal of a low cost system. CCDs as used in many astronomical AO systems represent the pinnacle of current devices with peak quantum efficiencies of 90%, frame rates of over 4000Hz and low read noise [11].

#### (d) - Controller

The controller provides the power requirements for the sensor array, sequences the readout of photo-electric charge from the elements and performs the amplification and subsequent analogue to digital conversion of these charges. Typically the controller will also set the frame rate, exposure and other similar parameters for the sensor array.

For an APD based system the controller is likely to be a custom development, whilst high end CCD devices tend to be interfaced to controllers from one of several prominent manufacturers such as SDSU or SciMeasure. Either approach is prohibitively expensive for a low-cost system. Previous work on low-cost adaptive optics [12][13], has focussed on the use of Dalsa CCD cameras which package a CCD device and Dalsa controller into a single physical device. A typical cost for such a camera is US\$6000 which whilst significantly less than for a separate CCD and controller is still high.

#### (e) and (f) - Image pre-processing and Wavefront processing

These two stages occur on the digital data emitted by the controller, and are both digital signals processing operations. (e) consists of various per-pixel operations to compensate for non-linearity effects in the sensor array, and to mitigate the effects of 'hot' and 'dead' pixels in the array. (f) constitutes the bulk of the processing and is specific to the type of wavefront sensor, for example calculating the position of centroids for a

Shack-Hartmann. The output of this section is the wavefront sensor vector, wfs.

#### (g) - Reference subtraction

When observing a flat wavefront a perfect WFS used in closed-loop should produce an output of  $\mathbf{wfs} = \mathbf{0}$ . However due to static aberrations in the system (see later sections) and the difficulty of achieving perfect alignment in a real system this is rarely the case, and the sensor will output some constant but non-null signal of  $\mathbf{wfs_0}$  when observing a flat wavefront. To convert the sensor to nulling operation  $\mathbf{wfs_0}$  must be recorded before closed loop operation is commenced and then subtracted from each WFS vector during closed loop operation, the resultant vector  $\mathbf{wfs'} = \mathbf{wfs} - \mathbf{wfs_0}$  is the final output of the wavefront sensor.

#### 2.2.2.2 Geometric wavefront sensors

All geometric wavefront sensors may be modelled with the intensity transport equation (ITE), which describes how the intensity of a beam changes as it is propagated past a phase distortion.

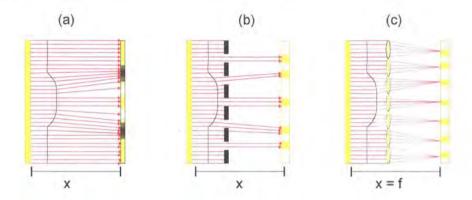

The basic application of this equation is shown in figure 2.3(a) in which a beam of uniform intensity passes through some aberration and is then propagated some further distance x to a plane in which the intensity encodes the phase information, which may be determined by an inverse solution of the ITE. This however assumes uniform illumination of the pupil which may not be guaranteed in a real system, and is computationally expensive.

The Hartmann sensor as illustrated in figure 2.3(b) simplifies the extraction of data from images generated using the ITE. A mask with a regular grid of holes in it, referred to as the Hartman mask, is inserted before the sensor array causing only parts of the input beam to be sampled. These parts now cast a discrete array of bright spots on the sensor, the position of which may be measured to determine the gradient of the phase of the input beam as sampled by the corresponding mask holes. Variations in pupil intensity structure will cause the spots to vary in intensity, but not position, so the phase measurement is now insensitive to pupil intensity. Further the extraction of the spot positions is computationally simpler than a reverse solution of the ITE. However such a system is inherently wasteful of the input light and is prone to errors as only a fraction of the beam is physically sampled.

The Shack-Hartmann (SH) sensor [14]. shown in 2.3(c) is a modification of the Hart-

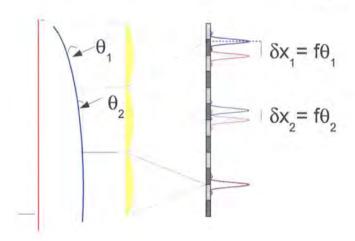

Figure 2.3: Geometric wavefront sensing - geometric propagation encodes wavefront slope in intensity in some plane (a) with a mask (b) or micro-lens array (c) employed to simplify the extraction of gradient from the intensity.

man device in which the mask is replaced with an array of lenses, often referred to as a 'micro-lens array' when fabricated on a small scale. The lenses allow the full pupil to be sampled, reducing susceptibility to aliasing and making more efficient use of available light. Further the spots produced by the device are well focussed compared to the Hartman mask, allowing their position and motion to be more accurately determined.

#### 2.2.2.3 The Shack-Hartmann Sensor

The basic theory of a SH device is that the average wavefront tilt across one microlens, or 'sub-aperture', will cause a displacement of the corresponding spot in the image plane, where the displacement is proportional to the average tilt, so long as the angles are sufficiently small for the paraxial approximation to hold. For example, a reference flat wavefront  $\mathbf{W_0}(\mathbf{s},\mathbf{t})$  is propagated through the microlens array as shown by the red lines in figure 2.4, forming an array of bright spots in the microlens focal plane, which is imaged by a pixelated detector array. A perturbed wavefront, shown in blue and described by  $\mathbf{W}'(\mathbf{s},\mathbf{t}) = \mathbf{W_0}(\mathbf{s},\mathbf{t}) + \Delta \mathbf{W}(\mathbf{s},\mathbf{t})$  perturbs the positions of the corresponding focal plane spots with a displacement of

$$\Delta x = f. \frac{\delta \Delta W}{\delta s}; \Delta y = f. \frac{\delta \Delta W}{\delta t}.$$

(2.1)

Typically the sensor-specific processing for a Shack-Hartmann consists of calculating the displacement of each of the spots cast by the microlens array and outputting these values as the WFS vector. Other methods do exist such as the Fourier transform method

#### Flat wavefront

Abberated wavefront

$\theta_n$  is average tilt across  $n^{th}$  microlens

### Microlens array

Pixelated imager in microlens focal plane

Figure 2.4: The Shack-Hartmann Sensor - an incoming flat wave, shown in red, produces a regular array of spots on the pixelated detector when propagated through the microlens array. A distorted wave, sown in blue, produces an array of displaced spots, with displacement depending on local wavefront gradient.

demonstrated by Carmon and Ribak[15], although such methods are in practice not found in high speed systems due to their computational overhead.

The position of a spot may be measured by a variety of centroiding algorithms, the most common of which is the center of mass algorithm in which the image is broken into a series of regions corresponding to individual spots, and the center of gravity of each region is calculated where mass is equivalent to the light intensity. This is done by multiplying the pixel grid values with linearly ramped weighting vectors in both dimensions and dividing the sum of weighted intensity by the sum of intensity as shown in the following equation

$$C_{y} = \frac{\sum_{i=0}^{n-1} \sum_{j=0}^{n-1} i.p_{i,j}}{\sum_{i=0}^{n-1} \sum_{j=0}^{n-1} p_{i,j}}; C_{x} = \frac{\sum_{i=0}^{n-1} \sum_{j=0}^{n-1} j.p_{i,j}}{\sum_{i=0}^{n-1} \sum_{j=0}^{n-1} p_{i,j}}.$$

(2.2)

where  $C_y$  and  $C_x$  are center of mass in 2 dimensions,  $p_{i,j}$  is the intensity of the pixel at coordinates y = i, x = j, and n is the number of pixels across the square subaperture.

In the simplest case of a quad cell arrangement in which just 2x2 pixels of a sensor array or 4 individual sensors such as APDs are used this can be represented as

$$C_y = \frac{p_{1,0} + p_{1,1}}{p_{0,0} + p_{1,0} + p_{0,1} + p_{1,1}}; C_x = \frac{p_{0,1} + p_{1,1}}{p_{0,0} + p_{1,0} + p_{0,1} + p_{1,1}}.$$

(2.3)

Note that in these equations the weighting vector runs from 0 to n-1, where n is the number of pixels across a subaperture - often weighting vectors are used running from -n/2 to +n/2, such that a spot in the center has a centroid of 0. How the enumeration is chosen is somewhat arbitrary, although a system working with positive only numbers relaxes the requirements on the division operation, which can be of benefit for hardware implementations.

#### 2.2.2.4 The Pyramid Sensor

The Pyramid wavefront sensor measures the first spatial derivative of optical phase across a pupil, as with the Shack-Hartmann. However they use significantly different optics detailed by Ragazzoni [16] to produce four images, with co-located pixels in each image forming a 'virtual quad-cell' that may be centroided to yield the gradient for the corresponding location in the pupil. They have been shown to have superior performance when used in closed loop systems where photon noise is an issue - i.e. low light levels, compared to a Shack-Hartmann [17]. The Pyramid sensor has primarily seen use in astronomical AO systems although Ragazzoni et. al. have demonstrated the use of Pyramid sensors to

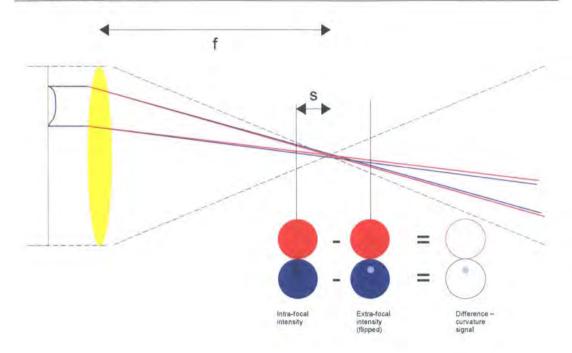

Figure 2.5: The Curvature Sensor - a flat wavefront, shown in red, is sent through a focus by a lens. If imaged in two planes equally spaced either side of the focus two images of uniform intensity are seen. When a distorted beam with some local curvature, shown in blue, is propagated the distortion causes an earlier focus for part of the beam, raising the signal in one imaged plane and lowering it in the other.

measuring aberrations in the human eye [18] and to running a closed loop AO system on the eye by Dainty et al[19].

#### 2.2.2.5 The Curvature Sensor

Unlike the SH and pyramid sensors a curvature sensor [20] measures the second derivative, or curvature, of the wavefront. The basic concept of the curvature sensor is illustrated in figure 2.5 - a flat wavefront, shown in red, is brought to a focus by a lens and is examined in two planes equally spaced either side of the focus. For a flat wavefront the illumination in these two planes will be uniform. When a curvature is introduced into part of the beam, as shown with the blue lines in the figure, this curvature shifts the focus axially, causing the intensity in one of the sensor planes to increase and a corresponding decrease in the other plane. The wavefront sensor signal is generated by subtracting images from the two planes to yield a difference frame, which is then divided into a series of regions, the intensity of each forms one element of the WFS vector.

As a curvature sensor measures the second derivative it is insensitive to the first derivative - the gradient - of the beam. A global gradient or tilt will cause the intra- and extrafocal images to translate in the two planes rather than modifying the intensity structure

within them, leading to registration errors between the beam and the sensor elements

leading to false signals. This can be avoided by using a separate system to remove global

tip/tilt or by monitoring the position of the pupils on the intra- and extra-focal images and

compensating in software. Such compensation however requires waiting for the complete

images to be acquired before the tilt can be correctly determined, introducing a significant

latency with adverse effects for high speed systems. Again, as with the Shack-Hartmann

sensor the requirements for a larger tilt range lead to a lowering of the speed at which the

sensor must run, again differentiating the design of open- and closed-loop systems.

#### 2.2.3 Wavefront Correction

The wavefront corrector (WFC) is a spatial light modulator (SLM) that may be a transmissive or reflective electro-optic element that modifies the phase of a light beam according to received control signals. The two main methods employed to achieve this are changing the refractive index of transmissive materials and moving the surface of a reflective material, i.e. deforming a mirror. First the operation of a generic corrector is examined below, followed by a summary of commonly used technologies, broken down into transmissive and reflective devices.

#### 2.2.3.1 Generic wavefront corrector

The optical phase of the WFC is represented by  $\theta_{dm}$  in figure 2.2. This phase is a result of control signals (typically analogue voltages) applied to the  $N_{dm}$  actuators on the device which are collectively referred to as the 'DM vector',  $\mathbf{dm}$ .

For an ideal wavefront corrector the response of each control channel is linear, and is orthogonal to the response of all other channels such that the phase response of the device may be represented as a linear superposition of the individual control channel response functions, i.e.

$$\theta_{dm} = \sum_{i=0}^{N_{dm}-1} dm_i R_i \tag{2.4}$$

where  $r_i$  is the phase response of the ith actuator and  $dm_i$  are the elements of dm.

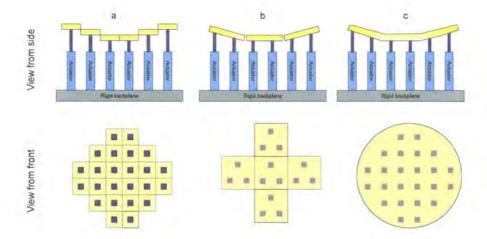

Figure 2.6: Types of push/pull actuated mirror - (a) shows a segmented piston only device that forms a stepwise approximation to a wavefront, (b) shows a device with three actuators per segment providing tip/tilt/piston control over each segment and (c) shows a continuous facesheet mirror

#### 2.2.3.2 Reflective devices

#### Position actuators

The most common forms of reflective devices consist of either a continuous or segmented sheet that is coated and polished for reflection on the front face, and bonded to push/pull actuators on the rear face. The three such forms a device may take are illustrated in figure 2.6.

The simplest device in (a) consists of a series of small tessellated mirror segments, each bonded to a single push/pull actuator. The individual segments can then be moved to create a step-wise approximation to the wavefront, with discontinuities at the segment edges. In practice this is a rarely seen form of device.

More common is that shown in (b) which again consists of a series of tessellated segments, but this time bonded to three actuators to give control of the tip/tilt and piston of each segment. An example of this type of mirror is the Thermotrex DM used in the NAOMI AO system[21].

Finally (c) shows the most common form of device, a continuous facesheet DM, in which a continuous sheet is bonded to and deformed by multiple actuators.

Various technologies are employed for the actuators depending on the required actuator

Figure 2.7: Types of force controlled mirror - in (a) an electrostatic potential is used to deform a thin membrane by means of attraction and in (b) the magnetic force is used to attract or repel mirrors bonded to a membrane

pitch, desired displacement range and temporal response etc. A typical example for a fine pitch device are the  $\mu DMs$  [22] from Boston Micromachines, which use parallel plate capacitors formed with MEMS technology to drive force actuators with a pitch of 60um and a stroke of 3.5um. For intermediate scales with a pitch on the order of 1cm, actuators exploiting the piezoelectric effect are a common choice and may be found on high quality astronomical AO DMs from companies such as Cilas and Xinetics. Typically the actuator pattern for such a mirror is either a square or hexagonal grid.

For larger scales such as devices intended to act as an adaptive secondary mirror in a telescope larger forces are required, leading to the use of physically bulky but effective magneto-strictive actuators, for example in the carbon fibre composite work from UCL[23].

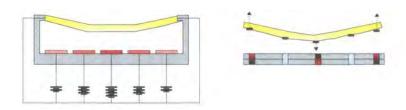

#### Flexure actuators

An alternative form of mirror is possible in which a thin Piezo material is bonded to the rear face of a thin reflecting membrane, these devices are normally called Bimorph mirrors. By applying a voltage across an area of piezo material it may be induced to expand or compress laterally compared to the reflecting membrane, producing a bending moment much like in a bimetallic strip. Typically radial actuator patters are seen on the Piezo wafer, leading to the use of a radially patterned curvature sensor (example is Subaru) or occasionally a radially patterned Shack-Hartmann as chosen to complement the radial mirror pattern the AO system for the Vulcan laser [24] at RAL. Some work has also been conducted on building such mirrors with a regular grid of actuators [25].

#### Force actuators

The second class of actuated mirrors consist of those in which the deformation of a continuous facesheet is controlled by a force rather rather than actuators. The most common forms of these are shown in figure 2.7.

Electrostatic membrane mirrors as shown in (a) are relatively inexpensive with a 37 actuator device from Flexible Optical B.V. (formerly OKO Technologies) retailing at euro 2000 and finding a place in many low-cost AO systems. In this mirror a thin reflecting membrane is clamped with radial tension by an insulating holder with the tension pulling the membrane flat. By applying various voltages to pixelated low resistance contacts under the membrane as illustrated in the figure the membrane is electro-statically attracted towards the contacts, deforming the surface. Due to the nature of the electrostatic force it is not possible to exert a push on the membrane, only a pull. Therefore it is necessary to operate the membrane from a bias position in which all contacts are at their mid-range voltage, causing a default shape of a parabola. By locally increasing or decreasing the voltage the surface may be moved in either direction. One benefit of this is that a global shift in actuator positions corresponds with a parabolic or focus term on the mirror rather than a piston, so a closed loop system with such a mirror is inherently unaffected by piston creep. A typical Flexible Optical DM is operated with a bias voltage of 100V producing a focus term of f=1200mm. A typical pitch for these devices is 1-3mm.

On a much larger scale the magnetic force may be used as illustrated in 2.7. (b). In this example a series of voice coils provide a magnetic force of controllable strength and polarity, repelling or attracting small magnets bonded to the rear surface of a thin reflecting membrane. This technology is used in various deformable secondary mirrors in large astronomical telescopes -for example on the VLT[26] and the LBT.

#### 2.2.3.3 Transmissive devices

Transmissive SLMs are typically based around liquid crystal (LC) technologies in which, rather than physically moving a reflective surface as with DMs, the optical path length is altered by varying the refractive index of a transmissive layer of birefringent LC material. Devices may be addressed either electronically or optically, and usually consist of a regular pixelated structure leading to a device similar in operation to the piston only DM from figure 2.6(a). Whilst the fundamental technology is transmissive a device with more than a few control channels is often reflective in operation, consisting of a transmissive LC layer with a mirror behind it causing it to act as a two pass device, and allowing the many electronic control signals to be connected through the rear of the device.

#### 2.2.4 Figure Reconstruction

Having both the means to measure the distortions present in the beam with the wavefront sensor, and a deformable mirror to correct these distortions, the final requirement is to connect the two such that the measurements from the sensor command the mirror surface, or figure.

As previously stated the wavefront sensor output **wfs** is not usually of the same form as the input to the deformable mirror, **dm** and so a transform is required.

If the assumptions from sections 2.2.3 and 2.2.3.1 that the WFS function and DM function are each linear and orthogonal are upheld then the reconstruction may take the form of a matrix operation:

$$dm = C.wfs (2.5)$$

where the DM vector **d** is derived by multiplying the wavefront vector(**wfs** with a transform matrix **C**, commonly referred to as the 'control matrix'

#### 2.2.4.1 Control Matrix Generation

If the behaviour of the WFS and the DM are well characterised and their relative alignment can be accurately determined then it is possible to generate the control matrix theoretically. However these requirements are in practice hard to achieve so an experimental method outlined below is often used to generate the control matrix.

If we take the model AO system for figure 2.1(b) but open the control loop and replace the aberrated input beam  $\theta_a$  with a flat reference beam  $\theta_0$  then the wavefront sensor will simply measure the phase of the DM such that

$$\mathbf{wfs} = WFS[\theta_{dm}] = WFS[DM[\mathbf{dm}]] \tag{2.6}$$

Given equation 2.4 this may be re-written as

$$\mathbf{wfs} = WFS[\theta_{\mathbf{dm}}] = \sum_{i=0}^{N_{dm}-1} d_i WFS[\mathbf{r_i}]$$

(2.7)

Now  $WFS[\mathbf{r_i}]$  is the WFS response to a unitary actuation on the ith DM channel, and is a constant for any given system configuration. It can be referred to as  $\mathbf{w_i}$  and may be theoretically calculated or experimentally measured. We now have the following for the response of the WFS to some DM command vector,  $\mathbf{dm}$ :

$$\mathbf{w} = \sum_{i=0}^{N_{dm}-1} d_i \mathbf{w_i} \tag{2.8}$$

Finally, this can be rewritten as a matrix equation:

$$\mathbf{wfs} = \mathbf{M}.\mathbf{dm} \tag{2.9}$$

where **M** is formally know as the *interaction matrix*. This matrix consists of  $N_{dm}$  rows, each of which consists of an  $N_{wfs}$  element vector - i.e. the ith row contains  $\mathbf{w_i}$ , the WFS unit response to the ith DM channel. This matrix is often referred to as the 'poke' matrix, due to the way DM channels are sequentially actuated, or poked, to produce this matrix.

The matrix may be visualised as

$$\mathbf{M} = \left(egin{array}{ccccc} w_{0,0} & w_{1,0} & \dots & w_{N_wfs-1,0} \ & w_{0,1} & w_{1,1} & \dots & dots \ & dots & dots & dots \ & & dots & dots \ & & & dots \ & w_{0,N_{dm}-1} & \dots & \dots & w_{N_wfs-1,N_{dm}-1} \ \end{array}

ight)$$

where w[i,j] is the response of the ith channel of the wavefront sensor to a wavefront produced by actuating the jth channel of the DM by one unit.

In a system where the responses of the mirror are spatially localised (such as a continuous facesheet mirror) and the wavefront sensor measures spatially localised quantities (such as a Shack-Hartmann or Curvature sensor) the resultant matrix will be relatively sparse and may present a diagonal structure - this is dependent on the arbitrary numbering of control and sensor channels. An example of such a matrix is shown in the results chapter, figure 6.3.

Referencing equation 2.9, we can multiply both sides by the pseudo-inverse of the interaction matrix to obtain:

$$\mathbf{M}^{-1}\mathbf{wfs} = \mathbf{M}\mathbf{M}^{-1}\mathbf{dm}. = \mathbf{dm} \tag{2.10}$$

This is the equation for figure reconstruction, and can be rewritten as follows, where  $C = M^{-1}$ . C is known as the control matrix.

$$dm = C.wfs (2.11)$$

Although the control matrix may be derived by the generalised inverse it is more common to use the singular valued decomposition (SVD) algorithm as this process generates

a set of arbitrary modes for the mirror that however resemble common optical distortions at lower order which are used to perform the inverse. By altering the prominence of these modes, especially the higher order ones it is possible to reduce the system sensitivity to noise etc.

#### 2.2.5 Wavefront Reconstruction

Using the theory outlined above, measurements from a derivative sensor such as a SH or Curvature are transformed directly into mirror drive commands, without the actual wavefront observed by the WFS ever being calculated. It may be desired to calculate the wavefront for either diagnostic purposes or use in a system monitoring GUI etc. This may be performed by running a second figure reconstruction for a virtual DM, the response functions of which are some set of orthogonal modes such as Zernike modes. The interaction and control matrices for such a virtual mirror may be calculated theoretically, and used to transform the wfs vector into modes, from which a phase map can be created.

#### 2.2.6 Modal Control

Modal control refers to a modification of the figure reconstruction in which the WFS vector is initially transformed into some set of intermediate modes (as with the wavefront reconstruction) as which may then be filtered etc. before being transformed into deformable mirror commands. This process may be useful to suppress high order modes that are poorly sensed by the WFS due to noise levels or aliasing etc., or to separate low order modes such as tilt and defocus for offloading to a separate low order mirror.

A further use is for coupling highly disparate sensors and correctors, for example when using a Shack-Hartmann sensor with a pixelated, piston only phase addressable element such as an optically addressed LC, the standard reconstructor approach breaks down, as the native modes of the corrector - piston - are unsensed by the WFS, meaning that it is not possible to directly generate an interaction matrix. For such a system an extra layer must be inserted such that a modified DM vector DM' addresses Zernike modes (for example) which are approximated into a piston only phase map for display on the LC. It is this modified vector that is used to generate the interaction matrix.

## 2.3 Temporal control

To fully correct an aberration, regardless of the temporal bandwidth of the aberration, an open loop system must operate with a gain of unity which is often not feasible due to non-linear and hysteresis effects in current DMs and non-linearity in wavefront sensors when required to operate over a high dynamic range. As such closed loop systems are used in the majority of cases, a gain of less than unity should be used, such that the system converges on the correct solution over several iterations allowing the closed loop to measure and adapt to these effects, whilst also reducing the dynamic range over which the WFS will typically operate improving uniformity.

Consequent to a gain of less than unity a closed loop system will require a faster sensing and DM update compared to an open loop system for any given temporal bandwidth aberrations, with the shorter times being required compensate for iteration, thus reducing the time available to integrate light and perform computation. Despite this most AO systems in practical use are closed loop systems.

In a closed loop system the WFS measures the deviation of the current mirror figure from the desired turbulence, so the dm commands derived from equation 2.11 refer to the change in mirror figure required to move from the current figure to one compensating the turbulence. Therefore the control system must include the current mirror figure in determination of the new one. This may be achieved by use of an integrator or PID control, e.g. with an integrator the mirror figure at time n+1 where n is the iteration number is given by

$$dm_{n+1} = \mathbf{dm}_n + \mathbf{wfs_n.C.} \tag{2.12}$$

### 2.4 System operation

Having examined the theory behind the essential components of an AO system the procedure for calibrating the system and closing the loop is presented below.

#### 2.4.1 System calibration

Before closed-loop operation can commence, the reference wavefront  $\theta_0$  must be measured and the control matrix must be generated. To measure the reference wavefront the deformable mirror is placed in its default flat, midrange position and a calibration

source replaces the usual light source into the system, providing a flat aberration free wavefront. The corresponding **WFS** vector is recorded, typically averaged over several hundred measurements spanning several seconds to eliminate low-order turbulence caused by air currents around the optical bench with this average forming  $\theta_0$ .

The interaction matrix is then generated by sequentially moving each mirror actuator from mid-range towards an extremity then back to mid-range with the corresponding WFS vectors being recorded at the extremity, again with averaging over several seconds. After subtracting the reference  $\theta_0$  from these readings the sequence of vectors forms the interaction matrix which is then conditioned and pseudo-inverted to give the control matrix.

The control matrix and reference wavefront are uploaded to the RTC, which once also informed of the desired gain is able to perform the various calculations summarised below and therefore close the loop.

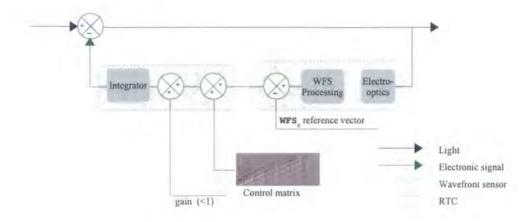

#### 2.4.2 Closed loop operation

Figure 2.8 draws together the various operations described earlier to show a complete breakdown in the stages of a closed loop AO system. These are (1) the measurement of some image encoding the properties of the wavefront, (2) the extraction of these properties from the image by signals processing, (3) the conversion of this sensor into a nulling mode by reference subtraction, (4) multiplication of this signal by the control matrix to transform the signal into mirror commands, (5) gain and integration for closed loop operation and (6) application of this signal to the DM.

#### 2.5 Static correction

Various sources of aberrations may exist in an AO system - perhaps imperfections in the quality of the optics themselves or in their alignment, or perhaps in the default surface of the deformable mirror due to such causes as the positional tolerance of the actuators, the mirror finish, or the differing responses of the various drive electronics.

These aberrations add their own distortions to the light propagated through the system and must be carefully managed to ensure that they do not impact the required performance. Whilst the simple model systems described earlier in this chapter only contain a few optical elements, a system designed for and constrained by a practical use often con-

Figure 2.8: Detailed breakdown of operations in an AO system

tains many more elements, for example the retinal imaging system described by Williams et. al.[27] contains 10 elements in the imaging path, each of which as the potential to impact on the system performance. Given the presence of a DM in the AO system it is possible to correct for these aberrations with a DM figure.

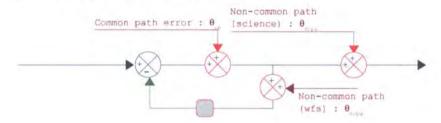

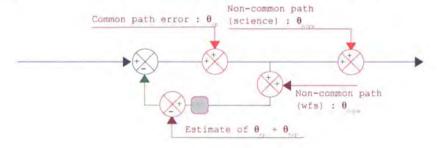

Static aberrations may be classified as one of two types according to their location in an AO system, as illustrated in figure 2.9(b) with 'common path' aberrations occurring before the separation of light for the wavefront sensor, and therefore being observed by both the wavefront sensing and science arms of the system, and 'non common path' errors which exist after this separation and affect only one path. Non-common path errors in the wavefront sensor arm are typically not an issue as these will be calibrated out in the reference wavefront sensor vector (section 2.4) and are not considered further, whereas errors in the science arm - which may be in optics external to the AO system - present more of a concern.

During the system calibration procedure outlined in section 2.4 the AO system is given a flat input wavefront reference,  $\theta_0 = \mathbf{0}$ . In the presence of common path aberrations the wavefront sensor measures a phase of  $\theta_0 + \theta_{cp} + \theta_{ncpw}$  and once the loop is closed will try and shape any incoming wavefront to this reference, so even if an input aberration is perfectly corrected, the common and non-common errors are still present after the DM.

These static aberrations may be mitigated by running the closed loop AO system with a default mirror figure that opposes the aberrations as shown in figure 2.9(c), achieved by adding the static corrective signal to the mirror drive signal.

## (a) Closed Loop AO system

## (b) Closed Loop AO system with static aberrations

## (c) Closed Loop AO system with static aberration and correction

Figure 2.9: Static aberrations in an AO system

If the primary source of static aberration is the poor 'default' surface of the DM correction may be achieved by examining the mirror with a phase shifting interferometer whilst using an iterative feedback algorithm such as that developed by Sivaramakrishnan and Openheimer [28] to flatten this figure. This method is suitable for the rapid optimisation of a system of many hundreds of channels with [28] demonstrating the flattening of a 241 channel device in 12 iterations. However this method requires the use of a phase shifting interferometer which typically costs many tens of thousands of pounds.

A more accommodating approach is to examine the final output of the system and determine some metric representing the quality (for example focal spot size; power in a box etc.) and to use an iterative method to maximise this by varying the optimising figure. The Simplex algorithm has been shown to be highly efficient at this task [29] and is, for example, used in the NAOMI AO system with an emphasis on non-common path correction[30]. A plethora of other optimisation methods are available such as genetic algorithms and stochastic gradient descent. In applications where the temporal bandwidth of the turbulence is very low an optimisation method may suffice as the only required control loop, replacing the WFS and full-blown RTC.

## Chapter 3

# FPGA/AO Theory

### 3.1 Introduction

As seen in chapter 2, a large quantity of calculations must be performed as a key component of an adaptive optics system. The forerunner of the modern AO system, fast steering tip/tilt correction systems, were first operated in the 1950s with simple analogue control systems. The first higher order AO system based around a WFS, figure reconstructor and DM was the ARPA real-time atmospheric compensator (RTAC), described in Hardy [31]. The requirements of this system exceeded digital technology which was still in its infancy, and thus an analogue control system was used with a 2D resistor network performing the matrix vector multiplication from the reconstructor. Such an analogue network has inherent speed benefits in that it is completely parallel. However such a system lacks the simple configurability and flexibility of digital systems, which have been rapidly adopted with a progression through systems using discrete multiply-accumulate (MAC) microchips through to central processing units (CPUs) and CPUs with specialist features for digital signals processing (CPU/DSPs). Whilst bringing flexibility and configurability compared to analogue systems, the poor ability of inherently serial systems to scale is leading to an examination of the use of field programmable gate array (FPGA) devices for future ELT AO systems and for use in second generation AO systems for current telescopes in the 8m-10m range. An FPGA is a two dimensional grid of parallel, configurable digital logic that combines the parallel execution of an analogue system with the flexibility of a programmable digital system. As seen in chapter 2, a large quantity of calculations must be performed as a key component of an adaptive optics system. The forerunner of the modern AO system, fast steering tip/tilt correction systems, were first operated

in the 1950s with simple analogue control systems. The first higher order AO system based around a WFS, figure reconstructor and DM was the ARPA real-time atmospheric compensator (RTAC), described in Hardy [31]. The requirements of this system exceeded digital technology which was still in its infancy, and thus an analogue control system was used with a 2D resistor network performing the matrix vector multiplication from the reconstructor. Such an analogue network has inherent speed benefits in that it is completely parallel. However such a system lacks the simple configurability and flexibility of digital systems, which have been rapidly adopted with a progression through systems using discrete multiply-accumulate (MAC) microchips through to central processing units (CPUs) and CPUs with specialist features for digital signals processing (CPU/DSPs). Whilst bringing flexibility and configurability compared to analogue systems, the poor ability of inherently serial systems to scale is leading to an examination of the use of field programmable gate array (FPGA) devices for future ELT AO systems and for use in second generation AO systems for current telescopes in the 8m-10m range. An FPGA is a two dimensional grid of parallel, configurable digital logic that combines the parallel execution of an analogue system with the flexibility of a programmable digital system.

Work to date on low cost AO has focused on the use of commodity personal computer (PC) hardware, with the PC's CPU performing the calculations, for example in systems by the NOAO[12] and TNG[32] observatories, and on the use of reasonably inexpensive DSP hardware assisted by a common PC, for example in the LOCADO system[13].

## 3.2 Architecture of Modern Devices

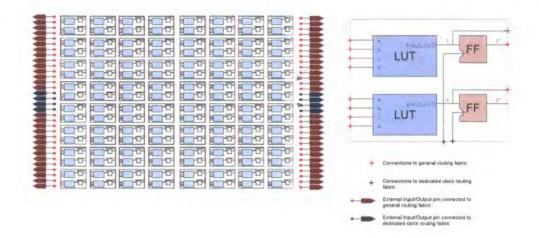

In this section we focus on the architecture of FPGA devices from Xilinx, although broadly speaking devices from other manufacturers such as Altera are comparable. The foundation of all modern FPGA devices from Xilinx was laid with the XC4000 series FPGA devices from 1999[33]. This device consisted off a 2 dimensional array of configurable logic blocks or CLBs as illustrated in figure 3.1. Each CLB consists of two independent 4-input look up tables that may be configured to produce any arbitrary function of between 1 and 4 inputs. These LUTs are asynchronous with their output stabilising some short time after the inputs stabilise. To convert the LUT into a synchronous element the output may be registered by a flip-flop (FF).

The 2D array of these CLBs is immersed in a configurable routing fabric such that outputs of one CLB may be connected to the inputs of another to cascade these simple 4-

Figure 3.1: Basic structure of Xilinx devices - illustration showing an FPGA as a 2d grid of asynchronous look-up tables (LUTs) and synchronous flip-flops. By programming the contents of the LUTs and the routing between IO pins, LUTs and FFs complex, custom digital logic systems may be created.

input logic functions and registers to build more complex functions, ranging from a simple counter to full blown signals processing systems. The device also offers input/output pins (IO pins) that include programmable logic to control their signalling standards and related behaviour. Finally there are dedicated pins and routing nets for connecting clock signals, as these have a higher fan-out than general logic and benefit from special consideration. A key feature of the LUTs in the Xilinx family is that they are implemented as a 16x1 RAM that is typically programmed when the device is configured, but may be operated within the FPGA design as a 16x1 RAM, with many LUTS being chained to create wider or deeper RAMs as necessary, this feature is described as distributed ram or SelectRAM.

Xilinx continued to produce new FPGA families with the same basic LUT/FF structure over several generations as shown in table 3.2 - However the Virtex-5 has changed the fundamental structure of the LUTs with a move to 6-inputs over 4. Until this change each successive generation was marked by an increase in the number of CLBs in a device, increases in the maximum speed at which the logic and routing fabric may operate and the addition of new features.

The Virtex devices represented an increase in LUT/FF count over the XC4000 series. The family also brought the addition of dedicated RAM to the FPGA. Whilst many LUTs may be chained to create RAM, part of the array of CLBs may be replaced by a dedicated RAM store built not from CLBs but directly on microchip offering higher

storage densities and faster speeds. These memories introduced into the Virtex family are called BlockRAM, and have a size of 4096 bits that may be configured as 4096x1, 2048x2, 1024x4, 2048x4, 1024x8 or 512x16. A key feature of these BlockRAMs is that they are true dual port memories, offering two independent read/write ports to the same memory store - particularly useful for a system where real time algorithms and configuration interfaces must share access to a memory.

The Virtex-II family saw BlockRAMs increase in size form 512x16 to 1024x18 with the depth being doubled and two extra bits added to the words, nominally for parity storage but free for any use. Following the precedent of replacing some general logic fabric with dedicated hardware set by the Virtex devices the Virtex-II family adds dedicated single clock cycle multipliers, with one multiplier for each BlockRAM. The multipliers accept two 18 bit signed integers and output a 35 bit signed integer. The prevalence of a large number of independent RAMs and dedicated multipliers allows for highly efficient parallel implementations of algorithms, particularly vector and matrix mathematics.

The Virtex-IIPro range saw the addition of features less useful for low cost embedded control such as multiple dedicated 3.125GBits/sec serial transceivers within the chip and dedicated PowerPC 405 CPU cores to enable complete computer systems to be built within the FPGA. This trend has continued through the Virtex 4 and 5 devices with multiple gigabit ethernet transceivers, 3-10Gb/sec serial transceivers and similar features being included. The Virtex-4 family offers three variants where the ratio of LUTs/FFs to dedicated multipliers and BlockRAM is varied to offer logic orientated devices for general use (LX), an abundance of multipliers for DSP applications (SX) and extra BlockRAM (FX).

The Virtex-5 has introduced changes to the dedicated multipliers replacing them with broader featured DSP blocks and also fundamentally altering the basic CLB structure. However these changes are not reflected in the low cost Spartan family targeted in this work so are not explored further.

The Spartan family of devices are a lower cost range of FPGAs from Xilinx with a decreased range of features - particularly in terms of lack of support for complicated IO standards and faster speeds - compared to the Virtex devices from which they derive. To date their has been a strong correspondence between generations of Virtex and Spartan devices, with the Spartan 3 FPGA having the same CLB structure, and BlockRAM and Multiplier configurations as the Virtex-II family.

| Family      | Device    | LUTs + FFs | BlockRAM (Kb) | SelectRAM (Kb) | Multipliers |

|-------------|-----------|------------|---------------|----------------|-------------|

| XC4000      | XC4085XL  | 6272       | 0             | 98             | 0           |

| Spartan     |           | 1568       | 0             | 24.5           | 0           |

| Virtex      | XCV1000   | 24576      | 128           | 384            | 0           |

| Spartan-II  | XC2S300E  | 6144       | 64            | 96             | 0           |

| Virtex-II   | XC2V8000  | 46952      | 3024          | 1456           | 168         |

| Spartan-3   | XC3S5000  | 33280      | 1872          | 520            | 104         |

| Virtex-4 LX | XC4VLX200 | 89088      | 6048          | 1392           | 96          |

| Virtex-4 FX | XC4VFX140 | 64512      | 9936          | 1008           | 192         |

| Virtex-4 SX | XC4VSX55  | 24576      | 7568          | 384            | 512         |

Table 3.1: Summary of resources for largest device in each Xilinx FPGA family, grouped by device generation

Table 3.2 sumarises the capacity of the largest device from each of these families.

# 3.3 Programming model and tool flow

As with CPU systems there are many levels at which an FPGA may be programmed, for example at the lowest level each individual LUT and FF and their interconnection may be configured manually to produce some functionality. This is somewhat analogous to programming a CPU in assembler, and offers the most control but with an unpractical amount for work for more than the smallest operations. Further tool support for manual control over routing in FPGAs is normally lacking.